# 7-bit Phase Shifter using SiGe BiCMOS Technology for X-band Phased Array Applications

by

Abdurrahman Burak

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabancı University

Summer, 2017

7-bit Phase Shifter using SiGe BiCMOS Technology

for X-band Phased Array Applications

APPROVED BY:

Prof. Dr. Yaşar GÜRBÜZ (Thesis Supervisor)

Assoc. Prof. Dr. Meriç ÖZÇAN

Asst. Prof. Dr. Erdinç ÖZTÜRK

### DATE OF APPROVAL: 01/08/2017

#### Acknowledgements

First and foremost, I would like to thank my advisor Prof. Yaşar Gürbüz, for his invaluable advice and support during my undergraduate and master's studies in Sabanci University. I would not be at this stage of my career without his support and endless motivation.

I also would like to thank Assoc Prof. Meriç Özcan and Asst. Prof. Erdinç Öztürk for taking their precious time to serve in my thesis committee and for their valuable comments and feedback.

I am very thankful to my friends and colleagues, Eşref Turkmen and Ilker Kalyoncu for always helping me along the way our research, their patience answer to my endless questions. I also would like to thank my companions in the SU Microsystems group, Dr. Melik Yazıcı, Dr. Ömer Ceylan, Alper Güner, Murat Davulcu, Emre Can Durmaz, Elif Gül Özkan Arsoy, Atia Shafique, Arman Galioğlu, Can Çalışkan, and Shahbaz Abbasi for creating such a friendly working environment, including the past members Barbaros Çetindoğan, Berktuğ Üstündağ, and Emre Özeren. I am happy to be a part of this group. I thank the laboratory stuff Ali Kasal and past member Mehmet Doğan for their help and support.

In addition, thanks to Ahmet Can, Alican, Didem, Emre, Metin, Onur, Ozan, Recep and many others for your dear friendship during my college and high school years.

Finally, but most importantly, I would like to thank my parents Huriye and Erdal, my sister Betül, and my fiancee Betül for their unconditional love and endless support. I would not come that far without their support and the sacrifices they made.

### 7-bit Phase Shifter using SiGe BiCMOS Technology for X-band Phased Array Applications

Abdurrahman Burak EE, Master's Thesis, 2017 Thesis Supervisor: Prof. Dr. Yaşar GÜRBÜZ

Keywords: Phased Array RADAR, Phase Shifter, T/R module, SiGe BiCMOS, X-Band Integrated Circuits.

#### Abstract

Phase array T/R modules achieve high performance with III-V technologies. However, the cost of III-V technologies is high. Recent developments in SiGe BiC-MOS technology show us that III-V technology can be replaced with SiGe BiCMOS. Moreover, thanks to the integration of the CMOS, digitally controlled T/R modules can be realized with that technology. Power dissipation, area, and integration complexity can be reduced with SiGe BiCMOS technology. Also, the number of radiating elements and the cost of T/R module can be reduced with phase shifters with high phase resolution. In the light of these trends, this thesis presents a 7-bit low insertion-loss SiGe X-band (8-12 GHz) passive phase shifter, realized in IHP  $0.25-\mu$ m SiGe BiCMOS process.

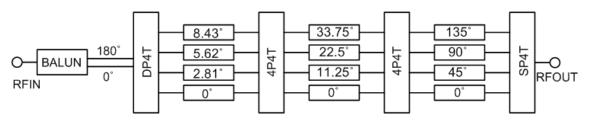

The phase shifter is based on high-pass/low-pass filter topology with a new proposed switching technique. This technique decreases the number of series switch by dividing each phase into 4 arms instead of two arms. Also, in this technique, instead of using two single pole switches consecutively, multiple pole switches are realized. Thanks to the IHP SiGe BiCMOS technology, isolated NMOSs are used which improve insertion-loss of the phase shifter. The overall phase shifter is composed of BALUN, SP4T, DP4T, 4P4Ts, and phase blocks to create a phase shift for achieving 7-bit phase resolution. The return loss of each state is better than 10 dB and the phase shifter has an average of 14.5 dB insertion loss. Minimum 1° RMS phase error is obtained at 10 GHz. RMS phase error is better than 6° at 9-11 GHz band. The phase shifter occupies an area of 6 mm<sup>2</sup> and it has no DC power consumption.

The thesis also summarizes the work that was contributed as part of the complete TR Module generation. These include active and passive gain equalizers that are utilized in the Module to generate desired slope in the receiver / transmitter chain.

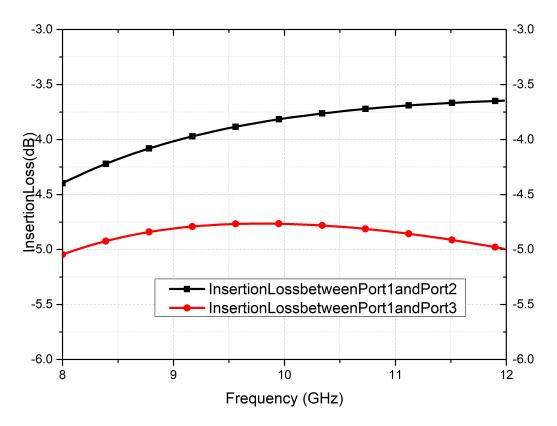

#### X-band Faz Dizinleri için SiGe BiCMOS 7-bit Faz Kaydırıcı

Abdurrahman Burak EE, Yüksek Lisans Tezi, 2017 Tez Danışmanı: Prof. Dr. Yaşar GÜRBÜZ

#### Anahtar Kelimeler: Faz Dizinli RADAR, Faz Kaydırıcı, Alıcı/Verici Modülü, SiGe BiCMOS, X-Bandında entegre devre.

#### Özet

III-V teknolojisi ile faz dizinli alıcı/verici (T/R) modüllerinden yüksek performans elde edilir. Buna rağmen, III-V teknolojilerinin maliyeti yüksektir. SiGe BiCMOS teknolojisindeki son gelişmeler, III-V teknolojisinin SiGe BiCMOS ile yer değiştirebileceğini göstermektedir. Dahası, CMOS'un entegrasyonu sayesinde dijital olarak kontrol edilebilir T / R modüller bu teknoloji ile gerçekleştirilebilir. SiGe BiCMOS teknolojisiyle güç dağıtımı, alanı ve entegrasyon karmaşıklığı azaltılabilir. Üstelik, yüksek bit çözünürlüklü faz kaydırıcılar ile radyasyonlu elemanların sayısı ve T/R modüllerin maliyeti azaltılabilir. Bu eğilimler ışığında, bu tezde, 7 bitlik düşük araya yerleştirme kaybına sahip SiGe BiCMOS teknolojisinde gerçekleştirilmiş Xband(8-12GHz) pasif faz kaydarıcı sunulmaktadır.

Faz kaydırıcı, yeni önerilen anahtarlama tekniğiyle beraber yüksek geçiren / düşük geçiren süzgeç topolojisine dayanmaktadır. Bu teknik, her fazı ikiye bölmek yerine dörde bölerek seri switch sayısını azaltmaktadır. Dahası, bu teknikte, ard arda tek bitişli anahtarlar kullanmak yerine çok bitişli anahatlar gerçekleştirilmiştir. IHP SiGe BiCMOS teknolojisi sayesinde, faz kaydırıcının araya yerleştirme kaybını geliştiren izole NMOSlar kullanıldı. Bu method faz kaydırıcının araya yerleştirme kaybını geliştirmektedir. 7-bit faz çözünürlüğünü elde etmek için faz kaydırıcı BALUN, SP4T, DP4T, 4P4T ve faz bloklarından oluşmaktadır. Her durumun geri dönüş kaybı 10 dB'den daha iyi, ve faz değiştirici ortalama 14.5 dB araya yerleştirme kaybına sahiptir. 10 GHz'de minimum RMS faz hatası 1 ° olarak elde edilmiştir. RMS faz hatası, 9-11 GHz bantında 6 ° ' den daha iyidir. Güç tüketmeyen faz kaydırıcı 6 mm<sup>2</sup> alana sahiptir.

Tezde, tamamlanmış T/R modül üretimine katkı sağlayan çalışmaları da özetlemektedir. Bunlar, alıcı / verici zincirinde istenen eğimi oluşturmak için modülde kullanılan aktif ve pasif kazanç edengeleyicileri içerir.

## Contents

| A        | ckno         | wledgements                                                                                                                                                   | iii             |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| A        | bstra        | act                                                                                                                                                           | iv              |

| Li       | ist of       | Figures                                                                                                                                                       | ix              |

| Li       | ist of       | Tables                                                                                                                                                        | x               |

| Li       | ist of       | Abbreviations                                                                                                                                                 | xii             |

| 1        | Intr         | roduction                                                                                                                                                     | 1               |

| •        | 1.1          | A Brief History of Radar                                                                                                                                      |                 |

|          | $1.1 \\ 1.2$ | Phased Array Radars                                                                                                                                           |                 |

|          | 1.2          | Phased Array Operating Principles                                                                                                                             |                 |

|          | 1.0          | 1.3.1 Time Delay vs Phase Shift                                                                                                                               |                 |

|          |              | 1.3.2 Beam Steering and Array Factor                                                                                                                          |                 |

|          |              | 1.3.3 Phased Array as a Receiver and Transmitter                                                                                                              |                 |

|          | 1.4          | Phased Array Architectures                                                                                                                                    |                 |

|          | 1.1          | 1.4.1 Passive Phased Arrays                                                                                                                                   |                 |

|          |              | 1.4.2 Active Phased Arrays                                                                                                                                    |                 |

|          |              | 1.4.3 RF phase shifting(All RF Transmit/Receive)                                                                                                              |                 |

|          |              | 1.4.4 IF phase shifting                                                                                                                                       |                 |

|          |              | 1.4.5 LO phase shifting                                                                                                                                       |                 |

|          |              | 1.4.6 Digital beam forming                                                                                                                                    |                 |

|          | 1.5          | All RF Transmit/Receive Module                                                                                                                                |                 |

|          | 1.6          | SiGe BiCMOS Technology                                                                                                                                        |                 |

|          | 1.7          | Motivation                                                                                                                                                    |                 |

|          | 1.8          | Organization                                                                                                                                                  | 17              |

| 0        | Б            |                                                                                                                                                               | 10              |

| <b>2</b> |              | idamentals of Phase Shifters         Introduction                                                                                                             | 19              |

|          | 2.1          |                                                                                                                                                               |                 |

|          | 2.2          | A Brief Description of Phase Shifter                                                                                                                          |                 |

|          | $2.3 \\ 2.4$ |                                                                                                                                                               |                 |

|          | 2.4          | Important Performance Metrics of the Phase Shifter                                                                                                            | 20              |

|          |              | 2.4.1RMS Phase Error                                                                                                                                          |                 |

|          |              | 2.4.2RMS Amplitude Error                                                                                                                                      |                 |

|          | 2.5          | Phase Shifter Topologies                                                                                                                                      |                 |

|          | 2.0          | 2.5.1       Switched-Line Phase Shifter                                                                                                                       |                 |

|          |              | 2.5.1 Switched-Line Phase Shifter                                                                                                                             |                 |

|          |              | 2.5.2 Loaded-Line Thase Shifter                                                                                                                               | $\frac{22}{23}$ |

|          |              | 2.5.4 Switched-Filter Phase Shifter                                                                                                                           | $\frac{23}{24}$ |

|          |              | 2.5.5 Vector Modulator Phase Shifter                                                                                                                          |                 |

|          | 2.6          | Quantization Loss of the Phase Shifter                                                                                                                        |                 |

|          | 2.0          | $\forall uanuaauon loss or one rase sinner \dots \dots$ | 20              |

| 3  | A 7        | -bit X-band Switched Filter Phase Shifter in SiGe BiCMOS                                                       | <b>27</b> |

|----|------------|----------------------------------------------------------------------------------------------------------------|-----------|

|    | 3.1        | Introduction                                                                                                   | 27        |

|    | 3.2        | Phase Shifter Requirements                                                                                     | 27        |

|    | 3.3        | High-Pass and Low-Pass Pi and Tee Networks                                                                     | 27        |

|    |            | 3.3.1 High-pass Tee Network                                                                                    | 29        |

|    |            | 3.3.2 Low-pass Tee Network                                                                                     | 30        |

|    |            | 3.3.3 High-pass Pi Network                                                                                     | 31        |

|    |            | 3.3.4 Low-pass Pi Network                                                                                      | 31        |

|    | 3.4        | Circuit Design                                                                                                 | 32        |

|    |            | 3.4.1 Ideal Lumped Element Values of 7-bit Phase Shifter                                                       | 35        |

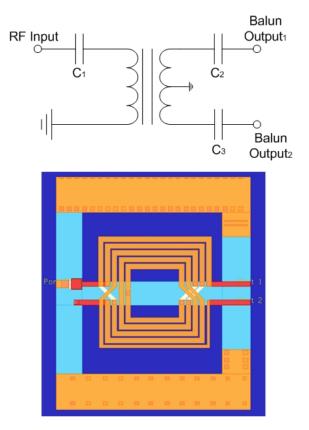

|    |            | 3.4.2 BALUN Design                                                                                             | 36        |

|    |            | 3.4.3 Phase Values of Each Arm and Ideal Component Values                                                      | 38        |

|    |            | 3.4.4 SP4T Design                                                                                              | 38        |

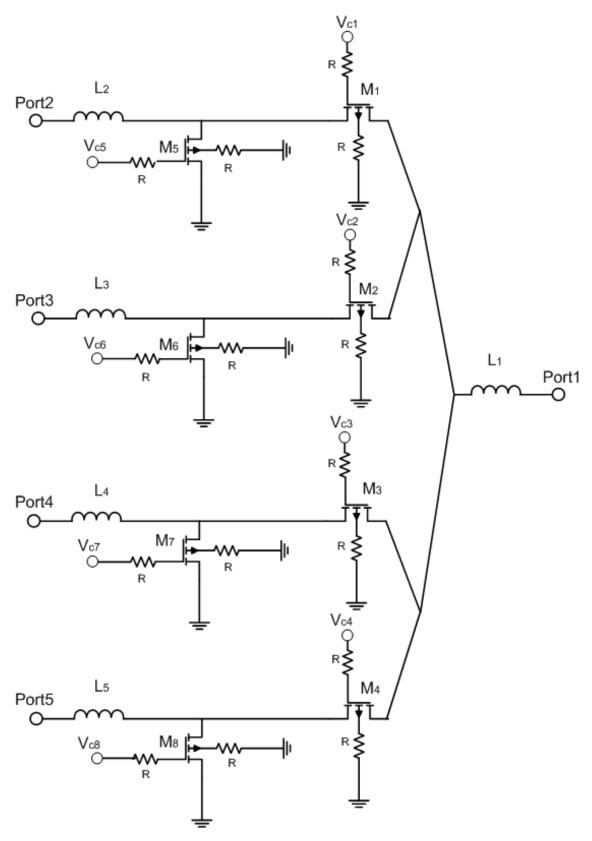

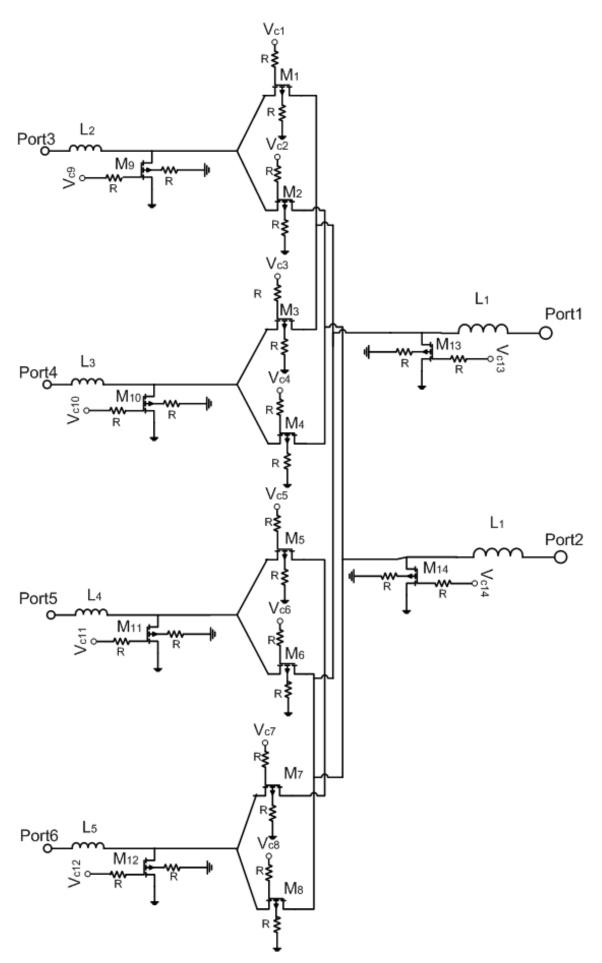

|    |            | 3.4.5 DP4T Design                                                                                              | 42        |

|    |            | 3.4.6 4P4T Design                                                                                              | 43        |

|    | 3.5        | Simulation Results of the Phase Shifter                                                                        | 50        |

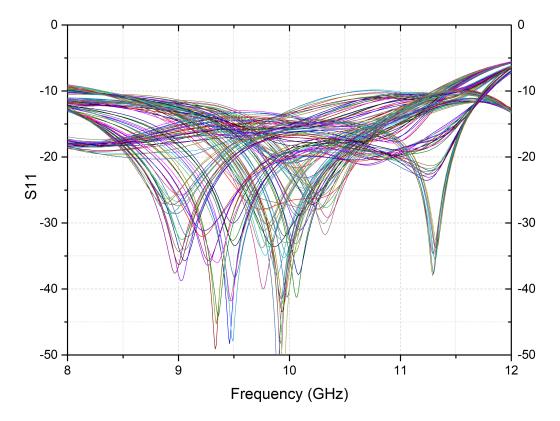

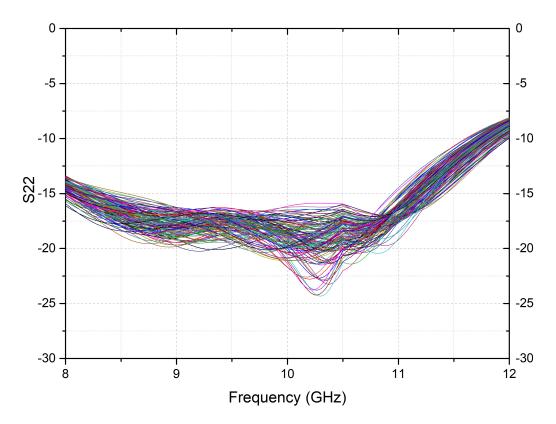

|    |            | 3.5.1 Return Loss                                                                                              | 50        |

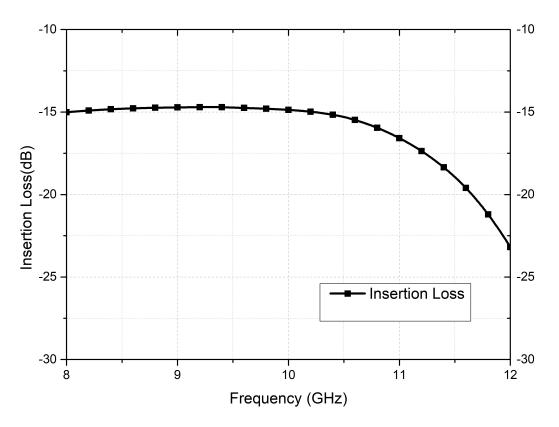

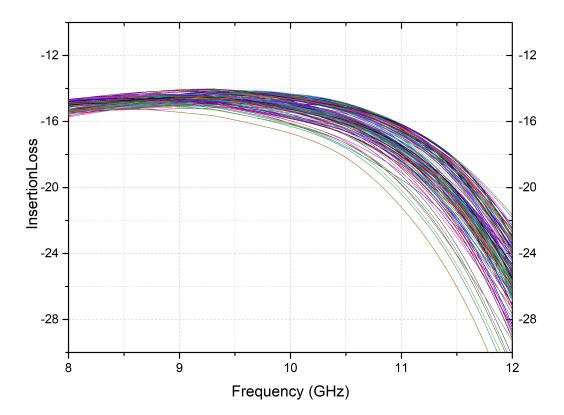

|    |            | 3.5.2 Insertion Loss $\ldots$ | 51        |

|    |            | 3.5.3 Phase and Amplitude Performance                                                                          | 51        |

|    | 3.6        | Comparison                                                                                                     | 55        |

| 4  | Dom        | formance Summary of Other Building Blocks of T/R Module                                                        |           |

| 4  |            | uding Passive and Active Gain-Equalizers                                                                       | 57        |

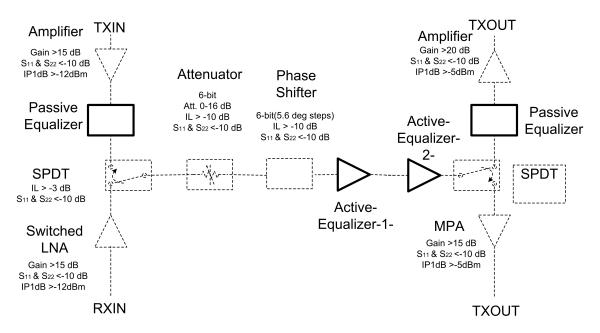

|    | 4.1        | Introduction                                                                                                   | 57        |

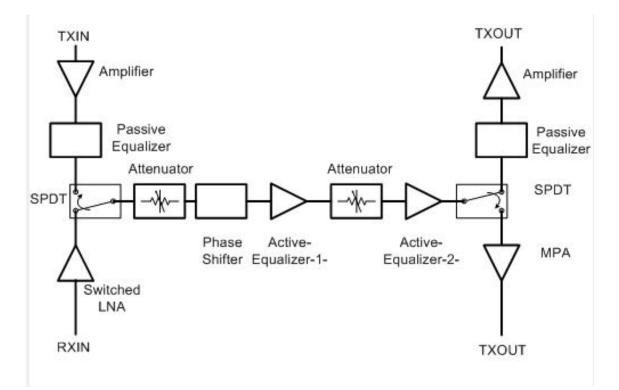

|    | 4.2        | System and Previously Designed Sub-Blocks                                                                      |           |

|    | 1.2        | 4.2.1 A 6-bit Active Phase Shifter                                                                             |           |

|    |            | 4.2.2 A 6-bit Attenuator                                                                                       |           |

|    |            | 4.2.3 CMOS SPDT Switches                                                                                       |           |

|    |            | 4.2.4 Switched LNA                                                                                             |           |

|    |            | 4.2.5 MPAs                                                                                                     |           |

|    |            | 4.2.6 Driver Amplifier                                                                                         | 60        |

|    |            | 4.2.7 Equalizer Requirements                                                                                   | 61        |

|    | 4.3        | Active and Passive Equalizers                                                                                  | 62        |

|    |            | 4.3.1 A Conventional Type Passive Gain-Equalizer                                                               | 64        |

|    |            | 4.3.2 A New Compact Passive Gain-Equalizer                                                                     | 65        |

|    |            | 4.3.3 Passive Gain-Equalizers for T/R Module                                                                   | 68        |

|    |            | 4.3.4 Active Gain-Equalizers for T/R Module                                                                    | 72        |

|    | 4.4        | T/R Module overall gain behavior                                                                               | 74        |

| -  | C          |                                                                                                                |           |

| 5  |            | clusion & Future Work                                                                                          | 76<br>76  |

|    | 5.1<br>5.2 | Summary of Work                                                                                                | 76<br>76  |

|    | 5.2        | Future Work                                                                                                    | 76        |

| Re | efere      | nces                                                                                                           | 80        |

## List of Figures

| 1              | AN/TPS-75 [1] (a) and AN/FPS-132 [2] (b) phased array radars                  | 3  |

|----------------|-------------------------------------------------------------------------------|----|

| 2              | Basic receiver block diagram of a phased array system                         | 3  |

| 3              | Normalized array pattern of a linear array with $\lambda/2$ spacing for (red) |    |

|                | N=8 (magenta) N=16 (blue) N=32 antenna elements                               | 6  |

| 4              | Block diagram of passive phased array                                         | 8  |

| 5              | Passive Phased array example: AN/FPQ-16 [3]                                   | 8  |

| 6              | Block diagram of active phased array                                          | 9  |

| $\overline{7}$ | Active phased array example: SAMPSON[4]                                       | 9  |

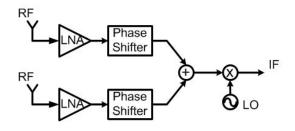

| 8              | RF phase shifting Phased array architectures                                  | 10 |

| 9              | IF phase shifting Phased array architectures                                  | 11 |

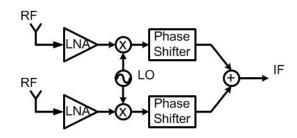

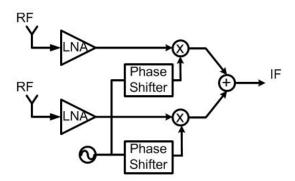

| 10             | LO phase shifting Phased array architectures                                  | 11 |

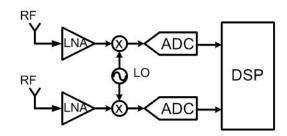

| 11             | Digital beam forming Phased array architectures                               | 12 |

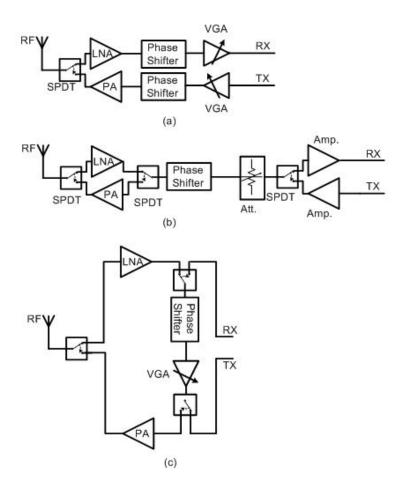

| 12             | Several system level architectures for RF transmit/receive modules            | 13 |

| 13             | $(f_T)$ and $(f_{MAX})$ for different SiGe HBT technologies. [5]              | 15 |

| 14             | SiGe X-band all-RF T/R module block diagram and component spec-               |    |

|                | ifications                                                                    | 17 |

| 15             | General diagram of the bit of the switched-line phase shifter                 | 23 |

| 16             | General diagram of the bit of the loaded-line phase shifter                   | 23 |

| 17             | General diagram of the bit of the reflection-type phase shifter               | 24 |

| 18             | Switched-filter topology with tee networks                                    | 24 |

| 19             | Tee and pi filter networks                                                    | 25 |

| 20             | Block diagram of a typical vector sum type phase shifter                      | 26 |

| 21             | Required antenna number to reach the same RMS side-lobe level with            |    |

|                | different phase resolutions $[6]$                                             | 28 |

| 22             | Schematic view of high-pass/low pass type phase shifter                       | 33 |

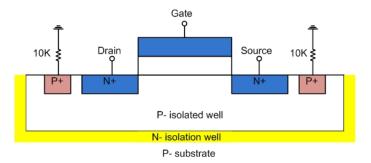

| 23             | Cross section of typical isolated NMOS transistor and body floating           |    |

|                | technique                                                                     | 34 |

| 24             | Block diagram of 7-bit passive phase shifter                                  | 34 |

| 25             | Schematic and Layout of the Transformer                                       | 36 |

| 26             | Simulation result of the insertion-loss between each output and input         | 37 |

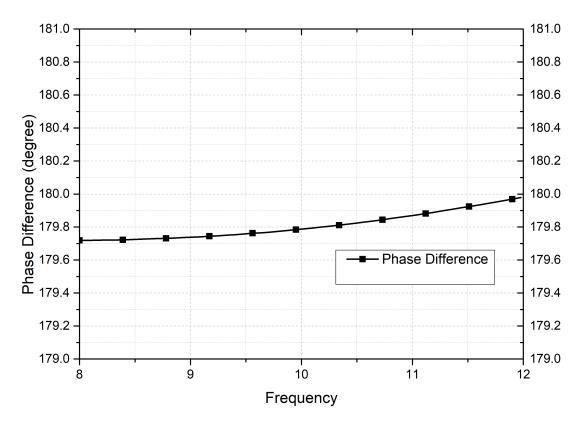

| 27             | Simulation result of the phase difference between each output of the          |    |

|                | transformer                                                                   | 37 |

| 28             | Schematic of the SP4T                                                         | 40 |

| 29             | Simulation result of the isolation of the SP4T                                | 41 |

| 30             | Simulation result of the insertion-loss of the SP4T                           | 41 |

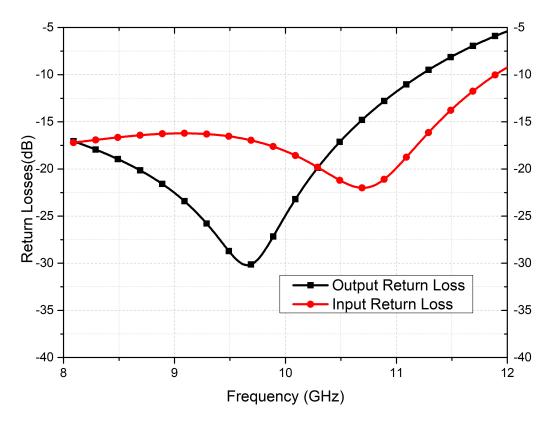

| 31             | Simulation result of the return losses of the SP4T                            | 42 |

| 32             | Schematic of the DP4T                                                         | 44 |

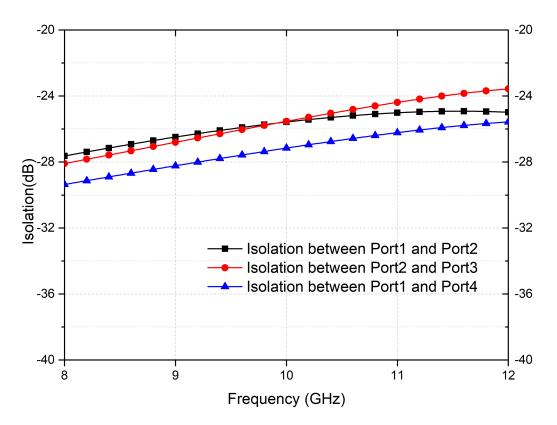

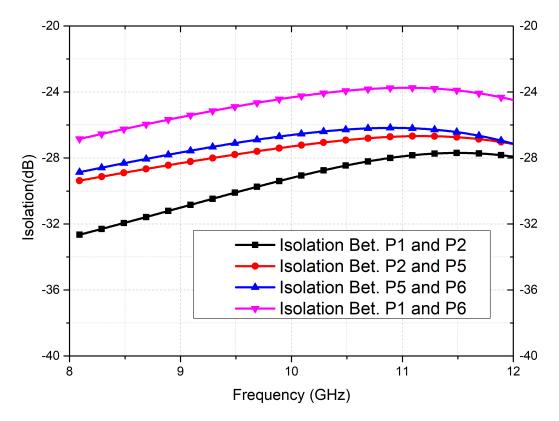

| 33             | Simulation result of the isolation of the DP4T                                | 45 |

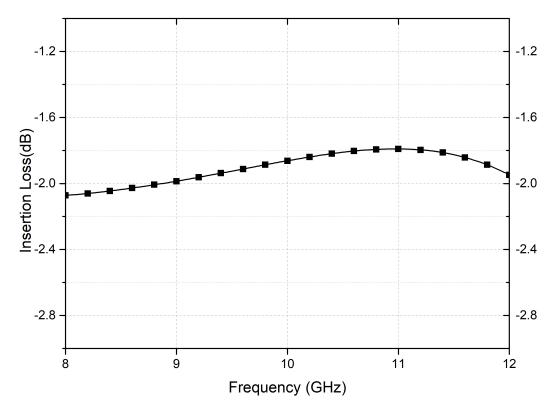

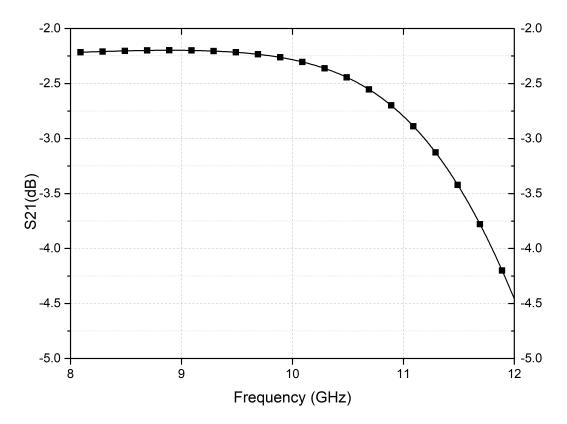

| 34             | Simulation result of the insertion-loss of the DP4T                           | 45 |

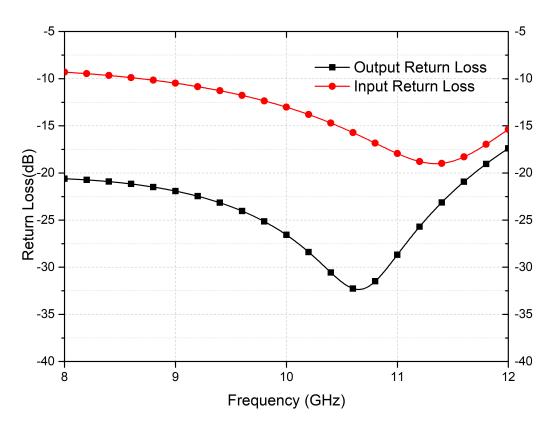

| 35             | Simulation result of the return losses of the DP4T                            | 46 |

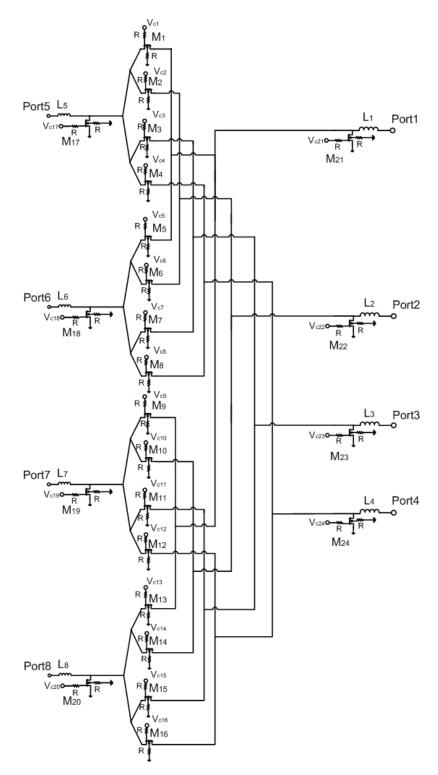

| 36             | Schematic of the 4P4T                                                         | 47 |

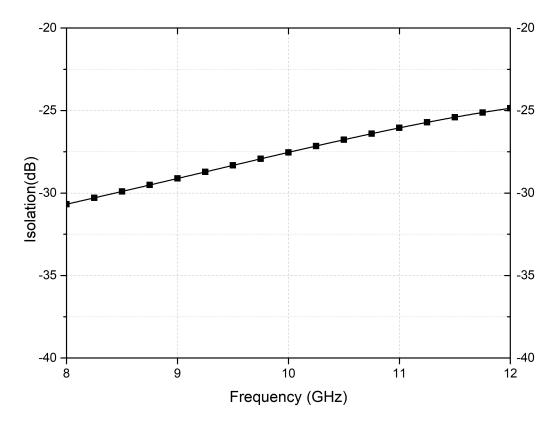

| 37             | Simulation result of the isolation of the 4P4T                                | 48 |

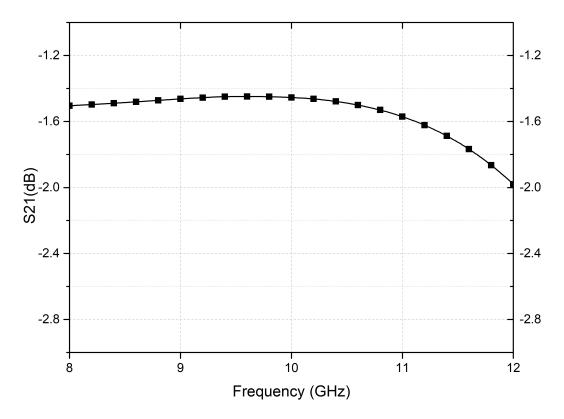

| 38             | Simulation result of the insertion-loss of the 4P4T                           | 48 |

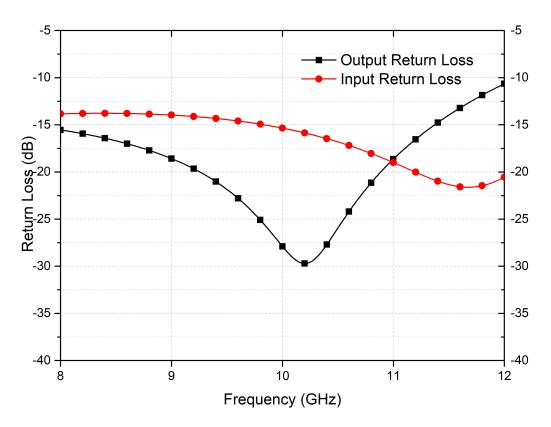

| 39             | Simulation result of the return losses of the 4P4T                            | 49 |

| 40             | Simulation result of the input return losses of all states of the designed    | -  |

|                | phase shifter                                                                 | 50 |

|                |                                                                               |    |

| 41       | Simulation result of the output return losses of all states of the de-       |            |

|----------|------------------------------------------------------------------------------|------------|

|          | signed phase shifter                                                         | 51         |

| 42       | Simulation result of the insertion-loss of the designed phase shifter        | 52         |

| 43       | Simulation result of the amplitude response of each state of the de-         |            |

|          | signed phase shifter                                                         | 53         |

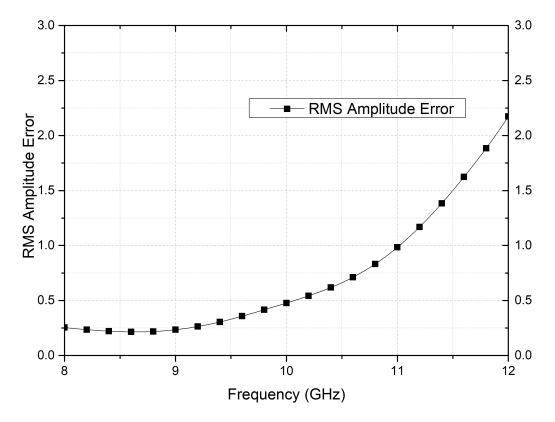

| 44       | Simulation result of the RMS amplitude error of the designed phase           | -          |

|          | shifter                                                                      | 53         |

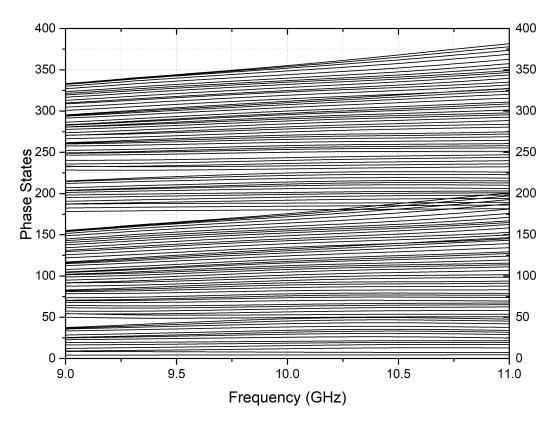

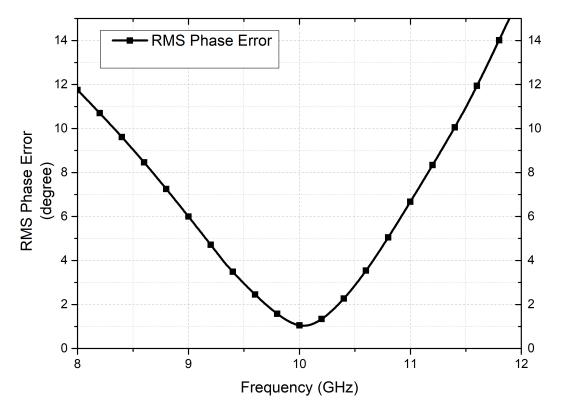

| 45       | Simulation result of the phase states of the designed phase shifter          | 54         |

| 46       | Simulation result of the RMS phase error of the designed phase shifter       | 54         |

| 47       | SiGe X-band all-RF T/R module block diagram and component spec-              | -          |

| 10       | ifications                                                                   | 58         |

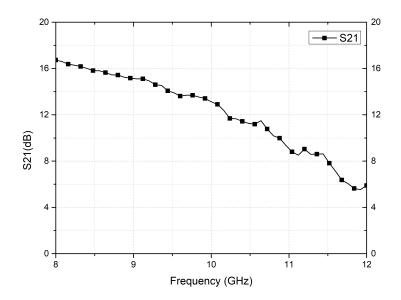

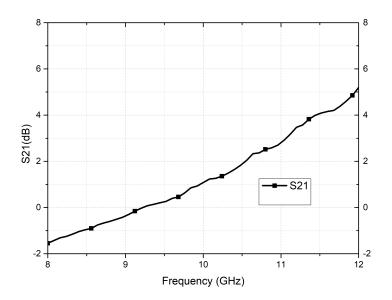

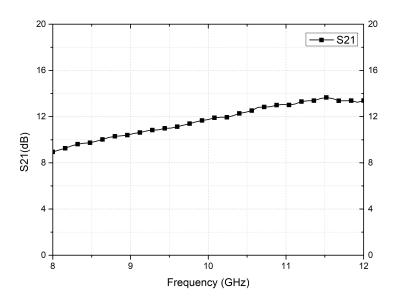

| 48       | Overall S21 result of the designed $T/R$ module blocks for RX chain .        | 61         |

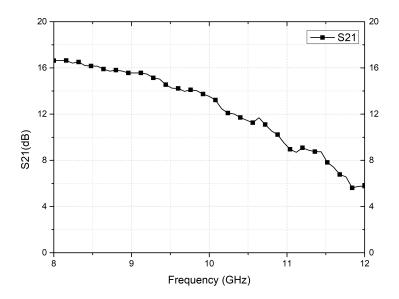

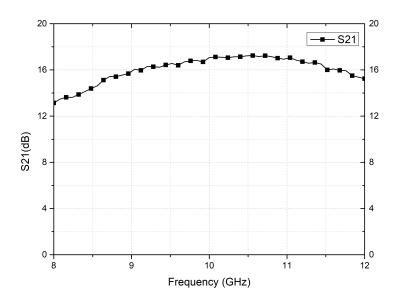

| 49<br>50 | Overall S21 result of the designed $T/R$ module blocks for TX chain .        | 61         |

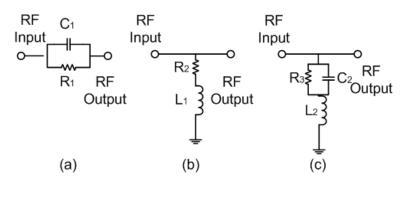

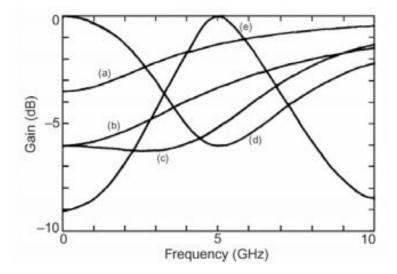

| 50<br>51 | Examples of the schematic of passive gain-equalizers                         | 63<br>63   |

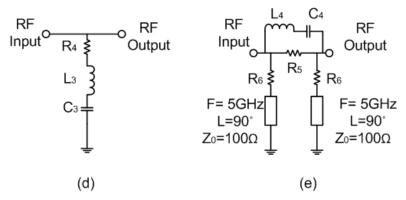

| 51<br>50 | The gain vs. frequency for the five example gain-equalizers[7]               | 63<br>67   |

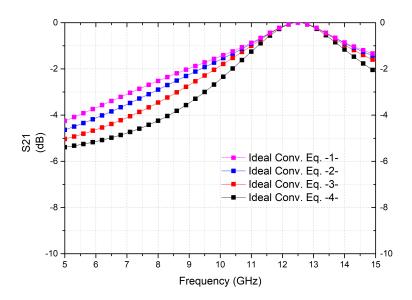

| 52       | The gain vs. frequency for four example conventional gain-equalizers         | 65         |

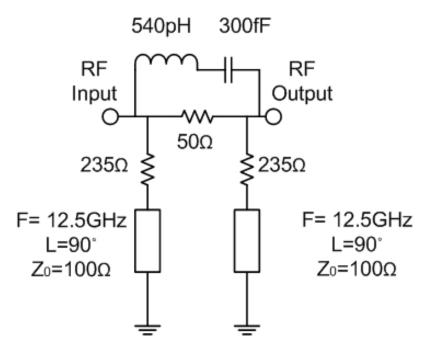

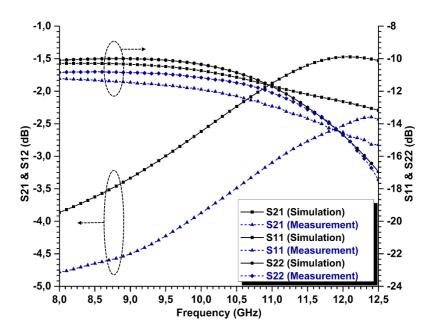

| 53<br>54 | The schematic of designed conventional type gain-equalizer                   | 65<br>62   |

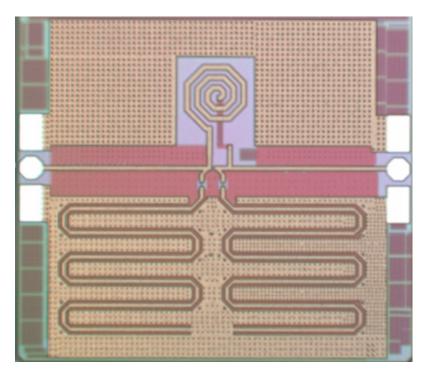

| 54       | The micrograph of designed conventional type gain-equalizer                  | 66         |

| 55       | Simulation and measurement results of designed conventional type             | 00         |

| FC       | gain-equalizer                                                               | 66<br>67   |

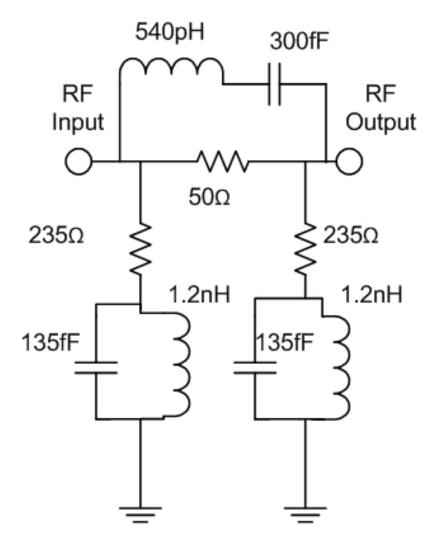

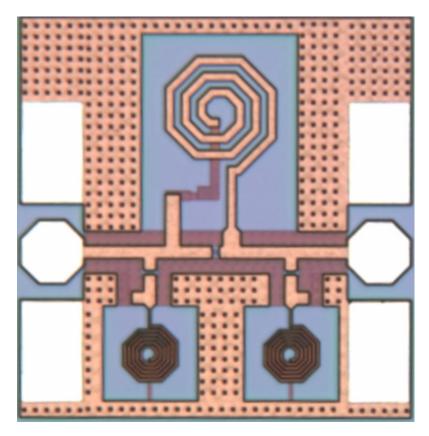

| 56       | The schematic of designed a new compact type gain-equalizer                  | 67<br>62   |

| 57<br>50 | The micrograph of designed a new compact type gain-equalizer                 | 68         |

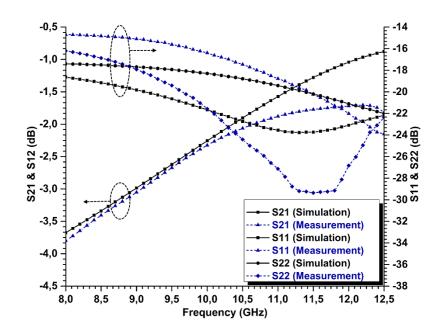

| 58       | Simulation and measurement results of designed a new compact type            | co         |

| 50       | gain-equalizer                                                               | 69         |

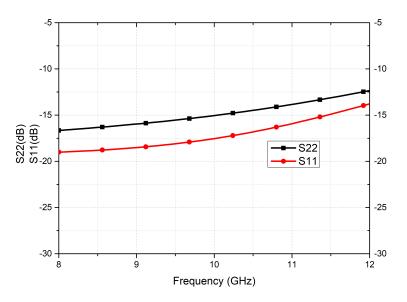

| 59       | S11 and S22 measurement results of designed compact type gain-               | 70         |

| 60       | equalizer for RX chain                                                       | 70         |

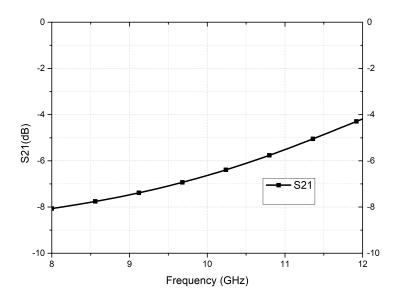

| 60       | S21 measurement results of designed compact type gain-equalizer for RX chain | 70         |

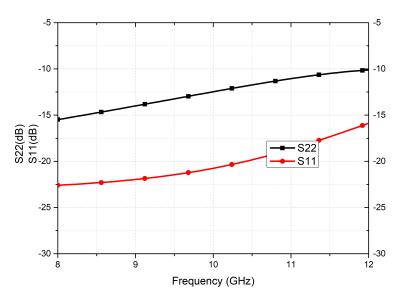

| 61       | S11 and S22 measurement results of designed compact type gain-               | 70         |

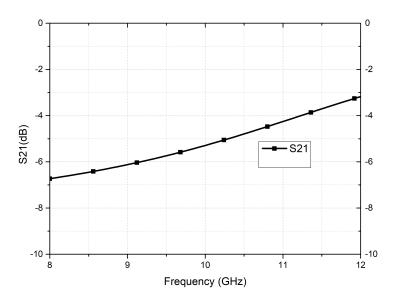

| 01       | equalizer for TX chain                                                       | 71         |

| 62       | S21 measurement results of designed compact type gain-equalizer for          | 11         |

| 02       | TX chain                                                                     | 71         |

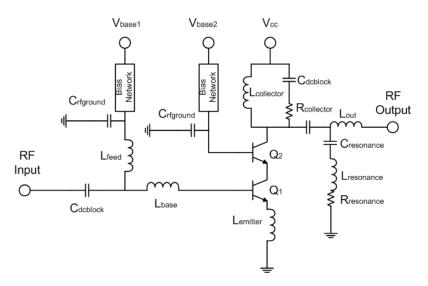

| 63       | Schematic of an active gain-equalizer                                        | 72         |

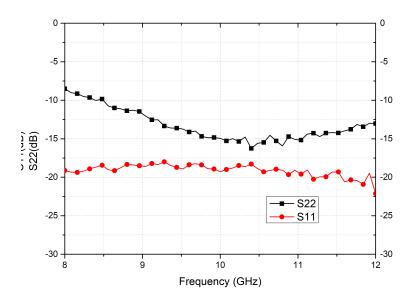

| 64       | S11 and S22 measurement results of designed first active gain-equalizer      | $72^{-12}$ |

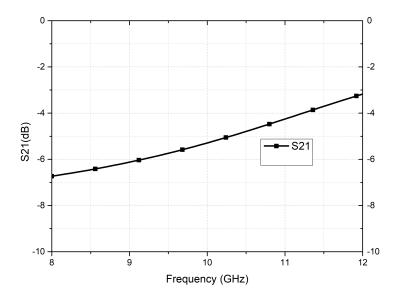

| 65       | S21 measurement results of designed first active gain-equalizer              | 73         |

| 66       | S11 and S22 measurement results of designed second active gain-              | 10         |

| 00       | equalizer                                                                    | 73         |

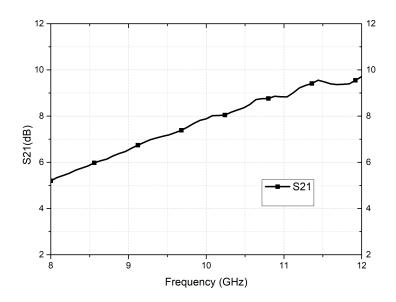

| 67       | S21 measurement results of designed second active gain-equalizer             | 74         |

| 68       | S21 measurement results of TX chain of T/R Module                            | 75         |

| 69       | S21 measurement result of RX chain of T/R Module                             | 75         |

|          |                                                                              |            |

## List of Tables

| 1 | Relative performance comparison of different IC technologies (Excel- |    |  |  |  |

|---|----------------------------------------------------------------------|----|--|--|--|

|   | lent: $++$ ; Very Good: $+$ ; Good: 0; Fair: $-$ ; Poor: $-$ ) [8]   | 16 |  |  |  |

| 2 | Ideal lumped element values for X-band 7-bit phase shifter           | 35 |  |  |  |

| 3 | Phase values of designed phase shifter                               | 39 |  |  |  |

| 4 | Comparison of 7-bit SiGe X-band phase shifters with reported works   | 56 |  |  |  |

## List of Abbreviations

| AF                     | Array Factor                                           |  |  |  |  |

|------------------------|--------------------------------------------------------|--|--|--|--|

| $\mathbf{A}\mathbf{M}$ | Amplitude Modulation                                   |  |  |  |  |

| BALUN                  | Balanced to Unbalanced                                 |  |  |  |  |

| $BV_{CEO}$             | Collector-Emitter Breakdown Voltage                    |  |  |  |  |

| BV <sub>CBO</sub>      | Collector-Base Breakdown Voltage                       |  |  |  |  |

| CB                     | Common-Base                                            |  |  |  |  |

| CCB                    | Constant Current Biasing                               |  |  |  |  |

| CE                     | Common-Emitter                                         |  |  |  |  |

| CVB                    | Constant Voltage Biasing                               |  |  |  |  |

| DBF                    | Digital Beam Forming                                   |  |  |  |  |

| DE                     | Drain Efficiency                                       |  |  |  |  |

| EIRP                   | Equivalent Isotropically Radiated Power                |  |  |  |  |

| FM                     | Frequency Modulation                                   |  |  |  |  |

| FOM                    | Figure-of-Merit                                        |  |  |  |  |

| GaAs                   | Gallium-Arsenide                                       |  |  |  |  |

| HP                     | High Pass                                              |  |  |  |  |

| IC                     | Integrated Circuit                                     |  |  |  |  |

| IF                     | Intermediate Frequency                                 |  |  |  |  |

| IL<br>IL               | Insertion Loss                                         |  |  |  |  |

| InP                    | Indium phosphide                                       |  |  |  |  |

| iNMOS                  | Isolated NMOS                                          |  |  |  |  |

| LNA                    | Low Noise Amplifier                                    |  |  |  |  |

| LO                     | Local Oscillator                                       |  |  |  |  |

| LP                     | Local Oscillator<br>Low Pass                           |  |  |  |  |

| MEMS                   |                                                        |  |  |  |  |

| MIM                    | Microelectromechanical System<br>Metal-Insulator-Metal |  |  |  |  |

| MMIC                   |                                                        |  |  |  |  |

|                        | Monolithic Microwave Integrated Circuits               |  |  |  |  |

| mm-Wave<br>MOS         | Millimeter-wave<br>Metal-Oxide-Semiconductor           |  |  |  |  |

| OAE                    |                                                        |  |  |  |  |

|                        | Overall Efficiency                                     |  |  |  |  |

| PA                     | Power Amplifier                                        |  |  |  |  |

| PAE                    | Power-Added-Efficiency                                 |  |  |  |  |

| PAWS                   | Phased Array Warning System                            |  |  |  |  |

| PS                     | Phase Shifter                                          |  |  |  |  |

| RADAR                  | Radio Detecting And Ranging                            |  |  |  |  |

| RF                     | Radio Frequency                                        |  |  |  |  |

| RMS                    | Root Mean Square                                       |  |  |  |  |

| RX                     | Receiver                                               |  |  |  |  |

| SiGe                   | Silicon-Germanium                                      |  |  |  |  |

| SPDT                   | Single-Pole Double-Throw                               |  |  |  |  |

| SP4T                   | Single-Pole Four-Throw                                 |  |  |  |  |

| DP4T                   | Double-Pole Four-Throw                                 |  |  |  |  |

| 4P4T                   | Four-Pole Four-Throw                                   |  |  |  |  |

| T/R                    | Transmit/Receive                                       |  |  |  |  |

| TX                     | Transmitter                                            |  |  |  |  |

| VGA                    | Variable-Gain Amplifier                                |  |  |  |  |

### 1 Introduction

#### 1.1 A Brief History of Radar

Radio Detection and Ranging (Radar) is a system for detecting the current information such as direction, distance and speed of the aircraft, ships, and other objects. Radars detect objects by sending out radio waves from a source which are reflected off the object back to the source. A radar uses electromagnetic radiation at high radio frequency in order to detect and locate remote reflecting objects. Then, the radiation is sent out in pulse form with a few second duration and these pulses are separated with "silent" intervals. Pulses which are sent out from the receiver are returned from the detected objects to the receiver. The detected objects are displayed by the receiver. The distance of the detected object is measured thanks to the speed of wave multiplied by the duration of the returned pulse signals from "target". The direction of the detected object is determined by use of highly directive radio antennas [9].

The history of the Radar begins with the invention of "Telemobiloskop" which is a device operating at 650 MHz by the German Cristian Hülsmeyer in May 1904 . This device is capable of detecting the presence of ships but it cannot detect the movement and distance of the ships. In 1914, Nikola Tesla introduced the idea of radar. In 1922, a lecture on the principle of radar was delivered by Guglielmo Marconi. In 1934, cargo ship Oregon and the ocean liner Normandie used the radar system which was installed by the French Emilie Girardeu [10].

During the World War II, radars played an important role to win the war. Mechanically scanned radars achieved hundreds scans per minute and they help to increase the visible area. The mechanically scanned radar system is replaced with the electronically scanned arrays, which is called as "phased arrays". This way of scanning achieved hundreds of scans per second and therefore they are commonly used in the military applications[11].

#### **1.2** Phased Array Radars

Today, phased array radar technology is used in both military and civilian applications. The number of civilian applications is increasing and we can see some examples from the civilian applications such as 5G, automotive radar, weather monitoring and radio astronomy. By placing a phased array into the automobile, collision avoidance is provided by measuring the distance between the placed car and an obstacle [12]. 5G systems are the great solution for boosting user data rates to accommodate rapidly increasing traffic demands of the user in the future in cellular technology [13]. In order to detect the place of storms, atmospheric and airborne hazards, phased arrays are used to monitor the results [14]. Sensitive phased arrays receive signals from the sky and detect gas, or other objects in the sky [15].

Although many examples are shown in civilian applications, phased array systems are mainly used in military applications. Fig.1a is one of the examples of the surface radar which is produced in the United States and called as AN/TPS-75 [1]. Fig. 1b is an example of ballistic missile warning radar system which is used for detecting missiles from the long-range and creates an early warning [2]. This radar is called as AN/FPS-132 and it is produced in the United States.

Phased array systems have more advantage than the conventional radar applications. Conventional radar applications are steering the beam by rotating the antenna mechanically. The mechanical rotation creates a reliability problem and a rotation time is needed to beam towards a single target. Phased array systems eliminate the reliability problem of the mechanical part and beam positioning does not need a mechanical rotation. Therefore, it takes less time than the conventional radar applications. Phased array systems can provide multi-target operation by targeting different frequencies at once. As a result, a multi-channel operation is created and it can increase data rates in communication application.

In phased arrays, the number of radiating elements directly increase the spatial resolution. Transmit/receive modules form the radiating elements and, phase and amplitude of the signal are controlled inside these modules. Today, GaAs, InP or SiGe are used for realizing these modules.

#### **1.3** Phased Array Operating Principles

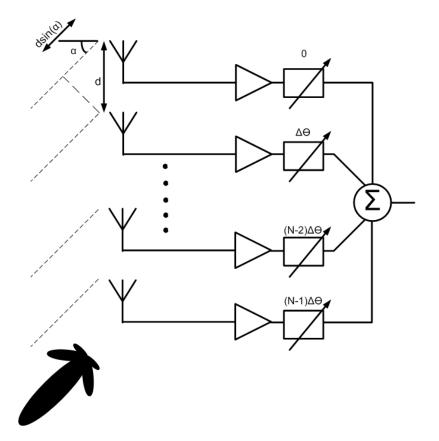

The block diagram of the phased array system in a receiver mode is shown in Fig. 2. Assume that the distance between each antenna is d, the  $\theta$  is the angle where the signal comes from a targeted source, the distance to reach the signal at

Figure 1: AN/TPS-75 [1] (a) and AN/FPS-132 [2] (b) phased array radars

Figure 2: Basic receiver block diagram of a phased array system

$i_{th}$  element can be found from

$$\delta d_i = id\sin\theta \tag{1}$$

The travel differences to each antenna element create a progressive time delay and phase difference. The comparison of the phased arrays based on time delays and the phase shift is provided in the following section.

#### 1.3.1 Time Delay vs Phase Shift

In order to find the time delay of the radiating element, the travel distance of each antenna is divided by the speed of the light. From this division, time delay of the  $i_{th}$  element is found as  $\frac{id\sin\theta}{c}$ . In order to find the phase difference of the radiating element, a carrier frequency is multiplied with the time delay. From this multiplication, the phase difference of the  $i_{th}$  element is found as  $w_c \frac{id\sin\theta}{c}$ . This can be rewritten as

$$\Delta_{\phi} = 2\pi \frac{d\sin\theta}{\lambda} \tag{2}$$

These time delay and phase difference will be used in defining the receiving signal. Generally, the  $k_{th}$  radiating element receive the signal as shown in (4).

$$S_0(t) = A\cos\left(\omega t + \phi_0(t)\right) \tag{3}$$

$$S_k = S_0 \left( t - k \Delta_\phi \right) \tag{4}$$

$$S_k = A\cos\left(w\left(t - k\Delta_t\right) + \phi\left(t - k\Delta_\phi\right)\right) \tag{5}$$

These equations are also valid for transmitter part of the radar systems because they are reciprocal. From these equations, depending on the control mechanism, timed-arrays and phased-arrays mechanisms are appeared as a solution. Due to the independence from the frequency of timed-arrays, they provide a much wider solution. However, due to the insertion-loss, noise, and nonlinearity of building blocks, it is hard to implement timed-arrays, especially for RF applications [16]. Consequently, in order to control the electronic beam, phase shifters draw the attention on employing the antenna system. As a result, phased array radars consist of thousands of radiating elements and by controlling the phase and amplitude of each element, the effective radiation pattern is created in the desired direction [17].

#### 1.3.2 Beam Steering and Array Factor

In phased array systems, by adjusting the phase shift and amplitude of the system in each transmitter/receiver channel, the main beam direction can be steered.

The angle between main beam direction and the array normal is dependent on the distance between each antenna element and incremental phase shift of each channel. This dependency can be found from (6) which is the rewritten version of (2).

$$\theta = \sin^{-1} \left( \frac{\lambda}{2\pi d} \Delta \phi \right) \tag{6}$$

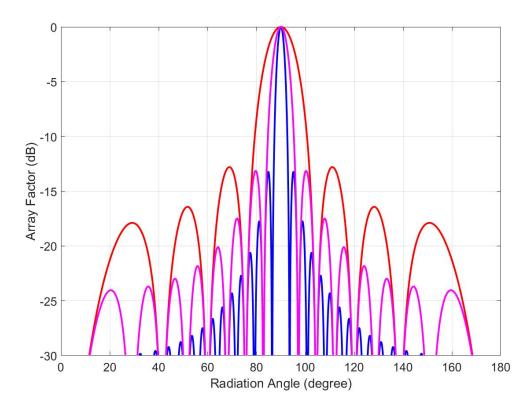

From this equation, the beam direction has a dependency only to the distance between each antenna elements and incremental phase shift value of each channel. When the distance between each antenna is increased, the beam width gets smaller, consequently, it increases the directivity of the antenna. However, after some point, increasing the spacing between each antenna creates grating lobes which make the phased array system more sensitive to interferer signals. The general distance between each antenna is chosen as  $\frac{\lambda}{2}$ .

When the array factor and antenna element is multiplied, the radiation pattern of an array is found[18]. Normalized array factor of a  $long(L>>\lambda)$  and uniform linear antenna array is given as

$$AF = \frac{\sin\left(N\frac{\psi}{2}\right)}{N\sin\left(\frac{\psi}{2}\right)} \tag{7}$$

where N is the number the antenna elements. This equation gives us, more antenna number will provide narrower main beam. As a drawback, more side lobe levels appear in the one period of  $\psi$ . Normalized array pattern of a linear array with  $\frac{\lambda}{2}$ spacing with a different number of antenna is given in Fig. 3. From this figure, we can see that when the number of the antenna increases, the narrower main beam appears.

#### 1.3.3 Phased Array as a Receiver and Transmitter

A phased array system needs to receive the signal with a low noise value from each channel. Assume that the number of phased array is N, the summed power of the received signal with N radiating element can be found as

$$S_{sum} = n^2 G S_{in} \tag{8}$$

Figure 3: Normalized array pattern of a linear array with  $\lambda/2$  spacing for (red) N=8 (magenta) N=16 (blue) N=32 antenna elements

where  $S_{in}$  is the input power in each receiver channel, G is the power gain of each receiver channel, n is the number of channels or antenna elements, and  $S_{sum}$  is the summed signal power at the receiver output.

Assuming that noise contributions of different receiver channels are uncorrelated, their signal powers (not voltages) are added at the receiver output, which can be written as

$$Noise_{sum} = nG\left(N_{ant} + N_{rec}\right) \tag{9}$$

where  $N_{rec}$  is the noise power added by each receiver channel,  $N_{ant}$  is the noise power feeding from an antenna, and  $Noise_{sum}$  is the combined noise power at the receiver output. Signal to noise ratio is found from the ratio of (8) and (9). From this ratio, we can see that the antenna element is directly proportional with the SNR. In order to improve the SNR of the system, the more antenna can be used. The drawback of using more antenna in the system is the cost and power consumption.

Using multiple channels also increases the radiated power in the main beam

direction [19]. The overall radiated antenna can be found from the multiplication of the square of the antenna number with the power of each radiating element. From this multiplication, the effective isotropic radiated power (EIRP) of an N-element active phased array in the main beam direction is  $N^2P$  watt [20]. This equation can be interpreted as the more antenna element will result as the more radiated power in the main beam direction. This ability can handle the drawback of the less output power of SiGe based power amplifiers due to the low-breakdown voltages with respect to III-V technologies.

#### **1.4** Phased Array Architectures

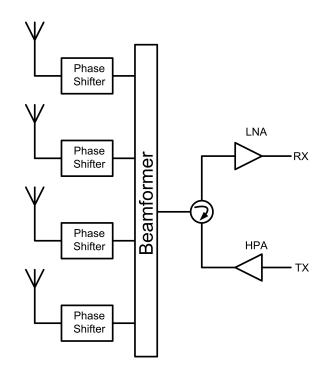

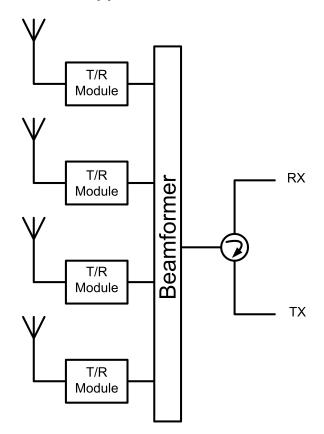

Phased array systems feed the antenna in two ways. The first way is feeding the antenna with a single high-performance low-noise amplifier(LNA) in receiving side and single high-performance power amplifier(PA) in transmitting side. Both sides is connecting to the multiple phase shifters and antennas. This approach is called as passive phased arrays. The second way is feeding each antenna with each low noise amplifier, power amplifier, and phase shifter separately. This approach is called as active phased arrays.

The way the phase shifting functionality is realized is another categorization type of the phased array systems. In this context, phased arrays divided into four groups, RF phase shifting, IF phase shifting, LO phase shifting and digital beam forming.

#### 1.4.1 Passive Phased Arrays

Block diagram of the passive phased arrays is shown in Fig.4. As we can see from the figure, passive phased arrays consist of a very high output power PA in transmit mode and very high noise performance LNA in receiver mode. These modes are connected to multiple passive phase shifters and radiating elements through a circulator. Since all elements are passive and using one LNA and one PA in this architecture, power consumption is low. Moreover, this architecture can be used in high power applications. One of the examples of using this architecture is showed in Fig. 5 is AN/FPQ-16 which is introduced in 1975 in United States [3].

Figure 4: Block diagram of passive phased array

Figure 5: Passive Phased array example: AN/FPQ-16 [3]

#### 1.4.2 Active Phased Arrays

Block diagram of the active phased arrays approach is shown in Fig.6. As we can see from the figure, each antenna element has its own active transmit/receive (T/R) module. Inside this module, PA, LNA, phase shifters and switches are used. One of the examples that uses this architecture is shown in Fig. 7, SAMPSON which is introduced in United Kingdom [4].

Figure 6: Block diagram of active phased array

Figure 7: Active phased array example: SAMPSON[4]

Active phased arrays consume high power and cannot deal with high power

Figure 8: RF phase shifting Phased array architectures

applications. However, this architecture is more reliable since each element has its own LNA and PA. In passive phased array structure, if one failure occurred in LNA or PA whole structure will fail. In this architecture, if one LNA or PA fail, only this part of the whole structure will fail. In receiving part, LNA is the first block in the active phased array structures. In passive phased array structures, antenna, phase shifter, and circulator receive the signal before the LNA. These blocks create a loss on the signal path. As a result, the noise performance of the active phased arrays is better than the passive phased arrays. These passive structures are also placed after PA in transmit mode. Therefore, due to this loss, output power performance of the active phased arrays is better than the passive phased arrays.

#### 1.4.3 RF phase shifting(All RF Transmit/Receive)

Fig. 8 shows the RF phase shifting(All RF Transmit/Receive) approach. RF phase shifting is the most dominant approach since it is the most compact approach than other phase shifting types. A single mixer is used after the RF combining part in this approach. The advantage of using a single mixer is that LO distribution network is not necessary.

#### 1.4.4 IF phase shifting

Fig. 9 shows the IF phase shifting approach. In this approach, phase shifters are realized in IF domain. Because passive component values are inversely proportional with frequency, passive component values are high in this approach. Moreover, in this approach, each radiating elements has its own mixer. Consumed power is increasing in this approach because of individual mixer components.

Figure 9: IF phase shifting Phased array architectures

Figure 10: LO phase shifting Phased array architectures

#### 1.4.5 LO phase shifting

Fig. 10 shows the LO phase shifting approach. In this approach, a single mixer is used for each radiating element. However, phase shifters are no longer exist in RF part of phased array. Therefore, the drawbacks of the phase shifter are eliminated with this approach such as insertion-loss, noise figure, and noise. The problem with this approach is that due to the realization of phase shifters in LO part, the distribution network is required for this part. As a result, a more complex system is required in this approach.

#### 1.4.6 Digital beam forming

Fig. 11 shows the digital beam forming phase shifting approach. In this approach, phase shifting is performed in digital domain instead of analog or RF domain. The advantage of this approach is that a large number of beams is synthesized by using a digital signal processor (DSP)[21]. The disadvantage of this approach is interference rejection only occurs after signal combining. Therefore, the dynamic range requirement of mixers increases, consequently, power consumption of mixers increases. This approach also needs separate ADC for each radiating element. It

Figure 11: Digital beam forming Phased array architectures

also increases the power consumption of the phased array.

#### 1.5 All RF Transmit/Receive Module

As explained in previous section, all RF T/R module has compact design and does not need LO distribution network. This architecture enables the phase shift in RF front end structure. RF front end phase shifting enables high phase resolution with low area and, consequently, it decreases the required number of element for each phased arrays. Due to the tendency for higher phase resolution, low area and low cost all RF T/R module is selected as a T/R module structure. The performance of active phased arrays strongly depends on the performance of transmit/receive (T/R) modules. In T/R modules, several blocks are realized. In order to amplify the received signal from the environment, low noise amplifier (LNA) is used. In order to transmit the signal to the environment with a high power, a power amplifier (PA) is used. Transmit and receive parts of a module has to be isolated from each other. LNA and PA need to be switchable in the module. This ability is provided with single-pole-double-throw (SPDT) switches. Phase shifters(PS) and variable gain amplifiers(VGAs) determine the performance parameter of T/R module. The aim of PS is to change the angle of the signal without changing the amplitude of the signal. The aim of the VGA is to change the amplitude of the signal without changing the phase of the signal.

In Fig. 12, different approaches on system-level architectures for all T/R modules is shown. Fig. 12.a shows that transmit and receive part of T/R module is separated from each other and high isolation can be achieved with this approach. However, the number of PS and VGA increases in this approach. As a result, the power consumption of this approaches increases.

Figure 12: Several system level architectures for RF transmit/receive modules

Fig. 12.b shows that PS and VGA must be bidirectional because, in both modes of T/R module, these blocks are used on two sides. Therefore, passive phase shifter and attenuator must be used in this approach. By using passive elements with this approach, the gain requirement of PA and LNA increase to compensate the losses from these sub-blocks. Additional SPDT also increases the loss on the signal path.

Fig. 12.c shows the solution for the direction problem of previous approaches. Moreover, with this approach isolation requirement of the SPDTs decreases. Thanks to the direction solution single direction of sub-blocks can be used in this approach. Active phase shifters and VGAs decrease the gain requirement of amplifiers.

#### 1.6 SiGe BiCMOS Technology

In RF applications, III-V, RF BiCMOS and RF CMOS technologies play an important role in realizing T/R modules for phased array applications. III-V technologies have the best performance parameters with respect to others. However, integration problems and high product cost are drawbacks of this technology. Recent advances in RF CMOS technologies show us high  $f_t$ ,  $f_{max}$  and low  $f_{min}$  values are achieved with low cost and easy integration. However, the layout of the RF CMOS changes these parameters. In other words, parasitic resistances and capacitances create a reliability problem on this technology. Today, SiGe BiCMOS enables to realize T/R modules for phased array applications without performance sacrifice when compared with III-V technologies and with less parasitic dependence with respect to RF CMOS. Thanks to this technology, the advantages of Si can be used with the same speed and performance with respect to the III-V technologies.

$f_t$  is the cutoff frequency where the current gain of transistor  $\beta$  becomes unity.  $f_{max}$  is the maximum oscillation frequency where the power gain of a transistor becomes unity. These two parameters are important in RF engineering because the highest they are, the larger gain they can achieve and the lower noise figure can achieve. The relationship between minimum noise figure level and  $f_t$  is shown in 10

$$NF_{min} = 1 + \frac{n}{\beta_{DC}} + \sqrt{\frac{2J_c}{V_t} \left(r_e + r_b\right) \left(\frac{f^2}{f_t^2} + \frac{1}{\beta_{DC}}\right) + \frac{n^2}{\beta_{DC}}}$$

(10)

As we see from the equation,  $f_t$  is inversely proportional with  $NF_{min}$ . In order to increase the  $f_t$  of the transistor, Ge is used with Si. In bipolar transistors, SiGe alloys are grown as base part of the transistor. Si has a band-gap of 1.12 eV and Ge has a bandgap of 0.66 eV. By combining Si with Ge enables injecting more electrons and as a result, current gain,  $\beta$ , of the transistor increases. Moreover, adding Ge to the base of a transistor increases the speed of carriers. This leads a decrement of the base transit time  $\tau_b$ . The relationship between  $f_t$  and  $\tau_b$  is shown in

$$f_T = \frac{1}{2\pi} \left( \tau_b + \tau_c + \frac{1}{g_m} \left( C_\pi + C_\mu \right) + \left( r_e + r_c \right) C_\mu \right)^{-1}$$

(11)

where  $\tau_c$  is the transit time in collector region,  $g_m$  is the transconductance,  $C_{\pi}$  and  $C_{\mu}$  are base-emitter and base-collector junction capacitances,  $r_e$  and  $r_c$  are emitter and collector resistances [8]. The  $g_m$  of the transistor is increased by increasing  $\beta_{DC}$  of the transistor. The higher  $f_T$  for the transistor is achieved via  $\tau_b$  and  $g_m$ .

As mentioned before, another important parameter of the transistor is  $f_{MAX}$ ,

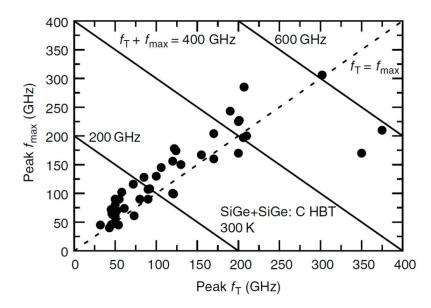

**Figure 13:**  $(f_T)$  and  $(f_{MAX})$  for different SiGe HBT technologies. [5]

where is shown as

$$f_{MAX} = \sqrt{\frac{f_T}{8\pi C_\mu r_b}} \tag{12}$$

where  $r_b$  is intrinsic base resistance. Another advantage of Ge with Si instead of pure Si, while adding doping into the base of the transistor, the current gain of the transistor does not reduce. In Si based and SiGe based transistors, the increment of doping reduces  $r_b$ . Without reducing current gain of transistor enables high noise performance without gain loss of transistor.

Adding Ge doping in the base region, all important high-frequency parameters increase. Fig. 13 shows reported  $f_T$  and  $f_{MAX}$  values for different SiGe HBT technologies.

The most important advantages of SiGe over other its III-V counterparts is the ability to integrate with CMOS. III-V technologies still achieve the highest output power level and the lowest noise figure level but the advancements on SiGe BiCMOS offers a competitive solution. Moreover, the cost and yield performance is increased with this technology. Furthermore, digital baseband and RF front-end blocks can be easily integrated into SiGe BiCMOS. A comparison between SiGe HBTs with alternative technologies is presented in Table 1.

Today, ultrahigh performance phased arrays which are mainly used in military applications can be realized in III-V technologies. However, SiGe technologies can

| Performance         | SiGe | SiGe | Si   | III-V  | III-V | III-V |

|---------------------|------|------|------|--------|-------|-------|

| Metric              | HBT  | BJT  | CMOS | MESFET | HBT   | HEMT  |

| Frequency Response  | +    | 0    | 0    | +      | ++    | ++    |

| 1/f and Phase Noise | ++   | +    | _    |        | 0     |       |

| Broadband Noise     | +    | 0    | 0    | +      | +     | ++    |

| Linearity           | +    | +    | +    | ++     | +     | ++    |

| Output Conductance  | ++   | +    | _    | _      | ++    | _     |

| Transconductance    | ++   | ++   |      | _      | ++    | _     |

| Power Dissipation   | ++   | +    | _    | _      | +     | 0     |

| CMOS Integration    | ++   | ++   | N/A  |        |       |       |

| IC cost             | 0    | 0    | +    | _      | _     |       |

**Table 1:** Relative performance comparison of different IC technologies (Excellent: ++; Very Good: +; Good: 0; Fair: -; Poor: --) [8]

be used instead of these technologies in both military applications and civilian applications due to the low-cost, fully-integrated structure, less area, and system-on-chip solutions for microwave and millimeter wave phased array applications.

#### 1.7 Motivation

Phase array T/R modules achieve high performance with III-V technology. However, the cost of III-V technologies is high. Recent developments in SiGe BiCMOS technology show us III-V technology can replace with SiGe BiCMOS. Moreover, thanks to the integration of the CMOS, digitally controlled T/R modules can be realized with that technology. Power dissipation and integration complexity can be reduced in SiGe BiCMOS. On the other hand, the limited breakdown voltage, the high noise levels reduce the performance of phased arrays with SiGe BiCMOS. Therefore, low sensitive receiver chain and low output power transmitter can be realized with SiGe BiCMOS. Taking everything into account, SiGe technologies can be used in phased arrays instead of III-V technologies with same performance parameters.

The objective of this thesis is to design integrated electronic phase shifter, the most important element in phased arrays, for- X-band. Passive phase shifter based on III-V technologies can achieve low insertion-loss with the conventional design techniques due to the high-quality passive components. Low-insertion-loss can also

Figure 14: SiGe X-band all-RF T/R module block diagram and component specifications

be achieved with the reduction of the series switches on the passive phase shifter. In order to improve the insertion-loss aspect of the passive phase shifter, in this thesis, new switching methodology is employed and this thesis is devoted to the development of phase shifter designs utilizing passive approaches rather than active topologies. Moreover, in collaboration with my colleagues, in T/R module 3-dB positive slope gain is aimed. In order to achieve this gain-behavior, on T/R module which is shown in Fig. 14, two positive slope gain behavior passive gain-equalizers and two positive slope gain behavior amplifiers are presented to balance the negative slope gain-behavior previously designed amplifiers.

#### **1.8** Organization

This thesis includes five chapters which are organized as follows. Chapter 2 introduces the different approaches on the phase shifter and compares the different topologies of the phase shifters. This chapter continues with the explanation of the advantages of using passive phase shifters instead of active phase shifters.

Chapter 3 begins with the design of high-performance low insertion-loss 7-bit

passive phase shifter. Specifically, approach on the passive phase shifter is explained the simulation result of the 7-bit passive phase shifter is depicted in this chapter.

Chapter 4 expresses the design considerations for achieving positive slope gain T/R Module. Specifically, measurement and simulation results of two active gain-equalizers and two passive gain-equalizers are demonstrated to achieve this gain behavior.

Chapter 5 concludes the thesis with the summary of work and provides information on possible future studies.

### 2 Fundamentals of Phase Shifters

#### 2.1 Introduction

In this chapter, fundamentals of phase shifters will be covered. This chapter begins with a brief description of the phase shifter. Then, categorization of the phase shifters will be done with different approaches. Important performance parameters of the phase shifter will be explained. In order to achieve the best performance, how different topologies performed the phase shift operation is discussed in the following section. At the end of the chapter, the effect of quantization error is discussed.

#### 2.2 A Brief Description of Phase Shifter

In phased array systems, the phase control of the signal is utilized by phase shifters. They are used to change the transmission phase angle, in other words, phase of S21, of a network. The phase shift is achieved in a controlled way. Ideally, this block varies the phase between 0 and 360 degrees without creating an insertionloss. Moreover, the insertion-losses of each phase state are the same. The important and challenging parameters of the phase shifters are phase resolution, RMS phase error, RMS amplitude error, bandwidth, chip size, linearity, and power dissipation.

#### 2.3 Classification of Phase Shifters

Phase shifters can be controlled in two ways: Analog and Digital. Analog phase shifters vary the phase between 0 and 360 degrees in a continuous way. Digital phase shifters vary the phase between 0 and 360 degrees in a discrete way.

Analog phase shifters achieve the continuous phase shift generally with a voltage control. Varactor diodes have the dependency on the voltage. By changing the voltage, the capacitance of the diode changes, as a result, continuous way phase shift is achieved.

Digital phase shifters achieve the discrete phase shift by "bits". Each bit has at least two states. One of the states of the "bit" is called as an "ON" and other states of the "bit" are called as an "OFF". The phase differences between the "ON" state and "OFF" state is called as an achieved phase shift. In digital phase shifters, MSB, most significant bit, is defined as the largest bit and LSB, least significant bit, is defined as the lowest bit. Assume that the range of the phase shifter is between 0 and M, in the N bit phase shifter, MSB is found as M/2 and LSB is found as  $M/2^N$ . For example, assume that phase shifter covers between 0 and 360 degrees, if the bit number of the phase shifter is 3, the LSB of the phase shifter is 45 degrees. If the bit number of the phase shifter is 6, the LSB of the phase shifter is 5.62 degrees. In both cases, the MSB of the each phase shifter is 180 degrees.

Between these two approaches, digital phase shifters are more common due to the immunity to the noise contribution of the voltage lines. In analog phase shifters, voltage lines lead the noise contribution on the block.

#### 2.4 Important Performance Metrics of the Phase Shifter

In RF-IC blocks, performance parameters are the key part of the designs. The comparison between each block is decided with respect to these results. In general, input and output return loss, noise; insertion-loss or gain, power consumption, linearity, chip size, bandwidth, and stability are common key parameters for all RF-IC blocks. Specifically, in phase shifters, RMS phase error, RMS amplitude error, and an effective number of bits determine the performance of the phase shifter. In this section, we focus on the performance metrics which are specific for phase shifters.

#### 2.4.1 RMS Phase Error

In the phase shifter, there is always an error between the desired phase shift value and the obtained phase shift value. These phase errors are different for each phase state and these values are changing with the frequency. In order to describe the errors of the phase shifter, root-mean square of each phase state is found. To find this value, the phase error between each phase state and the desired phase shift is found. These errors are summed up for each frequency and defined as a common error. This common error is added to each phase state. The error between the desired phase states and the phase states with an addition of common error is found. The standard deviation of these errors is defined as RMS phase error. The formula of the RMS phase error is defined as:

$$\theta_{\Delta,rms}(f) = \sqrt{\frac{\sum_{i=2}^{2^{N}} |\theta_{\Delta_i}(f)|^2}{2^{N} - 1}}$$

(13)

Where  $\theta_{\Delta i}$  denotes the phase error between the desired phase shift and the obtained phase shift at the  $i_{th}$  state and N is the number of bits of the phase shifter. Generally, RMS phase error is the minimum at the center frequency and increases for higher and lower frequencies.

#### 2.4.2 RMS Amplitude Error

An ideal phase shifter changes the phase of the transmission angle without changing the amplitude of transmission. However, in real life, it is not practicable. Amplitude error occurs in phase shifter because while changing the phase of the transmission, the amplitude of the transmission also varies. RMS amplitude error is defined with respect to the average amplitude of the phase shifter. In order to define the amplitude error of the phase shifter, RMS amplitude error can be expressed as

$$A_{\Delta_{rms}}(f) = \sqrt{\frac{\sum_{i=1}^{2^{N}} (\Delta A_{i}(f))^{2}}{2^{N}}}$$

(14)

where  $\Delta A_i$  is the error between the amplitude of the  $i_{th}$  state and the average amplitude. N is the number of bits of the phase shifter.

#### 2.4.3 Effective Number of Bits

The effective number of bits determines the useful bandwidth of the phase shifter. If the phase shifter has N bits in terms of an effective number between two frequencies, the useful bandwidth of the phase shifter is called as the between these two frequencies.

During the design period of the phase shifter, N bit performance is aimed and therefore N stage has "ON" and "OFF" states. However, due to the RMS phase error of the phase shifter, an effective number of bits is defined in a different way. In order to have N effective number of bits, the RMS phase error must be lower than LSB/2 for that specific N. For example; a phase shifter who has 5-bit operation has LSB value 11.25 degree. Therefore, RMS phase error must be lower than 5.62.

#### 2.5 Phase Shifter Topologies

Phase shift operation is realized with different topologies. These topologies can be grouped into two main categories: Passive phase shifter and active phase shifter. An active phase shifter consumes power during the phase shift operation and generally provides gain. A passive phase shifter does not consume power during the phase shift operation. Due to the passive networks, this type of phase shifter generally introduces attenuation.

On the one hand, active phase shifters have better insertion-loss, better noise figure value, wider bandwidth operation, and smaller size than the passive phase shifters. On the other hand, passive phase shifters have better linearity, less power consumption. Common passive phase shifter topologies are switched-line, loadedline, reflection-type, and switched-filter. Common active phase shifter topology is the vector modulator.

#### 2.5.1 Switched-Line Phase Shifter

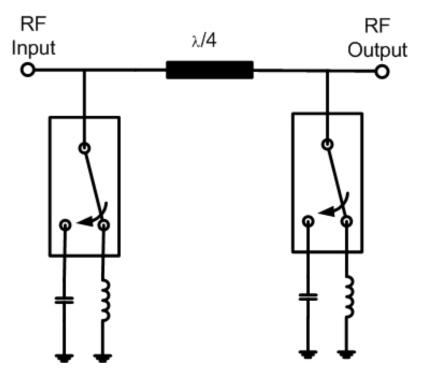

As shown in Fig. 15, switched line phase shifter operates as a true time delay element. This delay is determined by the difference of two path lengths. Ideally, phase shifter based on time delay operation gives the wide-band solution. However, practically, the time delay is not the same different frequencies. Moreover, additional path causes an additional loss and therefore amplitude error of the phase shifter increases. In this type of phase shifter, SPDTs degrade the performance of the phase shifter. This type of phase shifter cannot reach high bit resolution in wide-band operation region and RMS amplitude error of this phase shifter is high. We can see some switched-line type phase shifter examples in literature[22][23][24].

#### 2.5.2 Loaded-Line Phase Shifter

As shown in Fig. 16, in loaded-line phase shifters,  $\lambda/4$  transmission line is connected with either inductance or capacitances. By changing the load of the transmission line, the line characteristic changes. The advantage of this topology consumes less area than switched-line topology. The disadvantage of this topology is return loss depends on the desired phase shift. This dependency may lead an amplitude difference while combining next stage. Due to the dependency on  $\lambda$ , this

Figure 15: General diagram of the bit of the switched-line phase shifter

Figure 16: General diagram of the bit of the loaded-line phase shifter

type of phase shifter still has narrow-band operation problem and cannot reach high bit resolution [25].

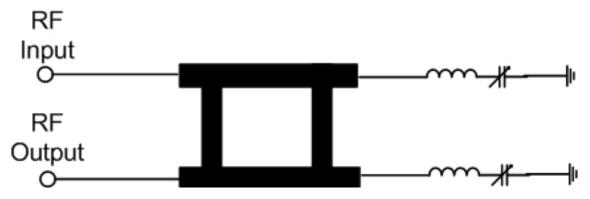

#### 2.5.3 Reflection-Type Phase Shifter

As shown in Fig. 17, a reflection type of phase shifters perform the phase shift operation using a circulator or coupler. RF input is directly connected to one port of the coupler, RF output is directly connected to another port of the coupler. Last

Figure 17: General diagram of the bit of the reflection-type phase shifter

Figure 18: Switched-filter topology with tee networks

two ports of the coupler are terminated with variable loads. These loads generate the desired phase shift. These type of phase shifters use in millimeter-wave. The advantage of this type of phase shifters is better insertion-loss and better return loss performances due to the isolation between ports. However, this type of phase shifters cannot reach 360 degrees cover range[26] [27] [28] [29].

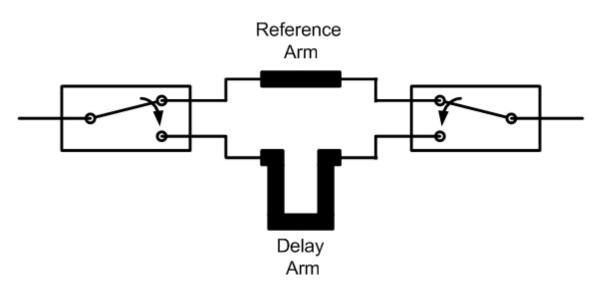

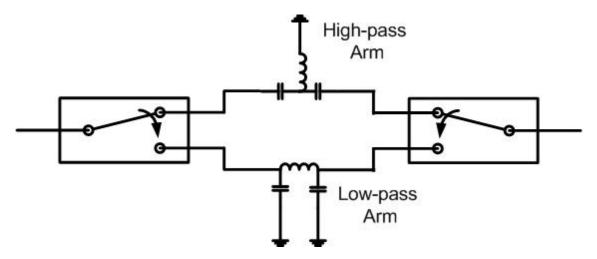

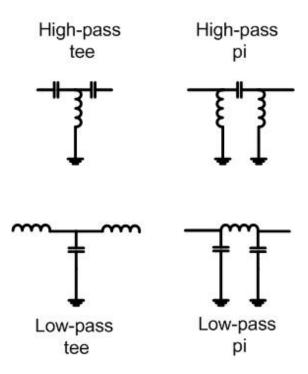

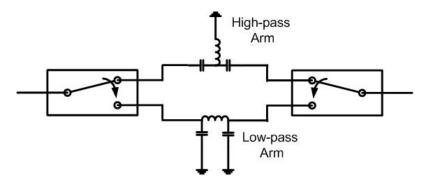

#### 2.5.4 Switched-Filter Phase Shifter

As shown in Fig. 18, switched-filter type phase shifters have a high-pass filter or low-pass filter networks to achieve phase shift operation. In one arm, these filters can achieve 90-degree phase shift. By using one type of filter in one arm and using another type of filter in the reference arm, the 180-degree phase shift can be achieved. Ideally, this type of phase shifter achieves desired phase shift at the center frequency. Practically, due to the passive components, RMS phase error degrades dramatically due to narrow-band operation.

Figure 19: Tee and pi filter networks

In this topology,  $\Pi$  and T type of filters can be used in arms. Equations for ideal lumped elements are shown in the formula in this order: High-pass tee, Low-pass tee, High-pass pi, Low-pass pi [30]. These networks are shown in Fig. 19.

$$L_{1} = \frac{Z_{0}}{2\pi f \sin(\phi)} \quad \& \quad C_{1} = \frac{\sin(\phi)}{2\pi f Z_{0} (1 - \cos(\phi))}$$

(15)

$$L_{2} = Z_{0} \frac{(1 - \cos(\phi))}{2\pi f \sin(\phi)} \quad \& \quad C_{2} = \frac{\sin(\phi)}{2\pi f Z_{0}}$$

(16)

$$L_{3} = \frac{Z_{0}\sin(\phi)}{2\pi f (1 - \cos(\phi))} \quad \& \quad C_{3} = \frac{1}{2\pi f Z_{0}\sin(\phi)}$$

(17)

$$L_4 = Z_0 \frac{\sin(\phi)}{2\pi f} \quad \& \quad C_4 = \frac{(1 - \cos(\phi))}{2\pi f Z_0 \sin(\phi)} \tag{18}$$

Some examples of high-pass/low-pass filter based phase shifter can be seen in the literature. Although, achieving phase shift operation without consuming power, they have narrow-bandwidth operation and large size [31] [32].

## 2.5.5 Vector Modulator Phase Shifter

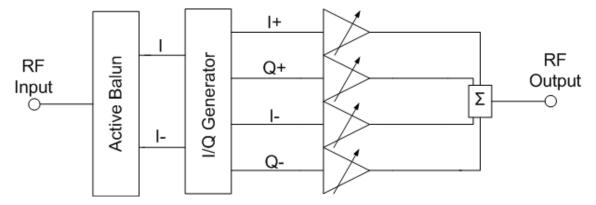

The figure of the vector modulator type phase shifter depicts in Fig. 20. By using all-pass RLC filters or hybrid couplers, the input signal is divided into four quadra-

Figure 20: Block diagram of a typical vector sum type phase shifter

ture vector: in-phase plus(I+), quadrature-phase plus(Q+), in-phase minus(I-), quadrature-phase minus(Q-). These vectors are amplifying by VGAs and adding these signals to create the output of the phase shifter. VGAs determine the amplitude of each quadrature vector and in order to achieve desired phase shift, gain setting of each VGAs is determined. High phase resolution, less area, low RMS phase error can be achieved with this type of phase shifter. However, power consumption, omnidirectional structure, and linearity are the drawbacks of vector modulator phase shifter[33] [34] [35].

## 2.6 Quantization Loss of the Phase Shifter

Due to the discrete phase shift operation of the digital phase shifter, it can change the phase of transmission with constant pre-defined values. For instance, if the phased array wants to steer the beam in  $\theta = 63$  degrees, and as we found in previous sections,  $\lambda/2$  spacing is required for antenna spacing,  $\Delta_{\theta}$  must be 153 degrees. Since digital phase shifter cannot operate this operation in a continuous way, 153 degrees will be provided with the closest phase shift value. If the phase shifter has 5 bits, this value is 157.5 degrees. The difference between the desired phase shift and required phase shift creates a quantization error. This quantization error degrades the overall performance of the phased array systems.

## 3 A 7-bit X-band Switched Filter Phase Shifter in SiGe BiCMOS

## 3.1 Introduction

In this chapter, design and analysis of 7-bit X-band switched-filter based phase shifter will be covered. In section 3.2 the requirement of a designed phase shifter is discussed. Then, in section 3.3, the analysis on the pi and tee networks will be given. The methodology used in phase shifter design is explained in detail in section 3.4. At the end of the chapter, the simulation results of the phase shifter are shown.

## **3.2** Phase Shifter Requirements

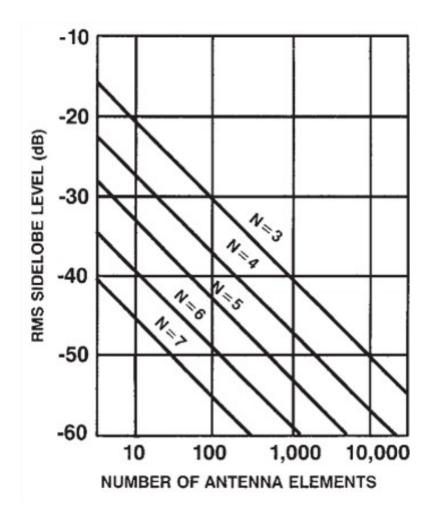

Phase shifter requirements can be listed as: Bit-resolution, RMS phase error, power dissipation, and insertion-loss. As shown in Fig. 21 the improvement of the bit resolution of the phase shifter decreases the number of the required antenna element to satisfy the same side-lobe level [6]. 7-bit is required to decrease the number of radiating elements. T/R modules should have the capability of adjusting the phases correctly for not inhibiting the performance degradation of the receiver sensitivity and output power of the transmitter. Therefore, low RMS phase error is required. Two important building blocks of a T/R module are phase shifters and attenuators. The phase shifter determines the phase resolution of the T/R module and the attenuator provides the amplitude control of the T/R module. Since these blocks are used in all T/R module arrays, the power consumption of the whole module is linearly proportional to the power dissipation of these blocks. In the light of the discussion in Chapter 2, switched-filter topology is chosen to meet the bit resolution, RMS phase error, and power dissipation requirements. In order to handle the insertion-loss problem of this type of phase shifter, new switching networks are employed.

## 3.3 High-Pass and Low-Pass Pi and Tee Networks

Switched-filter based phase shifters are based on high-pass/low-pass  $\Pi$  and T networks. Schematic views of these networks are shown in Fig. 19. As shown in the

Figure 21: Required antenna number to reach the same RMS side-lobe level with different phase resolutions [6]

figure, high-pass tee and low-pass pi networks provide the phase shift operation with one inductance while other two networks perform the phase shift operation with two inductances. Due to the large size of the inductances, high-pass tee and low-pass pi networks are generally chosen. The analysis of each network will be provided in this section.