# Kent Academic Repository Full text document (pdf)

# **Citation for published version**

Cheng, Zhiqun and Xuan, Xuefei and Ke, Huajie and Liu, Guohua and Dong, Zhihua and Gao, Steven (2017) Design of 0.8–2.7 GHz High Power Class-F Harmonic-Tuned Power Amplifier with Parasitic Compensation Circuit. Active and Passive Electronic Components, 2017. pp. 1-8. ISSN 0882-7516.

## DOI

https://doi.org/10.1155/2017/2543917

### Link to record in KAR

https://kar.kent.ac.uk/62311/

### **Document Version**

Publisher pdf

### **Copyright & reuse**

Content in the Kent Academic Repository is made available for research purposes. Unless otherwise stated all content is protected by copyright and in the absence of an open licence (eg Creative Commons), permissions for further reuse of content should be sought from the publisher, author or other copyright holder.

### Versions of research

The version in the Kent Academic Repository may differ from the final published version. Users are advised to check http://kar.kent.ac.uk for the status of the paper. Users should always cite the published version of record.

### Enquiries

For any further enquiries regarding the licence status of this document, please contact: **researchsupport@kent.ac.uk**

If you believe this document infringes copyright then please contact the KAR admin team with the take-down information provided at http://kar.kent.ac.uk/contact.html

### Research Article

# Design of 0.8–2.7 GHz High Power Class-F Harmonic-Tuned Power Amplifier with Parasitic Compensation Circuit

### Zhiqun Cheng,<sup>1,2</sup> Xuefei Xuan,<sup>1</sup> Huajie Ke,<sup>1</sup> Guohua Liu,<sup>1</sup> Zhihua Dong,<sup>1</sup> and Steven Gao<sup>3</sup>

<sup>1</sup>School of Electronics and Information, Hangzhou Dianzi University, Hangzhou 310018, China

<sup>2</sup>Key Laboratory of Nanodevices and Applications, Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences, Beijing, China

<sup>3</sup>School of Engineering and Digital Arts, University of Kent, Canterbury CT2 7NT, UK

Correspondence should be addressed to Huajie Ke; khj@hdu.edu.cn

Received 23 February 2017; Revised 3 May 2017; Accepted 22 May 2017; Published 14 June 2017

Academic Editor: Dixian Zhao

Copyright © 2017 Zhiqun Cheng et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The design, implementation, and measurements of a high efficiency and high power wideband GaN HEMT power amplifier are presented. Package parasitic effect is reduced significantly by a novel compensation circuit design to improve the accuracy of impedance matching. An improved structure is proposed based on the traditional Class-F structure with all even harmonics and the third harmonic effectively controlled, respectively. Also the stepped-impedance matching method is applied to the third harmonic control network, which has a positive effect on the expansion bandwidth. CGH40025F power transistor is utilized to build the power amplifier working at 0.8 to 2.7 GHz, with the measured saturated output power 20–50 W, drain efficiency 52%–76%, and gain level above 10 dB. The second and the third harmonic suppression levels are maintained at –16 to –36 dBc and –16 to –33 dBc, respectively. The simulation and the measurement results of the proposed power amplifier show good consistency.

### 1. Introduction

With the rapid development of wireless communication technology, the requirement of speed and frequency resource of communication is increasing dramatically [1]. For example, in the fourth-generation mobile communication technology, radio frequency power amplifiers used in base stations are expected to have high performances such as high efficiency and high output power. In order to improve the energy efficiency and signal coverage area of communication systems, efficiency and output power of power amplifier have been a hot topic since 2000 years [2–4]. At the same time, so as to cover more carriers' operating frequency bands, power amplifiers are required to have good performances of broadband. Thus, the importance of power amplifier as the most critical module in a communication system is self-evident.

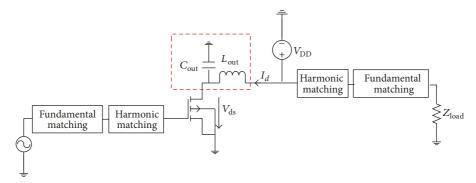

Harmonic tuning is one of key technologies to improve the efficiency and output power. Various operation classes such as Class-E [5], Class-F [6], and inverse Class-F [7] have been proposed. In particular, the Class-F operation has attracted attention due to its excellent performance [8]. A typical circuit model of Class-F power amplifier is shown in Figure 1 in which the Cout and Lout represent package parasitic effects of the transistor.

The output voltage and current of the transistor in time domain can be expressed as follows:

$$I_{d}(t) = I_{0} + \sum_{n=1}^{\infty} I_{n} \cdot \cos(n\omega t + \xi_{n})$$

$$V_{ds}(t) = V_{DD} - \sum_{n=1}^{\infty} V_{n} \cdot \cos(n\omega t + \psi_{n}),$$

(1)

where *n* is the order of the harmonics and  $\xi_n$  and  $\psi_n$  are the phases of the output current and voltage at the *n*th order, respectively. The current and voltage are both related to the impedance at a certain frequency. The impedance of each harmonic can be expressed as

$$Z_{L\cdot n} = \frac{V_n}{I_n} \cdot e^{j\phi_n},\tag{2}$$

where  $\phi_n = \psi_n - \xi_n$ .

FIGURE 1: Circuit diagram of a Class-F power amplifier model.

TABLE 1: Comparison with the state-of-the-art broadband power amplifiers.

| Ref.      | Bandwidth<br>(GHz) (%) | Power<br>(dBm) | Gain<br>(dB) | DE<br>(%)    |

|-----------|------------------------|----------------|--------------|--------------|

| [10]      | 0.5–1.8, 113           | 39-40.8        | 9-10.8       | 50-69        |

| [11]      | 1.0–2.9, 97            | >39.3          | >10.3        | >56.8        |

| [12]      | 1.9–4.3, 78            | 40-41.8        | 9–11         | 57-72        |

| [13]      | 1.4–2.7, 63            | 41 (around)    | 9 (around)   | 68 (average) |

| This work | 0.8–2.7, 109           | 43-47          | 10-14        | 52-76        |

According to the theory of Class-F power amplifiers [9], high efficiency and high output power can be anticipated when the impedance of all even harmonics is matched to zero, odd harmonics to infinite, and the fundamental to  $50 \Omega$ . However, it is extremely difficult to achieve the above requirements in real practices because of the existence of infinite orders of harmonics and the shift of the fundamental impedance caused by the parasitic effects of the package. The further analysis will focus on improving these two aspects in order to boost the performance of Class-F power amplifiers.

A new architecture has been proposed to compensate the parasitic effects of package and improve the harmonic control ability of the power amplifier. Using CGH40025F transistor, we designed a power amplifier with the proposed architecture, which operates in range from 0.8 to 2.7 GHz with a relative bandwidth of 109%. The designed power amplifier realizes saturated output power of over 43 dBm and average drain efficiency greater than 60%. The recent broadband power amplifier research works are listed in Table 1. It is obvious that this work has made great progress compared with the previous works which have been published in terms of output power, drain efficiency, frequency of operation, and gain across the whole frequency band.

### 2. Analysis and Design of Class-F Power Amplifier

2.1. Parasitic Effect Compensation. As the frequency goes higher, the parasitic effect becomes increasingly nonnegligible. Ignoring package parasitic effect will cause the mismatch of the transistor's output impedance. The control of the

fundamental impedance is given first priority to minimize the impedance mismatch since the fundamental is the main output signal.

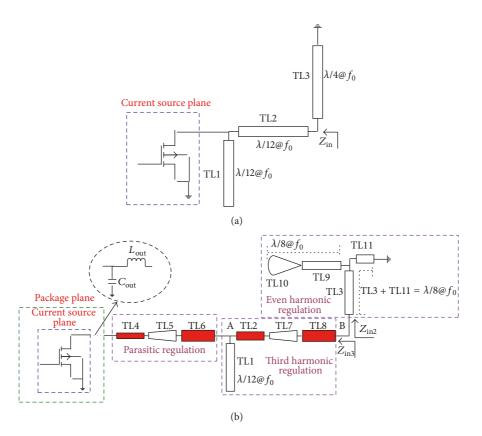

The conventional circuit of the transistor and the corresponding harmonic control network is shown in Figure 2(a) [14]. The novel structure is proposed as depicted in Figure 2(b). With full consideration of the actual package effect ( $L_{out}$  and  $C_{out}$ ), the improvement of the circuit (introducing compensation circuit TL4, TL5, and TL6) is presented so that package parasitic effect is alleviated at the fundamental frequency to a certain extent.

In the theoretical derivation of this Class-F power amplifier, the ideal reference plane is the voltage-controlled current source surface of the power transistor (Figure 2(a)). But the output pin can only reach the package plane (green dashed box) due to the physical limits of the actual package (Figure 2(b)). This position deviates from the ideal reference plane, introducing parasitic effects into actual model.

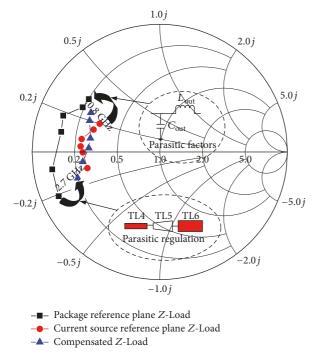

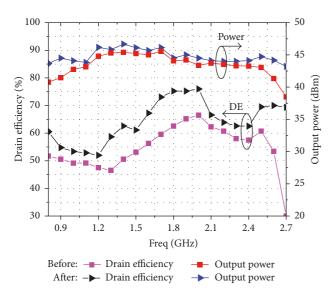

Microstrip lines TL4, TL5, and TL6 are used to adjust the electrical length and characteristic impedance so that the actual transistor's output impedance is close to the ideal output impedance without packaging. It can be observed that the measured transistor output impedance with parasitic effect (black curve) can be shifted to the compensated impedance (blue curve) by adding parasitic regulation, which is closer to the ideal simulated impedance (red curve) as illustrated in Figure 3. A measured comparison between before and after parasitic compensation is given in Figure 4. One can see that both drain efficiency and output power increase after the addition of the parasitic compensation circuit. Clearly the parasitic effect is reduced so that the fundamental impedance matching can be realized better by this design.

2.2. High-Order Harmonics Suppression. According to Figure 2(a), a conventional Class-F power amplifier by employing a high-Q harmonic control network is observed, which can only match harmonics up to the third order. This traditional harmonic control network severely limits the bandwidth as well as the ability to control higher order harmonics; hence, it affects the efficiency and output power of Class-F power amplifiers greatly [15, 16].

An improved harmonic control network design is proposed in Figure 2(b). Originating from the principle of quarter-wave impedance transformation, the input

FIGURE 2: Circuit design of (a) conventional and (b) improved harmonic control network.

impedance of the shorted-terminal TL11 combined with TL3 can be expressed as

$$Z_{4m} = jZ_{3,11} \tan\left[\frac{\pi}{4}\frac{f_{4m}}{f_0}\right] \quad m = 1, 2, 3, \dots,$$

(3)

where  $Z_{3,11}$  is the characteristic impedance of TL3 and TL11,  $f_{4m}$  is the (4*m*)th harmonic, and  $f_0$  is the fundamental frequency.

The radial line stub TL10 can maintain the same impedance characteristics over a wide bandwidth. The total electrical length of TL10 and TL9 is chosen to be  $\lambda/8$  ( $\lambda$  is the wavelength of the fundamental). The input impedance of the open-terminal TL10 combined with TL9 can be approximately expressed as

$$Z_{4m-2} = -j \frac{Z_{9,10}}{\tan\left[(\pi/4)\left(f_{4m-2}/f_0\right)\right]} \quad m = 1, 2, 3, \dots, \quad (4)$$

where  $Z_{9,10}$  is the characteristic impedance of TL9 and TL10 and  $f_{4m-2}$  is the (4m - 2)th harmonic. The input impedance  $Z_{in2}$  can be obtained from (3) and (4)

$$Z_{\text{in2}} = \begin{cases} Z_{4m-2} = 0 \\ Z_{4m} = 0 \end{cases} \qquad m = 1, 2, 3, \dots$$

(5)

As seen from (5), the impedance at all even-order harmonics is matched to zero. Considering the difficulty of matching and the limited area of the circuit layout, the odd harmonics are matched to the third order. Stepped-impedance matching technique is applied to harmonic control networks of Class-F power amplifier, which greatly reduces quality factor of the resonant network. The microstrip lines TL2, TL7, and TL8 are added to the harmonic network as adjusting auxiliary lines. Together with TL1, the third harmonic is suppressed. For TL1, the input impedance at point A can be expressed as

$$Z_A = -j \frac{Z_1}{\tan\left[(\pi/6)\left(f_3/f_0\right)\right]},$$

(6)

where  $Z_1$  is the characteristic impedance of TL1 and  $f_3$  is the third harmonic.  $Z_A$  holds zero for the third harmonic. The input impedance  $Z_{in3}$  can be expressed as

$$Z_{\text{in3}} = jZ_8 \frac{Z_2 \tan \left[6\pi/n_1\right] + Z_8 \tan \left[6\pi/n_2\right]}{Z_8 - Z_2 \tan \left[6\pi/n_1\right] \tan \left[6\pi/n_2\right]}.$$

(7)

$Z_2$  and  $Z_8$  are the characteristic impedance of TL2 and TL8, respectively. TL7 is the stepped-impedance line to reduce reflection caused by impedance mismatch. Theoretically when the total electrical length of TL2 and TL8 equals  $\lambda/12$ , the impedance of third harmonic is well maintained at high impedance region over a certain frequency range, which requires  $\lambda/n_1 + \lambda/n_2 \approx \lambda/12$ .  $\lambda/n_1$  and  $\lambda/n_2$  are the electrical lengths of TL2 and TL8, respectively.

FIGURE 3: Parasitic compensation of fundamental impedance.

FIGURE 4: Measured drain efficiency and the output power before and after parasitic compensation.

The newly proposed Class-F power amplifier topology (Figure 2(b)) is superior to the conventional structure (Figure 2(a)) in the sense that all even harmonics can be matched to zero and the impedance of the harmonics is controlled at a much broader frequency band (even harmonics are kept at low impedance and the third harmonic is kept at high impedance).

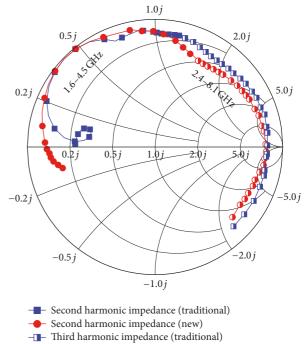

The simulated impedance of the second harmonic (1.6–5.4 GHz) and the third harmonic (2.4–8.1 GHz) are shown in Figure 5 for both topologies. Compared to the conventional structure, the new structure demonstrates that the

- Third harmonic impedance (new)

FIGURE 5: Simulated second and third harmonics impedance for conventional and improved structures.

impedance of the second harmonic and the third harmonic is better maintained in the low impedance zone and high impedance zone over the whole frequency band, respectively.

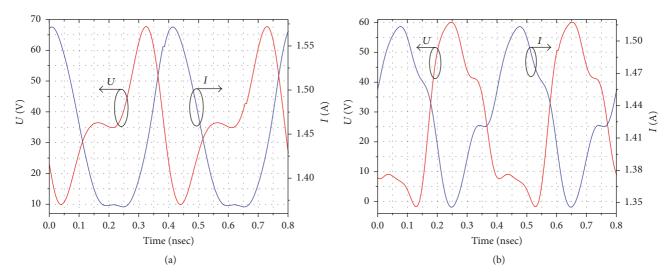

Drain current and voltage simulations for the two different topologies are displayed in Figures 6(a) and 6(b), respectively. It can be observed that the overlap of the drain current and the voltage waveform in the new topology is reduced, and therefore the efficiency and output power of the new topology get higher.

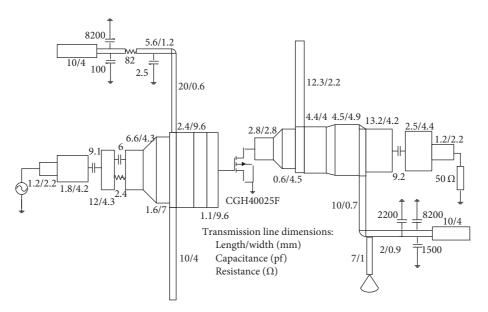

Harmonic control network is also added to the input. The impedance of the second and third harmonics is matched to zero and infinite, respectively. The fundamental impedance of the input and the output needs to be matched to  $50 \Omega$ . The final schematic of designed power amplifier is presented in Figure 7.

### 3. Fabrication and Measurement Results

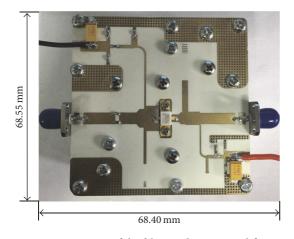

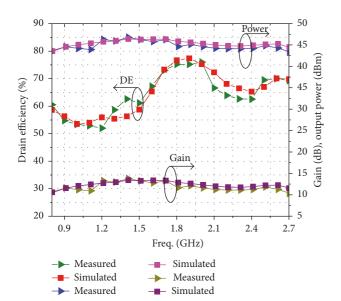

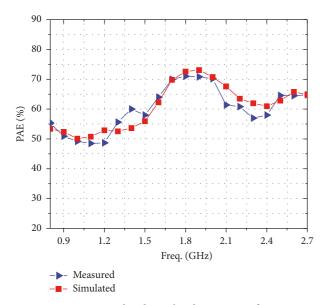

The transistor adopted in this work is CGH40025F, which is a GaN HEMT from Cree Company. The broadband power amplifier was implemented on a Rogers substrate with the dielectric constant of 3.66 and thickness of 0.762 mm, as shown in Figure 8. The gate bias is set as -2.7 V. Setting the drain voltage at 32 V instead of the typically suggested 28 V provides a higher output power at the expense of efficiency. Measurements were made using a continuous wave. The measurement and simulation results of output power, drain efficiency, power added efficiency (PAE), and gain are in good agreement as illustrated in Figures 9 and 10, respectively. The measured saturated output power is between 43 dBm and 47 dBm from 0.8 to 2.7 GHz giving a bandwidth of 109%.

FIGURE 6: Simulated drain current and voltage time domain waveform for (a) conventional structure and (b) improved structure.

FIGURE 7: Schematic of the complete power amplifier.

FIGURE 8: Picture of the fabricated power amplifier.

The drain efficiency and PAE are between 52%–76% and 48.5%–71%, respectively, and the gain is above 10 dB.

The maximum output power measured across the band is 47 dBm at 1.4 GHz while the minimum is 43 dBm at 2.7 GHz. The maximum drain efficiency measured across the band is 76% at 2 GHz with a maximum PAE of 71% at 1.8 GHz. Based on the results above, it is proved that the newly proposed structure is feasible in realizing broadband Class-F power amplifier with high efficiency and high output power.

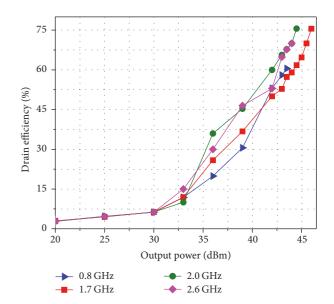

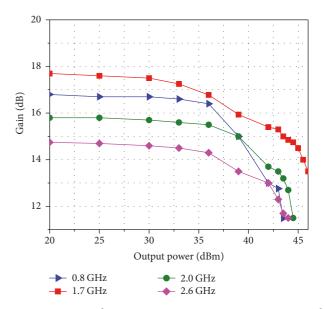

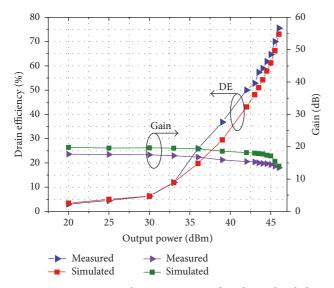

Measured drain efficiency and gain versus output power at 0.8, 1.7, 2.0, and 2.6 GHz are shown in Figures 11 and 12, respectively. These frequencies are chosen to cover our interested frequency range with 0.8 GHz and 2.6 GHz being the lower and upper frequencies, 1.7 GHz being the center frequency, and 2 GHz being the location where drain efficiency is maximal. The drain efficiency gradually increases with the

FIGURE 9: Measured and simulated output power, drive efficiency, and gain versus frequency.

FIGURE 10: Measured and simulated PAE versus frequency.

increase of output power as depicted in Figure 11. High drain efficiency can be obtained at high output power.

One can see that when the output power reaches a specific value, the gain begins to drop quickly while the efficiency is increased as shown in Figures 12 and 11. The decrease of gain suggests the loss of linearity. It is also demonstrated that high efficiency and high linearity are so difficult to obtain simultaneously that we have to trade off the design of power amplifiers.

Figure 13 shows the measured and simulated drain efficiency and gain versus output power at 1.7 GHz. When the output power arrives at 43 dBm and above, the gain begins to decline but the efficiency continues to increase. Simulation

FIGURE 11: Measured drain efficiency versus output power at 0.8, 1.7, 2.0, and 2.6 GHz.

FIGURE 12: Measured gain versus output power at 0.8, 1.7, 2.0, and 2.6 GHz.

and measurement agree with each other in the acceptable range.

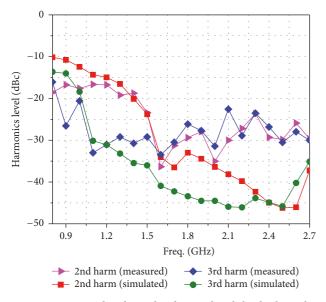

Figure 14 shows simulated and measured second and third harmonic distortion power levels relative to the fundamental frequency output power. Harmonic suppression level at lower frequencies is not as satisfying as at high frequencies, because the relative test band is wide and harmonics of low frequencies are included in high fundamental frequencies inevitably during measurement. In order to better match the fundamental, we need to compromise on the lower frequency harmonics impedance matching. The second and the third harmonic suppression levels are maintained at -16 to -36 dBc and -16 to -33 dBc, respectively.

FIGURE 13: Comparison between measured and simulated drain efficiency and gain versus output power at 1.7 GHz.

FIGURE 14: Measured and simulated second and third relative harmonics level. The results are presented relative to the fundamental frequency output power.

### 4. Conclusions

In this paper, a novel architecture is proposed to compensate the fundamental impedance offset due to package parasitic and suppress harmonics to achieve high efficiency and high output power. The feasibility of the structure was verified by measurement results. The measured results show that the relative bandwidth is 109% in the range of 0.8–2.7 GHz, the saturated output power is over 43 dBm, the average efficiency is more than 60%, and the gain is above 10 dB. The results manifest remarkable advantages over traditional Class-F power amplifiers.

### **Conflicts of Interest**

The authors declare that they have no conflicts of interest.

#### Acknowledgments

This work is supported by Key Project of Zhejiang Provincial Natural Science Foundation of China (no. LZ16F010001), Zhejiang Provincial Public Technology Research Project (no. 2016C31070), and National Natural Science Foundation of China (no. 61306100).

#### References

- P. Wright, J. Lees, J. Benedikt, P. J. Tasker, and S. C. Cripps, "A methodology for realizing high efficiency class-J in a linear and broadband PA," *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 12, pp. 3196–3204, 2009.

- [2] A. Inoue, T. Heima, A. Ohta, R. Hattori, and Y. Mitsui, "Analysis of class-F and inverse class-F amplifiers," in *Proceedings of the IEEE MTT-S International in Microwave Symposium Digest*, vol. 2, pp. 775–778, June 2000.

- [3] S. Goto, T. Kunii, A. Ohta et al., "Effect of bias condition and input harmonic termination on high efficiency inverse class-F amplifiers," in *Proceedings of the 31st European Microwave Conference*, September 2001.

- [4] Z. Kaczmarczyk, "High-efficiency Class E, EF2, and E/F3 inverters," *IEEE Transactions on Industrial Electronics*, vol. 53, no. 5, pp. 1584–1593, 2006.

- [5] T. A. Filipek, "Design and optimization of high efficiency GaN HEMT class-E power amplifiers," in *Proceedings of the 35th IEEE Region 10 Conference, TENCON 2015*, mac, November 2015.

- [6] J. Lin, Z. Zhang, K. Yu et al., "A linearity enhanced broadband class-F power amplifier with high harmonic suppressed matching circuits for S-band applications," in *Proceedings of the Microwave and Millimeter Wave Technology (ICMMT) International Conference*, vol. 1, pp. 270–273, 2016.

- [7] L. Dong, S. He, F. You, and Q. Lei, "High-efficiency class-F-1 power amplifier design with input harmonic manipulation," in *Proceedings of the 2012 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications, PAWR 2012*, pp. 1–4, USA, January 2012.

- [8] N. Tuffy, L. Guan, A. Zhu, and T. J. Brazil, "A simplified broadband design methodology for linearized high-efficiency continuous class-F power amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 6, pp. 1952–1963, 2012.

- [9] M. Hayati, A. Sheikhi, and A. Grebennikov, "Class-F power amplifier with high power added efficiency using bowtieshaped harmonic control circuit," *IEEE Microwave and Wireless Components Letters*, vol. 25, no. 2, pp. 133–135, 2015.

- [10] K. Mimis, K. A. Morris, S. Bensmida, and J. P. McGeehan, "Multichannel and wideband power amplifier design methodology for 4G communication systems based on hybrid class-J operation," *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 8, pp. 2562–2570, 2012.

- [11] T. Canning, P. J. Tasker, and S. C. Cripps, "Continuous mode power amplifier design using harmonic clipping contours: theory and practice," *IEEE Transactions on Microwave Theory* and Techniques, vol. 62, no. 1, pp. 100–110, 2014.

- [12] P. Saad, C. Fager, H. Cao, H. Zirath, and K. Andersson, "Design of a highly efficient 2-4-GHz octave bandwidth GaN-HEMT power amplifier," *IEEE Transactions on Microwave Theory and Techniques*, vol. 58, no. 7, pp. 1677–1685, 2010.

- [13] A. Grebennikov, "High-Efficiency Class-E Power Amplifier with Shunt Capacitance and Shunt Filter," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 63, no. 1, pp. 12–22, 2016.

- [14] S. F. Ooi, S. Gao, A. Sambell, D. Smith, and P. Butterworth, "High efficiency class-F Power Amplifier design," in *Proceedings* of the 2004 High Frequency Postgraduate Student Colloquium, pp. 113–118, gbr, September 2004.

- [15] Y. Wang, W. L. Fu, and Y. Z. Dong, "A 5.8 GHz class-F GaN power amplifier for solar power satellite," in *Proceedings of the IEEE International Conference on*, pp. 597–599, 2015.

- [16] T. Sharma, R. Darraji, and F. Ghannouchi, "Design methodology of high-efficiency contiguous mode harmonically tuned power amplifiers," in *Proceedings of the IEEE Radio and Wireless Symposium, RWS 2016*, pp. 149-150, usa, January 2016.

Submit your manuscripts at https://www.hindawi.com

Journal of Electrical and Computer Engineering

International Journal of Chemical Engineering

International Journal of Antennas and Propagation

Active and Passive Electronic Components

Modelling & Simulation in Engineering

Shock and Vibration

Advances in Acoustics and Vibration