DATA ADAPTOR UNIT FOR AN ELECTRONIC EXCHANGE:

SYSTEM DESIGN AND SIMULATION STUDY

KASPER REININK

A Dissertation submitted to the Faculty of Engineering, University of the Witwatersrand, Johannesburg, for the Degree of Master of Science in Engineering

Johannesburg 1981

a formation and the state of th

## ABSTRACT

The development of pulse code modulation systems and electronic exchanges, together with the increase in volume of data traffic, have made it desirable to establish a means for handling both voice and data traffic in the telephone network. A technique is required whereby integrated voice and data switching may be accomplished in an electronic exchange.

THE REPORT OF

H

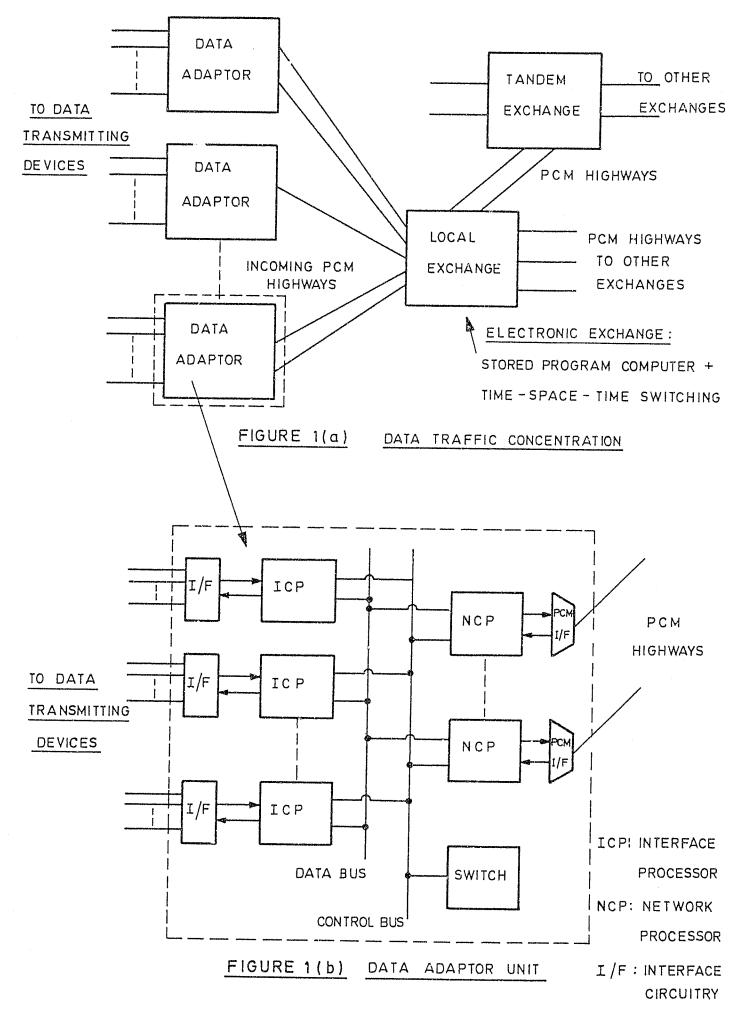

It is proposed that a data adaptor unit be incorporated in electronic exchanges for the purpose of concentrating data traffic onto PCM highways. A conceptual design for the architecture of such a unit is presented and its performance evaluated. The protocols for connecting data adaptors into a network, and the use of flow control procedures for regulating data traffic within the network, are described. The hardware implementation of the unit is not considered.

The proposed data adaptor operates on the packet switching principle. It is comprised of three types of modules each dedicated to carrying out a particular communication function. The modules are the interface processor that interacts with data transmitting devices, the network processor for sending data over PCM channels between adaptors, and the supervisory processor for regulating activities within the adaptor unit.

- i -

Specific features developed for the adaptor unit include a protocol allowing the sharing of a physical PCM channel by several logical paths, as well as the transmission of only incorrect packets; the partitioning of memory along topological lines to aid in flow control. An algorithm, situated in the supervisory processor, is presented for controlling packet exchanges between modules in the adaptor.

A simulation facility, written in FORTRAN IV, was developed to determine the performance capabilities of the data adaptor. Two networks based on the proposed unit were simulated. Response and throughput measurements have been listed. The effect of certain model parameters on network performance, such as the packet retransmission interval, were examined. The simulation plots listed indicate the characteristics of a data network consisting of adaptor units.

Comparison of the performance results attained by the hypothetical network with those of practical networks, indicates that the proposed data adaptor has the response and throughput capability to serve as the basis for a data traffic system. A unit path length response of 18 milliseconds was obtained for the hypothetical network at mean line utilization 0,46. The channel capacity was 64000 bits per second, and the mean packet size 470 bits.

the tot

A STATE OF A

- ii -

I hereby declare that this dissertation is my own work and that it has not previously been submitted for a degree at any University

KR\_h

K Reinink

1.1.1.1

### ACKNOWLEDGEMENTS

The work described in this dissertation was carried out in the Electrical Engineering Department at the University of the Witwatersrand, Johannesburg.

The author extends his sincere appreciation to the following people for their support and guidance:

Professor H E Hanrahan, Department of Electrical Engineering, for his supervision of the work.

Professor M G Rodd, Department of Electrical Engineering, for his constructive comments on the draft presentation.

The author expresses his gratitude to the Council for Scientific and Industrial Research, and the University of the Witwatersrand, for their generous financial assistance.

Finally, the author thanks Mrs Brooks for typing the dissertation.

# CONTENTS

Page No

۲,

| CHAPTER 1 | Data Adaptor for an Electronic Exchange   | 1  |

|-----------|-------------------------------------------|----|

| 1.1       | Introduction                              | l  |

| 1.2       | Review of Data Transmission               | 3  |

| 1.3       | Description of the Data Adaptor Unit      | 7  |

|           | 1.3.1 The Nodal Architecture              | 7  |

|           | 1.3.2 The Network Protocols               | 10 |

|           | 1.3.3 Flow Control                        | 12 |

| 1.4       | Chapter Survey                            | 13 |

|           |                                           |    |

| CHAPTER 2 | Flow Control Measures                     | 15 |

| 2.1       | Introduction                              | 15 |

| 2.2       | Resource Sharing in Packet Networks       | 16 |

| 2.3       | Characteristics of Packet Networks        | 18 |

| 2.4       | Global Flow Control                       | 21 |

| 2.5       | Local Flow Control                        | 23 |

|           | 2.5.1 Pricrity Allocation Technique       | 23 |

|           | 2.5.2 Memory Partitioning Technique       | 27 |

| 2.6       | Review                                    | 29 |

|           |                                           |    |

| CHAPTER 3 | Simulation Facility                       | 30 |

| 3.1       | Introduction                              | 30 |

| 3.2       | The Simulation Structure                  | 31 |

|           | 3.2.1 Initialization Block                | 32 |

|           | 3.2.2 Execution Block                     | 32 |

|           | 3.2.3 Description of Simulation Modules   | 32 |

|           | 3.2.4 Module Communication                | 36 |

| 3.3       | Input Parameters for the Simulation       | 38 |

|           | 3.3.1 Network Topology Simulated          | 38 |

|           | 3.3.2 Traffic Control by Virtual Circuits | 38 |

|           | 3.3.3 Link Specification                  | 40 |

|           | 3.3.4 Node-Processor Mapping              | 41 |

|           | 3.3.5 Packet Route Map                    | 10 |

|           |                                                  | Page No |

|-----------|--------------------------------------------------|---------|

|           | 3.3.6 Bus Multiplexing Table                     | 43      |

|           | 3.3.7 Partition Table                            | 44      |

|           | 3.3.8 Network Parameters                         | 45      |

|           | 3.3.9 Summary                                    | 45      |

| 3.4       | The Nodal Simulation Model                       | 48      |

|           | 3.4.1 Simulation of Nodal Replicas               | 48      |

|           | 3.4.2 Description of the Block Structure         | 50      |

|           | 3.4.3 Implementation of Models Using Arrays      | 51      |

| 3.5       | Review                                           | 52      |

| CHAPTER 4 | The Interface Communication Processor            | 53      |

| 4.1       | Introduction                                     | 53      |

| 4.2       | User-Network Protocol                            | 56      |

|           | 4.2.1 Source Host to ICP Interaction             | 59      |

|           | 4.2.2 Destination/Source ICP Interaction         | 60      |

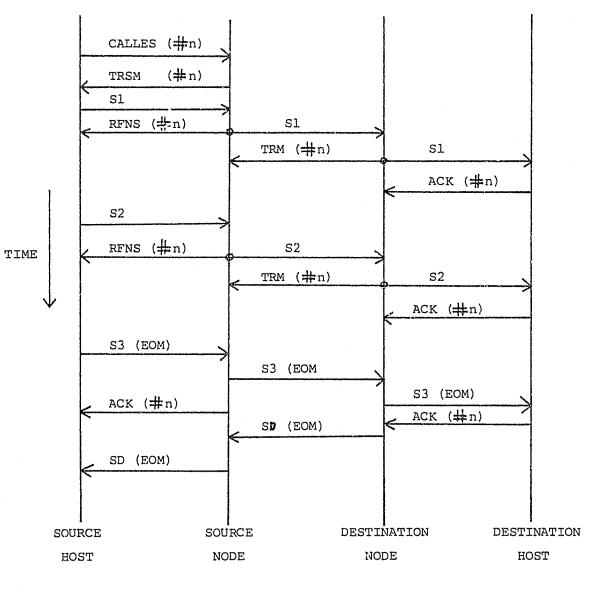

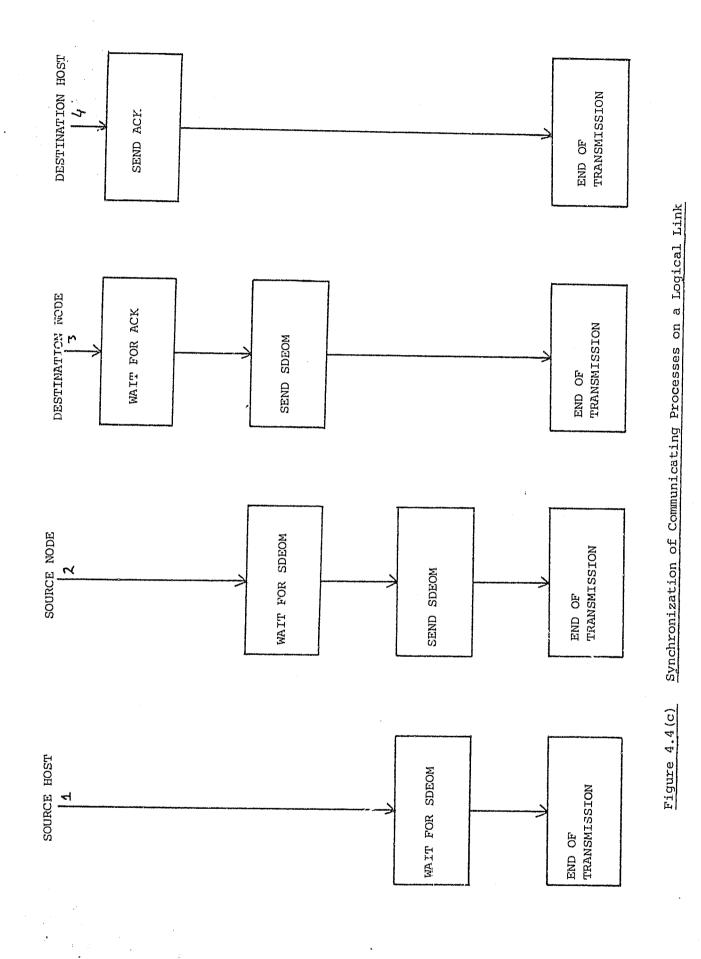

|           | 4.2.3 Synchronization of Processes               | 60      |

|           | 4.2.4 Pipelining Data Through the Network        | 64      |

|           | 4.2.5 Termination of the Transmission            | 66      |

|           | 4.2.6 Segment Sizes                              | 66      |

|           | 4.2.7 Source ICP to Destination ICP Transmission | 67      |

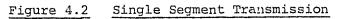

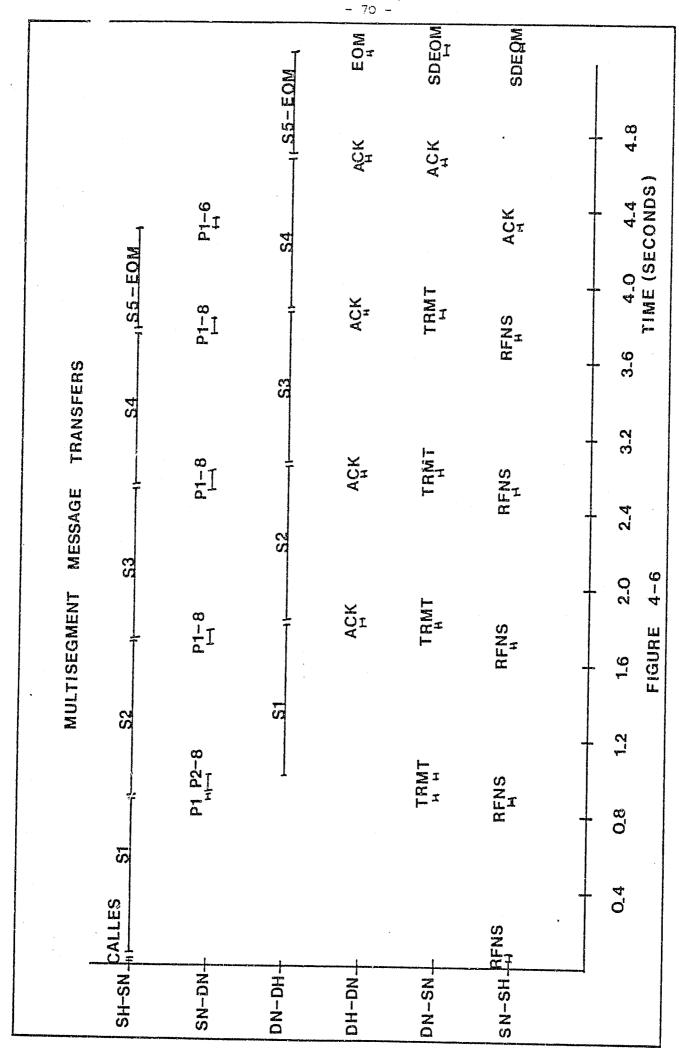

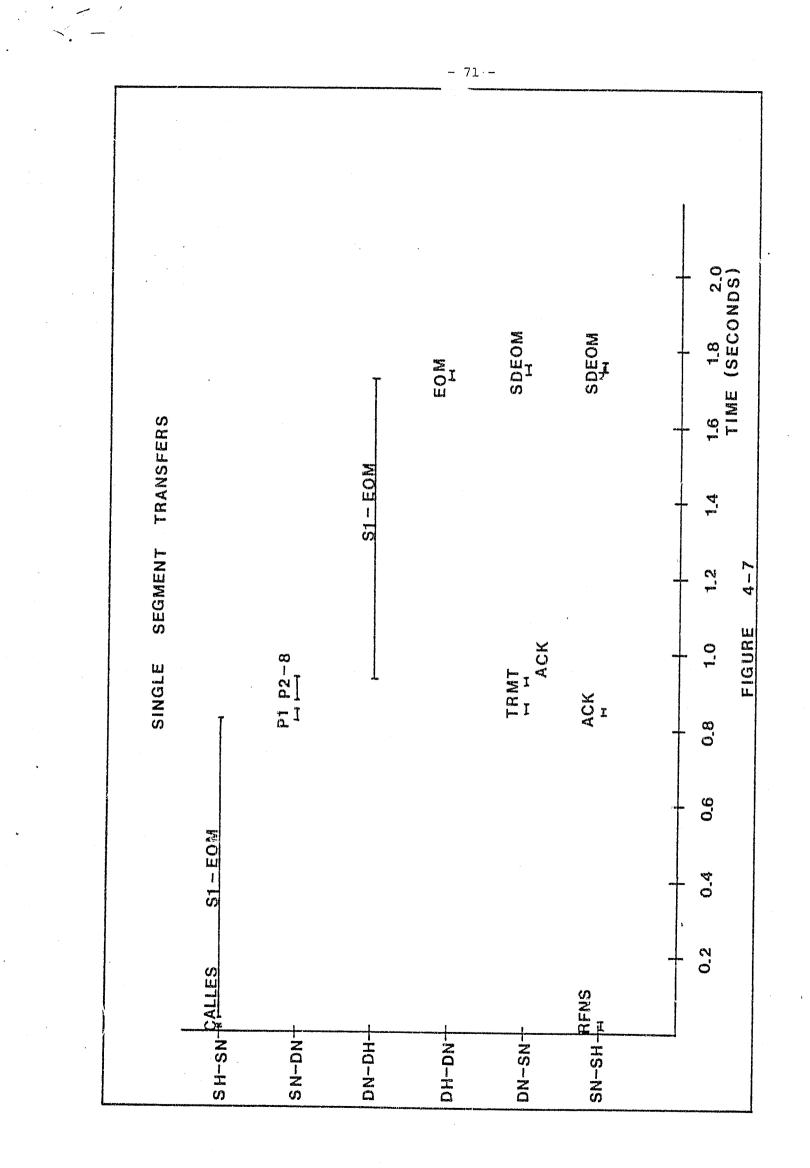

|           | 4.2.8 Demonstration of ICP Protocols             | 68      |

|           | 4.2.9 The ICP Protocol as a Flow Control Measure | 76      |

|           | 4.2.10 Summary                                   | 77      |

| 4.3       | Storage Management                               | 78      |

|           | 4.3.1 ICP Memory Partitions                      | 79      |

|           | 4.3.2 Packet and Buffer Sizes                    | 80      |

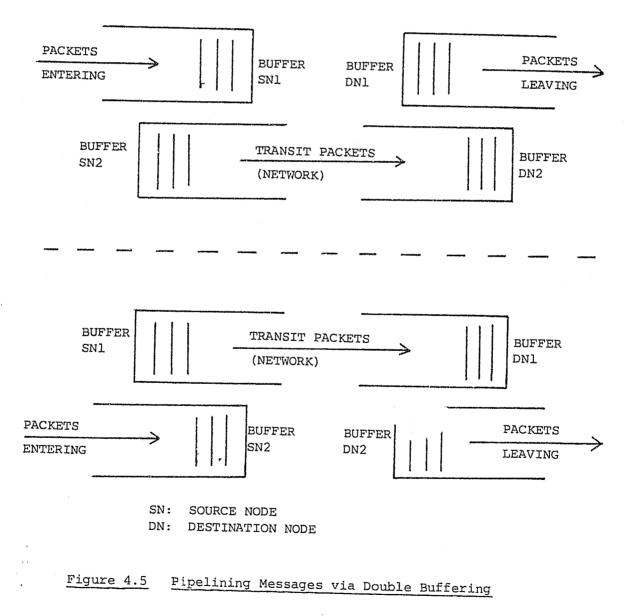

|           | 4.3.3 Message Buffering                          | 83      |

|           | 4.3.4 Double Buffering Concert                   | 83      |

|           | 4.3.5 Reserving Buffers                          | 85      |

|           | 4.3.6 Summary                                    | 89      |

| 4.4       | Review                                           | 89      |

| CHAPTER 5 | Channel Controller                               | 90      |

| 5.1       | Introduction                                     | 90      |

| 5.2       | Node-to-Node Protocol                            | 91      |

|           | 5.2.1 Link Throughput                            | 92      |

|           | 5.2.2 Outline of the Protocol                    | 93      |

Street of the local division of the local di

the second s

|           |                                                  | Page No     |

|-----------|--------------------------------------------------|-------------|

|           | 5.2.3 Logical Path Concept                       | 93          |

|           | 5.2.4 Synchronization Flags                      | 96          |

|           | 5.2.5 Packet Frame Format                        | 99          |

|           | 5.2.6 Valid Flag Settings                        | 101         |

|           | 5.2.7 Summary                                    | 102         |

| 5.3       | Storage Allocation                               | 103         |

| 5.5       | 5.3.1 Store-and-Forward Buffer Blocking          | 103         |

|           | 5.3.2 Memory Partitions                          | 104         |

|           | 5.3.3 Memory Partitioning According to Topology  | 105         |

|           | 5.3.4 Packet Frame Format and Memory Partitionin | 108 IO8     |

| 5.4       | Performance of the Link                          | 109         |

|           | 5.4.1 Parameters for the Channel Simulation      | 111         |

|           | 5.4.2 Channel Performance                        | 114         |

|           | 5.4.3 Channel Response                           | 114         |

|           | 5.4.4 Percentage Packets Rejected                | 115         |

|           | 5.4.5 Comparison with Analytic Response Calculat | tion 120    |

|           | 5.4.6 Discussion on Unequal Input/Output Rates t | to Link 123 |

|           | 5.4.7 Summary                                    | 128         |

| 5.3       | Review                                           | 128         |

|           |                                                  |             |

| CHAPTER 6 | Communication Processor Architecture             | .130        |

| 6.1       | Introduction                                     | 130         |

| 6.2       | Outline of Nodal Architecture                    | 130         |

| 6.3       | The Bus Access Problem                           | 134         |

| 6.4       | The Function of the Switching Processor          | 135         |

| 6.5       | Nodal Timing                                     | 138         |

| 6.6       | The Cycle Diagram                                | 141         |

| 6.7       | Description of the Sort Algorithm                | 146         |

|           | 6.7.1 Classification of the Status Data          | 146         |

|           | 6.7.2 Sort Algorithm                             | 149         |

| 6.8       | Description of the Switch Algorithm              | 153         |

|           | 6.8.1 Notation                                   | 154         |

|           | 6.8.2 Switch Algorithm                           | 155         |

| 6.9       | Description of the Format Algorithm              | 1.62        |

|           | 6.9.1 Data Bus Access Control                    | 163         |

|           | 6.9.2 Synchronization of Data-and-Switch Events  | s 164       |

|           |                                                  | Page No |

|-----------|--------------------------------------------------|---------|

|           | 6.9.3 Format Algorithm                           | 168     |

| 6.10      | Review                                           | 174     |

|           |                                                  |         |

| CHAPTER 7 | Network Performance                              | 176     |

| 7.1       | Introduction                                     | 176     |

| 7.2       | Discussion on the Topologies Simulated           | 176     |

|           | 7.2.1 Network Parameters                         | 178     |

|           | 7.2.2 Assumptions made in the Simulation         | 181     |

|           | 7.2.3 Performance Indices used in the Simulation | 182     |

| 7.3       | Performance of the Network                       | 184     |

|           | 7.3.1 Notational Details                         | 184     |

|           | 7.3.2 Simulation Run-Time                        | 184     |

|           | 7.3.3 Response and Throughput                    | 191     |

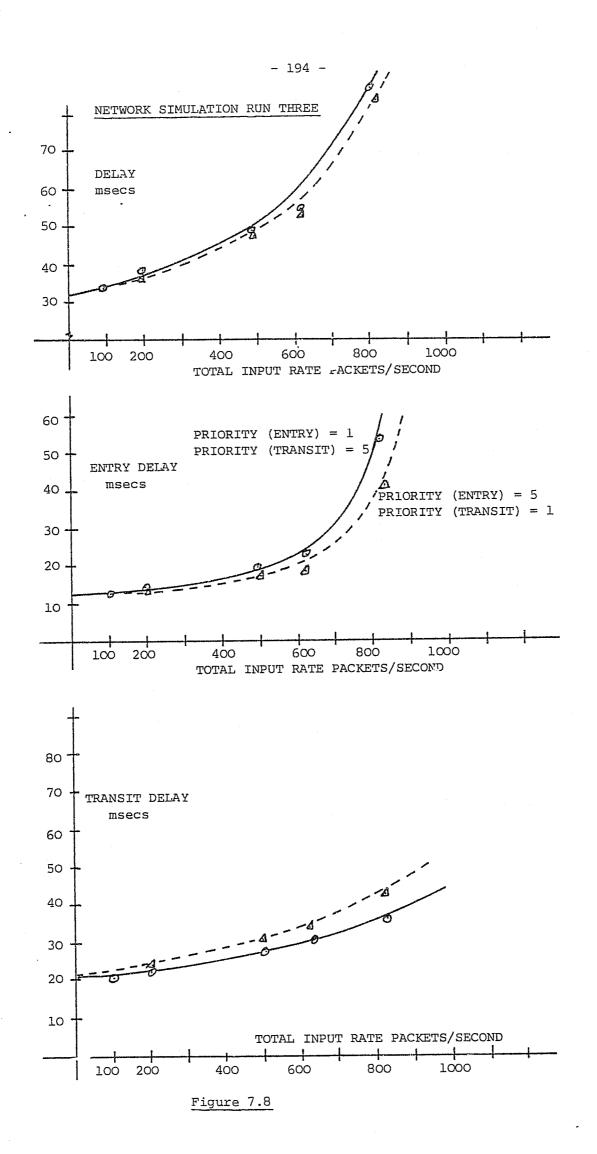

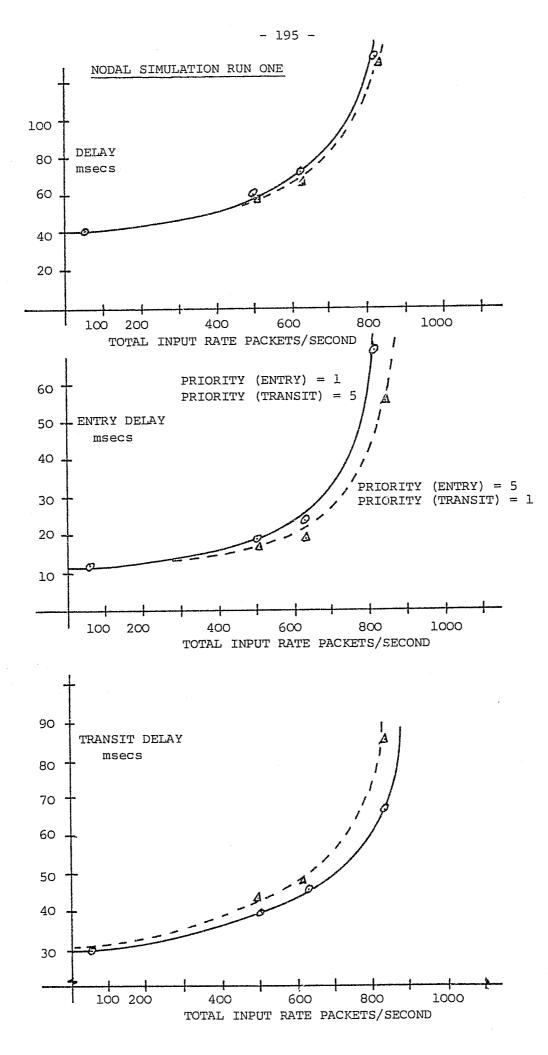

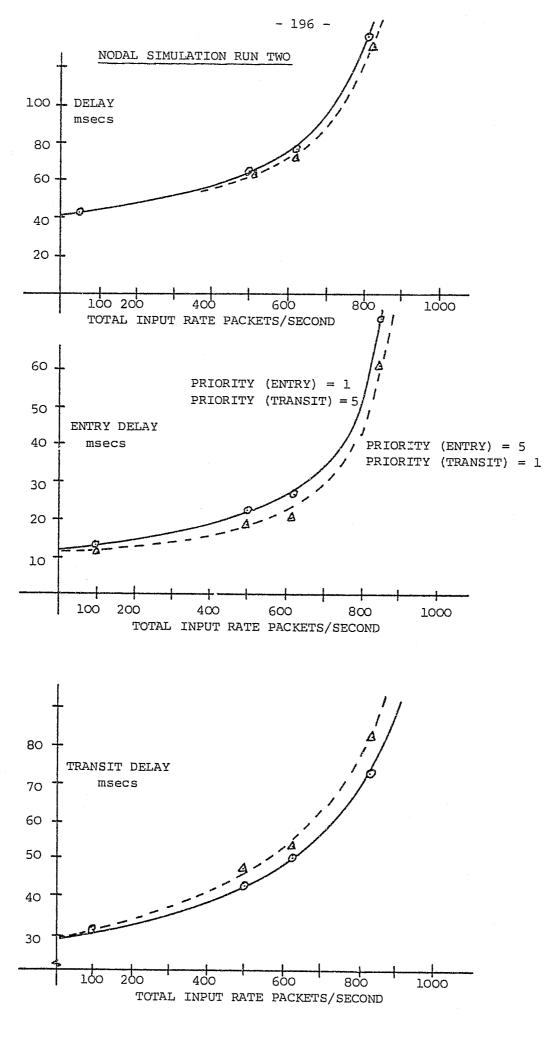

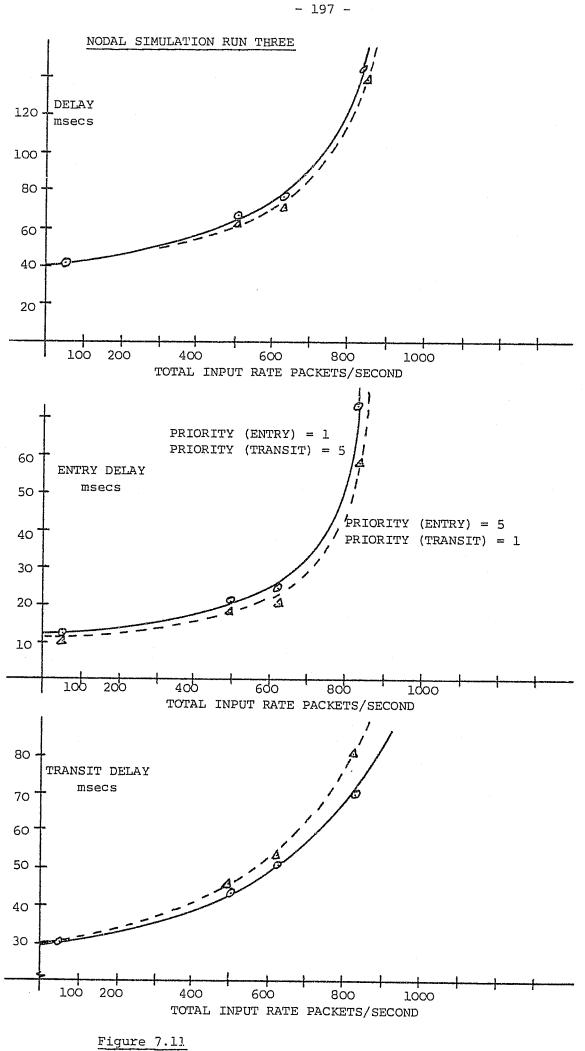

|           | 7.3.4 Switching Algorithm Priority Variations    | 204     |

|           | 7.3.5 Review Concerning Nodal Characteristics    | 209     |

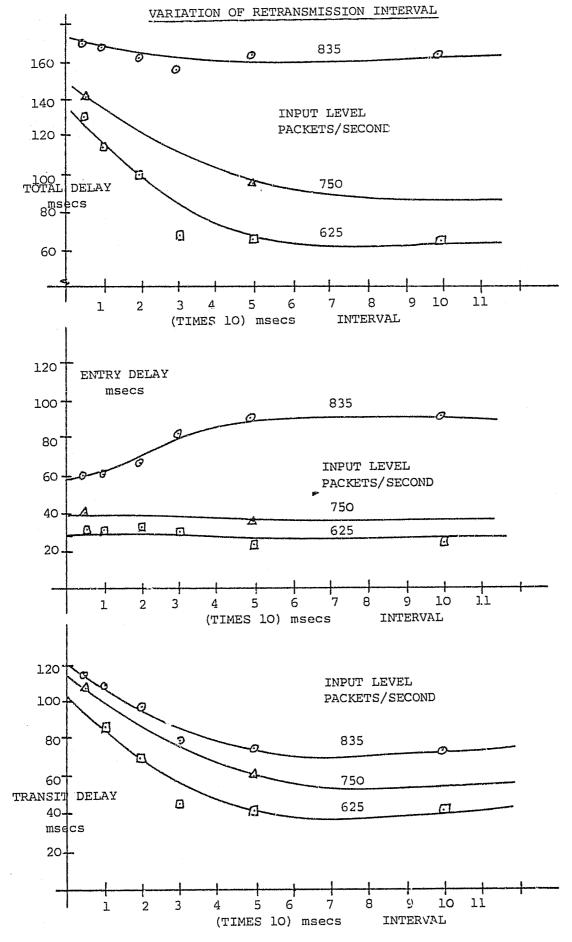

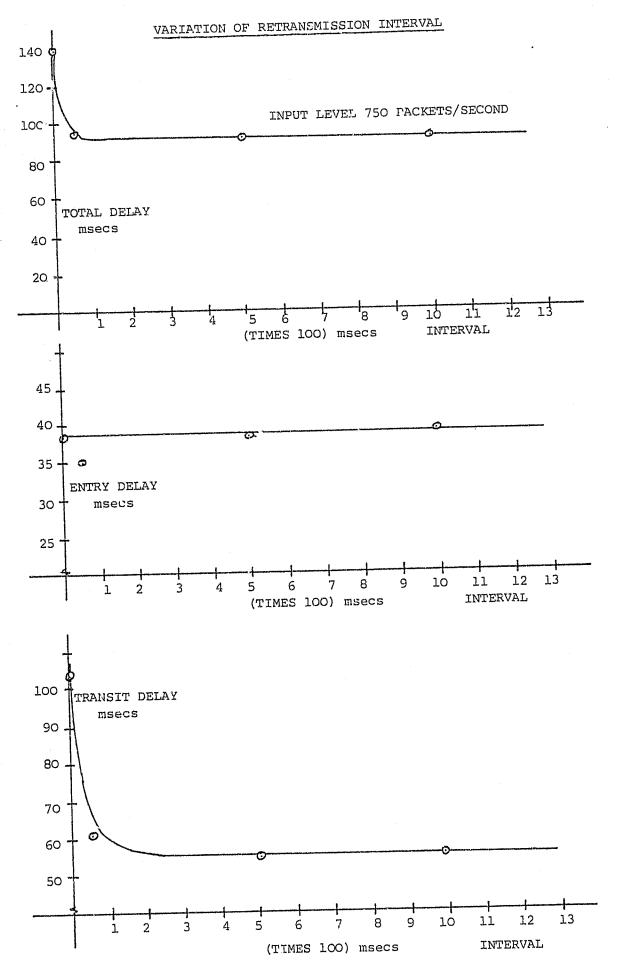

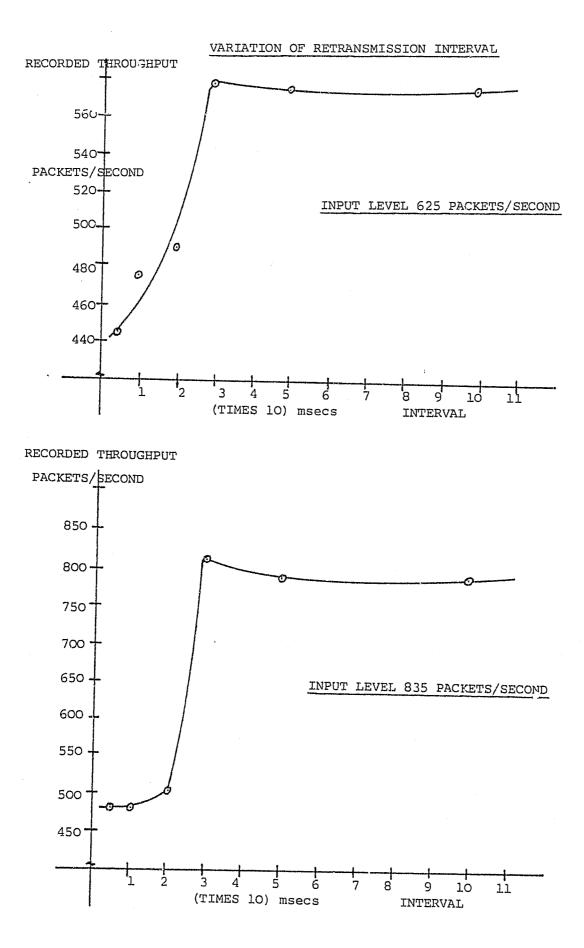

|           | 7.3.6 Variation of the Retransmission Interval   | 209     |

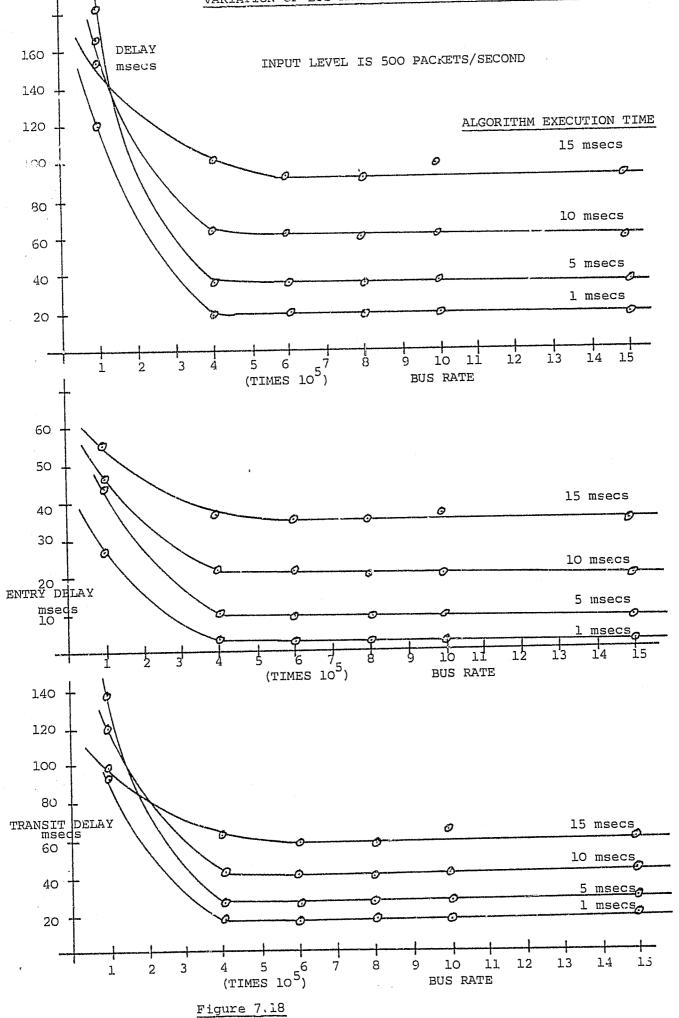

|           | 7.3.7 Variation of Bus Rate and Algorithm Period | 215     |

|           | 7.3.8 Nodal Capacity                             | 222     |

| 7.4       | Review                                           | 227     |

|           |                                                  |         |

| CHAPTER 8 | Conclusions                                      | 228     |

| 8.1       | Discussion                                       | 228     |

| 8.2       | Conclusions                                      | 229     |

| 8.3       | Future Developments                              | 234     |

|           | 8.3.1 Implementation of the Data Adaptor         | 234     |

|           | 8.3.2 Alternate Nodal Architectures              | 235     |

|           | 8.3.3 Developments at the Network Level          | 236     |

|            |                                   | Page NO |

|------------|-----------------------------------|---------|

| APPENDIX A | Array Definitions                 | 237     |

| APPENDIX B | Data Network Simulation Programs  | 256     |

| APPENDIX C | Parameters for Network Simulation | 359     |

| APPENDIX D | Parameters for Nodal Simulation   | 365     |

| APPENDIX E | Simulation Results                | 372     |

# TABLES

| 3.1        | Logical Link and Virtual Circuit Parameters   | 41       |

|------------|-----------------------------------------------|----------|

| 3.2        | Nodal Mappings                                | 41       |

| 3.3<br>3.4 | NCP-to-NCP Connection<br>Route Map            | 42<br>42 |

| 3.5        | Bus Multiplexing                              | 43       |

| 3.6        | Partition Table                               | 45       |

| 3.7        | Network Parameters                            | 46       |

|            |                                               |          |

| 4.1        | Notation for Transmission Figures             | 57       |

| 4.2        | Segment, Buffer and Packet Size Relationships | 84       |

|            |                                               |          |

| 5.1        | Channel Response                              | 127      |

|            |                                               |          |

| 7.1        | Response Characteristic                       | 198      |

| 7.2        | Node 1 Performance                            | 202      |

| 7.3        | Channel Utilizations                          | 226      |

|            |                                               |          |

| 8.1        | Performance of Networks                       | 232      |

| <b>0</b> 7 | Natwork Response Times                        | 233      |

#### CHAPTER 1

### DATA ADAPTOR FOR AN ELECTRONIC EXCHANGE

# 1.1 Introduction

The introduction of pulse code modulation (PCM) techniques and electronic exchanges for both the transmission and switching of information has led to a shift in thinking away from frequency division multiplexing to that of time division multiplexing systems. Whereas, in conventional exchanges, computers and terminals required modems to transmit their information over telephone lines, the PCM exchange system requires no such devices since all information is transmitted in digital fashion.

The 30/32 PCM system allows for a higher transmission rate than the existing rates of 4800 to 9600 bits per second at which data travel over the analogue lines.<sup>(2)</sup> This system consists of thirty speech and two control channels for signalling purposes, each of capacity 64000 bits per second.<sup>(1,2)</sup> Switching takes place via time-space-time division multiplexing, to connect the various subscribers of the network.

Developments such as terminal inquiry systems, bulk data transmission in the form of files, facsimile mail transmission and electronic fund transfer, means that the volume of data traffic exchanged between geographically separated devices is expected to increase significantly.<sup>(1)</sup> The transmission of data will become a major source of traffic alongside that of voice communications.

- 1 -

### CHAPTER 1

### DATA ADAPTOR FOR AN ELECTRONIC EXCHANGE

## 1.1 Introduction

The introduction of pulse code modulation (PCM) techniques and electronic exchanges for both the transmission and switching of information has led to a shift in thinking away from frequency division multiplexing to that of time division multiplexing systems. Whereas, in conventional exchanges, computers and terminals required modems to transmit their information over telephone lines, the PCM exchange system requires no such devices since all information is transmitted in digital fashion.

The 30/32 PCM system allows for a higher transmission rate than the existing rates of 4800 to 9600 bits per second at which data travel over the analogue lines.<sup>(2)</sup> This system consists of thirty speech and two control channels for signalline eurposes, each of capacity 64000 bits per second.<sup>(1,2)</sup> Switching takes place via time-space-time division multiplexing, to connect the various subscribers of the network.

Developments such as terminal inquiry systems, bulk data transmission in the form of files, facsimile mail transmission and electronic fund transfer, means that the volume of data traffic exchanged between geographically separated devices is expected to increase significantly.<sup>(1)</sup> The transmission of data will become a major source of traffic alongside that of voice communications.

- 1 -

The above considerations imply that the use of a PCM telephone network would result in the rapid assimilation of most forms of data traffic. It must be kept in mind, however, that telephone networks, PCM or otherwise, have been designed in the first place to facilitate the handling of voice traffic.

There exist certain differences in the characterisation of voice and data traffic. The transmission of data usually occurs in bursts, whereas the transmission rate in telephone channels is constant. Different coding techniques are made use of in data communications. Widespread channel capacities ranging from a few bits per second to (ideally) millions of bits per second are required. Telephone traffic requires only a single fixed capacity channel.

Certain requirements are to be met if communication between computers is to tak place. Examples are, negligible delay in setting up a call, provision for receiving messages at all times from remote terminals and other centres, automatic code and format translation.

The introduction of certain improved technologies over the past few years means that alternative solutions may be possible for data transmission, satisfying computer communication demands. The introduction of TDM techniques for information transmission in telephone networks has led to increased throughput capabilities up to 64000 bits per second per channel. The cost of processing and storing data has decreased to such an extent that it has become feasible to

- 2 -

dynamically allocate communication resources, making it possible to integrate traffic requiring a variety of bandwidths within a single network.

A technique is required wnereby integrated voice and data switching may be accomplished in an electronic exchange that makes use of pulse-code-modulation channels for information transmission.

## 1.2 Review of Data Transmission

A DESCRIPTION OF A DESC

A Sheek and a sheek and a sheek a sheek

Three types of network have been used for the transmission of data traffic: (3)

- Circuit switching systems that require a complete path to be set up from end to end, and only when the connection has been established may messages be multiplexed into the system.

Blocking of calls and therefore call connection times may become a problem.

- (2) Message switching that requires bulk storage devices for the buffering of entire messages before data is forwarded to the destination; these systems are generally more suitable for large file transfers.

- (3) Packet switching systems where a message is divided into shorter packets, each of which works its way through the network from node to node. The packet-switch method possesses

- 3 -

the capability of satisfying most of the requirements for adequate computer-communication.

It is a characteristic of packet-switching that, once a call has been set up, the channel resources are only used when a device transmits a message. When the pair of subscriber devices are idle, the channel may be allocated to other users. Provision is made for receiving messages at all times without on each occasion proceeding through the motions of call connection. Code and format translations are possible.<sup>(4)</sup>

The differences between computer and telephone type traffic have resulted in various solutions to the data transmission problem. These include:

- the use of modems for transmitting data over the analogue lines of the public telephone system,

- (2) the use of circuit-switch based networks for data transmission. The Electronic Data Switching System makes use of PCM transmission links and circuit switching data exchanges that include synchronous data multiplexers. <sup>(5)</sup> DATRAN is a specialized common carrier operating a fast-connect switched data network, switching carried out by means of computercontrolled time-space-time division multiplexing facilities. <sup>(6)</sup>

- 4 -

- (3) dedicated message and packet-switching circuits have been constructed, e.g., commercial time-sharing networks (TYMNET), airline reservation facilities (SITA), and computer resource sharing networks (ARPA). <sup>(6)</sup> Certain manufacturers have constructed their own networks, such as IBM's Synchronous Network Architecture that enables a variety of machines to be interconnected over geographically dispersed regions. <sup>(7)</sup>

- (4) ideas of integrating voice and data traffic systems. A number of analyses have been conducted to determine the conditions for which either a packet or a circuit switch based technique is to be used, the two techniques being incorporated into a single node in a network.<sup>(8,9)</sup> The majority of integrated voice and data switching systems have been confined to introducing a master frame format of a statistical TDM facility, allocating certain slots to voice and other slots to data information.<sup>(10)</sup>

Available integrated voice/data switching facilities have been based on the circuit-switch method. Packet-switching has generally been dedicated to specific applications. Required is a system incorporating both types of methods for switching voice and data traffic.

A survey was carried out ...ain an idea of the state of communication processors. The article by Newport and Ryzlak <sup>(11)</sup> contains a review of the use of small computers for communication processing. They discuss the software and hardware requirements for network processors, data concentrators, and message-switching systems.

- 5 -

A corresponding article by Mills<sup>(12)</sup> on communication software deals with network control, message processing, and error recovery. Steel and Mattson<sup>(13)</sup> describe a 16-bit general purpose minicomputer configured to operate as a communications processor. A minicomputer-multiprocessor built specifically to meet expanding traffic requirements, and to provide extreme reliability is the Pluribus system. It performs packet-switching in the ARPA network.<sup>(14)</sup>

The above constitute a shall selection of papers on communication Most deal with the software and hardware utilities processors. applicable to minicomputers. A paper describing the technology used in the implementation of packet processors has been published by Roberts.<sup>(15)</sup> He identifies three generations of architecture. In the late 1960's limited capacity minicomputers in a single-level hierarchy distributed network were utilized. A typical example is that of the ARPA network. The second generation networks utilized more powerful minicomputers in a two-level network with central office switching centres containing minicomputer subnets, e.g., TELENET. In the late 1970's, with the advent of the microprocessor, the third generation of networks is in the process of development in the form of multi-microcomputer systems serving as nodes in a three-level hierarchy.

A report by Sarch<sup>(16)</sup> confirms that there is a trend to multimicrocomputer configurations, due to the decreasing costs of microprocessors and memory. It is pointed out, however, that careful consideration must be given to the overheads involved in managing all

- 6 -

these decentralized processors. Each microprocessor is being seen as dedicated to single tasks, such as coding, diagnostics, interfacing, etc.

The above leads to the observation that mini-computers have been largely used to date to perform the packet-switch function, that the application of multi-microcomputer architectures for communication is regarded favourably, but that not much has been done to construct such computer structures. The idea of micro-computer based modules for packet-switching in electronic exchanges indicates the possibility of realizing an integrated voice-data switching system.

### 1.3 Description of the Data Adaptor Unit

It is proposed that a data adaptor unit, based on microprocessortype elements, be included in electronic exchanges for the purpose of handling data traffic. Adaptor units will make use of the packet-switch method, which is best suited to meet computer communication requirements. A solution for the architecture of such a data adaptor is presented in terms of functional modules, the communication protocols used to link data units into a network, and flow control procedures for regulating traffic in the network.

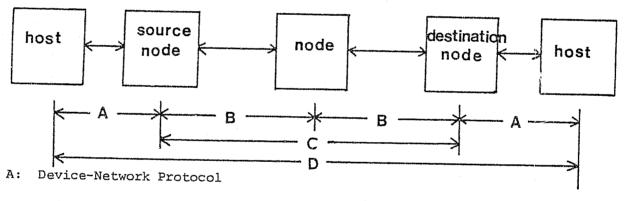

### 1.3.1 The Nodal Architecture

1

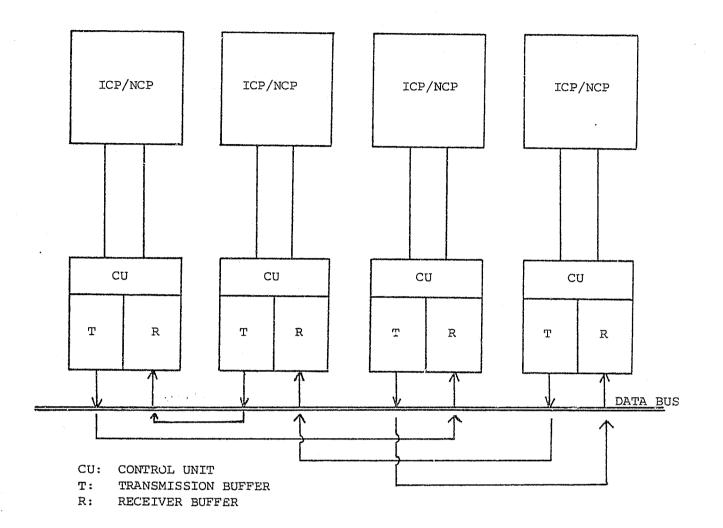

The architecture (see Figure 1.1) consists of three types of modules, interface and network processors, and a supervisory or switch processor. Each module is envisioned to consist of a microprocessor

- 7 -

- 8 -

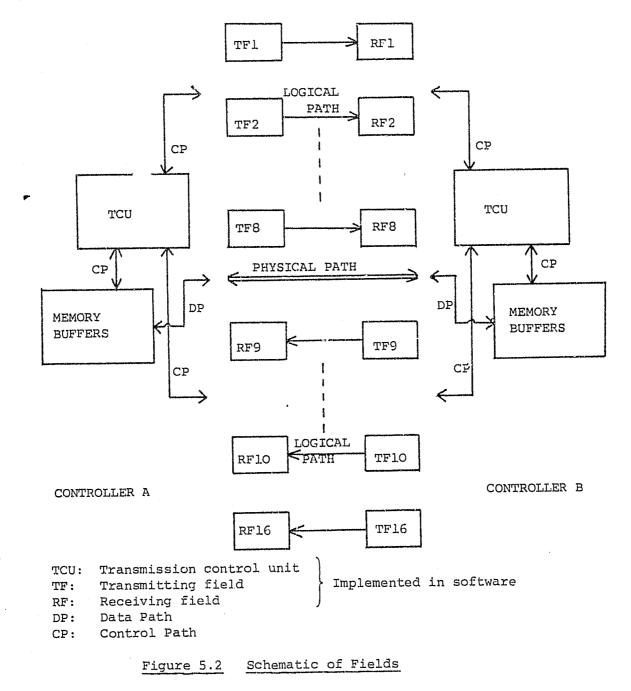

plus memory and appropriate interface integrated circuits. The modules are linked together via two separate, asynchronous busses, termed the data and control bus.

Each of the modules performs a specific function. The interface processors (ICP's) interface with user devices, and perform functions such as code and format translations, packetizing of messages, and reassembly. The network processors (NCP's) control the transmission of packets via PCM channels that connect nodes with one another. The switching processor controls the activities within the node. At regular intervals, it determines the status of the node by polling the NCP's and ICP's. The polled information is processed, and commands are subsequently issued to the interface and network processors, directing these modules as to which packets to send, and when transmission is to take place. The switching processor takes into account factors relevant to nodal operation, such as the availability of buffering in modules, and the congestion experienced on internodal channels.

Data packets are transferred between ICP and NCP modules via the data bus. Information exchange between the switch and the other processors in the node, takes place over the control bus. Note that the detailed design of the microprocessor elements is not of concern here.

The basic operation of the data adaptor unit is summarized as follows. The ICP modules interact with network users. Packets for network transmission are exchanged with NCP's via the data bus. The NCP's ensure packets are transmitted to, or received from, neighbouring nodes. The switch processor supervises the activities of the ICP and NCP modules over the control bus.

- 9 --

# 1.3.2 The Network Protocols

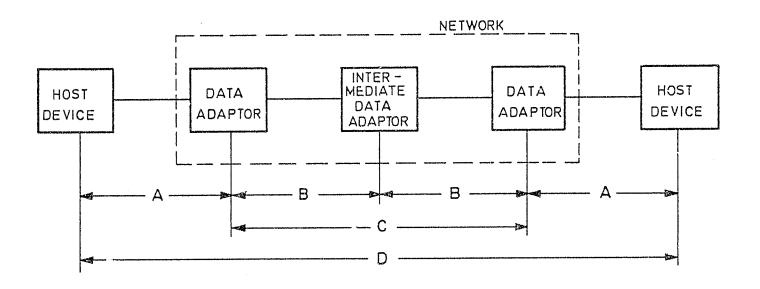

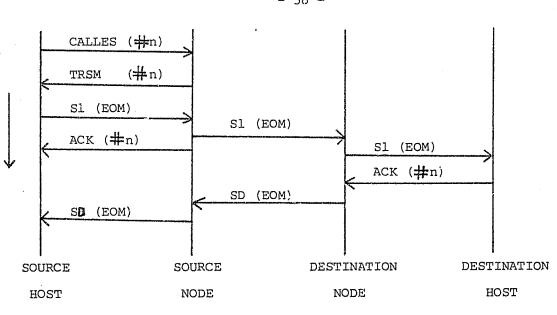

The protocols implemented for the network are shown in Figure 1.2. Depicted are two host devices that require high bandwidth communication facilities on demand. The traffic between the two host devices is bursty, with long gaps in time between the transmission of messages.

The host protocol is undefined. It is both specific to the pair of communicating host devices, and transparent to the network.

The host-network protocol allows communication of user devices with the network. Although the codes and formats used may be device specific, certain protocol procedures necessary for controlling the data flow are common to all ICP-host links.

The information flow between nodes is implemented via the internodal protocol. The protocol is based on the send-and-wait procedure commonly used in packet networks. It is a high-level bit-oriented protocol, allowing up to eight packets to be transmitted before an acknowledgement is required, thus ensuring full utilization of a channel. The protocol differs from commonly encountered bit-oriented protocols, such as Synchronous Data Link Control, in that the acknowledgement process relies upon associating a bit position in a transmitted frame with a packet to be acknowledged, rather than modulo sequence numbers.

The end-to-end protocol is used to control the traffic flow between two ICP's each connected to a pair of communicating host devices. It allows for the pipelining of long file transfers, and for the efficient

- 10 -

- A : HOST NETWORK PROTOCOL

- B : INTERNODAL PROTOCOL

- C : END TO END PROTOCOL

- D : HOST PROTOCOL

FIGURE 1-2 NETWORK PROTOCOLS

transmission of short interactive messages. User devices are connected via logical links, realized by the end-to-end protocol. Once a connection has been established, data may be transmitted at any time, the necessary channel and buffer resources being allocated when required.

No central or supervisory node is present in the network to control data flow between nodes. The above protocols are required to cooperate in the transmission of a message from one host to another.

#### 1.3.3 Flow Control

Traffic flow control measures may be divided into the two broad categories of local and global control. Global flow techniques extend across the entire network domain and, generally, have the function of limiting the number of packets in the network. It has been implemented in conjunction with the end-to-end protocol. Only a maximum specified number of packets per logical link may be in transit across the network at any one time.

The local flow measures operate within the domain of a node and its immediate neighbours, to prevent the occurrence of congestion in the nodal channels. Such a measure has been implemented in the switching processor of each node. Data traffic within the node is classified into the two catagories:

(i) traffic entering the network,

(ii) traffic in transit or leaving the network.

The second class of packets is given priority over the first. The measure has been implemented by the use of time-dependent priority scheduling.

- 12 -

## 1.4 Chapter Survey

This chapter has served to introduce the structure of the data adaptor unit. It was proposed that the data adaptor, based on the packet-switch method, be incorporated into an electronic exchange to deal exclusively with data traffic. The following chapters expand on the system design of the adaptor unit.

Chapter 2 concentrates on the local and global flow control measures incorporated into the data adaptor. The throughput and delay characteristics of packet networks is discussed. It is shown that excessive utilization of communication channels results in performance degradation.

The simulation facility used to model and test the performance of notworks based on the proposed data adaptor is described in Chapter 3. The input parameters required to describe a network are extensively listed. The facility concentrates on simulating the operation of a node; simulation of a network occurs by defining the topological connections between nodes.

A functional description of the interface processor module is contained in Chapter 4. An end-to-end protocol is described. A graphical demonstration of the protocol workings is included. Finally, the buffer management technique used in the interface processor is outlined.

- 13 -

Chapter 5 describes the functions of the network processor module. The internodal protocol and processor buffering structure are fined. To aid in flow control, memory is partitioned according to topological connections of a node to its neighbours. A nodal link was simulated to gain insight into the parameters affecting nodal performance.

.he method of packet interchange between modules within a node is discussed in Chapter 6. Nodal architecture is outlined. The role of the switching processor in controlling the activities of the network and interface processors is described. The chapter concentrates on the nature of the algorithm executed by the switch processor to perform the controlling action.

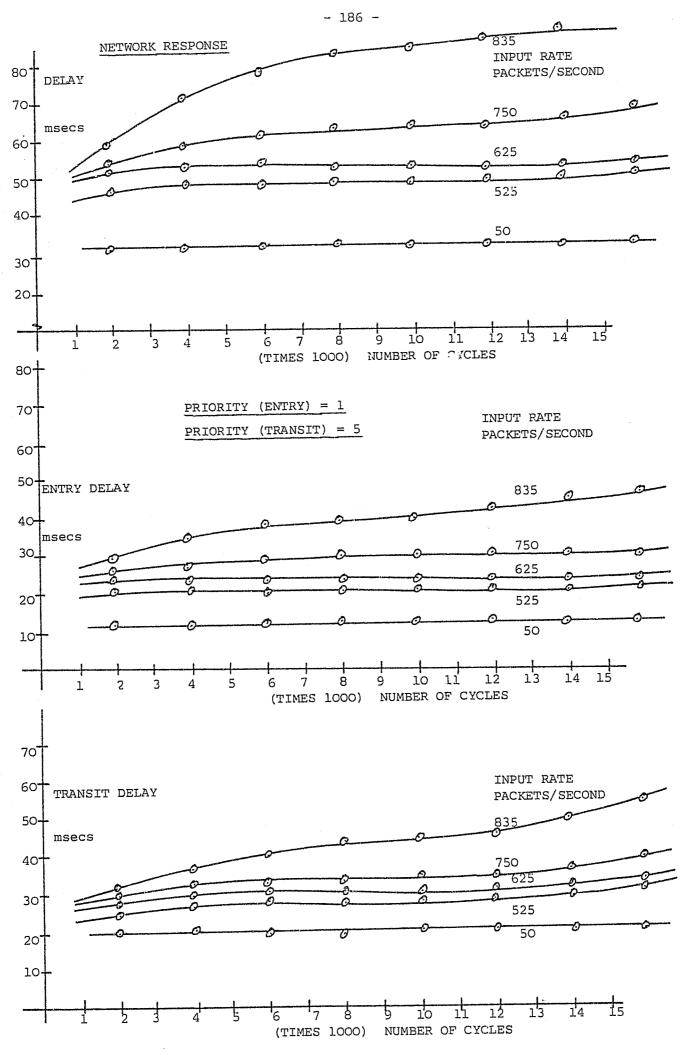

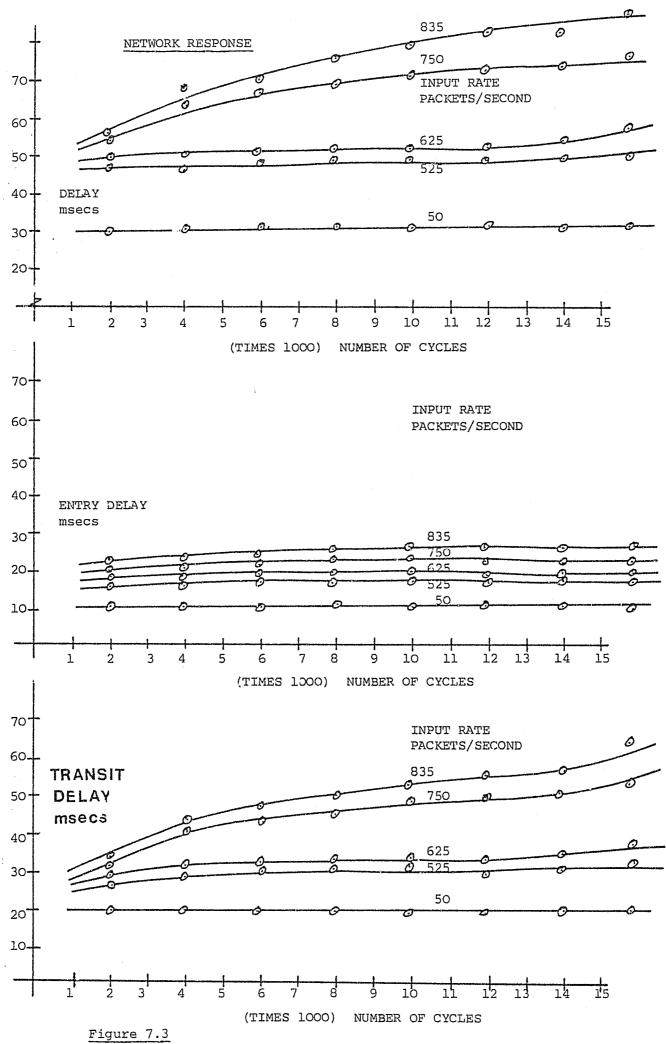

The performance of two simulated networks is listed and discussed in Chapter 7. A preview of the network parameters used, the assumptions made in the simulation, and the indices required for defining network performance, is contained. Tests conducted include, the simulation time required for the models to arrive at a state of equilibrium, response and throughput measurements, local flow control behaviour, and the effect of certain nodal parameters, the retransmission interval, data bus rate and switch algorithm period, on network performance.

Conclusions as to the feasibility of the proposed data adaptor are set out in Chapter 8. A number of suggestions for further work in this area is included.

- 14 -

## CHAPTER 2

# FLOW CONTROL MEASURES

### 2.1 Introduction

Chapter 2 stud: flow control aspects pertaining to a network consisting of a number of connected data adaptor units. The application of such control measures is in fact necessary for all packet-switch based networks.

The network is considered as consisting of a set of components or resources, e.g., buffers, channels, processors, that must be shared amongst a number of logical links for the packet transmission phase to be executed. An excessive number of conflicts over resources can result in the network performance of packet response and throughput, being degraded. Graphical plots have been included to illustrate this effect. To prevent the occurrence of excessive resource sharing conflicts, flow control procedures need to be instituted. Both local and global techniques have been incorporated into the data adaptor unit, and these are described.

Two terms relevant to this chapter are defined. 'Global Flow Control' is a procedure by which the network regulates traffic flow between a source user device and a destination user device. 'Congestion Control' or 'Local Flow Control' is a procedure whereby distributed network resources are protected from over-subscription. In general successful operation of global flow control procedures for every pair of communicating processes does not guarantee that the network resources will remain uncongested, hence the need for both global and local control.

- 15 -

# 2.2 Resource-Sharing in Packet Networks

One of the main problem areas to be found in packet-switching technology is that of the need for distributed resource sharing. Resources must be allocated on demand at various points in the network if successful transmission of data is to take place. The performance of the network is linked to the efficiency of resource allocation.

The principle of resource allocation is briefly explained. The computer network has, as one of its main resources, high capacity channels (others are buffers, processors, data busses, etc.). These channels are allocated to users for short durations of time - the time to transmit a packet of specified size via the 6 400 BPS link. If all users were to send data to the network for transmission at the same point in time, the capacity of the channel to transport the information would be exceeded. In practice such an event will rarely occur, and then only for a short duration.

As the number of messages to the network is increased per unit time, more conflicts will arise regarding the sharing of resources. In extreme conditions deadlock may occur in which two or more competing demands have each been assigned a subset of their necessary resources; neither can proceed until one of them collects some additional resources which, currently, are assigned to the other, and neither is willing to release any resources currently assigned to him. When too many conflicts for resources take place the network performance degrades; an increased time to transport a packet from source to destination host

- 16 -

results and the average number of packets transmitted per unit time, decreases.

The importance of the above discussion is that the data adaptor unit cannot be considered in isolation from its neighbouring nodes. A data adaptor acts, not only as a source and a destination of messages in its interaction with host devices, but it also serves as intermediate node, receiving and transmitting packets enroute from and to its neighbours. The unit must be regarded as one part of a network system for data transmission. The success of a nodal architecture can only be determined when a number of units are linked together into a network and the network system is able to achieve a satisfactory level of performance.

It is important to note that the functioning of any data unit is, to a large extent, determined by the operation of its neighbours. The difficulty of designing successful packet networks with adequate performance levels occurs due to the distribution of the resources in geographically dispersed communication units, where access to these resources arises from asynchronous processes in a highly bursty fashion. Not only is the demand process bursty, but it is also high unpredictable, in the sense that the instants when the demands arise are not known ahead of time.

The problem of resource sharing in a distributed environment manifests itself in the flow control problems. The problem of flow

A DESCRIPTION OF A DESC

- 17 -

control is to regulate the rate at which data crosses the boundary of the communication network.

It is to be noted that the data network envisaged would be decentralized. No one node would control the operation of the network in centralized fashion; this is impractical. By the time control data were to reach the supervisory node, and appropriate control action taken, the information received might have become invalid.

# 2.3 Characteristics of Packet Networks

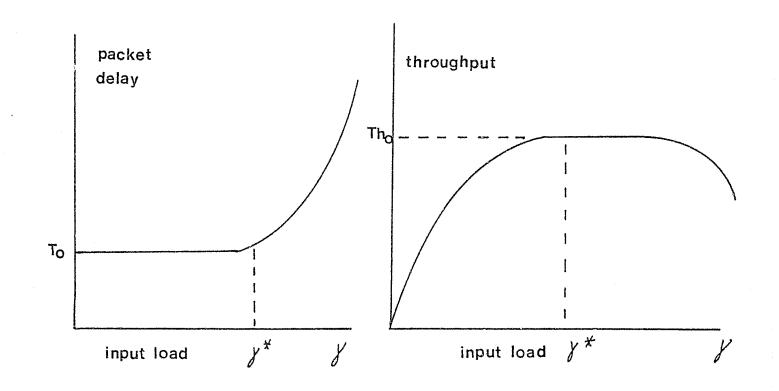

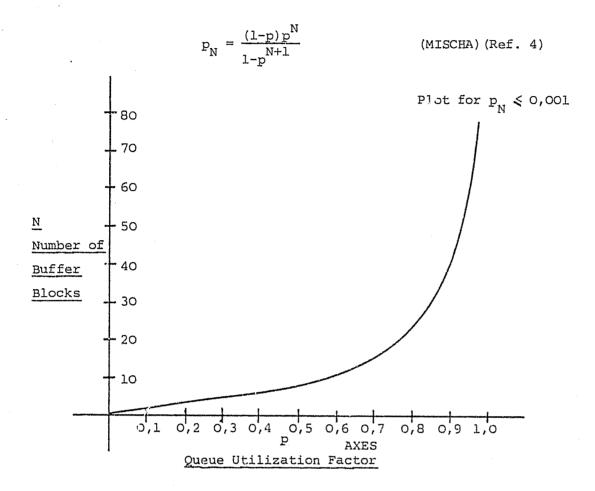

Investigations carried out by means of analyses and simulation <sup>(20)</sup> as well as data gathering on experimental networks, particularly ARPANET, <sup>(21)</sup> have shown that the response and throughput characteristics of packet networks, may be depicted as shown in Figure 2.1.

As the input load in packets per second is increased, the response of the network remains fast at the value of To milliseconds, the no-load packet delay, until an input load of  $\gamma^*$  is reached. Thereafter the network becomes 'unstable' due to an excessive number of resourcesharing conflicts occurring. The response time then increases at a virtually exponential rate.

The throughput curve shows a similar characteristic. Increasing the input load past a certain point (in the region of  $\gamma^*$ ) will cause

- 18 -

#### Figure 2.1 Network Characteristics

the throughput in packets per second to start decreasing. The interpretation is that under normal conditions the input load equals the network capacity; a point is reached, however, where the input will start to exceed the capacity of the network to transport the packets and performance degradation occurs.

The purpose of the flow control measures is to prevent the network from entering the region where the performance indices of response and throughput become degraded, and the amount of work performed by the system effectively decreases. The above graphs are somewhat deceptive in the sense that absolute input load values do not of themselves result in congestion taking place, rather resources become overloaded,

- 19 -

e.g., a channel may become blocked. .

A STATE OF A STATE OF

-----

Equations for a simplified threshold model of network delay, derived in Kleinrock, <sup>(21)</sup> are restated.

Consider an M-channel, N-node network. The channels are assumed to be noiseless, the i'th channel having capacity Ci bits/sec. The nodal processing times are assumed negligible. The packet lengths are assumed to follow an exponential distribution with mean  $1/\mu$  bits. All nodes in the network have infinite storage capacity. A fixed routing procedure is defined. Define  $\lambda_i$  as the average number of packets per second that travel over the i'th channel. In order to evaluate the delay at a channel imbedded in the network it is necessary to make use of Kleinrock's independence assumption: each time a packet is received at a node, a new length  $\bar{b}$  is chosen independently from the distribution;

$$p(b) = \mu e^{-\mu b}$$

$b \ge o$  (2.1)

This assumption has been shown to be reasonable for networks of moderate connectivity, i.e., that most nodes should have more than one channel entering and more than one leaving.

Representing the i'th channel by a M/M/l queueing system, i.e., Poisson arrival (M) and exponential server (M) distributions, single server, the mean packet delay is given by:

$$\mathbf{r} = \sum_{i=1}^{M} \frac{\lambda_{i}}{\gamma} \left| \frac{1}{\mu C i - \lambda i} \right|$$

(2.2)

where  $\gamma$  is the total input load in packets/sec.

- 20 -

If a relatively homogeneous set of Ci capacities is assumed then, as the load in the network is increased, no individual term in the above summation will dominate, until the flow in one channel io approaches the capacity of the channel. At that point T will grow rapidly. The mean packet delay curve will thus express a threshold behaviour.

The no-load delay To is expressed in terms of the mean path length  $\bar{n}$  as

To

$$= \overline{n} \sum_{i=1}^{M} \left( \frac{\lambda_i}{\lambda} \right) \left( \frac{1}{\mu C_i} \right)$$

(2.3)

The saturation load  $\gamma^*$  corresponds to the smallest value of  $\gamma$  at which some channel is saturated; this is the point at which  $\lambda io = \mu C io$ where io is the critical channel. The above equation corresponds to pio = 1. In practice saturation in a channel generally occurs with the utilization factor, p, taking on values of 0,7 and greater.

Control measures must be instituted to maintain the network at the response and throughput levels of To milliseconds and Tho packets/sec respectively, despite possible further increases in the input traffic load. If effective measures are not taken, congestion will result.

# 2.4 Global Flow Control

Global flow techniques extend across the entire network domain, and generally have the function of limiting the number of packets in

- 21 -

the network. The global flow control has been implemented in conjunction with the end-to-end or source node-to-destination node protocol.

The link connecting two communicating host devices consists of a number of resources, such as channels, processors, buffers, etc., that must be allocated on demand to the host connection for communication to take place. This connection is termed a logical link. It consists of both hardware and software components, e.g., memory, processing capacity. The link is not dedicated by providing a physical channel between the two hosts as in circuit switching. Rather, once a call establishment procedure has been evoked, the link may be identified by addresses stored in the supervisory processors in nodes. At any time thereafter a message may be forwarded to the source node by the host device. The required recources will be allocated in order for transmission of the packets, constituting the message, to take place.

The global control measure has been instituted by limiting the number of packets in transit per logical link at any one time. For proper functioning it is essential to obtain to me idea of the number of logical links that will be operational. Il be described by some statistical distribution, in terms of mere packet lengths and interarrival times, possibly as a function of the time of day.

and the second second second second

Long messages are divided into segments by the host devices, the

- 22 -

segments being divided into packets by the nodes. The packets are initially retained in the ICP's. The flow control procedure ensures that only a specified maximum number of packets may be in transit, in the case of the simulations, eight packets. The remaining packets (if any) must wait until the first eight have been transmitted. In effect, blocks of eight packets are sent into the network at a time, under control of the end-to-end protocol. Thus, although the number of messages stored in the interface processors may be large, the number allowed into the store-and-forward section (as realized by the network processors) is strictly limited.

#### 2.5 Local Flow Control

Local flow measures operate within the domain of a node and its immediate neighbours, to prevent the occurrence of congestion in the region of the node. The local flow measures are implemented in the switching processor of each node. The switch samples the state of the node at regular intervals, processes the status data, and sends commands to the ICP and NCP modules directing their activities. Two types of flow measures are considered, the allocation of priorities to packets, and the partitioning of memory along topological lines.

# 2.5.1 Priority Allocation Technique

The switch algorithm has been based on exploiting certain properties of a store-and-forward network, i.e., its queueing structure. The nodal operation may be reduced to the concept of the servicing of a set of

- 23 -

queues in the ICP and NCP modules by the switch processor. The algorithm does not rely upon lengthy mathematical calculations based on statistical traffic flow measures, as is the case in adaptive routing, but makes use of time-dependent priority evaluations. The use of time-dependent priority evaluations for preventing congestion is not treated in the literature.

Packets have been grouped into the following two classes:

i) packets entering the network;

ii) packets in transit, or leaving the network.

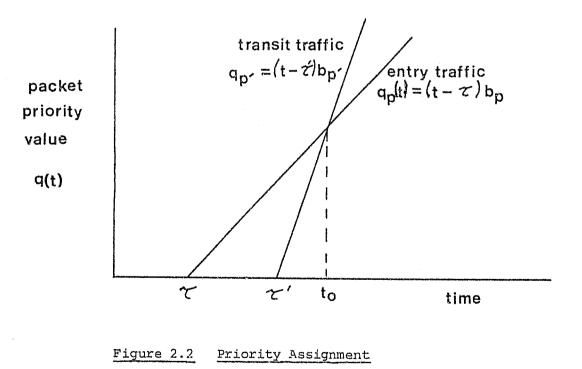

Each class is allocated a priority value that is incremented with respect to time (see Figure 2.2).

- 24 -

The function of the switch is to control the flow of traffic proceeding from the ICP modules to the store-and-forward section, realized by the NCP modules, on a local level. A node that starts to become congested will grant priority to transit traffic at the expense of the entry traffic, thereby causing less packets to gain admittance to the network.

The time-dependent priority system provides a set of variable parameters, bi, where

These parameters may be used to adjust the relative waiting times for the packets in the queue. Assume that the packet under consideration arrives at time  $\tau$  and is assigned at time t a priority qp(t) where

$qp(t) = (t - \tau)bp$

where t ranges from T until the time at which the packet's service time is completed. Whenever the service centre (i.e., the switch) is ready for another packet, it chooses to service that packet with the highest instantaneous priority q(t). If a tie for the highest priority occurs, the tie is broken by the first-come-first-served rule.

Figure 2.2 shows the manner in which packets from two priority groups interact. A packet from priority group p (entry traffic) arrives at time T and attains priority at a rate bp. At time T' another packet enters the node and attains priority at a rate bp' (transit traffic group). If the service facility becomes free at any time between T and to, the packet from group p will be serviced in preference to that of the packet

- 5 -

from group p'. For any time after to, the transit traffic packet will be serviced beforehand.

Kleinrock has analyzed such a queueing system. <sup>(21)</sup> The analysis models a node as consisting of an M/G/l queue - Poisson arrival rate, general service time distribution, and single server. Such forms an approximation to the queue maintained by the switch processor servicing ICP and NCP module requests.

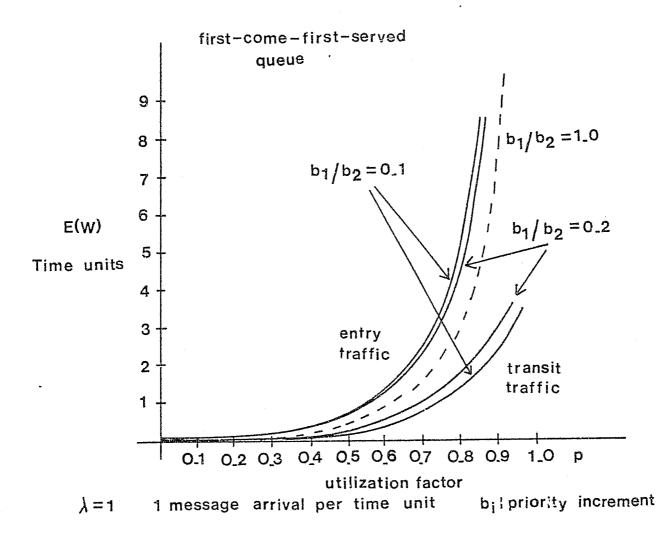

The mean waiting times for group p and group p' packets in a nonpreemptive time-dependent discipline is shown in Figure 2.3. The mean waiting times as a function of the queue utilization factor p, for the parameters bl/b2 = 1, bl/b2 = 0,2, and bl/b2 = 0,1 are plotted. The utilization factor p is defined to be the ratio of the mean arrival rate to the capacity of the system to service the arrivals. Note that it is not the absolute values bp and bp', but the ratios bp/bp' that are important. At the lower utilization factors (p < 0,4) the priority designations have little effect and the waiting times for both traffic groups is the same. At the larger values (p > 0,7) the mean waiting time of transit traffic is far less than that of entry traffic.

The maximum service rate of the data adaptor in packets per second is finite. By granting transit traffic servicing priority (as opposed to entry traffic) less packets wanting to gain entry to the network are serviced. The overall effect is to limit the number of packets that gain entry to the network under heavy traffic conditions. In Chapter 7, simulation results for various parameter ratios bp/bp' are listed,

- 26 -

showing the effect of this technique on mean packet response in a network.

Figure 2.3 Mean Waiting Times for Delay Dependent Traffic

### 2.5.2 Memory Partitioning Technique

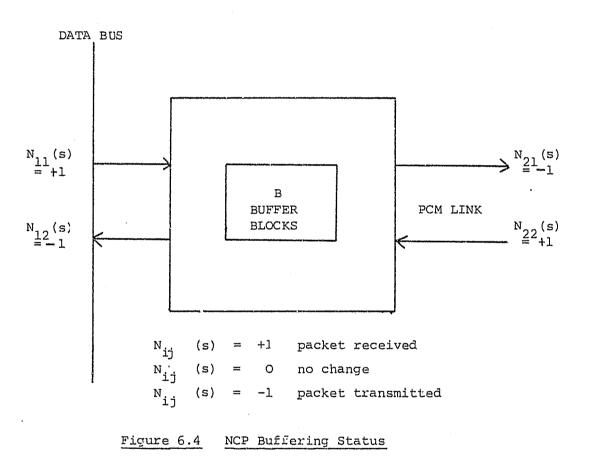

A second local flow control measure is realized by the internodal protocols. An NCP module is connected to each end of a PCM channel, implementing the data transmission protocol between two nodes. When the buffers of a destination NCP become blocked, a signal is sent to the source NCP, indicating this state. The source NCP will then cease transmitting packets until the elapse of a time-out period. Thereafter another attempt is made to transmit the data. The source NCP will indicate the blocking of its destination NCP buffers to its supervisory processor. The supervisor will subsequently ensure that no packets are transmitted to the source NCP by the other nodal modules, until the elapse of the time-out period, this being conveyed to the switch by the source NCP module.

The above discussion needs to be further clarified. Packets requiring to make use of the said NCP are divided into groups. The groups are classified according to topological attributes of the network (this aspect is further dealt with in Chapter 5). Each NCP contains a number of buffers dedicated to each of the groups; in addition a common buffering area is provided for use by all classes. Blocked buffering at a destination NCP usually means that the buffers belonging to a particular group are all occupied. The NCP therefore ceases the transmission of a particular class of packets (conveyed to the supervisory processor), whilst other classes are sent as normal.

The implication of use of this measure is that data flow of different groups enroute from a number of different source-destination nodes through the same intermediate node, will not cause excessive interference with each other. If this measure were not included, it would be possible for traffic enroute from one source-destination link whose service rate was poor and intensity high, to block traffic from other links passing through the same NCP.

- 28 -

### 2.6 Review

This chapter has described the resource-sharing aspect of packetswitching networks. It was pointed out that a data adaptor unit cannot be considered in isolation, but forms part of a network. The characteristics of such networks, and the subsequent need for flow control measures to prevent performance degradation, were described. Both global and local flow control measures have been incorporated. The global technique operates by limiting the number of packets per logical link in transit. It is implemented by means of the end-to-end protocol. Two local flow techniques have been incorporated in the switching processor:

- the allocation of different time-dependent priority increments to entry and transit traffic,

- control of the transmission of packets to the network communication processors.

#### CHAPTER 3

#### SIMULATION FACILITY

### 3.1 Introduction

The object of the simulation program is to model the interactions of the flow control measures and protocols that cause packets to be transported from one end of the network to the other. The performance and characterization of a network could then be determined as a function of the control measures and protocols.

It was found that simulation could be conducted either by utilizing available packages, or by designing a model in a high-level language.

A general Purpose Systems Simulator (GPSS version 3) was available. GPSS is based on the modelling of events. Entities such as packets, messages, jobs, customers, etc., are modelled as passing through a queueing system. A certain amount of time was spent experimenting with this package. It was found to be unsuitable as the emphasis of the work lay in modelling the mechanisms of the network that cause data transmission to take place, rather than in the entities or data packets themselves.

The high-level langu ges available were FORTRAN, PL/l and Pascal. In terms of language structure and the implementation of data types, Pascal and PL/l were favoured, but only a compiler was available for each. In contrast, a FORTRAN interpreter and compiler existed. The turn-around time for batch jobs could be considerable at the computer system where the simulation program was developed. Accordingly, the model was written in Fortran, on the basis that the advantages to be gained by writing and debugging the program interactively, outweighed those to be gained by using the data structure of Pascal or PL/1.

The simulation model developed is non-mathematical. It simulates the transition of states in the protocols for ensuring synchronization of sender and receiver, and the subsequent transmission of information.

The remainder of the chapter provides an overview of the simulation facility developed.

#### 3.2 The Simulation Structure

This section is concerned with introducing the structure of the simulation program developed to study the proposed network. Extensive use of arrays was made to represent the various parameters and quantities of the network. The array descriptions are contained in Appendix A, whilst the program listing, together with appropriate documentation, is to be found in Appendix B.

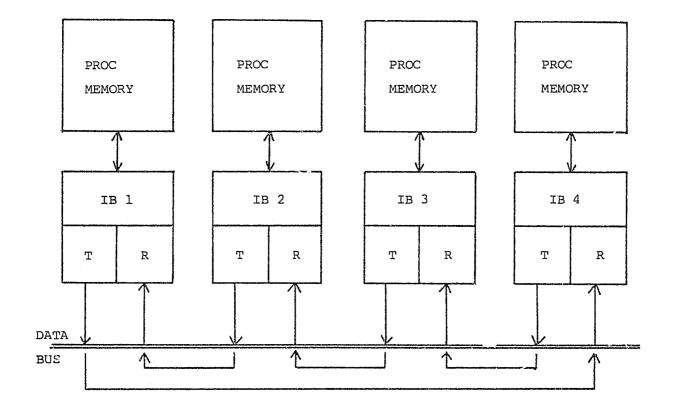

The simulation model may be divided into two main sections, the initialization and the execution blocks, as in Figure 3.1.

- 31 -

# Figure 3.1 Main Simulation Structure

# 3.2.1 Initialization Block

The initialization block is concerned with reading in the appropriate network parameters, and initializing the array structures. In addition this block provides for initializing the execution block into a state of readiness for simulating the network. The execution block contains the necessary code for simulating the network on an event-by-event basis. The output of data describing the performance of the network is also included in this block.

# 3.2.2 Execution Block

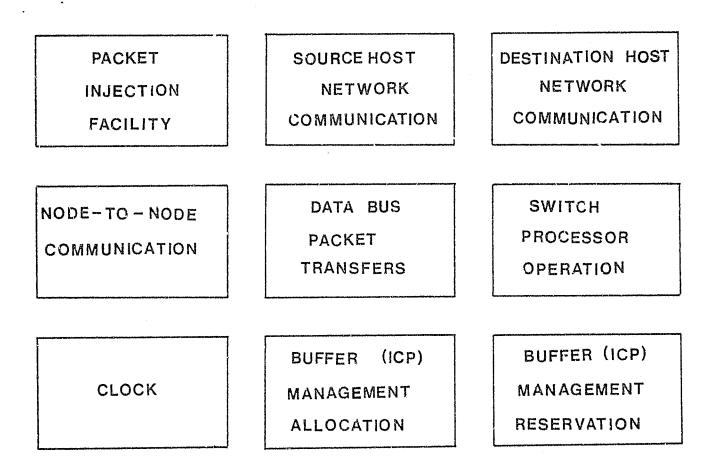

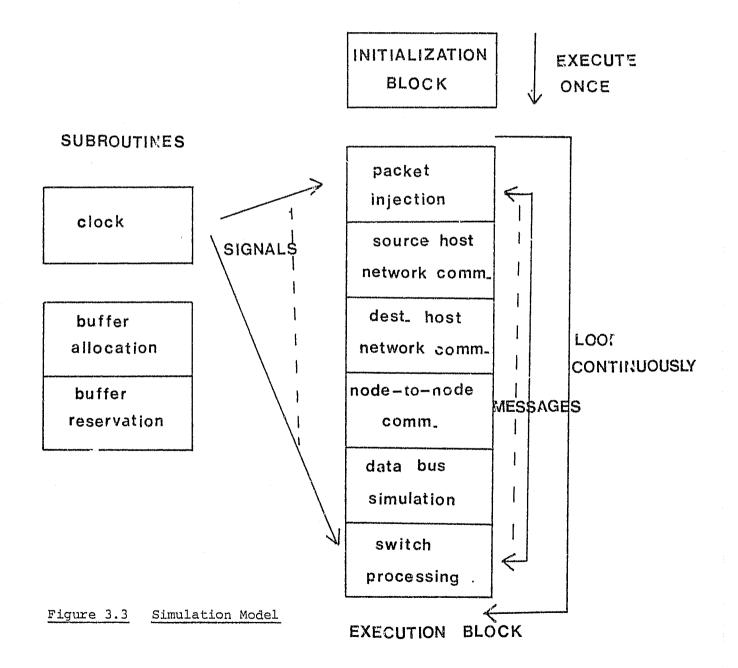

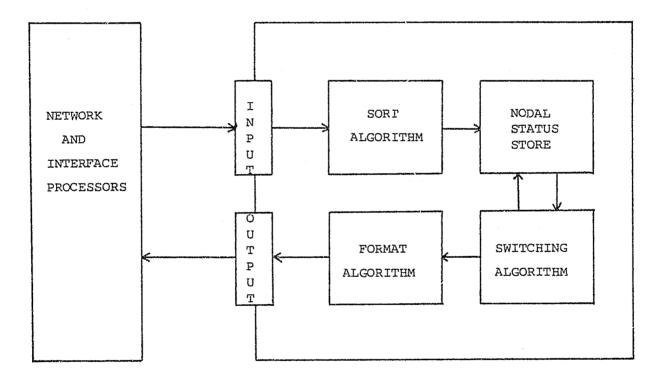

The execution block may further be subdivided into a number of modules, each simulating a particular aspect of the network. These modules are shown in Figure 3.2.

# 3.2.3 Description of the Simulation Modules

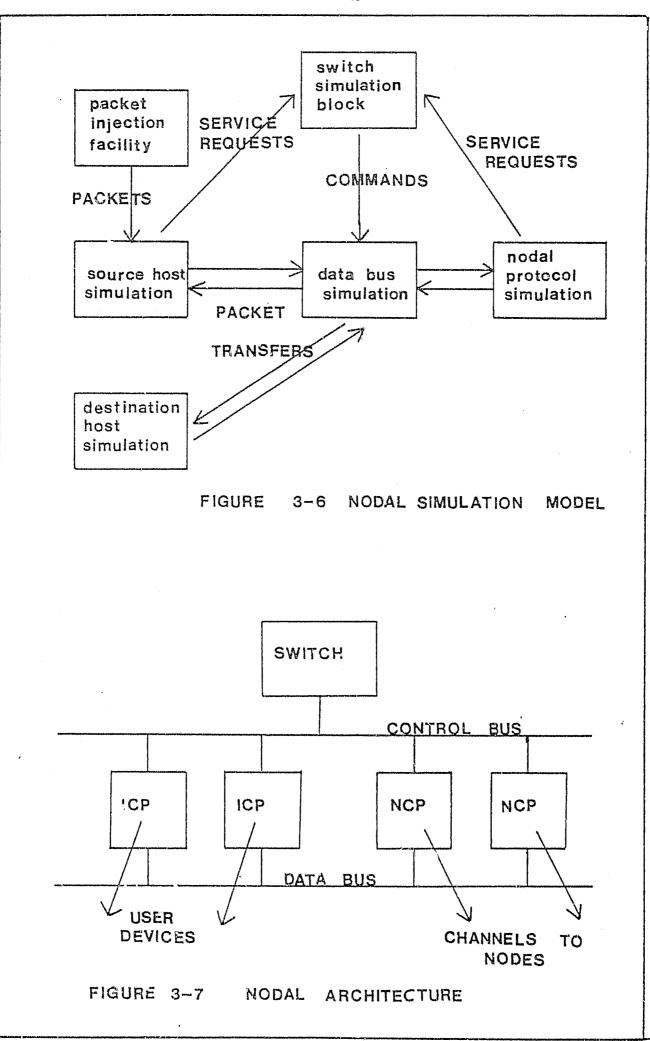

The node-to-node communication module simulates the protocol used to transmit data between two nodes via the network communication processors.

### Figure 3.2 <u>Simulation Modules</u>

The communication between processors (ICP's and NCP's), and the packet transfers via the data bus within a node are modelled by the data bus packet transfer module.

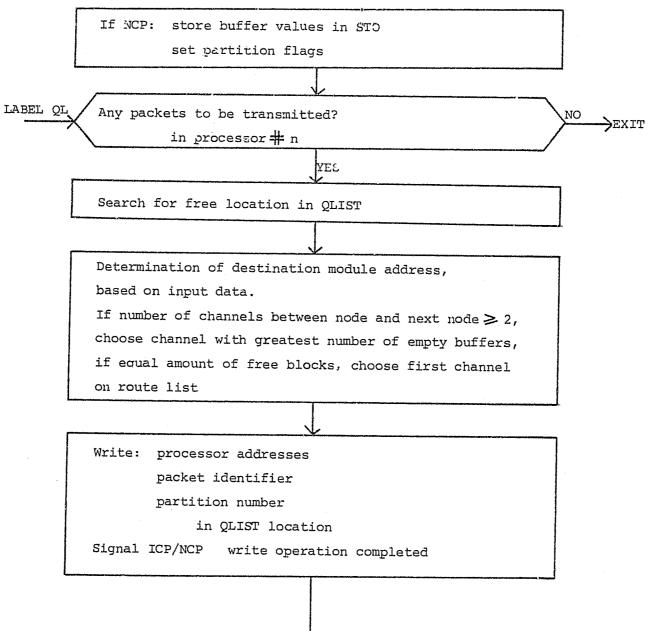

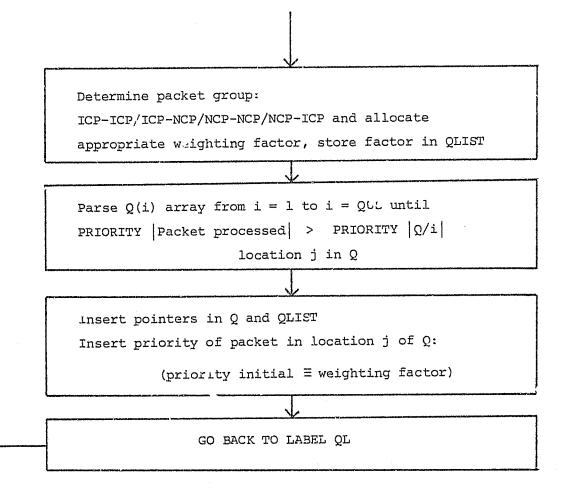

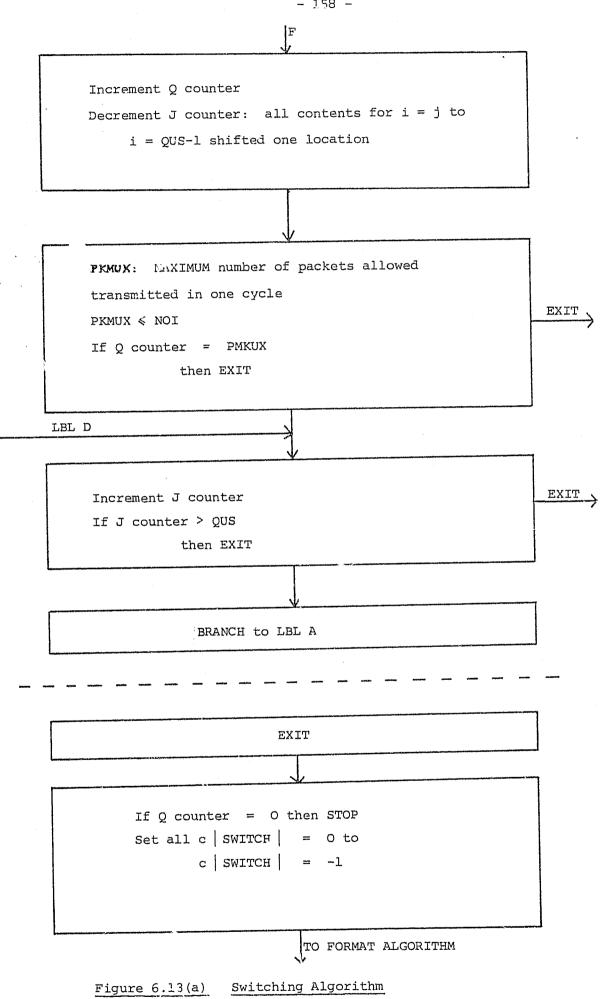

The finitching processor module contains the switching algorithms used to direct the nodal activity. This module simulates the activities of sampling the nodal status, processing the status data, and transmitting subsequent commands to the ICP's and NCP's. The above modules constitute the network simulation components for modelling the signalling and flow control measures.

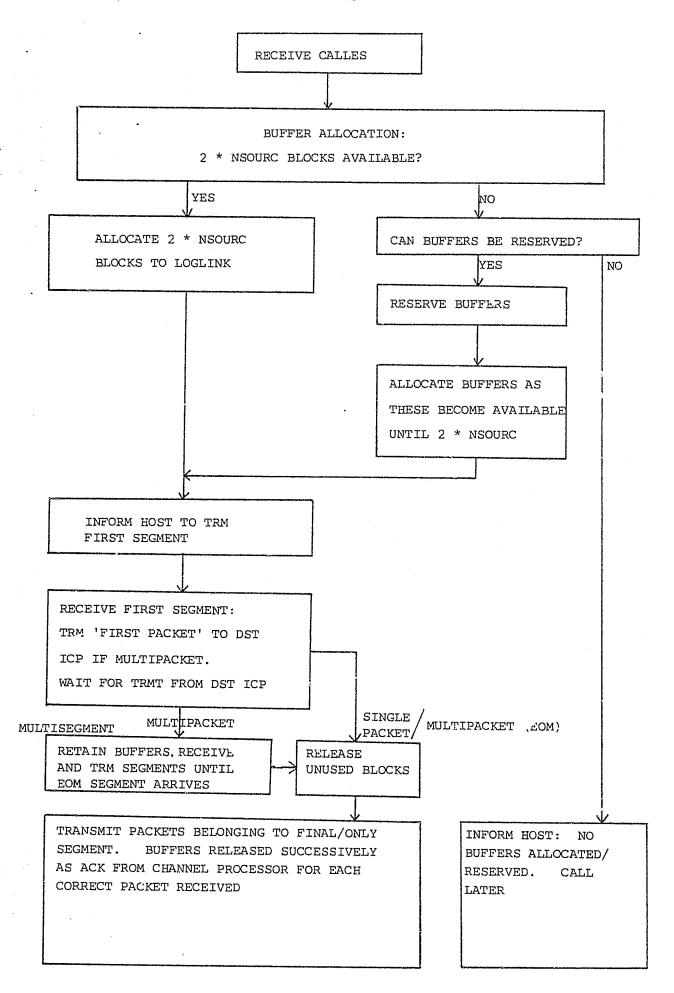

A number of additional modules have been included. Two of these, the buffer management allocation and reservation blocks, simulate the processes of allocating storage for message segments and packets in the ICP's. The allocation module models the granting of buffer blocks to logical devices; the reservation module maintains a list of requests for storage when the available ICP buffers are all occupied. The reservation module contains an algorithm that allows priorities to be allocated to different groups of messages, e.g., short interactive messages and long file transfers.

The packet injection facility generates the traffic to the network. The facility is used to generate data messages and packets with Poisson interarrival times and geometric or exponential length distributions.

Finally, the clock module is used as a timing mechanism for events. It keeps track of all events, and activates the relevant mechanisms in the main simulation section when the event occurs. This module maintains a clock using real numbers to represent time.

The structure of the simulation is such that the above modules may be placed in any order. Valid simulation of the network is not dependent on the order in which the modules are executed. This has been done specifically to allow additional modules to be incorporated if it is desired to simulate aspects of the network in greater detail

- 34 -

than represented here; or to simulate other protocols and flow control techniques.

The format of the program is shown in Figure 3.3. The clock and buffer management modules are subroutines. The remaining modules, constituting the execution block, are grouped together into a single loop.

And a second second

- 35 -

A double execution of the loop is termed a 'cycle'. The duration of the simulation is directly controlled by the number of cycles specified for the loop. To determine the performance characteristics of the network (see Chapter 7) initial runs were first conducted to determine the number of cycles required for the model to reach a state of equilibrium. These tests are conducted for different input loads.

### 3.2.4 Module Communication

And a second sec

Each module is an autonomous unit, simulating a particular aspect of the network. The following terminology, i.e., 'message' and 'signal', refer to the simulation itself.

The intercommunication between modules takes place via messages or signals. A signal is transmitted from one module to another when an event is to take place or has occurred. A message constitutes information passed from one module to another. The characteristics of a packet passing through the network may be passed between modules via messages. An example of signal use occurs when a packet is transmitted across a communication channel; such an event takes a certain amount of time. When the packet has reached the destination, i.e., use of the channel is terminated, then this event is indicated to the appropriate module via a signal generated by the clock module.

Signalling takes place between the clock module and the modules constituting the execution block. The clock enables each module to regulate the simulation of its own events relative to the events occurring in other modules with reference to the same time scale. An event

- 36 -

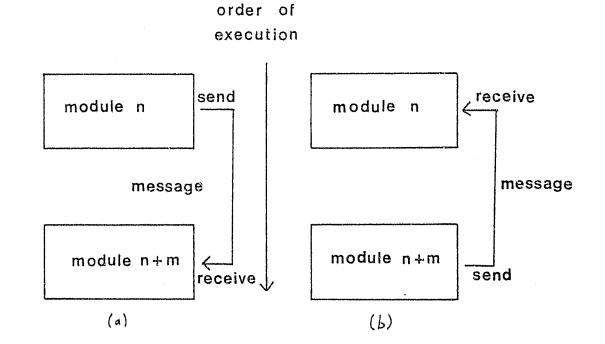

occurring in module n may cause an event to take place in module n + m, or V.V., such causal action being transferred between two modules via a message or signal (see Figure 3.4). It is important to note that such action implies that the execution of the code for the event in module (n + m) must take place in the same instant of simulated time as the events of module n. The code is therefore scanned more than once during each cycle, each cycle depicting a point in simulated time. Consider Figure 3.4(b). During the first scan a message is passed from module n + m to module n; during the second scan, events in module n, activated by the message, are simulated. The example in Figure 3.4(a) requires only one scan, the second having no effect. In the simulation model, two scans per cycle are sufficient.

Figure 3.4 Message Passing

- 37 -

#### 3.3 Input Parameters for the Simulation

This section deals with the data that is required to define a network to be simulated. The parameters that define network topology and operation are considered. Description of the input parameters will take place with reference to the example shown in Figure 3.5. The reasons for choosing this topology are considered in Chapter 7, where its characteristics are described.

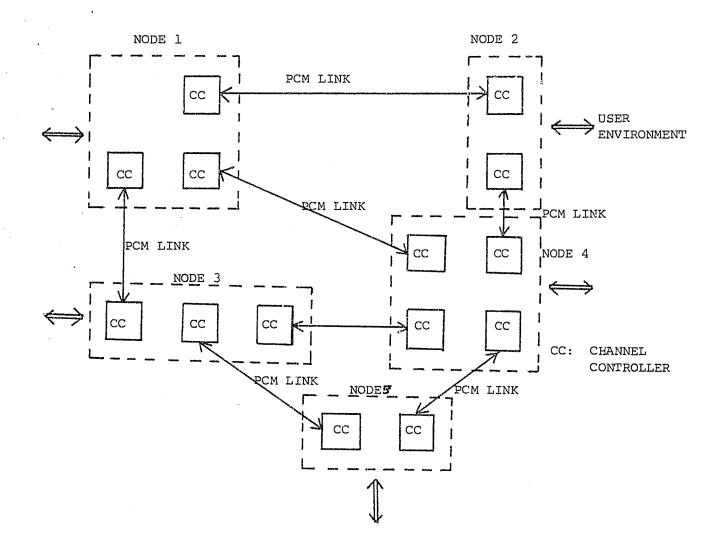

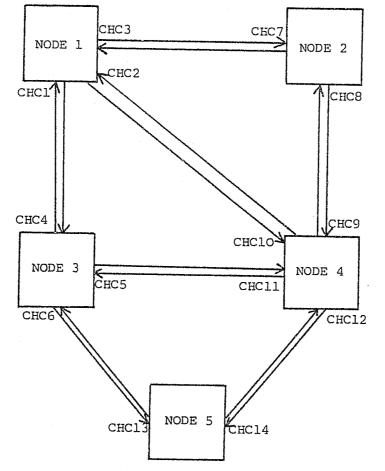

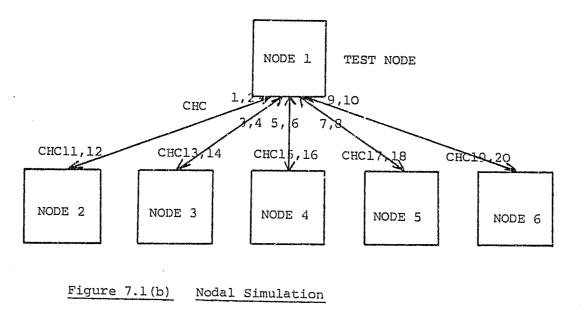

### 3.3.1 Network Topology Simulated

The topology consists of five nodes connected via PCM channels. Hierarchically-based networks consist of nodal clusters. The simulated topology approximates such a cluster. Simulation of a network with more than five nodes would require an excessive amount of computer time to determine the network characteristics. Each node contains a number of channel controllers that control the transmission of packets between nodes. There is a total of fourteen such controllers (also referred to as network communication processors). Each node contains eight interface communication processors that enable the network to interact with host devices. Fifty logical links and fifty virtual circuits have been implemented. A logical link refers to the connection between two communicating host devices. The network resources, e.g., lines, buffers, are allocated on demand.

### 3.3.2 Traffic Level Control by Virtual Circuits

And the second se

In order to raise the level of traffic within the network without having to resort to excessive use of computer time, the concept of a virtual circuit has been defined. A virtual circuit refers to the

- 28 -

NЗ N7 NODE 1 NODE 2 N2 NIA N8 <u>N4</u> N1Ù /N9 NODE 3 NODE 4 € N5 N11 N12 N6 NODE 5 N13 'N14

## Nitchannel or network control processor

Figure 3.5 Network Simulation Topology

link existing between a source ICP and destination ICP. Packets are generated at a given rate at the source ICP, transmitted via the network according to a fixed routing matrix, and sunk by the destination ICP. No simulation of host-network protocols is done. The level of traffic in the network and in particular along each route may be controlled by varying the mean packet generation rate and length. The distributions of interarrival time and length have been chosen to be Poisson and geometric or exponential, respectively.

### 3.3.3 Link Specifications

The parameters for defining logical links and virtual circuits are shown in Table 3.1. Each link and circuit is identified by a number. For each link it is necessary to specify the source node - and ICP numbers, and the destination node - and ICP numbers. Each ICP, NCP and node is identified via an integer. The values may be identical for the above three groups, e.g., ICP and NCP may both be identified by the integer 3, the context will distinguish between them.

The source and destination channel capacity slots refer to the capacity of the connection between user device and network in bits per second. The source and destination channels may be of different line rates.

The length and arrival slots refer to the mean values of the statistical distributions incorporated in the main program to generate packets or messages.

Finally, the contents of the slot denoted by 'NO MSGS' enables one to limit the number of packets or messages generated for the duration of the simulation. This feature is extremely useful for debugging purposes. A negative value in this slot causes an unlimited number to be generated.

| Link<br>NO | Sour Node | Source<br>ICP | Dest.<br>Node |    | Channel | Dest.<br>Channel<br>Capacity | Mean<br>Length | Mean<br>Arrival | NO<br>MSGS |

|------------|-----------|---------------|---------------|----|---------|------------------------------|----------------|-----------------|------------|

|            | 1         | l             | 1             | 7  | 7200    | 7200                         | 450            | 10              | 10         |

| 1<br>50    | 5         | 40            | 5             | 34 | 7200    | 7200                         | 450            | 10              | 10         |

(a) Logical Link Table

| Link<br>No   | Source<br>Node | Source<br>ICP | Dest.<br>Node | TOF | Source<br>Channel<br>Capacity | Dest.<br>Channel<br>Capacity | Mean<br>Length | Mean<br>Arrival | NO<br>MSGS |

|--------------|----------------|---------------|---------------|-----|-------------------------------|------------------------------|----------------|-----------------|------------|

|              | 1              | l             | 1             | 7   | -                             | _                            | 450            | 10              | -5         |

| ,<br>1<br>50 | 5              | 40            | 5             | 34  | -                             | -                            | 450            | 10              | 2          |

(b) Virtual Circuit Table

Table 3.1 Logical Link and Virtual Circuit Parameters

# 3.3.4 Node-Processor Mapping

State of the second sec

1

A CONTRACT OF A

The ICP's and NCP's forming part of a particular node must be specified as shown in Table 3.2

| Node<br>No |    |    |    | ICP | No |    |    |    | T |

|------------|----|----|----|-----|----|----|----|----|---|

| 1<br> <br> | 1  | 2  | 3  | 4   | 5  | 6  | 7  | 8  |   |

| ו<br>5     | 33 | 34 | 35 | 36  | 37 | 38 | 39 | 40 |   |

| Node<br>No  |    | NCP | No |   |

|-------------|----|-----|----|---|

|             | 1  | 2   | 3  | 0 |

| -<br>-<br>5 | 13 | 14  | 0  | 0 |

Mapping: Node-to-NCP

Mapping: Node-to-ICP

### Table 3.2 Nodal Mappings

- 41 -

A zero in a slot simply indicates an empty location. A unique mapping exists between each node and the NCP's and ICP's it contains.

The topology is formulated by specifying which two NCF's are linked. Table 3.3 shows, for example, that NCPl is linked to NCP4. The result is a connection between node 1 and node 3. The fixed topology produced is that shown in Figure 3.5.

| Source NCP | 1 | 2  | 13 | 14 |

|------------|---|----|----|----|

| Dest. NCP  | 4 | 10 | 6  | 12 |

| Table 3 | .3 | NCP-to-NCP | Connection |

|---------|----|------------|------------|

|---------|----|------------|------------|

### 3.3.5 Packet Route Map

The route that packets are to follow is implemented via a nodal route map, as shown in Table 3.4. Each packet will be a member of either a logical link or virtual circuit, the source and destination ICP's of which will have been specified as in Table 3.1.

|              |   |    | D  | est. No | odal No | ). |

|--------------|---|----|----|---------|---------|----|

|              |   | 1  | 2  | 3       | 4       | 5  |

|              | 1 | 0  | 3  | 1       | 2       | 1  |

| Present      | 2 | 7  | 0  | 7       | 8       | 8  |

| Nođal<br>No. | 3 | 4  | 4  | 0       | 5       | 6  |

|              | 4 | 10 | Э  | 11      | 0       | 12 |

|              | 5 | 13 | 14 | 13      | 14      | O  |

#### Table 3.4 Route Map

Routing functions are performed under the control of the supervisory processor in each node. By consulting the route map, the supervisor can direct a packet to the relevant NCP, once the present and destination

- 42 -

nodal positions are known. If the present and destination nodal positions coincide, then the supervisor knows that the destination node has been reached, and that the packet must be directed to the relevant ICP.

For example, a packet at node 2, having as destination node 5, will be directed to NCP8 (of node 2). Referring to Figure 3.5, the packet will be transmitted to NCP9 of node 4. From node 4 it will be sent to node 5 via NCP12 and NCP14, situated within each of the above nodes.

In the event of there being more than one channel between two nodes, an additional map for each extra channel is to be specified. A choice then exists as to which channel the packet is to be directed to. The choice has been based on assigning the packet to the NCP with the smallest queue.

### 3.3.6 Bus Multiplexing Table

and a second second

A table is needed to specify the number of packets multiplexed on the data hus of each node, every period. No attempt will be made to define further this concept; these parameters have been included for the sake of completeness.

| Node    | 1  | 2  | 3  | 4  | 5  |

|---------|----|----|----|----|----|

| NO PCKS | 11 | 10 | 11 | 12 | 10 |

| MUX     |    |    |    |    |    |

| Table 3.5 | Bus Multiplexing |

|-----------|------------------|

|           |                  |

- 43 -

### 3.3.7 The Partition Table

Packets enroute from one node to another may be grouped into a number of classes. These classes are a function of the network topology. Buffer blocks in the NCP are dedicated to each class. The term partition refers to the class of buffers set aside for a specific group of packets. Partitions have been implemented to prevent the traffic flow enroute to one destination from blocking flow enroute to other destinations. Such would occur if one class of traffic were to occupy all buffers in an NCP. See Table 3.6.

In addition, a node plot matrix of partitions must be provided to enable the supervisory processor to classify the packets into classes. If the buffers allocated to a particular class of packets are all occupied, then the supervisor will ensure that no packets belonging to that class will be transmitted to the NCP with blocked buffers. See Table 3.6.

Consider NCP 1 of node 1 (see Figure 3.5). Packets passing through NCP 1 will be enroute either to node 3 or node 5, such may be verified by referring to the packet route map. Accordingly, partitions denoted by 3 and 5 are set aside in NCP1. The simulation program provides for up to eight possible partitions. The node plot matrix enables the supervisory processor at node 1 to classify the packet with destination node 5 to be 3.

- 44 -

| NCP's       | 1      | 2      | 3      | Part<br>4 | titio<br>5 | ons<br>6 | 7      | 8      |                                  |

|-------------|--------|--------|--------|-----------|------------|----------|--------|--------|----------------------------------|

| 1<br>2<br>1 | 3<br>4 | 5<br>0 | 0<br>0 | 0<br>0    | 0          | 0<br>0   | 0<br>0 | 0<br>0 | Processor<br>Partition<br>Matrix |

| 14          | 2      | 4      | 0      | 0         | 0          | 0        | 0      | ο      |                                  |

#### Destination Node

|                |                       | 1                     | 2                     | 3                     | 4                     | 5                     |                        |

|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|

| Source<br>Node | 1<br>2<br>3<br>4<br>5 | 0<br>1<br>1<br>1<br>3 | 2<br>0<br>1<br>2<br>4 | 3<br>1<br>0<br>3<br>3 | 4<br>4<br>4<br>0<br>4 | 3<br>4<br>5<br>5<br>0 | Node<br>Plot<br>Matrix |

Table 3.6 Partition Table

## 3.3.8 Network Parameters

Finally, Table 3.7 contains a set of parameters that may easily be altered for a given topology to study the network performance. The parameters contained in the table are all variables, unlike the above input data (which are constants), and may be changed during execution.

### 3.3.9 Summary

14 . ...

1

-----

The defined parameters specify the topology of the network, the number and types of processors in each node, the logical links and virtual circuits for generating traffic, and the route map for packets.

| Parameter | Description                                                       |

|-----------|-------------------------------------------------------------------|

| N         | Total number of logical links and virtual circuits                |

| NUMBER    | Duration of simulation run in cycles                              |

| SCAN      | Number of loops of main block per cycle                           |

| BUFBLK    | ICP buffer block size in bits                                     |

| NSOURC    | Number of buffer blocks allocated at ICP per logical link         |

| SGMENT    | Message segment size in bits                                      |

| NONDS     | Total number of nodes in network                                  |

| NOICPS    | Total number of ICP's in network                                  |

| NONCPS    | Total number of NCP's in network                                  |

| PSZNO     | Packet size in bits                                               |

| MNOBFS    | Number of buffer blocks in NCP - send or receive                  |

| BITLNG    | Packet overhead in bits                                           |

| MAXCH     | Maximum number of channels between any two nodes                  |

| NOI       | Maximum number of processors in any node                          |

| NOPCKS    | Maximum number of packets that model can simulate                 |

| CMAX      | Number of switch cycles per period                                |

| NMAXIC    | Maximum number of ICP's in any node                               |

| NMAXIN    | Maximum number of NCP's in any node                               |

| QUS       | Total storage locations provided for algorithm execution          |

| TXMAX     | Retransmission interval for incorrect packets                     |

| PXMAX     | Partition retransmission interval                                 |

| MVXRT     | Data bus rate in bits per second                                  |

| PMEANC    | Mean packet interarrival time for virtual circuits                |

| SWPROC    | Estimated switch algorithm execution duration                     |

| NVC       | Number of virtual circuits                                        |

| NRDN      | Number of packets generated - exponential length, arrival<br>time |

| NRRN      | Number of packets generated per instant for virtual circuit       |

| NODPRC    | Estimated NCP processing time par packet                          |

| NPZ       | Estimated processing time for data bus transmission               |

Table 3.7 Network Parameters

the state is an

- 46 -

| Parameter  | Description                                   |  |  |

|------------|-----------------------------------------------|--|--|

|            | SUBROUTINE ACCESS                             |  |  |

| BLOCK(I,5) | Number of single packet blocks (ICP) - memory |  |  |

|            | Number of multipacket blocks (ICP) - memory   |  |  |

| BLOCK(I,7) | Number of multisegment blocks (ICP) - memory  |  |  |

|            | Number of blocks of common memory (ICP)       |  |  |

|            | SUBROUTINE RESERVE                            |  |  |

| NPRSIN     | Single packet priorily increment (ICP)        |  |  |

| NPRMUL     | Multipacket priority increment (ICP)          |  |  |

| NPRSOU     | Source segment priority increment (ICP)       |  |  |

NRSV Number of locations for requests

The second secon

Table 3.7 (Contd.) Network Parameters

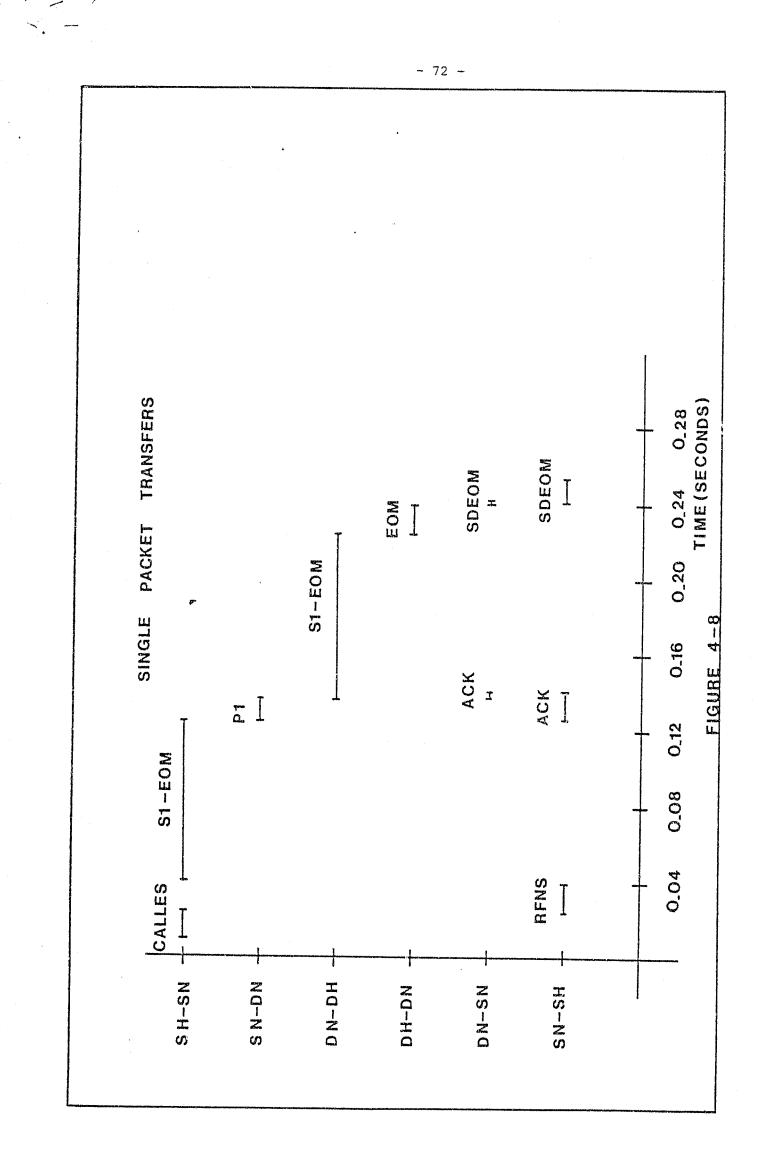

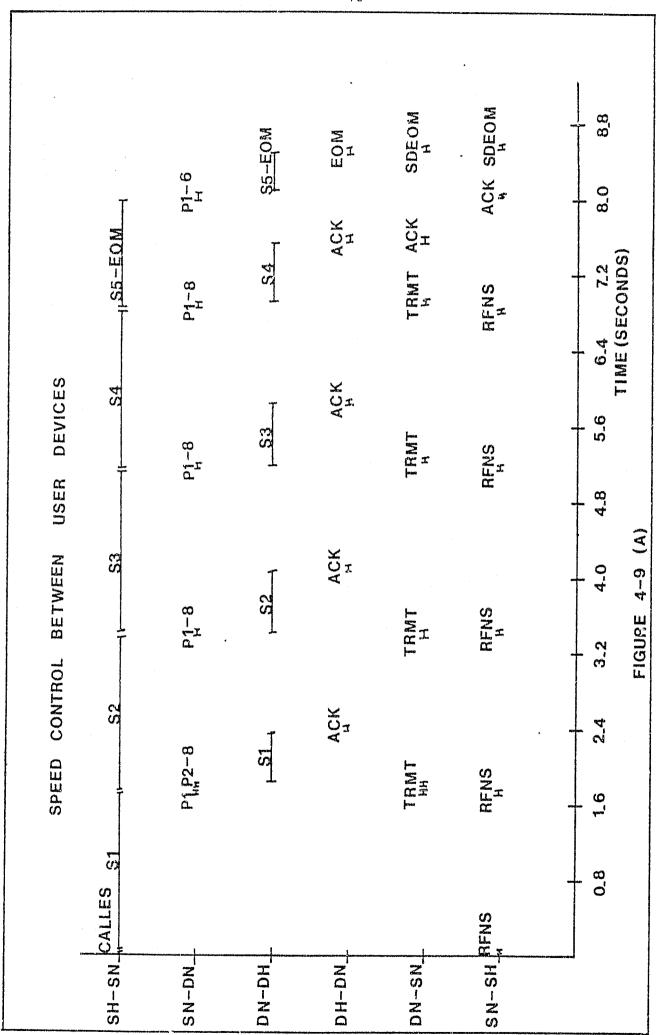

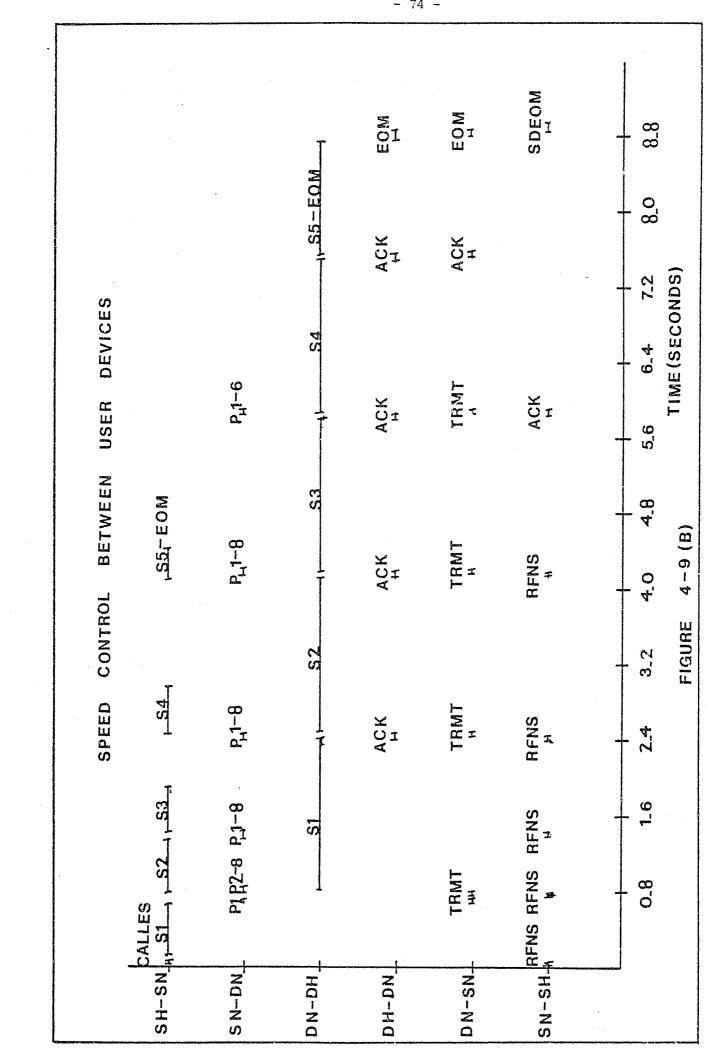

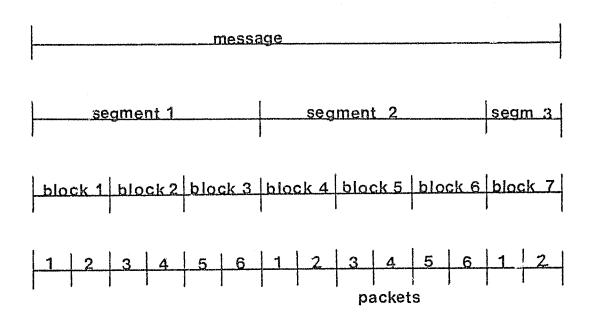

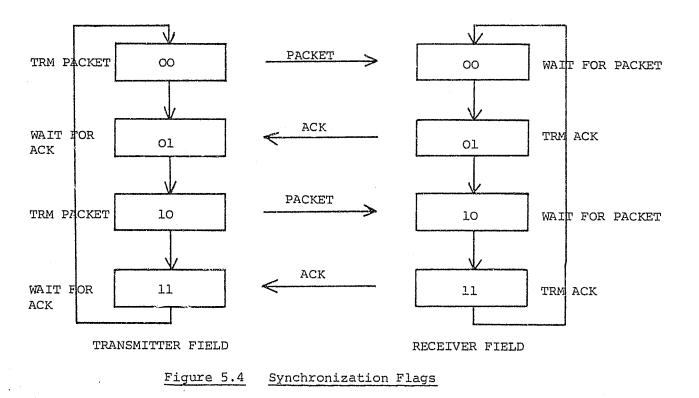

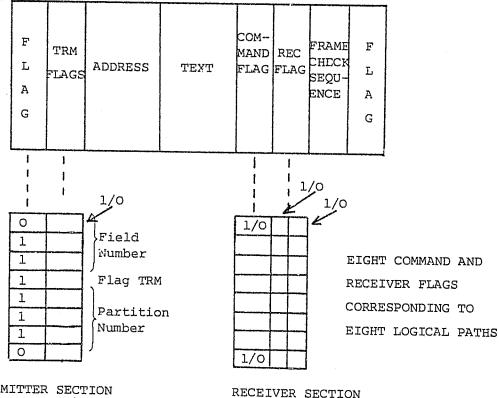

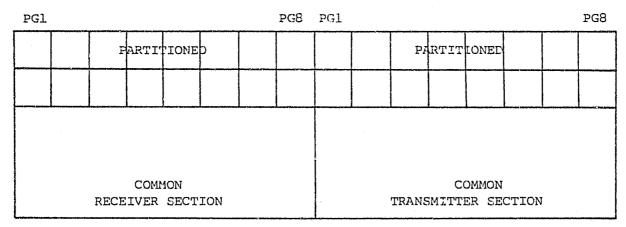

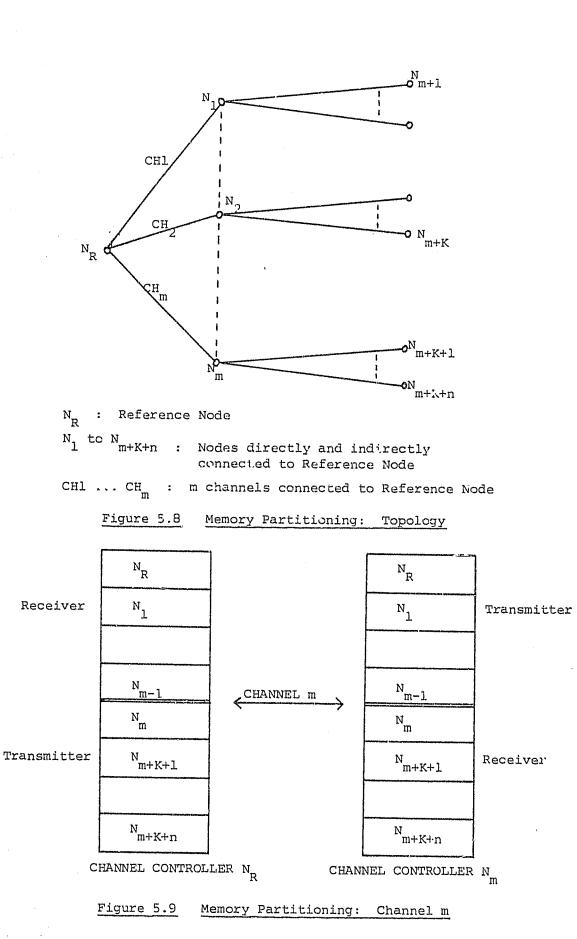

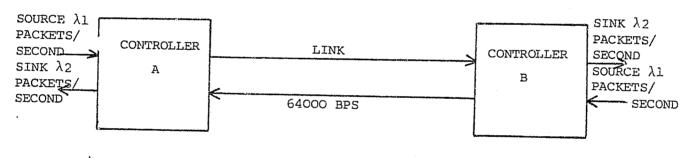

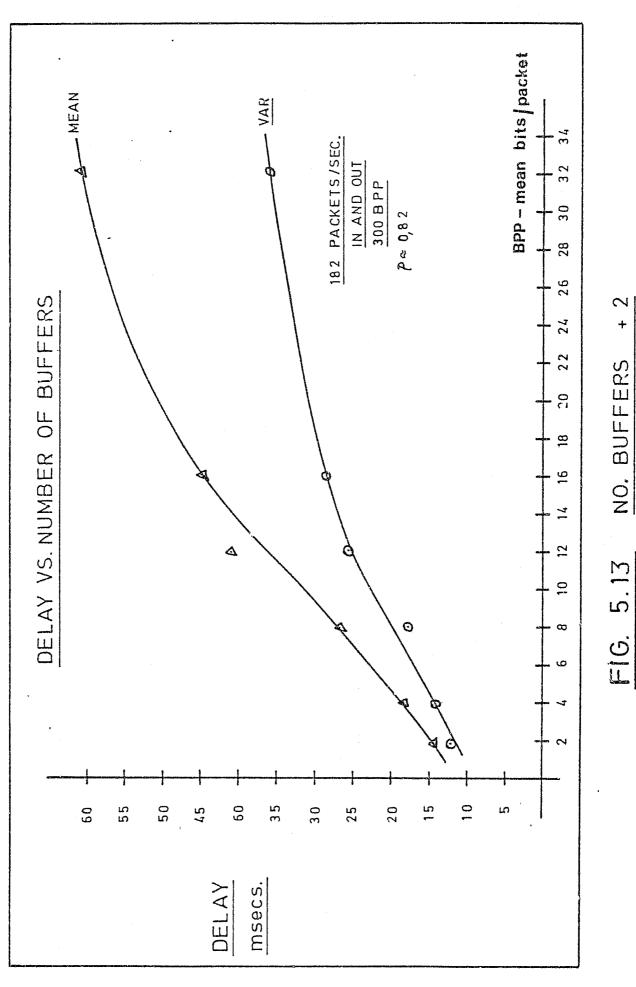

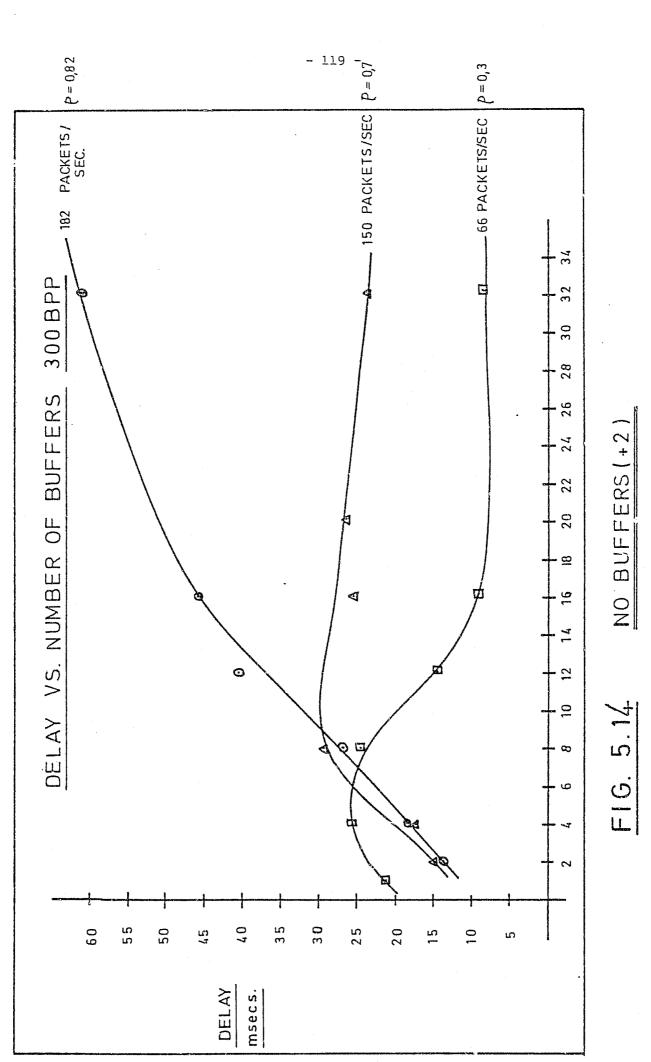

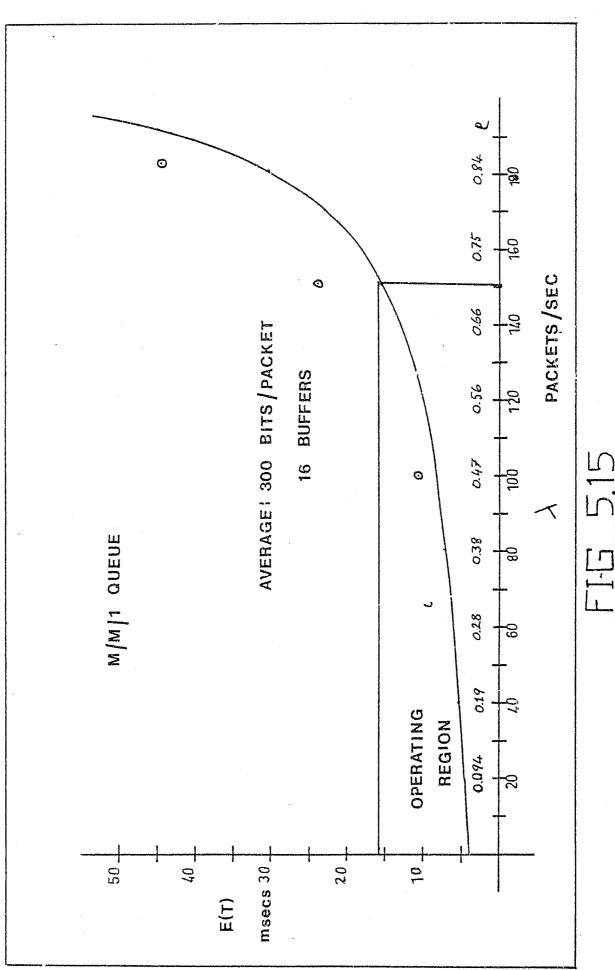

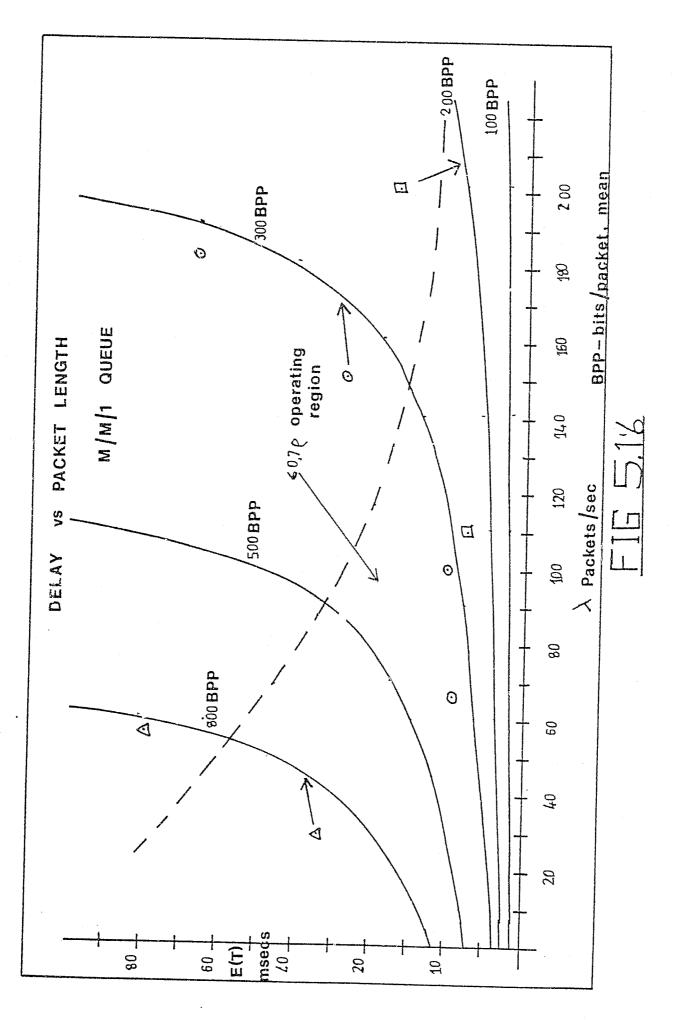

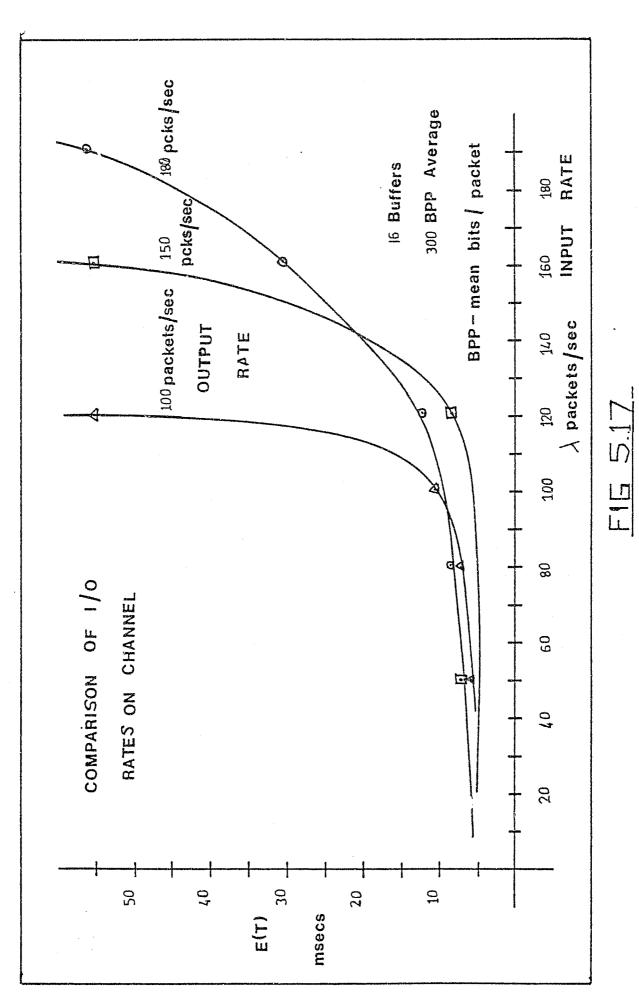

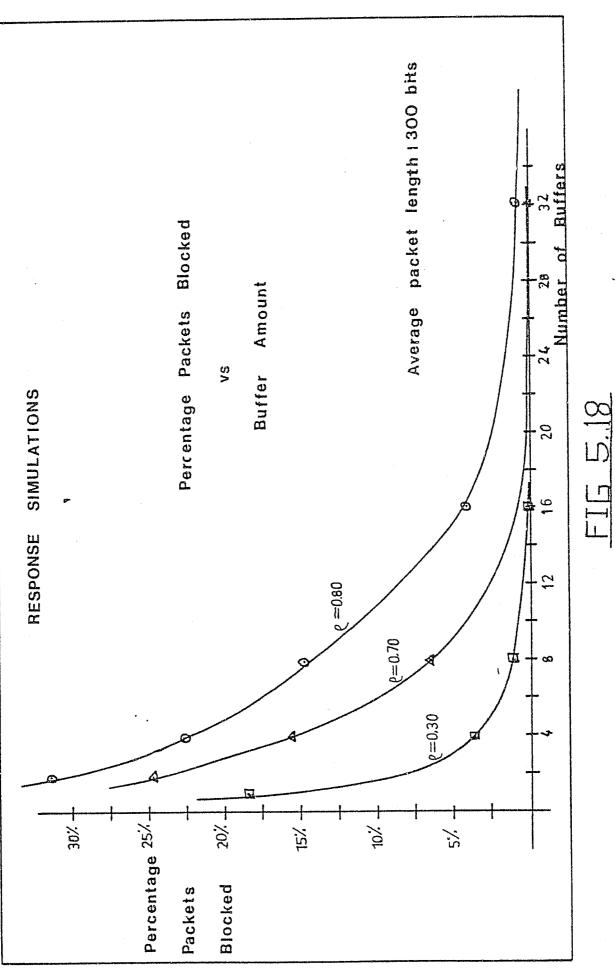

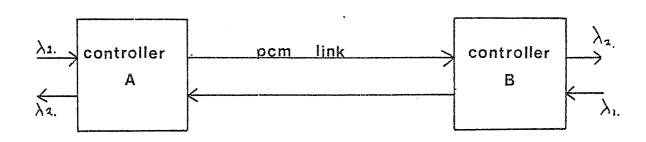

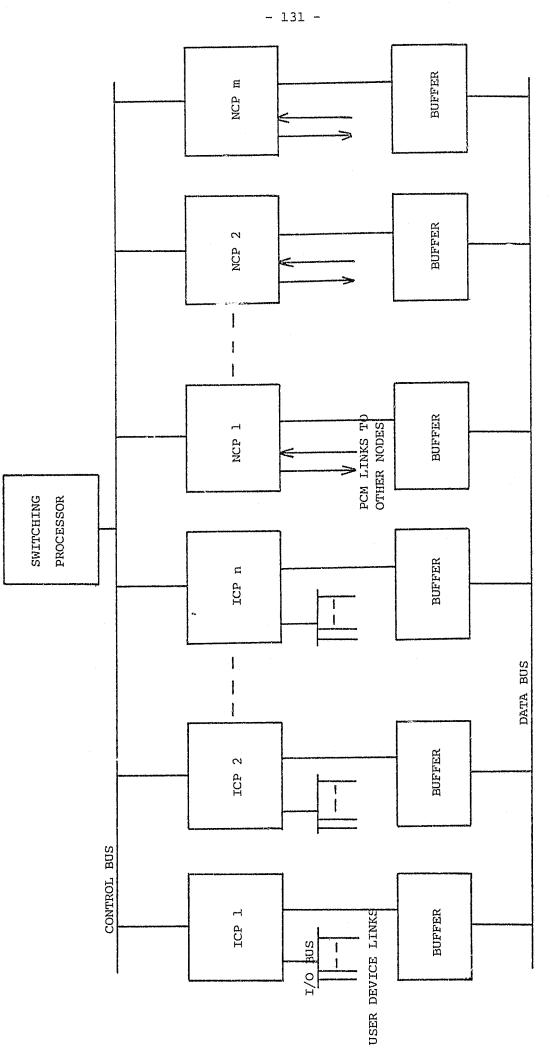

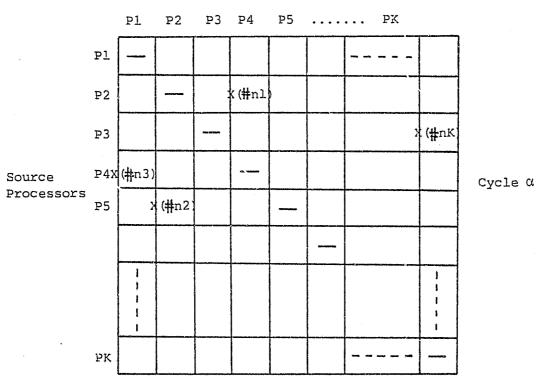

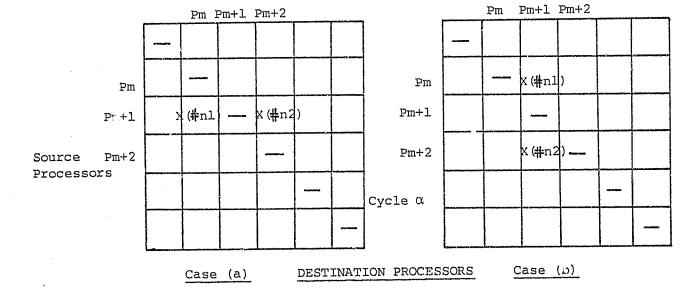

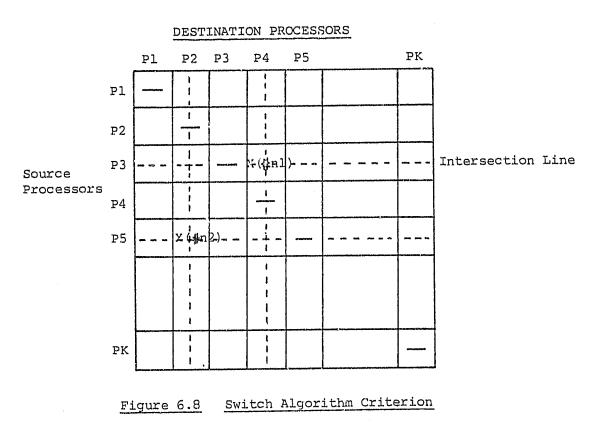

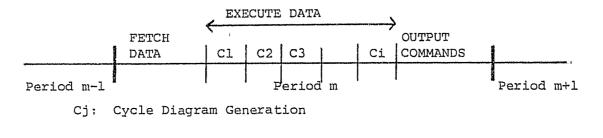

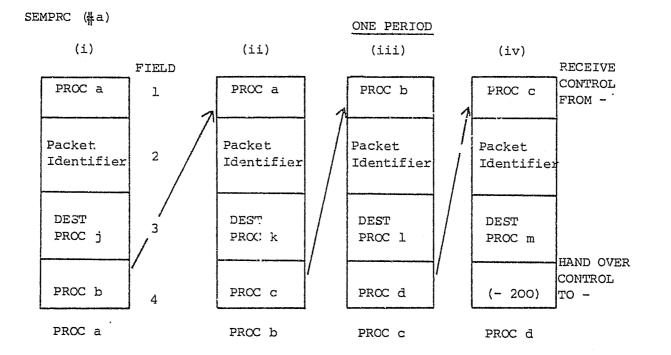

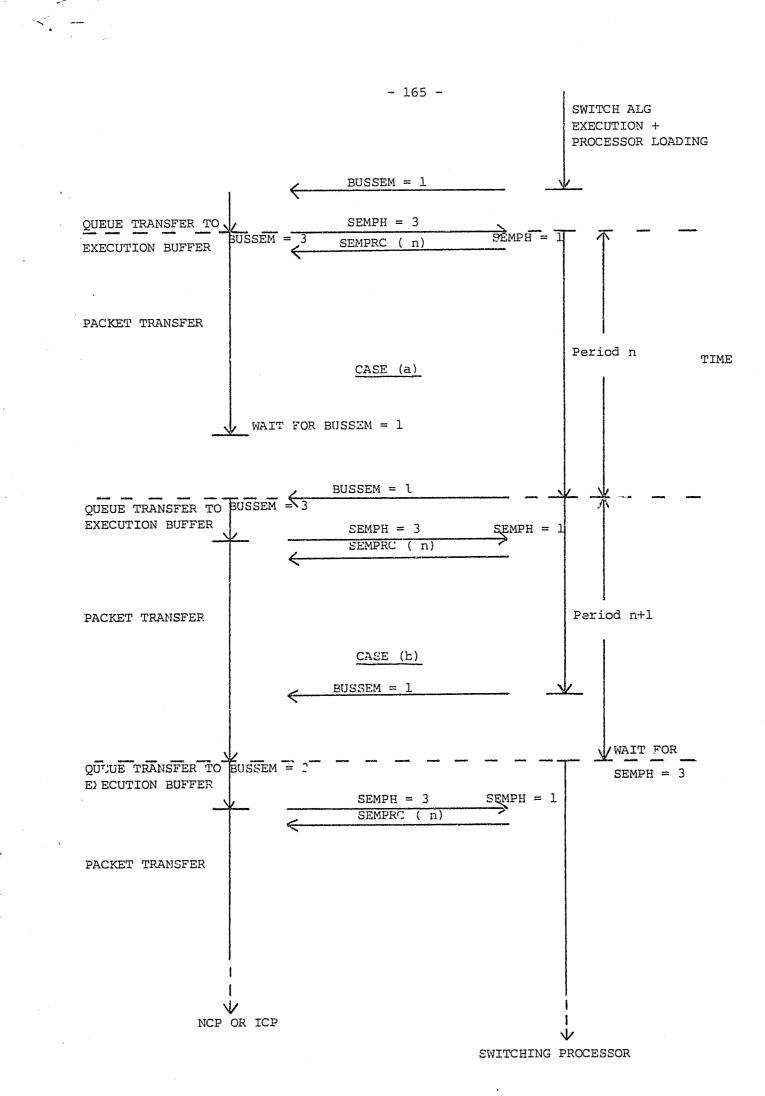

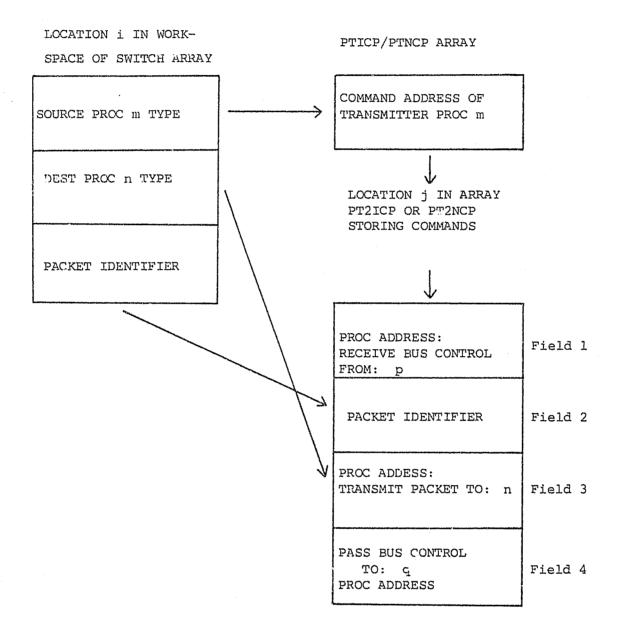

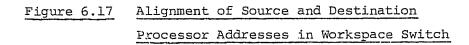

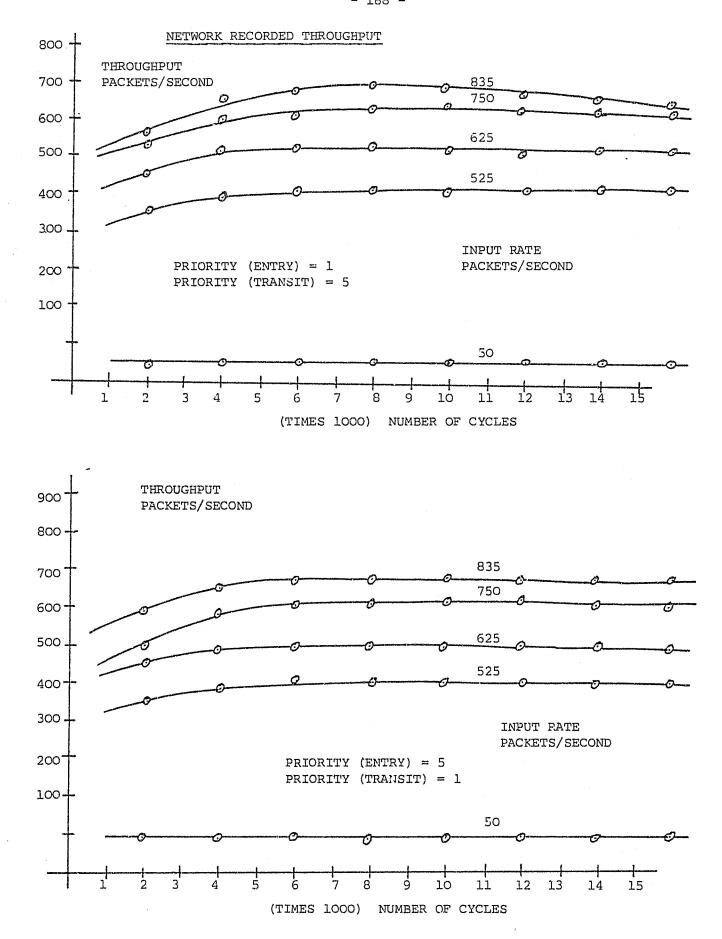

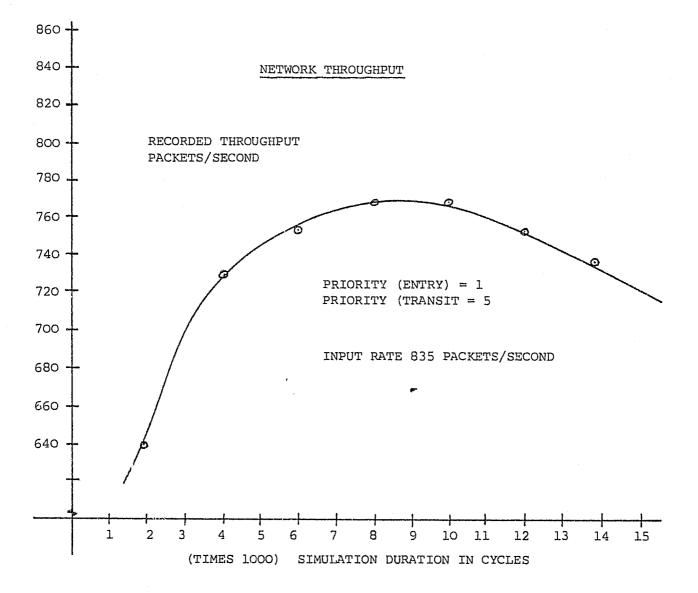

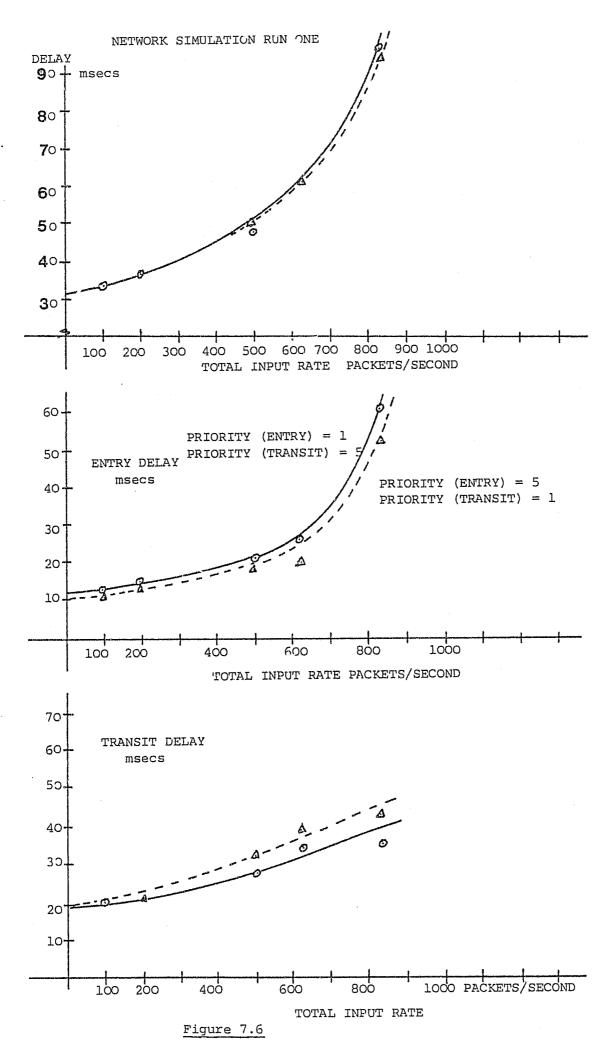

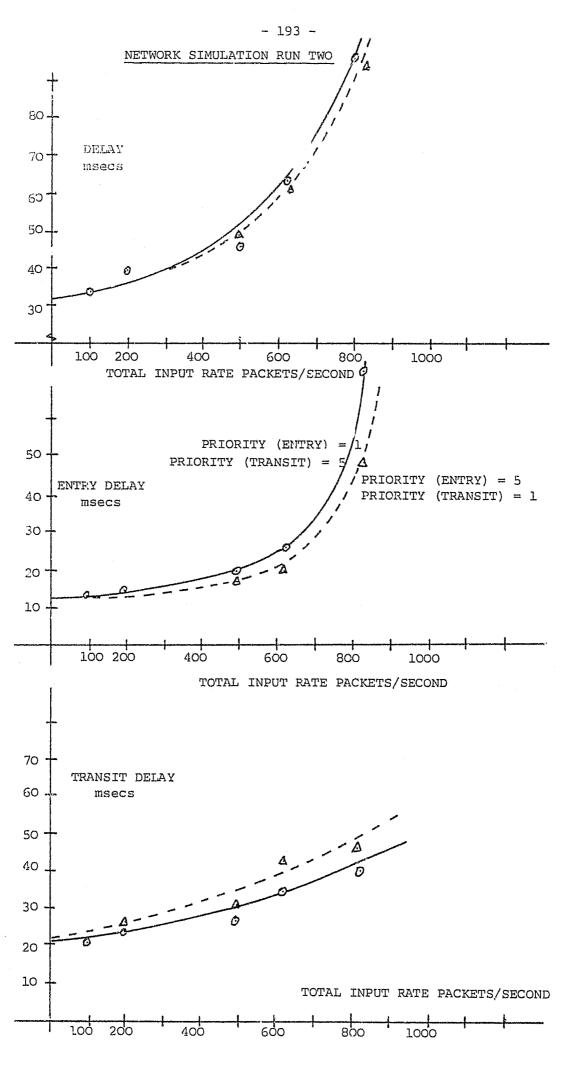

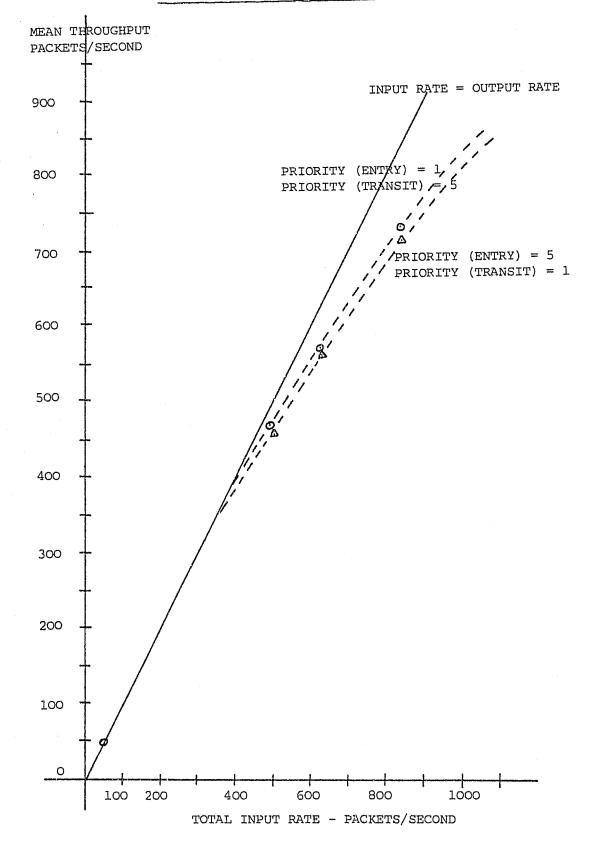

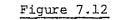

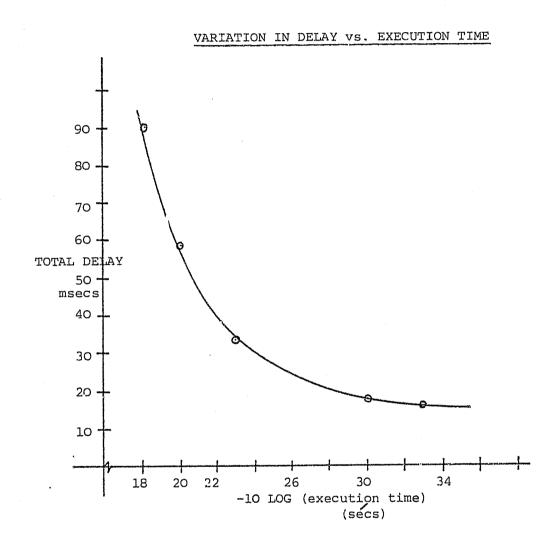

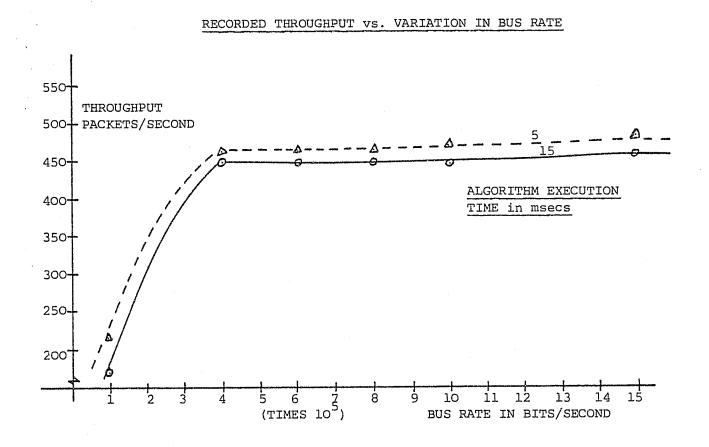

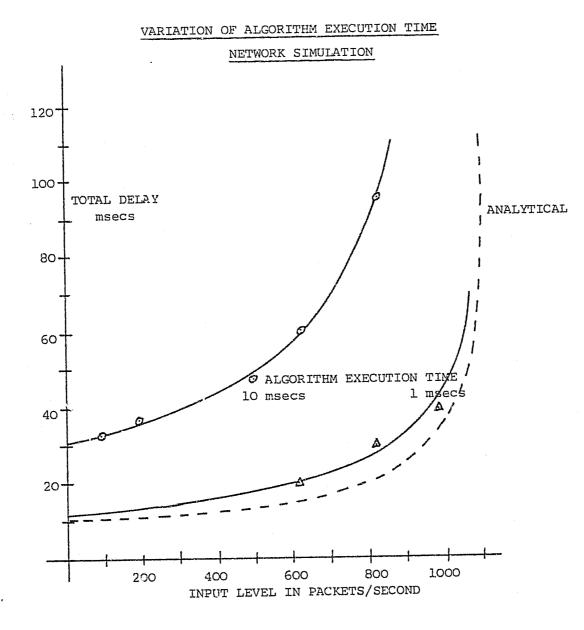

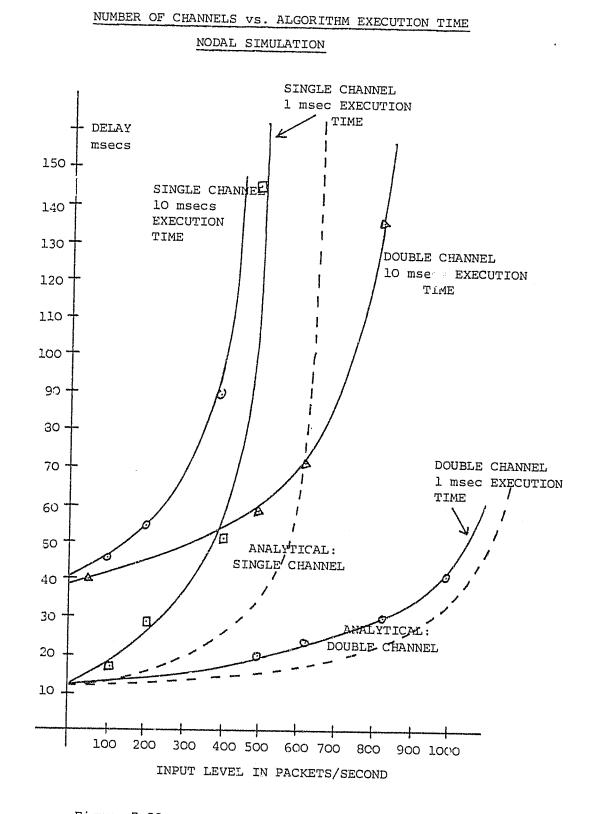

Each of these parameters is addressed by a subscript of a particular array. The size of the arrays allowed is dependent on the amount of storage available to the computer user. The Network Simulation was run on an IBM System/370 using a 512K memory partition.