### Power Quality Improvements of Single-phase Grid-connected Photovoltaic Systems

Abdalbaset Mohamed Mnider B.Eng., M. Eng.

A thesis submitted for the degree of

Doctor of Philosophy

May, 2017

School of Electrical and Electronic Engineering

Newcastle University United Kingdom

### To my Father, and my Mother

الى الوالد والوالدة أطال الله في عمر هما

### Abstract

The number of distributed power generation systems (DPGSs), mostly based on photovoltaic (PV) energy sources is increasing exponentially. These systems must conform to grid codes to ensure appropriate power quality and to contribute to grid stability. A robust and reliable synchronization to the grid is an important consideration in such systems. This is due to the fact that, fast and accurate detection of the grid voltage parameters is essential in order to implement stable control strategies under a broad range of grid conditions. The second-order generalized integrator (SOGI) based phase-locked loop (PLL) is widely used for grid synchronization of single-phase power converters. This is because it offers a simple, robust and flexible solution for grid synchronization. However, the SOGI-PLL is affected by the presence of a dc offset in the measured grid voltage. This dc voltage offset is typically introduced by the measurements and data conversion process, and causes fundamental-frequency ripple in the estimated parameters of the grid voltage (i.e. voltage amplitude, phase angle and frequency). In addition to this ripple, the unit amplitude sine and cosine signals of the estimated phase angle (i.e. unit vectors), that are used to generate reference signals in the closed-loop control of grid-connected PV converters will contain dc offset. This is highly undesirable since it can cause dc current injection to the grid, and as a consequence, the quality of the power provided by the DPGSs can be degraded. To overcome this drawback, a modified SOGI-PLL with dc offset rejection capability is proposed. The steady-state, transient and harmonic attenuation performance of the proposed PLL scheme are validated through simulation and experimental tests. The overall performance demonstrates the capability of the proposed PLL to fully reject such dc current injection as well as to provide a superior harmonic attenuation when compared with the SOGI-PLL and two other existing offset rejection approaches. It is shown that, the proposed PLL scheme can enhance the overall total harmonic distortion (THD%) of the injected power by 15% when compared to the conventional SOGI-PLL.

In addition to the synchronization, grid-connected PV systems require a current control scheme to regulate the output current. Due to the simple implementation, proportional-integral (PI) controllers in the stationary reference frame are commonly used for current controlled inverters. However, these PI-controllers exhibit a major drawback of failure to track a sinusoidal reference

#### Abstract

without steady-state error, which may result in low-order harmonics. This drawback can be overcome if the PI-controllers are implemented in direct-quadrature (dq) rotating reference frame. In single-phase systems, the common approach is to create a synthesized phase signal orthogonal to the fundamental of the real single-phase system so as to obtain dc quantities by means of a stationary-to-rotating reference frame. The orthogonal synthesized signal in conventional approaches is obtained by phase shifting the real signal by a quarter of the fundamental period. The introduction of such delay in the system deteriorates the dynamic response, which becomes slower and oscillatory. This thesis proposes an alternative way of implementing such PI-controllers in the dq reference frame without the need of creating such orthogonal signals. The proposed approach, effectively improves the poor dynamic of the conventional approaches while not adding excessive complexity to the controller structure. The results show that, in addition to its ability to regulate the current and achieve zero steady-state error, the proposed approach shows superior dynamic response when compared with that of conventional delay-based approach.

### Acknowledgements

First and foremost, Praise is to God (Allah), the most merciful and the most gracious, who gives me wisdom, strength and patience to complete this work. The author would like to take this chance to express sincere gratitude to those who have made this thesis possible.

I would like to thank the Libyan Government, as without their funding this work would not have been carried out. I am always indebted to my country Libya.

I acknowledge with deepest appreciation; the outstanding guidance, intellectual support and encouragement provided by my supervisor, Dr. David Atkinson, whose knowledge, and patience, added considerably to my research project. It was such a pleasant experience to work with Dave and learn from his expertise and experience in the field of control of grid-connected power converters which helped me through many difficulties.

Very special thanks are due to Dr Mohamed Dahidah for his valuable advice and consistent encouragement. His constructive notes always resulted in improvements to my work.

I would also like to acknowledge the significant contribution of Darren Mackie throughout the project; for his considerable help with the assembly of the electronic hardware. Also, special acknowledgement must also go to Gill Webber, the postgraduate research coordinator, for her support and great help.

Many thanks also go to my valuable friends in the UG lab, for their friendship and help throughout and in particular for the great time we have spent together.

My heartfelt appreciation goes to my first ever teachers in this life, my parents for their support and encouragement throughout my life. Without their constant assistance, prayers and blessings, I would not have reached this level of education.

Finally, the warmest thanks go to my wife, for her quiet patience, daily devotion and unwavering love. I am also indebted to my children; Moody, Jody, and little one Abdul for their warm hugs and lovely smiles every morning. I would like to say to them that from now on, we will enjoy more time together.

## Contents

| Abstract                                                     | i   |

|--------------------------------------------------------------|-----|

| Acknowledgements                                             | iii |

| Contents                                                     | iv  |

| Figures                                                      | xi  |

| Tables                                                       | xix |

| Symbols                                                      | XX  |

| CHAPTER 1 INTRODUCTION                                       | 1   |

| 1.1 Introduction                                             | 1   |

| 1.2 Project Motivation                                       |     |

| 1.3 Typical Operation of a Grid Connected PV Inverter System | 4   |

| 1.3.1 The choice of the DC/AC Inverter                       | 5   |

| 1.3.1.1 Five-level Diode-clamped Inverter                    | 6   |

| 1.3.1.2 PWM Switching Strategies                             | 9   |

| 1.3.2 Low-pass Filter                                        |     |

| 1.4 Grid Requirements for PV                                 |     |

| 1.4.1 Response to Abnormal Grid Conditions                   |     |

| 1.4.2 Power Quality Issues                                   |     |

| 1.4.2.1 DC Current Injection                                 |     |

| 1.4.2.2 Current Harmonics                                    |     |

| 1.4.2.3 Electromagnetic Interface (EMI)                      | 14  |

| 1.4.3 Anti-Islanding Protection                              | 14  |

| 1.5 Grid Connected Photovoltaic System Review                |     |

| 1.6 Thesis Overview                                          |     |

| CHAPTER 2 Grid Synchronisation in Single-Phase PV Systems    |     |

| 2.1 Introduction                                             |     |

| 2.2 Background                                               |     |

| 2.3 Zero-cross  | ing detection (ZCD) technique                       | 20 |

|-----------------|-----------------------------------------------------|----|

| 2.4 Phase-Loc   | ked Loop (PLL) technique                            | 21 |

| 2.4.1 Basic     | structure of a Phase-Locked Loop (PLL)              | 21 |

| 2.4.2 Conve     | ntional power-based pPLL                            | 22 |

| 2.4.3 PLL b     | ased on OSG (OSG-PLL)                               | 27 |

| 2.4.4 Overvi    | iew of different PLLs based on OSG                  | 29 |

| 2.4.4.1         | Transfer Delay-based OSG                            | 29 |

| 2.4.4.2         | Derivative-based OSG                                | 31 |

| 2.4.4.3         | Inverse Park Transform-based OSG                    |    |

| 2.4.4.4         | Other OSG techniques                                |    |

| 2.4.4.1         | Hilbert-transform                                   |    |

| 2.4.4.4.2       | All-pass filter                                     |    |

| 2.4.4.4.3       | Kalman filter                                       | 34 |

| 2.4.4.5         | Second-Order Generalized Integrator-based OSG       | 34 |

| 2.5 Summary     |                                                     | 34 |

| CHAPTER 3 S     | Second Order Generalized Integrator- PLL (SOGI-PLL) |    |

| 3.1 Introductio | n                                                   |    |

| 3.2 Overview    | of the SOGI-PLL structure                           | 35 |

| 3.3 Linearized  | Small Signal Model                                  | 42 |

| 3.4 Design Gu   | idelines                                            | 44 |

| 3.4.1 Stabili   | <i>ty</i>                                           | 45 |

| 3.4.2 Transi    | ent Performance                                     | 49 |

| 3.4.3 Distur    | bance Rejection                                     | 53 |

| 3.5 Performan   | ce Evaluation                                       |    |

| 3.5.1 Freque    | ency Variation                                      | 57 |

| 3.5.2 Phase     | Jump                                                | 60 |

| 3.5.3 Voltag    | e Sag and Swell                                     | 62 |

|                 |                                                     |    |

| 3.5.5 DC offset                                                                                                                                                                                                                                                                                                                                                                                                      | 67                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 3.5.6 Sub-harmonics                                                                                                                                                                                                                                                                                                                                                                                                  | 67                |

| 3.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| CHAPTER 4 DC Component Rejection in SOGI-PLL Algorithm                                                                                                                                                                                                                                                                                                                                                               |                   |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| 4.2 Overview of DC Component in PLL                                                                                                                                                                                                                                                                                                                                                                                  | 74                |

| 4.3 Effects of a DC Component in Grid Voltage Measurements                                                                                                                                                                                                                                                                                                                                                           |                   |

| 4.4 Proposed DC Offset Rejection Technique                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 4.4.1 Review of Conventional SOGI- OSG                                                                                                                                                                                                                                                                                                                                                                               | 80                |

| 4.4.2 Proposed CLPF-SOGI-OSG                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 4.4.3 Other Alternative Methods                                                                                                                                                                                                                                                                                                                                                                                      | 88                |

| 4.4.4 Comparison among CLPF-SOGI, and other existing dc offset rejection                                                                                                                                                                                                                                                                                                                                             | methods.92        |

| 4.5 Steady-state Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                              |                   |

| 4.6 The Effect of the PLL Method on the Grid-connected PV inverter Performa                                                                                                                                                                                                                                                                                                                                          | ince 101          |

| 4.7 Summary                                                                                                                                                                                                                                                                                                                                                                                                          | 105               |

|                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| CHAPTER 5 Grid Current Control                                                                                                                                                                                                                                                                                                                                                                                       | 107               |

| CHAPTER 5 Grid Current Control                                                                                                                                                                                                                                                                                                                                                                                       |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                      | 107               |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                     | 107<br>107        |

| <ul><li>5.1 Introduction</li><li>5.2 Background</li></ul>                                                                                                                                                                                                                                                                                                                                                            | 107<br>107<br>109 |

| <ul> <li>5.1 Introduction</li> <li>5.2 Background</li> <li>5.3 Current Regulation with PI Controller in the RRF</li> </ul>                                                                                                                                                                                                                                                                                           |                   |

| <ul> <li>5.1 Introduction</li> <li>5.2 Background</li> <li>5.3 Current Regulation with PI Controller in the RRF</li> <li>5.3.1 Mathematical Model</li> </ul>                                                                                                                                                                                                                                                         |                   |

| <ul> <li>5.1 Introduction</li> <li>5.2 Background</li> <li>5.3 Current Regulation with PI Controller in the RRF</li> <li>5.3.1 Mathematical Model</li> <li>5.3.2 Current Control Loop</li> </ul>                                                                                                                                                                                                                     |                   |

| <ul> <li>5.1 Introduction</li> <li>5.2 Background</li> <li>5.3 Current Regulation with PI Controller in the RRF</li> <li>5.3.1 Mathematical Model</li> <li>5.3.2 Current Control Loop</li> <li>5.4 Conventional Single-phase dq Current Controller</li> </ul>                                                                                                                                                        |                   |

| <ul> <li>5.1 Introduction</li> <li>5.2 Background</li> <li>5.3 Current Regulation with PI Controller in the RRF</li> <li>5.3.1 Mathematical Model</li> <li>5.3.2 Current Control Loop</li> <li>5.4 Conventional Single-phase dq Current Controller</li> <li>5.5 Simplified Single-phase dq Current Controller</li> </ul>                                                                                             |                   |

| <ul> <li>5.1 Introduction</li> <li>5.2 Background</li> <li>5.3 Current Regulation with PI Controller in the RRF</li> <li>5.3.1 Mathematical Model</li> <li>5.3.2 Current Control Loop</li> <li>5.4 Conventional Single-phase dq Current Controller</li> <li>5.5 Simplified Single-phase dq Current Controller</li> <li>5.6 Summary</li> </ul>                                                                        |                   |

| <ul> <li>5.1 Introduction</li> <li>5.2 Background</li> <li>5.3 Current Regulation with PI Controller in the RRF</li> <li>5.3.1 Mathematical Model</li> <li>5.3.2 Current Control Loop</li> <li>5.4 Conventional Single-phase dq Current Controller</li> <li>5.5 Simplified Single-phase dq Current Controller</li> <li>5.6 Summary</li> <li>CHAPTER 6 Implementation of Grid-Connected PV Inverter System</li> </ul> |                   |

| 6.4 Experimental Five-level Diode-clamped Inverter Module                  | 123 |

|----------------------------------------------------------------------------|-----|

| 6.5 Controller Details                                                     | 124 |

| 6.6 Gate Drives                                                            | 126 |

| 6.7 Voltage and Current Sensors                                            | 126 |

| 6.8 AC-Side Filter                                                         | 127 |

| 6.9 Variac and Isolation Transformer                                       | 127 |

| 6.10 Software Development Environment                                      | 128 |

| 6.11 The implementation of the PLL based CLPF-SOGI                         | 128 |

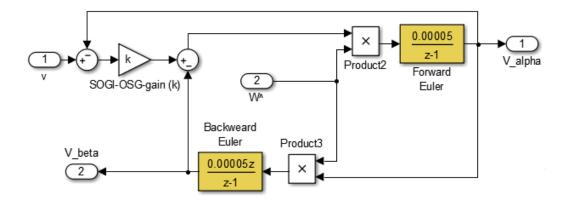

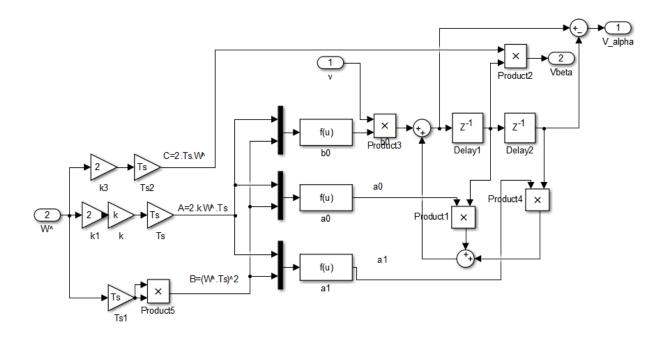

| 6.11.1 Discretization of the conventional SOGI                             | 129 |

| 6.11.2 Discretization of the proposed CLPF                                 | 134 |

| 6.11.3 Discretization of the loop filter (LF)                              | 135 |

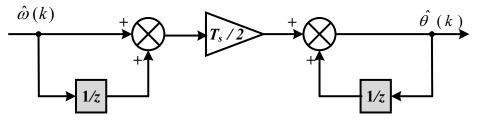

| 6.11.4 Discretization of the voltage-controlled oscillator (VCO)           | 137 |

| 6.12 The implementation of <i>dq</i> Current Controller                    | 138 |

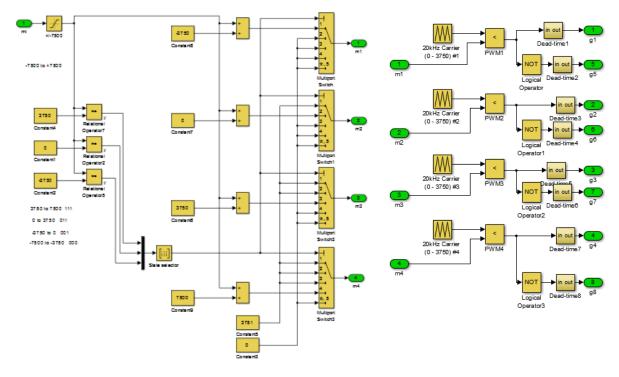

| 6.13 Pulse width modulation (PWM) set-up                                   | 139 |

| 6.14 Grid Connection Sequence                                              | 140 |

| 6.15 Summary                                                               | 141 |

| CHAPTER 7 Performance Evaluation of the CLPF-SOGI based PLL                | 142 |

| 7.1 Introduction                                                           | 142 |

| 7.2 Steady-state Performance Evaluation                                    | 143 |

| 7.3 Dynamic Performance Evaluation under Individual Disturbance Test Cases | 151 |

| 7.3.1 Performance Comparison under Frequency Variation                     | 151 |

| 7.3.2 Performance Comparison under Phase-angle Jump                        | 153 |

| 7.3.3 Performance Comparison under Voltage Sag                             | 155 |

| 7.3.4 Performance Comparison under Grid Voltage Harmonics                  | 157 |

| 7.3.5 Performance Comparison under DC Offset                               | 159 |

| 7.3.6 Performance Comparison with subharmonics added                       | 161 |

| 7.4 Dynamic Performance Evaluation under Combined Disturbances Test Cases  | 164 |

| 7.4.1 Performance Comparison under Frequency Variations with DC Offset     | 164 |

| v             | ormance Comparison under Voltage Sag, Phase Jump and Frequency (    | 0   |

|---------------|---------------------------------------------------------------------|-----|

|               | r                                                                   |     |

| CHAPTER 8     | Performance Evaluation of the DQ Current Controller                 | 170 |

| 8.1 Introduct | ion                                                                 | 170 |

| 8.2 Transient | Performance Evaluation                                              | 171 |

| 8.2.1 Conv    | ventional dq Current Controller                                     | 171 |

| 8.2.2 Simp    | lified dq Current Controller                                        | 174 |

| 8.3 The Effec | ct of the PLL Method on the Grid-connected PV Inverter Performance. | 176 |

| 8.4 Summary   | ,                                                                   | 182 |

| CHAPTER 9     | Thesis Conclusions                                                  | 183 |

| 9.1 Conclusio | on from CLPF-SOGI PLL Algorithm                                     | 183 |

| 9.2 Conclusio | on from Grid Current Control                                        | 185 |

| 9.3 Future W  | ork                                                                 | 186 |

| 9.4 Research  | Outcomes                                                            | 187 |

| Append        | ix A : Five-level Diode-clamped Inverter                            | 188 |

| Append        | ix B : LCL Filter Design                                            | 196 |

| Append        | ix C : Phase-locked Loop                                            | 203 |

| Append        | ix D : Programming Code                                             | 208 |

| References    |                                                                     |     |

## Figures

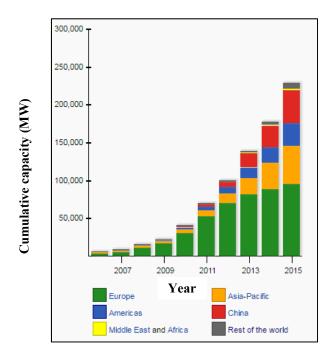

| Figure 1.1. The worldwide cumulative installed PV power in MW according to IEA [3]              |

|-------------------------------------------------------------------------------------------------|

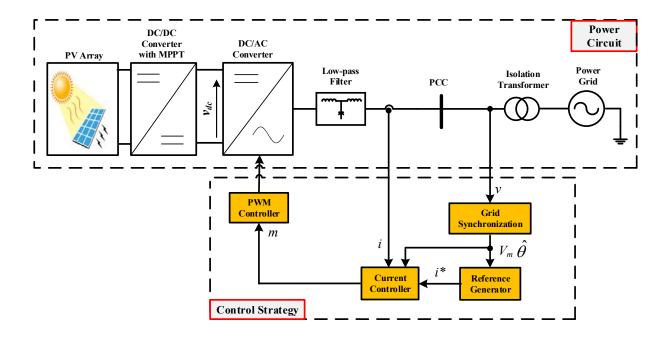

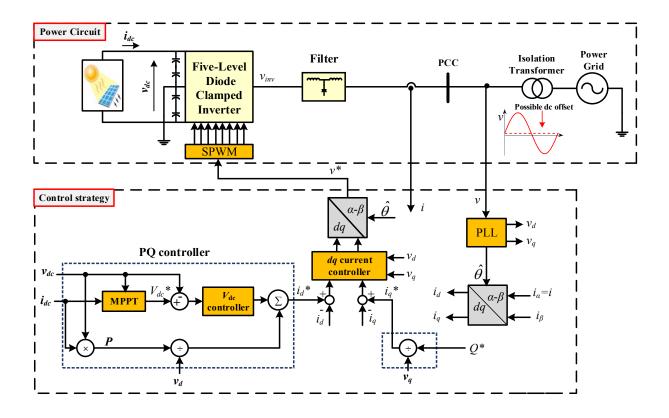

| Figure 1.2.Typical Grid Connected Photovoltaic Inverter System along with its associated        |

| control strategy                                                                                |

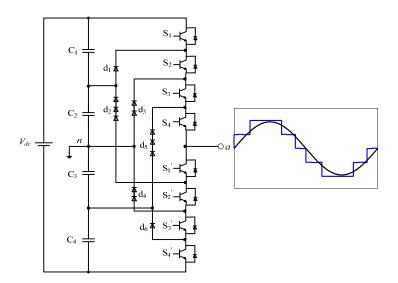

| Figure 1.3. Single-phase five-level diode-clamped inverter used in the proposed grid-connected  |

| PV system                                                                                       |

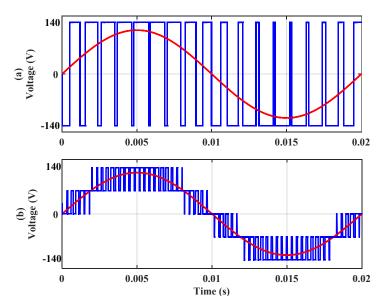

| Figure 1.4. Single-phase inverter output voltage waveforms: (a) two-level, (b) five-level       |

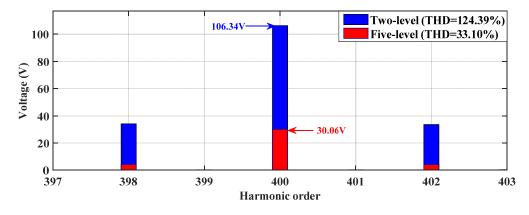

| Figure 1.5. Unfiltered inverter output voltage harmonics at 20 kHz switching frequency for two  |

| and five-level inverters                                                                        |

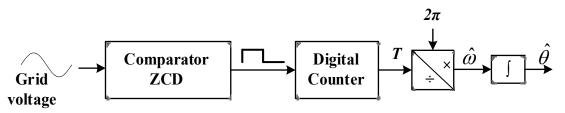

| Figure 2.1. Block diagram of zero crossing detection                                            |

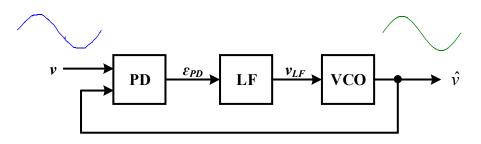

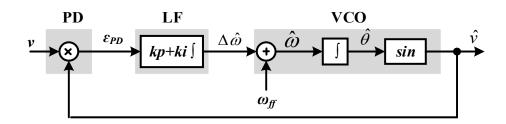

| Figure 2.2. Basic structure of a PLL                                                            |

| Figure 2.3. Block diagram of the single-phase pPLL                                              |

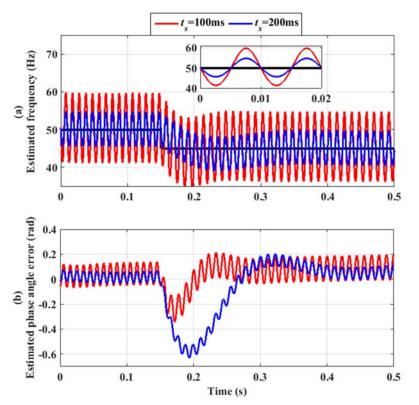

| Figure 2.4.Response of the pPLL when the input voltage undergoes a frequency step change a      |

| two different settling times: (a) estimated frequency, and (b) estimated phase-angle error24    |

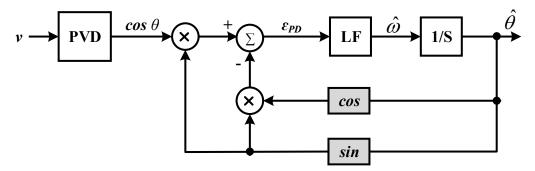

| Figure 2.5. Modified mixer PD (MMPD)-based PLL [72]25                                           |

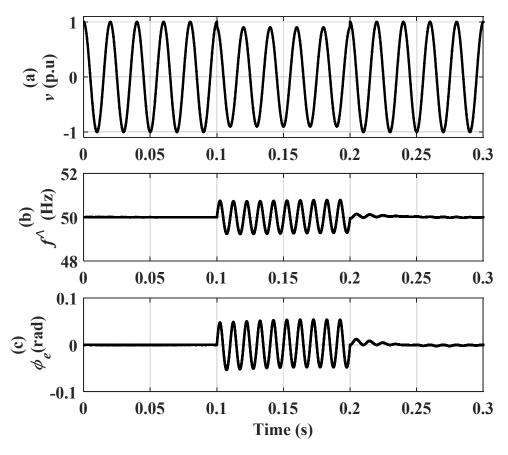

| Figure 2.6. Response of the MMPD-based PLL when the amplitude of input voltage undergoes        |

| voltage sag of 0.1p.u: (a) grid voltage, (b) estimated frequency, and (c) estimated phase-angle |

| error                                                                                           |

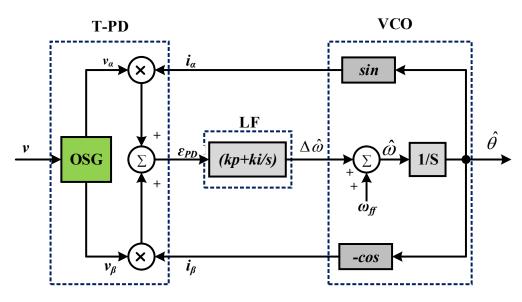

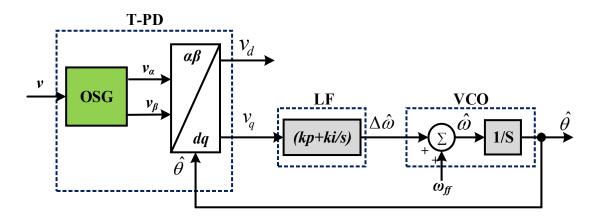

| Figure 2.7. Block diagram of single-phase PLL based-OSG-PD                                      |

| Figure 2.8. Block diagram of single-phase PLL in the rotating reference frame (SRF-PLL)28       |

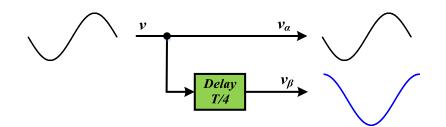

| Figure 2.9. Transport delay-based OSG                                                           |

| Figure 2.10. Response of the OSG-PLL transport delay-based under sudden frequency step o        |

| 5Hz                                                                                             |

| Figure 2.11. Response of the OSG-PLL transport delay-based when the input voltage undergoes     |

| an 8% THD                                                                                       |

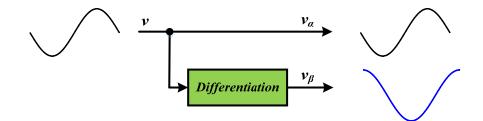

| Figure 2.12. Derivative-based OSG                                                               |

| Figure 2.13. Response of the OSG-PLL derivative-based under sudden frequency step of 5Hz        |

|                                                                                                 |

| Figure 2.14.Response of the OSG-PLL derivative -based when the input voltage undergoes an       |

| 8% THD                                                                                          |

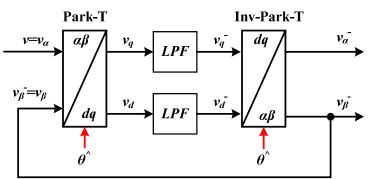

| Figure 2.15. Inverse Park Transform-based OSG                                                    | 33             |

|--------------------------------------------------------------------------------------------------|----------------|

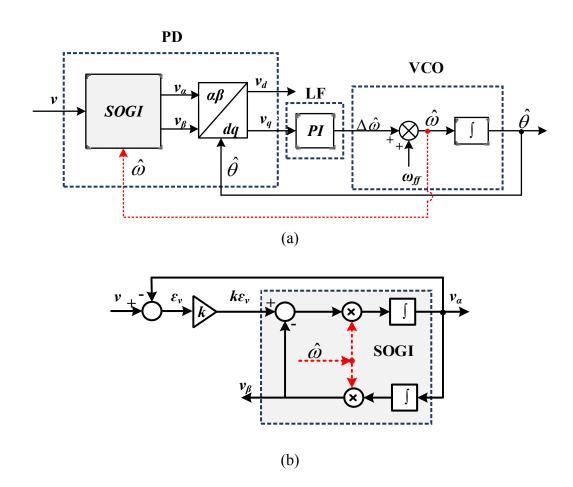

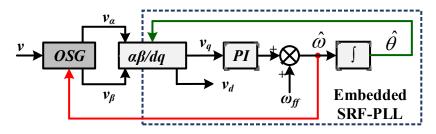

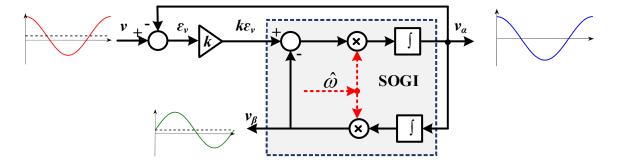

| Figure 3.1. SOGI-PLL: (a) Basic structure and (b) SOGI block.                                    | 36             |

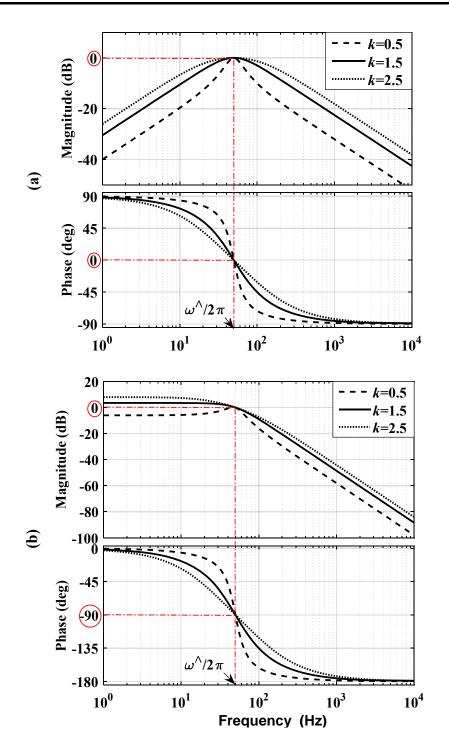

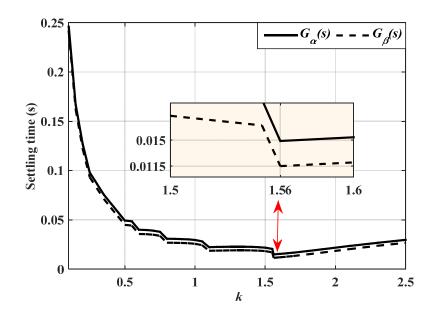

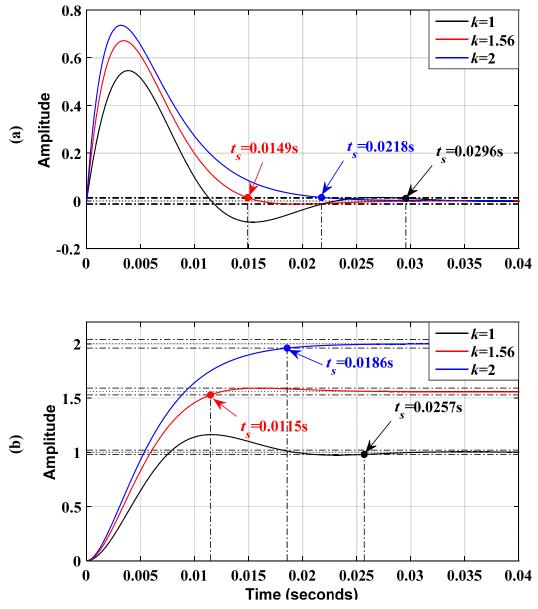

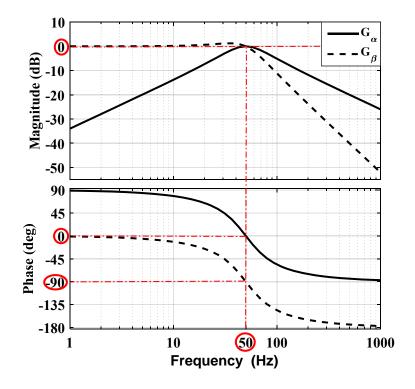

| Figure 3.2. Frequency response of the characteristic transfer functions of the SOGI              |                |

| for different values of gain k: (a) $G_{\alpha}s$ and (b) $G_{\beta}s$ .                         |                |

| Figure 3.3 Settling time <i>t</i> <sub>s</sub> versus gain <i>k</i>                              |                |

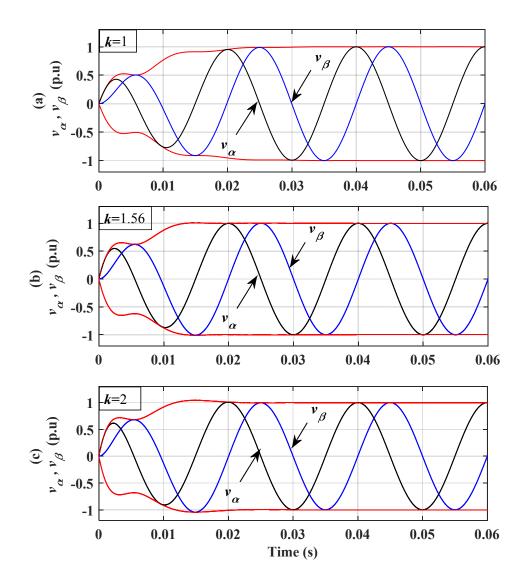

| Figure 3.4. Response of the SOGI-OSG for different values of gain $k$ : (a) ( $k$ =1), (b) ( $k$ |                |

| and (c) ( <i>k</i> =2)                                                                           |                |

| Figure 3.5. Step response of the characteristic transfer functions of the SOGI block for di      | fferent        |

| values of gain k: (a) $G_{\alpha}s$ and (b) $G_{\beta}s$                                         | 41             |

| Figure 3.6. Linearized model of the SOGI-PLL                                                     | 44             |

| Figure 3.7. An amplitude compensation block                                                      |                |

| Figure 3.8. Modified linearized model                                                            | 45             |

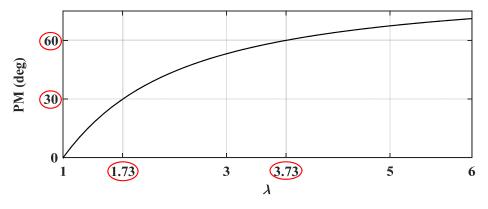

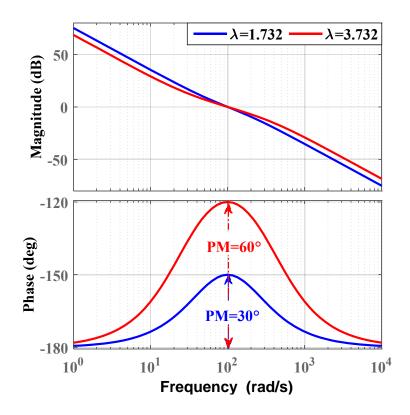

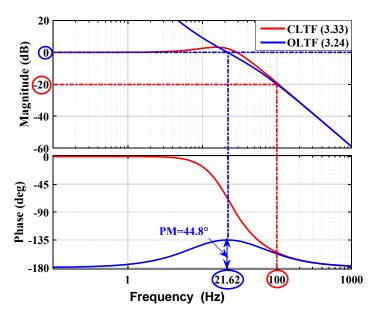

| Figure 3.9. Phase margin versus factor $\lambda$                                                 | 47             |

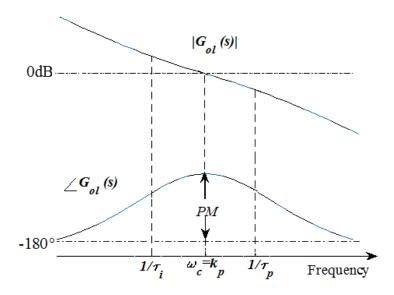

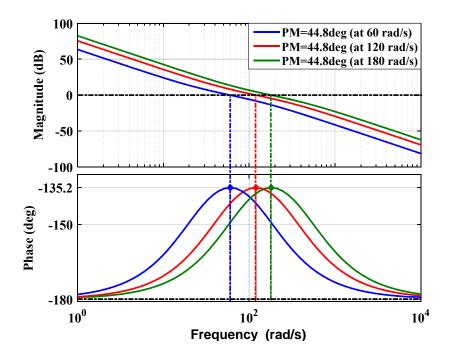

| Figure 3.10. Logarithmic plot of the open-loop transfer function                                 | 48             |

| Figure 3.11. Bode-plot of the open-loop transfer for two different values of $\lambda$           | 48             |

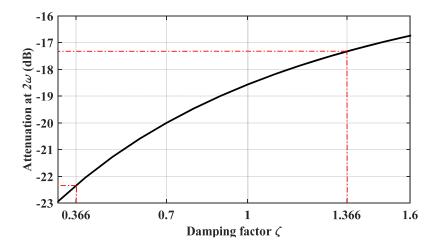

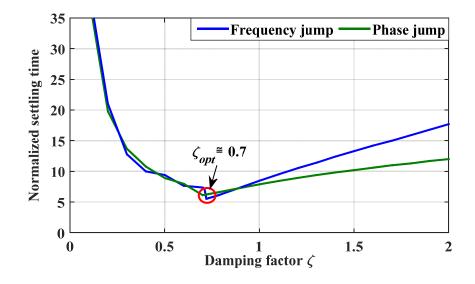

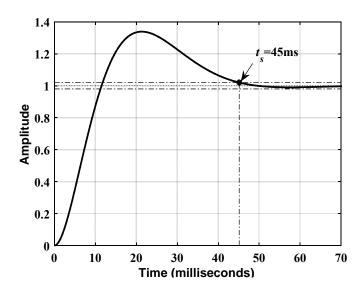

| Figure 3.12. Attenuation versus damping factor $\xi$                                             | 51             |

| Figure 3.13. Normalized settling time versus damping factor $\zeta$ for both phase and free      | quency         |

| jumps                                                                                            | 52             |

| Figure 3.14. Bode-plot of the open-loop transfer function as a function of natural frequen       | ncy $\omega_n$ |

|                                                                                                  | 52             |

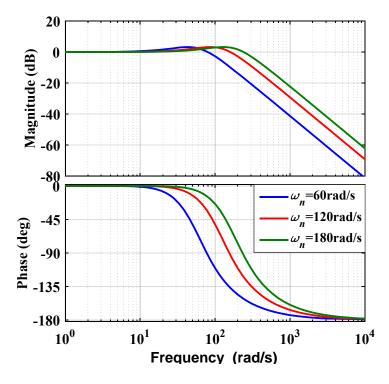

| Figure 3.15. Bode-plot of the disturbance transfer function as a function of the natural free    | quency         |

| Øn                                                                                               | 53             |

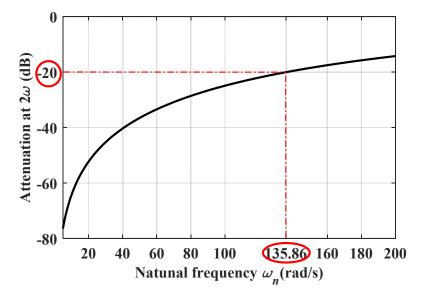

| Figure 3.16. PLL attenuation at $2\omega$ versus the natural frequency $\omega_n$                | 54             |

| Figure 3.17. Bode-plots of the open-loop (OLTF) and closed loop (CLTF) transfer fur              | nctions        |

| based on the PLL parameters of (3.34)                                                            | 55             |

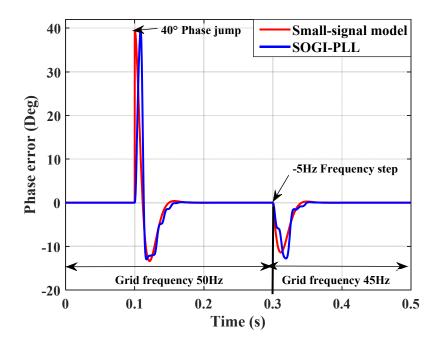

| Figure 3.18. PLL response to input step disturbance                                              | 55             |

| Figure 3.19. Accuracy assessment of the small-signal model of the SOGI-PLL                       | 56             |

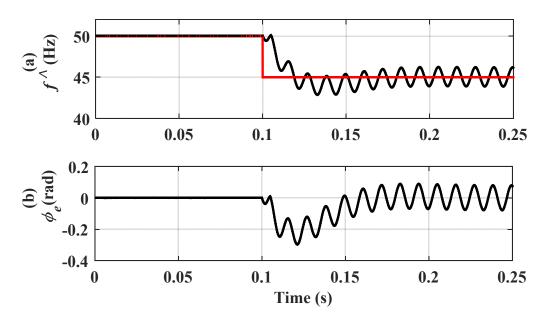

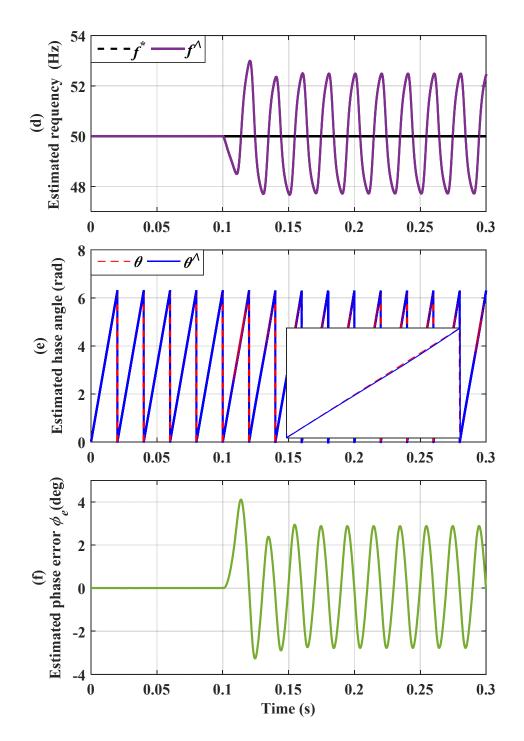

| Figure 3.20. Response of the SOGI-PLL when the input voltage undergoes frequence                 | cy step        |

| changes: (a) Input voltage, (b) orthogonal signals generated by the SOGI-OSG, (c) sig            | nals in        |

| the synchronous reference frame, (d) estimated frequency, (e) estimated phase-angle a            | and (f)        |

| estimated phase-angle error.                                                                     | 59             |

| Figure 3.21. Response of the SOGI-PLL when the input voltage undergoes a phase jump of 40°:            |

|--------------------------------------------------------------------------------------------------------|

| (a) Input voltage, (b) orthogonal signals generated by the SOGI-OSG, (c) signals in the                |

| synchronous reference frame, (d) estimated frequency, (e) estimated phase-angle and (f)                |

| estimated phase-angle error61                                                                          |

| Figure 3.22. Response of the SOGI-PLL when the input voltage undergoes voltage sag of 30%              |

| and voltage swell of 50%: (a) Input voltage, (b) orthogonal signals generated by the SOGI-             |

| OSG, (c) signals in the synchronous reference frame, (d) estimated frequency, (e) estimated            |

| phase-angle and (f) estimated phase-angle error64                                                      |

| Figure 3.23. Response of the SOGI-PLL when the input voltage undergoes a 15% third-                    |

| harmonic injection: (a) Input voltage, (b) orthogonal signals generated by the SOGI-OSG, (c)           |

| signals in the synchronous reference frame, (d) estimated frequency, (e) estimated phase-angle         |

| and (f) estimated phase-angle error66                                                                  |

| Figure 3.24. Response of the SOGI-PLL when the input voltage undergoes a 5% dc offset: (a)             |

| Input voltage, (b) orthogonal signals generated by the SOGI-OSG, (c) signals in the                    |

| synchronous reference frame, (d) estimated frequency, (e) estimated phase-angle and (f)                |

| estimated phase-angle error                                                                            |

| Figure 3.25. Response of the SOGI-PLL when the input voltage undergoes a 10% of 1Hz                    |

| subharmonic: (a) Input voltage, (b) orthogonal signals generated by the SOGI-OSG, (c) signals          |

| in the synchronous reference frame, (d) estimated frequency, (e) estimated phase-angle and (f)         |

| estimated phase-angle error                                                                            |

| Figure 4.1. System configuration of SPGCs                                                              |

| Figure 4.2. Block diagram of single-phase OSG-PLL77                                                    |

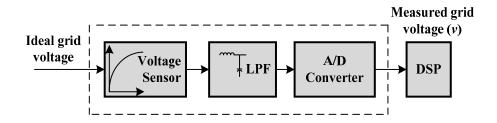

| Figure 4.3. Grid voltage measurement circuit                                                           |

| Figure 4.4. Basic structure of Conventional SOGI-OSG                                                   |

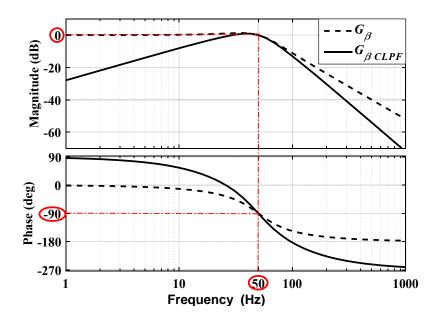

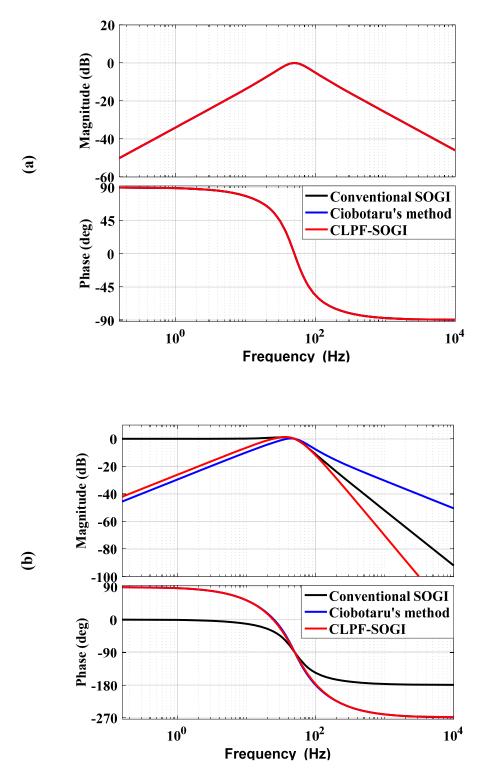

| Figure 4.5. Bode-plots of $G_{\alpha}s$ and $G_{\beta}s$ for $k=1$ and when $\omega = 2\pi.50$ rad/s80 |

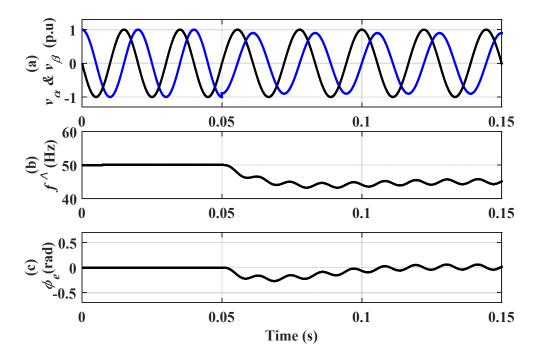

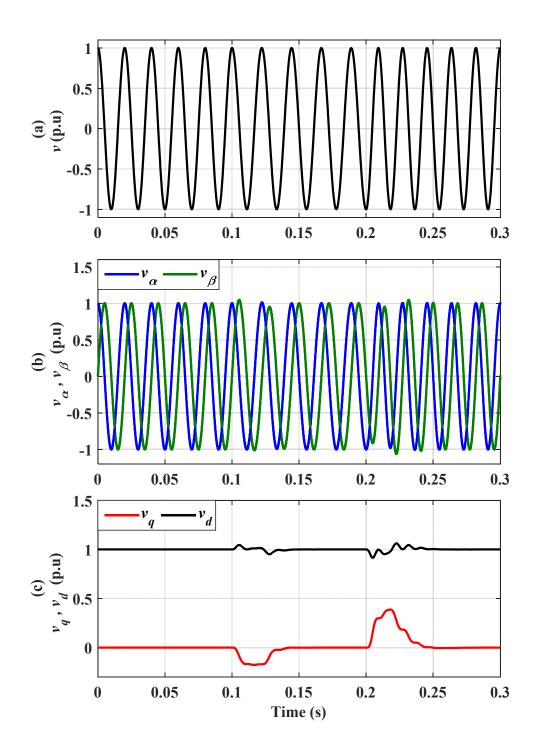

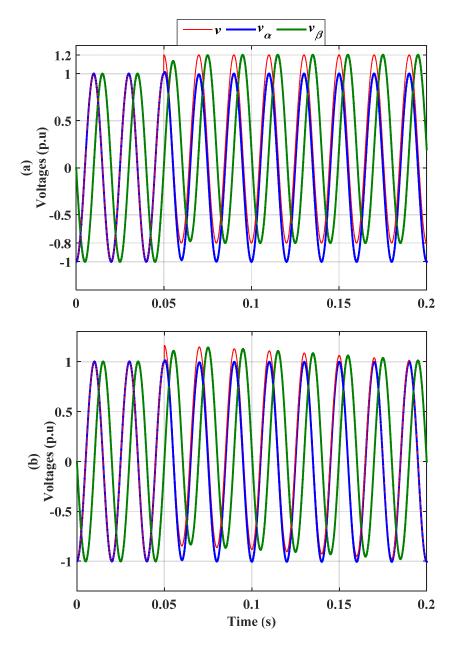

| Figure 4.6. SOGI-OSG responses when the input signal $v$ at time = 0.05s undergoes                     |

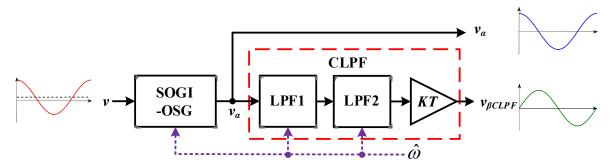

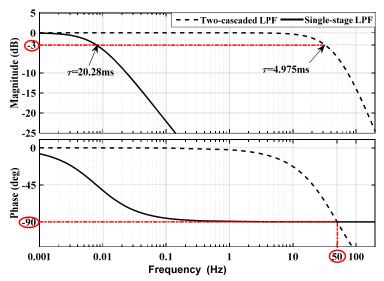

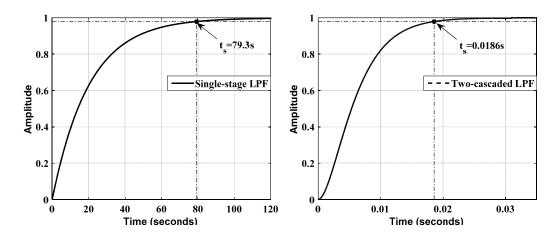

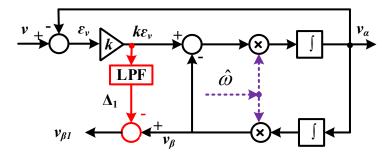

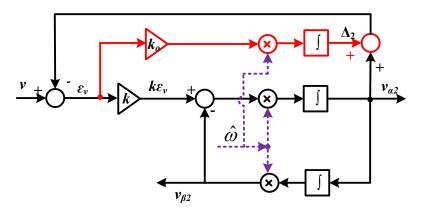

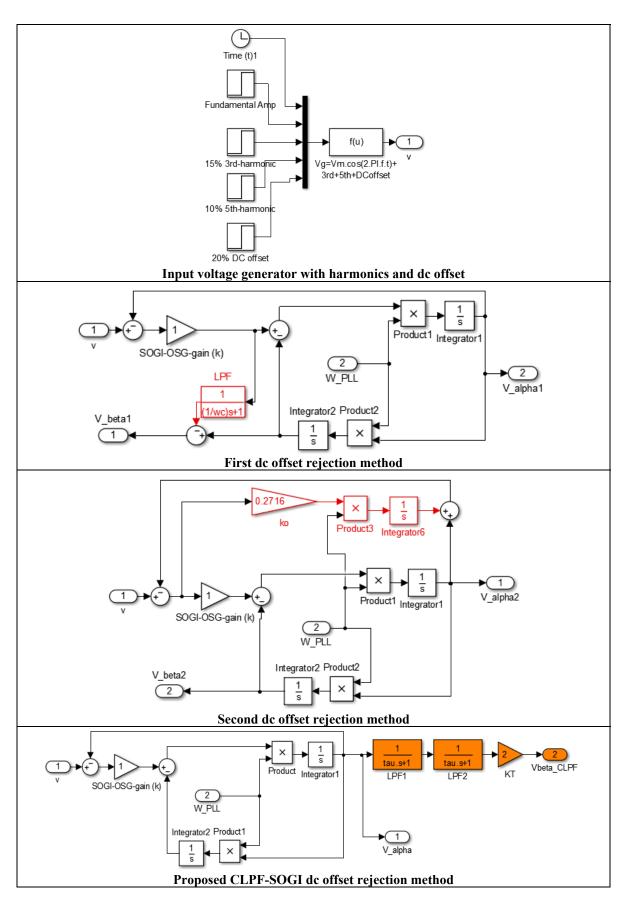

| Figure 4.7. General structure of the proposed CLPF-SOGI-OSG                                            |

| Figure 4.8. Bode-plots of (4.8) for creating $v_{\beta}$ using single-stage LPF, and two-cascaded LPF  |

|                                                                                                        |

| Figure 4.9. Step response of (4.8) for creating $v_{\beta}$ using a single-stage LPF, and Two-cascaded |

| LPF                                                                                                    |

|                                                                                                        |

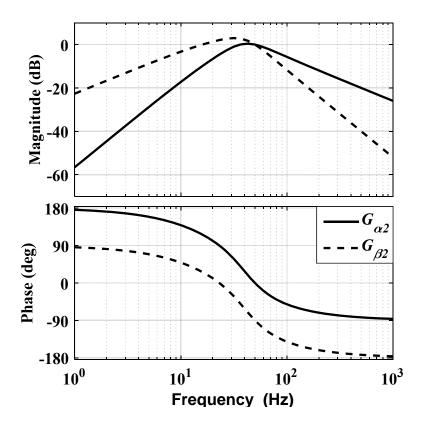

| Figure 4.10. Bode plots of $G_{\beta}$ and $G_{\beta CLPF}$ for $k=1$ and when $\omega = 2\pi.50$ rad/s               |

|-----------------------------------------------------------------------------------------------------------------------|

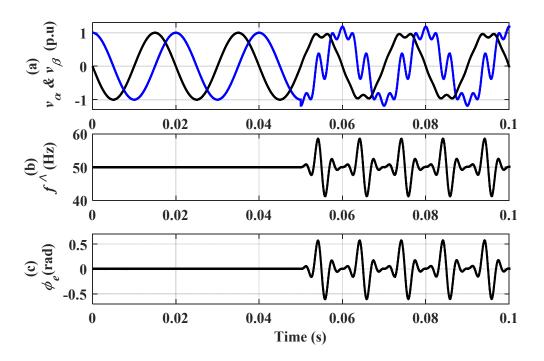

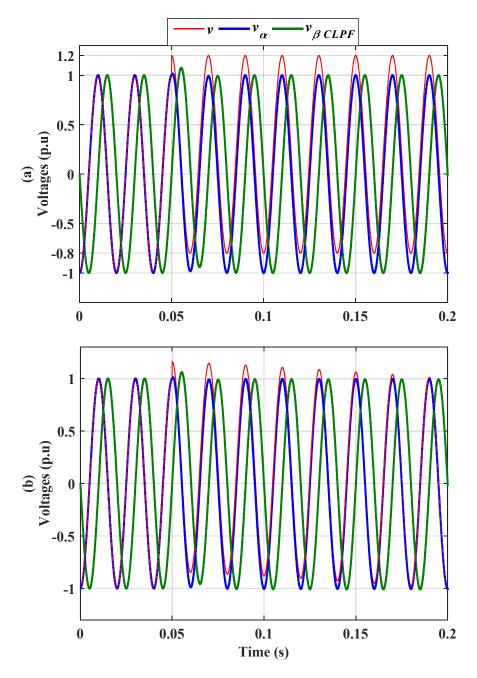

| Figure 4.11. CLPF-SOGI-OSG responses when the input signal $v$ at time = 0.05s undergoes87                            |

| Figure 4.12. Structure of Ciobotaru's method [113]                                                                    |

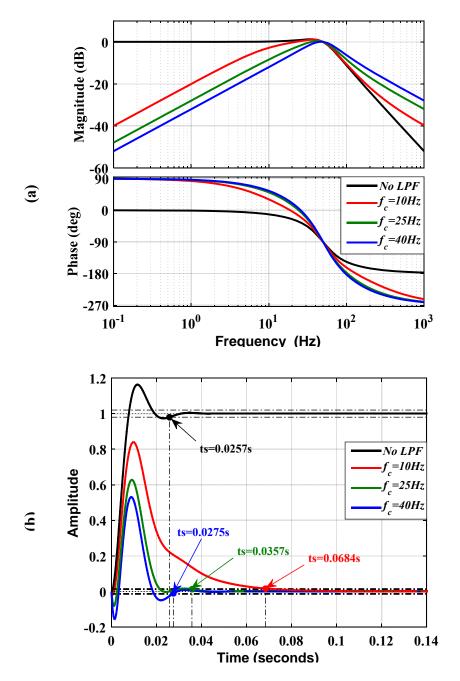

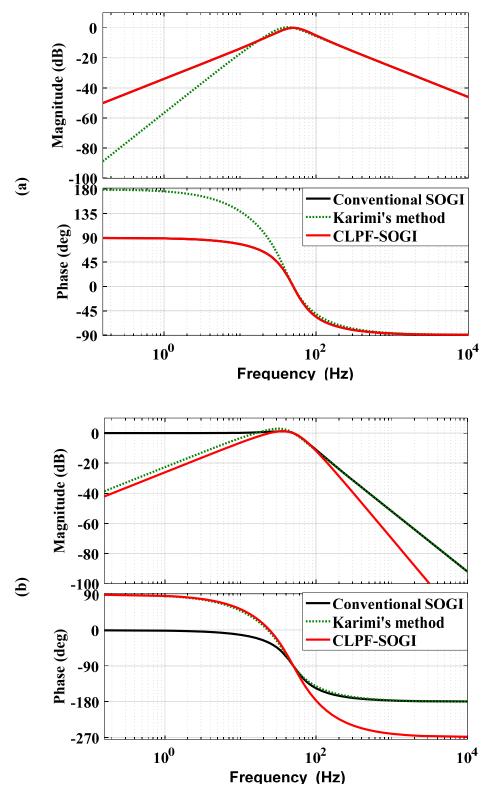

| Figure 4.13. Bode-plot (a) and step response (b) of $G_{\beta 1}s$ at different values of $f_c$ and when $k=1$        |

|                                                                                                                       |

| Figure 4.14. Structure of Karimi's method [114]                                                                       |

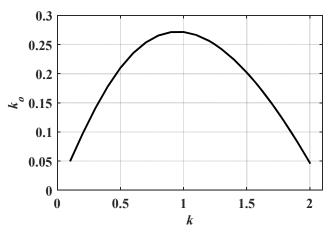

| Figure 4.15. Design of dc loop's gain                                                                                 |

| Figure 4.16. Frequency response of Karimi's method when $k=1$ and $k_0=0.271691$                                      |

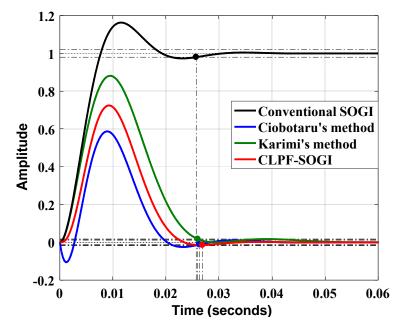

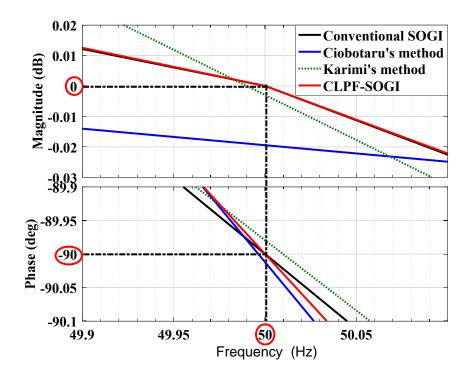

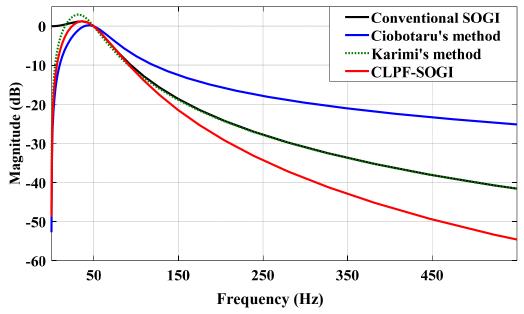

| Figure 4.17. Step response of $G_{\beta}s$ , $G_{\beta 1}s$ , $G_{\beta 2}s$ and $G_{\beta CLPF}s$ based on table 4-1 |

| Figure 4.18. Frequency response plotted with Ciobotaru's method, proposed CLPF-SOGI, and                              |

| conventional SOGI for relating (a) in-phase output to input v and (b) orthogonal output to inpu                       |

| <i>v</i>                                                                                                              |

| Figure 4.19. Frequency response plotted with Karimi's method, proposed CLPF-SOGI, and                                 |

| conventional SOGI-OSG for relating (a) in-phase output to input $v$ and (b) orthogonal output                         |

| to input v                                                                                                            |

| Figure 4.20. Zoomed frequency response of $G_{\beta}s$ for different SOGI-OSG techniques                              |

| Figure 4.21. Amplitude Bode-plot of the orthogonal output to the input for different SOGI-OSC                         |

| techniques                                                                                                            |

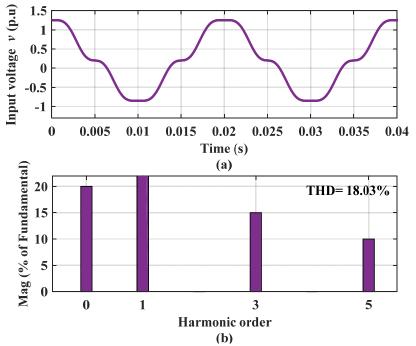

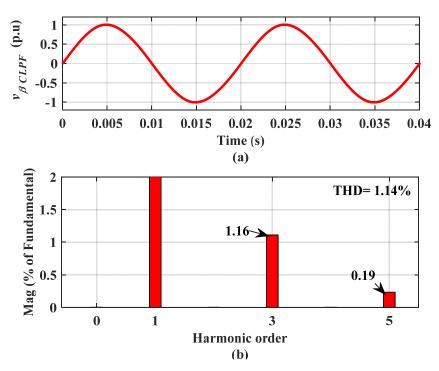

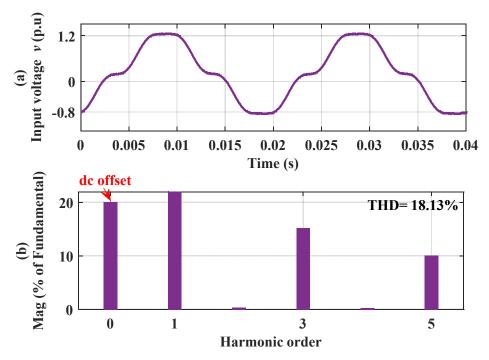

| Figure 4.22. Simulated results of (a) distorted input voltage waveform $v$ and (b) its harmonic                       |

| spectrum                                                                                                              |

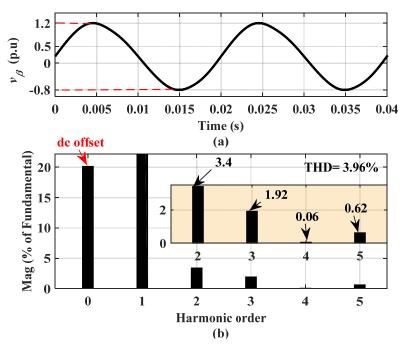

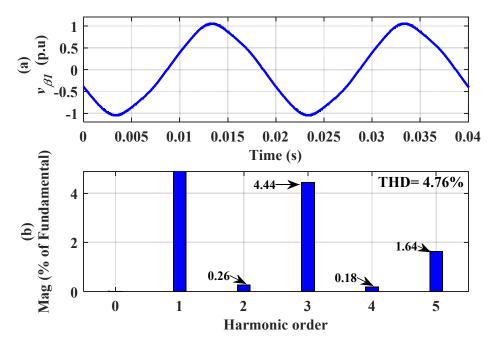

| Figure 4.23. Results obtained with the conventional SOGI (a) orthogonal signal (b) its harmonic                       |

| spectrum                                                                                                              |

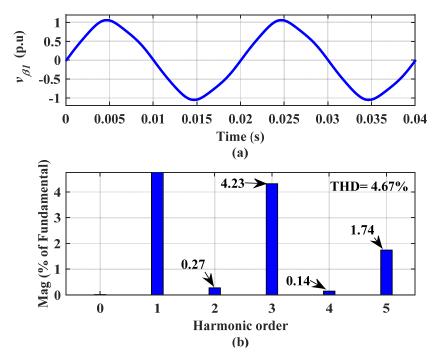

| Figure 4.24. Results obtained with Ciobotaru's method [113] (a) orthogonal signal (b) its                             |

| harmonic spectrum                                                                                                     |

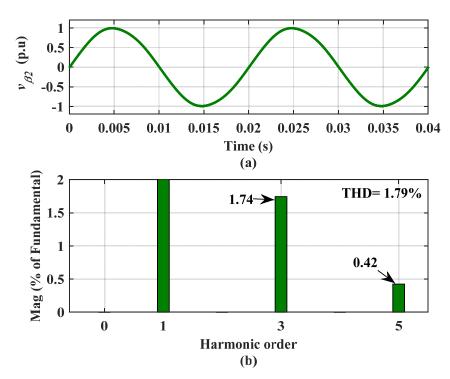

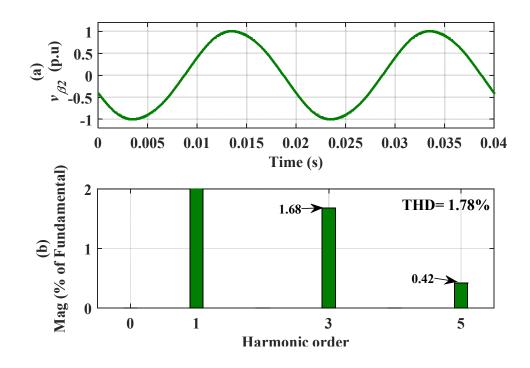

| Figure 4.25. Results obtained with Karimi's method of [114] (a) orthogonal signal (b) its                             |

| harmonic spectrum                                                                                                     |

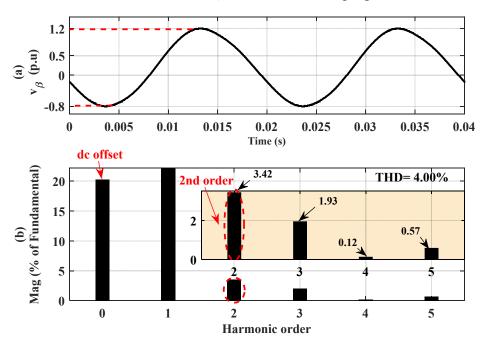

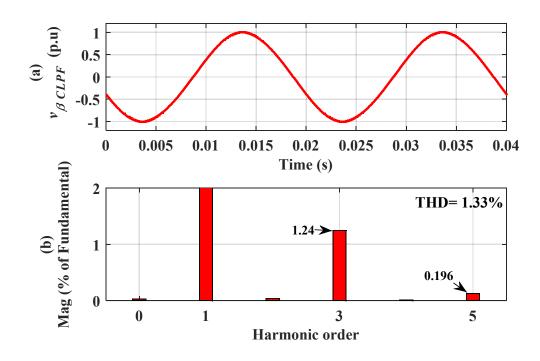

| Figure 4.26. Results obtained with the proposed CLPF-SOGI (a) orthogonal signal (b) its                               |

| harmonic spectrum                                                                                                     |

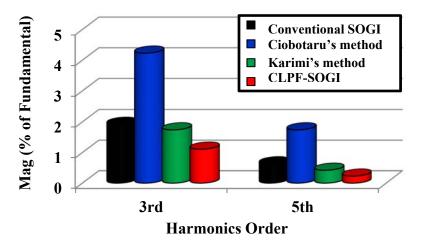

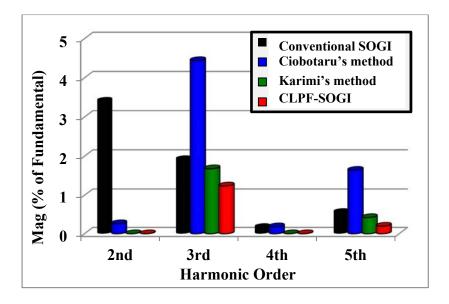

| Figure 4.27. Harmonic spectrum of the four methods 100                                                                |

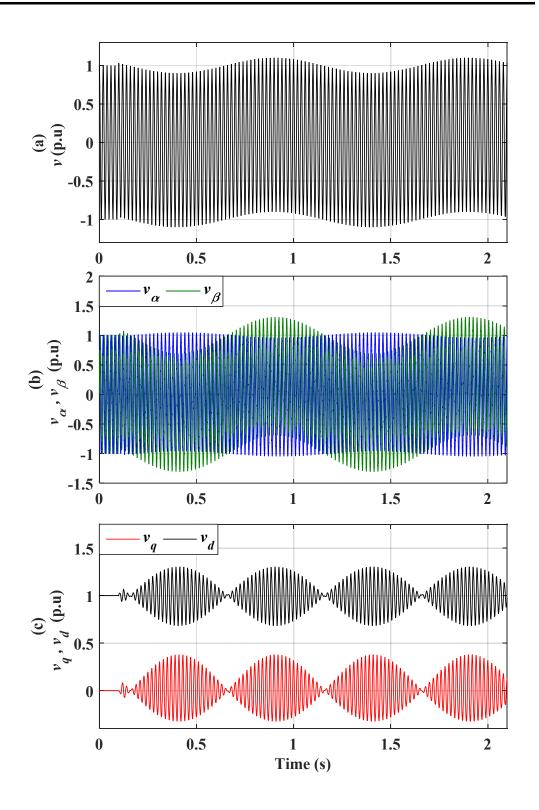

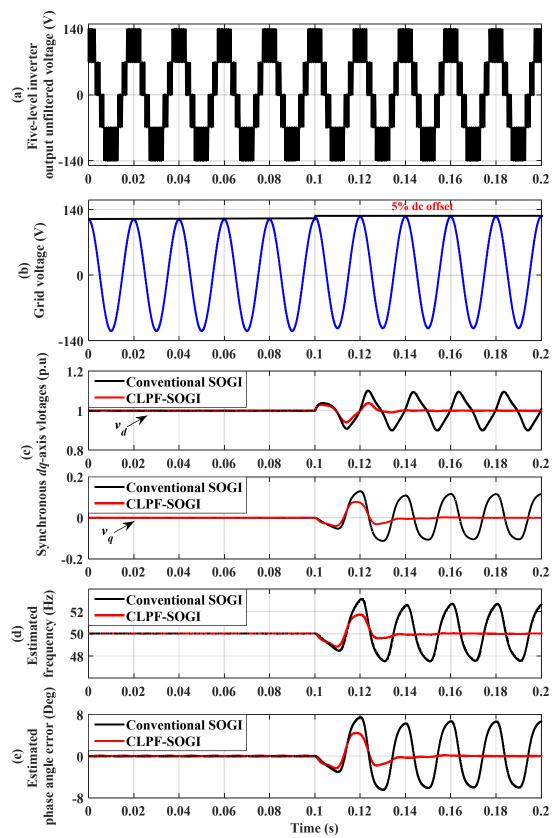

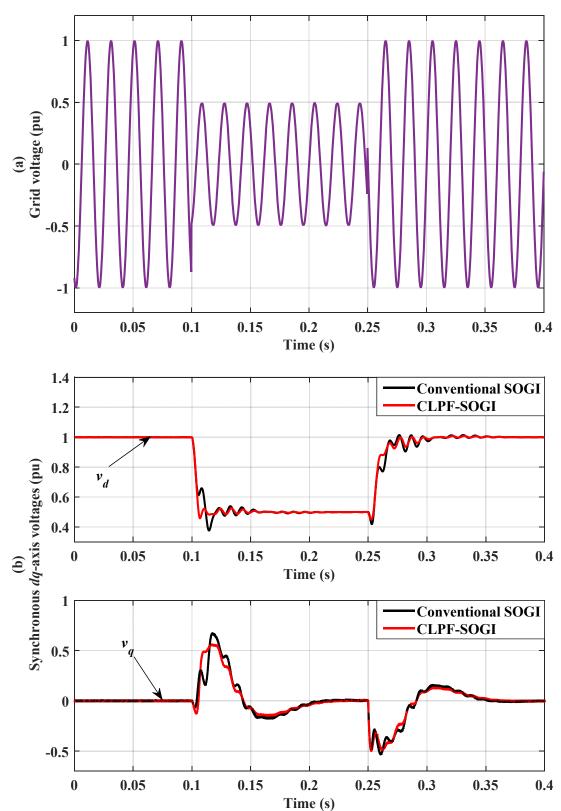

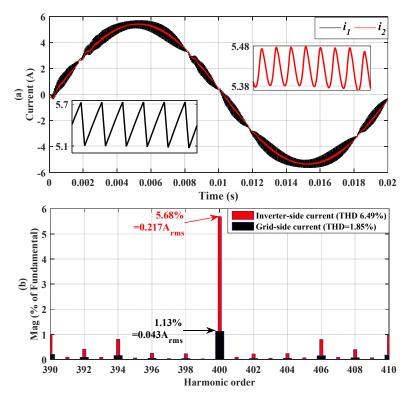

| Figure 4.28 Simulation results comparing the responses of the CLPF-SOGI and the                                       |

| conventional SOGI PLL when the input voltage undergoes a 0.05p.u dc offset: (a) the inverter                          |

| output voltage, (b) the grid voltage, (c) the synchronous dq-axis voltages, (d) the     | estimated   |

|-----------------------------------------------------------------------------------------|-------------|

| frequency, and (e) the estimated phase-angle error                                      |             |

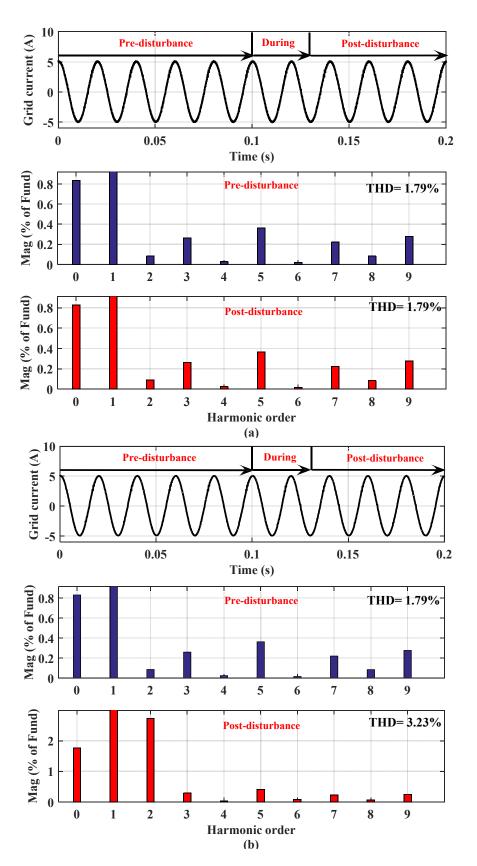

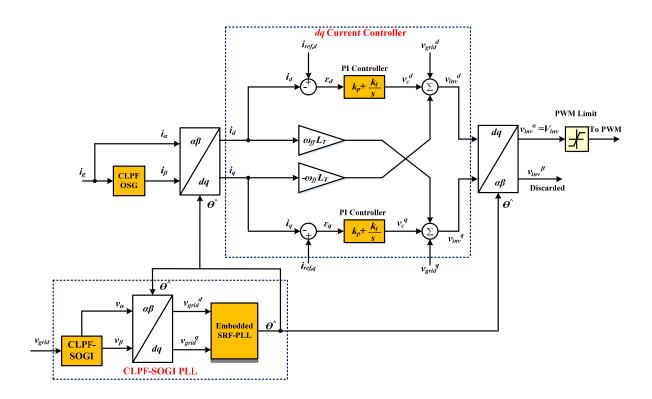

| Figure 4.29. Simulation results for the performance of the grid-connected PV system     | when the    |

| input voltage undergoes a 0.05p.u dc offset at t=0.1s, when using (a) the proposed CL   | PF-SOGI     |

| PLL, and (b) the conventional SOGI PLL.                                                 |             |

| Figure 4.30. Typical behaviour of a stationary reference frame PI controller            |             |

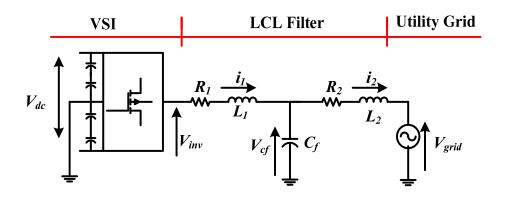

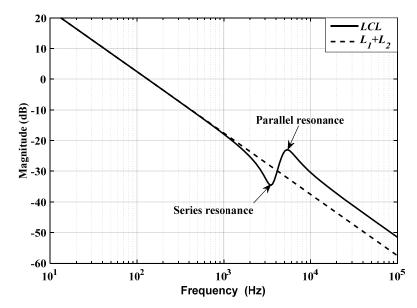

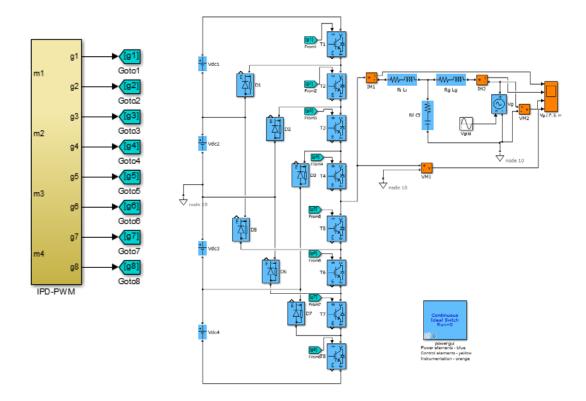

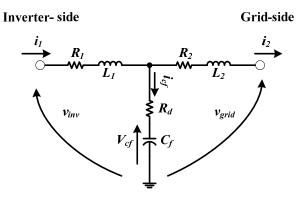

| Figure 5.1. The schematic of a single-phase five-level diode-clamped grid-connected     | d inverter  |

| test system                                                                             |             |

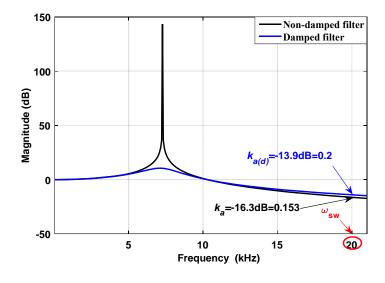

| Figure 5.2. Frequency characteristics of $(i/v)$ of the LCL filter                      | 111         |

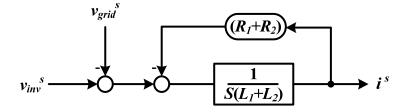

| Figure 5.3. Structural diagram of the test system in the SRF ( $\alpha\beta$ -frame)    |             |

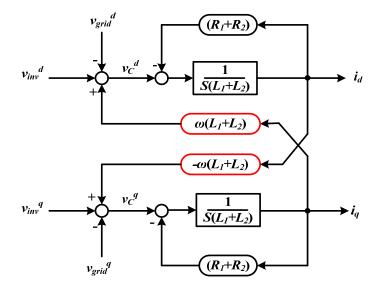

| Figure 5.4. Structural diagram of the test system in the RRF                            | 112         |

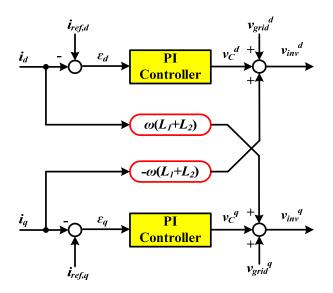

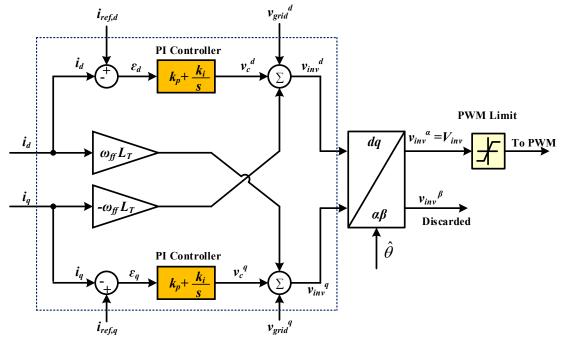

| Figure 5.5. Structural diagram of the decoupled dq current controller                   |             |

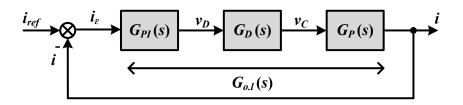

| Figure 5.6. Block diagram of current control loop                                       |             |

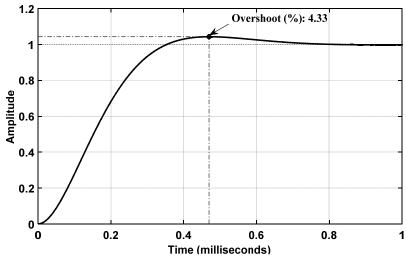

| Figure 5.7. A step response of (5.11) for $\boldsymbol{\zeta} = 0.707$                  |             |

| Figure 5.8. Structural diagram of the conventional single-phase dq controller           | 116         |

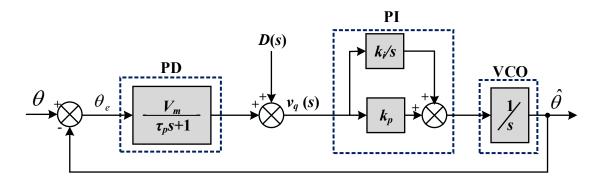

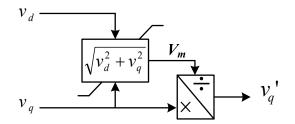

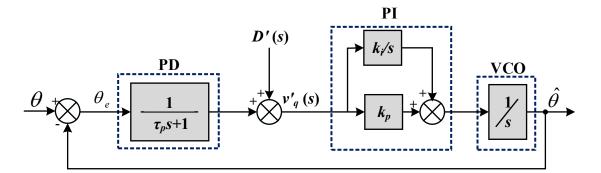

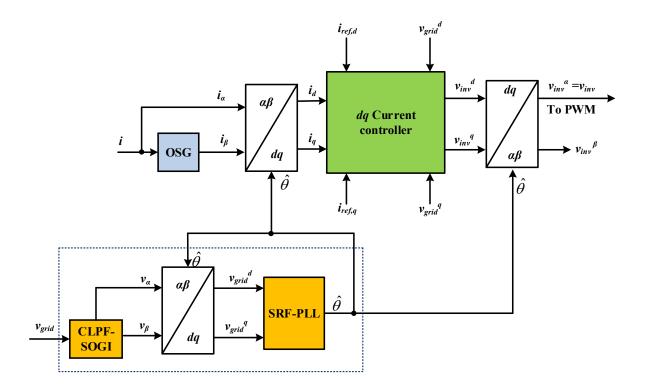

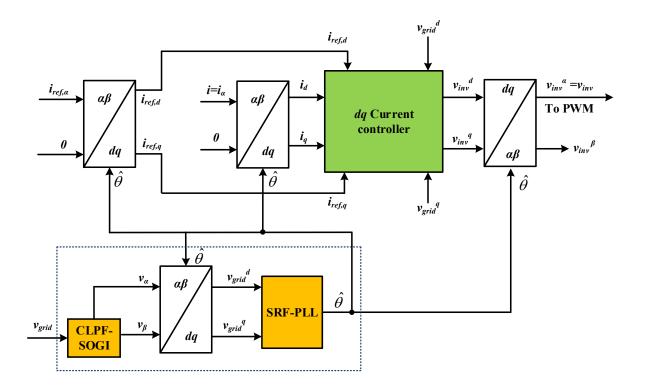

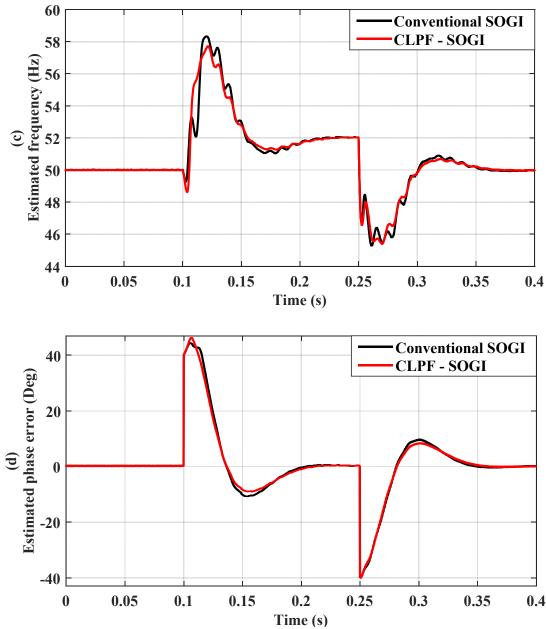

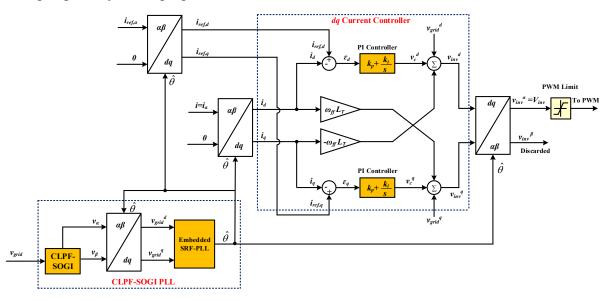

| Figure 5.9. Structural diagram of the simplified single-phase dq controller             | 118         |

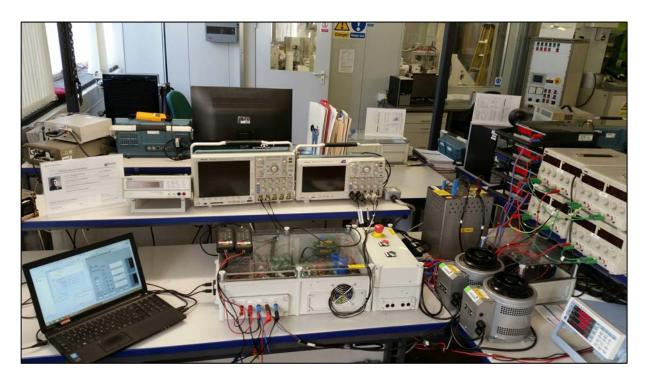

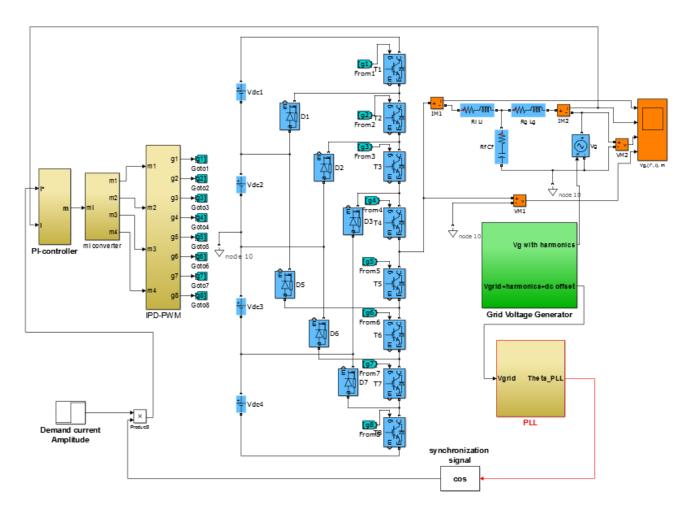

| Figure 6.1. Test rig for experimental grid-connected PV inverter system.                |             |

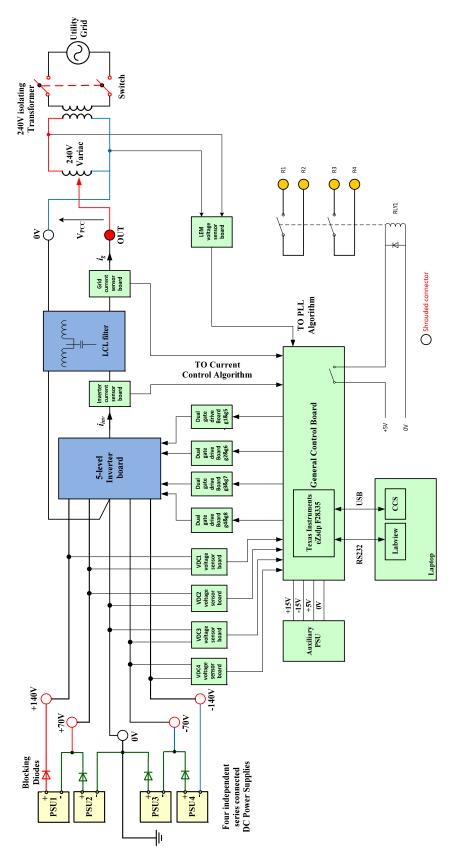

| Figure 6.2. Circuit layout of the experimental grid-connected PV inverter system        |             |

| Figure 6.3. Five-level Diode-clamped Inverter                                           |             |

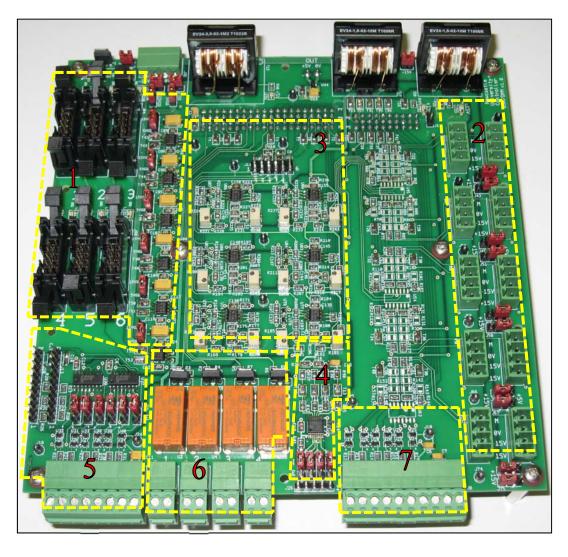

| Figure 6.4. General Purpose Power Interface Board; (1) Gate drive interface, (2         | 2) Sensor   |

| Interface, (3) Sensor out-of-range trip circuit, (4) Digital to Analogue (DAC) Conv     | verter, (5) |

| Shaft Encoder Interface, (6) Relay Circuits, and (7) General Analogue Interface         |             |

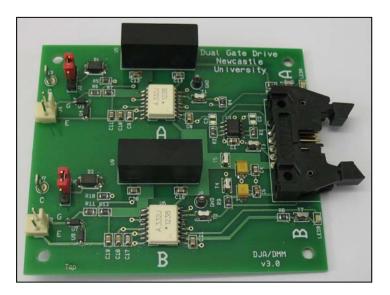

| Figure 6.5. Dual gate drive board                                                       |             |

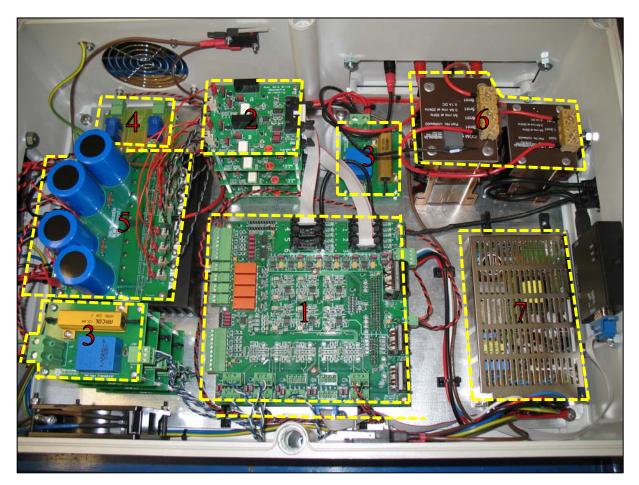

| Figure 6.6. Five-level diode-clamped inverter system including: 1) Power interface      | board. 2)   |

| Dual gate drive boards. 3) Voltage sensor boards. 4) Current sensor boards. 5) Five-lev | vel diode-  |

| clamped inverter 6) LCL filter 7) Control board PSU                                     |             |

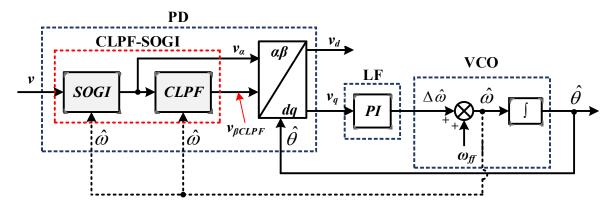

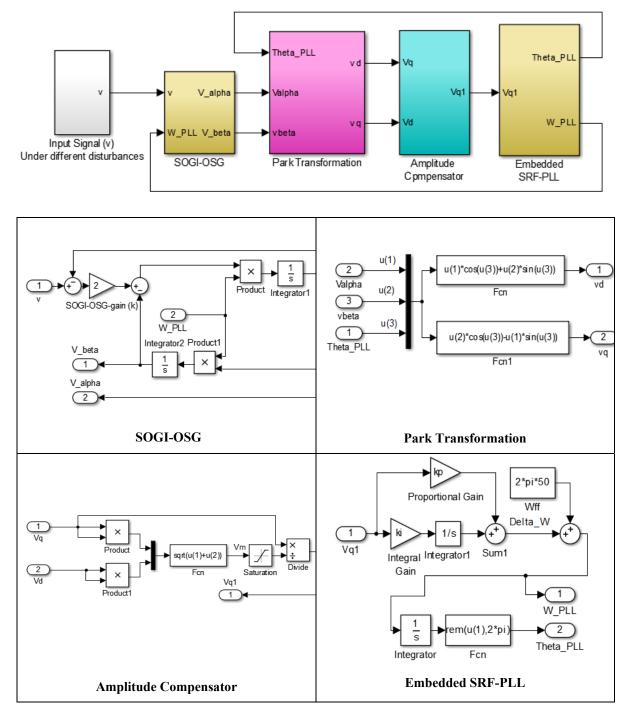

| Figure 6.7. Block diagram of the proposed CLPF-SOGI based PLL in the s domain           |             |

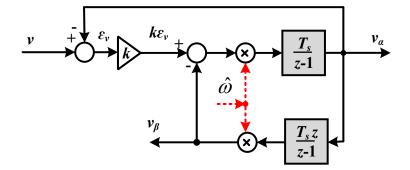

| Figure 6.8. The Euler method implementation of the SOGI-OSG                             |             |

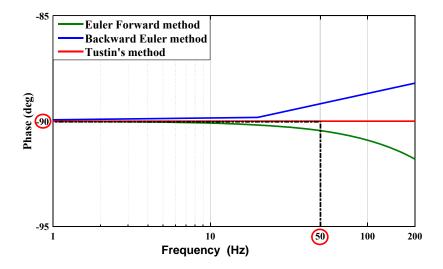

| Figure 6.9. Phase Bode-plot of a discrete-time integrator using Euler-forward, Backw    | ard-Euler   |

| and Tustin's methods when $T_s=50\mu$ s                                                 |             |

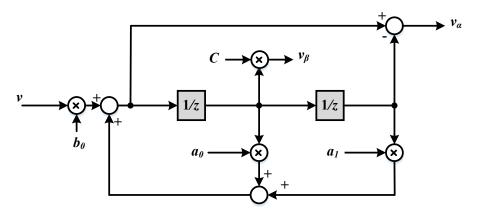

| Figure 6.10. The Tustin's method implementation of the conventional OSG-SOGI            |             |

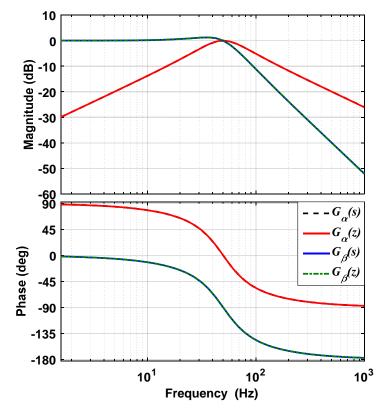

| Figure 6.11. Bod-plots of (5.4) and (5.6) along with (4.7)                              |             |

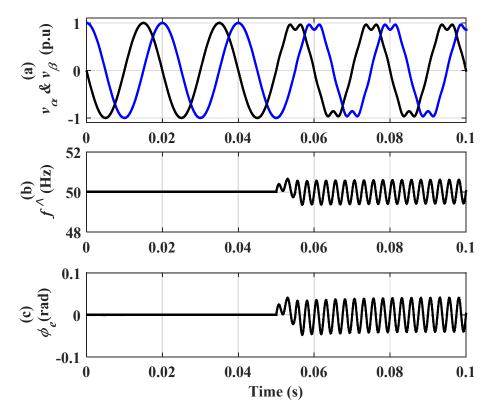

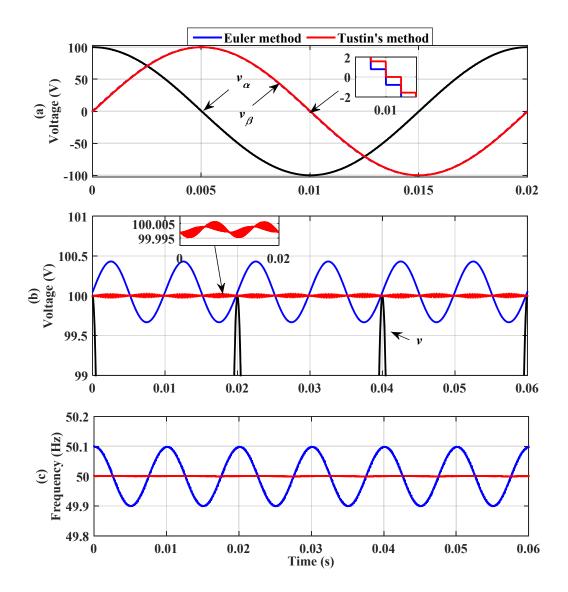

| Figure 6.12. Performance comparison when the Euler and the Tustin's methods are used (a)                        |

|-----------------------------------------------------------------------------------------------------------------|

| orthogonal signals ( $v_{\alpha}$ and $v_{\beta}$ ), (b) estimated amplitude and (c) estimated frequency of the |

| input signal v                                                                                                  |

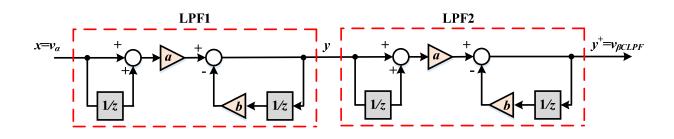

| Figure 6.13. The Tustin's method implementation of the CLPF                                                     |

| Figure 6.14. The Tustin's method implementation of the proposed CLPF-SOGI 135                                   |

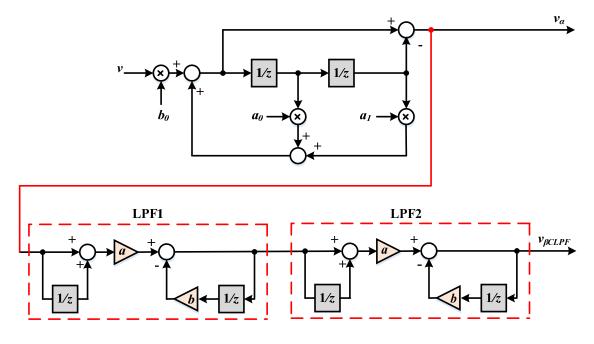

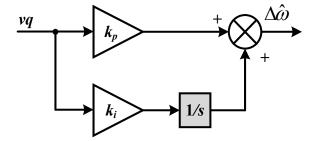

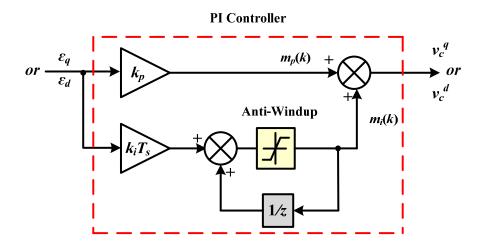

| Figure 6.15. Block diagram of a PI controller in the <i>s</i> domain                                            |

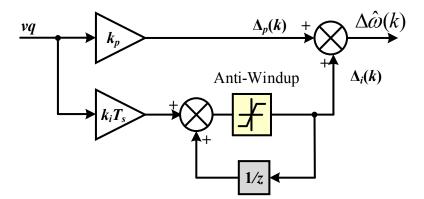

| Figure 6.16. Digital implementation of the PI controller used for the PLL                                       |

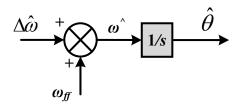

| Figure 6.17. Block diagram of the VCO in the s domain                                                           |

| Figure 6.18. Digital implementation of the VCO                                                                  |

| Figure 6.19. Block diagram of <i>dq</i> current controller in the <i>s</i> domain                               |

| Figure 6.20. Digital implementation of the PI controller used for the $dq$ current control                      |

| algorithm                                                                                                       |

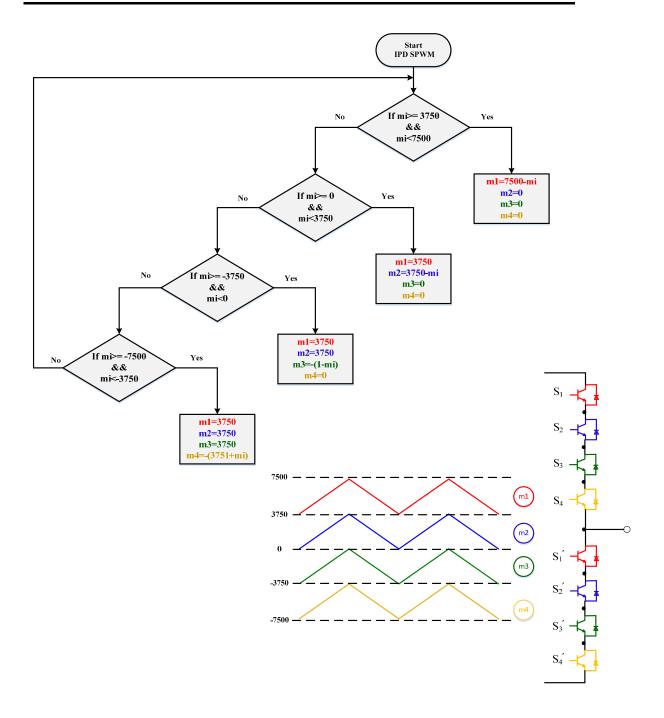

| Figure 6.21. The switching logic for the five-level inverter                                                    |

| Figure 7.1. Experimental results of; (a) distorted input voltage waveform $v$ and (b) its harmonic              |

| spectrum                                                                                                        |

| Figure 7.2. Results obtained with the conventional SOGI (a) orthogonal signal (b) its harmonic                  |

| spectrum                                                                                                        |

| Figure 7.3. Results obtained with the first method of [113] (a) orthogonal signal (b) its harmonic              |

| spectrum                                                                                                        |

| Figure 7.4. Results obtained with the second method of [114] (a) orthogonal signal (b) its                      |

| harmonic spectrum                                                                                               |

| Figure 7.5. Results obtained with the proposed CLPF-SOGI (a) orthogonal signal (b) its                          |

| harmonic spectrum                                                                                               |

| Figure 7.6. Experimental harmonic spectrum of the orthogonal signal generated using four                        |

| different methods 146                                                                                           |

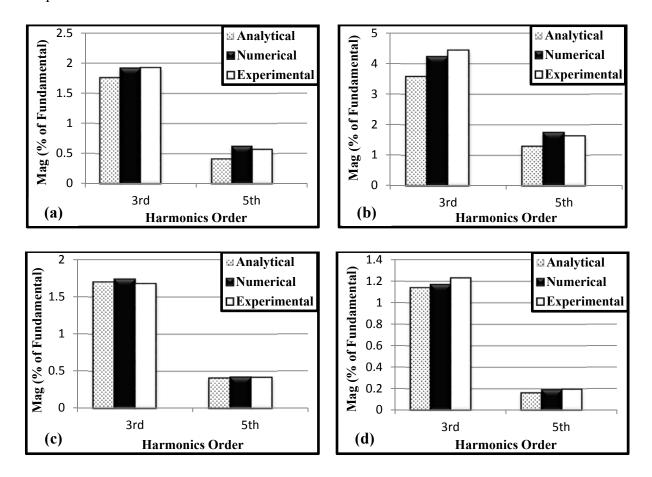

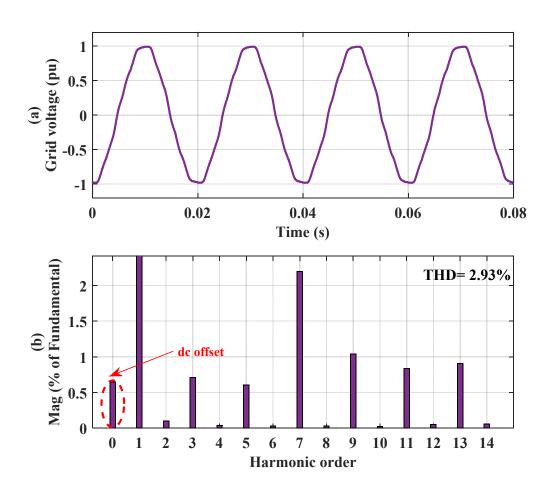

| Figure 7.7. Analytical, numerical and experimental harmonics of (a) the conventional SOGI,                      |

| (b) the first method, (c) the second method, and (d) the proposed CLPF-SOGI 147                                 |

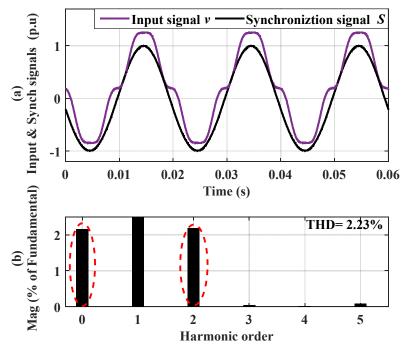

| Figure 7.8. Performance of the conventional SOGI in estimating the synchronisation signal: (a)                  |

| input signal and estimated signal, (b) harmonic content of the estimated synchronization signal                 |

|                                                                                                                 |

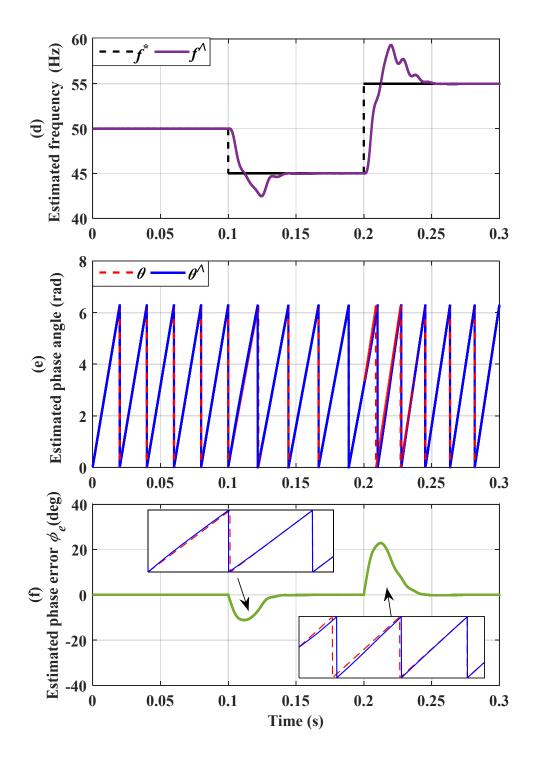

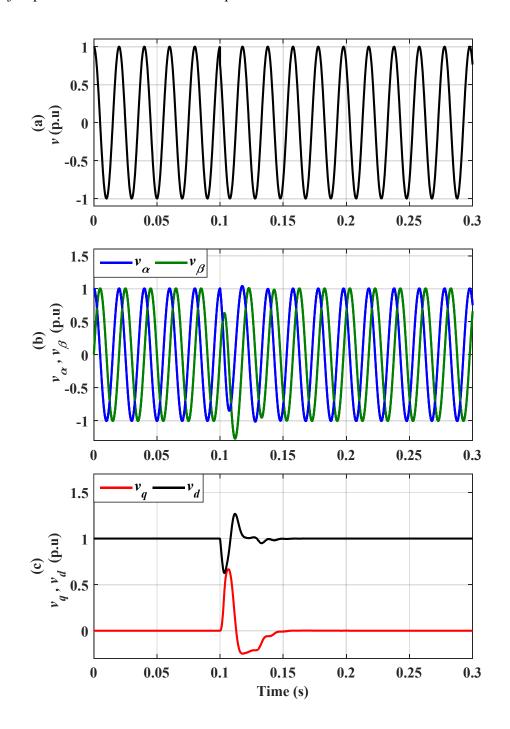

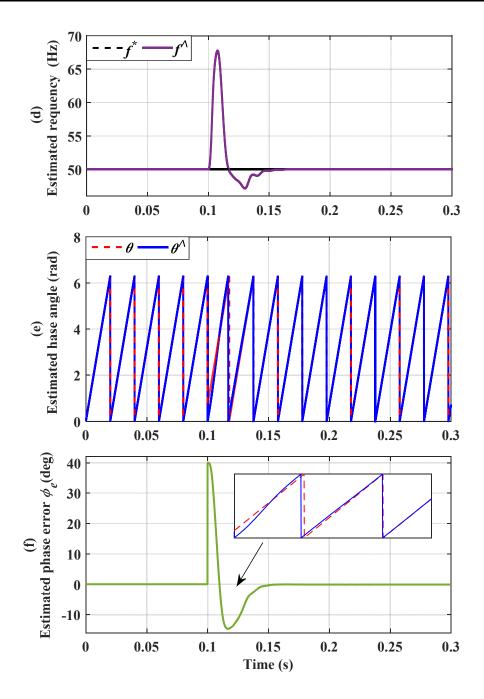

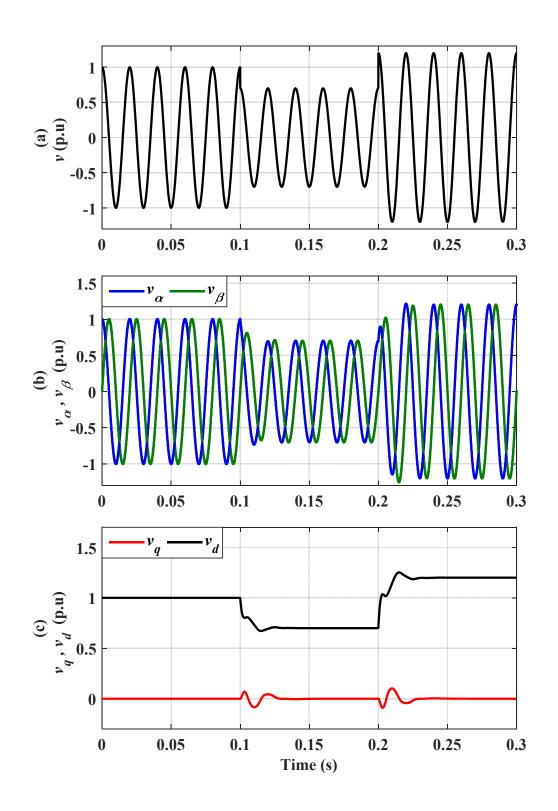

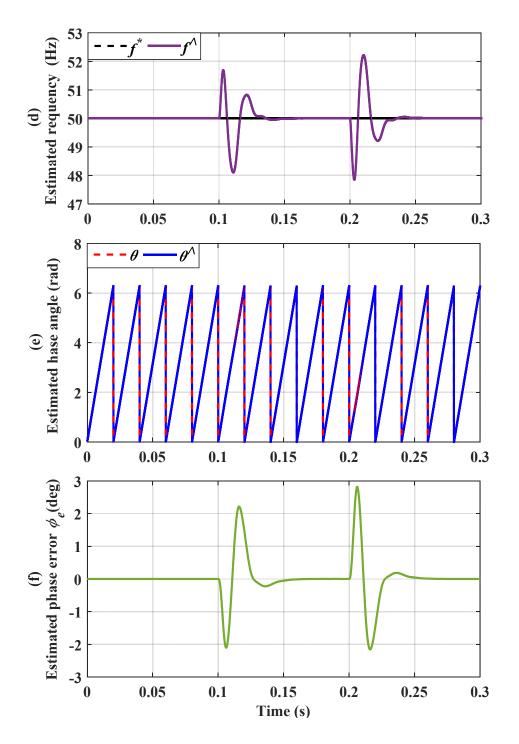

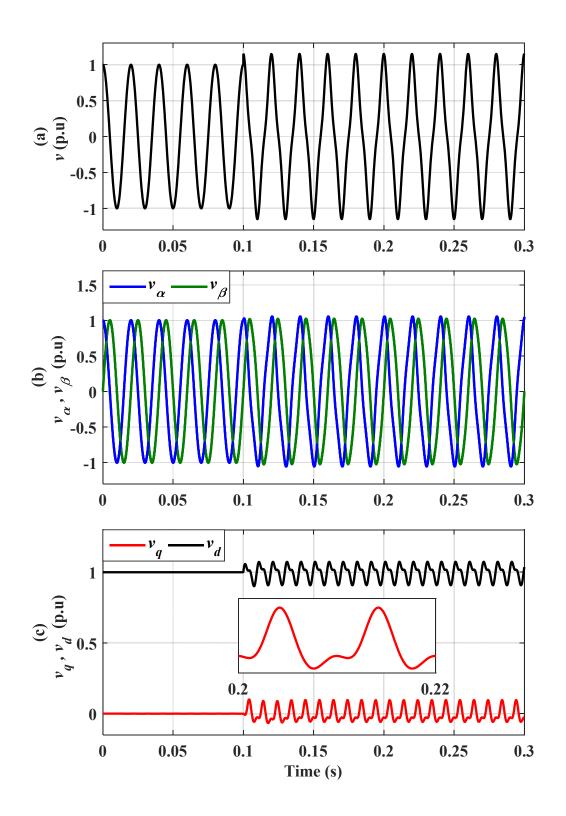

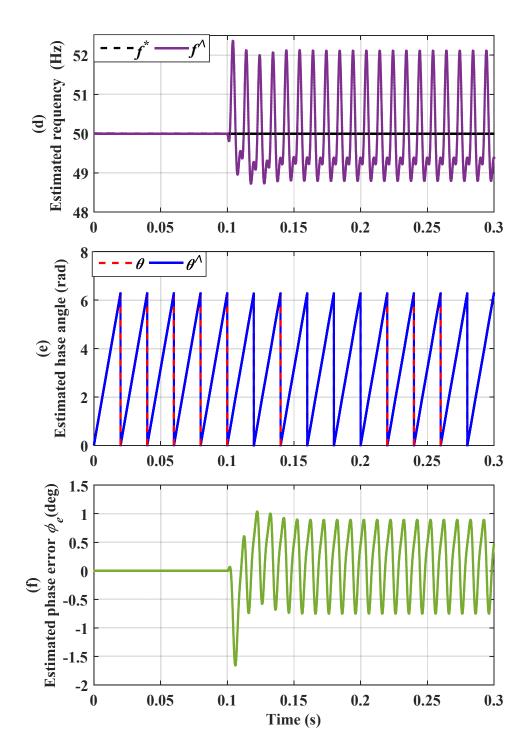

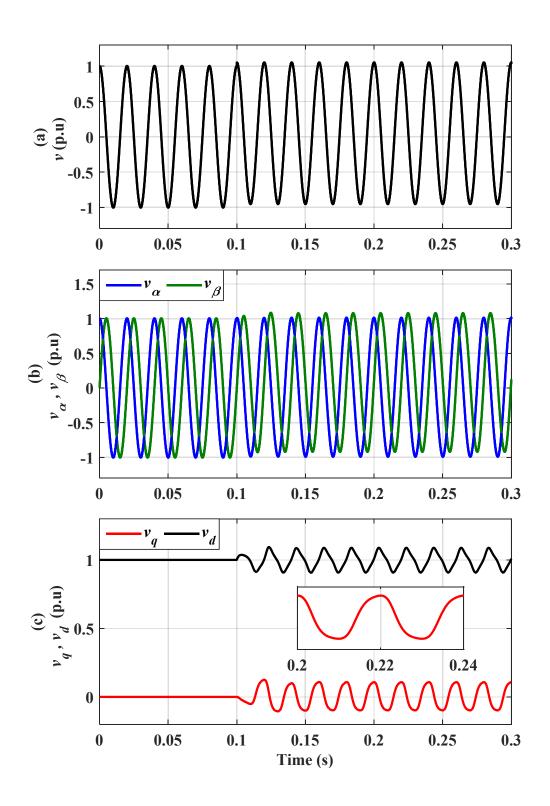

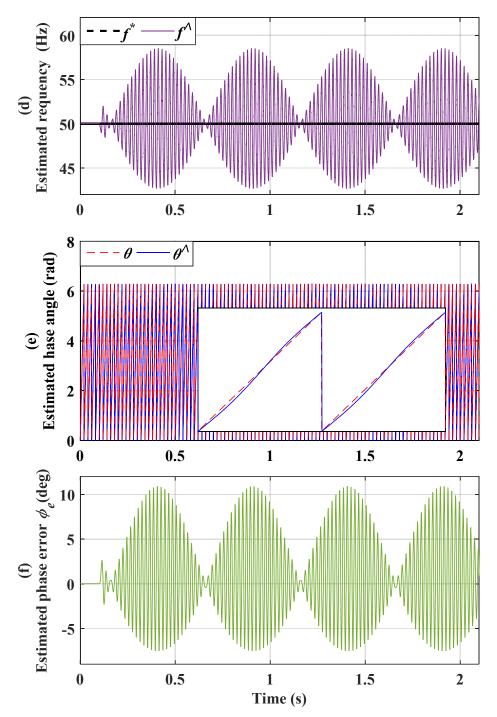

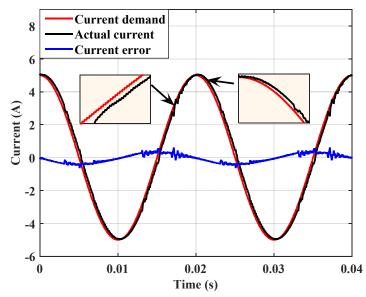

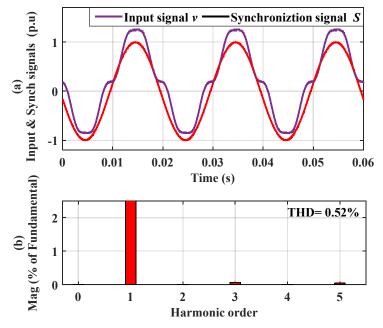

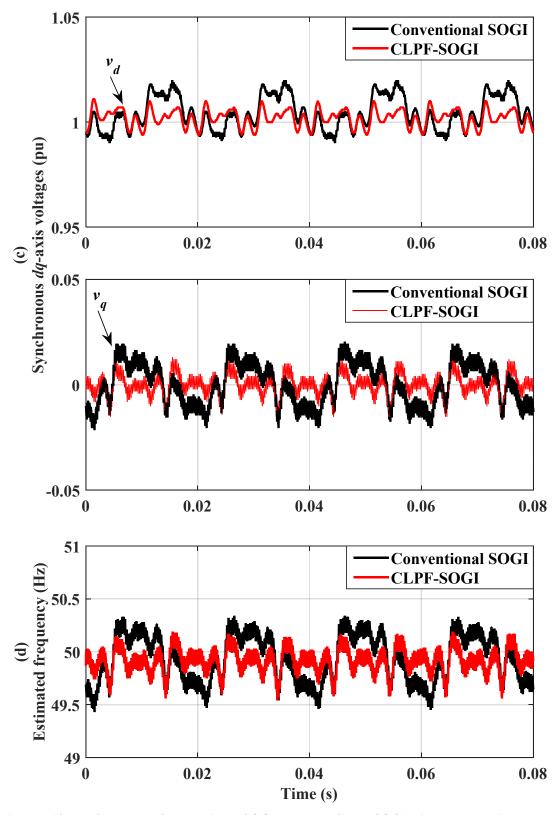

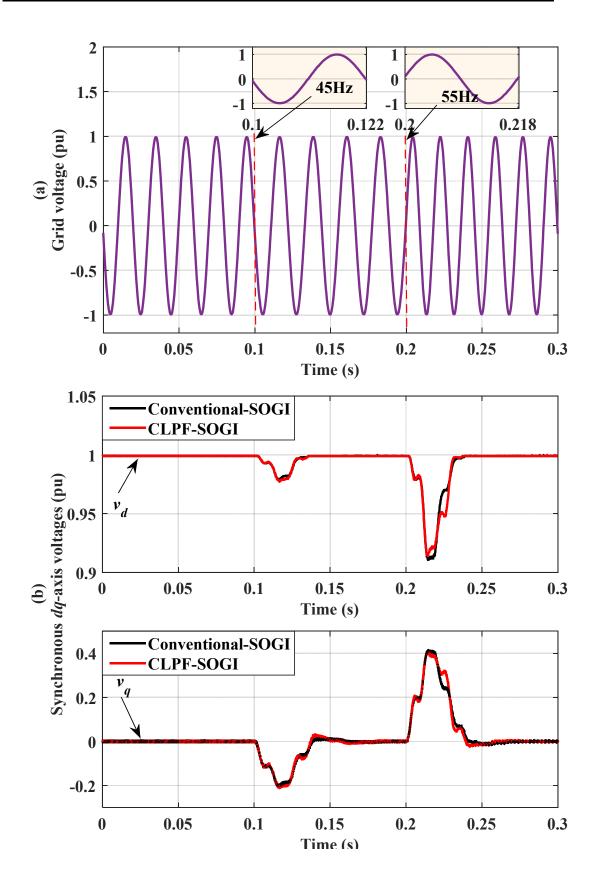

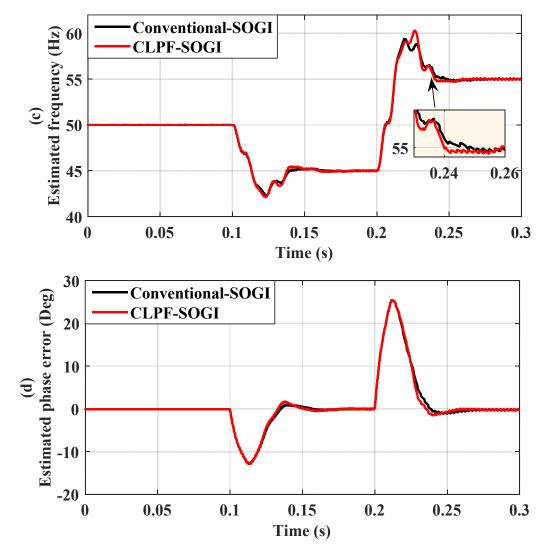

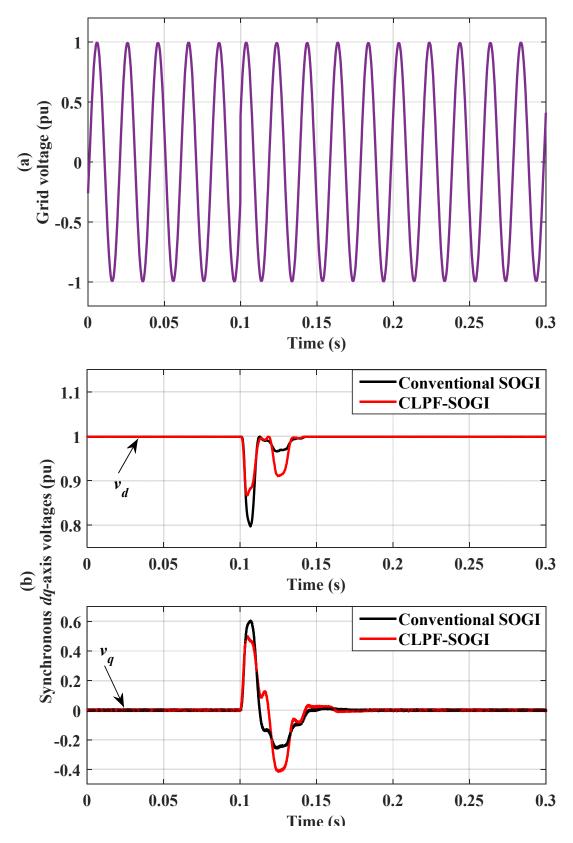

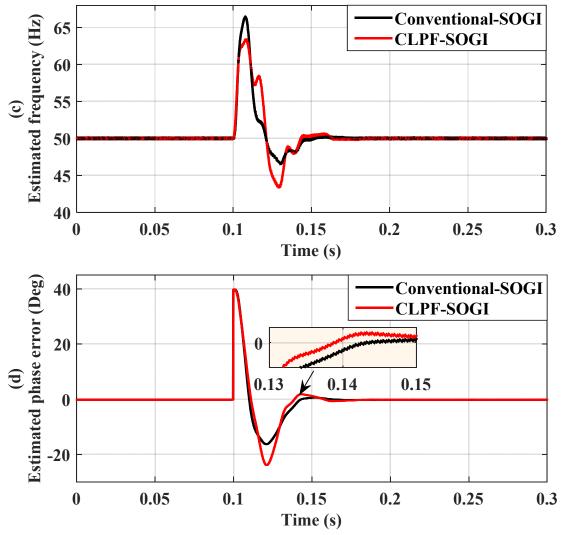

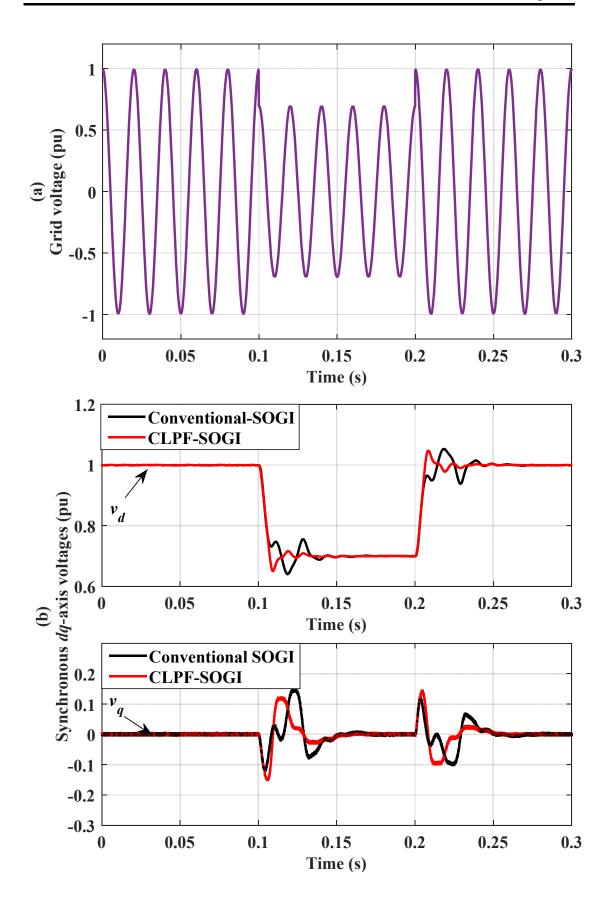

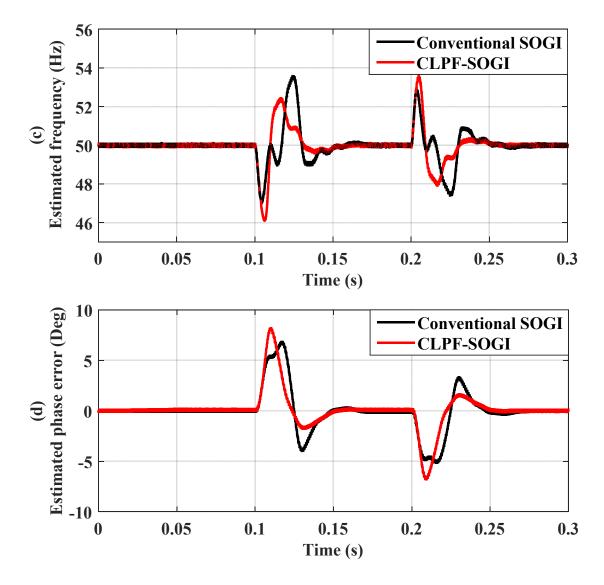

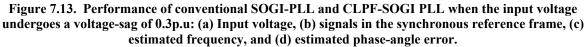

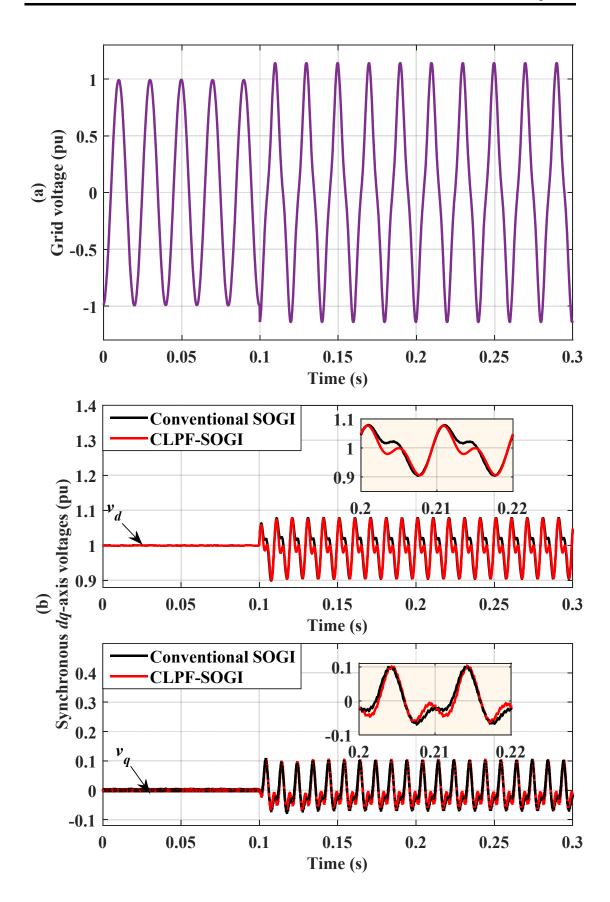

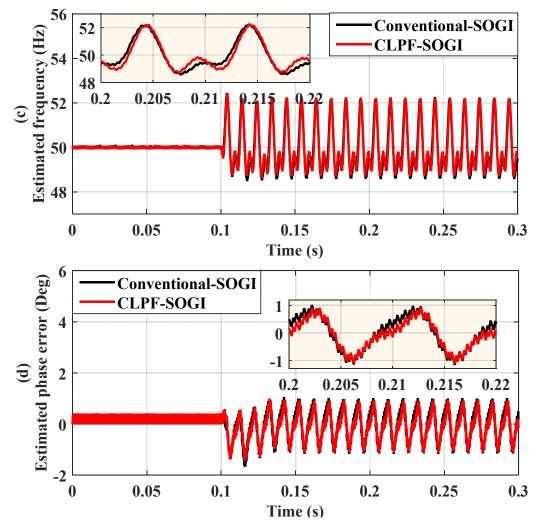

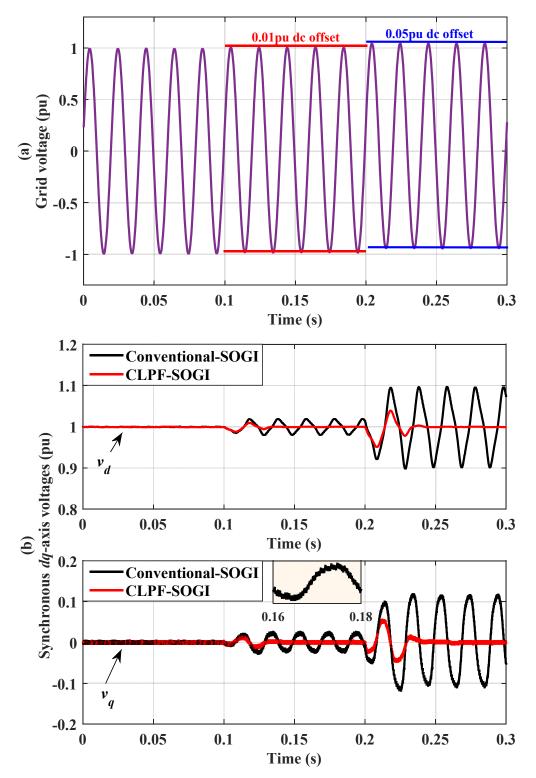

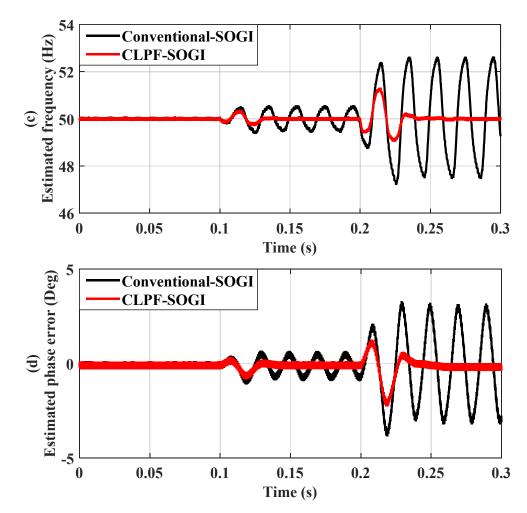

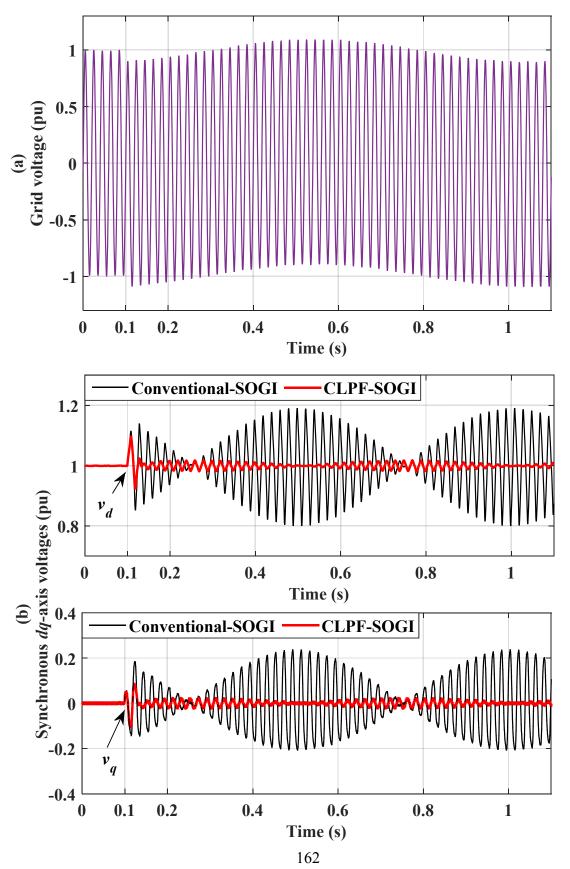

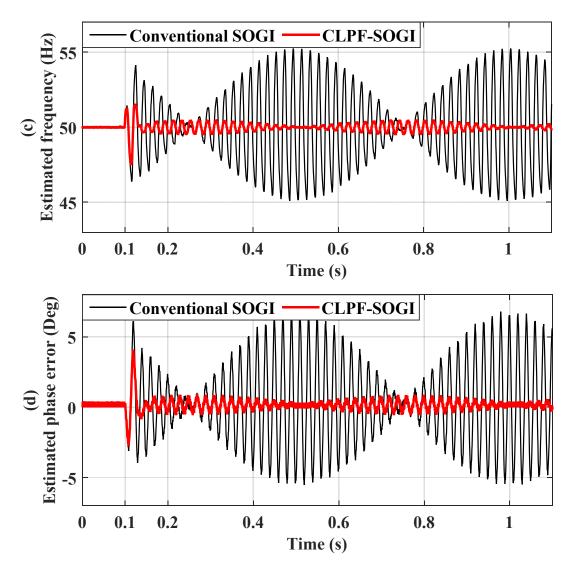

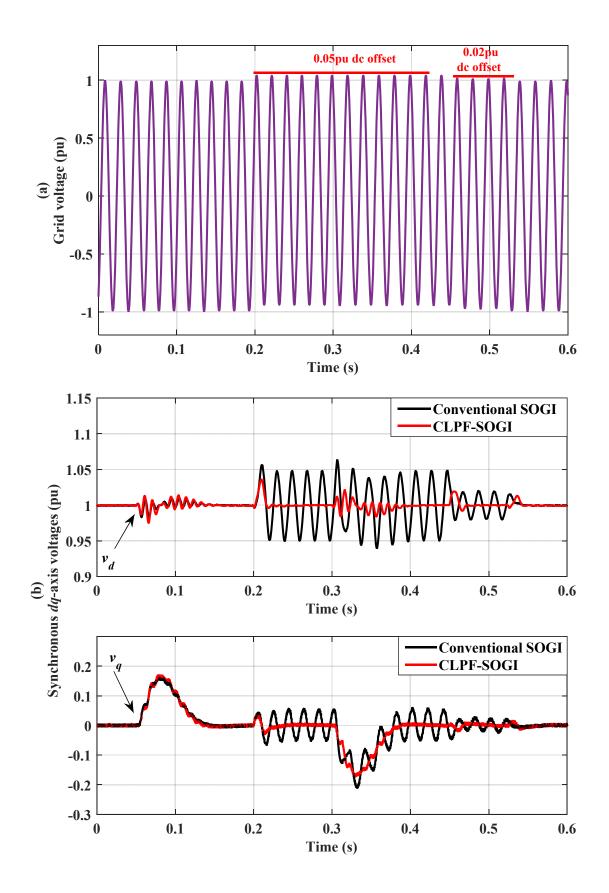

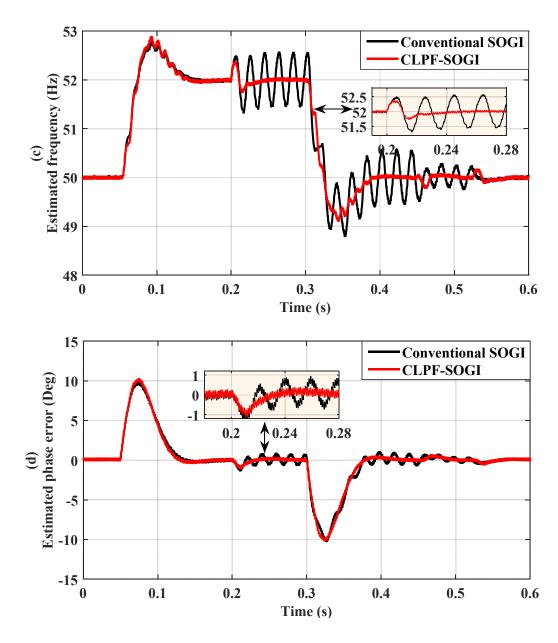

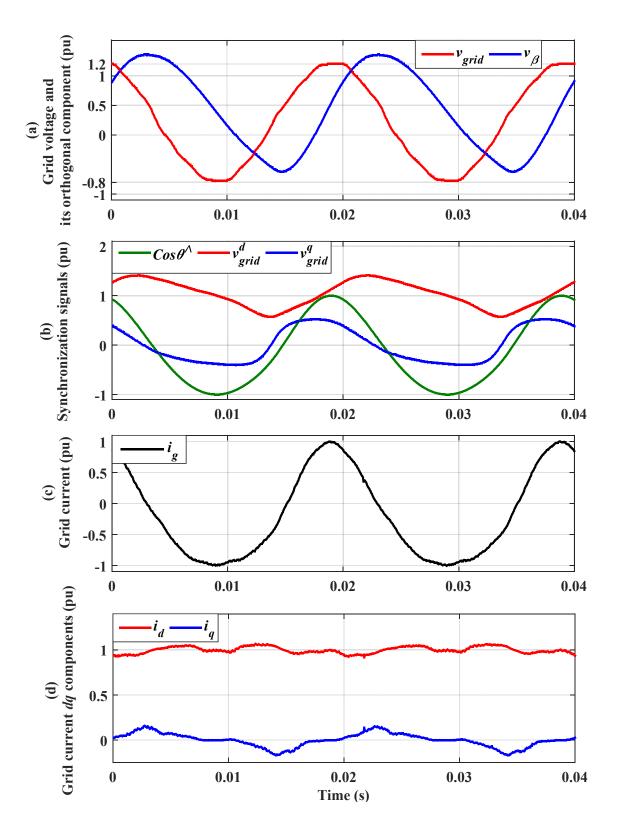

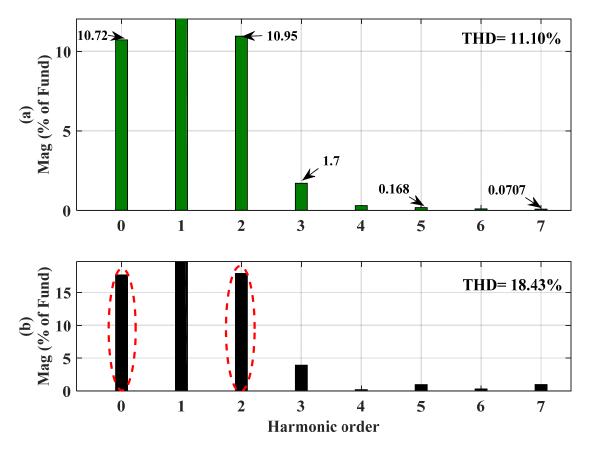

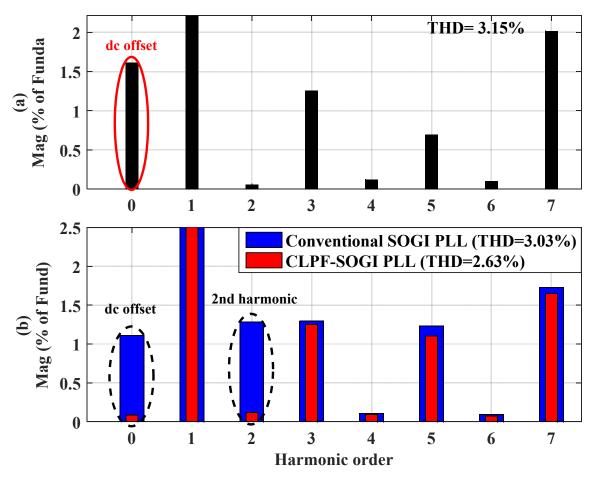

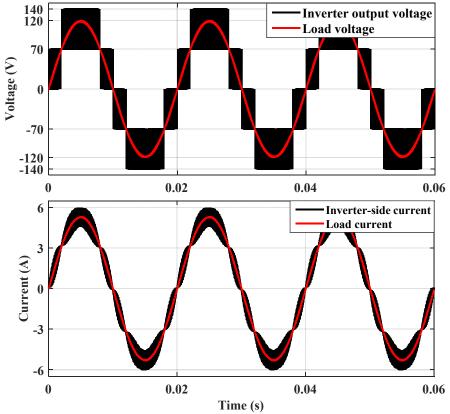

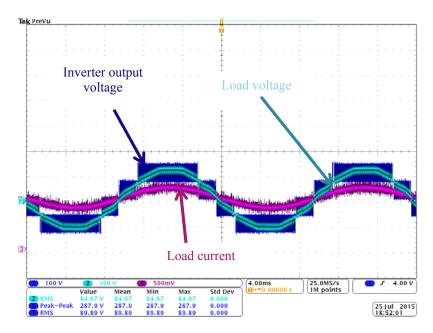

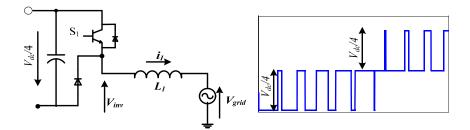

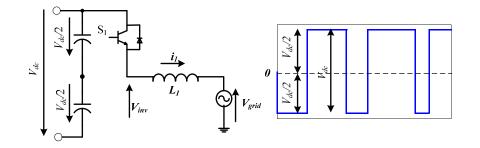

Figure 7.9. Performance of the proposed CLPF-SOGI in estimating the synchronisation signal: (a) input signal and estimated signal, (b) harmonic content of the estimated synchronization Figure 7.10. Performance of conventional SOGI-PLL and CLPF-SOGI with the real grid voltage signal: (a) Input grid voltage, (b) harmonic spectrum of the grid voltage, (c) signals in Figure 7.11. Performance of conventional SOGI-PLL and CLPF-SOGI PLL when the input voltage undergoes frequency step changes: (a) Input voltage, (b) signals in the synchronous Figure 7.12. Performance of conventional SOGI-PLL and CLPF-SOGI PLL when the input voltage undergoes a phase jump of 40°: (a) Input voltage, (b) signals in the synchronous Figure 7.13. Performance of conventional SOGI-PLL and CLPF-SOGI PLL when the input voltage undergoes a voltage-sag of 0.3p.u: (a) Input voltage, (b) signals in the synchronous Figure 7.14. Performance of conventional SOGI-PLL and CLPF-SOGI PLL when the input voltage undergoes a voltage-sag of 0.3p.u: (a) Input voltage, (b) signals in the synchronous Figure 7.15. Performance of conventional SOGI-PLL and CLPF-SOGI PLL when the input voltage undergoes a 0.01 and 0.05 dc offset: (a) Input voltage, (b) signals in the synchronous reference frame, (c) estimated frequency, and (d) estimated phase-angle error......161 Figure 7.16. Performance of conventional SOGI PLL and CLPF-SOGI PLL when the input voltage undergoes a 10% of 1Hz subharmonic: (a) Input voltage, (b) signals in the synchronous reference frame, (c) estimated frequency, and (d) estimated phase-angle error......163 Figure 7.17. Performance of conventional SOGI PLL and CLPF-SOGI PLL under frequency variations with dc offset: (a) Input voltage, (b) signals in the synchronous reference frame, (c) Figure 7.18. Performance of conventional SOGI PLL and CLPF-SOGI PLL under voltage sag with phase jump and frequency variations: (a) Input voltage, (b) signals in the synchronous

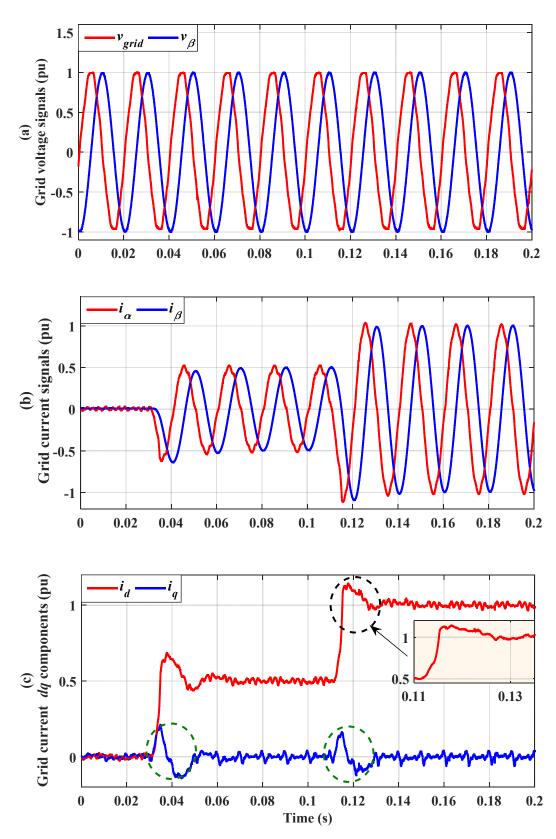

| Figure 8.2 Experimental results of the transient response of the conventional delay-based             |

|-------------------------------------------------------------------------------------------------------|

| controller during step changes in <i>d</i> -axis: (a) The grid voltage and its associated orthogonal  |

| component. (b) The grid current and its emulated orthogonal component. (c) The d-q-axes               |

| corresponding to the grid current and its emulated orthogonal component                               |

| Figure 8.3. Structure of the simplified single-phase current-regulation scheme                        |

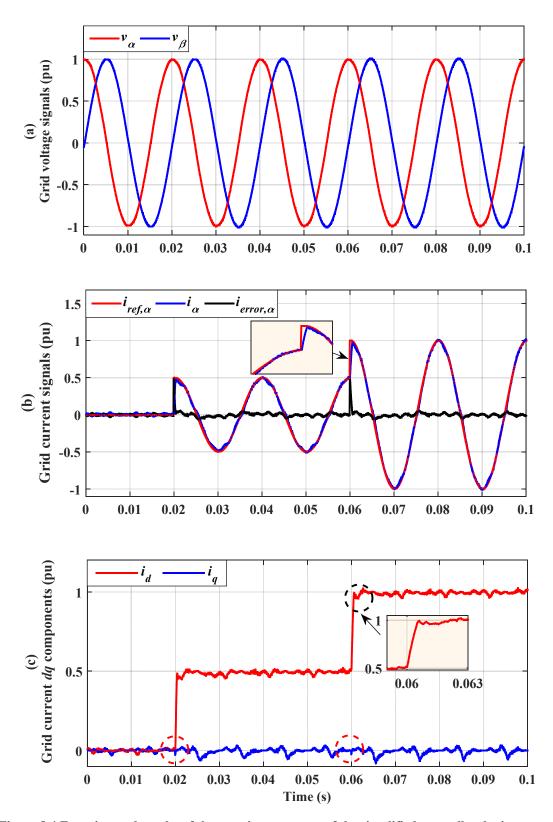

| Figure 8.4 Experimental results of the transient response of the simplified controller during step    |

| changes in <i>d</i> -axis: (a) The grid voltage orthogonal signals. (b) The reference and actual grid |

| currents with their associated tracking error. (c) The d- and q-axes corresponding to the grid        |

| current                                                                                               |

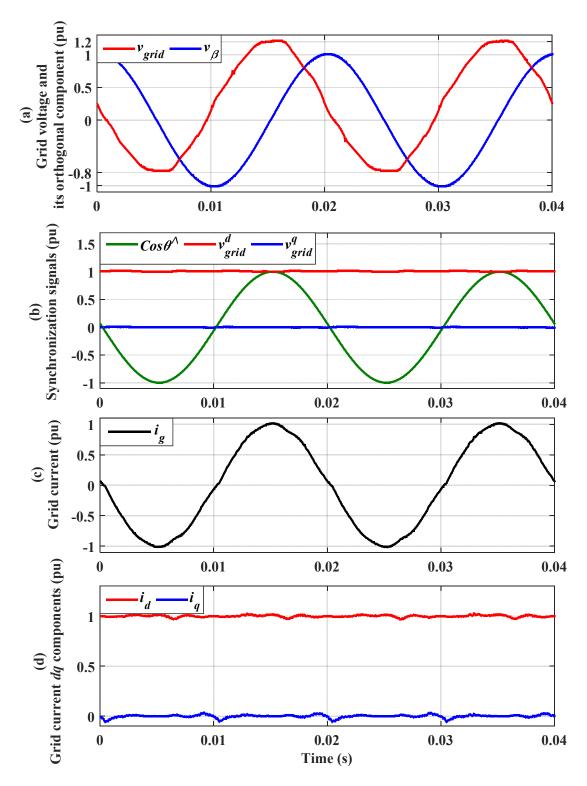

| Figure 8.5. Steady-state performance of the grid-connected PV system when the proposed                |

| CLPF-SOGI PLL is used with a large dc component of 0.2p.u in the measured grid voltage: (a)           |

| The grid voltage and its associated orthogonal component. (b) The synchronization signals             |

| associated with the CLPF-SOGI PLL. (c) The grid current. (d) The d- and q-axes corresponding          |

| to the grid current                                                                                   |

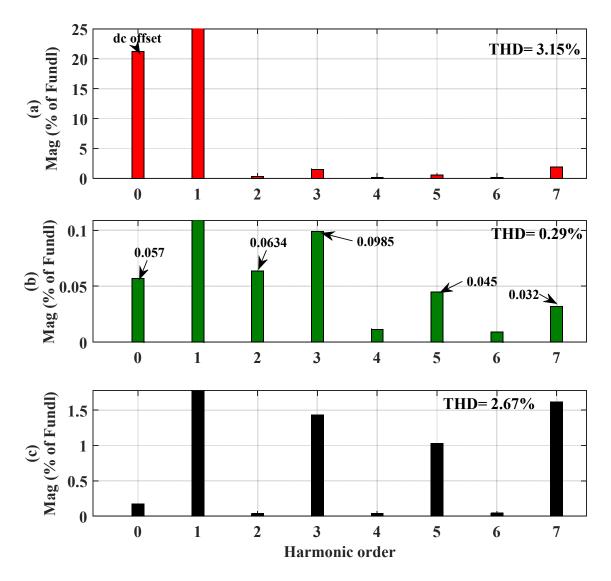

| Figure 8.6. Harmonic content of: (a) The utility grid, (b) The reference current. (c) The grid        |

| current, under the presence of large dc component in the grid voltage signal and when the             |

| proposed CLPF-SOGI PLL is used for synchronization                                                    |

| Figure 8.7. Steady-state performance of the grid-connected PV system when the conventional            |

| SOGI PLL is used with a large dc component of 0.2p.u in the measured grid voltage: (a) The            |

| grid voltage and its associated orthogonal component. (b) The synchronization signals                 |

| associated with the conventional SOGI PLL. (c) The grid current. (d) The d- and q-axes                |

| corresponding to the grid current                                                                     |

| Figure 8.8. Harmonic content of: (a) The reference current. (b) The grid current, under the           |

| presence of large dc component in the grid voltage signal and when the conventional SOGI              |

| PLL is used for synchronization                                                                       |

| Figure 8.9. Harmonic content of: (a) The actual grid voltage with no added dc offset. (b) The         |

| grid current when both conventional SOGI PLL and CLPF-SOGI PLL schemes are used for                   |

| synchronization                                                                                       |

## Tables

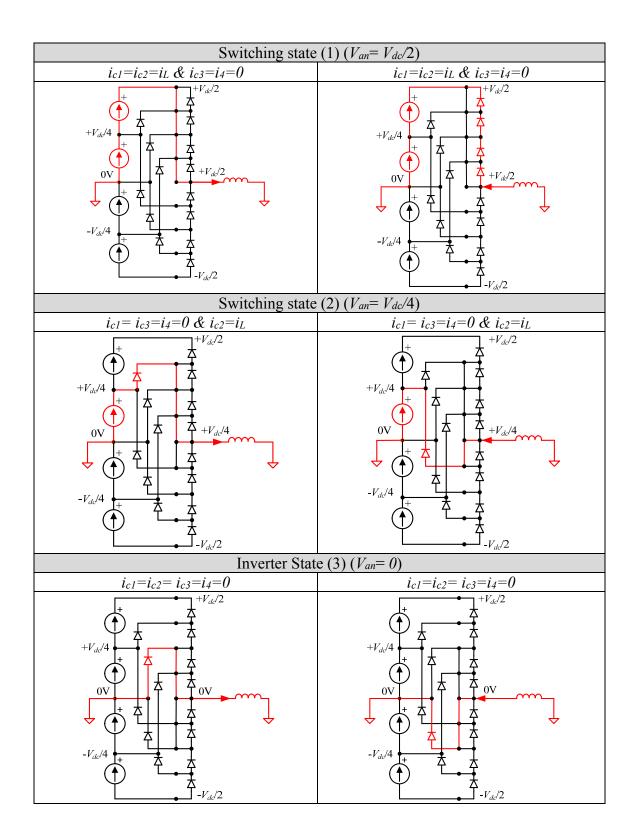

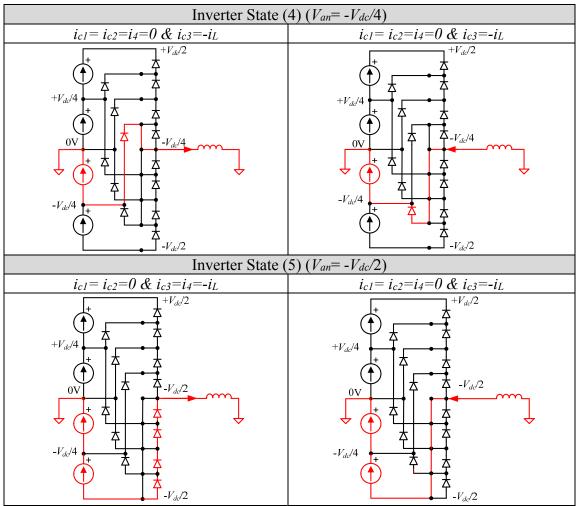

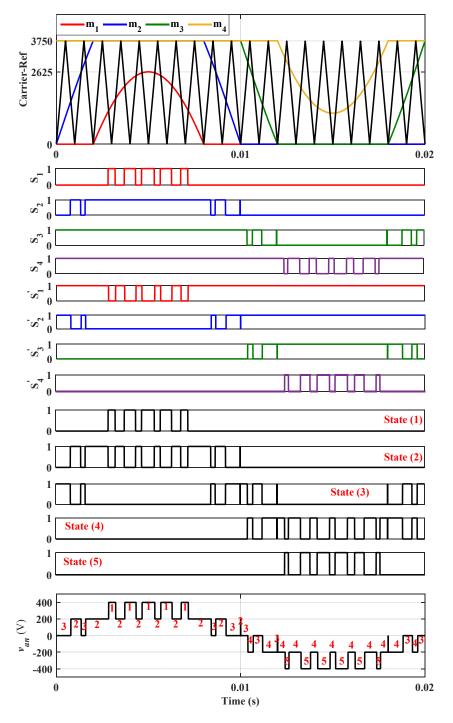

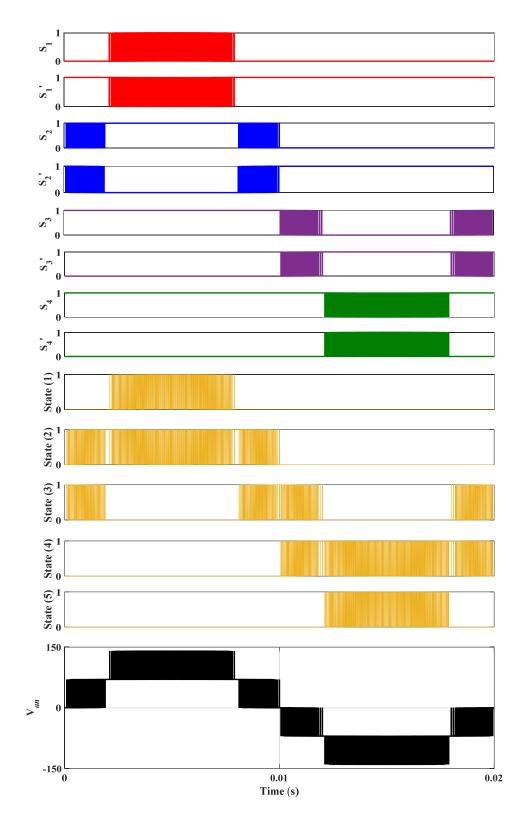

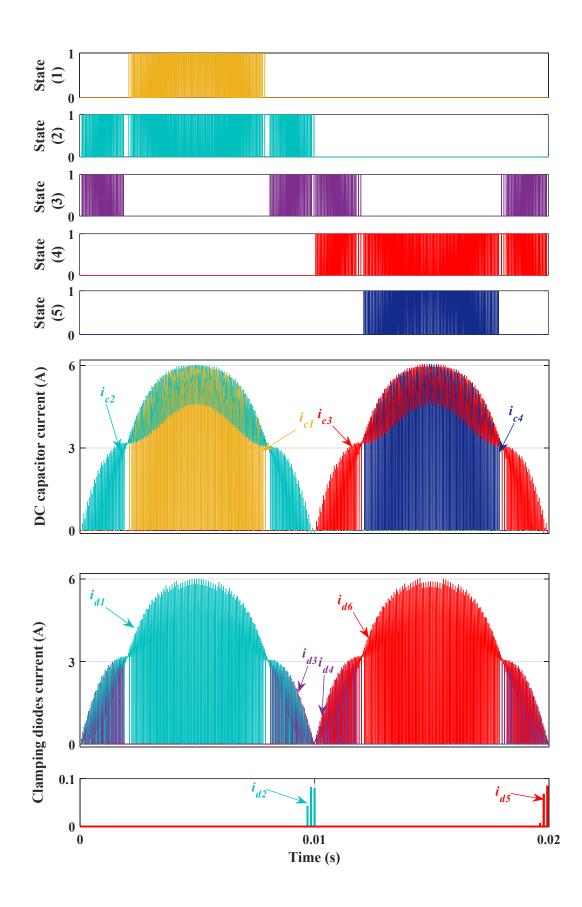

| Table 1-1 Switching state and magnitude of output voltage of a five-level d      | liode-clamped |

|----------------------------------------------------------------------------------|---------------|

| inverter                                                                         | 7             |

| Table 1-2: Disconnection time for voltage variations                             | 11            |

| Table 1-3: Disconnection time for frequency variations                           | 12            |

| Table 1-4: Conditions for reconnection after trip                                | 12            |

| Table 1-5: DC current injection limitation                                       | 13            |

| Table 1-6: Maximum current harmonics                                             | 14            |

| Table 3-1 SOGI-PLL parameters                                                    | 57            |

| Table 4-1 Parameters of different SOGI-OSG techniques                            | 92            |

| Table 4-2 Attenuation (dB) at different harmonics orders using different SOGI te | chniques 96   |

| Table 4-3 PLL parameters                                                         | 97            |

| Table 6-1: LCL filter parameters                                                 | 127           |

| Table 7-1 SOGI-PLL and CLPF-SOGI PLL parameters                                  | 151           |

| Table 7-2 SOGI-PLL and CLPF-SOGI PLL parameters                                  | 164           |

## Symbols

| Symbol | Definition                                  |

|--------|---------------------------------------------|

| AC     | Alternating Current                         |

| A/D    | Analogue to Digital Conversion              |

| ADC    | Analogue to Digital Converter               |

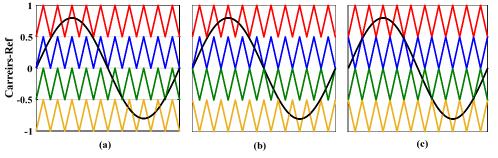

| APOD   | Alternative Phase Opposition Disposition    |

| AI     | Anti-islanding                              |

| BPF    | Band-pass Filter                            |

| СНВ    | Cascaded H-Bridge                           |

| CLPF   | Cascaded Low-pass Filter                    |

| CLTF   | Closed-loop Transfer Function               |

| DPGSs  | Distributed Power Generation Systems        |

| DQ     | Direct-quadrature                           |

| DFAC   | Double-frequency and Amplitude Compensation |

| DC     | Direct Current                              |

| DSP    | Digital Signal Processor                    |

| DAC    | Digital to Analogue Converter               |

| EMC    | Electromagnetic Compatibility               |

| EMI    | Electromagnetic Interface                   |

| FC     | Flying Capacitor                            |

| GUI    | Graphical User Interface                    |

| IPD    | In-phase Disposition                        |

| LPF    | Low-pass Filter                             |

| LS-PWM | Multi-carrier Level-shifted PWM             |

| LF     | Loop Filter                                 |

| MPPT   | Maximum Power Point Tracing                 |

| MMPD   | Modified Mixer Phase Detector               |

| MOSFET | Metal Oxide Field Effect Transistor         |

| NPC    | Neutral Point Clamped                       |

| OLTF   | Open-loop Transfer Function                 |

| OSG    | Orthogonal Signal Generator                 |

| PCBPrinted Circuit BoardPQActive and Reactive Power ControllerPODPhase Opposition DispositionPVPhotovoltaicPCCPoint of Common CouplingPIProportional-IntegralPRProportional-ResonantPLLPhase-locked LoopPWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage DetectionPMPhase Margin |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PODPhase Opposition DispositionPVPhotovoltaicPCCPoint of Common CouplingPIProportional-IntegralPRProportional-ResonantPLLPhase-locked LoopPWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                             |  |

| PVPhotovoltaicPCCPoint of Common CouplingPIProportional-IntegralPRProportional-ResonantPLLPhase-locked LoopPWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                            |  |

| PCCPoint of Common CouplingPIProportional-IntegralPRProportional-ResonantPLLPhase-locked LoopPWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                                          |  |

| PIProportional-IntegralPRProportional-ResonantPLLPhase-locked LoopPWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                                                                     |  |

| PRProportional–ResonantPLLPhase-locked LoopPWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                                                                                            |  |

| PLLPhase-locked LoopPWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                                                                                                                   |  |

| PWMPulse Width ModulationpPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                                                                                                                                       |  |

| pPLLpower-based phase-locked loopPS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                                                                                                                                                                |  |

| PS-PWMMulti-carrier Phase-shifted PWMPDPhase DetectorPVDPeak Voltage Detection                                                                                                                                                                                                                                                                                 |  |

| PD     Phase Detector       PVD     Peak Voltage Detection                                                                                                                                                                                                                                                                                                     |  |

| PVD         Peak Voltage Detection                                                                                                                                                                                                                                                                                                                             |  |

| 8                                                                                                                                                                                                                                                                                                                                                              |  |

| PM Phase Margin                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                |  |

| RRF         Rotating Reference Frame                                                                                                                                                                                                                                                                                                                           |  |

| StRF         Stationary Reference Frame                                                                                                                                                                                                                                                                                                                        |  |

| SRF Synchronous Reference Frame                                                                                                                                                                                                                                                                                                                                |  |

| SPWM Multi-carrier Based Pulse Width Modulation                                                                                                                                                                                                                                                                                                                |  |

| SHE-PWM Selective Harmonic Elimination                                                                                                                                                                                                                                                                                                                         |  |

| SVM         Multilevel Space Vector Modulation                                                                                                                                                                                                                                                                                                                 |  |

| SPGC Single-phase Grid-connected Converter                                                                                                                                                                                                                                                                                                                     |  |

| SOGI         Second-order Generalized Integrator                                                                                                                                                                                                                                                                                                               |  |

| SO Symmetrical Optimum                                                                                                                                                                                                                                                                                                                                         |  |

| SPI Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                |  |

| THD Total Harmonic Distortion                                                                                                                                                                                                                                                                                                                                  |  |

| T-PDs Transformation-based Phase Detectors                                                                                                                                                                                                                                                                                                                     |  |

| VSC Voltage-source Converter                                                                                                                                                                                                                                                                                                                                   |  |

| VSI Voltage-source Inverter                                                                                                                                                                                                                                                                                                                                    |  |

| VCO Voltage-controlled Oscillator                                                                                                                                                                                                                                                                                                                              |  |

| WD Window Detector                                                                                                                                                                                                                                                                                                                                             |  |

| ZCD Zero-crossing Detection                                                                                                                                                                                                                                                                                                                                    |  |

# CHAPTER 1 INTRODUCTION

#### **1.1 Introduction**

During the last decade, renewable energy sources have attracted most of the attention as a promising means to tackle the energy, sustainability and environmental concerns being faced today worldwide [1, 2]. Among these energy sources, the photovoltaic (PV) technology has been regarded as an environmentally friendly alternative energy source and has advanced considerably in recent years. As depicted in Figure. 1.1, over the past decade, the number of PV installations with the majority being grid-connected has experienced extraordinary growth. For example, the total installed global capacity grew from 177 GW installed in 2014 to reach 227.1 GW by the end of 2015 [3].

Figure 1.1. The worldwide cumulative installed PV power in MW according to IEA [3]

Nowadays, and due to the necessity of producing and delivering more reliable, flexible and clean energy technologies, the electrical power providers are turning toward distributed power generation systems (DPGSs). In such systems, a large number of small-scale electricity generation units mostly from renewable energy resources such as, roof-mounted photovoltaic

and wind generation systems are integrated into power systems at distribution level [1, 2, 4]. Recently, the number of distributed power generation systems (DPGSs) has reached significant penetration levels and are expected to become increasingly predominant in the near future [2, 5-7]. In such systems, the enabling technology of power electronic converters and associated control are utilized to perform different tasks. In addition to providing high-quality power to the electricity network, these systems should actively contribute to grid stability by supporting voltage/frequency under different grid conditions [8-10]. However, the action of interfacing such systems to the utility grid, can seriously affect the grid stability, power-quality and safety conditions if these systems are not appropriately controlled [2, 7, 11]. This issue has become of great concern to electricity supply companies, and as a consequence, new and more stringent standards have been in force. This is in respect of how these power sources interact with the grid, to ensure the power quality of the network is not compromised [11-14]. Accordingly, more attention should be given on ways of advancing the control strategy used in grid-connected power converters. Such a control strategy should be able to ensure that power extracted from renewable energy sources and transmitted to the grid-side does not violate the modern grid codes and standards [15]. Generally, this control strategy consists of, a synchronization unit to ensure fast and precise grid synchronization, and a current controller to enable a high-quality current injection [2, 7].

Synchronization is one of the most important aspects to be considered in the control of power converters interfacing renewable energy sources to the utility grid [16-19]. Grid-connected converters should be appropriately synchronized with the network and stay actively connected, supporting the grid services and maintaining the generation up under many different grid conditions [10, 20]. In such conditions, an accurate and fast detection of phase angle, frequency and amplitude of the grid voltage is an essential requirement for effective operation and control of the grid-connected converters [21]. Thus, grid voltage variables should be continuously monitored at the point of common coupling (PCC). This is to confirm the suitability of the network state for a correct operation of power converters, also to set the energy transfer between the power converter and the utility grid accordingly [11]. In addition to the synchronisation issue, regulating the current injected into the utility grid using advanced current control strategies is another very important feature to be investigated. Typically, the performance of such a current controller relies heavily on the estimated amplitude and phase-angle of the grid voltage, thus, it is greatly affected by the response of the synchronization algorithm. As a

consequence, the quality of the injected power from renewable energy sources under different grid disturbances, can be effectively enhanced by adopting a more robust synchronization method.

#### **1.2 Project Motivation**

This thesis is concerned with research into grid-connected photovoltaic (PV) systems, specifically low-power single-phase PV 'roof-mounted' systems. In such systems, the synchronization is normally performed using phase-locked loop (PLL) algorithms. The PLL as a key component in grid-connected systems will impact the power quality, stability and reliability of the power conversion system. Accordingly, the PLL used in the synchronization of PV inverters with the grid should be carefully designed to achieve optimal steady-state and transient response. Most of the previous studies have dealt with the performance developments of PLL algorithms under various disturbances in the grid voltage such as harmonics, voltage dip, frequency deviations and phase-angle jumps. However, errors generated from the grid voltage measurement circuits e.g. DC offset, can seriously affect the response of the PLL, and as a consequence, the entire performance of the grid-connected PV system may be degraded. For this reason, there is obviously considerable motivation to enhance grid-connected PV inverter performance through the use of more robust PLL algorithm that can estimate the grid voltage variables more accurately under different grid disturbance conditions including the presence of such a dc offset.

In addition to the synchronization algorithm, grid-connected PV inverter systems generally require a current control scheme to regulate their output current as well as to provide a high-quality power exchange with the utility grid. Owing to their simple structure and digital implementation, PI-controllers in the stationary reference frame are considered as the most conventional approaches used for current controlled inverters. However, because of the time-varying nature of the quantity being controlled, these PI-controllers have a major drawback of the inability to track a sinusoidal reference without steady-state error [22, 23]. This drawback can be overcome if the PI-controller is implemented in the synchronous reference frame (SRF) instead. In an SRF, usually referred to as a dq frame, ac (time varying) quantities appear as de (time invariant) quantities. This allows the controller to be designed as would be for dc–dc converters, presenting infinite control gain at the steady-state operating point, and leading to zero steady-state error [24, 25]. The dq-controller has been very effectively used for the current

control of three-phase systems to obtain zero steady-state [25-28]. However, they encounter shortcomings when utilized in single-phase systems. In such systems, the use of a dq-controller is not possible unless a fictitious quadrature signal is produced to form a two-axis environment (i.e., $\alpha\beta$ ) [24, 29]. Thus, in this regard, a new way of implementing such PI-controllers in the dq reference frame without the need for creating such a fictitious quadrature signal is proposed.

To assess where photovoltaic system performance can be improved, however, it is necessary to understand the typical operation of a grid-connected PV inverter system. This will therefore be the focus of the following discussion.

#### 1.3 Typical Operation of a Grid Connected PV Inverter System