# Measurement Schemes with Reduced Number of Sensors for Modular Multilevel Converter

Osama Alshebani Mohamed Abushafa

B.Sc., M.Sc.

A thesis submitted for the degree of Doctor of Philosophy

September 2017

School of Electrical and Electronic Engineering

Newcastle University United Kingdom

### ABSTRACT

During the last four decades there has been considerable development in voltage source converters (VSCs), which are widely contributed in multilevel converter topologies. Since then, multilevel VSC topologies have been used for applications with different power rating owing to the improvement of the output waveforms quality and minimising filtering requirements. In comparison with the conventional multilevel converters, modular multilevel converter (MMC) is considered as the most attractive topology for high and medium-power applications mainly due to the series connection of a high number of submodules (SMs).

The challenges associated with the implementation of a high number of SMs includes: voltage-balancing of the distributed SM, cost, reliability and the increased complexity in the circuit configuration. Furthermore, achieving efficient and fast closed-loop control of the MMC requires the accurate knowledge of the voltage and current measurements, which means a considerable number of sensors are usually required to operate the MMCs.

The main objective of this research is to propose several novel strategies for the converter to achieve voltage-balancing with fewer number of sensors to produce comparable performance to the sensor-based method. Four different sensorless schemes have been investigated, where two are current sensorless-based techniques and two are voltage sensorless-based techniques. The proposed current sensorless schemes are based on developed sorting algorithm, and the proposed voltage sensorless schemes employ two novel different recursive algorithms with the standard sorting algorithm. In regards to the voltage sensorless schemes, the first proposed method uses an exponentially weighted recursive least square (ERLS) algorithm, while the second proposed method employs a Kalman filter (KF) to estimate the SM capacitor voltages. Capacitance uncertainty has been investigated for the proposed voltage sensorless schemes. The proposed methods have been implemented via simulation but also on a scaled-down laboratory prototype.

The thesis also deals with capacitor diagnosis where a new scheme has been proposed which may be used for health monitoring technique, a comparison with an existing technique has been evaluated.

Detailed simulations and experimental tests are carried out to investigate the performance of the proposed sensorless schemes, and results are compared with the sensor-based approach. These various schemes have been implemented and tested in real-time using a commercial floating point microcontroller where a 4-level single-phase MMC was employed. The results achieved for these novel schemes show an important improvement in the performance of the MMC under different operation conditions while fewer sensors were used.

### DEDICATION

I dedicate my dissertation work to my loving parents: "Alshebani Abushafa L Khiriya Almadhoon"

اهدي هذه الاطروحة الي احبتي ابي وامي: "الشيباني ابوشعفة و خيرية المدمون"

### ACKNOWLEDGMENT

First and foremost, my deepest thanks always go to Allah for giving me the ability and the patience to complete this work.

I would like to acknowledge everyone who helped to make this work possible. My sincere gratitude goes to my supervisors: Dr Shady Gadoue, Dr Mohamed Dahidah and Dr David Atkinson for their encouragement, support and guidance. I highly appreciate the time they spent with me to further develop my academic career.

I have the deepest gratitude for my beloved parents, brothers, sisters, my wife and my little kids for always being supportive whenever I needed them to. Without their support this work would not have been completed, thanks again to my beloved family.

I would like to also acknowledge the Libyan Ministry of Higher Education and Scientific Research for sponsoring this research and Zawia University.

Finally, I would like to express my appreciation to my friends and all colleagues at home back in my country and here in Newcastle.

# TABLE OF CONTENTS

| AbstractI                                             |

|-------------------------------------------------------|

| DedicationIII                                         |

| AcknowledgmentIV                                      |

| Table of Contents                                     |

| List of FiguresXI                                     |

| List of symbolsXXI                                    |

| List of Abbreviations                                 |

| CHAPTER 1 1                                           |

| INTRODUCTION 1                                        |

| 1.1 Voltage Source-Based Converters                   |

| 1.2 Challenges Associated with Multilevel Converters2 |

| 1.3 Objectives of the Thesis                          |

| 1.4 Topologies and Tools Used                         |

| 1.5 Thesis Contributions and Publications             |

| 1.6 Layout of the Thesis5                             |

| CHAPTER 2                                             |

| MODULAR MULTILEVEL CONVERTER: PRINCIPLES OF           |

| OPERATION, MODELLING & CONTROL, AND APPLICATIONS      |

| 2.1 Introduction                                      |

| 2.2 Conventional Multilevel Converters                |

| 2.3 The MMC: Structure and Principles of Operation10                 |

|----------------------------------------------------------------------|

| 2.4 Currents Analysis in MMC13                                       |

| 2.4.1 Output and Arm Currents                                        |

| 2.4.2 The Circulating Current                                        |

| 2.5 The MMC Output Voltage14                                         |

| 2.6 Features Associated with the MMC Topology14                      |

| 2.7 MMC Modulation Strategies15                                      |

| 2.8 Challenges Associated with the MMC16                             |

| 2.9 Control of SM Capacitor Voltage with Voltage and Current Sensors |

| 2.9.1 Averaging and Balancing Control Method                         |

| 2.9.2 Sorting Algorithm-based Method                                 |

| 2.10 Control of SM Capacitor Voltage with Fewer Sensors              |

| 2.10.1 Sorting Algorithm Methods with Fewer Current Sensors          |

| 2.10.2 Observer-based Methods                                        |

| 2.10.3 Sorting Algorithm Methods with Fewer Voltage Sensors          |

| 2.10.4 Open-loop Control Methods                                     |

| 2.11 Capacitance Estimation                                          |

| 2.12 MMC Applications                                                |

| 2.12.1 Energy Generation                                             |

| 2.12.2 Transmission, Supporting Network and Distribution Systems     |

| 2.12.3 End-User and Stand Alone Usage Areas                          |

| 2.13 Chapter Summary                                                 |

| CHAPTER 3                                                            |

| THE EXPERIMENTAL SET-UP SYSTEM                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 Introduction                                                                                                                             |

| 3.2 The 4-Level Single-Phase MMC and R-L Load                                                                                                |

| 3.3 Microprocessor Control System                                                                                                            |

| 3.4 Hardware Implementation and Microprocessor Setting                                                                                       |

| 3.5 Chapter Summary                                                                                                                          |

| CHAPTER 4                                                                                                                                    |

| PROPOSED CURRENT SENSORLESS METHODS                                                                                                          |

| 4.1 Introduction                                                                                                                             |

| 4.2 Conventional method (sensor-based method)                                                                                                |

| 4.3 Load Current Monitoring Method                                                                                                           |

| 4.4 Sensor-never Current Monitoring Method42                                                                                                 |

| 4.5 Increasing the Output Level of the Converter                                                                                             |

| 4.6 Simulation Results                                                                                                                       |

| 4.6.1 Output Results of the Converter with Load Current Monitoring Method.<br>Sensor-Never Current Monitoring Method and Conventional Method |

| 4.7 Experimental Results                                                                                                                     |

| 4.7.1 Steady-State Results                                                                                                                   |

| 4.7.2 Dynamic Results                                                                                                                        |

| 4.8 Chapter Summary                                                                                                                          |

| CHAPTER 5                                                                                                                                    |

| PROPOSED SENSORLESS VOLTAGE ESTIMATION METHOD BASED<br>ON EXPONENTIALLY WEIGHTED RECURSIVE LEAST SQUARE<br>ALGORITHM                         |

|                                                                                                                                              |

| 5.1 Introduction70                                                             |

|--------------------------------------------------------------------------------|

| 5.2 Least Square (LS) Algorithm                                                |

| 5.3 Conventional RLS Algorithm72                                               |

| 5.4 Exponentially Weighted RLS Algorithm73                                     |

| 5.5 Proposed Estimation Technique75                                            |

| 5.5.1 Modelling and System Configuration of the SMs75                          |

| 5.5.2 Proposed Voltage Estimation Technique77                                  |

| 5.6 Simulation Results                                                         |

| 5.6.1 Conventional RLS Results                                                 |

| 5.6.2 ERLS Results                                                             |

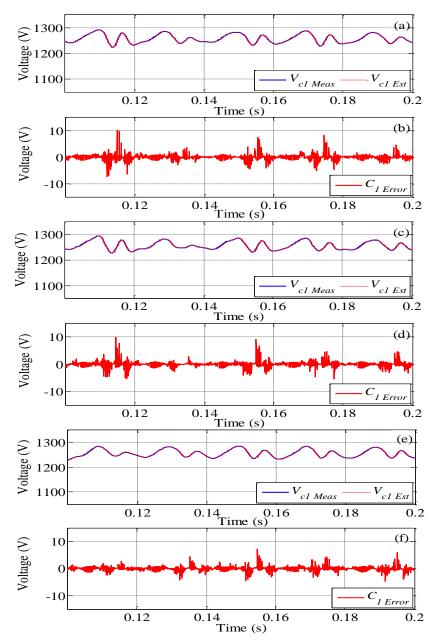

| 5.7 Experimental Results                                                       |

| 5.7.1 Impact of Voltage Drop on the System Model                               |

| 5.7.2 Steady-State Condition Results 100                                       |

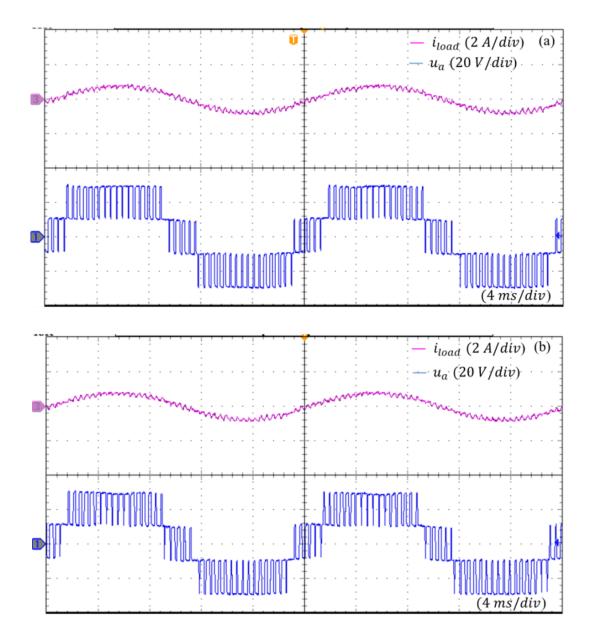

| 5.7.3 Results for Load Step Change Condition103                                |

| 5.7.4 Effect of a Fault in the DC Source on the Voltage Estimation Value . 104 |

| 5.7.5 Effect of an Extreme Increase in DC Voltage 104                          |

| 5.8 Chapter Summary 105                                                        |

| CHAPTER 6 107                                                                  |

| PROPOSED SENSORLESS VOLTAGE ESTIMATION METHOD BASED                            |

| ON KALMAN FILTER ALGORITHM                                                     |

| 6.1 Introduction107                                                            |

| 6.2 Kalman Filter 108                                                          |

| 6.3 Proposed Kalman Filter Voltage Estimation Scheme                           |

| 6.4 Simulation Results                                                       |

|------------------------------------------------------------------------------|

| 6.4.1 The Performance of the Proposed Method for Normal Operating Conditions |

| 6.4.2 Performance of the Proposed Method with Capacitance Deviation 115      |

| 6.4.3 Effect of Load Change on Performance                                   |

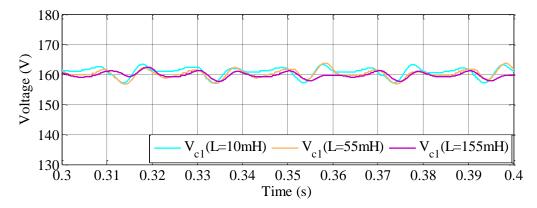

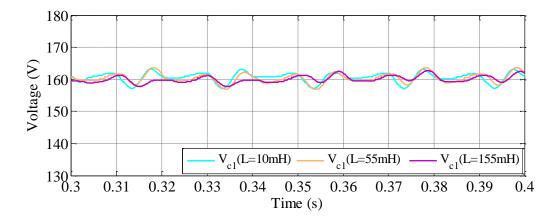

| 6.4.4 The Effect of Low Carrier Frequency on Performance                     |

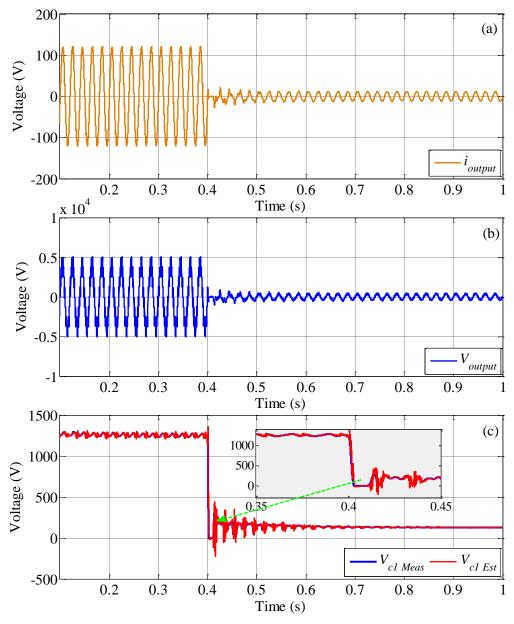

| 6.4.5 DC Fault and Start-up Performance                                      |

| 6.4.6 The Performance of the Proposed KF Method with a High Number of SMs    |

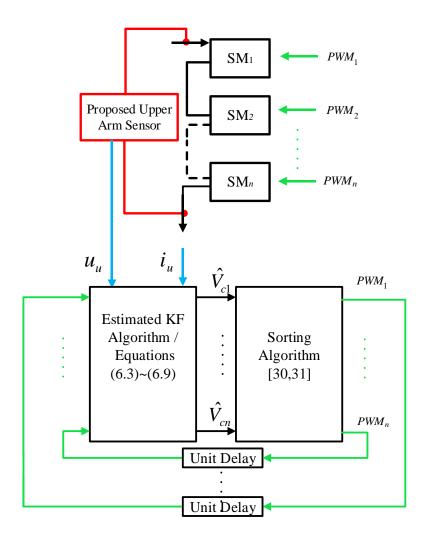

| 6.5 Experimental Results                                                     |

| 6.5.1 Steady-State Operation Performance                                     |

| 6.5.2 Effect of Load Change on Performance                                   |

| 6.5.3 The effect of a Fault in the DC Source on the Estimation Value 131     |

| 6.5.4 Extreme Increase in the DC Source                                      |

| 6.5.5 Comparison of ERLS and KF Proposed Methods132                          |

| 6.6 Chapter Summary                                                          |

| CHAPTER 7                                                                    |

| PROPOSED SCHEME FOR MONITORING SUBMODULE                                     |

| <b>CAPACITANCE</b>                                                           |

| 7.1 Introduction                                                             |

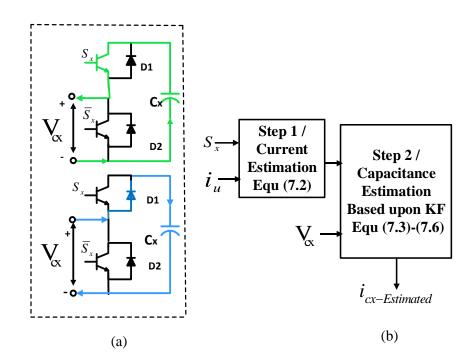

| 7.2 Proposed KF Capacitance Estimation Method                                |

| 7.2.1 Current Estimation                                                     |

| 7.2.2 Capacitance Estimation                                                 |

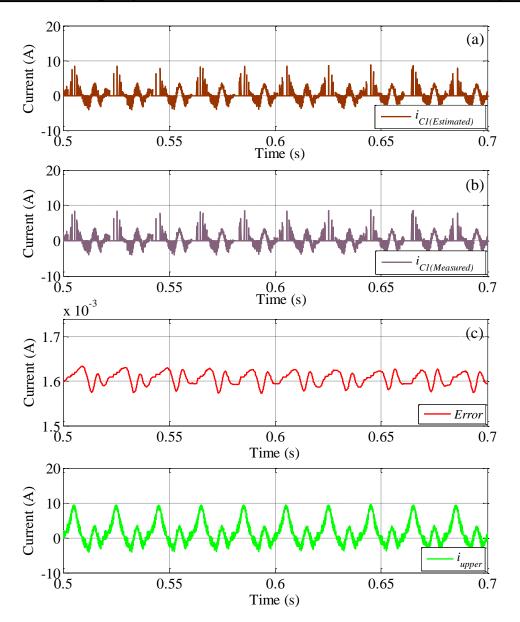

| 7.3 Results                                                                  |

| 7.3.1 Steady-State Results  |  |

|-----------------------------|--|

| 7.3.2 Dynamic Results       |  |

| 7.4 Chapter Summary         |  |

| CHAPTER 8                   |  |

| CONCLUSIONS AND FUTURE WORK |  |

| 8.1 Summary                 |  |

| 8.2 Future Work             |  |

| References                  |  |

| Appendix A                  |  |

# **LIST OF FIGURES**

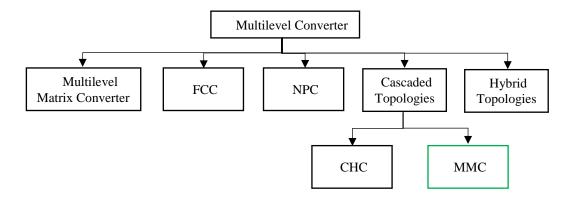

| Fig. 2.1. Classification of medium and high voltage multilevel converters 10                                                     |

|----------------------------------------------------------------------------------------------------------------------------------|

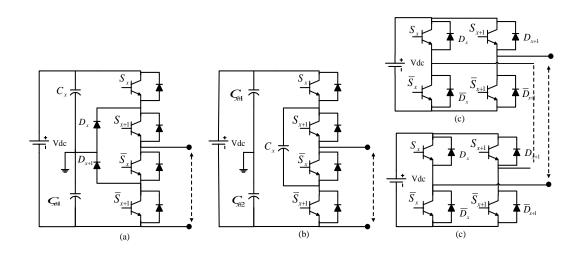

| Fig 2.2. Conventional multilevel converter topologies: (a) Three-level NPC converter, (b) Three-level FCC and (c) Five-level CHC |

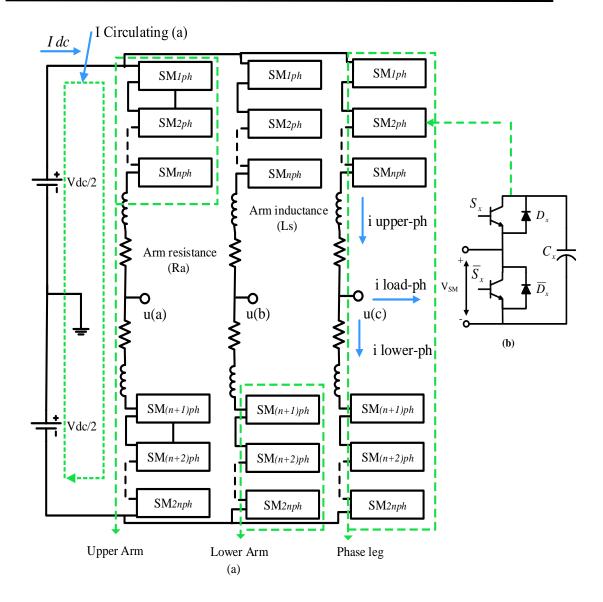

| Fig 2.3. Block diagram of MMC. (a) Three-phase block diagram. (b) Half-bridge SM configuration                                   |

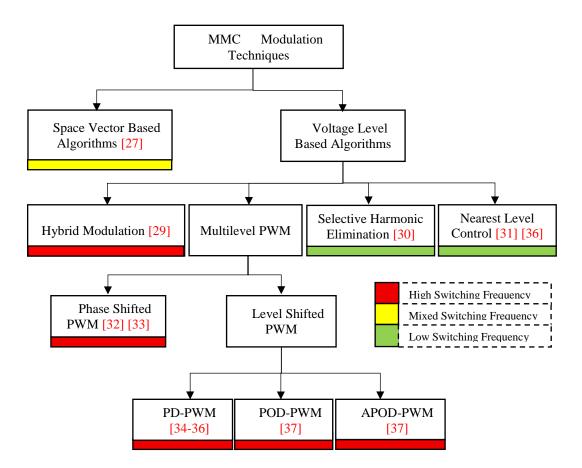

| Fig. 2.4. MMC Modulation Strategies16                                                                                            |

| Fig 2.5. Block diagram of voltage-balancing control based on sorting algorithm scheme                                            |

| Fig 2.6. General block diagram of the observe-based method                                                                       |

| Fig. 2.7. Percentages of failure rates in power electronic devices                                                               |

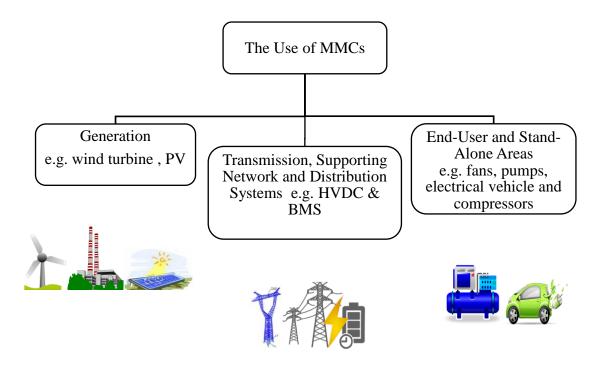

| Fig 2.8. Classify MMC applications                                                                                               |

| Fig 3.1. Block diagram of the experimental set-up                                                                                |

| Fig 3.2. Half-bridge SM configuration. (a) A photograph of the SM. (b) Schematic diagram of the SM                               |

| Fig 3.3. Dynamic R-L load configuration. (a) Photograph of the experimental load.<br>(b) Schematic diagram of the load           |

| Fig 3.4. Photograph of the experimental test bench                                                                               |

| Fig 3.5. Dual gate drive                                                                                                         |

| Fig 3.6. Sample of the three upper arm switches ( $PWM_1$ , $PWM_2$ and $PWM_3$ ) 35                                             |

| Fig 4.1. LS-PWM and PS-PWM techniques                                                                                            |

| Fig 4.2 General block diagram of the implementation of the load current monitoring method on a 4-level MMC                       |

| Fig 4.3. Load current monitoring method for <i>N</i> -level MMC level  |  |

|------------------------------------------------------------------------|--|

| Fig 4.4 Sensor-never current monitoring method for <i>N</i> -level MMC |  |

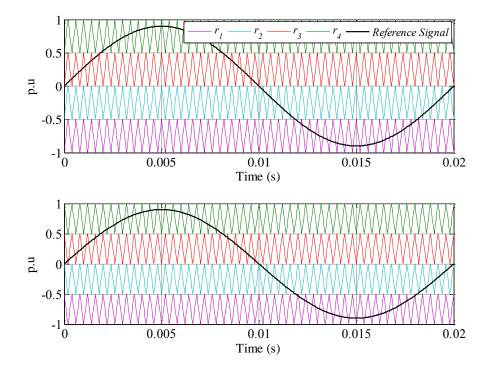

Fig 4.5 Interleaving modulation technique based on PD-PWM Scheme......45

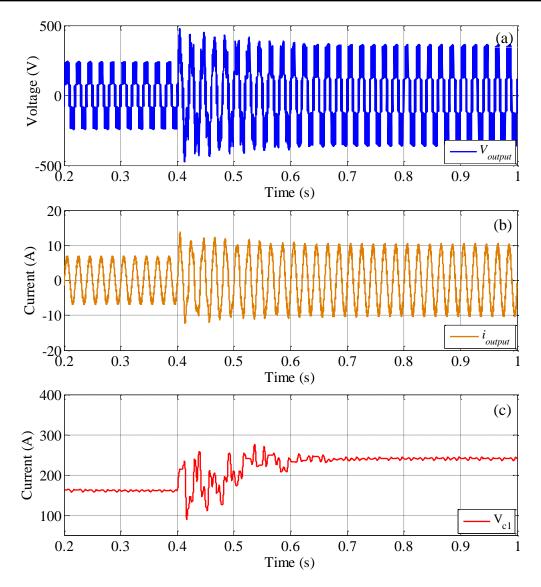

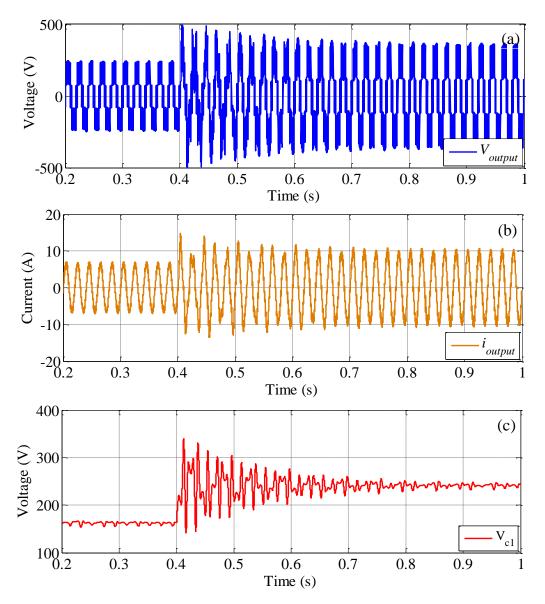

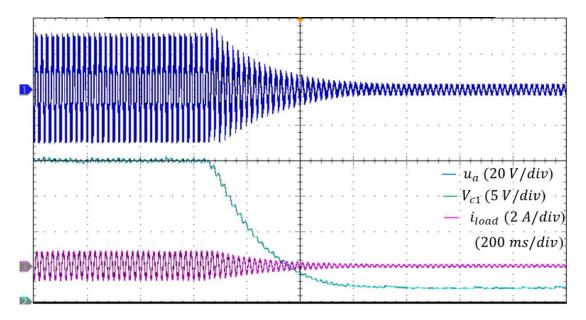

Fig 4.17 Simulation results of applying step change in the load condition for the sensor-based method. 57

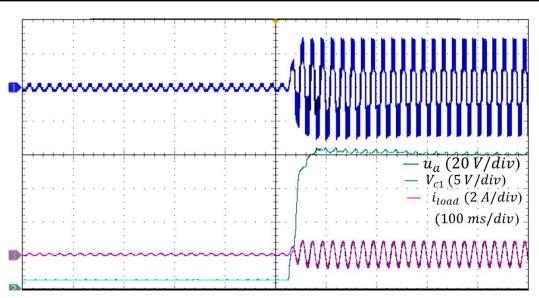

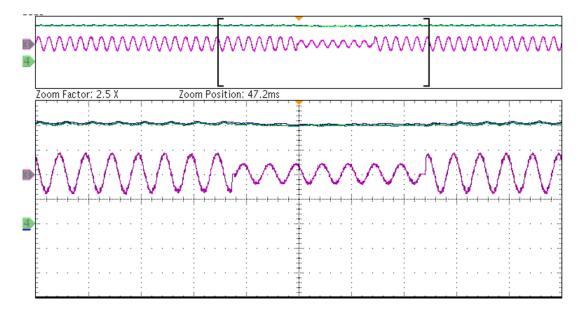

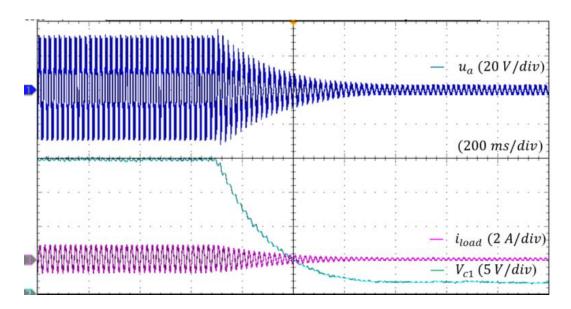

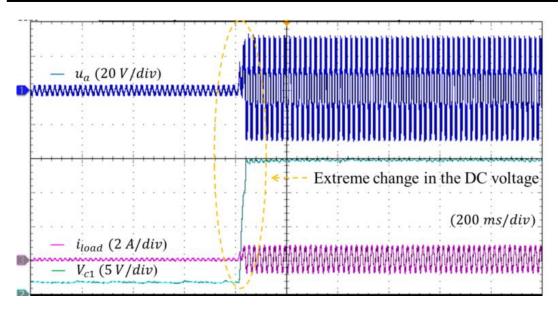

Fig 4.27 Experimental results of step change in the DC voltage and its impact on the voltage across Vc1 / Applied for the load current monitoring proposed scheme.  $\dots$  65

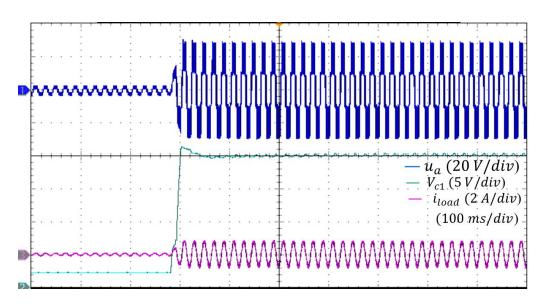

| Fig 4.28 Experimental results of step change in the DC voltage and its impact on the  |

|---------------------------------------------------------------------------------------|

| voltage across Vc1 / Applied for the sensor-never current monitoring proposed scheme. |

|                                                                                       |

|                                                                                       |

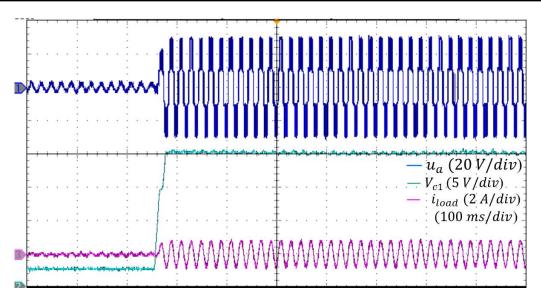

| Fig 4.29 Experimental results of step change in the DC voltage and its impact on the  |

| voltage across Vc1 / Applied for the sensor-based scheme                              |

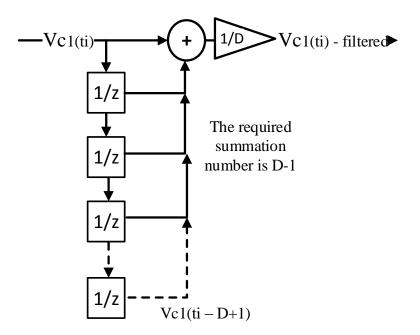

| Fig 4.30 Standard averaging filter used in the experimental implementation66          |

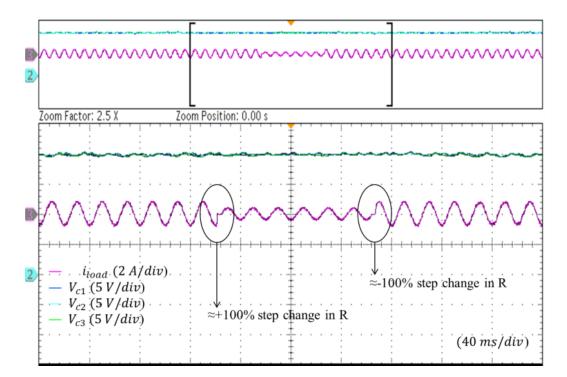

| Fig 4.31. Experimental results of step changes in the load condition of the load      |

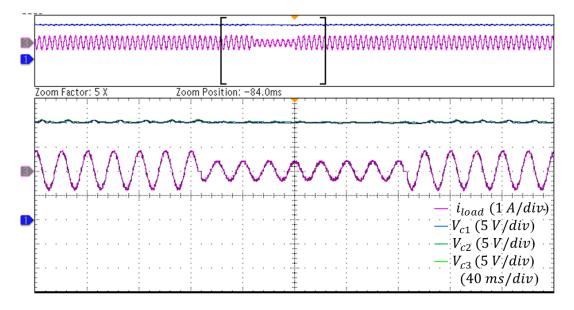

| current monitoring proposed scheme                                                    |

| eartent montoring proposed seneme                                                     |

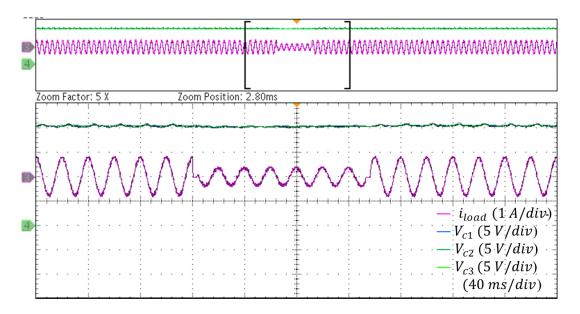

| Fig 4.32. Experimental results of step changes in the load condition of the sensor-   |

| never current monitoring proposed scheme                                              |

|                                                                                       |

| Fig 4.33 Experimental results of step changes in the load condition of the sensor-    |

| based scheme                                                                          |

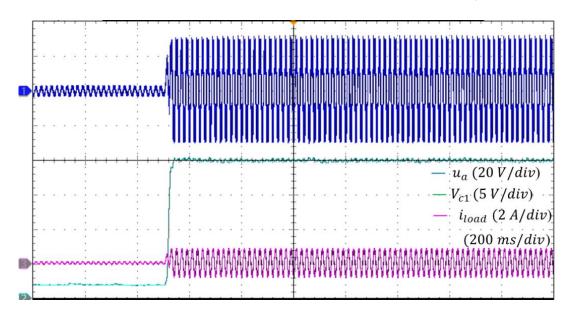

| Fig 5.1. Block diagram of MMC. (a) Single-phase (one-leg) Block diagram. (b)          |

|                                                                                       |

| Half-bridge SM configuration75                                                        |

| Fig 5.2. Connection arrangement of the proposed measuring technique for the MMC.      |

| (a) Upper voltage sensor arrangement. (b) Lower voltage sensor arrangement            |

|                                                                                       |

| Fig 5.3. Flow chart of the proposed SM voltage estimation method for the upper arm.   |

|                                                                                       |

|                                                                                       |

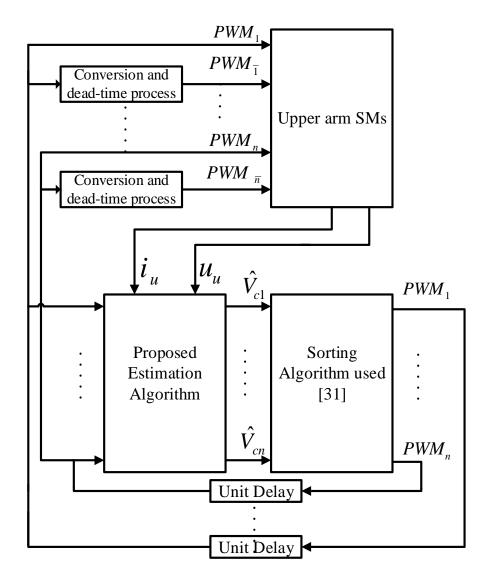

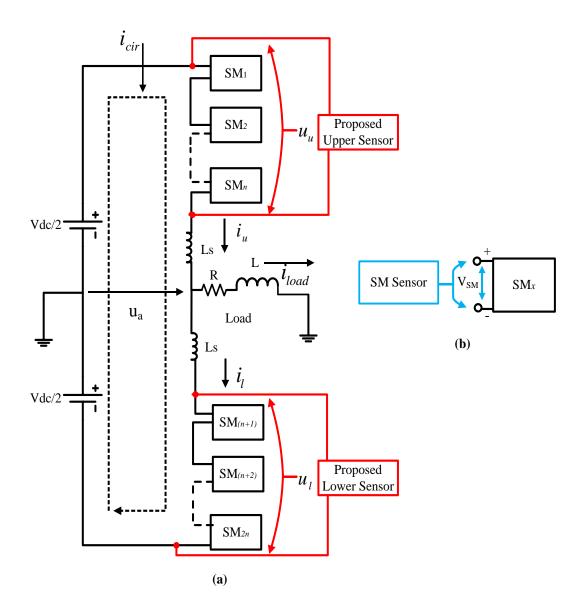

| Fig 5.4. The proposed estimation method and the associated sorting algorithms for     |

| the upper arm control                                                                 |

| Fig 5.5. Block diagram of the upper arm voltage-balancing strategy used               |

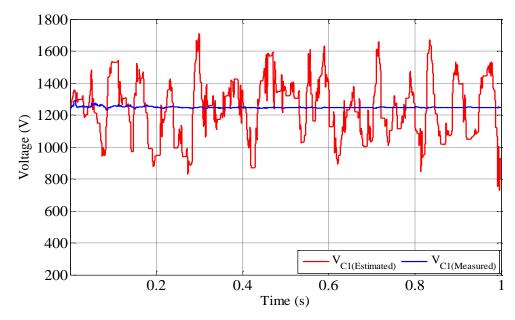

| Fig 5.6. Simulation results of the 9-level MMC with the conventional RLS scheme.      |

|                                                                                       |

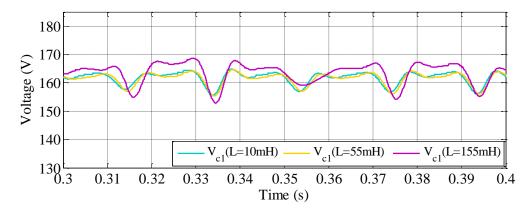

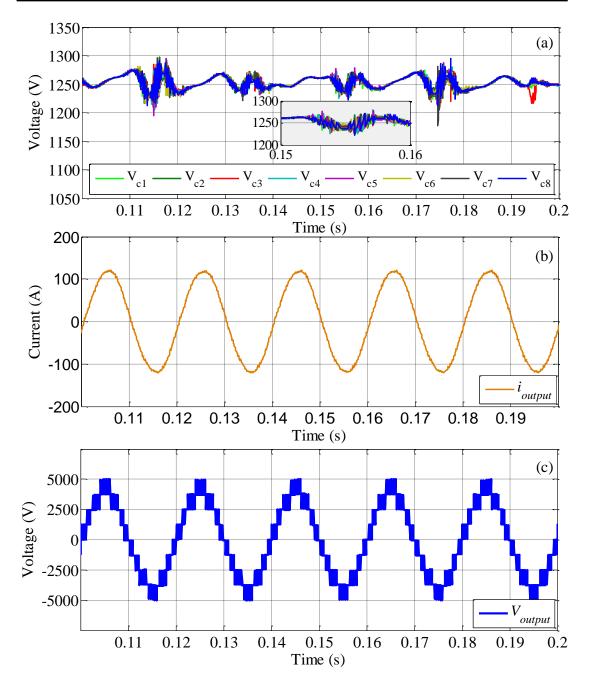

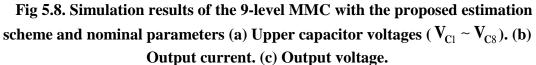

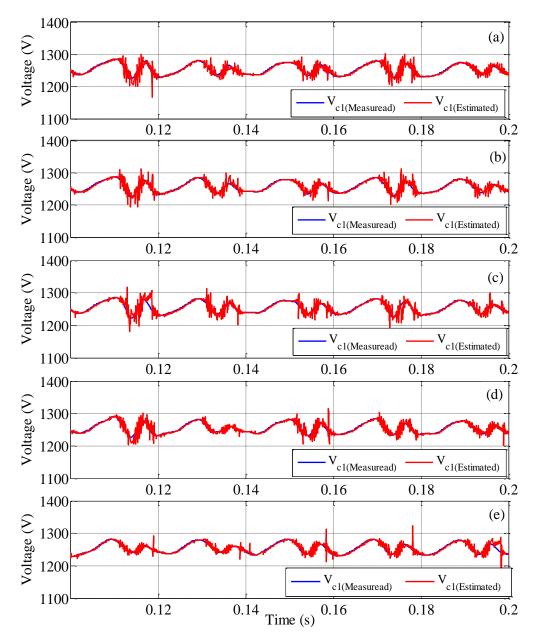

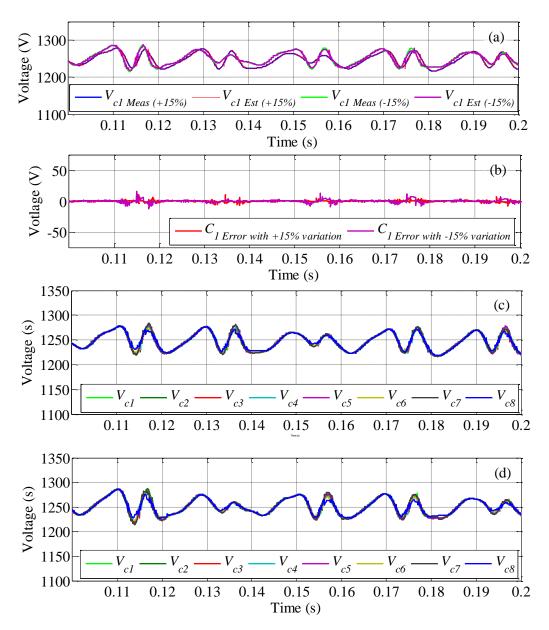

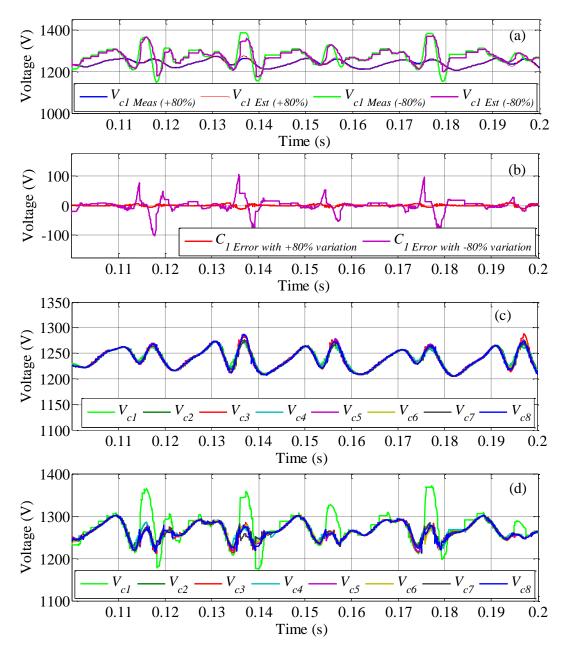

Fig 5.9. Simulation results of the upper arm capacitor errors with variations in all capacitors. (a) Measured and estimated voltage across *C*1 with ±22% variations. (b) Errors between the measured and estimated voltage values when *C*1variations are ±22%. (c) Estimated voltages for (*C*1~*C*8) where the capacitors values are : 2440  $\mu$ F, 1500  $\mu$ F, 1760  $\mu$ F, 2140  $\mu$ F, 1680  $\mu$ F, 2800  $\mu$ F, 1400  $\mu$ F, and 3000  $\mu$ F respectively. (d) Estimated voltages for (*C*1~*C*8) where the values are : 1560  $\mu$ F, 1500  $\mu$ F, 1760  $\mu$ F, 2800  $\mu$ F, 1400  $\mu$ F, and 3000  $\mu$ F respectively. (d) Estimated voltages for (*C*1~*C*8) where the values are : 1560  $\mu$ F, 1500  $\mu$ F, 1760  $\mu$ F, 2800  $\mu$ F, 1400  $\mu$ F, and 3000  $\mu$ F respectively.

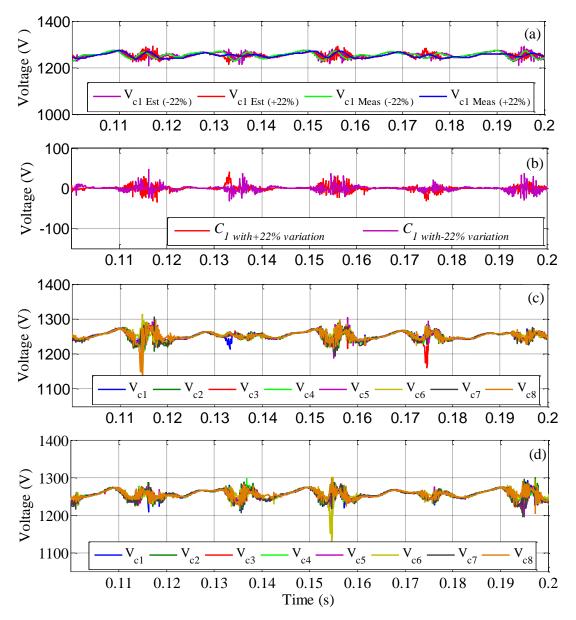

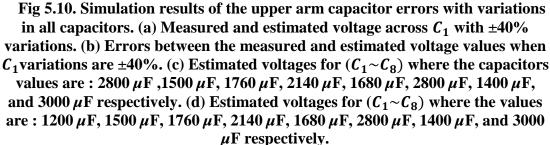

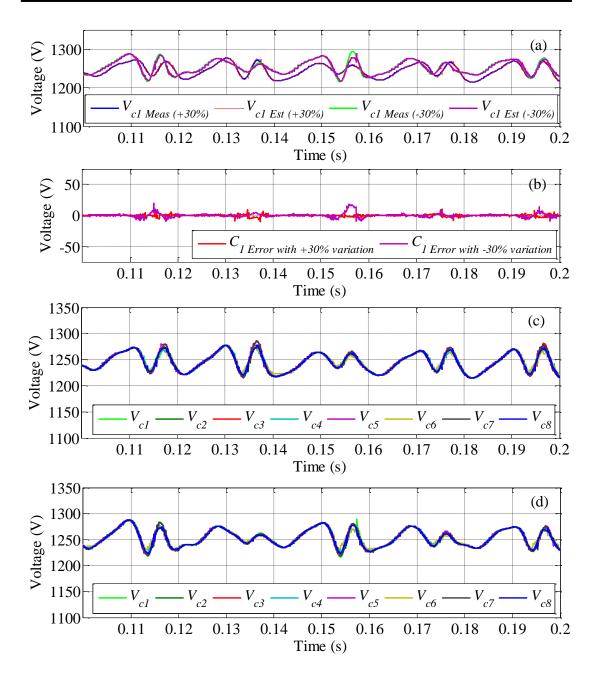

Fig 5.10. Simulation results of the upper arm capacitor errors with variations in all capacitors. (a) Measured and estimated voltage across *C*1 with ±40% variations. (b) Errors between the measured and estimated voltage values when *C*1variations are ±40%. (c) Estimated voltages for (*C*1~*C*8) where the capacitors values are : 2800  $\mu$ F, 1500  $\mu$ F, 1760  $\mu$ F, 2140  $\mu$ F, 1680  $\mu$ F, 2800  $\mu$ F, 1400  $\mu$ F, and 3000  $\mu$ F respectively. (d) Estimated voltages for (*C*1~*C*8) where the values are : 1200  $\mu$ F, 1500  $\mu$ F, 1680  $\mu$ F, 2800  $\mu$ F, and 3000  $\mu$ F respectively. (a) Estimated voltages for (*C*1~*C*8) where the values are : 1200  $\mu$ F, 1500  $\mu$ F, 1760  $\mu$ F, 2800  $\mu$ F, 1400  $\mu$ F, and 3000  $\mu$ F respectively.

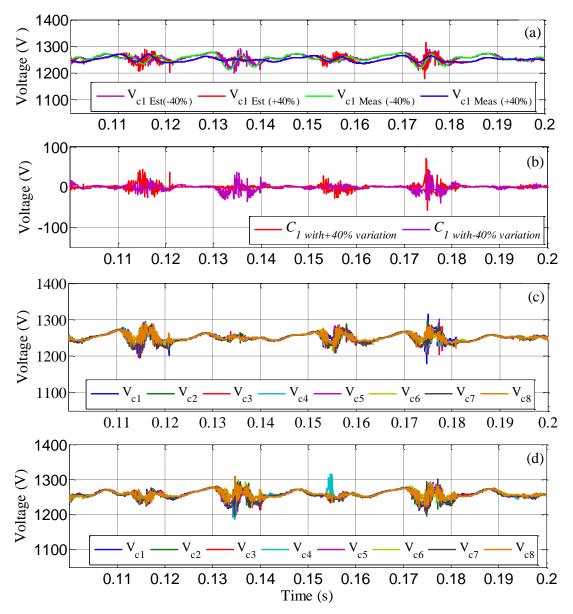

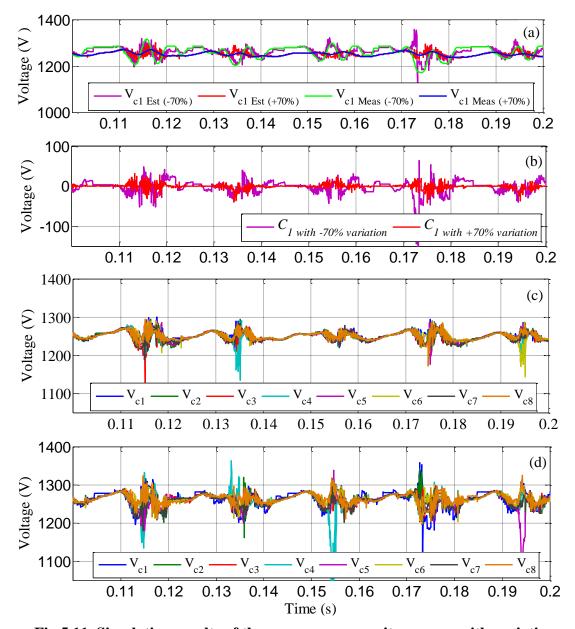

Fig 5.11. Simulation results of the upper arm capacitor errors with variations in all capacitors. (a) Measured and estimated voltage across *C*1 with  $\pm$ 70% variations. (b) Errors between the measured and estimated voltage values when *C*1variations are  $\pm$ 70%. (c) Estimated voltages for (*C*1~*C*8) where the capacitors values are : 3400  $\mu$ F, 1500  $\mu$ F, 1760  $\mu$ F, 2140  $\mu$ F, 1680  $\mu$ F, 2800  $\mu$ F, 1400  $\mu$ F, and 3000  $\mu$ F respectively. (d) Estimated voltages for (*C*1~*C*8) where the values are : 600  $\mu$ F, 1500  $\mu$ F, 1760  $\mu$ F, 2800  $\mu$ F, 1400  $\mu$ F, and 3000  $\mu$ F respectively. (2140  $\mu$ F, 1680  $\mu$ F, 2800  $\mu$

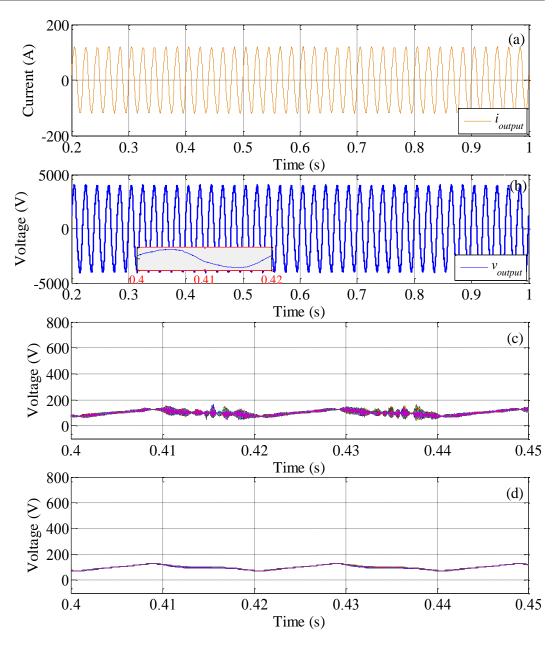

Fig 5.18 Simulation results of the performance of the proposed method with 204 SM per leg (fsampling=250 kHz). (a) Output current. (c) Output voltage. (c) Upper capacitor voltages Vc1~Vc102.......97

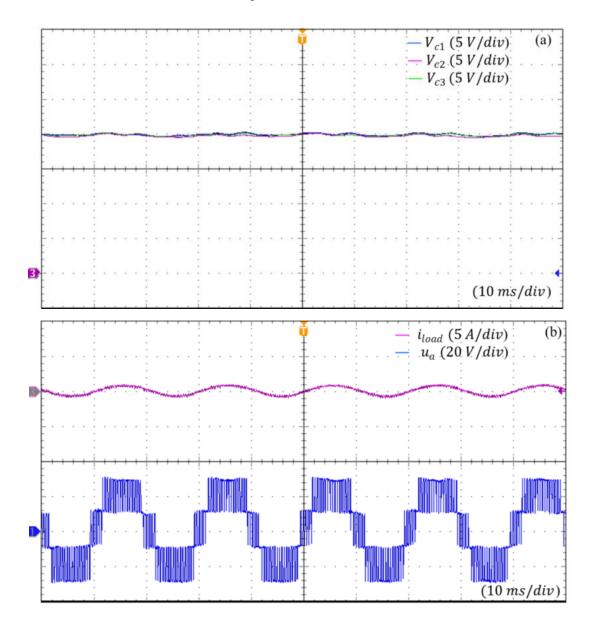

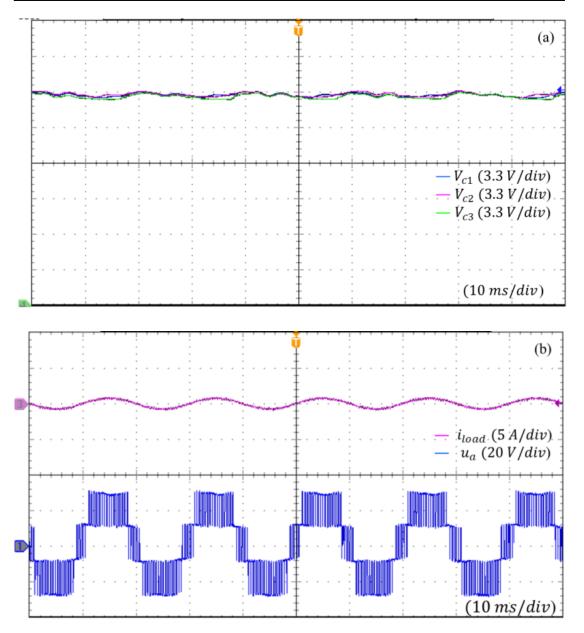

Fig 5.23. Experimental results of the output current and voltage. (a) Results of the sensor-based measurement technique. (b) Results of the proposed estimation technique.

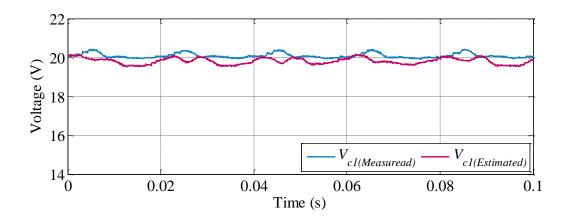

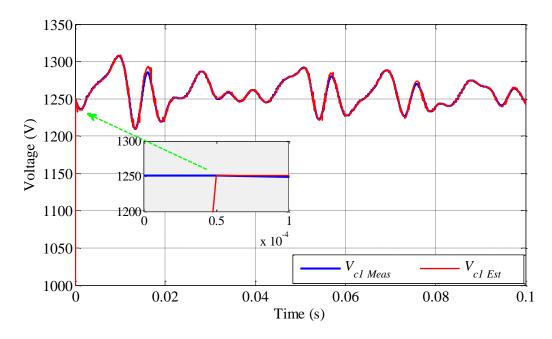

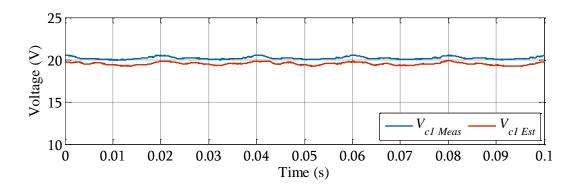

| Fig 5.24. Experimental results of the voltage comparison between the conventional |

|-----------------------------------------------------------------------------------|

| sensor-based method and the proposed method across C1                             |

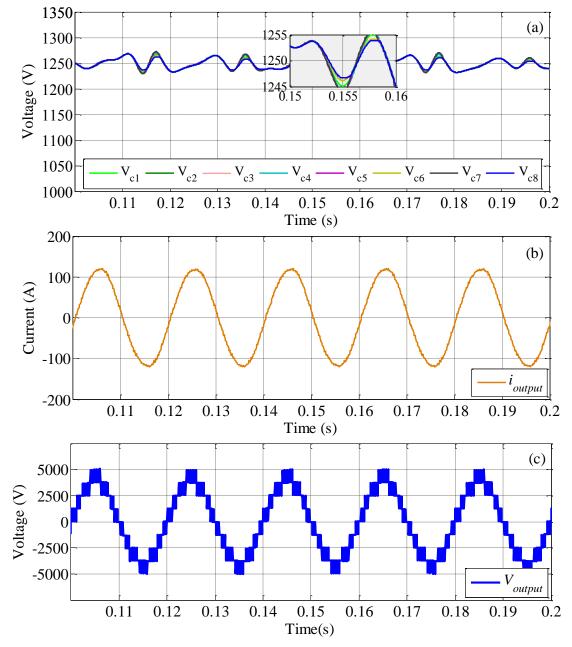

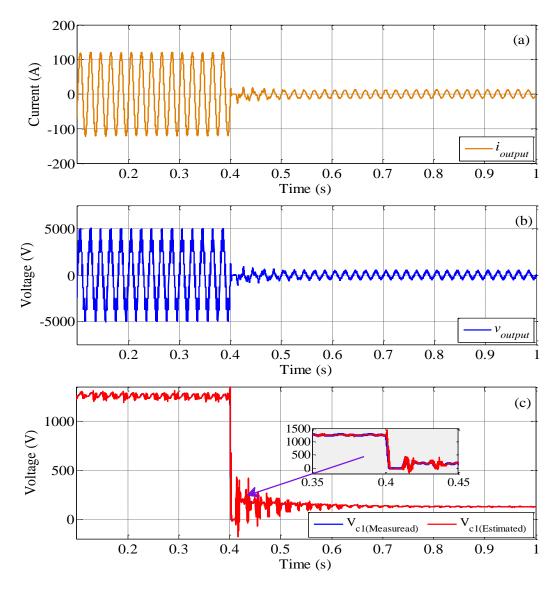

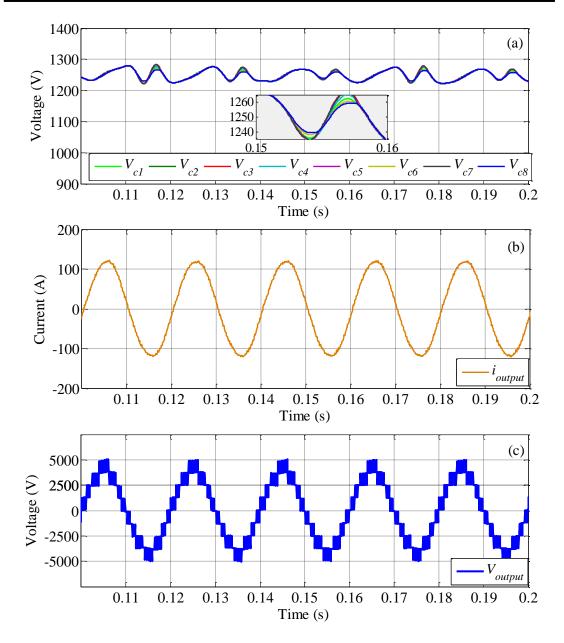

Fig 6.3. Steady-state simulation results for the 9-level MC with the sensor-based method. (a) Upper capacitor voltages  $Vc1 \sim Vc8$ . (b) Output current. (c) Output voltage. 114

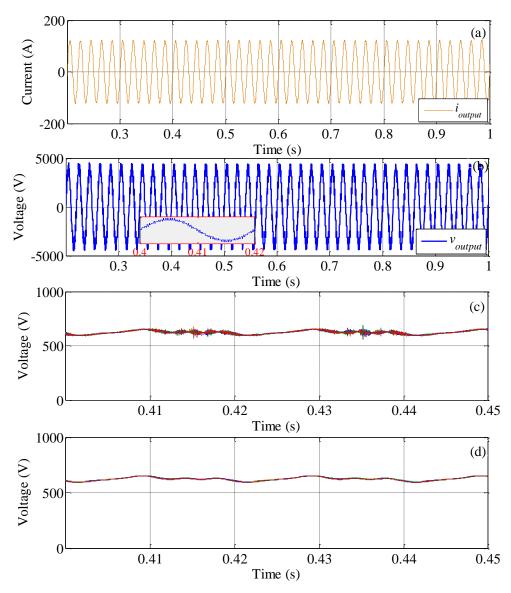

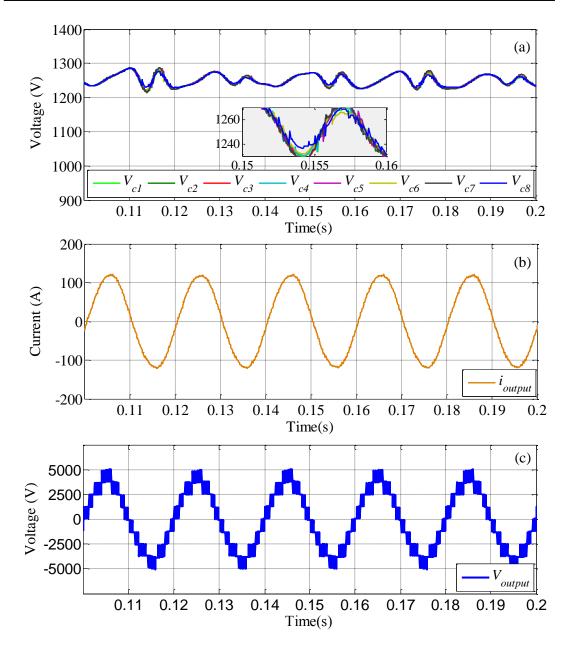

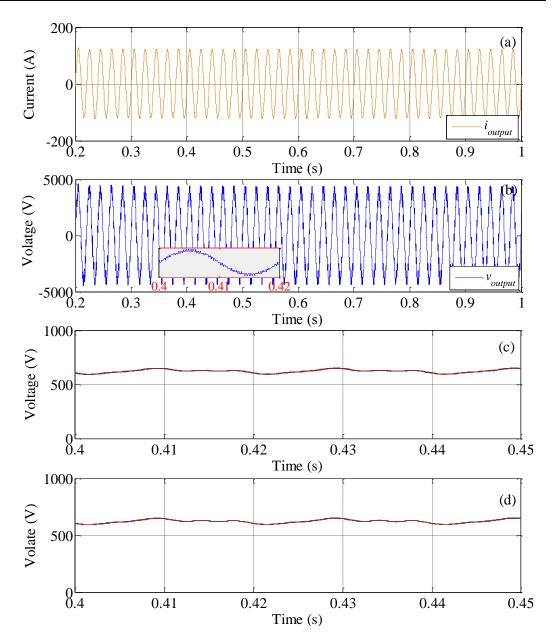

Fig 6.12 The performance of the proposed KF with 32 SMs per leg (fsampling=20 kHz). (a) Output current. (c) Output voltage. (c) Upper capacitor voltages  $Vc1 \sim Vc16$ . (d) Upper capacitor voltages  $Vc1 \sim Vc16$  / Simulation results.

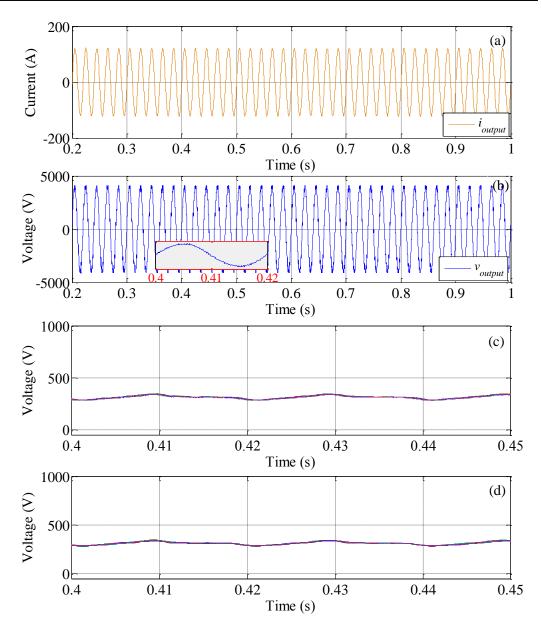

Fig 6.13 The performance of the proposed KF with 64 SMs per leg (fsampling=20 kHz). (a) Output current. (c) Output voltage. (c) Upper capacitor voltages  $Vc1 \sim Vc32$ . (d) Upper capacitor voltages  $Vc1 \sim Vc32$  / Simulation results.

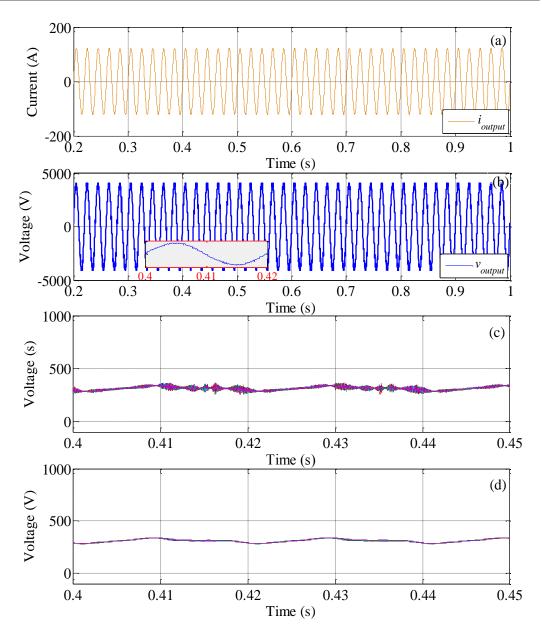

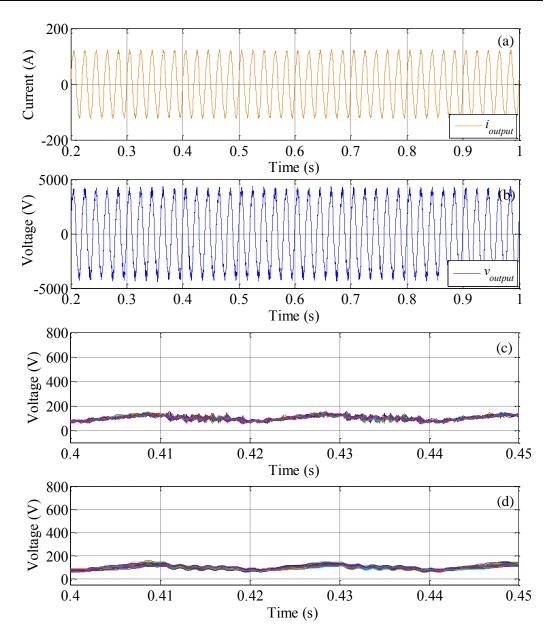

Fig 6.14 The performance of the proposed KF with 204 SMs per leg (fsampling=20 kHz). (a) Output current. (c) Output voltage. (c) Upper capacitor voltages  $Vc1 \sim Vc102$ . (d) Upper capacitor voltages  $Vc1 \sim Vc102$  / Simulation results.

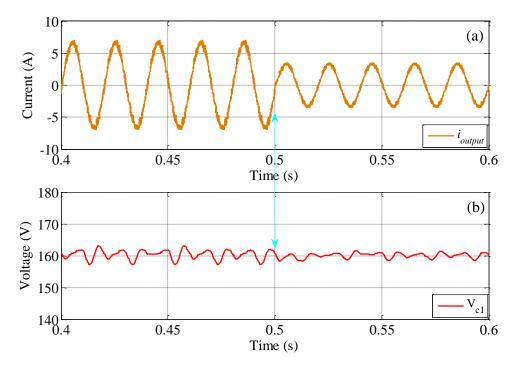

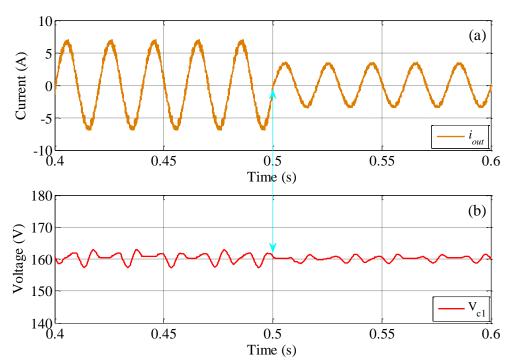

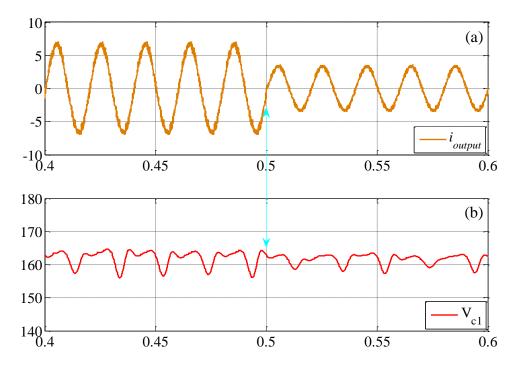

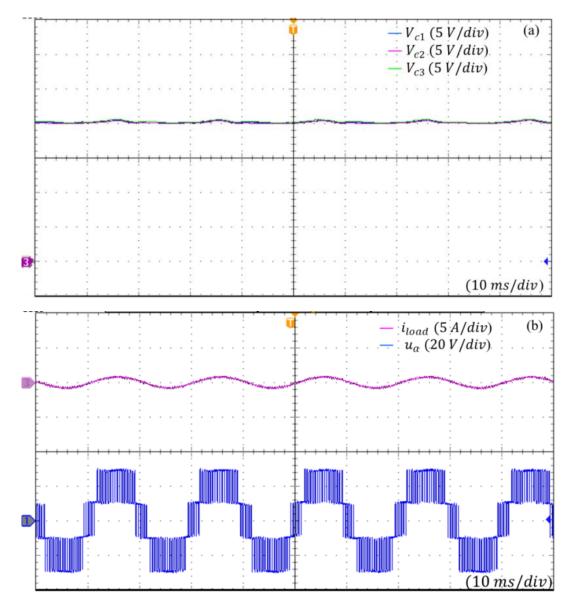

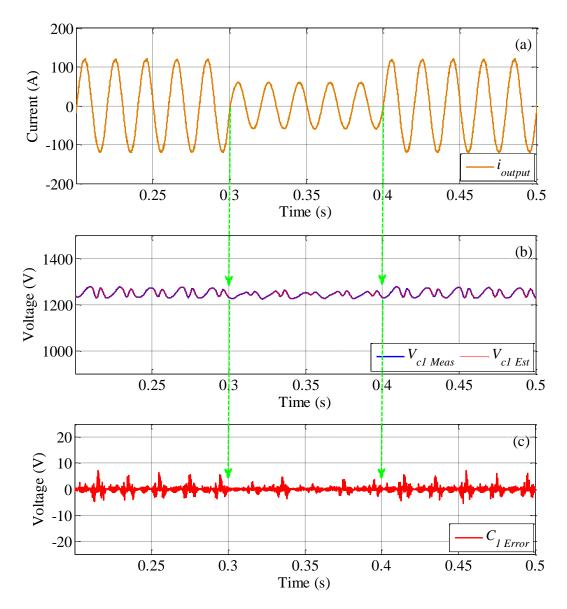

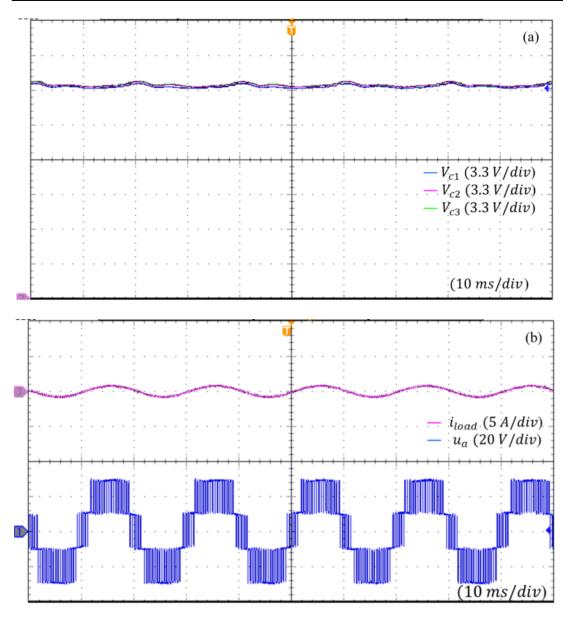

Fig 6.16. Experimental results of the proposed estimation scheme at constant R-L load. (a) Upper SM voltage capacitors. (b) Output current and voltage waveforms.

| Fig 6.17. Experimental results of the voltage  | s across C1 when the sensor-based |

|------------------------------------------------|-----------------------------------|

| method and proposed estimation scheme are used |                                   |

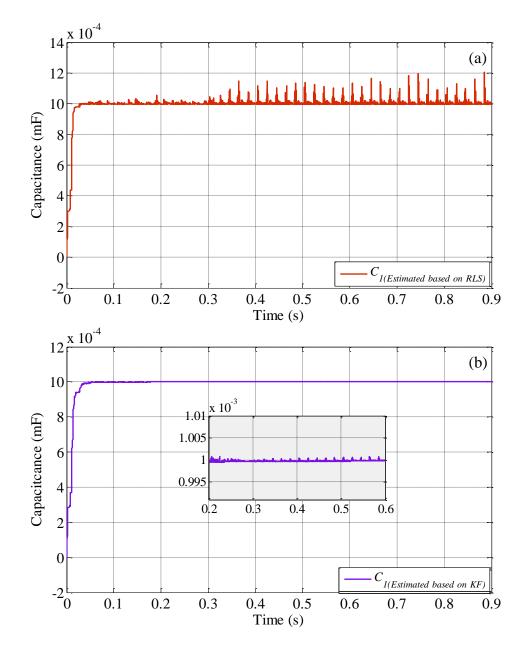

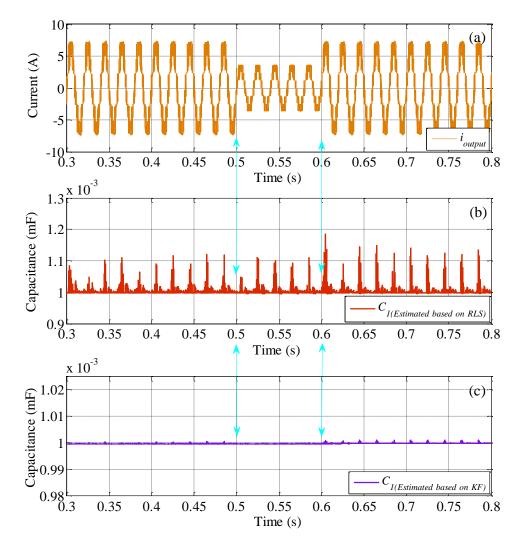

Fig 7.3 Steady-state performance. (a) Capacitance estimation based on RLS algorithm. (b) Capacitance estimation based on KF algorithm / Simulation results.

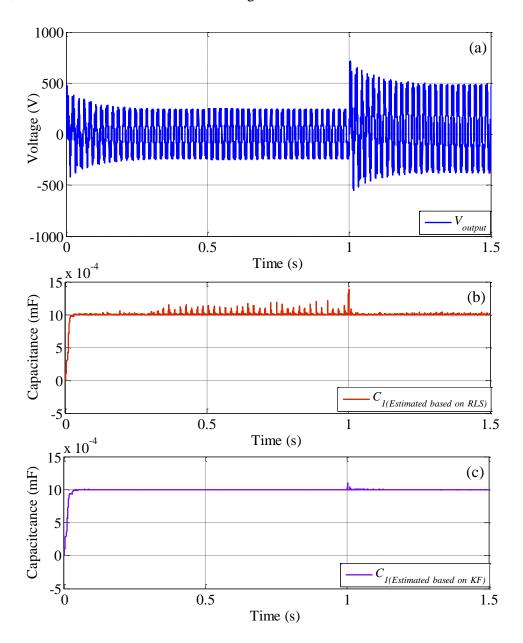

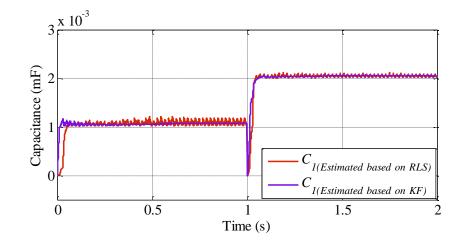

| Fig 7.6. Capacitance estimation with step change in the SM capacitance value f | rom |

|--------------------------------------------------------------------------------|-----|

| 1.0 mF to 2.0 mF / Simulation results.                                         | 144 |

# LIST OF SYMBOLS

| Ls                                 | : Arm inductor                                |  |

|------------------------------------|-----------------------------------------------|--|

| S <sub>x</sub>                     | : Switching states of an MMC SM               |  |

| $C_x$                              | : SM Capacitor                                |  |

| е                                  | : error between measured and estimated values |  |

| f                                  | : Output frequency                            |  |

| $f_c$                              | : Carrier frequency                           |  |

| $f_{sampling}$                     | : Sampling frequency                          |  |

| i <sub>cir</sub>                   | : Circulating current                         |  |

| i <sub>cir-ph</sub>                | : Circulating current of the phase            |  |

| I <sub>dc</sub>                    | : DC link current                             |  |

| i <sub>l-ph</sub>                  | : Lower phase arm current                     |  |

| i <sub>lower</sub>                 | : Lower arm current                           |  |

| i <sub>load</sub>                  | : Load current / output current               |  |

| $i_{load-ph}$ : Phase load current |                                               |  |

| i <sub>u-ph</sub>                  | : Upper phase arm current                     |  |

| i <sub>up</sub>                    | : Upper arm current                           |  |

| J <sub>u</sub>                     | : Cost function                               |  |

| λ                                  | : Forgetting factor                           |  |

| <i>K</i> : H | Kalman gain |

|--------------|-------------|

|--------------|-------------|

- *L* : Load inductance

- LS : Least Square

- *N* : Total output voltage levels

- $m_i$  : Modulation index

- *n* : Number of SM per arm

- *P* : Covariance matrix

- *r* : Number of carrier signals

- R : Load resistor

- *R* : Error covariance matrix

- Ra : Arm resistor

- *u<sub>a</sub>* : Output voltage

- **u**<sub>l</sub> : Lower arm voltage

- $u_u$  : Upper arm voltage

- $V_{dc}$  : DC-link voltage

- $\mathbf{V}_{cx}$  : Voltage across SM capacitor

- **V**<sub>SM</sub> : Voltage across SM

- *w* : Processing noise

-----

$\alpha$  : Shifted angle between carrier signals

- $\beta$  : Number of SMs to be involved.

- **θ** : Vector parameter.

#### Superscripts

- ... : Estimated value

- .... : Complementary value

# LIST OF ABBREVIATIONS

- AC : Alternating current

- ADC : Analogy to digital converter

- APOD : Alternative phase opposition disposition

- BESS : Battery energy storage system

- BMS : Battery management system

- CCS : Code Composer Studio

- CHB : Cascaded H-Bridge

- DC : Direct current

- DGs : Distributed generations

- DSP : Digital signal processor

- ERLS : Exponentially weighted recursive least square

- ESR : Equivalent series resistance

- FACTS : Flexible AC transmission systems

- FCC : Flying capacitor converter

- HVDC : High voltage direct current

- IGBT : Insulated gate bipolar transistor

- IGCT : Integrated gate commutated thyristor

- KF : Kalman filter

- MMC : Modular multilevel converter

- MOSFET : Metal-oxide semiconductor field-effect transistor

- NPC : Neutral point clamped

- PWM : Pulse width modulation

- PD : Phase disposition

- PI : Proportional integral

- POD : Opposition disposition

- RLS : Recursive least square

- RT-WEC : Real-Time Workshop Embedded Coder

- VSCs : Voltage source converters

- SM : Submodule

- SVPWM : Space-vector pulse-width modulation

- STATCOM: Static synchronous compensator

- TSP : Target Support Package

.....

## CHAPTER 1

# INTRODUCTION

#### **1.1 Voltage Source-Based Converters**

It is well known that the growth in the need for power electronic converters has been exponential due to the increased demand for medium-and high-power applications. These applications are usually operated based on voltage source converters (VSCs), which are mainly driven by medium-and high-power semiconductor devices such as the metal-oxide semiconductor field-effect transistor (MOSFET), the insulated gate bipolar transistor (IGBT) and the integrated gate commutated thyristor (IGCT). Twolevel and multilevel converters can now be found everywhere. However, as the main advantages of multilevel converters is the increase in output power level, this increase in VSC-based systems provides significant improvements over two-level VSC topologies. These include reduced filtering size and the low switching frequency required, which lead to lower switching losses. In addition, multilevel VSC topologies provide reduced semiconductor stresses due to distribution of the switching effort between the high numbers of semiconductor switches involved [1-4].

#### 1.2 Challenges Associated with Multilevel Converters

Different multilevel converter topologies have already been used in industry. One of the most attractive topologies for medium-and high-power applications is modular multilevel converter (MMC). More details as well as the most attractive features of MMCs compared to other conventional multilevel converter topologies are presented in Chapter 2.

Despite the use of multilevel topologies, each topology provides certain advantages; however, a number of challenges in their operation are also apparent, such as, reducing switching frequencies and the control of internal and output converter signals. Voltage and current control requirements are one of the most important challenges with these converters. Due to the high numbers of components which are usually involved in the multilevel converter structure, achieving such control increases overall system complexity and therefore decreases reliability. These two concerns of complexity and reliability specifically for MMCs are the main focus of this thesis.

#### 1.3 Objectives of the Thesis

The main objectives of the thesis are:

- To conduct a comprehensive study that contributes to the development of multilevel converters in general.

- To investigate the requirements and issues associated with MMCs.

- To propose novel voltage-balancing methods that can reduce the complexity and therefore the cost of the MMC when a medium or high output level of the converter is required. Usually with the conventional voltage-balancing methods, high number of sensors are needed. Therefore, the objectives of this research focus on developing new online sensorless schemes which can achieve the voltage-balancing of the converter with fewer voltage and current sensors.

- To develop a new online health condition monitoring scheme for the capacitors used in the series connected SMs which can improve MMC reliability.

- To develop a scaled down experimental set-up system that confirms the effectiveness of all proposed sensorless methods in this work.

#### **1.4 Topologies and Tools Used**

The results achieved in this work are based on detailed simulation and experimental analysis. The simulation results obtained in the thesis are provided by simulations in MATLAB/Simulink/Simpower, of which two different versions have been used (2012 © and 2015 ©). The experimental results achieved in Chapters 4, 5 and 6 are implemented using the TMS320F28335 microcontroller from the Texas Instruments semiconductor manufacturing company. The implementation of the methods proposed in those chapters are uploaded to the digital signal processor (DSP) with the help of Code Composer Studio (CCS5.5) development tools from the same supplier (Texas Instruments). A scaled down 4-level MMC is developed to validate all suggested sensorless schemes. Details of the practical implementation are presented in Chapter 3.

#### **1.5 Thesis Contributions and Publications**

The work reported in this thesis focuses on reducing the complexity of the MMC and improving its reliability under different operating conditions. The main contributions of the thesis are summarised as follows:

• Two current sensorless approaches are investigated for the converter to achieve voltage stability with lower cost and complexity (Chapter 4). In the first proposed method, monitoring load current is only required for the controller, whereas the second proposed scheme does not require any current monitor to achieve the voltage-balancing of the converter.

- A novel voltage sensorless scheme is proposed based on an exponentially weighted recursive least square (ERLS) algorithm (Chapter 5). The proposed technique is performed and evaluated at steady-state and dynamic conditions for both simulation and practical studies.

- A novel voltage sensorless approach is proposed for the converter based on the Kalman filter (KF) algorithm (Chapter 6). Employing KF with the converter is used for the first time to address the issue of the high numbers of voltage sensors required. .

- A new capacitance estimation scheme is proposed for the converter to improve system reliability.

- A comprehensive understanding is developed of the MMCs requirement and issues.

The work presented in this thesis has resulted in a number of published and submitted papers to different international conferences and journals as follows:

- O. Abushafa, M. Dahidah, S Gadoue, and David Atkinson "Submodule Voltage Estimation Scheme in Modular Multilevel Converters with Reduced Voltage Sensors Based on Kalman Filter Approach," submitted to *IEEE Transactions on Industrial Electronics*, 17-TIE-0266, 2017.

- O. Abushafa, S. Gadoue, M. Dahidah, and D. Atkinson "Capacitor Voltage Estimation Scheme with Reduced Number of Sensors for Modular Multilevel Converters" submitted to *IEEE Transactions on Emerging and Selected Topics in Power Electronics*, JESTPE-2017-09-0606.

- O. Abushafa, S. Gadoue, M. Dahidah, and D. Aktinson, "Capacitor Voltage Estimation in Modular Multilevel Converters using a Kalman Filter Algorithm," in International Conference on *Industrial Technology (ICIT), Seville, IEEE*, 2015, pp. 3016-3021.

- O. Abushafa, S. Gadoue, M. Dahidah, and D. Atkinson, "A New Scheme for Monitoring Submodule Capacitance in Modular Multilevel Converter", *in Power Electronic and Machines Drives (PEMD)*, 2016, IET, Glasgow.

- O. Abushafa, S. Gadoue, M. Dahidah, D. Atkinson, and S. Ethni, "Control Strategies for Capacitor Voltage Balancing in Modular Multilevel Converters."in the 7<sup>th</sup> International Renewable Energy Congress (*IRNC*), 2016, *IEEE*, Hammamet, pp. 1-6.

Throughout the study period, various academic awards have been received which are listed below:

- **First place** for the "Best Paper Presentation" in the Annual Research Conference 2016 (ARC-2016) at Newcastle University.

- **Third Place** for the "Best Paper" in the (ARC-2016) of Newcastle University.

- **Best Presentation** of research in the Electrical Power Group at the School of Electrical and Electronic Engineering (ARC-2015) of Newcastle University.

#### **1.6 Layout of the Thesis**

The thesis is organised in 8 chapters as follows:

Chapter 2 presents details of the MMC in terms of structure, principles of operation, modelling and control strategies needed. Greater emphasis is given to up-to-date attempts to reduce the converter's complexity. This includes achieving converter stability with fewer voltage and current sensors, and different methods are reviewed and discussed. The chapter also provides a literature review on capacitance estimation strategies.

Chapter 3 provides details of the experimental set-up used in this work. It describes selected components in the converter, including the voltage and current sensors used. In addition, it also provides a brief description of selected digital signal processors.

Following this, the procedure used for implementing all methods proposed in Chapters 4-6 is detailed.

Chapter 4 presents two current sensorless methods for the MMC. A detailed description of the conventional voltage-balancing scheme based on a sorting algorithm is discussed first in the chapter. This conventional scheme is also used in Chapters 5-7. Extensive simulation and experimental results that compare the two proposed methods with the conventional voltage-balancing method are then provided in the rest of the chapter.

Chapter 5 proposes a novel voltage-balancing method with fewer voltage sensors. An ERLS algorithm is employed in this chapter to achieve voltage-balancing with lower complexity. Simulation and experimental studies under different operating conditions are discussed along with the manner in which the proposed scheme is implemented.

Chapter 6 introduces another novel voltage-balancing method based on reducing the number of voltage sensors required. This chapter suggests the use of the KF for the converter. Similar to that in Chapter 5, the results of the scheme proposed in Chapter 6 demonstrate the effectiveness of the proposed algorithm under steady-state and dynamic operating conditions. All the obtained results are experimentally verified using the test rig described in Chapter 3.

Chapter 7 describes a new approach for capacitance estimation based on the KF algorithm. The method is compared with an existing approach based on a recursive algorithm and both methods are validated through simulation analyses.

Finally, Chapter 8 concludes the work, summarises the contributions of the study and makes some possible suggestions for future work.

# CHAPTER 2

# MODULAR MULTILEVEL CONVERTER: PRINCIPLES OF OPERATION, MODELLING & CONTROL, AND APPLICATIONS

#### **2.1 Introduction**

The importance of using power conversion is described in this part of the chapter, where the focus is mainly on the MMC. Using power converters is essential nowadays to convert power from one form into another (e.g. AC-DC, DC-AC, AC-AC or DC-DC). However, some challenges remain. The power obtained from such conversion is controlled based on the demand of the application via semiconductor switches. The power can be boosted, bucked or similar to the input level; however, the output frequency may also be different. The application attached to the converter decides this demand. In general, power converters can be found everywhere; in houses, or work, in industry, in various modes of transportation such as trains and electrical vehicle, and in hospitals.

Many studies are still being carried out to overcome the challenges associated with converters. There are many areas which still need to be improved in this regard. As a researcher with engineering background, three main areas are always under the microscope: the efficiency, cost and reliability of the targeted system. Details about these three gaps are addressed later in main body of the thesis including the rest of this chapter.

#### **2.2 Conventional Multilevel Converters**

A brief introduction to the conventional multilevel converters and their applications is provided here prior to introducing MMC topology. Three main multilevel converter topologies are well-developed and commonly used [1]. These include neutral point clamped (NPC) converter [5], cascaded H-bridge converter (CHC) [6] and flying capacitor converter (FCC) [7]. According to one review [2], these converters were first proposed more than four decades. A single phase (one-leg) illustrations of these topologies are shown in Fig. 2.2.

Other variations of multilevel converters, including hybrid and matrix configurations have been also investigated and reported in the literature (see Fig. 2.1). Examples of the Hybrid topologies is a combination between NPC and CHC or FCC and CHC [8]. The combination of two conventional or not conventional multilevel converter usually provide more features to the system. For example, the combination between NPC and CHC reduces the common mode voltage and improves power quality [9].

All aforementioned conventional technologies have been widely examined and accepted. They were introduced in the market and have been used in real applications for some time in various industrial applications for both medium and high power voltage rate [8].

Fig. 2.1. Classification of medium and high voltage multilevel converters.

Fig 2.2. Conventional multilevel converter topologies: (a) Three-level NPC converter, (b) Three-level FCC and (c) Five-level CHC.

#### 2.3 The MMC: Structure and Principles of Operation

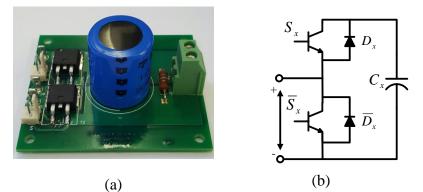

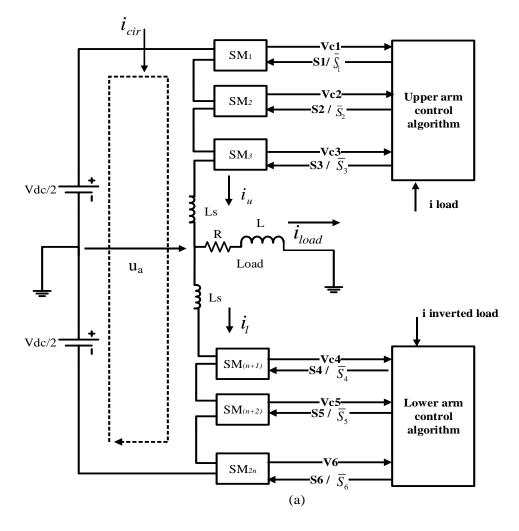

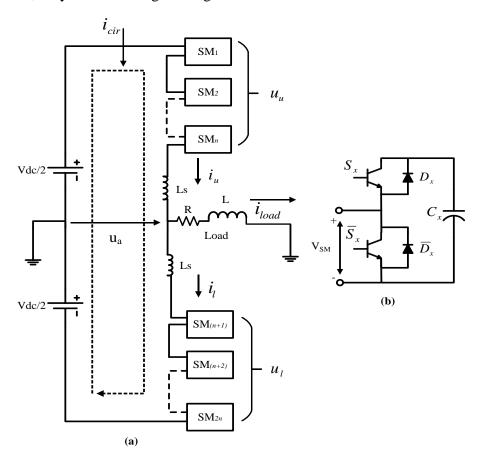

Fig. 2.3 shows the basic circuit configuration of a three-phase MMC. The converter consists of two arms; each of which has a series connection of cascaded submodules SMs and an arm inductor ( $L_s$ ). In most cases the configuration of these SMs is a half-bridge configuration as illustrated in Fig. 2.3 (b). Although the name MMC is usually related to half-bridge configurations; however, different arrangements can also be found in the literature such as full-bridge SM, three-level FCC, three-level NPC or hybrid arrangements [10]. The application will define the type of SM configuration which fits the system better [11].

Fig 2.3. Block diagram of MMC. (a) Three-phase block diagram. (b) Halfbridge SM configuration.

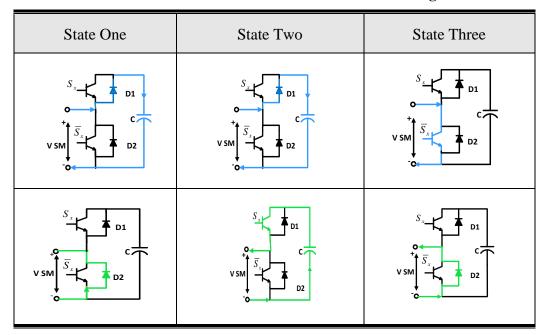

Considering the half-bridge configuration in Fig. 2.3, three switching states exist based on the status of  $S_x$  and  $\overline{S_x}$ . In state one, both  $S_x$  and  $\overline{S_x}$  are **OFF**, and this may happens during start-up or in the case of series failure [12], but this state is usually omitted during software simulation. In the second state,  $S_x$  is switched **ON** and  $\overline{S_x}$ remains **OFF**, the output voltage is equal to the voltage across the capacitor  $C_x$  ( $V_{cx}$ ), where x = 1,2,..., 2n, and n is the number of SMs per arm. The charging and discharging of the SM capacitor depends on the direction of the current passing through this SM, and this state is known as the ON state [13]. In state three, the SM voltage output is zero (OFF state), and this occurred when  $\overline{S_x}$  is ON and  $S_x$  is OFF.

For clarity purpose, the directions of the current flowing through both diodes and semiconductor switches in the three states are depicted in table 2.1, whereas, table 2.2 shows the only two main switching states during normal operating conditions [12] [14].

The buffer inductors ( $L_s$ ) in Fig. 2.3 have an important role in the operation of MMC. They not only assist in reducing the circulating current within the converter arms [15], but they also support the system when faults occur [16].

Total arm resistance (Ra) shown in the figure are usually omitted in the converter model; however, for the sake of accuracy, this small resistor should be added to the overall mathematical model.

Table 2.1. Current flow directions in the half bridge SM

Table 2.2. Switching signals and the output states of the SM

| State of the SM | <i>S</i> <sub>x</sub> | $\overline{S_{\mathrm{x}}}$ | Vsm                    |

|-----------------|-----------------------|-----------------------------|------------------------|

| ON              | ON                    | OFF                         | <b>V</b> <sub>cx</sub> |

| Off (bypassed)  | OFF                   | ON                          | 0                      |

#### 2.4 Currents Analysis in MMC

As the operation of MMC relies on the different currents following through the circuit, it is therefore essential to understand these currents in order to fully understand the operation of converter. Fig. 2.3 illustrates the directions of currents in the MMC, which are: output current  $(i_{load})$ , DC link current  $(I_{dc})$ , arms currents  $(i_{up})$  and  $(i_{lower})$  and circulating current  $(i_{cir})$ . These are defined in more details in the following paragraphs.

#### 2.4.1 Output and Arm Currents

The output current  $(i_{load-ph})$  can be calculated by subtracting the lower arm current from the upper arm current within the same phase, thus  $i_{load-ph}$  is defined as [17]:

$$\mathbf{i}_{load-ph} = \mathbf{i}_{u-ph} - \mathbf{i}_{l-ph} \text{ where } ph = a, b \text{ or } c$$

(2.1)

where the upper  $(i_{u-ph})$  and lower  $(i_{l-ph})$  arm currents are defined by equations (2.2) and (2.3) respectively:

$$i_{u-ph} = i_{cir-ph} + \frac{i_{load-ph}}{2}$$

(2.2)

$$\mathbf{i}_{l-ph} = \mathbf{i}_{cir-ph} - \frac{\mathbf{i}_{load-ph}}{2}$$

(2.3)

#### 2.4.2 The Circulating Current

By substituting  $i_{load-ph}$  in equation (2.1) into (2.2) or (2.3) the definition of circulating current can then be defined as:

$$i_{cir-ph} = \frac{i_{u-ph}+i_{l-ph}}{2}$$

(2.4)

This current is one of the main challenges in the MMC circuit, and many studies have investigated different means to supress or minimise it. Large circulating current can seriously influence the semiconductor components, increases losses and leads high voltage ripple in the SM capacitors [18].

#### 2.5 The MMC Output Voltage

As shown in Fig. 2. 3(a), the output voltage of phase-leg a of the converter  $(u_a)$  can be expressed as follows [19]:

$$\boldsymbol{u}_{a} = \frac{\boldsymbol{u}_{l} - \boldsymbol{u}_{u}}{2} - \frac{\boldsymbol{L}_{s}}{2} \frac{d\boldsymbol{i}_{load-ph}}{dt}$$

(2.5)

where  $u_u$  is the total output voltage of the upper cascaded SM<sub>S</sub> (from 1 to *n*) and  $u_l$  is the total output voltage of the lower cascaded SM<sub>S</sub> (from (n + 1) to 2n).

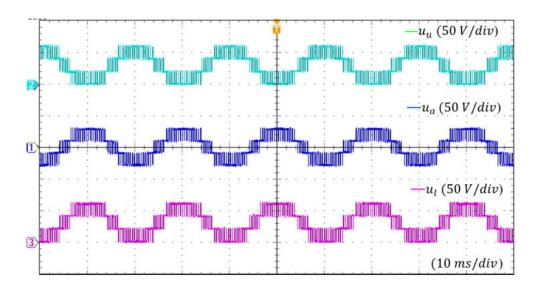

The total output voltage levels (N) that can be achieved using this multilevel topology is N = (1 + n) (line-neutral), where n is the number of SM per arm. Higher output levels can be achieved up to 2n + 1, where the arms of the same phase are modulated independently [20]. More information about increasing output level is presented in Chapter 4.

#### 2.6 Features Associated with the MMC Topology

Due to the modular construction of the MMC in comparison with two, three and some conventional multilevel VSC converters, the MMC topology has the following features [12, 21, 22]:

- Low harmonics can be achieved in the output voltage and current waveforms because of the series connection of high number of SMs.

- Reduced size (or even no) of filtering circuit.

- Generally, the MMC has low switching losses due to the low switching frequency required.

- Due to the fact that each SM has its own DC capacitor, the DC linked capacitor can be neglected [22]. Consequently, this will decrease the total cost of the converter connection as well as improving its performance and reliability in the case the appearance of faults [16]. As is known, the presence of a DC

capacitor will cause a high surge current plus consequent damage to the system, particularly when a fault at the DC bus side is not prevented [22].

- In a DC link when a pole-to-pole fault occurs, the total system stability can be recovered quickly because only a few sub-module capacitors are discharged.

- Arm inductance does not have any side-effects on the systems operation. On the contrary, it supports system stability.

- Similar to the CHC converter, it has scalability and flexibility by adding identical SM cells.

- Fault tolerant feature (i.e. in the case of a sudden fault occurring in one of the SMs, the other residual SMs can manage system stability without switching off the whole leg (phase) when an appropriate control method is used. Only unhealthy cells should be bypassed).

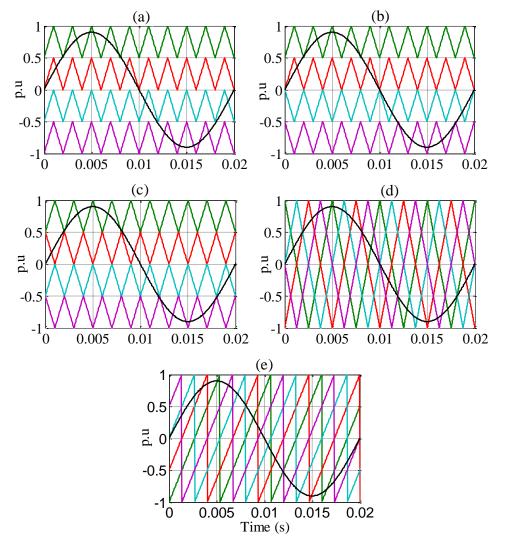

#### 2.7 MMC Modulation Strategies

This section reviews the most commonly used up-to-date modulation strategies for controlling voltage capacitors (voltage-balancing control) in MMCs. Over the last few years, different modulation strategies have been developed and investigated for MMCs. Regardless of the applications, Fig. 2.4 classifies these methods into two main groups: space vector-based algorithms and voltage level-based algorithms. The range of switching frequency has also been taken into consideration in this categorisation. To date, very few studies control the MMC based on the space-vector algorithm [23], whereas the majority of recent studies are based on voltage level-based algorithms as can be seen in the figure. Although multicarrier pulse width modulation (PWM)-based algorithms are classified as high switching frequency algorithms, most of the recent literature still consider them. This is mainly because of their ease of implementation when a sorting algorithm is used. However, several attempts have been reported to achieve successful voltage-balancing with lower switching frequency when the multicarrier PWM-based algorithm is used. For example, an improved phase-shifted-

based algorithm has been proposed for the hybrid MMC [24].

Fig. 2.4. MMC Modulation Strategies.

#### 2.8 Challenges Associated with the MMC

Despite the attractive features of the MMC which have been mentioned in section 2.6, there are some challenges associated with this kind of multilevel converters, especially if a high output level is required. Therefore, maintaining the voltage-balancing control of the capacitors' voltage requires many voltage sensors due to the use of high number of semiconductor devices and SM capacitors, which in turns increases the cost and the complexity of the system.

Another considerable challenge is the reliability of the converter. This is mainly because of the series connection of such components (i.e. semiconductor switches and SM capacitors). In addition to voltage-balancing control, the circulating current which appears within the converter's leg is another challenge (i.e. current control issue). This current influences the level of voltage ripple within the SM capacitors. The main challenges associated with MMCs are surmised below:

- Voltage control (voltage-balancing of SM capacitor voltages)

- Current control (circulating current within the converter legs which may effect on the SM voltage ripple).

- Reliability and complexity due to the series connection of high number of SMs.

- Parameter design (mainly for SM capacitance  $C_x$  and arm inductance  $L_s$ )

There have been great efforts put by the researchers towards addressing the voltage and current control issues. Three main control objectives for the MMC are widely considered in the literature, which are input current, output voltage and output current [34]. In this study, only the output voltage issue is investigated, aiming to achieve capacitor voltage-balancing with fewer voltage and current sensors. Whereas the issue of inner circulating current within each phase is beyond the scope of this study.

#### 2.9 Control of SM Capacitor Voltage with Voltage and Current Sensors

The majority of the existing solutions for voltage-balancing rely on monitoring each individual SMs voltage and arm current. However, due to the fact that MMCs are usually designed with high output levels, this means high numbers of voltage sensors are also required. For example the commissioned MMC converter presented in [35] utilizes hundreds of SMs per arm, which requires enormous numbers of voltage sensors in order to achieve the voltage-balancing of the SMs capacitors. The control of SM capacitor voltage with voltage and current sensors has been extensively investigated in recent research [27, 28, 30, 36, 37], but many voltage sensors are always used in such studies. However, it would be preferable if this issue could be resolved with lower cost and complexity.

#### 2.9.1 Averaging and Balancing Control Method

This method has been presented in [28], where two steps were used to regulate the converter's voltages: averaging control and balancing control. Both steps are based upon a simple proportional integral (PI) controller. In the averaging step, the average voltage arm is forced to follow its command value. An inner current loop is also included in this step so that the averaging voltage follows its command voltage without being affected by the converter load. However, a higher number of sensors still needed for measuring and monitoring all SM capacitors. Another disadvantage associated with this method is that, when the structure of the MMC is being changed, such as when the output level is increased, the parameters of the controller must be retuned again. In addition, in the case of a fault, when one SM is being bypassed, the proportional and integral gains of the PI controller need to be readjusted.

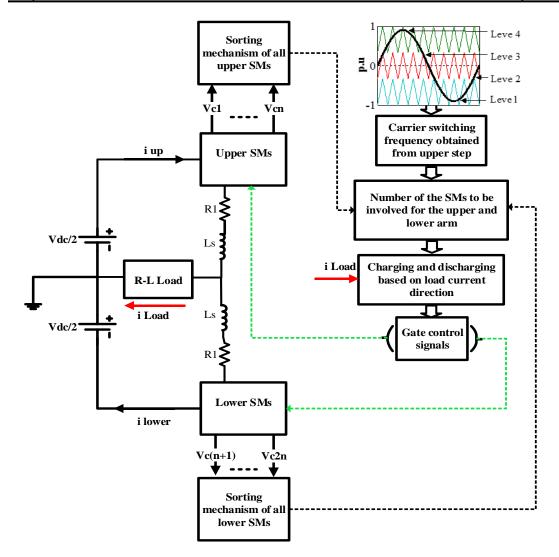

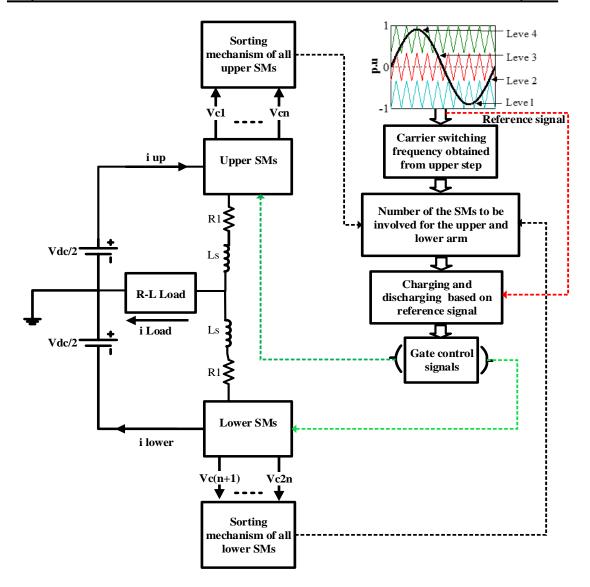

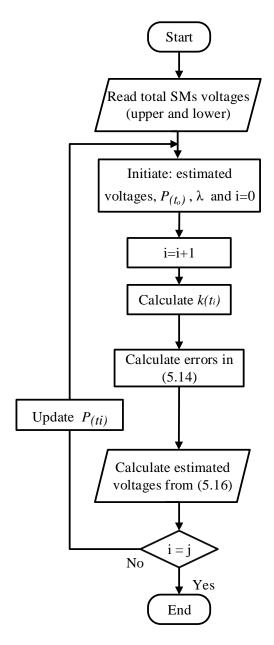

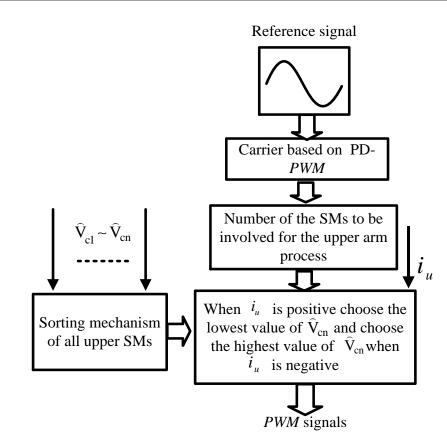

#### 2.9.2 Sorting Algorithm-based Method

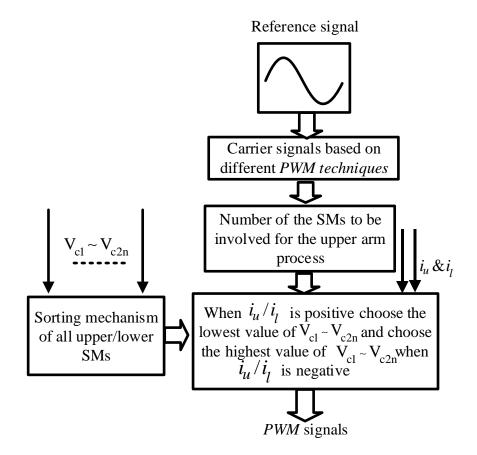

Regardless to the modulation strategies used, such as those illustrated in Fig. 2.4, the idea of a sorting algorithm-based method is to sort all arm SM voltages in descending/ascending order [31]. This means monitoring all SMs' voltages are required. In the Figure bellow the main requirement steps of achieving voltagebalancing control are shown. By considering the upper arm, the lowest capacitors will be charged when the upper current is positive and their values will be increased. However, if the upper current is negative, the capacitors with the highest value will be discharged. The number of capacitors that should be involved in the process is also defined by the algorithm. On the other side of the converter, the lower control algorithm works exactly in the same way. However, charging or discharging actions in the lower part of the converter depend on the direction of the lower arm current rather than the upper arm current. Similarly, the lowest capacitors will be charged when the lower current is positive and their values increases. Conversely, if the lower current is negative, the capacitors with the highest value will be discharged [31]. In terms of the computational complexity, this method does not require high execution time, however and similar to averaging and balancing control method, complexity might be an issue due to high measurement signals involved in the process. More details on this principle are explained in Chapter 4.

Fig 2.5. Block diagram of voltage-balancing control based on sorting algorithm scheme.

#### 2.10 Control of SM Capacitor Voltage with Fewer Sensors

While most of the reported literature is sensor-based methods, however there have been few attempts to reduce the number of the voltage and current sensors. The following sub-sections classify the up-to-date proposed methods into four main groups.

#### 2.10.1 Sorting Algorithm Methods with Fewer Current Sensors

Reducing the number of required current sensors has been recently considered by few researchers. For instance, in two recent studies [29] and [38], different methods

are introduced and demonstrated with both simulation and practical results. High frequency current components have been analyzed and controlled for the SM capacitors under different operating conditions [29]. Alternatively, the switching frequency of the semiconductor switch has been controlled and minimized [38]. The limitation of these methods is that only PS-PWM modulation technique can be used to control the converter. However, in comparison with the conventional sorting algorithm, arm currents are not required in achieving the voltage-balancing of the system.

In more recent study [23], another attempt to control SM voltage with fewer current sensors has been proposed, where a different modulation strategy was employed to the converter based on a dual space-vector pulse-width modulation (SVPWM) technique. In comparison with [29] and [38], the number of current sensor required for the MMC is one per phase, whilst the other two methods don't require any. Whereas, all methods including SVPWM-based technique are based on voltage sorting mechanism.

#### 2.10.2 Observer-based Methods

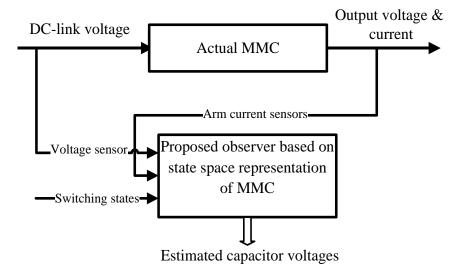

Observer-based schemes are based on estimating capacitor voltages by monitoring only input and output signals, where usually the DC-link voltage and arm currents are required. Fig. 2.6 shows a general block diagram of the observer-based methods. Thus, to design such a sensorless control scheme, it is necessary to investigate the observability of the converter [39]. It has been reported that the MMC is observable when the switch at the targeted state is on [40]. In one recent study [40], the proposed observer is employed for the MMC as a fault detection scheme where the algorithm used is based on a sliding mode observer. The sliding mode observer has also been proposed for the CHC [41, 42]. Although it is known that the slide mode-based algorithm is robust against parameter uncertainty in the system equations, however, capacitance uncertainty in the SM has not been investigated neither in [40] nor in [42]. It is important to validate the converter with such deviations representing capacitance uncertainty, especially when the application requires high voltage levels. In another recent study, a KF-based observer has also been proposed for the MMC [43]. One important feature of the KF approach is the ability of the algorithm to cope with both

#### Fig 2.6. General block diagram of the observe-based method

An improvement to the latter research [40] involves the estimation of the capacitance value as well as the capacitor voltage of the SM capacitors was subsequently proposed in [44]. Although this improves the robustness of the system against capacitance uncertainty, however, the effect of the variation associated with the arm inductance value was not considered in the observer design. On the other hand, the authors in the same study [44] have proved that the converter can perform well with up to +10% of the nominal arm inductor value. However, it can be summarised that, none of the observer-based methods consider arm inductance variation in the design analysis.

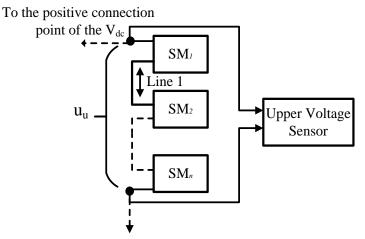

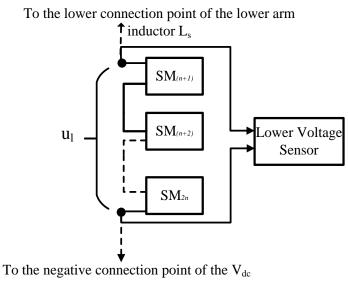

#### 2.10.3 Sorting Algorithm Methods with Fewer Voltage Sensors

In this group of methods and the observer-based methods have just mentioned above, a sorting algorithm is commonly used to control the voltages of SM capacitors. However, the technique presented here is based on measuring the total arm voltages rather than the DC-link voltage. On the other hand, similar to the observer-based methods, arm currents are also considered in the design. A majority of the recent proposed methods [45-47], the estimation techniques used are based on prediction and correction stages. In the prediction stage, an initial estimation from the straightforward relationship (see equation (2.6)) between the capacitor current and voltage along with the capacitance value are used as follows:

$$\mathbf{V}_{c1}(t) = \frac{1}{c_1} \int_{t_0}^t I(t) S_n(t) \, d(t) + \mathbf{V}_{c1}(t) \tag{2.6}$$

One critical issue with this step is the accumulated error caused by the integrator effect in equation (2.6). In [45], the error between the actual and the estimated arm voltages has been found to be divided equally between the number of inserted SM. This error is then used to correct each estimated voltage.

In more recent research [46, 47], the voltage-balancing of a seven-level MMC has been achieved with important reductions in the number of voltage sensors required, where the lowest number of voltage sensors needed are two when 7-level MMC is used. Two sensors contribute to measuring the total arm voltage of the converter. The increase in the number of arm voltage sensors required in these studies reduces the error in the individual SM capacitor estimation voltage. On the other hand, the main concern with these methods is that an advanced voltage-balancing method must be incorporated to guarantee stability. In addition, if the MMC level is higher than 7, more voltage sensors per arm are needed.

#### 2.10.4 Open-loop Control Methods

Different attempts based on open-loop schemes have been suggested, where fixed PWM signals have been applied to the converter switches [48, 49]. Although these proposed schemes do not use any sensors, since they do not require any form of feedback control, the well-known limitations of open-loop control schemes may threaten the performance of the system with such control scheme.

#### 2.11 Capacitance Estimation

As shown earlier in section 2.8, reliability in the MMC is considered as another important issue. Faults in any MMC components may cause serious problems. It is

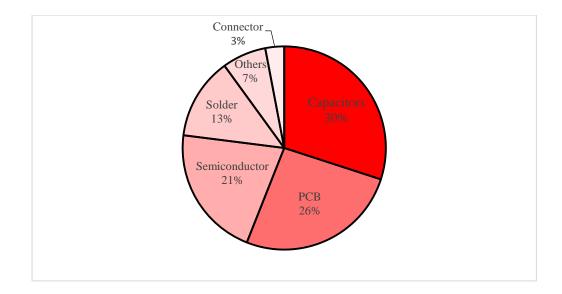

known that the failure rates in power electronic components are usually caused by six main factors as illustrated by Fig. 2.7. It is well known also that the passive components, such as the electrolytic capacitor, will gradually deteriorate with time [50]. As a result, the performance of the capacitor decreases due to changes in its internal equivalent series resistance (ESR) [51]. It is therefore clear that passive components such as capacitors cause the highest number of potential failures, as reported from several surveys from various companies [52]. However, for the MMC, not many studies so far have investigated the capacitance estimation, and only two recent studies have dealt with this issue [44] [53]. For that reason, such issue should be further investigated as well. For example, the capacitance estimation has been used as a part of an observer-based method to estimate the SM capacitor voltage [44]. The estimation of SM capacitance is used to improve the performance of the proposed sensorless scheme. Whereas in another study [53], the RLS algorithm was proposed to estimate the SM capacitance of the converter.

Fig. 2.7. Percentages of failure rates in power electronic devices.

#### 2.12 MMC Applications

Multilevel converters have gained great attention in medium and high power applications due to their distinctive features, especially the modularity and the high quality of the output waveforms [5, 6]. Usually, these converters employ selfcommutated semiconductor switching devices such as IGBTs, IGCTs, etc. These selfcommutated converters bring significant improvement to the utility in many aspects such as reactive power support, power factor correction, harmonic compensation and most importantly reduced filtering requirement [54].

Nowadays, multilevel converters are used in many different applications; for instance, pumps, gas turbine starters, reactive power compensation, submarine, compressors, fans, wind turbines, storage device conversion, mixers and high voltage direct current (HVDC) [55]. The following paragraphs mainly focus on the applications of MMCs, which in Fig. 2.8 are classified into three main application areas.

#### 2.12.1 Energy Generation

Due to the high power involved in the conventional and renewable power generation, it is important to use a high quality of power conversion with high capability [56]. Whereas, and owing to the high demand for having clean power sources, such as photovoltaic generation, fuel cells and wind turbine, the numbers of distributed generations (DGs) have significantly increased. Therefore, more multilevel power converters would be needed in order to convert the energy from these sources for the network. The MMC, for example, has been suggested as a DC-DC converter to boost power before connecting the resource to the grid [57-62]. In some other studies, the MMC has also proven to work as a buck converter [57, 63]. Furthermore, the double star bridge cell (based on full-bridge) configuration is capable of tolerating a high range of voltage deviations in the DC-link voltage, due to its greater ability to buck and boost the DC-link voltage in both rectification and inversion sides. Therefore, the MMC with a full-bridge configuration is appropriate for renewable resources such as solar and wind power, where weather conditions always vary, which means that the DC-link input voltage will be affected.

#### 2.12.2 Transmission, Supporting Network and Distribution Systems

Examples of the use of multilevel converters in transmission systems are the HVDC, the static synchronous compensator (STATCOM), active filters and flexible AC transmission systems (FACTS) [64].

One of the most promising applications based on the MMC is HVDC [15, 65-69]. For instance, double star chopper cell based on half-bridge configuration is suitable for HVDC and back-to-back systems [15]. A good and real example of employing MMC into the network is now allocated in a project called "Trans Bay Cable", the converter consists of 200 SMs per phase [70]. For transmitting 400 MVA rated power in that project, 600 SMs are required for each terminal converter.

It is well known that power supply companies have the responsibility to deliver a high power quality to the end terminal networks. In this final stage of delivering power to consumers, power electronic conversion plays a key role. Another promising application of MMC usage is the battery energy storage system (BESS) which can be connected to support a weak grid before delivering power to customers [15].

#### 2.12.3 End-User and Stand Alone Usage Areas

Meanwhile, it is assumed to have a good power quality at this stage of delivering power to costumer; however, and regardless to power quality received, connecting any application including stand-alone to the grid, needs a suitable power electronic converter [71]. MMCs have also been proven to be suitable for different applications in this usage area. In [72] for example, the MMC has been employed for electrical vehicle where the traditional battery management system (BMS) of electric vehicles is replaced by the control of the MMC. The proposed topology integrates the BMS in the system, without the necessity for more balancing circuits. Another usage of MMC in medium power application has been proposed where an induction motor drive with two different configurations has been investigated [73]. Other promising applications based on drives is also been proven for the MMC [72-75].

Examples of the most promising application of the MMCs based on the area of usage are illustrated in the figure below:

Fig 2.8. Classify MMC applications.

### 2.13 Chapter Summary

The importance of power conversion has been explained first in this chapter. Most common circuit topologies of multilevel converters with a focus on the MMC circuit configuration and principles of operation, have been demonstrated. Mathematical representations of converter's voltage and currents have also been stated.

In addition, Chapter 2 has described the most commonly used voltage-balancing control methods. A classification of these control methods has also been provided as well as the PWM techniques used. The speed of switching frequency used in the most well-known existing control methods was also considered. The focus in this classification was based on achieving voltage-balancing with fewer sensors, where four different groups of methods have been reviewed. In addition, as another challenge facing MMCs, the capacitance estimation of the converter's SMs has been briefly reviewed.

The chapter has also provided and classified the most attractive applications for MMCs. The advantages and challenges associated with MMCs among other conventional multilevel converters have also been presented.

Next chapter focuses on the experimental set-up system. In addition to the implementation requirement, it also describes most of the selected components in the converter.

## CHAPTER 3

# THE EXPERIMENTAL SET-UP SYSTEM

#### **3.1 Introduction**

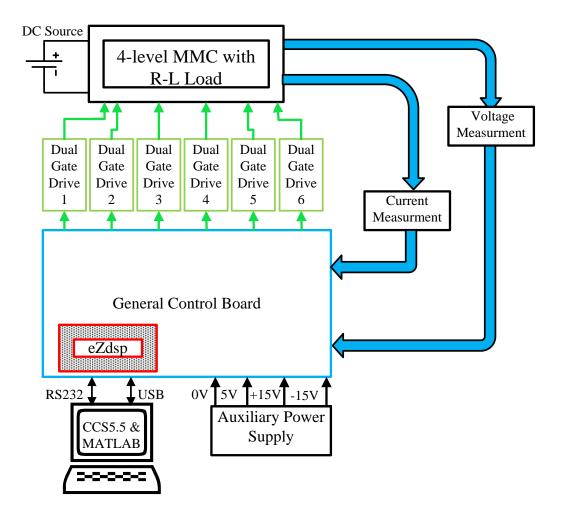

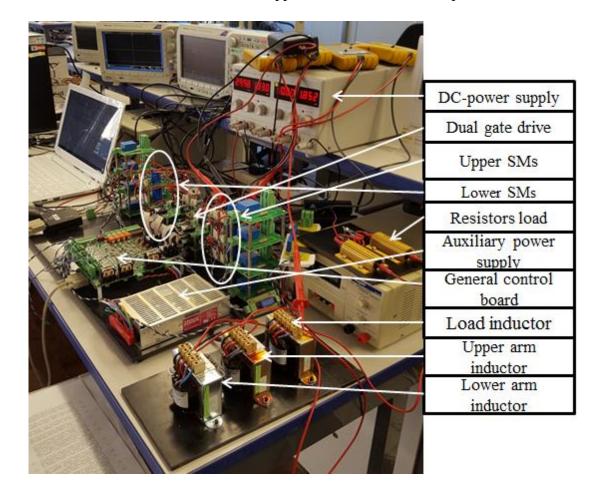

To practically evaluate and validate the proposed schemes in this thesis, an implementation in real time is required. A test rig has been developed specifically for this project. However some potential future works have also been considered in the design. Compared to the simulation studies, a scaled-down system is used here; however, the circuit was initially designed for 800W operation. This mainly involves a single-phase 4-level MMC with a dynamic load, DC power supply, number of voltage and current sensors, interphase circuits, dual gate drives and control board. A general block diagram of the whole experimental set-up system is illustrated in Fig. 3.1. Some of these components mentioned above are described in more details in the following sections.

#### 3.2 The 4-Level Single-Phase MMC and R-L Load

Three SMs and two inductors ( $L_s$ ) per arm are used in the design. An IRF530N power MOSFET is used to construct the converter's SMs. More information about the MOSFET used in this project is detailed in the datasheet. The half-bridge SM capacitor

used as demonstrated in Fig. 3.2 is the VISHAY 56 1000 $\mu F$  63 V DC with  $\pm$  20% tolerance.

Fig 3.1. Block diagram of the experimental set-up.

Fig 3.2. Half-bridge SM configuration. (a) A photograph of the SM. (b) Schematic diagram of the SM.

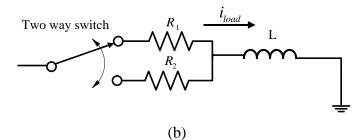

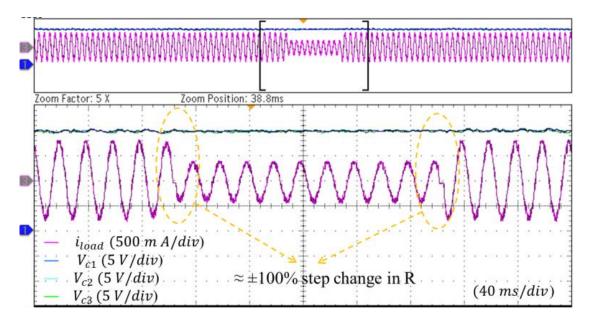

A dynamic load is attached to the converter to test the performance of the proposed methods during different load conditions. As shown in Fig. 3.3, two parallel resistors  $(R_1 \text{ and } R_2)$  and a tapped inductor are connected to the output of the converter. Two cases are considered in most studies:

- In the normal operation (case one),  $R_1$  is connected in series with the load inductor (L) where  $R_1 = 33 \Omega$  and L = 4 mH while  $R_2$  (68  $\Omega$ ) is disconnected.

- In case two, two actions have been considered in order to further validate the proposed methods against step changes in the load. Firstly, a sudden change from  $R_1$  to  $R_2$  is applied whilst *L* is still connected in series. The load current  $(i_{load})$  is decreased by around 100%. Secondly, another sudden change from  $R_2$  to  $R_1$  is applied where the current is approximately doubled to reach its original value. A manual two-way switch is used to alternate between  $R_1$  and  $R_2$  as shown in Fig. 3.3.

(a)

Fig 3.3. Dynamic R-L load configuration. (a) Photograph of the experimental load. (b) Schematic diagram of the load.

#### 3.3 Microprocessor Control System

To control the 4-level single-phase MMC described earlier, a TMS320F28335 floating point microcontroller is used. The TMS320F28335 is a member of the Texas Instruments C2000 family. In comparison to the fixed point microcontroller from the same supplier (Texas Instruments), the TMS320F28335-based floating point microcontroller offers about 50 percent more in the overall performance [76].

In order to implement and evaluate the proposed estimation schemes and the voltage-balancing algorithm using the TMS320F28335 microcontroller, Code Composer Studio (CCS5.5) development tools from Texas Instruments is used on the host ControlDesk (laptop) to generate the C-code. This was achieved with the help of the MATLAB/Simulink package, where the Simulink Embedded Target Support Package (TSP) and Real-Time Workshop Embedded Coder (RT-WEC) are employed. These tools provide a number of useful features, such as a quick and easy way to generate C-code, and the implementation and evaluation of proposed control schemes in a real-time environment. An External MATLAB mode is also used, where the data inside the DSP can be accessed in real-time processing. This feature (i.e. External MATLAB mode) provides the ability to tune some adjustable parameters in the developed algorithms when the converter is processing in real-time. However, for most of the proposed methods, off-line tuning was achieved first, and consequently the real-time tuning is then accomplished. This technique helps in avoiding the use of any inappropriate parameter values which might damage the circuit.

The execution time of the proposed voltage estimation methods was approximately  $34\mu s$ , this may lead to the use of a faster and more powerful processor when higher output voltage levels are needed especially for three phase applications. However, for the investigated current sensorless schemes, the execution time was low for all investigated schemes. It should also be noted that most of the MMCs applications are three phase based systems. In other words, microprocessors with parallel processing capabilities must be used for such applications (i.e. three phase with high output voltage levels) to guarantee an appropriate processing time. This condition is only for the proposed voltage sensorless schemes. Nevertheless, FPGA boards for example are

a very attractive and cost-effective alternative parallel processing which may reduce computation time by processing independent calculation concurrently.

#### 3.4 Hardware Implementation and Microprocessor Setting

The converter is fed with an EX354RT TRIPLE 300W power supply, where the input DC volt is 60V for most of the experimental tests. A photograph of the whole experimental test bench system is illustrated in Fig. 3.4. Other details of the hardware implementation system, including converter parameters, are summarized in table 3.1.

Eleven analogue input signals from the test rig are processed inside the controller; three of which are current signals and eight voltage signals. The sampling frequency ( $f_{sampling}$ ) which was used for all experimental tests are  $f_{sampling} = 20$ kH. Three CAS-15 current sensors are used to monitor the upper and lower arm and output currents

Fig 3.4. Photograph of the experimental test bench.

of the converter, while six LV25-P voltage sensors are used to monitor the SM voltages in order to evaluate the estimated voltages against their measured values. Although the three current sensors are not used for some sensorless current methods; these sensors are still required for the evaluation and comparison investigation with sensor-based current method. Another two voltage sensors are also used to measure the upper and lower arm voltages. These two voltage sensors (AD215AY isolation amplifier) are necessary for the proposed voltage estimation methods to estimate the six SM voltages of the converter.

The CAS-15 sensors require a +5V supply whilst the LV25-P voltage sensors require  $\pm$  15V supplies (see Fig. 3.1). Owing to the limited range of the analogy to digital converter (ADC) input channels of the controller, extra interphase circuits (e.g. voltage divider circuit) are implemented to the general control board to be compatible with the limited 0-3V range of the ADC input channels. The built-in ADCs sample the input current and voltage signals. The sampled data is then executed according to the software control algorithms.

| Parameter                             | Value              |

|---------------------------------------|--------------------|

| SM capacitor (C)                      | $1000 \mu\text{F}$ |

| Modulation index $(m_i)$              | 0.9                |

| DC-link voltage $(V_{dc})$            | 60V                |

| Output frequency $(f)$                | 50 Hz              |

| Carrier frequency ( $f_c$ )           | 2.5 kHz            |

| Number of SM per leg ( <i>N</i> )     | 6                  |

| Load resistor (R)                     | 33 Ω               |

| Arm inductor ( $L_s$ )                | 1 mH               |

| Load inductor (L)                     | 4 mH               |

| Sampling frequency ( $f_{sampling}$ ) | 20 kHz             |

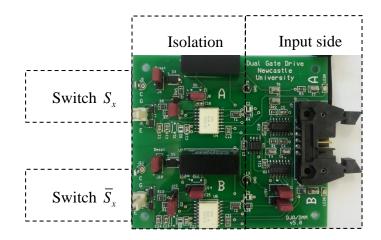

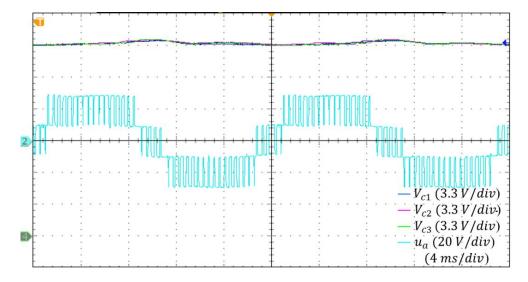

Fig 3.5. Dual gate drive.

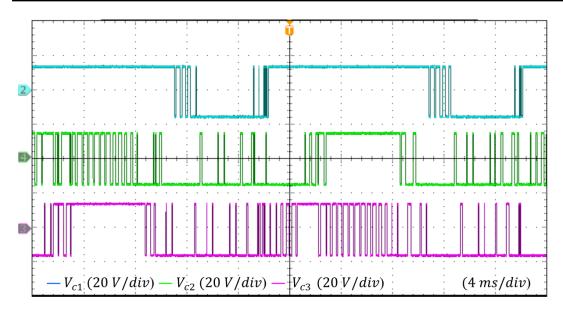

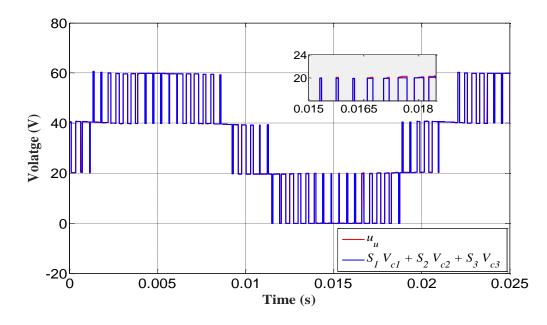

The output of the controller provides the *PWM* signals for the 4-level MMC. Due to the feature associated with the TMS320F28335, where the processor can generate 6 dual *PWM* signals, 6 dual gate drive boards are used for the converter (see Fig. 3.5). The design of these boards is beyond the scope of the present research. Each *PWM* signal within the same couple (i.e.  $PWM_x$  and  $\overline{PWM}_x$ ) is generated so as to be complementary to the other. All of these signals are switched at the switching frequency obtained for the voltage-balancing algorithm where the reference carrier signals are 2.5 kHz. The dead-time between  $PWM_x$  and  $\overline{PWM}_x$  is set at 3µs. The *PWM* signals generated are then passed through the input side of the dual gate drive, as shown in Fig 3.5. Random samples of the switching signals after balancing voltages across  $C_1$ ,  $C_2$  and  $C_3$  for the three upper arm switches ( $PWM_1$ ,  $PWM_2$  and  $PWM_3$ ) are shown in Fig. 3.6. The converter is then controlled with such signals.

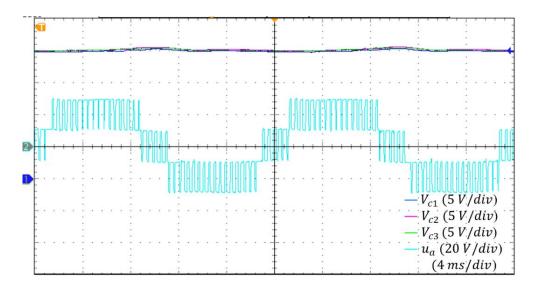

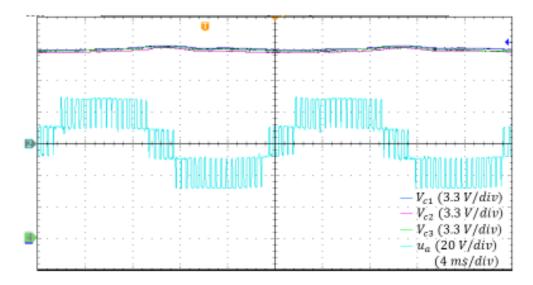

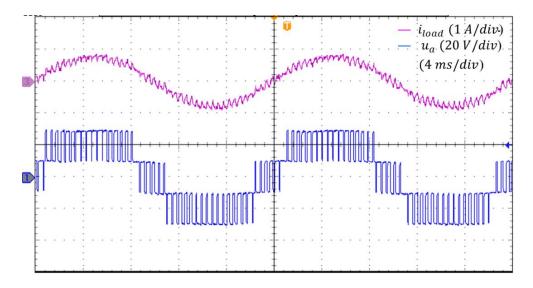

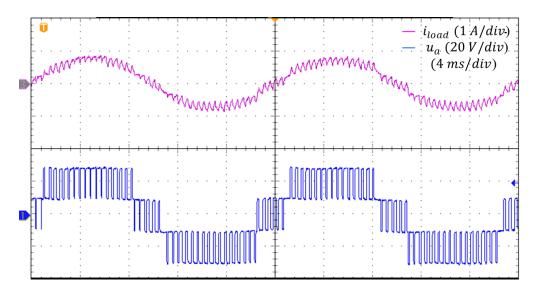

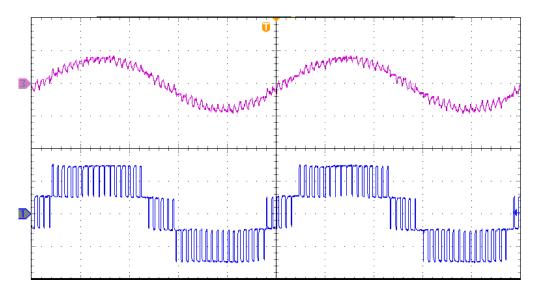

Fig 3.6. Sample of the three upper arm switches (*PWM*<sub>1</sub>, *PWM*<sub>2</sub> and *PWM*<sub>3</sub>).

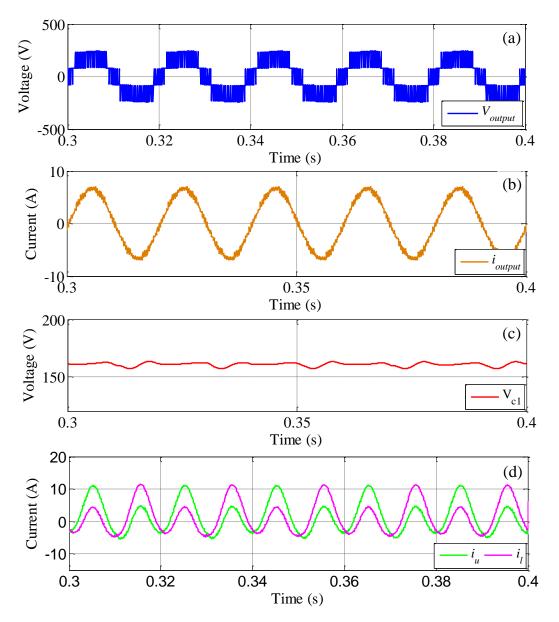

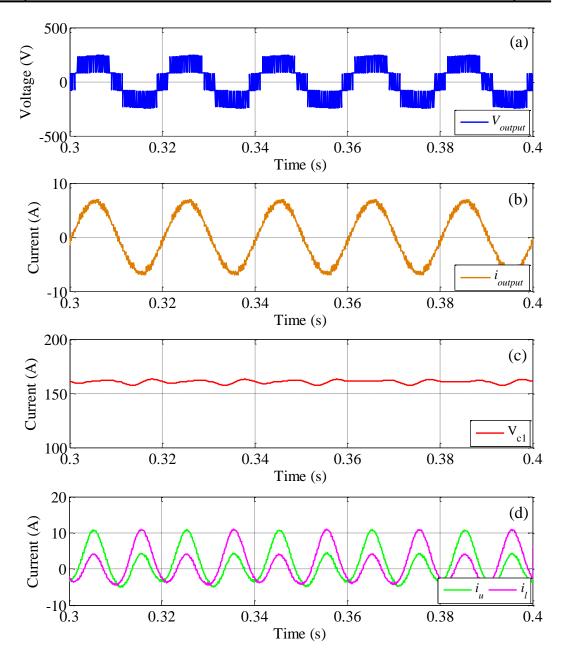

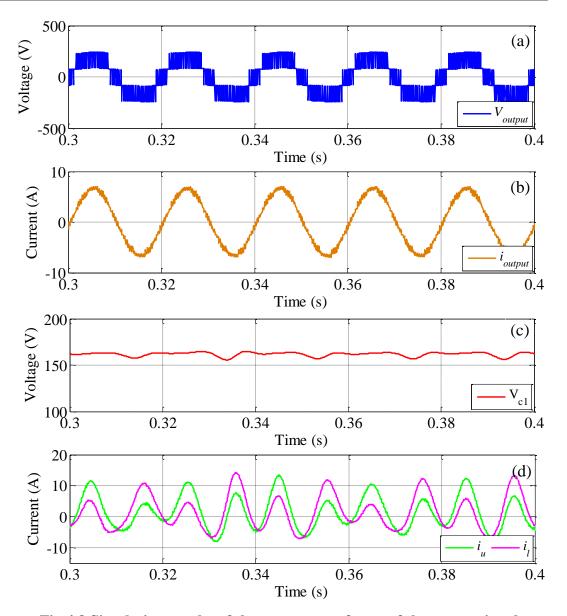

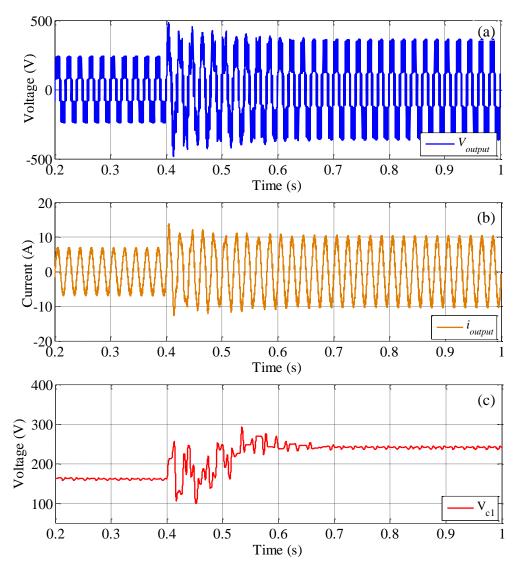

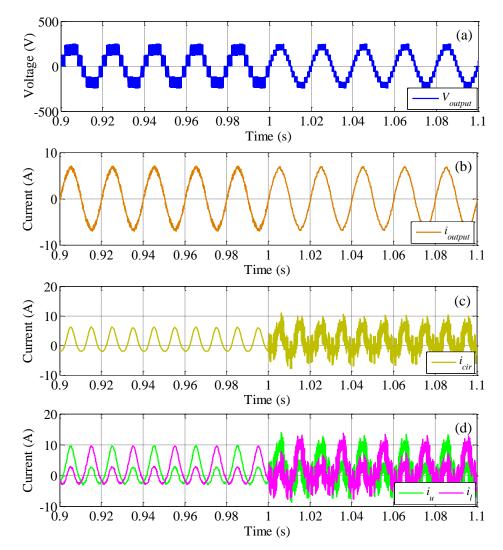

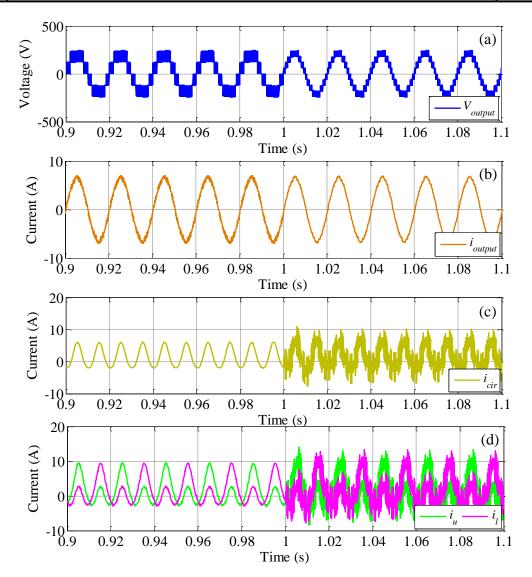

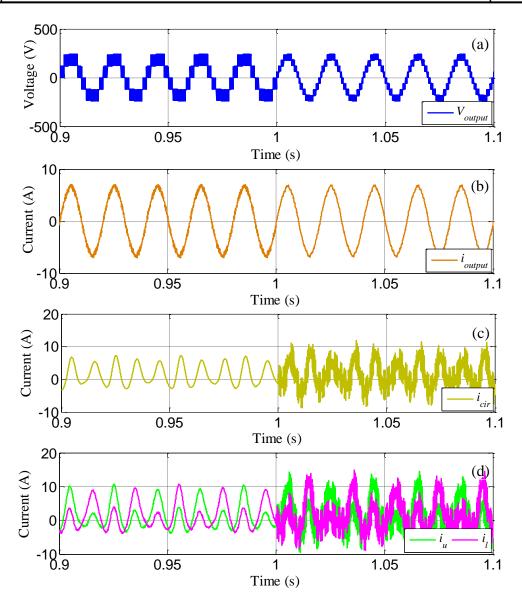

#### 3.5 Chapter Summary