# NON-INVASIVE POWER GATING TECHNIQUES FOR BURSTY COMPUTATION WORKLOADS USING MICRO-ELECTRO-MECHANICAL RELAYS

Haider M. Alrudainy

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University

School of Electrical and Electronic Engineering Faculty of Science, Agriculture and Engineering July 2017 Haider Alrudainy: Non-Invasive Power Gating Techniques for Bursty Computation workloads Using Micro-Electro-Mechanical Relays ©2017

## DECLARATION

| I hereby declare that this thesis is my<br>has not been submitted anywhere for<br>of information have been used, they l | any award. Where other sources |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Newcastle upon Tyne July 2017                                                                                           |                                |

|                                                                                                                         |                                |

|                                                                                                                         | Haider Alrudainy               |

|                                                                                                                         |                                |

# CERTIFICATE OF APPROVAL

| I confirm that, to the best of my knowledge, this thesis is from the |

|----------------------------------------------------------------------|

| student's own work and effort, and all other sources of information  |

| used have been acknowledged. This thesis has been submitted with     |

| my approval.                                                         |

ALEX YAKOVLEV

To the soul of my wonderful Mother, and my lovely family.

— Haider

I would like to express my deep gratitude to my supervisors Prof. Alex Yakovlev, Dr. Andrey Mokhov for their support and guidance through my PhD journey. They have always been a source of motivation and my inspirational model as a researcher.

I am grateful to the higher committee of education development in Iraq (HCED) for funding my PhD study their scholarship programme and also would like to express my sincere gratitude to the Iraqi Cultural Attache in London.

As part of my work, It is required establishing application of MEM relays in real applications, such as many-core systems. During this time, I worked with the Newcastle team of PRiME research project (which is a multi-million programme grant funded by EPSRC, UK). Thus, I would like to acknowledge the support I received from the PRiME project team.

I would like also to express my gratefulness and appreciation to my colleagues and friends in the School of Electrical and Electronic Engineering, especially those in Microelectronic Systems research (MSD) group, at Newcastle University for their guidance and assistance through my study. Especially, I appreciate the support of my wonderful colleagues Alaa Al-shkarchi, Yasir Abdullah, Dr. Nizar Dahir, Dr. Ra'ed Aldujaily, Dr. Hussein Leftah, and Ali Majeed for their productive suggestions, fruitful discussions, and subjective criticism.

I am also grateful to Dr Matthew Spencer for his advice in modifying and build the switch model simulator to include the more physical feature into simulating the MEMS.

I would like to offer my special regards to all the staff of the school of Electrical and Electronic Engineering in Newcastle university, especially Dr. Rishad Shafik, and Dr Fei Xia.

last but not least, I would like to thank my wonderful family for their continuous support and motivation throughout my PhD journey. Electrostatically-actuated Micro-Electro-Mechanical/Nano-Electro-Mechanical (MEM/NEM) relays are promising devices overcoming the energy-efficiency limitations of CMOS transistors. Many exploratory research projects are currently under way investigating the mechanical, electrical and logical characteristics of MEM/NEM relays. One particular issue that this work addresses is the need for a scalable and accurate physical model of the MEM/NEM switches that can be plugged into the standard EDA software.

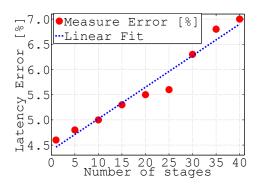

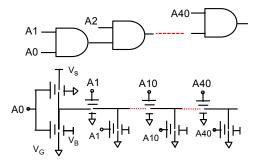

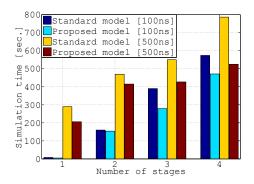

The existing models are accurate and detailed but they suffer from the convergence problem. This problem requires finding ad-hoc workarounds and significantly impacts the designer's productivity. In this thesis we propose a new simplified Verilog-AMS model. To test scalability of the proposed model we cross-checked it against our analysis of a range of benchmark circuits. Results show that, compared to standard models, the proposed model is sufficiently accurate with an average of 6% error and can handle larger designs without divergence.

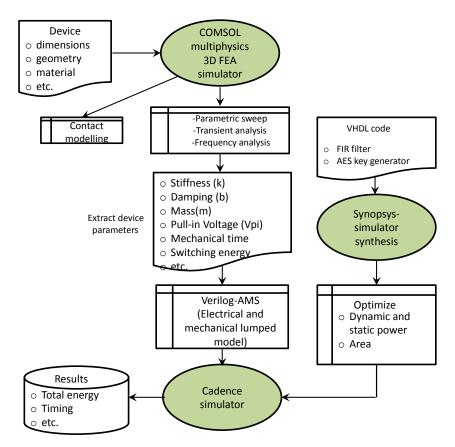

This thesis also investigates the modelling, designing and optimization of various MEM/NEM switches using 3D Finite Element Analysis (FEA) performed by the COMSOL multiphysics simulation tool. An extensive parametric sweep simulation is performed to study the energy-latency trade-offs of MEM/NEM relays. To accurately simulate MEMS/NEMS-based digital circuits, a Verilog-AMS model is proposed based on the evaluated parameters obtained from the multiphysics simulation tool. This allows an accurate calibration of the MEM/NEM relays with a significant reduction in simulation speed compared to that of 3D FEA exercised on COMSOL tool.

The effectiveness of two power gating approaches in asynchronous micropipelines is also investigated using MEM/NEM switches and sleep transistors in reducing idle power dissipation with a particular target throughput. Sleep transistors are traditionally used to power gate idle circuits, however, these transistors have fundamental limitations in their effectiveness. Alternatively, MEM/NEM relays with zero leakage current can achieve greater energy savings under a certain data rate and design architecture. An asynchronous FIR filter 4 phase bundled data handshake protocol is presented. Implementation is accomplished in 90nm technology node and simulation exercised at various data rates and design complexities. It was demonstrated that our proposed approach offers 69% energy improvements at a data rate 1KHz compared to 39% of the previous work.

The current trends for greater heterogeneity in future Systems-on-Chip (SoC) do not only concern their functionality but also their timing and power aspects. The increasing diversity of timing and power supply conditions, and associated concurrently operating modes, within an SoC calls for more efficient power delivery networks (PDN) for battery operated devices. This is especially important for systems with mixed duty cycling, where some parts are required to work regularly with low-throughput while other parts are activated spontaneously, i.e. in bursts. To improve their reaction time vs energy efficiency, this work proposes to incorporate a power-switching network based on MEM relays to switch the SoC power-performance state (PPS) into an active mode while eliminating the leakage current when it is idle. Results show that even with today's large and high pull-in voltages, a MEM-relay-based power switching network (PSN) can achieve a 1000x savings in energy compared to its CMOS counterpart for low duty cycle. A simple case of optimising an on-chip charge pump required to switch-on the relay has been investigated and its energy-latency overhead has been evaluated.

Heterogeneous many-core systems are increasingly being employed in modern embedded platforms for high throughput at low energy cost considerations. These applications typically exhibit bursty workloads that provide opportunities to minimize system energy. CMOS-based power gating circuitry, typically consisting of sleep transistors, is used as an effective technique for idle energy reduction in such applications. However, these transistors contribute high leakage current when driving large capacitive loads, making effective energy minimization challenging.

This thesis proposes a novel MEMS-based idle energy control approach. Core to this approach is an integrated sleep mode management based on the performance-energy states and bursty workloads indicated by the performance counters. A number of PARSEC benchmark applications are used as case studies of bursty workloads, including CPU- and memory- intensive ones. These applications are exercised on an Exynos 5422 heterogeneous many-core platform, engineered with a performance counter facilities, showing 55.5% energy savings compared with an on-demand governor. Furthermore, an extensive trade-off analysis demonstrates the comparative advantages of the MEMS-based controller, including zero-leakage current and non-invasive implementations suitable for commercial off-the-shelf systems.

Journal and magazines publications:

- 1. **Haider M. Alrudainy**; A. Aalsaud; R. Shafik; A. Mokhov; F. Xia; A. Yakovlev, *Understanding Idle Energy Minimization for Bursty Computation Workloads in Heterogeneous Many-Core Systems using Micro-Electro-Mechanical Relays*, (to be submitted), IEEE Transactions on Circuits and Systems II, TCAS-II

- 2. **Haider M. Alrudainy**; A. Mokhov; A. Yakovlev, A Survey of Emerging Applications Utilizing Miro-Electro-Mechanical Relays for Energy and Reliability Efficient Digital Circuits, (submitted), IEEE Circuits and Systems Magazine

#### Conference publications:

- 1. **Haider M. Alrudainy**; A. Mokhov; A. Yakovlev , *A Scalable Physical Model for Nano-Electro-Mechanical Relays*, Power and Timing Modeling, Optimization and Simulation (PATMOS), 29 Sept.-1 Oct. 2014, doi: 10.1109/PATMOS.2014.6951889, ISBN:978-1-4799-5412-4

- Haider M. Alrudainy; A. Mokhov; N. Dahir; A. Yakovlev, MEMS-Based Power Delivery Control for Bursty Applications, Cir- cuits and Systems (ISCAS), 2016 IEEE International Symposium on, 22-25 May 2016, pp 790-793, March 2015, DOI: 10.1109/IS-CAS.2016.7527359, ISBN: 978-1-4799-5341-7

- 3. **Haider M. Alrudainy**; A. Aalsaud; R. Shafik; A. Mokhov; F. Xia; A. Yakovlev, *MEMS-Based Runtime Idle Energy Minimization for Bursty Workloads in Heterogeneous Many-Core Systems*, (Submitted), Design, Automation Conference (DAC), 18-22 June 2017

- 4. **Haider M. Alrudainy**; A. Mokhov; F. Xia; A. Yakovlev, *Ultralow energy data driven computing using asynchronous micropipelines and nano-electro-mechanical relays*, in ISVLSI, pp. 1-6, July 2017 accepted.

- 5. **Haider M. Alrudainy**; R. Shafik; A. Mokhov; A. Yakovlev, *Lifetime Reliability Characterization of Nano/Micro -Electro-Mechanical Switches Used in Power Gating of Digital Integrated Circuits*, in DFT, pp. 1-6, October 2017 submitted.

Workshop and forum publications:

1. **Haider M. Alrudainy**, A. Mokhov; N. Dahir; A. Yakovlev, *A Scalable Physical Model for Nano-Electro-Mechanical Relays Based Finite Element Analysis (FEA) Parameters Verification*, in the proceedings of DAC, The 51st Annual Design Automation Conference, June 1-5, 2014, San Francisco, CA, USA, Work in Progress poster.

## CONTENTS

| I | Tł  | nesis Chapters                                       | 1  |

|---|-----|------------------------------------------------------|----|

| 1 | INT | RODUCTION                                            | 2  |

|   | 1.1 | Motivation                                           | 2  |

|   |     | 1.1.1 Energy in digital circuits                     | 4  |

|   |     | 1.1.2 Dynamic energy minimization                    | 5  |

|   |     | 1.1.3 Scaling Implications on Power Dissipation      | 7  |

|   |     | 1.1.4 Leakage energy reduction                       | 7  |

|   |     | 1.1.5 Applications                                   | 11 |

|   | 1.2 | Thesis Organization and Key Findings                 | 13 |

| 2 | BAC | CKGROUND AND LITERATURE REVIEW                       | 16 |

|   | 2.1 | Introduction                                         | 16 |

|   | 2.2 | Background of MEM/NEM relays                         | 17 |

|   | 2.3 | Operating Principles of Electrostatic Relay          | 18 |

|   | 2.4 | Survey of MEM/NEM relays                             | 21 |

|   | 2.5 | Survey of Applications Employing MEMS/NEMS           | 22 |

|   | 2.6 | Conclusion                                           | 28 |

| 3 | A S | CALABLE PHYSICAL MODEL FOR NANO-ELECTRO-ME-          |    |

|   | CHA | ANICAL RELAYS                                        | 31 |

|   | 3.1 | Introduction                                         | 31 |

|   | 3.2 | Analytical modelling of One-dimensional MEM/NEM      |    |

|   |     | Relay                                                | 32 |

|   |     | 3.2.1 Terminology and definition of MEM/NEM relay    |    |

|   |     | parameters                                           | 32 |

|   |     | 3.2.2 Mechanical Modelling                           | 32 |

|   |     | 3.2.3 Distribution of energy dissipation in the MEM- |    |

|   |     | S/NEMS                                               | 36 |

|   |     | 3.2.4 Electrical Modeling                            | 38 |

|   |     | 3.2.5 Simulation of Suspended Gate MEM/NEM relay     | 38 |

|   |     | 3.2.6 Proposed Model                                 | 39 |

|   | 3.3 | Model Evaluation                                     | 41 |

|   |     | 3.3.1 Simulation of the Proposed MEM/NEM Relay       |    |

|   |     | Model                                                | 41 |

|   |     | 3.3.2 Evaluation with Benchmark Circuits             | 42 |

|   | 3.4 | Finite Element Analysis (FEA)                        | 44 |

|   |     | 3.4.1 Structural stiffness                           | 47 |

|   |     | 3.4.2 Damping Analysis                               | 48 |

|   |     | 3.4.3 Natural and resonant frequency                 | 49 |

|   | 3.5 | Energy-Latency Analysis of MEMS                      | 50 |

|   | 3.6  | Implications of scaling on the energy-delay trade-off . | 52         |

|---|------|---------------------------------------------------------|------------|

|   | 3.7  | Switch model simulator based on (FEA)                   | 53         |

|   | 3.8  | Conclusion                                              | 55         |

| 4 | MEN  | IS-BASED POWER GATING OF ASYNCHRONOUS MICROP            | IPELINES   |

|   | FOR  | ULTRA LOW ENERGY DRIVEN COMPUTING                       | 58         |

|   | 4.1  | Introduction and motivation                             | 58         |

|   | 4.2  | Asynchronous pipeline stage                             | 60         |

|   | 4.3  | Power gating in asynchronous micropipeline              | 60         |

|   |      | 4.3.1 Conventional power gating in asynchronous mi-     |            |

|   |      | cropipeline                                             | 60         |

|   |      | 4.3.2 Power gating in the asynchronous micropipeline    |            |

|   |      | based on adjacent-state monitoring                      | 61         |

|   |      | 4.3.3 Power gating in the asynchronous micropipeline    |            |

|   |      | by controlling the status of delay line blocks          | 62         |

|   |      | 4.3.4 Proposed MEMS-based power gating in asyn-         |            |

|   |      | chronous micropipeline                                  | 62         |

|   | 4.4  | On-chip charge pump for MEMS implementations            | 63         |

|   | 4.5  | Evaluation setup                                        | 65         |

|   | 4.6  | Results                                                 | 66         |

|   | 4.7  | Zero Delay Ripple Turn On (ZDRTO)                       | 71         |

|   | 4.8  | Conclusion                                              | 73         |

| 5 | MEN  | IS-BASED POWER DELIVERY CONTROL FOR BURSTY AP           | _          |

|   | PLIC | CATIONS                                                 | 74         |

|   | 5.1  | Introduction                                            | 74         |

|   | 5.2  | Background                                              | <b>7</b> 5 |

|   | 5.3  | Proposed architecture of computer systems               | 76         |

|   | 5.4  | Voltage regulator network optimization                  | 78         |

|   | 5.5  | Proposed architecture of the PDN                        | 79         |

|   | 5.6  | Power Switch Network architecture                       | 79         |

|   |      | 5.6.1 PSN energy consumption                            | 8o         |

|   |      | 5.6.2 Power Switch controller (power switch controller  |            |

|   |      | (PSC))                                                  | 81         |

|   | 5.7  | Results                                                 | 81         |

|   | 5.8  | Conclusion                                              | 83         |

| 6 | MEN  | 1S-BASED IDLE ENERGY MINIMIZATION FOR BURSTY            |            |

|   | woi  | RKLOADS IN HETEROGENEOUS MANY-CORE SYSTEMS              | 84         |

|   | 6.1  | Introduction and motivation                             | 84         |

|   | 6.2  | Proposed Approach                                       | 87         |

|   |      | 6.2.1 Hardware experimental platform                    | 87         |

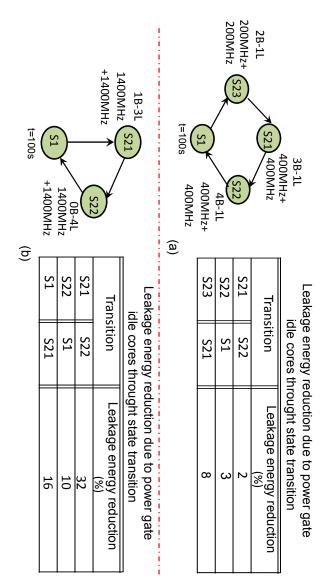

|   |      | 6.2.2 Energy-performance state models                   | 90         |

|   |      | 6.2.3 Measurements of Power Normalized performance      | -          |

|   |      | (IPS/Watt)                                              | 94         |

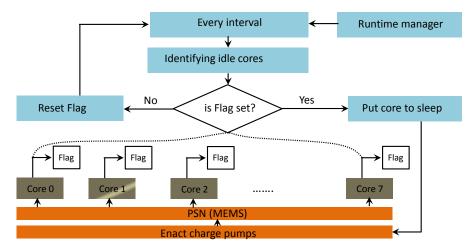

|   |      | 6.2.4 Power-gating management                           | 94         |

|   | 6.3  | Results                                                 | 96         |

|    | 6.3.1 Evaluation setup         | 96  |

|----|--------------------------------|-----|

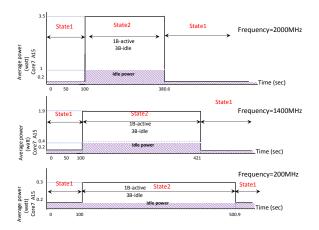

|    | 6.3.2 Application case studies | 97  |

|    | 6.3.3 Trade-off analysis       | 100 |

|    | 6.4 Conclusions                | 102 |

| 7  | CONCLUSIONS AND ENTURE WORK    | 102 |

| 7  |                                | 103 |

|    | 7.1 Summary and Conclusion     | 103 |

|    | 7.2 Future work                | 104 |

|    |                                |     |

| 11 | Thesis Appendices              | 107 |

| A  | VERILOG-AMS CODE FOR MEMS/NEMS | 108 |

|    |                                |     |

|    | Thesis Bibliography            | 112 |

| BI | BLIOGRAPHY                     | 113 |

## LIST OF FIGURES

| Figure 1.1  | IC power trends until 2020: actual vs. specified (Source: |    |

|-------------|-----------------------------------------------------------|----|

| O           | International Technology Roadmap for Semiconduc-          |    |

|             | tors (http://www.itrs.net/)                               | 3  |

| Figure 1.2  | Idle power dissipation of Exynos 5422 big.LITTLE          |    |

| O           | octa-core heterogeneous platform performing ferret        |    |

|             | application                                               | 9  |

| Figure 1.3  | Modified architecture of coarse power gating tech-        |    |

| 0           | nique based on [87]                                       | 10 |

| Figure 1.4  | Thesis organization.                                      | 15 |

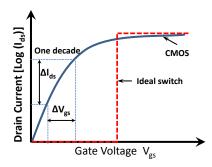

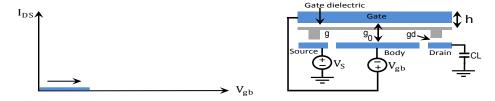

| Figure 2.1  | Sub-threshold regime of MEM relay and CMOS                |    |

| O           | transistor                                                | 16 |

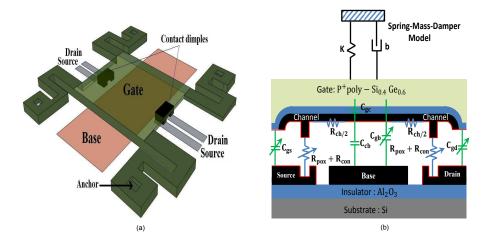

| Figure 2.2  | Shows the:(a) schematic 3D view of 4-terminal             |    |

| O           | suspended gate MEM relay based on [156]; (b)              |    |

|             | schematic 2-D cross section view in the off state.        | 18 |

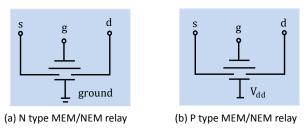

| Figure 2.3  | 4-terminal relay device symbol                            | 18 |

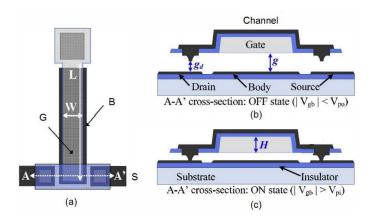

| Figure 2.4  | Cantilever beam relay as reported in [29]: (a)            |    |

|             | plan view; (b) cross section view in the off-state;       |    |

|             | (c) cross-section view in the on-state                    | 19 |

| Figure 2.5  | Schematic of MEMS before pull-in. This graph              |    |

| 0           | shows the MEMS with a gate-body voltage $(V_{qb})$        |    |

|             | applied that is below $V_{pi}$ and the corresponding      |    |

|             | $V_{qs}$ vs. $I_{ds}$ curve                               | 19 |

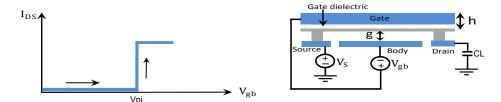

| Figure 2.6  | Schematic of MEMS after pull-in. This graph               |    |

| O           | shows the MEMS with a gate-body voltage $(V_{gb})$        |    |

|             | applied that is above $V_{pi}$ and the corresponding      |    |

|             | $V_{qs}$ vs. $I_{ds}$ curve                               | 20 |

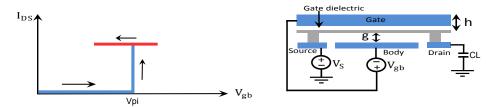

| Figure 2.7  | Schematic of MEMS before pull-out. This graph             |    |

|             | shows the MEMS with a gate-body voltage $(V_{qb})$        |    |

|             | applied that is above $V_{rl}$ and the corresponding      |    |

|             | $V_{qs}$ vs. $I_{ds}$ curve                               | 20 |

| Figure 2.8  | Schematic of MEMS after pull-out. This graph              |    |

| O           | shows the MEMS with a gate-body voltage $(V_{qb})$        |    |

|             | applied that is below $V_{rl}$ and the corresponding      |    |

|             | V <sub>gs</sub> vs. I <sub>ds</sub> curve                 | 21 |

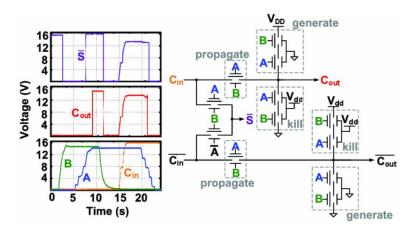

| Figure 2.9  | MEMS based carry adder circuit and measured               |    |

| 9           | waveform. This circuit is implemented on a 1μm            |    |

|             | test chip [156]                                           | 26 |

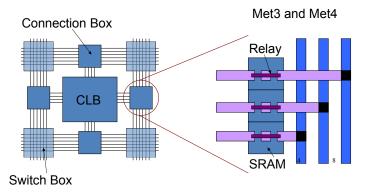

| Figure 2.10 | NEM relays as FPGA routing switches based on              |    |

| C           | [27, 28]                                                  | 27 |

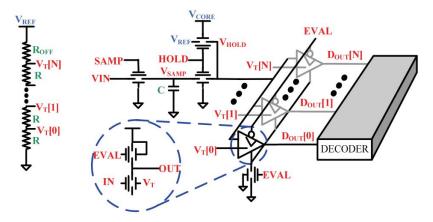

| Figure 2.11 | MEMS based ADC circuit diagram proposed in                | ,  |

| U           |                                                           | 20 |

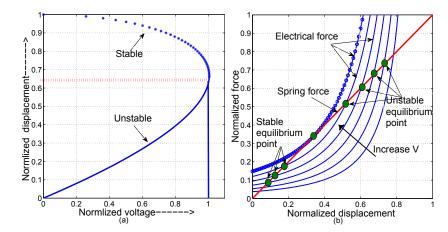

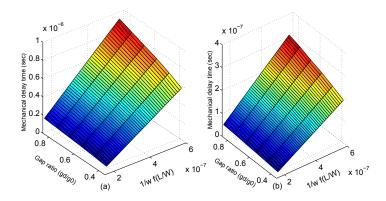

| Figure 3.1  | Illustrates that: (a) the solid blue line denotes the unstable actuation region, while the dotted one represents the stable region. The saddle-node bifurcation happens at 0.3 of the gap distance; (b) stability analysis, normalized displacement |         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 3.2  | vs. net forces                                                                                                                                                                                                                                      | 34      |

| Figure 3.3  | main [9]                                                                                                                                                                                                                                            | 35      |

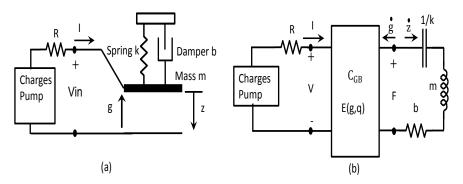

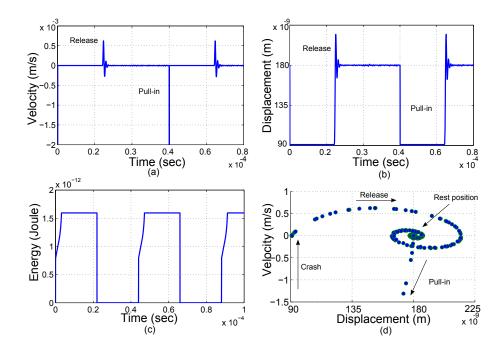

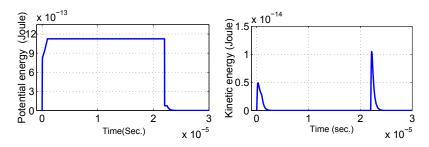

| Figure 3.4  | (d) phase-plane of velocity vs. displacement Distribution of energy consumption in the MEM                                                                                                                                                          | 36      |

| Figure 3.5  | relay                                                                                                                                                                                                                                               | 38<br>h |

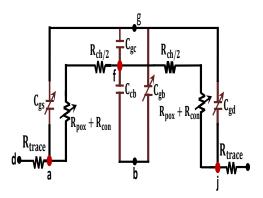

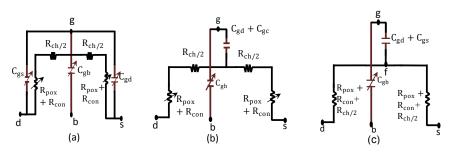

| Figure 3.6  | (MEMS/NEMS) [156]                                                                                                                                                                                                                                   | 39      |

| 8 9         | cuit                                                                                                                                                                                                                                                | 40      |

| Figure 3.7  | Latency error rate                                                                                                                                                                                                                                  | 41      |

| Figure 3.8  | CMOS-MEM relay mapping of cascade AND                                                                                                                                                                                                               |         |

|             | gates                                                                                                                                                                                                                                               | 42      |

| Figure 3.9  | Model execution time versus clock speed and                                                                                                                                                                                                         |         |

|             | number of stages                                                                                                                                                                                                                                    | 44      |

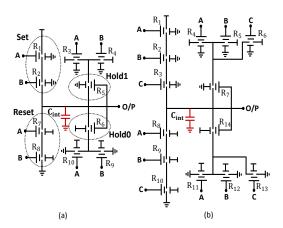

| Figure 3.10 | Proposed schematic circuit of C-element based                                                                                                                                                                                                       |         |

|             | NEM relay for (a) 2-input; and (b) 3-input                                                                                                                                                                                                          | 44      |

| Figure 3.11 | Input/output waveforms of 3-input C-element                                                                                                                                                                                                         |         |

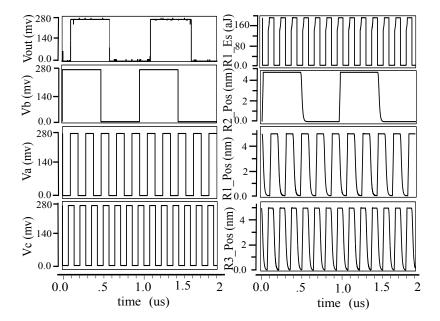

|             | using NEM relays at V <sub>dd</sub> =0.28 V                                                                                                                                                                                                         | 45      |

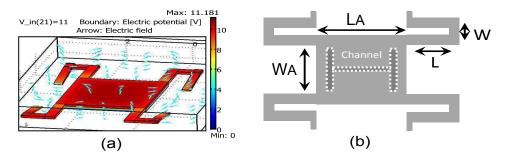

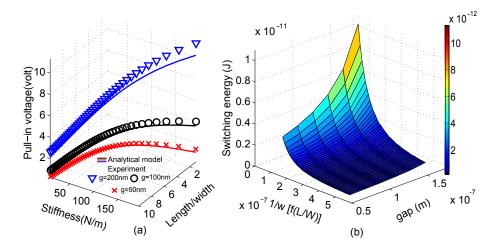

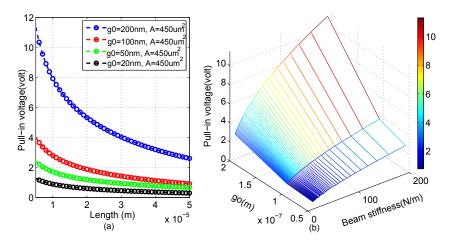

| Figure 3.12 | Demonstrates the: (a) FEA-simulated pull-in volt-                                                                                                                                                                                                   |         |

|             | age and displacement; (b) simplified sketch, sym-                                                                                                                                                                                                   |         |

|             | bols L, W, L <sub>A</sub> , W <sub>A</sub> and h denote, respectively,                                                                                                                                                                              |         |

|             | spring length/width, actuation area length/width,                                                                                                                                                                                                   |         |

| Eigung a sa | and thickness of the suspended gate [156]                                                                                                                                                                                                           | 45      |

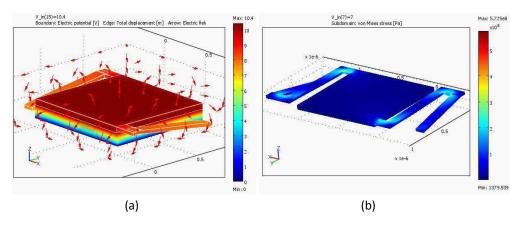

| Figure 3.13 | Demonstrates the 3D FEA of: (a) 4-terminals                                                                                                                                                                                                         |         |

|             | MEMS with single fold spring; (b) 4-terminals                                                                                                                                                                                                       | 16      |

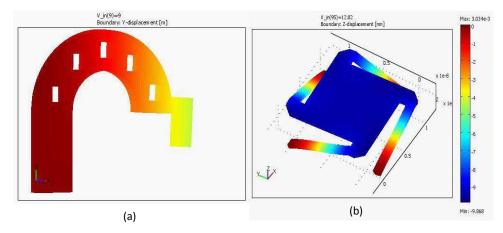

| Figure 3.14 | with double fold spring MEMS Demonstrates the 3D FEA of: (a) anchor MEMS                                                                                                                                                                            | 46      |

| 11guie 3.14 | [17, 137]; (b) 4-terminals with opposite-spring                                                                                                                                                                                                     |         |

|             | MEMS                                                                                                                                                                                                                                                | 46      |

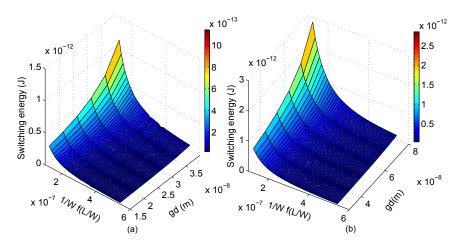

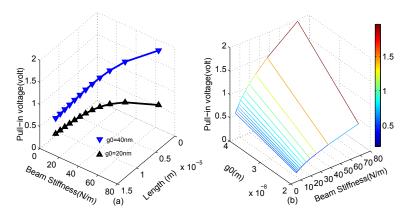

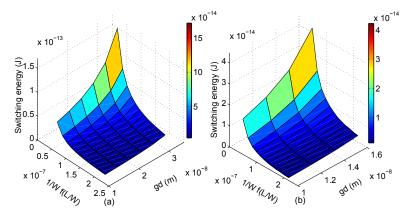

| Figure 3.15 | Shows the: (a) comparison of the pull-in voltage                                                                                                                                                                                                    | 40      |

| 8 33        | for three different gap distances obtained form                                                                                                                                                                                                     |         |

|             | 3D FEA and the analytical model; (b) switching                                                                                                                                                                                                      |         |

|             | energy at quality factor (Q)=1 based finite ele-                                                                                                                                                                                                    |         |

|             | ment analysis (FEA) of g <sub>0</sub> =200nm and A=450um <sup>2</sup>                                                                                                                                                                               |         |

|             | as a function of (g <sub>d</sub> ) and resonant frequency (w).                                                                                                                                                                                      | 47      |

| 48    |

|-------|

| 40    |

|       |

|       |

| .~ 40 |

| g. 49 |

| 50    |

|       |

|       |

|       |

|       |

| 50    |

|       |

|       |

|       |

|       |

| 51    |

|       |

|       |

|       |

|       |

| 52    |

|       |

|       |

|       |

|       |

|       |

| 52    |

|       |

| 53    |

|       |

|       |

|       |

| 54    |

|       |

|       |

|       |

| 54    |

|       |

|       |

|       |

|       |

|       |

|       |

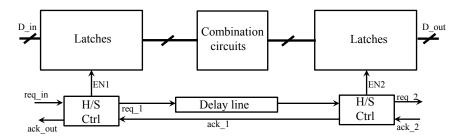

| Figure 4.1  | A conventional asynchronous-logic 4 phase bundle       |     |

|-------------|--------------------------------------------------------|-----|

|             | data micropipeline [102]                               | 60  |

| Figure 4.2  | Shows the: (a) power-gated asynchronous micropipeline  |     |

|             | [102]; (b) timing diagram of the conventional power-   |     |

|             | gated micropipeline stage                              | 61  |

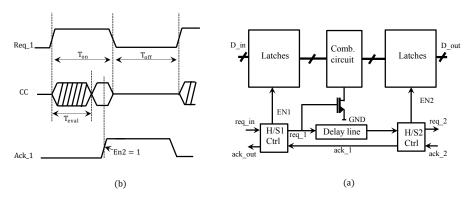

| Figure 4.3  | illustrates the: (a) timing diagram; (b) power-gated   |     |

|             | asynchronous micropipeline based on state monitor-     |     |

|             | ing approach [86].                                     | 62  |

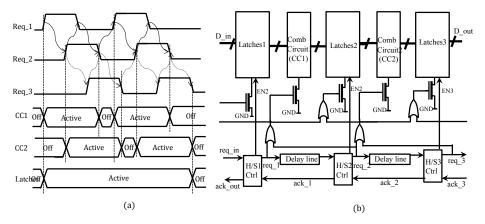

| Figure 4.4  | Shows the: (a) asynchronous power gating in[121];      |     |

| 0           | (b) proposed MEMS-based synchronous power              |     |

|             | gating                                                 | 63  |

| Figure 4.5  | Current consumption and area normalization to          |     |

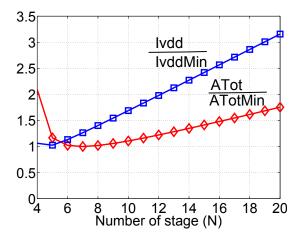

| 0 , 3       | their minimum values versus N                          | 64  |

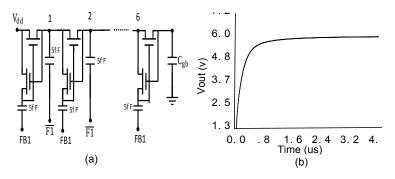

| Figure 4.6  | Illustrates the: (a) schematic circuit of the simu-    |     |

|             | lated charge pump; (b) simulated output voltage        |     |

|             | with respect to time for N=6 stages and $\varphi = 40$ |     |

|             | MHz                                                    | 64  |

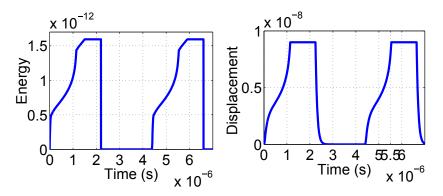

| Figure 4.7  | Impact of charge pump on the Micro-Electro-            | ·   |

| 0           | Mechanical Switch (MEMS) relay energy-latency.         | 65  |

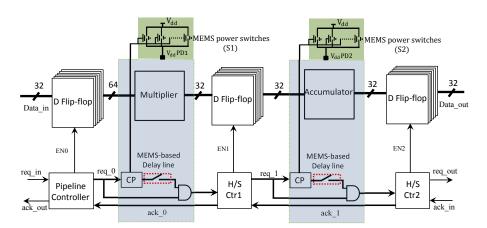

| Figure 4.8  | Asynchronous 32-tap FIR filter implemented             |     |

| 0 ,         | based on the proposed approach                         | 65  |

| Figure 4.9  | Flowchart of our evaluation process of the mixed       |     |

| 0 17        | MEMS/CMOS design                                       | 67  |

| Figure 4.10 | Shows the total energy consumption per com-            |     |

| 0 1         | putation for a various date rate with different        |     |

|             | power gating configurations                            | 69  |

| Figure 4.11 | Shows the total energy consumption per com-            |     |

| 0 ,         | putation for a various date rate with different        |     |

|             | power gating configurations at D=0.01                  | 70  |

| Figure 4.12 | Shows the total energy consumption for 32-tap          | •   |

| 0 ,         | FIR filter at various date rate and different power    |     |

|             | gating configurations                                  | 71  |

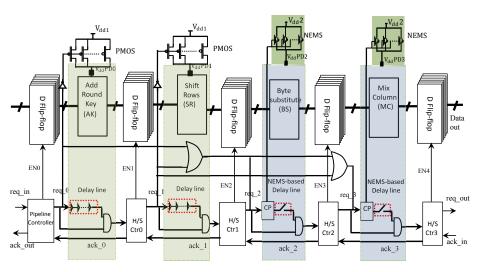

| Figure 4.13 | Shows the power gating scheme of AES asyn-             | •   |

| 0 , 3       | chronous micropipeline based on mixed NEM-             |     |

|             | S/PMOS power switch                                    | 72  |

| Figure 5.1  | Proposed portable system architecture [9]              | 75  |

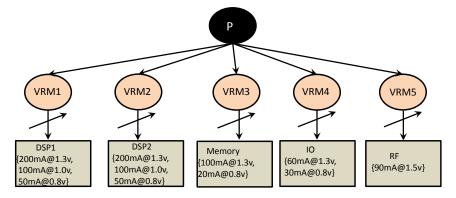

| Figure 5.2  | Shows the VRM tree in providing an appropriate         |     |

| 0 0         | voltage level for each function block (FB) [11]        | 79  |

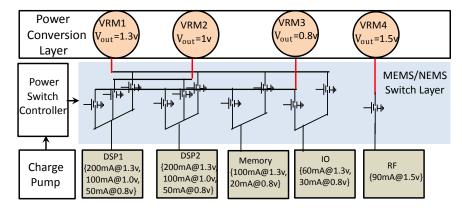

| Figure 5.3  | The modified architecture of the PDN to support        | • • |

| 0 33        | low-throughput and Bursty operated applications.       | 80  |

| Figure 5.4  | An optimised power delivery network (PDN) that         |     |

| J J.        | meets the target impedance (a) PMOS transis-           |     |

|             | tors; (b) MEMS                                         | 80  |

| Figure 5.5  | Test bench of operating states and state transition    |     |

| 0 00        | based on [11]                                          | 82  |

| Figure 5.6  | Energy ratio vs. $T_{off}$ , for various $T_{on}$ /cycle, for design power gated by a 90 nm PMOS transistor               |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------|-----|

|             | and current MEMS                                                                                                          | 82  |

| Figure 5.7  | Energy ratio vs. T <sub>off</sub> , for various T <sub>on</sub> /cycle, for design power gated by a 90 nm PMOS transistor | 0 - |

| Eigene ( a  |                                                                                                                           | 83  |

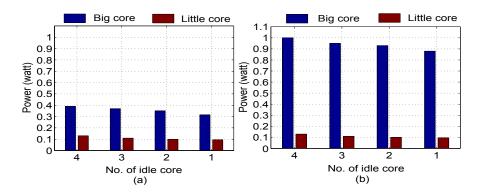

| Figure 6.1  | Experimental measurements of idle power consump-                                                                          |     |

|             | tion by adopting Odroid-XU3 big.LITTLE platform:                                                                          |     |

|             | (a) 1400MHz big.LITTLE; (b) 2000MHz big, 1400MHz                                                                          | 0   |

| Г'          |                                                                                                                           | 85  |

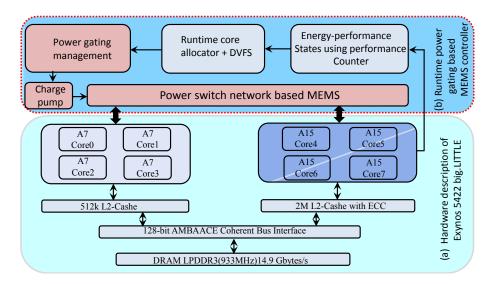

| Figure 6.2  | (a) Exynos 5422 block diagram; (b) proposed runtime                                                                       | 0.0 |

|             | 1 0 0                                                                                                                     | 88  |

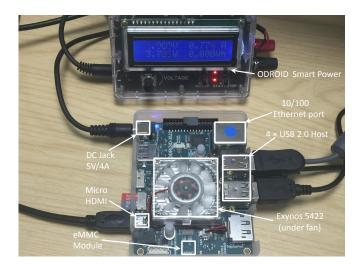

| Figure 6.3  | Experimental setup using Odroid-XU3 mobile                                                                                |     |

|             | •                                                                                                                         | 89  |

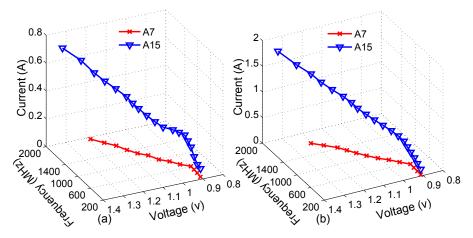

| Figure 6.4  | Voltage-frequency characteristics of Cortex-A7                                                                            |     |

|             | and Cortex-A <sub>15</sub> at: (a) without workload; (b)                                                                  |     |

|             |                                                                                                                           | 90  |

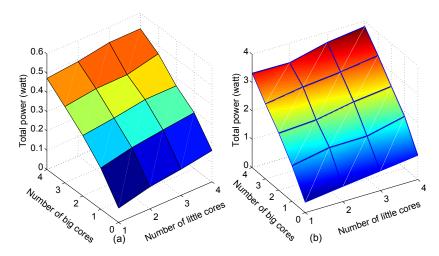

| Figure 6.5  | Total power for ferret application at: (a) 200 MHz;                                                                       |     |

|             | (b)1400 MHz                                                                                                               | 91  |

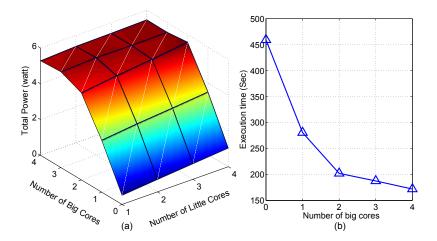

| Figure 6.6  | (a) Total power of ferret application at 2000 MHz big-                                                                    |     |

|             | cores and 1400 MHz little-cores; (b) execution time                                                                       |     |

|             | when 4 little cores fully operated with various big                                                                       |     |

|             | cores number                                                                                                              | 91  |

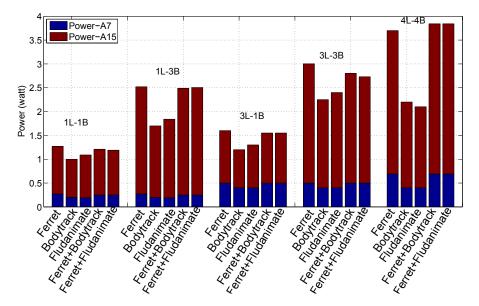

| Figure 6.7  | Total power for single and current applications                                                                           |     |

|             | in various set-ups exercising at 1400MHz                                                                                  | 93  |

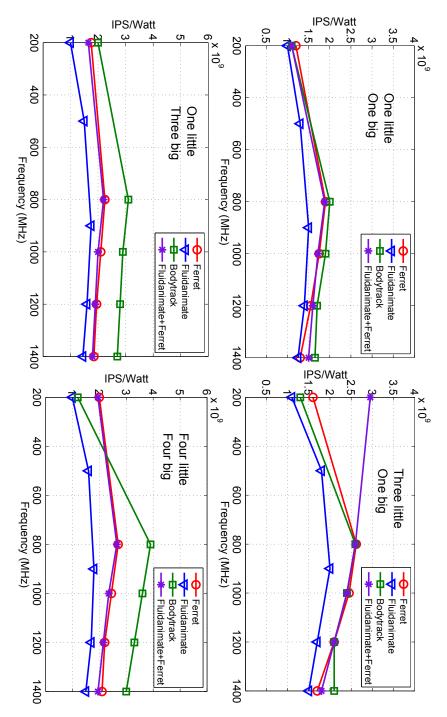

| Figure 6.8  | Total IPS/Watt for various applications exercised                                                                         |     |

| O           |                                                                                                                           | 95  |

| Figure 6.9  | Hardware flowchart of the power gating man-                                                                               |     |

| 0           | 1 0 0                                                                                                                     | 96  |

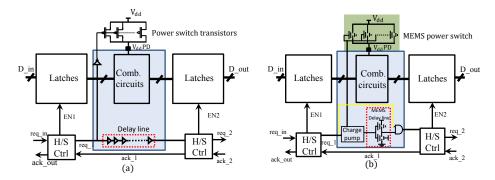

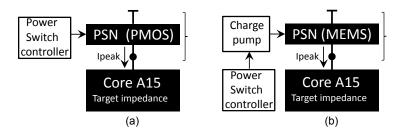

| Figure 6.10 | Power gating circuitry that meets target impedance:                                                                       |     |

| O           |                                                                                                                           | 97  |

| Figure 6.11 | Idle power dissipation of Exynos 5422 big.LITTLE                                                                          | ,,  |

| O           | octa-core heterogeneous platform exercising <i>fer-</i>                                                                   |     |

|             | 0 1                                                                                                                       | 98  |

| Figure 6.12 | Test bench of state transition based: (a) CPU-                                                                            | ,-  |

|             | intensive <i>ferret</i> application; (b) Memory-intensive                                                                 |     |

|             |                                                                                                                           | 99  |

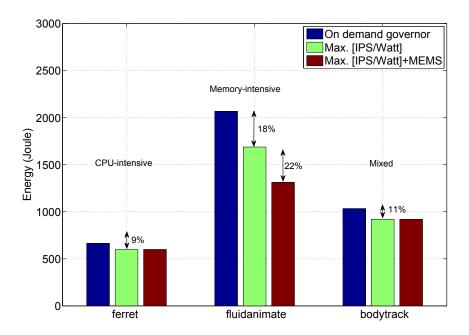

| Figure 6.13 | Comparative energy dissipations of <i>ferret</i> , <i>flu-</i>                                                            | フフ  |

|             |                                                                                                                           | OO  |

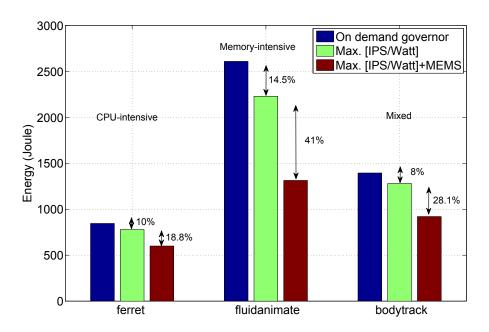

| Figure 6.14 | Comparative energy dissipations of <i>ferret</i> , <i>flu-</i>                                                            | -   |

| 116410 0.14 | idanimate, and bodytrack with applications (exer-                                                                         |     |

|             |                                                                                                                           | 01  |

|             | Civilia, Oboci villa, tillic cuudi Oilii ii ii ii ii ii ii ii ii                                                          | J   |

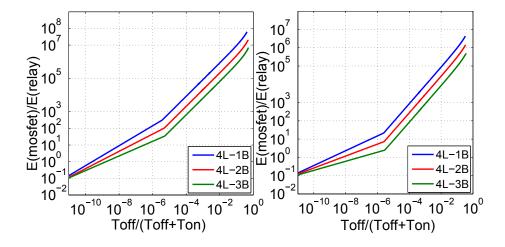

| Figure 6.15            | Energy gain vs (1-D) for various core allocations for a design power gated with MOSFETs and MEM relays while exercising <i>ferret</i> application at: (a) 2000MHz; (b) 200MHz |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF T              | ABLES                                                                                                                                                                         |

| Table 2.1              | Survey of electro-mechanical relays actuation scheme. This table compares MEMS actuation                                                                                      |

| Table 2.2              | characteristics                                                                                                                                                               |

| Table 2.3              | Digital Logic Applications                                                                                                                                                    |

| Table 2.4              | Mechanical Relays contained in Table 2.2 25 Survey of Emerging Applications Employing Micro-Electro-Mechanical (MEM)/Nano-Electro-                                            |

| TT 1.1                 | Mechanical (NEM) Relays 29                                                                                                                                                    |

| Table 3.1<br>Table 3.2 | MEMS Model Benchmark circuits                                                                                                                                                 |

| Table 4.1              | Total energy per computation for various asynchronous power gating configurations                                                                                             |

| Table 4.2              | Total energy consumption for 32-tap FIR filter at various asynchronous power gating configurations 71                                                                         |

| Table 6.1              | Features and limitations of the existing approaches. 86                                                                                                                       |

| Table 6.2              | The available voltage/frequency scaling set-ups                                                                                                                               |

| Table 6.3              | for GPU                                                                                                                                                                       |

|                        | tures of PARSEC benchmarks [18] 92                                                                                                                                            |

| Table 6.4              | Latency overhead                                                                                                                                                              |

|                        |                                                                                                                                                                               |

| LIST OF A              | LGORITHMS                                                                                                                                                                     |

| 3.2 Prop               | IS/NEMS Verilog-AMS model                                                                                                                                                     |

#### **ACRONYMS**

ZDRTO zero delay ripple turn on

DL delay line

MEMS Micro-Electro-Mechanical Switch

MEM Micro-Electro-Mechanical

NEMS Nano-Electro-Mechanical Switch

NEM Nano-Electro-Mechanical

PSC power switch controller

DSP digital signal processing

PDN power delivery network

VLSI very large scale integrate circuit

SoC system-on-Chip

CC combinational circuit

PCN power conversion network

VRM voltage regulator module

RFIDs radio-frequency identifications

EDA electronic design automation

PPS power performance state

FEA finite element analysis

ICs integrated circuits

FB function block

FBs function blocks

CMOS complementary metal-oxide-semiconductor

MEM/NEM Micro-Electro-Mechanical/Nano-Electro-Mechanical

MEMS/NEMS Micro-Electro-Mechanical Switch/Nano-Electro-Mechanical Switch

DSP digital signal processing

DVFS dynamic voltage and frequency scaling

DVS dynamic voltage scaling

PSN power switch network

ALE Arbitrary Lagrangian-Eulerian

Q quality factor

ICs integrated circuits

IOTs Internet of Things

WSNs Wireless Sensor Networks

PDN power delivery network

SoC system-on-chip

PVT process-voltage-temperature

VLSI very large scale integration

# Part I Thesis Chapters

#### 1.1 MOTIVATION

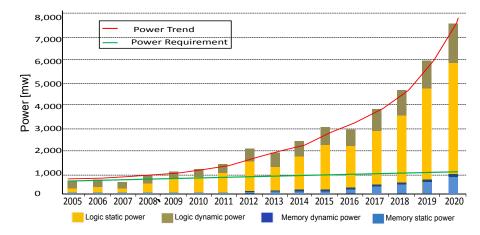

During the last four decades, scaling of the complementary metal-oxide-semiconductor (CMOS) has been the impetus in progressing of microelectronics industry enabling significant improvement in terms of performance, integration, and cost. This is attributed to the fact that higher performance and lower cost are two primary goals for many digital integrated circuits (ICs) [127]. Dynamic energy, historically, has been dominating the energy consumption of digital circuits and has been the central focus of energy reduction research for many years. However, continuing technology scaling has significantly caused an increase in leakage energy consumption, as shown in Fig. 1.1, demanding a variety of leakage reduction techniques to be developed. The mainstream of future electronics design in some emerging applications is to shift from performance-driven goals to energy constraints, and as the leakage energy continues to grow exponentially, this presents a fundamental challenge in achieving these targets.

From a system level point of view, dynamic and leakage energy reduction is a major design goal of modern embedded systems. Dynamic energy can be lowered either by reducing the work required to accomplish a task, or by adopting dynamic voltage and frequency scaling (DVFS) to run the task at lower frequency and voltage. Leakage energy, however, is not related to the circuit activity, but is more closely linked to the circuit's technology, operating temperature, and chip layout. Therefore, the only way to reduce it is by removing the supply voltage during idle periods.

According to a recent study presented in [46, 167], a large proportion of a chip has to be shut-off so that it can still operate within its given power budget due to the "dark silicon" phenomenon. This "dark silicon" issue becomes more obvious at 8nm, and 22nm technology node, where roughly 50%, and 21%, respectively, of the chip may have to be power gated at any given time while. Furthermore, according to the International Technology Roadmap for Semiconductor (ITRS), by the year 2020, the predicted chip power consumption for modern SoCs will have risen by a factor of roughly  $\times$ 10 compared to 2012 [21]. This leads to mandatory power gating of significant parts of the future many-core platforms.

One of the most prominent opportunities to mitigate leakage energy is during standby periods, when no computation occurs. The microprocessor industry has widely adopted power gating techniques

Figure 1.1: IC power trends until 2020: actual vs. specified (Source: International Technology Roadmap for Semiconductors (http://www.itrs.net/).

coupled with software-controlled sleep modes in such applications exhibiting substantial idle periods [26]. With this technique, transistors are used to disconnect the power from unused portions of a microprocessor, which reduces leakage power. This approach is attractive because it mitigates leakage without requiring any modification to the logic or operation of the power-gated circuitry. However, sleep transistors themselves contribute high leakage current, especially when driving a large capacitive load. This thesis, therefore, proposes a new power gating techniques based on the Micro-Electro-Mechanical Switch/Nano-Electro-Mechanical Switch (MEMS/NEMS) to completely eliminate leakage energy dissipation in applications whose workloads are bursty in nature.

The first chapter provides an overview of low energy designs in digital circuits and gives preliminary details of the subsequent chapters in the thesis. The major components of energy dissipation in digital circuits are discussed in Section 1.1.1. A synoptic outline of the established dynamic energy techniques is described in Section 1.1.2. Section 1.1.3 summarizes the impact of technology scaling on the leakage energy dissipation and Section 1.1.4 discusses some effective techniques employed for energy-efficient digital circuits which are relevant to the work reported in this thesis. Section 1.1.5 provides examples of energy-constrained applications where low-throughput microprocessors are used. Furthermore, a case of energy-efficient microprocessor architecture is discussed where two modes of operations are postulated as follows: firstly, high throughput coupled with burst activities; and secondly, rationally low throughput coupled with regular activities. Finally, the contributions of each subsequent chapter are outlined in Section 1.2.

#### 1.1.1 Energy in digital circuits

In order to design energy-efficient digital CMOS circuits, it is essential to understand the main sources of energy consumption. Typically, these can be mainly divided into dynamic energy and leakage energy [140]. Dynamic energy dissipation is caused by switching activity and occurs whenever the digital circuit is doing useful work. Leakage energy, whereas, is consumed whenever the digital circuits remain connected to the supply voltage regardless of whether or not a useful computation is being executed. This means that when the digital circuits are performing a useful work i.e. *active mode* of operation, total energy is presented by both dynamic and leakage energy. However, when the digital circuits are not performing useful computation i.e. *Idle mode* of operation, the leakage energy is the only contributor of energy consumption. The total energy dissipation of digital circuits, therefore, is given by:

$$E_{total} = E_{dyn} + E_{leak} \quad . \tag{1.1}$$

The total energy dissipation in digital CMOS circuits over a number of cycles  $N_{cycle}$  with clock period  $t_{period}$  can be expressed as follows:

$$E_{total} = E_{dyn} + E_{leak} = N_{cycle}.V_{dd}^{2}.C_{eff} + N_{cycle}.V_{dd}.I_{leak}.t_{period} , \eqno(1.2)$$

where  $C_{eff}$  represents the summed average capacitance given by the product of the switching probability  $\alpha$  and total load capacitance  $C_L$  [140]. Assuming the clock frequency is f, the total switching power of digital CMOS circuits can be then given as:

$$P_{total} = P_{dyn} + P_{leak} = V_{dd}^2.C_{eff}.f + V_{dd}.I_{leak} \quad . \tag{1.3}$$

It can be seen from Eqs. 1.2 and 1.3 that dynamic power is proportional to the product of the square supply voltage  $V_{\rm dd}$  and clock frequency, whereas dynamic energy is only proportional to the square of supply voltage  $V_{\rm dd}$ . Consequently, although reducing clock frequency can reduce dynamic power, the required dynamic energy to complete the task remains the same. A lower operating frequency, however, would result in an increase in total energy consumption because of the increasing clock period in Eq.1.2. As a result, more energy is consumed as leakage, leading to lower energy-efficiency.

Traditionally, scaling down the supply voltage ( $V_{\rm dd}$ ) can drastically lower the energy used per operation due to the quadratic dependence of dynamic energy consumption on  $V_{\rm dd}$ , as can be seen in Eq. 1.2. However, reducing the supply voltage ( $V_{\rm dd}$ ) increases propagation de-

lay time in digital circuits, which in turn causes a decrease in operating frequency. Consequently, further reduction in supply voltage, passing the  $V_{\rm optimum}$ , can result in an increase in total energy consumption due to the dominance of leakage energy. This is attributed to the exponential increment of propagation delay time for  $V_{\rm dd} < V_{\rm optimum}$  [146]. The propagation delay time of a gate can be roughly estimated as [4]:

$$T_{\text{propagation}} \propto \frac{C_L.V_{dd}}{(V_{dd} - V_{th})^n}$$

, (1.4)

where n is a technology-dependent parameter used to model short channel effects and ordinarily has a value ranging between 1-2, and  $V_{\rm th}$  represents the threshold voltage of the transistors.

## 1.1.2 Dynamic energy minimization

Dynamic energy has dominated the total energy dissipation of digital CMOS circuits for many years. Examining Eq. 1.2, it can be seen that dynamic energy can be lowered by reducing either the effective load capacitance  $C_{eff}$ , or the operating voltage  $(V_{dd})$ . However, lowering  $V_{dd}$  increases the propagation delay, Eq. 1.4, and hence methods to reduce dynamic energy consumption attempt to affect these variables without affecting any performance degradation. In this section, a brief summary of some extensively adopted dynamic energy reduction techniques is presented.

### 1.1.2.1 Clock gating

The dynamic energy dissipation of a processor is mostly dominated by the clock tree [143]. It has been noted that almost 32% of the dynamic power in the Alpha 21264 microprocessor is consumed because of the global clock network [53]. This relatively sizeable dynamic power dissipation is due to the large capacitive load of the clock tree as well as high activity. Furthermore, although a non-trivial proportion of registers may hold the same logic state over several clock cycles, the internal switching of the gate from the toggling of the clock adds to the total dynamic power dissipation. Consequently, this observation led to the development of the clock gating technique, which was presented to prevent the switching of parts of the clock tree where registers state did not demand to be updated. The simplicity of design and ease of implementation of clock gating allows it to be used in all types of sequential digital circuits. It has been reported that 33% and 50% savings in dynamic energy can be achieved by implementing clock gating techniques in microprocessors [52] and FPGAs [70] respectively.

#### 1.1.2.2 Dynamic Voltage and Frequency Scaling (DVFS)

Dynamic Voltage and Frequency Scaling (DVFS) targets both the operating clock frequency and the supply voltage ( $V_{\rm dd}$ ). This technique can be used when a system is not required to operate at its maximum frequency due to workload demands [51]. Therefore, the supply voltage can be reduced to significantly decrease dynamic energy and improve energy-efficiency, Eq. 1.2, resulting in lowering the operating frequency due to the increment of propagation delay, Eq. 1.4. It has been reported that the energy-efficiency of a processor can be improved by up to  $\times$ 10 when employing DVFS [51]. The advantage of DVFS is the capability to switch between low performance, low energy and high performance, high energy states relying on the current workload. As a result, its efficiency at minimizing dynamic energy consumption has prompted many runtime control algorithms in a variety of different systems[3, 15, 172].

An alternative to DVFS is to employ multi-supply/multi-voltage operation, where different sections of the system-on-chip (SoC) may require various levels of performance state. By utilizing multiple supplies, voltage islands can be formed to partition subsections of the SoC that are of the critical path, enabling dynamic energy savings [145, 168]. This means that the chosen path has to cope with rises in delay time correlated with the lowered supply voltage without hindering overall system performance. This method is most prevalent in SoCs that demand caches to be run as quickly as possible whereas CPUs and the rest of the SoC can operate at a decreased voltage while still satisfying the timing constraints of the overall system.

It is also possible to design systems with dynamic reconfiguration, which allows the choice between high-performance and energyefficient components in runtime depending on particular application [110], or alternatively trade energy for parallelism [169].

Others have proposed constructing a digital circuit that can dynamically tune  $V_{\rm th}$  and  $V_{\rm dd}$  to track the optimum operating voltages accordingly as the activity factor of the circuit is changed [130]. However, the actual implementation of such a system is extremely challenging because tracking the activity factor in an energy-efficient way is a difficult task. Furthermore, employing body-biasing regions and multiple power rails introduces significant area overheads. Moreover, the body-biasing technique is significantly less effective in newer CMOS technologies due to higher doping concentrations [134].

Asynchronous circuits can provide even higher flexibility in terms of the operating voltage and effective frequency. For example, a new methodology of building adaptive asynchronous controller to support a wide range of power and timing modes of operation which can be chosen during run-time has recently been proposed in [109].

#### 1.1.3 Scaling Implications on Power Dissipation

Over the last four decades, the semiconductor industry has followed a trend in CMOS scaling where the geometric dimensions of devices have been reduced by about 30% every 2-3 years [20, 61]. The foremost purpose behind this scaling trend is to decrease the cost of ICs fabrication [67]. With a 30% reduction in process size, area decreases by 50% (0.7×0.7=0.49) allows the doubling of number of CMOS transistors in the same silicon wafer die. Furthermore, a 30% reduction in device geometry drives to a 30% decrease in gate delay, resulting in an improvement of  $\frac{1}{0.7}$  in digital circuits performance [20]. Scaling the device dimensions and reducing supply voltage by 30% leads to an improvement in dynamic power consumption by 50% with each new CMOS generation, according to the "Dennard Scaling Law" [41]. This can be shown by substituting the decreased supply voltage and geometry into:

$$P_{dyn}(new) = (0.7 \times C_{eff}(old)) \times (\frac{1}{0.7} \times f(old)) \times (0.7 \times V_{dd}(old))^{2}$$

$$\approx 0.5 \times P_{dyn}(old) . \qquad (1.5)$$

The scaling of CMOS transistors has thus resulted in faster, smaller devices, and lower dynamic power dissipation. However, with each new generation of CMOS technology, the sub-threshold leakage current is increased, and this happens because of the demand to decrease the threshold voltage  $(V_{th})$  as a component of technology scaling [42, 140].

The continuing CMOS scaling trends predicted by the ITRS shows that the aggressive scaling of transistors to improve performance, reduce cost, and increase integration will continue to have a positive effect on dynamic power dissipation but at the expense of increased leakage power dissipation [141]. Accordingly, whilst leakage power consumption is already a problem now, it will become an even more pressing concern for future designs [89].

#### 1.1.4 Leakage energy reduction

Given the increasing predominance of leakage energy consumption in digital CMOS circuits, a plethora of studies are being conducted into decreasing it within these circuits. There are various techniques for overcoming leakage energy dissipation within a microprocessor as reported in the following Sections. Power gating is considered to be the most practical and effective technique to combat leakage [4, 90, 152] and is studied in Chapters 4, 5, and 6.

#### 1.1.4.1 Power gating

Power gating is a leakage minimization method that has obtained increasing attention over the last decade and is commonly used in many circuits, and at the micro architecture level [4, 90, 152]. Furthermore, it has recently been adopted in many system level designs such as Intel Core i7 microprocessor [26], and Nvidia Tegra microprocessors which is based on the ARM Cortex-A9. The substantial aim of power gating is to allow two modes of operation: an *active mode* in which a digital CMOS circuit can continue computing as normal, and a *sleep mode* in which the digital circuit can enter an idle state. Commonly, power gating facilitates the low leakage *sleep mode* by cutting off the supply voltage to the digital circuits and therefore can be termed as "shut-down power gating".

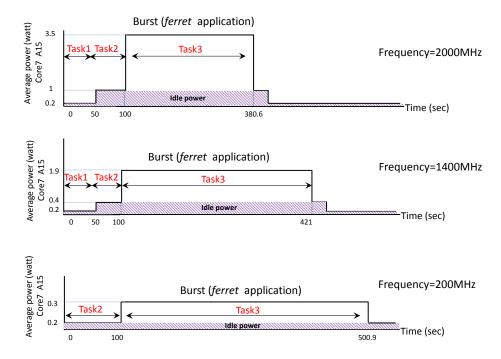

Fig. 1.2 describes a conceptual overview of the execution time and power dissipation of the CPU-intensive ferret application, where 4 LITTLE cores are fully operated with only one out of the four big cores kept active. This application is executed on the Exynos 5422 big.LITTLE octa-core heterogeneous platform. As the figure shows, the idle power of the big cores is experimentally measured as a function of operating frequency, as explained further in Chapter 6. In this experiment, three tasks separated by a period of time are observed. Firstly, no application is launched where only 0.2 watts are consumed by the system as indicated in "Task1". Secondly, the application is launched without executing, supply voltage and clock are remain operational, where the idle power consumed is a function of operating frequency and ranges from 1, 0.4, and 0.2 watt at 2000, 1400, and 200 MHz respectively. Finally, the application is instantiated and executed on core 7, which is the A<sub>15</sub> big core type, as indicated in "Task<sub>3</sub>". In this case, the total power consumption ranges from 3.5, 1.9, and 0.3 watt at 2000, 1400, and 200 MHz respectively. Therefore, power gating capitalizes on these idle periods to cut-off the supply voltage to the idle processor, and thereby leakage power dissipation in a heterogeneous many-core systems is reduced. When the idle period begins, a sleep signal is generated by the power gating controller which enables the power gating circuitry to cut off the supply voltage and place the processor into a low leakage state referred to as the *sleep mode* of operation.

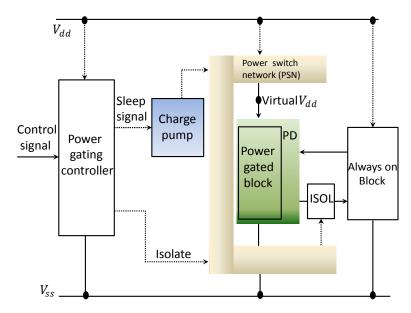

Fig. 1.3 illustrates a conceptual view of how power gating technique can be implemented in synchronous digital circuits. Normally, a power switch network (PSN), also referred to as sleep switches, is set in series with a computational logic block and provide power from the supply voltage to the entire block. Typically, these switches are based on CMOS transistors which comprise either PMOS power transistors referred to as *header* or NMOS power transistors referred to as *footer*. In this thesis, however, an emerging devices referred to as MEMS/NEMS have been adopted to target applications with low duty cycles mode

Figure 1.2: Idle power dissipation of Exynos 5422 big.LITTLE octa-core heterogeneous platform performing *ferret* application.

of operation as well as bursty workload behaviour. This is due to the high leakage energy dissipation of CMOS power transistors in such applications, especially when driving high capacitive loads. This in turn necessitates an increase in the width of these transistors to meet the on-state current requirement ( $I_{on}$ ), thereby increasing the leakage current ( $I_{off}$ ) in the idle state.

The source terminal of power switches in the PSN is connected to the supply voltage ( $V_{\rm dd}$ ) and the drain electrode becomes the effective power supply rail to the power gated block and is referred to as the virtual  $V_{\rm dd}$ . The state of these switches is controlled by a control signal generated by the power gating controller, as can be seen in Fig. 1.3. By shutting off the switches in the PSN, the virtual  $V_{\rm dd}$  discharges leading to leakage current ( $I_{\rm off}$ ) being decreased to that of the power gating switches [87]. This method of power gating is named as *coarse grain* power gating and the power gated block is often referred to as a *power domain* (PD).

To capitalise on CMOS scaling, as mentioned in Section 1.1.3, low-threshold transistors are being employed in the PD block to maintain high performance whereas high-threshold power switches are being used in the PSN to power gate the PD block. Adopting high-and low-threshold CMOS transistors in digital design is referred to as Multi-Threshold CMOS (MTCMOS)[87, 113]. Previous work has demonstrated that up to 25× reductions in leakage power can be achieved by employing this technique in the ARM926EJ CPU [87].

Figure 1.3: Modified architecture of coarse power gating technique based on [87].

However, a high-threshold power transistor has a low driving current ( $I_{on}$ ), thereby necessitating an increase in the number of parallel power switches in the PSN which in turn leads to an increase of the overall power dissipation in the power gating circuitry.

In practice, the inclusion of a PSN introduces a small IR drop, as these switches can typically be modelled as resistors when the digital circuit is in the active mode of operation [84]. It can be observed from Eq. 1.4, that when substituting virtual  $V_{\rm dd}$  with  $(V_{\rm dd}-V_{\rm drop})$ , where  $V_{\rm drop}$  is the voltage drop across the PSN, the propagation delay of the digital gates in the PD block is increased accordingly, thereby resulting in performance degradation. To that end, if the PSN is comprised of CMOS transistors, the effective on-state resistance of these transistors can be reduced by increasing their combined width. Furthermore, employing many power gating transistors in parallel can be used to limit the IR drop.

One challenge of implementing power gating in digital circuits is that the output of the PD blocks may ramp off very slowly, thereby causing large short circuit (crossbar) currents in blocks which are always powered on. To prevent these short circuit currents, isolation cells (ISOL) are typically employed between the output of the PD blocks and the input of the always on blocks. This is important because the signals float when the power is disconnected from the PD blocks and can cause short circuit currents in any always on blocks, thereby inducing functional problems and high energy consumption [87]. Isolation can be achieved by employing special isolation gates at the output of the PD blocks, including either "AND style" or "OR style" gates [87]. The assertion of the control signals to the isolation gates

and power gated switches necessitates careful timing to guarantee the valid functionality of the power gating technique. Typically, these signals are generated from a controller state machine which is referred to as *power gating controller*, and is shown in Fig. 1.3.

The present study proposes the employment of zero-leakage MEMS devices in the PSN to eliminate the leakage current by separating drain-source terminals via an air gap in the off-state. One of the challenges of implementing MEMS in any digital design is the requirement of a high actuation pull-in voltage  $(V_{pi})$ . To that end, the architecture of the power gating technique used in the previous study has been modified accordingly by incorporating a bootstrap charge pump block which is explained further in Chapter 4.

## 1.1.5 Applications

In the past, performance has been the impetus for the development of many applications due to the demand for interactive devices including tablet computers and smart phones, while, energy-efficiency has been kept as a desirable but not essential ultimate goal. However, there are a plethora of embedded applications where performance is not the primary target and instead energy-efficiency is the main constraint.

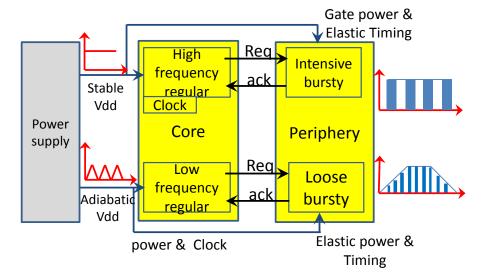

In this thesis a system level architecture is proposed for energy-constrained portable applications, as discussed in detail in Chapter 5. It is postulated that a computer system can be built in a similar fashion to biological systems where two types of operation, regular and burst, are incorporated such that a constantly active part has to be relatively slow and all the fast processing has to be done in specialised (peripheral) units.

Regular activities occur most of the time, and are intended to serve the needs of the entire system. These activities are typically determined by the dynamics of the system and overall structure. Intuitively, for large size systems regular activities are fast and for small systems they are slow. Typically, regular activities are synchronized effectively to the power supply as well as to the energy distribution inside the system, in an operation which is regulated itself in an energy efficient way. In fact, the supply itself is an activity which is regulated by such a central management core in the system. That is to say, it is better if something that is supposed to work all the time should be gated regularly rather than irregularly, and with a minimum of energy consumption during each power gating. The speed of change in each cycle is generally related with charging/discharging of energy buffers, and it is well known that if the speed of change is slow, as so called "adiabatic cycling", then the total amount of heat consumption during any charge/discharge cycles is significantly minimal [40, 171].

Bursty activities are not usually those regularly initiated by normal periodic cycles, but rather in response to the demand of interaction with external changes or conditions. Such activities that can be dealt with by special purpose peripheral subsystems, whose allotted energy resources are supplied by the action of the system's core, and whose operation are specified by their local dynamics and structure. Inspired by the biological evolution, the optimality of response to bursts is specified by the closet fit to the duty cycling required to respond to such bursts. The ultimate level of effectiveness in bursty modes will be specified corresponding to the amounts of energy resources allotted to these peripheral subsystems by the main core [171]. Intuitively, peripheral subsystems that operate in a bursty mode are normally locally timed (based on the limit cycles of the peripheral subsystem, that is to say, according to the characteristic inherent in its topology). The speed of charging/discharging of the energy buffers in the peripheral subsystems can be comparatively high because this is how they approach optimum energy utilisation in those bursts of activity [171]. For instance, a burst should be accompanied by minimum leakage energy as well as by the producing of an effective outcome within the allotted interval of power supply.

Power gating technique using zero-leakage MEMS relays has been employed in such a system, to capitalise on leakage energy reduction of burst activities, thus improving the total energy-efficiency. This is attributed to the fact that, unlike CMOS power switches, MEMS based power gating favour targeting complex architecture as well as burst nature of operation. Furthermore, MEMS relays can be preferably implemented in a non-invasive power gating applications due to their limited lifetime compare to that of CMOS counterparts, as explained further in Chapter 2.

As a result, to that end, power gating based on MEMS can also achieve more energy saving than CMOS counterparts in applications that operate at low throughput with a significantly long idle period. Wireless Sensor Networks (WSNs) are one of such type of applications. Typically, WSNs comprise of small sensing nodes that can be used for environment, habitat, and health monitoring. Hundreds of WSNs are placed out in the field to collect, process, and submit data over periods of months to years. Traditionally, the processor used in WSNs demands operating frequency in the range between kHz-MHz. Therefore, to maximize device life time average power dissipation of these devises are desirably set in the order of several μWs for 10s-10os. As an example, the Zebranet application uses a Texas Instruments MSP430 which operates at 32KHz and dissipates approximately 300µW [173]. Furthermore, biomedical devices are another area where high performance is inessential, but energy-efficiency is a key challenge. Moreover, the Internet of Things (IOTs) emerged applications are counted to be analogous to the WSNs necessitating similar low processor performance but one of the key challenges is constrained energy resources [12].

#### 1.2 THESIS ORGANIZATION AND KEY FINDINGS

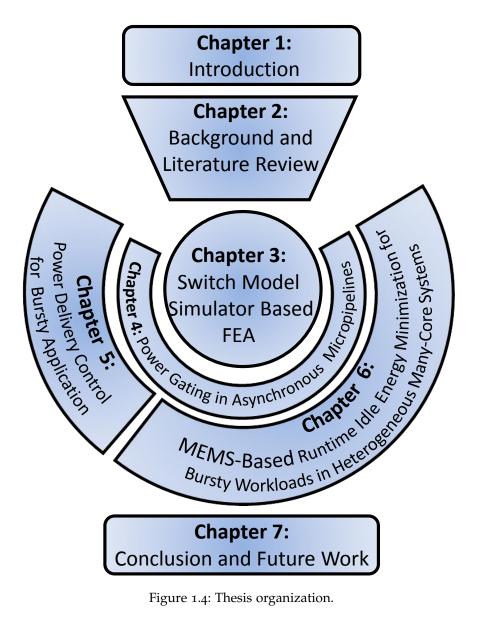

This thesis is organized into seven chapters, as shown in Fig. 1.4. The major contributions of this thesis is summarized as follows:

Chapter 1 "Introduction": introduces the motivations, objectives and structure of this thesis.

Chapter 2 "Background and Literature Review": This chapter provides a coherent overview of extensively adopted and recently reported state-of-the art MEMS/NEMS relays that can be used for particular kinds of applications. Subsequently, this survey can be the basis for any research intending to take advantages of using these emerging devices and to address their challenges. Furthermore, a device-level comparison of different types of MEMS/NEMS relays is provided. The result of this comparison highlights the future requirements for the characteristics of MEMS/NEMS so that they could be implemented in many emerging applications.

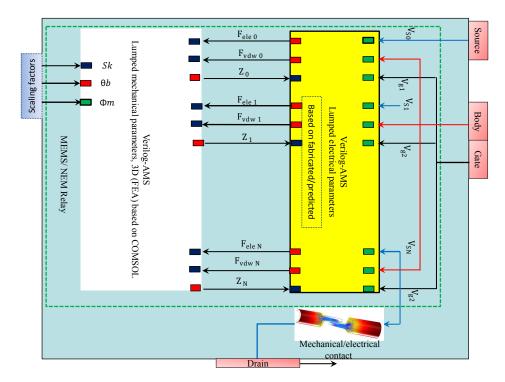

Chapter 3 "A Scalable Physical Model for Nano-Electro-Mechanical Relays": we propose a switch model simulator based on Verilog-AMS that can be plugged into the standard EDA software. To test the scalability of the proposed model we cross checked it against our analysis of a range of benchmark circuits. This chapter also investigates the modelling, designing and optimization of various MEM/NEM switches using 3D Finite Element Analysis (FEA) performed by the COMSOL multiphysics simulation tool. An extensive parametric sweep simulation is performed to study the energy-latency trade-offs of MEM/NEM relays. To accurately simulate MEMS/NEMS-based digital circuits, a Verilog-AMS model is proposed based on the evaluated parameters obtained from the multiphysics simulation tool. This allows an accurate calibration of the MEM/NEM relays with a significant reduction in simulation speed compared to that of 3D FEA executed on COMSOL tool.

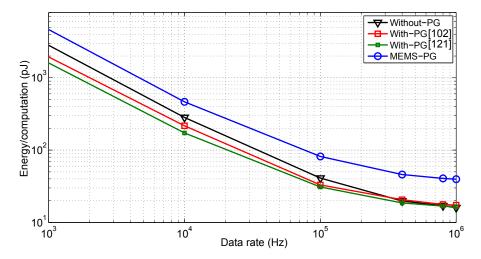

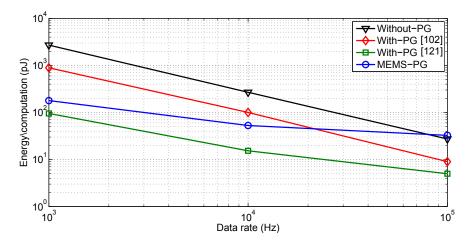

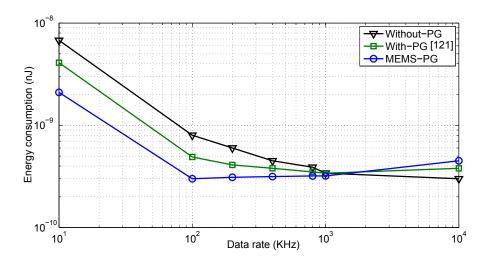

Chapter 4 "MEMS-based power gating of asynchronous micropipelines for ultra low energy driven computing": This study demonstrates the threshold at which our approach can achieve greater energy savings in relation to the design architecture and data rate of the input. Our proposed paradigm offers 69% energy improvements at data rate of 1KHz compared to a 39% achieved in the previous paradigm.

Chapter 5 "MEMS-Based Power Delivery Control for Bursty Applications" we propose to incorporate a power-switching network based on MEM relays to switch the SoC power-performance state (PPS) into an active mode while eliminating the leakage current when it is idle. Results show that even with today's large and high pull-in voltages, a MEM relay-based power switching network (PSN) can achieve a 1000× savings in energy compared to its CMOS counterpart for low duty cycle.

Chapter 6 "MEMS-Based Idle Energy Minimization for Bursty Workloads in Heterogeneous Many-Core Systems" we propose a novel MEMS-based zero-leakage current idle energy controller. Core to our approach is an integrated sleep mode management based on the performance energy states indicated by performance counters. For effective energy minimization we use a systematic optimization of the controller design parameters by adopting finite element analysis (FEA) in multiphysics COMSOL tool. We showed that for bursty workloads exemplified by a PARSEC benchmark application up to 55.5% energy savings can be achieved on an Exynos 5422 big.LITTLE octa-core heterogeneous platform. Further, our approach benefits from non-invasive design of the controller suitable for commercial off-the-shelf and low cost implementations.

Chapter 7 "Conclusions and Future Work" outlines the conclusions of the study and explore the implications of the presented work and draw the horizon for prospective future research.

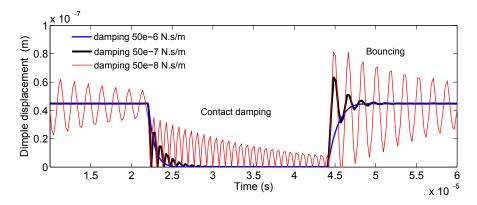

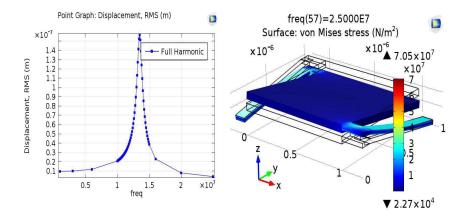

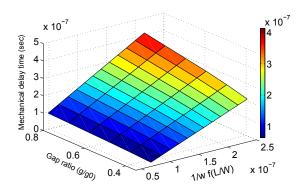

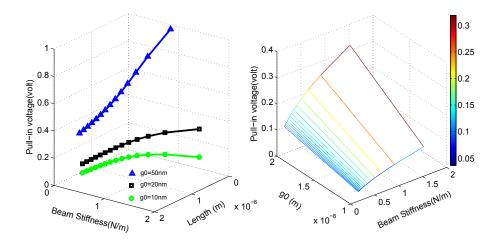

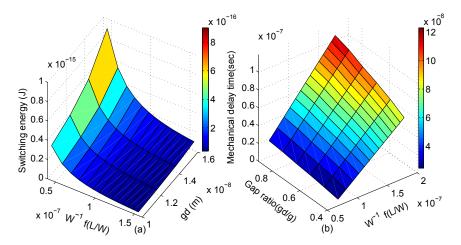

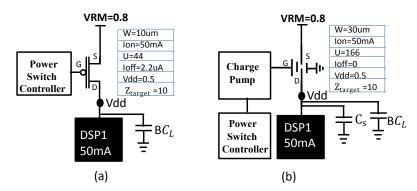

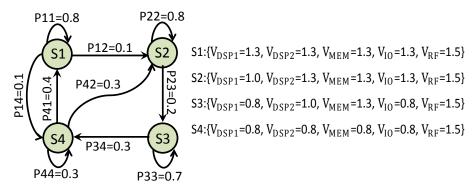

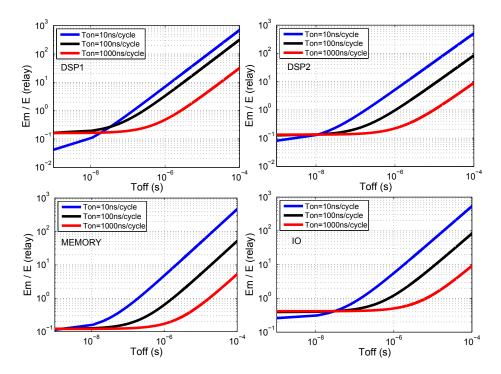

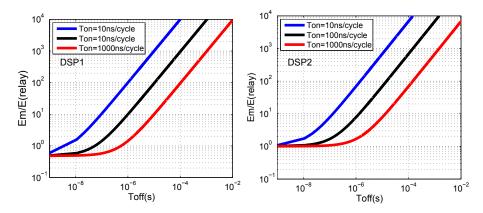

Figure 1.4: Thesis organization.