Microarchitectuur-onafhankelijke analytische prestatie- en vermogensmodellering van processors

Microarchitecture-Independent Analytical Processor Performance and Power Modeling

Sam Van den Steen

Promotor: prof. dr. ir. L. Eeckhout Proefschrift ingediend tot het behalen van de graad van Doctor in de ingenieurswetenschappen: computerwetenschappen

> Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. K. De Bosschere Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2018 - 2019

UNIVERSITEIT GENT

ISBN 978-94-6355-155-7 NUR 987 Wettelijk depot: D/2018/10.500/73

## **Examination Committee**

- Prof. dr. ir. Filip De Turck, *voorzitter* Vakgroep INTEC, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. dr. ir. Koen De Bosschere, *secretaris* Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. dr. ir. Lieven Eeckhout, *promotor* Vakgroep ELIS, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. dr. ir. Bart Dhoedt Vakgroep INTEC, Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. dr. Erik Hagersten Department of Information Technology Uppsala Universitet

- Dr. ir. Stijn Eyerman Intel Belgium

- Dr. Josué Feliu Pérez Parallel Architectures Group Universitat Politècnica de València

# Contents

| Examination Committee |              |        |                                                  | i     |  |

|-----------------------|--------------|--------|--------------------------------------------------|-------|--|

| Da                    | ankw         | oord   |                                                  | vii   |  |

| Sa                    | Samenvatting |        |                                                  |       |  |

| Sı                    | ımma         | ary    |                                                  | xiii  |  |

| Li                    | st of        | Figure | es                                               | xvii  |  |

| Li                    | st of        | Tables | 5                                                | xxi   |  |

| Li                    | st of        | Abbre  | eviations                                        | xxiii |  |

| 1                     | Intr         | oducti | ion                                              | 1     |  |

|                       | 1.1          | Motiva | ation                                            | . 1   |  |

|                       | 1.2          | Key C  | ontributions                                     | . 2   |  |

|                       |              | 1.2.1  | Micro-architectural Independent Analytical Model | . 2   |  |

|                       |              | 1.2.2  | Sampled Model Evaluation                         | . 3   |  |

|                       |              | 1.2.3  | Modeling Memory-Level Parallelism                | . 4   |  |

|                       |              | 1.2.4  | Open Sourced Framework                           | . 4   |  |

|                       | 1.3          | Other  | Research Activities                              | . 5   |  |

|                       | 1.4          | Thesis | Overview                                         | . 5   |  |

| <b>2</b>              | Bac          | kgrour | nd                                               | 7     |  |

|                       | 2.1          | Out-of | f-order Processor                                | . 7   |  |

|                       | 2.2          | Archit | ectural Simulation                               | . 10  |  |

|                       |              | 2.2.1  | Timing Simulation versus Functional Simulation   | . 10  |  |

|   |      | 2.2.2 Sampled Simulation $\ldots \ldots \ldots$    |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.3  | Performance Modeling                                                                                                                                               |

|   |      | 2.3.1 Empirical Modeling 13                                                                                                                                        |

|   |      | 2.3.2 Mechanistic Modeling $\ldots \ldots 14$                                                |

|   | 2.4  | Power Modeling                                                                                                                                                     |

|   | 2.5  | Interval Model                                                                                                                                                     |

|   |      | 2.5.1 I-Cache Misses                                                                                                                                               |

|   |      | 2.5.2 Branch Mispredictions $\ldots \ldots \ldots$ |

|   |      | 2.5.3 D-Cache Misses                                                                                                                                               |

|   |      | 2.5.4 Interval Model Equation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 21$                                                                  |

|   | 2.6  | Micro-Architecture Independent Modeling                                                                                                                            |

| 3 | Mod  | deling the Core 25                                                                                                                                                 |

|   | 3.1  | Improvements to the Interval Model                                                                                                                                 |

|   | 3.2  | CISC versus RISC                                                                                                                                                   |

|   | 3.3  | Instruction Dependences                                                                                                                                            |

|   | 3.4  | Issue Stage Modeling                                                                                                                                               |

|   | 3.5  | Branch Predictor Modeling 38                                                                                                                                       |

|   | 3.6  | Core Power Modeling 42                                                                                                                                             |

| 4 | Mod  | deling the Memory Subsystem 45                                                                                                                                     |

|   | 4.1  | Cache Hierarchy and the Interval Model                                                                                                                             |

|   | 4.2  | Cache Miss Rate Modeling                                                                                                                                           |

|   | 4.3  | Memory-Level Parallelism                                                                                                                                           |

|   | 4.4  | Cold-Miss MLP Model                                                                                                                                                |

|   | 4.5  | Stride-MLP Model                                                                                                                                                   |

|   | 4.6  | Modeling MSHRs                                                                                                                                                     |

|   | 4.7  | Main Memory Bus                                                                                                                                                    |

|   | 4.8  | Chained LLC Hits                                                                                                                                                   |

|   | 4.9  | Hardware Prefetching                                                                                                                                               |

|   | 4.10 | Memory Power Modeling                                                                                                                                              |

| 5 | Sam  | pling Methodology 65                                                                                                                                               |

|   | 5.1  | Instruction Mix Sampling                                                                                                                                           |

|   | 5.2  | Dependence Chain Interpolation                                                                                                                                     |

|   | 5.3 | Dependence Chain Sampling                                                                               | 9 |

|---|-----|---------------------------------------------------------------------------------------------------------|---|

|   | 5.4 | Memory Sampling 7                                                                                       | 0 |

|   |     | 5.4.1 Cache Miss Rates $\ldots \ldots 7$ | 0 |

|   |     | 5.4.2 Memory-Level Parallelism                                                                          | 1 |

| 6 | Eva | luation 7                                                                                               | 3 |

|   | 6.1 | Experimental Setup                                                                                      | 3 |

|   | 6.2 | Performance Prediction                                                                                  | 4 |

|   |     | 6.2.1 Absolute Accuracy                                                                                 | 4 |

|   |     | 6.2.2 Sampled Profiling 7                                                                               | 6 |

|   |     | 6.2.3 Micro-Architecture Independent Modeling                                                           | 8 |

|   |     | 6.2.4 Relative Accuracy across a Design Space                                                           | 9 |

|   | 6.3 | Power Prediction                                                                                        | 3 |

|   |     | 6.3.1 Absolute Accuracy                                                                                 | 3 |

|   |     | 6.3.2 Relative Accuracy across a Design Space                                                           | 4 |

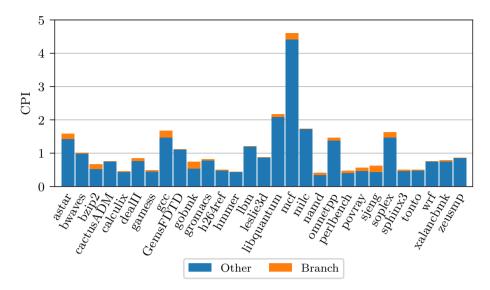

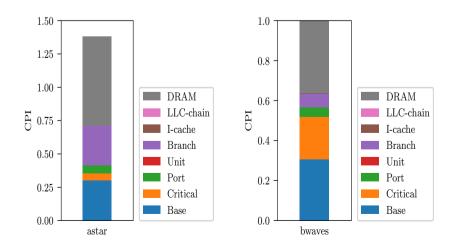

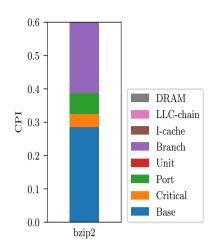

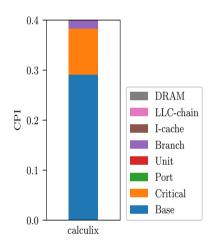

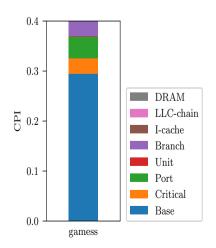

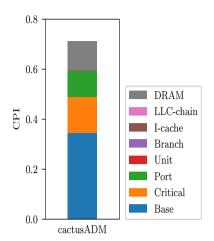

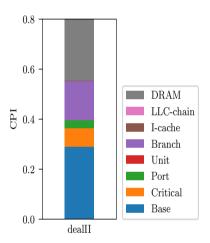

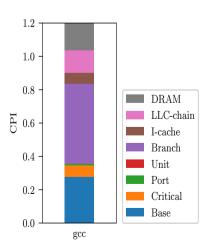

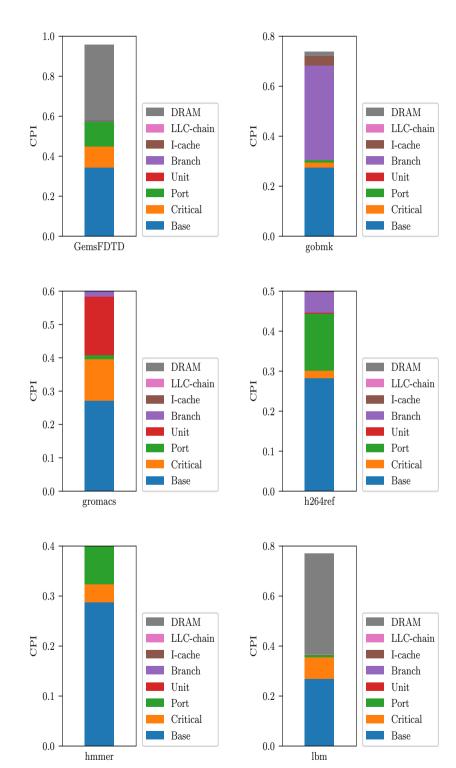

|   | 6.4 | CPI Stacks                                                                                              | 7 |

|   | 6.5 | Phase Analysis                                                                                          | 0 |

|   | 6.6 | Stride MLP and Prefetch Results                                                                         | 2 |

| 7 | App | plications 9                                                                                            | 7 |

|   | 7.1 | Understanding Processor Performance                                                                     | 7 |

|   | 7.2 | Optimizing Performance under Power Constraints 9                                                        | 9 |

|   | 7.3 | DVFS Exploration                                                                                        | 1 |

|   | 7.4 | Pareto Curves                                                                                           | 2 |

|   | 7.5 | Comparison to an Empirical Model                                                                        | 8 |

| 8 | Con | nclusion 11                                                                                             | 3 |

|   | 8.1 | Summary                                                                                                 | 3 |

|   | 8.2 | Future Work                                                                                             | 6 |

|   |     | 8.2.1 Multi-core Processors                                                                             | 6 |

|   |     | 8.2.2 SMT Processors                                                                                    | 6 |

|   |     | 8.2.3 Multithreaded Workloads                                                                           | 7 |

|   |     | 8.2.4 Different ISAs                                                                                    | 7 |

|   |     |                                                                                                         |   |

| Appendices   |              |     |  |

|--------------|--------------|-----|--|

| А            | CPI stacks   | 119 |  |

| В            | Phase plots  | 127 |  |

| $\mathbf{C}$ | Pareto plots | 139 |  |

| Bibliography |              |     |  |

## Dankwoord

Het uitvoeren van een doctoraatsonderzoek is een werk van lange adem. Gedurende een viertal jaar werk je grotendeels op één onderwerp om daar dan uiteindelijk een thesis over te schrijven. Bij momenten is de inspiratie ver te zoeken en heb je een grote dosis doorzettingsvermogen nodig. In dit dankwoord wil ik alle mensen bedanken die hebben meegeholpen om mijn doctoraat succesvol te beëindigen.

Eerst en vooral wil ik mijn promotor Lieven Eeckhout bedanken. Zonder hem was ik uiteraard nooit aan dit doctoraat kunnen starten. Voorts was zijn ervaring met het schrijven van papers onmisbaar. Zijn kritische ingesteldheid tijdens de vele *face-to-face meetings* dwongen mij om alle problemen van verschillende kanten te bekijken en te analyseren. Dit heeft heel veel bijgedragen tot de uiteindelijke kwaliteit van dit werk en uiteraard tot mijn ontwikkeling als onderzoeker. Verder wil ik ook Stijn Eyerman nog persoonlijk bedanken. Zijn continue begeleiding gedurende het eerste anderhalf jaar hebben ervoor gezorgd dat ik een vliegende start heb kunnen nemen met dit doctoraat.

I would like to thank all members of my jury. The internal defense that took place before finishing this thesis was, surprisingly, a fun experience. Furthermore, it is because of their critical questions and insightful feedback that I was able to further improve this thesis.

Uiteraard wil ik ook mijn vriendin, Helena, bedanken voor al haar steun de afgelopen jaren. Hoewel mijn doctoraat niet eenvoudig uit te leggen valt, heb ik toch meerdere keren pogingen mogen doen. Hierdoor kan ik haar tegenwoordig al wel eens aan het woord laten wanneer er iemand vraagt om mijn doctoraat uit te leggen, wat best handig is.

Vervolgens wil ik ook mijn ouders, broer en zus bedanken voor hun steun tijdens mijn studies en dit doctoraat. Er zijn momenten geweest dat mijn ouders een beetje skeptisch waren over mijn speciaal studietraject, maar gelukkig was ik koppig genoeg om het allemaal tot een goed einde te brengen.

Ten slotte wil ik uiteraard al mijn labogenoten bedanken. Gedurende de afgelopen jaren heb ik voornamelijk samengewerkt met Sander en vele discussies met hem gevoerd over alle uiteenlopende modellen in dit werk. Ook wil ik nog een aantal andere collega's en ex-collega's bedanken voor de ontspannende gesprekken en occasionele discussies: Ajeya, Cecilia, Jennifer, Josué, Kartik, Kristof, Mutaz, Shoaib, Trevor, Wim, Xia. Verder wil ik Bart nog bedanken voor de vele ontspannende roddels op momenten dat de zin om te werken net iets verder te zoeken was. Indien ik iemand vergeten te bedanken ben, wil dat uiteraard niets meer zeggen dan dat ik slecht ben in lijstjes maken.

> Sam Van den Steen Gent, September 26, 2018

## Samenvatting

Tot in het begin van de jaren 2000 focusten processorarchitecten zich voornamelijk op het versnellen van processors. Ze slaagden hierin door processors te voorzien van steeds complexere structuren zodat de software sneller uitgevoerd kon worden. Dit was mogelijk door de transistors – de bouwstenen van een processor – steeds verder te miniaturiseren. Hierdoor slaagden ze erin steeds meer transistors op het chipoppervlak te plaatsen en toch nog altijd constante vermogensdensiteit te garanderen. Echter, deze schalingstrend bekend als Dennard-schaling, bleek onmogelijk vol te houden.

Ondertussen explodeerde, door het ontstaan van het digitale tijdperk, het aantal mobiele toestellen met één of meerdere processors. Tegenwoordig wordt de meerderheid van processors, bedoeld voor de normale gebruikers, ingebouwd in mobiele toestellen zoals GSM's of *tablets*. Deze toestellen werken door middel van batterijen waardoor de processor best zo weinig mogelijk vermogen verbruikt en zo weinig mogelijk warmte genereert. Ondertussen moeten ze nog steeds voldoende prestatie bieden zodat de eindgebruiker niet de indruk heeft dat zijn/haar toestel 'traag' is. Niet enkel processors van mobiele toestellen ondervonden het nadeel van de stijgende vermogensdensiteit, zelfs processors in servers genereren tegenwoordig dusdanig veel warmte dat deze nog moeilijk efficiënt kan afgevoerd worden. Hierdoor moesten processorarchitecten hun focus op de prestatie van een processor (deels) verleggen naar een focus op energie- en vermogensefficiëntie.

De hoofdvraag voor processorarchitecten werd dus hoe de energie- en vermogensefficiëntie van een processor te verbeteren. Helaas is het fysiek produceren van een nieuw type processor om deze te evalueren tijdens het ontwerpsproces onmogelijk aangezien dit extreem duur en bijzonder tijdrovend is. Hedendaagse processors zijn bovendien heel complex en bestaan uit miljarden transistors waardoor het moeilijk is om ze te optimalizeren. Daarom vertrouwen processorarchitecten doorgaans op softwaresimulatie om nieuwe processors te evalueren tijdens de ontwerpsfase. Helaas zijn deze simulaties meerdere grootteordes trager dan het uitvoeren op een echte processor. Bovendien houdt de complexiteit van een processor in dat processorarchitecten doorgaans een ontwerpsruimte van processors moeten evalueren aangezien het effect van een optimalisatie niet altijd onmiddellijk duidelijk is. Dit leidt tot het probleem waarbij het ontwerpen van een processor, en dus de tijd tot deze

SAMENVATTING

geïntroduceerd wordt op de markt, vaak meerdere jaren in beslag neemt. Gezien de sterke concurrentie in deze markt, is dit onwenselijk.

Een alternatieve oplossing voor het evalueren van de prestatie van een processor en zijn vermogensverbruik is het inzetten van een mechanistisch analytisch model. Een mechanistisch model modelleert de eerste-orde interacties tussen een applicatie en de processor waarop deze uitvoert. Deze methodologie heeft als voordeel dat ze meerdere grootteordes sneller is dan simulatie, maar ook nog steeds vrij nauwkeurige resultaten produceert. Het gebruik van een mechanistisch analytisch model behelst doorgaans twee stappen: een profileringsstap (dit is de traagste stap) waarin applicatiekarakteristieken worden verzameld en een analysestap (die doorgaans slechts enkele seconden duurt) om de prestatie en het vermogensverbruik te voorspellen.

Het nadeel van de eerder voorgestelde mechanistische modellen is dat ze afhankelijk zijn van verschillende functionele simulaties om alle inputs te verzamelen. Hieronder vallen, onder meer, simulaties om het aantal incorrect voorspelde sprongen (sprongmissers) te bepalen, maar ook het aantal cachemissers en het aantal parallelle toegangen naar het hoofdgeheugen (Memory-Level Parallelism of MLP). Ook al zijn deze functionele simulaties veel sneller dan volledige tijdsgetrouwe simulaties, dewelke processorarchitecten normalerwijze gebruiken, toch introduceren ze nog steeds een niet-verwaarloosbare vertraging bij het evalueren van een grote processorontwerpsruimte.

Deze thesis pakt daarom twee problemen aan. Allereerst willen we hedendaagse, superscalaire, *out-of-order* x86-processors modelleren. Ten tweede willen we het gebruik van meerdere functionele simulaties om de inputs te verzamelen elimineren en zo het evalueren van een ontwerpsruimte versnellen. Daarom stellen we een nieuw, micro-architecturaal onafhankelijk, mechanistisch model voor dat zowel de prestatie als het vermogensverbruik van een processor kan voorspellen. Het grote voordeel van deze methodologie is dat de traagste stap, het verzamelen van het applicatieprofiel, slechts één keer moet uitgevoerd worden. Dit applicatieprofiel kan vervolgens gebruikt worden om er de inputs voor het analytisch model uit af te leiden en de prestatie en het vermogensverbruik van een waaier aan processors te voorspellen.

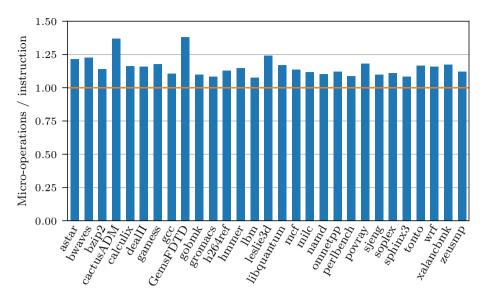

Om een mechanistisch model te ontwikkelen dat in staat is hedendaagse x86processors te modelleren, vertrekken we van het eerder voorgestelde intervalmodel [32]. Eerst stellen we een aantal aanpassingen voor aan de basiscomponent die de maximaal haalbare prestatie voorspelt wanneer er geen sprong- of cachemissers zijn. Het eerder voorgestelde intervalmodel maakte gebruik van instructies als kleinste werkeenheid, maar om x86-processors te modelleren, moeten we dit vervangen door het aantal micro-operaties afgeleid van de dynamische instructiestroom. Bovendien delen we het aantal microoperaties door de effectieve *dispatch*-snelheid, in plaats van deze te delen door de fysieke *dispatch*-breedte. *Dispatch* refereert hier naar de pijplijnstap waarbij instructies van de *front-end* van de pijplijn naar de *back-end* gestuurd worden. De effectieve *dispatch*-snelheid modelleert contentie in de processor ten gevolge van een (deels) ongebalanceerde processorpijplijn. Ze modelleert contentie door afhankelijkheden in de instructiestroom en contentie in de *issue*-stap in de processor ten gevolge van de functionele eenheden en *issue*-poorten. Voorts tonen we aan dat het modelleren van contentie in de processorkern vereist dat ons mechanistisch model wordt geëvalueerd op een zeer kleine tijdsschaal met behulp van wat wij *micro-traces* noemen. Dit is intuïtief logisch aangezien contentie doorgaans in bursts optreedt en op een grote tijdsschaal enkel uitgemiddeld gedrag gemodelleerd kan worden.

Voorts introduceren we extra modelleringsstappen die begrenzingen met betrekking tot geheugentoegangen modelleren. We stellen voor om de impact van miss status handling registers (MSHR) te modelleren en voegen een component toe die de extra vertragingen geïntroduceerd door het parallel uitvoeren van geheugentoegangen modelleert. Bovendien introduceren we een nieuwe vertragingscomponent die van elkaar afhankelijke toegangen naar het laatste cacheniveau modelleert. Deze term is vereist omdat een *out-of-order* processor normaal de tijd die gewacht moet worden op data kan verbergen door andere instructies uit te voeren. Echter, het laatste niveau van de cacheniërarchie is dusdanig traag dat deze veronderstelling niet altijd opgaat, zeker wanneer meerdere toegangen naar dit laatste cacheniveau afhankelijk zijn van elkaar.

Naast het aanpassen van het eerder voorgestelde intervalmodel om nauwkeurig prestatie en vermogensverbruik van een x86-processor te voorspellen, was het ook de bedoeling om de inputs verkregen met behulp van functionele simulatie te vervangen door inputs berekend uit micro-architectuur onafhankelijke statistieken. Daarom moeten we het aantal sprongmissers, cachemissers en MLP kunnen voorspellen. Het aantal sprongmissers voorspellen we aan de hand van een metriek die lineaire sprongentropie genoemd wordt. Deze metriek modelleert de (on)voorspelbaarheid van spronginstructies en laat toe de nauwkeurigheid van een sprongvoorspeller te schatten [22]. Het voorspellen van cachemissers gebeurt door het profileren van een distributie van hergebruiksafstanden. Deze hergebruiksafstanden kunnen, door gebruik te maken van StatStack [28], omgevormd worden tot een distributie van stack distances. Het voordeel van stack distances is dat deze gebruikt kunnen worden om cachemissers te voorspellen voor least-recently used (LRU) cachehiërarchieën. Het modelleren van MLP bleek één van de moeilijkste aanpassingen te zijn omdat dit afhankelijk is van verschillende factoren. We stellen twee methoden voor, het cold-miss MLP model en het stride-MLP model, die steunen op verschillende veronderstellingen gerelateerd aan het burstgedrag van geheugentoegangen.

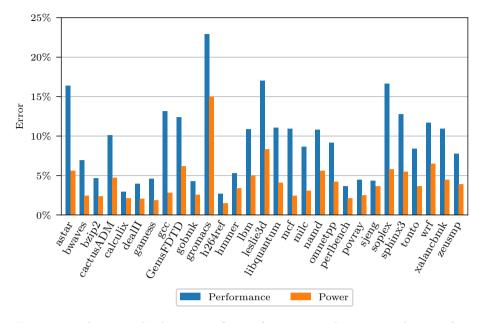

Gebruik makend van de voorgestelde aanpassingen en inputs afgeleid uit micro-architectuur onafhankelijke statistieken voorspellen we de prestatie en het vermogensverbruik van een referentie processorarchitectuur. De gemiddelde voorspellingsfouten zijn slechts 7.6% en 3.4% voor, respectievelijk, de prestatie en het vermogensverbruik in vergelijking tot cyclus-getrouwe simulaties. Ook tonen we hoe het model gebruikt kan worden om CPI-stapels te bouwen. Deze stapels zijn zeer nuttig om te analyseren waaraan de uitvoeringstijd van een applicatie gespendeerd wordt op een bepaalde processor. Het hoofddoel van een micro-architectuur onafhankelijk mechanistich model is het versnellen van de evaluatie van een ontwerpsruimte. Gebruik makend van dit model kunnen we een ontwerpsruimte, bestaand uit 243 processors en 29 applicaties, evalueren in 11,5 uur. Dezelfde ontwerpsruimte evalueren met behulp van simulaties, die uitvoeren aan een snelheid van 0,5 miljoen instructies per seconde, (MIPS) zou 150 dagen in beslag nemen. Het eerder voorgestelde intevalmodel kan de ontwerpsruimte evalueren in 200 uur ervanuit gaande dat de functionele simulaties een snelheid van 1,5 MIPS halen. Dit betekent dat we een versnelling van  $315 \times$  behalen ten opzichte van gedetaileerde simulatie en  $18 \times$  vergeleken ten opzichte van het eerder voorgestelde intervalmodel. Indien we onze voorspellingen met betrekking tot de prestatie en het vermogensverbruik voor de volledige ontwerpsruimte evalueren, behalen we een nauwkeurigheid van respectievelijk 9.3% en 4.3% voor prestatie- en vermogensvoorspellingen.

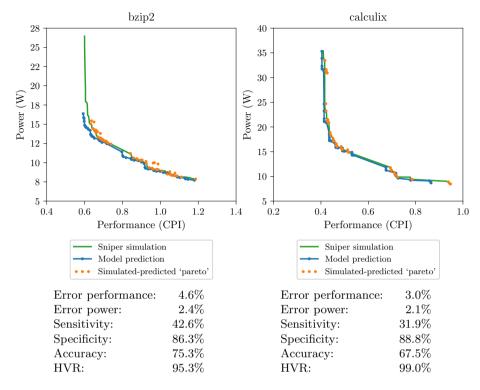

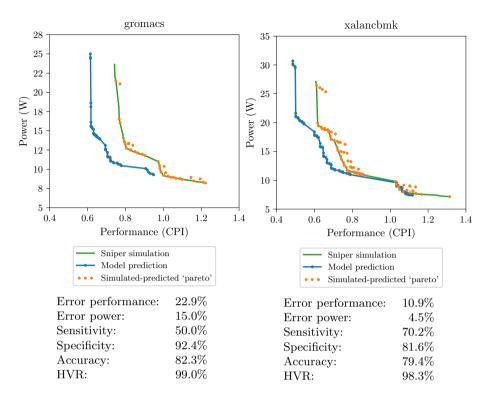

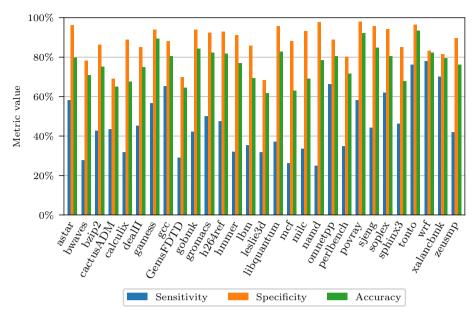

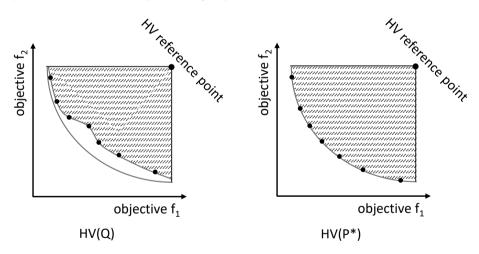

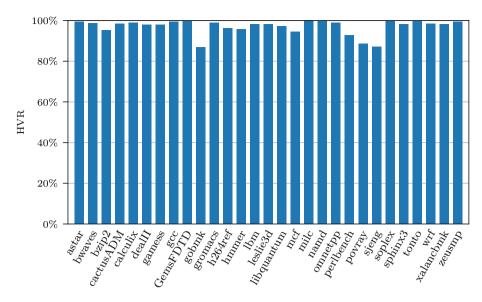

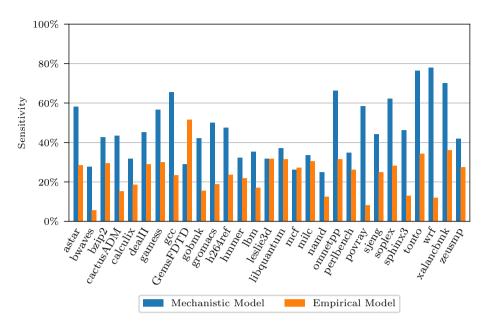

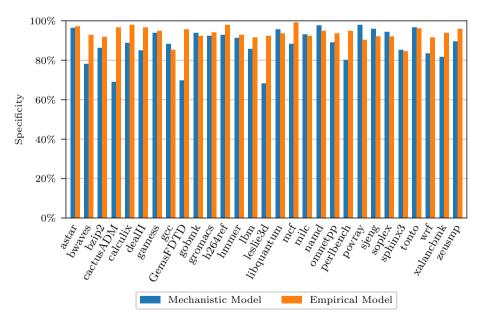

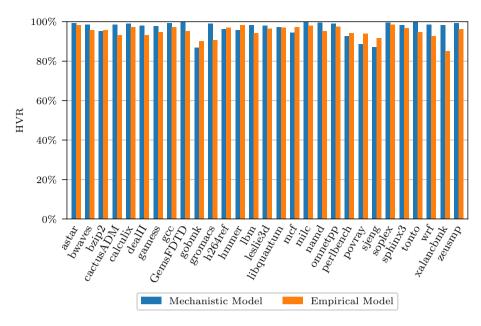

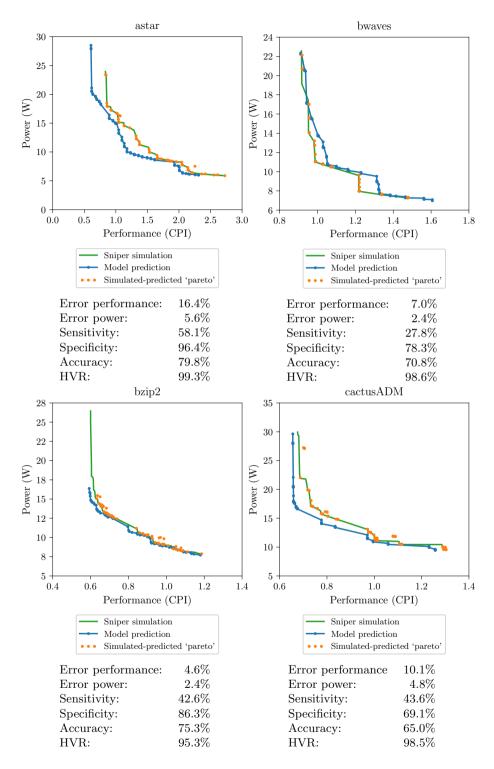

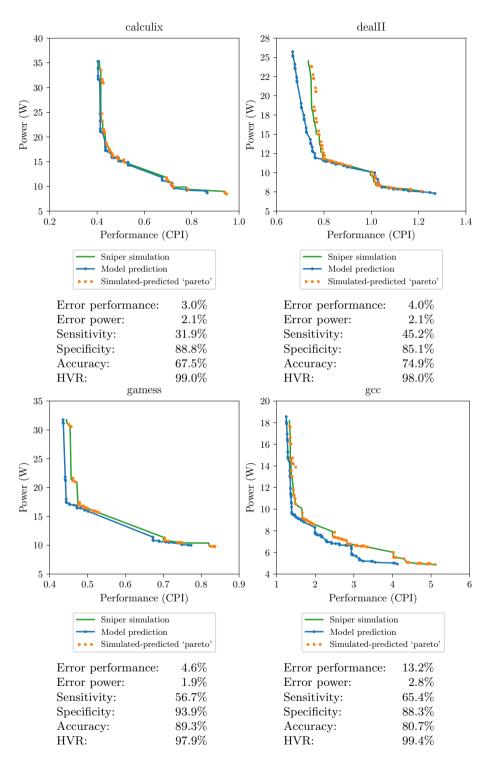

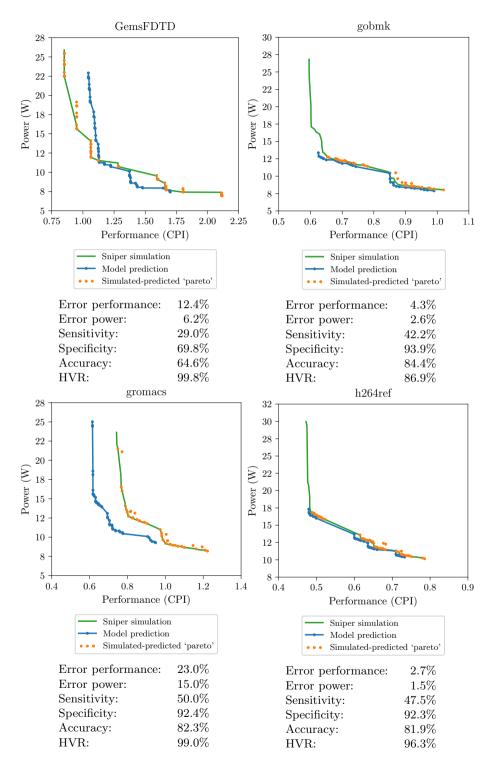

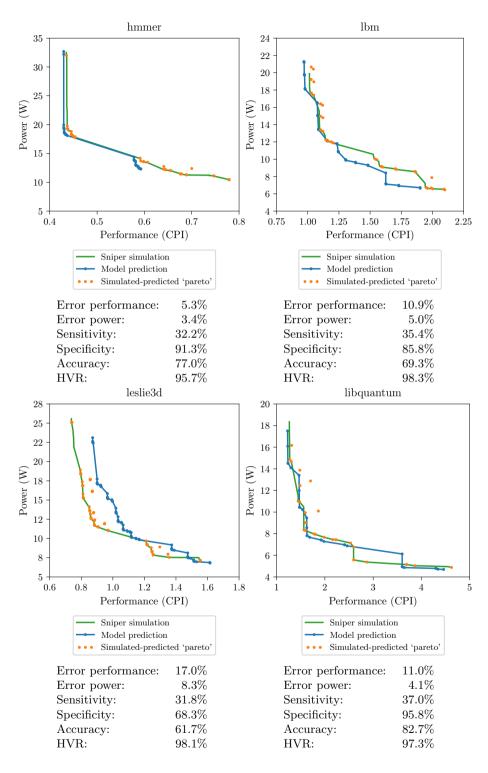

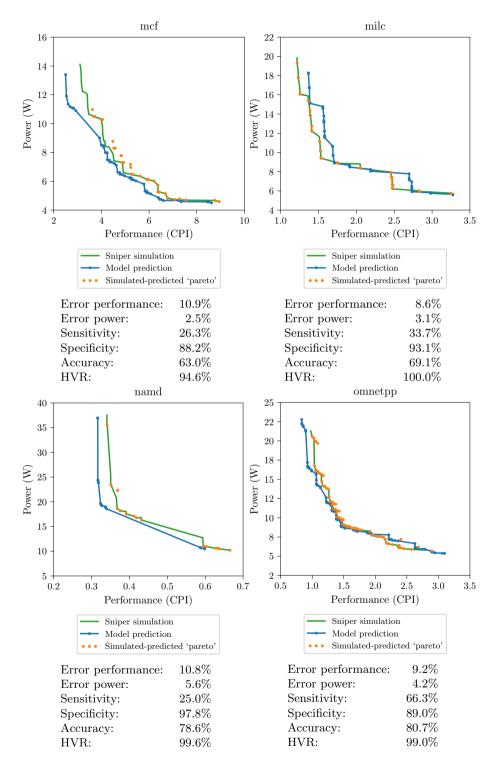

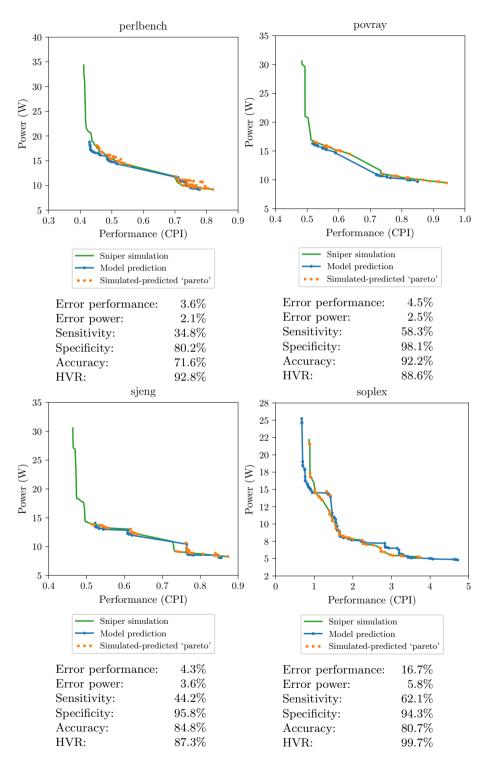

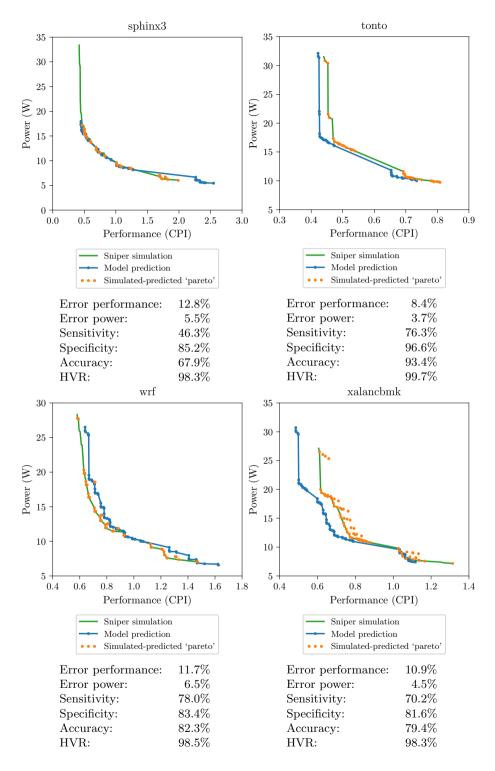

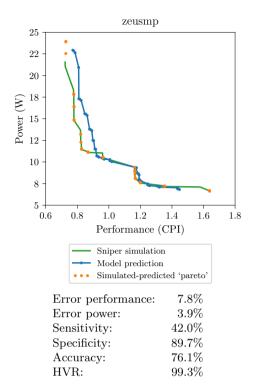

Ten slotte tonen we de bruikbaarheid van het model aan door Paretofronts te construeren die de afweging visualiseren tussen prestatie en vermogensverbruik en daardoor gebruikt kunnen worden om interessante processorarchitecturen uit een ontwerpsruimte te selecteren. Deze toepassing illustreert de belangrijkste eigenschap van ons model, namelijk de relatieve nauwkeurigheid. Deze eigenschap maakt het immers mogelijk om verschillende processors met elkaar te vergelijken, ongeacht de eventuele absolute fout op de prestatie- en/of vermogensvoorspellingen. We vatten de nauwkeurigheid van het filteren van de ontwerpsruimte samen met behulp van vier metrieken: sensitiviteit, specificiteit, nauwkeurigheid en HVR. Deze metrieken geven weer hoe goed we erin slagen Pareto-optimale ontwerpen te selecteren over de volledige ontwerpsruimte. De gemiddelde waardes voor sensitiviteit, specificiteit, nauwekeurigheid en HVR zijn respectievelijk 46.2%, 87.9%, 76.8% en 97.0%. De nauwkeurige specificiteitswaarde toont aan dat we erin slagen om de meeste niet-Pareto optimale architecturen weg te filteren terwijl de HVR-metriek aantoont dat we architecturen over de volledige ontwerpsruimte vinden. De gemiddelde waarde voor sensitiviteit is relatief laag, wat erop wijst dat we niet alle Pareto-optimale architecturen vinden. Dit is echter geen groot probleem omdat Pareto-optimale ontwerpen vaak voorkomen in clusters en één van die ontwerpen vinden reeds voldoende is. Globaal genomen toont dit aan dat we er in slagen om een ontwerpsruimte te exploreren en de Paretooptimale ontwerpspunten te identificeren.

Deze thesis vat het werk samen ter ontwikkeling van een micro-architectuur onafhankelijk model voor hedendaagse x86-processors dat in staat is om, in vergelijking met cyclus-getrouwe simulatie, de prestatie en het vermogensverbruik van een processor nauwkeurig te voorspellen. We tonen verder aan dat dit model een significante versnelling behaalt ten opzichte van zowel gedetailleerde simulatie als eerder voorgestelde mechanistische modellen. Dit maakt het mogelijk om grote ontwerpsruimtes van processors te evalueren en interessante processors te identificeren.

## Summary

Up until the early 2000's, processor architects focused mainly on developing faster processors. They achieved this through implementing increasingly complex structures into processors to optimize application execution. This was feasible because they could miniaturize transistors – the processor's building blocks – and include more of them on the same processor chip area while still maintaining constant power density. However, this scaling trend, known as Dennard scaling, started to break down shortly afterwards.

Meanwhile, the advent of the digital age introduced an incredible increase in mobile devices containing one or more processors. Nowadays, a majority of processors meant for the consumer market are built into mobile devices such as cell phones or tablets. These devices run on a battery necessitating the processor to consume as little power and generate as little heat as possible while still achieving sufficient performance for the end-user not to experience his/her device as being 'slow'. However, the problem is not limited to processors embedded in mobile devices, due to the increasing power density, even processors in high-end systems generate too much heat to dissipate easily. This required processor architects to not only focus on processor performance, but also on energy and power efficiency.

The main question became how to improve the energy efficiency of a processor. Unfortunately, physically producing new processor prototypes to evaluate during the design cycle is infeasible because this would be extremely expensive and time-consuming. Contemporary processors are also incredibly complex consisting of billions of transistors making it difficult to design and optimize. Therefore, processor architects generally rely on software simulation to design new processors. However, processor simulations are multiple orders of magnitude slower compared to a real execution on a processor. Furthermore, since contemporary processors are so complex, a processor architect will often need to evaluate a design space consisting of multiple different processors, as the effect of an optimization might not be obvious from the start. This introduces the problem where the processor design cycle, and thus time-to-market for a new processor often encompasses several years. Because of the fierce competition in the market of processors, this is undesirable.

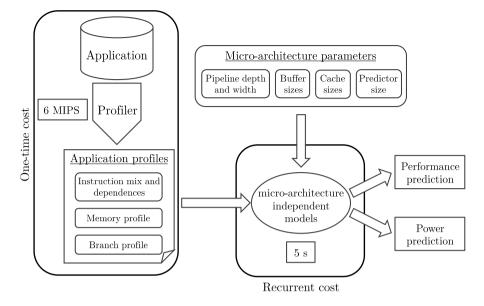

An alternative to evaluating processor performance and power consumption using simulation is mechanistic analytical modeling. A mechanistic model models the first-order interactions between the application and the processor it is executing on. The approach of modeling rather than simulating a processor has the advantage that it is orders of magnitude faster while still achieving relatively good accuracy. Employing a model to predict performance and power usually consists of two steps, a profiling phase (which is the slowest step) to collect application characteristics and an analysis phase (which takes only a couple of seconds) to predict performance and power.

The downside of previously proposed mechanistic models is that they rely on several functional simulations to collect the required inputs such as the number of branch mispredictions, cache miss rates, and memory-level parallelism (MLP). While these functional simulations are significantly faster than the full-blown timing-based simulations generally employed by processor architects, they still incur a significant slowdown for evaluating a large processor design space.

This thesis consists of two main objectives. Firstly, we want to model contemporary superscalar out-of-order x86-based processors. Secondly, we want to eliminate the use of several functional simulations to obtain inputs for the mechanistic model in order to speed up design space exploration. Therefore, we propose a new micro-architecture independent mechanistic model to predict both performance and power consumption. The key advantage of this approach is that the slowest step, collecting the application profile, only has to be performed once. This application profile can then be used to predict the inputs to the analytical model for predicting processor performance and power consumption.

To develop a mechanistic model capable of modeling contemporary x86based processors, we modify the previously proposed interval model [32]. To achieve this, we modify the base component which predicts the maximum achievable performance in the absence of miss events. The previously proposed interval model used instructions as smallest unit of work, but to model x86-processors, we have to replace this with the number of micro-operations derived from the dynamic instruction stream. Furthermore, instead of dividing the number of micro-operations by the physical dispatch width, we introduce a new divisor called the effective dispatch rate. The effective dispatch rate models contention within the processor due to imbalances in the processor pipeline. It models contention due to dependences within the instruction stream and contention due to the functional units and issue ports in the issue stage. We also show that modeling contention in the processor core requires evaluating our mechanistic model on very small time scales using what we call microtraces. Intuitively, this makes sense as contention will mostly occur due to bursty behavior and large time scales are only suitable to capture averaged-out behavior.

We also introduce extra modeling steps to capture limitations related to the memory requests performed by the processor. We propose to model the impact of miss status handling registers (MSHR) and add a component modeling the extra queuing delay introduced by executing parallel accesses to main memory. Furthermore, we introduce a new type of penalty called last-level cache (LLC) chaining. While out-of-order processors can usually hide the latency of load instructions fetching data from the cache hierarchy, the last level of the cache hierarchy cannot always provide data fast enough for the processor to hide its latency, especially when multiple loads depend on each other.

Next to modifying the previously proposed interval model to accurately predict performance and power for x86-processors, we also replace the inputs extracted from the functional simulations by inputs calculated using microarchitecture independent inputs. To achieve this, we have to predict the number of branch mispredictions, cache miss rates and MLP. Predicting the number of branch mispredictions is achieved through a metric called linear branch entropy which captures the (un)predictability of branch instructions [22]. For predicting cache miss rates we collect a reuse distance distribution which is transformed into a stack distance distribution using StatStack [28]. We can use the latter distribution to predict cache miss rates for least-recently used (LRU) cache hierarchies. Modeling MLP accurately proved to be the most difficult hurdle to overcome as it depends on various factors. We propose two different techniques called the cold-miss MLP and stride-MLP which leverage different assumptions related to the burstiness of memory accesses.

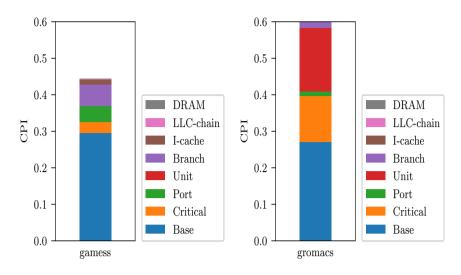

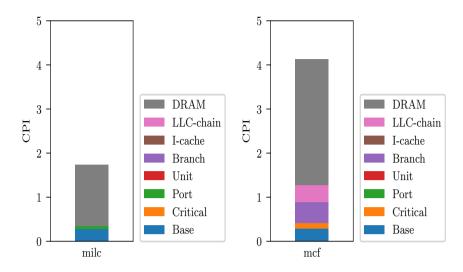

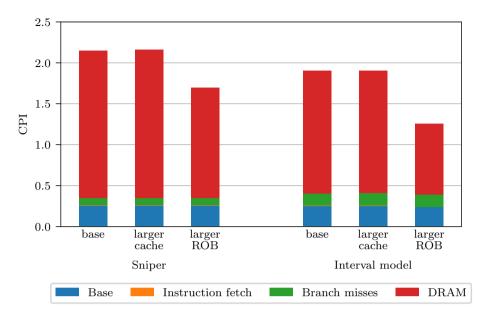

Using the proposed modifications and inputs derived from microarchitecture independent metrics we predict the performance and power consumption for a reference processor design. The average prediction errors are as low as 7.6% and 3.4% for performance and power predictions, respectively, compared to cycle-level simulation. We show the convenience of the model by generating so-called CPI stacks. These stacks are extremely useful to analyze where the cycles go when executing an application on a specific processor design.

The main goal of developing a micro-architectural independent mechanistic model is to speed up design space evaluation. Using the new model we can evaluate a design space of 243 processor architectures and 29 applications in 11.5 hours. Evaluating the same design space using detailed simulation running at 0.5 million instructions per second (MIPS) would take 150 days, while the previously proposed interval model would take 200 hours assuming the functional simulations can progress at a speed of 1.5 MIPS. This means we achieve a speedup of  $315 \times$  compared to detailed simulation and  $18 \times$  compared to the previously proposed interval model. Comparing our predictions to cyclelevel accurate simulation, we achieve an average prediction accuracy of 9.3% and 4.3% for performance and power, respectively, across the large processor design space considered in this thesis.

We demonstrate the usefulness of the developed micro-architectural independent model by constructing Pareto frontiers visualizing performance-power trade-offs and pruning the design space for interesting designs. This application shows the most important characteristic of our model, namely its relative accuracy. After all, even if the absolute prediction error is significant, as long as all errors across different processor designs exhibit the same bias, it is possible to accurately compare multiple different designs. We summarize the accuracy of pruning the design space exploration using the sensitivity, specificity, accuracy and HVR metrics. These metrics describe how well we can predict the actual Pareto-optimal processor architectures and whether we are able to find designs of interest over the complete range of the design space. The average values for sensitivity, specificity, accuracy and HVR are 46.2%, 87.9%, 76.8% and 97.0%, respectively. The good specificity value shows that we are able to exclude most non-Pareto optimal designs while the HVR metric shows that we find designs over the complete design space. The average sensitivity value is rather low, indicating we do not find all designs that are Pareto-optimal, but this is less of a problem as many Pareto-optimal processor designs are clustered and finding only one of those is acceptable. Overall, the Pareto-plots and these metrics indicate we are able to prune the design space accurately.

To summarize, this work describes a micro-architecture independent model for contemporary x86-based processors with good relative performance and power prediction accuracy compared to cycle-level simulations. Furthermore, we show that this model offers a significant speedup over simulation and previously proposed mechanistic models when evaluating a processor design space and identifying interesting processor designs.

# List of Figures

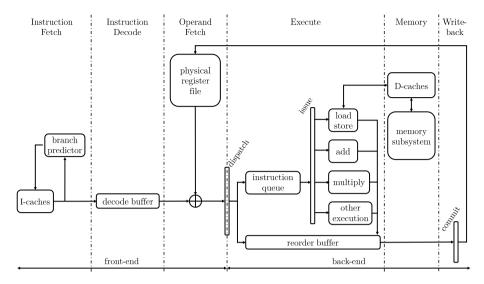

| 2.1  | Schematic overview of the pipeline of an out-of-order processor.                                   | 8  |

|------|----------------------------------------------------------------------------------------------------|----|

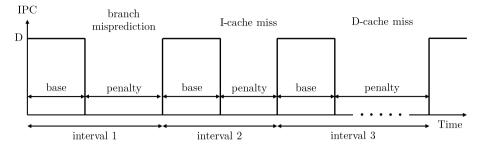

| 2.2  | Program execution according to the interval model                                                  | 17 |

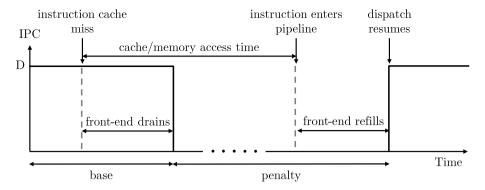

| 2.3  | Interval breakdown of an instruction cache miss. $\ldots$                                          | 18 |

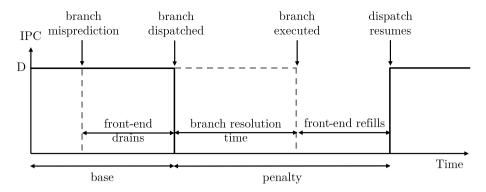

| 2.4  | Interval breakdown of a branch misprediction                                                       | 19 |

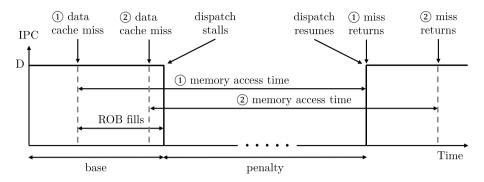

| 2.5  | Interval breakdown of a long-latency load data cache miss                                          | 20 |

| 2.6  | Schematic overview of the micro-architecture independent interval model.                           | 22 |

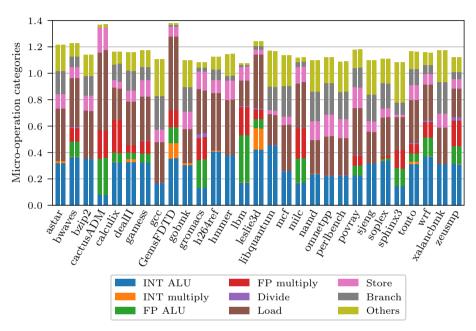

| 3.1  | Number of micro-operations per instruction for all SPEC CPU 2006 benchmarks                        | 27 |

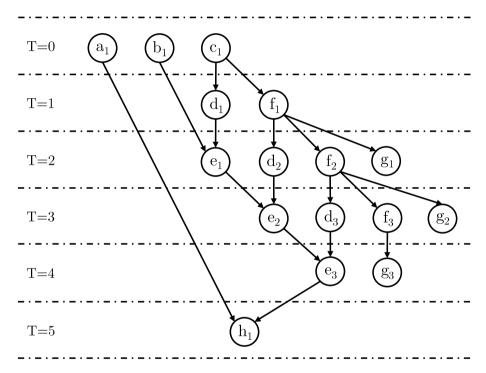

| 3.2  | Example of a data dependence graph                                                                 | 28 |

| 3.3  | Example of the calculation of instruction dependence chains                                        | 31 |

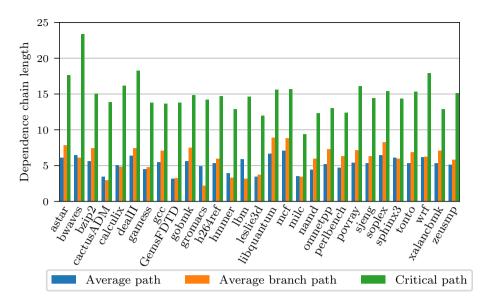

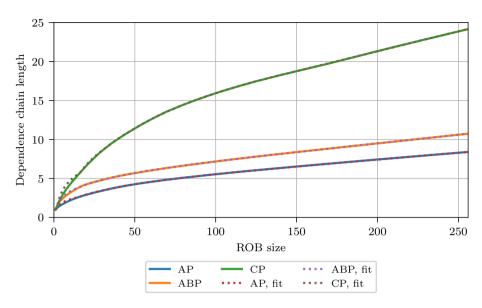

| 3.4  | Instruction dependences: average path, average branch path and critical path.                      | 32 |

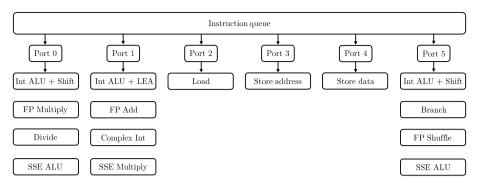

| 3.5  | Example of the Nehalem issue stage                                                                 | 34 |

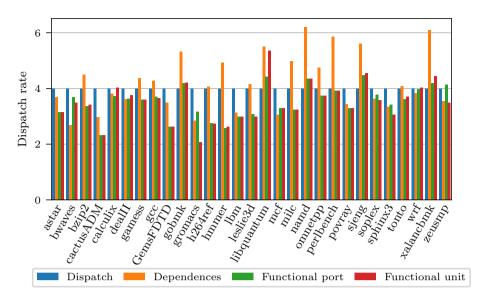

| 3.6  | Visualization of the factors limiting the effective dispatch rate.                                 | 36 |

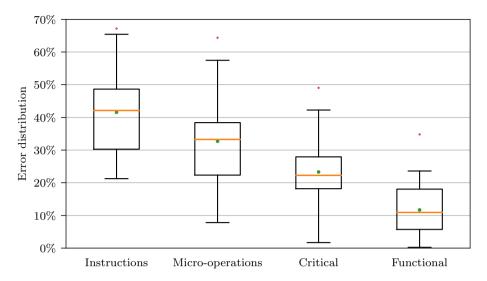

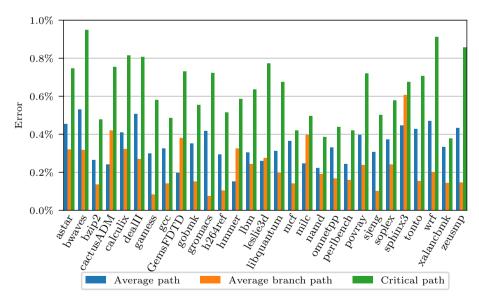

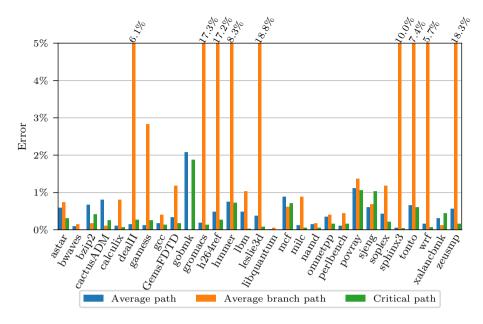

| 3.7  | Decrease in prediction error due to the different limitations for<br>the effective dispatch rate   | 37 |

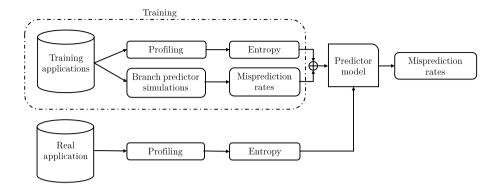

| 3.8  | Visualization of the training step and application profiling to obtain branch misprediction rates. | 40 |

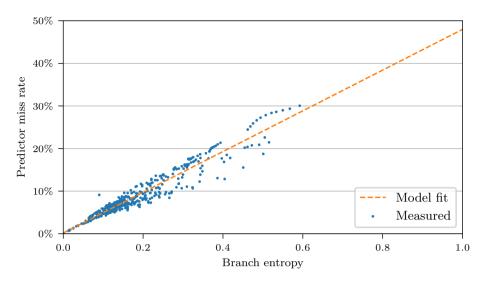

| 3.9  | Linear fit for branch entropy and missprediction rates for more<br>than 400 experiments            | 41 |

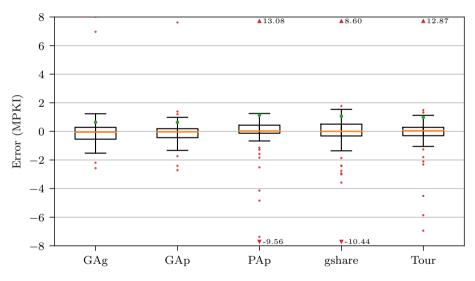

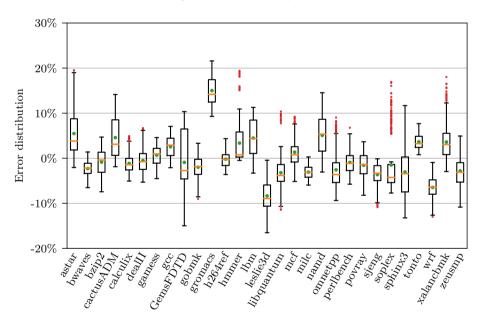

| 3.10 | Box-and-whiskers plot for five different branch predictors show-<br>ing the prediction accuracy.   | 41 |

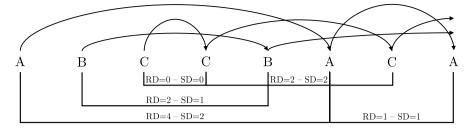

| 4.1  | Memory address stream with indicated reuses and respective stack distances                         | 47 |

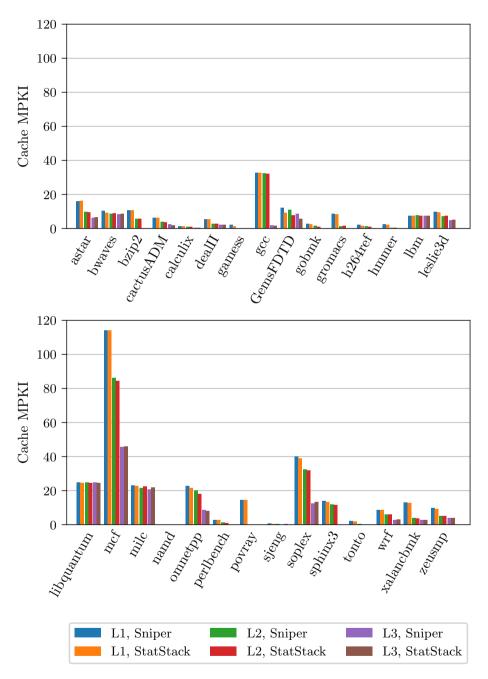

| 4.2  | Estimated cache misses for a three-level cache hierarchy with sizes 32, 256 and 8192 KB.                               | 48 |

|------|------------------------------------------------------------------------------------------------------------------------|----|

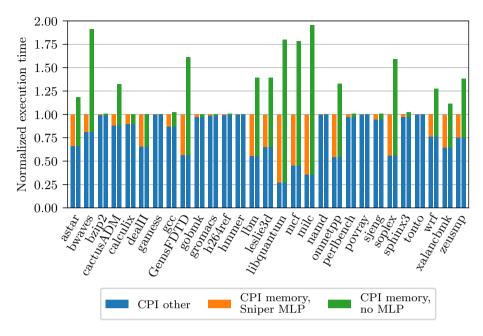

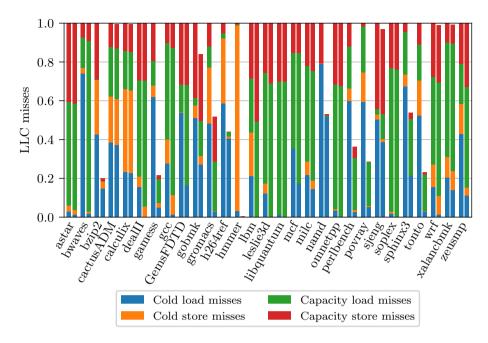

| 4.3  | Normalized execution time with and without MLP modeling                                                                | 50 |

| 4.4  | Breakdown of cold and capacity load and store misses                                                                   | 51 |

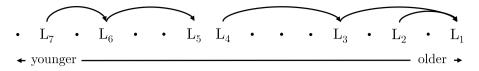

| 4.5  | Example of a load dependence distribution                                                                              | 53 |

| 4.6  | Illustrative virtual memory access stream                                                                              | 54 |

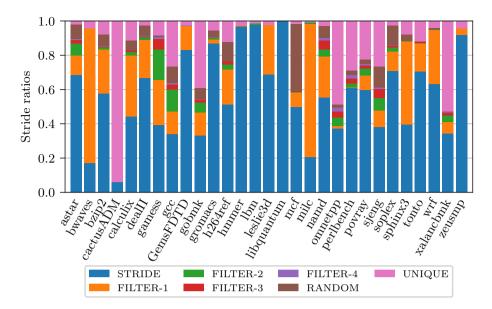

| 4.7  | Ratio of all stride categories per benchmark                                                                           | 56 |

| 4.8  | Visualization of the queuing delay due to multiple concurrent memory accesses                                          | 59 |

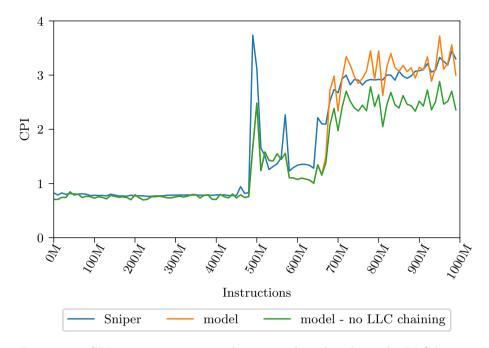

| 4.9  | CPI variation over time for gcc with and without the LLC hit chaining component.                                       | 61 |

| 4.10 | Example of the workings of a stride prefetcher                                                                         | 63 |

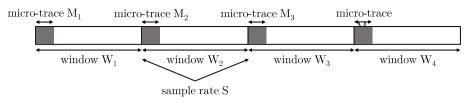

| 5.1  | Visualization of the micro-traces and windows in an instruction stream.                                                | 66 |

| 5.2  | Comparison of the sampled and non-sampled instruction mix                                                              | 66 |

| 5.3  | Comparison between profiled and interpolated AP, ABP and CP dependence chains for <i>astar</i>                         | 68 |

| 5.4  | Error on the dependence chain lengths due to interpolation be-<br>tween ROB sizes                                      | 68 |

| 5.5  | Error on the dependence chain lengths due to sampling                                                                  | 69 |

| 5.6  | Relative contribution of the branch component to the total exe-<br>cution time                                         | 70 |

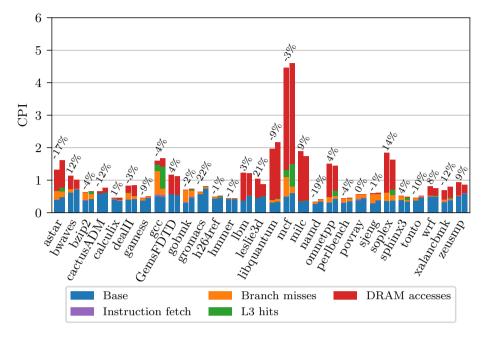

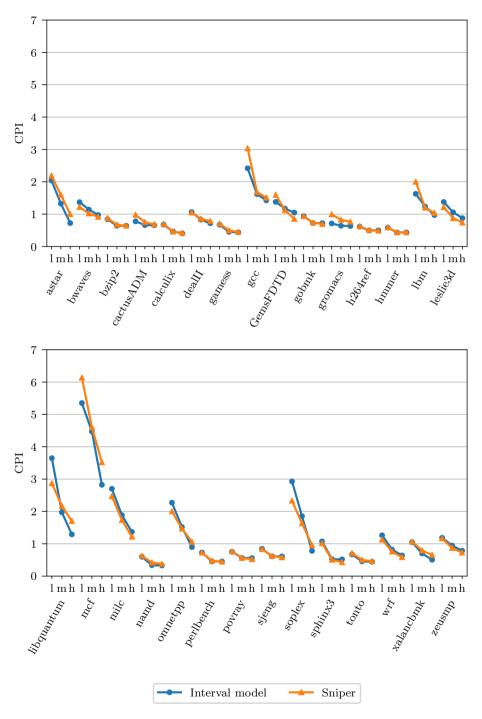

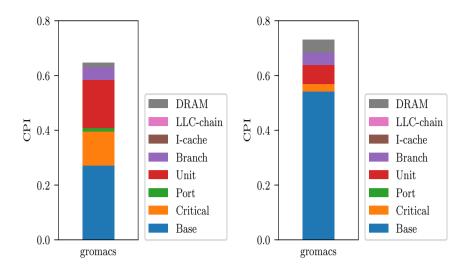

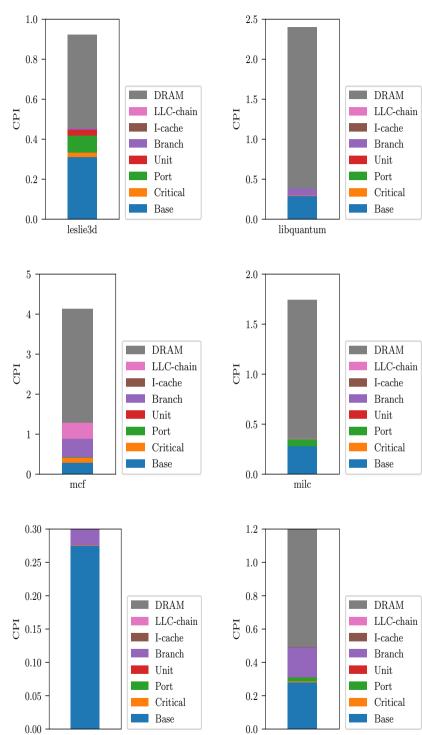

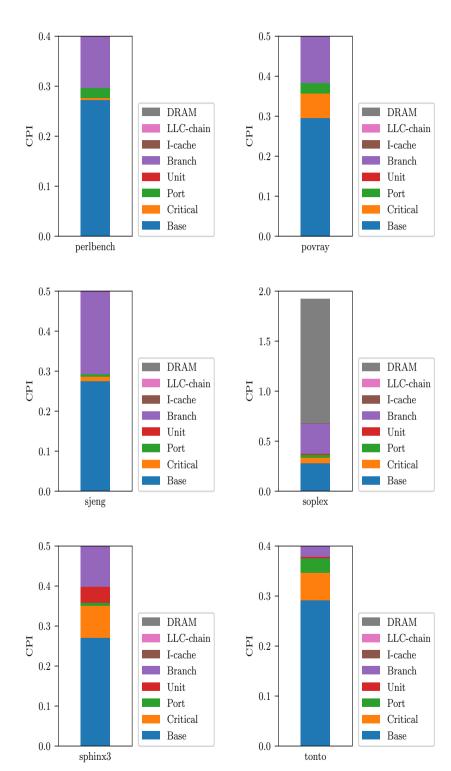

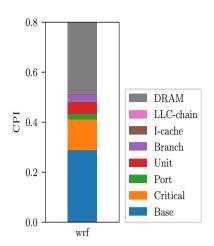

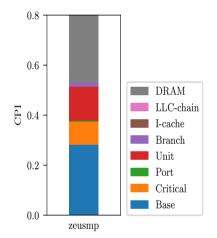

| 6.1  | CPI stacks generated by the model and by Sniper                                                                        | 75 |

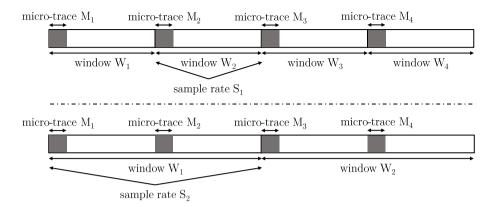

| 6.2  | Visualization of the different sampling approaches to collect micro-traces within windows in an instruction stream.    | 76 |

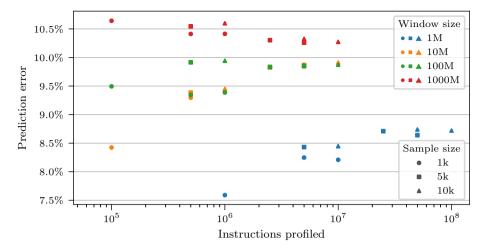

| 6.3  | Average absolute prediction error versus number of instructions profiled.                                              | 77 |

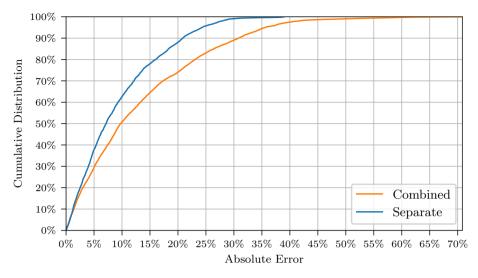

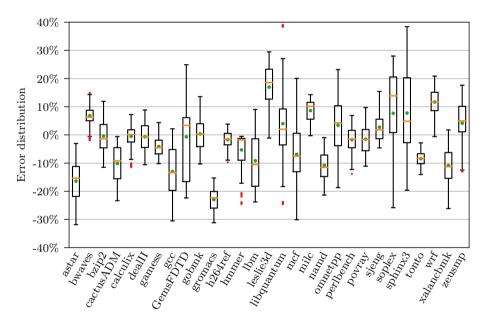

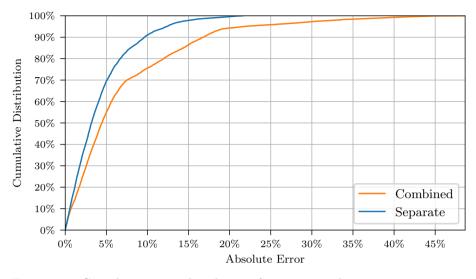

| 6.4  | Cumulative distribution of the performance prediction error<br>when evaluating micro-traces separately versus combined | 81 |

| 6.5  | Box-and-whiskers plot showing the performance prediction errors across our design space.                               | 81 |

| 6.6  | Micro-architecture independent interval model CPI estimation versus simulated CPI.                                     | 82 |

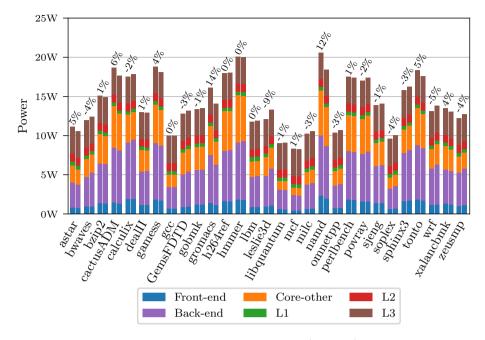

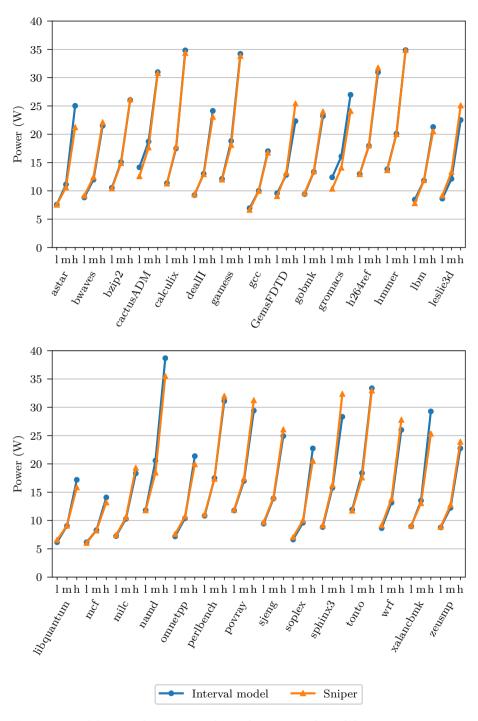

| 6.7  | Power stacks generated by the model and by Sniper                                                                      | 83 |

| 6.8  | Cumulative error distribution for power predictions.                                                                   | 85 |

| 6.9  | Box-and-whiskers plot showing the power prediction errors across our design space.                                  | 85  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

| 6.10 | Micro-architecture independent interval model power estimation versus simulated power                               | 86  |

| 6.11 | Comparison of the base component for the <i>gamess</i> and <i>gromacs</i> benchmarks                                | 88  |

| 6.12 | Comparison of the DRAM component for the <i>milc</i> and <i>mcf</i> benchmarks                                      | 89  |

| 6.13 | Comparison of the performance of the $gromacs$ benchmark on our reference architecture and a low-power architecture | 90  |

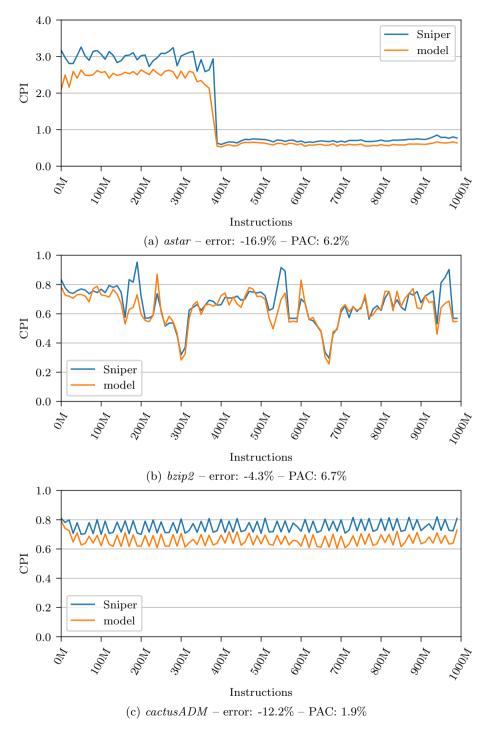

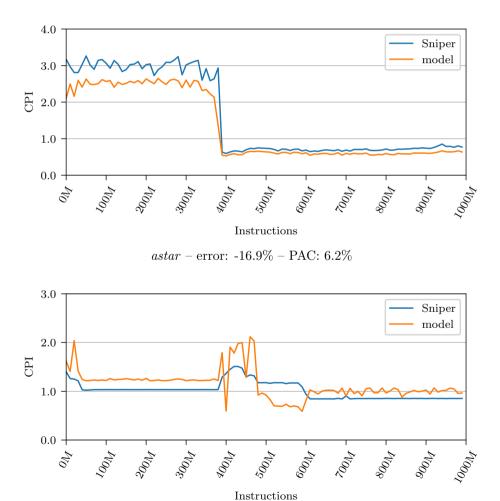

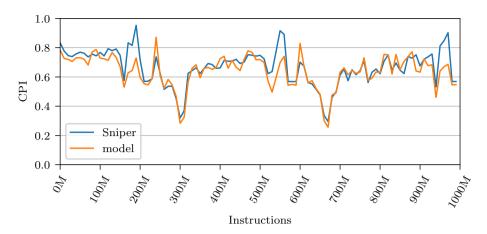

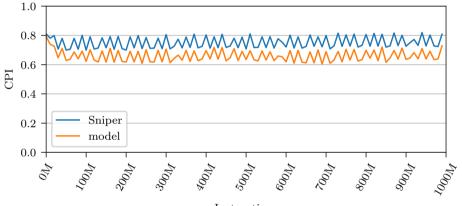

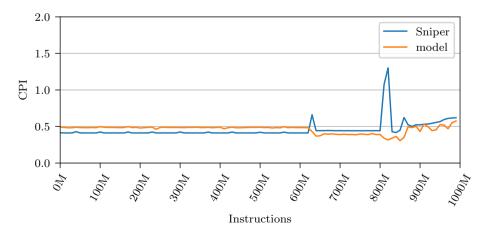

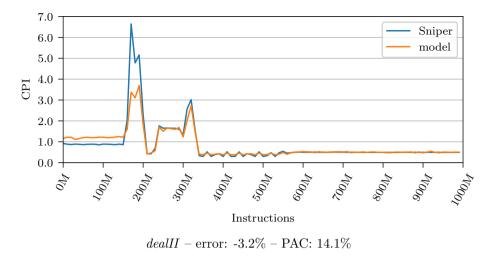

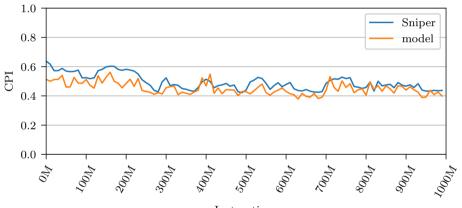

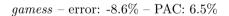

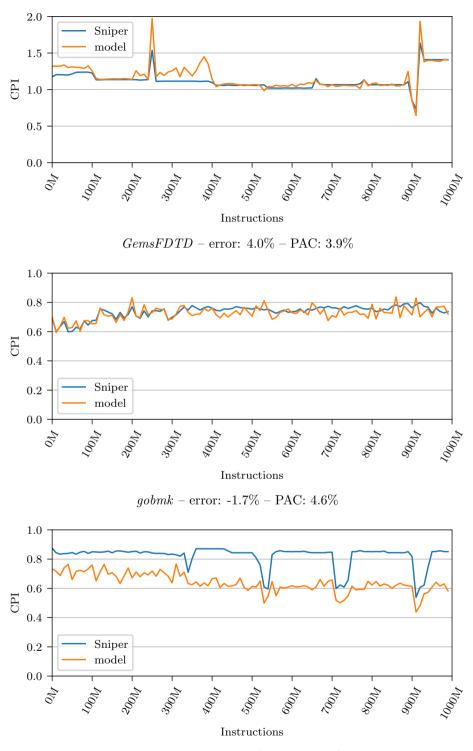

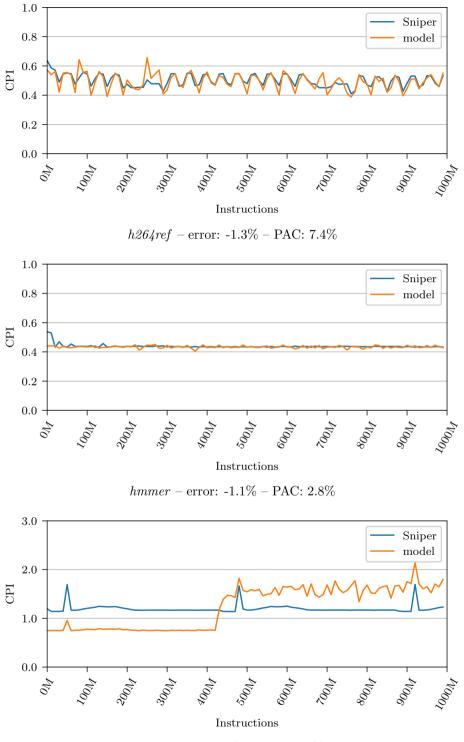

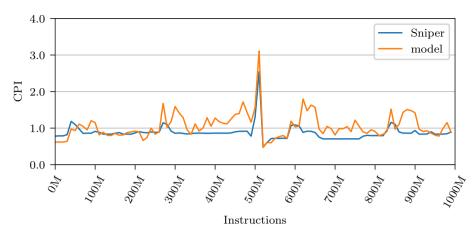

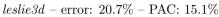

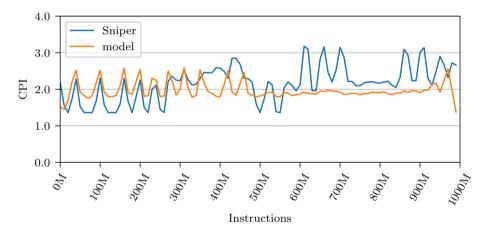

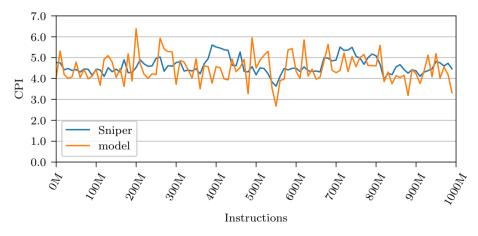

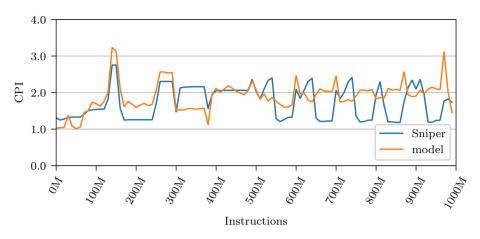

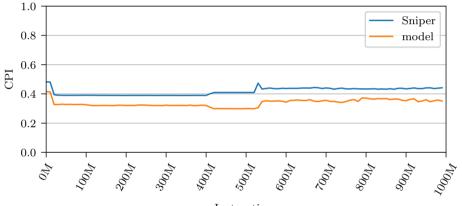

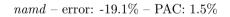

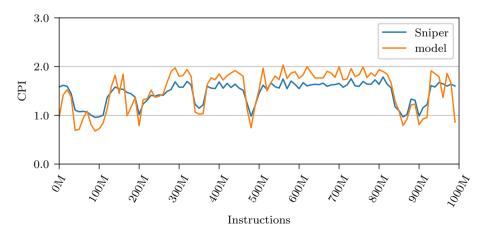

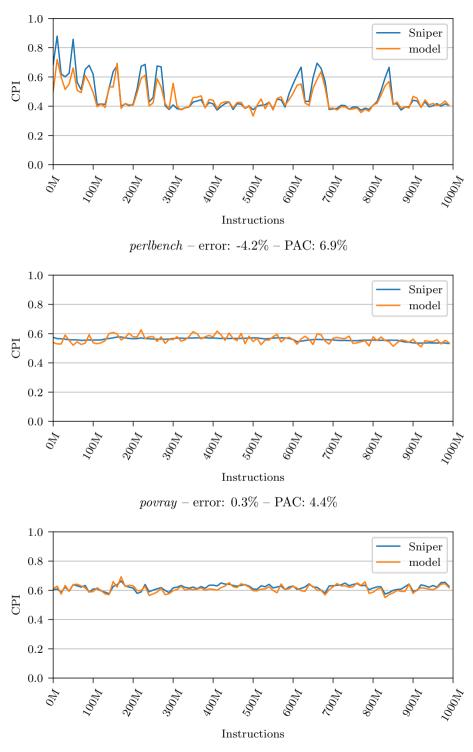

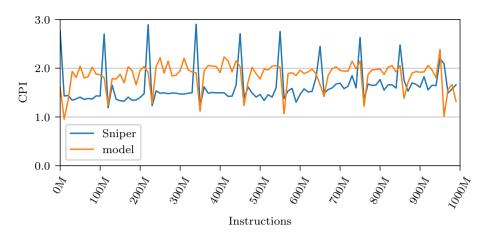

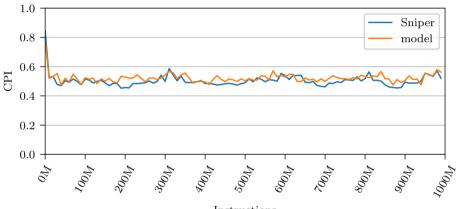

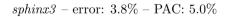

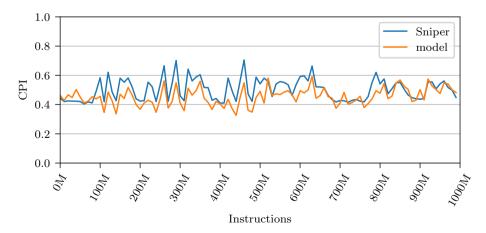

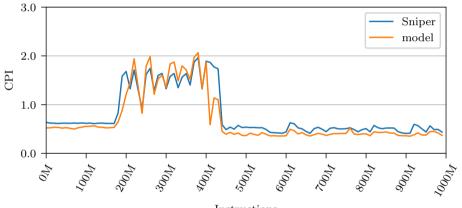

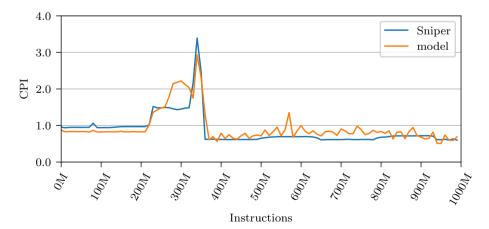

| 6.14 | Phase graphs for the $astar, bzip2$ and $cactusADM$ benchmarks.                                                     | 91  |

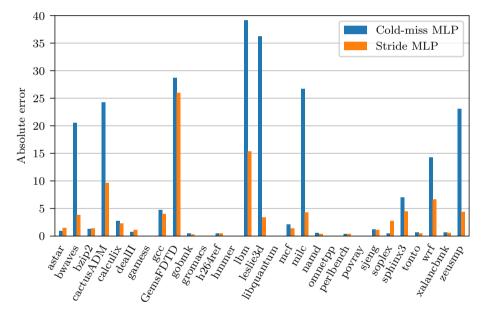

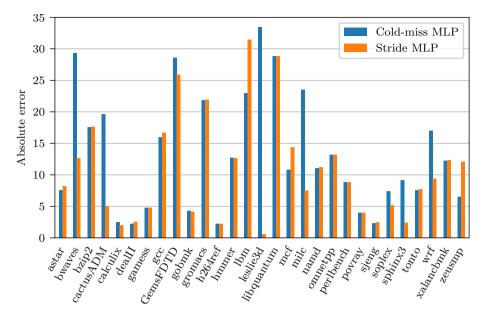

| 6.15 | Absolute error for the cold-miss and stride MLP models, assuming no hardware prefetching.                           | 93  |

| 6.16 | Absolute error for predicting performance using the stride and cold-miss MLP models.                                | 94  |

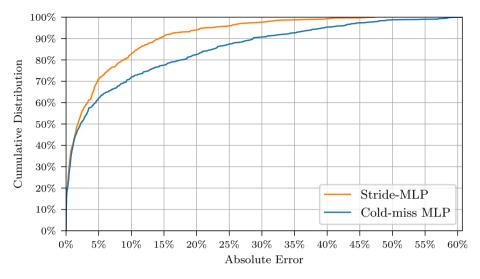

| 6.17 | Cumulative error distribution when using the stride MLP model versus the cold-miss MLP model.                       | 95  |

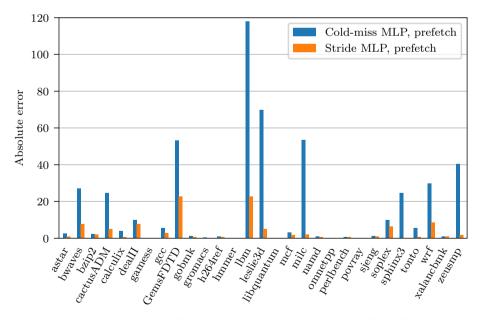

| 6.18 | Absolute error for the stride and cold-miss MLP models, assuming hardware stride prefetching.                       | 95  |

| 7.1  | Improving performance for the <i>libquantum</i> benchmark                                                           | 98  |

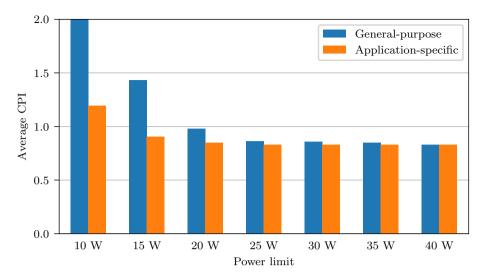

| 7.2  | Average CPI when selecting a general-purpose core versus se-<br>lecting an application specific core                | 99  |

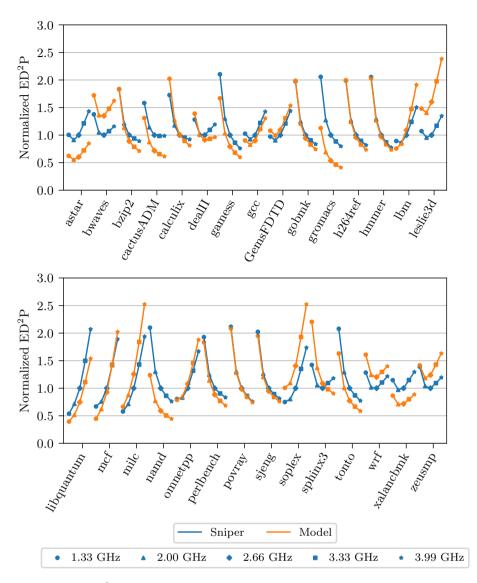

| 7.3  | $ED^2P$ for different frequencies calculated with Sniper and our model                                              | 102 |

| 7.4  | Pareto frontiers for the $bzip2$ and $calculix$ benchmarks                                                          | 103 |

| 7.5  | Pareto frontiers for the $gromacs$ and $xalancbmk$ benchmarks                                                       | 104 |

| 7.6  | Average absolute error for performance and power predictions for the complete design space                          | 105 |

| 7.7  | Sensitivity, specificity and accuracy of the Pareto-filtered pre-<br>dictions on the complete design space.         | 106 |

| 7.8  | Illustration of the HVR metric calculation                                                                          | 106 |

| 7.9  | HVR of the Pareto-filtered predictions on the complete design space.                                                | 107 |

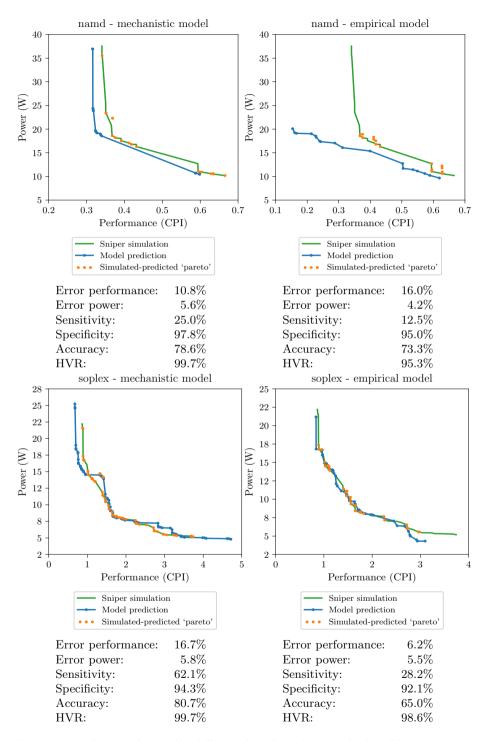

| 7.10 | Pareto fronts for different benchmarks as calculated by our mech-<br>anistic model and the empirical model          | 109 |

| 7.11 | Comparison between the interval model and the mechanistic model of the sensitivity values.                          | 110 |

| 7.12 | Comparison between the interval model and the mechanistic |     |

|------|-----------------------------------------------------------|-----|

|      | model for the specificity values                          | 110 |

| 7.13 | Comparison between the interval model and the mechanistic |     |

|      | model for the HVR values                                  | 111 |

# List of Tables

| 2.1 | Example of an instruction mix of an application.                                             | 23  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 3.1 | Two examples of instruction mixes resulting in limitations on<br>the effective dispatch rate | 35  |

| 6.1 | Core configuration for our reference architecture, based on the<br>Intel Nehalem processor   | 74  |

| 6.2 | Average and maximum error of introducing a new micro-<br>architecture independent component  | 78  |

| 6.3 | Core configuration design space.                                                             | 79  |

| 6.4 | Reference architecture, based on Intel Nehalem                                               | 93  |

| 7.1 | Results of optimizing performance under power constraints                                    | 100 |

| 7.2 | Nehalem-based architecture using different DVFS settings                                     | 101 |

# List of Abbreviations

**ABP** Average Branch Path ALU Arithmetic Logic Unit **AP** Average Path **ASIP** Application-Specific Instruction Processor **CISC** Complex Instruction Set Computer CMOS Complementary Metal Oxide Semiconductor **CPI** Cycles Per Instruction **CPU** Central Processing Unit **CP** Critical Path **DRAM** Dynamic Random Access Memory **DVFS** Dynamic Voltage and Frequency Scaling  $ED^{2}P$  Energy-Delay-Square Product **EDP** Energy-Delay Product **EX** Execution FPU Floating Point Unit HVR Hyper Volume Ratio **ID** Instruction Decode **IF** Instruction Fetch **ILP** Instruction-Level Parallelism **IPC** Instructions Per Cycle **ISA** Instruction-Set Architecture

**ITRS** International Technology Roadmap for Semiconductors

**L1D** Level-1 Data Cache

**L1I** Level-1 Instruction Cache

L2 Level-2 Cache

L3 Level-3 Cache

LLC Last-Level Cache

${\bf LRU}$  Least Recently Used

**MEM** Memory Access

${\bf MIPS}\,$  Million Instructions Per Second

$\mathbf{MLP}$  Memory-Level Parallelism

MPKI Misses Per Kilo Instructions

**MSHR** Miss Status Handling Registers

${\bf OF}\,$  Operand Fetch

PAC Phase-Accuracy Coefficient

**RAW** Read-after-Write

**RD** Reuse Distance

**RISC** Reduced Instruction Set Computer

ROB Re-Order Buffer

**RTL** Register Transfer Level

$\mathbf{SD}$  Stack Distance

${\bf SMT}$  Simultaneous Multithreading

**TLB** Translation Look-aside Buffer

WAR Write-after-Read

WAW Write-after-Write

WB Write-back

## Chapter 1

## Introduction

Everything should be made as simple as possible, but not simpler.

– Albert Einstein

### 1.1 Motivation

The demise of Dennard scaling, which promised constant power density with every successive process technology [25], ended an era where processor performance improvements originated largely from scaling chip technology. Before its demise, every new processor generation introduced performance gains because transistors were miniaturized, could switch faster and consumed less energy. Hence, processor designers could integrate more transistors on a chip realizing performance improvements while maintaining power density at a status quo.

Unfortunately, the physical scaling of a transistor was not followed by the scaling of its electrical properties. A transistor conducts when the supply voltage is higher than a certain threshold voltage. However, the continued miniaturization of the transistor led to a substantial increase in leakage current. As a result, scaling the threshold voltage down proportional to the transistor size became impossible. This meant that the active and passive power consumption of a transistor did not decrease with scaling technology anymore. Therefore, putting an increasing number of smaller transistors on a chip kept the area constant, but not its power consumption, increasing power density.

The increase in power density generated an excess of heat which has to be dissipated. The necessity to dissipate this excess heat grew to be a major concern for processor architects. Multiple solutions were devised, with the birth of multi-core processors where two or more cores are placed on one chip being crucial. However, these multi-core processors still suffer from excess heat generation, albeit less severe, if the processor's clock frequency is kept reasonably low. One promising direction to mitigate excess heat generation is to improve the energy efficiency of the processors through specialization for (a) specific application(s). This type of specialized processors is called Application Specific Instruction Processors (ASIP).

Application-specific cores are tailored to (a) specific application(s) by removing or reducing all components that are not used, or under-utilized, by the application(s) (e.g., smaller caches or a narrower pipeline), and/or enlarging and adding components that benefit the application (e.g., accelerators). Embedded processors are a typical use case for application-specific processors, because they execute a limited set of applications and can be tightly optimized. Moreover, processors operating in mobile devices are continuously power and/or energy constrained while still aiming to achieve the best performance. Thus, both types of processors are prime candidates for applicationspecific optimizations.

Unfortunately, contemporary superscalar out-of-order processors are incredibly complex to analyze and optimize. Much of this optimization work is performed using detailed simulation, which is very slow and can thus inhibit the full design space exploration needed for finding the specific optimizations. The main motivation for this thesis is to help processor architects with alternative tools that enable the development of application-specific processors to improve performance, power and energy efficiency.

### 1.2 Key Contributions

If designing application-specific processors requires fast design space exploration tools to optimize for a targeted application(s), an alternative to simulation is required. Analytical models are an excellent fit for such design space exploration as they provide fast performance predictions and insight into the interaction between an application's characteristics and the micro-architecture of a processor. The key contributions of this thesis all relate to improving a pre-existing analytical model helping to prune large design spaces.

#### 1.2.1 Micro-architectural Independent Analytical Model

Current analytical models require some micro-architecture dependent inputs, such as cache miss rates, branch misprediction rates and memory-level parallelism. This requires profiling the applications for each cache, branch predictor and reorder buffer (ROB) configuration of interest, which is significantly time-consuming compared to evaluating the actual analytical models. In this work we present a *micro-architecture independent* profiler and associated analytical models that allow us to produce performance *and* power estimates, based on a single profiling run, across a large design space almost instantaneously.

We show that using a micro-architecture independent profile leads to a speedup of  $300 \times$  compared to detailed simulation for our evaluated design

space. Over a large design space, the proposed model has an average error of 13% for performance and 7% error for power predictions, compared to cycle-level simulation. The model is able to accurately determine the optimal processor configuration for different applications under power or performance constraints, and provides insight into performance through cycle stacks.

This work was published at: S. Van den Steen, S. De Pestel, M. Mechri, S. Eyerman, T. Carlson, D. Black-Schaffer, E. Hagersten, and L. Eeckhout. Micro-architecure independent analytical processor performance and power modeling. In *Proceedings of the International Symposium on Performance Analysis of Systems Software (ISPASS)*, pages 32–41, 2015

This paper was nominated as one of the candidates for the best paper award at the 2015 ISPASS conference.

#### 1.2.2 Sampled Model Evaluation

The previously proposed model sampled the workload during profiling to limit profiling time, after which the profiles for the different samples were combined to create an average profile. This profile served as an input to the analytical model. The key insight in this work is that we can improve the prediction accuracy by evaluating the model for all samples separately and combining the performance predictions across the samples. For contention modeling this makes sense as it is important to look at individual samples to predict bursty behavior rather than averaged out samples. Furthermore, some statistics such as cache misses and Memory-Level Parallelism (MLP) can influence each other but by averaging out both, the model misses certain behaviors that cancel out or reinforce each other.

Over a large design space, the improved model has a 9.3% average error for performance and a 4.3% average error for power, compared to detailed cyclelevel simulation. Besides offering insight in the performance losses of an application running on a specific processor through cycles stacks, we employ the model to build Pareto plots. These Pareto plots offer insight into the performancepower trade-offs when picking either low-power or high-performance processors.

This work was published at: S. Van den Steen, S. Eyerman, S. De Pestel, M. Mechri, T. E. Carlson, D. Black-Schaffer, E. Hagersten, and L. Eeckhout. Analytical processor performance and power modeling using microarchitecture independent characteristics. *IEEE Transactions on Computers* (TC), 65(12):3537–3551, 2016

This paper was chosen as the featured paper of December 2016 and a video<sup>1</sup> explaining the work was uploaded to the IEEE Transactions on Computers YouTube channel.

<sup>&</sup>lt;sup>1</sup>https://youtu.be/g3cDPM54YFA

#### 1.2.3 Modeling Memory-Level Parallelism

The previously proposed analytical models relied heavily on cold cache misses to predict MLP. This technique works well for evaluating relatively short traces without the need for a significant warmup. However, it falls short when evaluating complete benchmarks. Hence, we develop a new technique to model MLP that relies on the stride behavior of static load instructions. We profile the workload once and measure a set of distributions to characterize the workload's inherent memory behavior. We subsequently generate a virtual instruction stream, over which we then process an abstract MLP model to predict MLP for a particular micro-architecture with a given reorder buffer and last-level cache (LLC) size. We also take the impact of the miss status handling registers (MSHR) and a stride-based prefetcher into account. Experimental evaluation reports an improvement in modeling error from 16.9% for the cold-miss MLP model to 3.6% on average for the stride-based MLP model for predicting the average time the processor has to wait on DRAM in the presence of a stride-prefetcher.

This work was published at: S. Van den Steen and L. Eeckhout. Modeling superscalar processor memory-level parallelism. *IEEE Computer Architecture Letters (CAL)*, 17(1):9–12, 2018

#### 1.2.4 Open Sourced Framework

The framework developed during this thesis is publicly available on GitHub. It consists of the Architecture Independent Profiler (AIP) available at https://github.com/samvandensteen/AIP, and the Processor Modeling Tool, available at https://github.com/samvandensteen/PMT. The tools are licensed under a GNU GPLv3 license.

To execute the tools, a number of other libraries are needed. The minimum requirements to execute the tools on an x86-based system are the following:

- Pin 2.x

- Google Protobuf 3.x

- Python 2.x

Some features of the framework to speed up the profiling or automatically produce performance plots rely on having other packages installed such as:

- google-sparsehash

- python-matplotlib

### **1.3** Other Research Activities

During the course of my PhD, from January to July 2017, I had the opportunity to intern at ARM in Cambridge, UK. The goal of this internship was to modify the developed models to work within the ARM simulation infrastructure. This required some modifications to the work flow presented in my thesis. First, I implemented the Pin-based profiling tool [48] into the ARM Fast Models framework [1]. Second, I modified the analysis tool to model an ARM core more faithfully. This primarily meant enforcing stricter constraints on the obtainable performance. I compared the predicted processor performance results both to an internal cycle-accurate simulator and real hardware for the SPEC CPU 2000 [9], SPEC CPU 2006 [10] and numerous EEMBC benchmark suites [3].

The final results of this internship approached the average accuracy of the proposed x86-based analytical model. Unfortunately, there were some outliers which I was unable to fix due to the brevity of the internship. The reason for these outliers are likely caused by ARM-processors being more resource-constrained, both in the processor front-end and back-end, which proved to be more challenging to capture in the analytical model than anticipated. However, I strongly believe that there are no fundamental limitations as to why the analytical model cannot be extended and fine-tuned to more accurately model ARM processors.

#### 1.4 Thesis Overview

The remainder of the thesis discusses the research and framework we developed building on the previously proposed mechanistic interval model [32] to enable fast design space exploration. The thesis is organized in the following chapters.

Chapter 2 introduces the necessary background to understand the thesis. We discuss how a superscalar out-of-order processor core is built. We explain the different pipeline stages and how an instruction is processed. Next, we clarify the difference between simulation, sampled simulation and both empirical and mechanistic modeling to obtain performance and power predictions. In the next section, we discuss how processor power consumption can be modeled using different tools. Afterwards, we introduce the interval model and describe how it predicts processor performance. Lastly, we explain the advantage of using a micro-architectural independent interval model.

In Chapter 3, we discuss the complications an x86-based processor introduces for predicting performance using the interval model. We explain the different modifications introduced to improve its accuracy. Furthermore, we show how branch misprediction rates can be calculated without simulating the branch predictor [22] and how we predict power consumption using activity factors. Chapter 4 introduces the statistics required to predict the influence of memory accesses on our performance predictions. We explain how we can predict cache miss rates using a statistical model called StatStack [28] and discuss two different techniques to estimate MLP. Accurate predictions of the latter are crucial to arrive at accurate performance predictions. Furthermore, we discuss a number of constraints imposed to the parallel execution of memory requests by the MSHRs and memory bus. We also, briefly, show the importance of including a prefetcher model and how power consumption for the memory hierarchy can be predicted.

Chapter 5 discusses the sampling approaches we implemented to speed up the collection of statistics necessary to estimate performance and power for the micro-architectural independent interval model. It also discusses the errors introduced by these sampling techniques.

Chapters 6 and 7 show the results obtained with the mechanistic model in this thesis. First, we describe our experimental setup. Afterwards, we discuss the accuracy of our performance and power predictions for our reference architecture and a design space of processor configurations. We show that we can generate CPI stacks offering insight into the performance losses of an application executing on a specific processor architecture. Furthermore, we demonstrate that our model can track the phases of an application relatively accurately and that modeling a prefetcher (when present) is necessary. When applying this model, we introduce Pareto plots to enable design space exploration and choosing an optimal core for a given application. We include a brief discussion using machine learning techniques for exploring a design space. We show that they produce accurate performance and power predictions on average, but fail to accurately predict performance and power trends. Lastly, we show that our model can even be used to find the optimal design point when Dynamic Voltage and Frequency Scaling (DVFS) is used.

Finally, in Chapter 8 we conclude the thesis and discuss some possible future work to extend the model to new types of processor cores and applications.

### Chapter 2

## Background

### 2.1 Out-of-order Processor

This thesis focuses on modeling the performance of pipelined superscalar out-of-order processors<sup>1</sup>. To understand how to model processor performance and power, one needs to understand the architecture of a processor. First and foremost, it is important to understand the different terms defining this type of processor. Pipelined execution means that processing an instruction takes multiple time steps (cycles) and different instructions reside in different stages of the processor pipeline in a given cycle. This is referred to parallelism in time. Superscalar execution means there are multiple, parallel pipelines through the complete processor. Hence, multiple instructions can enter the processor's parallel pipelines at the same time step which is called parallelism in space. Out-of-order execution means that the processor supports execution of instructions out of program order to improve performance, but the software is given the illusion of execution instructions in the order as specified by the programmer. The combination of both concepts leads to pipelined superscalar out-of-order processors, which offer high-performance, but unfortunately also consume a lot of power.

When an instruction is executed by the processor, it is flowing through a pipeline consisting of multiple stages. These stages are often again divided in multiple steps to exploit as much parallelism as possible. The stages of a processor are Instruction Fetch (IF), Instruction Decode (ID), Operand Fetch (OF), Execution (EX), Memory Access (MEM) and Write-Back (WB). The IF, ID and OF stages form the processor front-end, while the EX, MEM and WB stage comprise the back-end. Note that not every instruction needs all stages. Some instructions do not access any memory and others, e.g., unconditional branches, do not need any operands. Figure 2.1 shows a schematic overview of an out-of-order processor.

<sup>&</sup>lt;sup>1</sup>From now on, when we use the term processor, it denotes a pipelined superscalar out-oforder processor, unless mentioned otherwise.

Figure 2.1: Schematic overview of the pipeline of an out-of-order processor.

The Instruction Fetch stage of the processor is responsible for fetching the next instruction(s). When an instruction is fetched that changes the flow of the program (e.g., it jumps to another part of the program), it is unclear what the next instruction is. Therefore the IF stage of a processor also features a branch predictor, which predicts the next instruction. This allows for the IF stage to keep fetching correct-path instructions with a minimal delay provided the branch predictor performs well.

The Instruction Decode stage translates the bytes of an encoded instruction to a format that the processor understands. It determines the type of the instructions and figures out their operands and registers. Furthermore, if an instruction performs a complex operation, the ID stage can split it up into smaller parts, called micro-operations. All of this information is sent to the next stages in the processor pipeline.

1  $R_1 \leftarrow R_2 + R_3$ 2  $\dots$ 3  $R_5 \leftarrow R_1 + R_4$ 4  $\dots$ 5  $R_1 \leftarrow R_6 \times R_7$

Example 2.1: Illustration of the different types of register dependences.

In the ID stage, the processor will also rename the operand registers to eliminate false dependences. We distinguish between three types of dependences, namely real dependences or Read-after-Write (RAW) dependences, anti-dependences or Write-after-Read (WAR) dependences, and output dependences or Write-after-Write (WAW) dependences. The latter two are false dependences that can be eliminated through register renaming. Example 2.1 illustrates why the renaming step is necessary in out-of-order execution. Instruction 1 calculates the addition of  $R_2$  with  $R_3$  and stores the result in  $R_1$ which is consumed by instruction 3, thus there exists a RAW dependence between instructions 1 and 3 through register  $R_1$ . This type of dependence cannot be eliminated by register renaming. Instructions 1 and 5 exhibit a WAW dependence because they both write to register  $R_1$ . Instructions 3 and 5 are an example of a WAR dependence since instruction 3 reads  $R_1$  and instruction 5 overwrites  $R_1$ . For a superscalar out-of-order processor to work efficiently and correctly, both false dependences have to be eliminated. After all, instruction 5 does not depend on any previous instruction and, to maximize performance, an out-of-order processor can execute it before instruction 3. However,  $R_1$ now contains a newer value which is not the correct input for instruction 3. The processor still needs to supply the older, correct result to instruction 3. Example 2.2 illustrates the solution to this problem by renaming registers. Instruction 1 writes to a different physical register  $F_1$ , which is consumed by instruction 3, and instruction 5 writes to register  $F_2$ . The processor can now execute these instructions in any order and still arrive at the correct result. Note that in this example only the registers through which there are dependences are renamed, but in reality all registers will be renamed.

Example 2.2: Code example with renamed registers.

In the Operand Fetch stage, the register operands that are needed to execute an instruction are gathered. Here, the processor will read the physical register file. Note that, at that point in the pipeline, not every instruction has all of its operands available immediately. Example 2.2 already shows that instruction 3 depends on the result of instruction 1. Even with the missing operand(s), instruction 3 will still progress to the next pipeline stage.

After the OF stage, the instruction will be dispatched. This is where we enter the EX stage. In this stage the instruction is inserted into both the instruction queue and reorder buffer. Afterwards, if all operands are available, the instruction is issued to a so-called functional unit for execution. Depending on the type of instruction, it will be sent to a different functional unit (e.g., an addition or multiplier unit). If the instruction depends on the result of a previous instruction and has not received all of its operands in the OF-stage, it will wait in the instruction queue until that operand can be forwarded from one of the functional units. The EX-stage is the stage from which out-of-order execution derives its name. The processor will traverse the instruction queue and if an instruction has all its operands available, it will issue and execute the instruction. Because the processor can traverse the entire instruction queue and pick any instruction, instructions are not per se executed in program order.

If an instruction has to access memory, it will enter the Memory stage. In the previous stage, the functional unit will have calculated the address where to read or write the data in memory. It will first query the cache hierarchy which serves as intermediary fast storage, and if the data is not found there, request it from the memory subsystem. Depending on which level of cache or main memory the data has to be fetched from, this can take a long time.

The last stage is the WB stage. Here the results are committed to the physical register file and/or the memory hierarchy. The instructions are removed from the ROB. This operation is executed in-order, meaning that the instructions are taken out of the ROB in the same order they were put in. This guarantees that, despite internal reordering of instructions, the architectural state of the processor is always correct and consistent, which is particularly important in the context of precise exceptions.

## 2.2 Architectural Simulation

Physically producing a processor is so expensive and time consuming that it is impossible to evaluate improvements to the design of a processor by actually prototyping it. Instead, processor architects often rely on simulation to predict the performance of a (set of) program(s) executing on a processor. Generally these different simulation techniques can be classified according to the level of abstraction the processor designer employs. One could use very detailed simulation of every part of the processor, but it is also possible to omit or abstract parts of the processor. Truthfully simulating every part of a processor produces very accurate performance predictions, but is also extremely slow. Therefore, if fast results are required, the trade-off can be made to omit or abstract away as much of the processor as possible.

#### 2.2.1 Timing Simulation versus Functional Simulation

Many types of simulations exist, each with their own trade-offs with respect to speed and prediction accuracy. We briefly discuss the most important categories and highlight the difference between timing simulation versus functional simulation.

Two types of timing-focused simulation are cycle-accurate simulation (or RTL-simulation) and cycle-level simulation. A processor architect will employ a timing-based simulation to figure out how a processor executes a program, but also when it performs specific actions.

Cycle-accurate simulation will model every structure of the processor in software. Cycle-accurate simulators are able to simulate what happens inside the processor on a cycle-by-cycle basis. Hence, the produced performance predictions are usually accurate within a couple of percent compared to real hardware.

However, cycle-accurate simulators are typically very slow. They reach simulation speeds of up to 1 kHz, meaning that they are able to simulate 1000 processor cycles per second in real time. This is six orders of magnitude slower than a real system. Thus, if executing a program on a real system would take 1 s, simulating it using cycle-accurate simulation would take roughly 10 days. It is obvious why it is infeasible to generate performance predictions for multiple applications and processor designs.

Furthermore, most cycle-accurate simulators are not available to the academic world. The reason is that if a processor company would release its simulator, they would risk a third-party being able to find out how that processor works exactly. Since developing a processor is extremely expensive, it is understandable that companies do not release their simulators.

Luckily, there are a number of simulators available to academics to perform cycle-level simulation. These simulators still employ a timing model, but they tend to simplify the simulation of certain parts of the processor. Examples include SimpleScalar [16], Gem5 [14], PTLSim [74], Graphite [50], Sniper [17], etc. They are usually one or two orders of magnitude faster than true cycleaccurate simulators. Furthermore, the performance predictions are still relatively accurate and the simulators are usually validated against real hardware.

Functional simulation abstracts away the timing-related details and is thus not used to predict processor performance. These simulators focus on what happens in the processor, rather than when it happens. As a result, they are one or two orders of magnitude faster than cycle-level simulation. Many of the previously cited simulators (e.g., SimpleScalar [16] and Gem5 [14]) also offer a functional simulation model.

Functional simulation can also focus on only simulating specific parts of the processor, e.g., the cache hierarchy or branch predictor. Some simulators, e.g., Sniper [17], offer a cache-only simulation mode. This can be useful if the focus is to optimize one specific structure in the processor. Furthermore, the results of a cache or branch predictor simulator can be used as input to analytical models such as the interval model, see Section 2.5.

A tool that is widely used to build (functional) simulators is Pin [48], a binary instrumentation framework developed by Intel for x86-applications. This tool allows to instrument an application as it is executed, collecting statistics from the dynamic instruction stream. The collected statistics can be used to build a full timing-based simulator such as Graphite [50] and Sniper [17] as well as, for example, a functional cache simulator for multi-core processors such as CMP\$im [39].

#### 2.2.2 Sampled Simulation

Speeding up simulation can often be achieved through sampling. Sampled simulation has been researched extensively since it introduces two major challenges, namely the selection of a representative (set of) sample(s) and starting from a 'correct' (micro-)architectural state at each sample.

The selection of a representative (set of) sample(s) to simulate instead of simulating a complete application can be solved in one of two ways. Either a statistical approach is taken where samples are taken in a random fashion or periodically, or a targeted approach is used where the program is first analyzed to find representative samples.