# UCC Library and UCC researchers have made this item openly available. Please let us know how this has helped you. Thanks!

| Title                       | Integrated microinductors on semiconductor substrates for power supply on chip (Invited)                                                                                                                                                                                                                          |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)                   | Rohan, James F.; Casey, Declan P.; O'Brien, Joe; Hegarty, Margaret;<br>Kelleher, Anne-Marie; Wang, Ningning; Jamieson, Brice; Waldron,<br>Finbarr; Kulkarni, Santosh; Roy, Saibal; Ó Mathúna, S. Cian                                                                                                             |

| Publication date            | 2011-01                                                                                                                                                                                                                                                                                                           |

| Original citation           | Rohan, J. F., Casey, D., O'Brien, J., Hegarty, M., Kelleher, AM., Wang, N., Jamieson, B., Waldron, F., Kulkarni, S., Roy, S. and O'Mathuna, S. C. (2011) '(Invited) Integrated Microinductors on Semiconductor Substrates for Power Supply on Chip', ECS Transactions, 41(8), pp. 341-347. doi: 10.1149/1.3631510 |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                           |

| Link to publisher's version | http://ecst.ecsdl.org/content/41/8/341 http://dx.doi.org/10.1149/1.3631510 Access to the full text of the published version may require a subscription.                                                                                                                                                           |

| Rights                      | © 2011 ECS - The Electrochemical Society                                                                                                                                                                                                                                                                          |

| Item downloaded from        | http://hdl.handle.net/10468/7598                                                                                                                                                                                                                                                                                  |

Downloaded on 2021-11-27T06:58:20Z

# **Integrated Microinductors on Semiconductor Substrates for Power Supply on Chip**

J. F. Rohan, D. P. Casey, J. O'Brien, M. Hegarty, A-M. Kelleher, N. Wang, B. Jamieson, F. Waldron, S. Kulkarni, S. Roy and S. C. O'Mathuna.

Tyndall National Institute, University College Cork, Lee Maltings, Cork, Ireland

Microinductors were fabricated using electrodeposition for integration on semiconductor substrates. The process was optimised through validated models developed to focus on efficiency and footprint. Lithographic processing was performed to microfabricate Cu coils over a magnetic core. A racetrack design was used to maximise the high frequency response, yielding high inductance density and low DC resistance. The magnetic core was subsequently closed using a magnetic thin film deposition over a dielectric deposited on the Cu coils. Homogeneous ferromagnetic alloy, Ni<sub>45</sub>Fe<sub>55</sub> of uniform thickness over a high aspect-ratio 3D structure has been achieved. Ni<sub>45</sub>Fe<sub>55</sub> was chosen for the fabrication of micromagnetic cores due to its relatively high saturation flux density (1.6 T), resistivity (48  $\mu\Omega$  cm) and anisotropy field (9.5 Oe). The rationale, design, microfabrication process and characterisation results are presented.

### Introduction

The continuing miniaturization trend for electronic devices is also seen in the development and integration of passive magnetic components. Integrated voltage regulators fabricated on chip offer the possibility of miniaturisation, improved functionality and mass production. The stacked approach to power-supply-on-chip (PSOC) offers an enhanced monolithic solution for integrated passive components. High efficiency inductors-on-silicon for power conversion applications have been reported [1-3] ranging in size from 9–36 mm and aimed at operation in converters with switching frequencies of 1–5 MHz. To be comparable in area with discrete wire-wound or multi-layer ferrite based inductors, and to enable integration on chip, micro-fabricated inductors need to be significantly reduced in footprint area.

Since the inductance per unit area achievable for micro-fabricated inductors is typically limited by the thin film technology used, the converter switching frequency must be increased to the point where small values of inductors are required and hence the inductor size is small enough to make integration on chip feasible. High values of inductance density may be achieved at the expense of inductor dc resistance and current handling capability. However, in power conversion applications for battery operated products such as cell phones, the inductor must be capable of handling several hundred milli-amps of dc current and maintaining the low losses requires a low dc-resistance. For this reason we have focussed on the use of relatively thick Cu windings where the Cu coils are up to 35 µm

high and coil widths up to  $66 \mu m$ . The other significant functional element in the microinductor is the magnetic material. The focus of research on thin film magnetic cores can be divided into two major fronts: (a) a quest for improved magnetic materials capable of operating at high frequency and (b) suitable integration techniques. (4-7) The aim of this work was to fabricate microinductors using electrodeposition for integration on semiconductor substrates.

# **Experimental**

The authors have developed an analytical model for thin film microinductors [8]. The overall model consists of elements dealing with the Cu windings, magnetic core eddy currents and core hysteresis. It can accurately predict the inductance, winding resistance and sources of efficiency losses within an inductor, such as winding loss, core hysteresis loss, and core eddy current loss. The model has been validated by both finite element analysis and experiment results and is used in inductor design optimization. Given the converter specifications, an optimization program based on the inductor analytical model can automatically seek the most efficient inductor design and determine the geometrical parameters of the inductor. Electrodeposition of the magnetic material is a low cost and high rate deposition technique, capable of achieving good wafer scale uniformity. In a fabrication process with 35 µm high Cu coils and subsequent dielectric it is also a requirement that the magnetic deposition technique be capable of uniform deposition on structured substrates. The inductor parameters from the design phase are given in table 1 with size and efficiency as the key design parameters.

**Table 1. Inductor parameters**

| Inductor Specifications         |                                   |  |

|---------------------------------|-----------------------------------|--|

| Area                            | 3 mm <sup>2</sup>                 |  |

| Inductor range                  | 106 nH                            |  |

| Max. conductor thickness        | 35 μm                             |  |

| Min. conductor width            | 66 µm                             |  |

| Min. conductor spacing          | 15 μm                             |  |

| Number of turns                 | 4                                 |  |

| Magnetic core material          | Ni <sub>45</sub> Fe <sub>55</sub> |  |

| Resistivity                     | $45 \mu\Omega$ cm                 |  |

| Saturation flux density         | 1.5 T                             |  |

| Permeability                    | 280                               |  |

| <b>Convertor Specifications</b> |                                   |  |

| Operating frequency             | 30 MHz                            |  |

| Input voltage, V in             | 1.8 V                             |  |

| Output voltage, V out           | 1.0 V                             |  |

| Output current                  | 0.5 A                             |  |

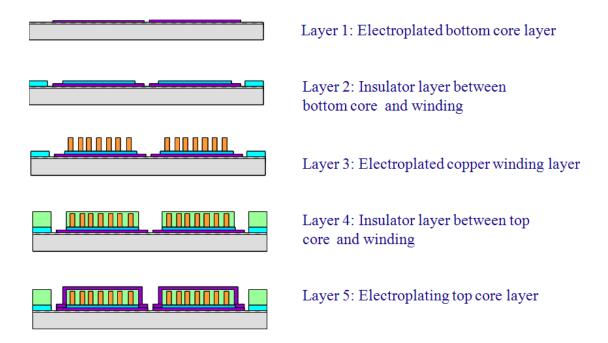

A schematic of the fabrication process for the micro-inductors is shown in figure 1 and consists of a racetrack shaped Cu coil sandwiched between the magnetic cores. The substrate is a Si wafer with a layer of insulation (BCB—Benzocyclobutane, approximately 5 µm thick). A seed layer of Ti/Cu is deposited by sputtering on the insulation. A layer of

magnetic material (Ni<sub>45</sub>Fe<sub>55</sub>) is electroplated and patterned (layer 1) on top of the seed layer. This layer is further insulated by a patterned layer of BCB (layer 2). The Cu windings are then deposited using electroplated Cu on top of a Ti/Cu seed layer (layer 3). These windings are covered by a layer of SU8 (epoxy type photoresist) to isolate them from the top magnetic layer (layer 4). Finally, the top magnetic layer is electroplated (layer 5) to obtain a closed magnetic path.

Figure 1. Schematic of the microinductor fabrication process showing the main functioning layers. The fabrication process is performed on 4 inch Si wafers.

#### Results and discussion.

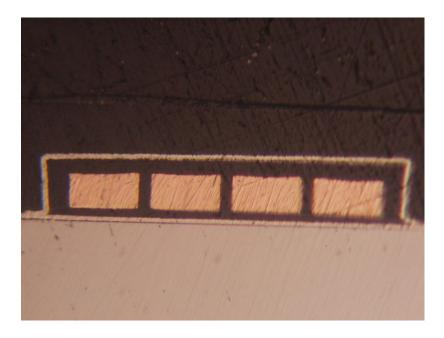

To minimise the footprint area the conductor width is specified in order to fit the turns into the area and maintain the ratio of dc resistance to inductance for smaller footprint areas. In order to decrease further the dc resistance to inductance ratio, the minimum conductor spacing would need to be reduced, the aspect ratio of the conductors increased or the thickness of the magnetic core increased. The conductor spacing and aspect ratio is dependent on the photoresist and lithography process limitations. The core thickness is limited by the requirement to keep eddy current losses low by limiting the core thickness to be approximately equal to the skin depth in the core material at the frequency of operation. In the device described in this work the target frequency of operation is 30 MHz, so that the core thickness is approximately 3.5  $\mu$ m. An optical micrograph of a cross-section taken through a microinductor as specified in table 1 is shown in figure 2. This image shows 30  $\mu$ m high windings 66  $\mu$ m in width and with 10  $\mu$ m gaps. The Ni<sub>45</sub>Fe<sub>55</sub> core above and below the windings is also clearly seen to be highly uniform and the target value of 3.5  $\mu$ m.

Figure 2. Optical image of microinductor cross section for the device specified in table 1.

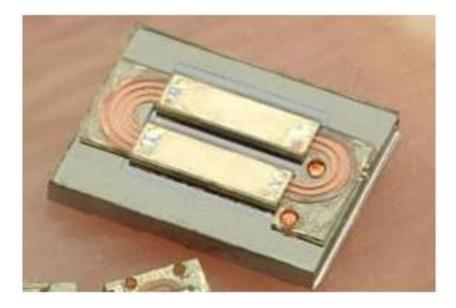

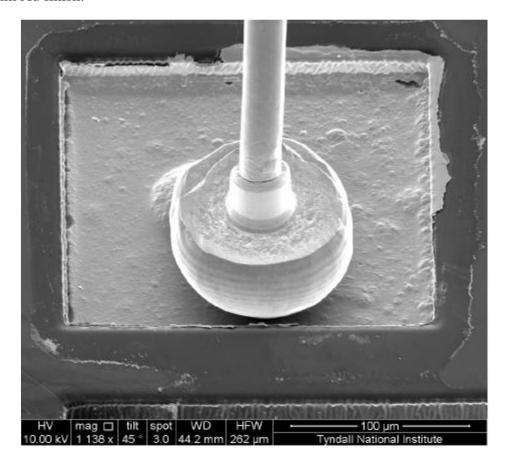

An example of a microinductor fabricated using this processing is shown in figure 3. The bond pads for wirebonding the devices and testing of the electrical performance of the device can be seen in this image. To achieve wirebonding at the Cu bond pads an electroless Ni and immersion Au process has been developed which is compatible with the topography of the devices and the various layer compositions. To ensure the Ni-P deposit forms on the Cu bond pads they must first be activated with a dilute palladium chloride + HCl solution (9) as the Cu substrate is not a catalytic surface for hypophosphite oxidation and hence the electroless Ni-P deposition will not commence on a Cu surface. It will, however, commence on Pd nuclei deposited from the chloride solution. Once the Ni-P layer deposits on the substrate the reaction can continue autocatalytically as the Ni-P substrate is active to hypophosphite oxidation.

Figure 3. Optical image of a microfabricated inductor showing the bond pads.

Following Pd activation the wafer is immersed in a commercial Ni-P electroless plating solution (Enplate by McDermid) at 85 °C at a pH of 4.6 for 20 minutes followed by immersion in a commercial Ormex gold displacement bath (Schloetter) at 90°C at a pH of 5.2 for 10 minutes which replaces the outer layer of Ni-P with a reliable and wirebondable 100 nm Au finish.

Figure 4. Typical Au wirebond on a Ni-P/Au metallised copper bond pad.

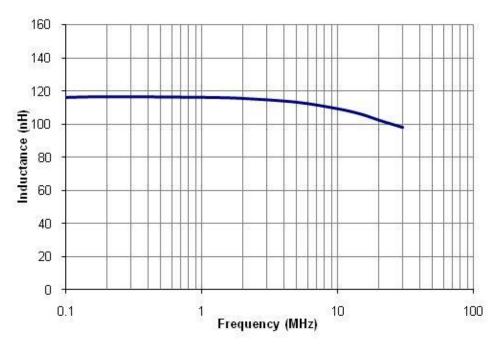

The inductance of the fabricated inductor has been measured vs. frequency up to 30 MHz, using a HP LCR Meter (Model 4285). The graph in figure 5 below shows the results for the micro-fabricated inductor with inductance values of 106 nH. It can be seen from the graph that the inductance is relatively flat up to 30 MHz with an inductance decrease of less than 15 % at 30 MHz. The measured dc resistance is 0.21 Ohm at room temperature.

Figure 5: Measured inductance of fabricated micro-inductor.

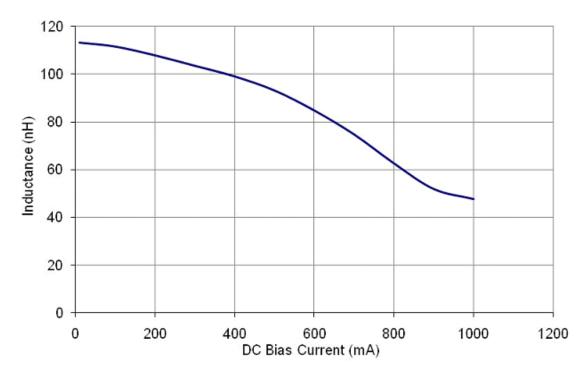

When used in a power converter the inductor must also be capable of carrying the maximum converter dc current while maintaining the inductance level, i.e. without core saturation. Fig. 6 presents the inductance (at 1 MHz) vs. dc bias current for the inductor. It can be seen that inductance holds up well with bias current and the inductance roll-off is relatively gentle. At 500 mA the reduction in inductance value is less than 20 %.

Figure 6: Measured inductance at 1 MHz vs. dc bias current of the fabricated inductor.

# Conclusions.

The process described above for micromagnetics integration on Si is compatible with standard CMOS fabrication. This is one important factor when considering monolithic integration of switching regulator to realize power supply on chip. The developed process is particularly aimed at thick Cu conductor fabrication. The thick Cu deposition is critical for power magnetics in order to reduce the conduction loss. The magnetic material is also electrodeposited which is a relatively faster and more cost-effective solution than sputtering. The pulse-reverse plating technique also enables achieving uniform deposition of magnetic material on a 3D topography. Finally the bond pad metallisation is achieved by electroless Ni-P and immersion Au processing to ensure a reliable surface for wirebon connection of the microfabricated device.

## Acknowledgments

This work has been supported by the Enterprise Ireland commercialisation fund technology development project CFTD/2008/331. We thank Mr. Vince Lodge for recording SEM images. The SEM was funded by "INSPIRE" Higher Education Authority via PRTLI4.

#### References

- 1. T. Sato, K. Yamasawa, H. Tomita, T. Inoue and T. Mizoguchi, *Proc. Int. Power Electronics Conf. (IPEC)*, p. 303 (2000).

- 2. K.H. Kim, J. Kim, H.J. Kim, S.H. Han and H.J. Kim, *IEEE Trans. Magn.*, **38**, p..3162 (2002).

- 3. S. Prabhakaran, S. Yuqin, P. Dhagat, L. Wei-dong and C.R. Sullivan, in *Proc. IEEE Power Electronics Specialists Conf.*, Recife, Brazil, p. 1513 (2005)

- 4. N. Wang, T. O'Donnell, S. Roy, P. McCloskey and C. O'Mathuna, *J. Magn. Magn. Mater.*, **316**, E233 (2007).

- 5. P.McCloskey, B. Jamieson, T. O'Donnell, D. Gardner, M. A. Morris and S.Roy, *J. Magn. Magn. Mater.*, **320** 2509 (2008).

- 6. J.F. Rohan, B.A. Ahern, K. Reynolds, S. Crowley, D.A. Healy, F.M.F. Rhen and S. Roy. *Electrochim. Acta*, **54** 1851 (2009).

- 7. B. Jamieson, T. O'Donnell, P. McCloskey, D.S. Gardner and S. Roy, *J. Magn. Magn. Mater.*, 322, 1527 (2010).

- 8. N. Wang, T. O'Donnell, S. Roy, P. McCloskey and C. O'Mathuna, *J. Magn. Magn. Mater.*, vol. 316, p. e233, 2007

- 9. J.F. Rohan, G. O'Riordan and J. Boardman, *Appl. Surf. Sci.*, **185**, 289 (2002).