# Design and Implementation of a Dynamic Partial Reconfigurable Demodulation System for Satellite Receivers

| 著者       | Mohamed Elhady Magdy Mohamed Gad Keshk |

|----------|----------------------------------------|

| その他のタイトル | 衛星受信機のための動的部分再構成型復調器の設計                |

|          | と実装                                    |

| 学位授与年度   | 平成30年度                                 |

| 学位授与番号   | 17104甲工第461号                           |

| URL      | http://hdl.handle.net/10228/00007059   |

Kyushu Institute of Technology

Department of Engineering

Graduate School of Engineering

# Design and Implementation of a Dynamic Partial Reconfigurable Demodulation System for Satellite Receivers

By

### Mohamed Elhady Magdy Mohamed Gad Keshk

A DISSERTATION SUBMITTED TO THE

GRADUATE SCHOOL OF ENGINEERING

AT KYUSHU INSTITUTE OF TECHNOLOGY

IN PARTIAL FULFILLMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN APPLIED SCIENCE FOR INTEGRATED SYSTEM

ENGINEERRING

Kyushu Institute of Technology

Department of Engineering

Graduate School of Engineering

# Design and Implementation of a Dynamic Partial Reconfigurable Demodulation System for Satellite Receivers

By

#### Mohamed Elhady Magdy Mohamed Gad Keshk

A DISSERTATION SUBMITTED TO THE

GRADUATE SCHOOL OF ENGINEERING

AT KYUSHU INSTITUTE OF TECHNOLOGY

IN PARTIAL FULFILLMENT OF

THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN APPLIED SCIENCE FOR INTEGRATED SYSTEM

ENGINEERRING

**Dissertation Supervisor**

Prof. Kenichi Asami

Dept. of Applied Science for Integrated System Engineering Kyushu Institute of Technology Kyushu Institute of Technology

Department of Engineering

Graduate School of Engineering

# Design and Implementation of a Dynamic Partial Reconfigurable Demodulation System for Satellite Receivers

By

## Mohamed Elhady Magdy Mohamed Gad Keshk

A DISSERTATION SUBMITTED TO THE GRADUATE SCHOOL OF ENGINEERING AT KYUSHU INSTITUTE OF TECHNOLOGY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN APPLIED SCIENCE FOR INTEGRATED SYSTEM ENGINEERRING

Approved by Examiners Committee:

| Prof. KENICHI ASAMI    | Kenichi Asami     |

|------------------------|-------------------|

| Prof. MENGU CHO        | Cho Mengi         |

| Prof. KEI-ICHI OKUYAMA | Keiichi Okurama   |

| Prof. KAZUHIRO TOYODA  | Kazuhiro Toyoda 🗃 |

| Prof. MOTOKI MIURA     | 1stoki Minra      |

رسم الله الرحمن الرحيم وَمَا أُوتِيتُم مِّنَ الْعِلْمِ إِلَّا هَلِيلًا صدق الله العظيم "Success is not final, failure is not fatal:

It is the courage to continue that counts."

By

- Winston S. Churchill -

# Mohamed Elhady Magdy Mohamed Gad Keshk All Rights Reserved

© 2018

### **DEDICATION**

To the soul of My Father, My great Mother,

My pretty Spouse,

And

My son

Without their support, this labor would not have been possible

#### **AKNOWLEDGMENTS**

First and foremost, all praises and gratitude means reciprocating gentleness to the one who has done worthy and kind things to me. The one who is most commendable of thanks and praise is Allah, the almighty, because of the great favoritisms and blessings that he has bestowed upon his slaves in both spiritual and worldly terms and who gave me the ability and bestowed me with perseverance to write this thesis.

I would like to express my sincere appreciation and thanks to my supervisor Professor KENICHI ASAMI, you have been a tremendous mentor for me. I would like to thank you for encouraging my research and for allowing me to grow as a research scientist. Your advice on both research as well as on my career have been priceless. I would also like to thank my committee members, Professor CHO MENGU, Professor KEI-ICHI OKUYAMA, Professor KAZUHIRO TOYODA, and Professor MOTOKI MIURA for serving as my committee members even at hardship. I also want to thank you for letting my mid-term evaluation and final defense be an enjoyable moment, and for your brilliant comments and suggestions, thanks so much to you. I would especially like to thank all members: Asami Lab members (Doctors, Masters, and Bachelors), Ten-koh satellite project and Cho Lab members (Post Docs, Doctors, Masters, and Bachelors) in the department of applied sciences and integrated system Engineering of Kyushu Institute of Technology (Kitakyushu, Japan). All of you have been there to support and help me to accomplish my doctoral study when I started my research.

A Lot of thanks especially Dr. Werner Balogh to the UNOOSA United Nations Office Outer Space Affairs in Austria, which offers me Japan Long-Term Fellowship Program 2015 till 2018 for Post-graduate study on Nano-Satellite Technologies (PNST) in collaboration with Egyptian Space Program and Kyushu Institute of Technology.

A special thanks to my family. Words cannot express how grateful I am to my parents, brother, and Sister, for all of the sacrifices that you've made on my behalf. Your prayer to

Allah for me was what sustained me thus far. I would also like to thank all of my Muslim friends (Professor Yasser, Dr. Yahia, Dr. Sidi, Emad, Ibrahim, Gaber, Hisham, Tamer, Rahmi, Fathin, ...) who respondents for the support, willingness and enchanted me to strive towards my goal.

The participants of Asami laboratory (Amartuvshin, Rafael, Cosmas, Tuguldur, and all the others) and many other students from other laboratories (Dr. Dima, Bonsu, Apiwat, Fukuda, ...) have been great relations and colleagues and I am appreciative for the great time we spent together, for our wonderful trips and for all the great retentions.

I would like express appreciation to my beloved wife and my baby who spent sleepless nights with and were always my support in the moments when there was no one to answer my queries.

#### **PREFACE**

The collaboration among countries in space field promotes the financial efficiency and political sustainability. The space faring nations have most of the responsibility to enhance and make the best use of such collaborations. There are many collaborations aim. The high cost of building a satellite and its ground infrastructure causes the increment of the number of international cooperation in space field to support and encourage the developing and emerging countries to have a position in space and participate in space activities by developing small or lean satellites without affording huge costs.

These collaborations are aimed to build the human capacity of these countries by participating in joint satellites projects. Instead of developing ground infrastructure which needs huge cost and takes a lot of time, these countries can use the existing facilities of the faring countries. The existing ground stations may face the problem of using different modulation and demodulation techniques limits the number of these stations that can communicate with the satellites. Developing the ground stations and/or satellites by installing several transceivers can be used as an alternative to overcome this problem but this solution increases both the complexity, power consumption, and the cost of both ground station and satellite. The same problem faces the communication between a satellite and a relay satellite.

This research aims to overcome such a problem by implementing a prototype of a dynamic partial reconfigurable demodulation system that can be used as a core of a generic receiver for the satellite receivers. This system performs the role of a generic receiver but with low complexity, power consumption, and cost of a satellite. In fact, the system is not only promoting the international collaboration, but also it overcomes the channel problems by alternating the modulation and demodulation techniques based on channel condition, which enhances the communication quality. The system is based on pattern recognition approach, software defined radio and FPGA dynamic partial

reconfiguration technology to reduce the hardware complexity and obsolescence, power consumption, and cost of a satellite.

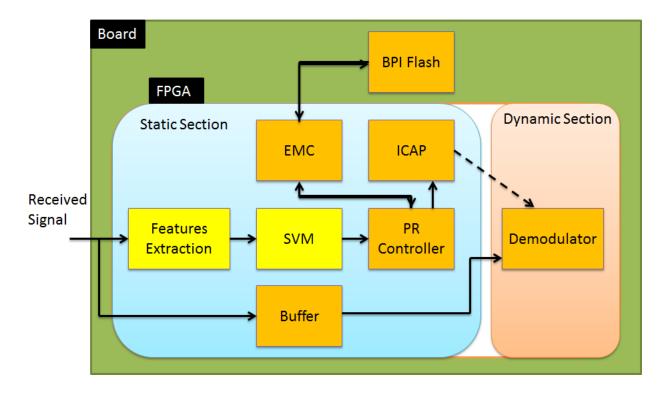

The dynamic partial reconfigurable demodulator system is divided into 2 main sections; automatic digital modulation recognition (ADMR), and dynamic partial reconfiguration (DPR) sections. The ADMR can be used in relay satellites and other satellites where the demodulation and re-modulation of the data is performed onboard. In addition, ADMR can be used to overcome channel problems during the communication session with a satellite as bandwidth congestion/crunch by changing the existing modulation scheme by another more efficient bandwidth modulation scheme. ADMR can be used to secure the received and transmitted signal by locating, classifying and preventing the unwanted signals. ADMR can be used in interference identification, spectrum monitoring, signal confirmation, electronic warfare, cognitive radio, threat analysis, and signal surveillance.

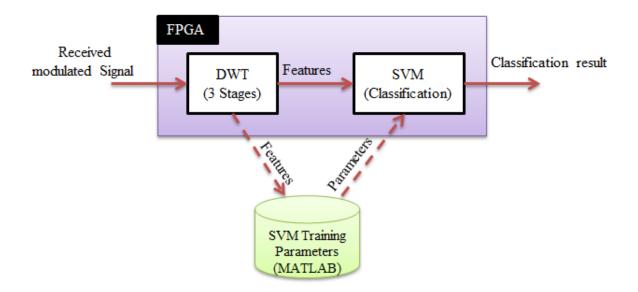

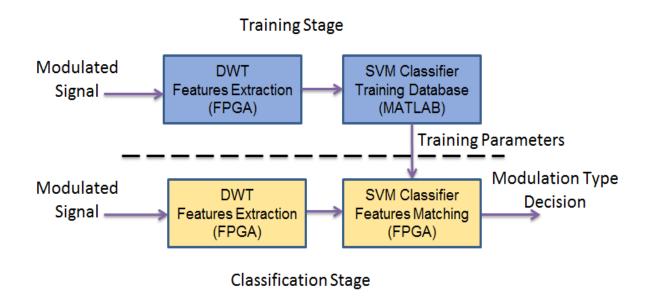

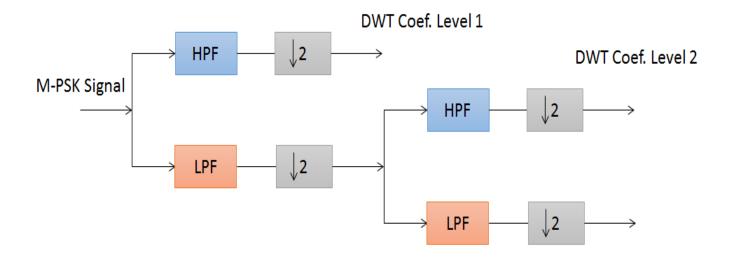

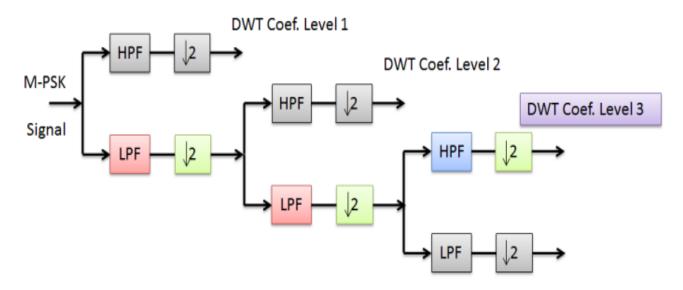

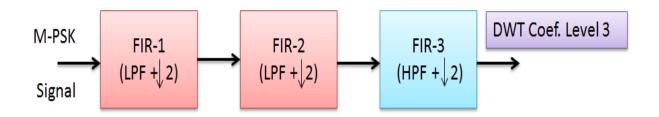

ADMR is responsible of the classification of the modulation type of the received modulated signal and it consists of features extraction and SVM classifier modules. Features module is to extract the features of the received modulated signal which in this thesis is the discreet wavelet transform (DWT) coefficients level3. The realization of this module on FPGA requires the use 3 DWT stages each stage is implemented by a finite impulse response filter. Two low pass filters and one high pass filter is required for the implementation. These features are the input to the SVM classifier.

SVM classifier is a binary classifier that uses to classify two received modulation types BPSK and QPSK. The classifier has two stages; training stage which is performed using MATLAB to train the classifier with the features of both BPSK and QPSK modulations. The aim of this stage is to construct the classifier then the resulting parameters will be used to design and implement the classifier on FPGA. The second stage is the classification stage which classify the received modulation types based on the prior generated parameters (weights, Alpha, bias) during training stage and using radial base function as a SVM kernel function. The classification result is the input of the DPR section.

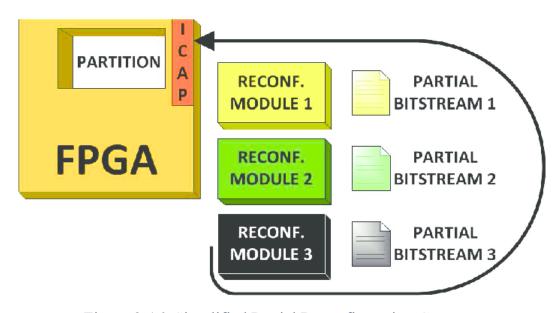

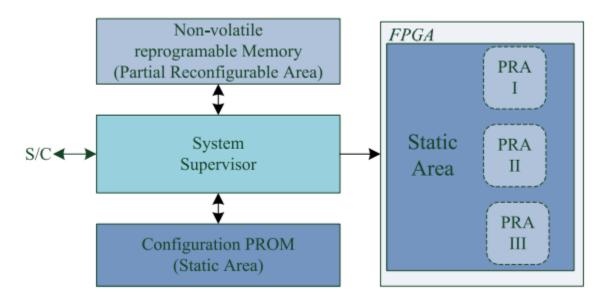

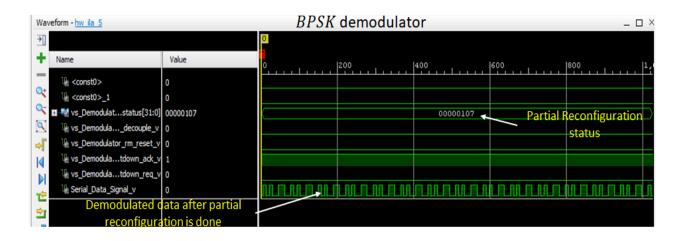

The DPR section consists of partial reconfiguration controller (PRC), external memory controller (EMC) and internal configuration access port (ICAP). PRC is the controller of the whole reconfiguration process. It stores the addresses of the BPSK and QPSK demodulator on external flash memory and according to the classification result, which act as a trigger to DPR controller, DPR sends the corresponding demodulator address to EMC to fetch the demodulator partial bitstream from external memory then resends this bitstream file to DPR controller. Then, DPR controller sends the partial bitstream file to ICAP port to reconfigure the reconfigurable partition by the proper demodulator. After that, the original binary sequence is obtained.

The BPSK and QPSK demodulators are implemented based on SDR using a sine and cosine lookup table instead of sine and cosine wave generator. The demodulation is done by multiplying the samples of the received signal by the sine/cosine samples that stored into the lookup tables.

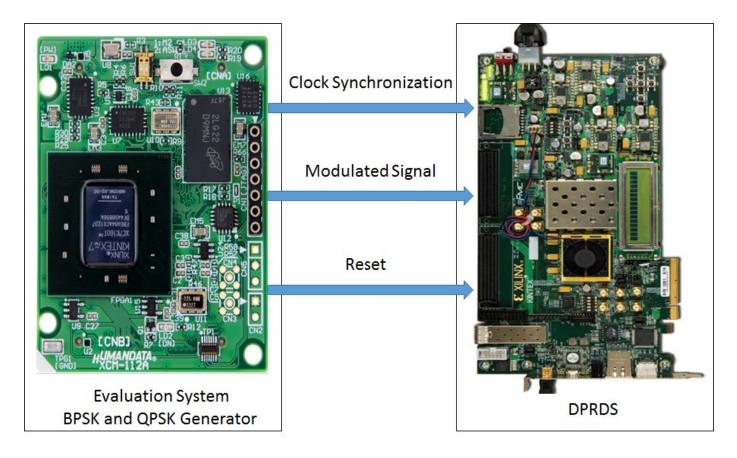

The performance of the system is evaluated by implementing a BPSK and QPSK modulator on a kintex-7 FPGA board to act as the received signal for dynamic partial demodulator system that implemented into another kintex-7 board to compute the classification rate with the presence of AWGN with SNR from -10 to 20 dB, classification time, and reconfiguration time.

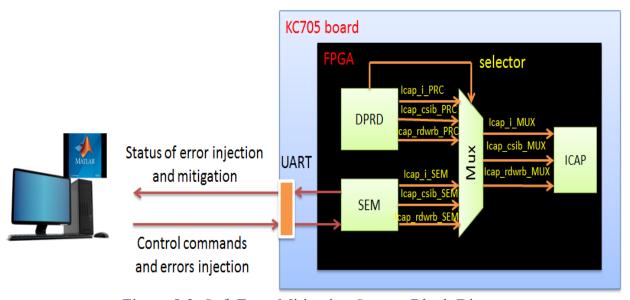

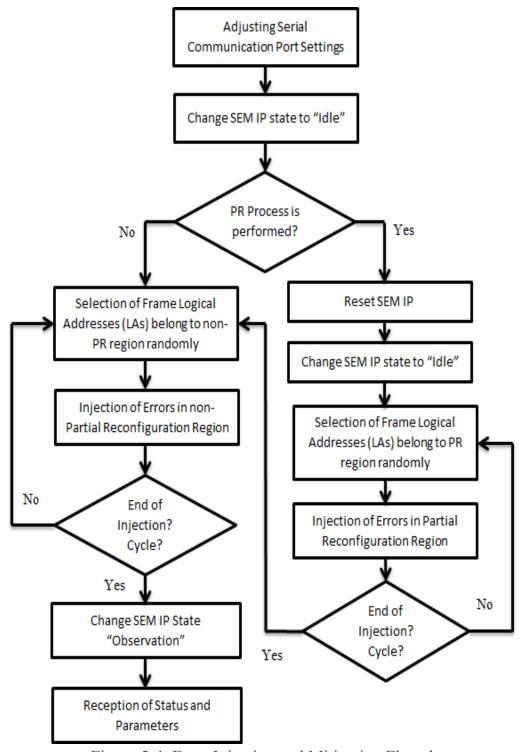

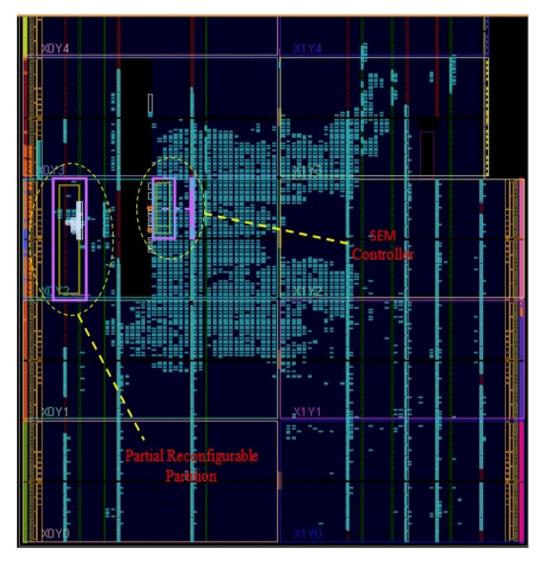

In this dissertation, the multiple access of ICAP primitive by several application is approved. The DPRDS and Soft Error Mitigation (SEM) systems are used to run together on FPGA and acquired the access of ICAP primitive. The results showed that the implementation of DPR design will not prevent the SEM application from the access of the ICAP primitive and vice versa.

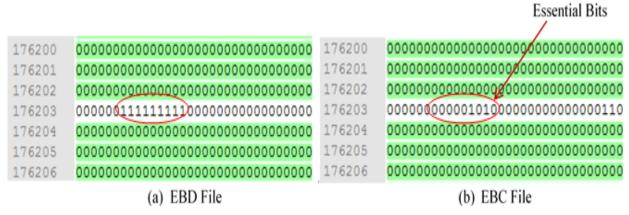

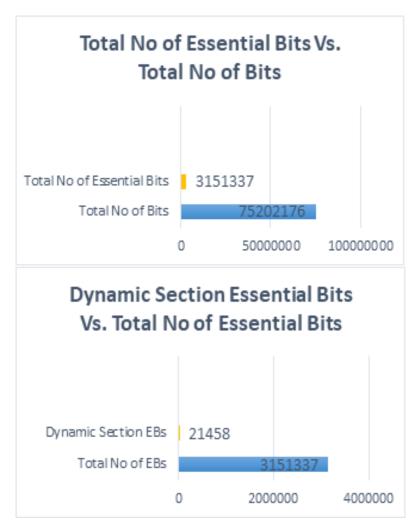

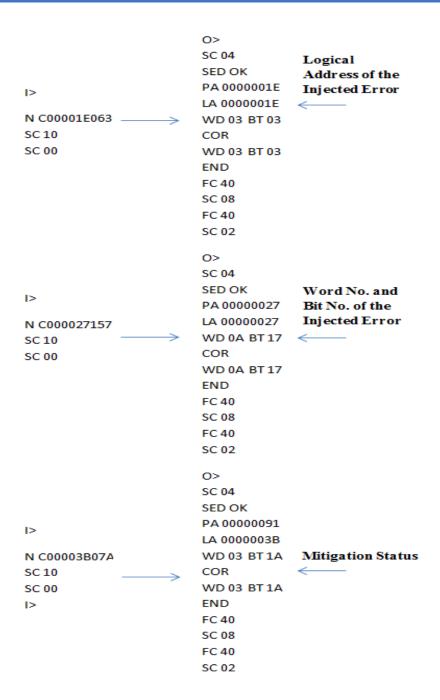

Using the Xilinx essential bit technology reduces the time required to inject and mitigate the errors in the DPRDS design by a 96%. The main reason is essential bit technology based of injecting the error only into the bits of the configuration frame that are used by the design and ignoring the other bits. To get the essential bits, Essential Bits Configuration (EBC) and Essential Bits Definition (EBD) files have to be generated for comparing the bits existing into EBD file with the corresponding bits of EBC file, where

bits of value 1 in EBD file mean the corresponding bits in EBC file are essential, otherwise, the corresponding bits in EBC file are not essential.

A MATLAB script is used to calculate the Logical Addresses (LAs) of these bits, and control and monitor the injection and mitigation of the errors on FPGA, through UART interface, in both static and dynamic sections of the DPRDS design on the conditions of SEM IP core and the results showed that the both DPRDS and SEM applications are working properly.

### **Table of Contents**

| AKNOWLEDGMENTS                                         | I      |

|--------------------------------------------------------|--------|

| PREFACE                                                | III    |

| Table of Contents                                      | VII    |

| List of Figures                                        | X      |

| List of Tables                                         | XIII   |

| List of Symbols                                        | XIV    |

| List of Acronyms                                       | XV     |

| Chapter 1 : Introduction                               | 1 -    |

| 1.1. Problem Statement and Motivation                  | 4 -    |

| 1.2. Research Objectives                               | 7 -    |

| 1.3. Research Originality                              | 7 -    |

| 1.4. Research Methodology                              | 8 -    |

| 1.5. Dissertation Challenges                           | 9 -    |

| 1.6. Dissertation Organization                         |        |

| Chapter 2 : Background and Literature Review           |        |

| 2.1. SDR Overview                                      | 13 -   |

| 2.1.1. SDR Background and Principle                    |        |

| 2.1.2. SDR Architecture                                | 14 -   |

| 2.1.2.1. SDR Transmitter                               | 16 -   |

| 2.1.2.2. SDR Receiver                                  | 17 -   |

| 2.1.3. SDR Platforms                                   | 18 -   |

| 2.2. Automatic Digital Modulation Recognition Overview | - 20 - |

| 2.2.1. ADMR Principle and Background                   | 20 -   |

| 2.2.2. ADMR Approaches                                 | 23 -   |

| 2.2.2.1 Decision-Theoretic                             | 23 -   |

| 2.2.2.2 Pattern Recognition                            | 23 -   |

| 2.2.2.2.1. Pre-Processing                              | 24 -   |

| 2.2.2.2 Features Extraction                            | 24 -   |

| 2.2.2.2.3 Pattern Recognizer                           | 24 -   |

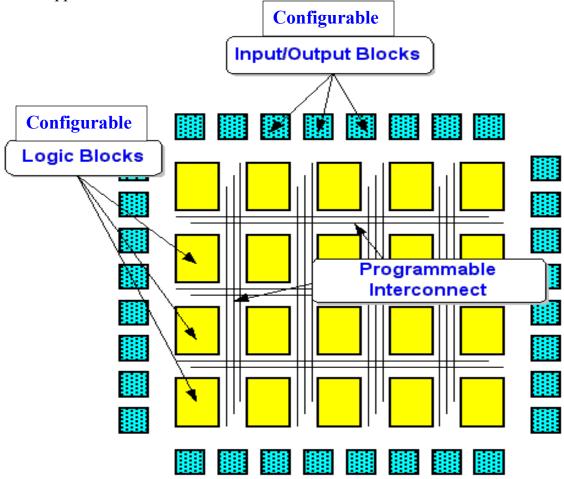

| 2.3. FPGA Overview                                     | 26 -   |

| 2.3.1. FPGA Architecture                               |        |

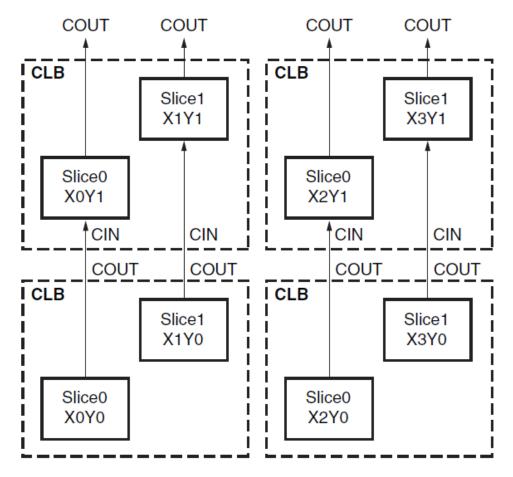

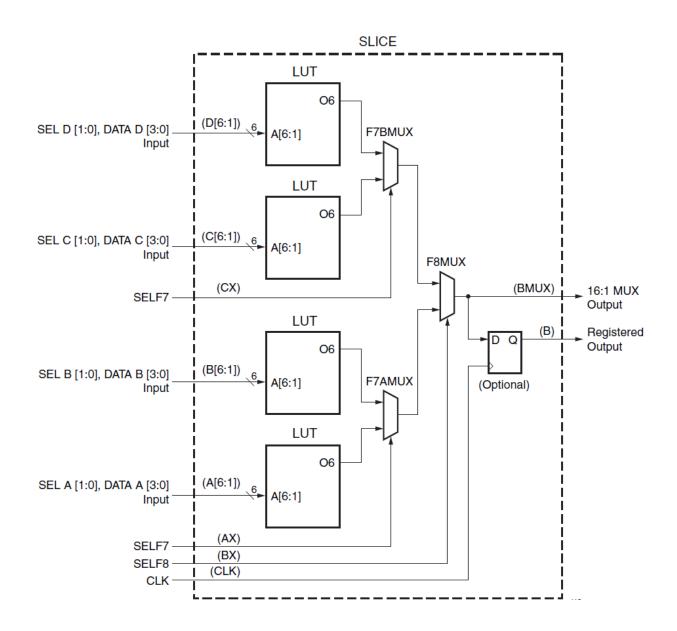

| 2.3.1.1. Configurable Logic Blocks                     | 28 -   |

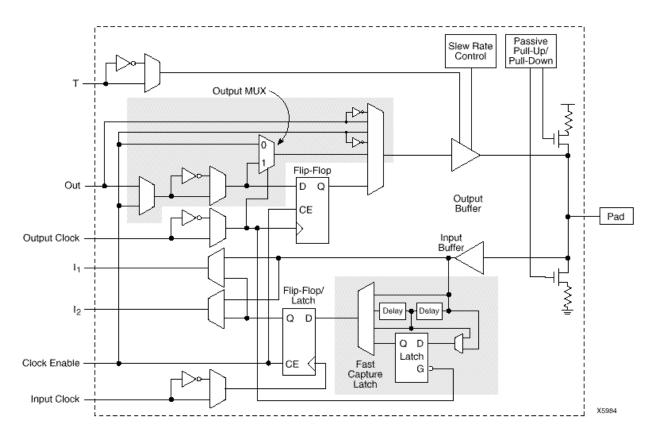

| 2.3.1.2. I/O Blocks                                    | 29 -   |

| 2.3.1.3. Programmable Interconnect                                              | 30 -  |

|---------------------------------------------------------------------------------|-------|

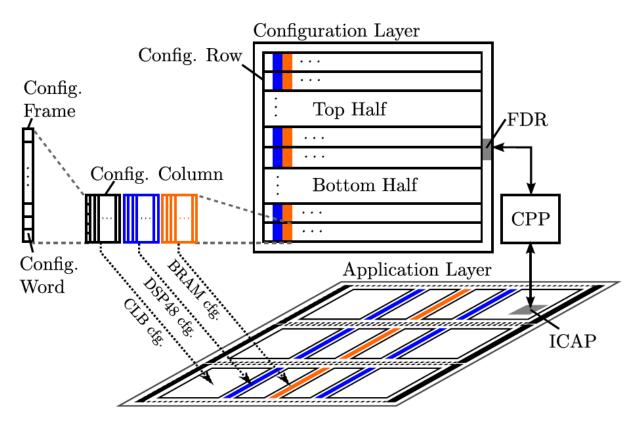

| 2.3.2. Application Layer                                                        | 32 -  |

| 2.3.3. Configuration Layer                                                      | 33 -  |

| 2.3.4. FPGA Configuration Methods                                               | 34 -  |

| 2.3.4.1. Full Configuration                                                     | 34 -  |

| 2.3.4.2. Partial Configuration and Reconfiguration                              | 34 -  |

| 2.3.4.2.1. Dynamic Partial Reconfiguration                                      | 35 -  |

| 2.3.4.2.2. Dynamic Partial Self-Reconfiguration                                 | 35 -  |

| 2.3.4.1. Advantages of Partial Reconfiguration                                  | 36 -  |

| 2.4. Digital Modulation Techniques                                              | 36 -  |

| 2.4.1. BPSK Concept                                                             | 37 -  |

| 2.4.1.1. BPSK Modulation                                                        | 37 -  |

| 2.4.1.2. BPSK Demodulation                                                      | 39 -  |

| 2.4.2. QPSK Concept                                                             | 39 -  |

| 2.4.2.1. QPSK Modulation                                                        | 40 -  |

| 2.4.2.2. QPSK Demodulation                                                      | 42 -  |

| 2.5. Related Work                                                               | 43 -  |

| Chapter 3 : Dynamic Partial Reconfigurable Demodulation System - Classification | 50 -  |

| 3.1. DPRDS – Classification                                                     | 51 -  |

| 3.2. Modulation Type Classification Based on Pattern Recognition                | 55 -  |

| 3.2.1. FPGA Based DWT                                                           | 55 -  |

| 3.2.2. FPGA Based SVM                                                           | 59 -  |

| 3.2.2.1. Binary Classifier Based SVM                                            | 59 -  |

| 3.3. Evaluation System Design                                                   | 72 -  |

| 3.4. Performance Evaluation Aspects of DPRDS-Classification System              | 76 -  |

| 3.4.1. Testing Configuration                                                    | 77 -  |

| 3.4.2. Results and Discussion                                                   | 80 -  |

| 3.4.2.1. Results and Discussion of Testing the DPRDS-Classifier using KIT GCS   | 94 -  |

| Chapter 4 : DPRDS - DPR                                                         | 98 -  |

| 4.1. DPRDS-DPR                                                                  | 98 -  |

| 4.2. Dynamic Partial Reconfiguration                                            | 100 - |

| 4.2.1. Dynamic Partial Reconfiguration Methodology                              | 100 - |

| 4.2.2. Dynamic Partial Reconfiguration Ports                                    | 101 - |

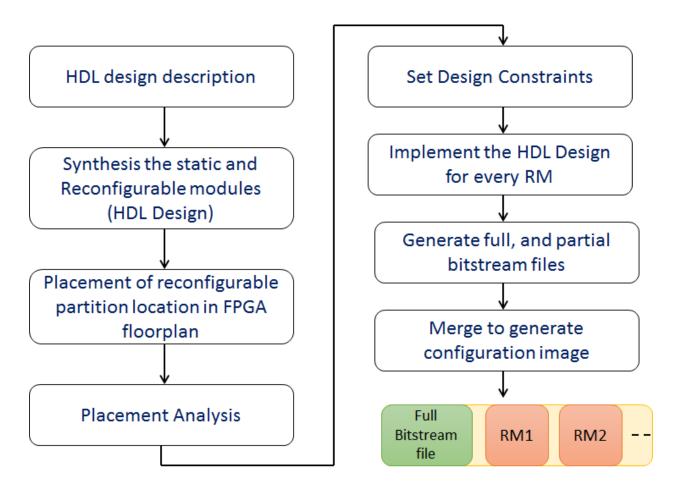

| 4.2.3. Dynamic Partial Reconfiguration Design Flow                      | 102 - |

|-------------------------------------------------------------------------|-------|

| 4.2.3.1. Difference-Based PR                                            | 102 - |

| 4.2.3.2. Module-Based PR                                                | 103 - |

| 4.3. FPGA Based BPSK and QPSK Demodulators                              | 105 - |

| 4.3.1. BPSK Demodulator                                                 | 105 - |

| 4.3.2. QPSK Demodulator                                                 | 106 - |

| 4.4. FPGA Based DPRDS-DPR                                               | 107 - |

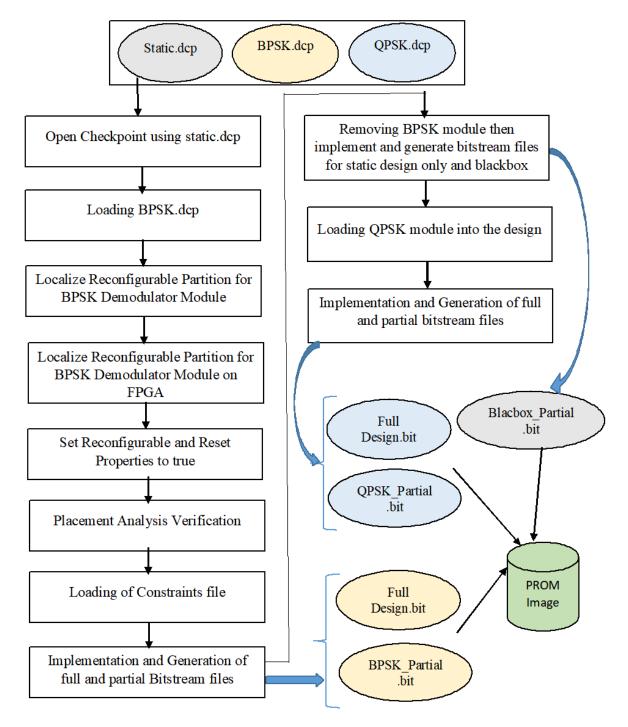

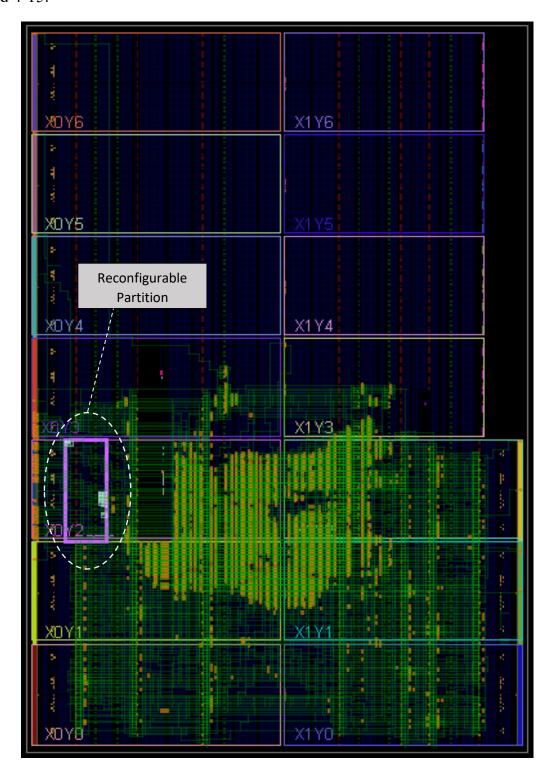

| 4.4.1. Design and Implementation Flow                                   | 111 - |

| 4.5. Performance Evaluation Aspects of DPRDS-Classification System      | 113 - |

| Chapter 5: ICAP Multiple Access by DPRDS and SEU Mitigation Systems     | 125 - |

| 5.1. Background of SEU mitigation                                       | 125 - |

| 5.2. The Principle of Soft Error Injection and Mitigation System        | 127 - |

| 5.3. Sharing ICAP for Soft Error Mitigation and Partial Reconfiguration | 129 - |

| 5.4. Soft Error Mitigation System                                       | 130 - |

| 5.5. Results and Discussion                                             | 133 - |

| Chapter 6 : Conclusion and Future Perspective                           | 140 - |

| 6.1. Conclusion                                                         | 140 - |

| 6.2. Future Perspective                                                 | 144 - |

| List of Publications                                                    | 146 - |

| Deferences                                                              | 1.47  |

## **List of Figures**

| Figure 1-1. Problem Statement Configuration                                    | 5 -    |

|--------------------------------------------------------------------------------|--------|

| Figure 1-2. Dissertation Challenges                                            | 9 -    |

| Figure 1-3. Dissertation Sequential                                            | 10 -   |

| Figure 2-1. Different Configurations of SDR System                             | 15 -   |

| Figure 2-2. Real SDR Model [15]                                                | - 16 - |

| Figure 2-3. SDR Transmitter Block Diagram                                      | 17 -   |

| Figure 2-4. SDR Receiver Block Diagram                                         |        |

| Figure 2-5. Comparison among FPGA and other programmable devices               | 19 -   |

| Figure 2-6. Basic pattern recognition system Block Diagram.                    | - 22 - |

| Figure 2-7. Pattern Recognition System Block Diagram.                          | - 23 - |

| Figure 2-8. Generic FPGA Architecture.                                         | 27 -   |

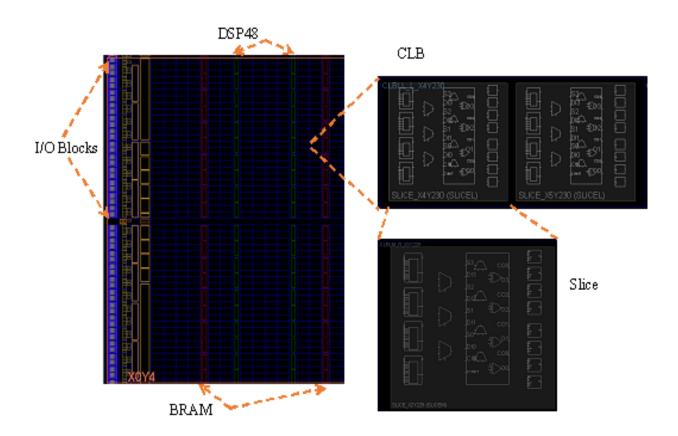

| Figure 2-9. CLB Architecture [28].                                             | - 28 - |

| Figure 2-10. Slice Block Diagram [28]                                          | - 29 - |

| Figure 2-11. I/O Block Architecture of XC4000EX Series.                        | - 30 - |

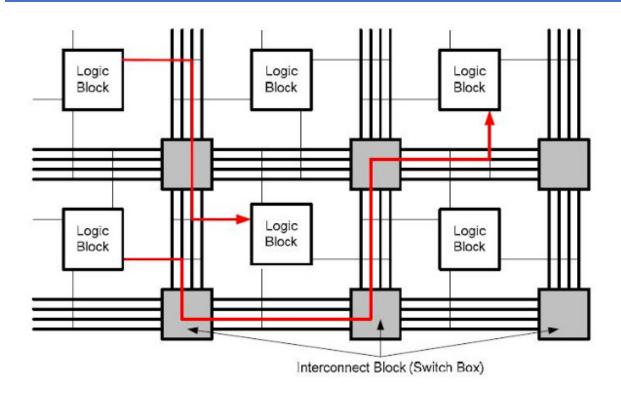

| Figure 2-12. Programmable interconnect with Switch Matrix.                     | 31 -   |

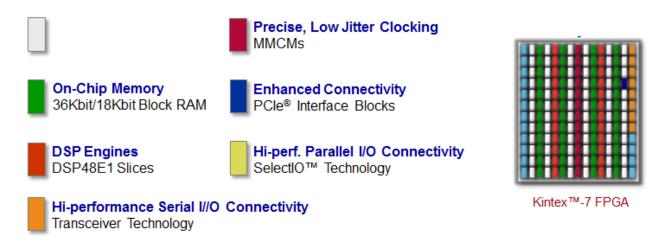

| Figure 2-13. FPGA Architecture Alignment.                                      |        |

| Figure 2-14. FPGA Application Layer Elements                                   |        |

| Figure 2-15. Concept of Operation of Configuration and Application Layers [27] | - 33 - |

| Figure 2-16. Simplified Partial Reconfiguration Concept.                       | - 35 - |

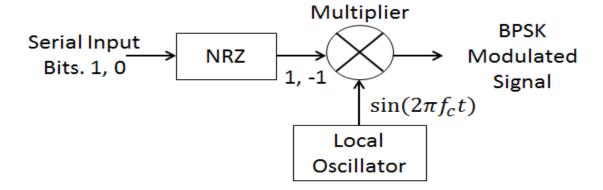

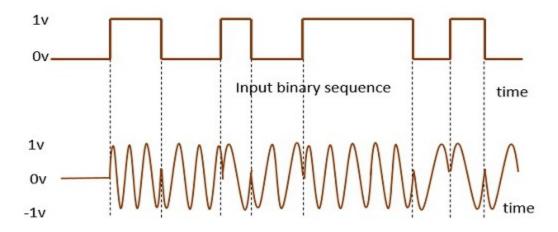

| Figure 2-17. BPSK Modulation Block Diagram.                                    | 37 -   |

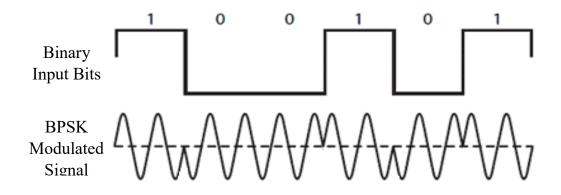

| Figure 2-18. Input Binary Data and Corresponding Output Symbols                | - 38   |

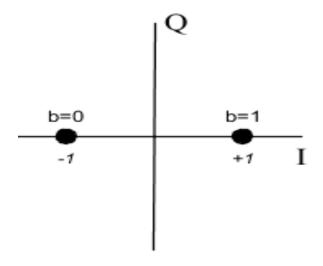

| Figure 2-19. BPSK Constellation Diagram.                                       |        |

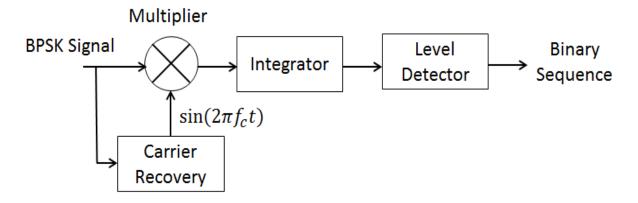

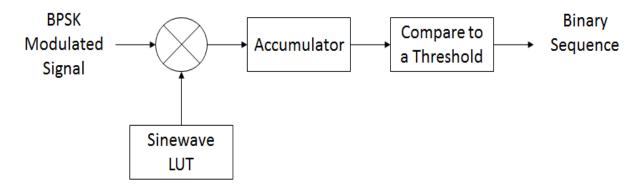

| Figure 2-20. BPSK Demodulation Block Diagram                                   | - 39 - |

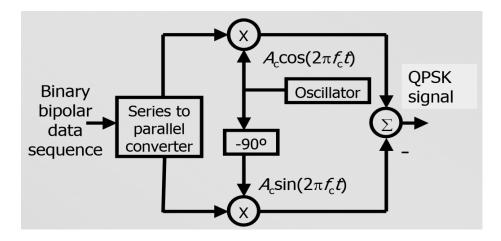

| Figure 2-21. QPSK Modulation Block Diagram.                                    | 41 -   |

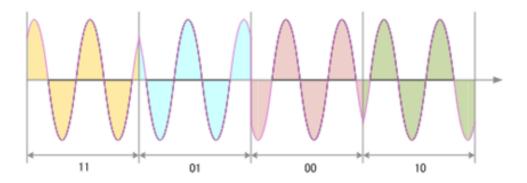

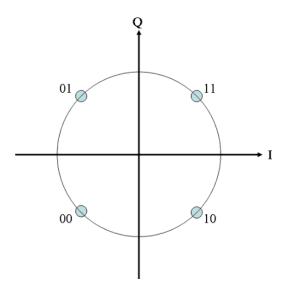

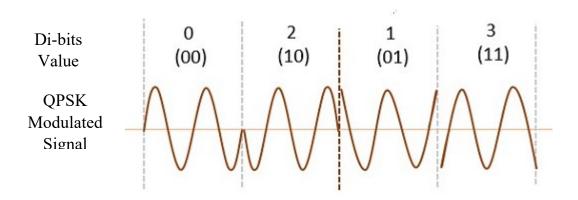

| Figure 2-22. Input di-bits and Corresponding Output Symbols.                   | 41 -   |

| Figure 2-23. QPSK Constellation Diagram.                                       | 42 -   |

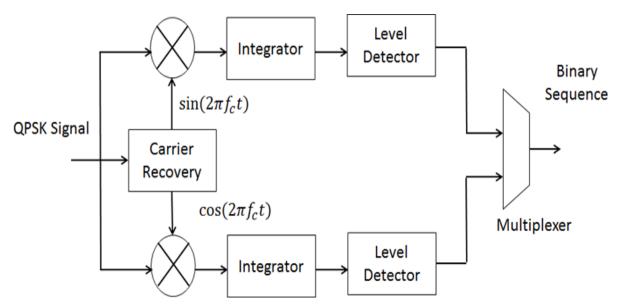

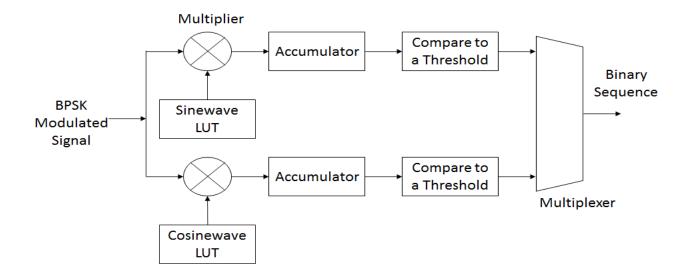

| Figure 2-24. QPSK Demodulation Block Diagram.                                  | 43 -   |

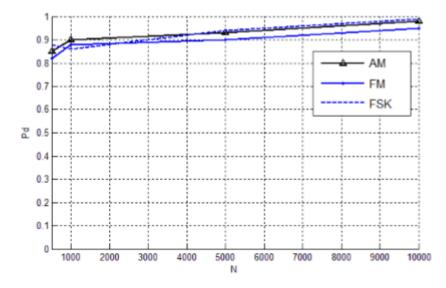

| Figure 2-25. Detection Probability According to Number of Samples.             | 45 -   |

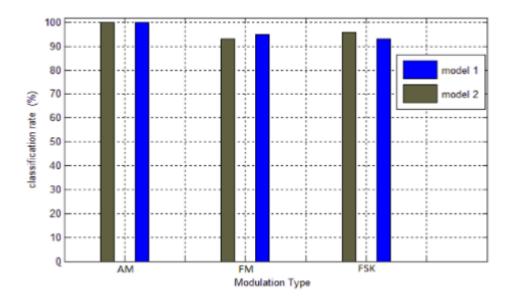

| Figure 2-26. Classification Rate for Original and Reduced Data.                |        |

| Figure 2-27. FPGA Reconfigurability Framework.                                 |        |

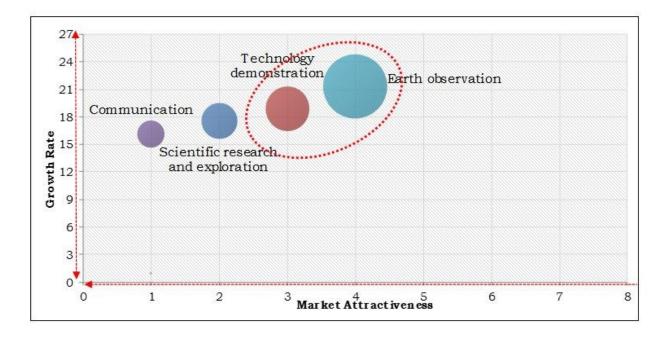

| Figure 3-1. Growth Potential of the Global Small Satellite Market              |        |

| Figure 3-2. Modified Basic Pattern Recognition System                          | - 51 - |

| Figure 3-3. DPRDS Design Block Diagram.                                        | - 52 - |

| Figure 3-4. Modulation Classification Process.                                 | 54 -   |

| Figure 3-5. ADMC Operation Concept.                                            | - 55 - |

| Figure 3-6. 2-D DWT Configuration.                                             | - 57 - |

| Figure 3-7. 3-D DWT Configuration.                                             | - 58 - |

| Figure 3-8. Realization of 3-D DWT on FPGA.                                    |        |

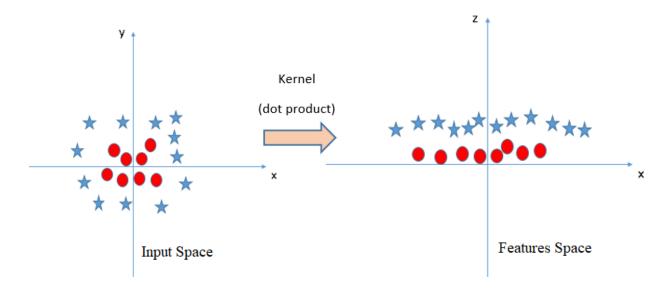

| Figure 3-9. Space Transformation using Kernel function.                        |        |

| Figure 3-10. SVM Concept.                                                      |        |

| Figure 3-11. SVM Learning Algorithm.                                           |        |

| Figure 3-12. ADMC Concept                                                      |        |

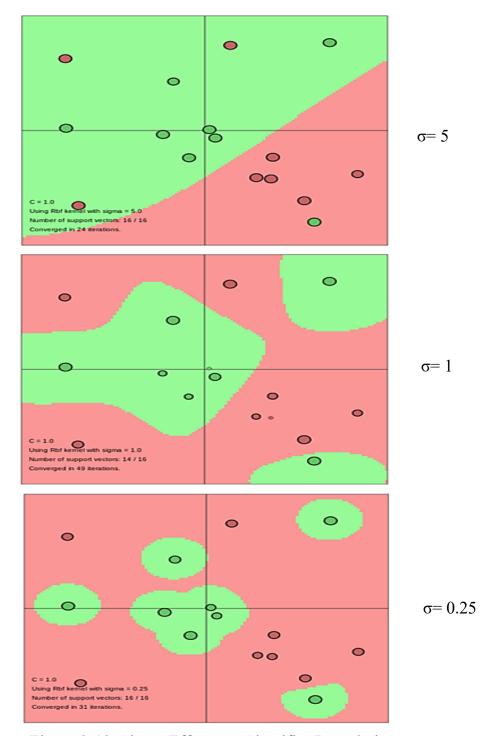

| Figure 3-13. Sigma Effects on Classifier Boundaries.                           | - 68 - |

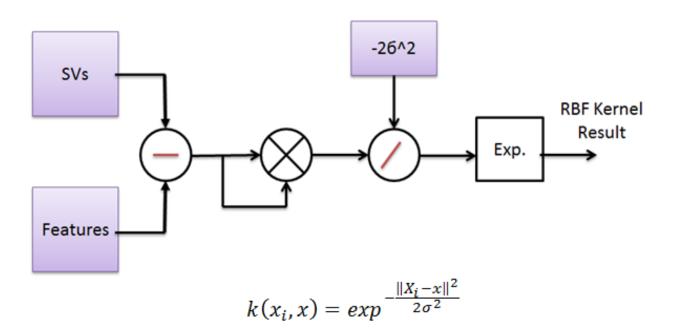

| Figure 3-14. RBF Implementation on FPGA.                                                       | 69 -    |

|------------------------------------------------------------------------------------------------|---------|

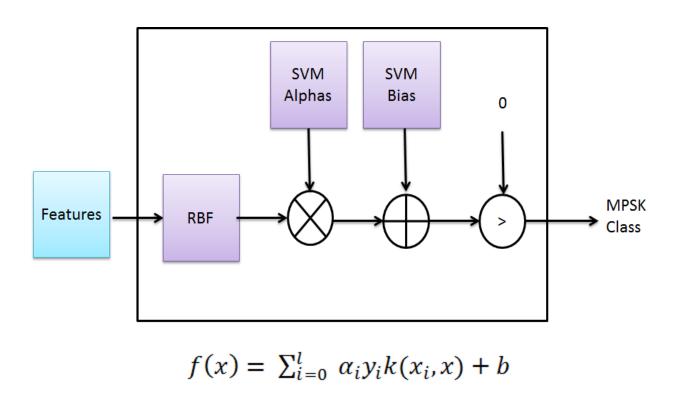

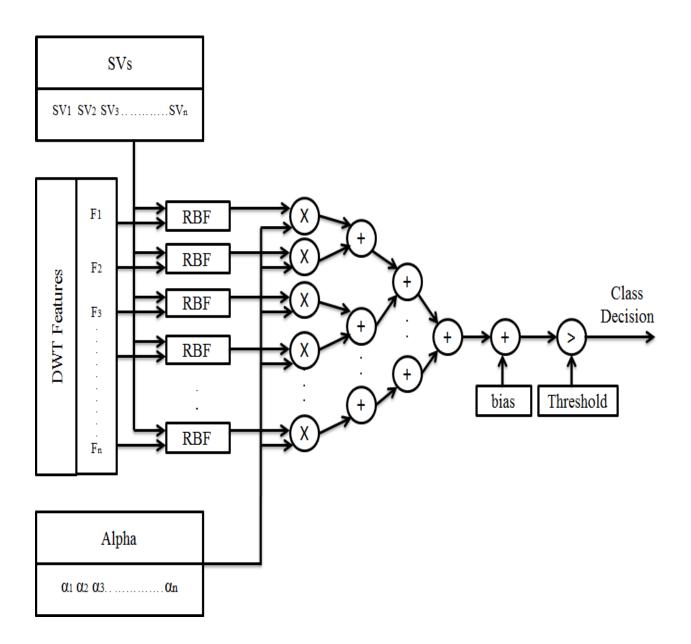

| Figure 3-15. SVM Classifier Implementation on FPGA.                                            | 70 -    |

| Figure 3-16. SVM Architecture.                                                                 | 71 -    |

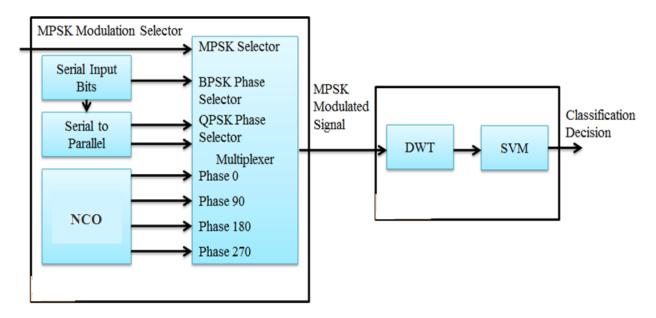

| Figure 3-17. Evaluation System Design.                                                         | 72 -    |

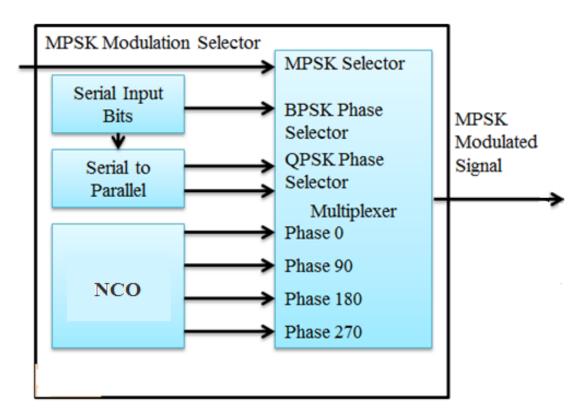

| Figure 3-18. BPSK Modulated Signal.                                                            | 74 -    |

| Figure 3-19. QPSK Modulated Signal.                                                            | 74 -    |

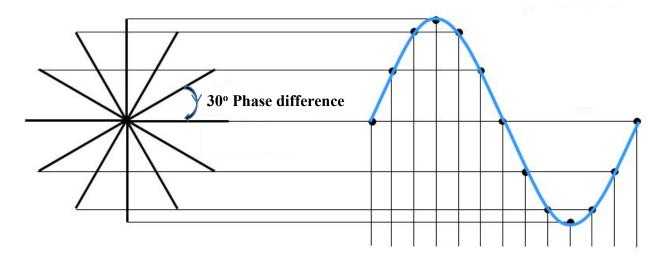

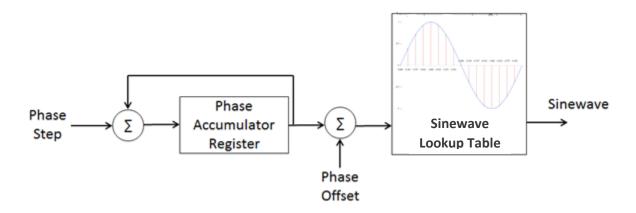

| Figure 3-20. Storing Sinewave Samples in LUT.                                                  | 75 -    |

| Figure 3-21. NCO Configuration.                                                                |         |

| Figure 3-22. Testing Configuration Block Diagram.                                              | 77 -    |

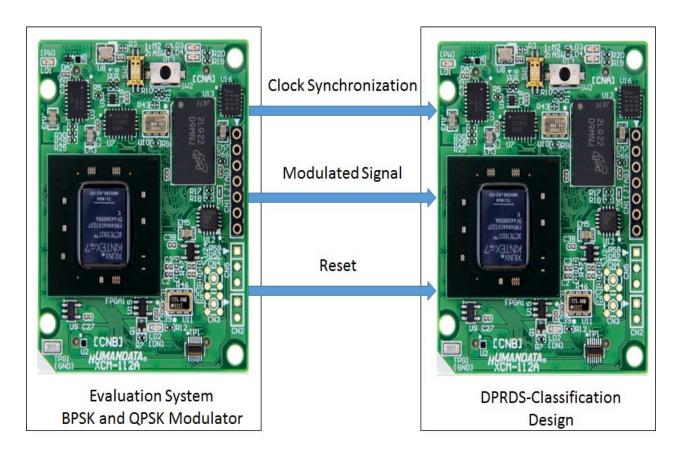

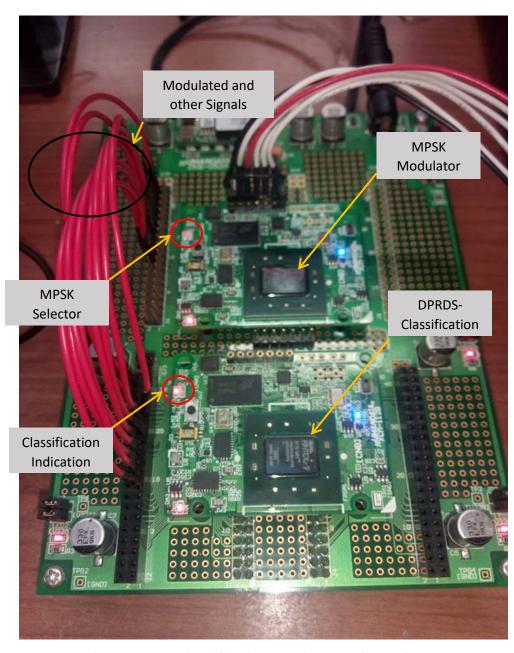

| Figure 3-23. Classification Testing Configuration.                                             |         |

| Figure 3-24. Classification Testing Configuration.                                             | 79 -    |

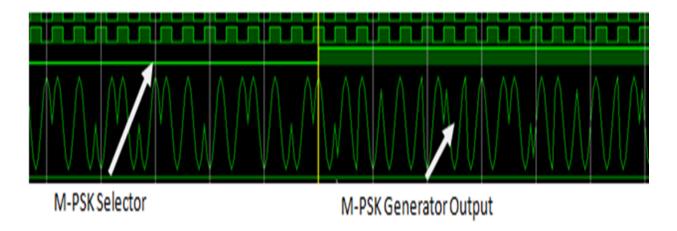

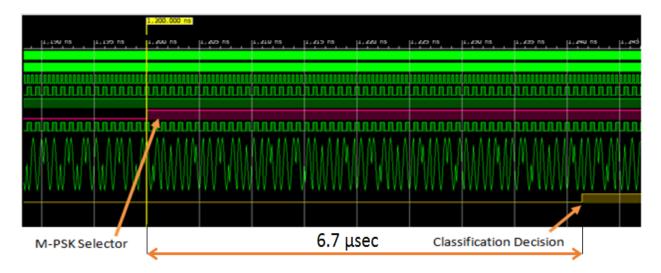

| Figure 3-25. MPSK User Switch Value and The Corresponding Modulated Signal                     | 80 -    |

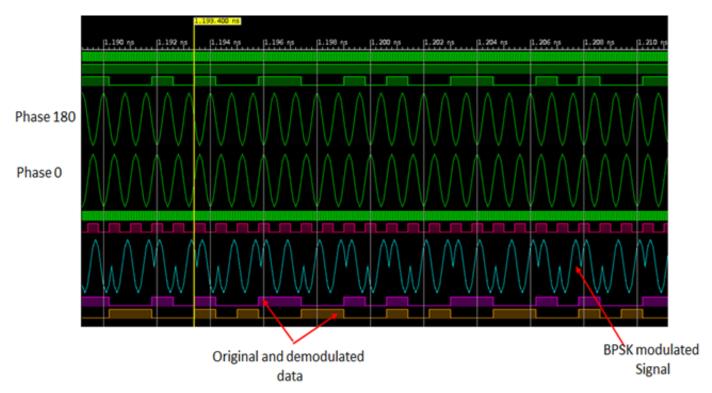

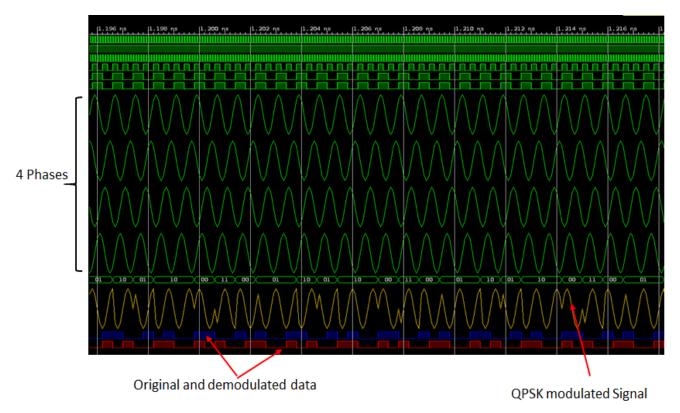

| Figure 3-26. BPSK Modulated and Demodulated Signal.                                            | 81 -    |

| Figure 3-27. QPSK Modulated and Demodulated Signal.                                            | 81 -    |

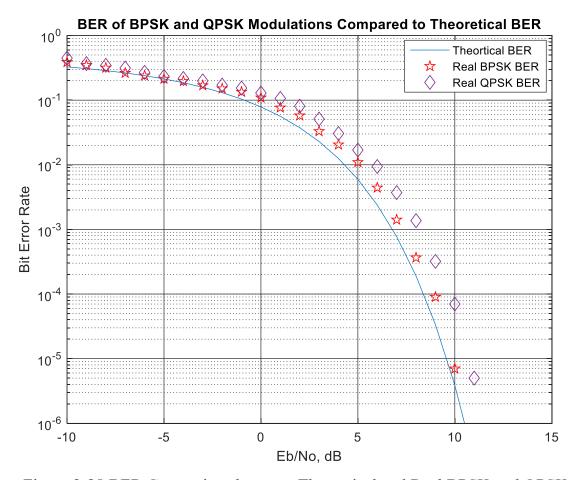

| Figure 3-28 BER Comparison between Theoretical and Real BPSK and QPSK                          | 82 -    |

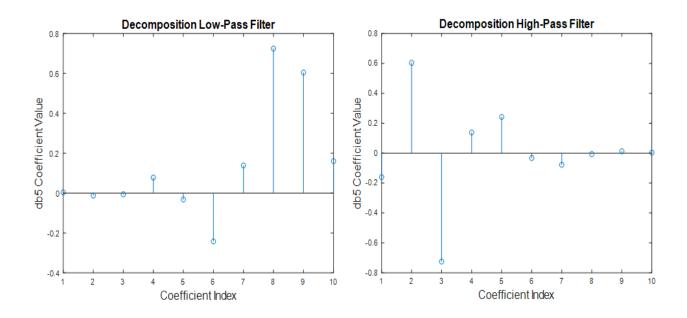

| Figure 3-29. Discrete Representation of LHP and HPF Coefficients.                              | 84 -    |

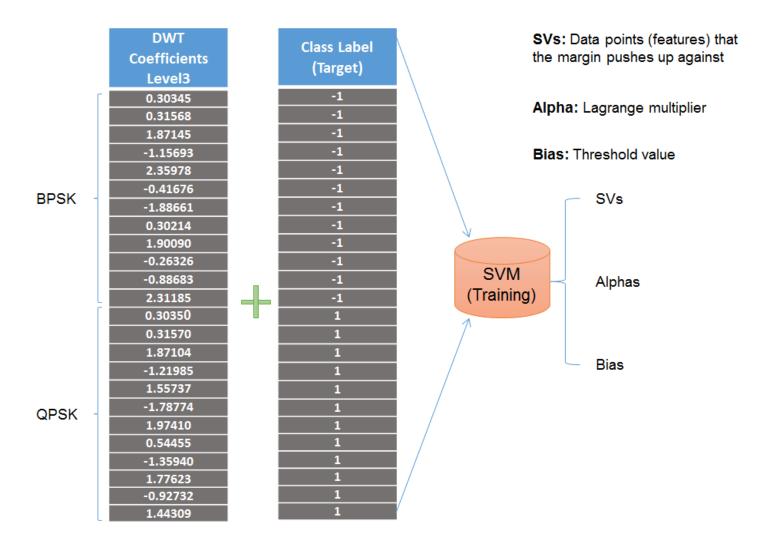

| Figure 3-30 Example on the Training Process of the SVM                                         | 86 -    |

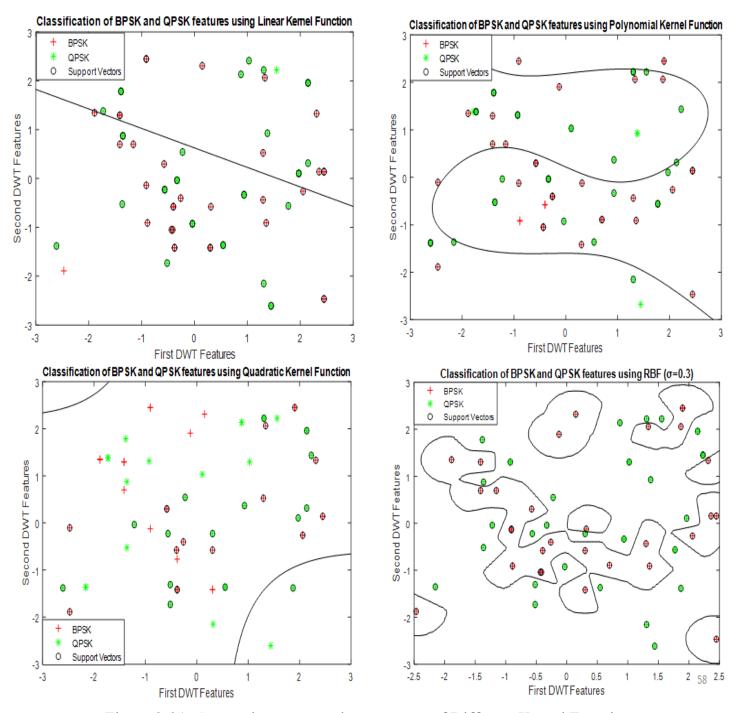

| Figure 3-31. Comparison among the Accuracy of Different Kernel Functions                       | 87 -    |

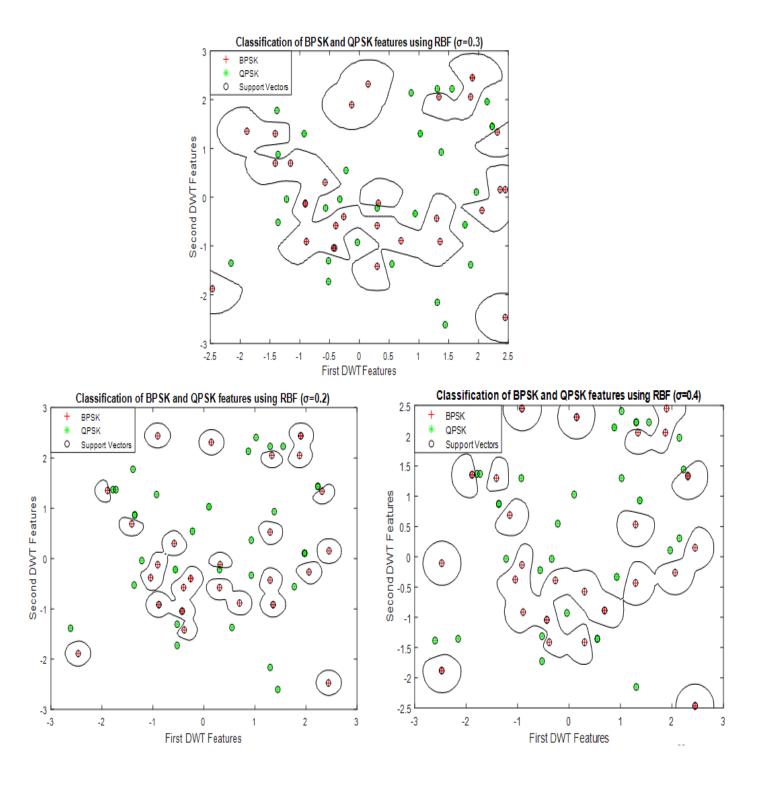

| Figure 3-32. Comparison among the Accuracy of Different Values of σ                            |         |

| Figure 3-33. DPRDS Classification Time.                                                        | 90 -    |

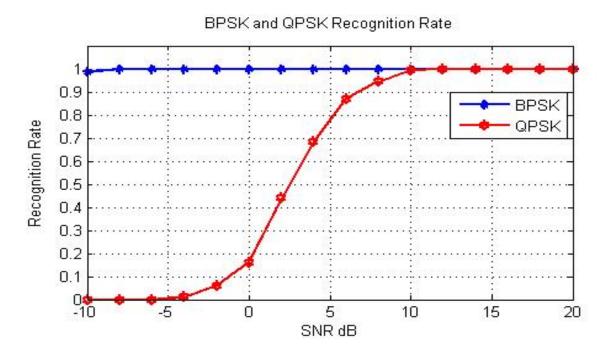

| Figure 3-34. SVM Classifier Recognition Rate for BPSK and QPSK.                                | 91 -    |

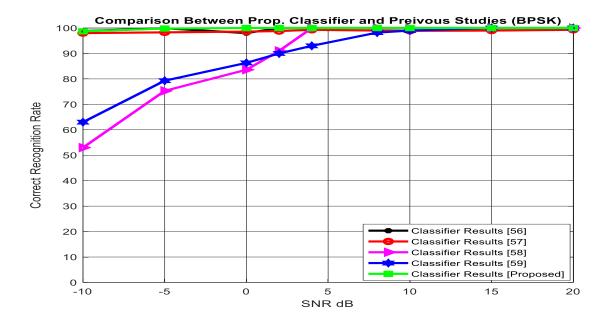

| Figure 3-35. Comparison between SVM Classifier and other studies for BPSK                      | 93 -    |

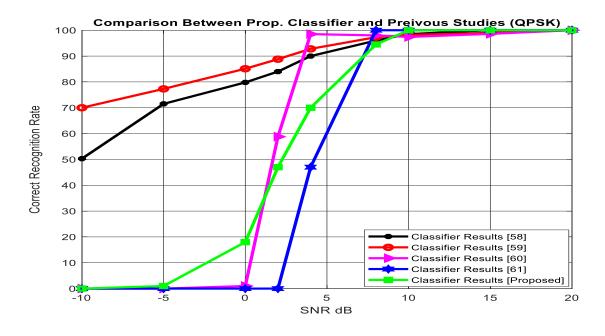

| Figure 3-36. Comparison between SVM Classifier and other studies for QPSK                      | 93 -    |

| Figure 3-37. BPSK Classification Test Setup at GCS of KIT                                      | 95 -    |

| Figure 3-38. The BPSK Classification Test Configuration                                        | 95 -    |

| Figure 3-39. The Extracted Features of BPSK Modulated Signal                                   | 96 -    |

| Figure 4-1. DPRDS Design Block Diagram.                                                        | 99 -    |

| Figure 4-2. Reconfiguration Methodologies.                                                     | 101 -   |

| Figure 4-3. Difference Based PR Concept.                                                       | 103 -   |

| Figure 4-4. Difference Based PR Configuration.                                                 |         |

| Figure 4-5. Module Based PR Configuration.                                                     | 104 -   |

| Figure 4-6. BPSK Demodulator.                                                                  | 105 -   |

| Figure 4-7. QPSK Demodulator                                                                   | 106 -   |

| Figure 4-8. PRC IP Core Configuration.                                                         | 109 -   |

| Figure 4-9. PRC IP Core Design.                                                                | 110 -   |

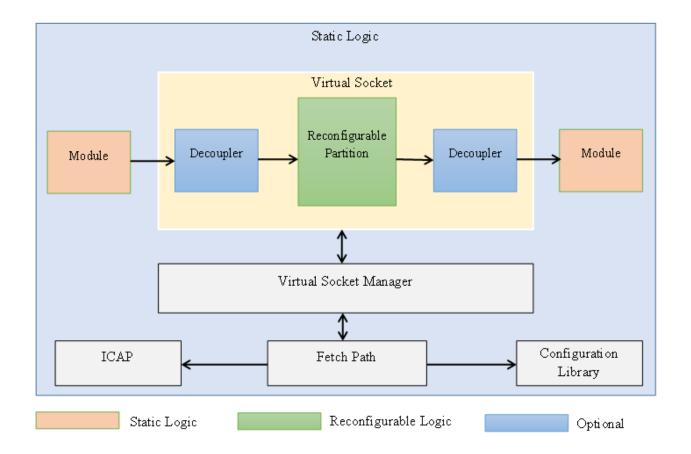

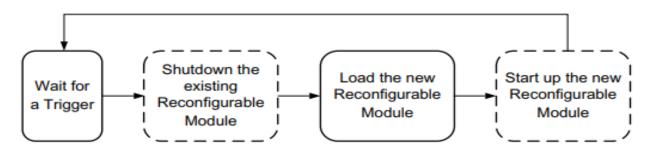

| Figure 4-10. Virtual Socket Manager Steps during DPR.                                          | 111 -   |

| Figure 4-11. DPRDS Flowchart.                                                                  | 112 -   |

| Figure 4-12. DPRDS Testing Configuration.                                                      | 114 -   |

| Figure 4-13. DPR Implementation Steps.                                                         |         |

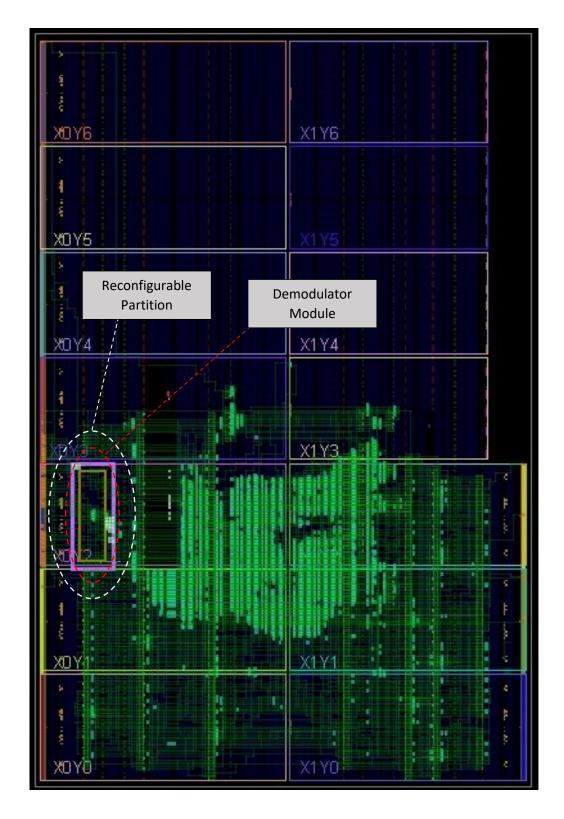

| Figure 4-14. DPRDS FPGA Floorplan without Demodulator Module                                   |         |

| Figure 4-15. DPRDS FPGA Floorplan with Demodulator Module.                                     |         |

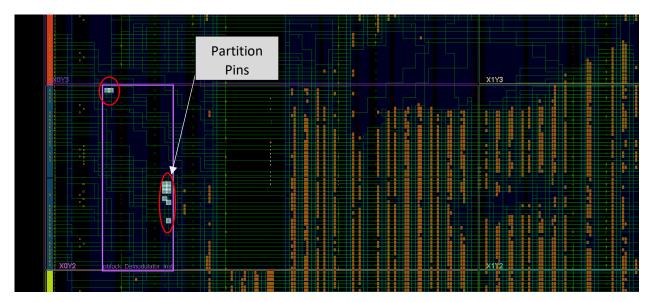

| Figure 4-16. Partition Pins.                                                                   |         |

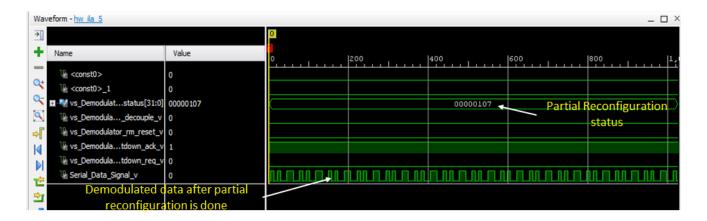

| Figure 4-17. Resulting Output after Reconfiguring the Reconfigurable Partition with BPSK Demod | ulator. |

|                                                                                                | - 120 - |

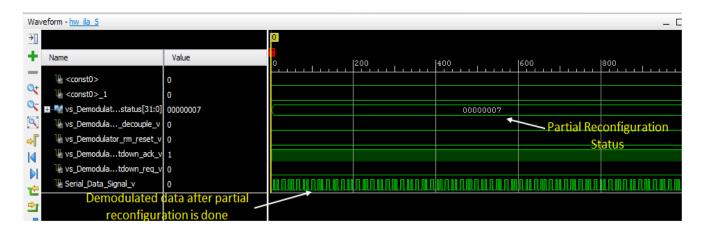

| Figure 4-18. Resulting Output after Reconfiguring The Reconfigurable Partition with QPSK     |            |

|----------------------------------------------------------------------------------------------|------------|

| Demodulator.                                                                                 | 121 -      |

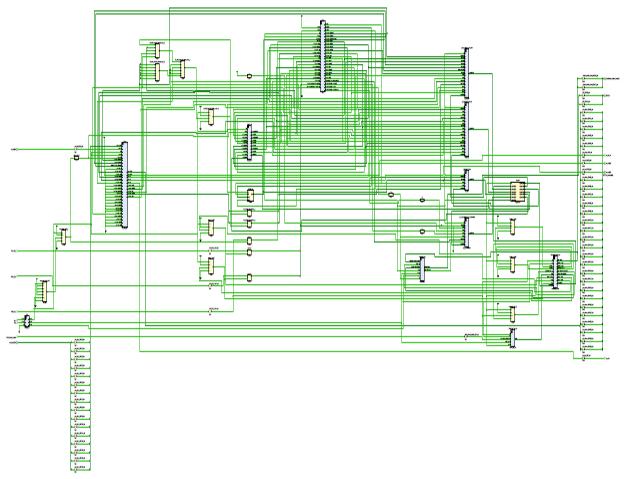

| Figure 4-19. Schematic of DPRDS Design.                                                      | 122 -      |

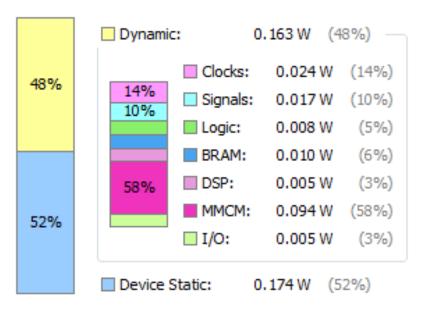

| Figure 4-20. Power Consumption of DPRDS System.                                              | 124 -      |

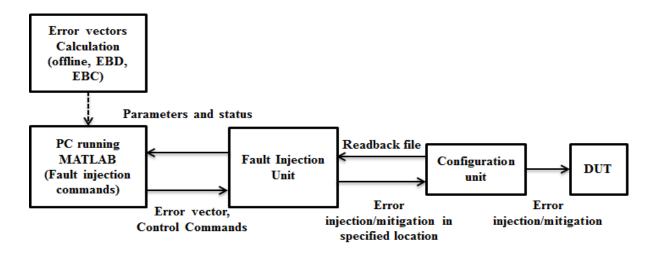

| Figure 5-1. Error Injection and Mitigation Principle.                                        | 128 -      |

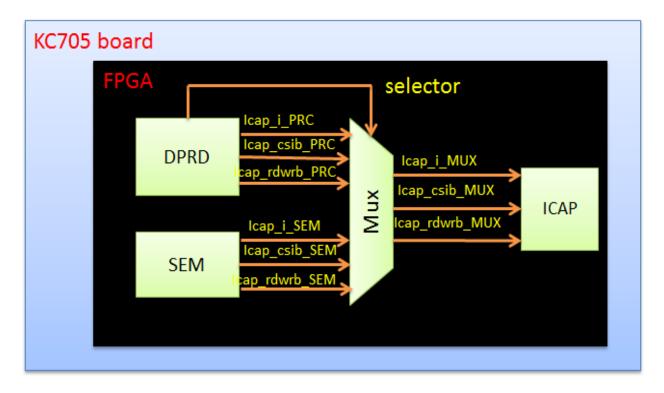

| Figure 5-2. Sharing ICAP Primitive Concept                                                   | 129 -      |

| Figure 5-3. Soft Error Mitigation System Block Diagram                                       | 130 -      |

| Figure 5-4. Error Injection and Mitigation Flowchart.                                        | 132 -      |

| Figure 5-5. FPGA Floorplan of Full Design.                                                   | 133 -      |

| Figure 5-6. Output Results of Partial Reconfiguration Process for RM 1(BPSK)                 | 134 -      |

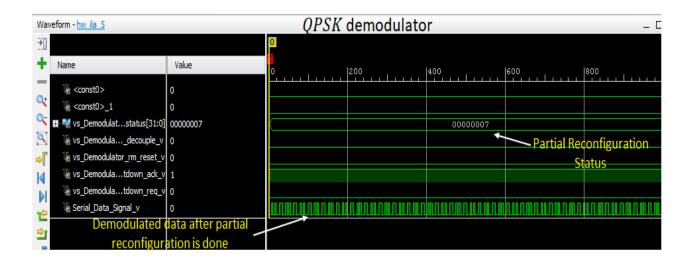

| Figure 5-7. Output Results of Partial Reconfiguration Process for RM 0 (QPSK)                | 135 -      |

| Figure 5-8. Comparing EBD and EBC Files to Determine Essential Bits                          | 136 -      |

| Figure 5-9. Essential Bits Number of Static and Dynamic Sections Comparing to Full Configura | ation Bits |

| Number                                                                                       | 136 -      |

| Figure 5-10. A Part of the Generated File of Soft Error Mitigation Process                   | 138 -      |

## **List of Tables**

| Table 2-1. Comparison among Different SDR Platform Chips                         | 18 -  |

|----------------------------------------------------------------------------------|-------|

| Table 2-2. Comparison between AMR Approaches                                     | 25 -  |

| Table 3-1. Kernel Functions Mathematical Expression                              | 66 -  |

| Table 3-2. Comparison among Different Kernel Function Accuracy                   | 67 -  |

| Table 3-3. MPSK Modulation Selector Value and Corresponding MPSK Modulation Type | 73 -  |

| Table 3-4. MPSK Modulation Selector Value and Corresponding MPSK modulation type | 73 -  |

| Table 3-5. LPF and HPF Coeficients                                               | 83 -  |

| Table 3-6 BPSK and QPSK Extracted Features form DWT Level 3.                     | 85 -  |

| Table 3-7. RBF Classification Accuracy for Different σ Values                    | 88 -  |

| Table 4-1. Comparison Among Different Configuration Ports                        | 102 - |

| Table 4-2. Partial Reconfiguration Supported Configuration Ports                 | 107 - |

| Table 4-3. Kintex-7 FPGA Resources Utilization for DPRDS System                  | 123 - |

## **List of Symbols**

| Symbol        | Description                          |

|---------------|--------------------------------------|

| $s_{SPK}(t)$  | BPSK modulated Signal in time domain |

| $f_c$         | Carrier frequency                    |

| $T_b$         | Bit duration                         |

| BW            | Bandwidth                            |

| C(t)          | Carrier signal in time domain        |

| $s_{QSPK}(t)$ | BPSK modulated Signal in time domain |

| W             | Weight vector                        |

| X             | Input features vector                |

| b             | Bias, scaler quantity                |

| f(x)          | Classification equation              |

| $y_i$         | Class label                          |

| $x_i$         | Support vectors vector               |

| С             | Penalty value                        |

| $\alpha_i$    | Lagrangian multiplier                |

| ε             | Marginal error                       |

| $f_{out}$     | NCO output frequency                 |

| $\sigma^2$    | variance                             |

## List of Acronyms

| Abbreviation | Description                                   |

|--------------|-----------------------------------------------|

| ADC          | Analog to Digital Converter                   |

| ADMC         | Automatic Digital Modulation Classification   |

| ADMR         | Automatic Digital Modulation Recognition      |

| ALU          | Arithmetic Logic Units                        |

| AM           | Amplitude Modulation                          |

| AMR          | Automatic Modulation Recognition              |

| ANN          | Artificial Neural Network ANN                 |

| ASIC         | Application Specific Integrated Circuits      |

| AWGN         | Additive White Gaussian Noise                 |

| BASK         | Binary Amplitude Shift Keying                 |

| BFSK         | Binary Frequency Shift Keying                 |

| BPI          | Byte Peripheral Interface                     |

| BPSK         | Binary Phase Shift Keying                     |

| BSTI         | Basic Space Technology Initiative             |

| CC           | Cyclic Cumulants                              |

| CLB          | Configurable Logic Blocks                     |

| COPUOS       | Committee on the Peaceful Uses of Outer Space |

| COTS         | Commercial Off-the Shelf                      |

| СРР          | Configuration Packet Processor                |

| CRC          | Cyclic Redundancy Check                       |

| CT           | Configuration Time                            |

| DAC   | Digital to analog Converter                        |

|-------|----------------------------------------------------|

| DCT   | Discrete Cosine Transform                          |

| DDC   | Digital Downconverter                              |

| DNST  | Doctorate in Nano-Satellite Technologies           |

| DPR   | Dynamic Partial Reconfiguration                    |

| DPRDS | Dynamic Partial Reconfigurable Demodulators System |

| DSM   | Digital Signal Modulator                           |

| DSP   | Digital Signal Processor                           |

| DST   | Discrete Sine Transform                            |

| DT    | Decision-Theoretic                                 |

| DUC   | Digital Upconverter                                |

| DUT   | Device Under Test                                  |

| DWT   | Discrete Wavelet Transform                         |

| ECC   | Frame Error Correcting Code                        |

| EMC   | External Memory Controller                         |

| ESA   | European Space Agency                              |

| ESP   | Egyptian Space Program                             |

| FCC   | Federal Communications Commission                  |

| FDR   | Frame Data Register                                |

| FFs   | Flip Flops                                         |

| FIR   | Finite Impulse Response                            |

| FIT   | Failures in Time                                   |

| FM    | Frequency Modulation                               |

| FPGA       | Field Programmable Gate Array            |

|------------|------------------------------------------|

| FSK        | Frequency Shift Keying                   |

| FSM        | Finite State Machine                     |

| GCSs       | Ground Control Stations                  |

| GMSK       | Gaussian Minimum Shift Keying            |

| GPP        | General Purpose Processor                |

| HOS        | Higher Order Statistics                  |

| HPF        | High Pass Filter                         |

| I/O Blocks | Input/ Output Blocks                     |

| ICAP       | Internal Configuration Access Port       |

| IF         | Intermediate Frequency                   |

| ILA        | Integrated Logic Analyzer                |

| IRSO       | Indian Research Space Organization       |

| ISS        | launching International space Station    |

| JTAG       | Joint Test Action Group                  |

| k-NN       | k-Nearest Neighbor                       |

| KUAR       | GNU Radio, Kansas University Agile Radio |

| LA         | Logical Address                          |

| LDA        | Linear Discriminant Analysis             |

| LPF        | Low Pass Filter                          |

| LUTs       | Lookup Tables                            |

| MBU        | Multiple Bit Upset                       |

| MFSK       | M-ary Frequency Shift Keying             |

| MIMO  | Multiple Input Multiple Output                                               |

|-------|------------------------------------------------------------------------------|

| MLPNN | Multi-Layer Perceptron Neural Network                                        |

| MMCM  | a Mixed Mode Clock Manager                                                   |

| MSK   | M-ary Phase Shift Keying MPSK                                                |

| NARSS | National Authority of Remote sensing and Space Sciences                      |

| NCD   | Native Circuit Description                                                   |

| NCO   | Numerical Controlled Oscillator                                              |

| NICT  | The Japanese National Institute of Information and Communications Technology |

| NN    | Naive Bayes (NB)                                                             |

| OFDM  | Orthogonal Frequency Division Multiplexing                                   |

| PAPR  | Peak to Average Power ratio                                                  |

| PLL   | Phase Locked Loop                                                            |

| PNST  | Post-graduate study of Nano-Satellite Technologies                           |

| PR    | Pattern Recognition                                                          |

| PR    | Partial Reconfiguration                                                      |

| PRC   | Partial Reconfiguration Controller                                           |

| PRM   | Partial Reconfigurable Module                                                |

| PSK   | Phase Shift Keying                                                           |

| QAM   | Quadrature Amplitude Modulation                                              |

| QPSK  | Quadrature Phase Shift Keying                                                |

| RBF   | Radial Base Function                                                         |

| RF    | Radio Frequency                                                              |

| RM      | Reconfigurable Module                            |

|---------|--------------------------------------------------|

| SAARC   | South Asian Association for Regional Cooperation |

| SDR     | Software Defined Radio                           |

| SEIC    | Space Engineering International Courses          |

| SEM     | Soft Error Mitigation                            |

| SEU     | Single Event Upset                               |

| SNR     | Signal to Noise Ration                           |

| SOC     | System-On-Chip                                   |

| SPENVIS | Space Environment Information System             |

| SPI     | Serial Peripheral Interface                      |

| S-RAM   | Static Random Access Memory                      |

| SVM     | Support Vector Machine                           |

| SVs     | Support Vectors                                  |

| UNOOSA  | United Nations Office for Outer Space Affairs    |

| USRP    | Universal Software Radio Peripheral              |

| WLAN    | Wireless Local Area Network                      |

## **Chapter 1: Introduction**

Recently, the number of international cooperation in space field increases rapidly. Several benefits can be gained from international cooperation such as funding, political sustainability, and financial efficiency. International cooperation has several topics and goals. For example, cooperation in space science, earth observation, deep space, interplanetary exploration, capacity building and technology transfer. After the end of cold war by many years, the first cooperation in space field is started by developing and launching International Space Station (ISS) in 1998 and involving U.S., Soviet union, Japan, Canada, and European Space Agency (ESA). Many experiments can be performed in space such as life sciences, space medicine, physical sciences where the conditions are achieved regarding the difficulties face these experiments to be performed on the earth which enhances the human science and promote the technological progress [1].

In twenty-first century, the regulation of international cooperation in Space exploration activities would be needed, so there was a necessary to set a theoretical framework that is able to manage all international cooperation. This framework explains all aspects of the cooperation and contains models of cooperation to illustrate how actors and initial conditions (political, scientific, economic, and technological) can work together to achieve promising outcomes [2]. United Nations Office for Outer Space Affairs (UNOOSA), Committee on the Peaceful Uses of Outer Space (COPUOS) in 1996 adopted a declaration to organize such type of international cooperation.

Indian Research Space Organization (IRSO) has rapid development in space science as the result of its activities in both economic and social fields based on its outer space exploration activities. IRSO engaged international cooperation with South Asian Association for Regional Cooperation (SAARC) in SAARC satellite project to promote the socio-economic development in that area, which improves and promotes the economy and security of India [3]. National Authority of Remote sensing and Space Sciences

(NARSS) representative by Egyptian Space Program (ESP) had engaged with Ukraine in Egypt-Sat1 satellite project which considered the first Egyptian remote sensing satellite. This cooperation encompassed all the processes of designing, manufacturing, and testing the satellite, in addition, technology transfer and capacity building.

Egypt is not the only North African country that engaged in international cooperation, and other countries such as Algeria and Morocco have international cooperation too. Morocco as an example, has many cooperation with European Union, ESA and other space agencies especially in micro-satellite projects for remote sensing purposes [4], so to get the most benefits of international cooperation, it is required to overcome the problems that can obstacle the cooperation. There are many trails performed among Latin America countries to go into such cooperation by overcome the regional problems to establish regional cooperation mechanism in space [5]. The same situation with India-Canada cooperation [6], and Canada-China cooperation [7] to overcome any obstacles prevents the fruitful outcomes of the cooperation.

International cooperation has several advantages and can be applied in several fields. Sharing Ground Control Stations (GCSs), capacity building, building satellites, establishment of facilities required for satellites development, space applications, and education can be a form of international cooperation. Basic Space Technology Initiative (BSTI) created by UNOSSA is aiming to spread the space engineering technology among the developing and emerging countries to start their first step toward space technology. BSTI and Kyushu Institute of Technology has a long time collaboration in space education programs under the framework of United Nation/Japan Long-Term Fellowship Program starting from Doctorate in Nano-Satellite Technologies (DNST), 2010, passing through Post-graduate study of Nano-Satellite Technologies (PNST), 2013-2018 which gives the chance for up to three students for Master course and up to three students for the Doctor course to study in Space Engineering International Courses (SEIC). The PNST program has been extended to 2020 to give the students from all over the world new opportunity to join the program.

I have got the opportunity to join the PNST program at Kyushu Institute of Technology and be one of the Ph.D. students that attended the SEIC course and used the Testing facilities of the institute. Of course, this is certainly considered elegant advantage and fruitful outcome of the international cooperation.

This research point promotes the international cooperation in both ground and space segments by implementing a prototype of Dynamic Partial Reconfigurable Demodulation System (DPRDS) that can be used as a main core of a generic receiver. Generic receiver can be implemented in different categories of the satellites to increase the number of Ground Control Stations (GCSs) where a satellite can communicate without the need to install several receivers where increase the complexity and the cost of a satellite. Generic receiver can promote the collaboration among countries in several fields especially remote sensing. This prototype would acquire the benefits of the rapid development in microelectronic technologies especially in FPGA. The prototype is implemented on FPGA which is based on the concept of Software Defined Radio (SDR) receivers to implement several demodulators defined in software, and FPGA partial reconfiguration technology that allows dynamic reconfigurability of a part of the design during runtime without any effects on the rest of the design.

Making the best use of the existing technology and the rapid development of these technologies provides suitable solutions to overcome some obstacles. The concept of SDR receivers states that some or all of hardware components of a radio communication can be implemented in software so as to be called software defined. This principle opens a new thinking field and smart way to reduce the complexity and cost and at the same completely finished the problem of obsoleting hardware. Simply you can change your design by replacing the old software with new one without the need of replacing costly hardware [8].

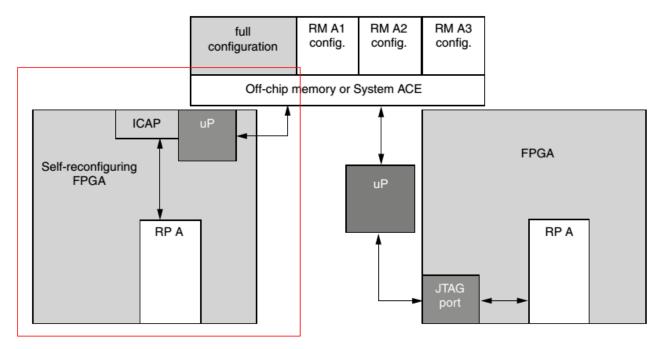

Rapid development in FPGA aims to increase speed of signal processing and exploration of techniques that can help in solving some challenges, which was in past is impossible to

be implemented. FPGA Dynamic Partial Reconfiguration (DPR) technique supports the designers to implement intelligent systems that were impossible to be implemented in real world. DPR capable of achieving space requirements starting from a high flexible System-On-Chip (SOC) to adaptive component algorithm [9]. DPR can be done by FPGA itself using Internal Configuration Access Port (ICAP) or by using external processor using Joint Test Action Group (JTAG). In the next sections, I would explain the motivation, objectives, and methodology of the research.

#### 1.1. Problem Statement and Motivation

The high cost of building space infrastructure causes the increment of the number of international cooperation in space field and allows the chance to the developing and emerging countries to participate in space activities without affording huge costs and in other cases achieves political sustainability, and financial efficiency. So the removing of any obstacles that may prevent or reduce this cooperation is a challenge.

The main existing problem is the limited communication capability of the satellites whereas they can communicate only with GCSs that use the same modulation and demodulation schemes in their transceivers. For example, if the satellite use Binary Phase Shift Keying (BPSK) modulation/demodulation technique, so it can demodulate the data of the received signal correctly if and only if the modulation of the received signal is BPSK too, otherwise, the demodulated data will not be correct as in Fig. 1-1. The same problem is applied for the communication between a satellite and a relay satellite. To solve this problem, satellites/GCSs receivers have to be more generic to permit communication with several relay satellites and GCSs that use different modulation and demodulation techniques without the need of using the traditional method that required installation of several receivers into satellites, therefore the complexity and cost of satellites increase.

This research aims to promote the international cooperation by using the recent development technologies by implementing a Dynamic Partial Reconfigurable

Demodulation System (DPRDS) where its design is based mainly on SDR principle and FPGA partial reconfiguration technique. DPRDS is the main core of a generic receiver and it considered a simple and low-cost method to implement a universal or generic receiver. DPRDS is considered the first data processing stage after receiver front end stage which contains antenna, low noise amplifier, and down conversion processes.

Figure 1-1. Problem Statement Configuration

The Automatic Digital Modulation Recognition (ADMR) or the classification part of the DPRDS system plays an important role between the detection of the signal and demodulation stages, which allows a satellite to adaptively demodulate the modulation scheme of the received modulated signal correctly after switching the modulation scheme by a GCS/s. There are many applications of ADMR in both civilian and military fields. The ADMR can be used in relay satellites and other satellites where the demodulation

and re-modulation of the data is performed onboard. In addition, ADMR can be used to overcome channel problems during the communication session with a satellite as bandwidth congestion/crunch by changing the existing modulation scheme by another more efficient bandwidth modulation scheme [35].

ADMR can be used to secure the received and transmitted signal by locating, classifying and preventing the unwanted signals. ADMR can be used in interference identification, spectrum monitoring, signal confirmation, electronic warfare, cognitive radio, threat analysis, and signal surveillance [23], [34].

National Aeronautics and Space Administration (NASA) is investigating cognitive radio technologies using ADMR for the improvement of the future communication architecture, which are expected to reduce the network operational complexity and interference to self and others, and increase science data return [88].

#### Motivations can be summarized as follows:

- Promotion of international cooperation in space field by developing generic GCSs/satellites receivers

- Help developing and emerging countries to establish their space activities

with low cost and less time by sharing existing facilities.

- The countries own the facilities could promote political sustainability, and enhance their economic efficiency

- Investigation of the ability to implement a dynamic partial reconfigurable demodulation system prototype that can be used as a main core of a generic receiver.

- Implementation of BPSK and QPSK demodulators based on SDR principle to increase flexibility.

- Reduction of complexity and cost of both GCS and satellite.

- Reduced Hardware Obsolescence.

### 1.2. Research Objectives

This research has several objectives and can be summarized as follows:

- Development and implementation of dynamic partial reconfigurable demodulators system as the main core of a generic receiver using DPR technique, SDR principle, and classification approach.

- Investigation of the suitable classification approach, and tradeoff between classification approaches; Decision Theoretical and Pattern Recognition approaches.

- Investigation of the suitable features extractors and classifier for the design.

- Implementation of several demodulators by software instead of hardware complexity based on SDR principle.

- Investigate the suitable DPR methodology.

- Discussion of the ability of sharing ICAP primitives among DPR and the other user applications.

- Applying soft error mitigation in laboratory on DPRDS as a case study.

## 1.3. Research Originality

The originality of this research can be summarized as follows:

- Appling FPGA dynamic partial reconfiguration technique in communication subsystem which can be used in building satellites that can communicate with several ground-stations (by replacing a demodulator by another one on the fly), which increases cross support.

- Implementing a classifier before the dynamic partial reconfiguration stage allows a satellite to adaptively demodulate the modulation scheme of the received modulated signal correctly after changing the modulation scheme by a GCS.

- Increasing the capability of FPGA to implement several applications as dynamic partial reconfiguration, fault management system, and laboratory soft error

injection mitigation that requires the access to ICAP using a multiple access technique.

- Merging both MATLAB and VIVADO tools capabilities in order to reduce the resources utilization and low power consumption.

### 1.4. Research Methodology

- Study of classification approaches then selection of the suitable approach.

- Study of partial reconfiguration and dynamic partial reconfiguration and their development methods.

- Study of SDR principle and developing of demodulators based on SDR.

- Selection of the proper FPGA board to implement the design.

- Developing of the classification section of the design including features extraction and SVM classifier.

- Using MATLAB R2015b together with VIVADO 2015.4, to implement complex system and get coefficients, parameters, and other needed results instead of implementation of complex system on FPGA.

- Developing of DPRDS using DPR technique and SDR concept.

- Testing of the performance of DPRDS in the presence of Additive White Gaussian Noise (AWGN).

- Proving of the ability of DPRDS to be implemented with other user applications that need the access to the ICAP primitive.

- Developing of Single Event Upset (SEU) mitigation of DPRDS as a case study of the multiple access of ICAP primitive.

- Results dissemination.

## 1.5. Dissertation Challenges

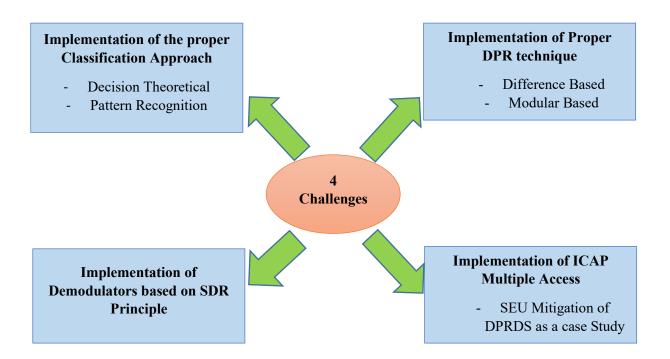

In this dissertation several principles, approaches, and techniques are used to achieve low power, less resources utilization and complexity, and low cost DPRDS. So the dissertation has four challenges as illustrated in Fig. 1-2.

Figure 1-2. Dissertation Challenges

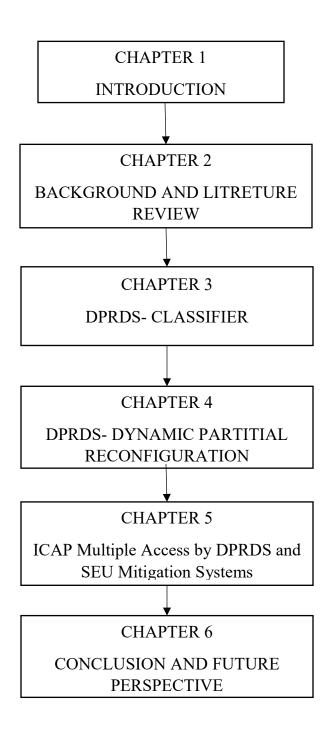

## 1.6. Dissertation Organization

The dissertation describes the methodology of developing DPRDS system based on FPGA DPR technique. The sequential of the dissertation explains the methods principles, techniques, and steps that required implementing the DPRDS and shows the obtained results. The dissertation is divided into 6 chapters as simply stated in Fig. 1-3.

CHAPTER 1 Introduction

Figure 1-3. Dissertation Sequential

CHAPTER 1 Introduction

Chapter 1 is an introduction of the dissertation which describes the problem statement of the limited capabilities of GCSs/ satellites to communicate with several satellites/GCSs that use different modulation and demodulation techniques. This chapter describes also the motivation of this dissertation and the benefits of applying such research on real cases for both local and international zone. In addition, the objective, originality, methodology, and challenges of the research would be decribed. In methodology, the sequence of the implementation of the DPRDS and how get the benefits of merging the use of MATLAB as an auxiliary tool beside VIVADO tool to reduce the resources utilization and power consumption by implementing the complex system such as the training of the classifier using MATLAB and by employing the resulted parameters and coefficients in VIVADO tool.

Chapter 2 presents the background related to SDR principle and signal processing functions replaced or implemented by the means of software. It refers to the fundamental of FPGA architecture, definitions and methods that related to programing or configuring FPGA. It overviews the FPGA partial reconfiguration technique in terms of dynamically partial reconfiguration methods and the processes of generating the configuration bitstream or the image that required for partial reconfiguration process. It presents the previous studies and researches related to this dissertation as much as possible, to show the new methods and techniques that are used to develop reconfigurable demodulators.

Chapter 3 describes the classification part of the DPRDS system. It presents the evaluation system that generates BPSK and QPSK modulations to test the performance of the DPRDS system. In addition to the classification approach, this chapter explains how to extract features from the signal and to implement a SVM classifier including kernel function and learning method using both MATLAB and VIVADO tools, in order to implement an efficient system with high recognition rate, low power consumption and less resources utilization. It presents the results of the classification part in the presence of AWGN and comparison with the results of the previous studies as well as the consumed classification time.

CHAPTER 1 Introduction

Chapter 4 describes the DPR part of the DPRDS system. It presents the partial reconfiguration approaches, dynamic partial reconfiguration implementing methods, and the procedures required implementing full and partial configuration bit-stream files that are used to configure FPGA before and during runtime. As well as, the communication method between partial reconfiguration controller and the storage memory would be explained. The results show the reconfiguration time required to reconfigure the dynamic section of FPGA with the corresponding reconfigurable module as BPSK or QPSK demodulator.

Chapter 5 describes the ability of sharing ICAP primitive among several user applications. It presents the ICAP multiple access by DPRDS and Soft Error Mitigation (SEM) application. It shows the method to inject and mitigate errors into static and dynamic parts of DPRDS design without any interruption to the reconfiguring performance. It presents a new error injection method that can reduce the error injection time by about 96% comparing to the traditional method. The results show that both systems are working properly without any effects on their performance.

Chapter 6 concludes the purposes and results of the dissertation and discusses the feasibility of developing such DPRDS systems in a generic receiver which promotes international cooperation. It presents the future perspective of the research by applying the generic receiver into a real GCSs and satellites.

# **Chapter 2: Background and Literature Review**

### 2.1. SDR Overview

### 2.1.1. SDR Background and Principle

Since 1890 when the first wireless transmission occurred, the wireless communication has been witnessing remarkable rapid development especially in transmission techniques. Passing through analog voice communication was transmitted by using limited bandwidths in 1930 [10], [11]. Then after 20 years the analog television broadcast required wider bandwidths was developed. Then, in the 60s, the computers are used as long-distance communication medium via the network system called Internet [12], [13]. Regarding to the continuous progress in communication field, Federal Communications Commission (FCC) has originated Wireless Local Area Network (WLAN) and organized the regulations of licensed and unlicensed spectrums, and allocated three regions for medicine, industry, and science [14]. Then the progress in wireless communication has been continued to investigate protocols as Wi-Fi and Bluetooth which nowadays were used in most network-based applications.

The rapid development and growth in wireless communications is evolving several technologies, but the main remarkable problem is most of the protocols and radios based on hardware, which reduce the flexibility of mitigating errors occurring in radios hardware. If there is an error happened in firmware or hardware, we cannot get suitable way to mitigate the errors. In that time, there is no visibility to reconfigure the devices by other protocols or software because the functionality of these devices is based on hardware component. These problems lead to think about a new concept and principle that can support and overcome the described problems and at the same time provide more benefits which is called now as SDR.

SDR is considered the base of generic wireless devices, where modulation schemes and some parameters such as carrier frequency and symbol rate, should be reconfigured or replaced via adaptive and reconfigurable communication system without any change in the platform. SDR can be defined as a radio communication where some or all hardware functions are implemented by means of software or software defined instead of hardware. It is a radio whose components are implemented in software rather than in hardware.

The principle of SDR is that more of the signal processing manipulation including filtering, modulation and demodulation functions are implemented in reprogrammable and reconfigurable digital hardware so that the platform can be used for several signal processing and SDR system provides portability and flexibility. Digital hardware that can be used for implementations of SDR modems include Field Programmable Gate Array (FPGA), Digital Signal Processor (DSP), and General Purpose Processor (GPP).

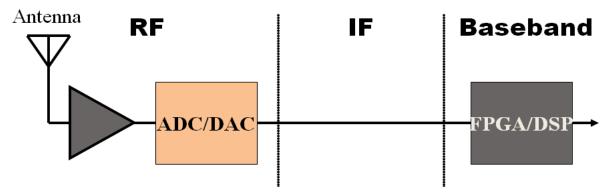

### 2.1.2. SDR Architecture

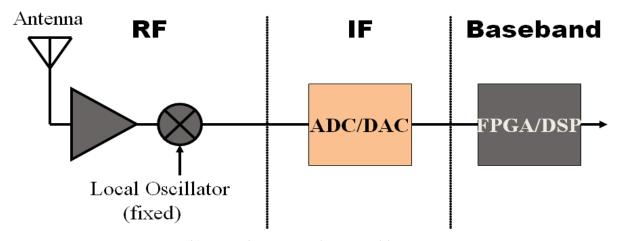

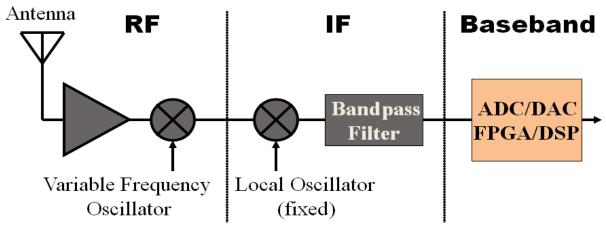

In SDRs most of the functionality is software defined without the need to equivalent hardware and most of the signal processing is digitally performed. Real SDR system is segmented into 3 stages; Radio Frequency (RF) front end, Intermediate Frequency (IF), and baseband signal processing stages. The radio analog signal is first received by the antenna, then the down conversion module converts the high frequency signal to IF signal, after that the IF signal is converted to digital signal through Analog to Digital Converter (ADC) to be digitally processing in baseband stage using FPGA, DSP or GPP. There are three SDR configurations depending on the down conversion and ADC stages, and the positions as can be seen in Fig. 2-1.

(a) ADC/DAC Implemented in RF Front End

(b) ADC/DAC Implemented in IF Stage

(c) ADC/DAC Implemented in Baseband Stage

Figure 2-1. Different Configurations of SDR System

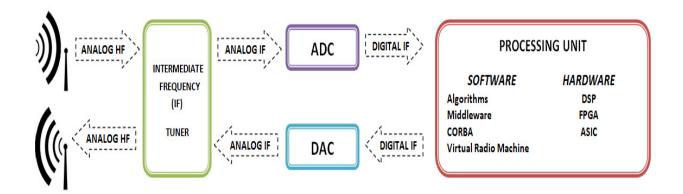

A real SDR model can be described in Fig. 2-2, where the received signal is down converted to IF, and then the IF signal is filtered to prevent the existing of the aliasing frequency into the band of frequencies. The IF signal will be digitized by generating numerical values from the filter through ADC. After that the digitized data can be processed using FPGA, DSP, or GPP [15].

Figure 2-2. Real SDR Model [15]

For the transmission path, after applying the processing on digital data, the processed data is converted to analog signal after passing through Digital to Analog Converter (DAC), and then analog IF signal is up converted to high frequency and transmitted by antenna.

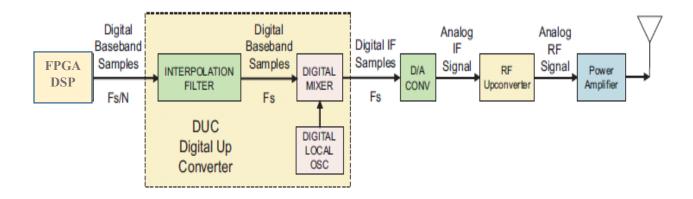

#### 2.1.2.1. SDR Transmitter

As described previously the digital data is applied to the transmitter input side of an SDR system, and this data is generated from FPGA or any other signal processing devices. Digital Upconverter (DUC) translates the baseband signal to the IF signal. IF signal samples are converted into analog IF signal via DAC. Then the analog IF signal is converted to RF signal of high frequency by passing through RF upconverter. To transmit the generated signal to travel for long distance, power amplifier is used to increase signal energy as seen in Fig. 2-3 [16].

Figure 2-3. SDR Transmitter Block Diagram

#### 2.1.2.2. SDR Receiver

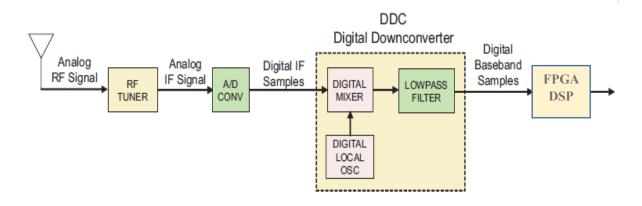

The receiver part of the SDR system starts by converting received RF signal into IF signal before passing through ADC that converts analog IF signal into digital samples. These samples have to apply to Digital Downconverter (DDC) to be easily manipulated by the FPGA/DSP devices. The DDC is considered as the key of SDR system and is implemented by FPGA IP core or externally single monolithic chip. The Finite Impulse Response (FIR) filter is used as low pass filter with decimation and limits the bandwidth of the dwonconverted signal. Therefore FPGA/DSP can perform the required signal processing such as demodulation, decoding, and other processing as seen in Fig. 2-4 [16].

Figure 2-4. SDR Receiver Block Diagram

#### 2.1.3. SDR Platforms

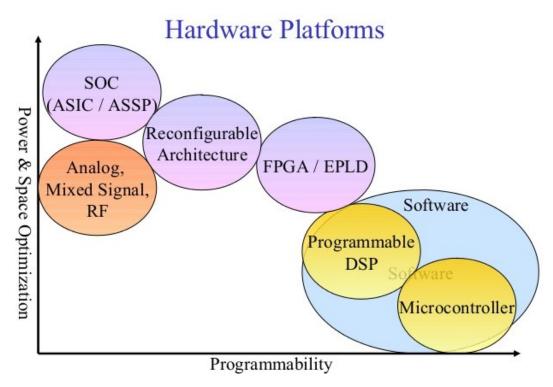

FPGA, DSP, and Application Specific Integrated Circuits (ASIC) are considered as hardware alternatives that can be used to implement SDR system. A comparison among these chips has to perform for taking the suitable chip selection to the corresponding application. The comparison aspects should cover power consumption, Resources utilization, cost, and other aspects that can help for making good selection as shown in Table 2-1 and Fig. 2-5.

| Comp. aspects\Type    | FPGAs        | High Speed<br>DSPs | GPPs     | Multiple<br>ASICs |

|-----------------------|--------------|--------------------|----------|-------------------|

| Power Consumption     | Low          | Very High          | Moderate | Very Low          |

| Resources Utilization | Low          | Moderate           | Moderate | Large             |

| Cost                  | Moderate/Low | Moderate/High      | Moderate | High              |

| Field Upgradable      | High         | High               | Some     | None              |

| Silicon Evolution     | Easy         | Easy               | Moderate | Available         |

Table 2-1. Comparison among Different SDR Platform Chips

From Table 2-1, using FPGA is the most suitable selection to implement SDR system especially, and it contains DSPs blocks that can be reconfigured and used for parallel computations. DSP is coming in the second ranks after FPGA because it can perform several signal processing applications and has microprocessors with architecture, instructions and features [17].

Several SDR platforms have been developed to support different research projects. The most five popular SDR platforms are Universal Software Radio Peripheral (USRP), GNU Radio, Kansas University Agile Radio (KUAR), The Japanese National Institute of Information and Communications Technology (NICT) SDR Platform, and Berkeley Cognitive Radio Platform.

Figure 2-5. Comparison among FPGA and other programmable devices

The USRP is SDR platform that is currently available and provides the GNU Radio with hardware platform. USRP can support up to 25 MHz of bandwidth and is considered mostly for experimentation because it does not match any communication standards. KUAR is the developed form of the GNU Radio to be a low-cost experimental SDR platform and can operate with frequencies range of 5.25 to 5.85 GHz with bandwidth margin of 25 MHz. NICT SDR platform is developed to test mobile networks and supports frequencies range from 1.9 to 2.4 and 5.0 to 5.3 GHz. And it manges the selection among existing standards. These SDR platforms are based mainly on FPGA and combination of CPU [18].

The advantage of using SDR platform especially for space application sector is to provide the reconfigurability and flexibility to communication subsystem as reduced cost, and Commercial Off-the Shelf (COTS) components due to fast development times. The combination of both SDR communication platform and SOC increases the reduction in both cost and mass.

# 2.2. Automatic Digital Modulation Recognition Overview

### 2.2.1. ADMR Principle and Background

Automatic modulation recognition (ADMR) technique objective is to recognize the modulation scheme of a received signal with a high probability of recognition rate within a minimum observation time. Two methods can be used to realize ADMR. One is based on a prior knowledge of the received signal parameters and the other which is called blind recognition method which does not need any prior knowledge of the received signal parameters to identify the modulation schemes. The blind recognition method identify the type of modulation from the information existing in the few possible number of received samples, and according to statistical inference based on errors in received signal, the modulation type can be identified. But the blind recognition method is more complex than the other method, therefore in this dissertation the unblind recognition method is used.

ADMR is considered to become one of the important applications in SDR receivers that gives the ability to change the demodulator of the receiver system according to the recognition of the received modulated. It has to identify the modulation scheme of received signal. So it plays an important role between detection and demodulation stages. ADMR is an intermediate step between signal identification and demodulation processes, and plays an important role in several civilian and military applications. ADMR is the key role in the implementation of advanced wireless communication system especially for satellite communication system. Since 1980s up to date, the interest in modulation recognition has been growing. It has several applications such as spectrum management, interference identification, monitoring, surveillance, and signal confirmation [19], [20]. Recently, SDR and reconfigurable communication system are the most attractive application scope.

ADMR is extremely important in communication intelligent applications for several reasons. Firstly, applying the signal to an improper demodulator may partially or

completely damage the signal information content. Secondly, knowing the correct modulation type helps to recognize the threat and to determine the suitable jamming waveform.

Modulation recognition is an important part in SDR, where the modulation scheme can be varied according to channel capacity, and the modulation scheme can be detected at receiver side in real time using automatic modulation recognition [21]. For all communication systems, signals should be safely transmitted and received, whereas noise and unwanted signals must be defined, identified, and jammed [22], because of the complexity of blind recognition method, Usually, auxiliary information is combined into transmitted signal to reconfigure the SDR system.

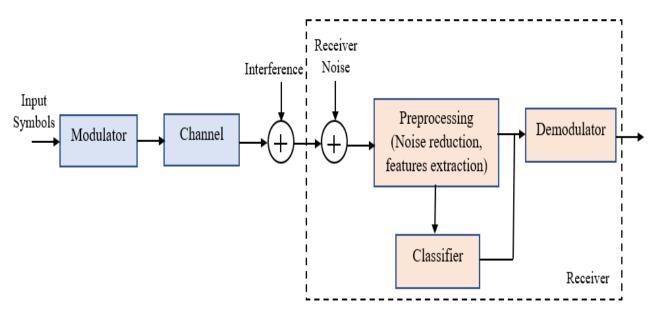

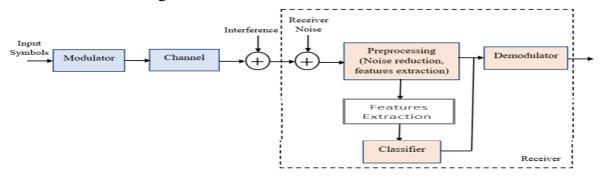

Block diagram of the communication system model can be simply drawn as shown in Fig. 2-6 [23]. The modulator converts input symbols to signal waveform, and then the channel model and jamming is applied on modulated signal for the transmission. At receiver side the noise is added to the received signal before the classification stage. The classification stage contains of two steps; Signal preprocessing and selection of the proper classification algorithm. Preprocessing includes some or all of, noise reduction, estimation of carrier phase and frequency, signal power, and symbol period, etc.

According to the selected the classification algorithm, the accuracy of preprocessing tasks varies; some classification algorithms require high precision, whereas others are less sensitive to the unknown parameters. Then after the proper classification of the modulation scheme of the received signal, the received signal is applied on the corresponding demodulator. Fig. 2-6 illustrates the block diagram and the sequential processes applied on the data or symbols that required to be transmitted till the regeneration of these symbols in the receiver side [23].

Figure 2-6. Basic pattern recognition system Block Diagram.

Two popular approaches are used to implement the classifier of received modulated signals; the Decision-Theoretic (DT) approach based on likelihood function, and the Pattern Recognition (PR) approach based on extracting unique measurable values (features) of the signal. DT approach based on multiple hypothesis testing has high performance in terms of correct classification percentage (optimal), but the drawbacks of this approach are high computational complexity which leads to that the classifier is impractical, and the sensitivity to impairments as frequency and phase offset.

On the other hand, PR approach based on pattern matching is suboptimal, simple to implement, and robust. PR consists of two stages. The feature extraction and classifier stages, Feature extraction stage extracts distinctive and small amount of information from the received signal, and classifier uses the distinctive information to classify the modulation scheme of the received signal. In this dissertation, pattern recognition approach is used [24].

### 2.2.2. ADMR Approaches

#### 2.2.2.1 Decision-Theoretic

In this approach, all classification methods is mainly based on likelihood function which is achieved mainly by statistics calculation. It is a function of transmitted data and channel parameters. The likelihood function is computed for each hypothesis, modulation schemes in this dissertation, by using the equally likely priors assumption, and the modulation scheme that maximizes the likelihood function is the decision result of the classification process. The features based method requires designers to select distinctive features of the signal that could represent each modulation scheme in a unique manner. Based on the observation of the features values the decision is taken.

The likelihood function based algorithm minimizes the probability of error of classification which makes this method optimal in the Bayesian sense. However, the defect of this method is that sometimes the evaluation of likelihood function could become complex and very messy because of the absence of knowledge of parameters, or channel conditions, which makes the likelihood based method impractical. Compared to the optimal one, a suboptimal method becomes a good choice with reasonable computation complexity [25].

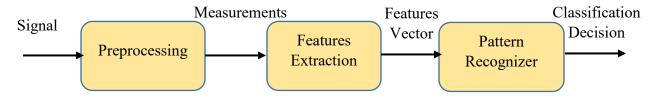

#### 2.2.2.2 Pattern Recognition

In this approach, the main key points are the features and the classifier. The modulation classification based on this approach is divided into three functional blocks, namely the pre-processing, feature extraction, and the classifier blocks as shown in Fig. 2-7 [26].

Figure 2-7. Pattern Recognition System Block Diagram.

#### 2.2.2.2.1. Pre-Processing

A noise reduction, filtering, encoding and other preprocessing functions can be applied on the signal in this stage for the enhancement of extracting the features vectors.

#### 2.2.2.2 Features Extraction

Features are any extractable measurements that can represent the input signal. The feature extraction part is used to reduce the dimension of the measurement by extracting the distinctive features which should be simple and fast to be calculated. Applying feature extraction to the input data can result in features as well [26].

Feature extraction keys are extracted from the radio signal. Some of the commonly feature extraction keys are a constellation shape recovery method, Discrete Wavelet Transform (DWT) and Discrete Sine and Cosine Transform (DST, DCT), higher-order statistics (HOS), including moments, cumulants, and cyclic cumulants (CC) of the signal, and usage of information contained in the received signal.

### 2.2.2.3 Pattern Recognizer

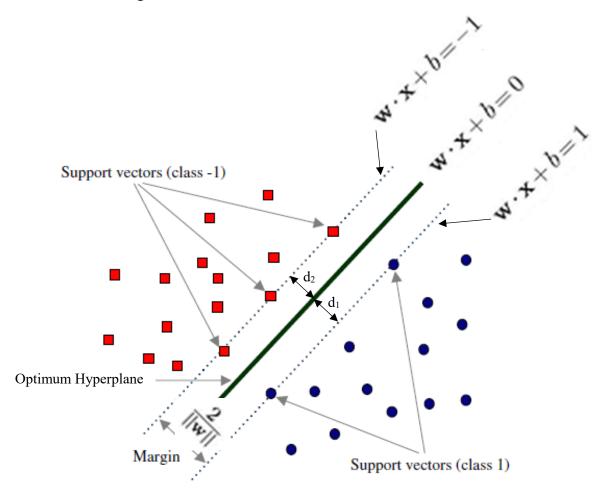

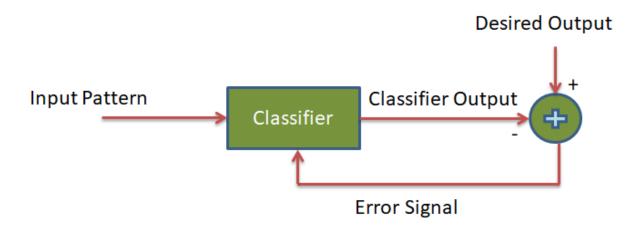

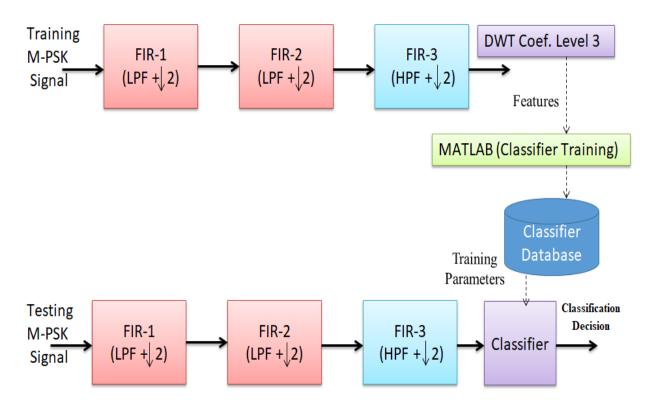

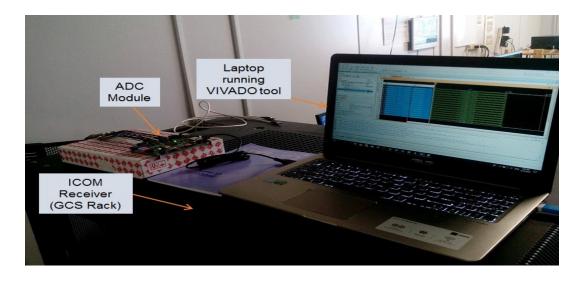

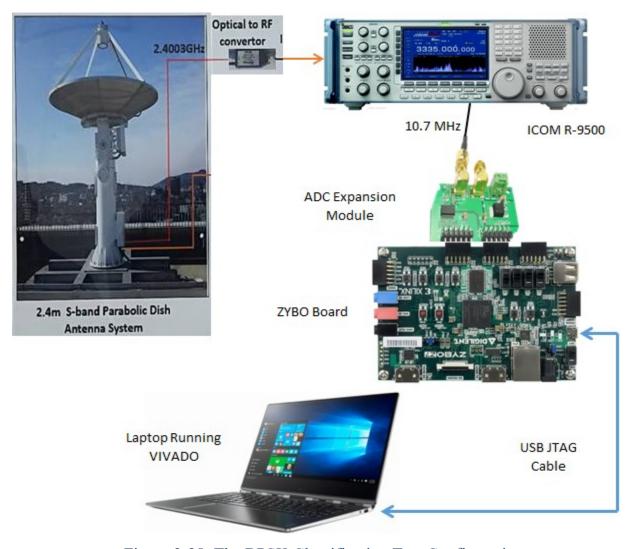

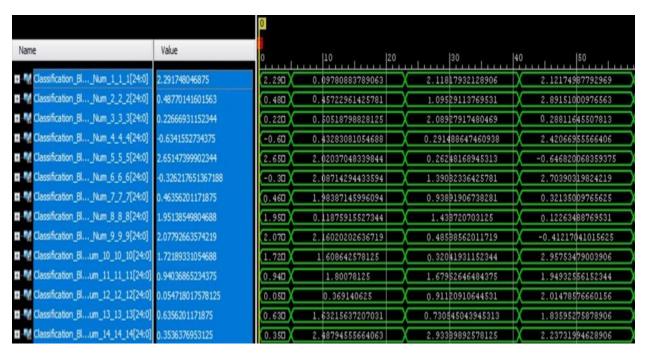

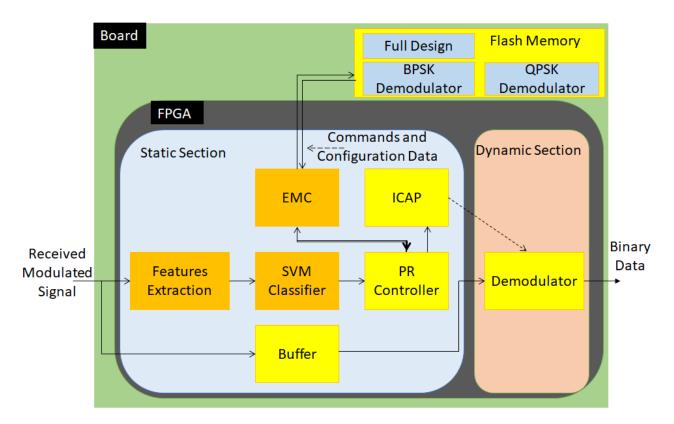

Pattern recognizer processes those extracted features to identify the modulation scheme of the received signal according to a pre-designed decision rule. The popular pattern recognizer methods used for classification purposes are SVM, Multi-Layer Perceptron Neural Network (MLPNN), and fuzzy logic [26].