## University of Nebraska - Lincoln DigitalCommons@University of Nebraska - Lincoln

Faculty Publications from the Department of Electrical and Computer Engineering

Electrical & Computer Engineering, Department of

5-11-2010

# ASSEMBLY OF ORDERED CARBON SHELLS ON SEMCONDUCTING NANOMATERALS

Eli Anguelova Sutter Westhampton Beach, NY, esutter@unl.edu

Peter Werner Sutter

Westhampton Beach, NY, psutter@unl.edu

Follow this and additional works at: http://digitalcommons.unl.edu/electricalengineeringfacpub

Part of the Computer Engineering Commons, and the Electrical and Computer Engineering

Commons

Sutter, Eli Anguelova and Sutter, Peter Werner, "ASSEMBLY OF ORDERED CARBON SHELLS ON SEMCONDUCTING NANOMATERALS" (2010). Faculty Publications from the Department of Electrical and Computer Engineering. 455. http://digitalcommons.unl.edu/electricalengineeringfacpub/455

This Article is brought to you for free and open access by the Electrical & Computer Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Faculty Publications from the Department of Electrical and Computer Engineering by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

US007714317B2

## (12) United States Patent Sutter et al.

## (10) Patent No.: US 7,714,317 B2 (45) Date of Patent: May 11, 2010

### (54) ASSEMBLY OF ORDERED CARBON SHELLS ON SEMICONDUCTING NANOMATERIALS

## (75) Inventors: Eli Anguelova Sutter, Westhampton Beach, NY (US); Peter Werner Sutter, Westhampton Beach, NY (US)

### (73) Assignee: **Brookhaven Science Associates, LLC**, Upton, NY (US)

### (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 281 days.

#### (21) Appl. No.: 11/854,168

(22) Filed: Sep. 12, 2007

#### (65) Prior Publication Data

US 2009/0057649 A1 Mar. 5, 2009

#### Related U.S. Application Data

- (60) Provisional application No. 60/968,991, filed on Aug. 30, 2007.

- (51) **Int. Cl.** *H01L 29/06* (2006.01)

- (52) **U.S. Cl.** ...... **257/15**; 257/414; 257/E29.024; 257/E29.001; 257/E51.04; 977/774; 977/840

| (58) | Field of Classification Search 257/9,   |

|------|-----------------------------------------|

|      | 257/15, 414, E29.024, E29.001; 977/774, |

|      | 977/840                                 |

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,916,642    | A * | 6/1999  | Chang 29/509           |

|--------------|-----|---------|------------------------|

| 2002/0172820 | A1* | 11/2002 | Majumdar et al 428/357 |

| 2006/0188774 | A1* | 8/2006  | Niu et al 429/44       |

| 2008/0081388 | A1* | 4/2008  | Yasseri et al 438/22   |

\* cited by examiner

Primary Examiner—Davienne Monbleau

Assistant Examiner—Benjamin Tzu-Hung Liu

(74) Attorney, Agent, or Firm—Dorene M. Price

#### (57) ABSTRACT

In some embodiments of the invention, encapsulated semiconducting nanomaterials are described. In certain embodiments the nanostructures described are semiconducting nanomaterials encapsulated with ordered carbon shells. In some aspects a method for producing encapsulated semiconducting nanomaterials is disclosed. In some embodiments applications of encapsulated semiconducting nanomaterials are described.

#### 10 Claims, 7 Drawing Sheets

Fig. 1(a)

Fig. 1(c)

Fig. 1(b)

Fig. 4(a)

Fig. 4(b)

May 11, 2010

Fig. 5(a)

Fig. 5(c)

Fig. 5(b)

Fig. 5(d)

Fig. 5(e)

May 11, 2010

Fig. 6(a)

Fig. 6(b)

Fig. 6(c)

Fig. 6(d)

Fig. 6(e)

Fig. 6(f)

Fig. 7(c)

### ASSEMBLY OF ORDERED CARBON SHELLS ON SEMICONDUCTING NANOMATERIALS

This invention was made with Government support under contract number DE-AC02-98CH10886, awarded by the 5 U.S. Department of Energy. The Government has certain rights in the invention.

#### BACKGROUND OF THE INVENTION

The invention relates to the field of encapsulating nanomaterials and, in particular, to the encapsulation of semiconducting nanowires and carbon-encapsulated semiconducting nanowires.

#### **SUMMARY**

Recognizing the challenges of obtaining passivated nanoscale semiconductors, the technology described herein offers a way of passivating nanoscale objects and discloses structures that result from employing the technology.

Thus, in some embodiments methods for passivating semiconducting nanomaterials are presented. In some embodiments passivation of elemental semiconductors is described; in some embodiments passivation of compound semiconductors is described. In some embodiments semiconducting superlattices are passivated by ordered shells of graphitic carbon. In some embodiments the passivated semiconducting nanomaterials retain their inherent optical, magnetic, and electrical properties.

In some embodiments passivated semiconducting nanomaterials are described. In some embodiments the passivated nanomaterials may be used in magnetic, electronic, optical, and electro-optical devices. In some embodiments the nanomaterials may be employed as sensors, light sources, light absorbers, and the like.

It should be understood that the foregoing, being a summary, is necessarily a brief description of some aspects of the invention, which may be better understood with reference to the drawings and the following detailed description.

#### BRIEF DESCRIPTION OF THE DRAWINGS

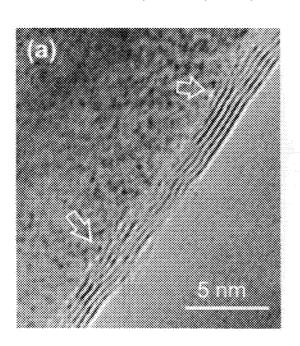

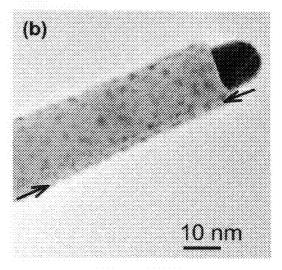

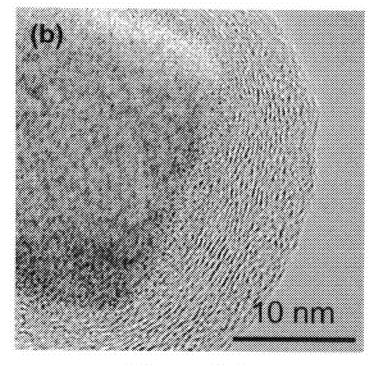

FIG. 1 depicts TEM images of as-grown Ge NWs taken at room temperature prior to annealing.

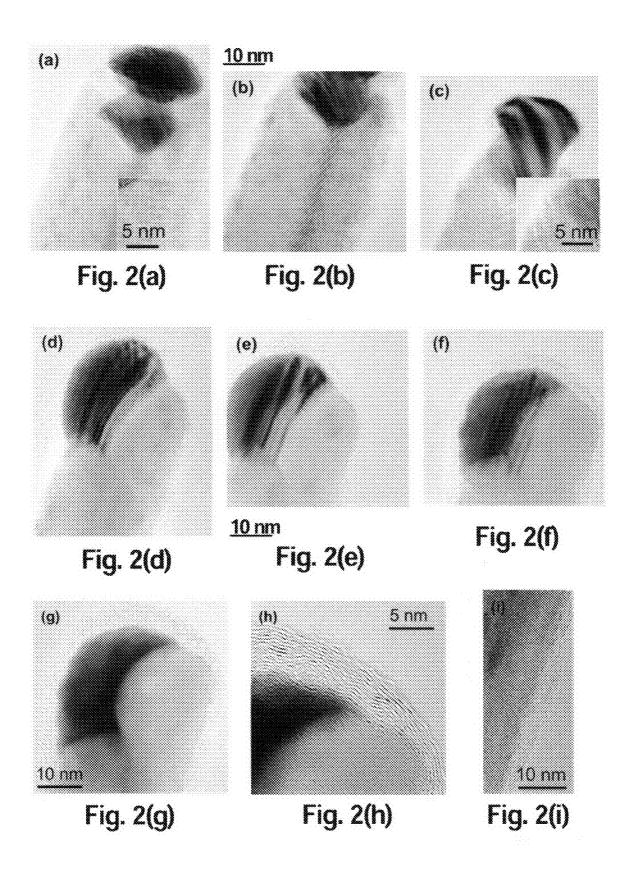

FIG. 2 shows a sequence of TEM images illustrating the process of removal of a germanium oxide surface layer and the assembly of a carbon shell around a Ge NW during in situ annealing.

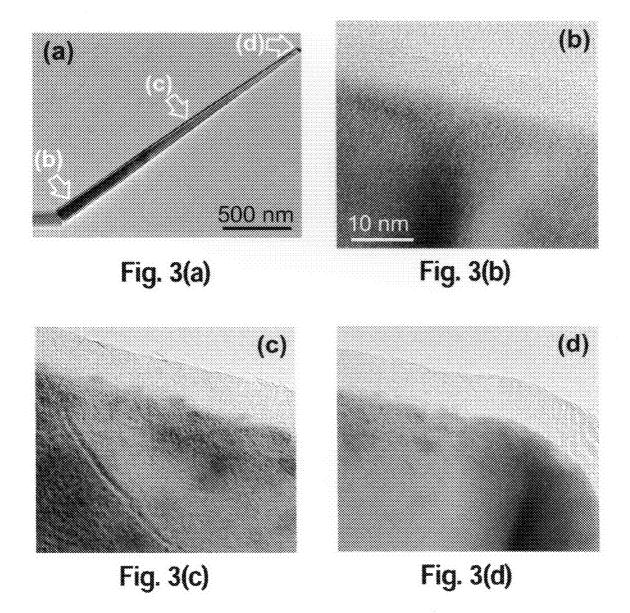

FIG. 3 shows TEM images of a Ge NW completely embedded in a multilayer C shell.

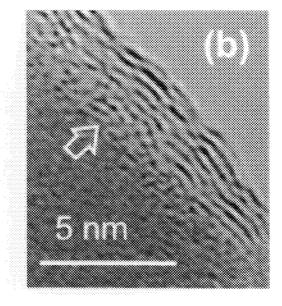

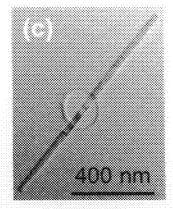

FIG. 4 shows TEM images of a Ge NW base embedded in a C shell before and after exposure to air.

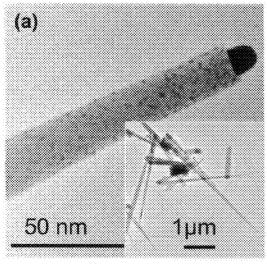

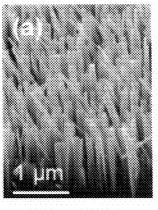

FIG. 5 shows overview and detailed images of catalyst-free GaN NWs on a Si(111) substrate.

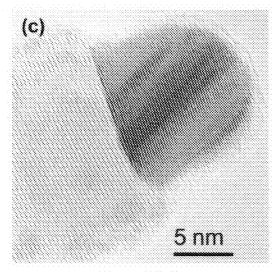

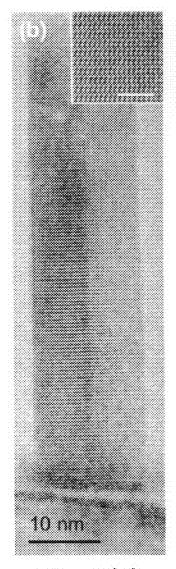

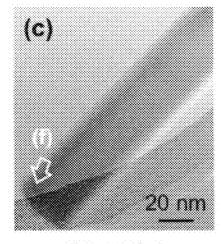

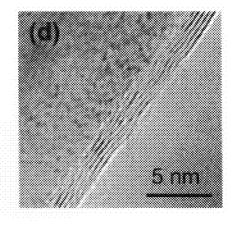

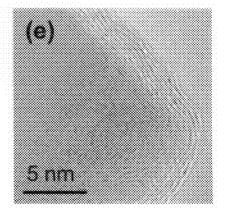

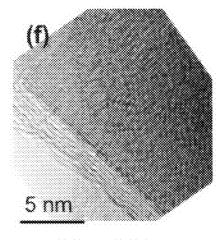

FIG. 6 contains TEM images showing a typical In-terminated GaN NW completely embedded in a C shell.

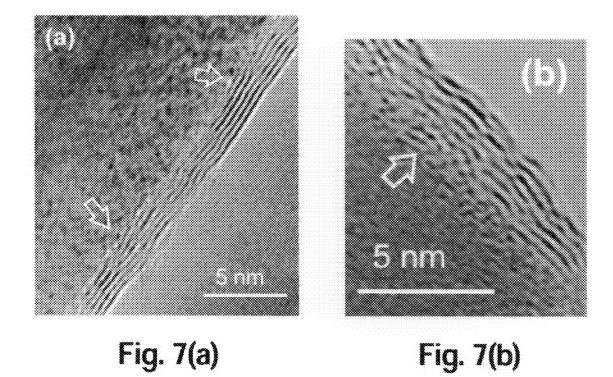

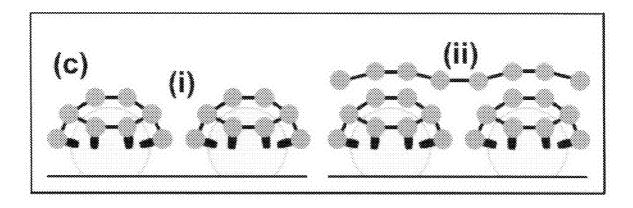

FIG. 7 contains TEM images and a schematic representation of the core/shell interface of an In-decorated GaN NW embedded in a C shell.

#### DETAILED DESCRIPTION

In the field of nanotechnology vocabulary is often ill-defined. However, as used herein, "nanoscale" refers to dimensions between about 0.1 nm and 500 nm. In this realm, objects may be referred to by their "dimensionality" from the number

2

of degrees of freedom available to the charge carriers in the object. Quantum dots, for example, are zero-dimensional clusters of atoms or molecules a few (≦10) nanometers in diameter. This is to be differentiated from the term "dimension" which refers to the size of the object. Usually the smallest dimension of an object is referred to as its "diameter," even if the cross-section of the object in the plane of the diameter is not circular. Thus quantum dots, nanorods, nanowires, nanotubes, nanospheres, nanoparticles, and so on all have diameters, the dimension of which is on the order of nanometers. In the abstract, and for purposes of discussion rather than limitation, these objects may all be termed "nanomaterials."

Semiconductors are materials that may be insulating or 15 conducting, depending on the temperature and the presence of impurities in the material. Silicon, on which virtually all modem electronic technology is based, is an elemental semiconductor. Elemental semiconductors consist of pure elements, like silicon (Si) and germanium (Ge). Si and Ge are both in Group IV of the periodic table of the elements, and are often referred to, with other elements of the same group, as group IV semiconductors. To obtain different properties, such as band gap or carrier mobility, members of Group IV may be substituted for each other, as in  $Si_{1-x}Ge_x$ , where x is less than or equal to one. Other semiconductors may be compounds. Gallium nitride (GaN), a material from which blue lightemitting diodes (LEDs) can be made, is a III-V semiconductor, so called because Ga is an element in Group III and N is a Group V element. Compounds of elements from Groups II and VI may also be semiconducting. An example of a II-VI semiconductor is cadmium selenide (CdSe), a preferred compound for quantum dots. Just as Si and Ge can substitute for one another, elements of Group III, e.g. Ga and Al, can be substituted in large or small amounts. In addition to other members of Group II, many transition metals may be substituted for Cd in II-VI compounds. In fact, any element that has the same, or equal, valence, i.e. is equivalent, may be substituted, e.g.  $Cd_{1-x}Mn_x$ Te or  $Cd_{1-x}Zn_x$ Te. Group V and VI substitutions work similarly, e.g.  $InAs_{1-x}P_x$  and  $CdSe_{1-x}Te_x$ . Some transition metal oxides, such as titania (TiO<sub>2</sub>) and zinc oxide (ZnO), both used in sunscreens, are also semiconduc-

Semiconductors have very interesting properties. For example, the resistance of a semiconductor can be changed over orders of magnitude by adding parts per million of dopants (desirable and controllable impurities). Semiconductors have gaps in their electronic energy bands which results in threshold voltages below which current cannot flow, making them suitable as diodes and transistors. These gaps also restrict absorption and emission of light by a semiconductor to discrete wavelengths. In addition, when light is absorbed charge carriers are created, changing the electrical properties of the semiconductor. Solar cells make use of this property to convert light energy into electrical energy.

Not all impurities are desirable or controllable, however. Impurities and imperfections can add electronic energy levels within the bandgap, which may have unpredictable effects on the semiconductor's properties. Surfaces of semiconductors are common sources of energy states such as these, producing surface electronic states, or surface states, in the band gap. Surface states, caused by the surface itself or by impurities adsorbed on the surface, change the properties of semiconductors in uncontrollable and unpredictable ways. To avoid surface states, semiconductors may be passivated by materials that leave their original electrical and optical properties intact. Si has a native oxide, SiO<sub>2</sub>, that serves to passivate the Si surface. This is one of the materials properties of Si that

makes it so suitable for use in electronic devices. Not all semiconductors have surface oxides, however, and even those that do may not be passivated by them. Other materials, then, must be found that can satisfy the bonds that cause surface states.

Bulk semiconductors, the form used in electronics and LEDs, depend on their intrinsic band gaps and impurity states for their electrical and optical properties. Nanoscale semiconductors, however, have quite different properties than their bulk cousins. Due to their small size, their charge carriers, 10 electrons and holes, are confined to energy levels that are allowed by quantum mechanics. For example, quantum dots absorb or emit light at different wavelengths depending on, and therefore tunable by, their dimensions. These properties, however, may be modified by surface states induced by unsatisfied bonds, oxides of one or more elements of the semiconductor, or adsorbed impurities on the surface of the nanoobjects, and the like. The much higher surface area per unit volume (surface-to-volume ratio) of these materials magnifies the difficulties posed by surface states.

Recognizing the challenges of obtaining passivated nanoscale semiconductors, the technology described herein offers a way of passivating nanoscale objects and discloses structures that result from employing the technology.

Semiconducting nanomaterials may be fabricated in any of 25 several ways, and no few of them may be bought from commercial suppliers. Some of the formation methods employ metal catalysts to direct the size and shape of the resulting nanomaterial. Other methods do not require catalysts. The choice of method for forming semiconducting nanomaterials 30 depends on the composition of the material and on the desired shape of the resultant semiconducting nanomaterial, i.e. quantum dot, nanowire, nanotube, etc. Some of the methods employed to form semiconducting nanomaterials include laser ablation, chemical vapor deposition (CVD), molecular 35 beam epitaxy (MBE), chemical vapor transport reactions, and low-temperature solution-phase synthesis. Other methods are also well known in the art. For example, high-aspect-ratio nanowires of Ge may fabricated by CVD using Au/Ge catalyst particles.

When Ge nanowires (NW) are transported through air, an oxide shell, typically 1-4 nm thick, forms on the surface. Unlike the case of the Si/SiO<sub>2</sub> system, the GeO<sub>x</sub> oxide layer does not passivate the Ge nanomaterial surface. FIGS. 1A through 1C are TEM images, taken at room temperature, 45 showing the detailed structure of as-grown Ge NWs close to the NW tip for one of the wires from the inset. The Au/Ge catalyst nanoparticles show darker contrast than do the Ge NWs themselves. In the high-resolution TEM images of FIGS. 1B and 1C, the (111) lattice planes of the Au/Ge alloy 50 with separation of 0.219 mn, close to the lattice spacing of Au, are clearly resolved. The NW axis is aligned with the [111] direction. The high-resolution images show lattice fringes with separation of 0.327 mn perpendicular to the NW axis, consistent with the spacing of (111) planes in bulk Ge. Au 55 from the catalyst particles segregates to the surface of the nanowires where it typically forms metal islands rather than smooth monolayers of metal. This is shown in FIG. 1B by the spots of darker contrast, pointed out by the arrows. During in situ annealing the Au aggregates have been observed to ripen 60 rapidly into larger, elongated crystalline clusters aligned with the NW axis.

FIGS. 2A through 2I show a sequence of TEM images illustrating the process of the removal of a germanium oxide surface layer and the assembly of a carbon shell around a Ge 65 NW during in situ annealing. The TEM samples were placed on amorphous carbon supports, which also served as a source

4

of C, and loaded into the microscope under vacuum conditions, i.e. at pressures below about 1 torr, down to about 1 or  $2\times10^{-5}$  torr or less. In an inert gas atmosphere any pressure, including atmospheric pressure, is applicable. Other sources of C may include other carbon-containing support materials or carbon-carrying precursor gases such as hydrocarbon gases including ethylene and acetylene. During in situ annealing the sample is also exposed to an electron beam. In general, during the process of forming the ordered carbon encapsulant the sample may be subject to irradiation by an electron beam with electron energy between 100 eV and 1 MeV.

The Ge NW shown in FIG. 2A exhibits a thick (~4 nm) layer of oxide. As seen in the inset, which shows the interface between the Ge wire and the GeO, surface layer, the oxide is amorphous and its interface with the Ge surface is atomically sharp. Upon heating the wires to 180° C. the thickness of the oxide layer can be observed to decrease over a course of minutes, sometimes about 5 minutes, under electron beam irradiation creating large areas of the NW surface that are entirely oxide free. FIG. 2B shows a stage of the process at which the oxide thickness has decreased to about 2.5 nm, while FIG. 2C shows the oxide entirely removed over large parts of the oxide surface (FIG. 2C inset). The remaining oxide patches are completely removed after the temperature is increased to about 290° C., as seen in FIG. 2D. The removal of the oxide may be caused by thermal or electron-beaminduced desorption or by the oxide's reduction by carbon.

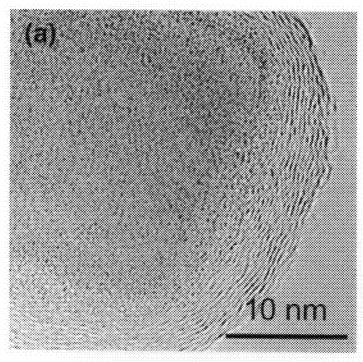

After removal of the surface oxide from Au-decorated Ge NW, also at a temperature of about 290° C., however, assembly of graphene C fragments is initiated at the tip of the NW adjacent to the Au/Ge nanoparticle. FIGS. 2E, 2F, and 2G show the continued build-up and organization of the C shell occurring both on the catalyst particle and on the surface of the Ge. FIG. 2E shows shell formation starting with the assembly of small curved segments at a temperature of about 340° C. These segments gradually build up several layers covering the whole NW (FIG. 2F, T=340° C.) and eventually straighten and organize into stacks of extended curved graphene sheets (FIGS. 2G and 2H, T=355° C.). From the high-resolution image of FIG. 2H the spacing of the graphene layers is determined to be about 0.3-0.4 nm, consistent with the c-axis spacing of graphite. From FIG. 2I, taken far from the NW tip and the Au/Ge catalyst particle, the entire Ge wire appears embedded in a C shell of several graphene layers. Under a variety of experimental conditions, metal-free Ge nanoparticles, i.e. pristine Ge nanoparticles, have not been observed to develop passivated surfaces. In particular, they do not form protective shells of ordered C. In general the chemistry of the surfaces of semiconductors prohibits the formation of passivating ordered shells of graphitic carbon.

FIGS. 3A through 3D show TEM images of a Ge NW completely embedded in a multilayer C shell. An overview of the embedded nanowire is shown in FIG. 3A. This wire gradually widens from the tip (nearest the catalyst particle) to the far end (farthest from the catalyst). The higher resolution micrographs of FIGS. 3B through 3D were taken at the respective areas pointed out with the arrows in FIG. 3A. They show that, although the thickness of the C shell decreases somewhat from the tip to the far end of the wire, the shell is relatively uniform throughout the length of the wire.

This controlled, metal-induced encapsulation of Ge nanomaterials allows assembly of a protective, passivating, C shell which may prevent oxidation of the wires in ambient environments. FIGS. **4A** and **4B** show TEM images of a Ge NW base encapsulated by a C shell before and after exposure to air. Comparison of the two micrographs shows that no oxide

is formed on the encapsulated nanomaterials during, and that the C shell itself is not degraded by, a 48-hour exposure to air.

Thus the inventive technology of seeding growth of a graphitic carbon encapsulant on a semiconducting nanomaterial using metal decoration of its surface offers a rational, controllable method of rendering oxidation-resistant nanomaterials not generally protected by native oxides.

As another example, GaN nanowires have been grown on Si(11) substrates without catalysts at  $790^{\circ}$  C. in an ultra-high-vacuum (UHV) chamber with a base pressure of  $2\cdot 10^{-10}$  torr. <sup>10</sup> FIGS. 5A and 5C show overviews, while FIGS. 5B, 5D, and 5E show detailed high-resolution TEM images, of such catalyst-free GaN NWs on a Si(111) substrate. Typical wires grown under such conditions (FIG. 5A) are straight, about 1  $\mu$ m in length and about 10-50 nm in diameter. FIG. 5B shows a detailed image of one nanowire. The inset, with a scale bar of 1 nm, shows the wurtzite crystal structure of the same wire. The TEM samples were placed on amorphous carbon supports, which also served as a source of C.

The wire in FIG. 5C is approximately 1.1 µm long with a 20 diameter of about 35 nm. FIG. 5D shows the detailed structure of the NW close to its surface. FIG. 1E shows the same section of the NW after in situ annealing at temperatures rising slowly from room temperature to about 500° C. The annealing conditions were similar to those described previously with respect to Ge NWs. Note that only an amorphous C film is generated on the surface of the NW by the annealing process.

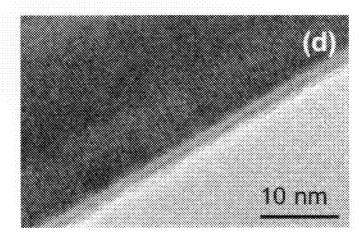

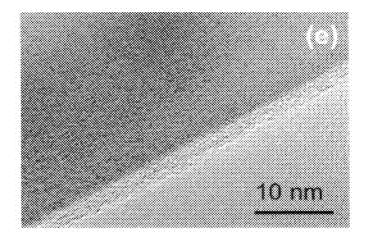

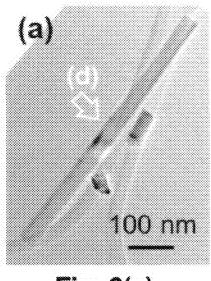

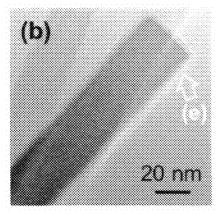

To decorate the surface of these metal-free semiconducting nanowires, such as the GaN NWs, with islands of metal, about 30 15 nm of InGaN may be deposited at a nominal In: Ga ratio of 2.1:3 under the same conditions as for the GaN growth. FIGS. 6A through 6F contain TEM images showing a typical Interminated GaN NW completely embedded in a C shell. FIG. **6**D is a high-resolution micrograph of the area of the nanowire of Fig. A noted by the arrow (d). Similarly FIGS. 6E and 6F are high-resolution micrographs of the corresponding areas pointed out with arrows in FIGS. 6B and 6C, respectively. In FIGS. 6B and 6C the C shell on the GaN core is clearly visible; taken near opposite ends of the NW the micrographs 40 show that the ordered graphene shell continuously covers the entire NW surface. The higher-resolution micrographs of FIGS. 6D through 6F show the ordered nature and uniform thickness of the C shell surrounding the semiconducting GaN core. The shell has about five graphene layers with a spacing 45 of 0.35-0.36 nm, in agreement with the c-axis spacing of graphene sheets in graphite.

Unlike the uniform TEM contrast throughout of FIGS. 5D (before annealing) and 5E (after annealing), dark spots are visible in the micrographs of the In-terminated GaN in FIGS. 50 6D through 6F. These spots may be attributed to In clusters randomly dispersed on the GaN surface. The clusters are observed to be about 1 nm in diameter and without discernable crystalline structure. A close look at the NW/C-shell interface reveals that the first layers of the shell consist of 55 small curved graphene fragments that envelop In clusters. As the graphene fragments are coated by progressively larger sheets they become less curved until they develop into extended, continuous graphene layers at the surface of the shell. FIGS. 7A and 7B contain TEM images of the core/shell 60 interface of an In-decorated GaN NW embedded in a C shell. Arrows indicate In clusters enveloped by curved graphene fragments.

FIG. 7C shows a schematic representation of the initial stages of the assembly of a C shell. FIG. 7C depicts an 65 envelope of curved graphene flakes surrounding In clusters (i) that then serves as a template for extended graphene layers

6

(ii). In general, the semiconducting core may be decorated with metallic nanoclusters by several methods. One such is direct deposition of the metal onto the surface of the semiconducting nanomaterial. In some cases metallic clusters form by segregation of metals from the interior of the nanomaterial or from a catalyst particle to the surface. For semiconducting nanomaterials incorporating a metallic component, the metal clusters may be generated by partial decomposition of the semiconducting nanomaterial. An example of the latter may be incorporating a metal into an outermost layer of a nascent semiconducting nanomaterial during growth, and allowing its subsequent partial decomposition into metal-rich areas (metallic clusters) and metal-poor areas (metal free surfaces).

Semiconductors need not be limited to uniform materials. Semiconducting superlattices are typically alternating nanoscale layers of at least two different materials that exhibit properties distinct from those of any of the constituent materials. Semiconducting nanomaterials, elemental, compound, or superlattices, have unique electrical, optical, and magnetic properties due to their physical properties (size, surface area, etc.) and chemical properties (e.g. surface bond configuration). It is these intrinsic properties that devices made from these materials seek to exploit. The passivating carbon shell as described herein may satisfy surface bonding configurations to reduce surface and interface states and allow the intrinsic properties to remain virtually unchanged. In other words, given the same stimulus, for example impinging electromagnetic radiation or an electrical potential, the encapsulated semiconducting materials give the same or virtually the same response, generation of charge carriers or an induced electrical current, as those of a pristine semiconducting nanomaterial absent surface states. The absence of surface or interface states may allow prediction of the response of the nanomaterial to a given stimulus, as opposed to the unpredictability of properties of unpassivated semiconducting nanomaterials.

Devices exploiting these properties may include, for example, sensors. The sensors work by detecting a change in response to a given stimulus. For example, the passivated core/shell structure may be irradiated by light (electromagnetic radiation) and an induced current or emission of light of a certain wavelength may be measured. The response to the stimulus, e.g. a change in the brightness or wavelength of the emitted light, may be different if the species, such as contaminant atoms or molecules, are attached to the C shell. The stimulus may be an applied voltage, an applied current, irradiation by electromagnetic radiation of at least one wavelength, or any useful stimulus such as a mechanical stress or exposure to particular chemical species, for example. The response to be detected may be an induced current or voltage, a mechanical strain, a change in the electronic structure of the nanomaterial, or absorption, reflection, or emission of electromagnetic radiation, i.e. light of at least one wavelength, and the like.

Species such as atoms, molecules, viruses, cells, bacteria, prokaryotes, and eukaryotes may be detected by such a sensor. Properties of these species, such as their presence or absence, their quantity (concentration or absolute magnitude), size, or identity, in addition to other properties such as oxidation state for example, may be determined by noting the modifications to the expected response. Other sensors may use an applied electrical potential to induce an electrical current, a current to induce a voltage, or a current to stimulate emission of light, for example.

In certain cases the atomically sharp interface between the shell and the core may create an electronically active junction.

7

Such a junction may have properties such as those exhibited by semiconductor-semiconductor, semiconductor-metal, or semiconductor-dielectric junctions. These properties may be exploited on the nanoscale for application in electronic devices and sensors.

While the foregoing description has been made with reference to individual embodiments of the invention, it should be understood that those skilled in the art, making use of the teaching herein, may propose various changes and modifications without departing from the invention in its broader 10 aspects.

The foregoing description being illustrative, the invention is limited only by the claims appended hereto.

The invention claimed is:

- 1. An encapsulated semiconducting nanomaterial compris- 15 ing:

- a semiconducting nanomaterial having a diameter and a surface, the diameter of the semiconducting nanomaterial having a magnitude between about 1 nm and about 100 nm.

- an encapsulant, the encapsulant enclosing the semiconducting nanomaterial and comprising an ordered carbon shell; and

- an interface between the ordered carbon shell and the semiconducting nanomaterial, the interface decorated with 25 islands of metal.

- 2. The encapsulated semiconducting nanomaterial of claim 1, wherein:

- the diameter of the semiconducting nanomaterial is between about 10 nm and about 50 nm.

- 3. The encapsulated semiconducting nanomaterial of claim 1, wherein:

- the ordered carbon shell comprises graphitic sheets of carbon.

- **4.** The encapsulated semiconducting nanomaterial of claim 35 **3** wherein:

8

- the interface between the ordered carbon shell and the semiconducting nanomaterial is atomically sharp.

- 5. The encapsulated semiconducting nanomaterial of claim 1, wherein:

- the semiconducting nanomaterial comprises one selected from the group consisting of a quantum dot, a nanoparticle, a nanorod, a nanowire, and a nanotube.

- **6**. The encapsulated semiconducting nanomaterial of claim **1**, wherein:

- the semiconducting nanomaterial comprises a semiconductor selected from the group consisting of an elemental semiconductor, a compound semiconductor, and a combination of elemental and compound semiconductors; and

- each element of the semiconductor is substitutable by an element of equal valence.

- 7. The encapsulated semiconducting nanomaterial of claim 6, wherein:

- the semiconductor comprises a semiconducting superlattice.

- 8. The encapsulated semiconducting nanomaterial of claim 1, wherein:

- the semiconducting nanomaterial is rendered oxidationresistant by the ordered carbon shell.

- 9. The encapsulated semiconducting nanomaterial of claim 1, wherein:

- the intrinsic electronic and optical properties of the semiconducting nanomaterial are preserved.

- 10. The encapsulated semiconducting nanomaterial of claim 1, wherein:

- an electronically active junction is formed between the semiconducting nanomaterial and the ordered carbon shell.

\* \* \* \* \*