# UNIVERSITÀ DEGLI STUDI DI MILANO

## DOCTORAL SCHOOL OF COMPUTER SCIENCE

DEPARTMENT OF COMPUTER SCIENCE "Giovani Degli Antoni"

> PhD in Computer Science Cycle XXX

# Toward Lower Communication in Garbled Circuit Evaluation

PhD Thesis of: Maryam Ehsanpour

Supervisor: Prof. Ernesto Damiani

Co Supervisors: Prof. Stelvio Cimato, Prof. Valentina Ciriani

PhD School Headmaster: Prof. Paolo Boldi

Academic year 2016/17

# Abstract

Secure Multi-party Computation (SMC) is a classical problem in theoretical security. In a SMC problem, two or more parties must compute correctly a function f on their respective inputs x and y, while preserving the privacy of their inputs and additional security properties.

One of the approaches proposed for addressing the SMC problem relies on the design of Garbled Circuit (GC). In *Garbled Circuits* (GCs), the function to be computed is represented as a Boolean circuit composed of binary gates. The input and output wire of each gate is masked such that the party evaluating the *Garbled Boolean Circuits* (GBC) cannot gain any information about the inputs or the intermediate results that appear during the function evaluation. The complexity of today's most efficient GC protocol depends linearly on the size of the Boolean circuit representation of the evaluated function. The total cost and run-time interaction between parties increase linearly with the number of gates and can be huge for complex GBCs. Actually, interest has grown in the efficiency of this technique and in its applications to computation outsourcing in untrusted environments.

A recent work shows that XOR gates in a Boolean circuit have no cost for the secure computation protocol. Therefore, circuits with a reduced number of non-XOR gates are more convenient and one of the possible ways to reduce the complexity of the computation is to reduce the number of non-XOR gates in the Boolean circuit.

Recalling that, the main aim of this work is to reduce the number of non-XOR gates, which directly results in a reduced number of interactions between the parties and transfer complexity at runtime, we present different approaches for reducing the communication cost of Secure Multi-party Computation (SMC) and improving the overall computation time and efficiency of the execution of SMC.

# Preface

The thesis deals with a secure multi-party computation. The problem set-up is interesting in the aspect of combining multiple fundamental issues including secure distributed computing, garbling circuits, and cost-optimization. Since the garbled circuit are useful in information security, we try to optimize garbled circuit transformation and construct it which requires minimum runtime interaction between the input owners.

# Acknowledgements

Foremost, I would like to express my sincere gratitude to my thesis supervisor Prof. Ernesto Damiani, not only for introducing me to the interesting concept of garbled circuit, but also for his patience, motivation, enthusiasm, and immense knowledge. I am very grateful for his support and trust. I would also like to thank my cosupervisors, Prof. Stelvio Cimato and Prof. Valentina Ciriani for their encouragement, and their aspiring guidance and friendly advice during my project. Besides, I would like to thank my thesis referees, Prof. Anna Bernasconi, Prof. June-Koo Kevin Rhee and Prof. Faisal Shah Khan, for their insightful comments.

I would like to express my deep appreciation to my husband, Ali Ahmadzadeh, for his support in every possible way. He continuously pushed me to do my best and reinforced my strength in times when I doubted myself.

My sincere thanks also goes to Lorena Sala for helping me adjust to the new environment and made me feel comfortable.

I am especially grateful to my parents for supporting me spiritually throughout my life. I always knew that they believed in me and wanted the best for me. This thesis would not have been possible without the support of my family, my husband, Professors and my friends.

"Knowledge is the most precious of all heritage and thought is the most clear of all mirrors" Imam Ali (AS)

# Contents

| 1        | Sec             | ure M                                                             | ulti-party Computation (SMC)                                | <b>21</b> |  |  |  |  |  |

|----------|-----------------|-------------------------------------------------------------------|-------------------------------------------------------------|-----------|--|--|--|--|--|

|          | 1.1             | Notat                                                             | ions and Definitions                                        | 21        |  |  |  |  |  |

|          |                 | 1.1.1                                                             | Protocol Parties                                            | 22        |  |  |  |  |  |

|          |                 | 1.1.2                                                             | Security in Multi-party Computation                         | 22        |  |  |  |  |  |

|          |                 | 1.1.3                                                             | Secure Two-party Computation                                | 23        |  |  |  |  |  |

|          |                 | 1.1.4                                                             | Comparison (Millionaires Problem)                           | 23        |  |  |  |  |  |

|          |                 | 1.1.5                                                             | Secure Multi-party Computation Using Virtual Party          | 24        |  |  |  |  |  |

|          |                 | 1.1.6                                                             | Secure Multi-party Computation Using Secure Sum Protocol .  | 25        |  |  |  |  |  |

|          |                 | 1.1.7                                                             | Secure Multi-party Computation Using Secret Sharing Schemes | 26        |  |  |  |  |  |

|          | 1.2             | Yao's                                                             | Garbled Circuit Protocol                                    | 27        |  |  |  |  |  |

|          |                 | 1.2.1                                                             | Basic Concepts and Definitions                              | 27        |  |  |  |  |  |

|          |                 | 1.2.2                                                             | Description of Yao's Garbled Circuit Protocol               | 29        |  |  |  |  |  |

|          | 1.3             | Efficie                                                           | nt GC-based Secure Multi-Party Computation (SMC)            | 33        |  |  |  |  |  |

|          |                 | 1.3.1                                                             | Free-XOR Protocol                                           | 33        |  |  |  |  |  |

|          | 1.4             | 4 Compiling Tools for Implementation of Two-Party Secure Computa- |                                                             |           |  |  |  |  |  |

|          |                 | tion P                                                            | rotocols                                                    | 36        |  |  |  |  |  |

|          |                 | 1.4.1                                                             | FAIRPLAY                                                    | 36        |  |  |  |  |  |

|          |                 | 1.4.2                                                             | CBFS-MPC                                                    | 38        |  |  |  |  |  |

|          |                 | 1.4.3                                                             | SCAPI                                                       | 38        |  |  |  |  |  |

|          |                 | 1.4.4                                                             | TASTY                                                       | 39        |  |  |  |  |  |

|          |                 | 1.4.5                                                             | ABY                                                         | 39        |  |  |  |  |  |

|          | 1.5             | Relate                                                            | ed Work                                                     | 39        |  |  |  |  |  |

| <b>2</b> | $\mathbf{Intr}$ | oducti                                                            | ion to Quantum Gates                                        | 42        |  |  |  |  |  |

|          | 2.1             | Quant                                                             | um Mechanics                                                | 42        |  |  |  |  |  |

|          |                             | 2.1.1   | Quantum State                                                                    | 43 |

|----------|-----------------------------|---------|----------------------------------------------------------------------------------|----|

|          |                             | 2.1.2   | Quantum Bit (Qubit)                                                              | 43 |

|          |                             | 2.1.3   | Quantum Key Distribution                                                         | 44 |

|          | 2.2                         | Quant   | um Logic                                                                         | 45 |

|          |                             | 2.2.1   | Reversible Computing                                                             | 46 |

|          |                             | 2.2.2   | Quantum Gates                                                                    | 47 |

|          | 2.3                         | RevKi   | t: Tool for the Design of Quantum Circuits                                       | 49 |

| 3        | Boo                         | olean F | unction Representation                                                           | 52 |

|          | 3.1                         | Truth   | Tables                                                                           | 53 |

|          | 3.2                         | DNF a   | and CNF forms                                                                    | 53 |

|          | 3.3                         | Binary  | y Decision Diagrams (BDDs)                                                       | 54 |

|          |                             | 3.3.1   | OBDD                                                                             | 55 |

|          |                             | 3.3.2   | ROBDD                                                                            | 55 |

|          |                             | 3.3.3   | CUDD: Tool to Build BDD Function Representation $\ldots$ .                       | 56 |

|          | 3.4                         | Multip  | ple-Valued Logic (MV)                                                            | 57 |

| 4        | $\mathbf{Sec}^{\mathbf{r}}$ | ure M   | ulti-Party Computation Exploiting Quantum Gates                                  | 61 |

|          | 4.1                         | Standa  | ard Garbling of Circuits                                                         | 62 |

|          |                             | 4.1.1   | Garbling the Comparison (Millionaires) Circuits                                  | 62 |

|          |                             | 4.1.2   | Garbling the adder circuits                                                      | 64 |

|          | 4.2                         | Quant   | um Implementation of Garbled Circuit (GC)                                        | 64 |

|          |                             | 4.2.1   | The Quantum Metrics                                                              | 65 |

|          |                             | 4.2.2   | Q-GBC for the Millionaires' Problem                                              | 65 |

|          |                             | 4.2.3   | Q-GBC for the 32-bit adder                                                       | 68 |

|          |                             | 4.2.4   | Q-GBC for the 64-bit adder $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 69 |

|          | 4.3                         | Discus  | ssion and Comparison of Results                                                  | 70 |

| <b>5</b> | BD                          | Ds for  | Secure Multi-Party Computation                                                   | 71 |

|          | 5.1                         | Using   | BDDs for Multi-Party Computation                                                 | 71 |

|          |                             | 5.1.1   | Using BDDs to Find Similar Classical Representation to XOR                       | 74 |

|          |                             | 5.1.2   | BDDs Method for Adders                                                           | 77 |

|          |                             | 5.1.3   | BDDs Method for Data Encryption Standard (DES)                                   | 77 |

|          |                             | 5.1.4   | BDDs Method for MD5 Cryptographic Function                                       | 78 |

|          |     | 5.1.5 Discussion and Comparison of Experimental Results | 80 |

|----------|-----|---------------------------------------------------------|----|

| 6        | Mu  | Itiple -Valued Logic for Secure Multi-Party Computation | 81 |

|          | 6.1 | Multiple Valued Yao's Protocol                          | 82 |

|          | 6.2 | Improved Evaluation for Multiple Valued Gates           | 85 |

|          |     |                                                         |    |

| <b>7</b> | Con | iclusions                                               | 87 |

|          | 7.1 | Future Work                                             | 89 |

# List of Tables

| 1.1 | Initial garbled circuit table for XOR gate                                                       | 31 |

|-----|--------------------------------------------------------------------------------------------------|----|

| 2.1 | RevKit Commands                                                                                  | 51 |

| 3.1 | Two-place MVL operators                                                                          | 59 |

| 4.1 | Comparison of our circuit in case of number of non-XOR gates                                     | 70 |

| 5.1 | Showing similarity of functions $f=A+B$ and $f=A\oplus B$ using their truth                      |    |

|     | tables                                                                                           | 72 |

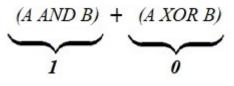

| 5.2 | Showing similarity of function $f = (A \oplus B) + (A,B)$ with $f = (A \oplus B) \oplus (A,B)$ . | 72 |

| 5.3 | Truth table of similar functions to XOR gate.                                                    | 73 |

| 5.4 | Comparison of our gaining for 32-bit Adder in BDDs method. $\ldots$ .                            | 77 |

| 5.5 | Comparison of our gaining for 64-bit Adder in BDDs method. $\ldots$ .                            | 77 |

| 5.6 | Comparison of our gaining for DES (Key Expanded) in BDDs method.                                 | 79 |

| 5.7 | Comparison of our gaining for DES (No Key Expanded) in BDDs                                      |    |

|     | method.                                                                                          | 79 |

| 5.8 | Comparison of our gaining for MD5 in BDDs method                                                 | 80 |

| 6.1 | Truth table of MV XOR (mod-sum) operation for $p=3$ in Garble                                    |    |

|     | Circuit.                                                                                         | 83 |

| 6.2 | Initial garbled circuit table for MV XOR gate                                                    | 84 |

# List of Figures

| 1.1  | Data flow in VPP with five layer structure consisting of party layer,    |    |  |  |

|------|--------------------------------------------------------------------------|----|--|--|

|      | virtual party layer, trusted anonymizer layer, untrusted anonymizer      |    |  |  |

|      | layer and computation layer from starting to end respectively [52]       | 24 |  |  |

| 1.2  | Secure Sum Protocol [65]                                                 | 26 |  |  |

| 1.3  | The Oblivious Transfer Protocol                                          | 29 |  |  |

| 1.4  | XOR gate with its corresponding wire keys                                | 31 |  |  |

| 2.1  | The qubit state as a Bloch sphere presentation [62]                      | 44 |  |  |

| 2.2  | Quantum key distribution process [58]                                    | 45 |  |  |

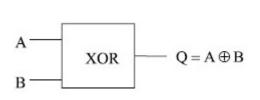

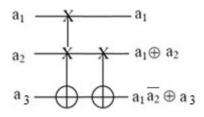

| 2.3  | Conventional XOR gates (gate and truth table)                            | 47 |  |  |

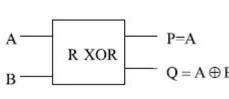

| 2.4  | Reversible XOR gates (gate and truth table). $\ldots$                    | 47 |  |  |

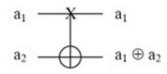

| 2.5  | Quantum NOT gate                                                         | 47 |  |  |

| 2.6  | Quantum XOR gate                                                         | 48 |  |  |

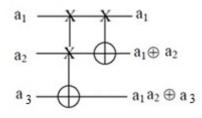

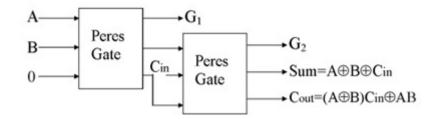

| 2.7  | Quantum Toffoli gate.                                                    | 49 |  |  |

| 2.8  | Quantum Peres gate                                                       | 49 |  |  |

| 2.9  | Quantum TR gate                                                          | 49 |  |  |

| 2.10 | Quantum Implementation of function $f=(a+b)\oplus c$ using RevKit        | 51 |  |  |

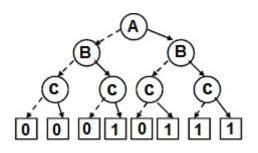

| 3.1  | Binary decision diagram (BDD) of the function $f=(A\oplus B)C\oplus AB.$ | 55 |  |  |

| 3.2  | Truth tables for two-input Boolean and MVL operators. $\hdots$           | 60 |  |  |

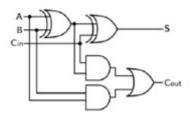

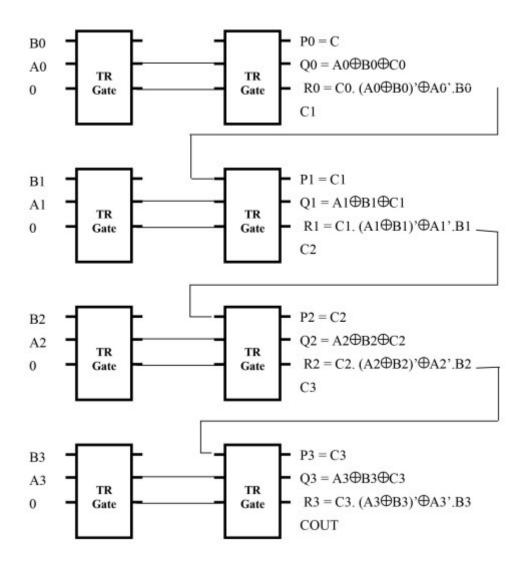

| 4.1  | Classical adder.                                                         | 64 |  |  |

| 4.2  | Quantum comparator [61]                                                  | 67 |  |  |

| 4.3  | Quantum implementation of TR gate using RevKit                           | 67 |  |  |

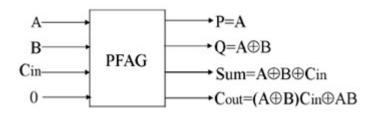

| 4.4  | Quantum Peres Full Adder gate (for 1-bit adder).                         | 68 |  |  |

| 4.5  | Implementation of PFAG using Peres gates (for 1-bit adder)               | 69 |  |  |

| 4.6  | Quantum Implementation of PR gate using RevKit (for 1-bit adder).        | 69 |  |  |

|      |                                                                          |    |  |  |

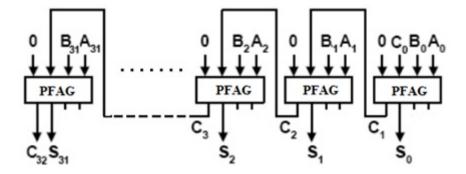

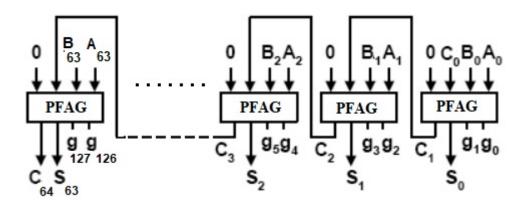

| 17  | Quantum adder 32-bit                                           |   |   |   |   |   | 60 |

|-----|----------------------------------------------------------------|---|---|---|---|---|----|

| 4.7 |                                                                | • | • | • | · | • | 09 |

| 4.8 | Quantum adder 64-bit                                           | • | • | • | • | • | 70 |

| 5.1 | Different results with input $(1,1)$ to both sides of OR gate. | • |   | • |   | • | 73 |

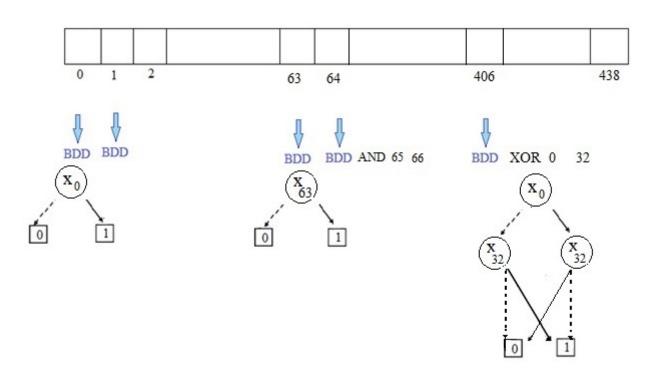

| 5.2 | Array of BDDs for 32-bit adder                                 | • | • | • | • | • | 75 |

| 6.1 | MV XOR gate (mod-sum) with its corresponding wire keys.        |   |   |   |   | • | 84 |

# Short Contents

# Introduction

# Chapter 1

Secure Multi-party Computation (SMC)

# Chapter 2

Introduction to Quantum Gates

# Chapter 3

Boolean Function Representation Binary Decision Diagrams (BDDs) Multiple-Valued Logic (MV)

# Chapter 4

Secure Multi-Party Computation Exploiting Quantum Gates

# Chapter 5

BDDs for Secure Multi-Party Computation

# Chapter 6

Multiple Valued Logic (MV) for Secure Multi-Party Computation

# Chapter 7

Conclusions

# Introduction

In a Secure Multi-party Computation (SMC) problem, two or more parties must compute correctly a function f on their respective inputs x and y, while preserving the privacy of their inputs. Besides inputs privacy, other security properties are requested for the execution of the SMC protocol, such as correctness, meaning that the output received is exactly f(x,y), and independence of inputs, meaning that neither party can choose its input as a function of the other party's. In [2], different paradigms for solving secure computation problems have been proposed, some relying on Homomorphic Encryption (HE), others on Linear Secret Sharing (LSS), usually deployed when more than two parties are involved.

In the mid 1980's, Yao proposed a first approach for addressing two-party SMC [79]. Yao's construction is based on the design of a Garbled Circuit (GC), that is a normal Boolean circuit representing the function to be computed securely, but whose evaluation is performed gate by gate using a protocol to respect inputs privacy. Indeed the input and output wires of each gate are masked so that the party evaluating the GC cannot gain any information about the inputs or the intermediate results that appear during the function evaluation. For each gate, an Oblivious Transfer (OT) protocol [56] is run between the two parties so that the resulting output value can be computed without knowing the input value of the other party. Specifically, all the inputs are encrypted and during the evaluation of the output of each gate the decryption keys are exchanged. The total OT payload increases linearly with the number of gates, and can be huge for complex GCs. A possible approach to increase the efficiency of the GC technique has been proposed by Kolesnikov et al. [37] in 2008, enabling the evaluation of XOR gates essentially free communication-wise (i.e., it requires one local XOR operation, and no garbled table entries to generate or transfer). For this reason, construction of GCs requiring less non-XOR gates, achieves the goal of reducing OT payload and therefore reduces the overall communication cost. The problem then is to design the GC that represents the function f to be computed and requires the minimum interaction at runtime between the collaborating parties. In turn, since there are multiple representations of the same function, or better equivalent Boolean circuits, this means that we try to select the one that has the minimum number of non-XOR gates, since XOR gates have no cost for the execution of the secure computation protocol.

The goal of this thesis is to study the possibility of decreasing the computational and communicational cost of the SMC by reducing the number of non-XOR gates. This directly results in a decreased runtime interactions between the input owners, thus improving the overall computation time and efficiency of the execution of the SMC.

Applications for two-party secure computation have three properties: (1) the application involves inputs from two independent parties; (2) each party wants to keep its own data secret; and (3) the participants agree to reveal the output of the computation. That is, the result itself does not imply too much information about either party's private input.

Secure Multi-party Computation (SMC). Secure Multi-party Computation (SMC) protocols have been introduced to give two or more parties the capability to compute a function f of their respective inputs x and y, still keeping their inputs private, and sharing only the final result z = f(x, y). In the last years, SMC was used as enabling technology for a large number of security- and privacy-critical applications (e.g., electronic auctions [48], data mining [40], remote diagnostics [14], medical diagnostics [5], or face recognition [23]).

Yao's Garbled Circuits (GCs) Protocol.Using Garbled Circuits (GCs) protocol [79], is the first approach to solve the SMC problem. Yao's GC construction introduces a protocol for the evaluation of the input function (f) represented as a Boolean Circuit composed of binary gates. The basic idea is that one party "encrypts" the circuit (using symmetric keys), the other party obliviously obtains the keys corresponding to both parties' inputs and the GC, and is able to decrypt the corresponding output. One party constructs the circuit C, and converts it into a garbled circuit and the garbled circuit is transferred to the other party. Specifically, the output of each gate in the GC is evaluated by exchanging some encrypted information between the two parties, so that none of the two parties learns any information about the inputs of the other party. So, the important note is that just a final output is shared between two parties and each party do not have any information about other party's value or any intermediate values during the protocol. For each gate, an Oblivious Transfer (OT) protocol [56] is run between the two parties so that the resulting output value can be computed without knowing the input value of the other party. The total OT payload increases linearly with the number of gates, and can be increased for complex GCs. Efficiency of GC protocol depends linearly on the size of the Boolean circuit representation of the evaluated function.

**Free XOR Protocol.** Kolesnikov and Schneider [37] proposed an improvement that allows XOR gates to incur zero communication with no cryptographic operations. This cryptographic protocols bring significant benefit to many SMC settings and allow to evaluate XOR gates at a substantially lower cost (i.e., in computation and communication required for creation, transfer and evaluation of the Garbled tables) than non-XOR gates such as AND gates. The *free-XOR* technique [37] allows all XOR gates to be executed by just XOR-ing the input wire labels, without the need of any encryption operations. Because of this, it is worth investing the effort to minimize the number of non-XOR gates in the construction of Garbled Circuits with the goal of reducing the communication cost. The main observation of this protocol is that it is not necessary to select all garblings independently.

Quantum Gates. One of today's most fascinating fields of research and innovation involves applying quantum phenomena to new technology. The belief is that these technologies promise to revolutionise society this century through secure communication, precision measurement, and powerful computation. Whereas in classical circuits the bit is the standard building block for storing information, in quantum circuits the information is represented by the quantum state of qu-bits. The logical properties of qubits also differ significantly from those of classical bits. Bits and their manipulation can be described using two constants (0 and 1) and the tools of boolean algebra. Qubits, on the other hand, must be discussed in terms of vectors, matrices, and other linear algebraic constructions. In particular, while a bit can have two states only, 0 > or 1 >, a qu-bit stores any linear combination c 0 > + d 1 > of 0 > and 1 >, where c and d are complex numbers. A quantum logic gate has the same number of inputs and outputs, and there is a bijective function between each input and output. Therefore, quantum gates are inherently reversible, meaning that any gate has a corresponding inverse operation. A quantum library contains a set of gates that compose a universal set meaning that it is possible to realize any reversible function using the gates in that library. NOT gate and two-bit Controlled-NOT (or C-NOT) gate [27] and three-bit Controlled-Controlled-NOT (or CC-NOT or Toffoli) gate [73] are some of the most common gates from NCT quantum library.

Over the last couple of decades, quantum cryptography and quantum gates have received growing attention. A large number of works in literature deals with quantum key distribution, i.e., the process of using quantum communication to establish a shared key between two parties (§2.2) [9].

**Binary decision diagrams(BDDs).** The standard representation form for logic was the sum of product (SOP) form, i.e., a disjunction (OR) of conjuctions (AND) made of literals. The advent of very large scale integration, the standard representation for logic moved from SOP to directed acyclic graphs (DAGs) [13]. A notable example of DAG where all the nodes realize the same function is binary decision diagrams (BDDs) [15]. BDDs are canonical and provide very efficient manipulation procedures. For this reason, BDDs found application in various areas, such as verification, testing, optimization, automated reasoning, etc.[44].

Multiple-Valued Logic (MVL). In the field of circuit design, Multiple Valued Logic (MVL) [10, 46] is a direct generalization of the standard Boolean logic, where the classical Boolean domain  $B = \{0, 1\}$  is replaced by  $P = \{0, 1, ..., |P| | -1\}$  with |P| > 1. For high level design it is natural to think of multiple valued variables, rather than Boolean ones, with the aim of reducing the number of interconnections required and circuit cost to implement logic functions [75].

# **Problem Statement and Contributions**

In this thesis we focus on improve efficiency of Garble Circuit(GC) protocol in Secure Multi-party Computation (SMC) with presenting methods for optimization of this protocol based on reducing number of non-XOR gates, which result in reducing OT payload and therefore reduce the overall communication cost. The overall research question we are interested in can be stated as follows: "Given a Boolean function f represented by a garbled Boolean circuit (GBC) and evaluated on the private inputs held by two parties, how can we optimize this GBC transformation and how can we construct the GBC that requires minimum runtime interaction between the input owners?"

In brief, our contributions are as follows:

- We have put forward the methods for building efficient Boolean-Circuit for SMC of functions based on Garbled Circuit (GC) protocols and decreasing the computational cost and improving the overall efficiency of the execution of the SMC.

- Using Free-XOR technique that allows XOR gates to be evaluated "for free" in GC construction, i.e., without relying on corresponding garbled gate. It can help us to reduce the number of non-XOR gates that result in reduced number of runtime interactions between the parties and the communication cost.

- Work on different design techniques (i.e., Quantum gates) and different function representation methods (i.e., BDDs, Multiple-Valued logic). Using Quantum gates can reduce the gate complexity and helps us to design quantum garbled circuit (Q-GC) equivalent to the original Boolean circuit, which can result in increasing the number of XOR gates, and decreasing the number of non-XOR gates, thus requiring less interaction. Moreover, using Binary Decision Diagrams (BDDs) method to identify non-XOR gates that could be replaced by XORs without altering the output of the circuit. This method can also result in reducing the number of operations, reducing the communication costs and circuit cost. In addition, we follow the idea of garbled circuit protocol from Boolean logic to the Multiple Valued Logic (MVL) setting to obtain more compact circuit descriptions.

In particular we have studied our methods (Quantum Garbled Circuit, BDDs, MV) for standard functionalities such as the *Millionaires' Problem*, which is the problem of determining which party has the greatest input, and for the *adder*, that is the computation of the sum of the private inputs. In all cases we try to show the improvements achieved in terms of reduced communication time.

The rest of this dissertation is organized as follows:

## Secure Multi-party Computation (SMC) (§1).

Starts with a detailed introduction of two-party secure multi-party computation (SMC) with special focus on Garbled circuit (GC) protocol as a solution to solve the problem of SMC and *free-XOR* technique for improving efficiency of GC. Besides introducing compiling tools for implementing two-party secure computation and making it as a practical applications.

### Introduction to Quantum Gates (§2).

Gives more detailed introduction to quantum logic concepts and simulation tool for synthesis, implementing and testing of quantum circuits.

### Boolean Function Representation (§3).

Reviews concepts of Boolean Function Representation as Binary Decision Diagrams (BDDs) and gives basic information on Multiple-Valued Logic (MVL) respectively.

### Secure Multi-Party Computation Exploiting Quantum Gates (§4).

Presents Garbling of Boolean function and quantum implementation of Garbled Boolean function. We show how to improve efficiency of SMC by using quantum gates instead of traditional gates in Garbled Boolean circuit construction. It also presents one of our proposed methods (Q-GBC) for improving efficiency of Garbled Boolean Circuits.

### BDDs for Secure Multi-Party Computation (§5).

Provides our proposed optimization technique in GC protocol using BDDs.

## MV for Secure Multi-Party Computation (§6).

proposes multiple valued GC protocol and the extension of the optimization technique for the evaluation of multiple valued gates.

## Conclusions (§7).

Summarizes the contributions of our thesis and states final conclusions with directions for future work in all of our proposed techniques, Q-GBC, using BDDs and Multi-valued Logics for improving efficiency of SMC.

## List of Related Publications:

"Toward Design of Garbled Circuits Using Quantum Gates", Maryam Ehsanpour, COMPSAC Conference, Building Digital Autonomy for a Sustainable World, Politecnico di Torino, 4 July - 8 July 2017, Turin, Italy.

"Exploiting Quantum Gates in Secure Computation", Maryam Ehsanpour, Stelvio Cimato, Valentina Ciriani, Ernesto Damiani, Euromicro Conference on Digital System Design, (DSD), 30 August - 1 September 2017, Vienna, Austria.

"A Multiple Valued Logic Approach for the Synthesis of Garbled Circuits", Stelvio Cimato, Valentina Ciriani, Ernesto Damiani, Maryam Ehsanpour, 25th IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), 23 October-25 October 2017, Yas Viceroy, Yas Island, Abu Dhabi.

# Chapter 1

# Secure Multi-party Computation (SMC)

This chapter introduces Secure Multi-party Computation and Two-Party Secure Computation. The most efficient solution to solve the problem of SMC (Garbled Circuits Protocol) in the two-and multi-party setting is explained in §1.2, and optimization of GCs protocol has been introduced in §1.3. Finally, compiling tools for implementation of Two-Party SMC protocols are introduced in §1.4, and related work are described in §1.5.

# **1.1** Notations and Definitions

Due to the tremendous growth of the huge amount of computers and distributed working environments, protocols are required for protecting the privacy of users and reliability of results. This problem is known as secure multi-party computation, which is a special case of a long-studied problem in cryptography.

in Secure Multi-party Computation (SMC) the parties  $P_1, P_2, \ldots, P_k$  with inputs of  $x_1, x_2, \ldots, x_k$  want to compute some common function  $f(x_1, x_2, \ldots, x_k)$  such that a party  $P_i$  can know only its own input  $x_i$  and the value of the function f. The aim of SMC protocol is to enable parties to compute a function f in a secure manner where keeping their inputs private, and sharing only the final result.

SMC problem provides a general solution to execute any computation in combi-

national circuits [78, 79]. It can have high communication cost as the complexity of the computation grows.

The design of efficient SMC protocols is considered for a variety of security-critical applications with sophisticated privacy and security requirements such as electronic voting, electronic auctions [48], electronic cash schemes, data mining [40], remote diagnostics [14], classification of medical data [5], or face recognition [23, 50, 60]. In addition the technology of secure multi-party computation has gain much interest recently in research community, governments and industry as a potential tool for their need.

# 1.1.1 Protocol Parties

Secure computation protocols have been introduced to provide two or more interacting parties with the capability of computing a function f of their respective inputs xand y, while keeping their inputs private. The protocol involves two players or participants, Alice and Bob, who want to evaluate and compute the function f together on that private data while keeping their inputs secret.

# 1.1.2 Security in Multi-party Computation

Security of input data is of prime importance for multi-party computation. protocol execution can be come under "attack" by an adversaries. The aim of this attack may be to learn private information or cause incorrect result of the computation. In order to prove that a protocol is secure and can endure any adversarial attack, a number of different definitions have been considered that ensure important security properties. The must central of these properties for multi-party computation are defined below:

• **Privacy:** Nothing should be learned more than what is necessary. Parties should learn their output and nothing else. What can be derived from the output itself, is the only information that should be learned about other parties' input. For example, the *privacy* requirement for an *election protocol* ensures that no parties should learn anything about the individual votes of other parties. Likewise, the *privacy* requirement for an *auction protocol* ensures that only

the winning suggestion is revealed and clearly possible to find that all other suggestions were lower than the winner's offer.

- **Correctness:** Parties are ensured that they can receive the correct output and trusted party can not be corrupted. For example, the *correctness* requirement for an *auction protocol* ensures that the party with the highest suggestion in guaranteed to win.

- Guaranteed Output Delivery: Adversary should not be able to prevent honest parties from receiving their output.

- Fairness: Adversaries or (corrupted parties) should receive their outputs if and only if the honest parties also can receive their outputs.

Security for Multi-party Computation (MPC) can be defined an "ideal-real-world" consisting of both "ideal world" model and "real world" model. In the "ideal world" model, players give their inputs to a incorruptible trusted party that computes the function on its own and sends back the result to each party. Notice that in this ideal computation, all of the above security properties hold. In contrast, in the "real world" model there is no trusted party, and the parties can only exchange messages between all the parties. So, security in MPC protocol means that adversaries can perform in the "real world" protocol and also do in the "ideal" setting.

# 1.1.3 Secure Two-party Computation

Secure Two-party Computation allows two parties to compute correctly a function f on their respective inputs x and y, while preserving the privacy of their inputs and additional security properties and sharing only the final results. The most important of these properties are *privacy* meaning that the parties learn the output f(x,y) but nothing else, *correctness*, meaning that the output received is indeed f(x,y) and not something else, and *independence* of inputs, meaning that neither party can choose its input as a function of the other party's.

# 1.1.4 Comparison (Millionaires Problem)

The "Millionaires Problem" was introduced by Yao in [78] as motivation for secure computation: two millionaires want to securely compare their respective private

Figure 1.1: Data flow in VPP with five layer structure consisting of party layer, virtual party layer, trusted anonymizer layer, untrusted anonymizer layer and computation layer from starting to end respectively [52].

input values without revealing more information than the outcome of the comparison to the other party (e.g., about their amount of money, in which two parties are millionaires and two millionaires want to know who is richer without letting each other know about the amount of money they have). Yao's Garbled Circuit (GC) protocol (cf.  $\S1.2$ ) is the most efficient solution to solve the Millionaires problem.

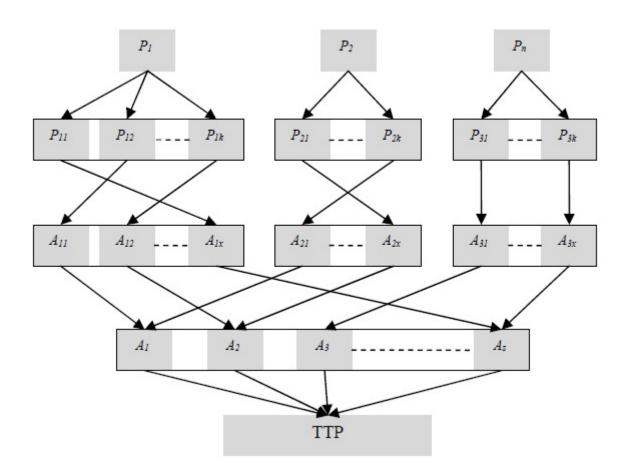

## 1.1.5 Secure Multi-party Computation Using Virtual Party

Virtual Party Protocol (VPP) can be used to ensure the privacy preserving the data input by not revealing the right data. In this protocol some fake data and some virtual party are created. There are *n* parties  $P_1, P_2, P_3, ..., P_n$ . Each party  $P_i$  has data  $X_{i1}, X_{i2}, X_{i3}, ..., X_{im}$ . Each party  $P_i$  has some trusted anonymizers  $A_{i1}, A_{i2}, A_{i3}, ..., A_{iX}$  and Z number of un-trusted anonymizers  $A_1, A_2, A_3, ..., A_Z$ . Each party  $P_i$  will create some fake data  $F_{i1}, F_{i2}, F_{i3}, ..., F_{iq}$ , where q is the total number of fake data entries. Each Party  $P_i$  will also create K virtual parties  $P_{i1}, P_{i2}, P_{i3}, ..., P_{iK}$ . Then the value of each data  $D_{i1}, D_{i2}, D_{i3}, ..., D_{i(m+q)}$  is encrypted and distributed randomly among the virtual parties. Corresponding modifier tokens for every  $P_i$  is also created that are mixed with fake data. These modifier tokens are distributed randomly among the virtual parties that will be used in the final computation to obtain the correct result. These parties will send their data to trusted anonymizers. Trusted anonymizers distribute their data randomly among the un-trusted anonymizers and the data of un-trusted anonymizers is sent to third party. Third party will use the data and the modifier tokens to compute the result.

The whole scenario of encryption, modifier tokens, encrypted data and the method of computation can be seen in Figure 1.1.

# 1.1.6 Secure Multi-party Computation Using Secure Sum Protocol

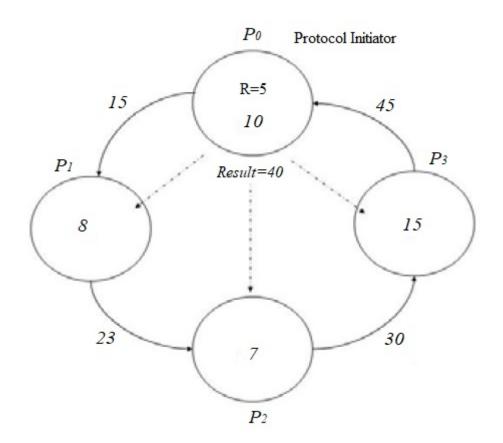

In Secure Sum Computation Protocol proposed by Clifon et al. [65] all the parties want to know the sum of their individual data inputs. In this protocol parties put in a unidirectional ring and one of these parties is selected as a *protocol initiator* party. Probability of data leakage is reduced to zero by changing the positions of the parties in the ring. Randomization method is used in this protocol for computing the sum as described below:

The computation will be started by choosing a random number and add its own data input. The sum is then transmitted to the next party. The next party adds the received sum to own data and then sends this new sum to the next party. This procedure is repeated until the *protocol initiator* receives the sum of all the data and the random number. The random number is known only to the protocol initiator party, Thus it subtracts the random number from the sum and allows all the parties to know the result.

Figure 1.2: Secure Sum Protocol [65].

All scenario of this protocol are depicted in Figure 1.2 where parties where parties  $P_0$ ,  $P_1$ ,  $P_2$  and  $P_3$  with their data 10,8,7 and 15 perform secure sum computation. Initiator party  $P_0$  selects a random number R=5 and sends to  $P_1$  the sum of this random number and its private data (10). Also the new sum 23 can be resulted by adding the data of  $P_1$  (8) and previous sum (15). This process is repeated until the sum 45 is received by  $P_0$ .  $P_0$  can subtract random number from 45 and send the final sum as 40 to all the parties.

# 1.1.7 Secure Multi-party Computation Using Secret Sharing Schemes

Where participation of president and his highest ranking is required to unlock the trigger for the nuclear missile, we call this *secret sharing* in cryptography.

Secret sharing is used as one of the secure protocols for solving the multi-party

computation problem. This protocol involves a set of n parties  $\{P_1, \ldots, P_n\}$ , a dealer who has a secret, and a collection of subsets of parties called the access structure. A secret is divided into n shares, and they are privately given to n parties. An access structure is a monotone collection  $\mathcal{A} \subseteq 2^{\{P_1, \ldots, P_n\}}$  of subset of  $\{P_1, \ldots, P_n\}$ . A collection  $\mathcal{A}$  is monotone if  $B \in \mathcal{A}$  and  $B \subseteq C$  imply that  $C \in \mathcal{A}$ . Sets in  $\mathcal{A}$  are called authorized subsets and sets not in  $\mathcal{A}$  are called unauthorized subsets. Access structure is a method of sharing a secret  $\mathcal{S}$  among a set of  $\mathcal{K}$  participants (parties)  $\mathcal{P}$  in such a way that the following two properties are satisfied:

- If an authorized subset of parties pool their shares, then they can determine the value of  $\mathcal{S}$ .

- If an authorized subset of parties pool their shares, then they can determine nothing about the value of S.

# **1.2** Yao's Garbled Circuit Protocol

In the mid 1980's, Yao proposed a first approach for addressing two-party Secure Computation [78, 79]. Yao's garbled circuit is a way to "encrypt a computation" that reveals only the output of the computation, but reveals nothing about the inputs or any intermediate values. In this section we introduce some standard notation and concepts corresponding to Garbled Circuit protocol ( $\S1.2.1$ ) and then Yao's garbled circuit protocol is explained in several steps ( $\S1.2.2$ ).

## **1.2.1** Basic Concepts and Definitions

In this section we introduce common definitions, function to circuit, Boolean Circuit, Bit-String, Garbled Values and Oblivious Transfer Protocol used in this thesis.

### Function to Circuit

According to Goldreich et al. in [31] it is possible to map any poly-time function f with fixed size input to a Boolean circuit C consisting of digital gates (AND,OR,NOT,..) that returns the same result.

### **Boolean Circuits**

Boolean circuits are classical and standard representations for functions which are particularly useful for SMC. A Boolean circuit consists of n-input gates  $G_n$  and wires that performs a mapping from n input bits to one output bit, i.e.,

$$G_n: (in_1, ..., in_n) \in \{0, 1\}^n \to \{0, 1\}.$$

Boolean circuit is an acyclic (i.e., loop-free or feed-forward) graph used as a mathematical model of digital logic circuits, defined in terms of the logic gates. Every gate that is used in Boolean circuit construction creates a cost. Thus, if we reduce the number of gates, we can reduce the cost involved in it. Generic gates are AND, OR, NOT, XNOR, XOR.

### **Bit-Strings**

Bit string is a sequence of bits, which defines and represents sets of binary data that are numbered from zero to the number of bits in the string less one. The length of a bit string is also defined as the number of bits that it contains.  $\{0, 1\}^l$  defined the space of binary strings of length l. A bit string can also contain zero or more bits.

### Garbled Values

Computations in a GC are not performed on obvious values 0 or 1, but on random bit strings, called garbled values. In construction of the GC, two random bit strings (garbled values)  $k_x^0$ ,  $k_x^1$  are assigned to each wire  $x_i$  of C. Two random bit strings, which are assigned to the corresponding value 0 and 1, do not disclose to them as they are chosen randomly.

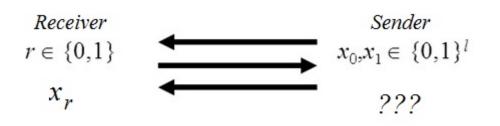

### 1-out-of-2 Oblivious Transfer Protocol (OT)

A foundation building block for almost all efficient protocols of secure computation is 1-out-of-2 Oblivious Transfer (OT) protocol [56, 25] that consists of two phases: the Transferring phase and the opening phase. Oblivious Transfer protocol works between two parties, a Sender (Alice) and a receiver (Bob). This protocol is called 1-out-of-2 since the receiver learns one of the 2 inputs of the sender and forget any information.

Figure 1.3: The Oblivious Transfer Protocol.

In the transferring phase, the goal of the sender (Alice) is to send a message (in general, a bit-string) to another party (Bob) in such a way that he can decide to obtain one of the 2 inputs of the sender at his choice but not both. In the opening phase, the goal of the receiver (Bob) is to open the message, but the sender never finds which message Bob received.

As you can see in Figure 1.3, a sender (Alice) has two messages  $(x_0,x_1)$ . She sends a one-bit message to another party (Bob) in such a way that he can decide to obtain one of the two messages according to his choosing bit (r). The result is that the receiver learn  $x_r$  without learning anything about sender's bit while the sender learn nothing about r. Alice never finds out which message Bob received and remain totally ignorant about which of the two messages he received.

## **1.2.2** Description of Yao's Garbled Circuit Protocol

Yao's GC construction, often called Garbled Boolean Circuit (GBC) introduces a protocol for the evaluation of the input function (f) represented as a Boolean Circuit and is based on the encryption of the input and intermediate values, so that only the final result is shared among the parties.

Yao's Garbled Circuit construction is composed of two phases: Garbling and Evaluation, which are distinctly executed by the two parties. During the Garbling phase, Alice converts a circuit into a garbled circuit, while Bob performs the Evaluation phase taking in input the garbled circuit, executing some interactions with Alice, and finally computing the output value. If we want to be a little more precise, a "garbling scheme" consists of the following steps:

- Alice generates a circuit representation C of function f.

- Alice transforms the circuit to a garbled Circuit representation by garbling every gate.

- Alice sends Garbled Circuit and her key to Bob.

- Alice and Bob perform 1-out-of-2 OTs to receive Bob's key.

- Bob evaluates the Garbled Circuit and outputs the results.

### 1.2.2.1 Generate Garbled Boolean Circuit

To generate the garbled Boolean circuit Alice selects and associates k-bit-string random keys to each input and output wire and for each possible value. She generates the random keys  $k_x^0$ ,  $k_x^1$  for input wire x and  $k_y^0$ ,  $k_y^1$  for input wire y and  $k_z^0$ ,  $k_z^1$  for output wire z. She puts these random keys for each wire and make "Garbled Boolean Circuit". In this encrypt circuit, inputs and outputs of each gates are masked such that the parties cannot gain any information about input or intermediate result. This process is repeated for each gate composing the Boolean circuit. Encryption is important because it helps the outputs to look random and additionally prevents Bob from obtaining further information.

#### 1.2.2.2 Generate Garbled Truth Table

Alice also encrypts the truth table of the gate using those random keys and sends the garbled truth table to Bob. She should cooperate with Bob to know about actual output. An initial table for an XOR gate and resulting garbled truth table is shown below in Figure 1.4 and Table 1.1.

### 1.2.2.3 Sending Alice's Garbled Values

Once that Alice has generated the garbled circuit she needs to define her own input values to send to Bob, then Alice selects the appropriate input keys for the garbled

Figure 1.4: XOR gate with its corresponding wire keys.

| x y |                                                                             |

|-----|-----------------------------------------------------------------------------|

| 0 0 | $\mathbf{E}  k^{\theta}_{x} (\mathbf{E}  k^{\theta}_{y}  (k^{\theta}_{z}))$ |

| 0 1 | $\mathbf{E}  k^{0}_{x} (\mathbf{E}  k^{l}_{y} (k^{l}_{z}))$                 |

| 1 0 | $\mathbf{E}  k^{l}_{x} (\mathbf{E}  k^{\theta}_{y}  (k^{l}_{z}))$           |

| 1 1 | $\mathbf{E}  k^{I}_{x} (\mathbf{E}  k^{I}_{y} (k^{0}_{z}))$                 |

Table 1.1: Initial garbled circuit table for XOR gate  $% \left( {{{\mathbf{T}}_{{\mathbf{T}}}}_{{\mathbf{T}}}} \right)$

circuit GC. Alice sends to Bob all the keys corresponding to the values she owns for each gate. Following the previous example, if Alice's first input bit is 0, she needs to send the garbled representation  $k^{\theta}_{x}$ . This process is repeated for all Alice's input bits, generating Alice's garbled input values and sending them together with the garbled circuit GC to Bob.

### 1.2.2.4 Using OT for Bob's Input Values

Now Bob needs the keys corresponding to his input value. Alice knows the keys for each possible input value but she does not know Bob's choice of input values, therefore they engage in a 1-out-of-2 Oblivious Transfer (OT) protocol for each input value from Bob to decrypt the corresponding entries in the garbled truth table. Thus, Bob and Alice execute an OT once per each input wire. After performing OT as many times as needed, Bob ends with all the information that he needs to evaluate the circuit.

As mentioned before, the Oblivious Transfer protocol in Yao's construction, is exploited to transfer information between the two parties when evaluating the GBC. Specifically, all the inputs are encrypted and during the evaluation the output of each gate the decryption keys are exchanged, so that none of the two parties learns any information about the inputs of the other party. For each gate, an Oblivious Transfer (OT) protocol is run between the two parties so that the resulting output value can be computed without knowing the input value of the other party.

To see how "1-out-of-2" OT is used to compute the GC, let consider  $W_1$ , ...,  $W_{u_1}$  be the circuit input wires corresponding to input held by Alice, and let  $W_{u_{1+1}}$ , ...,  $W_{u_1+u_2}$  be the circuit input wires corresponding to input held by Bob. Then: (a) Alice sends to Bob the garbled values  $W_1^{x_1}$ , ...,  $W_{u_1}^{x_{u_1}}$ . (b)For every

$$i \in 1, .., u_2$$

Alice and Bob execute the 1-out-of-2 OT protocol, where Alice's input is  $(k_0^{u_{1+i}}, k_1^{u_{1+i}})$ , and Bob's input is yi. Bob now has the garbled tables and the garblings of all circuit's input wires. Bob evaluates the garbled circuit, and outputs f(x, y).

## 1.2.2.5 Evaluating the Garbled Circuit

Finally, Bob will determine the corresponding output key that he can share to Alice to find out what the actual outputs were. The important note is that Bob can share just a final output with Alice and she does not have any information about Bob's value or any intermediate values during the protocol, and Bob doesn't know the input values of Alice and the intermediate values of the computation, which are randomly chosen values.

# 1.3 Efficient GC-based Secure Multi-Party Computation (SMC)

The total Oblivious Transfer (OT) payload and GC protocol runtime increases linearly with the number of gates, and can be huge for complex GBCs. Accordingly, the efficient GC-based Secure Multi-Party Computation (SMC) protocol is of crucial importance. We will introduce Free XORs method for improving Garbled Circuit efficiency in §1.3.1.

## 1.3.1 Free-XOR Protocol

An optimization of the basic GC construction has been proposed by Kolesnikov et al.[37]. In the modified protocol the evaluation of XOR gates comes "for free", in the sense that they do not require any communication for the generation and the evaluation of the associated garbled table.

The basic idea for the circuit generator is to keep a global random bit string R such that for every wire only the label  $W^0$  (representing 0) needs to be randomly sampled while the label  $W^1$  (representing 1) is simply set to  $W^0 \oplus R$  for every binary XOR gate (with input wires subscripted with i, j and the output wire with k), the label representing 0 on the output wire is derived from xor-ing corresponding input labels, i.e.,

$$W_k{}^{\varrho} = W_i{}^{\varrho} \oplus W_j{}^{\varrho}.$$

The implementation of the XOR gate, we will follow step-by-step Kolesnikov's improvement [KS08] which works as follows.

## 1.3.1.1.Garbling

In the first step, Alice computes the garbled Boolean circuit (GBC) as follows:

1.a Randomly choose global key offset,

$$R \in {}_{\mathrm{R}} \{0, 1\}^{\mathrm{N}}$$

- 1.b For each input wire Wi of C:

- (a) Randomly choose a garbled value

$$w^{\theta}{}_{i} = <\!k^{\theta}{}_{i}, p^{\theta}{}_{i}\!> \in \{0,1\}^{\mathsf{N}+1} \quad (keyk \in \{0,1\}^{\mathsf{N}}, p \in \{0,1\})$$

(b) Set the other garbled output value

$$w^{i}_{i} = \langle k^{i}_{i}, p^{i}_{i} \rangle = k^{0}_{i} \oplus R, p^{0}_{i} \oplus 1$$

1.c For each gate G<sub>i</sub> of C in topological order

- (a) label G(i) with its index: label (Gi) = i

- (b) If  $G_i$  is an XOR-gate Wc = XOR(Wa, Wb) with garbled input values

$$\begin{split} w^{0}{}_{a} &= < k^{0}{}_{a}, p^{0}{}_{a} > \\ w^{0}{}_{b} &= < k^{0}{}_{b}, p^{0}{}_{b} > \\ w^{1}{}_{a} &= < k^{1}{}_{a}, p^{1}{}_{a} > \\ w^{1}{}_{b} &= < k^{1}{}_{b}, p^{1}{}_{b} > \end{split}$$

Set garbled output value

$$w^{\theta}{}_{c} = k^{\theta}{}_{a} \oplus k^{\theta}{}_{b}, p_{a} \oplus p_{b}$$

Set garbled output value  $w_{c}^{l} = k_{a}^{0} \oplus k_{b}^{0} \oplus R$ ,  $p_{a} \oplus p_{b} \oplus 1$ (c) If Gi is a 2-input gate Wc = gi(Wa, Wb) with garbled input values

$$w^{0}{}_{a} = \langle k^{0}{}_{a}, p^{0}{}_{a} \rangle$$

$$w^{0}{}_{b} = \langle k^{0}{}_{b}, p^{0}{}_{b} \rangle$$

$$w^{1}{}_{a} = \langle k^{1}{}_{a}, p^{1}{}_{a} \rangle$$

$$w^{1}{}_{b} = \langle k^{1}{}_{b}, p^{1}{}_{b} \rangle$$

Randomly choose garbled output value

$$w^{0}_{c} = \langle k^{0}_{c}, p^{0}_{c} \rangle \in {}_{\mathbf{R}} \{0, 1\}^{\mathbf{N}+1}$$

Set garbled output value

$$w^{1}_{c} = \langle k^{1}_{c}, p^{1}_{c} \rangle = k^{0}_{c} \oplus R, p^{0}_{c} \oplus 1$$

Create Gi's garbled table. For each of  $2^2$  possible combinations of Gi's input values

$$\begin{split} v_{\rm a}, v_{\rm b} \, \in \, \{0, 1\}, set \\ e_{v_{\rm a}, v_{\rm b}} &= \, H(k^{v_a}{}_a \parallel k^{v_b}{}_b \parallel {}_{\rm i}) \oplus \, W^{gi(va, vb)} \end{split}$$

Sort entries e in the table by the input pointers, i.e. place entry  $e_{va,vb}$  in position

$$< h^{p_{va}}{}_{a} , p^{va}{}_{b} >$$

1.d.For each circuit-output wire Wi(the output of gate Gj) with garblings

$$w^{\scriptscriptstyle 0}{}_i = <\!k^{\scriptscriptstyle 0}{}_i$$

,  $p^{\scriptscriptstyle 0}{}_i >, \, w^{\scriptscriptstyle 1}{}_i = <\!k^{\scriptscriptstyle 1}{}_i$  ,  $p^{\scriptscriptstyle 1}{}_i >$

(a) Create garbled output table for both possible wire values

$$v \in \{0,1\}.$$

(b) Set  $e_v = H(k_i^v \parallel "out" \parallel j) \oplus v$

(c) Sort entries e in the table by the input pointers, i.e.

place entry  $e_v$  in position  $p^v_i$ . There is no conflict, since

$$p^1{}_i = p^0{}_i \oplus 1.$$

In this first phase, Alice executes Kolesnikov's algorithm and uses the output of H, modeled as a Random Oracle [6], to encrypt the garbled output values in the garbled (Step 1.d(b)). Any combination of H's inputs (keys and gate indices) is used for the encryption of at most one table entry.

Alice sends the encrypted circuit to the other party, the garbled circuit evaluator (henceforth called *Bob*). When Bob receives the garbled circuit he only knows one garbled value per wire, and can decrypt exactly one entry of Gi's garbled table. All other entries are encrypted with at least one key that Bob does not have. Therefore, one of the two of garbled values of every wire looks random to him.

#### 1.3.1.2. Evaluating

We now discuss Kolesnikov's GC evaluation algorithm, run by Bob. Bob receives all garbled tables, but cannot execute the randomized circuit unless it has the input values to feed to it. Alice sends her inputs to Bob through the Oblivious Transfer protocol (OT)

# 1.4 Compiling Tools for Implementation of Two-Party Secure Computation Protocols

While the theoretical foundations of two-party Secure Computation have been considered in [78], interest in practical SMC systems is growing and different privacypreserving frameworks are being developed [63], [64]. So, recent implementation's tool show that SFE is ready to be used in practical applications. To make SMC usable by automatically generating protocols from high-level descriptions, several frameworks for SMC consisting of languages and corresponding tools have been developed in the last years. We review some of these tools, Fairplay (§1.4.1) and CBFS-MPC (§1.4.2) that are used in our thesis and SCAPI (§1.4.3), TASTY (§1.4.4) and ABY (§1.4.5).

### 1.4.1 FAIRPLAY

A number of well-established frameworks have been presented to translate the theoretical results of SMC protocol into practical applications. Fairplay<sup>1</sup> [43] was one of the first library published for synthesizing GC starting from the definition of the input function. It provides a method to compile given function in a high-level language into a low-level language as a circuit. Indeed, the framework includes a high-level Secure Function Definition Language (SFDL) for specifying the computed function. The definition is then compiled into a low-level description in form of a Boolean Circuit. The language used for describing the Boolean Circuit is called Secure Hardware Definition Language (SHDL). The corresponding Garbled Circuit (GC) is created from the Boolean Circuit and a garbled version of the input data is generated from the original input.

<sup>&</sup>lt;sup>1</sup>http://www.cs.huji.ac.il/project/Fairplay/

#### 1.4.1.1 Fairplay Syntax using Example

Let us consider as a simple example the SFDL description of a 2-bit Adder:

```

program Add {

typeint = Int 2;

typeAliceInput = int;

typeBobInput = int;

typeAliceOutput = int;

typeBobOutput = int;

type Output = struct AliceOutputalice, BobOutput bob;

type Input = struct AliceInputalice, BobInput bob;

```

```

function Output output(Input input) {

output.alice = (input.bob + input.alice);

output.bob = (input.bob + input.alice);

}

```

The compiler, having in input the SFDL program produces the following circuit in SHDL format:

```

0 input //output$input.bob$0

1 input //output$input.bob$1

2 input //output$input.alice$0

3 input //output$input.alice$1

4 gate arity 2 table [0 0 0 1] inputs [2 0]

5 output gate arity 2 table [0 1 1 0] inputs [2 0] //output$output.alice$0

6 gate arity 2 table [0 1 1 0] inputs [3 1]

7 output gate arity 2 table [0 1 1 0] inputs [4 6] /output$output.alice$1

8 output gate arity 1 table [0 1] inputs [5] //output$output.bob$0

9 output gate arity 1 table [0 1] inputs [7] //output$output.bob$1

```

Each line specifies a wire in the generated circuit and shows input bit or a Boolean gate with its truth-table, e.g. table [0 1 1 0] shows XOR gate, table [0 0 0 1] shows AND gate, table [0 1] shows NOT gate.

## 1.4.2 CBFS-MPC

<u>Circuits of Basic Functions Suitable</u> for <u>Multi-Party Computation</u> (CBFS-MPC)<sup>2</sup> is a tool developed by the Bristol cryptography group. This tool is a set of basic combinatorial circuits, which may be useful for testing binary-circuit based SMC and two-party computation. They use Cadence Encounter  $RTL^3$  compiler in conjunction with the Faraday FSA0A\_C 0.18 mm ASIC Standard Cell Library<sup>4</sup> for synthesis. The resulting circuit reports the number of AND, XOR and INV gates for each circuit design in a given format, where each line contains in order the number of input wires, number of output wires, list of input wires and list of output wires, and the gate type (XOR, AND, or INV). For example, 2 1 3 4 5 XOR means that w5 = XOR (w3,w4).

## 1.4.3 SCAPI

<u>Secure Computation API</u> (SCAPI)<sup>5</sup> [21] is an open-source Java library (also has a c++ version) for implementing secure two-party and multiparty computation protocols. The main advantages of this framework are *flexibility*, *extendibility*, *efficiency* and *ease of use*. Its *flexibility* means that protocols implemented using SCAPI can be easily changed and replaced because of using primitives and sub-protocols in an abstract way. *Extendibility* means that the design of SCAPI ensure that any new implementations of primitives and sub-protocols that are even more efficient can be utilized in all existing protocols even if they were previously implemented. SCAPI can achieve also *efficient* property by supporting of highly efficient low-level libraries using JNI. Finally, because of focusing on keeping SCAPI easy to build and use, it has property of "ease of use".

Libscapi is developed by *Bar Ilan University Cryptography Research Group* that try to promote investigate in Academy and Industry practitioners by providing e.g., high performance implementation on standard Linux and using modern techniques like Pipelining and TCP optimization and providing a common platform for bench-

$<sup>^{2}</sup> https://www.cs.bris.ac.uk/Research/CryptographySecurity/MPC/$

<sup>&</sup>lt;sup>3</sup>https://www.cadence.com/content/cadence/

<sup>&</sup>lt;sup>4</sup>http://freelibrary.faraday-tech.com

<sup>&</sup>lt;sup>5</sup>https://github.com/cryptobiu/libscapi

marking different algorithms and implementation.

#### 1.4.4 TASTY

<u>Tool for Automating Secure Two-partY computations</u> (TASTY) [32] is used for describing, generating and compiling efficient secure two-party computation protocols that can generate protocols based on Homomorphic Encryption (HE) [71] and Garbled Circuit (GC) as well as combinations of both. HE can perform efficient addition and multiplication functions, whereas GC is better for non-linear functionality such as comparison function. By combining both HE and GC, it can provide optimizations for practical secure two-party computation with low latency and allows to automatically generate efficient secure protocols for many privacy-preserving applications, e.g., face recognition and remote diagnostics.

## 1.4.5 ABY

$ABY^6$  is a framework for efficient mixed-protocol secure two-party computation based on <u>A</u>rithmetic sharing, <u>B</u>oolean sharing, and <u>Y</u>ao's garbled circuits. It can also provide highly efficient computation based on pre-computed *oblivious transfer extensions*<sup>7</sup> and combine protocols.

# 1.5 Related Work.

Several approaches have been considered in the last few years [55, 33, 41, 69, 38], for improving communication running time in two-party secure computation using garbled circuit (GC) protocol.

The proposed approach in 2009 by Benny Pinkas and Thomas Schneider [55], presents a number of optimisations which reduce the effective size of the circuit and size of the garbled table (GT) by 50 percent, which can result in improving the communication cost for transmitting the circuit between the parties. They modeled the underlying key derivations (KDFs) as correlation robust using the *Free-XOR* technique [37] (§1.3.1), which in this situation they are able to reduce the data needed

<sup>&</sup>lt;sup>6</sup>https://github.com/encryptogroup/ABY

<sup>&</sup>lt;sup>7</sup>https://github.com/encryptogroup/OTExtension

to be sent for the other gates by 25 percent. Indeed, using the *free*-XOR gates result in 3/4(1-p)N amount of data needed to be sent per circuit gate, where Ndenotes the amount of data needed to be sent for circuit in the Yao construction and P illustrates the proportion of XOR gates within a circuit. This approach provided the first secure two-party evaluation of the Advanced Encryption Standard (AES) circuit using Fairplay compiler [43] (§1.4.1), considered as a highly complex (around 30,000 AND and XOR gates) function (also with some potential applications), taking around 20 minutes to compute and requiring 160 circuits to obtain a  $2^{-40}$  cheating probability.

Another method with the aim of improving efficiency and scalability of garbled circuit was proposed in 2011 [33] that provides a flexible framework for faster secure two-party computation. In this approach, it is not necessary to generate and store the entire garbled circuit in memory and allows users to build and evaluate the circuit modularly. Therefore, very complex circuits can be evaluated, generated and debugged. Also, they could get improve in efficiency and scalability by pipelining the process of circuit generation and evaluation. Thus, this simple pipelining approach result in minimizing circuit size and scalability of the garbled circuit, has led to the development of several complex protocols that make evaluation faster than previous work. E.g., the total number of non-free XOR gates for the entire AES-128 computation was 9280 and the overall time was 0.2 seconds that was 16 times faster than the best previous results.

In 2012, Kreuter et al.[38] focused on parallel implementations design based on garbled circuits to be run on CPUs with many cores. Their proposed circuit consisting of about 6 billion gates; and they could implement running this on 512 cores of powerful cluster computer. They used better optimized circuit compiler than Fairplay and previous method [55]; with several new optimizations such as pipelining, which was suitable for more complicated circuits to reduce the computation time. The time to compute AES was reduced to 1.4 second per block, because of beginning transmission of the GC across the network, while the rest of the circuit is still being generated. Another research group in 2013 investigated on using consumer-grade *Graphics processing unit* (GPUs) to achieve similar levels of parallelism [28]. They used OT extension techniques [34, 3] to design their GPU-specific protocol and achieve comparable efficiency to the cluster computing implementation, which results in reducing the number of gates in implementation of the AES to 50,000.

The TinyGarble method is another method, introduced by Ebrahim M.Songhori and Ahmad-Reza Sadeghi et al. [69] in 2015. TinyGarble<sup>8</sup> illustrates a high degree of compactness and scalability while using a sequential circuit description for garbled circuit (GC) protocol. It can compress the memory footprint of garbling operation while resulting in fewer cache misses and less CPU cycles. TinyGarble introduced new techniques based on a sequential circuit for synthesizing and optimizing of garbled circuit (GC) protocol, which result in minimizing the number of non-XOR gates and improving computation and communication time. The most significant advantage of TinyGarble is describing the function in a compact format as a sequential logic instead of combinational format (i.e., user can compress the 1024-bit addition function into only a 1-bit adder). Also, the total number of gates using this method for the entire AES-128 computation was 2588 and number of non-XOR gates was 576, which is the best result until now. We can say that TinyGarble introduces the concept of sequential circuits that consist of circuits and loops, where at execution time the loops are unrolled resulting in a combinational circuit that is evaluated with Yao's garbled circuit protocol.

<sup>&</sup>lt;sup>8</sup>https://github.com/esonghori/TinyGarble

# Chapter 2

# Introduction to Quantum Gates

"When we get to the very, very small world (say circuits of seven atoms) we have a lot of new things that would happen that represent completely new opportunities for design. Atoms on a small scale behave like nothing on a large scale, for they satisfy the laws of quantum mechanics. So, as we go down and fiddle around with the atoms down there, we are working with different laws, and we can expect to do different things. We can manufacture in different ways. We can use, not just circuits, but some system involving the quantized energy levels, or the interactions of quantized spins." – Richard P. Feynman

This chapter consists of four sections. In the first section, we will discuss about some of the key aspects of quantum mechanics needed for quantum computation (§2.1). This section introduces the basic definitions and notations of quantum mechanics and their characteristics like quantum states and quantum bit (see §2.1.1 and §2.1.2). We will also give some feeling about mathematical formalisms needed to work with quantum computation. Quantum key distribution will be describe in §2.2 and section §2.3 gives the background on reversible and quantum circuits required for this dissertation. Following these sections, we have explained the simulation tool for the design of the quantum circuit in §2.4.

# 2.1 Quantum Mechanics

This section discusses how quantum mechanics can be used to perform computations and how these computations make a quantum computer different from a conventional computer. For more information about quantum mechanics, see [13, 23]. In the early 1980's [26], Richard Feynman observed that computation, in general, could be done more efficiently if we use quantum mechanical effects. Considering on basic principles of quantum mechanics help us to explain where the power of quantum computer comes from.

In quantum systems, because of the exponential increase in computational space and the number of processors, and hence an exponential increase in the amount of physical space needed, we can have an exponential decrease in the time required for computation, programming, and complexity. Therefore, in quantum systems, we can have an exponential increase in parallelism with the size of the system [16]. According to this characteristic, quantum computing is separated from conventional computing.

#### 2.1.1 Quantum State

In quantum computing, Information is encoded in the form of quantum states that are described in terms of vectors or in the more compact bra/ket notation  $|\rangle$  invented by Dirac [17].

#### 2.1.2 Quantum Bit (Qubit)

In classical computing, bit is the basic element used to store information, which can be in one of the two states of 0 or 1. In quantum computing, this basic element is called a *quantum bit (qubit)*. Qubit is denoted by Dirac notation, which is a unit vector in a two-dimensional complex vector space that indicated by  $\{|0\rangle, |1\rangle\}$ .  $|0\rangle$ and  $|1\rangle$  could correspond to the spin-up and spin-down states of an electron. In contrast to a classical bit, a qubit is able to be in two quantum states containing 0, 1 at the same time (often called *superposition*). The quantum state of a qubit as a superposition of the two quantum basis states  $|0\rangle$  and  $|1\rangle$  is shown in Equation 2.1.

$$|\psi\rangle = \alpha |0\rangle + \beta |1\rangle \tag{2.1}$$

$\alpha$  and  $\beta$  are complex numbers such that  $|\alpha|^2 + |\beta|^2 = 1$ . Superposition state is measured according to the basic {  $|0\rangle, |1\rangle$ }. The value  $|0\rangle$  is measured with a probability of  $|\alpha|^2$  and the result  $|1\rangle$  is obtained with a probability of  $|\beta|^2$ . As shown

Figure 2.1: The qubit state as a Bloch sphere presentation [62].

in Equation 2.2, each unit vector illustrates the state of qubit in a two-dimensional complex vector space [49, 62].

$$|\psi\rangle = \begin{pmatrix} \alpha \\ \beta \end{pmatrix}$$

,  $|0\rangle = \begin{pmatrix} 1 \\ 0 \end{pmatrix}$ ,  $|1\rangle = \begin{pmatrix} 0 \\ 1 \end{pmatrix}$  (2.2)

The state of a quantum bit (qubit) can also be a point on the surface of a sphere called Bloch sphere [49] as shown in Figure 2.1 and can also be written as shown in Equation 2.3.

$$|\psi\rangle = \cos\frac{\theta}{2} |0\rangle + e^{i\varphi} \sin\frac{\theta}{2}|1\rangle \tag{2.3}$$

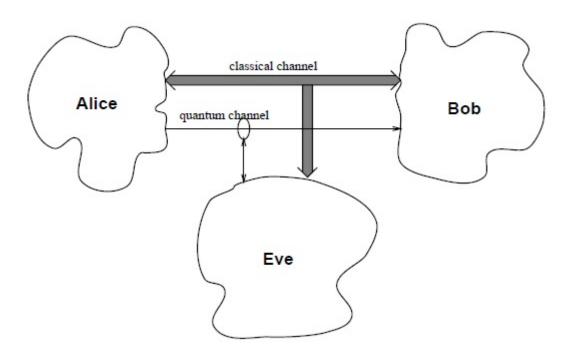

# 2.1.3 Quantum Key Distribution

In 1984, Bennet and Brassard [9, 8] considered the first quantum key distribution process, in which private keys on insecure channels can be transferred by sequences of single qubits.

Supposing that Alice and Bob want to agree on a secret key and communicate with each other privately. So, they are connected by the open classical channel and a uni-directional quantum channel that can be accessible by Eve, who wants to listen to their conversation. The process is illustrated Figure 2.2.

Figure 2.2: Quantum key distribution process [58].

Alice, through the quantum channel, sends photons to Bob, who can measure the quantum state. Eve also tries to measure the state of these photons and resend them to Bob. To establish a secret key, Alice sends a sequence of bits to Bob and encodes each bit in the quantum state of a photon that can be measured by Bob. Alice and Bob can identify those bits, which they have agreed for sending, receiving and using these bits as the key. The listener (Eve) can measure the state of this transmitted photon and resend new photons to Bob. Thus, Eve can use the wrong basis and resend the bit with this wrong basis. So, any listener on the quantum channel can use it for introducing a high error rate that Alice and Bob could detect by communicating their keys through the channel. Other proposed techniques for considering the quantum effects for key distribution have been introduced in [8, 22, 42].

# 2.2 Quantum Logic

One import fact is that quantum transformations are unitary and quantum gates inherently reversible. So, In this section at first, we have discussed about the reversibility property in designing quantum logics and quantum circuits. Finally, some common quantum(reversible) gates that are used in this thesis are introduced.

#### 2.2.1 Reversible Computing

In 1973 Bennet [7] showed that energy dissipation problem of VLSI circuits can be circumvented by using reversible logic.

Quantum logic gates are inherently reversible and quantum circuits are built based on reversible logic circuits. A reversible logic circuit is realized by a cascade of reversible gates. A gate that implements one to one mapping between n inputs and n outputs are called a  $n \times n$  reversible logic gate that can be represented as shown in Equation (2.4), where  $I_v$  and  $O_v$  are the input and output vector.

$$I_v = (x_1, x_2, x_3, \dots, x_n)$$

,  $O_v = (y_1, y_2, y_3, \dots, y_n)$  (2.4)

The reversible logic gate must have the same number of inputs and outputs, and for each input pattern there must be a unique output pattern [7]. Reversible logic circuits avoid energy loss by "un computing" the computed information using recycling the energy in the system [7].