# UML and MDA for Transactional Level Modeling

<u>S. Bocchio</u>, A. Rosti STMicroelectronics E. Riccobene, P. Scandurra University of Milan

brought to you by an arrowided by AIR Universita degli stud

# Outline

Introduction: motivation and objectives

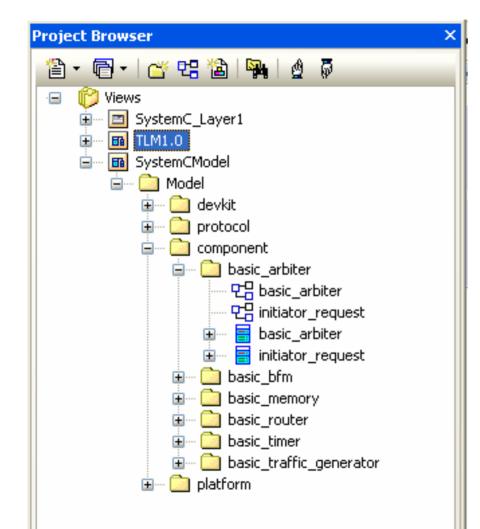

- Background: the SystemC UML profile and the tool for the UML/SystemC profile

- Update to SystemC2.1 and TLM

- **Examples**:

- Simple bus

- TLMinfra library and platform example

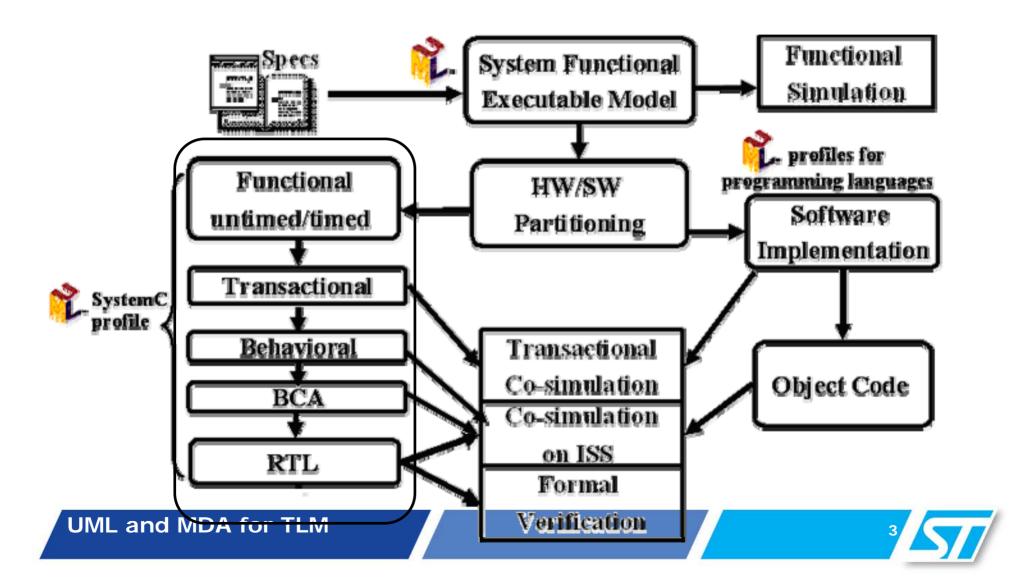

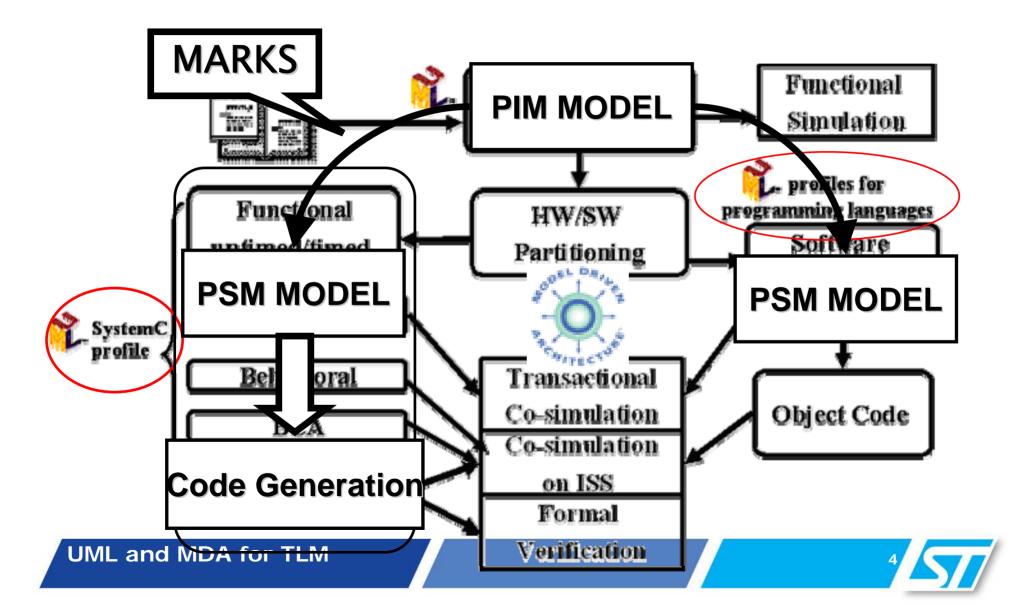

#### **MDA-SoC** design flow

#### **MDA-SoC** design flow

#### **Programming vs Modelling**

```

SC MODULE(producer){

sc outmaster<int> out1;

sc in<bool> start;

void generate_data(){

for(int i=0;i<10;i++)

out1 = i; // to invoke slave

SC_CTOR(producer){

SC_METHOD(generate_data);

sensitive<< start:

};

```

... and its model

**UML and MDA for TLM**

**SC MODULE**(consumer){ SC\_MODULE(top){ sc inslave<int> in1; sc\_link\_mp<int> link1; int sum; //state variable producer\* A1; void accumulate(){ consumer\* B1; sum +=in1; **SC CTOR**(top){ cout<<"Sum ="<< sum <<endl:</pre> A1 = new producer("A1"); A1.out1(link1); SC\_CTOR(consumer){ **B1** = new consumer("B1"); sum =0; //initialize **B1.in1(link1);** SC\_SLAVE(accumulate, in1); }; ì }; A bit of modern SW <sc\_prim\_channel> «sc\_module» link1\_sc\_link\_mp «sc\_module» A1: producer B1: consumer «sc\_port» «sc\_port» «sc\_port»

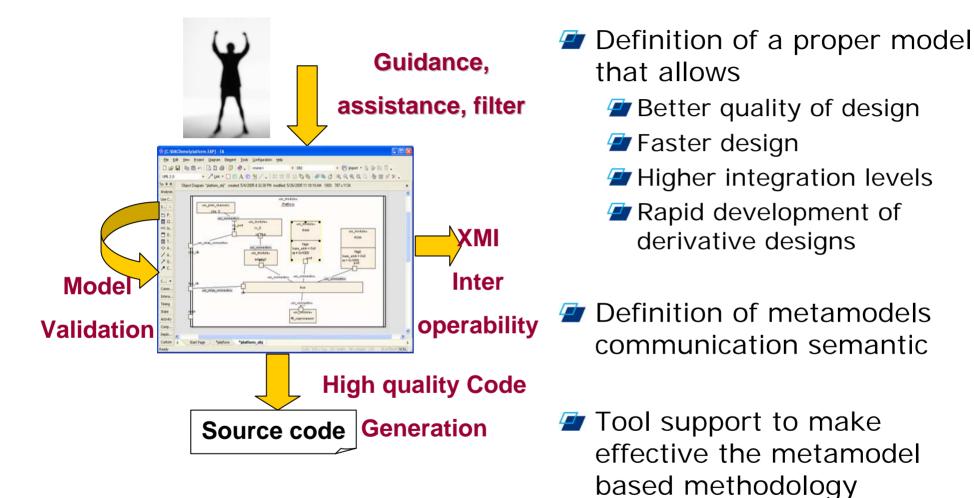

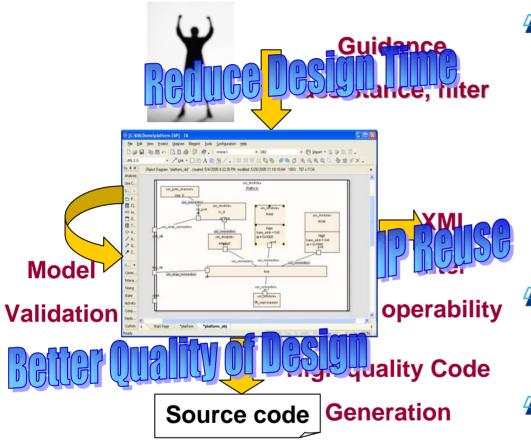

#### **MDA for SystemC-TLM**

### **MDA for SystemC-TLM**

- Definition of a proper model that allows

- Better quality of design

- 🖅 Faster design

- Higher integration levels

- Rapid development of derivative designs

- Definition of metamodels communication semantic

- Tool support to make effective the metamodel based methodology

#### **Does UML fit hw design?**

- SoC design = component based design

- Our view of an SoC design is defined by extensive use of reusable IP blocks, and mixed HW/SW design issues

- TLM methodology drives massive OO concepts usage in platform design

# UML PROFILE

A profile is a group of UML stereotypes, constraints, and tagged values that

- add domain-specific information to the UML

- possibly altering the notation (through special icons)

- A stereotype defines how a UML construct a class in the UML metamodel - is extended for a specific target domain

- with *tags* to state additional properties

- and constraints in the Object Constraint Language (OCL) to add some restrictions

- It can be intended as a way of creating a new dialect of the UML for a particular platform or domain

#### **Profile structure - updated**

- SystemC 2.1 profile structure

- 1. The SystemC core layer structure and communication (modules, interfaces, ports and channels)

- The SystemC core layer behavior and synchronization (method state machines)

- 3. The SystemC core layer data types defines a UML class library to represent the set of SystemC data types.

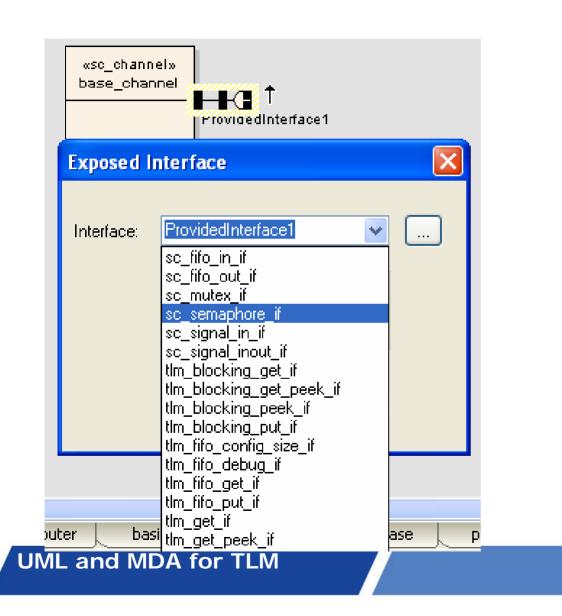

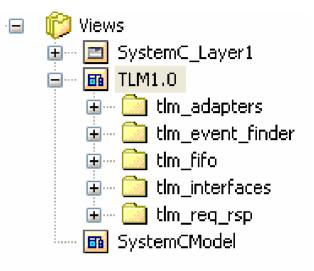

- 4. The SystemC layer of predefined channels, interfaces and ports

- 5. The OSCI TLM 1.0 library of predefined channels and interfaces.

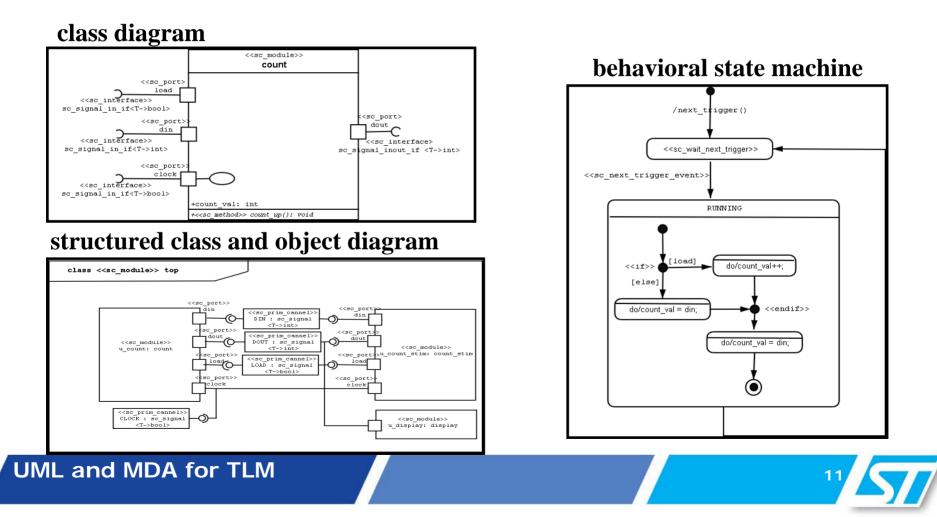

### **UML Profile for SystemC**

provides a **graphical entry** to SystemC stereotyped class, structured class and state machine diagrams

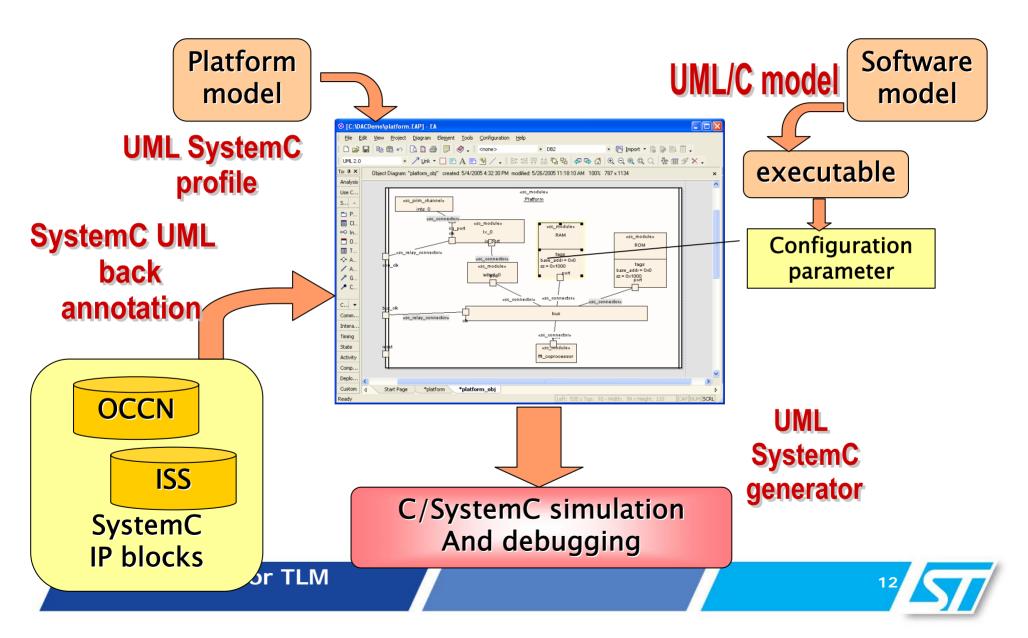

#### **EA Based framework for SystemC**

# SystemC code generator

|                                                            | Project Diagram            |           | HBC | ols <u>Configuration H</u> elp<br>Spell Check Model | Ctrl+F7        | ] | • 🕞 Import • 🕃 խ 🖺 🕅 .                          |             |

|------------------------------------------------------------|----------------------------|-----------|-----|-----------------------------------------------------|----------------|---|-------------------------------------------------|-------------|

| UML 2.0                                                    |                            |           | Ĩ   | Spell Check Current Package                         | Ctrl+Maiusc+F7 |   |                                                 |             |

|                                                            | ✓ Zink ✓                   |           |     | Spelling Language                                   |                |   |                                                 |             |

| Foolbox <b>P</b> ×                                         | Statechart Diagram: "exec" |           |     |                                                     |                | ^ | Project View                                    | д×          |

| Analysis                                                   |                            |           |     | Data Ma <u>n</u> agement                            | •              | ^ | 🖀 • 🖻 • 🖀 铝 🚵 🛼 🔬 🖗                             |             |

| Use Case                                                   |                            |           |     | Manage . <u>E</u> AP File                           | •              |   | i views<br>i SystemC_Layer1                     | <u>^</u>    |

| Structure                                                  |                            |           |     | <u>R</u> un Patch                                   |                |   | 😥 🗋 SystemCDataTypes                            |             |

| Composite                                                  |                            |           | -   | Export Reference Data                               |                |   | E      SystemCPredefinedChanne     SystemCModel | elsandPorts |

| Communication                                              |                            |           |     | Import Reference Data                               |                |   | 🖮 🧰 adder                                       |             |

| Interaction                                                |                            |           |     | Wordpad                                             |                |   | PB adder4                                       |             |

| Timing                                                     |                            |           |     | Windows Explorer                                    |                |   | P fulladder                                     |             |

| State 🔺                                                    |                            |           |     | SystemC                                             |                |   | 면 fulladder<br>만 halfadder                      |             |

| 🔿 State                                                    | T                          | Initial   |     |                                                     |                |   | <br>የርቅ or2<br>የርቅ xor2                         |             |

| 😔 Sub-Machine                                              |                            |           | 199 | Options                                             | Ctrl+F9        |   | 🖃 🖓 🔁 xorz                                      | _           |

| Initial                                                    | V                          |           |     | Customize                                           |                |   | 🖃 🧮 «sc_module» and2                            |             |

| Final     Running                                          |                            |           |     |                                                     |                |   | 😟 🐨 🧮 «sc_module» fulladder                     |             |

| History                                                    | + Do Action / I            | read ar   | t   |                                                     |                |   |                                                 | -1          |

| Synch                                                      | o = a.read                 |           |     | )                                                   |                |   | 🖃 🧧 «sc_module» xor2                            |             |

| Choice                                                     | A                          |           | _   |                                                     |                |   | exec                                            | >           |

| Junction                                                   | 1                          |           |     |                                                     |                |   | Project View Scresource View                    |             |

| • canoton                                                  |                            |           |     |                                                     |                |   |                                                 |             |

| Activity 🔹                                                 |                            | V         |     | ~                                                   |                |   | Tagged Values                                   | д×          |

| Component ( wait_next_trigger»<br>Waiting for next trigger |                            |           |     |                                                     |                |   |                                                 |             |

| Deployment                                                 | waiting for n              | ext trigg | jer |                                                     |                |   | ■ SystemCModel (Package)                        | ~           |

| Custom                                                     | <                          |           |     |                                                     | >              | ~ |                                                 |             |

| Profile                                                    | 4 Start Page               | *ея       | ec  |                                                     |                | Þ | 🔗 Instan   🗞 Proper   📑 Notes                   | °⊚Tagge     |

|                                                            |                            | ~         |     | ·                                                   |                |   |                                                 |             |

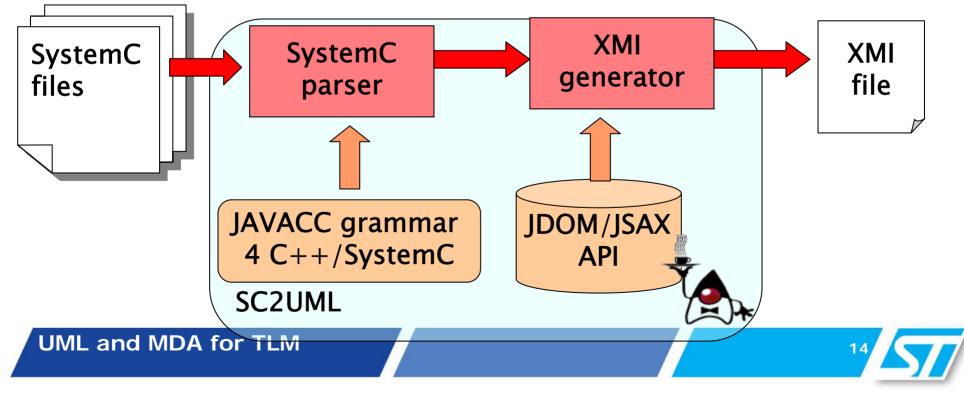

### SystemC back annotation

- import existing SystemC models into UML

- SystemC back annotation = SystemC parser + XMI generator

- EA selecting Project | Import/Export | Import package from XMI file..

#### SystemC 2.1: new features

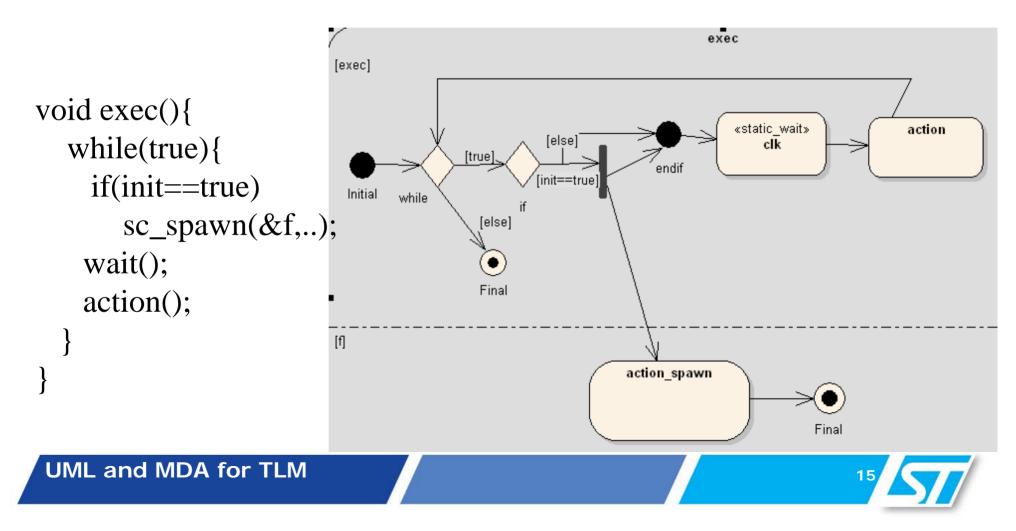

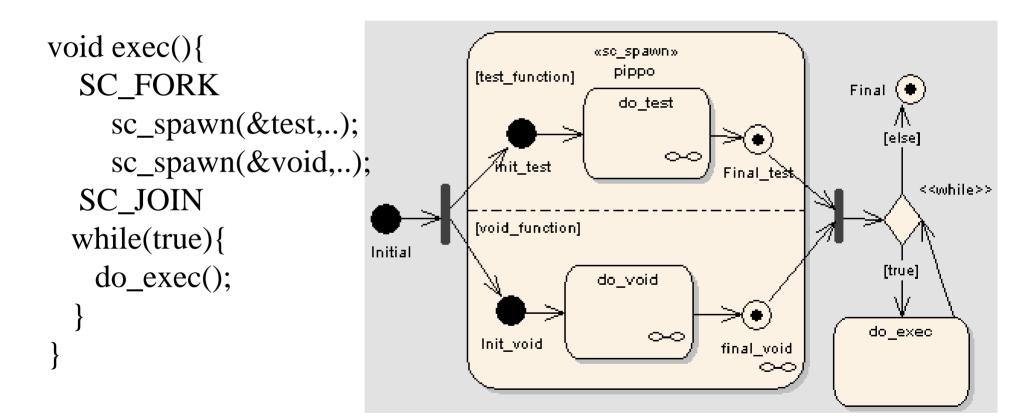

# Sc\_exportDynamic thread

#### systemC 2.1 new features

SC\_FORK, SC\_JOIN

# What is TLM?

Modeling communication through function calls

Based on the concept of interfaces

But can be accurate from the Timing perspective

Implemented by channels exposing interfaces.

Also gain simulation speed because communication is not pin accurate

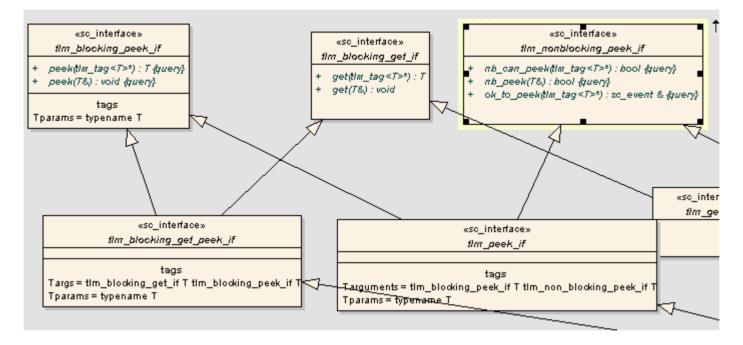

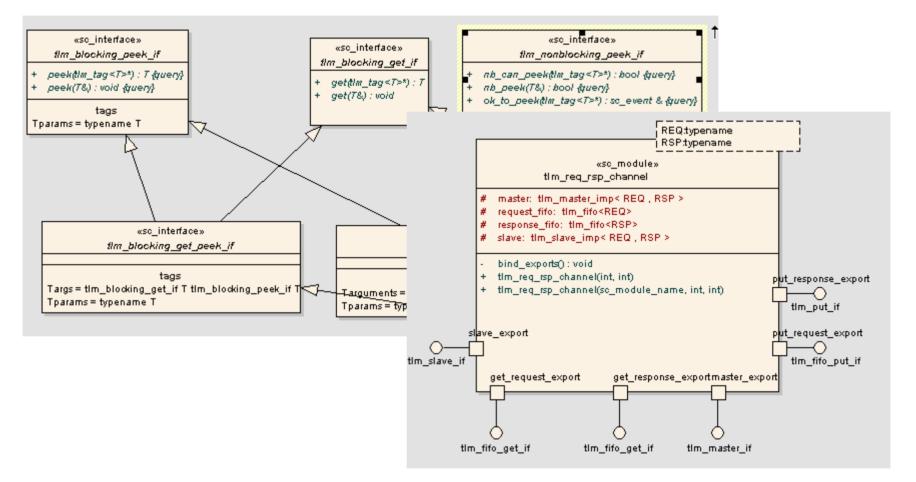

# **OSCI TLM 1.0 Standard**

- TML was possible since SystemC 2.0

- Lack of standard library and methodologies can lead to incompatibilities

- OSCI TLM standard set of API for communication

- Unidirectional blocking and non blocking

- put(.), get(.), peek(.)

- Bidirectional blocking interface

- /// Implemented by tlm\_transport\_channel<REQ,RSP>

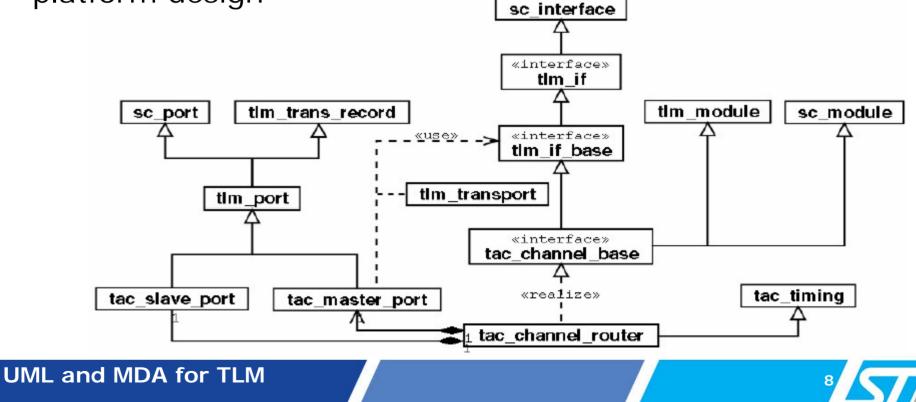

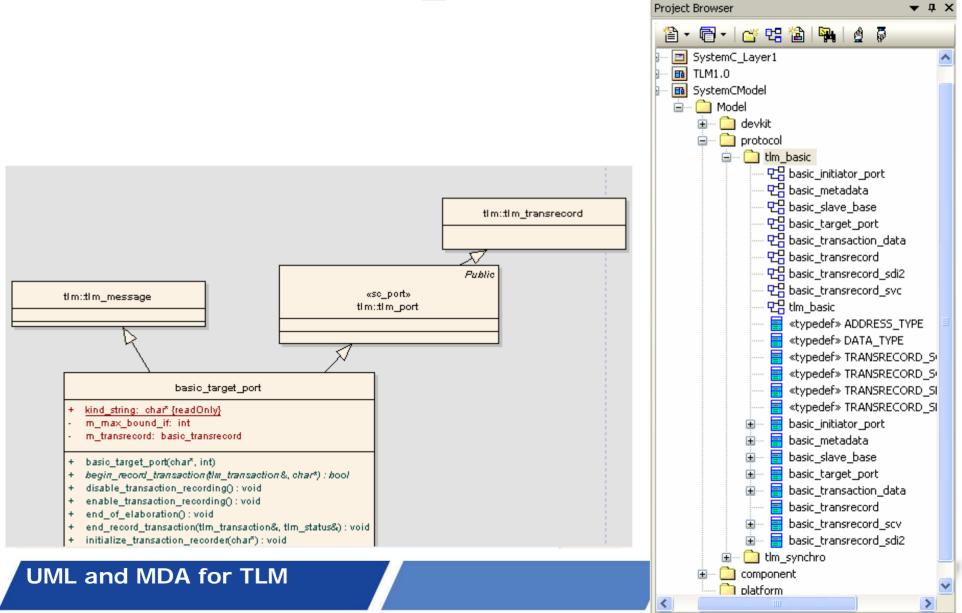

# **OSCI TLM library in UML**

#### A set of model..

# **OSCI TLM library in UML**

#### A set of model..

# **OSCI TLM 1.0 library**

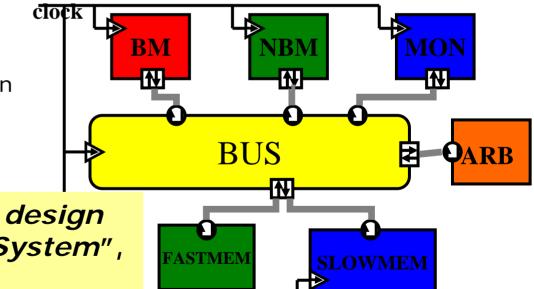

# The Simple Bus (transactional level)

- M1 uses the blocking master interface (a high level software)

- M2 uses the non blocking master interface (a processor executing on every clock)

edge even if its bus transactions are not completed)

- M3 uses the *direct master interface* to print debug information about memories

- S1, S2 provide the same interface

- S1 is a fast memory supporting single-cycle read/write operations

- S2 is a slow memory that takes n cycles per each read/write operation

S. Bocchio... "A model driven design Environment for Embedded System", DAC '06

#### ST TLM\_infra library

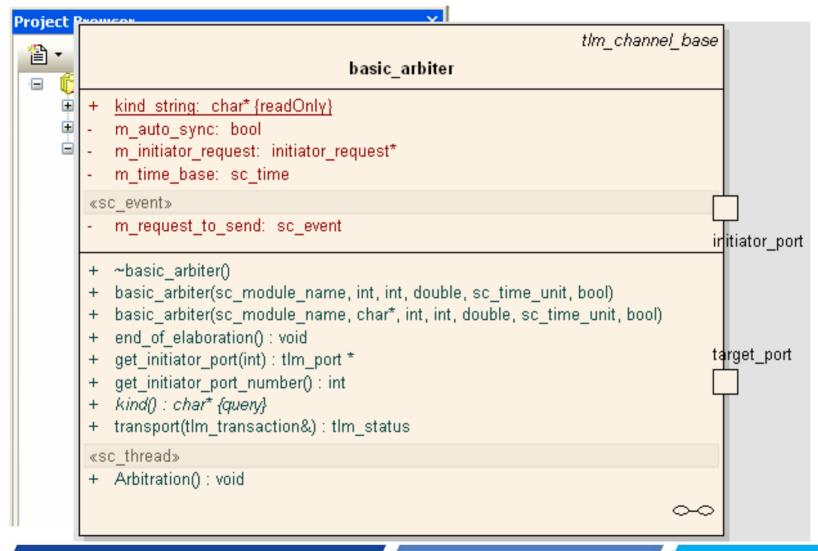

#### The arbiter

#### The arbiter

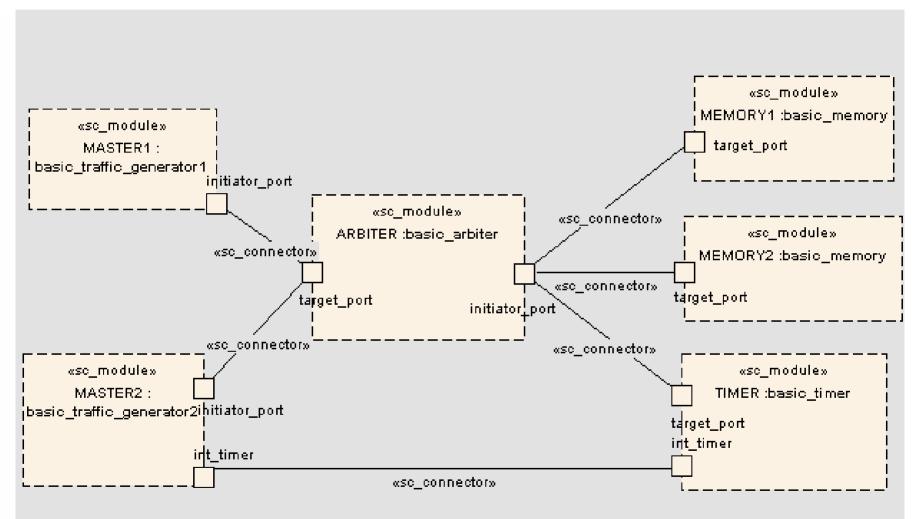

# The platform (class diagram)

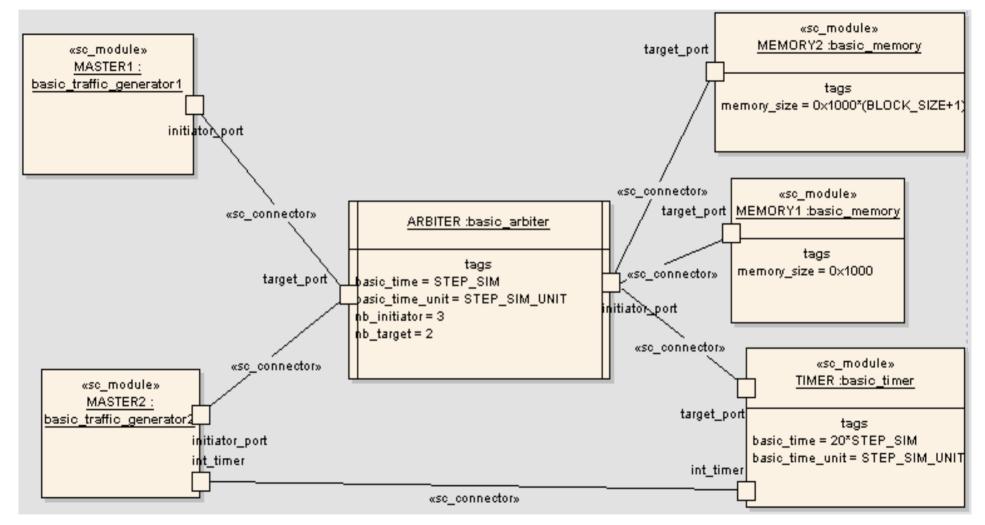

# The platform instance (object diagram)

#### Conclusion

UML profile make simpler platform building

UML is NOT just a way to have a composition tool!

Code generation

- System view

- Model validation...