# UCC Library and UCC researchers have made this item openly available. Please let us know how this has helped you. Thanks!

| Title                          | Behavioral modeling of SAR ADCs in Simulink                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Author(s)                      | Molina Salgado, Gerardo; Dicataldo, Alberto; O'Hare, Daniel;<br>O'Connell, Ivan; de la Rosa, José M.                                                                                                                                                                                                                                                                                                            |  |

| Publication date               | 2018-05-04                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Original citation              | Molina Salgado, G., Dicataldo, A., O'Hare, D., O'Connell, I. and de la<br>Rosa, J. M. (2018) 'Behavioral modeling of SAR ADCs in Simulink',<br>2018 IEEE International Symposium on Circuits and Systems (ISCAS),<br>Florence, Italy, 27-30 May, pp. 1-5. doi:10.1109/ISCAS.2018.8351056                                                                                                                        |  |

| Type of publication            | Conference item                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Link to publisher's<br>version | https://ieeexplore.ieee.org/document/8351056<br>http://dx.doi.org/10.1109/ISCAS.2018.8351056<br>Access to the full text of the published version may require a<br>subscription.                                                                                                                                                                                                                                 |  |

| Rights                         | © 2018, IEEE. Personal use of this material is permitted. Permission<br>from IEEE must be obtained for all other uses, in any current or<br>future media, including reprinting/republishing this material for<br>advertising or promotional purposes, creating new collective works,<br>for resale or redistribution to servers or lists, or reuse of any<br>copyrighted component of this work in other works. |  |

| Item downloaded<br>from        | http://hdl.handle.net/10468/7460                                                                                                                                                                                                                                                                                                                                                                                |  |

Downloaded on 2021-11-27T08:36:49Z

Coláiste na hOllscoile Corcaigh

# **Behavioral Modeling of SAR ADCs in SIMULINK**

Gerardo Molina Salgado, Alberto Dicataldo, Daniel O'Hare, and Ivan O'Connell Microelectronics Circuit Centre Ireland, MCCI Tyndall National Institute Cork, Ireland gerardo.salgado@tyndall.ie

This paper presents a toolbox for the behavioral simulation of SAR ADCs in Simulink<sup>®</sup>. The models include the most limiting circuit effects such as sampled thermal noise, capacitor mismatch, finite settling, comparator noise and offset. A user friendly interface is also included to allow study and high-level design of SAR ADCs, which is illustrated by means of a design example. It is also shown that the proposed toolbox is several orders of magnitude faster than electrical simulators, while keeping a high accuracy.

Keywords— Analog-to-Digital Converters, SAR, Behavioral Modeling and Simulation.

# I. INTRODUCTION

In recent years Successive-Approximation-Register (SAR) Analog-to-Digital-Converters (ADCs) have become the dominant low power ADC architecture [1]. Time Interleaved (TI) ADCs using SAR channels have also become the best performing ADCs at high frequencies with sampling frequencies up-to 90GS/s being reported [2]. The key building blocks of SAR ADCs are the capacitors, switches, state machines, and comparator latches. All of these blocks improve with CMOS process scaling leading to ADCs with lower power and faster speeds. The digital CMOS nature of these building blocks means SAR ADCs have minimal static power consumption and the ADC power consumption is proportional to the ADC conversion rate. As a sub-ADC advances in SARs have also enabled Hybrid ADCs with substantially lower power consumption than Flash based ADCs [3].

In spite of the above mentioned benefits, the efficient design of SAR ADCs requires using a suitable design methodology and CAD tools in order to maximize their performance with the minimum power dissipation. Simulation is a key tool supporting the design automation at different levels of the synthesis and verification flow. It is a common practice that SAR ADCs are simulated in electrical simulators with mixed-mode capabilities, like CADENCE® AMS-simulator. However, some important analog circuit limitations such as capacitor mismatch, finite settling time, and comparator noise, have forced the introduction of compensation techniques like calibration [4], redundancy [5], majority voting [6], noise-shaping [7], among others. These techniques are mostly implemented in the digital domain requiring extra conversion cycles, which might lead to long simulation times even at early stages of the design. José M. de la Rosa Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC/Universidad de Sevilla) C/Américo Vespucio, 41092 Seville, Spain jrosa@imse-cnm.csic.es

A well-known alternative simulation approach is based on the so-called behavioral modeling technique, which has been previously applied to other kinds of ADCs, such as  $\Delta\Sigma$  ADCs [8]-[9]. This approach essentially consists of emulating device and physical effects at a higher abstraction level, so that the simulation time can be drastically reduced in several orders of magnitude, while keeping a high accuracy compared to electrical simulation. However, to the best of the authors' knowledge, little work has been done in the behavioral modelling and simulation of SAR ADCs.

This paper contributes to this topic and presents a toolbox for the behavioral modeling and simulation of SAR ADCs in the MATLAB/Simulink® environment. The toolbox enables the simulation of SAR ADCs with two different Capacitive Digitalto-Analog Converter (CDAC) topologies by including their main circuit error mechanisms with a high level of accuracy and reduced CPU time as compared to electrical simulations. Additionally, a design example is presented to show the high capabilities and robustness of the proposed toolbox to quickly validate compensation techniques.

Following this introduction, the paper is organized as follows. Section II presents the proposed modeling of SAR ADCs, describing the behavioral models for the digital engine, CDAC and comparator. Section III gives an overview of the presented toolbox, which includes a Graphical-User-Interface (GUI) developed to guide designers through the different steps of the simulation. Section IV shows the high-level design flow of a 12-bit SAR, highlighting the capabilities of the toolbox. Finally, conclusions are drawn in Section V.

# II. BEHAVIORAL MODELLING OF SAR ADCS

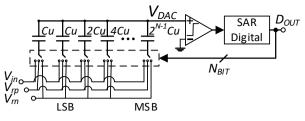

The working principle of SAR ADCs follows a successive digital approximation of the analog input voltage. To illustrate this process, consider the SAR ADC schematic shown in Fig. 1, which uses binary weighted CDAC, bottom plate sampling and unit capacitor  $c_u$ . The SAR-digital block is a state machine that controls all the conversion process. The first state is dedicated to the sampling of the incoming signal  $V_{in}$  onto the CDAC. In the second state, the SAR-digital connects the MSB-capacitor bottom plate to the positive reference,  $V_{rp}$ , and the remaining

This work was funded by Microelectronic Circuits Centre Ireland, MCCI.

Fig. 1. SAR ADC Schematic.

capacitors to the negative reference,  $V_{rn}$ , and due to charge redistribution the  $V_{DAC}$  node converges to  $-V_{in} + (V_{rp} - V_{rn})/2$ . Before the second state ends, the comparator makes a decision whether  $V_{DAC}$  is above or below ground, setting the MSB-bit to '0' or '1', respectively. In the third state the bit trial process is repeated with the MSB<sub>-1</sub>-capacitor, i.e. connecting it to  $V_{rp}$ , where  $V_{DAC}$  node now converges to  $-V_{in} + (V_{rp} - V_{rn})/4$ . The process continues through *N*-states for an *N*-bit ADC.

#### A. SAR-Digital engine

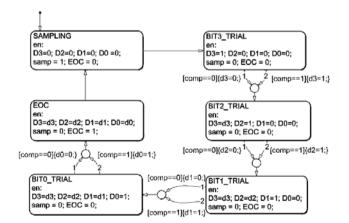

The SAR-digital engine can be easily modelled in the Stateflow® environment, where state machines are implemented with state transition diagrams and/or transition tables [10]. Fig. 2 illustrates the state transition diagram for a 4bit SAR-digital (single-ended). The first state activates the sampling signal. In the second state the sampling signal is deactivated and D3 (MSB) is set to logic '1'. In the third state, D3 takes the value provided by the comparator ('0' or '1') and at the same time D2 is set to '1'. The process continues until the sixth state is reached, where the end-of-conversion (EOC) signal is activated. The resulting SAR-digital block can be used in Simulink® as a clock triggered unit, making possible the implementation of synchronous SAR ADCs. Note that a synthesizable Verilog/VHDL code can be also generated from the state transition diagram with the HDL-Coder [11].

### B. Capacitive-DAC

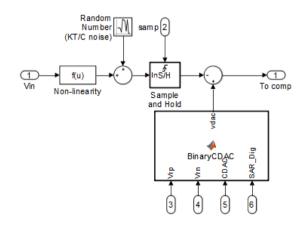

The sampling control-signal generated by the SAR-digital can be used to trigger a sample and hold block and store the analogue input signal, as it is illustrated in Fig. 3. Real sampling networks introduce non-linear distortion and thermal noise [12]. The distortion is modelled with the general function block, which implements a polynomial expression of the form:

Fig. 2. State transition diagram of a 4-bit SAR-digital.

$f(x) = a_1 \cdot x^1 + a_2 \cdot x^2 + \dots a_i \cdot x^i$ , where  $a_i$  corresponds to the *i-th* distortion term. On the other hand, thermal noise is originated due to random electron movement, so it can be modeled with a random number generator. It is assumed a normal distribution with zero mean value and a standard deviation given by the square-root of the well-known kT/C expression [12].

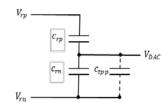

During the bit trials, different equivalent circuits around the  $V_{DAC}$  node are found. The general schematic shown in Fig. 4 provides a way to calculate the  $V_{DAC}$  node voltage as a function of the parallel-equivalent number of  $c_u$  connected to either  $v_{rp}$  or  $v_{rn}$ ,  $c_{rp}$  and  $c_{rn}$ , respectively. Additionally, it can take into account parasitic capacitances associated to the top-plates,  $c_{tpp}$ , as described by:

$$V_{DAC} = \frac{c_{rp}}{c_{rp} + (c_{rn} + c_{tpp})} \cdot (V_{rp} - V_{rn}).$$

(1)

Equation (1) can be implemented as a triggered MATLAB® function, where dynamic memory allocation can be used to make it configurable for any given number of bits. The bridge/split CDAC topology [4], also included in the presented toolbox, is modeled in a similar fashion.

To model process variations, every  $c_u$  is expressed as a normalized nominal value, i.e. 2, 4, 8 to  $2^{N \cdot I}$ , plus a given percentage deviation  $\sigma_{cu}$ . The deviation is a sample taken from an independent random number generator with a normal distribution and zero mean value.

Routing and finite on-switch resistance introduce *RC* time constants in the CDAC, leading to settling errors at the  $V_{DAC}$  output node. This limitation can be modelled as the step response of a first order RC circuit:

$$V_{DAC-st}(t) = V_{DAC} \cdot \left(1 - e^{-\frac{t}{\tau}}\right), \tag{2}$$

where  $\tau$  is the *RC* time constant. Equation (2) can be implemented with the Simulink block diagram shown in Fig. 5, where the error term is applied only to the current bit trial, i.e. assuming full settling from the previous state. The latter is a valid assumption given that CDAC continues its settling even during the comparator decision.

Fig. 3. Simulink CDAC Modeling.

Fig. 4. Equivalent schematic for  $V_{DAC}$  generation.

Fig. 5. CDAC finite settling modelling.

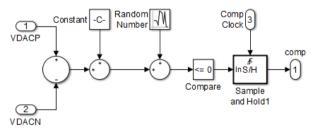

# C. Comparator

Comparators implemented in SAR ADCs are typically made up of a high gain differential pair and a latch stage that stores the decision at the rising/falling edge of the clock signal. Fig. 6 illustrates the behavioral model of a fully differential comparator that emulates this circuit topology.  $V_{DAC-N}$  is subtracted from  $V_{DAC-P}$  and any possible DC-offset is modelled by the addition of a constant term, while the comparator input-referred noise is once again modelled by a random number generator. The compare block outputs '1' if its input is equal or lower than 0, and '0' otherwise. The latch effect is modeled with the sample and hold block.

### III. PROPOSED SAR ADC TOOLBOX

A fully-differential SAR ADC model, built from the SARdigital, CDAC and comparator models, explained in the last section, can be downloaded from [13]<sup>1</sup>. The full model is accompanied by a GUI, in order to facilitate the study/design of SAR ADCs. The GUI, depicted in Fig. 7, allows the user to perform different ADC parametric analysis and to characterize main performance metrics such as DNL/INL, SNDR and ENOB. General ADC parameters such as, resolution, sampling frequency, input frequency and supply voltage, can be quickly set in the general parameters box. Under the CDAC parameters, the user can set the value for the sampling capacitor, mismatch, finite settling time, non-linear distortion term, and choose between binary or bridge CDAC. A dedicated comparator section allows users to set DC-offset and input referred noise, in LSB units. Additionally, the majority voting compensation technique described in [6] is also included, where the user can select the desired number of extra votes for the LSB<sub>-1</sub> and LSB.

Fig. 6. Fully differential comparator model.

<sup>1</sup>The toolbox download link was not ready at the submission time. However, a copy of this can be requested to the main author.

| General Para                                    | ameters                |                                       |

|-------------------------------------------------|------------------------|---------------------------------------|

| ADC                                             | Input Sinewave         |                                       |

| ADC Resolution [Nbit] 12                        | 0.1 Frequency [MH      | z] Parametric Simulation              |

| ADC Supply Voltage [V] 1                        | 0.45 Amplitude [V]     | Activate                              |

| Sampling Frequency [MS/s] 1                     | 0.5 Offset [V]         | <ul> <li>Total Capacitance</li> </ul> |

|                                                 |                        | <ul> <li>Unit Cap Mismatch</li> </ul> |

| Compara                                         | ~~~ O Settling Time    |                                       |

| Parameters                                      | Majority Vote          | <ul> <li>Majority Vote</li> </ul>     |

| Thermal Noise [LSB] 1                           | Activate Majority Vote |                                       |

| Comparator Offset [LSB]                         | Number of votes 3      | Start Step Stop                       |

| CDAC                                            | EN                     | IOB DNL/INL                           |

| Binary Weighted     Image Cap                   |                        | Number of Conversions [2^] 14         |

| Total Capacitance [pF] 1 Sampling Non-linearity |                        | SNDR [dB] 0                           |

| Unit Cap Mismatch [%] 0 2nd Term 0              |                        |                                       |

| Settling Time [rau] Inf 3r                      | rd Term 0              | ENOB [bit] 0                          |

Fig. 7. Proposed toolbox' GUI.

The GUI source-code and Simulink models included in the toolbox can be easily modified to model additional features, e.g. the quantization error at the end of the conversion can be easily integrated and used as a comparator offset for the next conversion cycle, achieving the so-called noise shaping property [9]. Similarly, the full SAR ADC block can be easily used as the basic building block in time-interleaved ADCs, and/or hybrid architectures.

# IV. DESIGN EXAMPLE AND PERFORMANCE COMPARISON

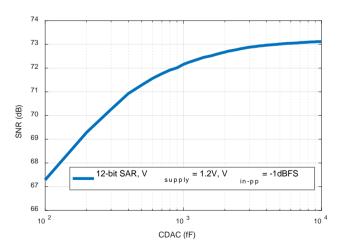

Consider the design of a 1.2V, 12-bit SAR. The high-level design flow is as follows. The first step is to identify the CDAC value necessary to achieve the targeted 73dB Signal-to-Noise-Ratio (SNR) at 1.2V supply. To this end, Fig. 8 shows the GUI results for the parametric analysis of CDAC, where it can be seen that 1pF represents a good trade-off between the target resolution and CDAC size.

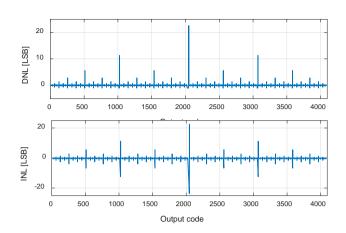

The second step would be the analysis of the impact of the settling time over the DNL/INL metrics. As an illustration, Fig. 9 shows an extreme case where the time allocated for the settling

Fig. 8. CDAC parametric simulation.

is just 4.5 $\tau$ , note that a larger error is introduced in the MSB transition, which reduces towards the LSB. A separate parametric analysis can be performed to identify the minimum number of RC time constants necessary to achieve a given DNL/INL, which is around 9 $\tau$  for ±0.5LSB.

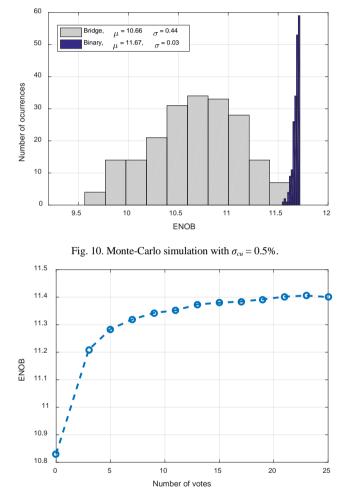

The third step in the design would be the mismatch sensitivity analysis trough Monte-Carlo simulations. To this end, it is first necessary to take a look at the targeted Process-Design-Kit (PDK) in order to identify the expected mismatch in the process. Fig. 10 shows a 200-run simulation considering  $\sigma_{cu} = 0.5\%$  for both the binary weighted and the bridge CDAC. It is clear that the bridge CDAC shows higher sensitivity to process variations and must not be used unless lower mismatch is guaranteed. At this point an iterative process with the total size of the CDAC and  $\sigma_{cu}$  would start.

The final step is the analysis of the impact of the comparator noise, where a parametric analysis could be carried-out. However, at circuit-level, comparator noise is highly constrained by its power consumption budget. As an initial assumption the high-level designer can consider 1LSB as the comparator noise, and then reduce is noise figure using majority voting. As an illustration, Fig. 11 shows the parametric analysis for the number of extra votes, considering 1LSB of comparator noise. It can be seen that 5 votes represent a good trade-off between resolution and extra conversion states.

In summary, the designed 1.2V, 12-bit SAR ADC would need a 1pF binary CDAC,  $\sigma_{cu} = 0.5\%$ ,  $9\tau$  settling time allocation, 1LSB of comparator noise and 5 votes in the LSB.<sub>1</sub> and LSB to achieve an effective resolution of 11.3bits.

# A. Simulation time performance

In order to illustrate the simulation advantages of the proposed toolbox, the previously designed 12-bit SAR is simulated during 1024 conversion steps. A DELL PowerEdge C6145 running Linux Red Hat Enterprise Server 6.6 is used as the test hardware platform. Although it has multi-core capabilities, it has been software-limited to run in single-core. The toolbox runs in Matlab® 2016(b) and takes only 4s to complete the simulation. On the other hand, the equivalent transistor-level simulation in CADENCE® VIRTUOSO® IC6.17, with AMS-Simulator and SAR-Digital in Verilog, reports an elapsed simulation time in excess of 167ks (1d 22h 19m). The simulated SNR is the same in both cases, meaning that the proposed toolbox is 41750x times faster than the electrical simulator, while maintaining the same precision. Moreover, the schematic entry in the circuit simulator could take several days starting from scratch, while in the toolbox everything is implemented and ready to run.

# V. CONCLUSIONS

A toolbox for the behavioral modeling and simulation of SAR ADCs in MATLAB/Simulink® has been presented. The effects of main building-block circuit nonidealities are included in the models, thus allowing to simulate SAR ADCs at system level with an accuracy comparable with electrical simulations. Moreover, the presented toolbox benefits from their implementation in MATLAB in terms of user-friendly signal processing capabilities and interface with circuit-design platforms.

Fig. 9. DNL/INL plot with settling time allocation of 4.57.

Fig. 11. Majority voting compensation.

### REFERENCES

- B. Murmann, "The successive approximation register ADC: a versatile building block for ultra-low-power to ultra-high-speed applications," *IEEE Communications Magazine*, vol. 54, pp. 78-83, 2016.

- [2] L. Kull, T. Toifl, M. Schmatz, P. A. Francese, C. Menolfi, M. Braendli, et al., "22.1 A 90GS/s 8b 667mW 64× interleaved SAR ADC in 32nm

digital SOI CMOS," in 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 378-379.

- [3] J.M.de la Rosa, R.Schreier, K.-P.Pun, and S.Pavan: "Next-Generation Delta-Sigma Converters: Trends and Perspectives," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 5, pp. 484– 499, December 2015.

- [4] J. Y. Um, Y. J. Kim, E. W. Song, J. Y. Sim and H. J. Park, "A Digital-Domain Calibration of Split-Capacitor DAC for a Differential SAR ADC Without Additional Analog Circuits," in *IEEE Transactions on Circuits* and Systems I: Regular Papers, vol. 60, no. 11, pp. 2845-2856, Nov. 2013.

- [5] J. H. Tsai et al., "A 0.003 mm<sup>2</sup> 10 b 240 MS/s 0.7 mW SAR ADC in 28 nm CMOS With Digital Error Correction and Correlated-Reversed Switching," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 6, pp. 1382-1398, June 2015.

- [6] M. Ahmadi and W. Namgoong, "Comparator Power Reduction in Low-Frequency SAR ADC Using Optimized Vote Allocation," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 11, pp. 2384-2394, Nov. 2015.

- [7] J. Fredenburg and M. Flynn, "A 90MS/s 11MHz bandwidth 62dB SNDR noise-shaping SAR ADC," in 2012 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 468-470.

- [8] J. Ruiz-Amaya et al., "High-Level Synthesis of Switched-Capacitor, Switched-Current and Continuous-Time ΣΔ Modulators Using SIMULINK-based Time-Domain Behavioral Models," *IEEE Trans. on* Circuits and Systems – I: Regular Papers, vol. 51, pp. 1795–1810, September 2005.

- [9] P. Malcovati et al., "Behavioral modeling of switched-capacitor sigmadelta modulators," *IEEE Trans. on Circuits and Systems – I: Regular Papers*, vol. 50, pp. 352–364, March 2003.

- [10] Mathworks, "Stateflow', available on line at: https://uk.mathworks.com/products/stateflow.html

- [11] Mathworks, "HDL-Coder", available on line at: https://uk.mathworks.com/products/hdl-coder.html

- [12] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw Hill, 2001.

- [13] G. M. Salgado and A. Dicataldo, "SIMSAR toolbox", available online at: www.mcci.ie.