#### João Pedro Castro da Rocha de Meneses Alarção

Licenciado em Ciências de Engenharia Eletrotécnica e de Computadores

# Design of a Multi-sensor and Re-configurable Smart Node for the IoT

Dissertação para obtenção do Grau de Mestre em Engenharia Eletrotécnica e de Computadores

Orientador: João Pedro Oliveira, Prof. Doutor, Universidade Nova de Lisboa - Faculdade de Ciências e Tecnologia

Júri

Presidente: Doutor Luis Filipe Lourenço Bernardo - FCT/UNL Arguente: Doutor João Carlos da Palma Goes - FCT/UNL Vogal: Doutor João Pedro Abreu de Oliveira - FCT/UNL

# Design of a Multi-sensor and Re-configurable Smart Node for the IoT Copyright © João Pedro Castro da Rocha de Meneses Alarcão, Faculdade de Ciências e Tecnologia, Universidade NOVA de Lisboa. A Faculdade de Ciências e Tecnologia e a Universidade NOVA de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de inves-

tigação, não comerciais, desde que seja dado crédito ao autor e editor.

#### ACKNOWLEDGEMENTS

I hereby express my deepest thanks, first of all for the sympathy and hard work of Professor João Pedro Oliveira, in the accompaniment and the advice that he gave me along the course of this thesis. I would also like to thank him for the opportunity he gave to me, to have had the pleasure of my thesis being part of the research project taking place in Unicova CTS, headed by the Professor. I am grateful for the opportunity I had to learn from his vast experience and expertise and to have worked with him on the project. I would also like to thank Prof. Rui Tavares, for the help and guidance he offered me, during the work that involved CADIT.

Secondly, I would like to thank my UNINOVA-CTS co-workers, pointing out Nuno Correia, Ricardo Madeira, Hugo Silva, Ivan Bastos for company, support and availability in helping me in my work.

Thirdly, I would like to thank my family for the support they gave me, for the patience they had and for the advice they gave me throughout my academic journey.

And lastly, I would like to thank all my friends, in particular, Tomas Oliveira and Tiago Vieira for their friendships and for the good times we spent that gave me good distractions.

## ABSTRACT

The rapid deployment of the Internet of Things (IoT) is much dependent on the capacity of the IoT node to be able to self-adapt to the target application. With the increase of sensor networks and diversity of sensors available and with the increasing integration of multiple sensors in a sensor node, it is necessary to develop systems capable of handling all of these sensors with high level of flexibility. These may have different characteristics that provide quite distinct interface requirements, thus giving rise to the need for systems with re-configurable properties. With the implementation of sensor networks in places where energy supply is limited or non-existent, and in situations where technician intervention is expensive, there is a need to exchange conventional energy sources by methods of storage and harvesting of the energy present in the environment, where the sensor node is used (autonomous and renewable energy sources). This thesis will focus on the study and implementation of a family of re-configurable and multi-sensor IoT nodes with special emphasis on the energy storage and power management. It will also focus on the develop of a CAD tool in order to help in the design of CMOS circuits, for the purpose of integrating all the strategies here presented.

**Keywords:** Soc, FPGA, IOT, Sensor, Self-adapt, Re-configurability, Super Capacitor, Renewable Energy, Energy Storage, Power Management, CAD.

#### RESUMO

A implantação rápida da Internet das coisas (IoT) depende muito da capacidade do nó do IoT para se adaptar ao aplicativo de destino. Com o aumento das redes de sensores e a diversidade de sensores disponíveis e com a crescente integração de múltiplos sensores em um nó de sensores, é necessário desenvolver sistemas capazes de lidar com todos esses sensores com um nível alto de flexibilidade. Estes podem ter características diferentes que fornecem requisitos de interface bastante distintos, dando origem à necessidade de sistemas com propriedades reconfiguráveis. Com a implementação de redes de sensores em locais onde o fornecimento de energia é limitado ou inexistente, e em situações em que a intervenção do técnico é dispendiosa, é necessário trocar fontes de energia convencionais por métodos de armazenamento e colheita da energia presente no meio ambiente, onde o nó de sensores é usado (fontes de energia autônomas e renováveis). Esta tese incidirá no estudo e implementação de uma família de nós, para a IoT, reconfiguráveis e multisensores com ênfase especial no armazenamento de energia e no seu gerenciamento. Também se concentrará no desenvolvimento de uma ferramenta de CAD para ajudar na concepção dos circuitos CMOS, com a finalidade de integrar todas as estratégias aqui apresentadas.

**Palavras-chave:** Soc, FPGA, IOT, Sensor, auto-adaptar-se, reconfigurabilidade, Super Condensador, energias renováveis, armazenamento de energia, gerenciamento de energia, CAD.

# CONTENTS

| Li | st of 1 | Figures                |                               | xvii  |

|----|---------|------------------------|-------------------------------|-------|

| Li | st of   | Γables                 |                               | xxiii |

| Li | sting   | S                      |                               | xxv   |

| A  | crony   | ms                     |                               | xxvii |

| 1  | Intr    | oduction               |                               | 1     |

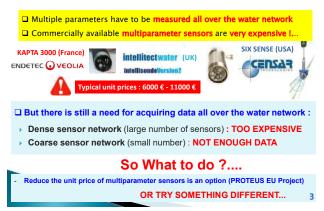

|    | 1.1     | Motivation and Backs   | ground                        | . 1   |

|    | 1.2     | Overview and Contri    | butions                       | . 2   |

|    | 1.3     | Thesis Organization    |                               | . 4   |

|    | 1.4     | Software Used in this  | s Thesis                      | . 4   |

| 2  | Des     | ign Considerations fo  | or the Multi-sensor IoT Node  | 7     |

|    | 2.1     | Introduction           |                               | . 7   |

|    | 2.2     | Internet of Things (Io | т)                            | . 7   |

|    | 2.3     | The IoT Node           |                               | . 8   |

|    |         | 2.3.1 Sensors          |                               | . 10  |

|    |         | 2.3.2 Connectivity     |                               | . 10  |

|    |         | 2.3.3 Energy and Po    | ower Management               | . 10  |

|    | 2.4     | Design consideration   | s                             | . 12  |

|    |         | 2.4.1 Analog Front     | End (AFE)                     | . 12  |

|    |         | 2.4.2 Processor Uni    | t                             | . 14  |

|    |         | 2.4.3 Power Manage     | ement                         | . 15  |

|    |         | 2.4.4 Software Tools   | s for IoT node circuit design | . 20  |

|    |         | 2.4.5 Conclusion .     |                               | . 21  |

| 3  | Pow     | er Management Unit     |                               | 23    |

|    | 3.1     | Introduction           |                               | . 23  |

|    | 3.2     | System Structure       |                               | . 24  |

|    | 3.3     | System Implementati    | ions                          | . 26  |

|    |         | 3.3.1 User Interface   | Description                   | . 27  |

|    |         | 3.3.2 Hardware Des     | signed                        | . 34  |

## CONTENTS

|    |       | 3.3.3 Software Implementation                    | 43  |

|----|-------|--------------------------------------------------|-----|

|    | 3.4   | System Test Results                              | 51  |

|    |       | 3.4.1 Test Setup                                 | 52  |

|    |       | 3.4.2 Results                                    | 53  |

|    | 3.5   | Conclusion                                       | 56  |

| 4  | CAI   | DIT                                              | 57  |

|    | 4.1   | Introduction                                     | 57  |

|    | 4.2   | Software Structure and Implementation            | 58  |

|    |       | 4.2.1 Equations automatically generated by CADIT | 59  |

|    |       | 4.2.2 Small signal models                        | 60  |

|    |       | 4.2.3 Software Prerequisite for Normal Operation | 61  |

|    | 4.3   | Software Test Results                            | 61  |

|    |       | 4.3.1 Circuit Analysis                           | 61  |

|    |       | 4.3.2 Circuit Equations                          | 63  |

|    |       | 4.3.3 Theoretical & Cadence Simulations          | 65  |

|    | 4.4   | Conclusion                                       | 79  |

| 5  | Syst  | tem Design of an IoT Sensor Node                 | 81  |

|    | 5.1   | Introduction                                     | 81  |

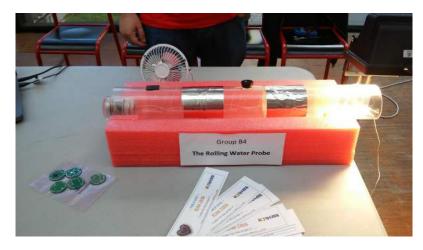

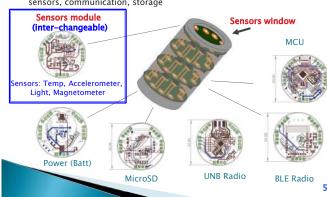

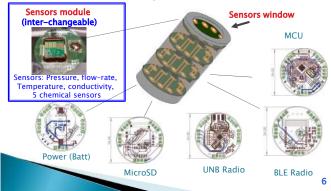

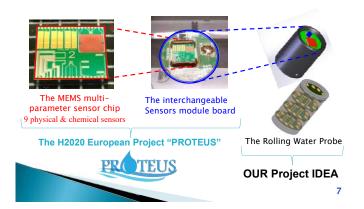

|    | 5.2   | Rolling Probe                                    | 82  |

|    | 5.3   | Node Sensors Test Results                        | 85  |

|    | 5.4   | Conclusion                                       | 87  |

| 6  | Con   | clusions                                         | 89  |

|    | 6.1   | Future Work                                      | 92  |

|    |       | 6.1.1 Power Management                           | 93  |

|    |       | 6.1.2 Node Sensor and Rolling probe              | 93  |

|    |       | 6.1.3 CADIT                                      | 94  |

| Bi | bliog | raphy                                            | 95  |

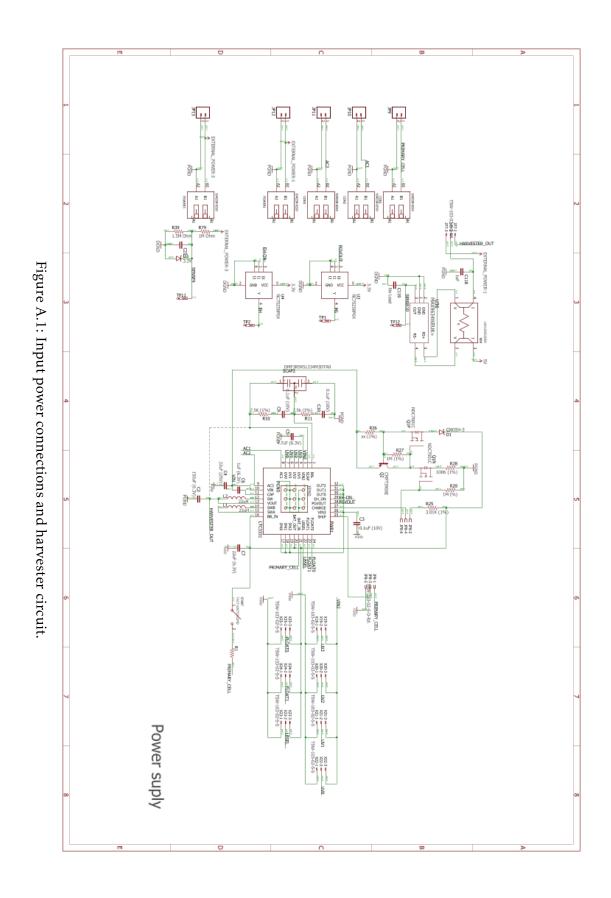

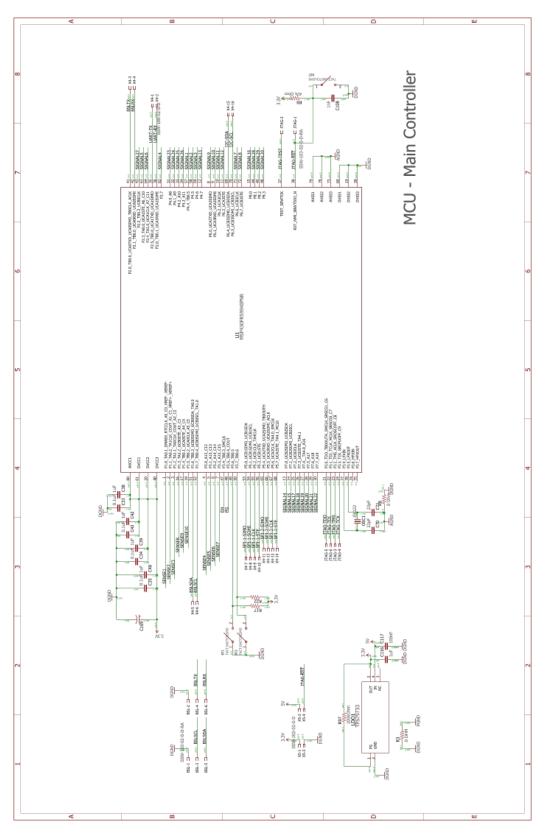

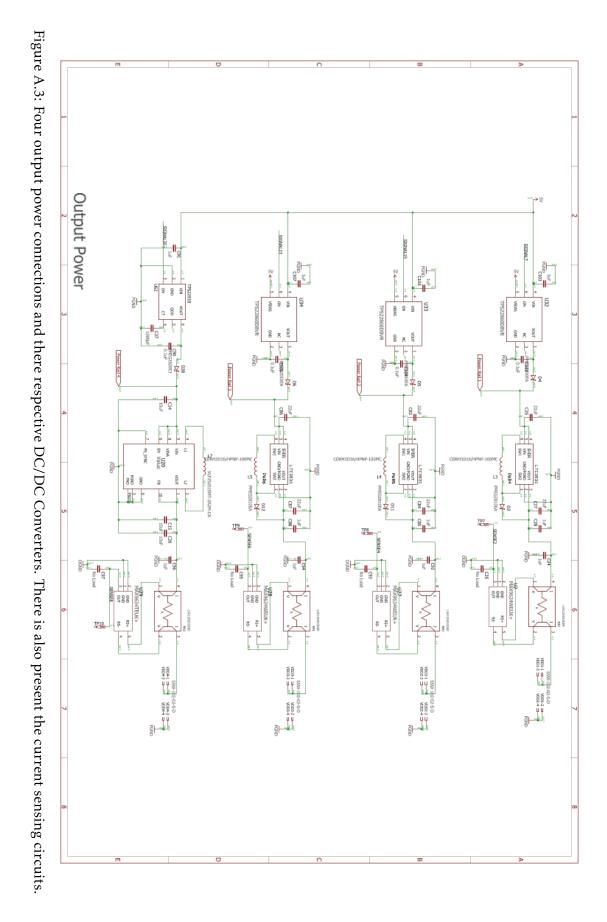

| A  | Pow   | rer Management                                   | 101 |

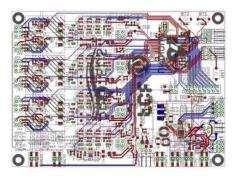

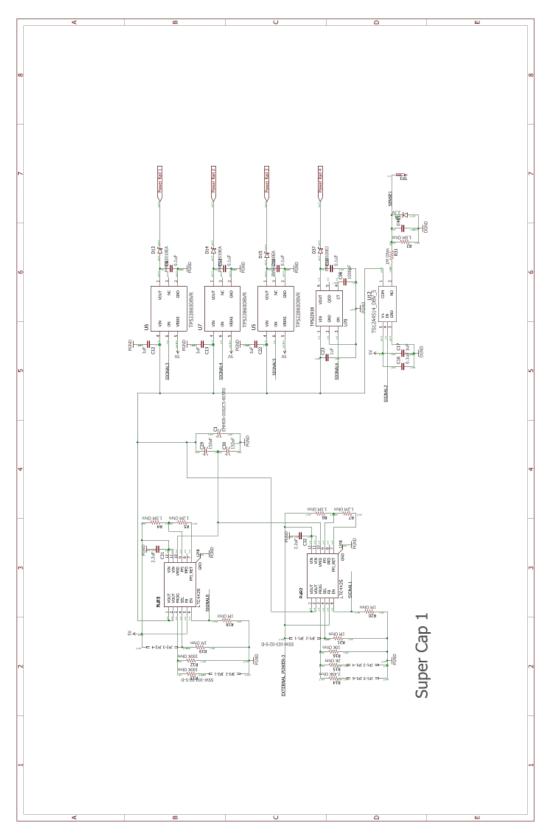

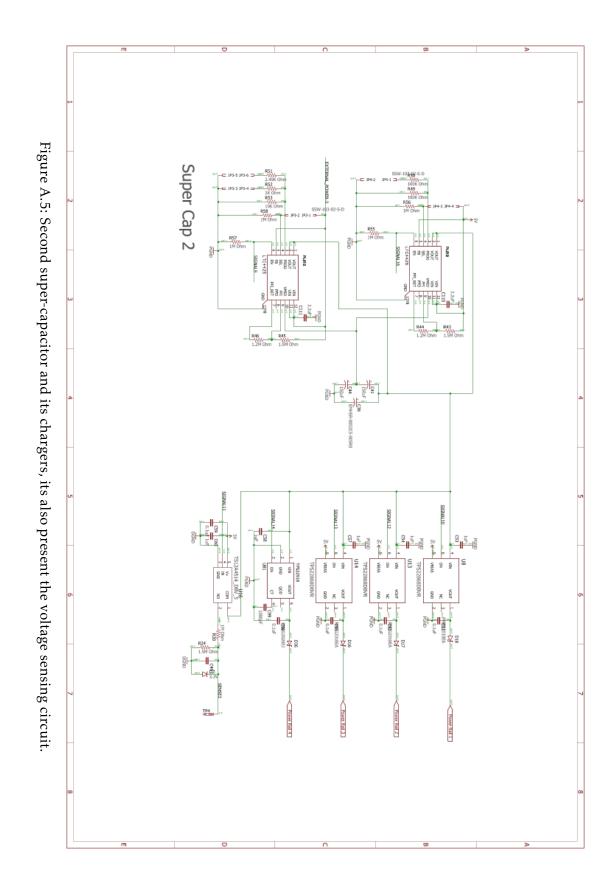

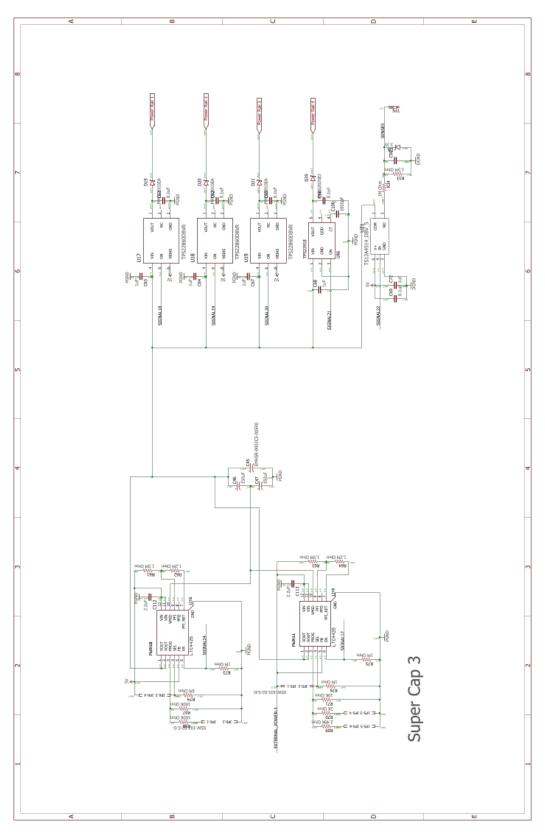

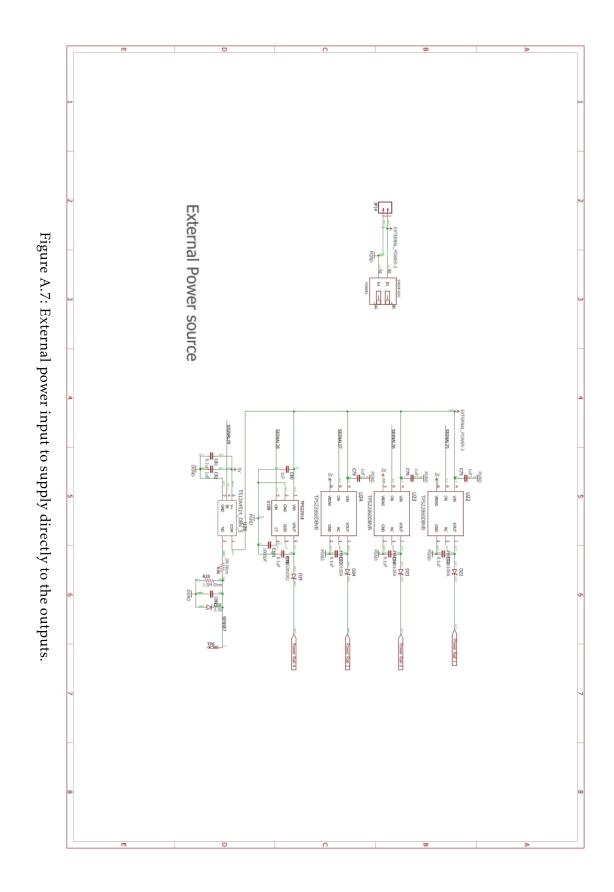

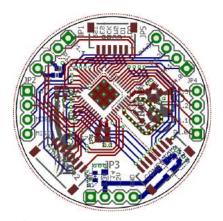

|    | A.1   | PCB Circuitt & Layout                            | 101 |

|    |       | •                                                | 112 |

|    |       | • •                                              | 112 |

|    |       | · · · · · · · · · · · · · · · · · · ·            | 115 |

|    | A.3   | ,                                                | 118 |

|    |       |                                                  | 118 |

|    |       |                                                  | 118 |

|    |       |                                                  | 120 |

|    |       |                                                  | 121 |

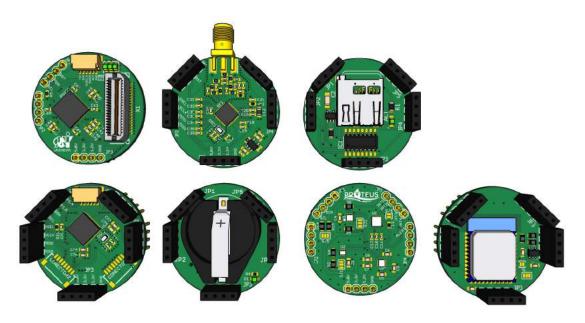

| В | Roll | ing Pro  | be                                          | 123 |

|---|------|----------|---------------------------------------------|-----|

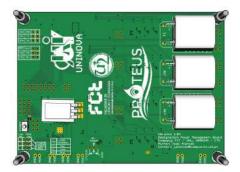

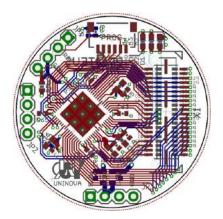

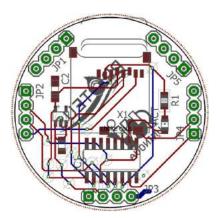

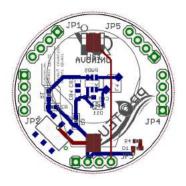

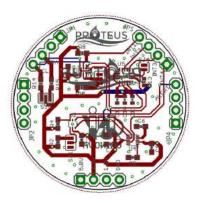

|   | B.1  | PCB C    | ircuit & Layout                             | 123 |

|   |      |          | Competition                                 |     |

| C | CAI  | DIT - Sc | oftware Relevant information                | 133 |

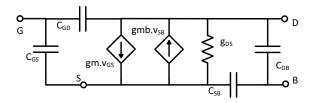

|   | C.1  | Model    | Equations Used to Simulate the Transistores | 133 |

|   |      | C.1.1    | AC Equations                                | 133 |

|   |      | C.1.2    | Noise Equations                             | 133 |

|   |      | C.1.3    | Parasitic Equations                         | 134 |

| D | Rele | evant A  | rticles Made by the Author of this Thesis   | 135 |

# List of Figures

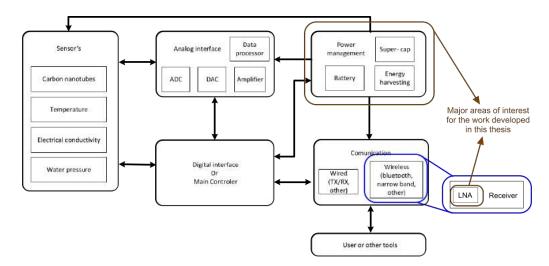

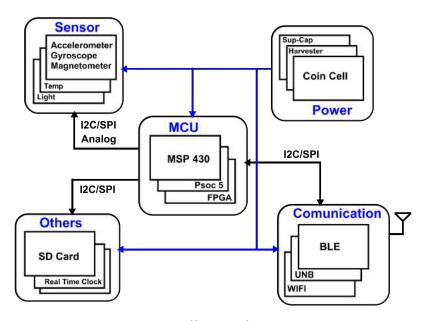

| Diagram of the project system proposed architecture                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

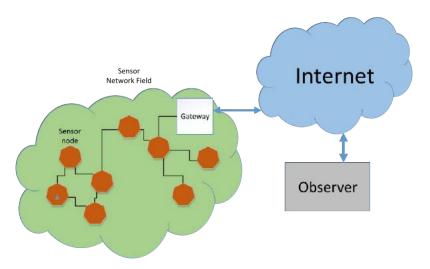

| Wireless sensor networks.                                                               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

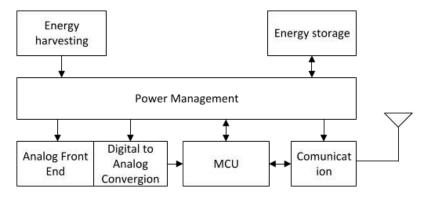

| Node sensor architecture                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

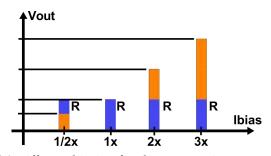

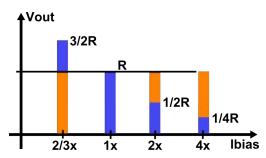

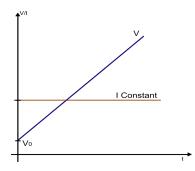

| Biasing graphics (sensor output amplification)                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

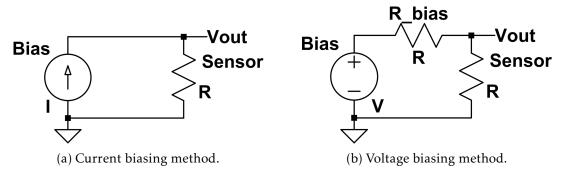

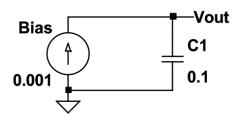

| Polarization circuit for resistive sensors                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

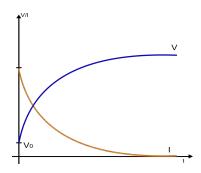

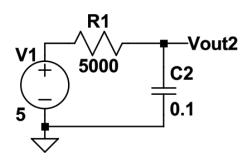

| Circuit and graphic behavior for voltage charge method                                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Circuit and graphic behavior for current charge method                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

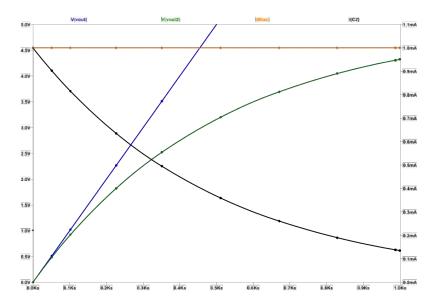

| Electrical simulation of current and voltage charging schemes for the compar-           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ison of the behavior of the circuits in Figures 2.6b and 2.5b                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

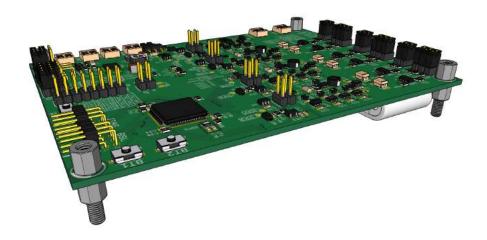

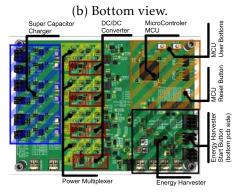

| PMU Board (theoretical representation)                                                  | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

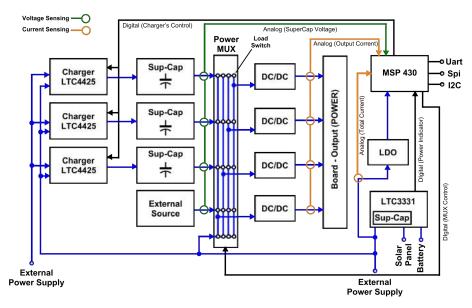

| PMU board block diagram (representation for power, digital and analog sens-             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ing signals).                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

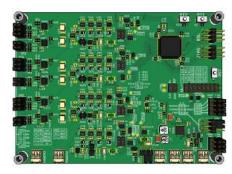

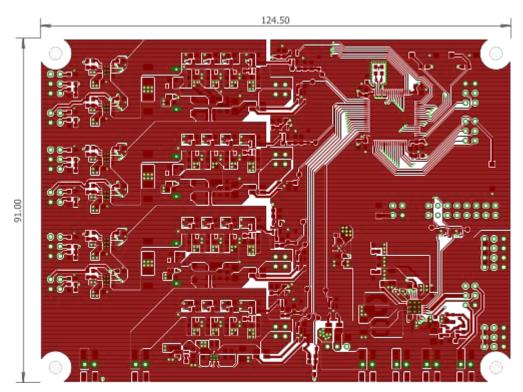

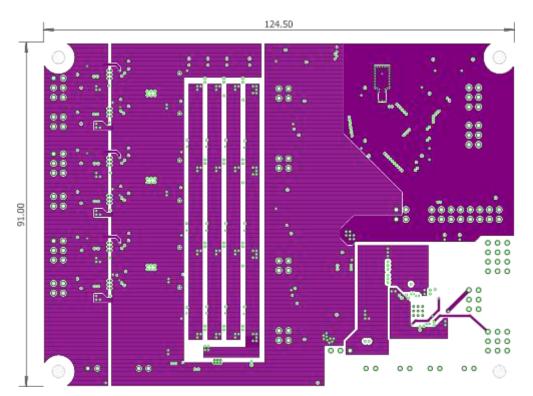

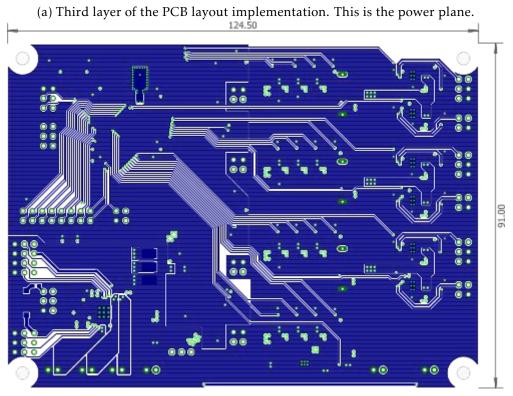

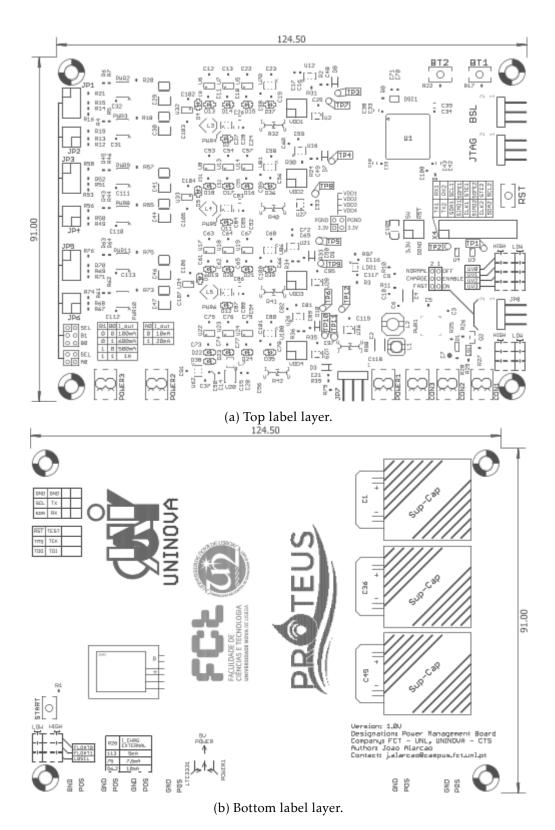

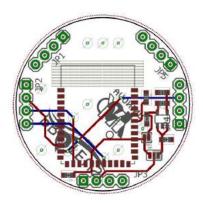

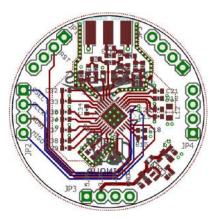

| Theoretical implementation, expected final result of the complete system (PMU           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Board - PCB Version V1)                                                                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

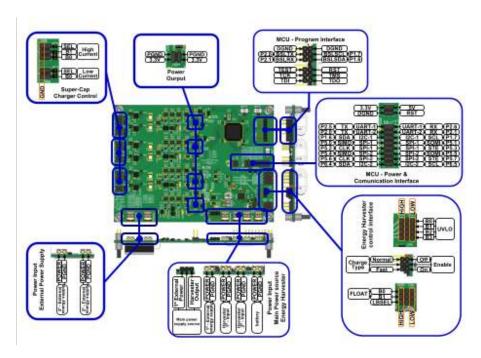

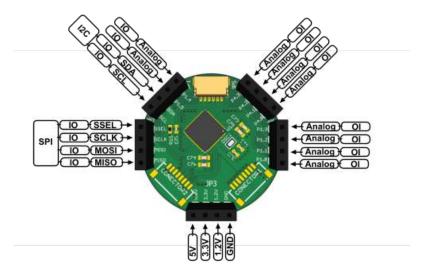

| PMU board pin-out description and configuration                                         | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

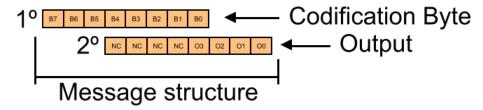

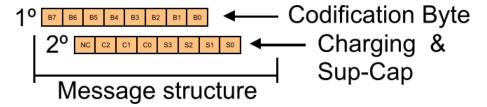

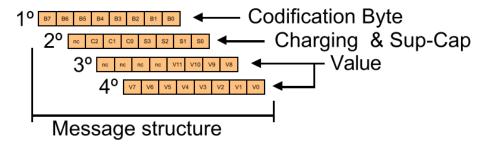

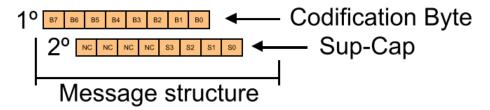

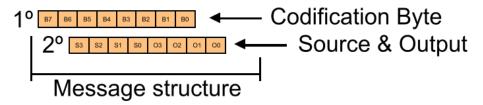

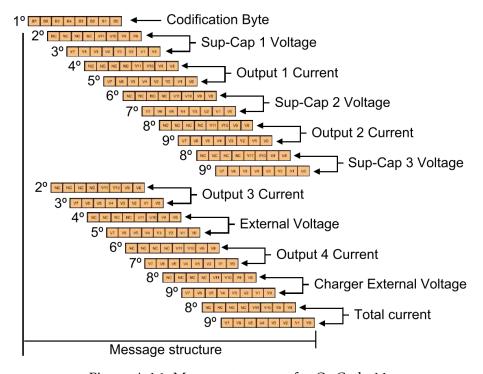

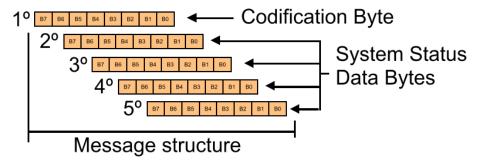

| UART communication protocol. Message structure                                          | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

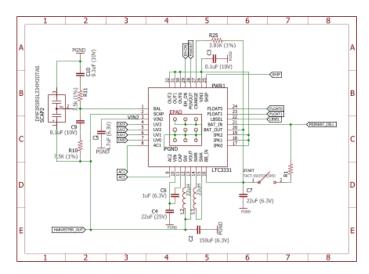

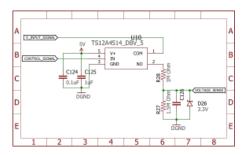

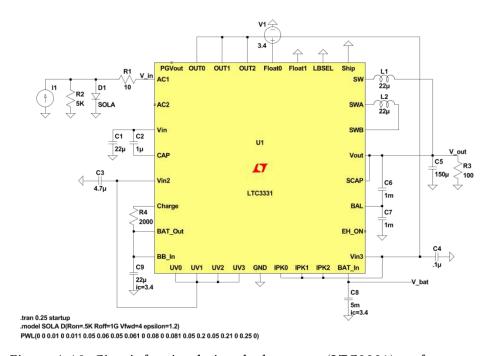

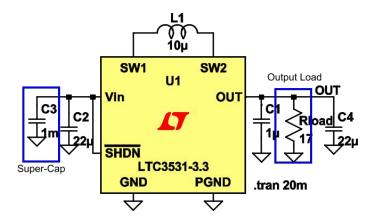

| Simplified circuit of energy harvester block, implemented with LTC3331, su-             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| percapacitor, additional passive components and a capacitor to simulate the             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| discharge of a battery                                                                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Simulation of the chip LTC3331, the circuit to simulate is present in Figure            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A.18                                                                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

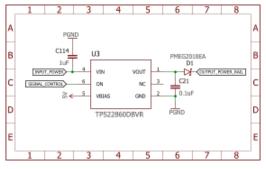

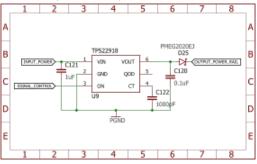

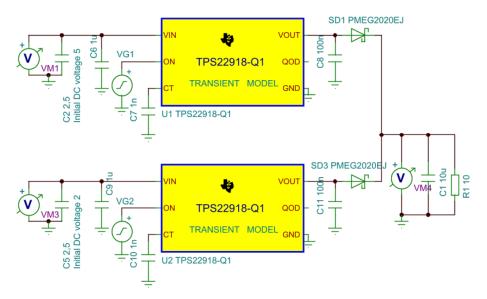

| Power MUX configuration and simplified circuits for the power MUX switches.             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

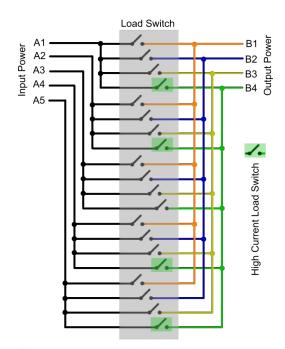

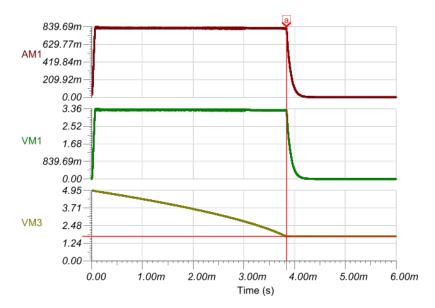

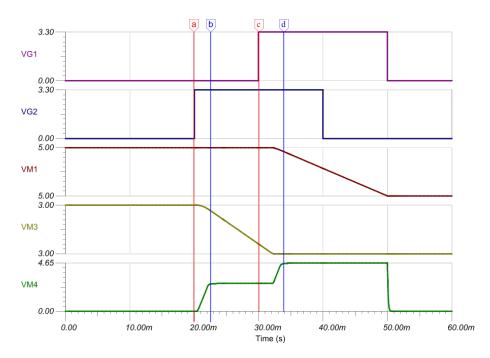

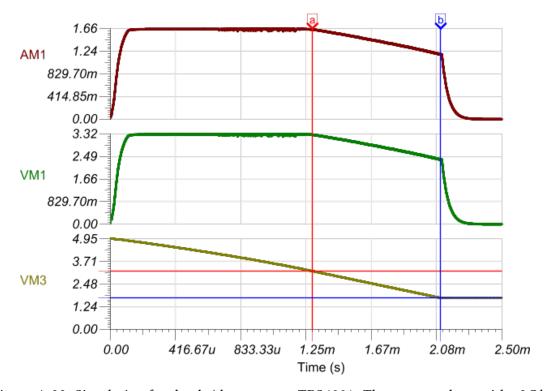

| Transition time simulation for the high current power switch, from circuit in           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure A.19                                                                             | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

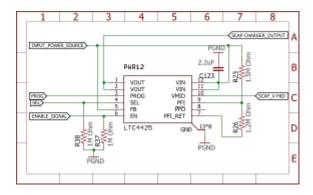

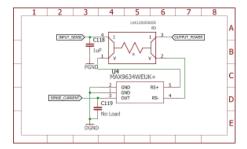

| $Simplified\ circuit\ for\ super-capacitor\ charger\ block, implemented\ with\ LTC4425$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and additional passive components                                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

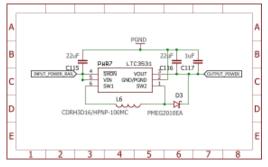

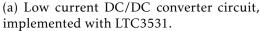

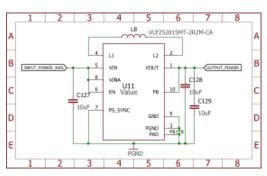

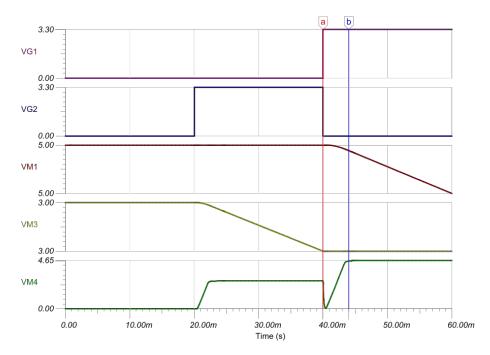

| Simplified circuits for high and low current DC/DC converters                           | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

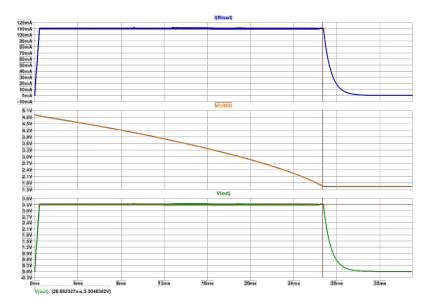

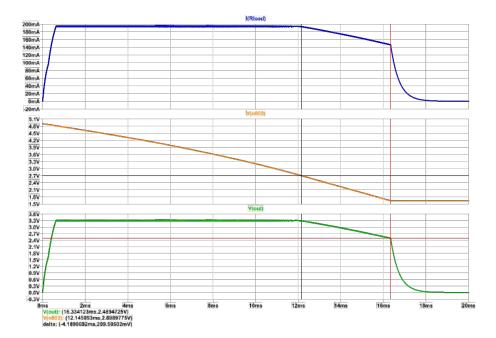

| Simulation of TPS63001 circuit, presented in Figure A.22. For input source              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| uses a capacitor with $1mF$ and initial voltage of $5V$ . The output is $3,3V$ and      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| the load is model whit a resistance of 40hms, resulting in a current of approx-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| imately 800 <i>mA</i>                                                                   | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                         | Wireless sensor networks.  Node sensor architecture.  Biasing graphics (sensor output amplification).  Polarization circuit for resistive sensors.  Circuit and graphic behavior for voltage charge method.  Circuit and graphic behavior for current charge method.  Electrical simulation of current and voltage charging schemes for the comparison of the behavior of the circuits in Figures 2.6b and 2.5b.  PMU Board (theoretical representation).  PMU board block diagram (representation for power, digital and analog sensing signals).  Theoretical implementation, expected final result of the complete system (PMU Board - PCB Version V1).  PMU board pin-out description and configuration.  UART communication protocol. Message structure.  Simplified circuit of energy harvester block, implemented with LTC3331, supercapacitor, additional passive components and a capacitor to simulate the discharge of a battery.  Simulation of the chip LTC3331, the circuit to simulate is present in Figure A.18.  Power MUX configuration and simplified circuits for the power MUX switches. Transition time simulation for the high current power switch, from circuit in Figure A.19.  Simplified circuit for super-capacitor charger block, implemented with LTC4425 and additional passive components.  Simplified circuits for high and low current DC/DC converters.  Simulation of TPS63001 circuit, presented in Figure A.22. For input source uses a capacitor with 1mF and initial voltage of 5V. The output is 3,3V and the load is model whit a resistance of 40hms, resulting in a current of approx- |

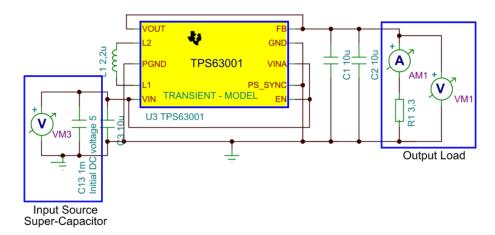

| 3.13 | Simulation of LTC3531 circuit, presented in Figure A.24. For input source uses a capacitor with $1mF$ and initial voltage of $5V$ . The output is $3,3V$ and the load |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | is model whit a resistance of 30 <i>Ohms</i> , resulting in a current of approximately                                                                                |    |

|      | 100mA                                                                                                                                                                 | 41 |

| 3.14 | Simplify circuits for analog signal sensing (voltage and current)                                                                                                     | 42 |

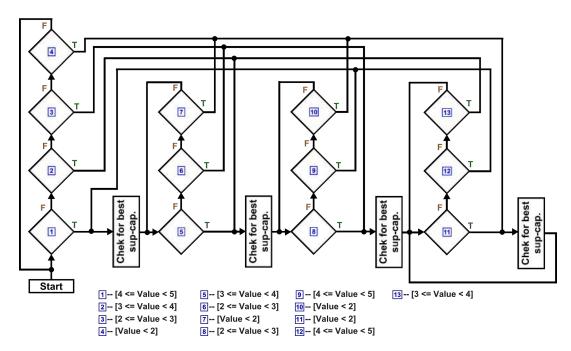

|      | Control algorithms for evaluating the super-capacitor condition                                                                                                       | 44 |

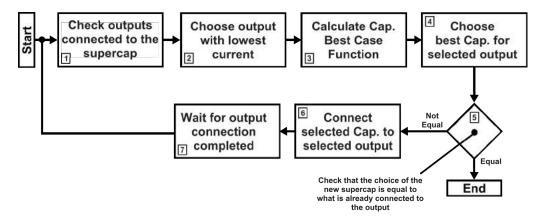

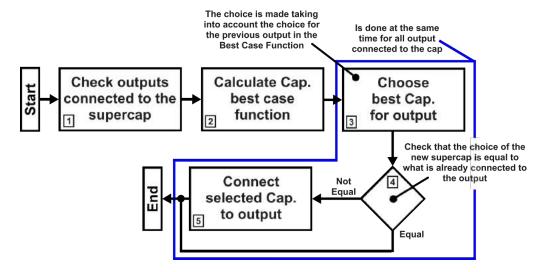

|      | A second control algorithm for choosing the best super-capacitor for the output.                                                                                      | 45 |

|      | First Control algorithm, for choosing the best super-capacitor for the output.                                                                                        | 45 |

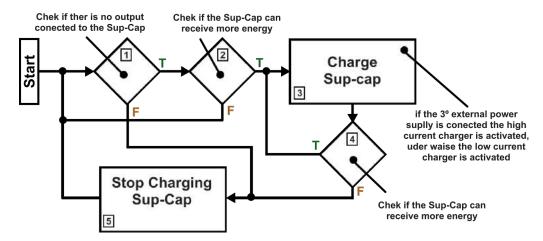

|      | Control algorithm for charging the super-capacitor to full capacity                                                                                                   | 47 |

|      | Computer graphical interface to visualize and control the PMU Board signals                                                                                           |    |

|      | (Super-capacitor voltage, output current, switch control signals, etc.)                                                                                               | 52 |

| 3.20 | PMU board test setup. Consist of a load circuit to test the power output and                                                                                          |    |

|      | launch pad to serve as a communication interface (UART to USB) with the                                                                                               |    |

|      | computer                                                                                                                                                              | 52 |

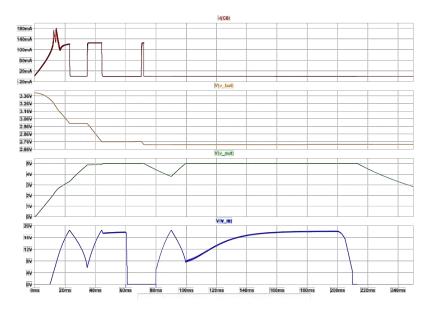

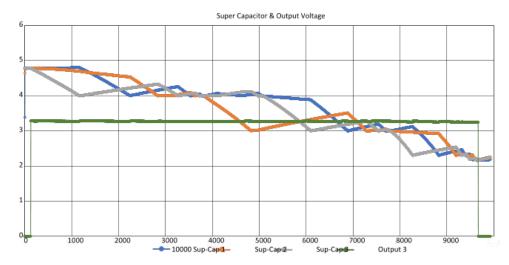

| 3.21 | Experimental data retrieved from the test setup in Figure 3.20. The data rep-                                                                                         |    |

|      | resent the commutations between supercapacitors to supply power to output                                                                                             |    |

|      | 3 that has an output current of approximately $100mA$                                                                                                                 | 54 |

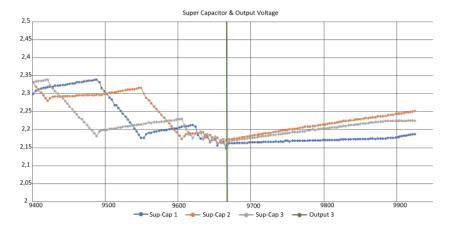

| 3.22 | A more detailed view of the final moments of the experimental data results.                                                                                           |    |

|      | The graph demonstrates the moment where the output is disconnected due to                                                                                             |    |

|      | insufficient energy in the supercapacitors                                                                                                                            | 55 |

| 3.23 | A more detailed view of the final moments of the experimental data results                                                                                            |    |

|      | with lower configuration values than those used to obtained Figure 3.22                                                                                               | 55 |

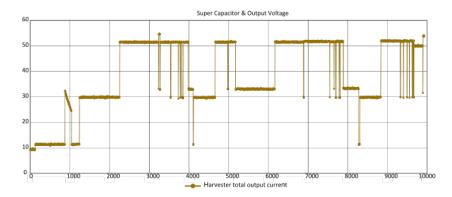

| 3.24 | Experimental data retrieved from the test setup in Figure 3.20. The data                                                                                              |    |

|      | represents the total current being supplied to the board. A percentage of this                                                                                        |    |

|      | current is used by the super-capacitor chargers                                                                                                                       | 55 |

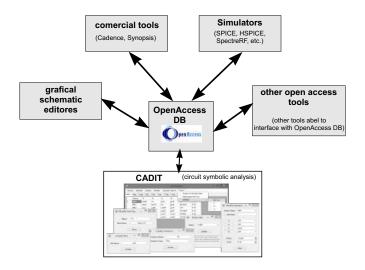

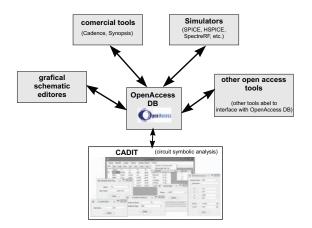

| 4.1  | Graphical interface of the CAD software available to the user                                                                                                         | 57 |

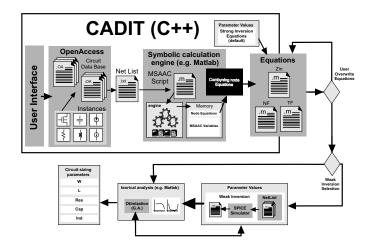

| 4.2  | Main blocks of CADIT tool                                                                                                                                             | 58 |

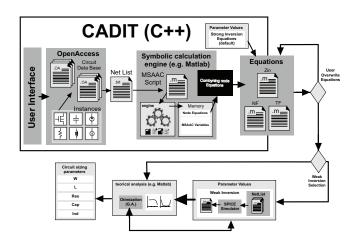

| 4.3  | The CAD software diagram of the process to calculate the circuit equations                                                                                            |    |

|      | and it simulations for circuit sizing                                                                                                                                 | 58 |

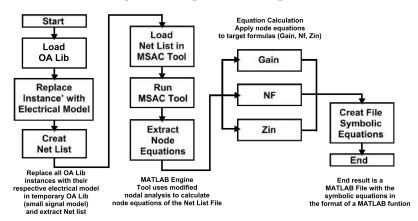

| 4.4  | The CAD software process work-flow to obtain the symbolic equations files of                                                                                          |    |

|      | the circuit functions.                                                                                                                                                | 59 |

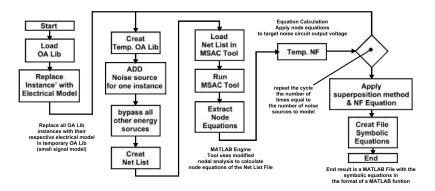

| 4.5  | The CAD software process work-flow to obtain the NF symbolic equations files                                                                                          |    |

|      | of the circuit                                                                                                                                                        | 60 |

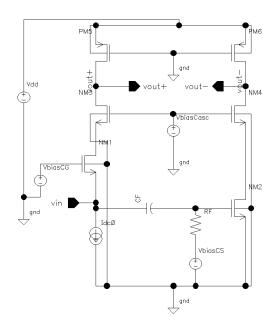

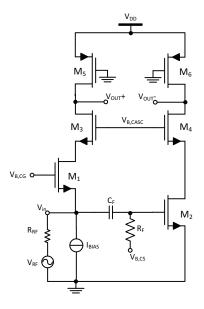

| 4.6  | LNA circuit.                                                                                                                                                          | 62 |

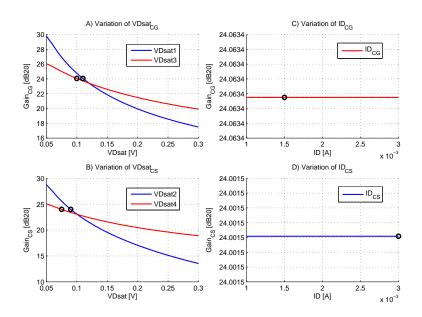

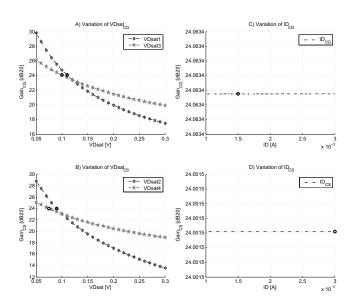

| 4.7  | Theoretical parametric simulation of the single ended Gain equations for <i>Lmin</i>                                                                                  |    |

|      | sizing. Variation of <i>VDsat</i> and <i>ID</i> from CG and CS                                                                                                        | 66 |

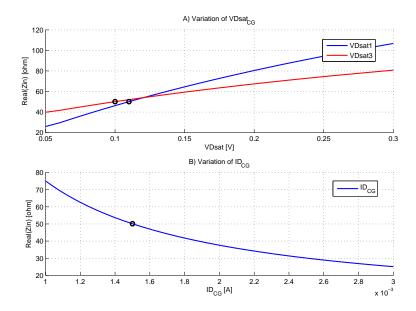

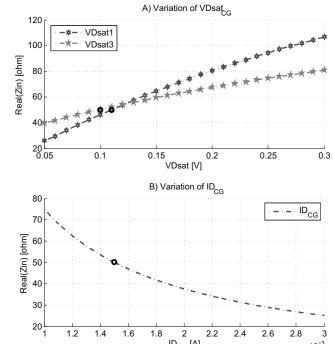

| 4.8  | Theoretical parametric simulation of the Zin equation for <i>Lmin</i> sizing. Varia-                                                                                  |    |

|      | tion of VDsat and ID from CG                                                                                                                                          | 67 |

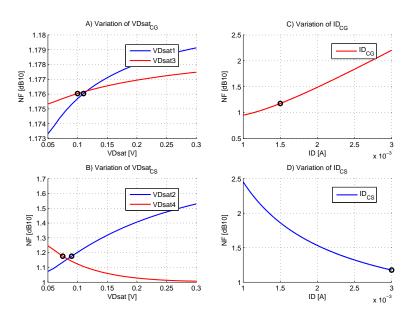

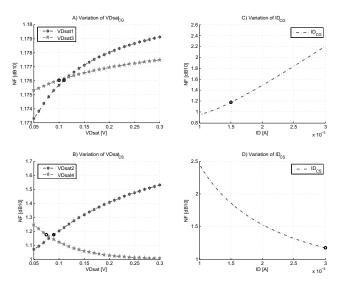

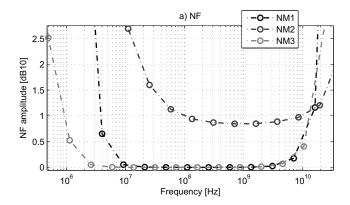

| 4.9  | Theoretical parametric simulation of the NF equations for <i>Lmin</i> sizing. Varia-                                                                                  |    |

|      | tion of <i>VDsat</i> and <i>ID</i> from CG and CS                                                                                                                     | 68 |

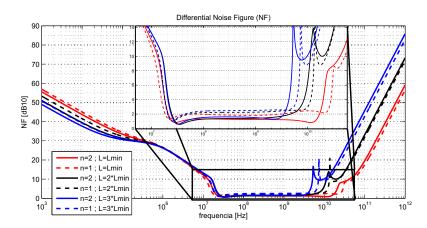

| 4.10 | Theoretical parametric simulation of the current (relationship between the current of the CG and CS stage, $n = \frac{ID_{CS}}{ID_{CG}}$ ) influence in the NF equation for |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | various sizing                                                                                                                                                              | 69  |

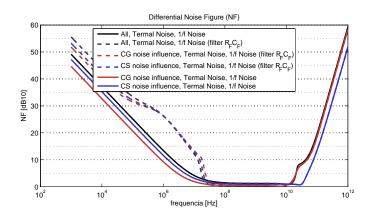

| 4.11 | CG and CS influence in the NF for <i>Lmin</i> and $n = 2$ sizing                                                                                                            | 70  |

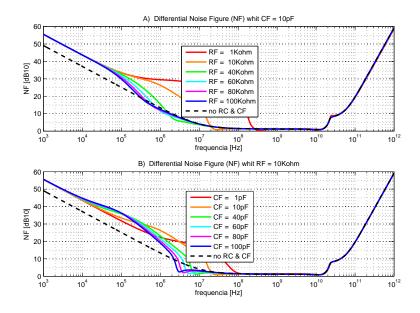

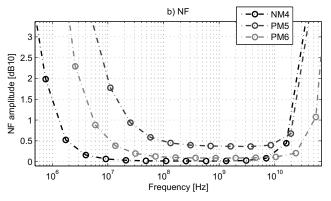

| 4.12 | Theoretical parametric simulation of the filter influence in the NF equation                                                                                                |     |

|      | for Lmin sizing.                                                                                                                                                            | 70  |

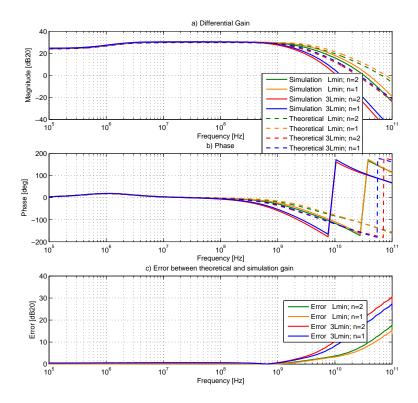

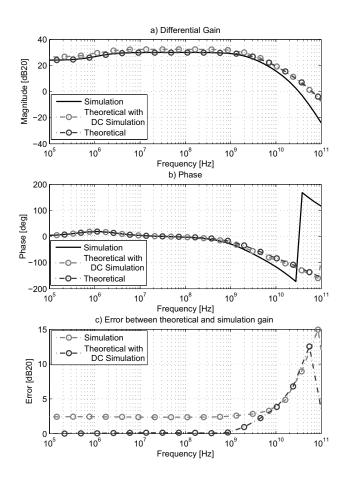

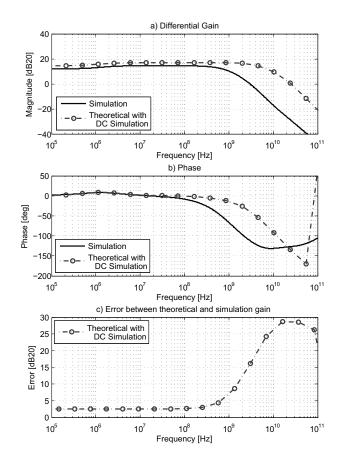

| 4.13 | Theoretical and Cadence Gain simulations and the error between them for                                                                                                     |     |

|      | Lmin and 3Lmin sizing                                                                                                                                                       | 71  |

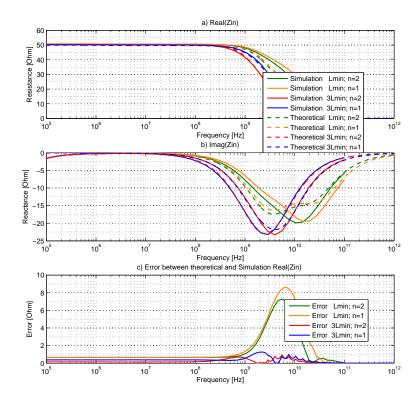

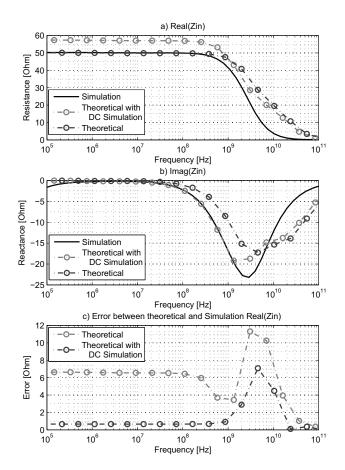

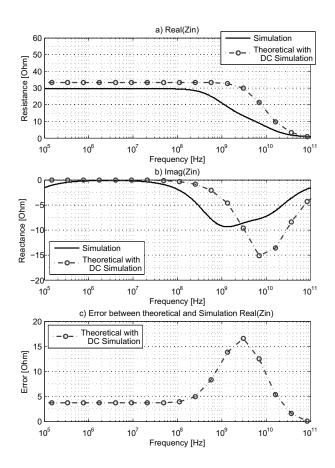

| 4.14 | Theoretical and Cadence Zin simulations and the error between them for <i>Lmin</i>                                                                                          |     |

|      | and 3 Lmin sizing                                                                                                                                                           | 72  |

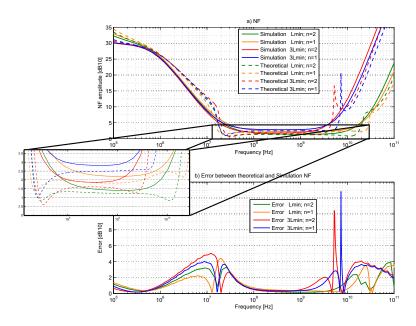

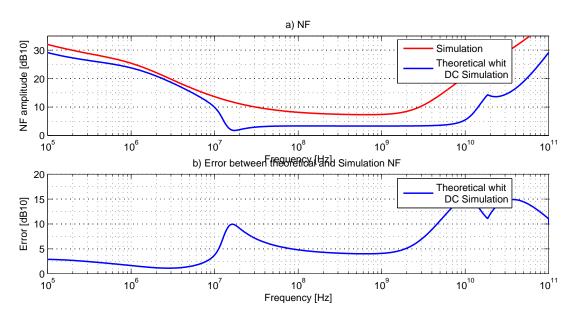

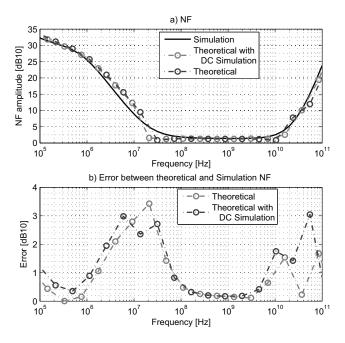

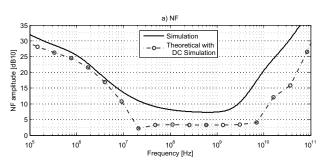

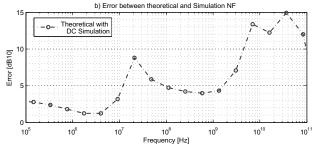

| 4.15 | Theoretical and Cadence NF simulations and the error between them for <i>Lmin</i>                                                                                           |     |

|      | and 3 Lmin sizing                                                                                                                                                           | 73  |

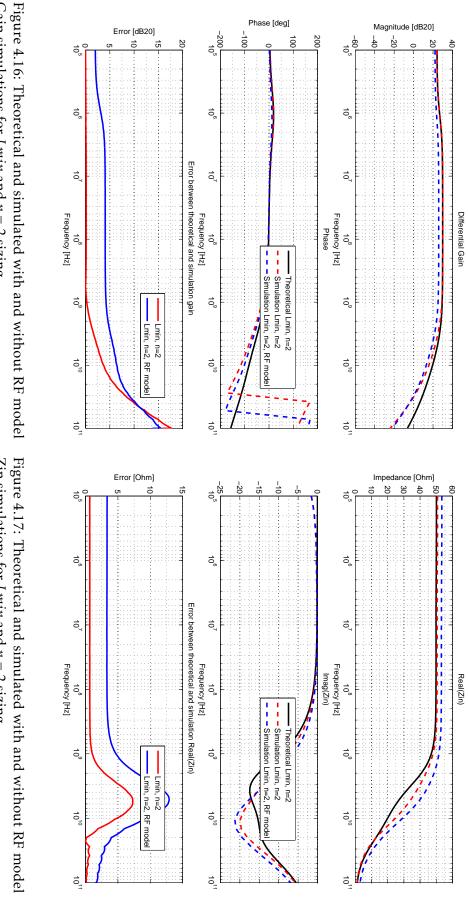

| 4.16 | Theoretical and simulated with and without RF model Gain simulations for                                                                                                    |     |

|      | <i>Lmin</i> and $n = 2$ sizing                                                                                                                                              | 74  |

| 4.17 | Theoretical and simulated with and without RF model Zin simulations for                                                                                                     |     |

|      | <i>Lmin</i> and $n = 2$ sizing                                                                                                                                              | 74  |

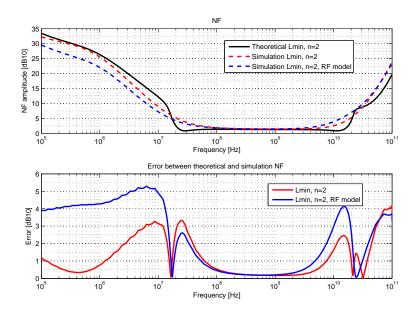

| 4.18 | Theoretical and simulated with and without RF model NF simulations for                                                                                                      |     |

|      | <i>Lmin</i> and $n = 2$ sizing                                                                                                                                              | 76  |

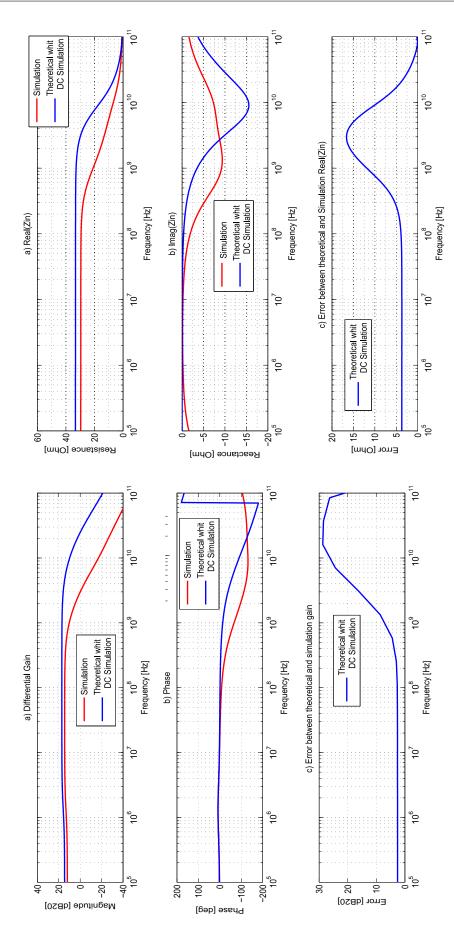

| 4.19 | Comparing the theoretical data (with DC simulation parameters) and simulated TF, of the circuit presented in Figure 4.6, in Cadence software, for weak                      |     |

|      | inversion. The TF represents the gain in the differential output                                                                                                            | 77  |

| 4 20 | Comparing the theoretical data (with DC simulation parameters) and simu-                                                                                                    | ,,  |

| 1.20 | lated Zin, of the circuit presented in Figure 4.6, in Cadence software, for weak                                                                                            |     |

|      | inversion                                                                                                                                                                   | 77  |

| 4.21 | Comparing the theoretical data (whit DC simulation parameters) and simulation parameters.                                                                                   |     |

|      | lated NF function, of the circuit presented in Figure 4.6, in Cadence software,                                                                                             | 7.0 |

|      | for weak inversion. The NF represents the noise in the differential output                                                                                                  | 78  |

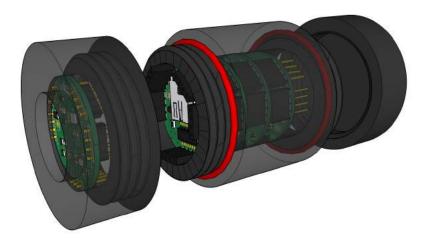

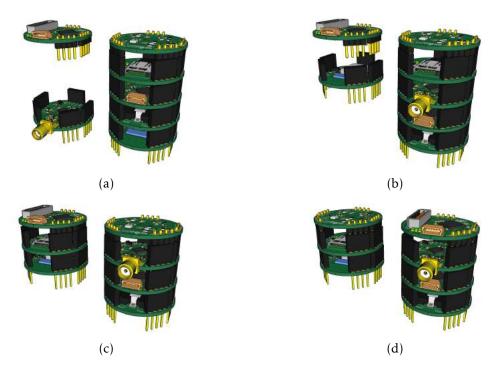

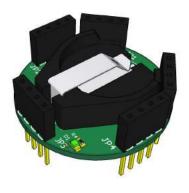

| 5.1  | Final expected result, the system is incorporated in a cylindrical container                                                                                                | 0.4 |

|      | with a small opening for the sensors                                                                                                                                        | 81  |