# RESOURCE MANAGEMENT ALGORITHMS FOR COMPUTING HARDWARE DESIGN AND OPERATIONS: FROM CIRCUITS TO SYSTEMS

A Dissertation

by

## HAO HE

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Jiang Hu            |

|---------------------|---------------------|

| Committee Members,  | Dilma Da Silva      |

|                     | Paul Gratz          |

|                     | Shuguang Cui        |

| Head of Department, | Miroslav M. Begovic |

December 2016

Major Subject: Computer Engineering

Copyright 2016 Hao He

#### ABSTRACT

The complexity of computation hardware has increased at an unprecedented rate for the last few decades. On the computer chip level, we have entered the era of multi/manycore processors made of billions of transistors. With transistor budget of this scale, many functions are integrated into a single chip. As such, chips today consist of many heterogeneous cores with intensive interaction among these cores. On the circuit level, with the end of Dennard scaling, continuously shrinking process technology has imposed a grand challenge on power density. The variation of circuit further exacerbated the problem by consuming a substantial time margin. On the system level, the rise of Warehouse Scale Computers and Data Centers have put resource management into new perspective. The ability of dynamically provision computation resource in these gigantic systems is crucial to their performance. In this thesis, three different resource management algorithms are discussed. The first algorithm assigns adaptivity resource to circuit blocks with a constraint on the overhead. The adaptivity improves resilience of the circuit to variation in a cost-effective way. The second algorithm manages the link bandwidth resource in application specific Networks-on-Chip. Quality-of-Service is guaranteed for time-critical traffic in the algorithm with an emphasis on power. The third algorithm manages the computation resource of the data center with precaution on the ill states of the system. Q-learning is employed to meet the dynamic nature of the system and Linear Temporal Logic is leveraged as a tool to describe temporal constraints. All three algorithms are evaluated by various experiments. The experimental results are compared to several previous work and show the advantage of our methods.

## DEDICATION

To my family.

#### ACKNOWLEDGMENTS

It has been a long way in pursuit of a doctoral degree. In the years I spent in Texas A&M, there were times of exuberance, disappointment, frustration, and ecstasy. Along the way I received great help from many people, some I am close with, some I admire and look up to, and some I do not even know the name of.

First and foremost, I want to thank my advisor, Professor Jiang Hu, for being a great guidance in research and in life. His tolerant attitude, strong work ethic and high standards for himself are true examples of what a professional should be like.

I would also like to express my gratitude for Jiafan Wang, Yiren Shen and Gongming Yang. There were many bumps and obstacles during the projects we worked together. They showed great patience and worked hard in the process.

I met many friends in Mathworks, Natick where I spent half a year doing my internship. I want to thank my manager Andy Bartlett for giving me the opportunity. I had many inspiring discussions with my colleague Evangelous Denaxas. And many of my best memories there are with Weijia Zhang, who is always up for the bigger challenge.

Lastly, I need to thank my family and Dr. Yining Huang for their support. They always bring up the best of me.

### CONTRIBUTORS AND FUNDING SOURCES

## Contributors

This work was supported by a thesis (or) dissertation committee consisting of Professor Jiang Hu [advisor], Professor Paul Gratz and Professor Shuguang Cui of the Department of Electrical & Computer Engineering and Professor Dilma Da Silva of the Department of Computer Science & Engineering.

The experiments presented in section 1 were conducted in collaboration with Jiafan Wang of the Department of Electrical & Computer Engineering and were published in 2015 in an article listed in the Biographical Sketch.

All other work conducted for the thesis (or) dissertation was completed by the student independently.

### **Funding Sources**

Graduate study was supported by research funding from Semiconductor Research Corporation.

## NOMENCLATURE

| LR   | Lagrangian Relaxation              |

|------|------------------------------------|

| ABB  | Adaptive Body Bias                 |

| FBB  | Forward Body Bias                  |

| DAG  | Directed Acyclic Graph             |

| SSTA | Statistical Static Timing Analysis |

| PCA  | Principal Component Analysis       |

| NoC  | Networks-on-Chip                   |

| QoS  | Quality-of-Service                 |

| GS   | Guaranteed Service                 |

| BE   | Best Effort                        |

| TDM  | Time Division Multiplexing         |

| SAT  | Boolean Satisfiability             |

| ILP  | Integer Linear Programming         |

| CNF  | Conjunctive Normal Form            |

| LTL  | Linear Temporal Logic              |

| MDP  | Markov Decision Process            |

| AP   | Atomic Proposition                 |

| DRA  | Deterministic Rabin Automaton      |

| DoD  | Depth of Discharge                 |

| DRF  | Dominant Resource Fairness         |

|      |                                    |

## TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                      | ii                                                         |

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                                                    | iii                                                        |

| CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                | iv                                                         |

| CONTRIBUTORS AND FUNDING SOURCES                                                                                                                                                                                                                                                                                                                                                                                              | v                                                          |

| OMENCLATURE                                                                                                                                                                                                                                                                                                                                                                                                                   | vi                                                         |

| ABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                              | vii                                                        |

| IST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                | X                                                          |

| IST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                 | xiii                                                       |

| . RESOURCE MANAGEMENT IN COMPUTER HARDWARE                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                          |

| 1.1Resource Management in Different Scope1.2An Algorithmic Approach                                                                                                                                                                                                                                                                                                                                                           | 1<br>3                                                     |

| . OPTIMIZATION FOR ADAPTIVE CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                          |

| <ul> <li>2.1 Introduction</li> <li>2.2 Related Work</li> <li>2.3 Background</li> <li>2.3.1 Lagrange Relaxation</li> <li>2.3.2 Gate Sizing</li> <li>2.3.3 Variation Modelling</li> <li>2.3.4 Adaptive Body Biasing</li> <li>2.3.5 Static Timing Analysis</li> <li>2.4 Problem Formulation</li> <li>2.4.1 Placement and Clustering</li> <li>2.4.2 Gate Implementation Selection</li> <li>2.4.3 Adaptivity Assignment</li> </ul> | 4<br>7<br>8<br>9<br>10<br>12<br>13<br>14<br>15<br>16<br>17 |

| <ul> <li>2.4.5 Adaptivity Assignment</li> <li>2.4.4 Collaborative Gate Implementation Selection and Adaptivity Assignment</li> </ul>                                                                                                                                                                                                                                                                                          | 17                                                         |

|    | 2.5 | Overview of Adaptivity Assignment Algorithm                     |

|----|-----|-----------------------------------------------------------------|

|    |     | 2.5.1 Lagrange Primal Problem: Gate Implementation Selection 20 |

|    |     | 2.5.2 Statistical Static Timing Analysis                        |

|    |     | 2.5.3 Lagrange Dual Problem                                     |

|    | 2.6 | Adaptivity Assignment Algorithm                                 |

|    | 2.7 | Experiment Result                                               |

| 3. |     | VER EFFICIENT QUALITY-OF-SERVICE FOR APPLICATION SPECIFIC       |

|    | NET | WORK-ON-CHIPS                                                   |

|    | 3.1 | Introduction                                                    |

|    | 3.2 | Background                                                      |

|    |     | 3.2.1 NoC Topology 34                                           |

|    |     | 3.2.2 Packet Format                                             |

|    |     | 3.2.3 Router Design                                             |

|    | 3.3 | Problem Formulation                                             |

|    |     | 3.3.1 Power Efficient QoS                                       |

|    |     | 3.3.2 Graph Model                                               |

|    | 3.4 | Boolean-Satisfiability-based Method    40                       |

|    |     | 3.4.1 Boolean Satisfiability Problem                            |

|    |     | 3.4.2 Candidate Path Generation                                 |

|    |     | 3.4.3 SAT Formulation                                           |

|    |     | 3.4.4 In-order Flits Delivery 42                                |

|    |     | 3.4.5 Experiment Result                                         |

|    | 3.5 | Integer Linear-Programming-based Method 44                      |

|    |     | 3.5.1 Problem Formulation                                       |

|    |     | 3.5.2 Experimental Results                                      |

| 4. | MO  | DEL CHECKING BASED RESOURCE MANAGEMENT IN DATA CEN-             |

|    | TER |                                                                 |

|    | 4.1 | Introduction                                                    |

|    | 4.2 | Related Work                                                    |

|    | 4.3 | Background                                                      |

|    |     | 4.3.1 Linear Temporal Logic                                     |

|    |     | 4.3.2 Deterministic Rabin Automaton                             |

|    |     | 4.3.3 LTL Constrained MDP                                       |

|    |     | 4.3.4 Q-learning                                                |

|    | 4.4 | LTL-based Resource Management                                   |

|    | 4.5 | Power Capping in Distributed UPS Data Center                    |

|    |     | 4.5.1 The Problem                                               |

|    |     | 4.5.2 LTL Constrained Power Capping                             |

|    |     | 4.5.3 Experimental Results                                      |

| 4.6    | Fair So | cheduling                   |  |

|--------|---------|-----------------------------|--|

|        | 4.6.1   | Emulation Platform          |  |

|        | 4.6.2   | Conventional Job Schedulers |  |

|        | 4.6.3   | F+LTL Scheduler             |  |

|        | 4.6.4   | Experimental Results        |  |

|        | 4.6.5   | Simulation Results          |  |

| 5. CON | NCLUS   | ION                         |  |

| REFER  | ENCES   | 85                          |  |

## LIST OF FIGURES

| FIGURI | Ε                                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------------------------|------|

| 1.1    | Resource management in multiple level                                                                  | 2    |

| 2.1    | An example of adaptive circuit through body biasing                                                    | 5    |

| 2.2    | Timing constraint of circuit design.                                                                   | 10   |

| 2.3    | Correlation matrix is defined to model the variation.                                                  | 11   |

| 2.4    | Body biasing a transistor.                                                                             | 12   |

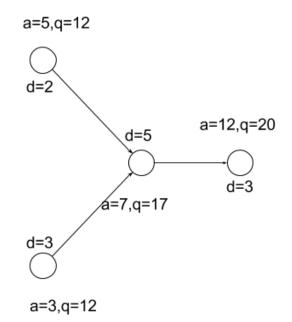

| 2.5    | An example for Static Timing Analysis.                                                                 | 14   |

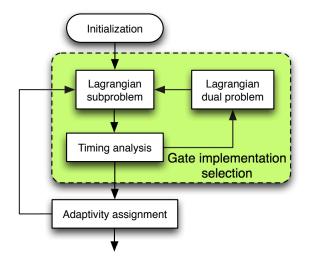

| 2.6    | Overview of algorithm flow.                                                                            | 19   |

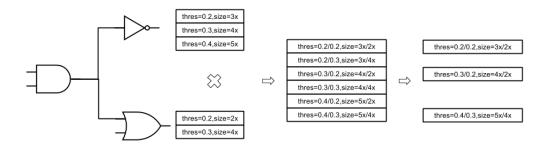

| 2.7    | An example of dynamic programming algorithm.                                                           | 20   |

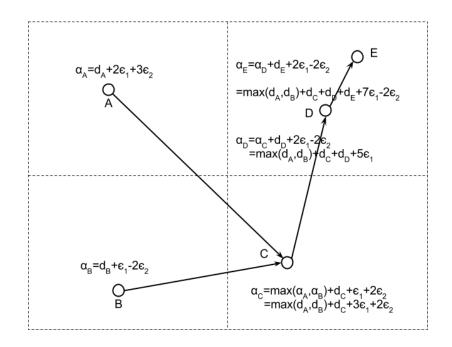

| 2.8    | An example of SSTA                                                                                     | 22   |

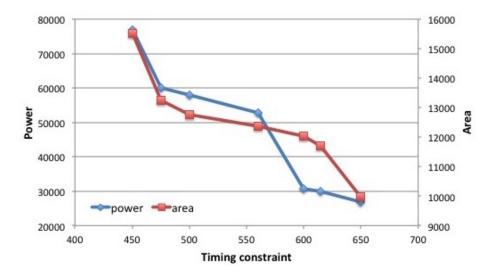

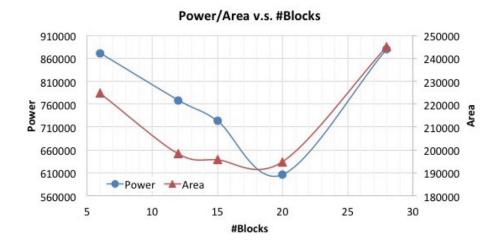

| 2.9    | Power/area-timing tradeoff for circuit c7552                                                           | 30   |

| 2.10   | Power/area vs. granularity for circuit fft.                                                            | 31   |

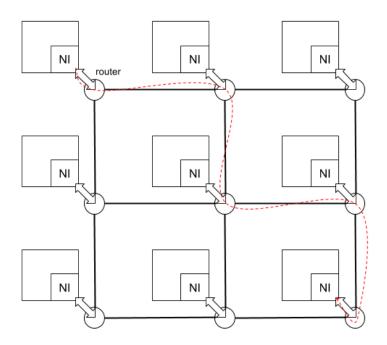

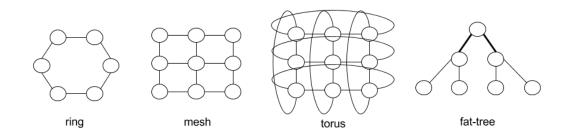

| 3.1    | Networks on Chip.                                                                                      | 33   |

| 3.2    | Common NoC topologies.                                                                                 | 34   |

| 3.3    | The layout of an NoC packet.                                                                           | 35   |

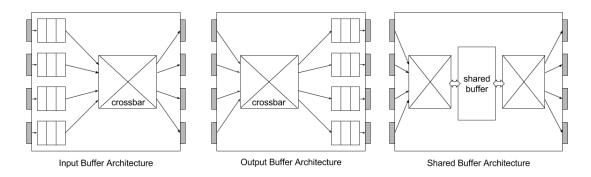

| 3.4    | Router Microarchitecture.                                                                              | 36   |

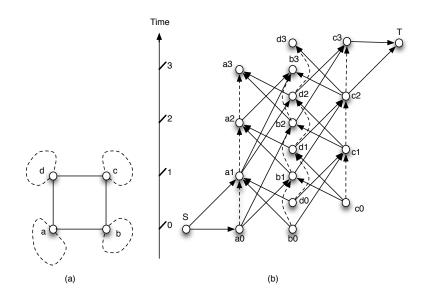

| 3.5    | (a) Physical graph; (b) Resource graph                                                                 | 38   |

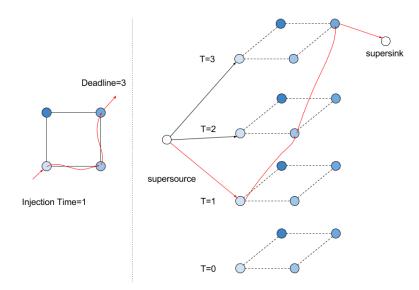

| 3.6    | A valid flit route that respects the injection time and latency constraint                             | 39   |

| 3.7    | Algorithm of candidate paths generation                                                                | 41   |

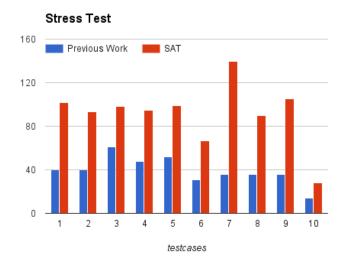

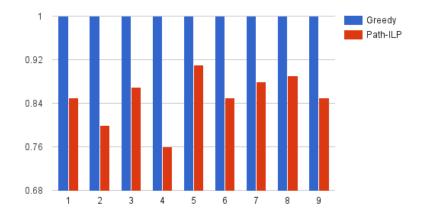

| 3.8    | The maximal number of packets can be routed. Cases 1-5: $6 \times 6$ mesh; cases 6-10: random topology | 45   |

| 3.9  | Normalized energy comparison for multimedia SoC cases                                                                                                                                                                                                                                                                                                                                                                                                                   | 51 |

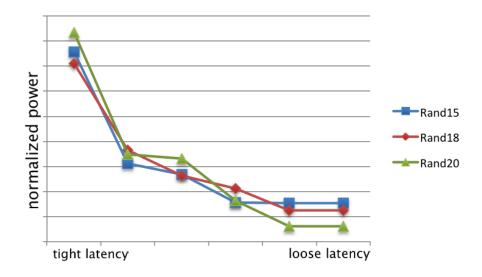

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.10 | Energy-latency tradeoff of 3 different cases.                                                                                                                                                                                                                                                                                                                                                                                                                           | 51 |

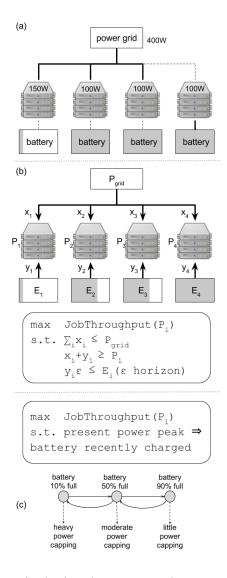

| 4.1  | (a) Single battery is depleted yet no need to cap power demand. (b) A static formulation: $x_i$ and $y_i$ are power provided by the power grid and battery, respectively. $P_i$ are the server power consumption. $E_i$ are the energy left in batteries. $\epsilon$ is a short time horizon starting from the current moment. (c) A Linear Temporal Logic formulation: the LTL constraint is transformed to a state machine that runs dynamically alongside the system | 53 |

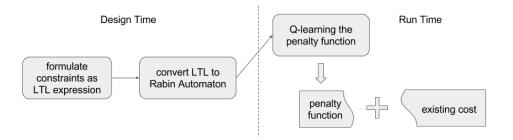

| 4.2  | An overview of LTL-based resources management.                                                                                                                                                                                                                                                                                                                                                                                                                          | 60 |

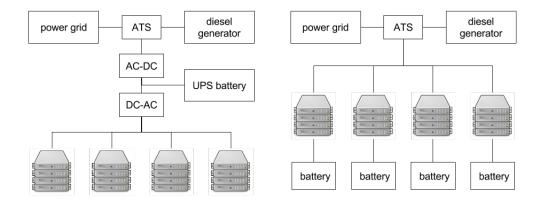

| 4.3  | Two power architecture of data centers                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62 |

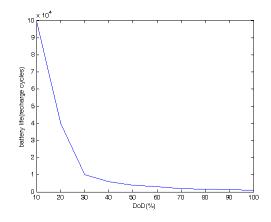

| 4.4  | Battery life deteriorates substantially for deeper discharge cycles                                                                                                                                                                                                                                                                                                                                                                                                     | 63 |

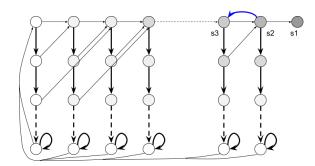

| 4.5  | DRA $\Gamma_{\phi}$ for power capping constraint.                                                                                                                                                                                                                                                                                                                                                                                                                       | 67 |

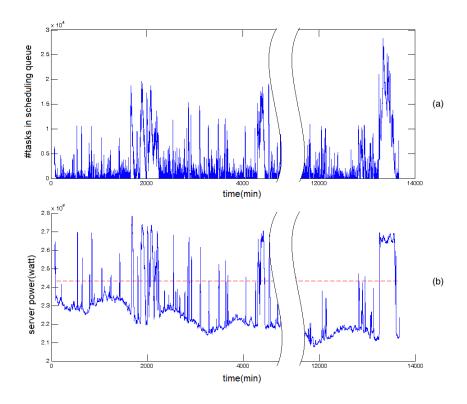

| 4.6  | Simulation of 10-day trace.                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69 |

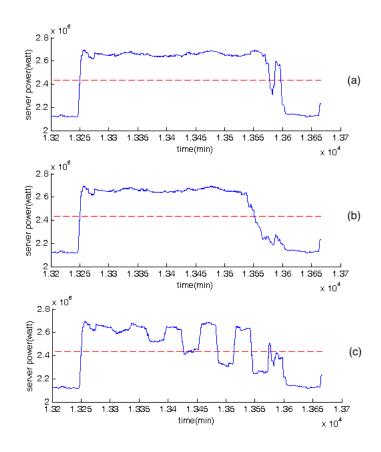

| 4.7  | Power demand for peak at 1320 minute with (a) $F$ , (b) $ClustCtrl$ , (c) $F + LTL$                                                                                                                                                                                                                                                                                                                                                                                     | 71 |

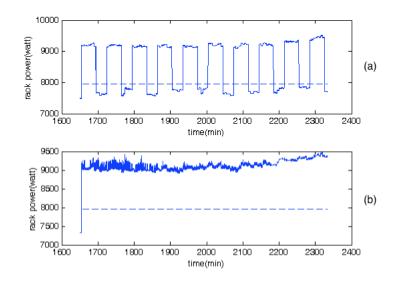

| 4.8  | F + LTL and hard bounding method on a particular rack with heterogenous job distribution. (a) Power capping by $F + LTL$ . (b) Power capping is not exerted for hard bounding method and a high battery depletion time ensues.                                                                                                                                                                                                                                          | 73 |

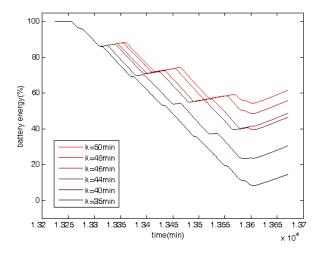

| 4.9  | Modulate n to adjust battery life to a desired level                                                                                                                                                                                                                                                                                                                                                                                                                    | 74 |

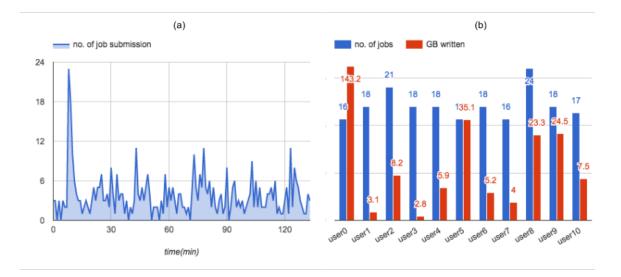

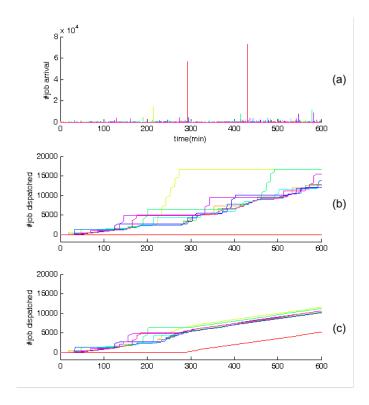

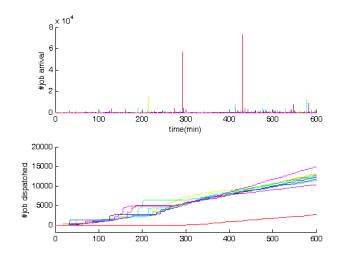

| 4.10 | 200 MapReduce jobs are randomly assigned to 11 users. The job submission lasts for 2 hours.                                                                                                                                                                                                                                                                                                                                                                             | 76 |

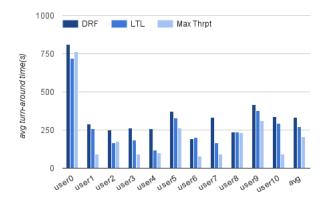

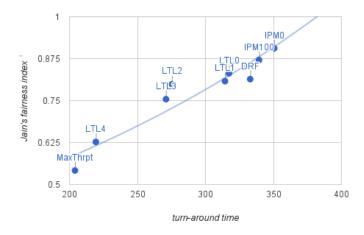

| 4.11 | The height of the last bar shows the average performance. The evenness of the bars indicates the resource allocation fairness. Max-throughput and DRF schedulers are on the extremes of the performance-fairness tradeoff. LTL falls in-between.                                                                                                                                                                                                                        | 79 |

| 4.12 | Performance-fairness tradeoff of DRF, 5 LTL and 2 IPM schedulers                                                                                                                                                                                                                                                                                                                                                                                                        | 79 |

| 4.13 | Max-throughput vs. round-robin. Round-Robin scheduler enforces <i>max-</i><br><i>min fairness</i> with a throughput degradation (20%)                                                                                                                                                                                                                                                                                                                                   | 82 |

| 4.14 | The max-throughput scheduler is augmented with starvation-free LTL con-  |    |

|------|--------------------------------------------------------------------------|----|

|      | straint $\phi$                                                           | 83 |

|      |                                                                          |    |

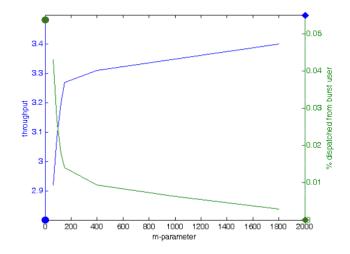

| 4.15 | Throughput-fairiness trade-off by modulating m. A continuous trade-off   |    |

|      | curve is achieved between max-throughput scheduler (diamonds) and round- |    |

|      | robin scheduler (circles).                                               | 83 |

## LIST OF TABLES

## TABLE

| 2.1 | Naïve method with only forward body bias (FBB). Power overhead, total area overhead, number of adaptive blocks% are denoted by $\Delta W$ ( $\mu W$ ), $\Delta A$ ( <i>unit</i> ), #B, respectively           | 26 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Our method with only forward body bias (FBB). Gate area overhead% is denoted by $\Delta A_g$ ( <i>unit</i> )                                                                                                  | 27 |

| 2.3 | Naïve method with forward body bias and reverse body bias (ABB). Power overhead, total area overhead, number of adaptive blocks% are denoted by $\Delta W (\mu W)$ , $\Delta A (unit)$ , $\#B$ , respectively | 28 |

| 2.4 | Our method with forward body bias and reverse body bias (ABB). Gate area overhead% is denoted by $\Delta A_g$ (unit)                                                                                          | 29 |

| 3.1 | Experimental results on 144 cases with timeout limit as 4 hours. The run-<br>time $T$ is for only the successful runs                                                                                         | 43 |

| 3.2 | Main results for TGFF cases.                                                                                                                                                                                  | 49 |

| 3.3 | Optimality test on small TGFF cases                                                                                                                                                                           | 50 |

| 4.1 | LTL syntax.                                                                                                                                                                                                   | 57 |

| 4.2 | LTL constrained power capping summary.                                                                                                                                                                        | 64 |

| 4.3 | Simulation and design parameters.                                                                                                                                                                             | 68 |

| 4.4 | Run time of PRISM model checker.                                                                                                                                                                              | 68 |

| 4.5 | Overall result of the 10-day trace. BatDepTime is the total amount of time rack batteries are depleted and records hazardous status of the datacenter.                                                        | 70 |

| 4.6 | Deterioration of hard bounding method with heterogeneous job distribution.                                                                                                                                    | 72 |

| 4.7 | Increase power budget to achieve the same AvgDoD as $F + LTL$                                                                                                                                                 | 74 |

| 4.8 | Schedulers of different turn-around time and fairness. Jain's index = 1 is |    |

|-----|----------------------------------------------------------------------------|----|

|     | the most fair case                                                         | 78 |

#### 1. RESOURCE MANAGEMENT IN COMPUTER HARDWARE

#### **1.1 Resource Management in Different Scope**

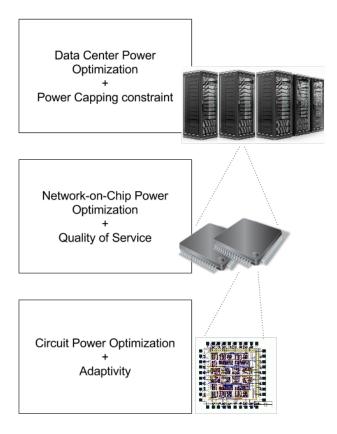

As the scale of computation system grows, proper resource management is becoming a crucial part to wield the power of computer hardware. Some examples of the resources to be allocated and provisioned are memory, cpu time, power budget and network bandwidth. These resources are usually competed for among instances in a large distributed system. For example, a data center may have more than 10K servers running collaborative tasks to perform a single big data analysis job. The servers are not homogenous because the hardwares are usually replaced batch by batch in a three-year rotation. So the performance and power profile of the servers may vary by a large extent inside the data center. In addition, the power supply network forms a hierarchical architecture. Power budget is split among different domains, racks and ultimately server machines. The complexity of resource management is well demonstrated considering the power capping problem in presence of server heterogeneity, location and power supply architecture.

In addition, resource management exists in various level of the system. Take power management as an example. In the data center level, the voltage and frequency of processors can be tuned down and servers can be put into sleep state by the power manager. In the chip level, part of the circuit that is not essential to the overall performance can be downsized to save power. The nature of the power management in different level is also very different. Power consumption of a data center is highly dynamic because of the workload fluctuation. A proper power manager should adapt its strategy, for example the power budget allocation, in the run time. The time scale for such adaptation is in hours, days or even months. In contrast, the computer chips cannot be altered after manufacture. Power management in this scale is mostly in the design time.

Figure 1.1: Resource management in multiple level.

What makes the problem more complex is the other design goals that are intertwined with the power management. For instance, to combat variation in the circuit, the ability to adapt to these variations needs to be added to the circuit. Adaptivity and power is intertwined because the power reduction techniques usually squeeze the safety work margin of the digital circuit, thus increases the need of adaptivity. In network resource management, power reduction can only be considered when the Quality-of-Services is not hurt. In the design of a power management policy, these other design goals should also be taken into account.

### **1.2** An Algorithmic Approach

In this dissertation, we study the resource management algorithms in different level of the computing hardware. In section 2, a Lagrangian-Relaxation-based algorithm is designed to optimize the gate implementation of the circuit. The algorithm minimizes the circuit power consumption and leaves a sufficient safety margin to combat variation for the circuit with adaptivity injected. The algorithm is run in design time with a probabilistic modeling of how much variation the circuit may suffer in the run time. In section 3, we look at the opportunity to tailor a Network-on-Chip specifically for a priori knowledge of the traffic pattern. We show the possibility to configure the packet routing and link bandwidth using a power-aware algorithm. With the help of proper network resource management, Quality-of-Service can be achieved in a power efficient manner. In the last section, we propose a way to enhance conventional resource managers with new design goals and constraints. The method is based on Q-learning and Linear Temporal Logic (LTL). LTL is used to formulate desired property of the system and then transformed into a state machine running alongside the original resource manager. The state machine warns the original resource manager about potential violations of the desired property. Our experiments show the method attains better tradeoff compared to existing methods.

#### 2. OPTIMIZATION FOR ADAPTIVE CIRCUIT\*

## 2.1 Introduction

Since the invention of silicon-based Integrated Circuit (IC), the density of transistors on a chip has grown exponentially over the years. In 1997, the Intel Pentium II processor is made of 7.5 million transistors with 350nm technology. Less than twenty years later, the 22-core Xeon Broadwell-E5 processor registered a transistor count of 7.2 billions with 14nm technology. As the process technology of digital circuit approaches the fundamental physical limit, this trend is unlikely to continue. Nevertheless, the integration density of modern IC has brought up great challenges in chip design. One of these challenges is the effect of variation.

Variation is the difference in the attributes of transistors such as length, width and oxide thickness. Variation is introduced when the chips are fabricated or in use. Sources of variation include manufacture process [1], device aging [2] and thermal fluctuations [3]. Process variation is the result of imperfections in the manufacturing process. These imperfections include the diffraction of light used in lithography, the variation in thickness when the gate oxide is grown, and the random fluctuation in the number of impurity atoms doped into the channel region of a transistor. Device aging causes the wear-out effect of Hot Carrier Injection (HCI) and Bias Temperature Instability (BTI), hence degrades the speed of transistors unevenly throughout the lifetime of the aging circuit. The temperature fluctuations of a chip may come from the ambient temperature change or the power dissipation of the circuit itself. An increase in temperature typically causes a decline of carrier mobility and an increase of interconnect resistance, hence slows down the circuit.

<sup>\*</sup>Part of this section is reprinted with permission from H. He, J. Wang, and J. Hu, "Collaborative gate implementation selection and adaptivity assignment for robust combinational circuits", in Low Power Electronics and Design, 2015 IEEE/ACM International Symposium on, 2015.

Because of the dwindling process technology, the variation of digital circuits has a higher and higher impact on the overall circuit. This imposes a big threat to the performance as well as the efficiency of the circuit. To compensate for the potential loss in the speed of transistors, digital designs often have to target for the worst degree of variation expected. Consequently, the transistors will be over-sized for the typical case, and thus consume more power and die area.

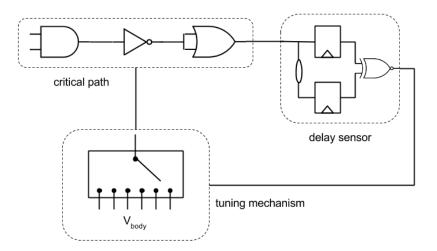

Adaptive circuit has been recognized as a power-efficient technology to overcome various variation throughout the entire life of hardware chips. Adaptive circuit contains variation sensors and tuning units in addition to the original circuit. The power and performance tradeoff of the circuit is tuned to compensate the variation after manufacture. Because of the existence of this post-silicon tuning mechanism, the chip design no longer has to tackle the worst-case scenario. Various tuning mechanism are proposed, such as body biasing [1], voltage adaptation [4], circuit reconfiguration [5].

Figure 2.1: An example of adaptive circuit through body biasing.

The effectiveness and overhead of adaptive circuit relies largely on its granularity, or the amount of circuit that is tuned together. With fine-grained adaptivity [4, 6], the circuit is able to adjust itself for fine level of variation, but large area overhead is incurred (50% area overhead for voltage interpolation [7] and 20% in [5, 6]). In contrast, coarse-grained adaptivity is applied to the entire die uniformly and is mostly for inter-die variations only. So it has relatively small overhead (0.2% reported in [8]).

The granularity problem limits the application of adaptive circuits. Coarse-grained adaptive circuit must adapt to the worse-case variation across the die, therefore it may either boost up the not-so-bad parts, causing unnecessary power increase, or miss the opportunity to save power in those parts. The fine-grained adaptivity has the ability to pinpoint the right tuning for circuit blocks of hundreds or thousands of gates. However without a careful design, the area overhead of the additional adaptivity logic could easily out shadow its benefits.

In this work, we develop a general algorithm to optimize the adaptive circuit design with overhead control. Evidently, variation must be accounted and this makes the optimization problem rather difficult. We make use of Lagrangian relaxation (LR) that solves a multi-objective problem in two layers – subproblem and dual problem. The subproblem is focused on solution search for the weighted multiple objectives while the dual problem employs variability-aware models to guide the tradeoff among multiple objectives. As such, accurate models are used in a lightweight manner without causing too long runtime.

Our work provides a relatively complete adaptivity assignment solution for general adaptive circuit designs while the works of [9,10] focus on clustering and ABB. Compared to [11], which is restricted to linear, continuous models, our work is a discrete approach and compatible with realistic models in industry. Moreover, area overhead is explicitly handled in our work but neglected in [11]. Experimental results show that our method usually reduces adaptivity overhead by more than a half compared to a naïve approach.

When gate area is counted together, our method often reduces the overall overhead by more than 70%.

### 2.2 Related Work

In adaptive VLSI circuits, power/performance is tuned by body bias [1], voltage adaptation [4], circuit reconfiguration [5] or a combination of them. The purpose of the adjustment is to compensate performance variability due to manufacturing process variations, device aging, thermal fluctuations, etc.

The effectiveness as well as overhead of adaptive design highly depend on its granularity. Coarse-grained adaptivity, such as uniform adaptivity for an entire processor core, has relatively small amortized overhead (0.2% reported in [8]). However, coarse-grained adaptivity is mostly for compensating inter-die variations. When intra-die variations are more pronounced [12], fine-grained adaptivity [4,6] (in blocks of hundreds or thousands of gates) brings significantly more power savings. Evidently, fine-grained adaptivity tends to entail large overhead of sensors, voltage regulators and control circuits (50% area overhead for voltage interpolation [7] and 20% in [5,6]).

Obviously, one prefers the power savings from fine-grained adaptivity but not its large overhead. The adaptivity overhead has been mentioned in several previous works [5–7], however, it has rarely been a main emphasis. The objective of [9, 10] is to minimize the overhead of adaptive body bias (ABB), but it assumes ABB is applied to all clusters. Another work [13] restricts variation sensors only at timing critical paths so that the overhead is not excessively large. However, it does not consider control or voltage generation overhead.

Adaptive design is highly related with conventional circuit optimization. A joint designtime and post-silicon tuning optimization algorithm is proposed in [11]. It assumes that gate size can be continuously changed while most of modern designs are based on highly discrete cell libraries. Variability-aware discrete gate sizing is discussed in [14, 15]. These works are focused on how to propagate statistical timing information during sizing without much emphasis on the optimization aspect.

### 2.3 Background

## 2.3.1 Lagrange Relaxation

Lagrange relaxation is a mathematical optimization framework that converts a difficult constrained optimization problem to a simpler relaxed formulation. By solving this relaxed formulation, it is possible to obtain an approximation to the optimal solution of the original problem. When the problem has a certain structure, it can be proven that the solution of the Lagrange relaxation problem is actually optimal.

In the most general form, an optimization problem solves

$$min_x \quad f(x)$$

s.t.

$$g_i(x) \le 0$$

$$h_j(x) = 0$$

(2.1)

The problem has an objective function  $f(\cdot)$ , several inequality constraints  $g_i(\cdot)$  and several equality constraints  $h_j(\cdot)$ . Lagrange relaxation of the problem is

$$\max_{u \ge 0, v} \min_{x} \mathcal{L}_{u, v}(x)$$

$$\mathcal{L}_{u, v}(x) = f(x) + \sum_{i} u_{i} g_{i}(x) + \sum_{j} v_{j} h_{j}(x)$$

(2.2)

The Lagrange function  $\mathcal{L}_{u,v}(x)$  can be viewed as a relaxation of the original problem. Instead of having hard equality and inequality constraints, the Lagrange relaxation allows constraint violations but penalizes the constraint violations in the objective.  $min_x \quad \mathcal{L}_{u,v}(x)$ is called the primal problem, and  $max_{u\geq 0,v}\mathcal{D}(u,v) = max_{u\geq 0,v} \quad min_x \quad \mathcal{L}_{u,v}(x)$  is called the dual problem. u, v are called dual variables or Lagrange multipliers. Note the range of the dual variables for inequality constraint is the half space  $u \ge 0$ .

$\mathcal{L}_{u,v}(x)$  has several interesting characteristics. Firstly, it is a linear function of dual variables u and v. This means  $min_x \quad \mathcal{L}_{u,v}(x)$  is concave with respect to u, v. Secondly, the original problem can be viewed as a min-max problem

$$min_x \quad max_{u \ge 0, v} \quad \mathcal{L}_{u, v}(x)$$

$$\mathcal{L}_{u, v}(x) = f(x) + \sum_i u_i g_i(x) + \sum_j v_j h_j(x)$$

(2.3)

If  $g_i(x) \leq 0$  and  $h_j(x) = 0$ , then the maximizer of  $\mathcal{L}_{u,v}(x)$  is  $u_i = 0$ . Otherwise,  $\max_{u\geq 0,v}\mathcal{L}_{u,v}(x) = \infty$  because either a coefficient of  $u_i$  is positive, or a coefficient of  $v_j$  is non-zero. So the minimization over x in the front will ensure the former condition is met, which means feasibility of the equality and inequality constraints. As such, the Lagrange relaxation swaps the minimization and the maximization operation. It can be shown the min-max problem (original problem) is equivalent to the max-min problem (Lagrange relaxation) when  $f, g_i, h_j$  are all convex functions.

### 2.3.2 Gate Sizing

Gate sizing is a well-studied topic in physical design of digital circuits. The input for the gate sizing process is a circuit with timing requirements. The algorithm adjusts the gate sizes to increase its power efficiency and to satisfy the timing constraint of the circuit.

Specifically, the circuit under design is represented as a Directed Acyclic Graph (DAG). The primary inputs of the circuit are the nodes in the graph without fanin. The primary outputs of the circuit are the nodes without fanout. The timing requirements are the signal arrival time a on the primary inputs and required arrival time q on the primary outputs. The timing requirement is that all signals that arrives at the primary inputs at a are transmitted to primary outputs no later than q.

Figure 2.2: Timing constraint of circuit design.

Each gate has a discrete number of size options  $1 \times, 2 \times, ...$  The size option has an effect on the power consumption as well as the gate delay. Gate sizing corresponds to the problem to find a size option for each gate such that the timing constraint is respected and the total circuit power is minimized.

## 2.3.3 Variation Modelling

There are two primary types of variations present in the circuit design. The first is interdie variation, in which all devices in the chip shift towards the same variation but different chips bear different variations. The other is intra-die variation, in which the variation's impact on the same chip is not uniform. The intra-die variation can cause the components of the chip design to diverge from the design specifications. This poses a threat to the functionality and performance of the chips. For example, the timing profile of a computer chip may become different from the critical path analysis in the design time. In contrast, the inter-die variation is relatively easier to compensate because it is uniform across the entire chip.

| Block 1 | Block 2 |

|---------|---------|

| Block 3 | Block 4 |

$$\sum = \begin{pmatrix} \sigma_{11} & \sigma_{12} & \sigma_{13} & \sigma_{14} \\ \sigma_{21} & \sigma_{22} & \sigma_{23} & \sigma_{24} \\ \sigma_{31} & \sigma_{32} & \sigma_{33} & \sigma_{34} \\ \sigma_{41} & \sigma_{42} & \sigma_{43} & \sigma_{44} \end{pmatrix}$$

Figure 2.3: Correlation matrix is defined to model the variation.

There can be multiple sources for the intra-die variation such as the variations in channel length and gate oxide thickness. The variations from different sources are usually assumed statistically independent. For example, the delay of a single gate d is calculated as the Taylor expansion

$$d = d_0 + \sum_i \frac{\partial d}{\partial p_i} \Delta p_i \tag{2.4}$$

where  $p_i$  denotes a single source of variation,  $\frac{\partial d}{\partial p_i}$  is the derivative of the delay model with

respect to  $p_i$ ,  $d_0$  is the nominal delay.

Note variation  $\Delta p_i$  in quation 2.4 is actually a function of gate position (x, y). The intra-die variation  $\Delta p_i(x, y)$  is often modeled as a multivariate Gaussian vector over the spatial location of the 2D circuit [16] [17]. Suppose a circuit is partitioned into 4 blocks, we can define the correlation of each pair of blocks in a  $4 \times 4$  matrix  $\Sigma$ . The delay variation of the gates in each block then follows  $\delta_{delay} \sim N(0, \Sigma)$ .

## 2.3.4 Adaptive Body Biasing

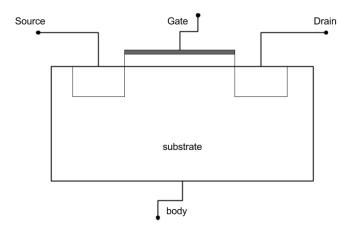

Figure 2.4: Body biasing a transistor.

Figure 2.4 shows the cross section through a MOSFET transistor. Body biasing is a technology to apply voltage to the substrate of the device. Reverse body biasing, i.e. applying a negative biasing voltage, is often used to reduce leakage power of the transistor. The bias voltage  $V_{bs}$  affects both the delay and the leakage power of the transistor.

$$V_{th} = V_{th0} + \gamma (\sqrt{2\phi_F + V_{bs}} - \sqrt{2\phi_F})$$

$$P_{leakage} = V_{dd}I_{subn} + |V_{bs}|(I_{jn} + I_{bn})$$

$$I_{subn} = \frac{W}{L}I_S[1 - e^{-\frac{V_{dd}}{V_T}}]e^{-\frac{V_{th} + V_{off}}{nV_T}}$$

$$d = \frac{d_0}{(V_{dd} - V_{th})^{\alpha}}$$

(2.5)

$P_{leakage}$  is the leakage power. d is the gate delay.  $V_{dd}$  is the power supply voltage.  $I_{subn}$  is the sub threshold leakage current.  $V_{th0}$ ,  $\gamma$ ,  $\phi_F$ ,  $I_{jn}$ ,  $I_{bn}$ .  $I_S$ ,  $V_T$ , W, L,  $V_{off}$ ,  $d_0$ ,  $\alpha$  are device parameters or empirical constants. It is shown in [9] that  $P_{leakage}$  can be approximated by a quadratic function of  $V_{bs}$  and d by a linear function.

#### 2.3.5 Static Timing Analysis

Static Timing Analysis (STA) is a tool to analyze the timing of the combinational circuit in design time. The input of STA is the circuit topology, delays of gates in the circuit, arrival time a and required arrival time q in the primary inputs and outputs of the circuit. Figure 2.5 shows the a simple example of STA. Each node in the figure represents a gate and the delay is given by d. The results of STA are the arrival time a and required arrival time q on each gate (gates that are not primary inputs or primary outputs).

The arrival time a is calculated by a forward traversal of the circuit graph. The arrival time at the output of a gate is given by  $a_g = max_{i \in fanin(g)}(a_i + d_g)$ . That is, the arrival time is the worst case arrival time of its fanins plus the gate delay. The arrival time shows when a signal will propagate to the gate in the worst case. Similarly, the required arrival time is calculated by a backward traversal. The required arrival time at the input of a gate is given by  $q_g = min_{i \in fanout(g)}(q_i) - d_g$ . The required arrival time shows the time before which a signal must arrive at the point. Once the arrival time and required arrival time are obtained for every point in the graph, the slack is calculated as q - a. It shows the how tight the timing requirement is at that point.

Figure 2.5: An example for Static Timing Analysis.

## 2.4 **Problem Formulation**

The input to our algorithm is a placed combinational circuit, timing constraints and adaptivity clusters. The combinational circuit can be viewed as a DAG. The nodes in this graph correspond to digital gates in the combinational circuit. The edges represent wire connections among gates. A combinational circuit has a set of primary inputs and outputs, through which the signals flow in and out of the circuit of interest. For all the primary inputs, the arrival time  $a_i$  of signals are specified. For all the primary outputs, the required arrival time  $q_j$  are specified. Timing constraint is the requirement that the longest time needed for a signal to propagate from input *i* to output *j* is less than  $q_j - a_i$ . In addition, we assume the circuit has been clustered into a set of blocks  $\mathcal{B} = \{B_1, B_2, ...\}$ . These blocks are the candidates to which the algorithm will assign adaptivity. If a block is assigned with adaptivity, the full set of variation sensor, tuning unit and control policy implementation will be added to the design for the selected block. Once a tuning level (the voltage of body-biasing, the power supply of a dual Vdd gate, etc.) is set by the tuning unit, all gates in the same block will be affected. Note our algorithm decides whether to assign adaptivity to each block in the design time, but the tuning level is determined by the variations of the circuit and set in run time. The optimization objective and constraints include power, timing, robustness to variations and area overhead.

## 2.4.1 Placement and Clustering

To find the appropriate clustering for a combinational circuit is a non-trivial task. Several aspects need to be taken into consideration. First of all, the variation of the clustered gates should be statistically correlated, since these gates are tuned together. The gates on the same signal path, for example, have correlated aging effect because they are usually turned on and off together. Secondly, gates in a circuit are not equally important for the timing constraint of the whole circuit. When variation is not present, timing of a digital circuit is determined by a set of critical paths. In the event of variation, path delay is a random variable, so the non-critical paths in the nominal sense may become critical. However the gates still impose an uneven impact to the final timing. As such, we want to make the cluster contain the most impactful gates. In addition, to properly implement the tuning mechanism by circuit, it is often required for the gates in a cluster to be placed in a contiguous region.

In our experiment, we only use the spatial location of the placed gates to form the clusters  $\mathcal{B} = \{B_1, B_2, ...\}$ . However, several work [9] [18] have been published on the clustering and placement of adaptive circuit. These more sophisticated algorithms can be easily incorporated into our adaptivity assignment method.

#### 2.4.2 Gate Implementation Selection

Gate implementation selection is closely coupled with adaptivity assignment problem, therefore our method performs a joint optimization of the two tasks. Gate implementation selection is a well-studied area in physical design of digital circuit. After the logic design of a digital circuit is finalized, the physical implementation of the gates in the circuit plays an important role on the correctness metric (e.g. timing) as well as the efficiency metric (e.g. power). Since the major concern of circuit variation is on the timing of the circuit, it is possible to rely solely on the gate implementation selection to combat the variation. However, this approach would be inefficient in the sense that all the manufactured chips must be designed to handle the worst-case variation, while only a small fraction will actually experience the worst-case variation. With the option to make part of the circuit adaptive, this worst-case oriented design can be avoid. Since adaptivity itself also incur an implementation cost, we rely on the algorithm to determine the right trade-off between adaptivity and gate implementation selection.

In our work, we consider two kinds of gate implementation options: gate size and threshold voltage. The larger size a gate is implemented in circuit, the faster the gate is and the more die area it consumes. Similarly, a decrease in the threshold voltage of a gate will cause an increase in speed as well as leakage power consumption.

Apart from gate size and threshold voltage, we consider the case of Adaptive Body Biasing (ABB). The adaptive circuit tunes the biasing voltage of the circuit blocks to compensate for variation. The power and delay model for a single gate v is  $power_v(V_{th}, X_{size}, V_{bias}) \approx leakage_{V_{th}, X_{size}}^v * quadratic(V_{bias})$

$$+ \alpha V_{dd}^2 f \sum_{u \in fanout(v)} C_{V_{th}, X_{size}}^u$$

(2.6)

$$delay_v(V_{th}, X_{size}, V_{bias}) \approx linear(V_{bias}) * R^v_{V_{th}, X_{size}} * \sum_{u \in fanout(v)} C^u_{V_{th}, X_{size}}$$

In equation 2.6,  $X_{size}$  denotes the size of the gate,  $V_{th}$  denotes the threshold voltage,  $V_{bias}$  denotes the body biasing voltage level.  $leakage_{V_{th},X_{size}}, R_{V_{th},X_{size}}, C_{V_{th},X_{size}}$  are the leakage power, output resistance and input capacitance of a gate, respectively. These parameters for available  $V_{th}, X_{size}$  can be found in a standard cell library. Previous work [9] shows the effect of body biasing on power can be accurately approximated by a quadratic function quadratic ( $V_{bias}$ ) and the effect on delay by linear ( $V_{bias}$ ).

### 2.4.3 Adaptivity Assignment

For each block  $\mathcal{B} = \{B_1, B_2, ...\}$ , the 0-1 decision variable  $\Phi(B_i)$  chooses whether the block should become adaptive. If the block is adaptive, the tuning mechanism can offset the body biasing level of the block to one of several discrete options  $V_{bias}^1, V_{bias}^2, ..., V_{bias}^n$ . The body biasing voltage affects the power and delay of the circuit as formulated in 2.6. An adaptive block enables the optimization to choose smaller size and higher threshold voltage implementation for the gates, and thus reduce the average-case power consumption. However, it also pays an area overhead for implementing the tuning mechanism in circuit. We approximates these overhead using a linear function.

$$A(B_i) = k \sum_{v \in B_i} Area_v + b \tag{2.7}$$

#### 2.4.4 Collaborative Gate Implementation Selection and Adaptivity Assignment

We formulate the gate implementation selection and adaptivity assignment problem as a joint optimization.

$$min \quad E_{V_{bias}}(power(\vec{\xi}, V_{bias}))$$

$$subject \ to \quad max_{V_{bias}}\mathcal{P}(a_v + delay_v(\vec{\xi}, V_{bias}) + \delta_{delay_v} < a_u) > probability \ limit \quad (2.8)$$

$$A(G) = \sum_i A(B_i)\Phi_{B_i} < overhead \ limit$$

We let  $\vec{\xi} = (V_{th}, X_{size})$  for simple notation. *G* is the circuit.  $a_v$  is the signal arrival time of gate *v*.  $a_v$  for the primary inputs and outputs are constants obtained from the design.  $a_v$ for the intermediate nodes are variables set by the optimization.

In this formulation, the objective is set to minimize the expected power consumption of the circuit. The expectation is over the body biasing level  $V_{bias}$  tuned by the adaptive circuit. Because the variation is random, the tuning level  $V_{bias}$  is also random. To calculate  $E_{V_{bias}}(power(\vec{\xi}, V_{bias}))$ , the probability of each tuning level is required. We assume a monotonic relation between the minimum slack of the circuit and the tuning level. The probability is calculated by quantizing the distribution of the minimum slack in the circuit.

$$E_{V_{bias}}(power(\vec{\xi}, V_{bias})) = \sum_{i} \mathcal{P}(V_{bias}^{i} * power(\vec{\xi}, V_{bias}^{i})$$

$$\mathcal{P}(V_{bias}^{i}) = \mathcal{P}(l_{i} < min \ slack < h_{i})$$

(2.9)

The timing constraint asserts the gate needs to be fast enough to propagate signal from v to u, when the tuning level  $V_{bias}$  is set to the highest compensating level. Because the variation  $\delta_{delay}$  is Gaussian, we can easily translate the probability limit to a variance limit. For example, 99.7% probability means the gate delay must have at least 3 standard deviation slack.

### 2.5 Overview of Adaptivity Assignment Algorithm

Figure 2.6: Overview of algorithm flow.

The overall algorithm is shown in figure 2.6. The algorithm iterates between gate implementation selection and adaptivity assignment. The gate implementation selection part is handled by Lagrangian relaxation (LR). Its formulation is to minimize power dissipation subject to timing constraints with consideration of variations. Area is not explicitly in the formulation as power and area are correlated in gate sizing. By solving the problem in two layers of Lagrangian subproblem and dual problem, the calls to SSTA can be restricted to the dual problem part. Then, the subproblem can be solved using simple models while the overall solution quality is not compromised due to the SSTA guidance in solving the dual problem. The problem size of adaptivity assignment is significantly smaller and allows SSTA to be called more frequently. Therefore, the adaptivity assignment is solved by a sensitivity-based heuristic.

### 2.5.1 Lagrange Primal Problem: Gate Implementation Selection

The primal problem follows the standard Lagrangian Relaxation framework. The constrained optimization problem described in 2.8 is transformed to an unconstrained primal problem. In this step, the adaptivity assignment is fixed. This means whether a block has adaptivity is known for the primal problem.

$$min \quad \mathcal{L}_{\vec{\mu}}(\vec{\xi}) = E(power(\vec{\xi})) + \sum_{v} \mu_{v}(delay_{v}(\vec{\xi}) + \delta_{delay_{v}})$$

(2.10)

where  $\vec{\mu}$  is the Lagrangian dual variables,  $\vec{\xi}$  is the decision variables for gate size and threshold voltage [19].  $power_v(\cdot)$  is the power model of an individual gate.  $delay_v(\cdot)$  is the delay model of the gate v.

The objective is a weighted sum of power consumption and timing constraint, the Lagrangian dual problem is responsible for finding the optimal weights  $\mu_v$  to balance power and speed. Because the problem is combinatorial, we employ a dynamic-programmingbased previous work [20] to solve it. Here we use a simple example to show the algorithm.

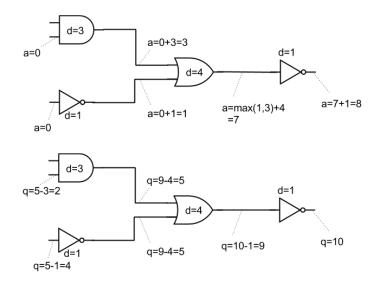

Figure 2.7: An example of dynamic programming algorithm.

Figure 2.7 shows a simple circuit of 3 gates. The algorithm starts from the primary

outputs and work its way back in reverse topological order. The NOT gate has 3 options for gate implementation and the OR gate has 2 options. Each option achieves a different trade-off between the power consumption and the speed of the gate. Because the NOT gate and the OR gate are only examined individually at this stage, it is not possible to tell which option is better. So all options are kept in the gates. In the next stage, the upstream AND gate is examined. A cross product of the options of its fan-out gates is performed. This includes all possible combination of gate implementation of two branches of the AND gate. Then, the algorithm carries out a pruning operation on the 6 cross product options. An option is said to be "inferior" if both the weighted objective and the input capacitance are larger than the other option. The weighted objective indicates the power and speed cost of downstream gates. The input capacitance determines the option's effect on upstream gates. After the pruning operation, only the options that are in the Pareto frontier of upstream-downstream tradeoff are kept.

#### 2.5.2 Statistical Static Timing Analysis

Static Timing Analysis (STA) is widely adopted to analyze the timing aspect of digital circuit. In essence, STA finds the worst-case signal arrival time of a gate's inputs, and add the delay of the gate itself. When large variation is present, the gate delay becomes a random variable. More importantly, the delay of different gates are correlated because the variation is correlated. A proper timing analysis is supposed to represent and calculate the correlation among gates in the circuit. To this end, several Statistical Static Timing Analysis (SSTA) methods are proposed. In this work, we use a previous work [17] to perform SSTA for the circuit under design.

The work in [17] models the spatial correlation of variation as a Gaussian multivariate function. The circuit is first partitioned into blocks  $L_1, L_2, ..., L_n$  and a  $n \times n$  correlation matrix  $\Sigma$  is specified.  $\Sigma$  captures the correlation of any two blocks. Then a Principal Component Analysis (PCA) is performed. The result of PCA enables the representation of gate delay variation in the form

$$delay_v = d + \sum_i k_i \epsilon_i \tag{2.11}$$

where d is the nominal delay that is calculated through the same procedure as STA,  $k_i$  are the PCA coefficients and  $\epsilon_i$  are standard Gaussian variables  $\epsilon_i \sim N(0, 1)$  that are independent with each other.

The power of this representation lies in its ability to compute correlation quickly. For example, if gate A has delay  $d_A + 3\epsilon_1 - 2\epsilon_2$  and gate B has delay  $d_B + 2\epsilon_1 + 2\epsilon_2$ , then  $corr(A, B) = E[(3\epsilon_1 - 2\epsilon_2) * (2\epsilon_1 + 2\epsilon_2)] = E[6\epsilon_1^2 - 4\epsilon_2^2] = 2.$

Figure 2.8: An example of SSTA.

Again we use an example to show how SSTA works. Figure 2.8 is an example of

circuit broken into 4 blocks. After performing PCA on the correlation matrix of the 4 blocks, we obtain the variational delay of gate A,B,C,D,E in terms of two independent Gaussian variables  $\epsilon_1$  and  $\epsilon_2$ . Note gate D and E have the same variation because they are in the same block. We assume gate A and B are the primary inputs that input signals arrive at time 0. Then the signal arrival time at the output of each gate  $\alpha_A$ ,  $\alpha_B$ ,  $\alpha_C$ ,  $\alpha_D$ ,  $\alpha_E$  can be calculated by performing a topological order traversal of the graph. For single input gates, the variation on its output is the sum of variation on its input and the variation of the gate delay. Hence the output variation is still Gaussian. When a gate has multiple inputs, a  $MAX(\cdot)$  operation is applied, and the output variation is no long Gaussian. But we can calculate a linear approximation [17] of the resulting variation such that the computation is tractable.

From SSTA we can also obtain the distribution of timing slack (the slack of the gate delay beyond which the circuit will fail). Timing yield of a circuit is the probability that any gate in the circuit has a negative slack.

#### 2.5.3 Lagrange Dual Problem

The dual problem solves  $\mu_{u,v}$  in equation 2.10. It is well known the dual problem

$$max_{\vec{\mu}} \quad \mathcal{D}_{\vec{\mu}} = max_{\vec{\mu}} \quad min_{\vec{\xi}} \quad \mathcal{L}_{\vec{\mu}}(\vec{\xi})$$

(2.12)

is a concave problem, and a subgradient for  $\mu_v$  is

$$\frac{\partial \mathcal{D}_{\vec{\mu}}}{\partial \mu_v} = delay_v(\vec{\xi}) \tag{2.13}$$

We use subgradient ascent to update  $\mu_v$  at each inner iteration of figure 2.6.

Algorithm 1 Sensitivity-based adaptivity assignment. **Require:** Circuit G composed by blocks  $\mathcal{B} = \{B_1, \overline{B_2, ...\}}$ 1: Timing yield constraint  $\Upsilon$ 2: Adaptivity area constraint  $\Omega$ 3: Perform statistical static timing analysis 4: while (true) do if  $Y(G) < \Upsilon$  then 5: mode  $\leftarrow$  timing  $\mathcal{B}^* \leftarrow \{B_i | \Phi(B_i) = 0\}$ 6: 7: else mode  $\leftarrow$  overhead  $\mathcal{B}^* \leftarrow \{B_i | \Phi(B_i) = 1\}$ 8: 9: end if  $\alpha \leftarrow A(G) > \Omega ? 1 : 0 ; // A(G)$ : area overhead 10:  $B^* \leftarrow \arg \max_{B \in \mathcal{B}^*} \theta(B)$ 11:  $\Phi(B^*) \leftarrow \Phi(B^*) ? 0 : 1 ; //$  Trial adaptivity change 12: perform SSTA, obtain  $Y^*(G)$  and  $A^*(G)$ 13: if mode == timing and  $Y^*(G) > Y(G)$  then 14: 15: continue end if 16: if mode == overhead then 17: if  $\alpha$  and  $A^*(G) < A(G)$  then 18: continue 19: end if 20: if (power reduced) and  $A^*(G) \leq \Omega$  then 21: 22: continue end if 23: end if 24:  $\Phi(B^*) \leftarrow \Phi(B^*) ? 0 : 1 ; // Undo adaptivity change$ 25: 26: end while

# 2.6 Adaptivity Assignment Algorithm

Our algorithm iteratively assigns or deassigns adaptivity for a block. Depending on if timing yield Y(G) evaluated by an SSTA, each iteration may be in either timing mode or overhead mode. If  $Y(G) < \Upsilon$ , the timing mode tries to add adaptivity to improve circuit robustness. If  $Y(G) \ge \Upsilon$ , the overhead mode attempts to remove adaptivity from a block to reduce power and area overhead. Timing mode sensitivity  $\theta_t(B)$  for a block B is defined by

$$\theta_t(B) = \sum_{g \in B} \Delta_{delay}(g) \cdot \sqrt{\psi_t(g)}$$

$$\Delta_{delay}(g) = (d_g(\phi_0) - \sum_{i=1}^{max} P_B(\phi_i) \cdot d_g(\phi_i))$$

(2.14)

where  $d_g(\phi_i)$  is the gate g delay with adaptivity level  $\phi_i$  and  $P_B(\phi_i)$  is the probability that block B operates with adaptivity level  $\phi_i$ . The number of timing critical paths  $\psi_t(g)$ passing through g is defined by

$$\psi_t(g) = \sum_{u \in fanin(g), fanout(g)} \begin{cases} 1 & \text{if } \tilde{s}(u) \le 0.5 \tilde{s}_{min} \\ 0 & \text{otherwise} \end{cases}$$

(2.15)

where  $\tilde{s}(u)$  is the slack at node u and  $\tilde{s}_{min}$  is the minimum slack over the entire circuit. The tilde here indicates that they are mean plus certain  $\sigma$  (standard deviation) value.

The overhead mode sensitivity  $\theta_o(B)$  is defined by

$$\theta_o(B) = \frac{\sum_{g \in B} \Delta_W(g) + W_B}{\sum_{g \in B} \Delta_{delay}(g) \cdot \sqrt{\psi_o(g)}}$$

$$\Delta_W(g) = \left(\sum_{i=1}^{max} P_B(\phi_i) \cdot w_g(\phi_i) - w_g(\phi_0)\right)$$

(2.16)

where  $w_g(\phi_i)$  is the power dissipation of gate g when it is at adaptivity level  $\phi_i$  and  $W_B$ is the adaptivity power overhead for block B. The number of timing critical paths  $\psi_o(g)$ passing through g in the overhead mode is defined by

$$\psi_o(g) = \sum_{u \in fanin(g), fanout(g)} \begin{cases} 1 & \text{if } \tilde{s}(u) \le 1.5 \tilde{s}_{min} \\ 0 & \text{otherwise} \end{cases}$$

(2.17)

In timing (overhead) mode, the block  $B^*$  without (with) adaptivity and the maximum  $\theta_t$  ( $\theta_o$ ) is selected. A trial adaptivity change is made for  $B^*$  based on the sensitivity. Then, we consider if to commit this trial change according to SSTA, area and power analysis. In timing mode, the commitment is based on timing yield improvement. In overhead mode, we first check adaptivity area overhead, which has a hard constraint. If the constraint is not satisfied and the area is reduced, then the change is committed. The third case for commitment is when power dissipation is reduced. The iteration continues as long as we see improvements on either of these three cases, and terminates when no such improvement is obtained. The pseudo code for this heuristic is given in Algorithm 0.

# 2.7 Experiment Result

Table 2.1: Naïve method with only forward body bias (FBB). Power overhead, total area overhead, number of adaptive blocks% are denoted by  $\Delta W$  ( $\mu W$ ),  $\Delta A$  (*unit*), #B, respectively.

|             |        |                 | Baseline |       | Naïve      |                |         |

|-------------|--------|-----------------|----------|-------|------------|----------------|---------|

| Circuit     | #gates | $ \mathcal{B} $ | Yield    | Yield | $\Delta W$ | $\Delta A/\#B$ | CPU (s) |

| c432        | 171    | 4               | 94.9%    | 99.3% | 6564       | 707/4          | 1       |

| c499        | 218    | 5               | 91.6%    | 97.7% | 10975      | 1433/5         | 1       |

| c880        | 383    | 5               | 96.3%    | 98.9% | 5123       | 809/4          | 1       |

| c1355       | 562    | 4               | 88.8%    | 99.9% | 26442      | 1587/4         | 2       |

| c1908       | 972    | 6               | 75.9%    | 99.9% | 19049      | 1380/4         | 4       |

| c2670       | 1287   | 5               | 94.6%    | 98.2% | 6156       | 947/2          | 5       |

| c3540       | 1705   | 5               | 73.6%    | 99.9% | 21952      | 1759/4         | 8       |

| c5315       | 2351   | 6               | 90.9%    | 99.8% | 29364      | 2602/4         | 10      |

| c6288       | 2416   | 6               | 93.9%    | 99.9% | 50323      | 1931/2         | 11      |

| c7552       | 3625   | 5               | 41.8%    | 99.9% | 42878      | 3291/4         | 18      |

| usb_phy     | 609    | 6               | 88.0%    | 99.3% | 1729       | 518/2          | 2       |

| edit_dist   | 130661 | 29              | 81.3%    | 99.9% | 15460      | 24640/5        | 804     |

| fft         | 32281  | 20              | 81.2%    | 99.1% | 194576     | 15742/5        | 310     |

| cordic      | 41601  | 20              | 73.9%    | 99.5% | 443511     | 22618/10       | 493     |

| des_perf    | 112644 | 22              | 83.5%    | 99.2% | 204159     | 43608/6        | 750     |

| matrix_mult | 155325 | 20              | 44.0%    | 99.1% | 1382050    | 78028/14       | 1378    |

| Ave         | rage   |                 | 80.8%    | 99.3% | 153769     | 12600/4.9      | 237     |

|              |               |                 | Baseline                |       |            | Ours           |              |         |

|--------------|---------------|-----------------|-------------------------|-------|------------|----------------|--------------|---------|

| Circuit      | #gates        | $ \mathcal{B} $ | Yield                   | Yield | $\Delta W$ | $\Delta A/\#B$ | $\Delta A_g$ | CPU (s) |

| c432         | 171           | 4               | 94.9%                   | 99.9% | 2524       | 323/1          | 7%           | 1       |

| c499         | 218           | 5               | 91.6%                   | 99.9% | 3688       | 355/2          | -26%         | 3       |

| c880         | 383           | 5               | 96.3%                   | 99.3% | 1790       | 504/1          | 14%          | 3       |

| c1355        | 562           | 4               | 88.8%                   | 99.4% | 12922      | 388/2          | -17%         | 5       |

| c1908        | 972           | 6               | 75.9%                   | 99.8% | 9162       | 762/2          | -5%          | 9       |

| c2670        | 1287          | 5               | 94.6%                   | 99.1% | 544        | 176/1          | -7%          | 12      |

| c3540        | 1705          | 5               | 73.6%                   | 99.6% | 13924      | 603/2          | -13%         | 16      |

| c5315        | 2351          | 6               | 90.9%                   | 99.2% | 3350       | 293/1          | 0%           | 24      |

| c6288        | 2416          | 6               | 93.9%                   | 98.9% | 10549      | 1248/1         | 4%           | 24      |

| c7552        | 3625          | 5               | 41.8%                   | 99.9% | 20053      | 404/3          | -16%         | 40      |

| usb_phy      | 609           | 6               | 88.0%                   | 99.3% | 779        | 167/1          | -3.9%        | 6       |

| edit_dist    | 130661        | 29              | 81.3%                   | 99.3% | 4430       | 7781/2         | 0%           | 1937    |

| fft          | 32281         | 20              | 81.2%                   | 99.2% | 32167      | 10376/3        | 0%           | 759     |

| cordic       | 41601         | 20              | 73.9%                   | 99.1% | 146446     | 9590/4         | 0%           | 1141    |

| des_perf     | 112644        | 22              | 83.5%                   | 99.4% | 5726       | 15060/2        | 0%           | 1795    |

| matrix_mult  | 155325        | 20              | 44.0%                   | 99.0% | -200650    | -47184/6       | -15%         | 3193    |

| Ave          | Average 80.8% |                 |                         | 99.4% | 4213       | 15/2.1         | -4.9%        | 561     |

| % difference | e vs. naïve   | · = `_          | urs–naïve)<br>bs(naïve) |       | -97.3%     | -99.8%/-57.1%  |              |         |

Table 2.2: Our method with only forward body bias (FBB). Gate area overhead% is denoted by  $\Delta A_g$  (*unit*).

To the best of our knowledge, there is no previous work on joint gate implementation selection and adaptivity assignment with consideration of overhead control. Therefore, we compare with the following approaches.

- Baseline. Variability-aware gate implementation selection without adaptivity. This is to emulate conventional non-adaptive designs.

- Naïve adaptivity assignment. If only forward body bias (FBB) is considered, adaptivity is assigned to any block that has negative slack in terms of mean plus certain  $\sigma$ value. This is to emulate what designers may do for adaptive circuit design without adaptivity optimization tools. In ABB where both FBB and reverse body bias are allowed, the naïve method simply assigns adaptivity for all blocks. Actually this is

Table 2.3: Naïve method with forward body bias and reverse body bias (ABB). Power overhead, total area overhead, number of adaptive blocks% are denoted by  $\Delta W$  ( $\mu W$ ),  $\Delta A$  (*unit*), #B, respectively.

|             |        |                 | Baseline |       | Naïve      |                |         |

|-------------|--------|-----------------|----------|-------|------------|----------------|---------|

| Circuit     | #gates | $ \mathcal{B} $ | Yield    | Yield | $\Delta W$ | $\Delta A/\#B$ | CPU (s) |

| c432        | 171    | 4               | 99.7%    | 99.5% | 1857       | 689/4          | 1       |

| c499        | 218    | 5               | 99.9%    | 99.9% | 664        | 1358/5         | 1       |

| c880        | 383    | 6               | 99.9%    | 99.6% | 1452       | 921/6          | 1       |

| c1355       | 562    | 4               | 99.8%    | 99.1% | 271        | 1354/4         | 2       |

| c1908       | 972    | 6               | 99.5%    | 99.2% | 2623       | 1550/6         | 4       |

| c2670       | 1287   | 5               | 99.9%    | 99.9% | -435       | 1543/5         | 5       |

| c3540       | 1705   | 5               | 99.9%    | 99.7% | -1481      | 1821/5         | 7       |

| c5315       | 2351   | 6               | 99.9%    | 99.9% | -3949      | 2668/6         | 10      |

| c6288       | 2416   | 6               | 99.9%    | 99.9% | -8302      | 2175/6         | 11      |