# INTERCONNECTED MODULAR MULTILEVEL CONVERTER (IMMC) USING WIDE BAND GAP DEVICES FOR MULTIPLE APPLICATIONS

#### A Dissertation

By

#### AHMED KHALID A ALLEHYANI

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Prasad Enjeti

Committee Members, Le Xie

Jun Zou

Mahmoud El-Halwagi

Head of Department, Miroslav M. Begovic

December 2018

Major Subject: Electrical Engineering

Copyright 2018 Ahmed Khalid A Allehyani

#### **ABSTRACT**

This dissertation proposes a high-power density Interconnected Modular Multilevel Converter (IMMC) with sinusoidal output voltage for multiple applications. The proposed converter utilizes wide band gap devices at a high switching frequency to achieve compact size/weight/volume. The proposed converter is modular in construction, employs high frequency L-C components and can be stacked for voltage sharing.

The IMMC is proposed for motor drives applications due to the following advantages: sinusoidal output with adjustable voltage and frequency (v/f), no acoustic noise, low EMI and absence of dv/dt related issues due to long motor leads. Two design examples for low voltage drives using Gallium Nitride (GaN) devices and medium voltage drives using Silicon Carbide (SiC) are discussed in this dissertation.

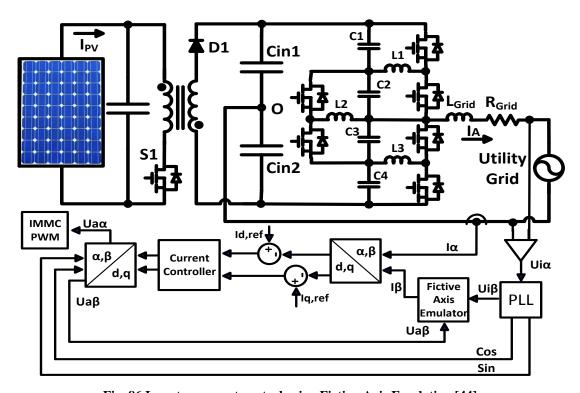

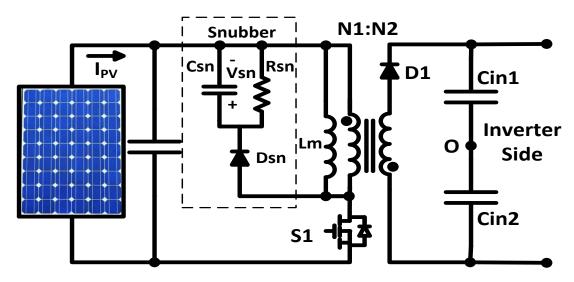

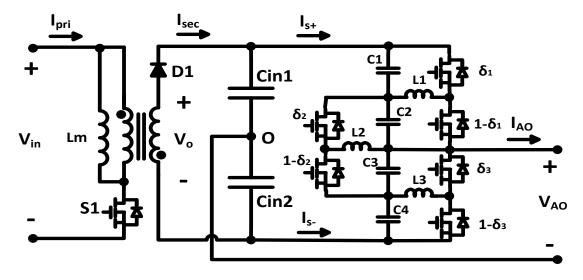

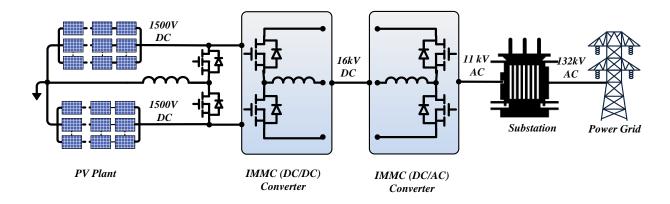

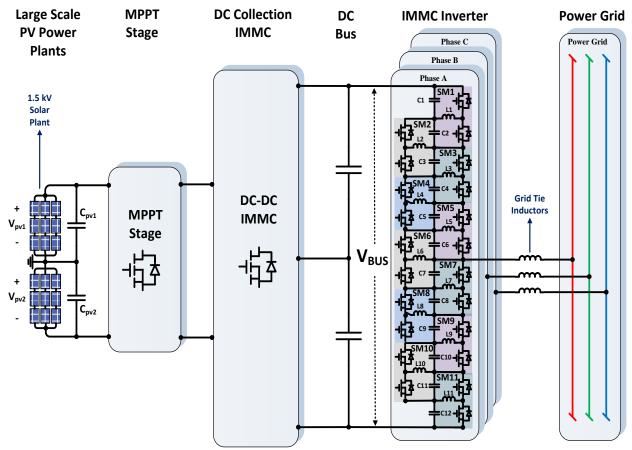

The proposed converter is also evaluated for solar micro-inverter applications due to its compact size and the high-quality output. The proposed system connects the inverter to the PV solar panel through a flyback converter for stepping up the voltage to the grid level, isolation and Maximum Power Point Tracking (MPPT). The proposed inverter eliminates the need for a bulky grid-tie inductor or complex LCL filter. The power can be injected to the grid using a small iron-core inductor due to the sinusoidal nature of the output voltage. A grid-tie control using Fictive Axis Emulation (FAE) is implemented on the converter to optimize the power injected to the grid. Moreover, a DC-AC IMMC to integrate two PV power plants through medium voltage DC collection grid (MVDC) system is proposed. The sinusoidal output of the IMMC facilitates the integration of the solar plants. The inductance required to connect the inverter to the grid is less due to the sinusoidal nature of the output of the IMMC.

#### **ACKNOWLEDGEMENTS**

All praise is to Allah for giving me the opportunity and strength to complete this dissertation. I owe every achievement and blessing in my life to him. I would like also to express my deepest gratitude to my parents who taught me everything, without their love and support I would have not accomplished this.

I am sincerely grateful to my supervisor Dr. Prasad Enjeti for his time, guidance and help. Although his schedule was extremely busy, he took the time to guide me to overcome all obstacles ranging from technical to professional. He was a great mentor and I am pleased to have worked with him.

I would like to thank the committee members Dr. Le Xie, Dr. Jun Zou and Dr. Mahmoud El-Halwagi for their time and effort. Their collaboration and feedback improved the overall quality of the dissertation.

I am very grateful to my friends and colleagues in the PQ Lab Sinan Al-Obaidi, Fahad Alhuwaishel, Salwan Sabry, Ahmed Morsy, Eric Pool, Jose Sandoval, Michael Daniel and all other PQ Lab members. Their presence made this journey much easier,

#### CONTRIBUTORS AND FUNDING SOURCES

#### **Contributors**

This work was supervised by a dissertation committee consisting of Professor Prasad Enjeti [advisor], Le Xie and Jun Zou of the Department of [Electrical Engineering] and Professor Mahmoud El-Halwagi of the Department of [Chemical Engineering].

All work conducted for this dissertation was completed by the student independently.

# **Funding Sources**

The main author of this dissertation, Ahmed Allehyani, is on a scholarship rewarded by the government of Saudi Arabia.

# TABLE OF CONTENTS

|                                                       | Page |

|-------------------------------------------------------|------|

| ABSTRACT                                              | ii   |

| ACKNOWLEDGEMENTS                                      | iii  |

| CONTRIBUTORS AND FUNDING SOURCES                      | iv   |

| LIST OF FIGURES                                       | vii  |

| LIST OF TABLES                                        | xiv  |

| 1. INTRODUCTION                                       | 1    |

| 1.1 Wide Band Gap (WBG) Devices.                      | 1    |

| 1.2 Literature Review: Multilevel Converters.         | 4    |

| 1.2.1 Neutral Point Clamped Converter (NPC)           | 5    |

| 1.2.2 Modular Multilevel Converter (MMC)              | 8    |

| 1.2.3 Cascaded H-Bridge Converter (CHB)               | 10   |

| 1.2.4 Flying Capacitor Converter (FCC)                | 11   |

| 1.3 Research Objective                                | 13   |

| 1.4 Thesis Outline                                    | 14   |

| 2. INTERCONNECTED MODULAR MULTILEVEL CONVERTER (IMMC) | 16   |

| 2.1 DC-DC IMMC                                        |      |

| 2.1.1 DC-DC IMMC Circuit Analysis                     | 17   |

| 2.2 Proposed DC – AC Topology                         | 22   |

| 2.3 Operation and Modulation                          | 23   |

| 2.4 DC-AC IMMC Circuit Analysis                       | 32   |

| 2.5 Comparison                                        | 39   |

| 3. DC TO AC IMMC FOR ADJUSTABLE SPEED AC MOTOR DRIVES | 45   |

| 3.1 Low Voltage Drives                                | 45   |

| 3.1.1 Low Voltage Drive Design Example                | 47   |

| 3.1.2 Simulation Results                              | 52   |

| 3.1.3 Experimental Results                          | 57  |

|-----------------------------------------------------|-----|

| 3.2 Medium Voltage Drives                           | 65  |

| 3.2.1 Medium Voltage Drive Design Example           |     |

| 3.2.2 Simulation Results                            | 73  |

| 3.2.3 Experimental Results                          | 77  |

| 4. SOLAR MICRO INVERTER                             | 84  |

| 4.1 Solar Photo-Voltaic (PV) Topologies             |     |

| 4.1.1 Central Inverter                              |     |

| 4.1.2 String Inverter                               |     |

| 4.1.3 Micro Inverter                                | 87  |

| 4.2 Problem Definition                              | 92  |

| 4.3 Proposed Topology                               | 94  |

| 4.4 Inverter Control                                | 96  |

| 4.5 Flyback                                         | 98  |

| 4.5.1 Boundary Condition Mode (BCM)                 | 98  |

| 4.5.2 Design Example                                | 99  |

| 4.6 Simulation Results                              | 102 |

| 5. GRID-TIE MEDIUM VOLTAGE DC COLLECTION SYSTEM FOR |     |

| SOLAR PV PLANTS                                     | 105 |

| 5.1 Conventional Solar Power Collection Systems     |     |

| 5.2 Proposed Grid-Tie Solar Power Collection System | 106 |

| 5.3 Experimental Results                            | 107 |

| 6. CONCLUSION AND FUTURE WORK                       |     |

| 6.1 Future Work                                     | 113 |

| REFERENCES                                          | 114 |

# LIST OF FIGURES

|         | Pa                                                                                                                                                                                                                            | age |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

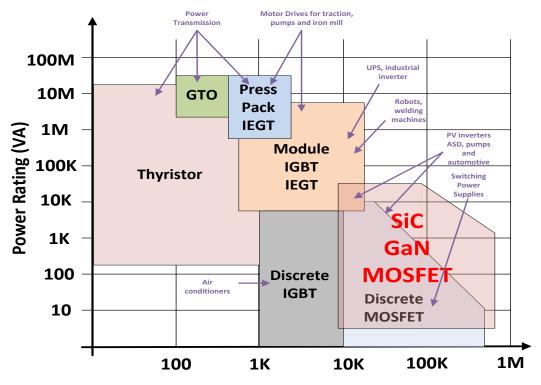

| Fig. 1  | Market integration of devices applications [2].                                                                                                                                                                               | 1   |

| Fig. 2  | Predicted applications for transistors [3]                                                                                                                                                                                    | 2   |

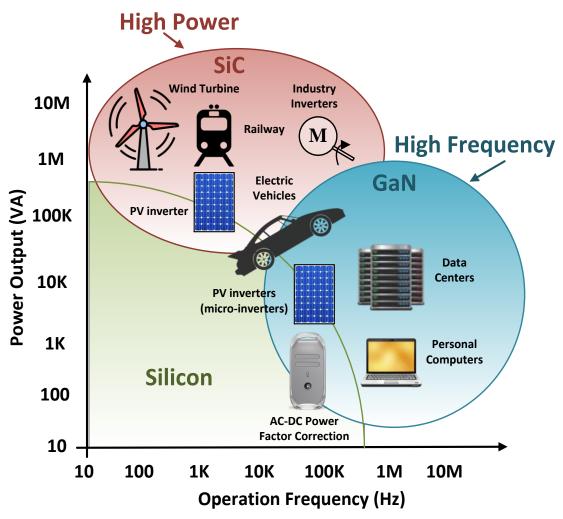

| Fig. 3  | Material property analysis of Wide Bandgap Devices [5].                                                                                                                                                                       | 3   |

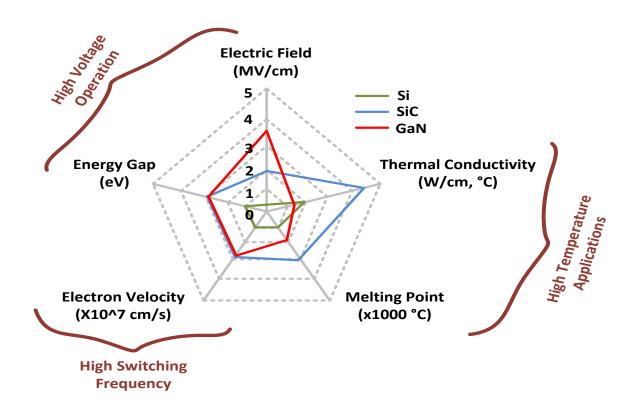

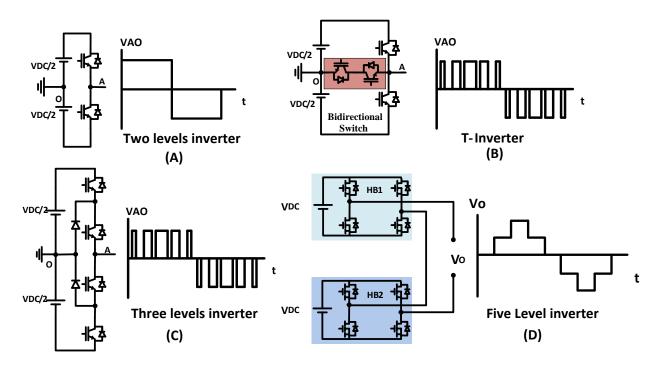

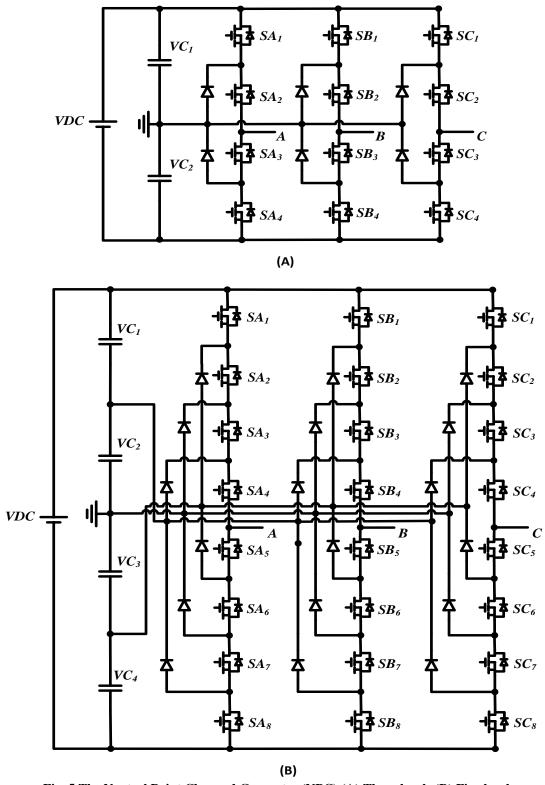

| Fig. 4  | Evolution of inverters (A) Two levels inverter (B) T-inverter (C) Three levels inverter (D) Five levels inverter.                                                                                                             | 5   |

| Fig. 5  | The Neutral Point Clamped Converter (NPC) (A) Three levels (B) Five levels                                                                                                                                                    | 6   |

| Fig. 6  | Three level Modular Multilevel Converter (MMC).                                                                                                                                                                               | 8   |

| Fig. 7  | Five Level Modular Multilevel Converter (MMC)                                                                                                                                                                                 | 9   |

| Fig. 8  | Five level Cascaded H-Bridge Converter.                                                                                                                                                                                       | 10  |

| Fig. 9  | Flying Capacitor Converter (FCC) (A) Three levels (B) Five Levels                                                                                                                                                             | 12  |

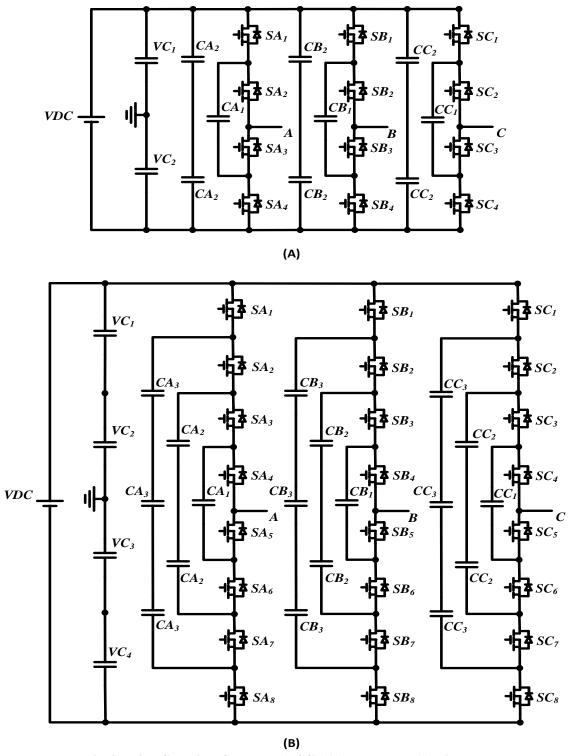

| Fig. 10 | The DC-DC version of the IMMC that can step up or step down the input voltage. Each submodule can be a half of full bridge (A) Buck IMMC (B) Boost IMMC (C) Half-bridge submodule (D) Full Bridge submodule                   | 16  |

| Fig. 11 | The DC-DC IMMC with the half-bridge submodules structure to step the voltage up or down (A) Buck IMMC (B) Boost IMMC                                                                                                          | 17  |

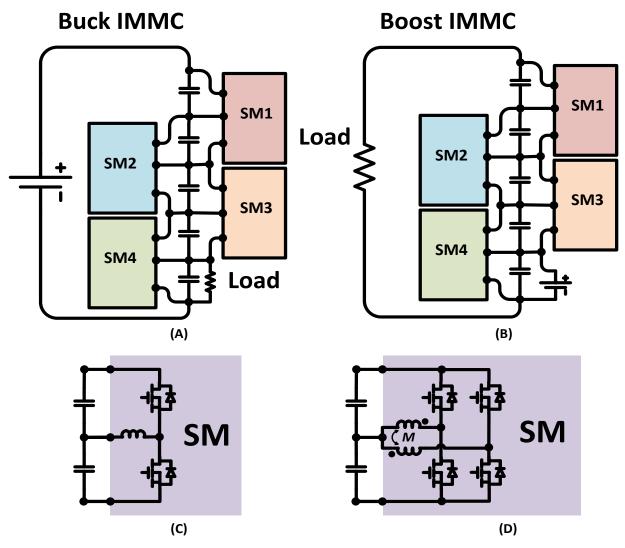

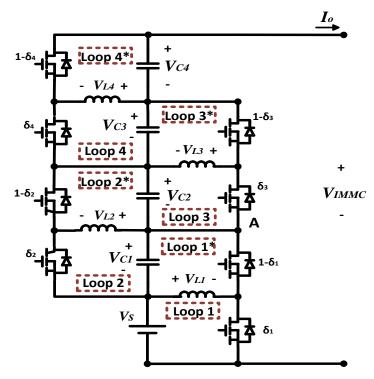

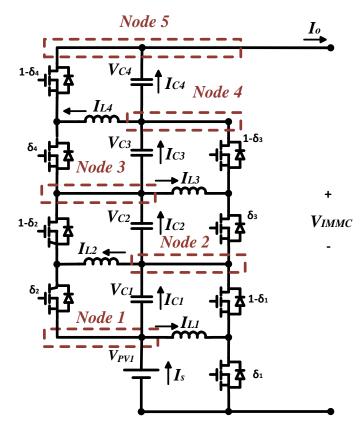

| Fig. 12 | Loops to determine the inductor equations                                                                                                                                                                                     | 18  |

| Fig. 13 | Nodes to derive the capacitors current equations.                                                                                                                                                                             | 21  |

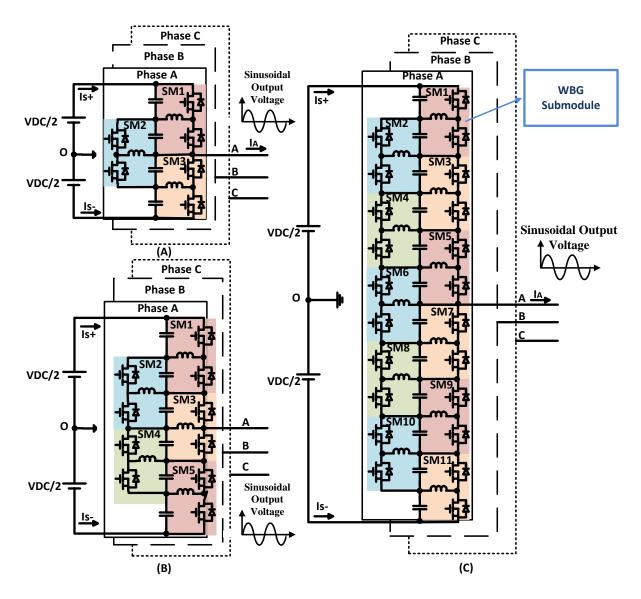

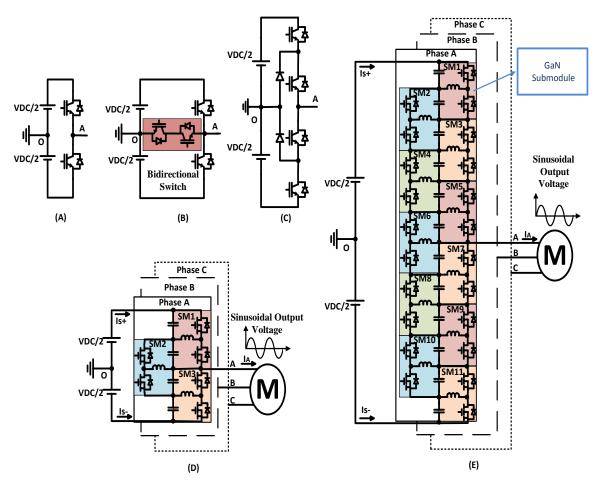

| Fig. 14 | (A), (B) and (C) shows the proposed IMMC with 3, 5 and 11 submodules respectively                                                                                                                                             | 22  |

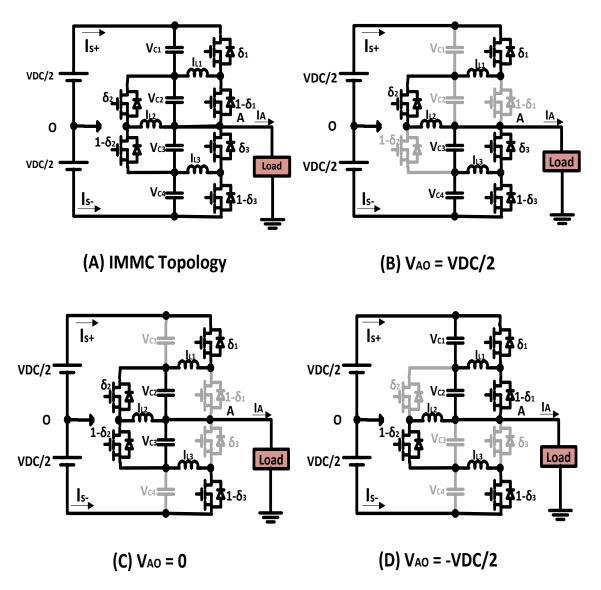

| Fig. 15 | (A) The proposed IMMC with for different operating modes. (B) The state to generate Vout= VDC/2. (C) The state to generate Vout= 0. (D) The state to generate Vout= -VDC/2. Note: $\delta$ is the duty ratio of the submodule | 24  |

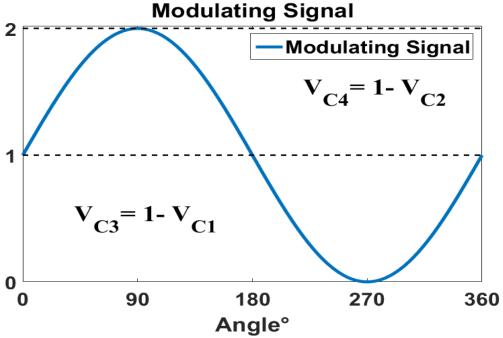

| Fig. 16 | The modulating signal for the 3 submodules design.                                                                                                                                                                            | 25  |

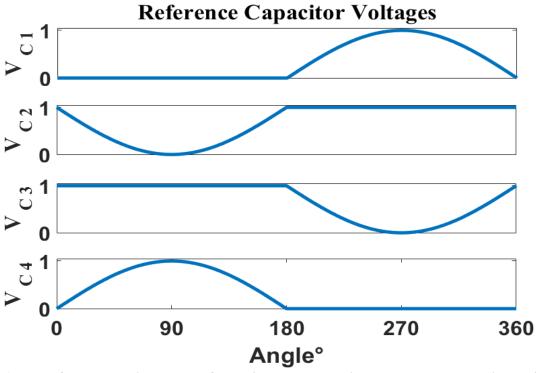

| Fig. 17 | The reference capacitor voltages for the 3 submodules design. The lower two capacitors reference voltages are one minus the corresponding upper capacitor reference voltage.                                                  | 25  |

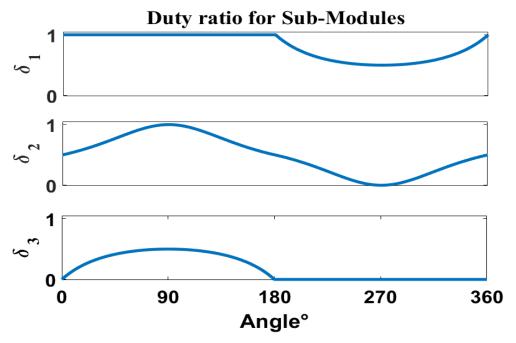

| Fig. 18 | The duty cycle for the three submodules. 81is the duty for SM1; 82 for SM2; 83 for SM3. The duty is calculated from the ratio of the two reference voltages of the submodules capacitors as illustrated in equation (21) and (22). Each submodule has two switches that work in a complementary manner to each other. | . 26 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

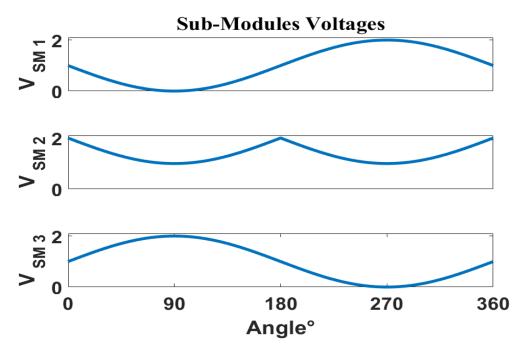

| Fig. 19 | The submodules voltage with 3 submodules. Note: $VSM1 = VC1 + VC2$ ; $VSM2 = VC2 + VC3$ ; $VSM3 = VC3 + VC4$ .                                                                                                                                                                                                        | . 26 |

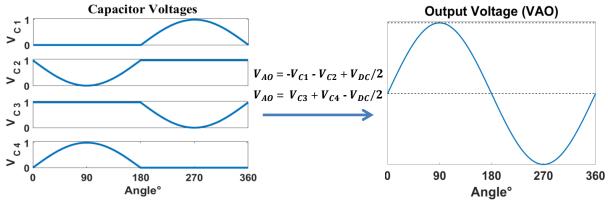

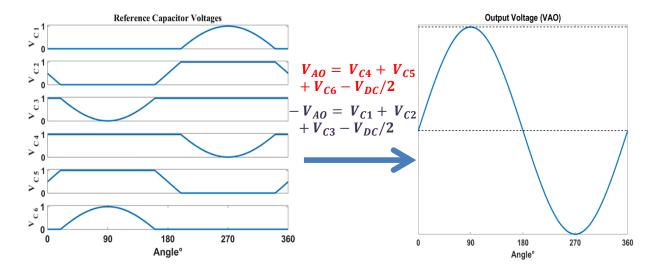

| Fig. 20 | shows how the converter works. Each capacitor is switched to have a slice of the sine wave and the output voltage is the sum of two capacitors minus <i>VDC</i> /2                                                                                                                                                    | . 28 |

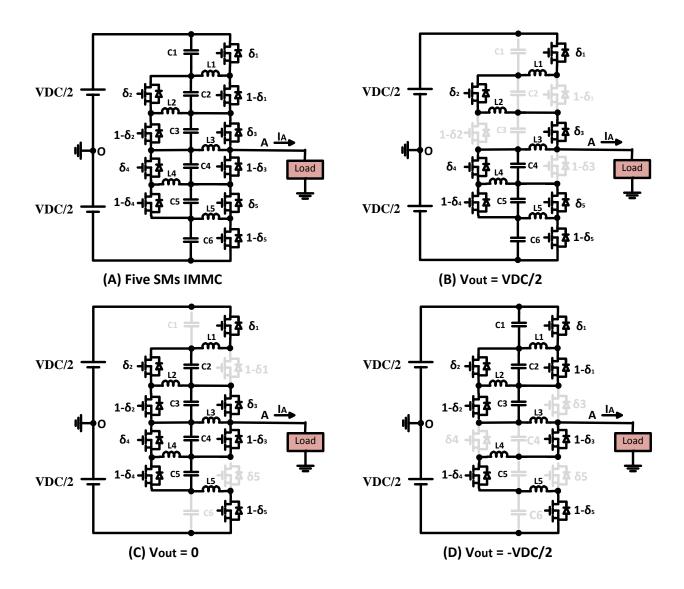

| Fig. 21 | (A) The proposed IMMC with five submodules. (B) The state to generate Vout= VDC/2. (C) The state to generate Vout= 0. (D) The state to generate Vout= - VDC/2. Note: $\delta$ is the duty ratio of the submodule                                                                                                      | . 29 |

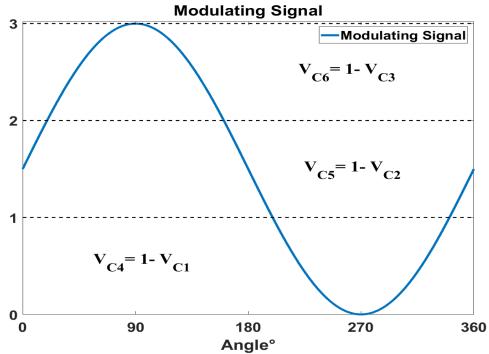

| Fig. 22 | The modulating signal for the 5 submodules design.                                                                                                                                                                                                                                                                    | . 30 |

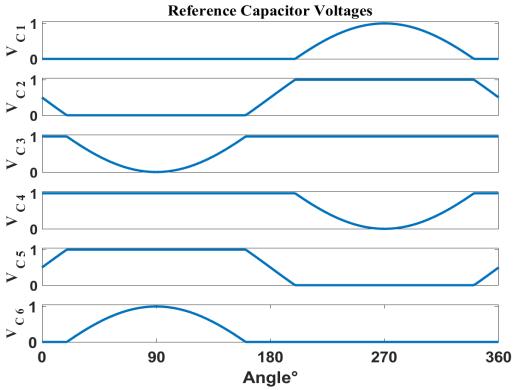

| Fig. 23 | The reference capacitor voltages for the 3 submodules design. The lower two capacitors reference voltages are one minus the corresponding upper capacitor reference voltage.                                                                                                                                          | . 30 |

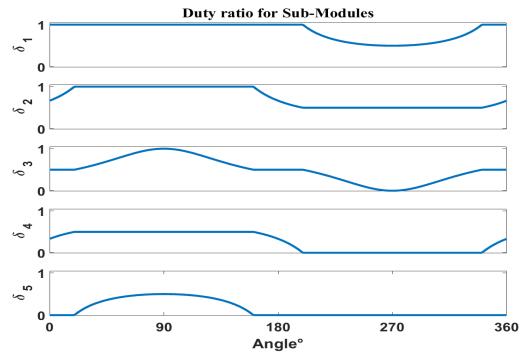

| Fig. 24 | The duty cycle for the three submodules. $\delta 1$ is the duty for SM1; $\delta 2$ for SM2; $\delta 3$ for SM3; $\delta 4$ for SM4; $\delta 5$ for SM5                                                                                                                                                               | . 31 |

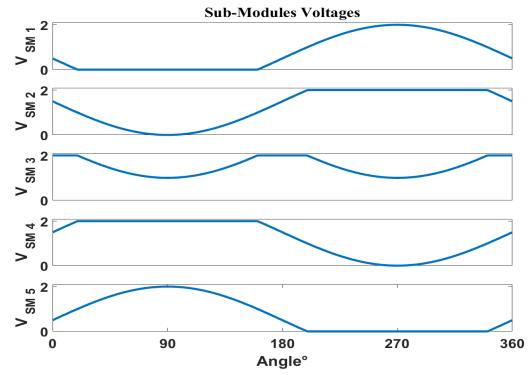

| Fig. 25 | The submodules voltage with 3 submodules. Note: $VSM1 = VC1 + VC2$ ; $VSM2 = VC2 + VC3$ ; $VSM3 = VC3 + VC4$ ; $VSM4 = VC4 + VC5$ ; $VSM5 = VC5 + VC6$                                                                                                                                                                | . 31 |

| Fig. 26 | The mechanism of the five submodule IMMC. Each capacitor is switched to have a slice of the sine wave and the output voltage is the sum of two capacitors minus VDC/2.                                                                                                                                                | . 32 |

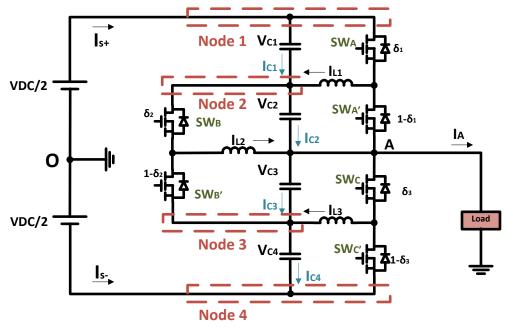

| Fig. 27 | Nodes to obtain the capacitors current equations.                                                                                                                                                                                                                                                                     | . 34 |

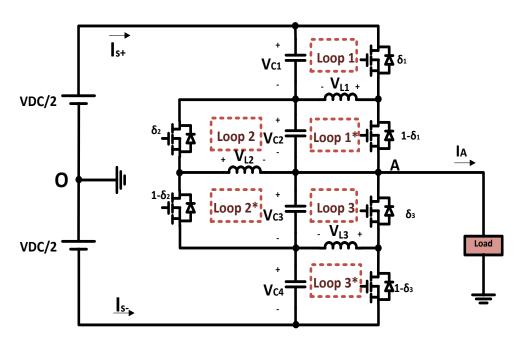

| Fig. 28 | Loops to obtain the inductors voltage equations.                                                                                                                                                                                                                                                                      | . 34 |

| Fig. 29 | Submodules current RMS rating as a function of the RMS output current in per unit for the 3 submodules design.                                                                                                                                                                                                        | . 37 |

| Fig. 30 | Submodules current RMS rating as a function of the RMS output current in per unit for the 5 submodules design.                                                                                                                                                                                                        | . 38 |

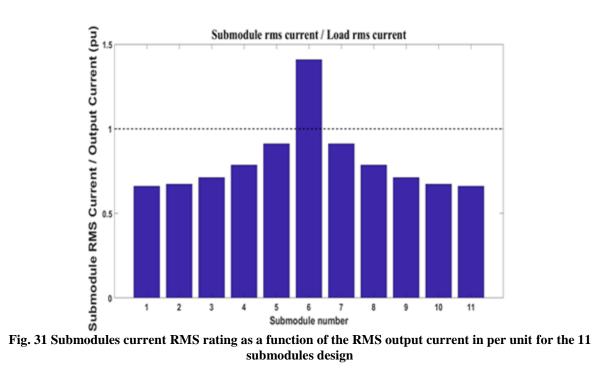

| Fig. 31 | Submodules current RMS rating as a function of the RMS output current in per unit for the 11 submodules design                                                                                                                                                                                                        | . 38 |

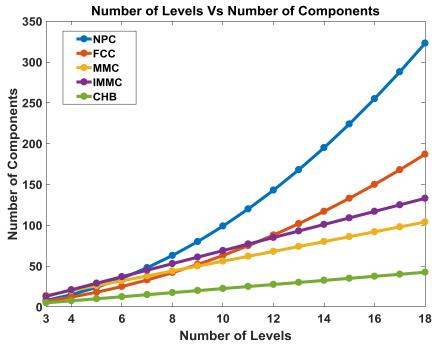

| Fig. 32 | Number of levels VS number of components.                                                                                                                                                                                                                                                                             | . 42 |

| Fig. 33 | Number of levels VS overall capacitor size index.                                                                                                                                                                                                                                                                                       | . 42 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

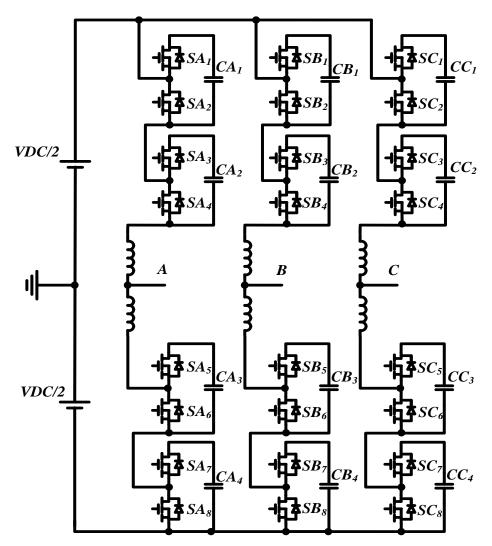

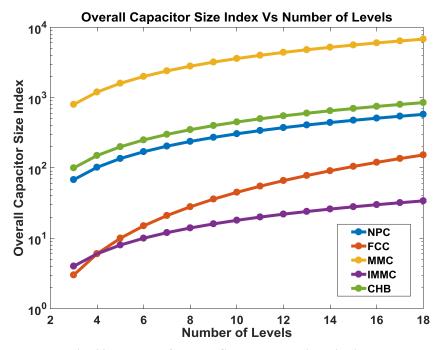

| Fig. 34 | (A) Two level inverter [22] (B) T-type three level inverter [20], (C) NPC inverter [4], (D) Proposed IMMC with 3 submodules to realize sinusoidal output voltage. (E) IMMC with 11 submodules. Note: The number of submodules can be increased to reduce the blocking voltage of the devices and to scale the voltage and power levels. | . 45 |

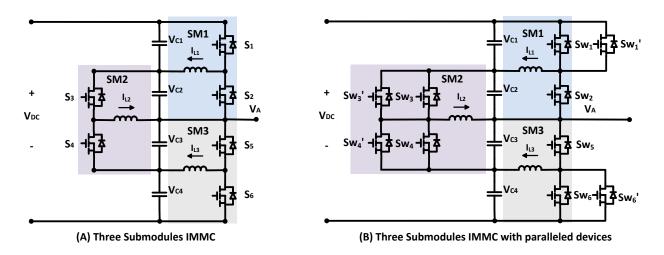

| Fig. 35 | The proposed 3 submodules IMMC shown in Fig. 34 (E) with parallel submodules to reduce current stress on the devices.                                                                                                                                                                                                                   | . 47 |

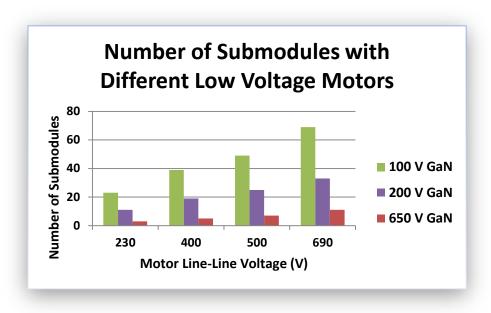

| Fig. 36 | The number of submodules needed for each motor rating.                                                                                                                                                                                                                                                                                  | . 48 |

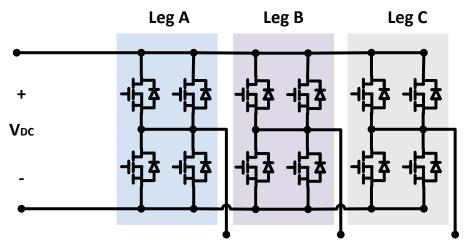

| Fig. 37 | A classic three phase inverter.                                                                                                                                                                                                                                                                                                         | . 51 |

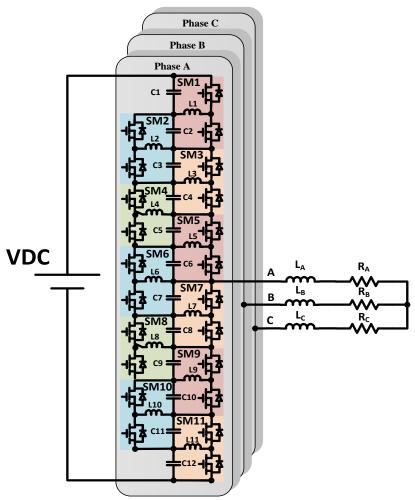

| Fig. 38 | The Simulated 11 submodules converter with a three phase RL-Load                                                                                                                                                                                                                                                                        | . 52 |

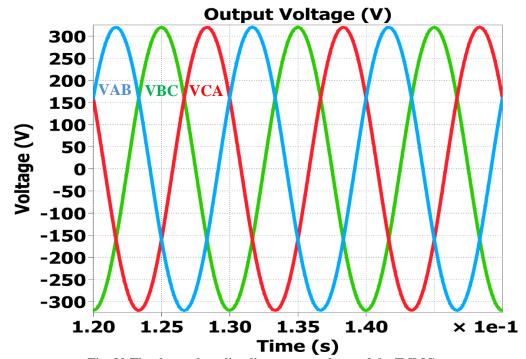

| Fig. 39 | The three-phase line-line output voltage of the IMMC.                                                                                                                                                                                                                                                                                   | . 54 |

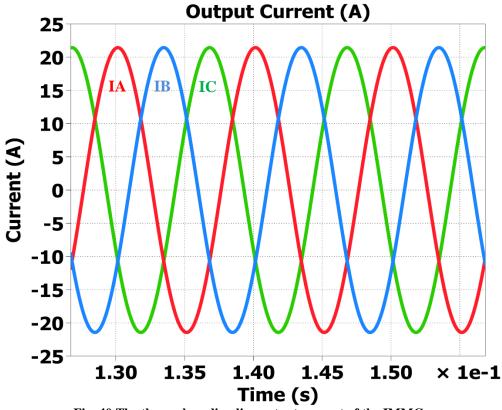

| Fig. 40 | The three-phase line-line output current of the IMMC.                                                                                                                                                                                                                                                                                   | . 54 |

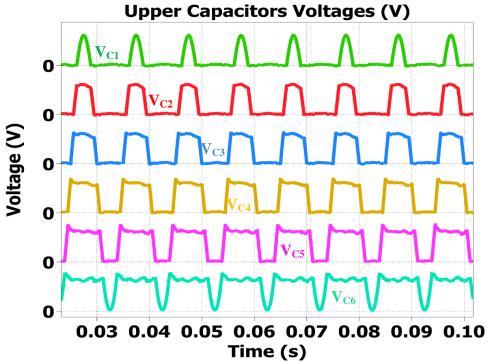

| Fig. 41 | The voltages of the upper capacitors (from $C_1$ to $C_6$ )                                                                                                                                                                                                                                                                             | . 55 |

| Fig. 42 | The voltages of the lower capacitors (from $C_7$ to $C_{12}$ )                                                                                                                                                                                                                                                                          | . 55 |

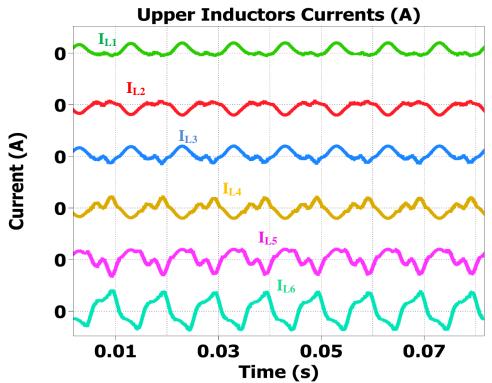

| Fig. 43 | The current through the upper inductors (from $L_1$ to $L_6$ )                                                                                                                                                                                                                                                                          | . 56 |

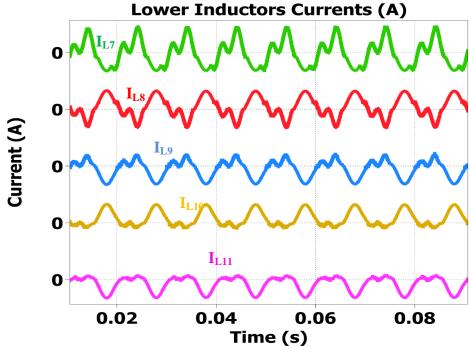

| Fig. 44 | The current through the lower inductors (from $L_7$ to $L_{11}$ )                                                                                                                                                                                                                                                                       | . 56 |

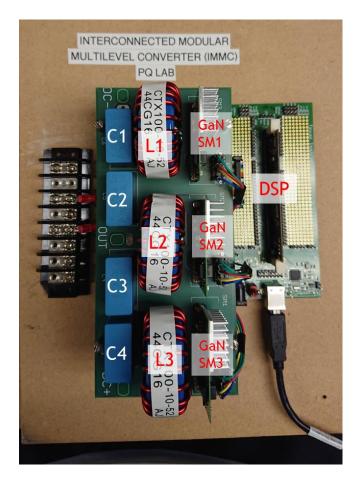

| Fig. 45 | The laboratory prototype built using TI LMG3410 GaN modules.                                                                                                                                                                                                                                                                            | . 57 |

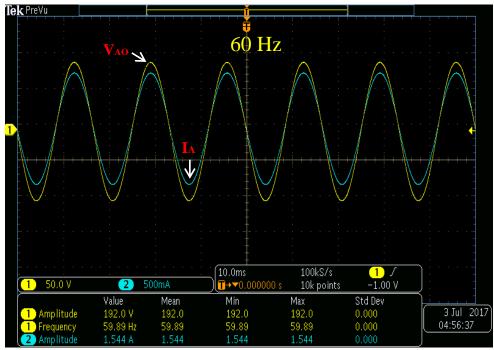

| Fig. 46 | The output voltage and current of the proposed IMMC shown in Fig. 27 is a sinusoidal wave with a fundamental frequency of 60 Hz.                                                                                                                                                                                                        | . 59 |

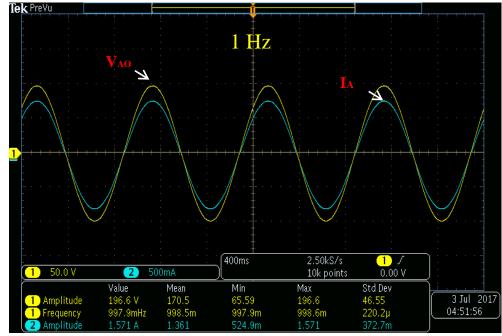

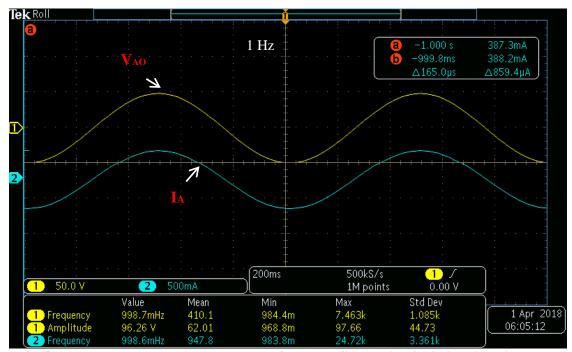

| Fig. 47 | The 1 Hz output voltage and current of the IMMC shown in Fig. 27 is a sinusoidal wave which proves the topology is a good candidate for ASD                                                                                                                                                                                             | . 59 |

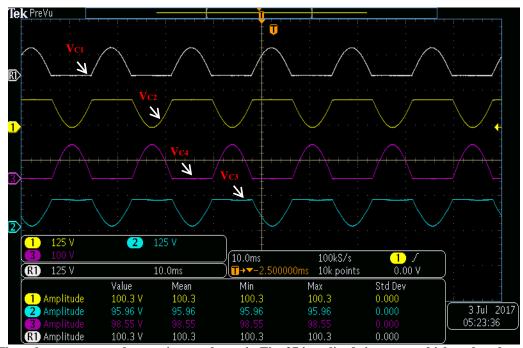

| Fig. 48 | The voltage across each capacitor as shown in Fig. 27 is a sliced sine wave which makes the sum of the output a full sinewave                                                                                                                                                                                                           | . 60 |

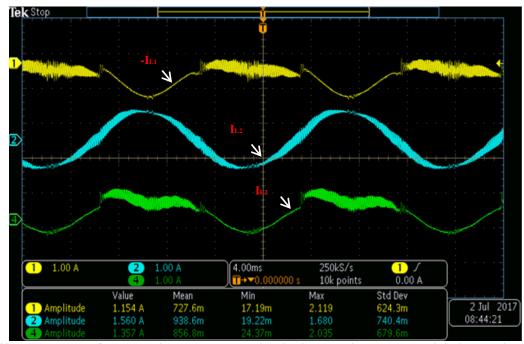

| Fig. 49 | The currents of the three inductors as seen in Fig. 27. The ripple can be minimized by increasing inductor size or the switching frequency of the converter                                                                                                                                                                             | . 60 |

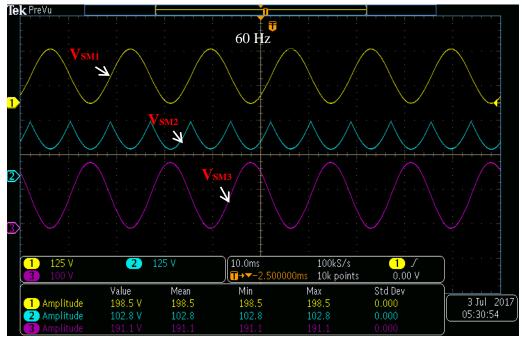

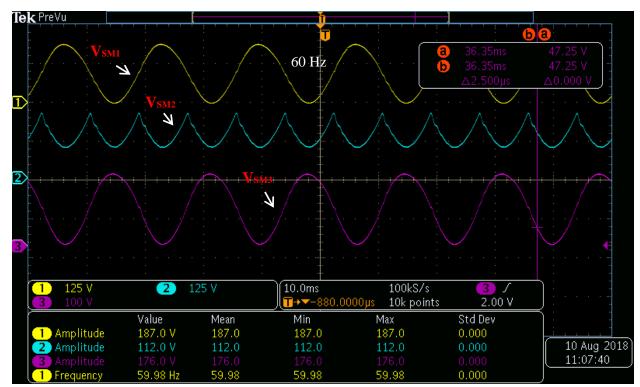

| Fig. 50 | Submodules (SM) voltages with 60 Hz shown in Fig. 27. Channel 1 (yellow) is submodule 1 voltage, channel 2 (light blue) is submodule 2 voltage and channel 3 (yielet) is submodule 3 voltage                                                                                                                                            | 61   |

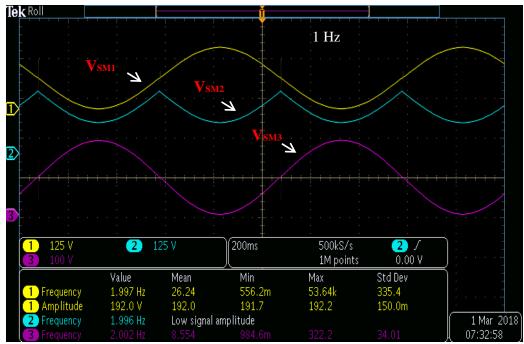

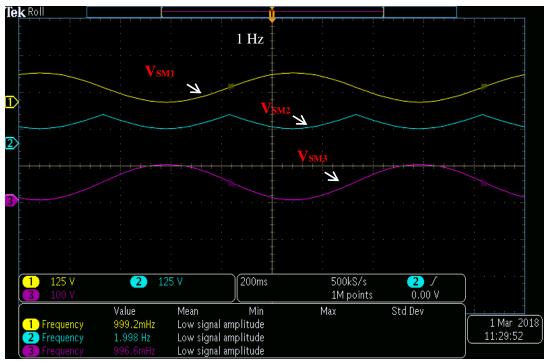

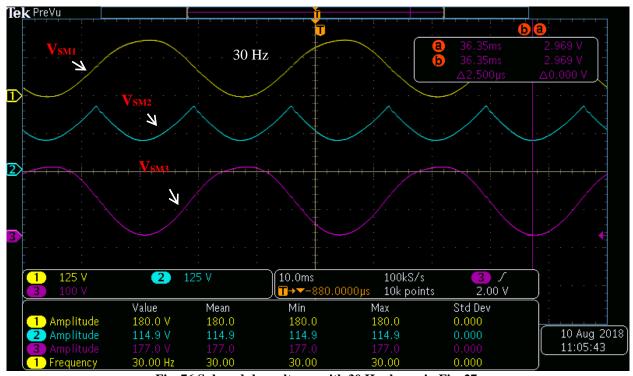

| Fig. 51 | Submodules (SM) voltages with 1 Hz shown in Fig. 27. Channel 1 (yellow) is submodule 1 voltage, channel 2 (light blue) is submodule 2 voltage and channel 3 (violet) is submodule 3 voltage. | . 61 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

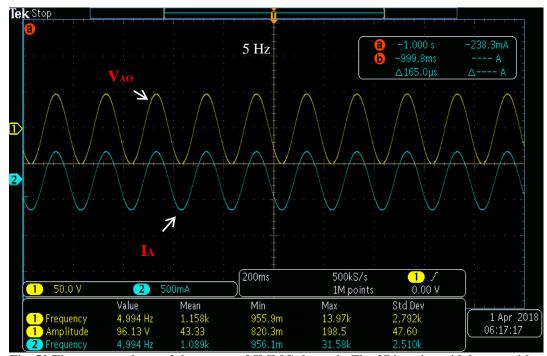

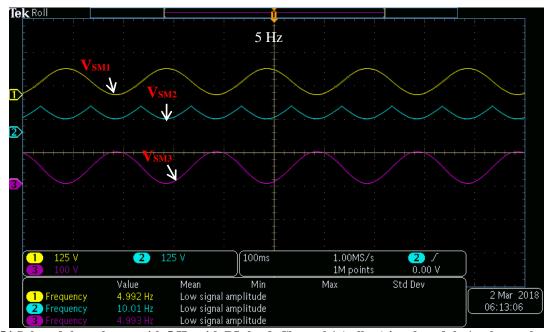

| Fig. 52 | The output voltage of the proposed IMMC shown in Fig. 27 is a sinusoidal wave with a fundamental frequency of 5 Hz.                                                                          | . 63 |

| Fig. 53 | The 1 Hz output voltage and current of the IMMC shown in Fig. 27 is a sinusoidal wave which proves the topology is a good candidate for ASD                                                  | . 63 |

| Fig. 54 | Submodules voltages with 5 Hz with RL-load. Channel 1 (yellow) is submodule 1 voltage, channel 2 (light blue) is submodule 2 voltage and channel 3 (violet) is submodule 3 voltage.          | . 64 |

| Fig. 55 | Submodules voltages with 1 Hz with RL-load. Channel 1 (yellow) is submodule 1 voltage, channel 2 (light blue) is submodule 2 voltage and channel 3 (violet) is submodule 3 voltage.          | . 64 |

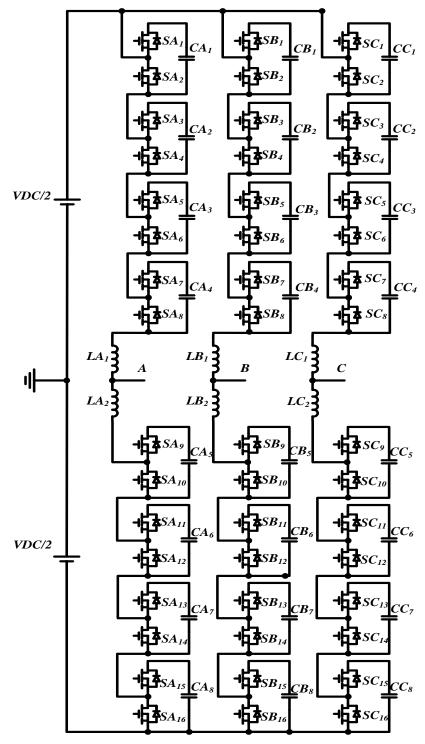

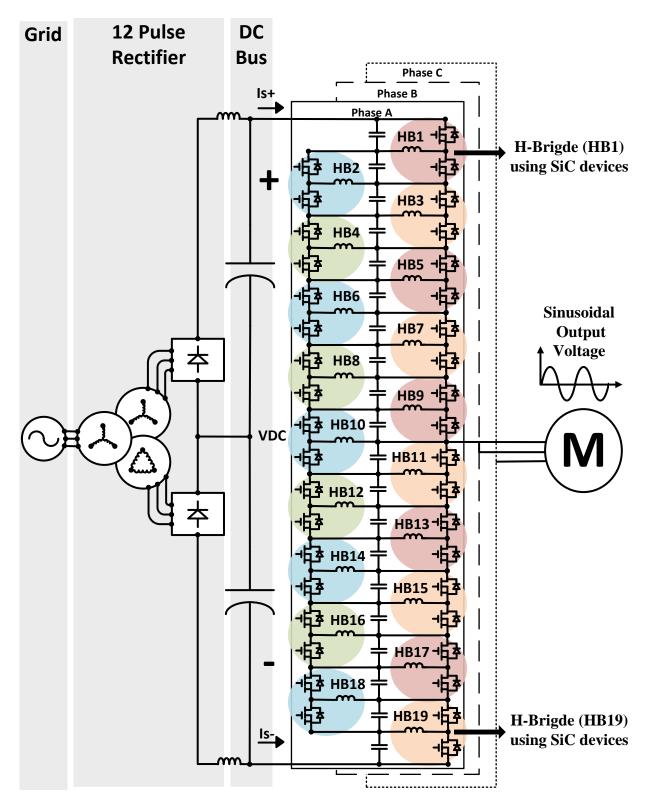

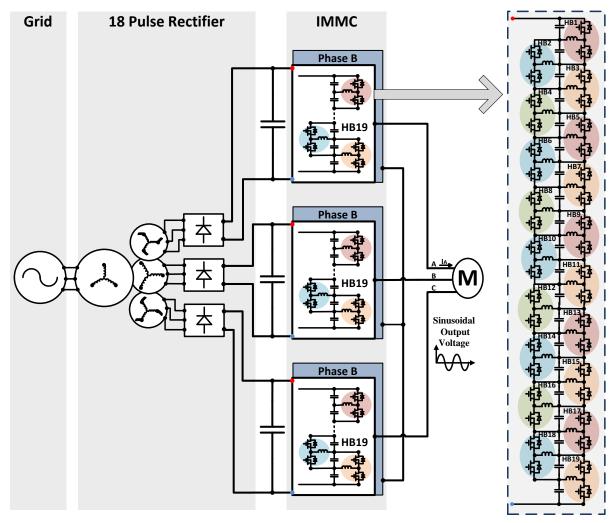

| Fig. 56 | The proposed medium voltage adjustable speed drive topology with IMMC and a 12-pulse rectifier dc-link.                                                                                      | . 66 |

| Fig. 57 | Another variation of the proposed medium voltage adjustable speed drive with IMMC with 18-pulse rectifier.                                                                                   | . 67 |

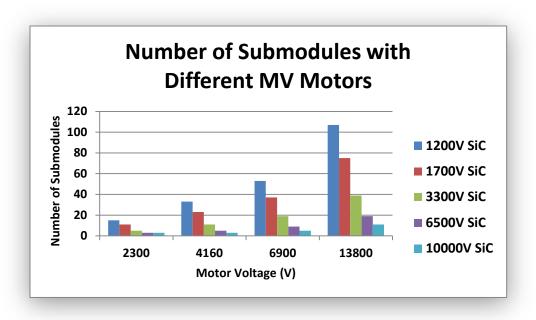

| Fig. 58 | The number of submodules recommended for different MV motors                                                                                                                                 | . 69 |

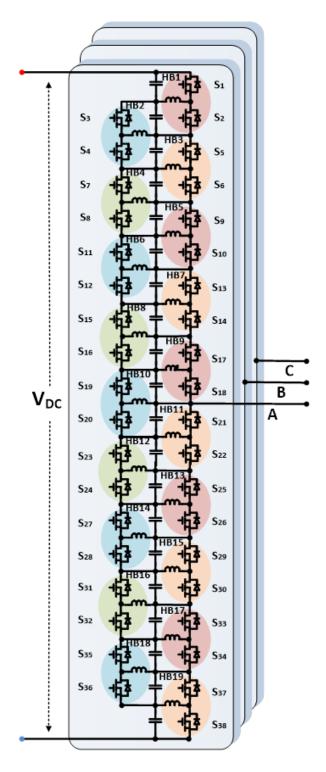

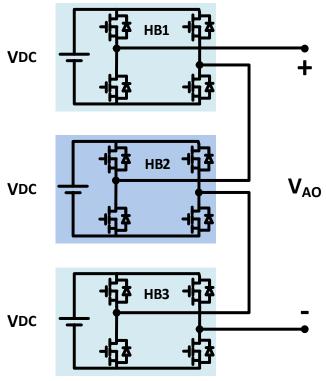

| Fig. 59 | Medium Voltage IMMC                                                                                                                                                                          | . 70 |

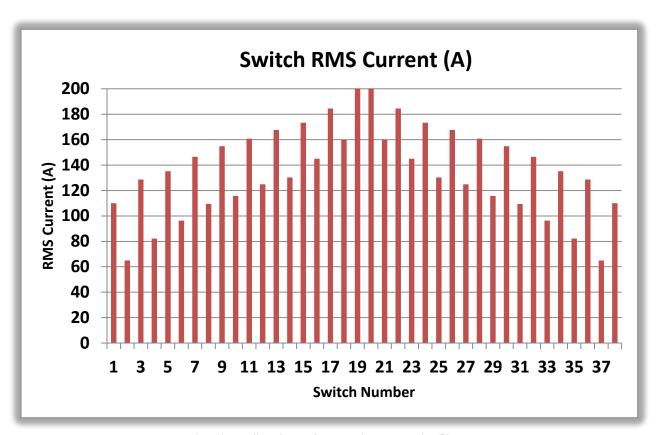

| Fig. 60 | RMS ratings of the devices seen Fig. 59                                                                                                                                                      | . 71 |

| Fig. 61 | An equivalent CHB design to drive the 13.8 kV motor                                                                                                                                          | . 72 |

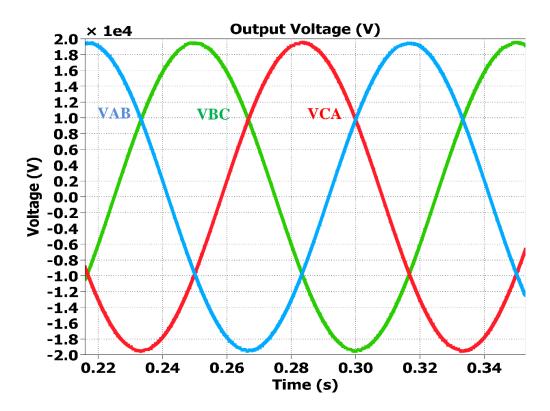

| Fig. 62 | The three-phase line-line output voltage of the IMMC.                                                                                                                                        | . 74 |

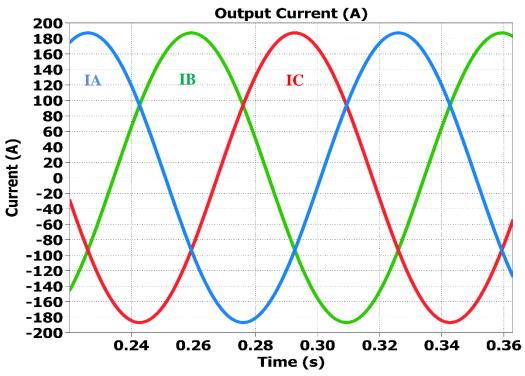

| Fig. 63 | The three-phase line-line output current of the IMMC.                                                                                                                                        | . 74 |

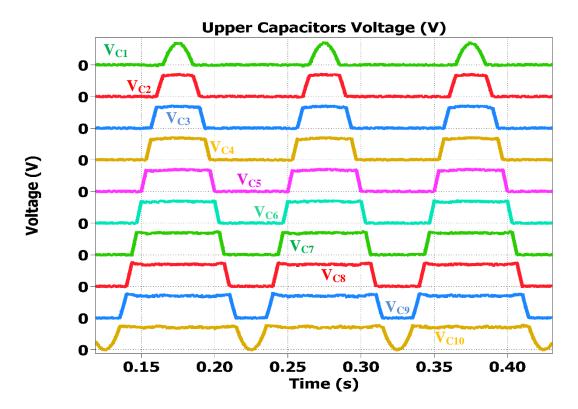

| Fig. 64 | The voltages of the upper capacitors (from $C_1$ to $C_{10}$ )                                                                                                                               | . 75 |

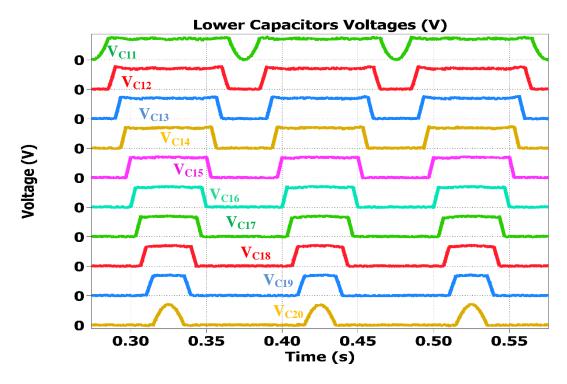

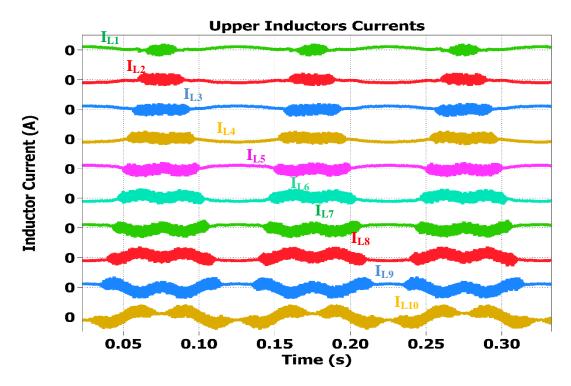

| Fig. 65 | The voltages of the lower capacitors (from $C_{11}$ to $C_{20}$ )                                                                                                                            | . 75 |

| Fig. 66 | The current through the upper inductors (from $L_1$ to $L_{10}$ )                                                                                                                            | . 76 |

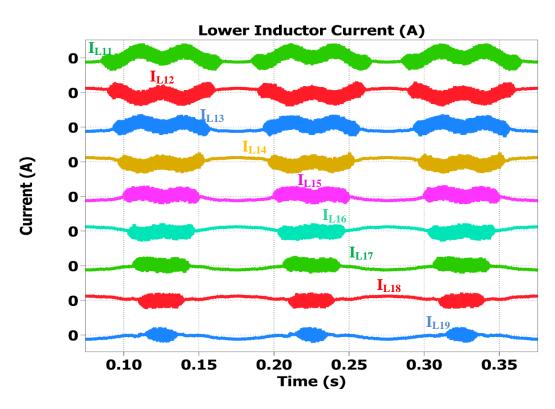

| Fig. 67 | The current through the Lower inductors (from $L_{11}$ to $L_{19}$ )                                                                                                                         | . 76 |

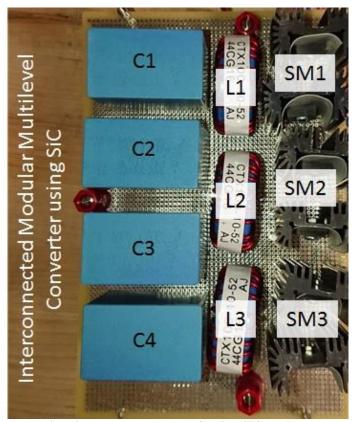

| Fig. 68 | The proposed IMMC using SiC devices                                                                                                                                                          | . 77 |

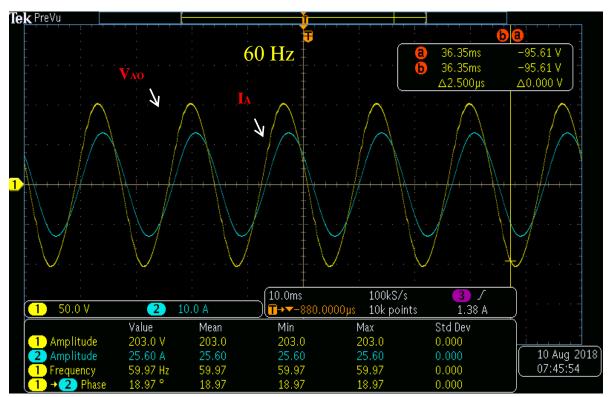

| Fig. 69 | The output voltage and current of the proposed SiC IMMC shown in Fig. 27 is a sinusoidal wave with a fundamental frequency of 60 Hz. The load is an RL-load with a phase shift of 18.97o | . 79 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 70 | The output voltage and current of the proposed SiC IMMC shown in Fig. 27 is a sinusoidal wave with a fundamental frequency of 30 Hz. The load is an RL-load with a phase shift of 8.250. | . 79 |

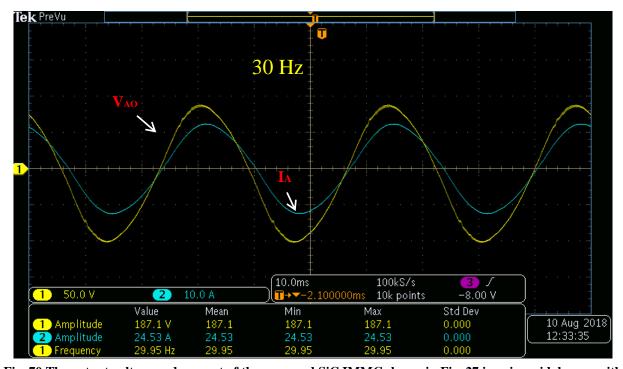

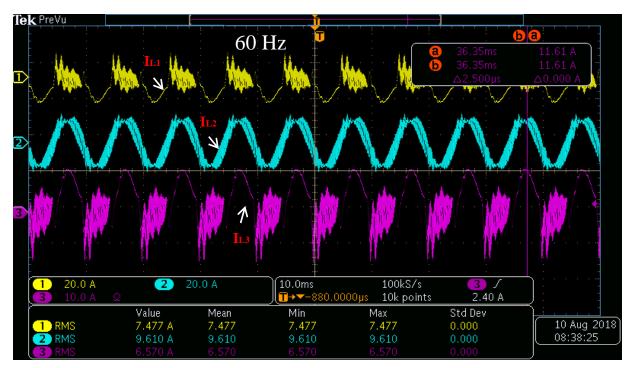

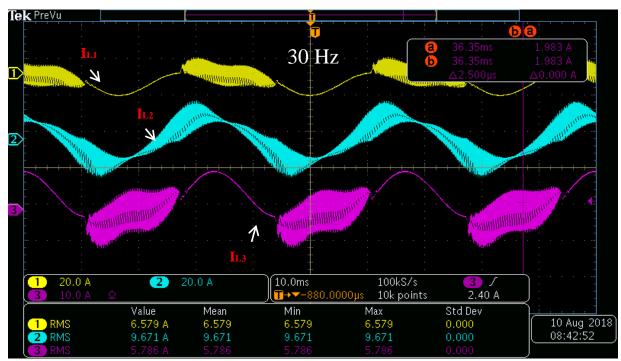

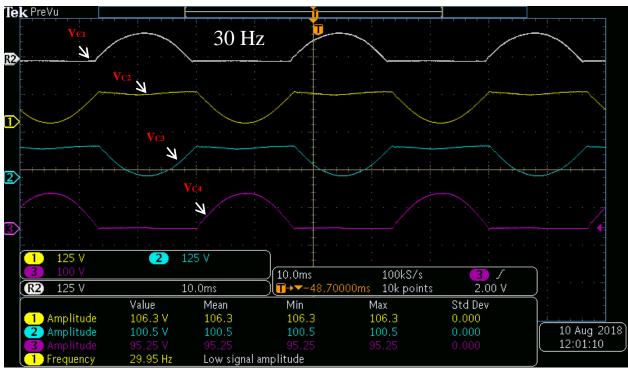

| Fig. 71 | The currents of the three inductors as seen in Fig. 27 when the output is 60 Hz. The ripple can be minimized by increasing inductor size or the switching frequency of the converter.    | . 80 |

| Fig. 72 | The currents of the three inductors as seen in Fig. 27 when the output is 30 Hz. The ripple can be minimized by increasing inductor size or the switching frequency of the converter.    | . 80 |

| Fig. 73 | The voltage across each capacitor when the output is 60 Hz as shown in Fig. 27 is a sliced sine wave which makes the sum of the output a full sinewave                                   | . 81 |

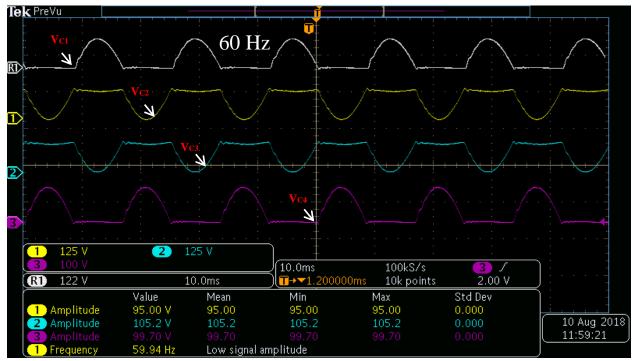

| Fig. 74 | The voltage across each capacitor when the output is 30 Hz as shown in Fig. 27 is a sliced sine wave which makes the sum of the output a full sinewave                                   | . 81 |

| Fig. 75 | Submodules voltages with 60 Hz shown in Fig. 27.                                                                                                                                         | . 82 |

| Fig. 76 | Submodules voltages with 30 Hz shown in Fig. 27.                                                                                                                                         | . 82 |

| Fig. 77 | Nonlinear rectified load is connected to the IMMC. VDC=300V, R=60 ohm and C=870 uF.                                                                                                      | . 83 |

| Fig. 78 | The experimental result of the nonlinear load shown in Fig. 77.                                                                                                                          | . 83 |

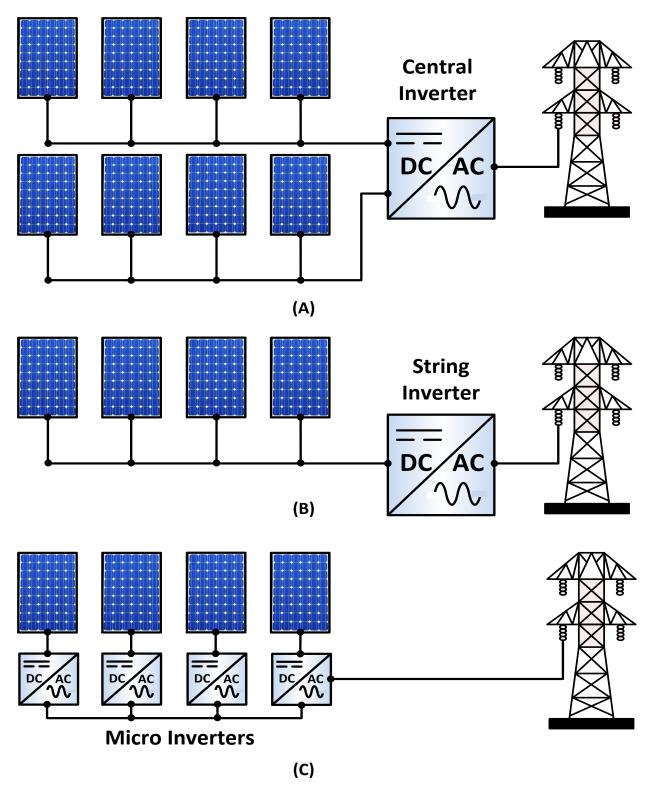

| Fig. 79 | The structures of PV energy harvesting systems (A) Central Inverter (B) String Inverter (C) Micro Inverters.                                                                             | . 85 |

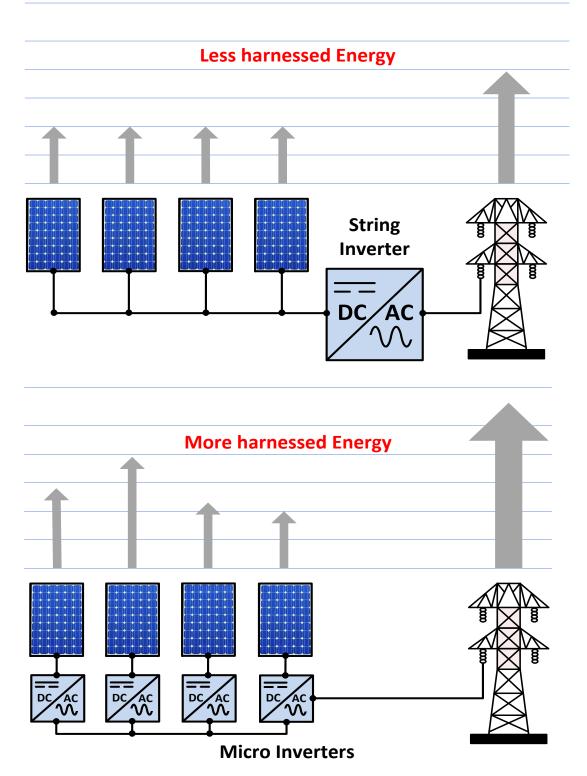

| Fig. 80 | harnessed energy comparison between string and micro-inverters with no shading conditions                                                                                                | . 88 |

| Fig. 81 | harnessed energy comparison between string and micro-inverters with shading conditions                                                                                                   | . 89 |

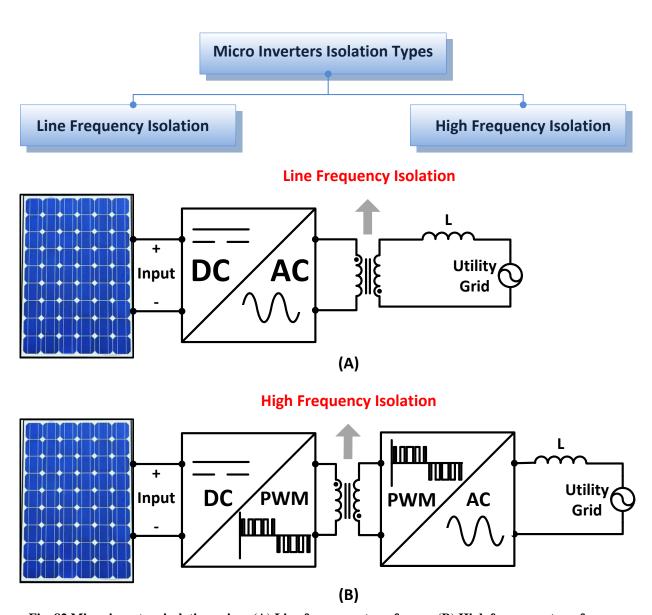

| Fig. 82 | Micro inverters isolation using: (A) Line frequency transformer (B) High frequency transformer.                                                                                          | . 91 |

| Fig. 83 | Two Stage Micro-inverter                                                                                                                                                                 | . 92 |

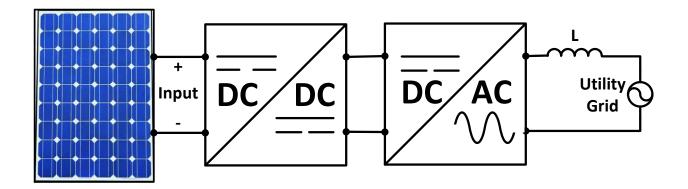

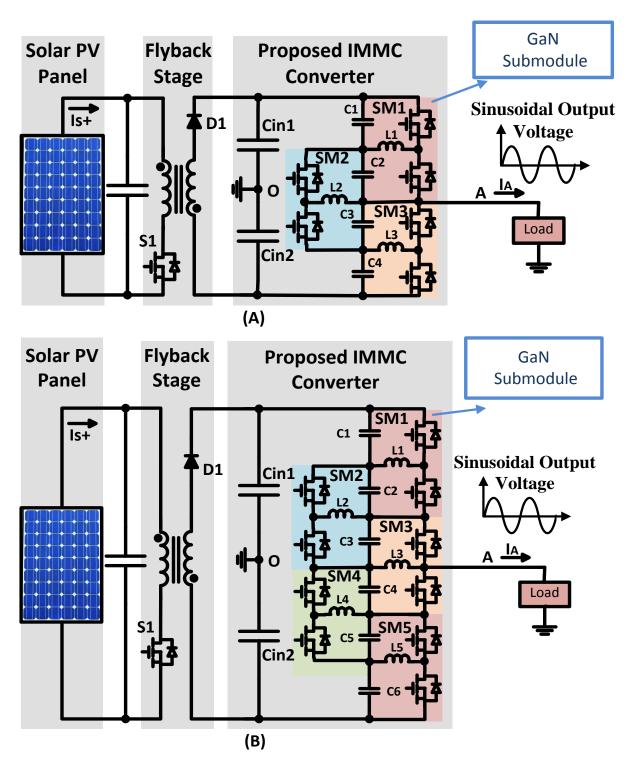

| Fig. 84  | Conventional methods to connect micro inverters to the grid using (A) L-filter (B) LCL-filter                                                                                    | . 92 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

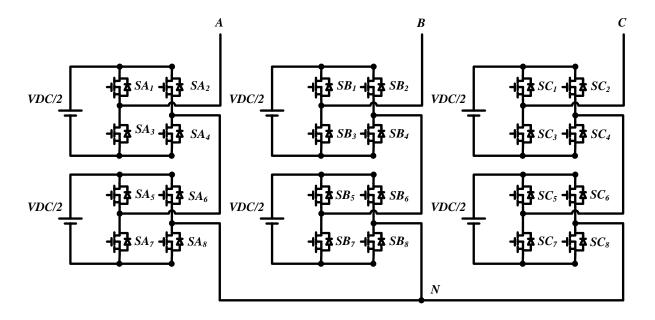

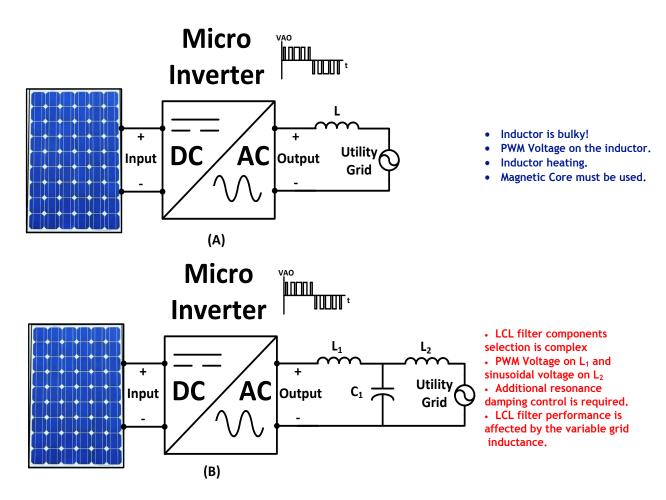

| Fig. 85  | The proposed micro-inverter (A) Three submodules (B) Five submodules stacked design to reduce the voltage stress on the GaN switches.                                            | . 95 |

| Fig. 86  | Inverter current control using Fictive-Axis Emulation [43]                                                                                                                       | . 96 |

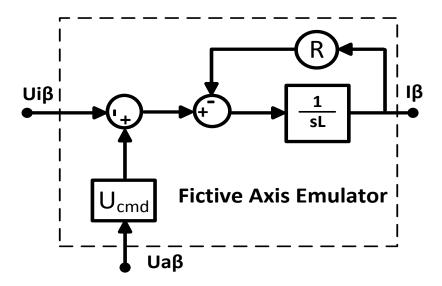

| Fig. 87  | Under mask diagram of the Fictive Axis Emulator [43].                                                                                                                            | . 97 |

| Fig. 88  | The snubber circuit used for the flyback converter.                                                                                                                              | . 98 |

| Fig. 89  | The proposed topology.                                                                                                                                                           | . 99 |

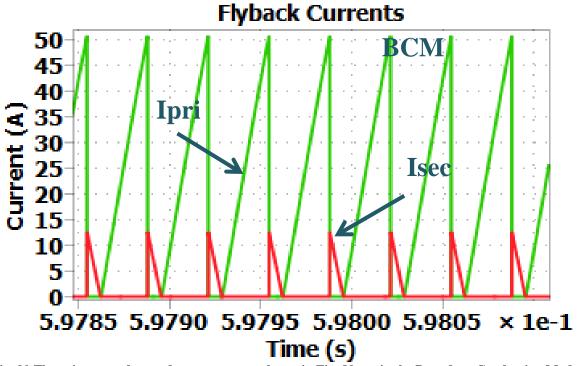

| Fig. 90  | The primary and secondary currents as shown in Fig. 89 not found. are in the Boundary Conduction Mode (BCM)                                                                      | 102  |

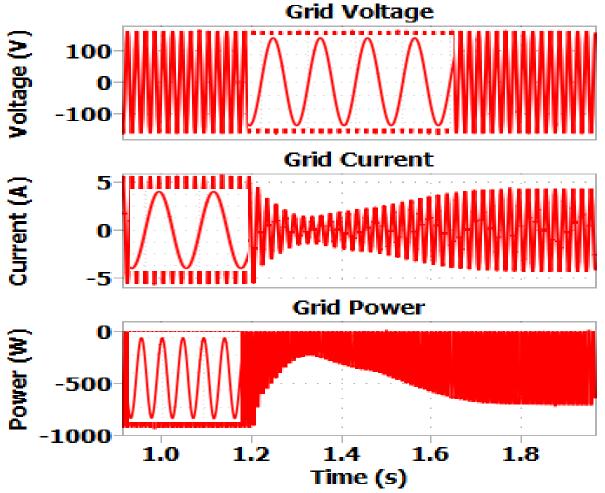

| Fig. 91  | The grid voltage, current and power behaviors when the irradiance changes. The controller injected the available current to the grid and the voltage of the grid does not change | 103  |

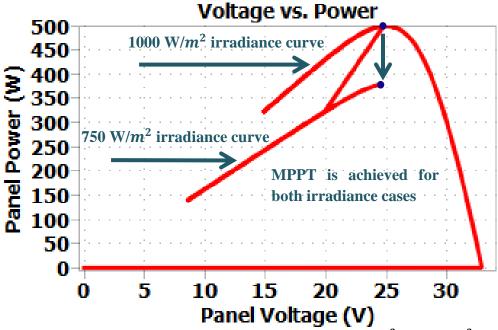

| Fig. 92  | PV-curve of the panel. When the irradiance changes from $1000 \text{ W/}m2$ to $750 \text{ W/}m2$ , the controller operates the micro-inverter at the MPP of the new curve       | 104  |

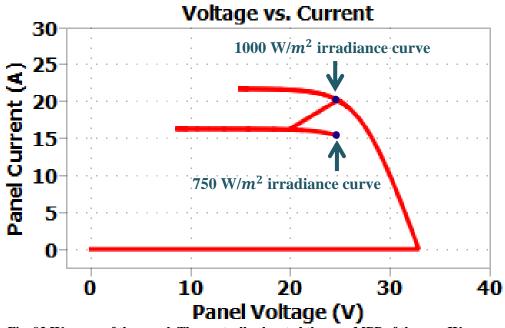

| Fig. 93  | IV-curve of the panel. The controller located the new MPP of the new IV-curve                                                                                                    | 104  |

| Fig. 94  | The conventional AC solar power collection systems (A) Medium voltage AC collection grid (B) Low voltage AC collection grid                                                      | 105  |

| Fig. 95  | Proposed medium voltage DC collection system.                                                                                                                                    | 106  |

| Fig. 96  | Detailed schematic of the proposed Gird-tie Medium voltage DC collection<br>System for Large Scale Solar PV Plants Using the IMMC [45]                                           | 107  |

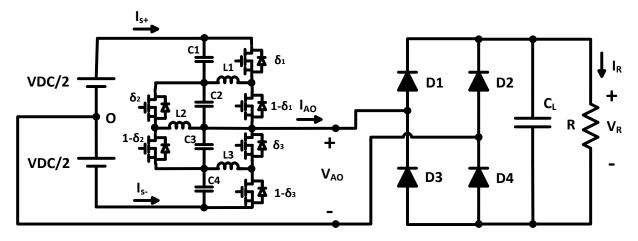

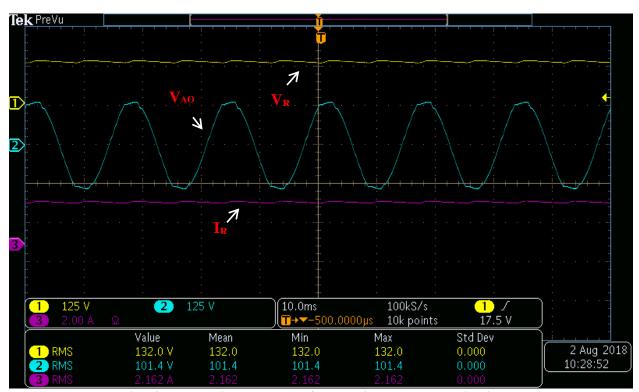

| Fig. 97  | Circuit diagram of the laboratory prototype.                                                                                                                                     | 108  |

| Fig. 98  | The laboratory protoype of the proposed system shown in Fig. 97                                                                                                                  | 108  |

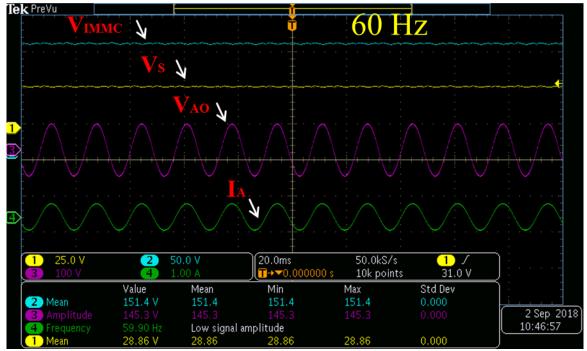

| Fig. 99  | The waveforms of the input DC voltage $(Vs)$ , stepped up DC voltage $(VIMMC)$ , the AC output current $(IAO)$ , and voltage $VAO$ when the grid frequency is 60 Hz              | 110  |

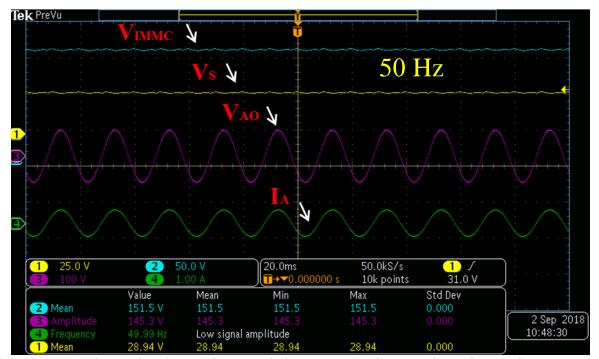

| Fig. 100 | The waveforms of the input DC voltage (Vs), stepped up DC voltage (VIMMC), the AC output current (IAO), and voltage VAO when the grid frequency is 50 Hz.                        | 110  |

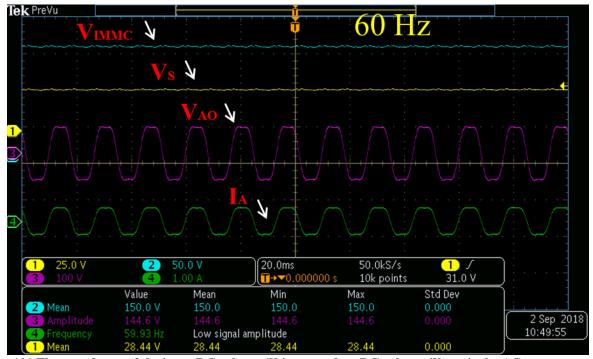

| Fig. 101 | The waveforms of the input DC voltage (Vs), stepped up DC voltage (VIMMC), the AC output current (IAO), and voltage VAO when third harmonic is injected                                |     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | with a grid frequency of 60 Hz.                                                                                                                                                        | 111 |

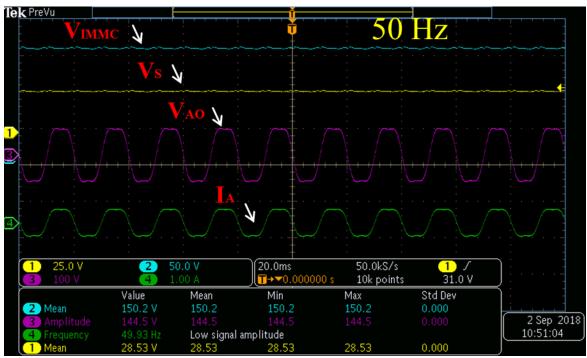

| Fig. 102 | The waveforms of the input DC voltage (Vs), stepped up DC voltage (VIMMC), the AC output current (IAO), and voltage VAO when third harmonic is injected with a grid frequency of 50 Hz |     |

# LIST OF TABLES

|          |                                                                                 | Page |

|----------|---------------------------------------------------------------------------------|------|

| Table 1  | Material Properties of Si, SiC and GaN                                          | 4    |

| Table 2  | voltage stress on switches with respect to the number of SMs                    | 39   |

| Table 3  | Comparison between single phase IMMC and popular multilevel existing topologies | 40   |

| Table 4  | Size Comparison                                                                 | 43   |

| Table 5  | Low voltage drives Commercial products                                          | 46   |

| Table 6  | IMMC designs for different motors                                               | 47   |

| Table 7  | Design example parameters                                                       | 49   |

| Table 8  | Simulation parameters                                                           | 53   |

| Table 9  | Experimental prototype parameters                                               | 58   |

| Table 10 | Another RL-Load prototype parameters                                            | 62   |

| Table 11 | Market products for medium voltage drives                                       | 65   |

| Table 12 | IMMC designs for different motors                                               | 68   |

| Table 13 | Design example parameters                                                       | 71   |

| Table 14 | Simulation parameters                                                           | 73   |

| Table 15 | Experimental prototype parameters                                               | 77   |

| Table 16 | Design Example Parameters                                                       | 100  |

| Table 17 | Laboratory prototype parameters                                                 | 109  |

#### 1. INTRODUCTION

#### 1.1 Wide Band Gap (WBG) Devices.

The rapid progress of renewable energy resources integration has resulted a need for efficient, high power, fast and high temperature semiconductor switches. Because of that, Wide Band Gap (WBG) devices came into existence. The emergence of the WBG devices improved the power density and the efficiency of the power electronic interface of renewable energy resources. The most commercially available WBG devices are the Gallium Nitride (GaN) and Silicon Carbide (SiC) due to their superior performance in the blocking voltage, switching losses, temperature and switching speed [1].

Fig. 1 Market integration of devices applications (Reprinted with permission from IEEE [2] - Copyright © 2014, IEEE).

Fig. 1 shows that the future predicted market will be dominated by WBG devices (SiC and GaN) in multiple applications. The blocking voltage of the GaN is limited to 1200 V using the deposition of GaN on a silicon substrate [3]. Therefore, preventing GaN devices from entering medium and high-power range applications. However, GaN is still a suitable candidate for applications that require high switching frequency as shown in Fig. 2. For higher power applications, SiC devices become a better candidate due to the higher blocking voltage and higher temperature limit.

Fig. 2 Predicted applications for transistors (Reprinted with permission from IEEE [3] - Copyright © 2014, IEEE).

Operating a converter with a high switching frequency using Silicon (Si) based devices affects the efficiency and the performance of the converter adversely [4]. The high switching losses of the Si devices resulted from the low bandgap (1.1 eV) and critical electric field (0.3 MV/cm) of the Si decreases the efficiency of the converter. Moreover, the low bandgap of the Si limits the maximum junction temperature of the devices. With the development of Wide Band Gap (WBG) semiconductors such as Gallium Nitride (GaN) and Silicon Carbide (SiC), switches can operate at a higher switching frequency and temperature with higher efficiency. Fig. 3 summarizes the impact of each material property on operation, power module and power system. Table 1 shows the material properties of WBG devices compared to Si [4].

Fig. 3 Material property analysis of Wide Bandgap Devices (Reprinted with permission from IEEE [5] - Copyright © 2014, IEEE).

Table 1 Material Properties of Si, SiC and GaN

| Property                                     | Si   | SiC | GaN  |

|----------------------------------------------|------|-----|------|

| Bandgap Energy (eV)                          | 1.1  | 3.2 | 3.4  |

| Electron Mobility (cm2/Vs)                   | 1350 | 700 | 1500 |

| Critical Electric Field (MV/cm)              | 0.3  | 3   | 3.3  |

| Saturated Electron Drift Velocity (107 cm/s) | 1    | 2   | 2.5  |

#### 1.2 Literature Review: Multilevel Converters.

The evolution of inverters started with the two levels inverter as shown in Fig. 4. Research continued to improve the output of inverters to serve different applications. Therefore, proposing a higher number of levels to resemble a sinusoidal waveform leading to the birth of multilevel converters. The first concept of multilevel converter was proposed in 1975 [6]. After that, multilevel converters gained the attention of researchers from all around the world due to their advantages over the two levels inverter shown in Fig. 4 (A). Great effort is spent to improve their performance and optimize their control to suit several applications.

Consequently, new multilevel topologies are invented and proposed. The fundamental mechanism of multilevel converters is to synthesize a staircase waveform by switching a series of semiconductors. This section presents an overview of the existing state of the art multilevel converters since the proposed converter in this thesis will be compared with existing multilevel converter topologies.

Fig. 4 Evolution of inverters (A) Two levels inverter (B) T-inverter (C) Three levels inverter (D) Five levels inverter.

There are many existing multilevel topologies and the number is expanding every year. However, this section will provide an overview of most popular topologies which are Neutral Point Clamped Converter (NPC) Modular Multilevel Converter (MMC) Cascaded H-bridge (CHB) Flying Capacitor Converter (FCC).

#### 1.2.1 Neutral Point Clamped Converter (NPC)

The Neutral Point Clamped Converter (NPC) was proposed in 1981 by Nabae, Takahashi, and Akagi as a three levels inverter [7]. The NPC topology gained success in the field and researchers published many papers to investigate the topology and propose higher number of levels. Fig. 5 shows the three level and five level NPC. The NPC found a place in multiple applications such as high power medium voltage drives and solar Photo-Voltaic (PV) inverters.

Fig. 5 The Neutral Point Clamped Converter (NPC) (A) Three levels (B) Five levels

#### **Advantages:**

- Low number of passive components (capacitors and inductors)

- Simple structure and low cost

#### **Disadvantages:**

- High  $\frac{dV}{dt}$  and common mode voltages.

- Complex balancing control is required to balance the DC link capacitors.

- Asymmetrical loss distribution in the clamping diodes.

- Large number of components when operated with high number of levels.

#### **1.2.2** Modular Multilevel Converter (MMC)

Fig. 6 Three level Modular Multilevel Converter (MMC).

The modular multilevel converter (MMC) was proposed by A. Lesnicar and R. Marquardt in 2003 [8]. The MMC is one of the most popular multilevel topologies for High Voltage Direct Current Transmission (HVDC). It a consists of submodules stacked in series, each submodules contains half bridge switches and a capacitor as shown in Fig. 6 and Fig. 7. The output is a staircase waveform that depends on the number of half-bridge submodules.

Fig. 7 Five Level Modular Multilevel Converter (MMC)

Fig. 6 shows a three-level MMC that contains four submodules per leg and Fig. 7 shows a five-level MMC that contains six submodules per leg.

#### **Advantages:**

- Scalability and modularity to suit high voltage/power applications.

- Fault tolerant: submodules can be replaced easily in case of faults.

#### **Disadvantages:**

- High  $\frac{dV}{dt}$  and common mode voltages.

- Large submodules capacitors.

- Low frequency operation (10Hz) results low frequency harmonic (10Hz) on the submodule capacitors when the submodule is a half bridge.

## 1.2.3 Cascaded H-Bridge Converter (CHB)

Fig. 8 Five level Cascaded H-Bridge Converter.

The cascaded H-Bridge (CHB) consists of several stacked single-phase H-Bridge inverters (full bridge) connected in series as seen in Fig. 8. The series connection builds the steps of the multilevel (staircase) output of the converter. The advantages of CHB paved the way for the topology to become a popular choice for many applications such as AC motor drives, Static Synchronous Compensation (SVC) and renewable energy resources integrations.

#### **Advantages:**

- The number of levels in the output voltage is more than two times the dc sources.

- Scalability and modularity to suit high voltage/power applications.

- Fault tolerant: submodules can be replaced easily in case of faults.

#### **Disadvantages:**

- High  $\frac{dV}{dt}$  and common mode voltages.

- Each H-Bridge requires a separate DC source. Therefore, several transformers and rectifier stages are required.

- Low frequency operation results low frequency harmonic in the DC link.

#### 1.2.4 Flying Capacitor Converter (FCC)

The flying capacitor converter (FCC) was proposed by Meynard and Foch in 1992 [9]. The FCC was inspired by the NPC topology, but the NPC diodes were replaced with capacitors. The output of the FCC is a multilevel staircase waveform. A step in the waveform results from two neighboring capacitor legs. Increasing the number of levels in the output can be achieved by increasing the number of capacitor legs. Fig. 9 (A) and Fig. 9 (B) show a three level and five level FCC respectively.

Fig. 9 Flying Capacitor Converter (FCC) (A) Three levels (B) Five Levels

#### **Advantages:**

- Scalability to any number of levels.

- Ride through capability due to the high number of capacitors.

#### **Disadvantages:**

- High  $\frac{dV}{dt}$  and common mode voltages.

- Large number of capacitors.

- Complex control is required to balance the capacitors.

### 1.3 Research Objective

The main objective of this dissertation is to exploit the emergence of the wide band gap devices to develop high efficiency and power density converters. Wide band gap devices are not fully utilized and there are several research opportunities to optimize the power conversion process. This dissertation introduces wide band gap solutions for motor drives, solar microinverter and large scale PV power plants integration applications.

The first objective of this dissertation is to propose a new high-power density converter using wide band gap devices for motor drives. The proposed converter solves major problems with existing converters used for motor drives. The proposed converter produces a sinusoidal output that eliminates the need for an output filter. Therefore, eliminating the dv/dt related issues due to long motor lead. Moreover, the sinusoidal output of the proposed converter diminishes the acoustic noise resulted from the pulsating torque in the existing PWM converter. A low voltage drive converter using GaN and a Medium voltage drive converter using SiC are built in the laboratory to validate the operation of the converter.

The second objective is to propose a new micro-inverter that solves the grid-tie filter issues. Existing micro-inverters could be tied to the grid using a bulky and unfeasible inductor or a complex LCL-filter that has several design issues. The proposed micro-inverter produces a sinusoidal output that reduces the grid-tie inductor requirements. The grid-tie inductor used with the proposed micro-inverter is small due to the sinusoidal nature of the output. Moreover, an iron core can be used due to the line frequency of the voltage on the inductor. Additionally, low voltage GaN can be used due to the multilevel feature and the passive components are small due to the high switching frequency of the converter.

The third objective of the dissertation is to propose a full system to integrate large PV power plants to the grid using medium voltage DC collection grid. The power sharing stage has an essential role in allowing the series connected PV power plants to supply different powers under partial shading conditions. The DC collection side of the proposed system eliminates the bulky 50/60 HZ AC collection transformers. The proposed medium voltage class central inverter is a high-power density IMMC using SiC that inject power to the grid with minimum grid-tie inductor requirements.

#### 1.4 Thesis Outline

The first chapter introduces an overview of wide bandgap devices and a comparison with the other existing devices. The comparison includes the material properties that gave wide band gap devices a superior performance compared to the traditional Silicon based devices. The predicted applications for each device are discussed. Moreover, a literature review on existing multilevel topologies such as Neutral Point Clamped Converter (NPC) Modular Multilevel Converter (MMC) Cascaded H-bridge (CHB) Flying Capacitor Converter (FCC) is covered.

The second chapter introduces the Interconnected Modular Multilevel Converter (IMMC) as a new high-power density converter that utilizes Wide Band Gap devices. The operation and modulation of the converter are discussed in detail. Additionally, the derivation of the equations started for the three submodules design and then it is extended to an N number of submodules. After that, the proposed IMMC is compared with existing multilevel topologies to evaluate the proposed converter in different comparison aspects.

The third chapter introduces the converter for motor drives application. A low voltage drive design IMMC is proposed and a low voltage laboratory prototype is built using Gallium Nitride (GaN) devices to prove the concept. Another design for medium voltage applications using Silicon Carbide (SiC) is proposed. A laboratory prototype is built using SiC and experimental results are demonstrated.

In the fourth chapter, a micro-inverter using the IMMC is introduced. The solar panel is connected to the IMMC using a flyback converter to provide isolation and Maximum Power Point Tracking (MPPT) operation. A full design of the micro-inverter elements is covered. Additionally, a micro-inverter grid tie control using Fictive-Axis-Emulation method is explained. The grid-tie control is simulated to demonstrate the viability of the proposed micro-inverter.

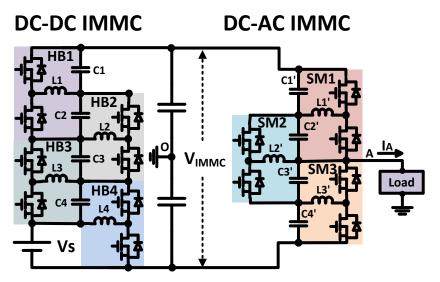

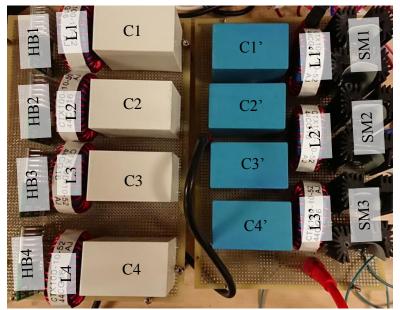

The fifth chapter proposes a full system to integrate two PV power plants to the grid. The focus of the chapter is on the DC/AC IMMC that integrates the PV power plants to the grid. Experimental results of a DC/DC and DC/AC IMMC laboratory prototype are presented as well.

## 2. INTERCONNECTED MODULAR MULTILEVEL CONVERTER (IMMC)\*

#### 2.1 DC-DC IMMC

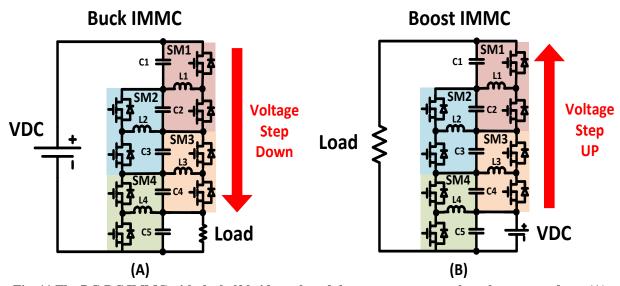

Fig. 10 The DC-DC version of the IMMC that can step up or step down the input voltage. Each submodule can be a half of full bridge (A) Buck IMMC (B) Boost IMMC (C) Half-bridge submodule (D) Full Bridge submodule.

<sup>\*</sup> Reprinted with permission from:

A. Allehyani, A. Morsy and P. Enjeti, "A new Interconnected Modular Multilevel Converter (IMMC) with sinusoidal voltage output suitable for high performance AC drives," 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, 2017, pp. 1-8. Copyright 2017 by IEEE.

The DC-DC version of the IMMC is proposed in [10, 11]. It can operate as a buck or boost converter by operating the stacked submodules as step-down or step-up stages as shown in Fig. 10 and Fig. 11. The modulation and control of the DC-DC converter is a simple 50% duty cycle on each submodule. The 50% operation of the submodules achieves capacitor balancing for each submodule. Therefore, achieving charge equalization for the stacked capacitors.

Fig. 11 The DC-DC IMMC with the half-bridge submodules structure to step the voltage up or down (A) Buck IMMC (B) Boost IMMC.

#### 2.1.1 DC-DC IMMC Circuit Analysis

This section focuses on the half bridge submodule DC-DC IMMC. The equations derivations of the inductors and capacitors are covered due to the similarity to the proposed DC-AC IMMC in this dissertation.

Fig. 12 Loops to determine the inductor equations.

The most fundamental rule in power electronics is that the sum of the voltage on an inductor in a full cycle must be zero. The previous rule is used to derive the voltages of the capacitors. It is shown in Loop 1 in Fig. 12 that applying the rule on  $L_1$  derives the equation of the voltage across  $C_1$ . Therefore, the voltage on  $C_1$  is expressed in (1).

$$V_{C1} = \frac{\delta_1}{1 - \delta_1} V_s \tag{1}$$

The same approach is applied on the rest of the inductors to derive the voltage on each capacitor. The voltage on  $C_2$ ,  $C_3$  and  $C_4$  are expressed in (2), (3) and (4) respectively.

$$V_{C2} = \frac{\delta_2}{1 - \delta_2} V_{C1} \tag{2}$$

$$V_{C3} = \frac{\delta_3}{1 - \delta_3} V_{C2} \tag{3}$$

$$V_{C4} = \frac{\delta_4}{1 - \delta_4} V_{C3} \tag{4}$$

Therefore, a generalized equation for capacitors voltage for an N number of submodules can be calculated using (5).

$$V_{CN} = \frac{\delta_N}{1 - \delta_N} V_{C(N-1)} \tag{5}$$

As seen in Fig. 13, the output voltage of the DC-DC IMMC is the sum of the source voltage and the capacitors voltages. Thus, the output voltage of the IMMC ( $V_{IMMC}$ ) is expressed in (6).

$$V_{IMMC} = V_s + V_{C1} + V_{C2} + \dots + V_{CN}$$

(6)

The output voltage of the IMMC ( $V_{IMMC}$ ) is dependent on the capacitors voltages. The capacitor voltages are dependent on the submodules duty ratio as explained in the previous equations. However, it is recommended to operate the duties of the submodules at %50 to ensure the capacitors are balanced.

The size equation of the inductor, as a function of the ripple, is found from the equation of the voltage on the inductor shown in Fig. 12 in the first segment of the cycle. Therefore, (7) represent the sizing equation of the  $L_1$ .

$$L_1 = \frac{V_s}{(\frac{\Delta i_{L1}}{\delta_1 T})} \tag{7}$$

The same approach is applied on the rest of the inductors. The sizing equation for  $L_2$ ,  $L_3$  and  $L_4$  are indicated in (8), (9) and (10) respectively.

$$L_2 = \frac{V_{C1}}{(\frac{\Delta i_{L2}}{\delta_2 T})} \tag{8}$$

$$L_3 = \frac{V_{C2}}{(\frac{\Delta i_{L3}}{\delta_3 T})} \tag{9}$$

$$L_4 = \frac{V_{C3}}{(\frac{\Delta i_{L4}}{\delta_4 T})} \tag{10}$$

Therefore, for an  $N\neq 1$ , The generalized inductor equation for a converter that has an N number of levels is expressed in (11).

$$L_N = \frac{V_{C(N-1)}}{\frac{\Delta i_{LN}}{\delta_N T}} \tag{11}$$

Fig. 13 defines the currents and the nodes used to derive the capacitors currents equations. Therefore, the capacitors currents  $I_{C1}$ ,  $I_{C2}$ ,  $I_{C3}$  and  $I_{C4}$  are calculated in (12), (13), (14) and (15) respectively.

$$I_{C1} = I_s + \delta_2 I_{L2} - I_{L1} \tag{12}$$

$$I_{C2} = I_s - \delta_1 I_{L1} - (1 - \delta_2) I_{L2} + \delta_3 I_{L3}$$

(13)

$$I_{C3} = I_S - \delta_1 I_{L1} - (1 - \delta_3) I_{L3} + \delta_4 I_{L4}$$

(14)

$$I_{C4} = I_0 - (1 - \delta_4)I_{L4} \tag{15}$$

The equation for the first capacitor current is always the same regardless to the number of submodules. The equations for the rest of the capacitors currents can be extended to an N number of capacitors. The general capacitor current equation for  $I_{C2}$  to  $I_{C(N-1)}$  is found in (16).

$$I_{C(N-1)} = I_s - \delta_1 I_{L1} - (1 - \delta_{(N-1)}) I_{L(N-1)} + \delta_N I_{LN}$$

(16)

The equation for the last capacitor (N) is always expressed in (17).

$$I_{C(N)} = I_o - (1 - \delta_N)I_{LN} \tag{17}$$

Fig. 13 Nodes to derive the capacitors current equations.

The average capacitor current is always zero. Therefore, average inductors currents can be derived from the capacitor current equations (12), (16) and (17).  $I_{L1}$ ,  $I_{C1}$  and  $I_{C1}$  are expressed in (18), (19) and (20) respectively.

$$I_{L1} = I_S + \delta_2 I_{L2} \tag{18}$$

$$I_{LN-1} = \frac{[I_s - \delta_1 I_{L1} + \delta_N I_{LN}]}{1 - \delta_{N-1}}$$

(19)

$$I_{LN} = \frac{I_o}{1 - \delta_N} \tag{20}$$

## 2.2 Proposed DC – AC Topology

Fig. 14 (A), (B) and (C) shows the proposed IMMC with 3, 5 and 11 submodules respectively.

In this chapter the new DC-AC Interconnected Modular Multilevel Converter (IMMC) is presented. The proposed converter produces a sinusoidal output with adjustable voltage and frequency (v/f) suitable for multitude of applications. The output voltage/frequency can be varied over a wider range. The proposed converter is a promising candidate for applications that require

sinusoidal voltage or current. The proposed converter has the following advantages: sinusoidal output voltage with v/f control; no acoustic noise in motor drives applications; absence of dv/dt related issues due to long wire connections; compact size/weight/volume. The converter is modular in construction, employs high frequency L-C components and semiconductor switches can be stacked for voltage sharing. This chapter details the operating modes, control aspects along with an illustrative design example for a three and eleven submodules converter. Experimental results on a laboratory prototype converter employing 600V GaN and 1200 V SiC devices are discussed in the following chapters.

The IMMC consists of several interconnected modular submodules as seen in Fig. 14. Each submodule is connected across two capacitors and has two wide bandgap switches and an inductor. The DC-AC conversion is achieved by switching on and off capacitors to produce the desired output. On the contrary to several switched capacitors multilevel converters, the proposed IMMC requires small capacitors to filter the switching frequency. The size of the LC components of the converter can be decreased by operating the converter at a high switching frequency.

# 2.3 Operation and Modulation

The IMMC operation and modulation can be explained using the 3-submodule topology shown in Fig. 15 (A). The capacitors will share the total input DC voltage. Fig. 15 shows the voltage across the capacitors  $V_{C1}$ ,  $V_{C2}$ ,  $V_{C3}$ , and  $V_{C4}$ .

Fig. 16 shows the modulating signal that controls the voltage across the capacitors. The sum of  $V_{C1}$ , and  $V_{C2}$  or  $V_{C3}$ , and  $V_{C4}$  shown in Fig. 17 gives a full sinusoidal wave which is the output voltage  $V_{AO}$ .

Fig. 15 (A) The proposed IMMC with for different operating modes. (B) The state to generate Vout= VDC/2. (C) The state to generate Vout= 0. (D) The state to generate Vout= -VDC/2. Note:  $\delta$  is the duty ratio of the submodule.

To illustrate that using the 3 submodules design, two capacitors are bypassed and the other two are in the balancing mode as seen in Fig. 15. For the 11 submodules design, six capacitors will be bypassed and the remaining six are in the balancing mode. The sum of the voltages across the balancing mode capacitors is the sinusoidal voltage.

Fig. 16 The modulating signal for the 3 submodules design.

Fig. 17 The reference capacitor voltages for the 3 submodules design. The lower two capacitors reference voltages are one minus the corresponding upper capacitor reference voltage.

Fig. 18 The duty cycle for the three submodules.  $\delta_1$  is the duty for SM1;  $\delta_2$  for SM2;  $\delta_3$  for SM3. The duty is calculated from the ratio of the two reference voltages of the submodules capacitors as illustrated in equation (21) and (22). Each submodule has two switches that work in a complementary manner to each other.

Fig. 19 The submodules voltage with 3 submodules. Note:  $V_{SM1} = V_{C1} + V_{C2}$ ;  $V_{SM2} = V_{C2} + V_{C3}$ ;  $V_{SM3} = V_{C3} + V_{C4}$ .

Fig. 15 shows the operating states of the proposed IMMC. Two capacitors are equally balanced at a time to generate a certain output voltage. Fig. 15 (B) shows that balancing the  $V_{C3}$ , and  $V_{C4}$  while bypassing the rest gives  $V_{AO} = V_{DC}/2$ . When  $V_{C2}$  and  $V_{C3}$  are balancing,  $V_{AO} = 0$  as in Fig. 15 (C). Moreover, balancing  $V_{C1}$  and  $V_{C2}$  yields an output voltage of  $V_{DC}/2$ .

The modulation technique to produce a sinusoidal output voltage is achieved by slicing the modulating sinusoidal signal according to half the number of capacitors used in the topology. The reference capacitor voltages for all capacitors are generated as shown in Fig. 17. From the reference capacitor voltages, the duty cycle of each submodule is generated using (21) for the upper submodules and (22) for the lower submodules. The factor  $\epsilon$  is a very small number introduced to the equation to avoid the division by zero. The term (n) in (21) and (22) is the submodule's number and N is the number of capacitors +1.

The duties for the upper submodules for  $0 < n < \frac{N}{2}$ :

$$\delta_{n} = 1 - \frac{V_{C(n+1)}}{V_{C(n)} + V_{C(n+1)} + \epsilon}$$

(21)

The duties for the lower submodules for  $\frac{N}{2} < n \le N - 2$ :

$$\delta_{\rm n} = \frac{V_{C(n)}}{V_{C(n)} + V_{C(n+1)} + \epsilon} \tag{22}$$

As shown in Fig. 18, the duties smoothly change between 0 that bypasses the lower capacitor of the submodule, 0.5 that balances the two submodules capacitors and 1 that bypasses the upper capacitor of the submodule. The submodules voltages are illustrated in Fig. 19.

Fig. 20 shows how the converter works. Each capacitor is switched to have a slice of the sine wave and the output voltage is the sum of two capacitors minus  $V_{DC}/2$ .

In summary, the output voltage is the sum of the voltage of two capacitors minus half the DC link voltage as seen in Fig. 20. Therefore, producing a pure sinusoidal output with any frequency (it can be as low as 1 Hz) is possible by synthesizing the desired waveform shape and frequency on the capacitors.

The mechanism of the five submodules IMMC is explained as well to strengthening the understanding of how the converter works for any number of submodules. Fig. 21 shows the states to generate the major values of the output sine wave ( $V_{DC}$ , 0 and  $-V_{DC}$ ). Each state represents a point on the sinusoidal waveform. Fig. 22 shows the modulating signal used in the modulation of the converter. The modulating signal is sliced according to half the number of the capacitors in the converter. For example, the five submodules IMMC has six capacitors in total; therefore, the modulating signal is sliced to three slices as shown in Fig. 22. The upper three capacitors will have reference voltages that are opposite to the three lower capacitors as seen in Fig. 23. The duty ratio of each submodule is calculated from equation (21) and (22) to result the duty ratios seen in Fig. 24.

Fig. 21 (A) The proposed IMMC with five submodules. (B) The state to generate Vout= VDC/2. (C) The state to generate Vout= 0. (D) The state to generate Vout= -VDC/2. Note:  $\delta$  is the duty ratio of the submodule.

Fig. 25 shows the submodules voltages of the five submodules IMMC. Each submodule's voltage is the sum of the two capacitors voltages connected to the submodule. For example, the voltage across  $SM_1$  ( $V_{SM1}$ ) is the sum of  $V_{C1}$  and  $V_{C2}$ . The same principal is applied to the rest of the submodules as shown in Fig. 25.

Fig. 22 The modulating signal for the 5 submodules design.

Fig. 23 The reference capacitor voltages for the 3 submodules design. The lower two capacitors reference voltages are one minus the corresponding upper capacitor reference voltage.

Fig. 24 The duty cycle for the three submodules.  $\delta_1$  is the duty for SM1;  $\delta_2$  for SM2;  $\delta_3$  for SM3;  $\delta_4$  for SM4;  $\delta_5$  for SM5.

Fig. 25 The submodules voltage with 3 submodules. Note:  $V_{SM1} = V_{C1} + V_{C2}$ ;  $V_{SM2} = V_{C2} + V_{C3}$ ;  $V_{SM3} = V_{C3} + V_{C4}$ ;  $V_{SM4} = V_{C4} + V_{C5}$ ;  $V_{SM5} = V_{C5} + V_{C6}$ .

Fig. 26 The mechanism of the five submodule IMMC. Each capacitor is switched to have a slice of the sine wave and the output voltage is the sum of two capacitors minus VDC/2.

Fig. 26 summarizes the basic principal of how the five submodules IMMC works. The principal is similar to the three submodules IMMC. Each capacitor voltage is synthesized to have a slice of a sine wave. Therefore, the sum of the slices minus the half the DC link (for the one phase inverter) is a full sine wave at the output.

#### 2.4 DC-AC IMMC Circuit Analysis

The modeling of the topology is derived for the three submodules design seen in Fig. 14 (A) and then extended to an arbitrary number of submodules similar to Fig. 14 (B) and (C). For modeling purposes, the topology is subdivided into four nodes and the dc-link voltage with center point ground is shown. The currents of the capacitors are derived by applying the Kirchhoff's Current Law (KCL) at the nodes defined in Fig. 27. The currents of the capacitors are written in (23), (24), (25) and (26).

$$I_{C1} = C \frac{dV_{C1}}{dt} = -\delta_1 * I_{L1} + I_{s+}$$

(23)

$$I_{C2} = C \frac{dV_{C2}}{dt} = (1 - \delta_1) * I_{L1} - \delta_2 * I_{L2} + I_{s+}$$

(24)

$$I_{C3} = C \frac{dV_{C3}}{dt} = (1 - \delta_2) * I_{L2} - \delta_3 * I_{L3} - I_{s-}$$

(25)

$$I_{C4} = C \frac{dV_{C4}}{dt} = (1 - \delta_3) * I_{L3} - I_{s-}$$

(26)

The currents for the inductors (submodules) written in (27), (28) and (29) are found by rearranging (23), (25) and (26).

$$I_{SM1} = I_{L1} = \frac{I_{s+} - I_{C1}}{\delta_1}$$

(27)

$$I_{SM2} = I_{L2} = \frac{I_{C3}}{1 - \delta_2} + \frac{\delta_3}{(1 - \delta_2)(1 - \delta_3)} I_{C4} + \frac{1 + \delta_3}{(1 - \delta_2)(1 - \delta_3)} I_{S-}$$

(28)

$$I_{SM3} = I_{L3} = \frac{I_{C4} + I_{s-}}{1 - \delta_3}$$

(29)

Similarly, the converter is subdivided into 6 loops that contain an inductor as seen in Fig. 28. Kirchhoff's Voltage Law (KVL) is applied to the loops to find the inductors voltages. The voltages of the inductors for the topology shown in Fig. 28 are represented in (30), (31) and (32).

$$V_{L1} = L \frac{di_{L1}}{dt} = \delta_1 * V_{C1} + (\delta_1 - 1) * V_{C2}$$

(30)

$$V_{L2} = L \frac{di_{L2}}{dt} = \delta_2 * V_{C2} + (\delta_2 - 1) * V_{C3}$$

(31)

$$V_{L3} = L \frac{di_{L3}}{dt} = \delta_3 * V_{C3} + (\delta_3 - 1) * V_{C4}$$

(32)

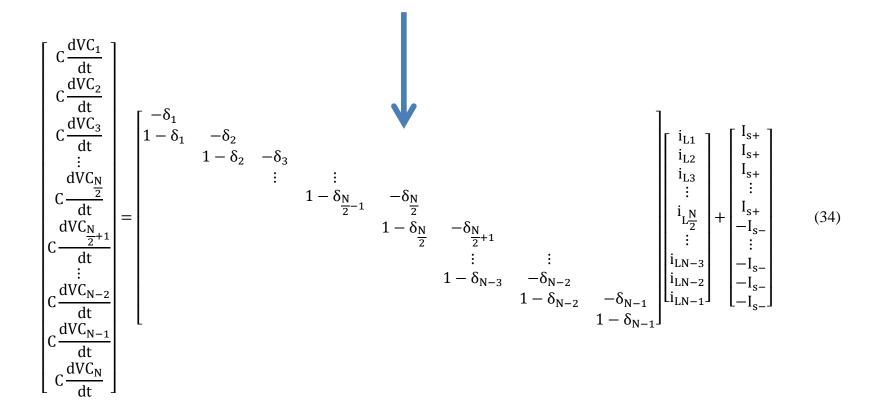

Increasing the number of submodules reduces the voltage stress on the devices allowing lower device ratings as shown in Fig. 14. Thus, (23), (24), (25) and (26) are expressed in the matrix format as shown in (33) and then extended to an N number of submodules as seen in (34). Similarly, (30), (31) and (32) are written in the matrix format shown in (35) and then extended to an N number of submodules as shown in (36).

Fig. 27 Nodes to obtain the capacitors current equations.

Fig. 28 Loops to obtain the inductors voltage equations.

$$\begin{bmatrix} C \frac{dVC_1}{dt} \\ C \frac{dVC_2}{dt} \\ C \frac{dVC_3}{dt} \\ C \frac{dVC_3}{dt} \\ C \frac{dVC_4}{dt} \end{bmatrix} = \begin{bmatrix} -\delta_1 \\ 1 - \delta_1 & -\delta_2 \\ 1 - \delta_2 & -\delta_3 \\ 1 - \delta_3 \end{bmatrix} \begin{bmatrix} i_{L1} \\ i_{L2} \\ i_{L3} \end{bmatrix} + \begin{bmatrix} I_{s+} \\ I_{s+} \\ -I_{s-} \\ -I_{s-} \end{bmatrix}$$

$$\begin{bmatrix} c \frac{dVC_4}{dt} \\ c \frac{dVC_4}{dt} \\ \end{bmatrix}$$

For N number of Submodules (33)

$$\begin{bmatrix} L \frac{di_{L1}}{dt} \\ L \frac{di_{L2}}{dt} \\ L \frac{di_{L3}}{dt} \end{bmatrix} = \begin{bmatrix} \delta_1 & \delta_1 - 1 \\ & \delta_2 & \delta_2 - 1 \\ & & \delta_3 & \delta_3 - 1 \end{bmatrix} \begin{bmatrix} V_{C1} \\ V_{C2} \\ V_{C3} \\ V_{C4} \end{bmatrix}$$

(35)

# For N number of Submodules

$$\begin{bmatrix} L \frac{di_{L1}}{dt} \\ L \frac{di_{L2}}{dt} \\ L \frac{di_{L3}}{dt} \\ \vdots \\ L \frac{di_{LN-3}}{dt} \\ L \frac{di_{LN-3}}{dt} \\ L \frac{di_{LN-2}}{dt} \\ L \frac{di_{LN-2}}{dt} \end{bmatrix} = \begin{bmatrix} \delta_1 & \delta_1 - 1 \\ & \delta_2 & \delta_2 - 1 \\ & & \delta_3 & \delta_3 - 1 \\ & & & \vdots & \vdots \\ & & & \delta_{N-2} & \delta_{N-3} - 1 \\ & & & & \delta_{N-3} & \delta_{N-3} - 1 \\ & & & & \delta_{N-1} & \delta_{N-1} - 1 \end{bmatrix} \begin{bmatrix} V_{C1} \\ V_{C2} \\ V_{C3} \\ \vdots \\ V_{CN-2} \\ V_{CN-2} \\ V_{CN-1} \\ V_{CN} \end{bmatrix}$$

$$(36)$$

The normalized current rating of the submodules with respect to the output current is calculated in (37). The submodules current RMS ratings are found by dividing the RMS value of the inductor current  $(I_{L(N)})$  by the RMS value of the output current  $(I_A)$  shown in Fig. 27.

$$I_{SM(N)-pu} = \frac{I_{L(N)-RMS}}{I_{A-RMS}}$$

(37)

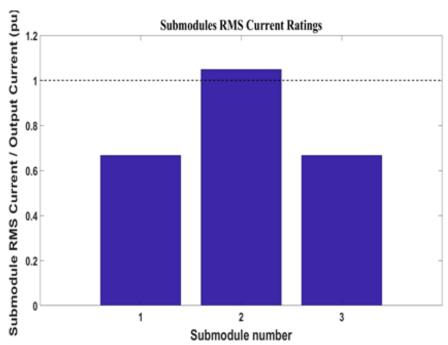

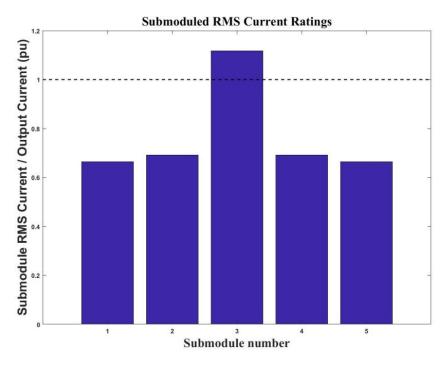

The Normalized RMS current of the submodules (as a function of the RMS output current) of the 3, 5 and 11 submodules IMMC are shown in Fig. 29, Fig. 30 and Fig. 31. The middle submodule has the highest current ratings. Increasing the number of submodules decreases the voltage stress but increases the current stress.

The voltage stress on the devices is reduced when the number of submodules increases.

Table 2 summarizes the voltage stress on the devices with respect to the number of submodules.

Fig. 29 Submodules current RMS rating as a function of the RMS output current in per unit for the 3 submodules design.

Fig. 30 Submodules current RMS rating as a function of the RMS output current in per unit for the 5 submodules design.

submodules design

Table 2 voltage stress on switches with respect to the number of SMs

| Number of SMs | <b>Blocking voltage</b> | Total # of Cs | Total # of Ls |

|---------------|-------------------------|---------------|---------------|

| 3             | VDC                     | 4             | 3             |

| 5             | $\frac{2VDC}{3}$        | 6             | 5             |

| 7             | $\frac{VDC}{2}$         | 8             | 7             |

| 9             | 2 <i>VDC</i> 5          | 10            | 9             |

| 11            | $\frac{VDC}{3}$         | 12            | 11            |

| 13            | 2 <i>VDC</i> 7          | 14            | 13            |

| 15            | $\frac{VDC}{4}$         | 16            | 15            |

| 17            | 2 <i>VDC</i> 9          | 18            | 17            |

| 19            | <u>VDC</u><br>5         | 20            | 19            |

| N             | $\frac{4}{N+1}VDC$      | N+1           | N             |

# 2.5 Comparison

Table 3 compares the number of switches, diodes, passive components, and size index for the IMMC to the major multilevel topologies which are Neutral Point Clamped Converter (NPC), Flying Capacitor Converter (FCC), Modular Multilevel Converter (MMC), and the Cascaded H-Bridge Converter (CHB).

Table 3 Comparison between single phase IMMC and popular multilevel existing topologies.

| Number of levels = n                | NPC [7, 12, 13] | FCC [14, 15]                       | MMC [8, 16] | Proposed<br>IMMC | CHB [17, 18] |

|-------------------------------------|-----------------|------------------------------------|-------------|------------------|--------------|

| Number of modules                   | -               | -                                  | 2(n-1)      | 2(n-1.5)         | (n-1)/2      |

| Number of switches                  | 2(n-1)          | 2(n-1)                             | 4(n-1)      | 4(n-1.5)         | 2(n-1)       |

| Number of<br>Clamping<br>Diodes     | (n-1)(n-2)      | -                                  | -           | -                | -            |

| Number of capacitors                | n-1             | $\frac{1}{2}\mathrm{n}(n-1)$       | 2(n-1)      | 2(n-1)           | (n-1)/2      |

| Number of inductors                 | -               | -                                  | 2           | 2(n-1.5)         | -            |

| Total<br>Components<br>count        | (n^2 - 1)       | (n-1)(n+4)/2                       | 6(n-1)+2    | 8n – 11          | 2.5(n-1)     |

| Capacitance ratio index             | 34              | 1                                  | 200         | 1                | 100          |

| Capacitor<br>Overall size<br>index  | 34(n-1)         | $\frac{1}{2}\operatorname{n}(n-1)$ | 400(n-1)    | 2(n-1)           | 50(n-1)      |

| Inductance ratio index              | -               | -                                  | 100         | 1                | -            |

| Inductance<br>Overall size<br>index | -               | -                                  | 200         | 2(n-1.5)         | -            |

The total number of components is defined as an equation by adding all components together as function of the number of levels. Fig. 32 plots the total number of components needed to achieve a certain number of levels for each one of the topologies. It is important to note that the IMMC does not generate a multilevel output but a pure sinewave that does not need

filtering. The number of levels for the IMMC is the number of submodules which is half the number of capacitors +1 and it is just used as a common base for comparison.

The CHB displays a superior performance in terms of the total number of components needed. It requires the lowest number of components for all numbers of levels. However, CHB requires multi-winding transformers and rectifier circuits to provide the DC for each submodule which makes the CHB expensive and bulky [19].

The NPC needs the highest number of components for number of levels larger than 7 levels. Therefore, the NPC is an unpractical solution [20, 21].

The IMMC has a linear relationship between the number of levels and components. However, with only 3 submodules the quality of the output is a pure sinusoidal wave which the other multilevel cannot generate without a filter. Therefore, it is recommended to operate the IMMC with a small number of submodules if the quality of the output is the only concern.

The overall capacitor index of all topologies is shown in Fig. 33. The IMMC has the least capacitor size index for almost all number of levels. This is because the capacitors are only used to filter the high switching frequency. Therefore, the IMMC reduces the overall capacitance requirements ensuring a high-power density operation.

Fig. 32 Number of levels VS number of components.

Fig. 33 Number of levels VS overall capacitor size index.

Table 4 Size Comparison

|                                                   | MMC   | IMMC  | СНВ   | FCC   | NPC   |

|---------------------------------------------------|-------|-------|-------|-------|-------|

| Capacitor Voltage Ripple ΔV                       | 5%    | 1%    | 5%    | 1%    | 5%    |

| Inductor Current Ripple $\Delta I$                | 5%    | 1%    | -     | -     | -     |

| Switching Frequency $f_s$                         | 6kHz  | 60kHz | 6kHz  | 60kHz | 6kHz  |

| Output Frequency f <sub>o</sub>                   | 60Hz  | 60Hz  | 60Hz  | 60Hz  | 60Hz  |

| Inductor Current Ripple Frequency $f_{\Delta IL}$ | 120Hz | 60kHz | -     | -     | -     |

| Capacitor Current Frequency $f_{Ic}$              | 60Hz  | 60kHz | 120Hz | 60kHz | 360Hz |

| Capacitor Voltage Ripple Frequency $f_{\Delta V}$ | 60Hz  | 60kHz | 120Hz | 60kHz | 360Hz |

| Capacitor Ratio Index                             | 200   | 1     | 100   | 1     | 34    |

A detailed comparison between the proposed converter and the other multilevel converter topologies is established in Table 4. The approach to compare the passive elements size is to study the ripple on the capacitor and the inductor. After that, the size needed to minimize the ripple to an acceptable range is calculated. The size comparison is discussed for the proposed converter and the MMC converter seen in Fig. 6 to illustrate the comparison process. The same approach can be taken for the other multilevel topologies.

The capacitance ratio index in Table 3 is a term introduced to compare the capacitor size requirement for each to topology. Table 4 defines the parameters for the proposed IMMC and MMC with the following assumptions: the maximum allowed ripple on the capacitor for the IMMC and MMC are 1% and 5% respectively; the proposed converter is switching at 60 kHz.

The choice of 5% allowed ripple of the MMC is given a higher margin because an output filter is used with the MMC. On the other hand, the IMMC does not require an output filter; thus, the ripple must be minimized to generate a high quality sinusoidal output voltage. The capacitor of the MMC has a low frequency ripple component (60 Hz) and the capacitors of proposed converter are used to filter the high switching frequency (60kHz). Therefore, the capacitance ratio index is calculated in (38):

Capacitor Ratio Index =

$$\frac{C_{MMC}}{C_{IMMC}} = \frac{f_{Ic-IMMC}*\Delta V_{IMMC}}{f_{Ic-MMC}*\Delta V_{MMC}} = \frac{60000 \, Hz * 1\%}{60 \, Hz * 5\%} = 200$$

(38)

The size of the capacitor needed to filter the 60 Hz ripple of the MMC is 200 times the capacitor size needed for the proposed IMMC.

The same approach can be used for the inductor ratio index. The inductor in the MMC is used to suppress the circulating current which is a negative sequence current at double-fundamental frequency (120Hz). On the other hand, the ripple in the inductor current in the IMMC is a high frequency ripple. Inductor Ratio Index is calculated in equation (39):

Inductor Ratio Index =

$$\frac{L_{MMC}}{L_{IMMC}} = \frac{f_{\Delta IL-IMMC}*\Delta I_{IMMC}}{f_{\Delta IL-MMC}*\Delta I_{MMC}} = \frac{60000 \, Hz * 1\%}{120 \, Hz * 5\%} = 100$$

(39)