# Research on COordinate Rotation DIgital Computer Hardware Architectures and Applications

# NGUYEN THI HONG THU

Department of Engineering Science The University of Electro-Communications

A dissertation submitted for the degree of  $Doctor\ of\ Engineering$  September 2018

# Research on COordinate Rotation DIgital Computer Hardware Architectures and Applications

by

# NGUYEN THI HONG THU

A Dissertation Submitted for the degree of DOCTOR OF ENGINEERING

at

THE UNIVERSITY OF ELECTRO-COMMUNICATIONS

SEPTEMBER 2018

I would like to dedicate this dissertation to my beloved family, especially my mother. I am thankful to my closet friends and my beloved husband for encouraging me during the time of this work.

Tokyo, 2018.09

#### Acknowledgements

First of all, I would like to express my deepest appreciation to my supervisors, Professor Cong-Kha PHAM and Professor Koichiro ISHIBASHI, for their encouragement, guidance, and support during my doctor course. Throughout the time of my doctor course, I received many advice to solve not only the problem in the research but also the problem in my life. Thank for their supports, I grew-up on doing research and writing papers. It is my pleasure to become their student, and I hope that we still maintain the good relationship and the cooperation in the future.

I would like to thank the University of Electro-Communications Tokyo (UEC) and Japan Ministry of Education, Culture, Sports, Sicence, and Technology (MEXT) for giving me a chance to study in Japan. Thank to the scholarship, I have an opportunity to research on Electronic technology and to study about Japanese culture. I also would like to thank the UEC's professors and my Japanese teachers for their careness and support during my doctor course.

I would like to send my thank to my teachers and colleagues in the Faculty of Electronics and Telecommunications, Ho Chi Minh Vietnam National University, University of Science. I also would like to say thank you to all of members in PHAM's laboratory and my friends in Japan and in Vietnam. Their kindness and their help encouraged me to finish my researches.

Last but not least, I would like to acknowledge VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Synopsys, Inc. and Cadence Design Systems, Inc for their supporting for this work.

# Research on COordinate Rotation DIgital Computer Hardware Architectures and Applications

| APP]  | ROVED                   |

|-------|-------------------------|

| Prof. | Cong-Kha PHAM, Chairman |

| Prof. | Koichiro ISHIBASHI      |

| Prof. | Yoshinao MIZUGAKI       |

| Prof. | Eriko WATANABE          |

| Prof. | Yasushi YAMAO           |

| Date  | Approved by Chairman    |

# Copyright © 2018 by NGUYEN THI HONG THU

#### 和文要旨

CORDIC のハードウェア構成及び応用に関する研究

## グエンティホントゥ 電気通信大学

大学院情報理工学研究科 先進理工学専攻 博士後期課程

本論文では、CORDIC (Coordinate Rotation Digital Computer) のハードウェア構成及び応用の研究について述べる。

三角での角度と辺の関係を計算する三角法は、天文学の研究ではさまざまな用途でよく知られている。さらに、その応用は、今日、アーキテクチャ、測量、物理学、工学などの他の分野にも広がっている。sine、cosine、tangentは3つの重要な三角関数である。その逆関数はそれぞれarcsine、arccosine、arctangentである。これらの関数は、電卓、ロボット、デジタル信号プロセッサ、通信機器などの様々な科学製品にとって必須のものとなっている。従って、三角関数の高効率、低リソース及び低消費電力を有するアーキテクチャは、効果的な応用の実装につながる。

ルックアップテーブルやテイラー級数など、三角関数を計算する従来の方法がいくつかある。しかしながら、これらの方法は、複雑なアーキテクチャと多くのハードウェア資源を必要とする。 現実的には、ルックアップテーブルやテイラーシリーズのような手法は使用せず、三角関数を評価するために COordinate Rotation DIgital Computer アルゴリズム (以下 CORDIC と呼ぶ)を使用する。簡易なアプローチにより、CORDIC はシフターと加算器だけ構成でき、モーター制御、ナビゲーション、信号処理、無線通信等の様々な組み込み応用で重要な役割を果たしている。

1959 年に J. E. Volder によって最初に提出され、1971 年に J. S. Walther によって開発された CORDIC は、その単純な構成にもかかわらず、様々な超越計算を実行することができる。伝統的な CORDIC は、N ビットの精度の場合 N 回の反復を必要とするため、高精度の場合にはより多くのハードウェア資源や長い計算時間を要する。結果として、削減した実行時間及び合理的なハードウェア資源を有する CORDIC ハードウェア構成は、今日でも依然として必要とされている。さらに、現在、固定小数点および浮動小数点を扱うハードウェア構成は、その長所と短所がそれぞれ異なるため、多くの注目を集めている。具体的には、固定小数点ハードウェア構成ではハードウェア資源は少ないが、ある程度満足できる精度の結果が得ら

れる。一方、浮動小数点ハードウェア構成は、高精度を達成しながらも多 少のハードウェア資源を要求する。

本論文において、第一に2つの固定小数点 CORDIC ハードウェア構成を提案した。最初は、ARD-SCFE CORDIC ハードウェア構成である。この構成は、Angle Recording CORDIC (ARD) と Scaling-Free CORDIC (SCFE)を組み合わせた構成であり、回転モードでのみ動作する。提案した ARD-SCFE CORDIC ハードウェア構成は、ハードウェアの複雑さ、実行時間、及び計算精度との間の良いトレードオフを得た。さらに、ベクトルモードと回転モードの2つのモードで動作できる COR QR CORDIC ハードウェア構成を提案した。提案したCハードウェア構成を用いて多入力多出力(MIMO)信号検出器の一部である Sphere Decoder (SD) を実装した。結果として、実装されたSDは、LTE (Long Term Evolution) ダウンリンクモジュールに適していることが分かった。

第二に、ハイプリッド(HA)-CORDIC である浮動小数点 CORDIC ハードウェア構成を提案した。固定小数点データを入力し、浮動小数点データを出力する構成である。結果として、低リソース、低レイテンシ及び高精度出力を達成できた。さらに、HA-CORDIC ハードウェア構成を基本にし、並列にデータを入力できるパイプラインパラレル(PP)-CORDIC ハードウェア構成も提案した。PP-CORDIC は、離散コサイン変換(DCT)を使用するアプリケーションなどの固定の既知入力データ応用に適している。

結果として、提案した複数の CORDIC ハードウェア構成は、異なる利点を含み、異なる応用に適していることが確認できた。

## Abstract

Research on COordinate Rotation DIgital Computer

Hardware Architectures and Applications

#### NGUYEN THI HONG THU

Doctoral Program in Electronic Engineering

The University of Electro-Communications

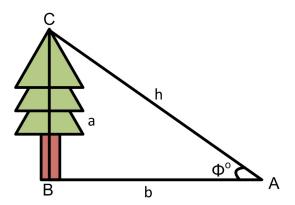

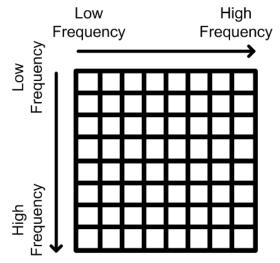

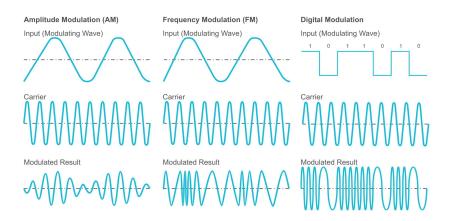

Trigonometry, the study of the relationship of angles and sides in triangles, is well known for various applications in the astronomical study. Furthermore, its applications nowadays are spreading to other fields such as architecture, surveying, physics, and engineering. Sine, cosine, and tangent are three significant trigonometric functions, of which inverse functions are arcsine, arccosine, and arctangent, respectively. Those functions have become essential tasks to various scientific products such as a calculator, robotics, digital signal processors, and communication devices. Therefore, a high efficiency, low resource, and low power consumption architecture for trigonometric functions will lead to effective application implementations.

There are several traditional ways to calculate a trigonometric function such as lookup-table and Taylor series. However, those methods require a complex architecture and high resources. In practical, calculator nowadays does not use an approach like lookup-table or Taylor series but the COordinate Rotation DIgital Computer algorithm (from now on referred as CORDIC) to evaluate trigonometric functions. Thanks to its straightforward approach, CORDIC requires only shifter and adder to operate, thus leading to a vital role in various embedded applications such as motor controls, navigation, signal processing, and wireless communication.

First presented by J. E. Volder in 1959 and then developed by J. S. Walther in 1971, CORDIC is capable of performing various transcendental calculations despite its simple architecture. The traditional CORDIC requires N iterations for N-bit accuracy, thus leading to high resources and latency for a high precision implementation. As a result, a CORDIC architecture with reduced execution time and reasonable resources cost is still in need nowadays. Moreover, fixed-point and floating-point designs nowadays draw much attention due to their different advantages and disadvantages. For specific, a fixed-point design needs low resources requirement while gives a satisfactory accuracy outcome. On the other hand, a floating-point design spends a high amount of resources while achieves a high precision.

In this dissertation, two fixed-point CORDIC architectures are proposed and analyzed. The first architecture is called ARD-SCFE CORDIC which is the combination of Angle Recording (ARD) and Scaling-Free (SCFE) techniques, and it only operates in the rotation mode. The proposed architecture gained the advantages of both original algorithms while overcame their drawbacks. As a result, ARD-SCFE CORDIC provided a good trade-off between hardware complexity, processing time, and error results. Furthermore, it can be configured as an arithmetic processor to calculate sine, cosine, hyperbolic sine, hyperbolic cosine, and multiplication. Another fixed-point CORDIC architecture presented in this dissertation is the CORDIC-based QR Decomposition (CQRD), and it can operate in two modes of vectoring and rotation. The purpose of CQRD architecture is to evaluate the QR Decomposition calculation. The proposed design achieved high performance, low resource, and low latency. Moreover, the CQRD module was applied to construct the Sphere Decoder (SD) implementation; the SD utilization is a signal detector in the Multiple-Input Multiple-Output (MIMO) system. After implemented, the experimental results of CQRD module were analyzed, and the proposed architecture was proven to be suitable for Long-Term Evolution (LTE) downlink module.

Furthermore, in this dissertation, a floating-point CORDIC architecture is

also proposed; the proposed design is called Hybrid Adaptive (HA) CORDIC. The HA-CORDIC architecture produces floating-point format output data based on fixed-point format input data. Thanks to the hybrid architecture, the HA-CORDIC design is capable of achieving low resource, low latency, and high accuracy performances. Moreover, an improvement of HA-CORDIC, called Pipeline Parallel (PP) CORDIC, was also developed in this work. The PP-CORDIC can process data continuously, which leading to a further improvement in processing time. The proposed PP-CORDIC is suitable for fixed and known input data applications such as Discrete Cosine Transform (DCT).

In summary, the proposed CORDIC hardware architectures in this work provide various advantages, and they are suitable for various applications especially for those high-performance systems that target low resources and low power consumption.

# List of Abbreviation

ARD Angle Recoding CORDIC

ASIC Application-specific integrated circuit

BER Bit-Error Rate

CORDIC COordinate Rotation DIgital Computer

CQRD CORDIC-based QR Decomposition

DCT Discrete Cosine Transform

DHT Discrete Harley Transform

DPD Digital Predistortion

DST Discrete Sine Transform

DSP Digital Signal Processor

FFT Fast Fourier Transform

FIFO First In, First Out

FPGA Field-programmable gate array

GR Givens Rotation

HA Hybrid Adaptive

IP Intellectual Property

LUTs Lookup tables

ML Maximum Likelihood

MMSE Minimum Mean Square Error

MSE Mean Square Error

MIMO Multiple Input Multiple Output

OFDM Orthogonal Frequency Division Multiplexing

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase-Shift Keying

QRD QR Decomposition

PP Pipeline Parallel

RM Rotation Mode

SCFE Scaling-Free

SD Sphere Decoding

${\rm SDA} \quad \ \, {\rm Sphere \; Decoding \; Algorithm}$

${\bf SOTB \quad Silicon\text{-}on\text{-}Thin\text{-}BOX}$

${\it VLSI} \quad {\it Very-Large-Scale Integration}$

VM Vectoring Mode

# Contents

|   | Abstract                                   |    |

|---|--------------------------------------------|----|

|   | List of Appreviation                       | i  |

|   | List of Figures                            | vi |

|   | List of Tables                             | ix |

| 1 | Introduction                               | 1  |

|   | 1.1 Research Background                    | 1  |

|   | 1.1.1 Trigonometric Functions              | 1  |

|   | 1.1.2 COordinate Rotation DIgital Computer | 3  |

|   | 1.2 Motivation and Contributions           | 5  |

|   | 1.2.1 Motivation                           | 5  |

|   | 1.2.2 Research Issues                      | 6  |

|   | 1.2.3 Research Approach                    | 7  |

|   | 1.2.4 Contributions                        | 8  |

|   | 1.3 Dissertation Layout                    | 10 |

| 2 | Technical Background                       | 11 |

|   | 2.1 CORDIC Literature                      | 11 |

|   | 2.1.1 CORDIC Formulas                      | 11 |

|   | 2.1.2 CORDIC Rotation Mode (RM-CORDIC)     | 12 |

|   | 2.1.3 CORDIC Vectoring Mode (VM-CORDIC)    | 13 |

|   | 2.2 Related Work                           | 14 |

|   | 2.2.1 Angle Recoding (ARD) CORDIC          | 14 |

|   |          | Scaling-free (SCFE) CORDIC                   |    |

|---|----------|----------------------------------------------|----|

| 3 |          | ed Fixed-point CORDIC Hardware Archi-        | 10 |

| _ | -        | s and Applications                           | 22 |

|   |          | dware Architecture for Rotation Mode (RM)    |    |

|   |          | Design Idea                                  |    |

|   |          | Architecture                                 |    |

|   |          | Results and Disscussion                      |    |

|   |          | dication of the Proposed RM-CORDIC           |    |

|   |          | Architecture                                 |    |

|   |          | Results and Discussion                       |    |

|   | 3.3 Hare | dware Architecture for Multi-Mode (MM) Dedi- |    |

|   |          | d to QR Decomposition                        | 36 |

|   | 3.3.1    | The QR Decomposition Issue                   | 36 |

|   |          | Design Idea                                  |    |

|   | 3.3.3    | Architecture                                 | 40 |

|   | 3.3.4    | Results and Discussion                       | 43 |

|   | 3.4 App  | dication of the Proposed MM-CORDIC           | 45 |

|   | 3.4.1    | Architecture                                 | 45 |

|   | 3.4.2    | Results and Discussion                       | 48 |

|   | 3.5 Cha  | pter Conclusion                              | 52 |

| 4 | Propos   | ed Floating-point CORDIC Hardware Ar-        |    |

|   | _        | are and Application                          | 54 |

|   |          | rid Adaptive (HA) CORDIC                     | 54 |

|   |          | Design Idea                                  |    |

|   |          | Architecture                                 |    |

|   |          | Results and Discussion                       |    |

|   |          | Improvement of the HA-CORDIC: Pipeline Par-  |    |

|   |          | (PP) CORDIC                                  | 70 |

|   |          | Design Idea                                  |    |

### Contents

|              | 4.2.2 Architecture                        | 71         |

|--------------|-------------------------------------------|------------|

|              | 4.2.3 Results and Discussion              | 72         |

|              | 4.3 Chapter Conclusion                    | 75         |

| 5            | Conclusions and Future Work               | <b>7</b> 6 |

|              | 5.1 Conclusion                            | 76         |

|              | 5.1.1 Achievement                         | 78         |

|              | 5.1.2 Limitations                         | 79         |

|              | 5.2 Future Work                           | 80         |

|              | Appendix                                  | 82         |

| $\mathbf{A}$ | Full chip photos                          | 82         |

| В            | List of Publications                      | 85         |

|              | B.1 Journals                              | 85         |

|              | B.2International Conference Presentations | 86         |

|              | Author Biography                          | 98         |

# List of Figures

| 1.1  | Example of trigonometric functions                                               | 2  |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | Discrete Cosine Transform [1]                                                    | 2  |

| 1.3  | Trigonometric functions in modulations [2]                                       | 3  |

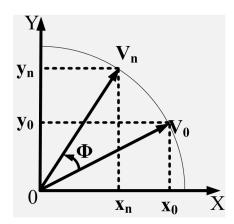

| 2.1  | A coordinate of a vector in two-dimentional plane                                | 13 |

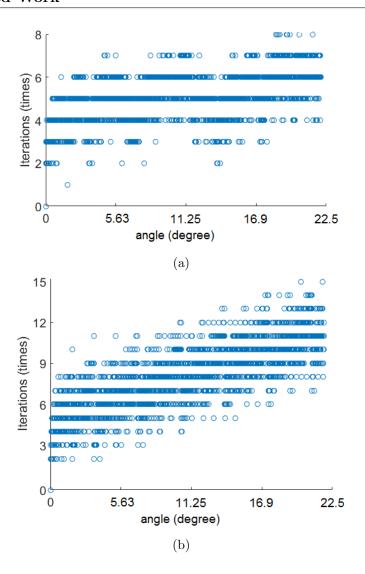

| 2.2  | The iterations of: (a) ARD CORDIC. (b) SCEF CORDIC                               | 18 |

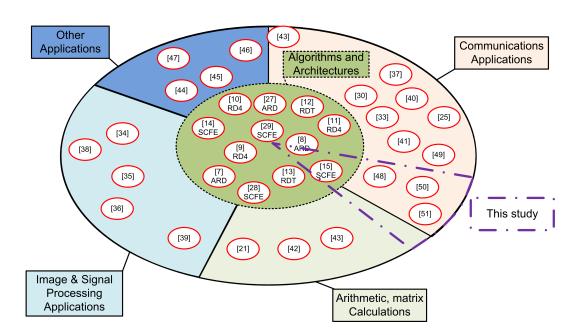

| 2.3  | The literature review and our research                                           | 19 |

| 3.1  | The flow chart of ARD-SCFE                                                       | 23 |

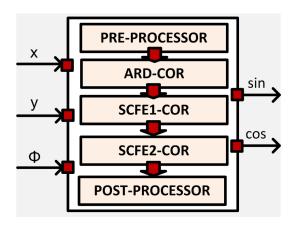

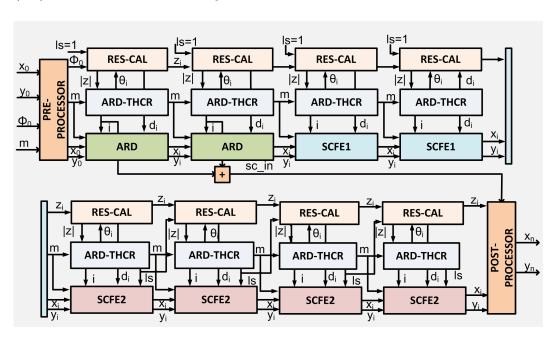

| 3.2  | The architecture of ARD-SCFE                                                     | 25 |

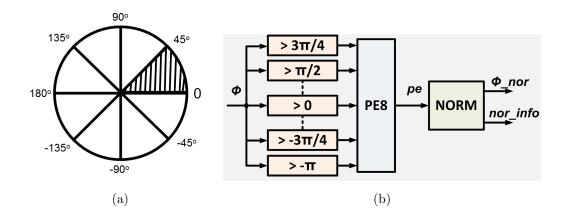

| 3.3  | (a) The circular circle. (b) The architecture of PREC module                     | 25 |

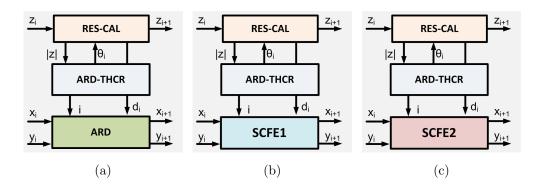

| 3.4  | The archiecture of: (a) ARD-COR module. (b) SCFE1-COR module. (c)                |    |

|      | SCFE2-COR module                                                                 | 26 |

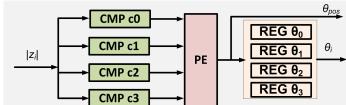

| 3.5  | The architecture of ARD-THCR module                                              | 27 |

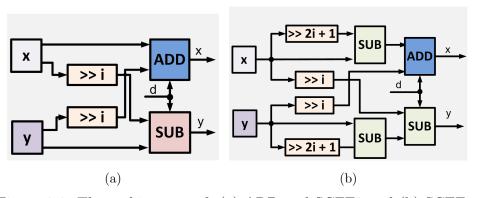

| 3.6  | The architecture of: (a) ARD and SCFE2 and (b) SCEF1                             | 27 |

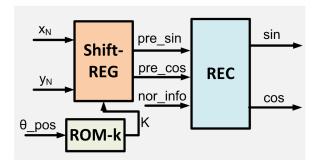

| 3.7  | The architecture of POSC module                                                  | 28 |

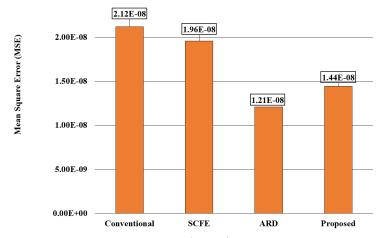

| 3.8  | The Mean Square Error (MSE) comparison of ARD-SCFE with other pre-               |    |

|      | vious algorithm.                                                                 | 29 |

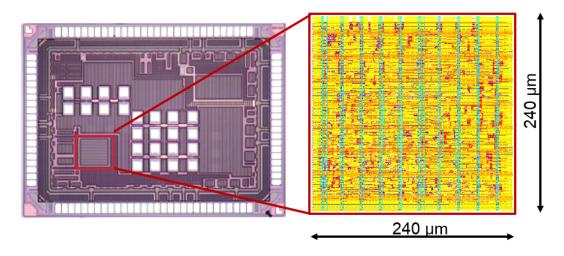

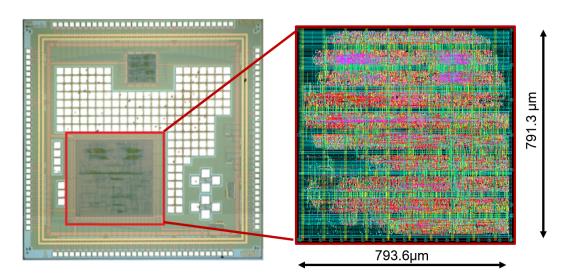

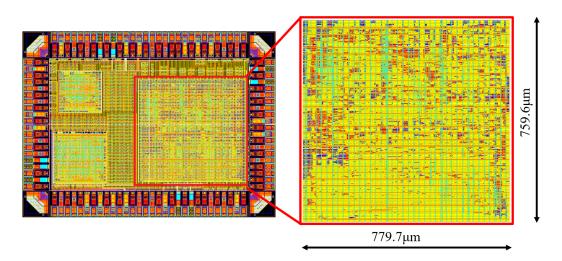

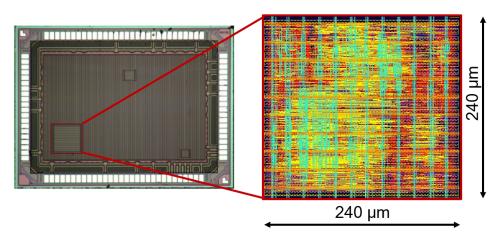

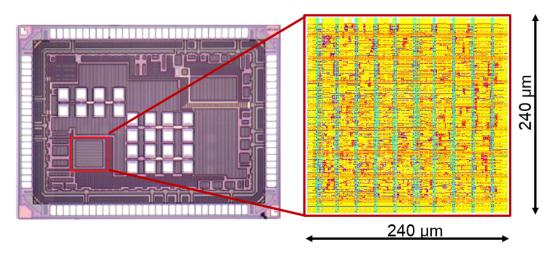

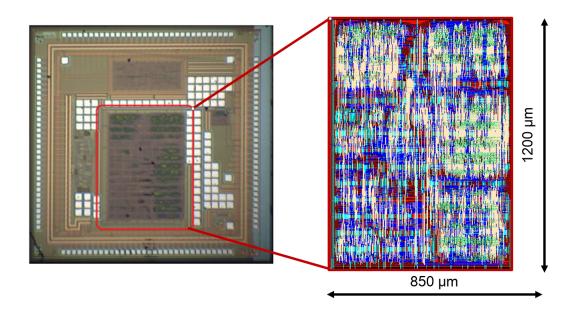

| 3.9  | The fabrication of ARD-SCFE (red square) and its layout on SOTB $65~\mathrm{nm}$ |    |

|      | process                                                                          | 30 |

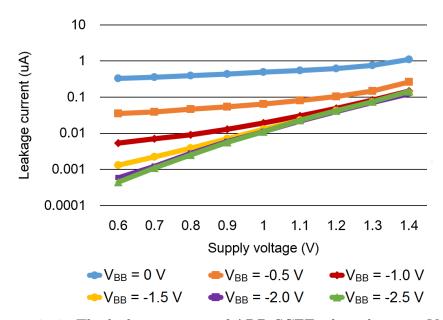

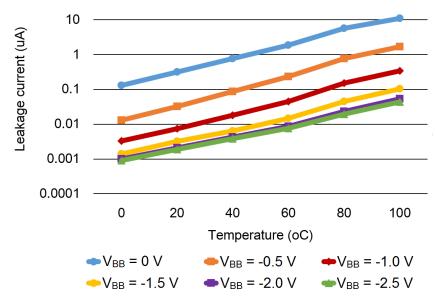

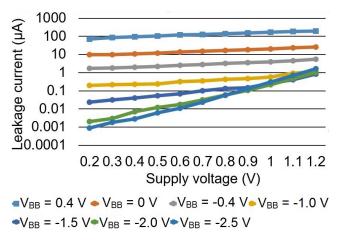

| 3.10 | The leakage current of ARD-SCFE when changing $V_{BB}$                           | 33 |

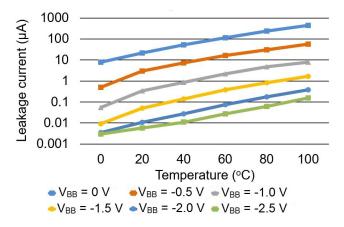

| 3.11 | The leakage current of ARD-SCFE when changing the temperature. $$                | 33 |

| 3.12 | The architecture of ARI-ARD-SCFE                                                 | 34 |

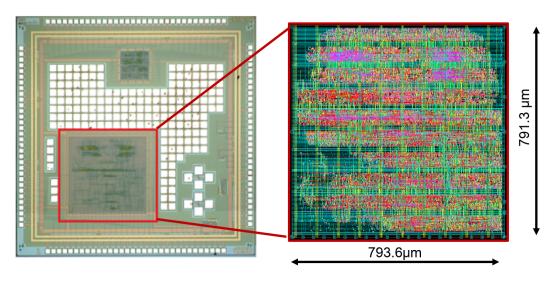

| 3.13 | The fabrication of ARI-ARD-SCFE (red square) and its layout on 180 nm            |    |

|      | CMOS process                                                                     | 35 |

# List of Figures

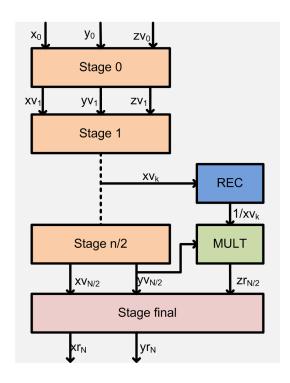

| 3.14 | The architecture of COR-QR                                                                                                  | 40 |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

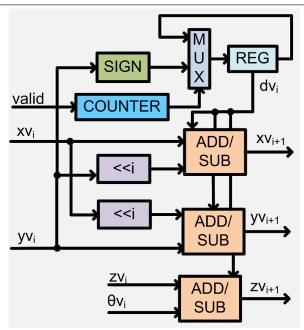

| 3.15 | The architecture of stage $i^{th}$ in COR-QR                                                                                | 41 |

| 3.16 | The architecture of final stage in COR-QR                                                                                   | 42 |

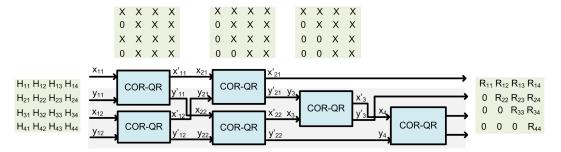

| 3.17 | The architecture of CQRD                                                                                                    | 42 |

| 3.18 | The application system of CQRD                                                                                              | 44 |

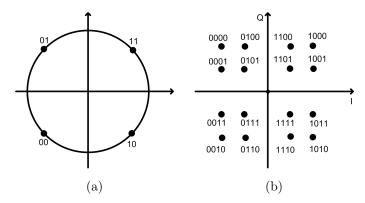

| 3.19 | The constellation of: (a)QPSK modulation. (b)16-QAM modulation                                                              | 45 |

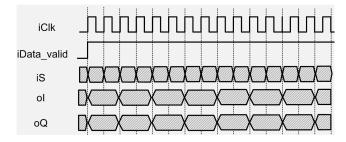

| 3.20 | The waveform of QPSK modulation                                                                                             | 45 |

| 3.21 | The waveform of MIMO mapper                                                                                                 | 46 |

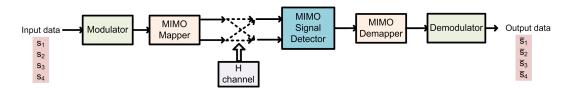

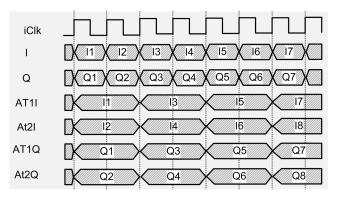

| 3.22 | MIMO channel                                                                                                                | 47 |

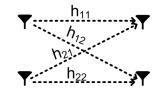

| 3.23 | The architecture of SD module                                                                                               | 47 |

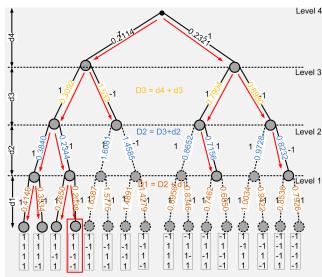

| 3.24 | The priciple of K-best algorithm                                                                                            | 47 |

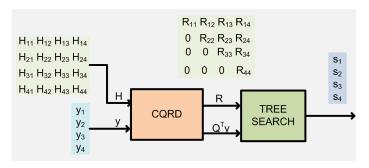

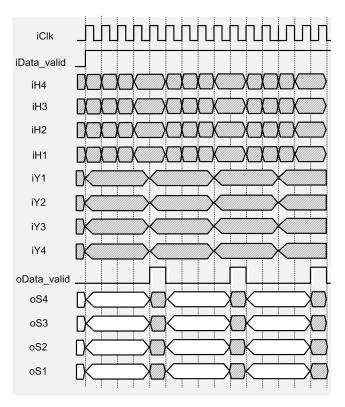

| 3.25 | The waveform of SD module                                                                                                   | 48 |

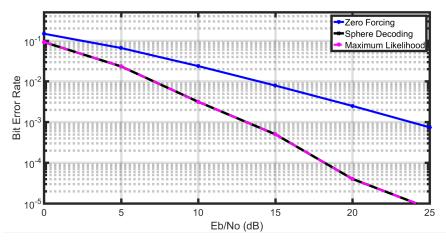

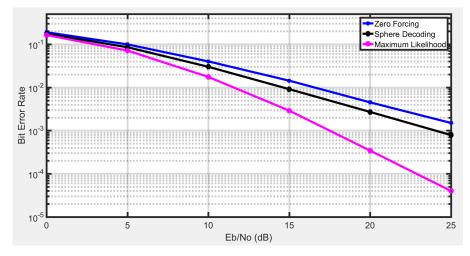

| 3.26 | BER of MIMO system in case of QPSK modulation and SD K-search with                                                          |    |

|      | $K = 16. \dots \dots$ | 49 |

| 3.27 | BER of MIMO system in case of QPSK modulation and SD K-search with                                                          |    |

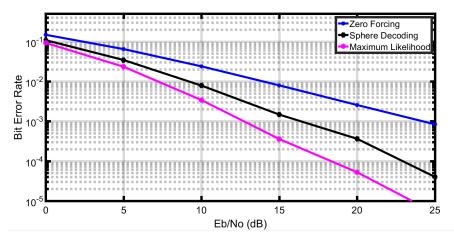

|      | K=4.                                                                                                                        | 49 |

| 3.28 | BER of MIMO system in case of QAM modulation and SD K-search with                                                           |    |

|      | K=4.                                                                                                                        | 49 |

| 3.29 | The layout of SD module for QPSK modulation                                                                                 | 51 |

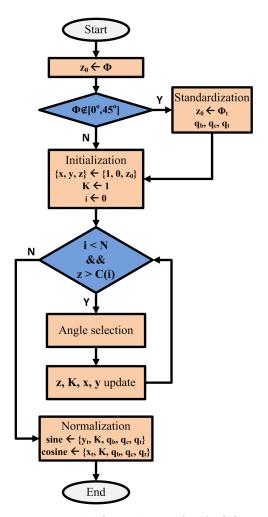

| 4.1  | The flow chart of HA-CORDIC                                                                                                 | 55 |

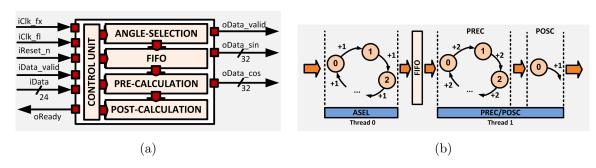

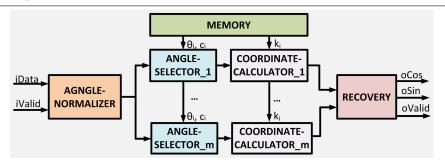

| 4.2  | (a) The general block diagram of HA-CORDIC. (b) The mechanism of HA-                                                        |    |

|      | CORDIC                                                                                                                      | 58 |

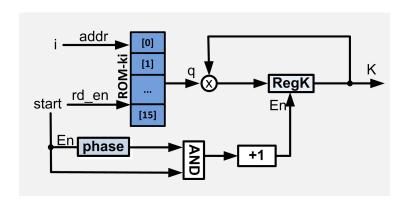

| 4.3  | The hardware architecture of ASEL module                                                                                    | 59 |

| 4.4  | A description of normalization technique                                                                                    | 59 |

| 4.5  | The hardware architecture of SNR module                                                                                     | 59 |

| 4.6  | The hardware architecture of PREC module                                                                                    | 60 |

| 4.7  | The hardware architecture of FADD-SUB module                                                                                | 60 |

| 4.8  | The hardware architecture of FMUL-ki module                                                                                 | 61 |

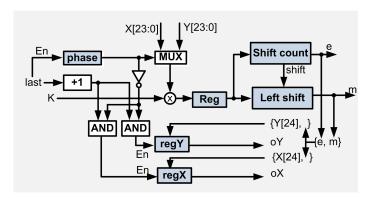

| 4.9  | The hardware architecture of FMUL-XYK module                                                                                | 62 |

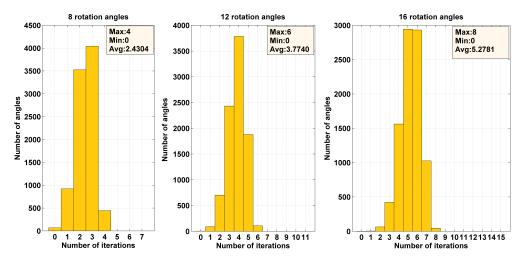

| 4.10 | The comparison in number of iterations in case of 8, 12, and 16 angle                                                       |    |

|      | constants                                                                                                                   | 62 |

# List of Figures

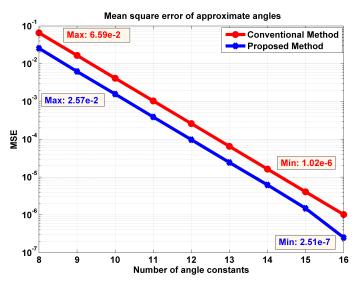

| 4.11 | The comparison in Mean Square Error (MSE) between HA-CORDIC with                                        |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | conventional algorithm                                                                                  | 63 |

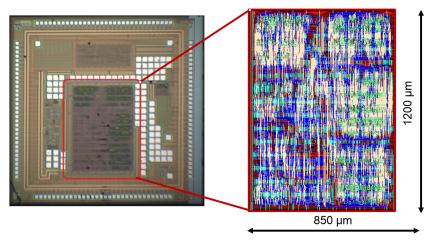

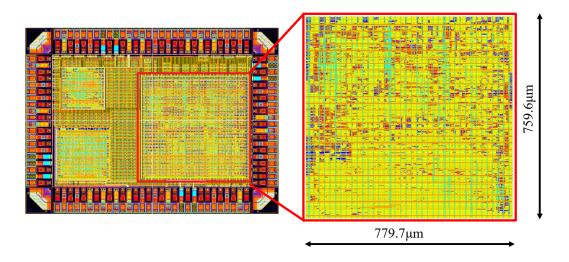

| 4.12 | The fabrication of HA-CORDIC (red square) and its layout on SOTB $65$                                   |    |

|      | nm process                                                                                              | 64 |

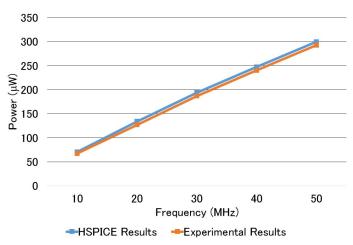

| 4.13 | The power comparison between HSPICE simulation and experimental results. $$                             | 65 |

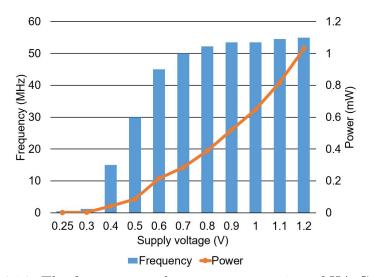

| 4.14 | The frequency and power consumption of HA-CORDIC                                                        | 65 |

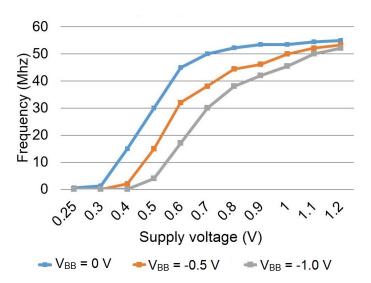

| 4.15 | The maximum frequency of HA-CORDIC in different $V_{DD}$ where $V_{BB}$ is                              |    |

|      | parameterized by SOTB process                                                                           | 65 |

| 4.16 | The leakage current of HA-CORDIC when changing $V_{BB}$                                                 | 66 |

| 4.17 | Leakage current of HA-CORDIC when changing the temperature                                              | 66 |

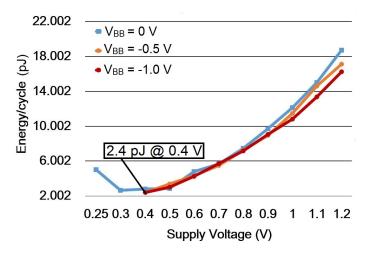

| 4.18 | The energy per cycle of HA-CORDIC in case of active mode                                                | 67 |

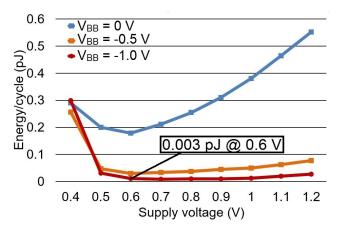

| 4.19 | The energy per cycle of HA-CORDIC in case of sleep mode                                                 | 68 |

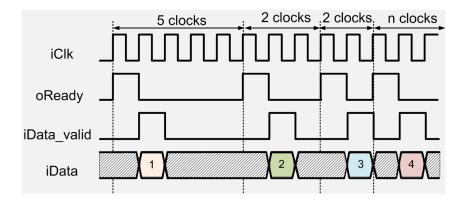

| 4.20 | The overview of HA-CORDIC operation                                                                     | 70 |

| 4.21 | The hardware architecture of PP-CORDIC                                                                  | 71 |

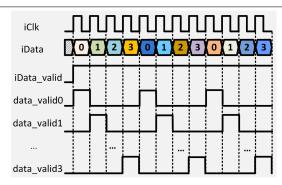

| 4.22 | The overview of PP-CORDIC operation.                                                                    | 72 |

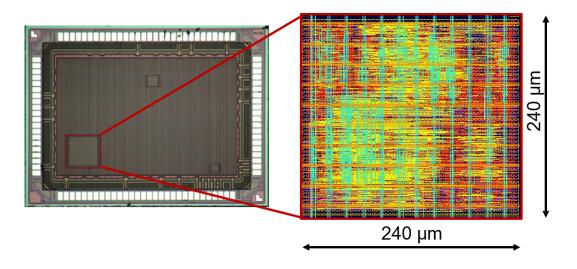

| 4.23 | The fabrication of PP-CORDIC $\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |    |

|      | CMOS process.                                                                                           | 74 |

| A.1  | The fabrication of ARD-SCFE CORDIC in 65 nm SOTB technology and                                         |    |

| 71.1 | its layout                                                                                              | 82 |

| A.2  | The fabrication of arithmetic processor on 180 nm CMOS technology and                                   | 02 |

| Π.Δ  | its layout                                                                                              | 82 |

|      |                                                                                                         |    |

| A.3  | The full chip layout of SDA module in 65 nm SOTB technology                                             | 83 |

| A.4  | The fabrication of HA-CORDIC on $65~\mathrm{nm}$ SOTB technology and its layout.                        | 83 |

| A 5  | The fabrication of PP-CORDIC on 180 nm CMOS technology and its layout                                   | 84 |

# List of Tables

| 2.1 | The final results of RM-CORDIC and VM-CORDIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | The values of $\theta_i$ , and $k_i$ when the number of predefined angles is 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15 |

| 3.1 | The comparison of ARD-SCFE implementation with other previous designs $% \left( 1\right) =\left( 1\right) \left( 1$               |    |

|     | in hardware complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 |

| 3.2 | Specification parameters of ARD-SCFE implementation on SOTB $65~\mathrm{nm}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30 |

| 3.3 | The comparison between the implementations of ARD-SCFE CORDIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | with other fixed-point CORDIC on 65 nm process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31 |

| 3.4 | The comparison between ARI-ARD-SCFE implementation with other fixed-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|     | point CORDIC designs on 180 nm CMOS process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36 |

| 3.5 | The summary of VM-CORDIC and RM-CORDIC in QR Decomposition. $% \left( 1\right) =\left( 1\right) \left( 1\right) $ | 39 |

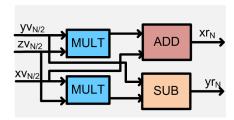

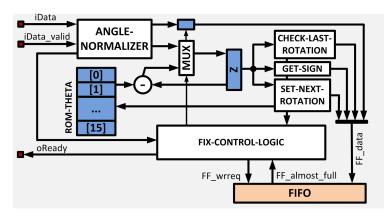

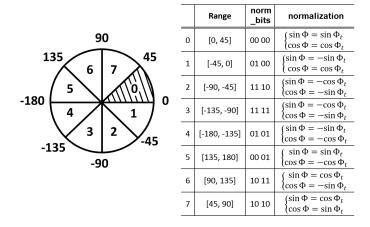

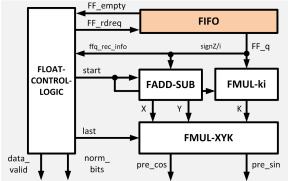

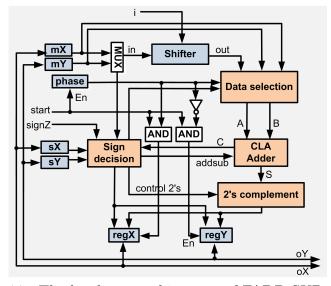

| 3.6 | The comparison between CQRD implementation with other previous de-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |