### Università degli Studi di Padova

Centro Ricerche Fusione (CRF)

### Universidade de Lisboa

Instituto Superior Técnico (IST)

### Università degli Studi di Napoli Federico II

JOINT RESEARCH DOCTORATE IN FUSION SCIENCE AND ENGINEERING Cycle XXIX

THESIS TITLE

# New hardware and software technologies for real-time control in nuclear fusion experiments

Coordinator: Prof. Paolo Bettini

Supervisor: prof. Leonardo Giudicotti Co-Supervisor: Ing. Gabriele Manduchi

Ph.D. student: Marco Gottardo

Padova, January 2018

JOINT Doctorate and NETWORK in Fusion Science and Engineering.

Network Partners:

- Instituto Superior Técnico (IST) Lisboa, Portugal

- Universitá degli studi di Padova, Italy

- Ludwig Maximilians University Munich, Germany In collaboration with:

- Consorzio RFX, Italy

- IPP Garching, Germany

## Abstract

The current machines for the study of nuclear fusion does not produce energy, and their output is substantially a large amount of data.

The accuracy of the data collected, and their density within narrow temporal samples, can determine the effectiveness of the real time control systems to install in future reactors.

We set ourselves the objective to design and test a high-speed and high-density data acquisition system based on the latest generation FPGA technologies.

in the thesis is used the latest products released by Xilinx to design a acquire stream system of signals from generic probes (specifically magnetic probes).

The Zynq 7000 family is nowadays state of the art of sistemy SoC that integrating a powerful and extensive FPGA section with an ARM multicore.

Of fundamental importance will be the drastic reduction of signal cables between the sensory apparatus and acquisition systems with the dual objective of eliminating the noise induced and drastically lower installation costs.

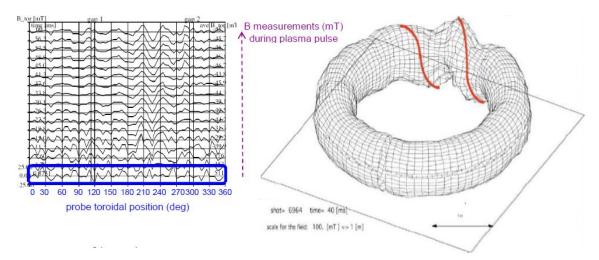

Magnetic field configuration in RFX is characterised by fast variations of all the three field components during the pulse, with relevant non axis-symmetry in toroidal direction. Typical spectra exhibit modes up to n=15 in toroidal direction and mainly m=0 and m=1 in poloidal direction.

As a consequence, probe signals have a large dynamic (more than 60 dB), and extended frequency spectrum (several tens of kHz).

Therefore, a large number of probes are required to correctly identify the complex spatial structure of the plasma column.

To reduce shielding effects, probes must be installed inside the stabilising shell.

The three components of field outside the vacuum vessel can be very different in amplitude.

At the same time, one can reach 0.8 T and another can be typically lower than some *m*T. Furthermore, they vary very quickly.

The probes to be installed have to guarantee an uncertainty less than 1 mT to correctly reconstruct the plasma behaviour.

These two specifications are particularly stringent and require an accurate calibration and a careful probe alignment to minimise the spurious effect of unwanted components.

A further design specification for the sensors is due to the maximum operation temperature of the vacuum vessel (200 °C).

The analogic acquires systems must exhibit high isolation, high speed and resolution, but above all a low noise level.

The noise must be below minimum margins throughout the frequency spectrum contained in the signals provided by magnetic probes.

The main topic of the thesis is to verify the suitability of the ATCA MIMO ISOL modules in the upper and lower part of the signal spectrum of bi-axis magnetic probes in order to be able to be integrated into the new FPGA acquisition and realtime control in RFX systems.

## Abstract

Le attuali machine per lo studio della fusione nucleare producono un grande ammontare di dati.

L'accuratezza di questi, la loro densità allinterno di stretti intervalli temporali può determinare la efficacia dei sistemi di controllo in tempo reale che dovranno essere installati nei futuri reattori.

Ci siamo posti l'obiettivo di sviluppare e valutare un sistema di acquisizione dati ad alta velocità basato sulla ultima generazione di FPGA.

In questa tesi abbiamo impiegato gli ultimi prodotti rilasciati da Xilinx per produrre un sistema in grado di acquisire segnali in streaming provenienti da sonde magnetiche generiche, installate in RFP e Tokamak.

La famiglia 7000 Zynq è oggi lo stato dell'arte dei sistemi SoC integrando una potente sezione FPGA con un sistema multicore ARM Cortex A9 di ultima generazione.

Di fondamentale importanza sarà la drastica riduzione dei cablaggi tra la macchina e l'apparato di concentrazione dei dati acquisiti con l'obiettivo di eliminare il rumore indotto e ridurre drasticamente i costi di assemblaggio.

La configurazione dei campi magnetici in RFX è caratterizzata da veloci variazioni nelle tre component di campo, nella durata dell'impulso, con rilevanti componenti non assial-simmetriche specialmente in direzione toroidale. Tipicamente lo spettro mostra dei modi superiori a n=15 in direzione toroidale pricipalmente con m=0 e m=1 in direzione poloidale.

Come conseguenza, i segnali alle sonde hanno un largo range dinamico, superiore a 60 dB e estendono lo spettro di frequenza oltre svariati decine di kHz.

Quindi, molte sonde sono richieste per identificare correttamente la complessa struttura spaziale della Colonna di plasma.

Per ridurre l'effetto schermo, le sonde devono essere installate dentro la shell stabilizzatrice. Le tre componenti del campo fuori dalla camera da vuoto possono essere molto differenti in ampiezza.

Allo stesso tempo, una può raggiungere 0.8 T e un'altra può essere dell'ordine dei mT. Inoltre queste risultano essere molto veloci.

Le sonde istallate devono garantire una incertezza minore di 1 mT per ricostruire correttamente il comportamento del plasma.

Queste due specifiche sono particolarmente stringenti e richiedono una accurate calibrazione e allineamento dei sensori per minimizzare gli effetti spuri e il rilevamento di componenti indesiderate.

Un ulteriore specifica di progetto per i sensori è dovuta alla massima temperatura della camera da vuoto che può raggiungere i 200 °C.

I sistemi di acquisizione analogica devono mostrare un alto isolamento, velocità e risoluzione; ma soprattutto la qualità deve essere maggiore di qanto richiesto dal livello di rumore.

Il rumore deve rimanere infatti sotto una soglia minima nello spettro di uscita.

L'obiettivo principare della tesi è di verificare l'applicabilità del modulo ATCA MIMO ISOL nella parte alta e bassa dello spettro del segnale delle sonde magnetiche biassiali in modo da metterlo in grado di essere integrato nella nuova acquisizione FPGA e controllo in tempo reale per RFXmod.

### Resumo

Os dispositivos atuais para o estudo da fusão nuclear não produzem energia e tem como saída uma quantidade substancialmente grande de dados.

A precisão dos dados coletados e sua densidade em amostras temporais estreitas podem determinar a eficácia dos sistemas de controle em tempo real para serem instalados em futuros reatores.

Nós estabelecemos o objetivo de projetar e testar um sistema de aquisição de dados de alta velocidade e alta densidade baseado nas tecnologias FPGA de última geração.

Na tese são usados os produtos mais recentes lançados pela Xilinx para projetar um sistema de aquisição de fluxo para sondas genéricas (especificamente sondas magnéticas).

A família Zynq 7000 é hoje em dia o mais avançado sistema SoC que integra uma poderosa e extensa seção FPGA com um ARM "mullticore".

De fundamental importância será a redução drástica dos cabos de sinal entre o aparelho sensorial e os sistemas de aquisição com o duplo objetivo de eliminar o ruído induzido e reduzir drasticamente os custos.

A configuração do campo magnético no RFX é caracterizada por variações rápidas de todas as três componentes do campo durante o pulso, com relevante não simetria na direção toroidal. Os espectros típicos exibem modos até n = 15 na direção toroidal e principalmente m = 0 e m = 1 na direção poloidal.

Como consequência, os sinais da sonda possuem alta dinâmica (mais de 60 dB) e um espectro de freqüência estendido (várias dezenas de kHz).

Portanto, um grande número de sondas é necessário para identificar corretamente a estrutura espacial complexa da coluna de plasma.

Para reduzir os efeitos de blindagem, as sondas devem ser instaladas dentro do escudo estabilizador.

As três componentes do campo fora do vaso de vácuo podem ser muito diferentes em amplitude.

Ao mesmo tempo, pode-se alcançar 0,8 T e outro pode ser tipicamente inferior a alguns mT. Além disso, eles variam muito rapidamente.

As sondas a serem instaladas devem garantir uma incerteza inferior a 1 mT para reconstruir corretamente o comportamento do plasma.

Essas duas especificações são particularmente rigorosas e exigem uma calibração precisa e um alinhamento cuidadoso da sonda para minimizar efeitos espúrios de componentes indesejados.

Outra especificação de projeto para os sensores é devido à temperatura de operação máxima do vaso de vácuo (200 ° C).

Os sistemas de aquisição analógicos devem exibir alto isolamento, alta velocidade e resolução, mas acima de tudo um baixo nível de ruído. O ruído deve estar abaixo das margens mínimas em todo o espectro de frequência contido nos sinais fornecidos pelas sondas magnéticas.

## Index

| Abstract        | i                                                                                  | ii         |

|-----------------|------------------------------------------------------------------------------------|------------|

| Resumo.         | i                                                                                  | v          |

| THESI           | S TITLE                                                                            | . i        |

| Chapter         | 1. Introduction                                                                    | 1          |

| 1. 1.           | Thesis introduction                                                                | 1          |

| 1. 2.           | Fusion experiment diagnostics                                                      | 4          |

| 1. 3.           | A Simplified customizable DAQ                                                      | 5          |

| 1.4.            | The new proposed approach                                                          | 8          |

| 1. 5.           | Daq system for array of 5 pin balanced electrostatic probe (or fast magnetics<br>9 | 3)         |

| 1. 6.<br>CCD, a | Daq system for general purpose magnetics, soft X-Ray detectors, PMT,<br>arrays1    | 1          |

| Chapter         | 2. Definition and roles of magnetic diagnostic in a fusion machine1                | 3          |

| Chapter         | 3. Probe and transmission line specification2                                      |            |

| 3.1             | Magnetic probe circuit model2                                                      | !1         |

| 3. 1.           | Probe electrical modelling2                                                        | 27         |

| 3. 2.           | Transmission line circuit model2                                                   |            |

| Chapter         | 4. Analog frontend specification                                                   |            |

| 4. 1.           | Analog frontend to Zynq, the ATCA MIMO ISOL module                                 |            |

| 4. 2.           | Frontend Low Pass Filter                                                           | 5          |

| 4. 3.           | Frontend to FPGA connector                                                         | 7          |

| 4.4.            | Opto-isolated differential input stage                                             |            |

| 4. 5.           | 18 bit ADC SAR integrated circuit4                                                 |            |

| 4. 6.           | The AD7641 features4                                                               |            |

| 4. 7.           | AD7641 microprocessor interface capability4                                        |            |

| 4. 8.           | AD7641 SPI interface capability4                                                   |            |

| Chapter         |                                                                                    |            |

| 5. 1.           | Power supply stage, DC/DC converter4                                               |            |

| Chapter         | 5                                                                                  |            |

| 6. 1.           | Interfacing the analog ATCA MIMO ISOL module to FPGA5                              | <b>i</b> 1 |

| 6. 2.<br>FPGA   |                                                                                    |            |

| Chapter         |                                                                                    |            |

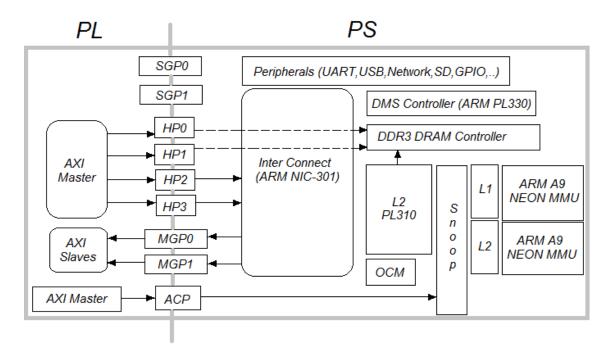

| Chapter         | 8. Zynq Architectures6                                                             | 5          |

| 8. 1.           | AXI Interconnect Block6                                                            | ;9         |

| 8. 2.     | Bloo           | ck schematic and Internal architecture of Zynq 7000           | 70       |

|-----------|----------------|---------------------------------------------------------------|----------|

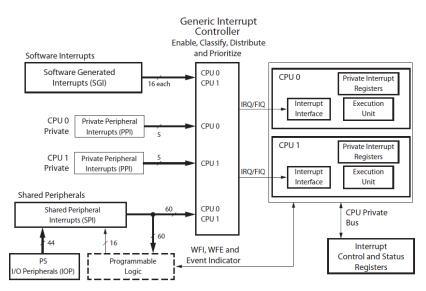

| 8. 3.     | GIC            | c, Generic Interrupt Controller                               | 71       |

| 8. 4.     | Priv           | rate, shared and software interrupts                          | 73       |

| 8. 5.     | GIC            | functionality                                                 | 73       |

| 8. 6.     | Inte           | rrupts, priorities and handling                               | 75       |

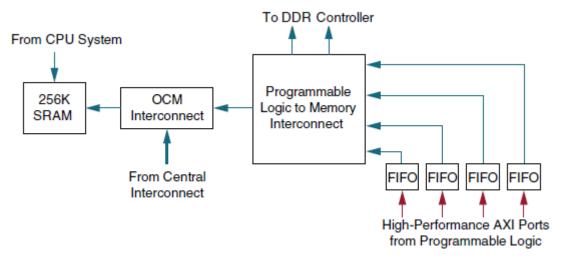

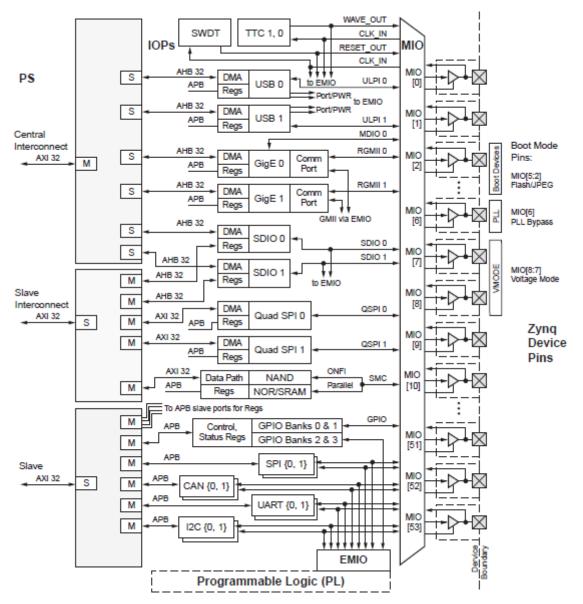

| 8. 7.     | The            | e central interconnect module                                 | 77       |

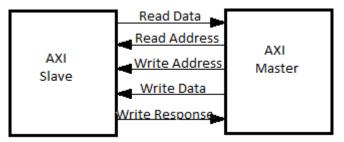

| Chapte    | er 9.          | The AXI interface                                             | 79       |

| 9. 1.     | The            | AMBA protocol                                                 | 79       |

| 9. 2.     | The            | AXI interface                                                 |          |

| Chapte    | er 10.         | AXI- Stream FIFO                                              |          |

| 10. 1     | . AXI          | Stream FIFO first experimental test                           | 85       |

| Chapte    | er 11.         | ADC DMA interface                                             |          |

| 11. 1     | . The          | Zynq7000 DMA overview                                         |          |

| 11. 2     | . The          | Xilinx DMA logic                                              |          |

| 11.3      | . AXI          | -DMA and streaming data acquire, block diagram                |          |

| 11. 4     | . Stru         | cture of the AXI dataflow                                     | 94       |

| Chapte    | er 12.         | Final tests and results                                       |          |

| 12. 1     | . Pytł         | non                                                           | 97       |

| 12. 2     | . Acq          | uisitions test                                                |          |

| 12. 3     | . Free         | quency response                                               |          |

| 12. 4     | . The          | noise spectral density                                        |          |

| 12. 5     | . Mea          | asurement of intrinsic noise                                  |          |

| 12.6      | . Sigr         | nal numerical integration                                     |          |

| 12. 7     | . Tes          | t without DC/DC converter                                     |          |

| 12.8      | . Low          | <i>i</i> frequency noise noise analysis                       |          |

| 12.9      | ). Noi:<br>125 | se integration and expected integrated signals on modified AD | C module |

| 12. 1     | 0. Mag         | gnetic probe measurement test circuit                         |          |

| Chapte    | er 13.         | Conclusion                                                    |          |

| <b>A.</b> | Appen          | dix: Source codes                                             |          |

| <b>B.</b> | Appen          | dix: Software tools for PL section                            |          |

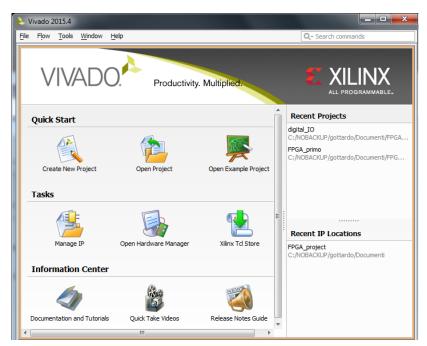

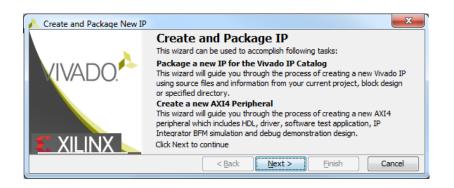

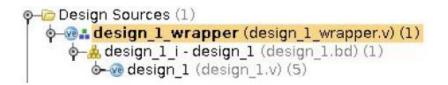

| The       | design         | on Vivado                                                     |          |

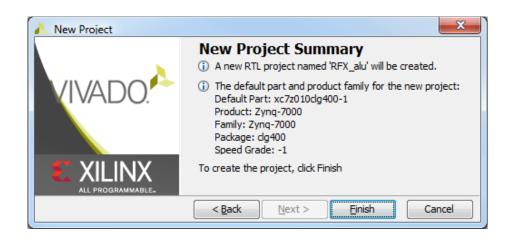

| Crea      | te a ne        | ew Verilog project Step by Step                               |          |

| Ste       | əp 1 - I       | Hardware definition                                           |          |

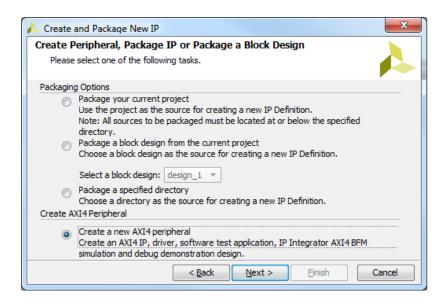

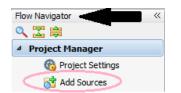

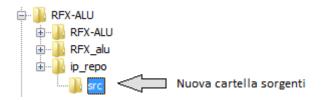

| Ste       | әр 2 –         | Adding the source to be packaged in IP block design           |          |

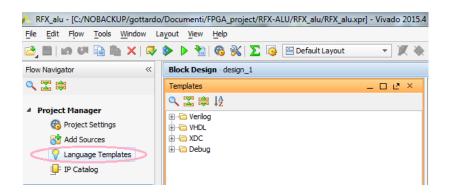

| Ste       | ер 3 –         | Creating a new Verilog IP                                     |          |

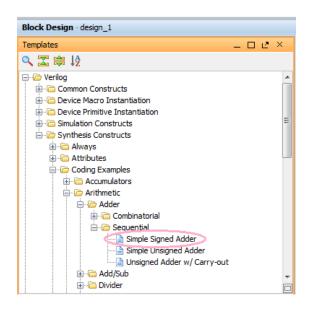

|    | Step 4 – Editing IP and sources add                      | 169 |

|----|----------------------------------------------------------|-----|

|    | Step 5 – Module insertion using the template             | 175 |

|    | Step 6 – AXI wrapper                                     | 178 |

|    | Step 7 – Add a new custom IP to the design               | 180 |

|    | Step 8 – TOP module creation and start synthesis         | 181 |

|    | Step 9 – Manually creating a test application            | 182 |

|    | Step 10 – Deploy on RedPitaya and test program execution | 184 |

| C. | Appendix: FPGA to ARM interfacing                        | 187 |

| Т  | he AXI write tool                                        | 187 |

| Re | ferences                                                 | 189 |

| Ac | knowledgements                                           | 191 |

# Index of figures

| Figure 1-1A Typical approach for a diagnostic system                              | 6    |

|-----------------------------------------------------------------------------------|------|

| Figure 1-2 Current situation, typical diagnostic wiring                           | 7    |

| Figure 1-3 The new proposed approach with simplified wiring.                      | 8    |

| Figure 1-4: Triple Langmuir probe configuration                                   | 9    |

| Figure 1-5: 5 pin balanced Langmuir probe configuration                           | 10   |

| Figure 2-1 inductive sensors in a toroidal machine                                | 13   |

| Figure 2-2 RFX-Mod external magnetic probes layout.                               | 14   |

| Figure 2-3 Overview of magnetic probes on RFX-Mod                                 | 15   |

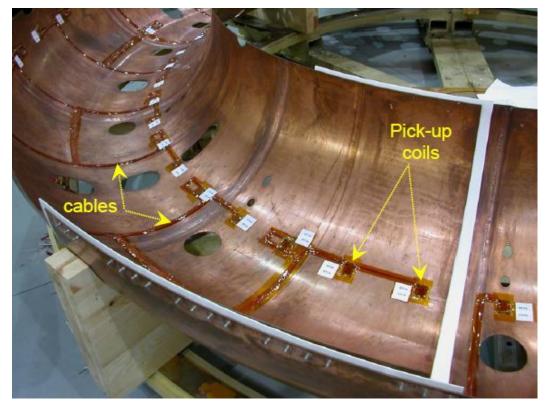

| Figure 2-4 Integrated System of Internal Sensors (ISIS) for RFX-Mod               | 15   |

| Figure 2-5 View of RFX-mod first wall with probes layout                          | 16   |

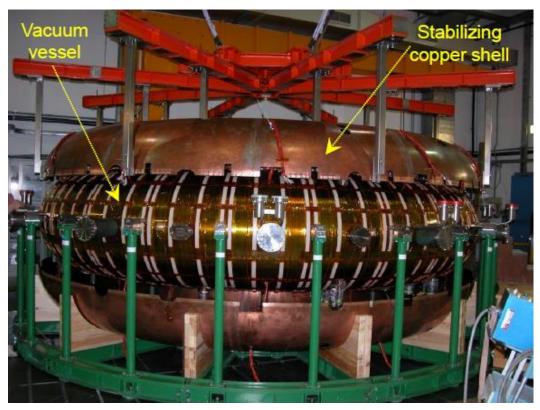

| Figure 2-6 mm copper shell. Exploded view                                         | 17   |

| Figure 2-7 Biaxial magnetic probes RFX installation                               | 17   |

| Figure 2-8 RFX-Mod copper shell                                                   | 18   |

| Figure 2-9 Magnetic probes connectors on RFX vacuum chamber                       | 18   |

| Figure 2-10 Biaxial probe LEMO connectors                                         | 19   |

| Figure 3-1 Magnetic probe model typical                                           | 22   |

| Figure 3-2 Two axes magnetic sensor model                                         | 22   |

| Figure 3-3 Derivative of the frequency response two-axis probe                    | 23   |

| Figure 3-4 Size and appearance of the magnetic probe                              | 23   |

| Figure 3-5 Torlon Vs Peek core probe capacitance and inductance                   | 24   |

| Figure 3-6 Bi-axial magnetic pick-up coils                                        | 25   |

| Figure 3-7 Plasma position from magnetic measurements                             | 25   |

| Figure 3-8 RFX-mod waveform of magntic field from pick-up array                   | 26   |

| Figure 3-9 Differential acquisition of magnetic probes                            | 26   |

| Figure 3-10 Basic model of a magnetic probe                                       | 27   |

| Figure 3-11 Two axes magnetic sensor model connect to transmission line           | 28   |

| Figure 3-12 Two axes probe and transmission line frequency response               | 29   |

| Figure 3-13 Capacive model of the line                                            | 29   |

| Figure 3-14 Capacive transmission line frequency response                         | 30   |

| Figure 4-1 ATCA MIMO ISOL module, isolated differential analog fronted board      | 31   |

| Figure 4-2 Block schematic of the ADC module                                      | 32   |

| Figure 4-3: Flow chart of data streaming acquisition to be implemented on the FPG | A 34 |

| Figure 4-4 Low pass filter schematic                                              | 35   |

| Figure 4-5 Molex 87833, probe connector                                           | 35   |

| Figure 4-6 Low pass filter PSim.                                                        | . 36 |

|-----------------------------------------------------------------------------------------|------|

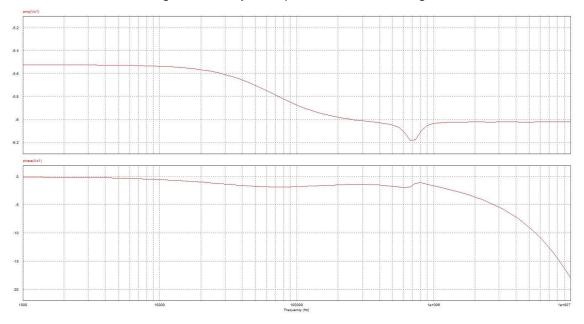

| Figure 4-7 Low pass filter Bode diagrams                                                | . 36 |

| Figure 4-8 Analog frontend to FPGA connector.                                           | . 37 |

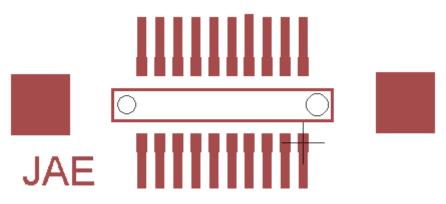

| Figure 4-9 JAE connector footprint                                                      | . 38 |

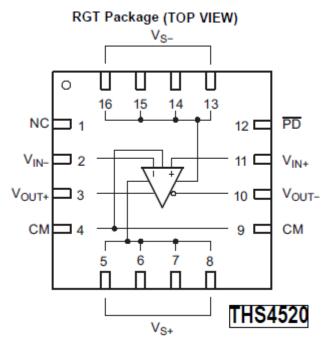

| Figure 4-10 Differential operational amplifier THS4520                                  | . 38 |

| Figure 4-11 THS4520 internal configuration                                              | . 39 |

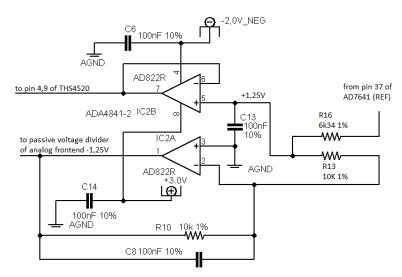

| Figure 4-12 Acitive voltage reference generator                                         | . 39 |

| Figure 4-13 Differential amp. op. schematic on insulated frontend                       | . 40 |

| Figure 4-14 Generic voltage noise spectral density                                      | . 41 |

| Figure 4-15 The AD7641 functional block diagram                                         | . 43 |

| Figure 4-16 input capacitors rail                                                       | . 44 |

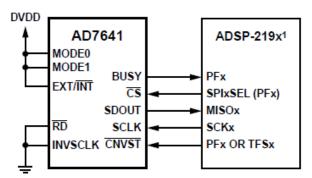

| Figure 4-17 The AD7641 SPI signals and wiring                                           | . 46 |

| Figure 4-18 The AD7641 typical application                                              | . 47 |

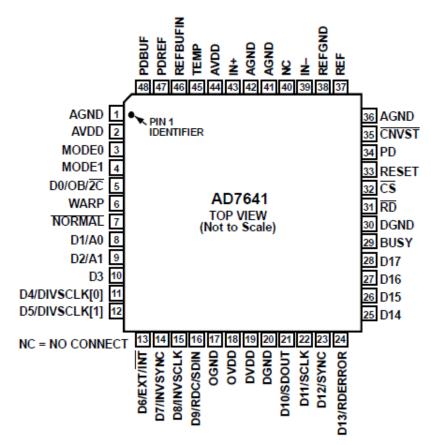

| Figure 4-19 The AD7641 pinout                                                           | . 48 |

| Figure 5-1 DC/DC converter internal block diagram                                       | . 49 |

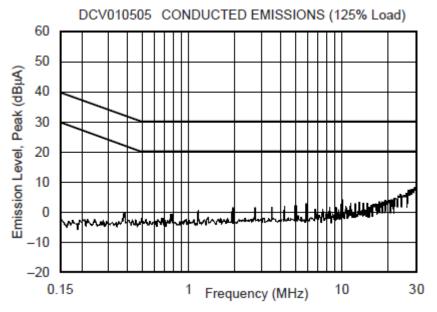

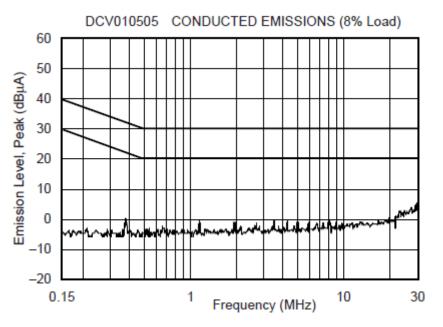

| Figure 5-2 DC/DC converter emission at 125% load                                        | . 50 |

| Figure 5-3 DC/DC converter emission at 8% load                                          | . 50 |

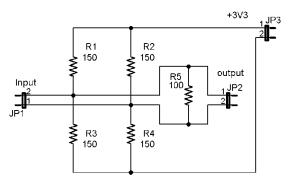

| Figure 6-1 Resistive net level adapter                                                  | . 51 |

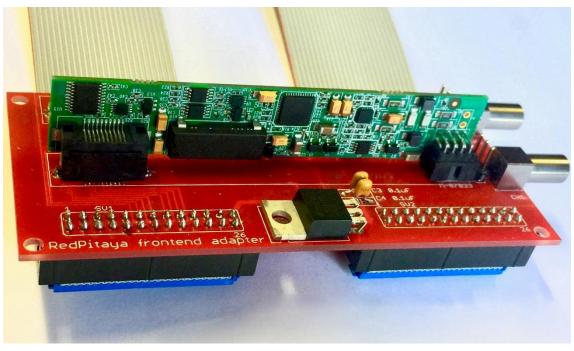

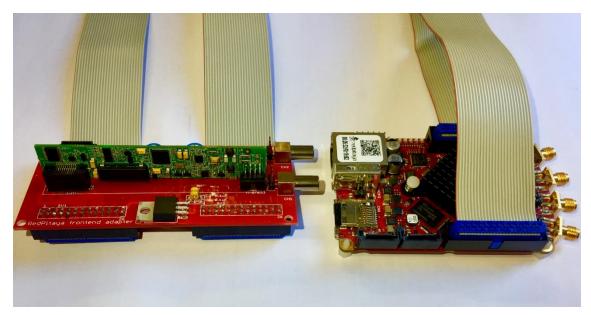

| Figure 6-2 Frontend to Pitaya adapter with channel 1 mounted.                           | . 52 |

| Figure 6-3 Fronted to Pitaya overview.                                                  | . 53 |

| Figure 6-4 ATCA- MIMO-ISOL to RedPitaya interface, in use version                       | . 53 |

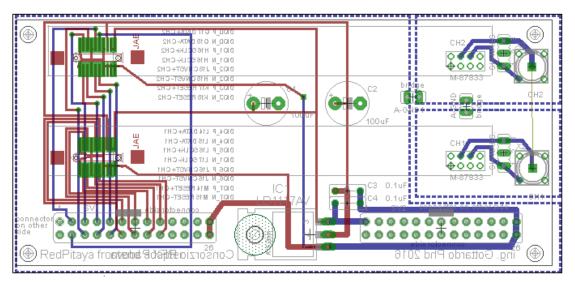

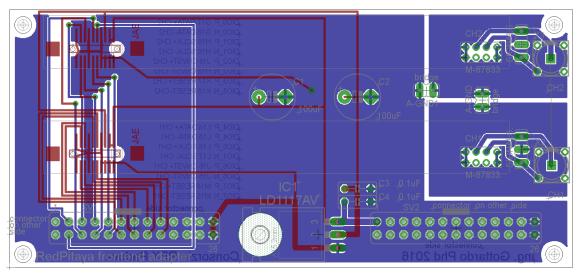

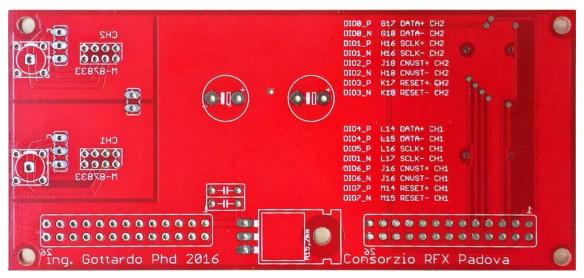

| Figure 6-5 Analog frontend to pitaya interface, Dual layer PCB                          | . 54 |

| Figure 6-6 PCB Bottom side, with signals table on silkscreen                            | . 54 |

| Figure 6-7 carry board layout final revision                                            | . 55 |

| Figure 6-8 ATCA- MIMO-ISOL to RedPitaya interface, ptototype                            | . 56 |

| Figure 6-9 Carry board connectors                                                       | . 57 |

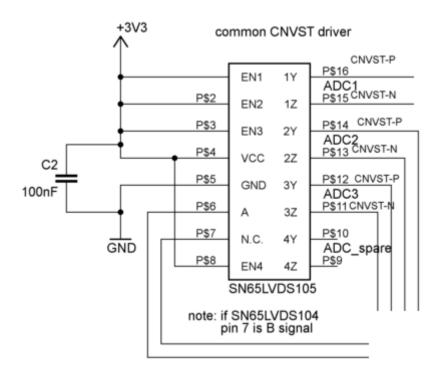

| Figure 6-10 SNLVDS105 internal schematic                                                | . 58 |

| Figure 6-11 SNLVDS105 LVDS repeaters pinout                                             | . 58 |

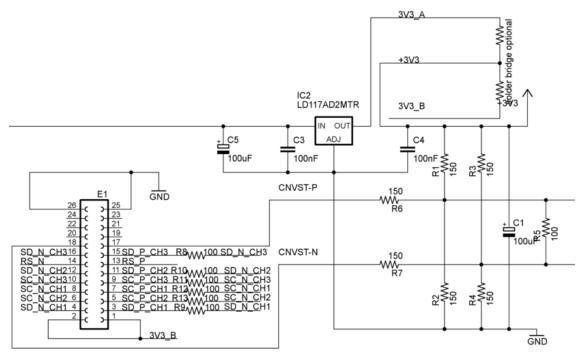

| Figure 6-12 Regolated 3v3 supply and resitors interface                                 | . 59 |

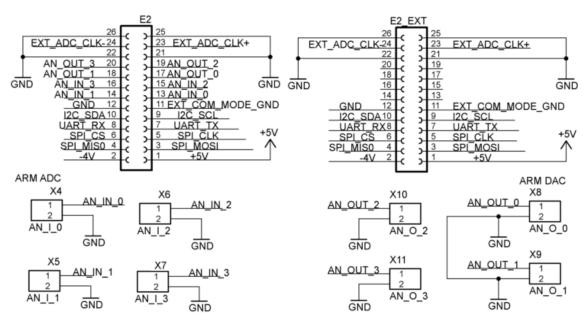

| Figure 6-13 Carry board BNC of on board ARM ADC                                         | . 59 |

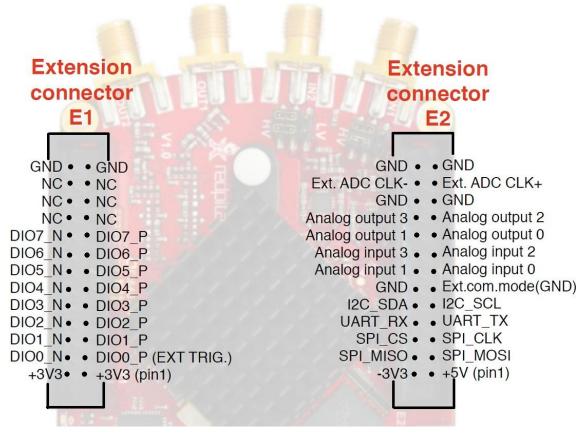

| Figure 6-14 RedPitaya extension connectors                                              | . 60 |

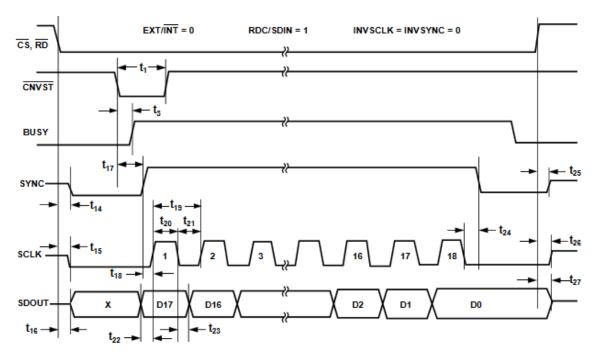

| Figure 7-1 Master Serial Data Timing for Reading (Read Previous Conversion Dur Convert) |      |

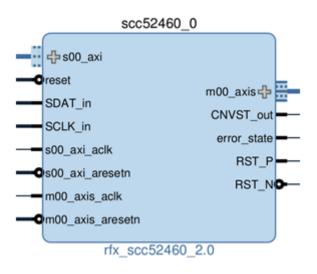

| Figure 7-2 IP implementation of scc52460 module.                                        | . 63 |

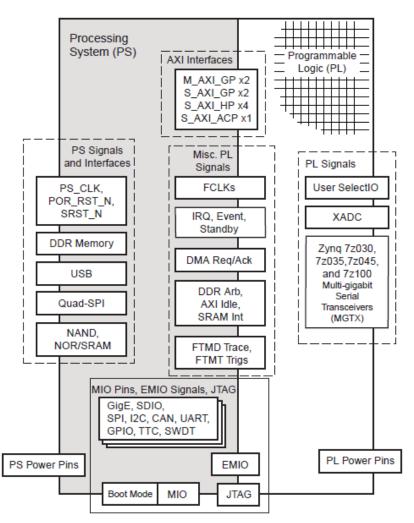

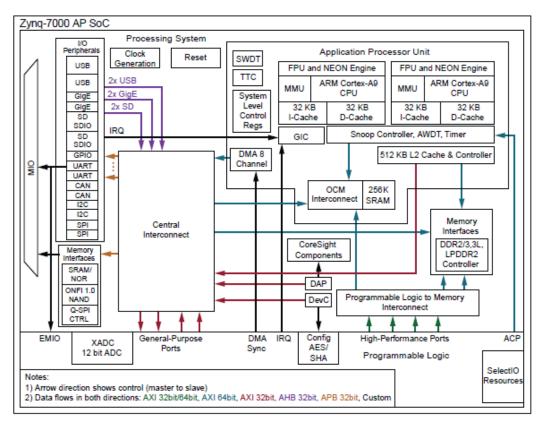

| Figure 8-1 Zynq® Architectures, simplify block schematic.                               | . 65 |

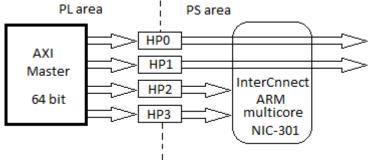

| Figure 8-2 PL interface to PS memory subsystem                                          | . 67 |

| Figure 8-3 Zynq® 7000 internal architecture                                                                    | 70         |

|----------------------------------------------------------------------------------------------------------------|------------|

| Figure 8-4 Generic Interrupt Controller, block schematic                                                       | 71         |

| Figure 8-5 I/O Peripherals System Diagram and central interconnect                                             | 77         |

| Figure 9-1 The five signals evolved in the AXI memory mapped protocol                                          | 80         |

| Figure 9-2 AXI data exchange                                                                                   | 81         |

| Figure 9-3 AXI data transfer FPGA to ARM                                                                       | 81         |

| Figure 9-4 PL to PS and vice versa internal interface                                                          | 83         |

| Figure 9-5 Zynq-7000 AP SoC internal block diagram                                                             | 84         |

| Figure 9-6 Axi Interconnect block represented in HDL                                                           | 84         |

| Figure 10-1 AXI4-Stream FIFO Block Diagram                                                                     | 85         |

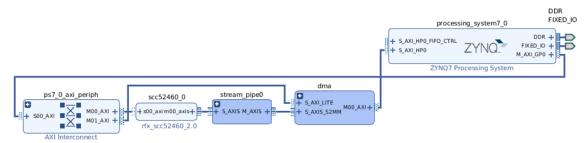

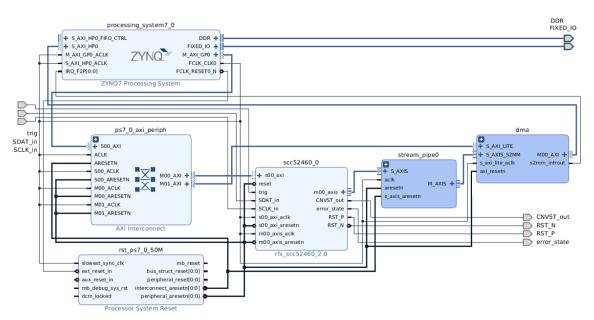

| Figure 10-2 Module design connection                                                                           | 86         |

| Figure 10-3 AXI Stream Complete Vivado design                                                                  | 87         |

| Figure 10-4 scc52460 Module internal design                                                                    | 88         |

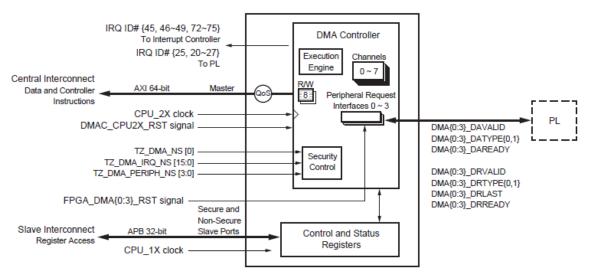

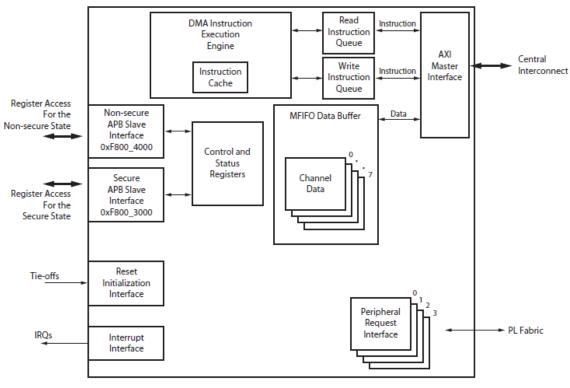

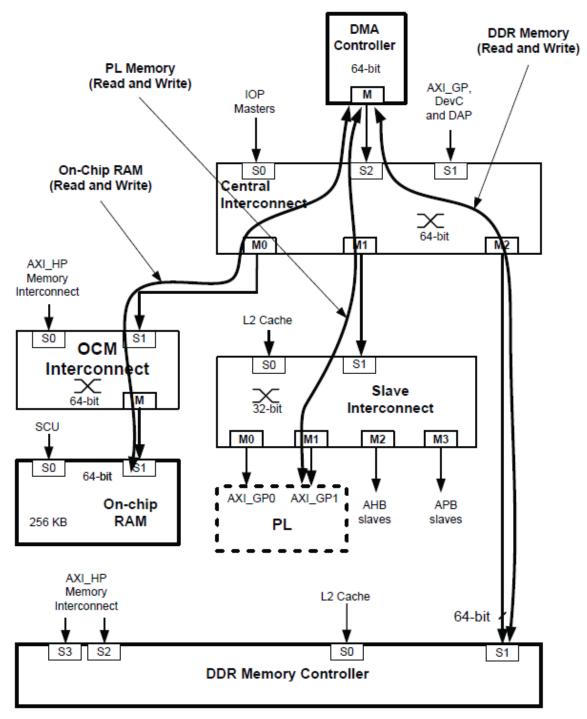

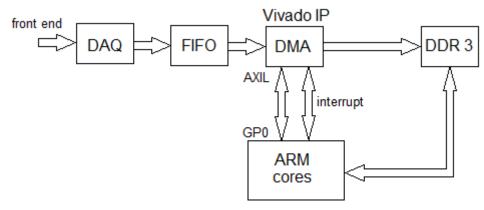

| Figure 11-1 DMA controller interconnection.                                                                    | 91         |

| Figure 11-2 DMA controller block diagram.                                                                      | 91         |

| Figure 11-3 DMA access diagram                                                                                 | 93         |

| Figure 11-4 block diagram of the interfacing principle with the hardware module                                | 94         |

| Figure 11-5 AXI-DMA logic chain and HDL implementation                                                         | 95         |

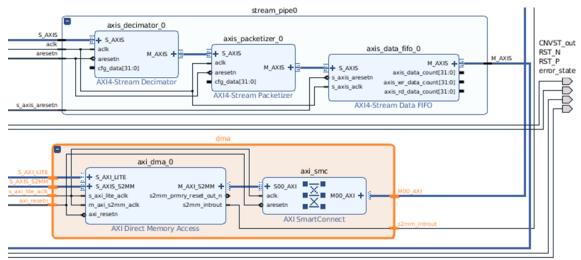

| Figure 11-6 ATCA MIMO ISOL MODULE implemented on RFX_scc52460 logic IP AXI interconnect to stream pipe and DMA | with<br>95 |

| Figure 11-7 AXI-DMA and stream_pipe IP internal HDL Vivado rappresentation                                     | 96         |

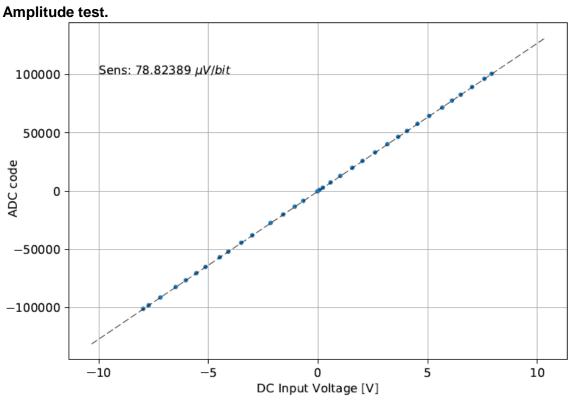

| Figure 12-1 ADC module input voltage sensitivity                                                               | . 101      |

| Figure 12-2 functions generator HP33120A                                                                       | . 102      |

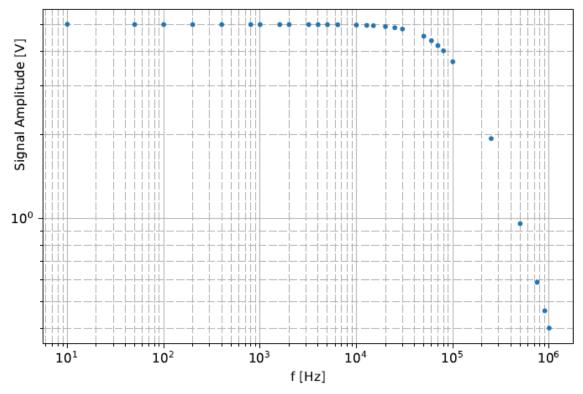

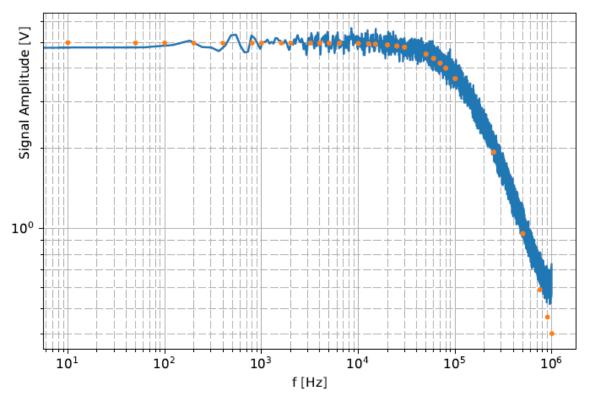

| Figure 12-3 Frequency response of ADC module with sinusoidal input                                             | . 103      |

| Figure 12-4 frequency response of ADC module with white noise input                                            | . 104      |

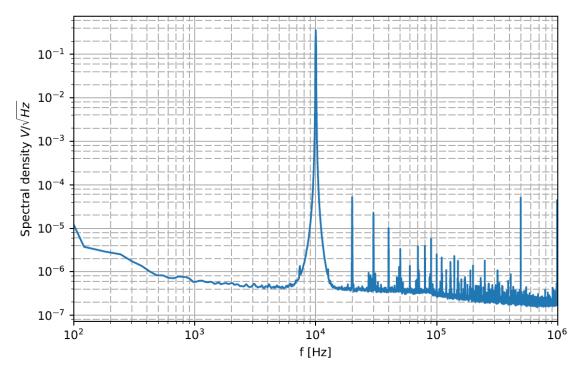

| Figure 12-5 Harmonic spectrum of ADC module at 10kHz sinusoidal input                                          | . 106      |

| Figure 12-6 General characteristic of Op. Amp voltage noise                                                    | . 108      |

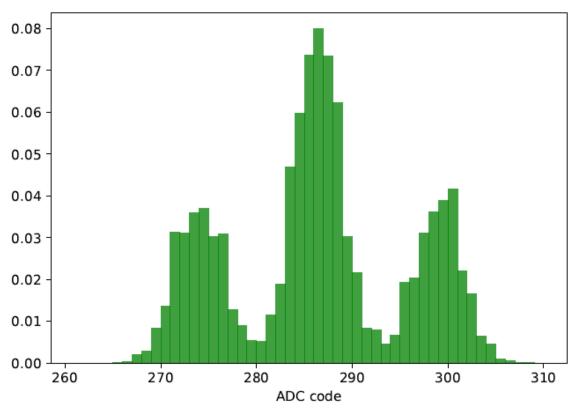

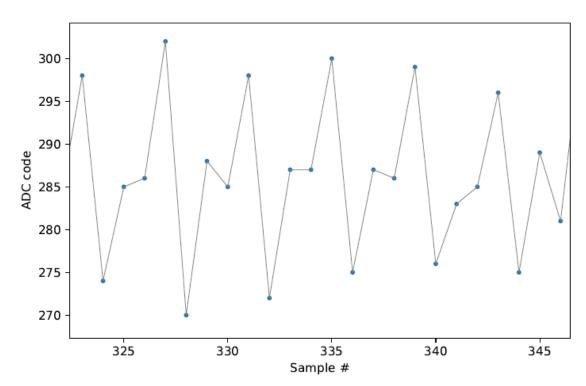

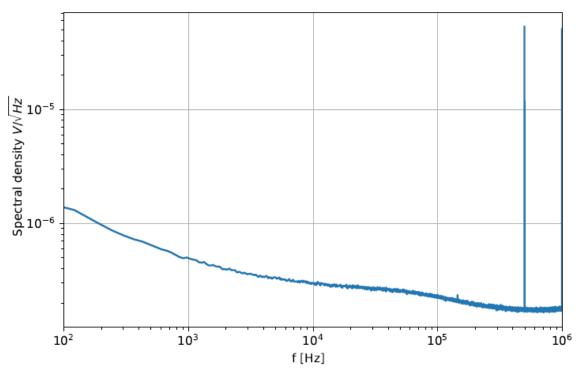

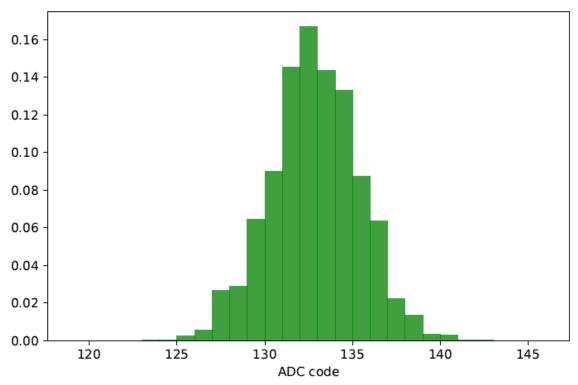

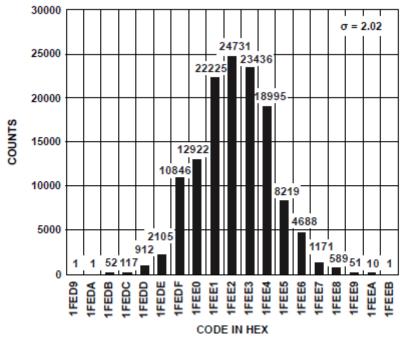

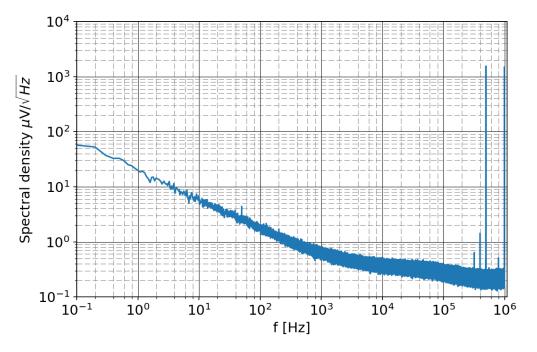

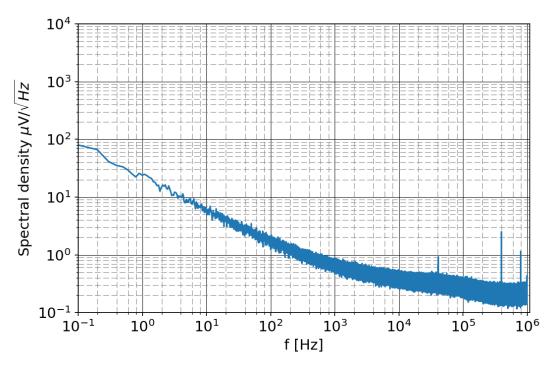

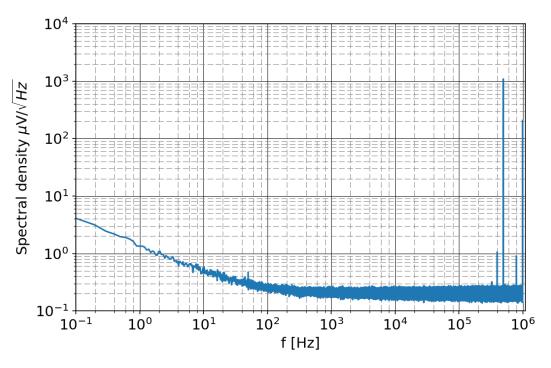

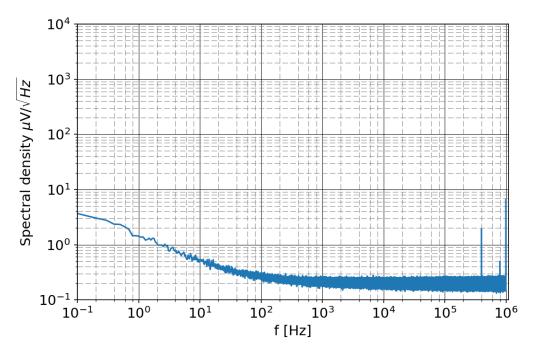

| Figure 12-7 Noise sampling of ADC module with 50 Ohm terminated input                                          | . 110      |

| Figure 12-8 Sampled Noise histogram of ADC module with 50 Ohm terminated                                       | •          |

| Figure 12-9 Noise sampling of ADC module with 50 Ohm terminated input (Zoom).                                  | . 111      |

| Figure 12-10 internal divider integrated on DC-DC converter                                                    | . 112      |

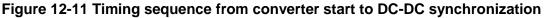

| Figure 12-11 Timing sequence from converter start to DC-DC synchronization                                     | . 112      |

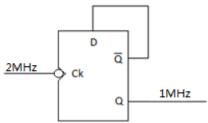

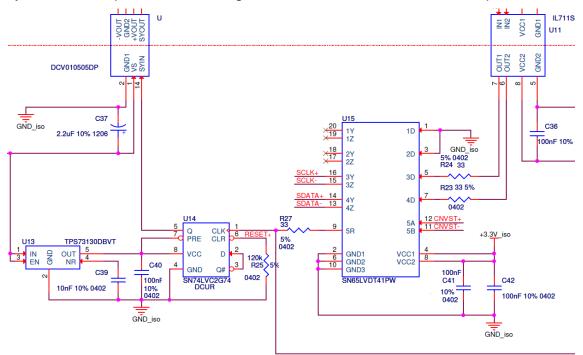

| Figure 12-12 Flip Flop divider                                                                                 | . 113      |

| Figure 12-13 The SN74LVC2G74 Flip flop in the diagram context                                                  | . 113      |

| Figure 12-14 Sampled Noise spectrum of ADC module                                                              | . 114      |

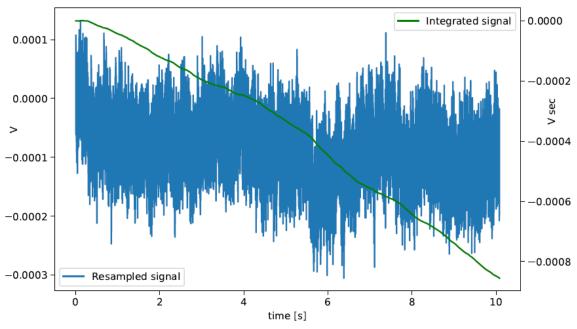

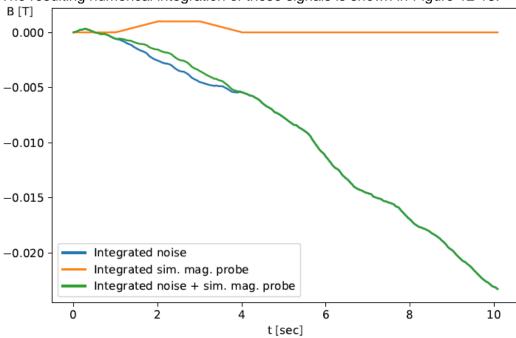

| Figure 12-15 Resampled input and time integrated signal115                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

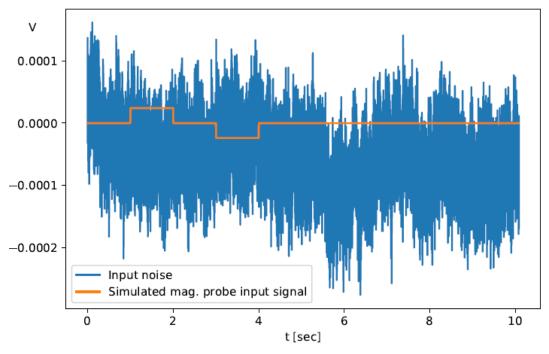

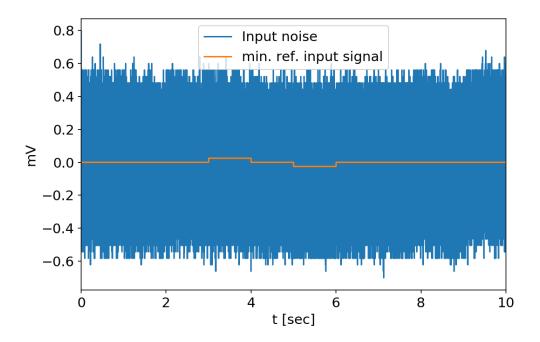

| Figure 12-16 Minum level reference magnetic signal                                                                                                                  |

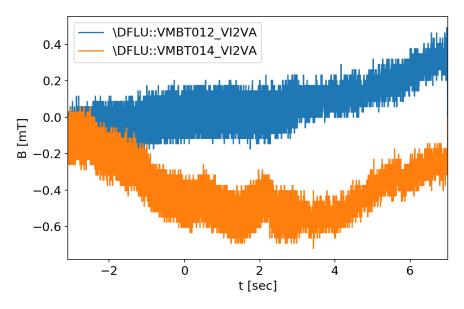

| Figure 12-17 Resampled noise compared with the simulated minum level reference magnetic signal                                                                      |

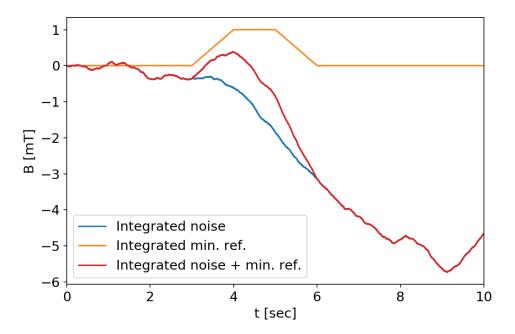

| Figure 12-18 Resampled integrated input compared with the simulated worst case. 117                                                                                 |

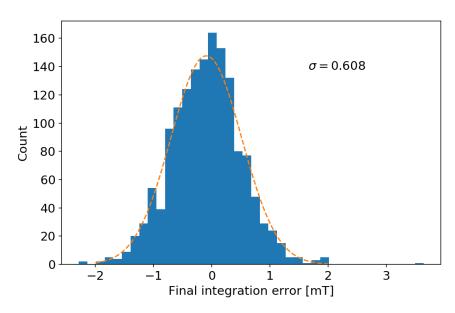

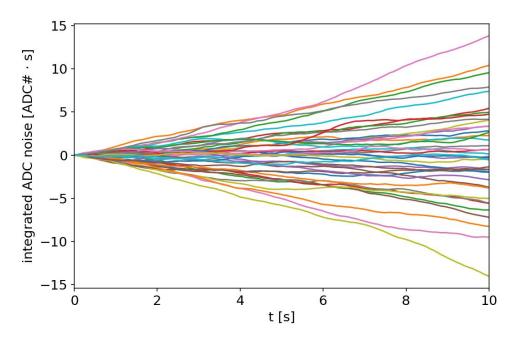

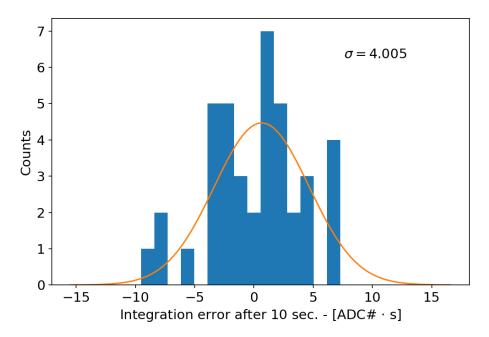

| Figure 12-19 Typical drift error of the RFX-mod analog signal integrator                                                                                            |

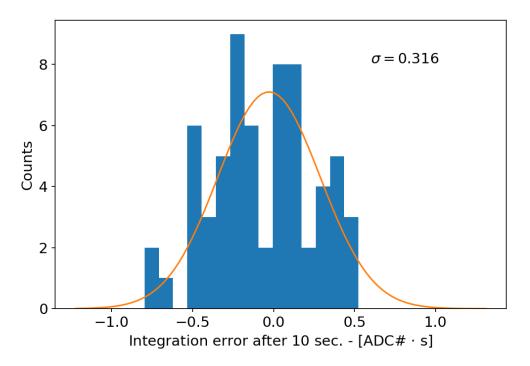

| Figure 12-20 Distribution of final integration error of the analog integrators of RFX-mod after 10 s                                                                |

| Figure 12-21 Noise sampling of ADC module with 50 Ohm terminated input, without DC-DC coneveter                                                                     |

| Figure 12-22 Sampled Noise histogram of ADC module with 50 Ohm terminated input without DC-DC converter                                                             |

| Figure 12-23 Histogram noise input from AD7641 datasheet                                                                                                            |

| Figure 12-24 Sampled Noise spectrum of ADC module without DC-DC converter 121                                                                                       |

| Figure 12-25 Resampled input direct and time integrated signal, without DC-DC converter                                                                             |

| Figure 12-26 Noise spectrum of the ADC module in its basic configuration, with 50Ω termination at input                                                             |

| Figure 12-27 Noise spectrum of the ADC module with linear power supply and $50\Omega$ terminator                                                                    |

| Figure 12-28 Noise spectrum of the ADC module with analog input section bypassed and DC/DC converter power supply                                                   |

| Figure 12-29 Noise spectrum of the ADC module with analog input section bypassed and linear power supply                                                            |

| Figure 12-30 Numerically integrated signals obtained from the ADC module in its original configuiration                                                             |

| Figure 12-31 Histogram of the final values after 10 s of numerical integration of the sample signals from original ADC module configuration                         |

| Figure 12-32 Low level reference signal and experimental noise of original ADC module configuration                                                                 |

| Figure 12-33 Numerical integration of low level reference signal and experimental noise of original ADC module configuration                                        |

| Figure 12-34 Numerically integrated signals obtained from the ADC module in with the analog input section bypassed                                                  |

| Figure 12-35 Histogram of the final values after 10 s of numerical integration of the sample signals from the ADC module with the analog input section bypassed 128 |

| Figure 12-36 Low level reference signal and experimental noise of the ADC module with the analog input section bypassed                                             |

| Figure 12-37 Numerical integration of low level reference signal and experimental noise of the ADC module with the analog input section bypassed                    |

| Figure 12-38 Histogram of the final values after 10 s of numerical integration c sample signals from the ADC module with the analog input section bypassed and I power supply. | inear |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

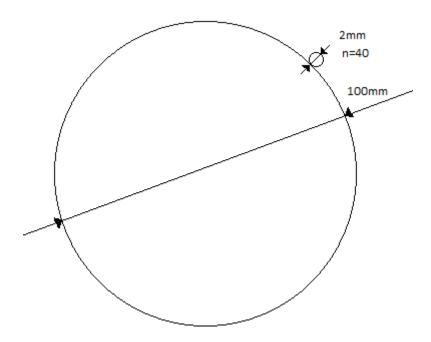

| Figure 12-39 Test coil sketch                                                                                                                                                  | . 130 |

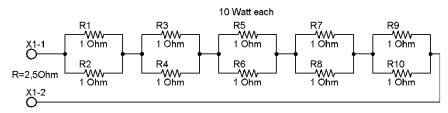

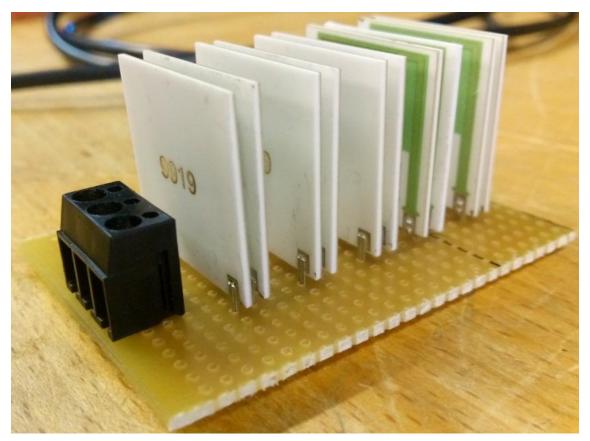

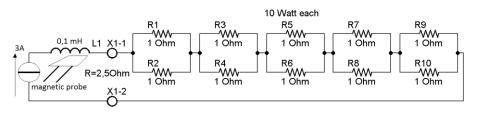

| Figure 12-40 Resistive load circuit                                                                                                                                            | . 131 |

| Figure 12-41: 2.5 Ω resistive load                                                                                                                                             | . 131 |

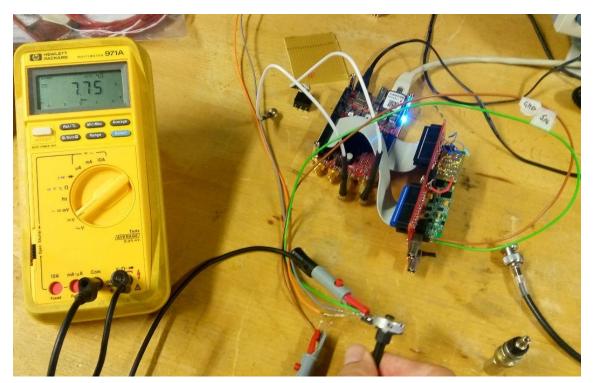

| Figure 12-42 Resistive load connect to test coil and probe                                                                                                                     | . 131 |

| Figure 12-43 Voltage signal by a potentiometer                                                                                                                                 | . 132 |

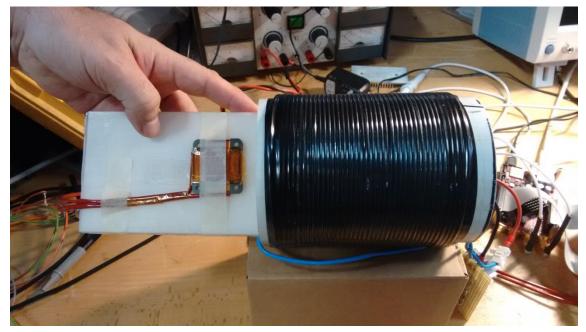

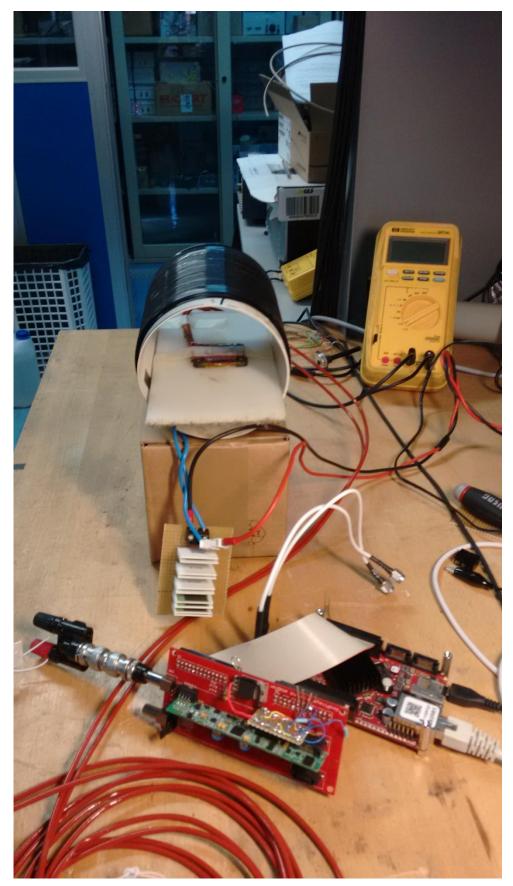

| Figure 12-44 Test coil and magnetic probe                                                                                                                                      | . 132 |

| Figure 12-45 Acquisition system connected to coil and probe                                                                                                                    | . 133 |

| Figure 12-46 Direct acquired signal from the probe directly connected to the ADC and its time integrated signal                                                                |       |

| Figure B-1 Xilinx Vivado setup package                                                                                                                                         | . 157 |

| Figure B-2 Vivado Welcome Page.                                                                                                                                                | . 158 |

## Index of tables

| Table 3-1 Magne      | tic probe technical characteristics.           | 21  |

|----------------------|------------------------------------------------|-----|

| Table 4-1 Different  | ial analog signals                             |     |

| Table 7-1 Serial (   | Clock Timing in Master Read After Convert Mode | 61  |

| Table 8-1 Zynq700    | ) PL Interrupt Signals                         | 75  |

| Table 11-1 DMA R     | eq/Ack signals on PL section                   |     |

| Table 12-1 List of A | DC module input voltage sensitivity test files | 100 |

| Table 12-2 List of A | DC module frequency response test files        | 102 |

### Chapter 1. Introduction

#### 1.1. Thesis introduction

The aim of the thesis is to produce a new software and hardware system for data acquisition, mainly from magnetic-type probes, for general use, simpler and more economic, for research groups involved in various experimental plasma magnetic confinement machines around the world.

The goal is to get a system that maintains the speed and isolation features of the actual one but greatly reduces the size and expense, and allows to approach the data acquisition system to diagnostic electronic as much as possible to the machine, reducing or nearly eliminating any long transmission line that may act as source of disturbance.

The research application and the experimental section took place at the laboratories of the CNR of Padua where the RFP machine named RFX operates.

Magnetic field configuration in RFX-mod is characterized by fast variations of all the three field components during the pulse, with relevant non axis-symmetry in toroidal direction.

Typical spectra exhibit modes up to n=15 in toroidal direction and mainly m=0 and m=1 in poloidal direction.

As a consequence, probe signals have a large dynamic (more than 60 dB), and extended frequency spectrum (several tens of kHz).

Magnetic diagnostics are among the most sensitive subsystems on RFX-mod. This is both due to the nature of the signal itself (noisy and easily susceptible) and to the number of signals, which is close to a thousand of various kinds. These probes are installed both in-vessel and ex-vessel. In the present thesis we will focus on the development of the system of 48x4 bi-axial pick-up coils, measuring poloidal and toroidal magnetic field, and of the 48 toridal windings. The study can be extended to magnetic probes of different nature.

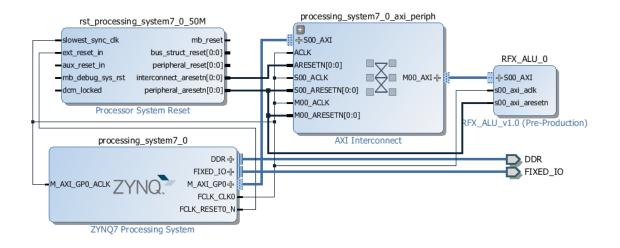

The thesis will propose a number of modifications to an original analog system based on ATCA-MIMO-ISOL components. Such a system is already in use for real-time control on JET, RFX-mod and is a candidate for ITER. The software interface will use MARTe, a framework of growing popularity within the fusion community and which represents a promising option for real-time control on ITER. At the present time the system comprises three racks. The first computer is equipped with twelve ATCA fabric channels (x1/x4 full-duplex PCIe), RTOS multicore processor (RTAI for Linux), PCIe/PCI legacy extra slots. The second machine has the multichannel system with 32 analog input channels (digitizer/transient recorder) which are removable one by one for replacement. The third computer contains the data transfer module, reaching up to 800 Mb/s over x4 PCIe to the host processor. In the present work we propose to keep the ATCA-MIMO-ISOL analog modules, which will be made autonomous by interfacing them with a SoC embedded system (commercially sourced). The new system will use the ATCA-MIMO-ISOL module as a frontend, to which circuit modifications are proposed, an interface with the SoC system and a new framework to manage timing and possible integration.

The new proposal consists in the development of a compact system, with a reduced number of analog channels directly installable on the hosting Linux based .Acquired signals will then be transmitted to the central system via TCP/IP or UDP.

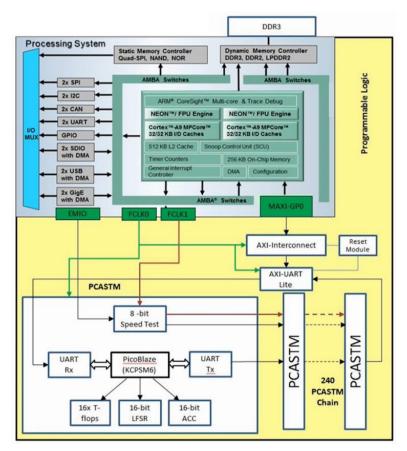

The front end and the ADC section is the same used in the original solution, but in the new system it is directly interfaced to a FPGA board. The recent ZINQ architecture, providing on the same chip a programmable FPGA and amulticore ARM processor, represent an attractive approach for interfacing rgw ADC board, using the FPGA hor handling the serial line digital line from the ADC and the processor to send data over the network to the central system. The board selected for this application is Red Pitaya, histing a Zinq FPGA with a dual core ARM processor. Even if that board hosts its own ADC, in this application the internal ADC is not used, taking input signals from he external ADC board via a serial link connected to the FPGA.

The idea is that every new electronic board assigned to the research groups will be part of all diagnostic systems and will be accessible from the control room as a simplify data acquisition system, in the next chapter identify like sDAQ.

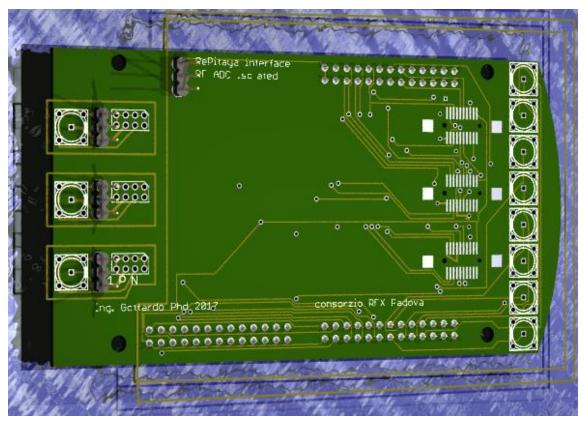

In the first part of the research, the development of an interface board connecting the ATCA-MIMO-ISOL to the RedPitaya is presented.

Two prototypes have been obtained, a first version capable of interfacing 4 ATCA-MIMO-ISOL modules applied in the experimental phase, and a second version, with three channels, much more complete than it can be installed on RedPitaya, using the appropriate topologically coincident connectors to direct insert dougtherboard to motherboard.

A two layer system is obtained in which the are 4 RF connectors. These 4 BNC are 2 analog inputs and 2 analog outputs that remain active in the motherboard (RedPitaya), while the daughterboard, inserted as a top floor, shown the three BNC connectors associated with their respective ATCA-MIMO-ISOL modules, and on the other side the 8 standard ADC channels, standard speed, in the ARM section.

All the digital I/O available in Red Pitaya are reported on the Daughter board connectors and it is available for other applications both in ARM or FPGA Zynq internal section.

The second version solves the problem of adapting the voltages needed at some I / O points due to constraint due to both hardware configuration and transmission protocols implemented firmware in HDL.

The developed electrical diagrams, the layout and construction files gerber are available for those who want to continue the search at [1].

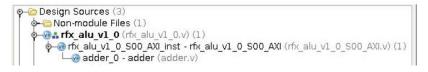

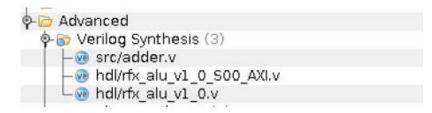

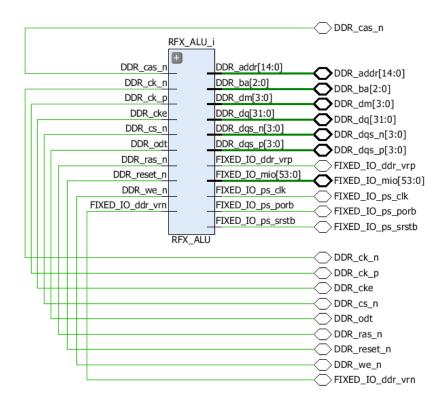

In the second part of the thesis, the software of the FPGA section has been developed which allows serialization of the output of the 18bit ADC mounted on the ATCA- MIMO-ISOL modules. The same software implements the transfer between the two internal sections of the ZYNQ using the AXI 4 lite protocol in order to send data to the processor and eventually over the network.

The FPGA program will manage a data stream acquisition and implement DMA procedures ttransferring acquired samples into processor memory.

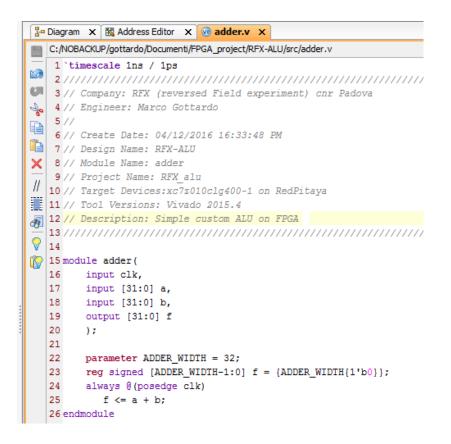

The software platform used for FPGA programming is Vivado 2015-4 with which using HDL language IPs have been developed.

A dedicated driver was developed and continuous streaming acquisitions were key to collecting data in the experimental part of the thesis.

A possible application of the FPGA-based acquisition and, in particular, of the new electronic board that mount the SoC FPGA systems is the possible integration of complex timing systems such as protocol 1588 for Ethernet synchronization.

Signal processing, like filtering or integration, could also take place in the FPGA section before sending data to the ARM system.

This opens the way for the possible implementation of complex operations performed locally and with predetermined time in the design phase of logic making intrinsically compatible operations possible for real-time use.

For example, a possible application of fundamental importance to the acquisition of signals from magnetic probes is the possibility of numerical integration in hardware and before transmission, exploiting the typical times of an FPGA architecture.

The integrated value in the FPGA section can be reprocessed in the region itself or transmitted to the ARM section without the need for further integration without the need for further post processing.

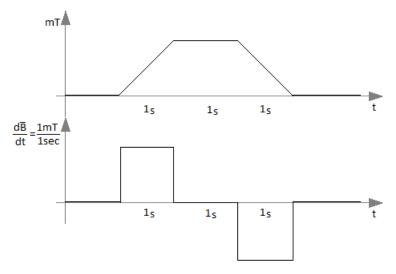

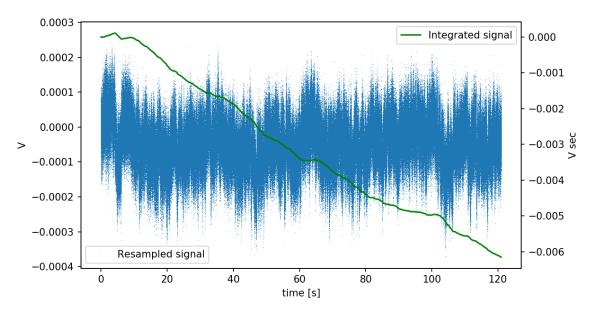

numerical integration is crucial due to the nature of probes that return a signal proportional to the derivative of the magnetic field.

During the implementation of the system, it turned out that the current front end and ADC solution are not fit for numerical integration because of the added noise, originating an unacceptable drift when integrating input signals for few seconds.

The reason for the added noise has been investigated and the problem was found in the circuit section that creates the reference for the ADC at differential inputs, an anomaly has been encountered and will be discussed in a separate paragraph.

Some hardware alternatives are proposed to solve them and will be presented in the end of this thesis. and in addition of a new software solution to be located in each single SoC (system on Chip) that corresponds to any low-cost diagnostics.

Another goal, other to maintaining an equal or greater performance of these simplified, and the low cost diagnostic, is the possibility of assigning to each individual research group although the number of captured signals greatly increases.

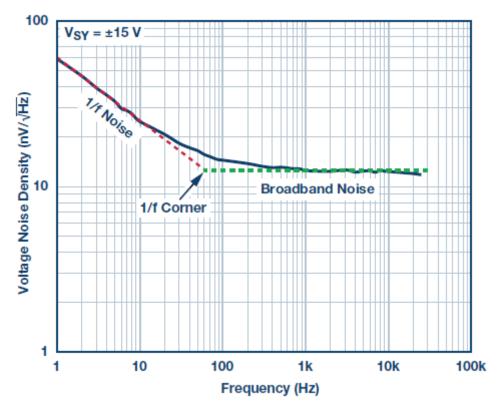

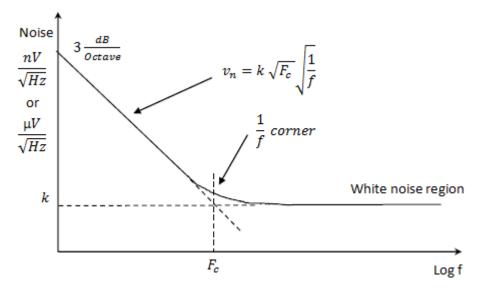

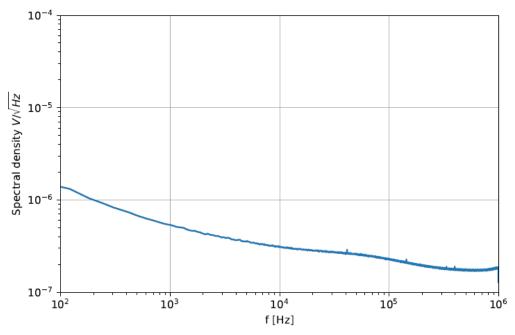

More in detail, the low frequency noise orived to be the cause of the drift in integration. It is noise detected under the frequency we indicate with Fc, "corner Frequency", prevents the numerical integration of the acquisition for long periods, in case of RFX over 10 seconds.

However, the inadequacy of the circuit section from the connector to the input of the ADC is identified, which contributes to introducing the signal non-integrability.

In a specific chapter, the developed hardware interface, in two versions is presented, and the constructive gerber files are available at [2].

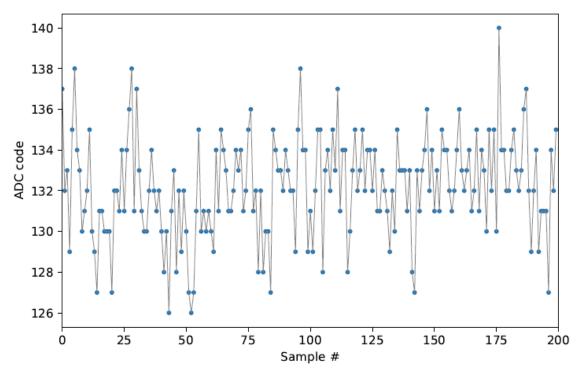

The final part of the thesis consists in some test to measurements of intrinsic noise of the components used and the circuit configurations in which these components are inserted in the context of the ATCA-MIMO-ISOL modules. This activity has been carried out in order to better characterize the system and its limits.

In the experimental section a test case, consisting of an induction coil, was created like shown in the § 0 powered by a low noise power supply and terminated on a resistive load.

A coil voltage was supply to a modulating, well-known, harmonic signal.

In the test coil a biaxial magnetic probe was inserted whose output was sampled by our experimental system for periods ranging from 10 to 40 seconds depending on the test performed.

The tests had two purposes, the noise measurement at the top of the spectrum and the measurement at the low end of the spectrum.

Several graphs have been derived, including standard noise deviation depending on the duration of the sampling, the trend of the integrated signal, the noise density histograms under various conditions of use.

#### **1.2.** Fusion experiment diagnostics

In current fusion experiment machines many diagnostic equipment are involved with heterogeneous type, generating a large amount of signals that must be acquired, stored and processed. The signal acquisition and processing recently received more and more attention due to the possibilities in the machine active control that proved to be a valuable choice for long lasting pulses stabilization.

The diagnostic type is often closely related to the way the data is achieved and elaborated, passing from the sensor system through the digitalization of the signals and finally to the computing devices that generate a possible control feedback or store data in archives.

We can divide diagnostics in main categories, associated to different physical phenomena and of course to the different type of acquisition system involved. The four major families are listed below:

- Spectroscopic diagnostics, like XUV-VUV or X-Ray, or electron cyclotron emission.

- Refractometers and interferometers, which manipulate optical and laser signals by performing demodulation.

- Thomson scattering. It is an elastic scattering of electromagnetic radiation by a free and charged particle. measurement of electron temperature Te is provided by Thomson scattering of laser light (TS).

- Arrays of other diagnostics representing many different other physical quantities acquired from the experiment.

The last type of diagnostics are the heart of the investigation for the development of new hardware and software solutions in this thesis. These are represented by broadband signals that usually extend within a 500kHz band, acquired from probe arrays. Common signals of this kind could be represented by:

- Signals from magnetic probes

- Detectors of soft x-ray, acquired by probes derived by photodiodes.

- Langmuir probes.

- photomultipliers.

In particular we will focus on the sensor chain used to acquire the magnetic field inside the experiment vessel. This specific diagnostic use to present low SNR, high dynamic range, wide bandwidth, and superimposed noise. But mainly the problem comes from the integral nature of the signal itself because the acquired quantity is proportional to the derivative of magnetic field.

Indeed the actual minimum signal detectable by the RFX magnetic probe system is:

$$\frac{dB(t)}{d(t)} = \frac{1 mT}{1 sec}$$

Thus it follows immediately that the magnetic field comes from an integration of the acquired signal in time.

The concept of acquisition makes desiderable to design compact embedded equipment to ease the installation. It also asks for a strong insulation of the frontend with respect to the converters in order to both mitigating the possible ground loops and eddy signals coming from impulsive variations of the local magnetic field passing through the circuits.

#### 1. 3. A Simplified customizable DAQ

The aim is to realize a simple, possibly modular, system for acquiring analog signals from a plasma diagnostic in contact with or very close to the plasma. The application requires a reasonable bandwidth (typically from DC to 1 or 10 MHz, depending on the application) in an environment subject to strong EM disturbances (arc-discharges, voltage spikes, RF). Usually measurements are carried out on arrays of sensors, and number of channel to be acquired at each station is often high (say from 8 to 64).

The advent of SoC FPGA devices now allows the building of DAQ/control systems which can be connected directly close to or even embedded in plasma diagnostic systems. This approach now appear feasible and at low cost. The advantages are clear. From the technical point of view it would increases the robustness and the quality of the signals. From the management point of view it will bring a great simplification of the system cabling, overall design and maintenance, reduce the necessary documentation and deployment cost and time.

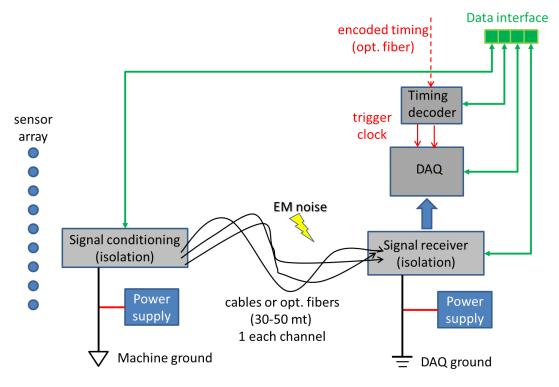

Figure 1-1A Typical approach for a diagnostic system.

Signals are coming from a variety of sensors like PMTs, diode detectors, probes and magnetic coils. Most of these are low voltage, high impedance outputs and require amplification and buffering to be sent over cables. In most cases their ground reference are at different potential, which at best causes noise disturbances and in worst cases can (and often did) destroy part of the electronics. Differential transmitter/receiver requires expensive balanced cables and the rejection it is not effective at high frequency. Moreover serious spike can still damage the electronics. In many cases expensive fiber optic systems have been used.

The acquisition system is to be synchronized and triggered by the general timing of the experiment and this done by using another separate module system.

Morover often an additional local PC is needed to perform simple but essential tasks or add missing interface functionalities.

Figure 1-2 Current situation, typical diagnostic wiring

In Figure 1-2 Current situation, typical diagnostic wiringa real world example is shown, the cabling of fast magnetics and Langmuir probe systems (taken out from the trays for maintenance) on RFX-mod.

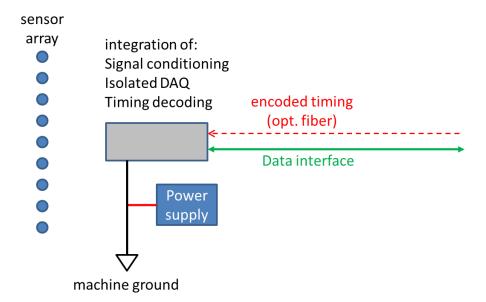

#### 1.4. The new proposed approach

The new proposed approach:

Figure 1-3 The new proposed approach with simplified wiring.

Beside the extreme simplification of the layout two other important benefits can be achieved:

a) a short electrical connection between the transducers (typically less than 5 or 10 meters, depending on the application) signals and the Daq system;

b) the isolation of all I/O channels, including data interface and triggering signals.

The interface and cabling requirement are drastically reduced, being needed only the power supply, the analog signal inputs/outputs, the data interface (Ethernet (100M/1G).

For less demanding timing requirement the timing distribution can be accomplished without fiber, using PTP protocol (IEEE 1588) over the Ethernet connection.

The system should be realized in order to accommodate the additional custom electronics needed for signal conditioning, which is application dependent.

In the following the specification for two kind of system are listed.

minimum requirement (optimal requirement)

Both systems should be modular and to be mounted either stand alone or inside an Eurocard 3U rack.

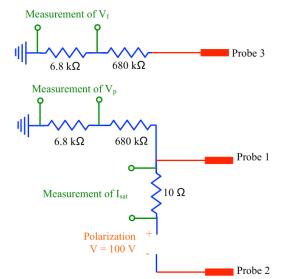

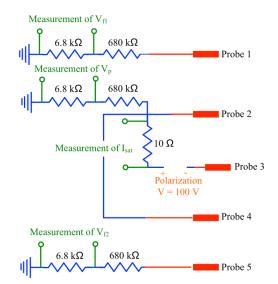

# 1. 5. Daq system for array of 5 pin balanced electrostatic probe (or fast magnetics)

### Specification for optimal acquisition system of one 5 pin balanced electrostatic probe.

The 5 pin balanced probe is an extension of the basic triple Langmuir probe configuration. The triple probe consists of three electrodes immersed into a plasma which are polarized according to Figure 1-4 [20]

Figure 1-4: Triple Langmuir probe configuration

Three simultaneous measurements are taken: the current (Isat) flowing from probe1 to probe 2, and the two voltages of probe1 (Vp, plasma potential) and probe2 (Vf, floating potential). From these three measurements it is possible to obtain an estimate of the local electron temperature ( $T_e$ ) and electron density ( $n_e$ ) of the plasma [21].

The 5 pin balanced probe (see Figure 1-5) is a refinement of this basic configuration: Vp and Vf are splitted onto two pins, so that their value can be on the average referred to the central spatial position, where the current measurement is taken, in order to reduce measurement errors due to non uniform distribution of the plasma density and temperature.

Figure 1-5: 5 pin balanced Langmuir probe configuration

Moreover the Vf are taken as two separate measurements which are also used to compute the electric field E=(Vf1 - Vf2)/d, which can be used in a magnetized plasma to estimate the transverse drift velocity:  $v_{\perp} = (E \times B)/B^2$ .

From the electrical poin of view these measurements are not easy because very often the ground reference for the plasma is different from that of the acquisition system and in some conditions the plasma generates voltage spikes of 1 kV or more, which can damage the electronics. Thus a reliable measurement of these probes requires a galvanically insulated input.

The requirements can be summarized in the following list:

5 isolated  $\geq$  2kV ADC channels :

1 - 10 (20) Ms/sec

14 (16) bit resolution

Sync between different devices:  $\leq$  10 ns

Direct clock / trigger recovery from single optical fiber input:

MPB RFX-mod

Asdex timing

W7-X timing

acquisition time window : 100 ms – 5 s

(repetition rate TBD, for W7-X depends on the ability to send event data)

(event recording with post trigger, for W7-X)

(real time output of reduced quantities)

Ethernet connection for data readout and device control

Possible use of additional interface for slow digital or analog signals via SPI for monitor and control of additional devices (e.g. probe biasing power supply).

# 1. 6. Daq system for general purpose magnetics, soft X-Ray detectors, PMT, CCD, arrays.

Specification for optimal acquisition system of small arrays (usually from one single chip sensor) of photodiodes or photomultipliers (PMT).

4 or 8 isolated  $\geq$  2kV ADC channels

0.1 - 1 (2) Ms/sec

18 (20) bit resolution

i.e. an interface to support for existing ADC modules designed by IST

Sync between different devices: ≤ 200 ns

Clock/trigger through Ethernet, using PTP Ethernet and a dedicated protocol:

Direct clock/trigger recovery from single optical fiber input:

MPB RFX-mod

Asdex timing

W7-X timing

Acquisition time window : 100 ms - 5 s

Real time Ethernet output of averaged signals.

## Chapter 2. Definition and roles of magnetic diagnostic in a fusion machine

#### Magnetic diagnostics are instrumentations used for measurements of:

- magnetic fields outside the plasma

- electric currents that are the source of the magnetic fields

#### Magnetics measurements are crucial in fusion devices for:

• Machine protection and basic plasma control 'plasma current', 'plasma position', 'plasma shape', 'magnetic field errors', 'halo currents'

• Advanced plasma control 'MHD instabilities control', 'Plasma current density profile', 'equilibrium magnetic field distribution'

• Physic studies and performance optimization 'High frequency MHD instabilities'

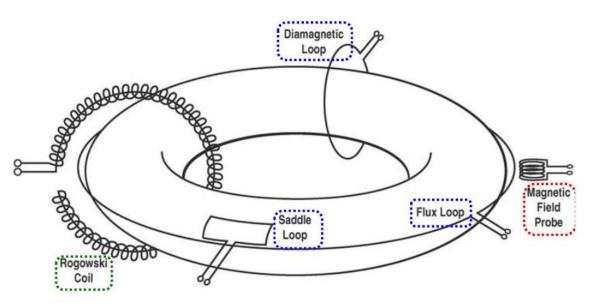

Figure 2-1 inductive sensors in a toroidal machine

The image shown the field of application and positioning of the probes in a toroidal machine.

Inductive sensors: (measurement)

- Extended loops (V, <B>)

- Localized probes (B)

- Rogowski coils (I)

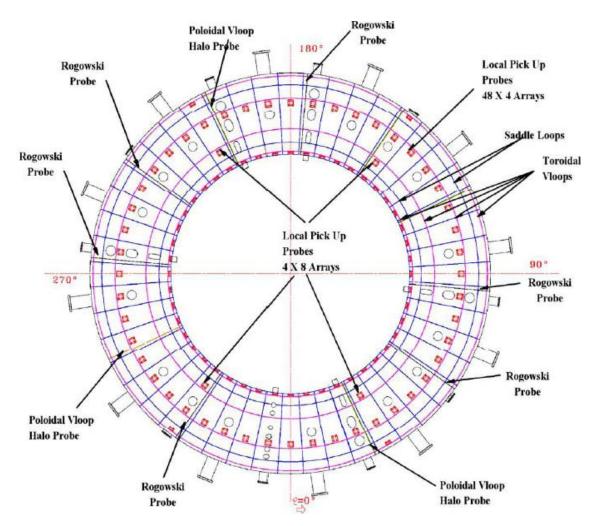

#### Figure 2-2 RFX-Mod external magnetic probes layout.

- •8 continuous flux loops

- •6 Rogowski coils (for plasma current measurement)

- •5 diamagnetic loops

- •32 partial poloidal loop voltage (Halo Currents)

- •48 x 4 saddle loops (full vessel coverage)

- •48 saddle loops (error fields at gap)

- •48 x 4 bi-axial pick-up coils (poloidal & toroidal)

- •32 bi-axial local coils (poloidal & toroidal)

In the very narrow space between the vessel and the shell, a uniformly distributed system of 220 thermocouples and 700 magnetic transducers has been designed to reconstruct the complete map of the energy deposition and of the magnetic field. The frequency bandwidth of the magnetic transducers are limited to few tens of kHz due to the shielding effect of the vacuum vessel and the sensitivity of the pick up coils is sufficient to discriminate a signal less than 1 mT whereas the maximum expected field is in the order of 0.8 T.

The magnetic transducers will also provide the feedback signals for the active control of the MHD modes.

Figure 2-3 Overview of magnetic probes on RFX-Mod

The magnetic probes, in the current RFX-mod, are 139 inside the vessel and 739 exvessels. A complete refurbishment/upgrade is presently under study for a major modification of the RFX machine.

In the Figure 2-3 is shown the 32 partial poloidal voltage probes for halo currents

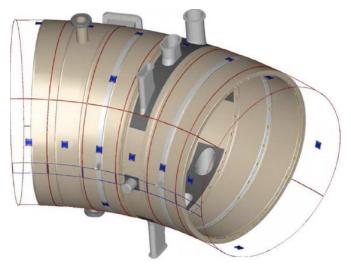

Figure 2-4 Integrated System of Internal Sensors (ISIS) for RFX-Mod

In the Figure 2-4 is shown the first wall, that is, the inner surface of the vacuum chamber immediately in contact with the plasma: it is entirely covered by a 2016 graphite tile system, which resist temperatures up to 3000 °C. On the inner equatorial line, a set of magnetic probes are visible. These are a subset of the 139 inside the vessel.

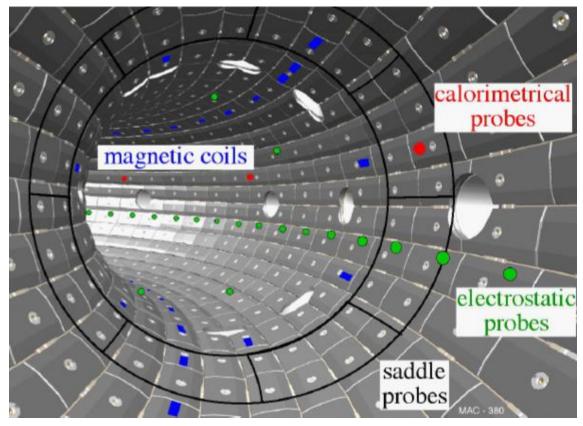

Figure 2-5 View of RFX-mod first wall with probes layout.

- Blue: Magnetic pick-up coils: 131

- Black: Saddle flux loops: 8

- Green: Electrostatic probes: 97

- Red: Calorimetrical probes: 8

During the machine upgrade in 2004 a close fitting 3 mm thick Copper shell has replaced the previous 65 mm Aluminum shell.

The modification is part of a set of enhancements aimed at optimizing active control of the MHD and resistive wall effect to induce plasma mode rotation and to prevent mode phase locking to prevent non axisymmetric configuration of plasma column.

The shell has one poloidal gap with a toroidal overlap of 23° (Figure 2-6).

The outer equatorial gap is short-circuited with bolted copper plates. The shell is clamped to the vessel through stainless steel bands that sustain the electrodynamic forces arising in the shell.

Precise field reconstruction requires accurate calibration and accurate alignment of the probes to minimize the spurious effect of unwanted components.

The probe distribution must be chosen carefully to avoid such aliasing effect, due to conducting structures, which influence the field spatial components typical of the plasma modes.

Figure 2-6 mm copper shell. Exploded view.

Figure 2-7 Biaxial magnetic probes RFX installation

To reduce shielding effects, probes must be installed inside the stabilising shell.

The three components of field outside the vacuum vessel can be very different in amplitude.

At the same time, one can reach 0.8 T on one component and the other can be of the order of some mT. Furthermore their time variation can be very fast.

In general the probes installed have to guarantee an uncertainty less than 1 mT to correctly reconstruct the plasma behaviour.

Figure 2-8 RFX-Mod copper shell

Figure 2-9 Magnetic probes connectors on RFX vacuum chamber

In the Figure 2-9 is shown the position and the size of the probe connector on the top side of the copper shell in RFX-Mod experiment.

The whole system is composed by 4 toroidal arrays of 48 bi-axial (Bt & Bp) probes each (4 x 48). Then an arry of 4x48 saddle coils fro the emasurement of radial filed component. The cables from the probes are grouped in 12 sections, each with connectors.

Figure 2-10 Biaxial probe LEMO connectors

Each probe uses a twisted pair and two pin on the connector.

On RFX mod there are four pairs of connectors like the ones shown in Figure 2-10 for every thirty degrees of the vessel.

The two connectors of each pair are of different diameter and different number of pin, this is not an optical effect due to the perspective of the photo.

## Chapter 3. Probe and transmission line specification

### 3.1 Magnetic probe circuit model

In this section is analysed a two axes magnetic sensor used on the toroidal device RFX in Padua.

The sensor was produced and tested by Laboratorio Elettrofisico s.r.l. Via G. Ferrari, 14-20014 Nerviano (MI) Italy.

A large number of probes are required to correctly identify the complex spatial structure of the plasma column.

An accurate calibration and a careful probe mounting is required.

Probes are installed inside the stabilising shell, placed very close to the vessel.

To allow a more detailed study of plasma behaviour, the electromagnetic diagnostic was split to two parts. The first is internal to the vacuum vessel and is integrated with an extended set of electrostatic and calorimetric probes. It is devoted to the study of turbulence and fast MHD phenomena not easily observable from the outside of the vessel due to its shielding effect. The second is placed between the vacuum vessel and shell. It is devoted to the study of global plasma parameters and low frequency MHD phenomena, which largely affect the plasma equilibrium.

The two parts of the diagnostics have been designed in order to be complementary and provide a complete and detailed set of information on RFX magnetic configuration.

| Kind: Magnetic probe        | Sensor number on machine: 244           |

|-----------------------------|-----------------------------------------|

| number of internal windings | 260 (270 from technical specifications) |

| number of external windings | 214 (220 from technical specifications) |

| internal winding resistance | 23Ω                                     |

| external winding resistance | 21Ω                                     |

| internal winding inductance | 0.23mH                                  |

| external winding inductance | 0.32mH                                  |

| Probe area                  | 0.021m <sup>2</sup>                     |

The specific sensor is the number 244 installed.

| Table 3-1 | Magnetic probe technical characteristics. |

|-----------|-------------------------------------------|

|-----------|-------------------------------------------|

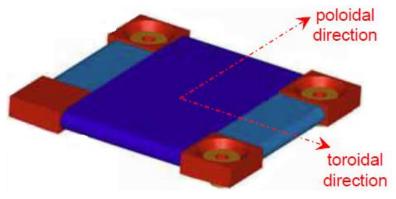

Probes are realised by winding two independent and orthogonal windings on the same core, leaving four corners free (Figure 3-6).

Each winding is made with enamelled copper wires, and composed of two layers.

Special high temperature Kapton<sup>©</sup> tape is used between the two windings and between layers in each windings.

This tape has also a protective function and helps to keep the winding turns in position during thermal cycles.

The core thermal expansion coefficient must to be as close as possible to that of copper, as the probes are bolted to a copper surface.

This guarantees also that the probes are subjected to low stresses due to the thermal expansion of the shell.

At the same moment must be not conductive in order not to reduce the frequency response.

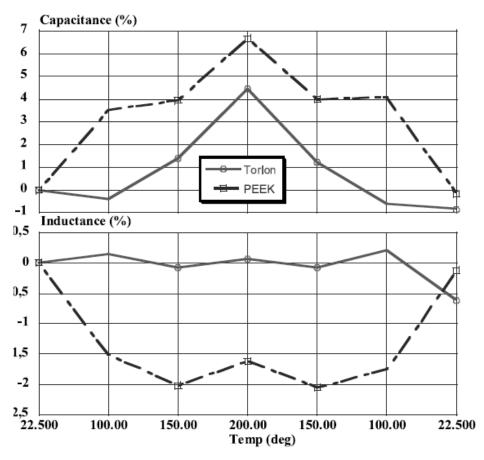

A class of high performance polymers were chosen. Ceramics have been discarded due to their fragility and too low thermal expansion coefficient compared with that of copper. Two materials were selected, PEEK<sup>©</sup> and Torlon<sup>©</sup>.

Figure 3-1 Magnetic probe model typical.

Figure 3-2 Two axes magnetic sensor model.

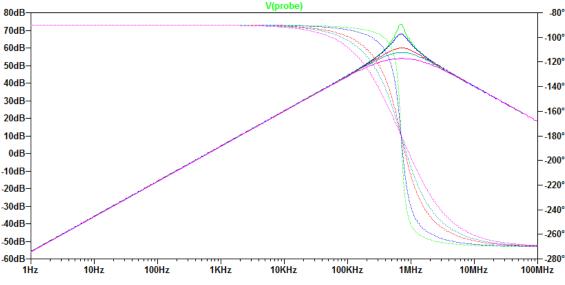

Figure 3-3 Derivative of the frequency response two-axis probe.

Figure 3-4 Size and appearance of the magnetic probe.

The probes must react as quick is possible to the variations of all the three components of magnetic field during the pulse, even in the presence of high spatial asymmetries in toroidal direction.

In RFX, due to modes up to n=15 in toroidal direction and mainly m=0 and m=1 in poloidal direction the signals is typically in the dynamic range up of 60dB with a frequency spectrum of several kHz.

Probe bandwidth is limited by internal resonances of the two coils, which result around 200 kHz for both the coils.

A further design specification for the sensors is due to the maximum operation temperature of the vacuum vessel (200 °C).

The RFX probes have to guarantee an uncertainty less than 1 mT to correctly reconstruct the plasma behaviour.

The latest ones installed should allow to study local behaviour of the plasma and to operate the new saddle coils.

These specifications are particularly stringent and require an accurate calibration and a careful probe alignment to minimize the spurious effect of unwanted components.

According to the Sampling Theorem, a correct reconstruction of the magnetic field from the signals collected by the local probes could be obtained only if at least 144 toroidal X eight poloidal measurement points are used but a so large number of probes are not acceptable.

To minimize the aliasing effect the sensors spatial distribution must be chosen carefully on the machine to avoid the effect of metal structures.

Figure 3-5 Torlon Vs Peek core probe capacitance and inductance.

In Figure 3-6 Bi-axial magnetic pick-up coils, is shown how the probes are realised by winding two independent and orthogonal windings on the same core, leaving four corners free. Each winding is made with enamelled copper wires, and composed of two layers. Three of the corners are drilled with holes, so that the probe can be bolted to the internal surface of the new shell.

Figure 3-6 Bi-axial magnetic pick-up coils

The fourth corner is not drilled and is useful to define the correct mounting rientation. In order to minimise the radial size of the probe one of the major sides of the probes is carefully machined to fit exactly with the curved surface of the vessel.

These two axis pick up probes, are placed on the machine close to the axis of saddle loops, which measure the radial field, are intent to measured local toroidal and poloidal fields.

The radial field measurement results averaged per the loop area, but this should not alter the measurement of the spatial harmonics of interest.

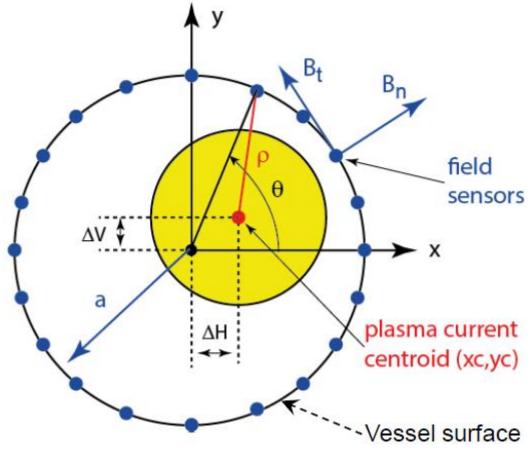

Figure 3-7 Plasma position from magnetic measurements.

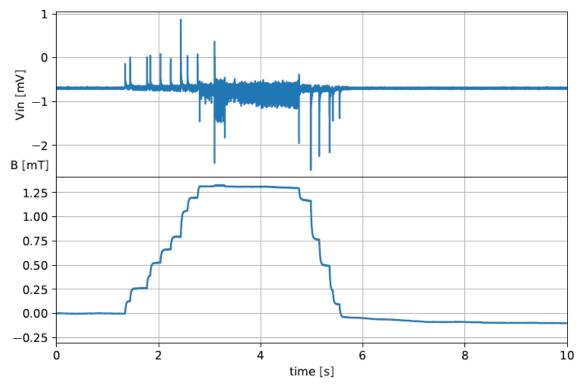

#### Figure 3-8 RFX-mod waveform of magntic field from pick-up array

The probes acquisition typically occurs like a differential signal as shown in the following diagram.

The operational amplifier, in these principle diagram, is ideal.

In a real application it add some troubles due to the intrinsic noise and the band width. We will see that the typical noise, present in the low end of the band, between 0.1Hz and 10Hz, or even lower, plays a fundamental role in signal acquisition, especially if extended over ten seconds.

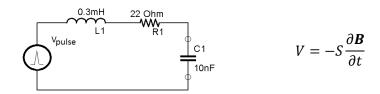

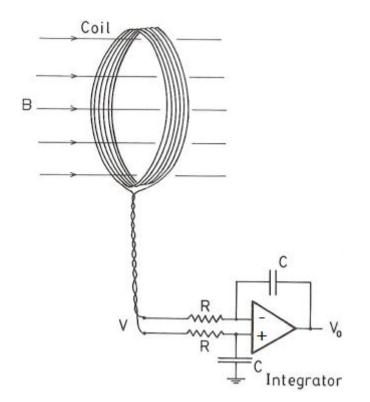

#### Figure 3-9 Differential acquisition of magnetic probes.

From Faraday law:

$$v_{in} = -\frac{d\Theta(t)}{dt} = -\frac{d}{dt} \int_A \boldsymbol{B} \, dS$$

If **B** is uniform within the loop:

$$v_{in} = NA \frac{dB}{dt}$$

After the integrator:

$$v_{out} = \frac{NA}{RC}B(t)$$

RC is the time constant of the integrator.

A passive RC integrator, placed in the frontend, provides accurate integration of transient that are too rapid for ADC sampling rate.

For slowly varying signals the digital integral dominates and the RC term becomes negligible.

A kind of magnetic probes are the pick-up coils, that is small magnetic sensors, that locally sample  $B_{\theta}$ ,  $B_{\phi}$  and  $B_{r}$ .

Large arrays with hundred of coils are used in fusion machines, placed outside the vacuum vessel.

The plasma shape is reconstructed with high detail by Fourier analysis.

Pick-up coils also provide information on plasma instabilities, MHD activity and magnetic fluctuations.

#### 3.1. Probe electrical modelling

Figure 3-10 Basic model of a magnetic probe

An ideal magnetic pick-up coil is considered to have an output exactly proportional to to the derivative of the applied magnetic field, However a proper description of real probe requires a more complete description to take into account its structure and the connected components.

A probe itself is basically an inductance loaded connected to cable and to a detection circuit. The probe itself have some internal capacitance which close the circuit causing

some current flowing into the probe, which reduce the signal amplitude the signal at high frequency.

A probe can be modelled as inductance, in series with a voltage generator (which is proportional to dB/dt) a resistance, with the parasitic capacitance in parallel.

A better modelling of the voltage source can be using an idellay coupled transofmer transformer driven by a current generator. The equivalent magnetic field is directly represented by the current at the primary. The secondary when open will behave like an ideal probe giving the dB/dt term, while it can be connected to external component chain to simulate its response on a real system.

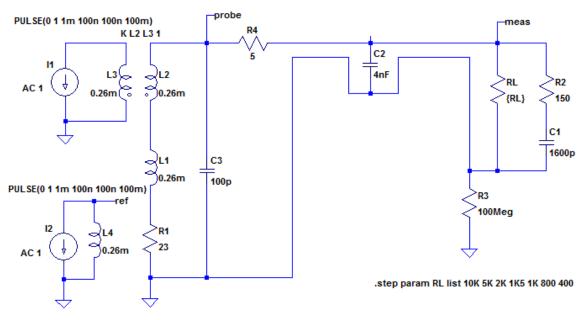

Given the circuit shown in Fig. 3-10 the basic scheme of the probe is an RLC circuit connected to a generator. The resonance frequency depends on the value of the capacitor C3, which includes the parasitic capacitance of the probe and the capacitance of the transmission line.

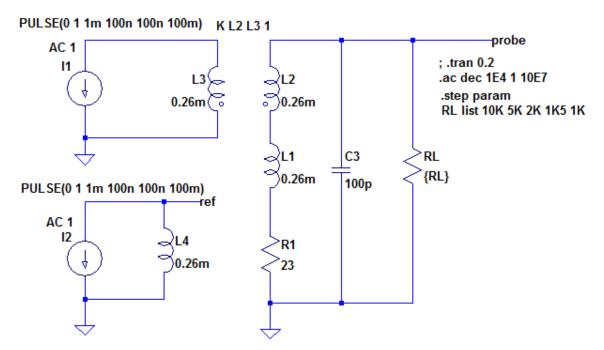

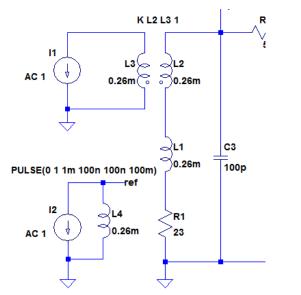

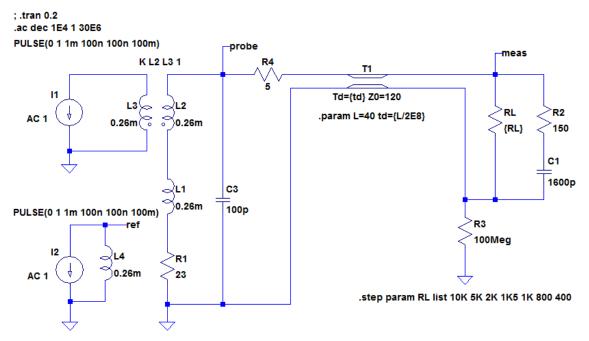

### 3. 2. Transmission line circuit model

Actually the sensors are connected to acquire system by a transmission line typically 40 meters long.

Being the typical impedance of the line about to 120 Ohms, it has a capacitance of 100 pF/m.

It is introduced a line capacitance equal to:

$$Cl = 100 \frac{[pF]}{[m]} * 40 [m] = 4 nF$$

Figure 3-11 Two axes magnetic sensor model connect to transmission line.

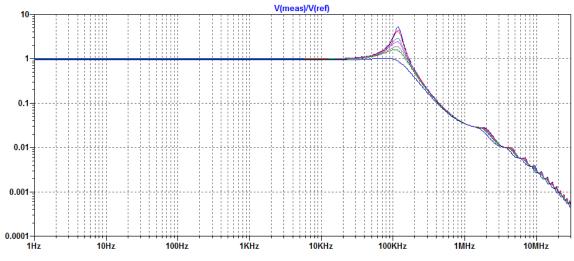

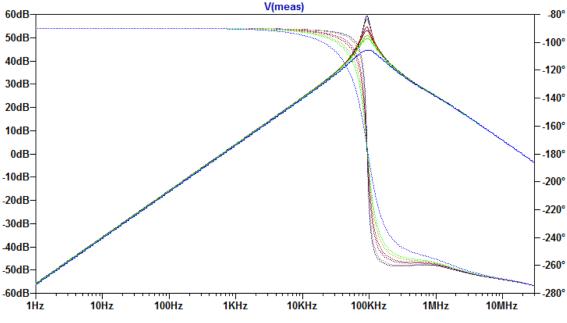

Figure 3-12 *Two axes probe and transmission line* frequency response.

; .tran 0.2 .ac dec 1E4 1 30E6

Figure 3-13 Capacive model of the line

Figure 3-14 Capacive transmission line frequency response

Here a comparison of two models, one with a transmission line and the other with its equivalent capacitor. In the frequency range of interest (< 1 MHz), the response is the same, so both models can be considered equivalent. At high frequency the line becomes dissipative and the small peak observed can be neglected.

## Chapter 4. Analog frontend specification

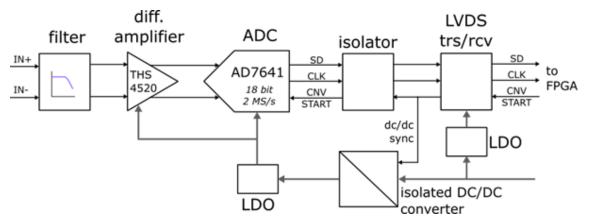

# 4. 1. Analog frontend to Zynq, the ATCA MIMO ISOL module

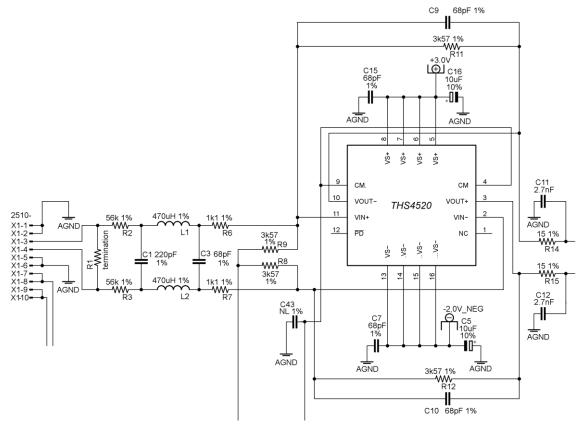

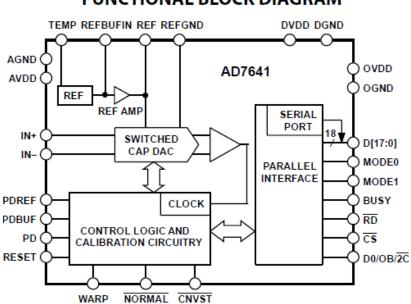

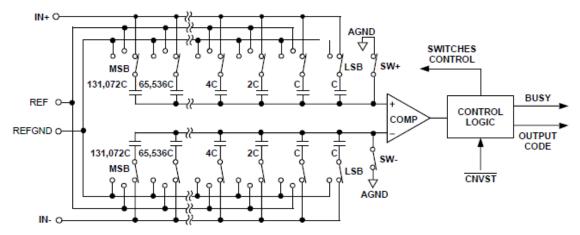

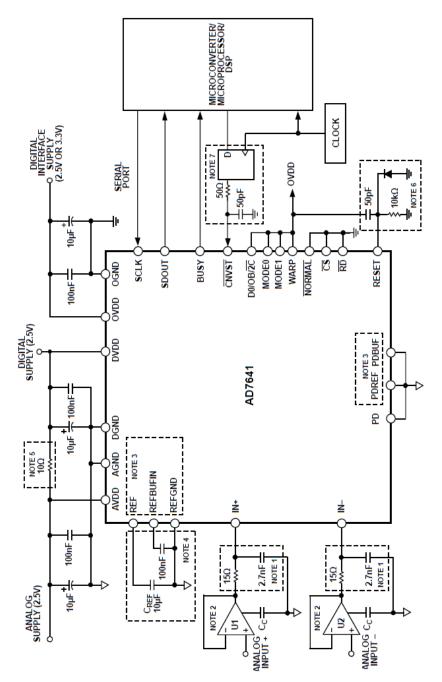

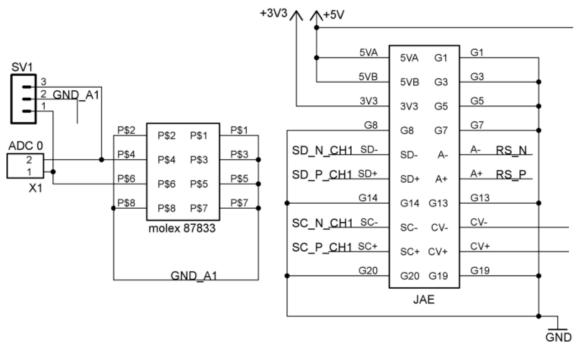

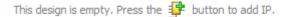

The AD conversion is delegated to the chip AD7641 and occurs with a discretization in 18bit SAR converter that acquires signals from a fully differential input in the range [+-2.048] V at the maximum rate of 2 MSamples/s.

The board is configured for serial communication according to the SPI protocol.

The 18 bit conversion is sent to pin 21, SDOUT.

The signal reaches the insulator IL 711-spin 3. Here is where the galvanic separation occurs from the field.

Downstream of the galvanic separation the signal passes through the SN65LVDT driver, which has an interface with other devices also outside of the board, making the system insensitive to electrostatic and electromagnetic interference.

More can be found in [15] and [16].

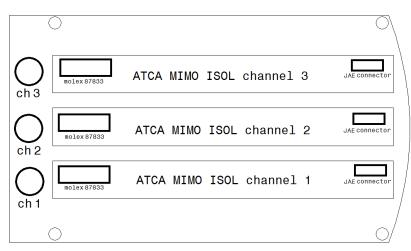

Figure 4-1 ATCA MIMO ISOL module, isolated differential analog fronted board.

The input of the module, Figure 4-1, so the part connected to the machine and the magnetic probes, is on the right side, on the Molex 87833 connector.

On the left side i visible the JAE connector, isolated side, which allows connection to the FPGA acquisition system.

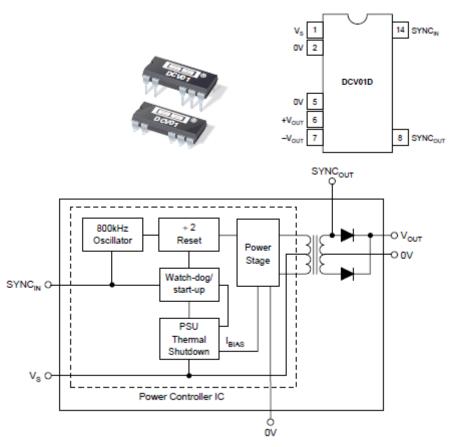

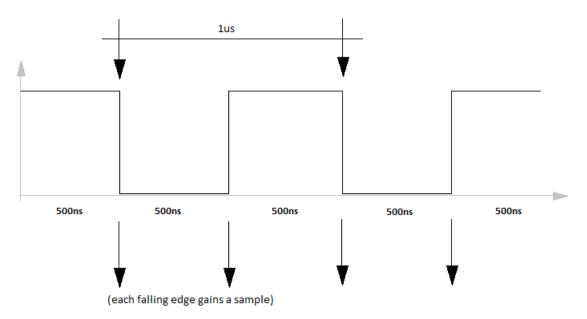

The analog input is initially filtered by a 1 poles, 100 kHz passive component connected to a differential amplifier THS4520 used as input range adapter; the AD7641 is configured to operate using serial communication protocol and the digital signals are delivered to the FPGA by means of a digital isolator. The power is supplied through an isolated DC/DC converter which is synchronized with the ADC conversion start

command in order to minimize the noise spikes generated during power switching phase.

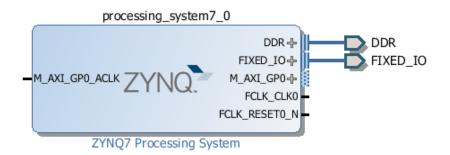

Figure 4-2 Block schematic of the ADC module.

Observing the block diagram in above figure it is noted that the external connector has two pairs of signals in two pairs of input and output connections.

All of these pass through the LVDS driver in the pin indicated in the figure, on the isolated section of the field that is the one which will refer the masses and power supplies to the Zynq.

| LVDS output signals from SN65LVDT |  | Input control signals SN65LVDT<br>(connector to Zynq) |     |

|-----------------------------------|--|-------------------------------------------------------|-----|

| SDATA +                           |  | CNVST+                                                | K16 |

| SDATA -                           |  | CNVST-                                                | J16 |

| SCLK +                            |  | RESET+                                                | M14 |

| SCLK -                            |  | RESET-                                                | M15 |

Table 4-1 Differential analog signals.

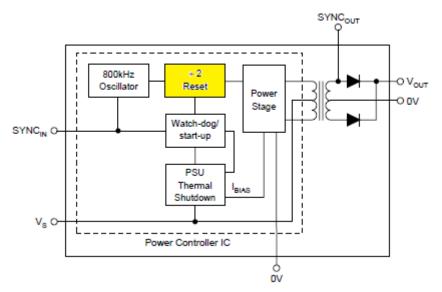

RESET+ is connected to power down signal of the ADC, and the RESET- is connected, through flip-flop, on the SYN signal of the DC/DC converter, named DCV010505, useful for the isolation:

To filter signals (getting more square) and clean them from unexpected noise, it is necessary to going through the Flip/Flop before going to DCV01 that allow the connection towards other devices even off the board.

Setting the SYNCIN pin low the oscillator stops in order to turn off the card when not in use, it reacts in about 2 microseconds.

The other signals are passed in single ended and connected to the ADC through opto isolators.

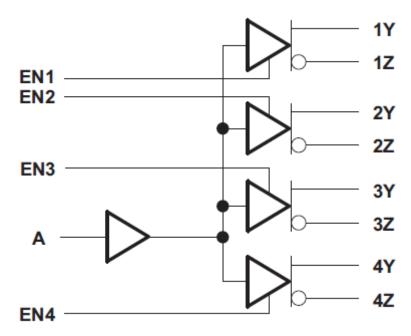

The ADC 7641 is the setting in pinMode [1: 0] = 11 so, from data book, (page 22), the system is placed in the operation mode **MASTER SERIAL INTERFACE** - Internal Clock.

Other settings of the ATCA MIMO ISOL board are Pin WARP = 1 and pin \_NORMAL=0.

This configuration puts the chip at the fastest acquisition speed of 2 MS/s, called WARP mode.

Insights are given on page 15 of the data book, chapter MODES OF OPERATION.

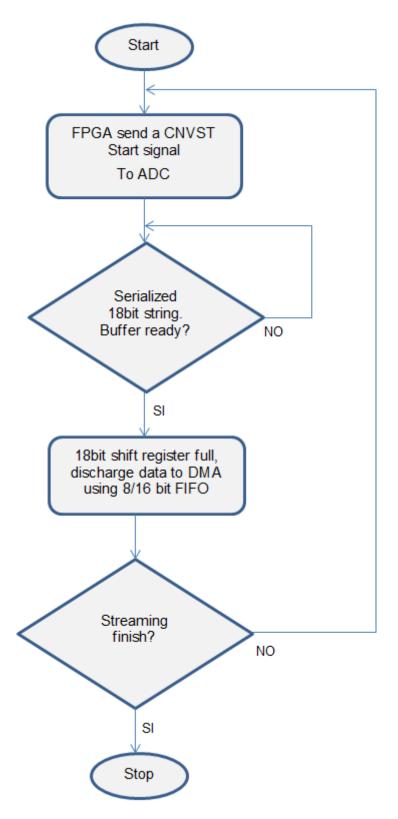

## Figure 4-3: Flow chart of data streaming acquisition to be implemented on the FPGA

The serial output of the ADC requires a 18 bit shift register in the FPGA to transform the serial data in 32 bit parallel word which can be handled by the processor or DMA.

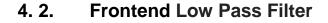

Figure 4-4 Low pass filter schematic.

The input stage is a passive low pass filter with a diagram in the Figure 4-4. The spice modeling leads to the tracing of the bode diagram in the Figure 4-7.

The resistive divider, composed of R9 and R8, is powered by the reference voltage generator shown in the Figure 4-12.

Figure 4-5 Molex 87833, probe connector

in Figure 4-5 Molex 87833, probe connector the input connector to which the magnetic probes are connected is shown. This is the 8-pin Molex 87833 model.

In the official diagrams, issued by the module manufacturer, it is erroneously reported to 10 pins.

A careful circuit analysis suggests that the feedback shown in fig 4-11 could be disadvantageous from the noise point of view during long-term integration processes.

Moreover, the operational amplifier used as a differential buffer in the frontend already has a reference generation option, making it possible to eliminate all the circuit part of Figure 4-12.

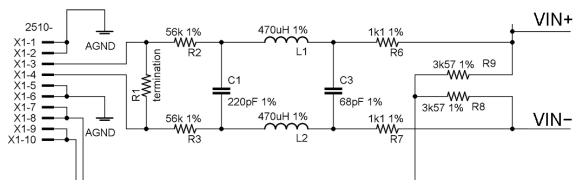

#### Figure 4-6 Low pass filter PSim.

Spice model of the low pass analog filter at the ADC module input.

For a correct simulation of the circuit it is necessary to inject in the middle of the resistive divider -1.25V generated by the operational IC2A of Figure 4-12.

Figure 4-7 Low pass filter Bode diagrams.

### 4. 3. Frontend to FPGA connector

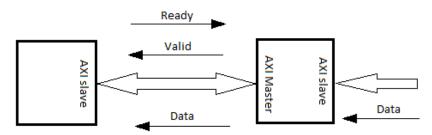

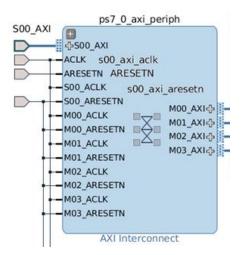

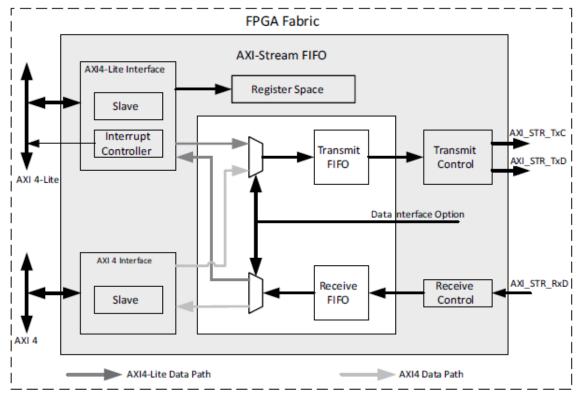

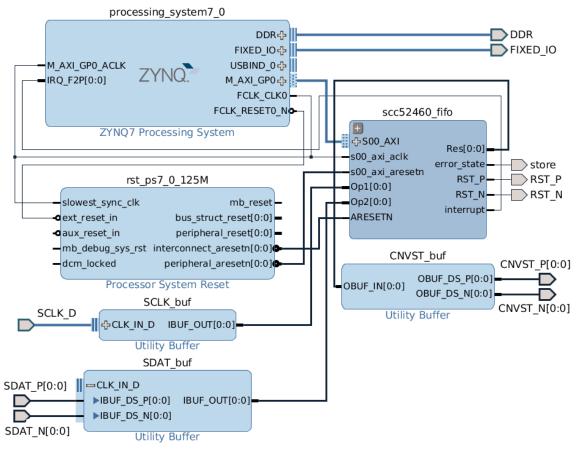

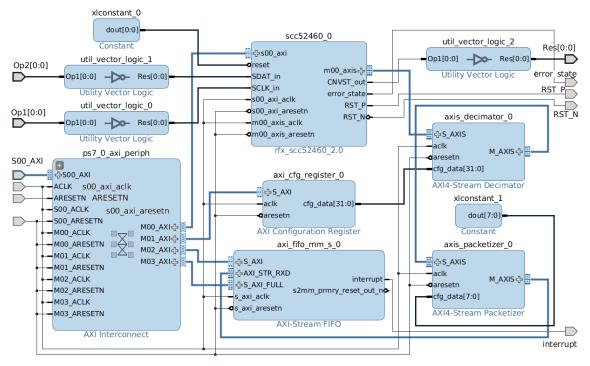

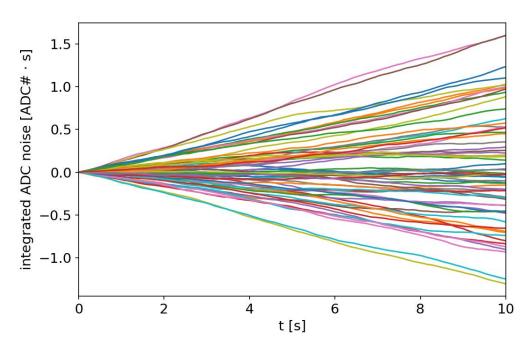

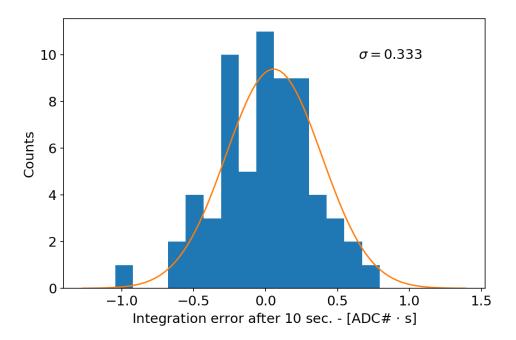

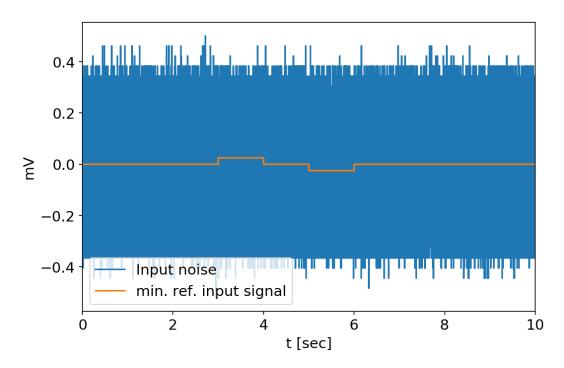

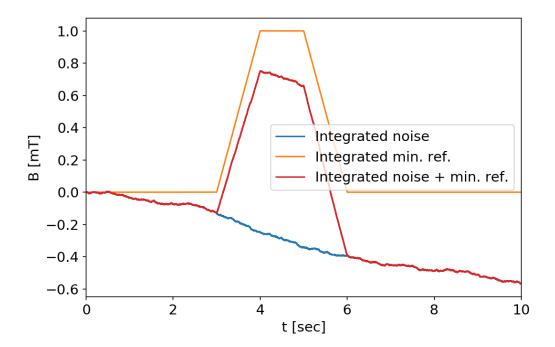

#### Figure 4-8 Analog frontend to FPGA connector.