# THERMAL DESIGNS, MODELS AND OPTIMIZATION FOR THREE-DIMENSIONAL INTEGRATED CIRCUITS

#### BY

#### LESLIE K. HWANG

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2018

Urbana, Illinois

#### Doctoral Committee:

Professor Martin D. F. Wong, Chair

Professor Deming Chen

Professor Wen-Mei Hwu

Assistant Professor Nenad Miljkovic

## ABSTRACT

Three-dimensional integrated circuits (3D ICs), a novel packaging technology, are heavily studied to enable improved performance with denser packaging and reduced interconnects. Despite numerous advantages, thermal management is the biggest bottleneck to expanding the applications of this device stacking technology. In addition to implementing the thermal-aware designs of existing methodologies, it is necessary to implement new features to dissipate heat efficiently.

This work presents two main aspects of thermal designs: on-chip level and package level. First, we propose a novel thermal-aware physical design on chip between devices. We aim to mitigate localized hotspots to ensure the functionality by adding thermal fin geometry to existing thermal through-silicon via (TTSV). We analyze design requirements of thermal fin for single TTSV as well as TTSV cluster designs with the goal of maximizing heat dissipation while minimizing the interference with routing and area consumption. An analytical model of the three-dimensional system and thermal resistance circuit is built for accurate and runtime-efficient thermal analysis.

In terms of high-performance computing systems in 3D ICs, thermal bottlenecks are much more challenging with merely on-chip design solutions. Intertier liquid cooling microchannel layers have been introduced into 3D ICs as an integrated cooling mechanism to tackle the thermal degradation. Many existing research works optimize microchannel designs based on runtimeintensive numerical methods or inaccurate thermo-fluid models. Hence, we propose an accurate but compact closed-form model of tapered microchannel to capture the relationship between the channel geometry and heat transfer performance. To improve the accuracy, our correlations are based on the developing flow model and derived from numerical simulation data on a subset of multiple channel parameters. Our model achieves 57% less error in Nusselt number and 45% less error in pressure drop for channels with inlet width  $100-400 \,\mu m$  compared to a commonly used approximate model on fully developed flow.

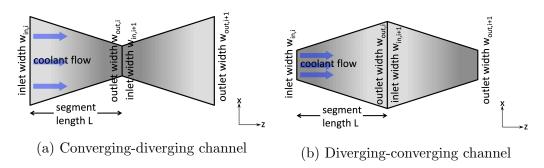

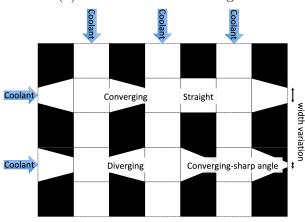

Next, we present the correlations for diverging channels as well as complete correlations that extend to any linearly tapering channel models, that include diverging shape, uniformly rectangular shape and converging shape. The complete models provide the flexibility to analyze and optimize any arbitrary geometry based on the piecewise linear channel wall assumption.

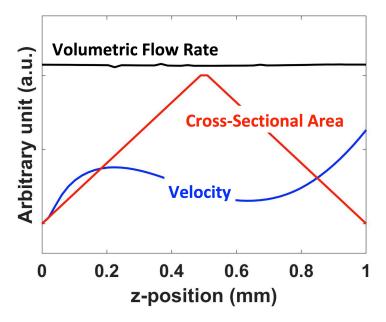

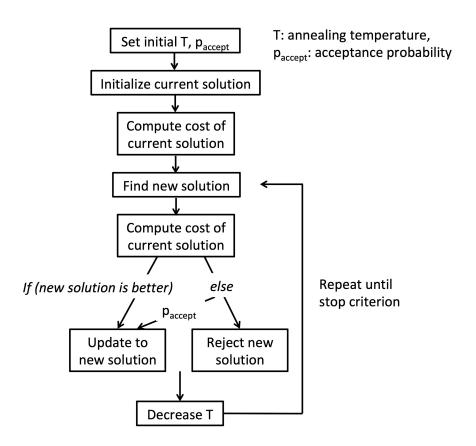

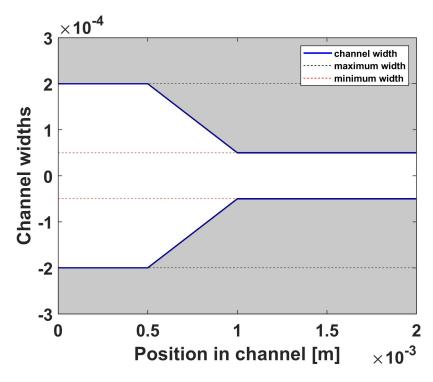

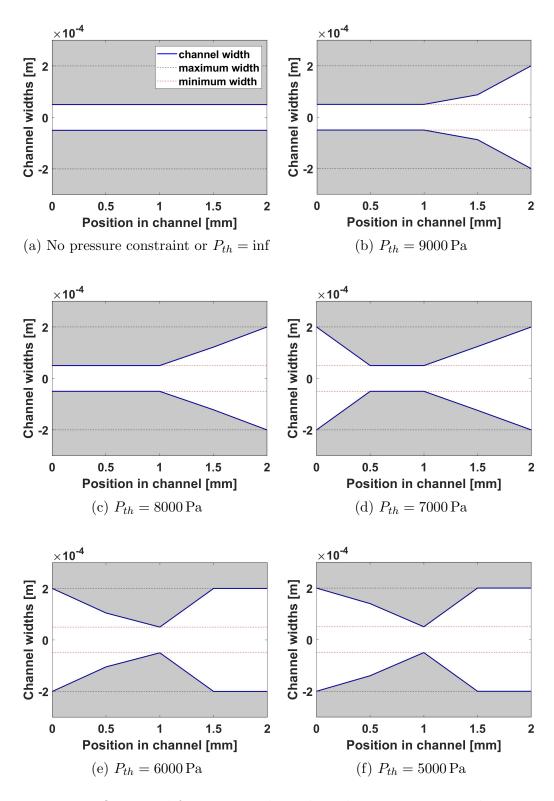

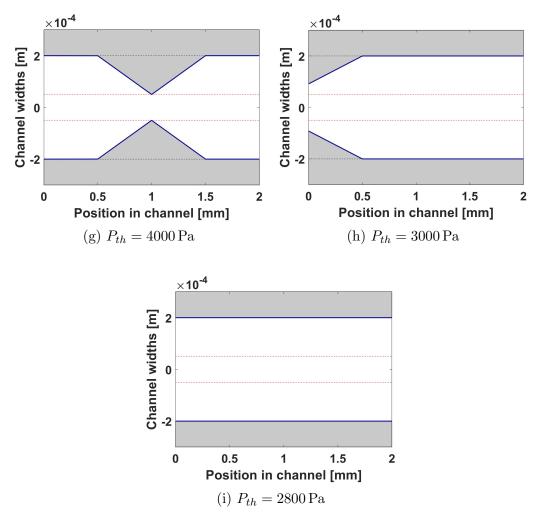

Finally, we demonstrate the optimized channel designs using the derived correlations. Tapered channel models provided the flexibility to incorporate any arbitrary shapes and explore the advanced geometries during the optimization. The microchannel is divided into small segments in axial direction from inlet to outlet and piecewise optimized. The simulated annealing method is applied in our optimization, and channel width at one randomly chosen segment interface is altered to evaluate the design at each iteration. The objective is to minimize the overall thermal resistance while pressure drop is maintained less than a threshold value and channel widths have minimum and maximum boundaries. We compare the designs with the optimization based on fully developed flow models and verify the channel performance through numerical simulations.

To guarantee optimality, accurate analysis is crucial. Our proposed models have significantly improved the accuracy by applying the appropriate flow assumption. However, many opportunities exist to increase the design flexibility and the accuracy. Fluid conditions, such as coolant material and varying volumetric flow rate, can also be part of the optimization parameters to expand the design scope. Moreover, physical phenomena, such as reduced friction on the channel walls or a vortex created on abrupt angle changes, can be considered to improve the accuracy in the closed-form models.

To my Romeo, for his love and memory.

## ACKNOWLEDGMENTS

Foremost, I would like to deeply thank my adviser, Professor Martin D. F. Wong, for his admirable guidance and supportive advice throughout my graduate studies. He has always encouraged me, led me with patience through the challenges and shared insightful advice for me to expand the scope and build critical thinking. This dissertation would not have been possible without his unconditional support.

I also want to share my gratitude to all my doctoral committee members, Professor Deming Chen, Professor Wen-Mei Hwu and Professor Nenad Miljkovic. Professor Chen brought a new analytical perspective and suggested potential work with high impact. I was able to learn the importance of details and think thoroughly on all matters through his keen observations. Professor Hwu guided me with inspirational insights on the work. His enthusiasm and curiosity in technology and passion in education taught me to continuously think about how each work connects in the bigger scope and contributes to industry and real life. Professor Miljkovic provided in-depth scientific knowledge and current interests and trends of leading industries. His advice and feedback were helpful to strengthen the work and motivated me to continue the research in the field.

Many people supported my PhD studies along the process in various aspects. Above all, I am sincerely grateful to Professor Beomjin Kwon, the best collaborator, mentor and my husband. His exceptional insight, constructive advice and endless discussions were the light to this work, and it would not have been completed without his support. I also would like to thank my friends and collaborators, Dr. Kevin L. Lin who initiated the idea of the research topic and Dr. Choden Konigsmark for his dedicated discussions and sincere support. I feel very fortunate to know them and have the opportunity to work with them.

My current and former research group members and fellow colleagues,

Khine Nyo Le' Han, Professor Tsung-Wei Huang, Chun-Xun Lin, Dr. Zigang Xiao, Dr. Pei-Ci Wu, Dr. Ting Yu, Daifeng Guo, Dr. Haitong Tian, Dr. Adeel Ahmad, Chun Yang, Jie Lv, Anant Agarwal, and Sitao Huang, have been an unforgettable source of support and friendship. Endless hours on campus were enjoyable and delightful through the interaction, conversations, technical discussions and fun I had with them.

Last but not least, I deeply appreciate my family for their support, unconditional love and sacrifice. They have always encouraged me to approach the end of the tunnel with abundant support. I cannot extend enough thanks to Romeo for the unforgettable memories and joy you have given and for sharing the time with me, and to Lyla for joining our family. We will be sharing a heartwarming future together.

# TABLE OF CONTENTS

| LIST O | F ABBREVIATIONS i                            | X  |

|--------|----------------------------------------------|----|

| NOME   | NCLATURE                                     | х  |

| СНАРТ  | TER 1 INTRODUCTION                           | 1  |

| 1.1    |                                              | 1  |

| 1.2    |                                              | 3  |

| 1.3    | 0                                            | 6  |

|        | TER 2 THERMAL THROUGH-SILICON VIA WITH THER- |    |

| MA     | L FIN DESIGN                                 | 8  |

| 2.1    |                                              | 8  |

| 2.2    | Analytical Model                             | 9  |

| 2.3    |                                              | 4  |

| 2.4    | Conclusion                                   | 20 |

| СНАРТ  | TER 3 ACCURATE MODELS FOR TAPERED MICROCHAN- |    |

| NEI    | L HEAT SINKS                                 | 2  |

| 3.1    | Introduction                                 | 2  |

| 3.2    | Related Works                                | 24 |

| 3.3    | Fundamentals of Heat Transfer                | 25 |

| 3.4    |                                              | 31 |

| 3.5    | - 0                                          | 10 |

| СНАРТ  | TER 4 COMPLETE MODELS FOR LINEARLY TAPERED   |    |

| MIC    | CROCHANNELS                                  | 2  |

| 4.1    | Introduction                                 | 2  |

| 4.2    | Complete Microchannel Models                 | 2  |

| 4.3    |                                              | 18 |

| СНАРТ  | TER 5 LIQUID COOLING MICROCHANNEL OPTIMIZA-  |    |

| TIO    | N                                            | 0  |

| 5.1    | Introduction                                 | 0  |

| 5.2    | Related Works                                | 1  |

| 5.3    | Constant Inlet Volumetric Flow Rate 5        | 1  |

| 5.4   | Microchannel Optimization              | 54         |

|-------|----------------------------------------|------------|

| 5.5   | Experimental Results                   | 57         |

| 5.6   | Conclusion                             | 55         |

|       |                                        |            |

| СНАРТ | FER $6$ CONCLUSION AND FUTURE WORK $6$ | 57         |

| 6.1   | Significance of Work                   | <i>i</i> 7 |

| 6.2   | Potential Future Work                  | <b>i</b> 8 |

|       |                                        |            |

| REFER | RENCES                                 | 71         |

## LIST OF ABBREVIATIONS

2D IC Two-Dimensional Integrated Circuits

3D IC Three-Dimensional Integrated Circuits

CFD Computational Fluid Dynamics

FEM Finite Element Method

FVM Finite Volume Method

ILD Inter-Layer Dielectric

SA Simulated Annealing

SIMPLE Semi-Implicit-Method for Pressure-Linked-Equations

SOI Silicon-On-Insulator

TSV Through-Silicon Via

TTSV Thermal Through-Silicon Via

## NOMENCLATURE

| $\dot{V}$ | Volumetric flow rate                                | $[\mathrm{m}^3/\mathrm{s}]$ |

|-----------|-----------------------------------------------------|-----------------------------|

| ν         | Kinematic viscosity                                 | $[\mathrm{m}^2/\mathrm{s}]$ |

| $\rho$    | Density                                             | $[\mathrm{kg/m^3}]$         |

| A         | Cross-sectional area                                | $[\mu m^2]$                 |

| $A_{wet}$ | Wetted surface area                                 | $[\mu m^2]$                 |

| AR        | Aspect ratio                                        |                             |

| d         | Distance between objects                            | $[\mu m]$                   |

| $D_h$     | Hydraulic diameter                                  | $[\mu m]$                   |

| dz        | Section length                                      | $[\mu m]$                   |

| f         | Fanning friction factor                             |                             |

| $f_D$     | Darcy friction factor                               |                             |

| $f_i$     | Volume fraction of the layer $i$                    |                             |

| H         | Height                                              | $[\mu m]$                   |

| h         | Convection coefficient or heat transfer coefficient | $[\mathrm{W/m^2\text{-}K}]$ |

| $h_{avg}$ | Average heat transfer coefficient                   | $[\mathrm{W/m^2\text{-}K}]$ |

| I         | Electrical current                                  | [A]                         |

| k         | Thermal conductivity                                | [W/m-K]                     |

| $k_{eff}$    | Effective thermal conductivity       | $[\mathrm{W/m}\text{-}\mathrm{K}]$ |

|--------------|--------------------------------------|------------------------------------|

| L            | Length                               | $[\mu m]$                          |

| $L_{fd,h}$   | Hydrodynamic entrance length         | $[\mu m]$                          |

| $L_{fd,t}$   | Thermal entrance length              | $[\mu m]$                          |

| $L_{fin}$    | Thermal fin length                   | $[\mu m]$                          |

| N            | Number of sections                   |                                    |

| Nu           | Nusselt number                       |                                    |

| $Nu_z$       | Local Nusselt number in position $z$ |                                    |

| P            | Pressure                             | [Pa]                               |

| p            | Perimeter                            | $[\mu m]$                          |

| Pr           | Prantdl number                       |                                    |

| Q            | Heat flux                            | $[\mathrm{W/cm^2}]$                |

| Q            | Heat rate                            | [W]                                |

| R            | Electrical resistance                | $[\Omega]$                         |

| $R_{th,con}$ | ad Conductive thermal resistance     | [K/W]                              |

| $R_{th,con}$ | Convective thermal resistance        | [K/W]                              |

| $R_{th,eq}$  | Equivalent thermal resistance        | [K/W]                              |

| $R_{th}$     | Thermal resistance                   | [K/W]                              |

| Re           | Reynolds number                      |                                    |

| T            | Temperature                          | [K or $^{\circ}$ C]                |

| t            | Thickness                            | $[\mu m]$                          |

| $T_b$        | Bulk temperature                     | [K]                                |

| $T_w$        | Channel wall temperature             | [K]                                |

| u         | Velocity                        | [m/s]     |

|-----------|---------------------------------|-----------|

| V         | Electrical voltage              | [V]       |

| w         | Width                           | $[\mu m]$ |

| $w_{in}$  | Channel inlet width             | $[\mu m]$ |

| $w_{out}$ | Channel outlet width            | $[\mu m]$ |

| z         | Length-wise position in channel |           |

## CHAPTER 1

## INTRODUCTION

Moore's law has been the golden rule for the electronic industry for more than 50 years since 1965. It is the observation that the number of transistors in an integrated circuit (IC) doubles every 18 months to two years [1]. As semiconductor technology scales, highly integrated circuits face various bottlenecks in two-dimensional integrated circuits (2D IC) manufacturing technology and can no longer scale in accordance with Moore's law [2]. Limited by the nature of physics, the future of Moore's law is diminishing and numerous scientists and engineers have been developing technologies to prolong the trend or even achieve advanced improvement. Vertical, or three-dimensional (3D), integration is a promising manufacturing technology to realize denser packaging and increased performance with reduced interconnect lengths. However, the thermal challenge is exacerbated on 3D integration implementations due to the low thermally conductive adhesive layer between device tiers and denser packaging that causes an increase in power density, and thus might further result in malfunction.

## 1.1 Three-Dimensional Integrated Circuits

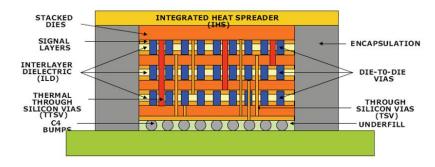

More than a decade ago, three-dimensional integrated circuits (3D ICs) were introduced as a promising breakthrough to overcome the physical bottleneck of denser packaging previously achieved from transistor miniaturization for "more than Moore" [3]. The 3D IC is realized by adding a third dimension to the two-dimensional devices. Two or more conventional 2D ICs are vertically stacked on one another (die-to-die, die-to-wafer, or wafer-to-wafer [4]) with electrically insulated bonding layer in between as shown in Figure 1.1. To complete the electric connections between the stacked device tiers, through-silicon vias (TSV) are inserted as routing. The structure resembles the struc-

ture of a multistory building, where each device layer is considered as a floor. It has become an attractive field of research to mitigate several problems. Stacked ICs reduce interconnect lengths mainly due to the usage of electronic TSVs. This leads to less wire delay and reduction in Joule heating. Not only can it achieve higher transistor densities and shorter interconnect lengths on a given footprint, but it is also a new paradigm for heterogeneous integration, such as central processing unit (CPU) and memory or digital and analog components on a single chip [5].

Figure 1.1: Three-dimensional integrated circuit diagram [6].

Recently, a 3D stacked memory chip was officially announced [7] and mass production is imminent [8]. However, 3D IC also comes with some problems as well as exacerbated issues. Inserting TSVs leads to the increase in footprint and decrease in chip reliability due to manufacturing difficulties and stress to the neighboring features. Moreover, higher active transistor count per cooling area and increased vertical thermal resistances in bonding layer due to multiple silicon-on-insulator (SOI) layers and inter-layer dielectrics (ILD) increases on-chip operating temperature. Thus, high-performance multi-processors or heterogeneous device integrations still face thermal bottlenecks due to high heat density.

Heat dissipation has been the most critical barrier to advancing core-tomemory or core-to-core stacking, which has higher power density compared to memory-to-memory stacking. Remaining unresolved, the thermal issue will act as a limiting factor on the number of device layers to be stacked, and in an extreme case, it can further result in malfunction even on two device layers.

## 1.2 Thermal Challenges and Designs

First, we evaluate the temperature variations of four-devices stacked IC from the international technology roadmap for semiconductors from 2002 [9]. Average temperature at each device layer from bottom to top is measured as 30 °C, 100 °C, 135 K and 150 K. We can observe how temperature rises as the device layer goes up, farther from the air cooled heat sink. Increased temperature will not guarantee the functionalities of the upper devices and will limit the number of device layers to be stacked. Efficient vertical heat dissipation paths are sorely needed to fully utilize the benefits of 3D IC.

To solve the thermal problems of the 3D IC structure, there have been many research works on different aspects of the design. We can divide the cooling methodology in two main scopes: 1) on-chip level and 2) package level [10]. On-chip thermal design on an actual device layer is necessary to reduce the elevated heat generation of localized regions with high power density, also known as hotspots, down to an operational range in close proximity. In package level cooling techniques, air cooling at the heat sink, liquid cooling with various geometry heat exchangers [11] are being studied.

#### 1.2.1 On-Chip Thermal Designs

Thermal-aware designs from the high-level system to the physical level implementations have been studied to alleviate the aggravated thermal issues while coping with existing chip designs. Dynamic thermal management techniques on 2D high-performance core designs or data centers include fetch throttling [12], task and thread scheduling [13], [14], [15], and dynamic voltage and frequency scaling [16]. These works can also be applied to 3D stacked designs to study the effect on the temperature profile. However, this approach often sacrifices performance to reduce the hotspots.

Contrary to the system-level techniques, physical design approaches have to consider a new factor for 3D IC packaging, the TSVs, which serve as electric connections through multiple device tiers [17]. Research works include thermal-aware placement for hotspot reduction [18], heat dissipation through TSV routing [19], thermal wires [20], dummy TSV insertion [21] and so on.

Previous research works on physical design approaches include the insertion of thermal TSV (TTSV) in reserved space depending on the density and

thermal dissipation effectiveness [22], heat pipe insertion to minimize the temperature gradient on the horizontal plane [23], thermal driven floorplanning [24] and placement [25]. TTSVs are electronically isolated from other components of the chip, which are inserted solely to act as vertical heat dissipating paths from each device layer to the heat sink. Numerous research works have planned to insert TTSVs on different physical design stages; these include partitioning [26], placement [22], floorplanning [27], routing [28], [20] and so on. From analytical studies to experimental results, the TSV manufacturing process is found to stress surrounding features on the chip; therefore the number of TSVs needs to be minimized for maximum process reliability. In our work, a new design of thermal vias with fin-like geometries is studied primarily for the usage in 3D ICs [29]. Our thermal-aware design structures are easily manufacturable, less stressful to neighboring devices and interconnects, more reliable and thermally effective. Furthermore, there is a high possibility to decrease the number of TTSVs inserted for similar or better heat dissipating effectiveness. The potential benefits of the design are higher yield, improved performance and commercialization of 3D IC devices.

#### 1.2.2 Package Thermal Designs

The aforementioned works are mostly based on conductive heat transfer resolved in solids within chips. Conductive thermal management designs in combination with conventional air cooling based heat sinks are often insufficient to keep the chip in operational and reliable range for high performance applications [30]. The heat flux upper limit with air cooling methods for most applications is around  $100\,\mathrm{W/cm^2}$ . The 3D multi-chip modules that dissipate more than  $300\,\mathrm{W/cm^2}$  at the die are beyond the capability of most conventional air cooling solutions [31]. Major heat transfer blockages in 3D IC, that create localized, trapped heat, or hotspots, result mainly from the bonding layer between the device stacks. The bonding layer is composed of very low thermally conductive ILD to isolate the unnecessary electric connections between device tiers. Hence, it is crucial to introduce additional cooling mechanism for thermally isolated device layers that are distant from the heat sinks.

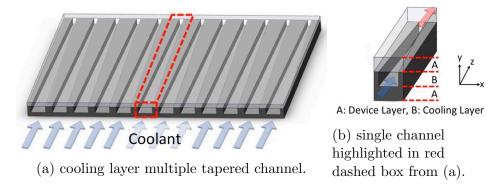

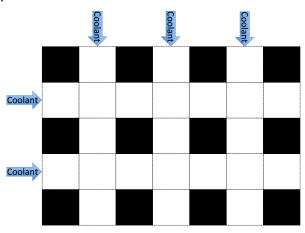

Due to the scale limitation of on-chip thermal solutions, package level

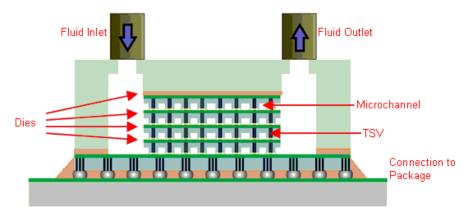

designs are considered to possess greater potential for 3D IC applications. Engineers have been exploring more effective ways of cooling by pumping liquid coolants directly onto the chips, rather than circulating air around them or using backside cold plating. The inter-tier liquid cooling micrometerscale channel, or microchannel, illustrated in Figure 1.2, layer has been gaining attention as an integrated cooling mechanism to tackle thermal degradation in 3D ICs [32], [33]. The use of liquid coolant, commonly water, has become an attractive option due to higher convective heat transfer coefficient compared to air cooling. The heat transfer coefficient of water  $h_{water} = 50-3000 \, \text{W/m}^2$ -K is higher than air  $h_{air} = 0.5-1000 \, \text{W/m}^2$ -K for natural convection, and becomes even more effective in forced convection,  $h_{water} = 50\text{-}10\,000\,\text{W/m}^2\text{-K}$  versus  $h_{air} = 10\text{-}1000\,\text{W/m}^2\text{-K}$ . A single-phase loop in the liquid cooling system consists of a miniaturized pump and heat exchanger (e.g. cold plate or microchannels). Conventional board-level liquid cooling heat exchangers are not suitable for chip-level implementations due to bulky modules. Therefore, there has been interest in compact microchannel heat exchangers that could directly be etched on the back of the silicon dies [34], [35].

The majority of the research on microchannel design optimizations is based on runtime expensive numerical simulations, oversimplified thermo-fluidic models or correlations with incorrect assumptions. Numerical models are typically unsuitable for optimization considering intensive computing. Ap-

Figure 1.2: Liquid-cooling microchannel scheme on 3D IC packaging [36].

proximate models or correlations with improper assumptions pose a fundamental limitation to accurately derive the relationships between the channel parameters and the thermal performance. Applying a fully developed flow model on a short channel that presents developing flow will cause large discrepancy. In microchannel optimization, inaccuracy on the base channel model will significantly affect the optimality and quality of the resulting design.

## 1.3 Dissertation Organization

The remainder of this dissertation is organized as follows.

Chapter 2 presents our proposed thermal design of thermal via-fin structure [29]. We study the design criteria for thermal fin to be effective in thermal performance and analyze the improvements for various designs. Thermal via cluster design with and without the insertion of thermal fin is studied and proves the potential of minimizing the area with this new design component.

In Chapter 3, we derive accurate thermo-fluid correlations of the microchannel to capture the relationship between the channel physical parameters and the thermal performance [37]. The correlations are based on developing flow model to properly establish the parametric study at the entrance region of the channel. In microchannel design optimization, the flow behavior at the entrance region will be prolonged when microchannel dimensions vary across the flow direction. Therefore, correlations based on developing flow model will serve as a solid foundation for finding the optimal microchannel design. Tapered channel was chosen for the design flexibility in the microchannel optimization. To verify the accuracy of our model, we have made comparison with commonly used fully developed flow-based correlations and reliable numerical simulation.

Chapter 4 applies the same technique to derive the thermo-fluid correlations of diverging shape microchannels. Then, we merge the correlations to fully analyze any linear-walled channels with single correlation for each thermal performance and cooling power consumption. The resulting correlations provide the foundation for the microchannel design optimization.

In Chapter 5, we perform microchannel geometric optimization based on the derived tapered channel models [38]. The microchannel is divided into small sections and optimized piecewise linearly at each section. An iterative simulated annealing optimization technique is applied for multi-section channels. Our model finds the channel inlet width and tapering angle to maximize the thermal performance subject to cooling energy and manufacturing constraints. This work determines the optimal tapering angle of the microchannel at each location.

Finally, we highlight the proposed works and summarize the impact in Chapter 6. Based on what we have observed, we propose potential future works. Thermo-fluid models can be improved in accuracy and flexibility by adding more design parameters and analyzing more complicated physical phenomena. In addition, microchannel design can be extended to non-straight channels, such as branching out in forks, merging multiple streams into single channel and so on. The multistream analysis will be helpful to design grid-like microchannel structures.

## CHAPTER 2

# THERMAL THROUGH-SILICON VIA WITH THERMAL FIN DESIGN

#### 2.1 Introduction

Greater than 50% of dynamic power consumption in current IC chips is contributed by interconnect networks; the lengths of which do not generally scale down with each technology node [39]. 3D IC, a novel packaging technology, is heavily studied to realize the improved performance with denser packaging and reduced wirelength. Despite numerous advantages, thermal management is the biggest bottleneck to realize the device-stacking technology.

In this chapter, we propose a thermal-aware physical design for 3D IC [29]. We aim to mitigate localized hotspots to ensure functionality by adding thermal fin geometry to existing thermal through-silicon via (TTSV). We analyze various ways to insert thermal fin for single TTSV as well as TTSV cluster designs with the goal of maximizing heat dissipation while minimizing the interference with routing and area consumption. A global analysis of a 3D system is developed and a thermal resistance circuit is built for an accurate and runtime-efficient thermal analysis of a complete 3D IC.

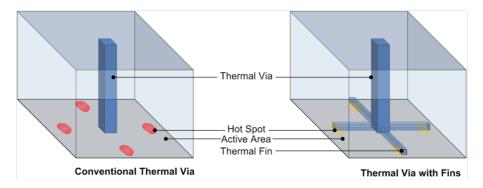

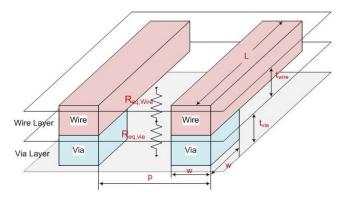

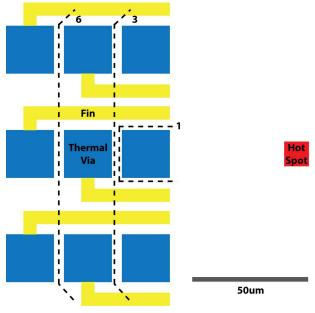

We design thermal vias with laterally elongated fins in the device layer to minimize the maximum temperature of the chip as in Figure 2.1 and also decrease the number of TTSVs to improve the reliability. This structure not only eases the manufacturing but also simplifies the routing strategies. In addition, we use the advantage of reserved space for the TTSV cluster region placed in close proximity to hotspots to insert fins. Finite element method (FEM) simulations and analytical models are shown to verify the presented geometries.

Figure 2.1: 3D view of thermal via-fin structure.

## 2.2 Analytical Model

#### 2.2.1 Thermal Fin Geometry

To successfully dissipate heat from hotspots on a chip to guarantee the proper functionality, bundles of TTSVs are typically deployed. In our design, we will take advantage of the space between TTSVs inside the TTSV cluster region to insert additional thermally conductive fin geometry extending from interior TTSVs to the boundary. By utilizing the space in between the TTSVs, no extra space is consumed. The fins can be placed in the whitespace between the TTSVs in close proximity to the hotspots which construct heat dissipating paths to maximize their effectiveness. In addition, they do not penetrate the ILD layer, where the metal interconnects lie, hence the adverse effects to the interconnect routing are minimal.

Heat flux to TTSV is inversely proportional to the distance from hotspots. Moreover, within the via cluster, TTSVs closer to the hotspot might act as lateral heat blockage to further TTSVs [40]. Thermal fin structure enables TTSVs outside the efficient heat dissipation region to be more effective as heat conduits.

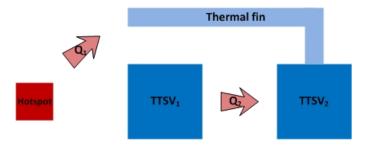

However, there is a requirement for the fin structures to be more effective in heat transfer than conventional structure without fins. Figure 2.2 illustrates simple top view of two TTSVs and a single thermal fin extending towards the hotspot from further TTSV, labeled  $TTSV_2$ . There can be two major heat dissipation paths through  $TTSV_2$  from the hotspot, heat flux through

thermal fin denoted as  $Q_1$ " and the other path through  $TTSV_1$  to  $TTSV_2$  represented as  $Q_2$ ". The heat flux  $Q_1$ " has to be greater than  $Q_2$ " in order for the thermal fin to be more effective than the TTSV without fin structure.

Figure 2.2: TTSV and thermal fin with two heat paths (top view).

From Figure 2.2, we set three assumptions for simplicity:

- Length of the thermal fin can be assumed as  $L_{fin} \approx \frac{3}{2}w_{via} + d_{via}$ , where  $w_{via}$  is the width of the thermal via (TTSV) and  $d_{via}$  is the distance between the vias.

- Minimum pitch between the fin and nearest TTSV is assumed to be the same as TTSV pitch,  $d_p \approx d_{via}$

- Temperature is horizontally isothermal in two-dimensional TTSV plane; temperature difference in the horizontal surface area is not considered in the resistive model.

Integrating the assumptions listed above, we can find the appropriate condition for the thermal fin to be effective for heat dissipation using the terms specified in the Table 2.1.

Table 2.1: Symbols in the Analytical Model

| Symbols          | Description                                                               |

|------------------|---------------------------------------------------------------------------|

| $\overline{A_i}$ | cross-sectional area of structure (i.e. via, fin, hotspot)                |

| $k_{i}$          | thermal conductivity of the material (i.e. ILD, copper)                   |

| $w_i$            | width of the geometry                                                     |

| $t_{i}$          | thickness of the geometry                                                 |

| $d_{i}$          | distance between any neighboring structures (i.e. via-to-via, fin-to-via) |

As a result, the cross-sectional area necessary for the fin to be an effective thermal conduit is derived as below,

Theorem: Cross-sectional area  $A_{fin}$  of the effective thermal fin should be,

$$A_{fin} > \frac{A_{via}A_{HS}(k_{ILD}(L_{fin} + d_{via}) + k_{cu}\sqrt{d_{HS}^2 + d_{via}^2})}{k_{cu}(d_{via}A_{HS} + d_{HS}A_{via})}$$

$$A_i = w_i t_i \qquad for \ i=fin, \ via, \ hotspot(HS)$$

$$(2.1)$$

#### 2.2.2 Heat Transfer Model of ILD

Thermal management is key to the success of a given multi-chip design. Our proposed thermal-aware structural design is based on the assumption that additional TTSVs are inserted to prevent thermal exacerbation. For comprehensive understanding of the design, a modified analytical heat transfer model of the design is necessary. Heat is dissipated mainly through a high thermally conductive substrate in 2D IC design, which is vertical direction (one-directional heat flow); however, in 3D IC, active layers are embedded in the ILD regions [41] such that the ILD thermal resistance should be considered as well. Low-k materials are widely adopted as new ILDs, and this porous material has an even lower thermal conductivity than silicon dioxide, SiO<sub>2</sub>. Im et al. [42] listed the thermal conductivity of ILD  $k_{ILD} = 0.3 \,\mathrm{W/m}$ -K. As Figure 2.3 shows, by assuming metal wire with width w and length L, aligned with each other with the pitch p, the volume fraction of the wire  $f_{wire}$  will be  $f_{wire} \approx w/p$  and the volume fraction of the via  $f_{via}$  will be  $f_{via} = f_{wire} * w/L$ . The effective thermal conductivity will be  $k_{i,eff} = f_i k_m + (1 - f_i) k_{ILD}$ , where  $f_i$  will be either  $f_{via}$  or  $f_{wire}$  on each layer i, and  $k_m$  is the thermal conductivity of the interconnect metal, which is usually  $k_{cu} = 401 \,\mathrm{W/m\text{-}K}$  for copper, Cu. The equivalent thermal resistance  $R_{th,eq}$  will be

$$R_{th,eq,ILD} = R_{th,eq,via} + R_{th,eq,wire}$$

$$= \sum \frac{t_{via}}{k_{i,eff,via}} + \sum \frac{t_{wire}}{k_{i,eff,wire}}$$

(2.2)

Figure 2.3: TSV and wire layers with the lumped thermal resistance model.

#### 2.2.3 3D Thermal Resistance Circuits

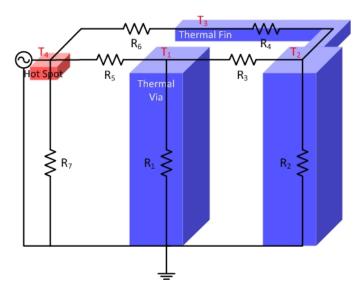

There are some similarities between the electric circuit model and heat transfer equations [43]. Hotspot where heat is generated is modeled as the current source and the thermal resistance is similar to the electric resistance. Temperature on each position is analogous to the voltage and ambient temperature is represented as ground in the circuit (sometimes, it can also be represented as the DC voltage source). We developed an analytical 3D resistive network heat transfer model as shown in Figure 2.4, to be able to simulate our proposed design as well as conventional TTSV structures. Our thermal design has lateral structures on each device tier and 3D heat flow should be considered in the model; 2D heat flow is analyzed on the horizontal device plane. The 3D analytical model will provide more accurate understanding compared to the previous analytical models which only consider one-dimensional heat flow on the device plane [44]. Furthermore, the simulation can be extended to larger benchmark applications with reduced runtime as compared to the commercially available FEM tools or commonly used finite difference method.

Similar to Section 2.2.2, each thermal resistance between the nodes (geometries) of the circuit is expressed with the dimension parameters, characteristics of the structure,  $R_{th} = t/(kA)$ , where t is the thickness, k is the thermal conductivity and A is the cross-sectional area of the structure.

Figure 2.4: Three-dimensional thermal resistance model for TTSV-Fin structure.

$$R_{th,1} = R_{th,2} = \frac{t_{via}}{k_{cu}w_{via}^{2}}$$

$$R_{th,3} = \frac{d_{via}}{k_{ILD}w_{via}t_{via}}$$

$$R_{th,4} = \frac{L_{fin} + d_{p}}{k_{cu}w_{fin}t_{fin}}$$

$$R_{th,5} = \frac{d_{HS}}{k_{ILD}w_{HS}t_{HS}}$$

$$R_{th,6} = \frac{\sqrt{d_{HS}^{2} + d_{p}^{2}}}{k_{ILD}w_{fin}t_{fin}}$$

$$R_{th,7} = \frac{t_{via} - t_{HS}}{k_{ILD}w_{HS}^{2}}$$

(2.3)

In the resistive model, heat generating sources are modeled as current sources and temperature is analogous to the voltage at each node of the circuit. Thermal resistances are expressed as regular resistors and heat transfer in Equation (2.4),  $R_{th} = \Delta T/Q$  is expressed similarly to Ohm's law, R = V/I. Setting the resistance equations of the given circuit is done based on Kirchhoff's current law. Note that Q is heat rate, which equals to the product of the heat flux and the area, Q = Q" A.

$$R_{th}Q = \Delta T \tag{2.4}$$

$$\frac{T_4 - T_1}{R_{th,5}} - \frac{T_1 - T_2}{R_{th,3}} - \frac{T_1}{R_{th,1}} = 0$$

$$\frac{T_1 - T_2}{R_{th,3}} + \frac{T_3 - T_2}{R_{th,4}} - \frac{T_2}{R_{th,2}} = 0$$

$$\frac{T_4 - T_3}{R_{th,6}} - \frac{T_3 - T_2}{R_{th,4}} = 0$$

$$Q - \frac{T_4 - T_3}{R_{th,6}} - \frac{T_4 - T_1}{R_{th,5}} - \frac{T_4}{R_{th,7}} = 0$$

(2.5)

Table 2.2 lists the parameter values that can be applied into this TTSV and fin structure. These parameters also fulfill the requirement for the effective thermal fin in Equation (2.1).

Table 2.2: TTSV, Thermal Fin Structure Parameters

| Parameters | Values                     | Parameters | Values                     |

|------------|----------------------------|------------|----------------------------|

| $t_{fin}$  | 5 µm                       | $t_{HS}$   | $2\mu\mathrm{m}$           |

| $w_{fin}$  | $5\mathrm{\mu m}$          | $w_{HS}$   | $10\mu\mathrm{m}$          |

| $t_{via}$  | $100\mathrm{\mu m}$        | $d_{via}$  | $5\mu\mathrm{m}$           |

| $w_{via}$  | $20\mu\mathrm{m}$          | $d_{HS}$   | $50\mu\mathrm{m}$          |

| $k_{ILD}$  | $1.4\mathrm{W/m}\text{-K}$ | $k_{cu}$   | $401\mathrm{W/m}\text{-K}$ |

## 2.3 Experimental Results

#### 2.3.1 2D Simulation

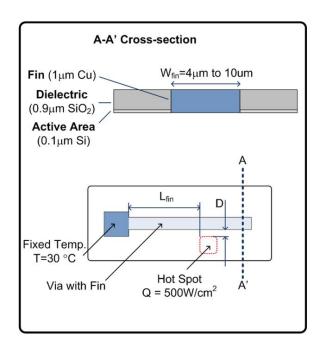

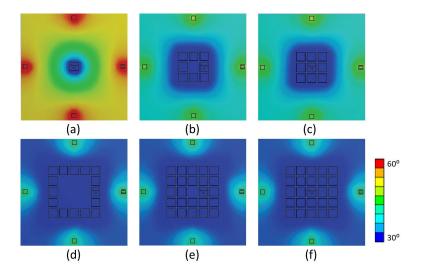

Steady-state thermal FEM simulations using ANSYS Workbench are used to verify the analytical results. The first set of the simulations model is the 2D heat spreading through the active region with a thin-film silicon layer (0.1  $\mu$ m thickness) on top of a silicon dioxide layer (0.9  $\mu$ m thickness), a copper via with fin (1  $\mu$ m thickness), as shown in Figure 2.5. The copper via is fixed

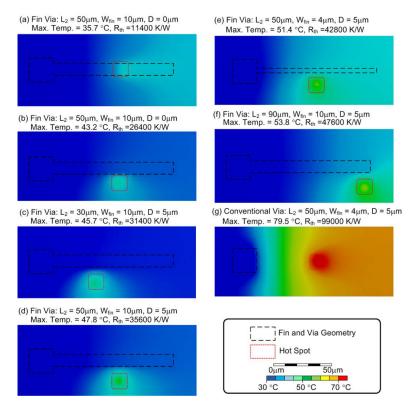

at a temperature of 30 °C, a 100  $\mu$ m² hotspot with a heat flux of 500 W/cm² is placed in the thin-film silicon region, and all other surfaces are adiabatic. The temperature distribution of the 2D model is shown in Figure 2.6. FEM results confirm that thermal fins reduce the maximum temperature of the hotspot (Figure 2.6-a  $\sim$  2.6-f), as compared to the geometry without a thermal fin (Figure 2.6-g). As predicted, hotspot placement is crucial; ideally, the hotspot should be adjacent to the fin, and the effective fin length should be less than 50  $\mu$ m. A wider fin width (10  $\mu$ m in Figure 2.6-d vs. 4  $\mu$ m in Figure 2.6-e) is more effective, but comes at a tradeoff of additional chip area.

Figure 2.5: Two-dimensional simulation model.

#### 2.3.2 3D Simulation on Thermal Via Cluster

One study has shown that TTSVs can also act as lateral heat blockage to the vias further from the hotspot [40]. For heat to be dissipated from the hotspot, the distance between TTSV and the hotspot affects the amount of total heat dissipation. In 3D simulation, the locations of the hotspot for all models were fixed but we varied the number of TTSVs in the cluster

Figure 2.6: Two-dimensional simulation of TTSV and fin.

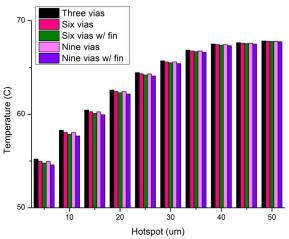

for the difference in the distance between the closest via and the hotspot. In addition, the largest area via cluster example is compared with full via insertion and selective elimination of inner TTSVs. The simulation result shows that overall reduction in maximum temperature depends heavily on the distance and the number of vias inserted (which also can be interpreted as the size of the cluster). Furthermore, although more vias are inserted inside the cluster, inner TTSVs are not as effective as the closer vias on the boundary of the thermal via cluster. The simulation results are shown in Figure 2.7 and Table 2.3.

#### 2.3.3 Fin Stretched Inside TSV Cluster

From the analytical studies, the dimension of the fin is a key parameter in heat dissipation efficiency. Both width and depth of the fin structure will affect the performance, but in this work, we will fix the depth of the fin

Figure 2.7: FEM simulation on different number of TTSVs (minimum distance to the hotspot:  $50\,\mu\text{m}$ , TTSV width:  $20\,\mu\text{m}$ , hotspot width:  $10\,\mu\text{m}$ ) (a) Single TTSV, (b) 8 TTSVs, (c) 9 TTSVs, (d) 16 TTSVs, (e) 24 TTSVs, (f) 25 TTSVs.

Table 2.3: Simulation Result of TTSV Cluster Model

| # of TTSVs                    | 1     | 8     | 9     | 16    | 24    | 25    |

|-------------------------------|-------|-------|-------|-------|-------|-------|

| $T_{max}[^{\circ}\mathrm{C}]$ | 59.61 | 46.95 | 47.24 | 41.85 | 41.44 | 42.11 |

| Improvement [%]               | Ref.  | 42.76 | 41.77 | 59.98 | 61.36 | 59.10 |

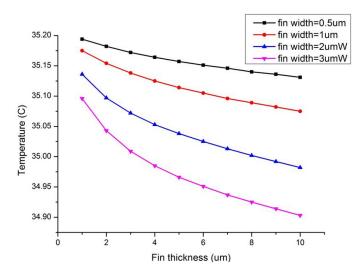

and mainly focus on the width variance. There will be a trade-off with the area consumption on the device surface and the enhanced heat dissipation from the fin width widening. To optimize for both fin width and thermal performance, Figure 2.8 shows the simulation result of four via clusters with the fin extended from further vias varying in width from 0.5 µm to 3 µm. The other parameters for the structures are  $w_{via} = 10 \,\mu\text{m}, \ d_{via} = 20 \,\mu\text{m}, \ A_{HS} = 300 \,\mu\text{m}^2, \ d_{HS} = 5 \,\mu\text{m}.$

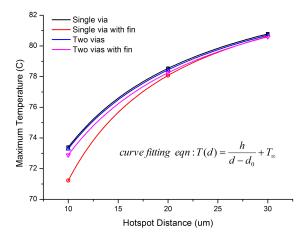

The effect of the fin structure is simulated on the simplest model under the conditions described in previous sections. Figure 2.9 shows the comparison between single via and two vias structures and with or without the fin structure by varying the distance of the hotspot. In the single via case,

Figure 2.8: Simulation results of thermal fin width variation.

the distance between the hotspot and the TTSV via was reduced by adding the fin structure stretching toward the hotspot. However, for multiple vias, the fin was extended until it meets the boundary of the TTSV cluster. In Figure 2.9, we have fitted the curve for the data points we have collected. Based on Fourier's law,  $\Delta T = T_{HS} - T_{via} = Qd/(kA)$ , k and Q are constant values but area A is the function of the distance d as the heat diffusion path is no longer linear as the distance increases. For simplicity, assume that A is a second-order polynomial function of d. Hence, the temperature was inversely proportional to the distance and the coefficient and intercept values were obtained accordingly.

The fin structure helps to construct an efficient heat dissipation path toward the hotspot from farther TTSVs. By inserting fin structures, the heat flowing through the fin path can exceed the heat flux through the closer via. Figure 2.10 illustrates the comparison between three, six and nine vias with and without fin structure from a 3 x 3 square via cluster. Three vias are the closest column of the cluster, six vias are two closer columns and nine vias are the whole via cluster. We can observe from the simulation result that the temperature difference between six and nine vias is almost negligible compared to three vias. The result can be interpreted to mean that the last farthest column was not contributing at all. To efficiently utilize the last col-

Figure 2.9: FEM simulations on single TTSV, two TTSVs with and without fin.

umn, thermal fins are inserted. There is approximately 2.5% improvement in temperature distribution for the  $5\,\mu m$  away hotspot with  $w_{fin}=1\,\mu m$ ,  $t_{fin}=2\,\mu m$ ,  $A_{HS}=900\,\mu m^2$ , and  $w_{via}=10\,\mu m$ . We can also observe that six vias with fin is lower in temperature compared to the nine vias without the fin. This result shows the potential in decreasing the number of TTSVs inserted for similar or even better thermal performance. It allows less area consumption as well as lower stress to the neighboring devices. However, the effect is diminished as the hotspot is farther away. We can conclude that with the fins inserted inside the cluster, the effect is maximized as the cluster is closer to the hotspot. Table 2.4 shows the maximum temperature values and the percentage improvement of each structure with respect to single via structure.

Table 2.4: Simulation Result of TTSV and Thermal Fin Cluster Model

| # of TTSV+Fin                 |        | 3      | 6      | 6+Fin  | 9      | 9+Fin  |

|-------------------------------|--------|--------|--------|--------|--------|--------|

| $T_{max}[^{\circ}\mathrm{C}]$ | 58.985 | 55.218 | 54.961 | 54.776 | 54.951 | 54.587 |

| Improvement [%]               | Ref.   | 12.996 | 13.883 | 14.521 | 13.917 | 15.173 |

(a) Nine TTSV-thermal fin model (red: hotspot, blue: TTSV, yellow: thermal fin).

(b) Simulation results of TTSV cluster model with hotspot distance variation.

Figure 2.10: TTSV cluster model and simulation results.

#### 2.4 Conclusion

Analytical and FEM models show that a conventional TTSV design is effective only when the hotspot is near the TTSV. A via with fin-like geometries adds flexibility to the design such that hotspots farther away from the TTSV can be cooled effectively without additional fabrication or routing constraints.

This work presents a new design of TTSV with fin-like geometries to enhance cooling in 3D ICs. Fin-like geometries reduce the number of TTSVs needed for 3D IC cooling, which relaxes the fabrication and routing constraints on the design. The distance of the hotspot from the fin was found to play a crucial role in the combined equivalent thermal resistance. The usage of fins is recommended if the hotspot can be reached from the via in less than 10 µm. Otherwise, additional complexity in manufacturing processes and stricter routing constraints due to the extra fins will outweigh the small efficiency gains. New structures and designs of TTSVs to reduce the thermal management issues in 3D ICs were found to merit further exploration.

## CHAPTER 3

# ACCURATE MODELS FOR TAPERED MICROCHANNEL HEAT SINKS

#### 3.1 Introduction

The majority of existing thermal-aware designs on 3D ICs are based on conductive heat transfer resolved in solids within a chip. Conductive thermal management designs only in combination with conventional air cooling based heat sinks are often insufficient to keep the chip in operational and reliable temperature range for high-performance applications [30]. The upper limit of the heat flux with air cooling methods for most applications is around  $Q'' = 100 \,\mathrm{W/cm^2}$ . 3D multi-chip modules that dissipate more than  $Q'' = 300 \,\mathrm{W/cm^2}$  at the die are beyond the capability of most conventional air cooling solutions [31]. In addition to the fact that heat sink is attached to only one of the device layers, major heat transfer blockages in 3D IC that create localized, trapped heat, or hotspots, result mainly from the bonding layer between the device stacks. Bonding layer is composed with very low thermally conductive ILD to isolate the unnecessary electric connections between device tiers. Hence, it is crucial to introduce an additional cooling mechanism for thermally isolated device layers that are distant from the heat sinks.

Packaging level designs can introduce larger scale solutions for effective performance. The use of liquid coolant has become an attractive option due to higher convective heat transfer coefficient compared to the traditional air cooling method. By pumping the liquid coolant directly onto the chips, we can achieve a higher heat transfer rate. Compact microchannel heat exchangers that could directly be etched on the back of the silicon dies [34], [35] are studied which also have the benefit of being placed between the device layers. Hence, the inter-tier liquid cooling microchannel layer has been gaining attention as an integrated cooling mechanism to tackle thermal

degradation in 3D ICs [32], [33].

Pumping power is the cost to pay for effective microchannels, often resulting in prohibitive expense. Designing microchannel with a well-balanced trade-off between thermal performance and the cooling power is important. Flow conditions as well as channel design will dominantly define the performance. To reduce the complexity and achieve more accurate relationship, we focus on channel design and leave the fluid condition in the future extension.

Traditional approaches to novel microchannel designs are usually inherited from the intuition of the engineer and verified through numerical simulations or empirical data. Then, some of the earlier optimization works were proposed, but they are either based on numerical simulations or oversimplified thermo-fluidic models. Numerical models are typically unsuitable for optimization considering intensive computing and long runtime. Approximate models or compact correlations used in the optimization are often based on improper assumptions and pose a fundamental limitation to accurately derive the relationships between the channel parameters and the thermal performance. For example, many of the previous works claim that fully developed flow models within microchannel have good agreement with the numerical solution and the corresponding experimental data [45]. However, applying a fully developed flow model to analyze short or arbitrary channels that presents developing flow characteristics will cause large discrepancy. Inaccuracy on the base channel model will significantly affect the optimality and quality of the resulting microchannel design.

In this chapter, we derive thermo-fluid correlations of the microchannel to accurately capture the relationship between the channel physical parameters and the thermo-fluid performance [37]. Thermal correlations are based on developing flow model to properly establish the parametric study at the entrance region of the channel as well as varying channel shapes. In the microchannel, the flow behavior at the entrance region will be prolonged when microchannel dimensions vary across the flow direction. Therefore, correlation based on developing flow model will serve as a solid foundation for finding the optimal microchannel design. Assuming the channel is symmetrical in length-wise axis, arbitrary shapes can be considered as piecewise linear channel; therefore, a tapered channel was chosen in our model. It provides more flexibility and accuracy than a rectangular channel with constant width. To verify the accuracy of our models, we have compared them with

commonly used fully developed flow based correlations and reliable numerical simulation.

## 3.2 Related Works

The concept of liquid cooling microchannel integrated to electronics was introduced by Tuckerman and Pease [11]. Kishimoto and Ohsaki [46] numerically simulated non-monotonic relationship of thermal resistance and channel width. They also fabricated board level via hole channels and tested the cooling performance. Working with popular 28-nanometer field-programmable gate array devices made by Altera Corporation, Sarvey et al. have demonstrated a monolithically cooled chip using microfluidic passages that could operate at temperatures more than 60 percent below those of similar air cooled chips with heat sink or cooling fans [47].

From the early 1990s until now, numerous studies on the heat transfer performance of various channel geometries have been of great interest. Hoopman [48] and Peng and Peterson [49] studied the influence of the geometry on heat transfer performance of rectangular microchannels and optimal geometry design under fixed height and total cross-section area. Harley and Bau [50] and Qu et al. [51] studied heat transfer of micrometer-scale rectangular and trapezoidal channels in silicon wafers. Rahman [52] investigated heat transfer performance of parallel and serpentine microchannels in silicon wafers. Lee et al. [53] studied heat transfer of various channel widths with constant aspect ratio and Foli et al. [54] explored optimal cross-section geometry based on constant cross-section area. Kuo et al. [55] assessed the effect of channel geometry on heat transfer for fully developed flow and found the optimal channel width decreased with increasing pumping power. Most of the designs studied and analyzed even with very unique and complicated cross-sectional shapes had a uniform shape and area along the fluid flow direction.

One of the challenges in single-phase liquid cooling is the increased thermal gradient due to absorbed sensible heat which leads to performance degradation. To achieve more uniform heat distribution, Sabry et al. [56] proposed to alter the channel width along the traveling direction of the fluid. Channel design in Sabry's work [56], [57] has a relatively wider inlet based on

fixed incoming coolant temperature and narrower outlet due to increased temperature from absorbed heat. This work assumes a piecewise constant channel and is based on rectangular channel approximate model for fully developed flow. All channels at the inlet start with the developing flow and there is a distinct difference in velocity and thermal profiles between developing and fully developed regions. Thus, applying a fully developed flow model to analyze a developing region is fundamentally incorrect. Especially for non-uniform channels, flow will be more perturbed and fluctuated, and likely to remain developing both hydrodynamically and thermally. Although it is reasonable to conclude that the tapered channel geometry contributes to thermal gradient reduction, it is uncertain whether the design is optimal when the microchannel design is optimized based on a fully developed flow model.

Hung and Yan [58] studied similar tapered channel but using finite volume based numerical analysis. The results provide insight into the performance with parameter variation. However, numerical approach is very compute-intensive and inappropriate for further optimization. Moreover, this model is based on a single-sided heat source, which is inapplicable for inter-tier cooling stacked between device layers in 3D IC. Thus, it is crucial to establish a compact model for fast microchannel design optimization that incorporates 3D IC applications.

In this work, we propose a compact and accurate closed-form model of the tapered channel for microchannel design optimization. The presented model is of fundamental importance in channel design study and can improve the accuracy with proper flow assumption and computation speed compared to the numerical approach in optimizing the design of various microchannels.

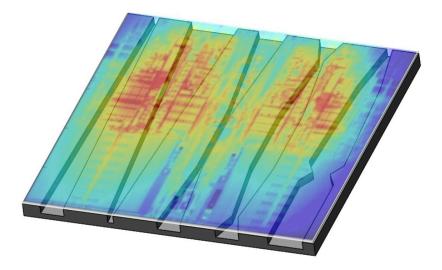

# 3.3 Fundamentals of Heat Transfer

Three-dimensional chips are composed of multiple vertically stacked device layers. To effectively dissipate heat from the device layers further to air cooled heat sinks, liquid cooling microchannel layers are fabricated in between the tiers. Figure 3.1 depicts a 3D view of two device tiers with a single microchannel layer.

In this section, we start by introducing the parameters of the tapered mi-

Figure 3.1: 3D stacked device layers with inter-tier liquid cooling microchannel layer. Tapered channels are etched at the bottom of the device layer. Top device layer is presented transparent for clear cooling layer illustration. Note that figure is not to scale.

crochannel dimensions, followed by the metric used to determine the thermal efficiency of liquid cooling heat exchangers. Then, appropriate heat transfer models for tapered microchannel design and analysis are proposed and further improved with parameter fitting.

# 3.3.1 Microchannel Geometry

In heat and mass transfer community, various channel geometries, such as circular, triangular, rectangular, trapezoidal, and wavy channels, are modeled and simulated for the past few decades. Considering practical manufacturing simplicity and the cost, rectangular cross-sectional microchannel has been applied in electronic design implementations. To provide a solid base model of the channel geometry, a straight channel is considered in this work rather than a channel that bends or branches out. Applying a single channel model to multiple channels will be a straightforward expansion. Moreover, complicated structures such as grid, mesh or tree can be developed upon the base channel model but are outside the scope of this work.

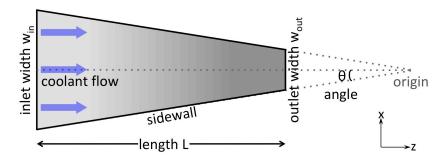

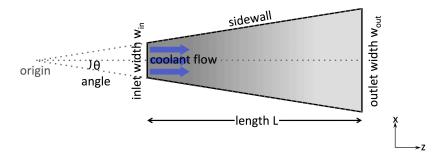

An increased thermal gradient across a chip has been the rising challenge in liquid cooling designs. Tapering channel with a large inlet and a small outlet has been proposed to reduce the temperature gradient [56]. The top view of the tapered rectangular channel is portrayed in Figure 3.2.

Figure 3.2: Tapered channel with inlet width  $w_{in}$ , outlet width  $w_{out}$ , length L, and half angle  $\theta$  (top view).

Given the channel inlet width  $w_{in}$ , outlet width  $w_{out}$  and length L, the channel angle  $\theta$  will be expressed as Equation (4.1). Opposed to a tapered channel, a channel with a uniform cross-section from inlet to outlet is denoted as uniform channel in the remaining of the work.

$$\theta = \arctan\left(\frac{w_{in} - w_{out}}{2L}\right) \tag{3.1}$$

Sabry et al. [56] have proposed design-time technique to optimize channel width at a given location to minimize the thermal gradient using channel width modulation. Given uniform heat flux across the chip, the optimized channel design has nearly a linear-tapered rectangular channel. The top view of a single channel is a rough trapezoid.

#### 3.3.2 Thermal Resistance

Within the microchannel cooling systems, conduction and convection are primary modes of heat transfer. To evaluate the thermal effectiveness of the design, thermal resistance is considered. Objectives for most of the thermal optimization are based on the temperature. However, there hardly exists an analytical closed-form model of temperature for a given design. To replace the metric, we focus on the temperature gradient instead of the temperature. Overall temperature drop  $\Delta T$  is the product of thermal resistance  $R_{th}$  and heat rate Q,  $\Delta T = QR_{th}$ . The compact closed-form relationship makes temperature gradient a good design metric. Total thermal resistance  $R_{th}$  is

the summation of resistance from conductive  $R_{th,cond}$  and convective  $R_{th,conv}$  heat transfer as Equation (3.2), and each term is dependent on the material property, physical dimensions as well as the hydrodynamic conditions in the fluid region. Heat transfers to all directions but more heat flows where there is higher temperature drop. In device layers, heat will mainly dissipate from hotspots to the inter-tier microchannel layer, y-axis direction. Equivalent thermal circuit will consist of pairs of series vertical conductive resistance and horizontal convective resistance connected in parallel along the channel length. Note that each thermal resistance is two-dimensional, but the overall thermal circuit becomes three-dimensional.

$$R_{th} = R_{th,cond} + R_{th,conv} = \frac{d}{kA_c} + \frac{1}{hA}$$

(3.2)

In IC design, we formulate the conductive resistance only in solid: silicon device layers and walls surrounding the microchannels where the majority of the conduction occurs. Conductive thermal resistance is defined by distance d, thermal conductivity k and the cross-sectional area in solid A. Convective thermal resistance is defined in the liquid region: microchannel layer. Convective thermal resistance is inversely proportional to the product of the convective coefficient h and wetted area  $A_{wet}$ . Overall  $R_{th,conv}$  can be considered as parallel connections of each local cross-sectional convective thermal resistance  $R_{th,conv,i}$  at location i as in Equation (3.3). In a tapered channel, both h and  $A_{wet}$  vary across the channel length and local values are represented as  $h_i$  and  $A_{wet,i}$  respectively. For each section,  $A_{wet,i}$  is computed with local perimeter  $p_i$  and the length segment dz. In a lumped model, average convective coefficient  $h_{avg}$  is the mean of the local convective coefficient  $h_i$ as in Equation (3.4). The total wetted area  $A_{wet}$  is the product of wetted perimeter  $p_{wet}$  and the channel length L. For each section, local perimeter is computed with local channel width  $w_i$ , channel height H and the length segment dz.

$$R_{th,conv} = \left(\int_{i} \frac{1}{R_{th,conv,i}}\right)^{-1} = \frac{1}{\sum_{i} h_{i} A_{wet,i}} = \frac{1}{\sum_{i} h_{i} p_{wet,i} dz}$$

(3.3)

$$h_{avg} = \frac{1}{L} \sum_{i} h_i dz \tag{3.4}$$

$$A_{wet} = P_{wet}L = \sum_{i} 2(w_i + H)dz \tag{3.5}$$

#### 3.3.3 Convective Heat Transfer

Heat dissipated in liquid cooling microchannels is based on forced convection. Convective heat transfer coefficient h, one of the factors to determine  $R_{th,conv}$ , depends on numerous parameters, such as coolant properties, fluid velocity, and channel dimensions, and yet there does not exist any closed-form analytical model. Thus we rely on the empirical or numerical correlations. Similar to the overall thermal resistance, temperature difference is computed by the product of the heat rate Q and the convective thermal resistance  $R_{th,conv}$ . Using this relationship, we can derive h as in Equation (3.6),

$$h = \frac{1}{R_{th,conv} * A_{wet}} = \frac{Q}{(T_w - T_b) * A_{wet}} = \frac{Q''}{T_w - T_b}$$

(3.6)

where Q" is the heat flux,  $T_w$  is the channel wall temperature and  $T_b$  is the bulk fluid temperature.

The efficiency ratio of the convection to conduction in fluid is defined as Nusselt number,  $Nu = hD_h/k$ , where k is the thermal conductivity and  $D_h$  is the hydraulic diameter. Non-circular channels are often formulated into circular-shaped channels using hydraulic diameter and computed using equation  $D_h = 4A/P_{wet}$ . The Nusselt number is used to compare the values from correlations with numerical results. Here, h is derived from exising empirical and numerical Nusselt number correlations on various case studies using the Equation (3.7).

$$h = \frac{Nuk}{D_h} \tag{3.7}$$

Shah and London [59] have studied Nusselt number approximate model on various channel geometries. Six-digit accuracy polynomial approximate model on rectangular channel in terms of aspect ratio, AR, for fully developed flow is shown in Equation (3.8). This model is valid when is  $AR \leq 1$ , hence AR is computed by height to width or width to height interchangeably.

$$Nu = 8.235(1 - 2.0421AR + 3.0853AR^{2} - 2.4765AR^{3} + 1.0578AR^{4} - 0.1861AR^{5})$$

(3.8)

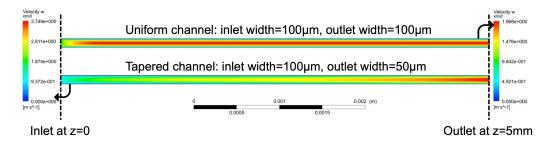

Many recent works on microchannel design and optimization have adopted this approximate model [56], [60]. However, depending on the flow assumption and the channel geometry, this model in Equation (3.8) cannot fully capture the phenomenon and becomes inapplicable for accurate optimizations. This model is based on rectangular channel with fully developed flow. Based on commonly used microchannel dimensions in circuits, fully developed flow is reached in multiple folds (e.g. 5x-30x) in rectangular channel and non-negligible portion preserves developing flow toward the entrance region. Fully developed region is defined where flow velocity profile and normalized temperature gradient profile remain unchanged along the flow direction. In a uniform channel, fully developed hydrodynamic flow will be reached after length  $L_{fd,h} \approx 0.05 Re * D_h$  and fully developed thermal flow will be reached after length  $L_{fd,t} \approx 0.05 Re * Pr * D_h$  for laminar flow (Re < 2300), where Re is Reynolds number and Pr is Prandtl number. For example, a uniform rectangular channel of width  $w = 100 \,\mu\text{m}$ , height  $H = 100 \,\mu\text{m}$ , inlet flow velocity  $u = 1 \,\mathrm{m/s}$  with water at 300 K as coolant, hydrodynamic and thermal entrance lengths will be  $L_{fd,h}=560\,\mu\mathrm{m}$  and  $L_{fd,t}=3300\,\mu\mathrm{m}$  respectively.

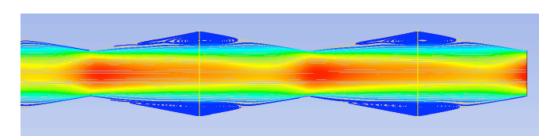

However, in a tapered channel, normalized velocity profile continuously changes in the flow direction based on mass conservation law and therefore, fully developed flow will not be reached. Figure 3.3 shows the velocity profile comparison between uniform channel and tapered channel. In addition, piecewise channel optimization will vary the channel dimensions at each segmented section. The fluid dynamics and heat transfer in channel with varying cross-sectional shape differ from those in the uniform channel as the flow cannot reach the developed condition. Non-constant channel geometry will contribute to flow alterations and extend the length to reach the fully developed flow.

The local Nusselt number,  $Nu_z$ , correlation for developing flow in the entrance region for circular and non-circular channel developed by Shah and London [61] is shown in Equation (3.9).

$$Nu_z \approx 0.517 (fRe)^{1/3} (z^*)^{-1/3}$$

(3.9)

Figure 3.3: Velocity profile comparison of uniform channel and tapered channel at mid-plane in length-wise direction.

The Nusselt number is dependent on the Fanning friction factor f and position z. For simplification, some of the parameters are formulated into the variable  $z^*$ , where  $z^* = z/(D_h * Re * Pr)$ . In laminar flow, Fanning friction factor f is 16/Re which leads the term f \* Re constant as 16. This simplification is based on fully developed assumption, but we have verified that this exponent value has minimum effect in improving the accuracy through fitting, hence we have concluded this assumption is justified in our correlations. Pr is also a fixed constant for water at room temperature. As a result, the only remaining variables are  $D_h$ , Re and z.

# 3.4 Closed-Form Developing Flow Models

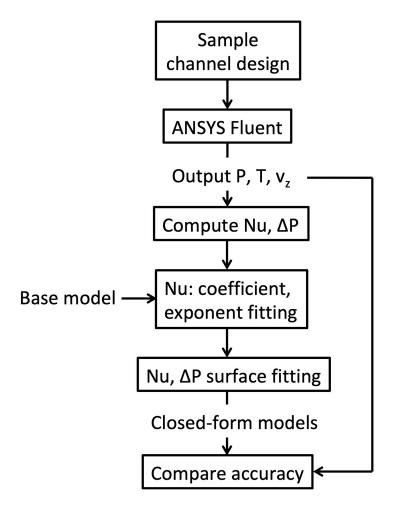

Figure 3.4 illustrates the procedure of the model derivation. To derive a closed-form model, we have first collected numerical simulation data of selected microchannel with various design parameters and extracted the values for the thermo-fluid performance analysis. Then, we have performed parameter fitting from the base model that we aim to improve the accuracy from. In our work, we have used the least-squares method in the parameter fitting. Finally, we have surface-fitted model parameters to create the correlations with the function of design variables. The surface fitting functions vary depending on the resulting function formula. This method is a commonly used approach and can be applied to other model derivations as well.

Figure 3.4: Flow chart of the model derivation.

## 3.4.1 Simulator

For numerical simulations, we used commercial computational fluid dynamics (CFD) solver, ANSYS Fluent v.18, in our experiments. The software uses the finite-volume method (FVM) with the support of the semi-implicit-method for pressure-linked-equations (SIMPLE) method. We applied rectilinear mesh with less than 0.1 maximum skewness, 0.1-0.5 million nodes depending on the channel size,  $5\,\mu\rm m$  mesh element size and double precision simulation setting. The solutions converged within 100 iterations.

### 3.4.2 Parameters

Microchannel dimensions used in the experiment are shown in Table 3.1. Height and length of the channel are fixed to single values as they are mainly defined by the manufacturing technology and the chip footprint. Channel inlet and outlet widths are varied between the minimum and maximum range listed. The range is selected based on commonly used manufacturing dimensions listed in previous works [11], [56], [62], [63]. To ensure the converging tapered shape, channel outlet width is set less than or equal to the channel inlet width for each geometry. Tapering angle is computed using Equation (4.1). Table 3.2 lists the thermo-fluid conditions and the properties of materials used for the simulations. Water at room temperature is used as coolant and inlet flow velocity is set to 1 m/s. Adding fluid velocity into the optimization variable can be the future extension of this work.

First, we have compared the models of different flow conditions and analysis methods. Figure 3.5a compares four models: 1) Shah-London fully de-

Table 3.1: Microchannel Parameters

| Definitions  | Param.    | Min    | Max        |

|--------------|-----------|--------|------------|

| Height       | Н         | 100 μm |            |

| Length       | L         | 0.5 mm |            |

| Inlet width  | $w_{in}$  | 100 μm | $400\mu m$ |

| Outlet width | $w_{out}$ | 10 μm  | $400\mu m$ |

| Angle        | $\theta$  | 0°     | 19.8°      |

Table 3.2: Thermal and Fluid Properties

| Definitions                         | Param.      | Values                                         |

|-------------------------------------|-------------|------------------------------------------------|

| Silicon thermal conductivity        | $k_{si}$    | $130\mathrm{W/m}\text{-K}$                     |

| Water thermal conductivity at 300 K | $k_{water}$ | $0.613\mathrm{W/m}\text{-K}$                   |

| Water kinematic viscosity           | ν           | $1.004 \times 10^{-6} \mathrm{m}^2/\mathrm{s}$ |

| Coolant inlet flow velocity         | u           | $1\mathrm{m/s}$                                |

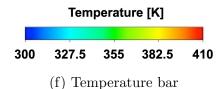

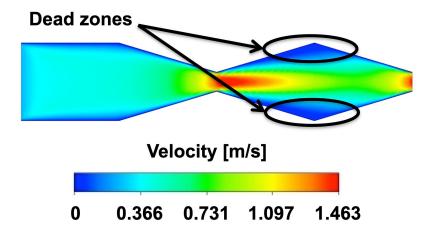

| Coolant inlet temperature           | $T_{inlet}$ | 300 K                                          |

| Prandtl number for water at 300 K   | Pr          | 5.83                                           |

| Reynolds number                     | Re          | 99-159                                         |

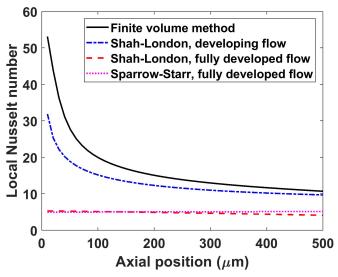

veloped model for rectangular channel [59], 2) Sparrow-Starr fully developed model for tapered cylindrical channel [64], and 3) Shah-London developing flow model for general channel [61] compared with 4) FVM numerical simulation. Model comparison experimented on a single tapered channel with inlet width of 400  $\mu$ m, outlet width 200  $\mu$ m, length 500  $\mu$ m with inlet flow velocity 1 m/s and heat flux 100 W/cm². Regardless of two different geometry approaches, rectangular versus tapered channel, both fully developed models showed large gaps between the local Nusselt number values as well as the Nusselt number gradients along the channel to the FVM result. On the contrary, developing flow model for circular and non-circular channels has a reasonably well-matching curve to the FVM result.

## 3.4.3 Constant Inlet Velocity

#### Nusselt Number

It is a widely used approach to derive a close-fitting Nusselt number or convective coefficient correlation from empirical data [65]. In this work, the model is built from numerical simulation data instead of the physical experimental results. Based on the Shah-London developing flow model with fixed constants for coefficient and exponents, we have further improved the model by fitting these parameters: 1) coefficient, denoted as  $\alpha$ , and 2) exponent, denoted as  $\beta$ , in Equation (3.10) to the numerical results. Exponent of fRe remains unchanged as the term is constant in laminar flow.

$$Nu_{z,fitted} \approx \alpha (f \cdot Re)^{1/3} (z^*)^{\beta}$$

(3.10)

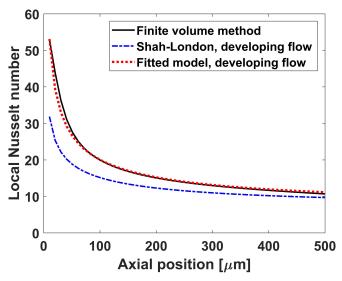

We have simulated 15 channel sizes: combination of three inlet widths and five tapering angles for each channel width. Flow velocity and heat flux are fixed to a single value for in-depth study of the channel geometry dimensions in our model. These values can also be varied to induce more comprehensive correlations, but this is beyond the scope of this work. Each  $(\alpha, \beta)$  value pair is determined by the least squares method for all datasets. Figure 3.5b exhibits the improvement of our fitted correlation from Shah-London general channel developing flow model, matching closer to the FVM result on the same tapered channel used in Figure 3.5a.

(a) Numerical simulation, fully developed and developing flow correlations comparison.

(b) Numerical simulation, general channel developing flow and fitted developing flow model comparison.

Figure 3.5: Local Nusselt number comparisons on tapered channel with inlet width 400 µm, outlet width 200 µm, length 500 µm, inlet flow velocity 1 m/s, heat flux 100 W/cm<sup>2</sup>.

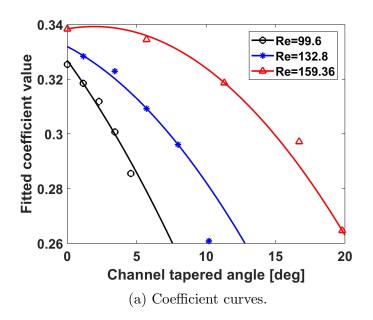

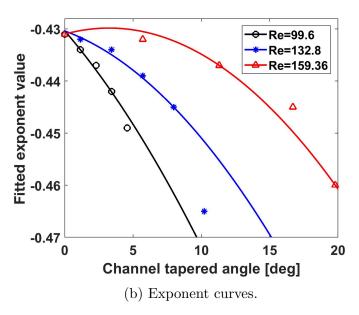

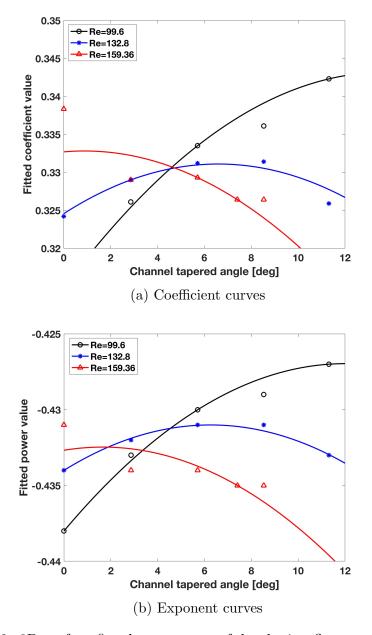

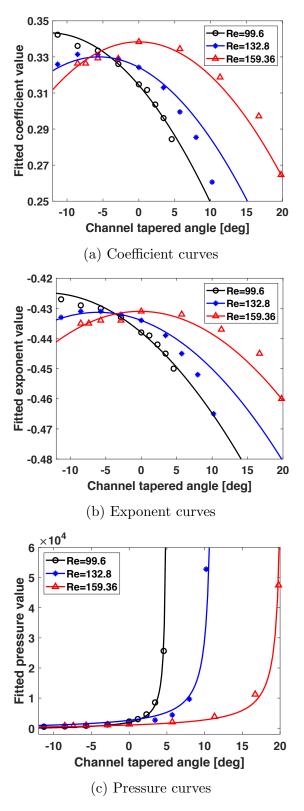

Next, fitted  $(\alpha, \beta)$  pair values for selected channel geometries are extended to derive the 3D correlations of the parameters as a function of two variables: 1) tapered angle  $\theta$  and 2) Reynolds number Re, using polynomial least squares surface fit. The Reynolds number is a representative indicator of the flow condition, defined by volumetric flow rate V, hydraulic diameter  $D_h$  and kinematic viscosity  $\nu$ ,  $Re = \dot{V}D_h/\nu = uAD_h/\nu$ . Volumetric flow rate  $\dot{V}$  is expanded to the product of flow velocity u and cross-sectional area A. We fixed flow velocity and channel height, thus inlet width is the only variable for determining the Reynolds number. Therefore, equivalently, fitting parameters can be expressed as a function of channel tapering angle  $\theta$  and the inlet width  $w_{in}$ . The 3D correlations were within 95% accuracy compared to the individually fitted parameters of each geometry. Then, we have determined the function of the surface fitting. In the case of the local Nusselt number, polynomial-22 function formula was used. Finally, we have 3D fitted the model parameters in terms of microchannel design variables using least absolute residuals method. The fitting algorithm applied depends on the target function formula and can be altered for the highest accuracy. The results of the 3D surface fitted curves for coefficient and exponent value are illustrated in the Figure 3.6a and 3.6b respectively. The resulting correlations for  $\alpha$  and  $\beta$  in terms of  $\theta$  and Re are shown in Equations (3.11) and (3.12). These fitted functions are combined to the Equation (3.10) to compute the convective coefficient in developing flow for tapered rectangular channel.

$$\alpha(\theta, Re) = 0.3317 - 0.02029\theta - 0.0001991Re - 0.0002337\theta^2 + 0.000133\theta Re + 1.513 * 10^{-6}Re^2$$

(3.11)

$$\beta(\theta, Re) = -0.435 - 0.009296\theta + 8.235 * 10^{-5}Re - 0.0001101\theta^2 + 6.282 * 10^{-5}\theta Re - 3.586 * 10^{-7}Re^2$$

(3.12)

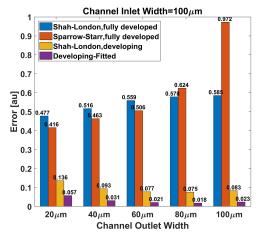

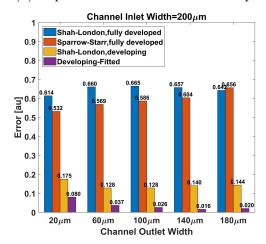

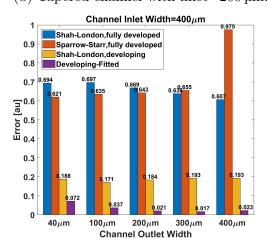

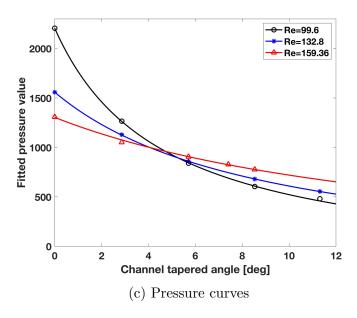

For qualitative and quantitative analysis between the models, mean error values on the local Nusselt number for simulated set of channels are compared in Figure 3.7. Each model is compared with respect to FVM. Average error percentage of Shah-London and Sparrow-Starr fully developed correlations are 62% and 72% respectively and the Shah-London developing flow model tremendously dropped down to 14%. Our fitted model further improved up to 4% error. Deviation is bigger on channels with a larger tapered angle, but

Figure 3.6: 3D surface fitted parameters of developing flow Nusselt number models for converging tapered channel on various tapering angles and Reynolds numbers.

the difference is 1-3.5%.

Furthermore, the Sparrow-Starr model is based on a tapered cylindrical model, which incorporates the effect of the slanted channel wall. However, this model is inapplicable for uniform channels with 0° angle. Rightmost bars from Figure 3.7a and 3.7c show uniform channels with the same inlet and outlet widths. Both Shah-London and Sparrow-Starr fully developed flow models were comparable between tapered channels, but the error rose significantly on the uniform channel and exhibited 97% error from the FVM. On the other hand, our model is reliably accurate throughout all channel wall angles.

Referring to Figure 3.5, the discrepancy of analytical models to FVM is larger near the entrance region of the channel. The observation indicates that the fully developed assumption will lead to more unreliable result for channels which are significantly shorter than entry length. Channel geometry design with piecewise optimization will dissect the channel into small sections and apply the heat transfer model to each channel sections. In this design optimization, every channel section will carry large error, eventually accumulate throughout the entire channel and exacerbate the effect. Moreover, channel dimensions can alter between the sections and cause the flow to fluctuate. As a result, fully developed flow will never be reached in the extreme case.

#### Pressure Drop

Cooling efficiency in microchannel comes at a price which can be mainly quantified by the pressure drop. Given microchannel design and the flow rate, pressure drop is determined. Darcy-Weisbach analytical pressure model for general channel in laminar flow is shown in Equation (3.13), where  $f_D$  is Darcy friction factor, four times the Fanning friction factor f from Equation (3.9),  $\rho$  is the density of the fluid, and  $u_{mean}$  is the mean flow velocity. Although it is a commonly used model in rectangular channels, there are discrepancies with numerical results on tapered channel design. Correlations for friction factor used in pressure formula for rectangular channels are derived in numerous works [66], [67]; however, the pressure model for tapered channel is not heavily studied.

(a) Tapered channel with inlet=100 μm.

(b) Tapered channel with inlet= $200 \, \mu m$ .

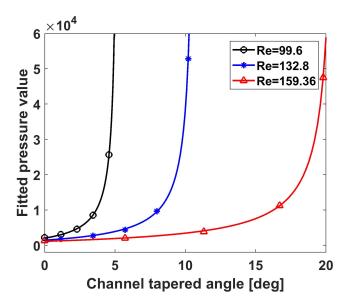

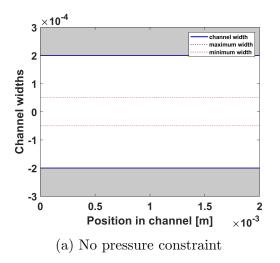

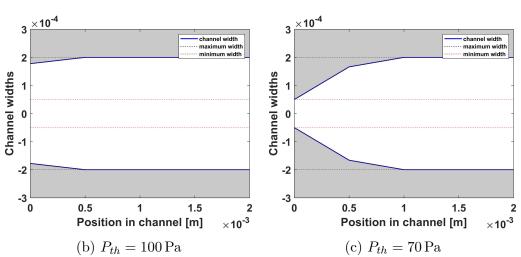

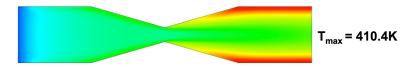

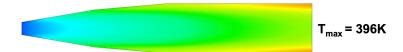

(c) Tapered channel with inlet=400 μm.