© 2018 Izzat El Hajj

#### TECHNIQUES FOR OPTIMIZING DYNAMIC PARALLELISM ON GRAPHICS PROCESSING UNITS

BY

IZZAT EL HAJJ

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2018

Urbana, Illinois

Doctoral Committee:

Professor Wen-mei Hwu, Chair Professor Deming Chen Associate Professor Steven Lumetta Dr. Dejan Milojicic, Hewlett Packard Labs

# ABSTRACT

Dynamic parallelism is a feature of general purpose graphics processing units (GPUs) whereby threads running on a GPU can spawn other threads without CPU intervention. This feature is useful for programming applications with nested parallelism where threads executing in parallel may each identify additional work that can itself be parallelized. Unfortunately, current GPU microarchitectures do not efficiently support using dynamic parallelism for accelerating applications with nested parallelism due to the high overhead of grid launches, the limited number of grids that can execute simultaneously, and the limited supported depth of the dynamic call stack.

The compiler techniques presented herein improve the performance of applications with nested parallelism that use dynamic parallelism by mitigating the aforementioned microarchitectural limitations. Horizontal aggregation fuses grids launched by threads in the same warp, block, or grid into a single aggregated grid, thereby reducing the total number of grids launched and increasing the amount of work per grid to improve occupancy. Vertical aggregation fuses grids down the call stack with their descendant grids, again reducing the total number of grids launched but also reducing the depth of the call stack and removing grid launches from the application's critical path.

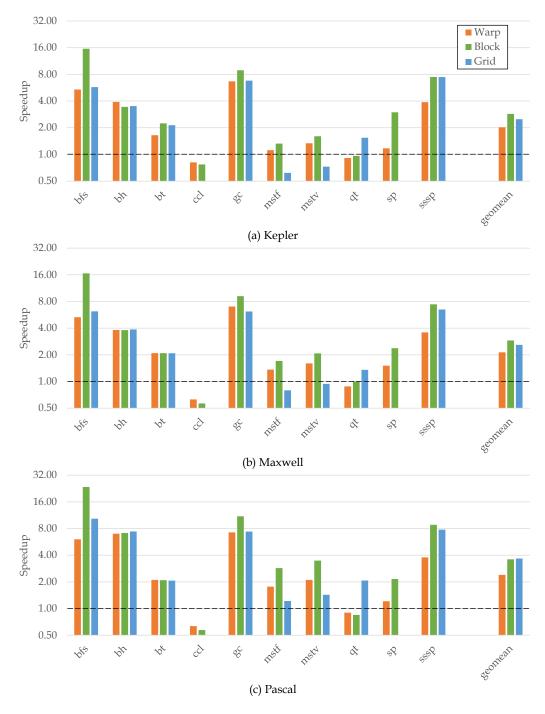

Evaluation of these compiler techniques shows that they result in substantial performance improvement over regular dynamic parallelism for benchmarks representing common nested parallelism patterns. This observation has held true for multiple architecture generations, showing the continued relevance of these techniques.

This work shows that to make dynamic parallelism practical for accelerating applications with nested parallelism, compiler transformations can be used to aggregate dynamically launched grids, thereby amortizing their launch overhead and improving their occupancy, without the need for additional hardware support. To Mama, Baba, Hind, Mohamad, Mona, and Amal

# ACKNOWLEDGMENTS

All praise is due to God.

I would like to thank my advisor, Professor Wen-mei Hwu, who has been an exemplary role model for me in all aspects, whether in his intelligence and integrity as a researcher, his passion and clarity as a teacher, or his humility and compassion as a person. Wen-mei always puts people first and is concerned about their well-being before being concerned about their technical progress, always willing to listen and always willing to help. He continues to inspire us who work with him to strive for high standards of academic excellence and character through the example that he sets.

I would also like to thank Dr. Dejan Milojicic from Hewlett Packard Labs who has been the equivalent of a second advisor to me. Getting to know Dejan was a turning point in my career because of the opportunities he opened up for me and the confidence he instilled in me by believing in me. Dejan's humility, openness, empathy, and genuine care for others make him a great mentor, a great collaborator, and a great human being.

I would also like to thank the rest of my committee, Professors Steven Lumetta and Deming Chen, for going above and beyond their duty in their responsiveness and the thoroughness of their feedback. My work is much stronger because of their contributions.

I would like to thank the IMPACT Research Group for their feedback and companionship throughout this journey and for being a fun bunch of people. I especially would like to thank Liwen Chang for his brilliance and his eagerness to help others, and Juan Gómez-Luna for his dedication and remarkable work ethic. I would also like to thank Marie-Pierre Lassiva-Moulin for the positive energy she provides.

I am not who I am without my parents, my siblings, my wife, and my daughter. I thank them wholeheartedly for their love and support. They are my biggest blessing.

# TABLE OF CONTENTS

| CHAPTER 7 VERTICAL AGGREGATION EVALUATION 5                                                                                                          | 59 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 Performance                                                                                                                                      | 59 |

| 7.2 Profiling $\ldots \ldots \ldots$ | 52 |

| CHAPTER 8 CASE STUDY: TRIANGLE COUNTING                                                                                                              | 53 |

| 8.1 Application Overview                                                                                                                             | 53 |

| 8.2 Baseline Implementation                                                                                                                          | 53 |

| 8.3 Dynamic Parallelism Implementation 6                                                                                                             | 55 |

| 8.4 Performance Evaluation                                                                                                                           | 57 |

| CHAPTER 9 RELATED WORK                                                                                                                               | 6  |

| 9.1 Applications using Dynamic Parallelism                                                                                                           | 6  |

| 9.2 Dynamic Parallelism Optimizations                                                                                                                | 80 |

| 9.3 Parallelization and Optimization of Recursion and Producer-                                                                                      |    |

| Consumer Chains                                                                                                                                      | 33 |

| 9.4 Other Trends in GPU Computing                                                                                                                    | 33 |

| CHAPTER 10 CONCLUSION                                                                                                                                | 87 |

| REFERENCES                                                                                                                                           | 39 |

# CHAPTER 1 INTRODUCTION

Over the past decade, since the introduction of CUDA [1], graphics processing units (GPUs) have proven effective as general purpose accelerators. The most straightforward targets for GPU acceleration have been applications with parallel computation patterns that are flat and regular in nature, and are thus a good match for GPU architectures. However, as GPUs become more mainstream as processors for general purpose acceleration, there is an increased interest in using them to accelerate a wider range of computation patterns. Of particular interest are computation patterns with nested parallelism.

Nested parallelism is a computation pattern in which an application has multiple levels of parallelism that can be exploited. The application typically creates multiple workers to span the first level of parallelism, then each of those workers does a certain amount of serial work, discovers more parallel work, and creates multiple workers to span that next level of parallelism. This process can happen recursively across multiple levels of nesting.

One example of applications that exhibit nested parallelism is graph traversal [2] where the first level of parallelism consists of nodes at the current frontier and the second level of parallelism consists of those nodes' neighbors. Another example is mesh refinement trees [3] where bounding boxes at one level of parallelism are recursively divided into multiple sub-divisions at subsequent levels of parallelism based on the amount of activity happening in those boxes. Finally, some applications with inter-worker dependences can be expressed using nested parallelism for convenience and ease of programming. For example, producer-consumer chains in which a consumer worker must wait for a producer worker to partially execute before it can begin its execution can be expressed as though the consumer worker is nested in the producer worker. Such producer-consumer chains are common in data sliding algorithms [4] such as multi-dimensional array padding/unpadding as well as stream compaction.

To enable intuitive programming of nested parallelism computation patterns on GPUs, a feature called *dynamic parallelism* [5, 6] was introduced whereby threads running on the GPU can spawn other threads without CPU intervention. Dynamic parallelism improves developer productivity and code maintainability [2, 7, 8, 9] by allowing developers to express nested parallelism computation patterns more naturally. For example, in graph traversal algorithms, a thread visiting a node in the current frontier can launch other threads to visit that node's neighbors. Without dynamic parallelism, the thread would have to loop over those neighbors sequentially, capturing less parallelism, or use other queuing-based techniques, which can be complicated and error prone. Similarly, in data sliding algorithms, a producer can launch consumers when their dependences have been satisfied rather than the programmer having to manually write complicated synchronization code using atomic operations.

While dynamic parallelism is an attractive feature for ease of programming, it has seen limited adoption in practice due to its poor performance [7, 8, 10]. One limitation is that dynamic parallelism on current hardware incurs high overhead when grids are launched from a GPU [7, 8]. Another limitation is that there can be a limited number of grids that can execute at the same time [7, 10]. These limitations are exacerbated when threads in a parent grid (which are typically large in number) each launch a small child grid. In this case, child grids are launched without enough work to amortize the launch overhead, and the grid count limit is reached before the GPU is fully utilized. Another limitation of dynamic parallelism is the bound on the depth of the call stack, which is problematic for computation patterns with deep recursion [7], such as those that express producer-consumer chains using nested parallelism. All these limitations have led application developers to resort to other programming techniques to avoid the use of dynamic parallelism [8, 11, 12, 13].

There have been multiple efforts to address the inefficiency of dynamic parallelism, both in hardware and software. Proposed hardware approaches include coalescing dynamically launched thread blocks with existing grids on the fly [10], co-locating child grids with their parents for better locality [14], and providing feedback on the profitability of a launch before launching [15]. However, these hardware proposals are not available on current hardware. Proposed software approaches for addressing the inefficiency of dynamic parallelism include overprovisioning parent grids with slave threads [8] or reusing parent threads/blocks [16] to execute the nested parallel work. These approaches eliminate dynamic grid launches entirely by using mega-kernels that inline the code of all kernels participating in the call hierarchy into a single one that is supplied with maximal resources. The latter approach also uses persistent threads to keep parent threads/blocks active so that they can be reused in the future. In contrast, the compiler techniques presented herein avoid the use of mega-kernels and persistent threads by continuing to use dynamic grid launches for executing nested parallel work, but controlling the granularity of those launches.

The compiler techniques presented herein aim to reduce the overhead of device-side grid launches that use dynamic parallelism by fusing child grids together to amortize their launch overhead. Horizontal aggregation fuses grids launched by threads in the same warp, block, or grid into a single aggregated grid, thereby reducing the total number of grids launched and increasing the amount of work per grid to improve occupancy. Vertical aggregation fuses grids down the call stack with their descendant grids, again reducing the total number of grids launched but also reducing the depth of the call stack and removing grid launches from the application's critical path.

These compiler techniques have been implemented in a real compiler and have been evaluated on three recent generations of NVIDIA GPU architectures: Kepler, Maxwell, and Pascal. They have been evaluated using benchmarks representing common nested parallelism patterns. The evaluation shows that these techniques result in substantial performance improvement over regular dynamic parallelism and continue to be relevant across architecture generations.

This work shows that to make dynamic parallelism practical for accelerating applications with nested parallelism, compiler transformations can be used to aggregate dynamically launched grids, thereby amortizing their launch overhead and improving their occupancy, without the need for additional hardware support.

# CHAPTER 2

# BACKGROUND AND MOTIVATION

Over the past decade, graphics processing units (GPUs) have gained adoption as general purpose accelerators. As GPUs become more mainstream, there is an increased interest in using them to accelerate a wider range of applications such as applications exhibiting nested parallelism. This interest has led to the introduction of a feature called dynamic parallelism. This chapter gives an overview of the basic GPU architecture and programming model (Section 2.1), describes nested parallelism (Section 2.2), describes dynamic parallelism and how it is used to accelerate applications with nested parallelism (Section 2.3), and finally discusses the overhead of dynamic grid launches to motivate the need for compiler optimizations to reduce this overhead (Section 2.4).

### 2.1 GPU Architecture and Programming Model

Mainstream CPUs contain a few heavyweight cores which are significantly optimized for single-threaded performance with techniques such as out-of-order execution, branch prediction, and other speculative execution techniques. In contrast, GPUs consist of a large number of lightweight execution cores with coarser-grain control, and are thus optimized for massive parallelism at the expense of single-threaded performance. This section describes the GPU architecture and programming model in detail.

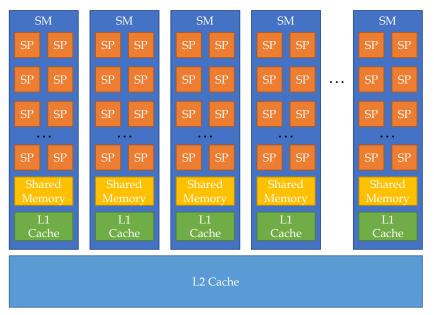

Figure 2.1(a) illustrates a simplified diagram of a typical GPU architecture. The most basic unit of a GPU is the streaming processor (SP), which executes a single thread of instructions. Multiple SPs are grouped into a streaming multiprocessor (SM). The number of SPs per SM varies significantly across architectures: 32, 192, 128, and 64 for Fermi, Kepler, Maxwell, and Pascal architectures, respectively. An SM contains a *shared memory* structure and

(a) GPU Architecture Overview

Figure 2.1: GPU Architecture and Programming Model

an L1 cache that are private to the SM and shared across all SPs in the SM. The shared memory is managed by the programmer, while the L1 cache is managed by the hardware. The GPU is comprised of many SMs that all share an L2 cache. The number of SMs per GPU also varies significantly across architectures: 16, 15, 24, and 56 for Fermi, Kepler, Maxwell, and Pascal architectures, respectively.

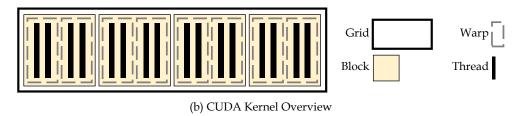

The structure of a CUDA program running on a GPU is illustrated in Figure 2.1(b). The smallest unit of work in a CUDA program is a thread, which executes a sequential stream of instructions on a single SP. Threads are grouped into warps such that threads in the same warp logically execute in lock-step (SIMD) on different SPs of the same SM. There are typically 32 threads per warp, which has been the case for all architecture generations to date, but that value is a characteristic of the hardware and could change in the future. At the next level, warps are grouped into thread blocks. Threads/warps in the same thread block execute on the same SM, can share memory via the shared memory structure, and can perform local barrier synchronizations. Different warps of the same block are co-scheduled on the same SM, which helps hide memory access latency. The number of threads per block is chosen by the application but is limited by the hardware. The maximum number of threads allowed per block depends on the architecture but has been 1,024 threads/block for all recent architecture generations. Finally thread blocks are grouped into grids, the largest unit of work, which runs on the entire GPU. Different thread blocks may execute on different SMs, therefore threads in different thread blocks cannot access the same shared memory structure. The only way for threads in different thread blocks to communicate is through global memory.

Threads in different thread blocks cannot perform barrier synchronization because there is no guarantee that they will all be scheduled simultaneously. The only way to synchronize across all thread blocks is by terminating the grid and launching a new one. This lack of scheduling control limits the types of parallelism that can be expressed on the GPU. Some works have demonstrated how barrier synchronization across all thread blocks can be implemented using atomic operations on global memory [17, 18] and similar techniques have also been recently added to CUDA [19]. However, these techniques require the grid to use (and reuse) a limited number of thread blocks to ensure that they are all simultaneously resident on the GPU in order to synchronize.

### 2.2 Nested Parallelism

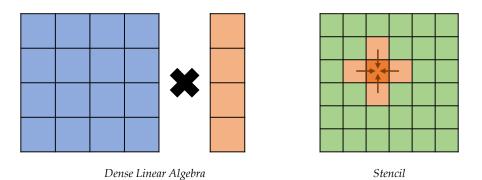

The grid structure of CUDA programs makes them a good fit for regular computation patterns with a single level of parallelism, i.e., flat parallelism. Figure 2.2(a) illustrates examples of computation patterns with flat parallelism. One example is dense linear algebra operations such as dot-products, dense matrix-vector multiplication, and dense matrix-matrix multiplication. To process these operations, it is typically sufficient to launch a single grid with as many threads as there are elements in the input or output vectors or matrices. Another example of flat parallelism is stencil operations, for which it is typically sufficient to launch a single grid with a thread to process each

(a) Computation Patterns with Flat Parallelism

Figure 2.2: Examples of Flat and Nested Parallelism

grid point in the domain.

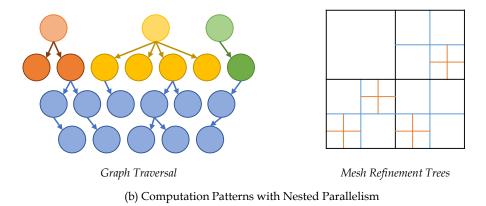

On the other hand, CUDA grids are unsuitable for computation patterns with multiple levels of parallelism, i.e., nested parallelism. Applications with nested parallelism typically create multiple workers to span one level of parallelism, then each of those workers does a certain amount of serial work, discovers more parallel work, and creates multiple workers to span the next level of parallelism. This process can happen recursively across multiple levels of nesting. Figure 2.2(b) illustrates examples of computation patterns with nested parallelism. One example is graph traversal [2] operations: to capture the parallelism present in these operations, a worker must typically be created for every node in the current frontier of the search, and each worker then creates more workers to visit the neighbors of that node in parallel. Another example of nested parallelism is mesh refinement trees [3]. To capture all the parallelism present in these operations, a worker must typically be created for every bounding box at one level of the tree. Each worker then assesses the amount of activity happening in its box and, if needed,

(a) Programming model without dynamic parallelism

(b) Programming model with dynamic parallelism

Figure 2.3: CUDA Dynamic Parallelism Overview

divides its box into multiple sub-divisions and creates a worker to process each sub-division. This process may continue recursively.

# 2.3 Dynamic Parallelism

Dynamic parallelism is a feature that was introduced with CUDA 5.0 whereby threads running on a GPU can create other threads without CPU intervention [5]. Similar features were also introduced for other programming models around the same time [6]. Dynamic parallelism enables intuitive programming of nested parallel computation patterns on GPUs, thereby improving developer productivity and code maintainability.

Without dynamic parallelism, there are several ways in which developers can deal with nested parallelism in their applications. The simplest way is to serialize the work of the second level of parallelism within the first. For example, in graph traversal, a thread visiting a node can process its neighbors serially. The drawback of this approach is that it does not extract all the

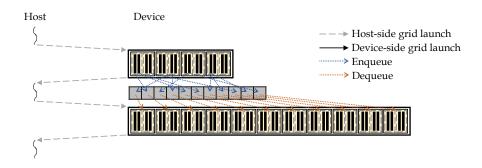

Figure 2.4: Launch Overhead

parallelism available in the application and can suffer from control divergence if adjacent threads have significantly different amounts of nested work. Another way to deal with nested parallelism without dynamic parallelism is to have threads add their nested tasks to queues, then launch a subsequent grid from the CPU based on the number of tasks in the queue. An illustration of this approach is shown in Figure 2.3(a). The drawback of this approach is that it is not an intuitive way to express nested parallelism which makes the code hard to write, read, and maintain.

Dynamic parallelism presents a simple way for developers to express nested parallelism in applications. Threads that discover nested parallel work can simply launch a new grid of threads to execute that work in parallel as shown in Figure 2.3(b). For example, in graph traversal, a thread visiting a node in a graph can launch a new grid with as many threads as it has neighbors after visiting its node and identifying the number of neighbors it has. Similarly, in mesh refinement trees, a thread/block processing a bounding box can launch a new grid with as many threads/blocks as there are sub-divisions after it has discovered whether or not the bounding box needs to be sub-divided for finer resolution.

### 2.4 Dynamic Parallelism Overhead

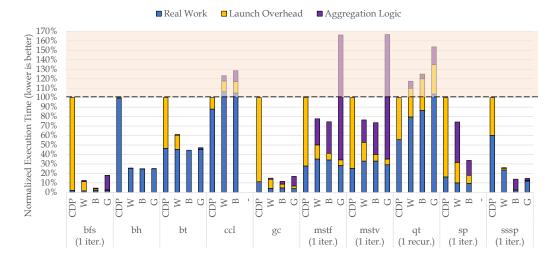

In addition to enhancing the ease of programming, one would expect dynamic parallelism to also improve resource utilization (hence, performance) for applications with nested parallelism because it enables launching just the right number of threads needed at each level of parallelism. However, it has been shown that dynamic parallelism has high overheads in practice [7, 8] which has resulted in low adoption.

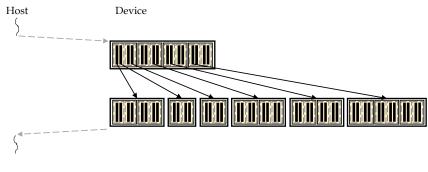

Figure 2.4 shows the breakdown of execution time for some benchmarks that use dynamic parallelism (see Chapter 5 for experimental details). These results demonstrate that workloads using dynamic parallelism can be dominated by the launch overhead. The compiler techniques presented herein aim at reducing this high overhead incurred by dynamic grid launches to make dynamic parallelism more usable in practice.

# CHAPTER 3

# HORIZONTAL AGGREGATION

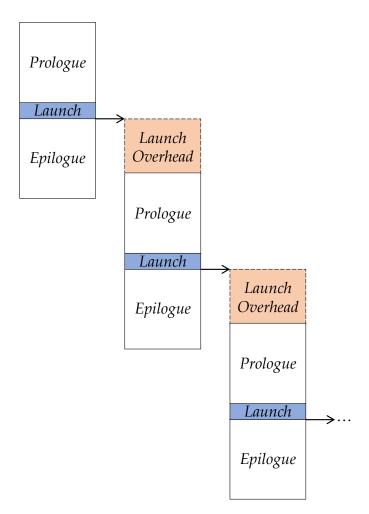

The primary compiler technique proposed in this work for mitigating the high launch overhead of dynamic parallelism is horizontal aggregation. We use the term aggregation in general to refer to a transformation whereby grids that were originally launched by different threads are fused together into a single grid that is launched by a single representative thread. Aggregation can be thought of in various dimensions - threads, call stack, and code sequence - as well as hybrid combinations of these dimensions. Aggregation across threads is the aggregation of grids launched by different threads in the same grid executing the same line of code. This dimension is referred to as *horizontal* aggregation, which is the subject of this chapter. Aggregation across the call stack is the aggregation of grids launched by a thread with the grids to be launched by its children threads in the presence of recursion. This dimension is referred to as *vertical aggregation* and is the subject of Chapter 4. Aggregation across the code sequence is the aggregation of grids launched at different lines of code in a single kernel. This dimension of aggregation is outside the scope of this work.

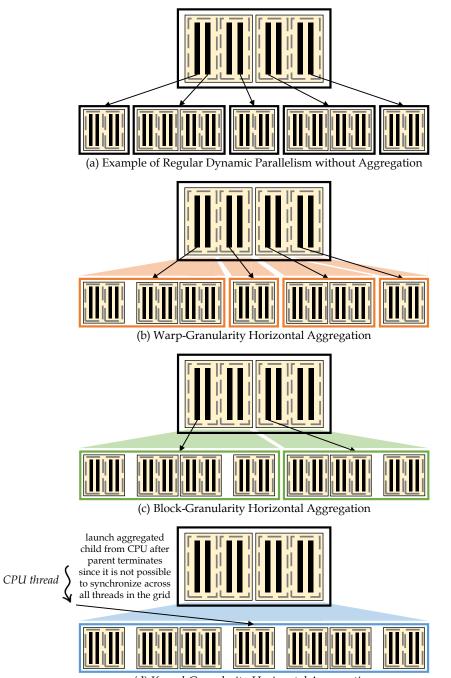

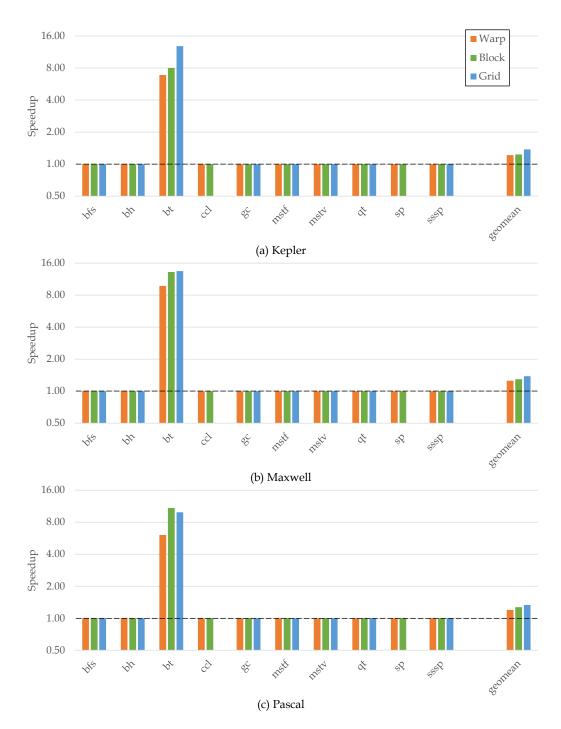

Horizontal aggregation can be performed at various levels of granularity, which is the scope of parent threads in the same parent grid across which the launched child grids are aggregated. For example, horizontal aggregation at warp granularity means that grids launched by threads in the same warp are aggregated into a single grid which is launched by one of the threads in that warp. On the other hand, grids launched by threads in different warps remain in separate aggregated grids. This work explores horizontal aggregation at three different levels of granularity: warp, block, and grid. Warp and block granularity is described in Section 3.1, while grid granularity is described in Section 3.2.

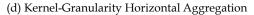

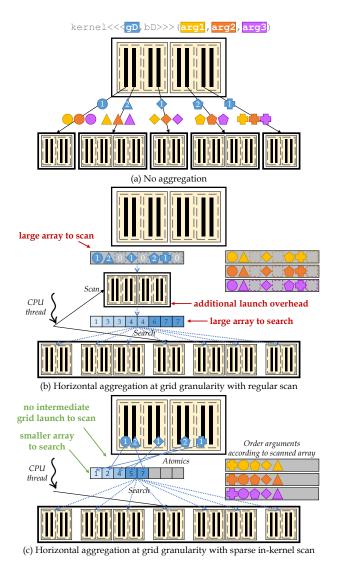

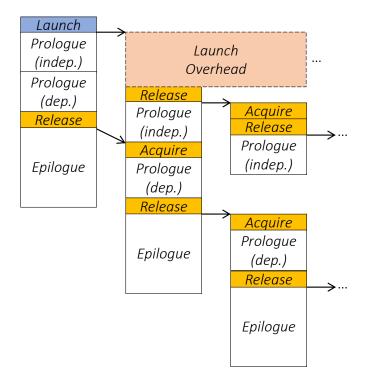

Figure 3.1: Horizontal Aggregation for Different Levels of Granularity

## 3.1 Warp and Block Granularity

Horizontal aggregation at warp (or block) granularity fuses grids launched by threads in the same warp (or block) into a single aggregated grid launched by a single thread. The transformations necessary for these two levels of granularity are similar, so they are explained together with differences indicated where necessary.

#### 3.1.1 Transformation Overview

Figure 3.1 illustrates the impact of horizontal aggregation at each level of granularity using a toy example. Figure 3.1(a) shows an example of regular dynamic parallelism without any aggregation applied. Five child grid launches are performed by five different threads of the parent grid. Figure 3.1(b) illustrates the transformation that takes place when horizontal aggregation is applied at warp granularity. The first warp in the parent grid originally had two threads each launching a child grid. In the transformed version, the two child grids are aggregated into one aggregated grid, which is launched by one of the two threads in the parent warp. This transformation effectively reduces the number of kernel launches by up to a factor of the warp size. Warps of size two are used in this toy example for simplicity, but warps are typically 32 threads, as explained in Section 2.1.

Figure 3.1(c) illustrates the transformation that takes place when horizontal aggregation is applied at block granularity. Here, only one thread per block launches a kernel on behalf of all the threads in the block. For example, the first block in the original kernel performs three different grid launches by different threads. These three grids are converted into one aggregated grid launched by one thread. This transformation effectively reduces the number of grid launches by up to a factor of the block size, which can be up to 1,024, as explained in Section 2.1.

Figure 3.1(d) illustrates the transformation that takes place when horizontal aggregation is applied at grid granularity. This transformation is discussed in Section 3.2. 01 kernel<<<gD,bD>>>(args)

#### (a) Original Kernel Call

```

02 __global__ void kernel(params) {

03 kernel body

04 }

```

#### (b) Original Kernel

allocate arrays for args, gD, and bD 05 06 store args in arg arrays store gD in gD array, and bD in bD array 07 new gD = sum of gD array across warp/block (includes implicit barrier) 08 new bD = max of bD array across warp/block (includes implicit barrier) 09 10 if(threadIdx == launcher thread in warp/block) { 11 kernel\_agg<<<<new gD, new bD>>> (arg arrays, gD array, bD array) 12 13 }

#### (c) Transformed Kernel Call (called in a kernel)

| 14 | globalvoid kernel_agg(param arrays, gD array, bD array) { |

|----|-----------------------------------------------------------|

| 15 | calculate index of parent thread                          |

| 16 | <i>load</i> params <i>from param arrays</i>               |

| 17 | load actual gridDim/blockDim from gD/bD arrays            |

| 18 | calculate actual blockIdx                                 |

| 19 | if(threadIdx < actual blockDim) {                         |

| 20 | kernel body (with kernel launches transformed and with    |

| 21 | using actual gridDim/blockDim/blockIdx)                   |

| 22 | }                                                         |

| 23 | }                                                         |

#### (d) Transformed Kernel (called from a kernel)

Figure 3.2: Code Generation for Aggregation at Warp and Block Levels of Granularity

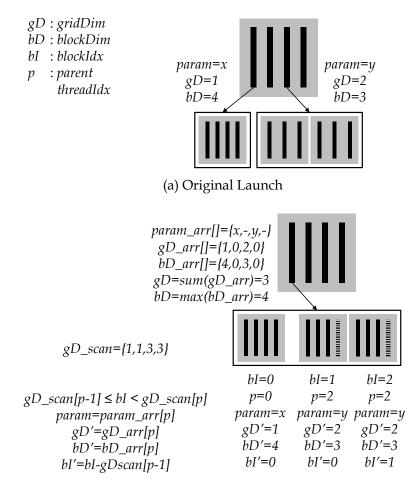

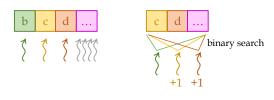

#### 3.1.2 Code Transformation of Kernel Call

The code transformation necessary to perform horizontal aggregation at warp (or block) granularity is shown in Figure 3.2. Pseudocode is used to keep the explanation simple. Figure 3.2(a) shows the original dynamic parallelism kernel call as called from a parent kernel. The kernel is configured with the grid dimension gD (number of thread blocks in the launched grid) and the block dimension bD (number of threads in a block) as well as passed a set of arguments args (line 01). Note that gD and bD can be arbitrary expressions so their values are not known at compile time.

Figure 3.2(c) shows how kernel calls such as the one in Figure 3.2(a) are transformed to achieve horizontal aggregation at warp (or block) granularity. The first step in the transformed code is for the warp (or block) to allocate global arrays to store the arguments and configurations to be passed to the aggregated kernel (line 05). Since dynamic memory allocation on the device using cudaMalloc can be expensive, this overhead is avoided by preallocating a memory pool on the host and passing it to the parent kernel. The parent kernel can therefore perform lightweight allocation of global arrays using atomic operations to grab memory from that pool. The size of the pool can be provided as a compiler option if the default size is too large or too small.

Next, each thread stores its arguments and configurations in the allocated arrays (lines 06-07). The reason the aggregated kernel needs to be passed these arguments and configurations in arrays is that different threads in the original parent kernel may have been passing different arguments and configurations to their child kernels and all these values need to be passed to the aggregated kernel. In practice, not all arguments and configurations vary across parent threads, which presents an opportunity for optimizations, as discussed in Sections 3.4.1 and 3.4.2.

Next, the number of thread blocks in the aggregated grid is calculated (line 08). The number of thread blocks in the aggregated grid is the sum of the number of thread blocks in each of the original grids launched by each thread participating in the aggregation. Likewise, the number of threads per block in the aggregated grid is calculated (line 09). The number of threads per block in the aggregated grid is calculated as the maximum number of threads per block in all child grids launched. The maximum is used is to

ensure that all blocks in the aggregated child grid have enough threads to execute their work. However, using the maximum means that some blocks may have more threads than they originally did. To address this situation, these threads are masked out, as shown later.

Finally, one of the threads in the warp (or block) executes a single aggregated kernel launch on behalf of the others (line 10). A synchronization across the threads in the warp (or block) is needed before the launch to ensure that all the threads have completed the preparation of the arguments and configurations. This synchronization is already achieved implicitly during the warp-wide (or block-wide) summation/max. In the aggregated kernel call, the new configurations are used (line 11), arguments are replaced with argument arrays, and arrays containing the configurations for each original child are added (line 12).

#### 3.1.3 Code Transformation of Called Kernel

In addition to transforming kernel calls to collect parameters and calculate the new configurations of the aggregated grid, a version of the launched kernel must also be created that identifies its original caller, unpacks its parameters, and calculates its actual configurations accordingly. Figure 3.2(b) shows the original example kernel launched in Figure 3.2(a). The kernel receives a set of parameters **params** and has a kernel body that performs a set of operations using the various parameters as well as the reserved indexing variables **threadIdx**, **blockIdx**, **blockDim**, and **gridDim**.

Figure 3.2(d) shows how the kernel in Figure 3.2(b) is transformed into an aggregated version. First, the function signature of the kernel is transformed (line 14) so that all parameters are converted into parameter arrays that contain the parameters passed by each of the original parent threads. Moreover, configuration arrays are added to the parameter list to pass the number of blocks and threads per block of each of the original non-aggregated grids.

Next, code is added before the kernel body for the block to identify which thread in the parent warp (or block) was its original parent (line 15). For the block to identify its original parent, it needs a scanned (prefix sum) version of the gD (gridDim) array to find at which point in the aggregated grid the blocks of each parent thread are. Since all child blocks need to scan the same gD array, the scan is actually performed once by the parent warp (or block) before the array is passed to the aggregated child kernel (not shown in Figure 3.2). Conveniently, the scan can be performed while the reduction is taking place to calculate the total number of thread blocks making it incur little additional overhead. With the scanned array of grid dimensions, the child thread block searches the array to identify between which two values its own blockIdx falls, thereby identifying the thread index of its original parent thread. The search is performed as follows. First, an initial guess is made that assumes that the child thread blocks in the aggregated grid are evenly distributed across parent threads. This initial guess will be correct in cases where all parent threads launch the same number of child blocks. If the initial guess is incorrect, then an actual search is performed. If the number of threads available in the child thread block exceeds the size of the parent warp/block, then each thread checks one element of the scanned array. The thread which finds the correct position broadcasts the result to the rest of the threads in the thread block using shared memory. If the number of threads available in the child thread block is less than the size of the parent warp/block, then a p-ary [20] search is used.

After identifying its original parent, the block is then able to locate its actual parameters and configurations and load them (lines 16-18). Since the array containing the number of thread blocks in each original grid is scanned, the actual gD configuration is recovered by subtracting adjacent scan elements. The block also calculates its actual blockIdx within the original non-aggregated grid by subtracting its blockIdx in the aggregated grid from the starting point of the original grid in the aggregated grid. A check against the recomputed actual blockDim is made to mask out threads that did not exist in the original child grid (line 19). This accounts for the variation in the number of threads per block in the grids before aggregation and the usage of the maximum for all grids after aggregation.

Finally, in the kernel body, all uses of blockDim and blockIdx are replaced with the actual values computed previously (lines 20-21). Moreover, all kernel launches are also transformed into aggregated kernel launches which supports having multiple levels of nesting.

(b) Transformed Launch

Figure 3.3: Aggregation Logic Example

#### 3.1.4 Aggregation Logic Example

Figure 3.3 shows a toy example of how horizontal aggregation works in practice. In the original kernel launch in Figure 3.3(a), the parent warp (or block) has 4 threads. Parent thread 0 launches a child grid with 1 thread block of 4 threads and passes the value x the parameter **param**. Parent thread 2 launches a child grid with 2 thread blocks of 3 threads and passes the value y the parameter **param**.

In the transformed version in Figure 3.3(b), the following changes take place. Arrays of length 4 (equal to the number of original parent threads) are allocated for the parameter **param** as well as the kernel launch configurations gD and bD. Parent threads 0 and 2 store their **param** values x and y respectively in their corresponding slot in the array for that parameter.

Similarly, they store their values for gD and bD in the configuration arrays. The sum of the values in the gD array is calculated to be 3, which is the number of thread blocks to be launched in the aggregated grid. The maximum of the values in the bD array is calculated to be 4, which is the number of threads per block to be launched in the aggregated grid. The gD array is actually scanned while it is being summed resulting in the array gD\_scan where every entry in the array indicates the number of child thread blocks up to and including the parent thread for that position.

In the launched kernel, the first step is for a block to identify the index of its parent thread in the parent warp (or block) denoted by  $\mathbf{p}$ . To do so, the block searches the  $\mathbf{gD\_scan}$  array for the index  $\mathbf{p}$  that satisfies the condition  $gD\_scan[p-1] \leq bI < gD\_scan[p]$  where bI is the index of the block in the aggregated array. For example, block 1 identifies that its index 1 is greater than or equal to  $gD\_scan[1]$  and less than  $gD\_scan[2]$ ; therefore, its parent thread must have been thread 2.

After having identified its parent thread, the thread block loads the actual parameters and configurations from the arrays to be used by the child threads. It also calculates its real block index by subtracting the number of thread blocks up to and including the previous parent thread's thread blocks. For example, block 2, whose parent thread is 2, subtracts  $gD\_scan[1] = 1$ from its block index to obtain its actual block index which is 1. Finally, the thread block masks out threads that did not exist in the original child grid. For example, all thread blocks in the aggregated child grid have 4 threads because the children of parent thread 0 (i.e., block 0) need 4 threads to execute. However, the children of parent thread 2 (i.e., blocks 1 and 2) only need 3 threads so they mask out 1 thread based on the recalculated block dimension.

### 3.2 Grid Granularity

Horizontal aggregation at grid granularity is when grids launched by threads in the same parent grid are fused together into a single grid launched from the host. While aggregation at warp granularity and aggregation at block granularity are fairly similar, aggregation at grid granularity has some significant differences, which are highlighted in this section.

#### 3.2.1 Transformation Overview

Figure 3.1(d) illustrates the transformation that takes place when horizontal aggregation is applied at grid granularity. At this granularity, all the original child grids are aggregated into a single grid. Since no global synchronization on the GPU is allowed across threads in different blocks, a single thread in the parent grid cannot be chosen to launch the grid on behalf of the others because it is not possible for that thread to know when the others are ready. For this reason, the aggregated grid is instead launched from the host after the parent grid terminates. For this transformation to be possible, it must be legal for the grid launch to be postponed until later in the execution. For such postponing to be legal, the transformation requires that the parent kernels do not explicitly synchronize to wait for their child kernels to finish (by default, kernel launches are asynchronous which means that parent execution can continue before the child grid completes). For this reason, aggregation at grid granularity is only supported when there is no explicit synchronization on child grids by the parent grid.

#### 3.2.2 Code Transformation of Kernel Call

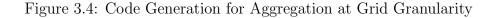

Figure 3.4 shows the code transformation applied to perform horizontal aggregation at grid granularity for the same example as in Figure 3.2. Many parts of the transformation are similar to aggregation at warp and block granularity, but there are some key differences.

The main difference in the transformation of the kernel call is that the call is moved to the host function that calls the parent instead of being called from within the kernel. This transformation is shown in Figure 3.4(c), wherein the kernel launch in Figure 3.4(a) is replaced by just the allocation of arrays and storing of parameters and configurations (lines 05-07). After that, once the kernel returns to the host, a new kernel is called to scan the gD array and calculate the total sum to get the number of thread blocks in the aggregated grid (line 08). The scan operation must be done by a separate kernel call because it must wait for threads in all thread blocks to finish storing their configurations which requires a global synchronization that is achieved via kernel termination. Similarly, another kernel is called to calculate the maximum number of threads (line 09). Finally, a launchpad

01 kernel<<<gD,bD>>>(args)

#### (a) Original Kernel Call

```

02 __global__ void kernel(params) {

03 kernel body

04 }

```

#### (b) Original Kernel

#### On device in place of child kerne launch:

allocate arrays for args, gD, and bDstore args in arg arrays

07 store gD in gD array, and bD in bD array

On host after parent kernel launch:

08 new gD = sum of gD array across grid 09 new bD = max of bD array across grid 10 11 kernel\_launchpad(new gD, new bD 12 arg arrays, gD array, bD array) 13

#### (c) Transformed Kernel Call (called in a kernel)

| 14 | globalvoid kernel_agg(param arrays, gD array, bD array) {                                   |

|----|---------------------------------------------------------------------------------------------|

| 15 | calculate index of parent thread                                                            |

| 16 | <i>load</i> params <i>from param arrays</i>                                                 |

| 17 | load actual gridDim/blockDim from gD/bD arrays                                              |

| 18 | calculate actual blockIdx                                                                   |

| 19 | if(threadIdx < actual blockDim) {                                                           |

| 20 | kernel body (with kernel launches transformed and with                                      |

| 21 | using actual gridDim/blockDim/blockIdx)                                                     |

| 22 | }                                                                                           |

| 23 | }                                                                                           |

| 24 | <pre>void kernel_launchpad(gD, bD, param arrays, gD array, bD array) {</pre>                |

| 25 | <pre>kernel_agg&lt;&lt;&lt;<gd, bd="">&gt;&gt; (arg arrays, gD array, bD array)</gd,></pre> |

| 26 | postponed kernel launches from kernel body (if any)                                         |

| 27 | }                                                                                           |

|    | (d) Transformed Kernel (called from a kernel)                                               |

function is called which launches the aggregated child grid from the host (line 11-12).

#### 3.2.3 Code Transformation of Called Kernel

The transformation of the called kernel for horizontal aggregation at grid granularity is similar to that at warp and block granularity. However, one key difference is that this kernel is launched using a launchpad function from the host rather than from another kernel. If the child kernel body itself has any kernel calls that are to be aggregated, those kernel calls can be moved to the launchpad function. The usage of a launchpad function is important for handling multiple levels of nesting or recursion. Without the usage of launchpad functions, the compiler must extract all nested calls in the call hierarchy at the call site of the uppermost parent call, which is difficult, especially in the case where there is recursion and the depth of the call hierarchy is not statically known. This problem does not exist at warp and block granularity because the child kernel call is transformed within the parent kernel, not moved outside the parent kernel like with grid granularity.

#### 3.2.4 Limitations

Unlike horizontal aggregation at warp and block granularity, there are some limitations faced at grid granularity due to the inability to perform a gridwide synchronization to perform the aggregation on the device. The first limitation, which has been mentioned in Section 3.2.1, is that horizontal aggregation at grid granularity requires that the parent thread does not explicitly synchronize (using cudaDeviceSynchronize()) on the kernel launch that is being aggregated. The reason is that if the parent thread explicitly synchronized on the kernel launch, then the kernel launch cannot be postponed after the synchronization, and therefore it cannot be taken outside the kernel to be launched from the host.

The second limitation is when child kernel launch takes place inside of a loop. In this case, the number of launches that each parent thread performs may not be known. Handling such a case requires that the number of loop iterations in each thread be tracked so that it can be recovered on the host to

Figure 3.5: Aggregation Granularity Tradeoffs

identify how many aggregated child grids to launch. While this is possible, it is not currently supported.

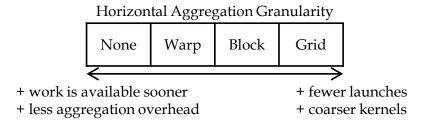

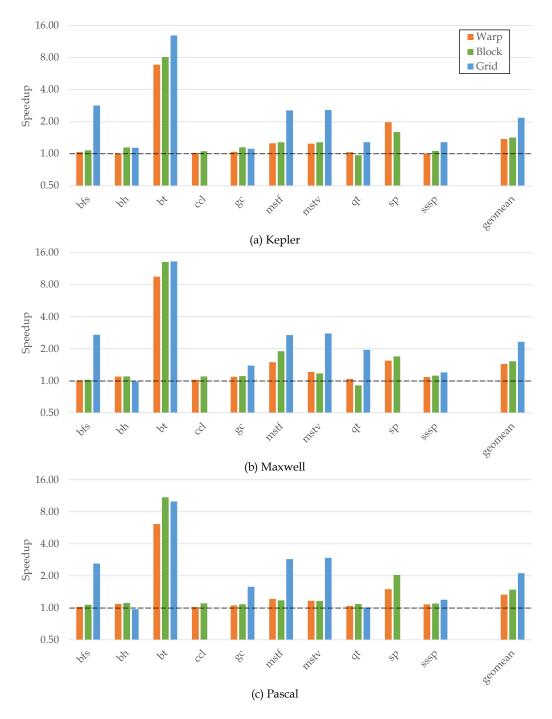

# 3.3 Tradeoffs between Levels of Granularity

Figure 3.5 shows the tradeoffs associated with varying the level of granularity at which horizontal aggregation is performed. Coarser granularity has the advantage of having fewer launches, hence fewer cycles wasted due to launch overhead, and larger grids, hence better resource utilization due to the availability of more thread blocks to schedule at a time. For example, at grid granularity, there will only be a single child grid launch per kernel call, whereas at warp granularity, there will be as many child grid launches as there are warps in the parent grid with at least one thread in that warp performing a dynamic launch.

However, finer granularity has the advantage of work being available sooner because there are fewer parent threads to wait for, and lower aggregation overhead due to smaller scan and max operations that need to be performed and a smaller array that needs to be searched to identify the original parent thread.

### 3.4 Additional Optimizations

This section describes a few additional optimizations that enhance horizontal aggregation. While the techniques described in this section are not essential for correctness, they result in substantial performance improvements in some cases and are therefore important for the overall performance of this technique. These optimizations include: scalarization of uniform arguments,

scalarization of uniform configurations, sparse in-kernel scan of block dimensions at grid granularity, and aggregation of dynamic memory allocation.

#### 3.4.1 Scalarization of Uniform Arguments

Recall that when grids are aggregated, the arguments passed to the original grids are stored in arrays to be passed to the aggregated grid as shown in Figure 3.2 line 06. However, it is often the case that some of these arguments are uniform across all parent threads. In this case, storing duplicate values of these configurations and arguments is a waste of space and, more importantly, a waste of time spent storing them to global memory in the parent threads and then loading them from global memory in the child grids. Instead, as an optimization, no arrays are allocated for uniform arguments, and they are passed as scalar values to the child grid.

To support this optimization, it is necessary for the compiler to analyze the code to identify which arguments are uniform and which ones are not. This analysis is done via standard iterative dataflow analysis techniques that iterate over the code until convergence. The following are the main rules applied by the analysis:

- Constant literals are uniform.

- Reserved words blockDim and gridDim are uniform.

- Reserved words threadIdx and blockIdx are non-uniform.

- A unary, binary, or ternary operation is uniform if all its operands are uniform, and non-uniform otherwise.

- An array access is uniform if the base pointer and index are both uniform, and non-uniform otherwise.

- An object member variable access is uniform if the base object is uniform, and non-uniform otherwise.

- A function call return value is conservatively considered non-uniform unless the function is a pure function with uniform arguments.

- The LHS of an assignment statement is uniform if its RHS is uniform and the assignment takes place in a non-divergent context.

• A control structure is non-divergent if its condition is uniform and divergent otherwise.

Note that the analysis also gives information about when code is in a divergent or non-divergent context. This information is useful for handling control divergence as described in Section 3.5. Such analyses on variable uniformity and control structure divergence are useful in research and tools that involve transformation and optimization of GPU code [21, 22, 23, 24].

#### 3.4.2 Scalarization of Uniform Configurations

Recall that when grids are aggregated, the configurations passed to the original grids are stored in arrays to be passed to the aggregated grid as shown in Figure 3.2 line 07. This passing of arrays can be avoided if the configurations are uniform, similar to what is done for uniform arguments as discussed in Section 3.4.1. Moreover, if the block dimension configuration is uniform, the maximum operation over the child block dimensions is unnecessary and can be eliminated. In this case, there is no need to pass any parameter for the child block dimension since the child can obtain its block dimension from the **blockDim** reserved word.

### 3.4.3 Sparse In-kernel Scan of Block Dimensions at Grid Granularity

One of the most expensive operations in the aggregation logic is the scan operation which is used to calculate the grid dimension of the aggregated grid and also to provide an array which the child thread blocks can search to identify their original parent. While the cost of these operations remains reasonable at warp and block granularity, it can become prohibitive at grid granularity for two reasons:

1. At grid granularity, the scan operation must be performed in a separate grid to ensure global synchronization which incurs the overhead of an additional grid launch and does not benefit from the grid dimension values being in the cache as is the case at warp and block granularity.

Figure 3.6: Sparse In-kernel Atomic-based Scan of Block Dimensions at Grid Granularity

2. While the widths of the scanned array for warp and block granularity are 32 and  $\leq 1,024$  respectively, the width can be much greater at grid granularity since a parent grid may contain many more threads. This larger array results in a larger scan operation after the parent terminates and a larger search operation by each child block, which can incur high latency.

These drawbacks are illustrated in Figure 3.6(a).

To mitigate this overhead, a different technique is used at grid granularity to scan the grid dimension values as illustrated in Figure 3.6(b). Instead of performing a grid-wide scan after all threads have stored their values, atomic operations can be used to calculate the total number of thread blocks, as well as the number of thread blocks up to a certain thread for each parent thread. Using this approach, parent threads will likely not access the atomic operation in the same order as their order in the parent thread block so the "scanned" array will not be in that order. However, this change in order is acceptable because what matters is that whatever order parent threads use to store the cumulative grid dimensions, this same order is used to store arguments and configurations in their respective arrays. Using this technique, the "scan" operation can be performed on the fly in the parent grid without the need for a separate grid launch.

An additional advantage of performing the scan operation in this way is that zeros can be eliminated from the array by the parent thread simply not grabbing an entry in the array if it does not perform a launch (as opposed to storing a zero). By doing so, the array becomes much smaller when the child launches are sparse, resulting in a faster search operation by the blocks in the aggregated child grid. Child launches are sparse when the launch is guarded by some condition that is not true for all parent threads.

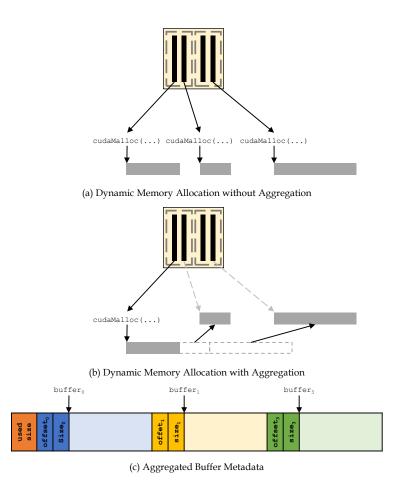

#### 3.4.4 Aggregation of Dynamic Memory Allocation

In the same way that grid launches performed by every thread incur high overhead and aggregating these launches amortizes that overhead, dynamic memory allocation by every thread also incurs high overhead and can be aggregated. When every thread in the grid calls cudaMalloc for a small amount of memory as shown in Figure 3.7(a), they put a lot of pressure on the device to service these requests. Instead, calls to cudaMalloc are aggregated as shown in Figure 3.7(b) by: (1) summing the total requested memory allocation across all threads in the scope of aggregation, (2) using one thread to allocate that total memory on behalf of the others, then (3) redistributing the allocated memory to all threads. It is only possible to aggregate cudaMalloc at warp and block granularity since cudaMalloc is a blocking call and blocking calls cannot be aggregated at grid granularity as explained in Section 3.2.4. This observation is not a limitation since cudaMalloc can be aggregated at a different granularity than other launches in the same kernel so it will not block grid granularity aggregation from being

Figure 3.7: Aggregation of Dynamic Memory Allocation

applied elsewhere.

One important consideration when aggregating calls to cudaMalloc is ensuring that the corresponding calls to cudaFree behave correctly. Simply partitioning the allocated buffer across threads is not viable because the corresponding calls to cudaFree will either attempt to free in the middle of the buffer which will fail, or free the entire buffer which would deallocate data that may still be in use by other threads. For this reason, the aggregated call to cudaMalloc not only partitions the allocated buffer across threads, but also stores some metadata in the buffer that is used by a transformed version of cudaFree to perform the deallocation correctly.

Figure 3.7(c) shows the metadata stored in the buffer containing the aggregated allocations. Upon allocation, metadata is initialized at the beginning of each sub-buffer in the aggregated buffer containing the **size** of the subbuffer as well as its **offset** from the beginning of the buffer. Metadata is

```

A

if(condition) {

B

kernel<<<gD, bD>>>(arg1, arg2, arg3);

C

}

(a) Original Divergent Kernel

A

gD = 0

if(condition) {

B

_gD = gD;

}

kernel<<<_gD, bD>>>(arg1, arg2, arg3);

D

(b) Divergence Elimination by Postponing Kernel Launch

```

Figure 3.8: Handling of Control Divergence

also initialized at the beginning of the entire buffer containing the used size which is the amount of space in the buffer that is still being used (initially, all of it). When cudaFree is called on each of the sub-buffers, the transformed call to cudaFree looks up the offset of the sub-buffer being freed, uses it to identify the location of the used size variable, and atomically decrements that variable by size. If used size reaches zero, then all the sub-buffers in the buffer have been freed, so the thread that last atomically decremented the counter then proceeds to free the entire buffer.

# 3.5 Handling of Control Divergence

For horizontal aggregation at warp and block granularity, all threads in the warp or block must be active to participate in the aggregation operations. These operations include the scan and maximum operations necessary to compute the aggregated grid's configurations. Moreover, the designated launcher thread must always be active to allocate from the memory pool as well as launch the aggregated grid on behalf of the other threads. This requirement does not exist when aggregation is applied at grid granularity since the scan and maximum operations are done in separate kernels or using atomics and the aggregated launch is performed from the host after the kernel terminates. The requirement that all threads are active to participate in aggregation operations is violated in the presence of control divergence. For this reason, the parent kernel is transformed to ensure that the child kernel is called at a point in the program when all threads are active. Therefore, the child kernel call is postponed to a later point in the parent kernel where there is no control divergence. These points in the program can be identified using the uniform variable analysis and divergence analysis described in Section 3.4.1. The transformation also requires that the kernel's launch configurations and arguments are preserved for use at the later launch point. An example of this transformation is shown in Figure 3.8. Since launches are asynchronous by default, performing this transformation is legal provided that there is no explicit synchronization (using cudaDeviceSynchronize()) by the parent thread between the launch's original and new location and that the launch is not taken outside of a loop.

## CHAPTER 4

# VERTICAL AGGREGATION

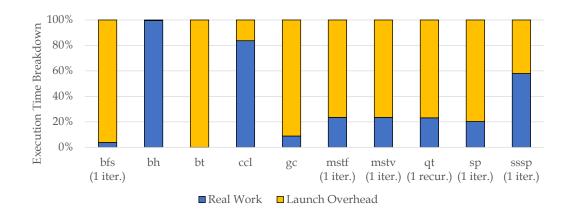

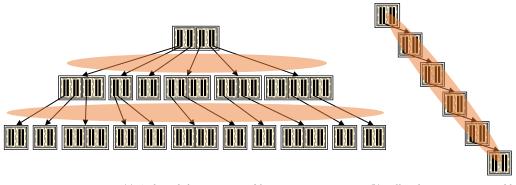

The horizontal aggregation transformation is good for wide and short call trees where many threads in the same parent grid launch child grids simultaneously. An example of such a call tree is shown in Figure 4.1(a). However, for tall and narrow call trees, such as that shown in Figure 4.1(b), horizontal aggregation is not useful because there are not many launches at each level of the tree to be aggregated. For this reason, another type of aggregation is proposed, which is vertical aggregation.

Vertical aggregation is a transformation whereby kernel launches are aggregated across different levels of the call tree. In other words, thread blocks of child grids are aggregated with the thread blocks of their parent grids. This requires target kernels to be recursive since aggregation must be applied to launches of the same kernel. In this work, a specific type of recursive kernel is targeted, namely data sliding kernels [4], which are producer-consumer kernels whereby each grid consists of a single thread block that is launched by its producer and that subsequently launches its consumer resulting in the most extreme version of a tall and narrow call tree such as that shown in Figure 4.1(b).

It is possible to implement data sliding kernels without dynamic parallelism using traditional atomic operations for inter-block wait and release flags [4]; however, these kinds of programs are difficult to write. Dynamic parallelism offers a more intuitive way to express these kinds of patterns. However, using dynamic parallelism has several issues: (1) there are many grid launches, (2) there are many small grids in flight, and (3) there is a deep call stack. Vertical aggregation aims to address these issues.

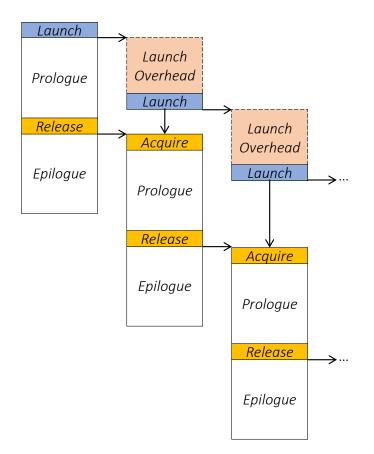

Throughout the explanation in this chapter as well as in the evaluation in Chapter 7, the transformation for vertical aggregation is broken down into multiple steps to better understand the workings of the transformation as well as the breakdown of its performance benefit. These steps are pro-

(a) Wide and short trees suitable for horizontal aggregation

(b) Tall and narrow trees suitable for vertical aggregation

Figure 4.2: Original Program

Figure 4.3: Promotion Transformation

motion (Section 4.1), aggregation (Section 4.2), overlap (Section 4.3), and aggregation with overlap (Section 4.4). Each step in the transformation is explained with reference to the baseline program shown in Figure 4.2. In this program, every thread block is considered to execute a prologue, launch the next thread block, and then execute an epilogue.

### 4.1 Launch Promotion

Promotion is the first step in the transformation whereby recursive kernel calls are hoisted to the beginning of the kernel body. Figure 4.3 illustrates the transformation that takes place when promotion is applied to the example in Figure 4.2. In the transformed code, the kernel call is moved to the beginning

of the kernel before the prologue. However, to preserve correct ordering in between the parent and child, code is inserted to *release* a flag that the child will *acquire* to know when it is safe to execute. In all but the first kernel instance (which is launched from the host), code is also inserted before the prologue to acquire the release from the parent. The main advantage of this step is that the launch overhead is removed from the critical path and replaced with a more lightweight release acquire chain. The launch is thus set up by the device runtime and the child thread blocks are scheduled on the SMs while the parent thread block executes the prologue and before it reaches the release operation.

Figure 4.4 shows in pseudocode the code transformation that takes place to achieve kernel launch promotion. The target pattern of the original kernel is shown in Figure 4.4(a). The pattern is such that the kernel executes some prologue code, then selects a single launcher thread to perform a kernel launch, then executes an epilogue code. The kernel launch must be configured to have a single thread block. Moreover, the parameters/arguments of the kernel can be classified into two categories. The first category is the available parameters/arguments which are those that are available at the beginning of the kernel before the prologue. The second category is the postponed parameters/arguments which are those that are not available until after the prologue.

The kernel in Figure 4.4(a) is transformed to two different versions, one called from the host and one called recursively from the device, shown in Figures 4.4(b) and (c) respectively. In the kernel called from the host in Figure 4.4(b), the transformation is as follows. First, code is inserted before the prologue for the launcher thread to perform the launch prematurely. The launcher thread starts by allocating buffers (line 10) to be passed to the child grid where the postponed arguments will be stored later once they become available. The launcher thread also allocates a flag that is used by the parent to communicate with the child to release it when its data is ready (line 11). The child is then launched prematurely (lines 12-13) with the available arguments kept as they are and the postponed arguments replaced with their corresponding buffers. Performing a premature launch requires that any launch condition (not shown in the figure) also be promotable to the beginning of the kernel before the epilogue. In cases where the condition is not promotable because it is dependent on the prologue, the launch can be

```

args<sub>avail</sub> : arguments available at the beginning of the kernel

: arguments whose values are "postponed" because they

args<sub>post</sub>

are not available at the beginning of the kernel

params<sub>avail</sub> : parameters corresponding to available arguments

params<sub>post</sub> : parameters corresponding to postponed arguments

__global___void kernel(params<sub>avail</sub>, params<sub>post</sub>) {

01

02

prologue

03

if(launcher thread) {

kernel<<<1,nThreads>>>(args<sub>avail</sub>, args<sub>post</sub>)

04

05

06

epilogue

07

}

(a) Original Kernel

08

__global___ void kernel(params<sub>avail</sub>, params<sub>post</sub>) {

09

if(launcher thread) {

10

allocate postponed arg buffers

11

allocate child flag

kernel_from_kernel<<<1,nThreads>>>

12

(args<sub>avail</sub>, postponed arg buffers, child flag)

13

}

14

15

prologue

16

if(launcher thread) {

17

store \mathtt{args}_{\mathtt{post}} in postponed arg buffers

18

memory fence

19

set child flag to release child

20

}

21

epilogue

22

}

(b) Transformed Kernel (called from host)

23

global void kernel_from_kernel(params<sub>avail</sub>,

24

postponed param buffers, flag) {

25

if(launcher thread) {

26

allocate postponed arg buffers

27

allocate child flag

28

kernel from kernel <<<1, nThreads>>>

29

(args<sub>avail</sub>, postponed arg buffers, child flag)

30

}

31

wait to acquire flag

32

load params post from postponed param buffers

33

prologue

34

if(launcher thread) {

store \mathtt{args}_{\mathtt{post}} in postponed arg buffers

35

memory fence

36

37

set flag to release child

38

}

39

epilogue

40

}

(c) Transformed Kernel (called from kernel)

```

Figure 4.4: Code Generation for Basic Promotion

performed speculatively and an abort signal can be sent instead of a release signal to abort trailing launches.

After the child grid is launched prematurely, the prologue is executed normally. At the end of the prologue, the values of the postponed arguments become available so the launcher thread stores these variables in the postponed argument buffers previously allocated (line 17). A memory fence is then executed to ensure that these values become visible to the child grid before it is released (line 18). Finally, the flag is set to be released (line 19) which signals to the child that it is safe to start executing. The release is implemented in CUDA as a non-cached store while the acquire is implemented as a polling loop with a volatile load. In OpenCL 2.0 [25], it is also possible to use built-in support for release and acquire. After the child is released, the execution of the epilogue continues normally.

The second version of the transformed kernel is the one intended to be launched from the device. The transformation is shown in Figure 4.4(c). The transformation is largely similar to that in Figure 4.4(b) with a few essential differences. One difference is that postponed parameters are replaced with parameter buffers and a flag parameter is also added to the parameter list (line 24). Another difference is that between the premature child launch and the prologue, a wait is inserted to make sure that a child thread block waits for its parent thread block to release it before executing its prologue (lines 31). After the thread block is released, it also loads the postponed parameters from the parameter buffers.

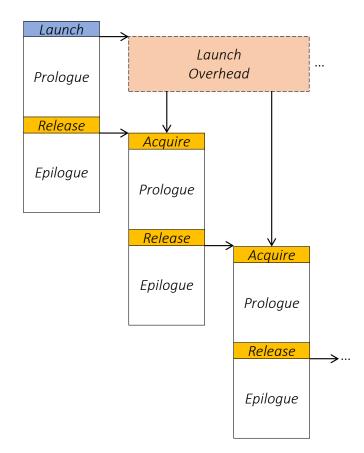

#### 4.2 Vertical Aggregation

After kernel launches are promoted, they pave the way for two orthogonal optimizations: vertical aggregation and overlap of independent portions of the prologue. This section discusses how promotion enables vertical aggregation to be applied.

Figure 4.5 illustrates the transformation that takes place when aggregation is applied to the promoted kernel launch. The main difference between this version and the previous version with just promotion illustrated in Figure 4.3 is that the chain of single thread block launches is replaced with a single launch of a large pool of descendant thread blocks. The launching

Figure 4.5: Promotion with Vertical Aggregation Transformation

thread block also allocates buffers and flags for all of its descendants in the aggregated grid as opposed to just its immediate descendant.

The size of the aggregated descendant pool defines the granularity of vertical aggregation. Large pools imply more aggregation, therefore fewer launches and larger kernels with better occupancy. They also imply longer chains of thread blocks since the depth of the original call stack is divided by the granularity of aggregation. If the pool of descendants is exhausted, the last descendant in the pool launches a new pool. If the last thread block in the chain is reached and the pool is not yet exhausted, then the final descendant is responsible for sending an abort message for all tail thread blocks in the pool to terminate. However, until the abort message is sent, these thread blocks will occupy resources unnecessarily. Larger pools result in larger tails, hence more unnecessary resource usage and longer tail abortion time. One important consideration during aggregation is that parent thread blocks in the aggregated pool of descendants must be scheduled before their child thread blocks. Otherwise, deadlock may occur where descendants are scheduled before their ancestors and are waiting for their ancestors to release them, while the ancestors cannot be scheduled because their descendants are occupying the GPU resources. Since software has no control over the order in which thread blocks are scheduled, the static block indices cannot be used. Instead, the index of the thread block within the pool of descendants is assigned dynamically after the thread block is scheduled [26], which ensures that parent thread blocks are always scheduled before their children.

There are multiple benefits of applying the vertical aggregation step. First, the number of grid launches is reduced which results in less launch overhead incurred. Second, the sizes of the grids are increased which results in better utilization of the device. Third, the architectural limitation of the depth of descent is mitigated because the depth of the call stack is divided by a factor equal to the aggregation granularity (size of the descendant pool).

#### 4.3 Overlapping Parents and Children

Another optimization enabled by promotion of kernel launches is the overlap of independent portions of the prologue. This optimization is orthogonal to aggregation so it is described independently in this section. In the next section, aggregation and overlap are combined together.

The overlap optimization is based on the observation that portions of the prologue of a child kernel can be executed independently from the parent. The prologue can thus be divided into two portions: an independent prologue and a dependent prologue. Informally, this independent prologue must satisfy two conditions: (1) it must not use any postponed parameters and (2) it must not have any data dependence with the prologue of the parent. If these two conditions are met, then this portion of the prologue can be executed in parallel with the parent before it releases the child.

The transformation that takes place to achieve the overlap step is shown in Figure 4.6. In this transformation, the prologue is divided into two regions – the independent region and dependent region – and the independent region is hoisted before the acquire logic. If the independent region of the  $j^{th}$  block

Figure 4.6: Promotion with Overlap Transformation

in the chain is denoted as  $P_{i,j}$ , the dependent region is denoted as  $P_{d,j}$ , and the entire prologue is denoted as  $P_j$ , then for this transformation to legal, it must satisfy the conditions that:  $P_j$  does not write to any memory referenced by  $P_{i,j+n}$ , and  $P_{i,j+n}$  does not write to any memory referenced by  $P_j$  where n > 0. A simple programmer annotation is used to indicate the boundary between the independent and dependent regions of the prologue. However, dataflow analysis can also be used to detect these regions in many cases.

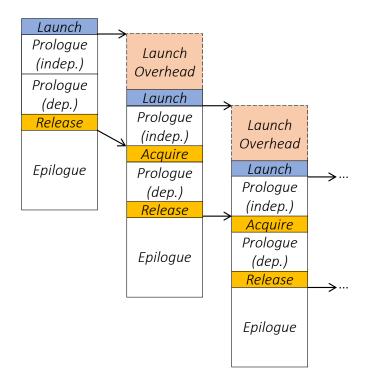

## 4.4 Combining Vertical Aggregation and Overlapping

As mentioned earlier, aggregation and overlap are orthogonal optimizations. Putting the three steps together – promotion, aggregation, and overlap –

Figure 4.7: Promotion with Vertical Aggregation and Overlap

gives the complete vertical aggregation transformation proposed in this work. This transformation is illustrated in Figure 4.7.

The topmost parent thread block launches a pool of descendant thread blocks and releases its immediate child after it completes its own prologue. The subsequent children synchronize with each other using two release-acquire chains. In the first release-acquire chain, a thread block checks if it must launch a descendant. If yes, it either sends a release signal to the next child in the descendant pool or launches a new pool if the pool has been exhausted. If no, it sends an abort signal to its descendants. If the descendant receives a release, it proceeds. If it receives an abort, it forwards the abort to the rest of its descendants and terminates.

Once a thread block has been released by the first release-acquire chain, it executes the independent part of the prologue and that waits to be released

Figure 4.8: Tradeoffs of Vertical Aggregation Steps

by its parent as part of the second chain. Once released by the parent, it executes the dependent part of the prologue, sends a release signal to its child (except for the final thread block in the chain), and then executes its epilogue and terminates.

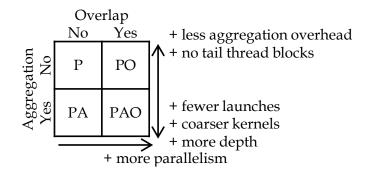

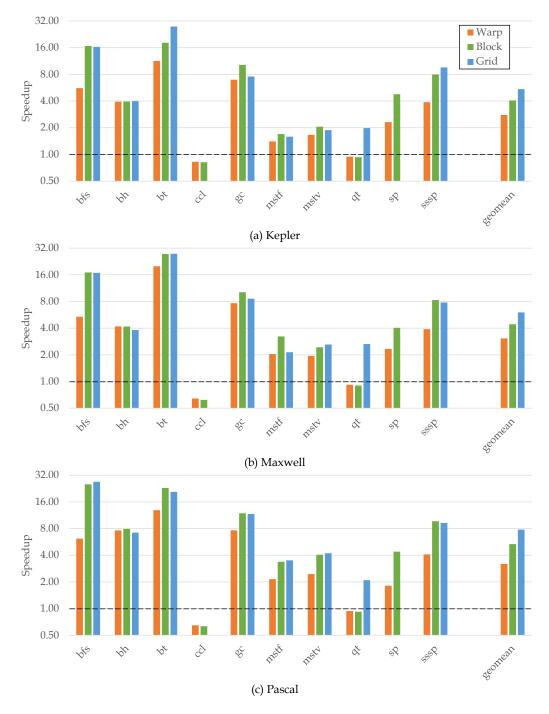

#### 4.5 Advantages and Tradeoffs

The advantages of promotion compared to no promotion are that it removes the launch from the critical path and replaces it with lightweight release acquire chains. The disadvantages are that it holds onto processing resources for a longer amount of time as child thread blocks busy-wait until they are released by their parents. While these resources are not used by the transformed kernel itself for anything else, they may be useful to other kernels in co-run scenarios.

The advantages and tradeoffs of vertical aggregation and overlap are summarized in Figure 4.8. The advantages of aggregation are that it reduces the number of kernels, increases their granularity, and reduces the depth of the call stack as explained previously. The disadvantage is that it results in additional aggregation overhead as well as unnecessary tail thread blocks that waste resources. The advantage of overlap is that it extracts more parallelism from the long serial dependence chain.

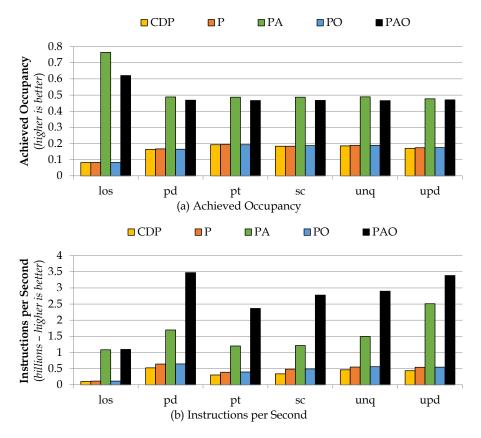

Figure 4.8 also defines acronyms for the different versions of the transformation (P, PA, PO, PAO) based on what combinations of optimizations are applied. The same acronyms are used in the evaluation in Chapter 7.

## CHAPTER 5

# METHODOLOGY AND IMPLEMENTATION

### 5.1 Benchmarks

#### 5.1.1 Horizontal Aggregation Benchmarks

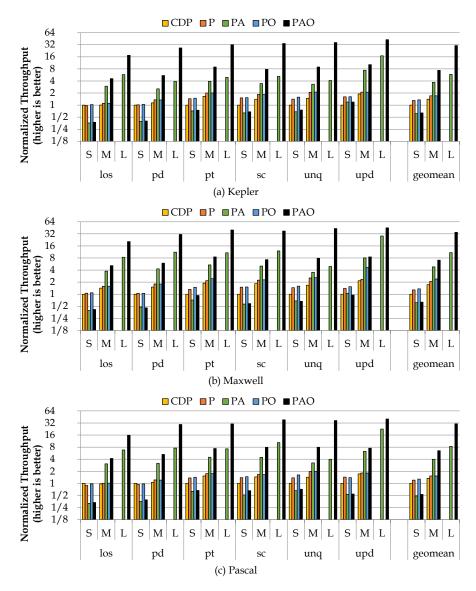

Table 5.1 shows the benchmarks and datasets used in the evaluation of the horizontal aggregation transformation. Some of the benchmarks (bt, ccl, qt) use CUDA Dynamic Parallelism (CDP) in the original version of the benchmark. The rest were converted to using CDP from original versions that used nested loops to loop over work sequentially within each thread. For example, in the *bfs* benchmark, the loop over the neighbors of a node is converted to a kernel launch with one thread in the launched grid processing each neighbor.

For all benchmarks, private streams are used by each thread to ensure that launches by threads in the same thread block are not placed in the same stream and serialized which is the default semantic [33]. Using private streams makes the baseline CDP versions faster than serializing in the default stream (geometric mean  $1.90 \times$  on Kepler and  $1.83 \times$  on Maxwell). Using private streams is also essential for the benchmarks to be amenable to horizontal aggregation; otherwise, aggregation parallelizes kernels that should be serialized according to the default semantic. Moreover, cudaDeviceSetLimit is used to adjust the fixed-size pool of the pending launch buffer appropriately for the baseline CDP version. Without the right size, the cost of overflowing the launch buffer pool penalizes the execution time of the baseline versions [34]. By using private streams and setting the fixed-size pool appropriately, the baseline CDP versions are made as efficient as they can be to ensure a fair comparison.

| Name | Description             | Dataset                       | Block Sizes |

|------|-------------------------|-------------------------------|-------------|

| bfs  | Breadth First           | Random, 10000 nodes           | parent=1024 |

|      | Search [27]             | 1000 degree                   | child=32    |

| bh   | Barnes Hut Tree [28]    | 4096 bodies, 4 time-steps     | parent=256  |

|      |                         |                               | child=256   |

| bt   | Bezier Lines            | 25600 lines                   | parent=64   |

|      | Tessellation [29]       |                               | child=32    |

| ccl  | Connected Component     | 8 frames, 4 host streams      | parent=2    |

|      | Labelling [30]          |                               | child=256   |

| gc   | Graph Coloring [31]     | 1 4096 0.01                   | parent=256  |

|      |                         | bcsstk13.mtx [32]             | child=256   |

| mstf | Minimum Spanning        | rmat12.sym.gr [28]            | parent=1024 |

|      | Tree (find) $[28]$      |                               | child=1024  |

| mstv | Minimum Spanning        | rmat12.sym.gr [28]            | parent=1024 |

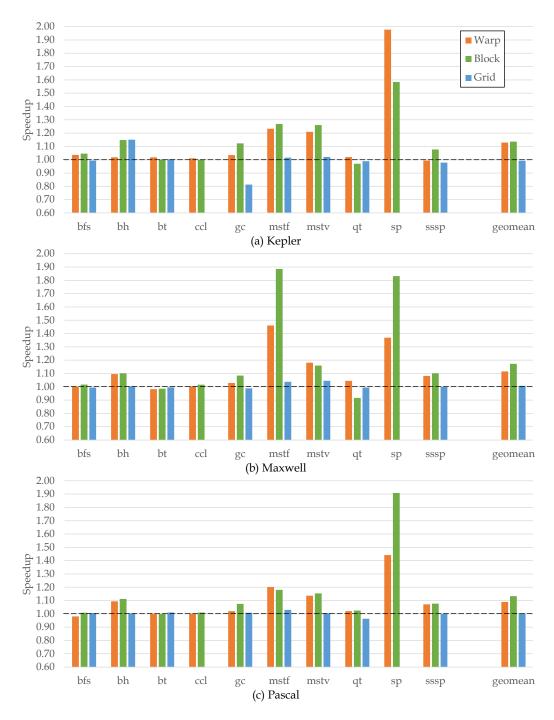

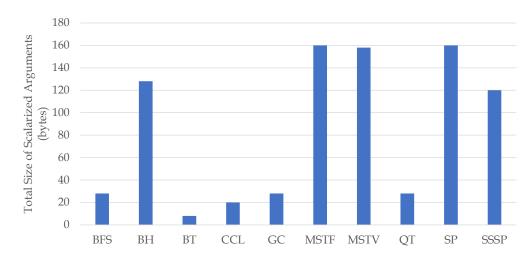

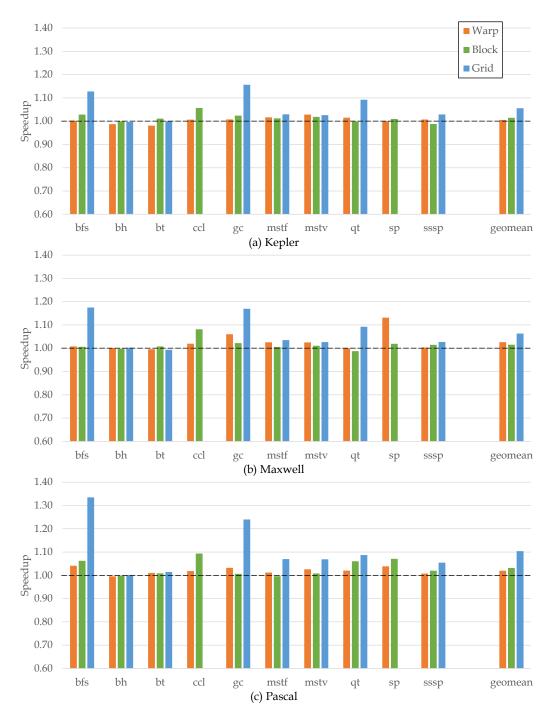

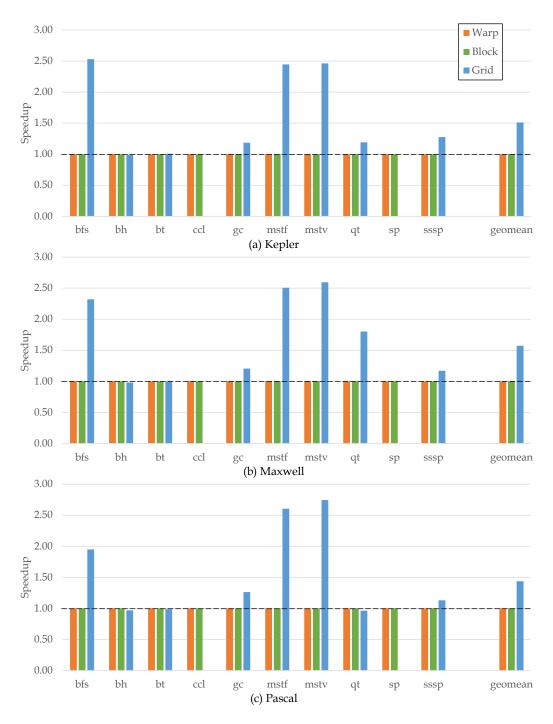

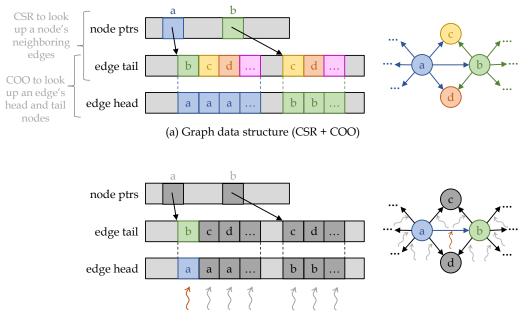

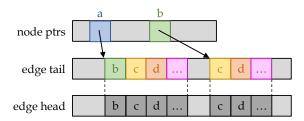

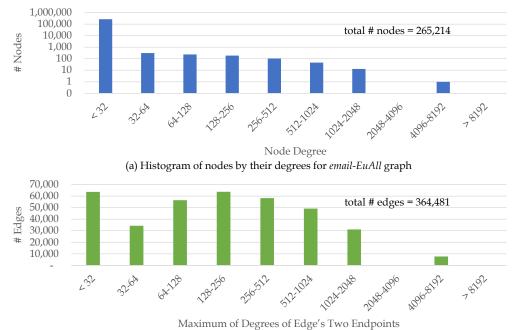

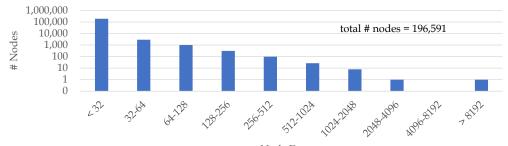

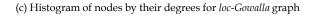

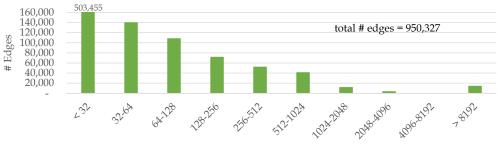

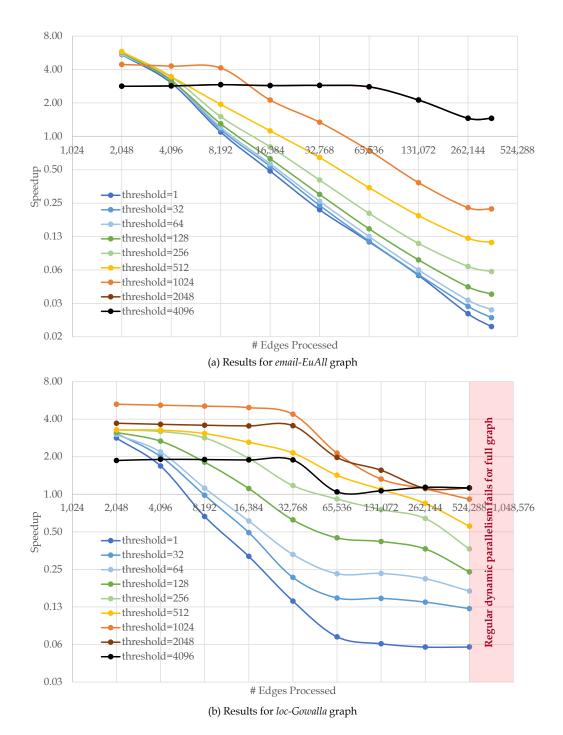

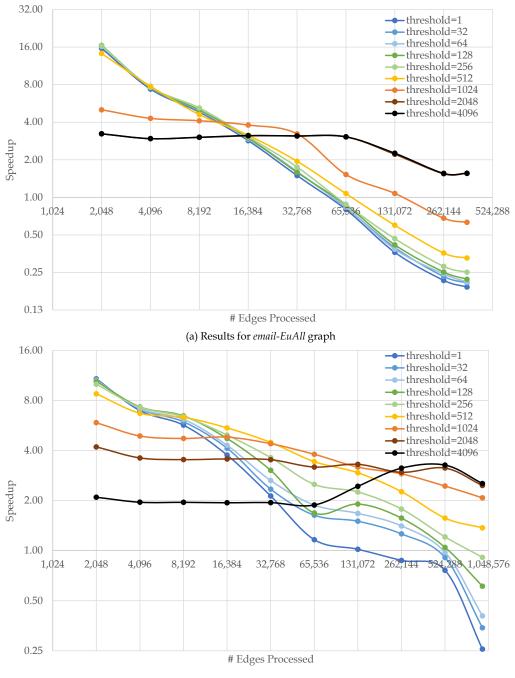

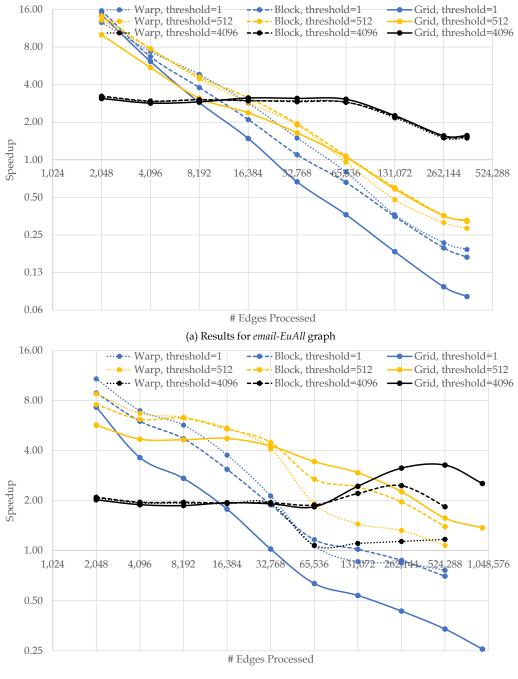

|      | Tree (verify) [28]      |                               | child=1024  |