# RIGOROUS CODE GENERATION FOR DISTRIBUTED REAL-TIME EMBEDDED SYSTEMS

#### ALI ALMOHAMMAD

PhD

## RIGOROUS CODE GENERATION FOR DISTRIBUTED REAL-TIME EMBEDDED SYSTEMS

#### ALI ALMOHAMMAD

A thesis submitted in partial fulfilment of the requirements of the University of Northumbria at Newcastle for the degree of Doctor of Philosophy

Research undertaken in the Faculty of Engineering and Environment

September 2013

This thesis is dedicated to Khuzama Mobark and Isaa Almohammad.

#### ABSTRACT

This thesis addresses the problem of generating executable code for distributed embedded systems in which computing nodes communicate using the Controller Area Network (CAN). CAN is the dominant network in automotive and factory control systems and is becoming increasingly popular in robotic, medical and avionics applications. The requirements for functional and temporal reliability in these domains are often stringent, and testing alone may not offer the required level of confidence that systems satisfy their specifications. Consequently, there has been considerable research interest in additional techniques for reasoning about the behaviour of CAN-based systems. This thesis proposes a novel approach in which system behaviour is specified in a high-level language that is syntactically similar to Esterel but which is given a formal semantics by translation to bCANDLE, an asynchronous process calculus. The work developed here shows that bCANDLE systems can be translated automatically, via a common intermediate net representation, not only into executable C code but also into timed automaton models that can be used in the formal verification of a wide range of functional and temporal properties. A rigorous argument is presented that, for any system expressed in the high-level language, its timed automaton model is a conservative approximation of the executable C code, given certain well-defined assumptions about system components. It is shown that an off-the-shelf model-checker (UPPAAL) can be used to verify system properties with a high-level of confidence that those properties will be exhibited by the executable code. The approach is evaluated by applying it to four representative case studies. Our results show that, for small to medium-sized systems, the generated code is sufficiently efficient for execution on typical hardware and the generated timed automaton model is sufficiently small for analysis within reasonable time and memory constraints.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude and thanks to my supervisors Dr David Kendall and Dr William Henderson. I have been fortunate to do this work supervised by such an excellent team. I should acknowledge that without their generous support, this work would not have been completed.

I would like to thank my colleagues in Lab F7, Pandon Building, School of Computing, for the friendly and kindly atmosphere provided.

I would like also to thank my scholarship sponsor, the ministry of higher education, Syria, for the financial support of my study.

I am grateful, last but not least, to my family, without their loving support and encouragement, I would have given up long ago.

#### **DECLARATION**

| I declare that the work contained in this thesis has not been submitted for any |

|---------------------------------------------------------------------------------|

| other award and that it is all my own work. I also confirm that this work fully |

| acknowledges opinions, ideas and contributions from the work of others. Any     |

| ethical clearance for the research presented in this thesis has been approved.  |

| Approval has been sought and granted by the School Ethics Committee on 17th     |

| December 2008. I also confirm that the thesis is (40,725) words in length.      |

Name: Ali Almohammad

Signature:

Date:

#### CONTENTS

| 1. | Intr | oduction and Overview              | 1 |

|----|------|------------------------------------|---|

|    | 1.1  | Embedded System                    | 1 |

|    | 1.2  | Real-time Embedded System          | 1 |

|    | 1.3  | Distributed Embedded System        | 3 |

|    | 1.4  | Formal Methods                     | 6 |

|    | 1.5  | Related Work                       | 7 |

|    |      | 1.5.1 Synchronous Approach         | 8 |

|    |      | 1.5.2 Scheduling Analysis Approach | 0 |

|    |      | 1.5.3 Other Approaches             | 2 |

|    | 1.6  | The Dissertation                   | 4 |

|    |      | 1.6.1 Justification                | 4 |

|    |      | 1.6.2 Structure and Contributions  | 4 |

| 2. | Met  | shods, Techniques and Tools 1      | 7 |

|    | 2.1  | Overview of the Approach           | 7 |

|    | 2.2  | System Characteristics             | 8 |

|    | 2.3  | The bCANDLE Modelling Language     | 0 |

|    |      | 2.3.1 Data Model                   | 1 |

| Co | onten | $\mathbf{ts}$ |                                       | viii |

|----|-------|---------------|---------------------------------------|------|

|    |       | 2.3.2         | Network Model                         | 22   |

|    |       | 2.3.3         | Process Model                         | 27   |

|    |       | 2.3.4         | Example of bCANDLE                    | 28   |

|    | 2.4   | The N         | et: The intermediate model of bCANDLE | 31   |

|    |       | 2.4.1         | Definitions and Notation              | 32   |

|    |       | 2.4.2         | Behaviour                             | 34   |

|    |       | 2.4.3         | Example of Net Behaviour              | 36   |

|    | 2.5   | The T         | ranslation of bCANDLE to Net          | 36   |

|    | 2.6   | The C         | ANDLE Programming Language            | 39   |

|    | 2.7   | The Th        | ranslation of CANDLE to bCANDLE       | 43   |

|    | 2.8   | Summ          | ary                                   | 46   |

| 3. | CA    | NDLE          | Code Generator                        | 47   |

|    | 3.1   | Introd        | uction                                | 47   |

|    | 3.2   | The In        | mplementation Model                   | 48   |

|    |       | 3.2.1         | Features and Notation                 | 48   |

|    |       | 3.2.2         | Comparison with Other Models          | 50   |

|    |       | 3.2.3         | Scheduling                            | 53   |

|    | 3.3   | Repres        | sentation of the Net                  | 57   |

|    |       | 3.3.1         | Data Representation                   | 57   |

|    |       | 3.3.2         | Overview of ISR Implementation        | 65   |

|    | 3.4   | Impler        | mentation of Channel                  | 69   |

|    |       | 3.4.1         | External Channel                      | 71   |

| Contents | ix |  |

|----------|----|--|

|          |    |  |

|    |     | 3.4.2 Local Channel                 | 72 |

|----|-----|-------------------------------------|----|

|    | 3.5 | Representation of the Architecture  | 72 |

|    | 3.6 | Summary                             | 76 |

| 4. | Cor | rectness of System Implementation   | 77 |

|    | 4.1 | Introduction                        | 77 |

|    | 4.2 | Computation Release and Termination | 78 |

|    |     | 4.2.1 Internal Computations         | 78 |

|    |     | 4.2.2 Observable Computations       | 80 |

|    |     | 4.2.3 Delay                         | 81 |

|    |     | 4.2.4 Response-Time Analysis        | 82 |

|    | 4.3 | Guard Evaluation                    | 85 |

|    | 4.4 | Message Reception                   | 85 |

|    |     | 4.4.1 Receive Buffers               | 86 |

|    |     | 4.4.2 Reception Readiness           | 86 |

|    |     | 4.4.3 Reception Order               | 88 |

|    | 4.5 | Message Transmission                | 91 |

|    |     | 4.5.1 Transmission Readiness        | 91 |

|    |     | 4.5.2 Multiple Ready Transmissions  | 93 |

|    | 4.6 | Process Combinators                 | 94 |

|    | 4.7 | Summary                             | 95 |

| 5. | Ato | mic Update of Data                  | 96 |

|    | 5.1 | The Interrupt Operator              | 96 |

| Contents |  | x |

|----------|--|---|

|          |  |   |

|    | 5.2 | The problem of the Interrupt Operator                 |  |  |  |

|----|-----|-------------------------------------------------------|--|--|--|

|    | 5.3 | Related Work                                          |  |  |  |

|    | 5.4 | The Proposed Solution Ensuring Atomic Update 102      |  |  |  |

|    |     | 5.4.1 Worst-Case Response Analysis                    |  |  |  |

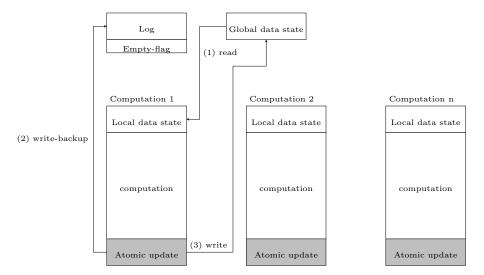

|    |     | 5.4.2 Atomic Update Methods                           |  |  |  |

|    | 5.5 | Evaluation and Discussion                             |  |  |  |

|    | 5.6 | Summary                                               |  |  |  |

| 6. | Eva | uation and Experiments                                |  |  |  |

|    | 6.1 | Introduction                                          |  |  |  |

|    | 6.2 | Case Studies                                          |  |  |  |

|    |     | 6.2.1 Flow Regulator System                           |  |  |  |

|    |     | 6.2.2 Steam Boiler Control System                     |  |  |  |

|    |     | 6.2.3 Security Alarm System                           |  |  |  |

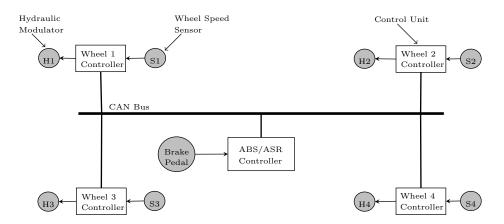

|    |     | 6.2.4 ABS/ASR System                                  |  |  |  |

|    | 6.3 | Performance Evaluation                                |  |  |  |

|    | 6.4 | Formal Verification                                   |  |  |  |

|    |     | 6.4.1 Model Checking Properties                       |  |  |  |

|    |     | 6.4.2 Verifying Transmit/Receive Buffer Resources 142 |  |  |  |

|    | 6.5 | Summary                                               |  |  |  |

| 7. | Con | clusions and Future Work                              |  |  |  |

|    | 7.1 | Summary of Contributions                              |  |  |  |

|    | 7.2 | Limitations                                           |  |  |  |

| Conte | nts xi                      |

|-------|-----------------------------|

| 7.3   | Future Work                 |

| Apper | ndix 158                    |

| A. Ca | se <b>Studies</b>           |

| A.1   | Flow Regulator System       |

| A.2   | Steam Boiler Control System |

| A.3   | Security Alarm System       |

| A.4   | Anti-lock Braking System    |

| B. UF | PAAL Models                 |

| В.1   | The CAN Communication Model |

| B.2   | Flow Regulator System Model |

|       |                             |

#### LIST OF FIGURES

| 1.1 | Flow Regulator System                               | 3  |

|-----|-----------------------------------------------------|----|

| 1.2 | CAN Frame - Standard Format                         | 4  |

| 2.1 | Overview of Code and Model Generation Approach.     | 10 |

|     | Work done as part of this thesis is shown in bold   | 19 |

| 2.2 | Distributed Embedded System (Kendall, 2001b)        | 20 |

| 2.3 | Network Transition Rules                            | 26 |

| 2.4 | Example of network behaviour                        | 27 |

| 2.5 | Flow regulator in bCANDLE.                          | 29 |

| 2.6 | Net of the flow regulator example                   | 32 |

| 2.7 | Rules for fire                                      | 35 |

| 2.8 | Example of net behaviour                            | 37 |

| 2.9 | Flow regulator in CANDLE                            | 40 |

| 3.1 | Features and notation of the implementation model   | 49 |

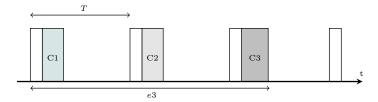

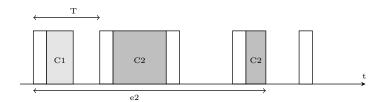

| 3.2 | Simple round-robin scheduling of short computations | 54 |

| 3.3 | Cooperative scheduling of short computations        | 55 |

| 3.4 | Pure round-robin scheduling                         | 55 |

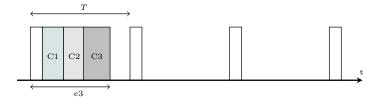

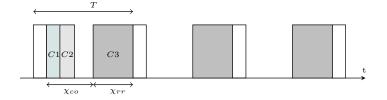

| 3.5 | Weighted round-robin scheduling                     | 56 |

| List of Figures xiii |                                                                                                                                                     |    |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 3.6                  | Example of hybrid scheduling                                                                                                                        | 56 |  |

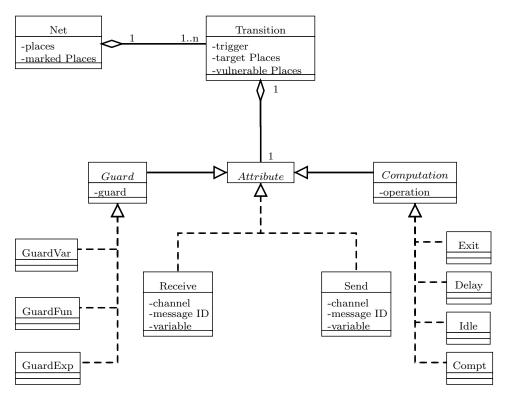

| 3.7                  | Net architecture in UML                                                                                                                             | 58 |  |

| 3.8                  | Transition Structure                                                                                                                                | 60 |  |

| 3.9                  | Modified flow regulator in CANDLE                                                                                                                   | 63 |  |

| 3.10                 | Nets of the modified flow regulator example                                                                                                         | 64 |  |

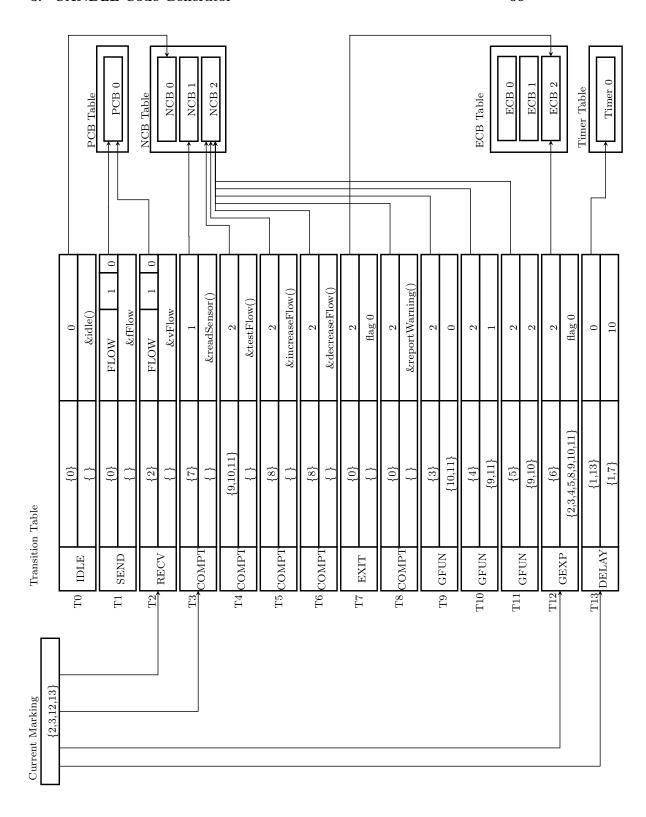

| 3.11                 | Example of transition table                                                                                                                         | 66 |  |

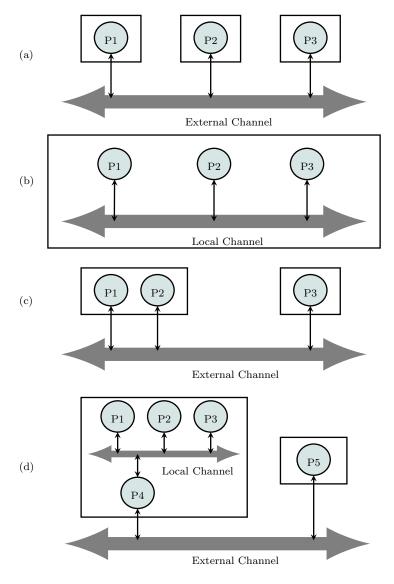

| 3.12                 | Processes-to-nodes mapping                                                                                                                          | 70 |  |

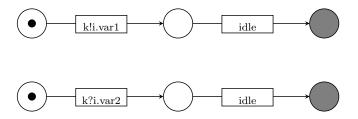

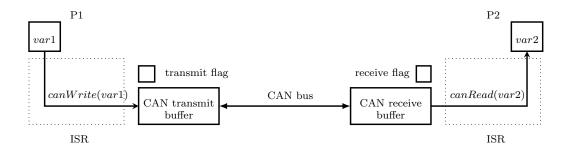

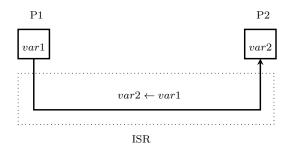

| 3.13                 | The bCANDLE model of simple send/receive example                                                                                                    | 71 |  |

| 3.14                 | The Net of simple send/receive example                                                                                                              | 71 |  |

| 3.15                 | P1 communicates with P2 by external channel                                                                                                         | 72 |  |

| 3.16                 | P1 communicates with P2 by local channel                                                                                                            | 73 |  |

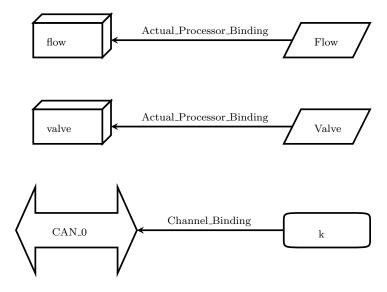

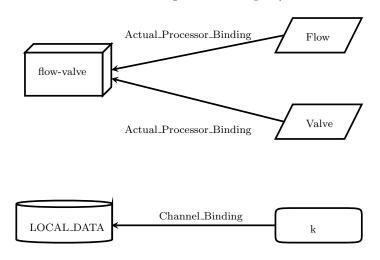

| 3.17                 | The architecture description of the flow regulator example                                                                                          | 74 |  |

| 3.18                 | The AADL of the flow regulator example (distributed architecture). $ \\$                                                                            | 75 |  |

| 3.19                 | The AADL of the flow regulator example (single-node architec-                                                                                       |    |  |

|                      | ture)                                                                                                                                               | 75 |  |

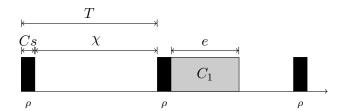

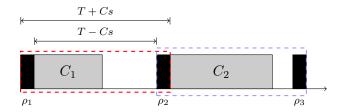

| 4.1                  | Internal computation bounds ( $we(C_1) \le \chi$ )                                                                                                  |    |  |

|                      | $[C_1: T-Cs, T+Cs]; [C_2: T-Cs, T+Cs]$                                                                                                              | 79 |  |

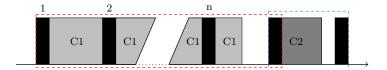

| 4.2                  | Internal computation bounds $(we(C_1) > \chi)$                                                                                                      |    |  |

|                      | $[C_1: n.T - Cs, n.T + Cs]; [C_2: T - Cs, T + Cs]. \dots$                                                                                           | 80 |  |

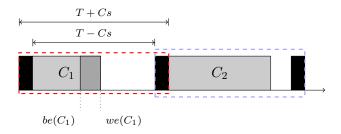

| 4.3                  | Observable computation bounds $(C_1 \in \mathcal{O}, C_2 \in \mathcal{I})$<br>$([C_1 : be(C_1), we(C_1)]; idle[>[T-Cs, T+Cs]); [C_2 : T-Cs, T+Cs].$ | 90 |  |

| 4.4                  |                                                                                                                                                     | 30 |  |

| 4.4                  | Delay bounds $(elapse(microseconds(5500)), T = 2 ms$<br>, $[3T - Cs, 3T + Cs]$                                                                      | 82 |  |

List of Figures xiv

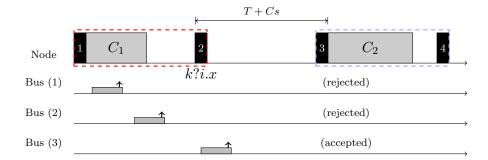

| 4.5  | Message reception (↑ denotes the message acceptance point)   |

|------|--------------------------------------------------------------|

|      | $[C_1: T-Cs, T+Cs]; k?i.x; [0, T+Cs]; [C_2: T-Cs, T+Cs].$ 87 |

| 4.6  | Example of message reception in a gateway node 89            |

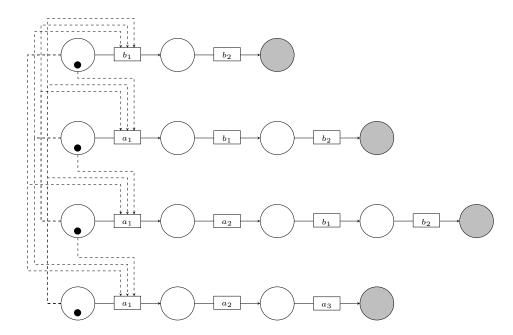

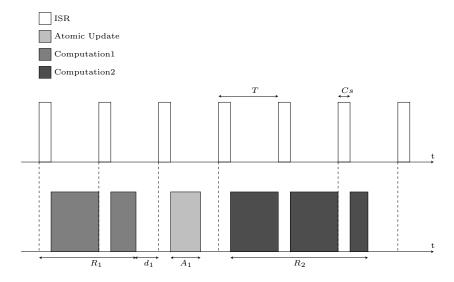

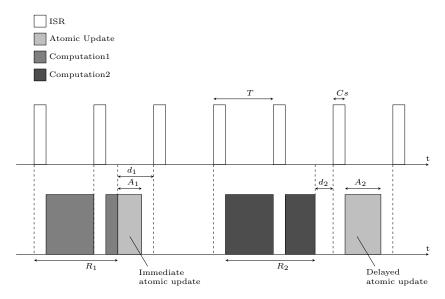

| 5.1  | Net of the interrupt expression                              |

| 5.2  | Net of the choice expression                                 |

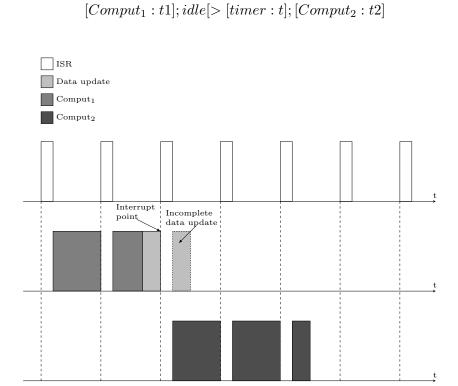

| 5.3  | Interrupt problem                                            |

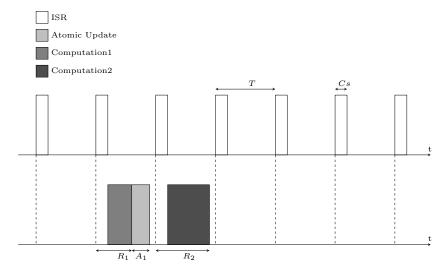

| 5.4  | Method(1): One-tick duration computation                     |

| 5.5  | Method(2): Computation disables interrupts                   |

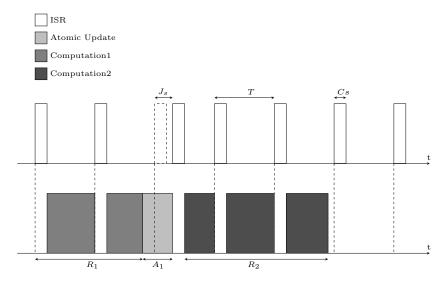

| 5.6  | Method(3): Update data inside the interrupt handler 109      |

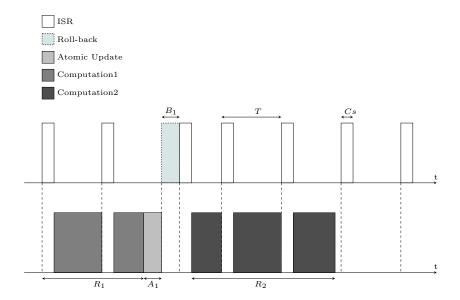

| 5.7  | Roll-back mechanism                                          |

| 5.8  | Method(4): Update data with roll-back                        |

| 5.9  | Method(5): Delayed atomic update                             |

| 5.10 | Method(6): Update now or delay update                        |

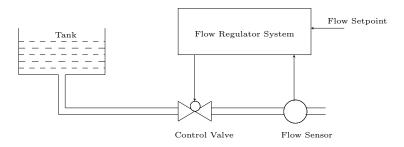

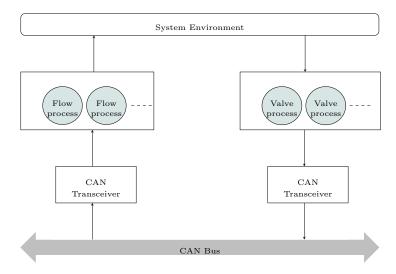

| 6.1  | Flow Regulator System                                        |

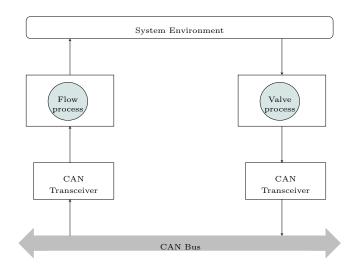

| 6.2  | Architecture of the flow regulator system                    |

| 6.3  | Architecture of the modified flow regulator system           |

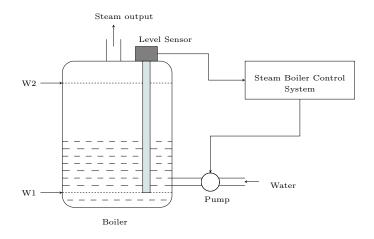

| 6.4  | Steam Boiler Control System                                  |

| 6.5  | Architecture of the steam boiler control system              |

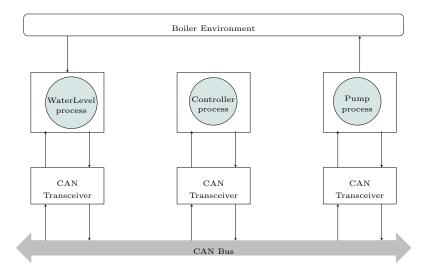

| 6.6  | Security Alarm System                                        |

| 6.7  | Architecture of the security alarm system                    |

| 6.8  | ABS/ASR Control System                                       |

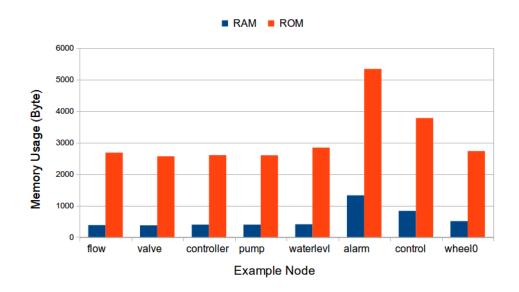

| 6.9  | RAM vs. ROM memory usage of the case studies                 |

| List | of Figures | XV |

|------|------------|----|

|      |            |    |

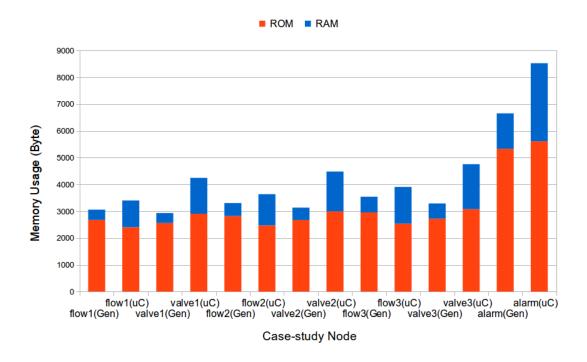

| 6.10 | Memory usage comparison                                               |  |

|------|-----------------------------------------------------------------------|--|

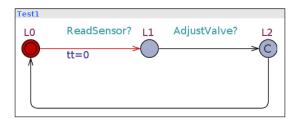

| 6.11 | Test automaton of the property P1.2 of the flow regulator example.134 |  |

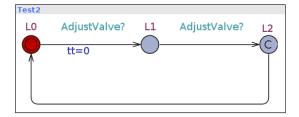

| 6.12 | Test automaton of the property P1.3 of the flow regulator example.136 |  |

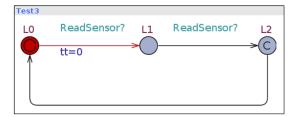

| 6.13 | Test automaton of the property P1.4 of the flow regulator example.137 |  |

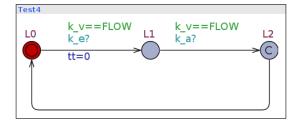

| 6.14 | Test automaton of the property P1.5 of the flow regulator example.138 |  |

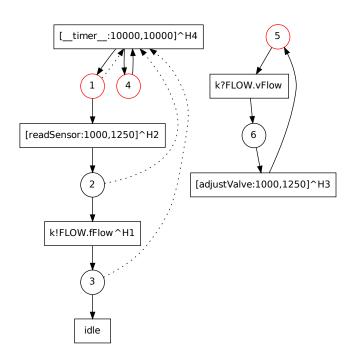

| 6.15 | Test automaton of receive buffer verification                         |  |

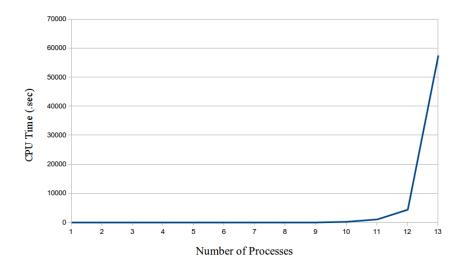

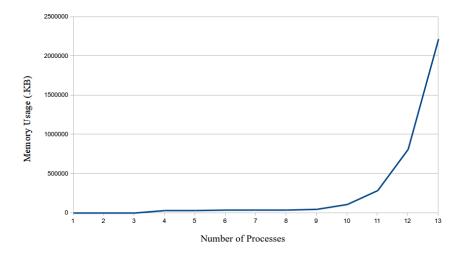

| 6.16 | Time complexity of receive buffer verification                        |  |

| 6.17 | Space complexity of receive buffer verification                       |  |

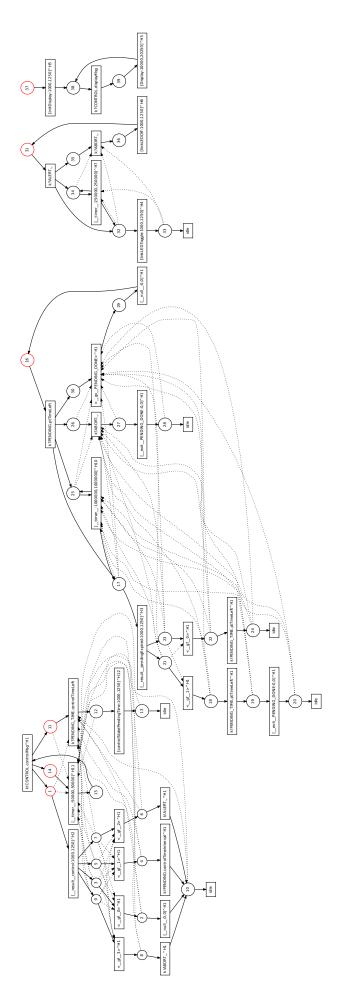

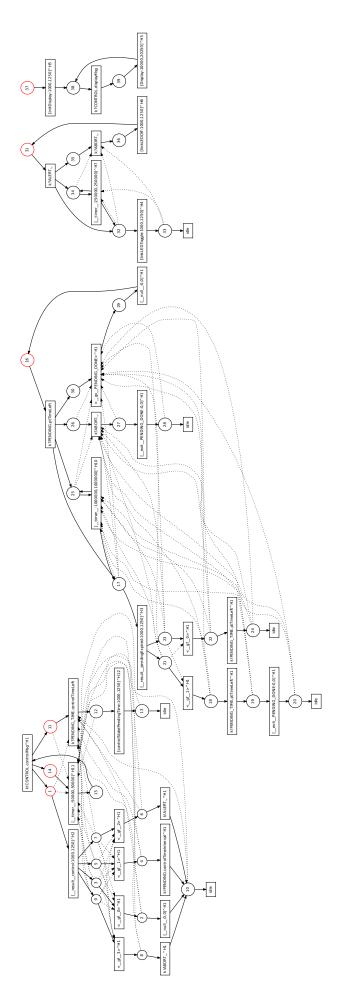

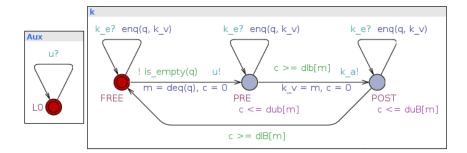

| B.1  | The UPPAAL model of the CAN communication                             |  |

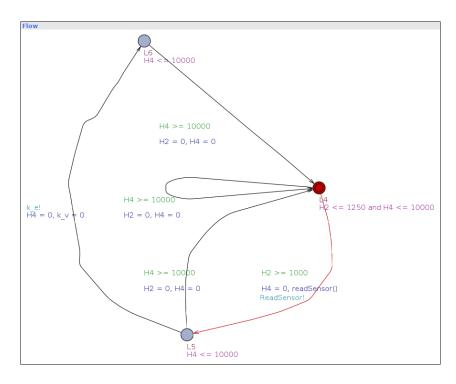

| B.2  | The UPPAAL model of the <i>Flow</i> process                           |  |

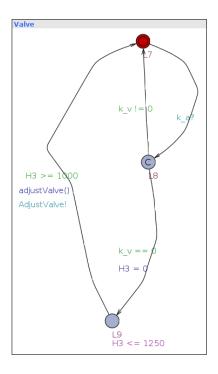

| B.3  | The UPPAAL model of the <i>Valve</i> process                          |  |

#### LIST OF TABLES

| 1.1  | CAN frame fields                                                  |

|------|-------------------------------------------------------------------|

| 2.1  | Transmission Status Notation                                      |

| 3.1  | Attribute representation summary                                  |

| 5.1  | Response times and completion times of atomic update methods. 115 |

| 6.1  | Features of the case studies                                      |

| 6.2  | Transformation times from CANDLE into C and UPPAAL 128 $$         |

| 6.3  | IAR C compiler options                                            |

| 6.4  | Memory usage of the case studies                                  |

| 6.5  | Comparison with RTOS code                                         |

| 6.6  | UPPAAL verification options                                       |

| 6.7  | Model-checking results of the flow regulator example              |

| 6.8  | Model-checking results of the steam boiler example 140            |

| 6.9  | Model-checking results of the security alarm example 140          |

| 6.10 | Model-checking results of the ABS example                         |

| 6.11 | TA model comparison of the ABS system                             |

| 6.12 | Transmit buffer verification of the flow regulator examples 145   |

| List o | f Tables | xvii |

|--------|----------|------|

|        |          |      |

| 6.13 | Receive buffer verification of flow regulator examples                  |

|------|-------------------------------------------------------------------------|

| 6.14 | Transmit buffer verification of flow regulator examples with offset.147 |

| 6.15 | Receive buffer verification of flow regulator examples with offset. 148 |

|      |                                                                         |

#### 1. INTRODUCTION AND OVERVIEW

#### 1.1 Embedded System

An embedded system is a computer system that is part of a larger system to perform a dedicated function such as monitoring and controlling. We see such computer systems everywhere around us, for example: cell phones, domestic appliances, medical systems, traffic control systems, and automotive applications. Embedded computer systems are becoming more attached to our life, therefore embedded development methods are very important in order to ensure reliability particularly where a failure may cause loss of life or financial damage. On June 4, 1996 the Ariane 5 rocket launched by the European Space Agency exploded just 40 seconds after initiation of the flight sequence (Dowson, 1997). A software failure was identified as a primary cause of the disaster. The catastrophe was valued at approximately \$370 million. More recently, Toyota, the world's largest automobile manufacturer, announced in 2010 the recall of thousands of cars because of a problem in a braking system. A software glitch also has been suspected in the braking system. Embedded system engineers need to ensure that the systems which they deliver will behave correctly. Tools and techniques that support that are highly demanded.

#### 1.2 Real-time Embedded System

Mostly, embedded systems are real-time systems. In other words, they have real-time constraints where the correctness of their behaviour depends not only

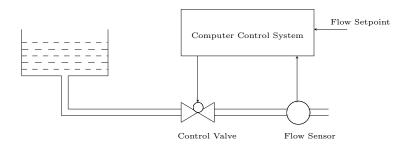

on the logical results of the computation, but also on the time at which these results are produced. In a vehicle air-bag example, once a crash is detected, the air-bag has to inflate rapidly within a short time. In this example, the system should respond to the event of the crash on the correct time in order to prevent driver from striking the steering wheel or window. Real-time systems are classified into two types depending on how strict are the timing requirements: soft real-time systems and hard real-time systems (Liu, 2000). A soft real-time system has more relaxed timing constraints. The system can continue to operate even if it fails to meet its deadline. Examples are multimedia applications, telephone switches, and on-line reservation systems. In a hard real-time system, if a timing constraint or deadline is not met, errors consequences may occur threatening human lives or causing sever damage or financial loss. Examples include safety-critical applications: medical machines, automotive and avionics. Consider the simple example shown in Fig. 1.1 (Kopetz, 1997), where the computer performs a single activity. The system controls the flow of a liquid through a pipe. For a given set-point, the computer system must maintain the flow of the liquid despite changing environmental conditions, such as varying level of the liquid in the vessel or temperature sensitive viscosity of the liquid. The computer system continuously observes the rate of flow, using the flow sensor, and adjusts the control valve accordingly. The response to a change in the flow must occur within a finite period of time in order to prevent an overload situation. This however may require complex calculation in order to obtain the new valve position. Checking that the system meets some functional properties is necessary, for example: whenever an increase of the flow rate is detected, the valve is eventually adjusted. However, verifying non-functional (or timing) properties is very important, for example: whenever an increase of the flow rate is detected, the valve is eventually adjusted before x time units. Tools and techniques that provide a prior analysis about the worst-case behaviour of such systems, are demanded.

Fig. 1.1: Flow Regulator System.

#### 1.3 Distributed Embedded System

Embedded systems tend to be distributed because of the nature of the environment in which they operate. In this case a system may have a number of computing nodes that are interconnected by a communication network in order to exchange information for the purpose of monitoring and control. Modern vehicles may have over a hundred computing units to control, for example, air-bag, driver's doors, anti-lock brakes, engine functions and many other activities in the car (Pop et al., 2004). Distribution is required for various reasons such as performance increase, location of sensors and actuators, and fault tolerance (Caspi et al., 1999). For instance, consider the example shown in Fig 1.1. For a geographical reason, the computing node that reads the flow rate, may be placed close to the flow sensor and interconnected with a suitable communication bus with another computing node that controls the valve. Unfortunately, it is a challenging task to design and implement real-time embedded systems in such a way that guarantees that the functional and timing properties are satisfied under all possible workloads. The problem becomes even harder when the system is distributed.

A lot of distributed embedded systems are implemented using Controller Area Network (CAN). The CAN is the dominant network in automotive and factory control systems and is becoming increasingly popular in robotic, medical and avionics applications. In the following, a brief introduction of the CAN is

presented.

#### The Controller Area Network

Controller Area Network (CAN) (Bosch, 1991; ISO-CAN, 1993; Natale et al., 2012) is a broadcast, message-oriented communication protocol developed originally for the automotive industry by Bosch GmbH in the mid-eighties. CAN was devised to replace the complex wiring harness in automobiles with a two-wire bus, and suited to operate in a harsh electromagnetic environment at transmission speeds of up to 1 Mbit/s over short distances. CAN is a multi-master protocol, any node on the network can send a broadcast message to other nodes. The message does not contain the address of the destination node(s), but it has a unique static number which defines the priority of the message in the network. CAN implements the carrier-sense, multiple-access (CSMA/CA) protocol with a deterministic collision avoidance policy. This feature has made CAN particularly suitable for hard real-time systems which require high reliability. Currently its use has been expanded to include new application domains, for example: manufacturing, construction, agriculture and healthcare (Ortiz et al., 2011; Eugenio, 2008; Riti and Pozzi, 1999; Parent and Cassin, 1999).

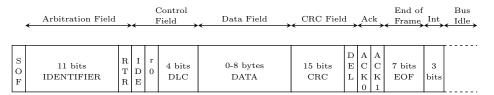

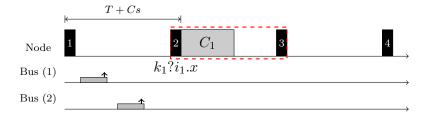

Fig. 1.2: CAN Frame - Standard Format.

Messages are transmitted over the CAN network as fixed format frames which consist of a data field, a message identifier field and other trailing fields, see Fig 1.2. The data field is between 0 and 8 bytes long. The identifier field is 11 (29) bits in the standard (extended) frame format. The other fields of the frame are explained in Table 1.1. Additional bits are inserted when a frame is trans-

| Field name | Purpose                                                   |

|------------|-----------------------------------------------------------|

| SOF        | Denotes the start of frame transmission.                  |

| ID         | Represents message identifier.                            |

| RTR        | Remote transmission request.                              |

| IDE        | Identifier for the data which also represents the message |

|            | priority.                                                 |

| r0         | Reserved bit.                                             |

| DLC        | Data length code which represents the number of bytes     |

|            | of data.                                                  |

| DATA       | Represents message data field which is between 0 and 8    |

|            | bytes long.                                               |

| CRC        | Cyclic redundancy check.                                  |

| DEL        | CRC delimiter.                                            |

| ACK0       | ACK slot.                                                 |

| ACK1       | ACK delimiter.                                            |

| EOF        | End of frame.                                             |

| Int        | Inter-frame space.                                        |

Tab. 1.1: CAN frame fields.

mitted over the network for synchronisation. This process is called *bit stuffing* that means after five consecutive equal bits, a complementary bit is inserted into the bit stream. Bit stuffing occurs from SOF up to, but not including, the CRC delimiter. Stuff bits introduce uncertainty to the transmission time of CAN messages. However, the maximum number of stuff bits can be calculated in order to estimate the worst-case transmission time of a CAN message. This is discussed in detail in section 2.3.4.

The identifier represents the priority of the message which is a non-negative integer starting from 0; the smaller the number the higher the priority. When two or more nodes try to transmit a message, the node with the higher priority message gains access to the bus. First when the bus is free, a number of nodes may start to transmit at the same time. Each node first transmits the message identifier starting from the most significant bit, and then it monitors the bus. In this mechanism, the bit is classified as either *dominant* or *recessive*. The node can only read a recessive bit if all other nodes write recessive bits, otherwise it reads a dominant bit. The behaviour of the bus in this case is similar to an

AND-gate. When a node monitors a bit value that is not the one transmitted it stops transmission, and behaves as a receiver to the highest priority message, and then waits until the bus becomes idle again. Therefore, during arbitration, the node with the highest priority message wins and continues to transmit the rest of the message. Additionally, the message identifier expresses the type of the message. Each node may be configured to accept a subset of messages. A receiver node performs the acceptance test to the received message. If the message is accepted it is stored in a receive buffer, otherwise it is rejected.

#### 1.4 Formal Methods

Embedded systems may have high reliability requirements, e.g. a mean time to failure of 10<sup>9</sup> hours is not unusual. Traditional approaches to testing embedded systems may not alone provide the required confidence in their reliability. In (Gluck and Holzmann, 2002) two problems are identified in conventional testing in terms of concurrent systems: "limited controllability" and "limited observability". The first one means that it is not possible to control the specifics of thread interleavings; the second one means that it is very hard to reproduce the error scenario to identify the root cause. Therefore, finding errors such as race conditions and deadlock in concurrent software is very challenging using conventional testing.

However, these approaches can be supplemented by a variety of analytic techniques. One such technique is model-checking (Baier and Katoen, 2008). Model-checking has proved to be a very effective method to verify requirements and the design of concurrent systems and communication protocols. Basically, a model-checking tool accepts an abstract model of the system and a specification of properties of the system. The tool then performs an exhaustive state-space search to check if the model satisfies the given specification. A counterexample (sequence of events or path) is generated if the specification is not satisfied

by the model. Therefore, by studying the counterexample, the error may be discovered and corrected. A major obstacle to the widespread deployment of model-checking in practice is the state-space explosion problem: the number of states to be checked in a realistic model of the system may exceed the available computing resources. Furthermore, model-checking verifies a system model which is an abstraction of the actual system. Thus the model may exhibit a behaviour that can not be expressed by the actual implementation of the system. Despite of these limitations, model-checking can increase the level of confidence in a system design.

#### 1.5 Related Work

The problem of real-time system has been subject to exhaustive research during the last few decades. Many approaches have been proposed to ensure that systems hold some useful properties. The synchronous approach is based on very conservative assumptions on system computations and communications which make the system difficult to implement particularly when the system is distributed. Traditional scheduling analysis has been widely used by real-time system engineers. It provides a simple mathematical analysis of system behaviour. Based on the success of its application to single-processor systems, the approach has been extended to the distributed applications. However, the approach requires restrictive assumptions on the system implementation, and does not allow system level properties to be checked. Other approaches based on formal languages have been proposed, but they are mainly limited to uniprocessor applications.

#### 1.5.1 Synchronous Approach

The synchronous languages Esterel (Berry, 2000), Lustre (Halbwachs et al., 1991) and Signal (LeGuernic et al., 1991) are designed around the *synchrony hypothesis* which assumes a system responds to its environment's events in zero time (Benveniste et al., 2003). Moreover, all communications between the system components are also performed instantaneously. The concept is similar to the synchronous model of digital circuits. The circuits are described using gates that must react during one clock cycle which means conceptually in zero time. This approach allows one to reason formally about the operations of the system (Benveniste and Berry, 1991). Synchronous languages and their compilers are now widely used in industry for automotives, railways, and avionics.

The Esterel language is suited to the development of control-dominated embedded reactive applications (Potop-Butucaru et al., 2007). An Esterel program consists of a collection of concurrently running threads which are described in a traditional imperative syntax. The concurrency however is compiled away in order to generate a single-threaded source program that behaves like a state machine at run-time. Many compilers have been developed for Esterel such as Esterel Technologies Compiler v7 (Esterel-Tech, 2005), Saxo-RT Compiler (Weil et al., 2000; Closse et al., 2002), and Columbia Esterel Compiler (Edwards and Zeng, 2007).

In order to validate the synchronous assumption in realistic applications of a synchronous language, the tool TAXYS (Bertin et al., 2000; Closse et al., 2001) has been developed. The main goal of TAXYS is to generate a formal model that captures the temporal behaviour of a real-time application and its external environment. The formal model is produced in a timed automata form (Alur and Dill, 1994). Esterel is used as a development language for the application. The KRONOS model checker (Daws et al., 1996) is used to check whether the program satisfies its timing constraints. Although the tool is applied success-

fully for some applications, for example (Bertin et al., 2001) and (Tripakis and Yovine, 2001), the approach is limited to a single-task implementation of a synchronous real-time application running on a single-processor platform (Sifakis et al., 2003).

Generating an executable code from a synchronous language for a distributed architecture has been addressed in Next-TTA (Caspi et al., 2003) and COLA (Haberl et al., 2008a,b). The approach of Next-TTA translates a high-level control design of Simulink (MathWorks, 2012) to a SCADE/Lustre program for validation purpose. Then the implementation is derived for TTA execution layer. TTA (Time Triggered Architecture) (Kopetz, 1997) supports distributed implementations based on a synchronous bus. The TTA conforms with a notation of global synchronisation and ideally matches the synchronous assumption. Although the tool aims to benefit from the Lustre model-checker Lesar (Ratel et al., 1991) to check whether the implementation satisfies its functional and timing properties, the analysis is limited to uni-processor implementations (Caspi et al., 2003) because the tool Lesar assumes only this kind of implementation when its input model is constructed. COLA (Kugele et al., 2007) is a component language for design and development embedded systems. The language has a formal semantics based upon synchronous dataflow. An approach is presented in (Haberl et al., 2008a) to translate models given in COLA to C code. The approach employs a time division multiple access (TDMA) communication schema (similar to TTA) to ensure the timely delivery of data in order to retain the synchronous semantics of the COLA model (Haberl et al., 2008a). Furthermore, although COLA is defined by a rigorous formal semantics in which automated tools, such as model-checking, can be applied to check its correctness, such a verification tool does not yet exist for the language, and it remains for future work (Haberl et al., 2008a).

Although time-triggered systems obey well the synchronous approach, main-

taining a global clock for both computation and communication is difficult to implement, and the overhead of the implementation is often large when adopting the fully synchronous approach (Potop-Butucaru and Caillaud, 2007). Asynchronous communication schemes (e.g. CAN (Bosch, 1991)) which are now widely used in industries, allow a number of computing nodes operating at different rates to be connected via a communication bus with no need to a global clock for synchronisation. Globally Asynchronous Locally Synchronous (GALS) is an architecture emerged to combine the two approaches. In this architecture, synchronous components are connected via an asynchronous communication media. The requirement for a global time is removed when a synchronous specification is implemented within the GALS model (Potop-Butucaru and Caillaud, 2007).

#### 1.5.2 Scheduling Analysis Approach

This approach has been exhaustively studied in the real-time systems literature. A real-time application is considered to be composed of a set of tasks that interact. A task is a piece of code which is executed in response to an event from the environment. Tasks may share resources such as processor, memory, and communication media. Timing requirements of a system design are represented in a form of periods, deadlines and priorities to the tasks. The main role of the scheduling approach is to provide an analysis used to confirm that the timing constraints of the system are satisfied. There are two main scheduling approaches: the cyclic executive approach and the priority-based approach (Burns and Wellings, 2001). In the former approach, each task has cyclic access to the processor in a predefined order. In the latter approach, each task is assigned a unique priority according to some policy (e.g., RMA or EDF (Burns and Wellings, 2001)). When a higher priority task is released during the execution of a lower priority one, then the processor will imme-

diately switch to execute the instructions of the higher priority task. is called a preemptive schema. However, in the non-preemptive schema, the lower priority task is allowed to complete its execution before switching to the higher priority task. A simple schedulability analysis is given by Liu and Layland (Liu and Layland, 1973) in order to test if a set of fixed-priority periodic tasks meet their deadlines. An enhanced analysis is proposed in (Joseph and Pandya, 1986) which calculates the worst-case response time of each task, and then compares it with the deadline of the task. Although the main focus of traditional analysis is on the worst-case behaviour in order to ensure that tasks meets their deadlines, the best-case response time analysis has been addressed in (Redell and Sanfridson, 2002) and (Bril et al., 2004). One such application of this analysis is to estimate the maximum variation in a task response time. The scheduling analysis has been extended to allow distributed systems performance evaluation where end-to-end response times are computed for tasks running in a distributed environment and communicate via a real-time communication protocol. For example, the work of Tindell et al (Tindell and Hansson, 1995), Henderson et al (Henderson et al., 1998), and Redell et al (Redell et al., 2004).

The scheduling approach in general assumes very restrictive assumptions on the system implementation in order to analysis the behaviour of the system. For example, all tasks are periodic, tasks have deadlines equal to their periods, and tasks are independent. Additionally, special purpose resources such as a real-time operating system (RTOS) (e.g., (WindRiver, 1999)) and protocols (e.g., (Sha et al., 1990)), are often required to implement preemptive scheduling policies and to avoid deadlocks. Moreover, the approach does not allow system level properties (e.g. safety and functionality) to be verified, and only deals with implementation level properties (tasks meet their deadlines).

#### 1.5.3 Other Approaches

Process algebra languages have been widely used in the specification and design telecommunication protocols and distributed systems. A system is represented as a process, or composed of other smaller processes. Their formal semantics makes them amenable to formal verification (e.g. (Garavel and Sifakis, 1990)) as well as simulation. Their formalism has been extended to allow modelling real-time aspects of a system, for instance: ET-LOTOS (Léonard and Leduc, 1997), ATP (Nicollin and Sifakis, 1994). Despite their expressiveness and clean formalism, and the availability of analysing tools: simulators, model-checkers, and theorem provers, their applications have been limited to support only the specification and verification (e.g. TRAIAN Compiler of LOTOS NT (Garavel et al., 2002)) rather than implementation of a system (and distributed system in particular). Moreover, they can not deal with a broadcast communication mechanism such as CAN (Bosch, 1991; ISO-CAN, 1993) that is most frequently employed in the implementation of distributed embedded systems. However, generating an implementation code from a process algebra language for uniprocessor platform has been addressed in the work of Bradly et al (Bradley et al., 1994c,b,a). A real-time system can be represented in the timed process algebra, AORTA (Bradley, 1995). The language is designed to consider both verification and implementation of a system. An implementation C code is generated for each process of an AORTA design from the same graph that is used in the generation of an analytical model (Bradley, 1995). The AORTA system can be validated via simulation and formally verified by model-checking (Bradley et al., 1996).

PTIDES is a programming model for distributed real-time systems (Zhao et al., 2007; Lee et al., 2009). It is based on a discrete-event model which has been used for simulations. In this model, a network of components reacts to input events in time-stamp order and produces output events in time-stamp order. PTIDES

leverages network time synchronisation with bounded error and bounded latency in order to use the model to produce efficient distributed implementations. However, the approach, similarly to traditional scheduling analysis, is limited to schedulability analysis which does not provide system level analysis, and uses a special purpose architecture (PRET architecture (Liu et al., 2010)) to achieve timing predictability.

Additionally, other formalisms such as Time Petri Nets (Berthomieu and Diaz, 1991), Timed Automata (Alur and Dill, 1994), and State Machines have been applied in the development of real-time embedded systems, and implemented in the tools: Roméo (Lime et al., 2009), Times (Amnell et al., 2003) and IAR visualSTATE (IAR-Systems, 2012) respectively. However, in addition to their less expressiveness (i.e. low-level representation format) compared to the process algebra formalism, their usages has not yet considered distributed implementations. Roméo facilitates automated verification via model-checking for the time petri net model of real-time system. The tool does not support the implementation of such systems. Other works however consider this problem, i.e. producing an implementation program (e.g. RT Java) from a Petri net model for a real-time system, see for example (Moreno et al., 2006). In Times, an approach to modelling and implementing embedded systems that combines both schedulability analysis and formal verification is presented in (Norstrom et al., 1999). The idea is to extend the standard time automata (Alur and Dill, 1994) with real-time tasks to allow a more relaxed task model (e.g. nonperiodic tasks) to be analysed using a formal verification tool such as UPPAAL model checker (Behrmann et al., 2004). The approach is implemented in the tool, Times (Amnell et al., 2003). Although an executable code can be generated from the extended timed automata model, the approach assumes that the generated code is executed on a uni-processor platform that guarantees the synchronous hypothesis (Amnell et al., 2003). A state machine-based approach (such as (Samek, 2008) and (IAR-Systems, 2012)) generates event-driven

code for uni-processor embedded systems. The tool IAR visualSTATE (IAR-Systems, 2012) can verify a fixed list of untimed properties such as the absence of deadlocks and unreachable states. More complex properties can be verified by constructing another state machine, that expresses the desired property, parallel to the system design.

#### 1.6 The Dissertation

#### 1.6.1 Justification

The work presented in this thesis addresses the problem of generating executable code for CAN-based distributed embedded systems in a way that guarantees that both functional and timing properties expressed in a high-level formal language are satisfied. The thesis proposes a novel approach in which system behaviour is specified in CANDLE, a high-level language which is given a formal semantics by translation to bCANDLE, an asynchronous process calculus. A bCANDLE system is translated automatically, via a common intermediate net representation, both into executable C code and into a timed automaton model that can be used in the formal verification of a wide range of functional and temporal properties.

#### 1.6.2 Structure and Contributions

Chapter 2 introduces our code and model generation approach, and provides all the essential details including models, languages, and formal notations. The chapter presents no new results but provides the necessary information on which the rest of the thesis is built.

Chapter 3 is concerned with the implementation of the formal language. The executable code is derived from the language via an intermediate model. An

efficient C representation of the intermediate model is presented. The chapter presents our implementation model which defines certain assumptions about system components. A single broadcast asynchronous communication mechanism is adopted and implemented. The communication mechanism is an abstraction of the CAN. All communications occur through this mechanism and never through the use of shared variables. This single notion, employed both for external and local communication between system components, provides flexibility to the system developer to freely distribute system components on a number of nodes, and simplifies the process of generating a formal model of the system. An AADL-like language is adopted to describe the system architecture. The Architecture Analysis and Design Language (AADL) (Feiler et al., 2006) is an industry standard language to specify a system architecture. The system description provides details to the code generator about processes, nodes, process-to-node allocation, scheduling algorithm, tick rate, and communication details, including the IDs of messages and network transmission rate.

Chapter 4 presents a rigorous argument that, for any system expressed in the high-level language, its formal model is a conservative approximation of the executable C code. This allows the system developer to conclude that if a model satisfies any universally quantified property, then it is guaranteed that the implementation will also satisfy the same property.

Chapter 5 proposes a number of methods that ensure an atomic update of data which is required to implement the semantics of the language correctly. The methods are evaluated against some criteria we identify depending on the worst-case behaviour analysis of the methods in order to select a suitable one for our code generation approach.

Chapter 6 assesses the applicability and performance of the approach by implementing four case studies. The performance is measured in terms of the computational effort required to generate an executable code and a formal model

for a given design, and the computational resources including memory (RAM and ROM) and CPU load required to execute the examples on the target. Performance results are compared with the results obtained from an alternative method employing a widely-used real-time kernel that implements the same case studies. The chapter also assesses the tractability of the formal models which are generated from the case studies. A number of functional and temporal properties are verified using an off-the-shelf model checker.

Chapter 7 summarises the work, discusses the limitations of the work, and suggests possible directions for future research.

### 2. METHODS, TECHNIQUES AND TOOLS

This chapter introduces our code and model generation approach, and provides all the essential details including models, languages, and formal notations, on which the rest of the thesis is built.

#### 2.1 Overview of the Approach

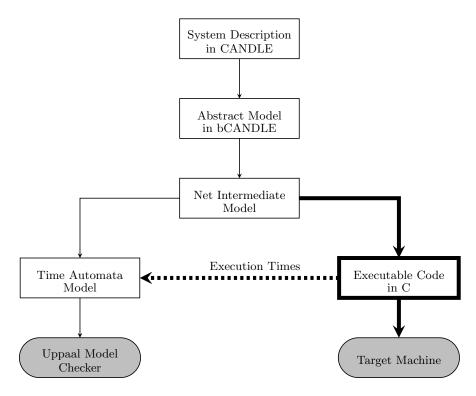

An overview of our code and model generation approach is depicted in Fig. 2.1. The primary component in our approach is bCANDLE (Kendall, 2001b), a timed process calculus intended for modelling CAN-based embedded systems. The language features a value-passing, broadcast communication primitive, message priorities and an explicit time construct. The motivation to use bCANDLE is that it enables system developers to construct system models that are amenable to formal analysis by model-checking. There is a well-defined translation from bCANDLE to timed automata (TA) models upon which standard model checkers can be used. The existing translator is built upon a low-level intermediate net representation (Kendall, 2001b). The idea of the thesis is to make use of the net representation developed by the TA translator to generate executable code. The approach of generating executable code from a net is discussed in Chapter 3. The main reason for employing the net is that it will be easier to establish a connection between the behaviour of the model and the executable code since they are both produced from the same source.

This will be the subject of Chapter 4 of the thesis. The executable code is generated in the C language. The model is generated in the form of a timed automaton so an off-the-shelf model-checker (such as UPPAAL) can be used to verify system properties. In order to be able to verify temporal properties of the system, time bounds of the execution of system components can be predicted using static analysis tools such as the Bound-T (Tidorum, 2012) and aiT (Absint, 2012). Although bCANDLE is a simple language, it is likely to be too low level for routine use in system description. Therefore, CANDLE (Kendall, 2001b) was introduced for the purpose of a system design. The CANDLE is a high-level programming language dedicated for CAN-based embedded systems. The language has a formal semantics defined by translation into bCANDLE. In summary, the system is expected to be designed in CANDLE. Then, a bCANDLE model is produced from the CANDLE design of the system. Next, a net representation is derived from the bCANDLE model. Finally, an executable C code of the system is generated from the net.

The rest of the chapter is organised as follows. Section 2.2 presents the main assumptions made and constraints on systems for which the code and model generation approach is proposed. Section 2.3 introduces the bCANDLE modelling language and its formal semantics. Section 2.4 introduces the intermediate representation of bCANDLE, the net and its formal semantics. Section 2.5 outlines the translation rules of bCANDLE into the net. Section 2.6 introduces the high-level language of bCANDLE, CANDLE. Section 2.7 outlines the translation rules of CANDLE into bCANDLE. Finally, section 2.8 concludes the chapter.

#### 2.2 System Characteristics

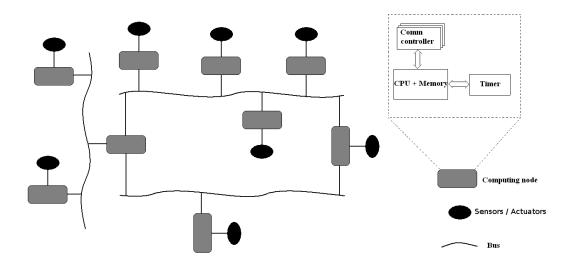

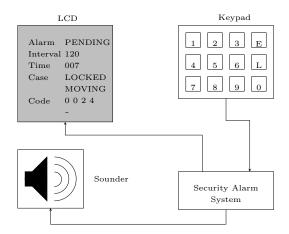

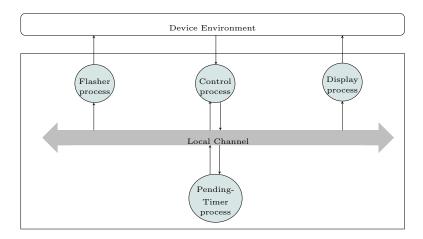

The proposed code and model generation approach targets a class of embedded systems (Fig. 2.2) characterised by a number of properties:

**Fig. 2.1:** Overview of Code and Model Generation Approach. Work done as part of this thesis is shown in bold.

- 1. A system comprises a number of software processes that are statically distributed to computing nodes.

- A computing node consists of a processor which has access to a local memory, a programmable timer, zero or more communication controllers, and zero or more sensors and actuators to interact with the physical world.

- 3. A restricted scheduling approach (e.g., cooperative or round-robin, discussed in section 3.2.3) is applied when two or more processes are allocated to a single computing node in order to allow off-line calculation of computation response times.

- 4. Processes communicate via asynchronous broadcast channels which implement an abstraction of the CAN protocol in which the send operation is non-blocking and the receive operation is blocking. The abstraction of the CAN is formed by the following assumptions:

Fig. 2.2: Distributed Embedded System (Kendall, 2001b).

- communication channels operate without errors,

- the details of bit-level data transmission are abstracted so that messages are assumed to be transmitted atomically,

- the CAN message ID field is 11 bits in length.

- 5. Processes that reside in the same computing node are not allowed to share memory and typically use (local) broadcast channels to communicate.

- 6. Shared access to I/O is not allowed, i.e. in the case of multi-tasking, access to a sensor or actuator is limited to a single software process.

## 2.3 The bCANDLE Modelling Language

bCANDLE (Kendall et al., 1997, 1998b; Kendall, 2001b) is a timed process calculus dedicated for modelling distributed, real-time embedded systems based on the CAN network. The language features a value-passing, broadcast communi-

cation primitive, message priorities and an explicit time construct. A bCAN-DLE system comprises three components: a data model, a network model, and a process model. It is defined formally by a tuple (P, N, D). In the following, the definition and notations are presented for each component of bCANDLE system.

#### 2.3.1 Data Model

Let Var be a finite set of data variables. Each variable  $x \in Var$  takes its value from some non-empty, finite set of values,  $\mathsf{type}(x) \subset V$ , where V is the set of data values. We assume that V contains at least the distinguished value  $\bot$ , where  $\bot \notin \bigcup_{x \in Var} \mathsf{type}(x)$ , which is taken to be the "undefined" data value, then:

- $Valuation = Var \rightarrow V$

- $Operation \cong Valuation \leftrightarrow Valuation$

- $Predicate = 2^{Valuation}$

Let  $\Omega$  be a finite set of operation names,  $\Gamma$  be a finite set of predicate names, then a data environment D over Var,  $\Omega$  and  $\Gamma$  is a tuple D= (type, operation, predicate, val) where

- type:  $Var \to 2^V$  is a total function, giving for each variable  $x \in Var$ , a non-empty, finite set of data values, type(x), ranged over by x;

- operation :  $\Omega \to Operation$  is a total function, giving for each operation name  $\omega \in \Omega$ , an operation, operation( $\omega$ ), which interprets it;

- predicate :  $\Gamma \to Predicate$  is a total function, giving for each predicate name  $\gamma \in \Gamma$ , a predicate, predicate( $\gamma$ ), which interprets it;

• val:  $Var \to V$  is a total function which, for each variable  $x \in Var$ , gives the current valuation of x, where  $val(x) \in type(x)$  or  $val(x) = \bot$ .

Let D = (type, operation, predicate, val) be a data environment. Let  $x, y \in Var$  be data variables, and  $v \in V$  a data value, then the following notational conventions are employed:

- D. type, D. operation, D. predicate and D.val denote type, operation, predicate and val, respectively.

- D.x denotes the value val(x).

- D[x := v] denotes the data environment D' = (type, operation, predicate, val')

where val'(x) = v and val'(y) = val(y) for all y ≠ x (≡ denotes syntactic identity and ≠ its negation).

- D → dD' abbreviates the condition (val, val') ∈ operation(ω) ∧ D' = (type, operation, predicate, val'). The operation name ID is reserved for the identity relation on valuations, i.e. it must be interpreted in any data environment by the operation operation(ID) ≜ {(val, val)|val ∈ Valuation}

- $D \models \gamma$  abbreviates the condition  $val \in predicate(\gamma)$ .

#### 2.3.2 Network Model

The network model of bCANDLE is an abstraction of the CAN network which consists of a number of broadcast channels. Each channel implements an abstraction of the CAN protocol. A message transmitted through a channel is viewed as a pair consisting of a data value and an identifier. The data value and the identifier corresponds to the data field and the arbitration field of the CAN frame respectively. Transmission of a message is divided into three phases: pre-acceptance, acceptance, and post-acceptance phase. The acceptance phase is the interval during the transmission of a message when receiver nodes perform

their acceptance test. The pre-acceptance phase extends from the beginning of the transmission to the point of acceptance. The post-acceptance phase extends from the the point of acceptance to the point at which the channel next becomes free. In practice, the location of the acceptance point may vary from one type of CAN controller to another. For example, for some CAN controllers, the acceptance point may occur on the leading edge of the ACK0 bit of the CAN frame, see Fig 1.2. It is assumed that the time which passes during the pre-acceptance and post-acceptance phases can be calculated for all messages. This time is called *transmission latency*. The transmission latency of a message gives the upper and lower bounds on the time which passes during the pre-acceptance and post-acceptance phases of the message.

A channel is defined by the tuple  $(M, \prec, \delta, s, u)$  where:

- M ⊆ I × V is a set of messages. I is a set of message identifiers and V is a set of data values.

- $\prec$ :  $I \leftrightarrow I$  is a priority ordering of messages.

- $\delta: M \to \mathbb{R}_{\infty} \times \mathbb{R}_{\infty} \times \mathbb{R}_{\infty} \times \mathbb{R}_{\infty}$  is a transmission latency function. The functions  $\delta^{lb}, \delta^{ub}, \delta^{lB}, \delta^{uB}: M \to \mathbb{R}_{\infty}$  give the lower and upper bounds on the duration of the pre- and post-acceptance phases for the transmission of a message.  $\delta^{lb}$  (resp.  $\delta^{ub}, \delta^{lB}, \delta^{uB}$ ) is abbreviated as lb (resp. ub, lB, uB).

- s is a transmission status. The channel is either free or is transmitting a message (pre-acceptance, acceptance or post-acceptance phase). The notation shown in Table 2.1 denotes the transmission status.

- $\bullet$  *u* is a message queue.

It is assumed that M,  $\prec$  and  $\delta$  are static components, they are defined at the initialisation of a system and are unchanged after that. By contrast, s and u are

| Notation                         | Transmission Status                                                                                                                         |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| <u></u>                          | FREE, no message is in transmission.                                                                                                        |

| $\stackrel{t1,t2}{\leadsto} m$   | pre-acceptance phase of transmission of message $m$ with bounds                                                                             |

|                                  | $t_1,t_2$ on time to completion, $0 \le t_1 \le lb$ , $0 \le t_2 \le ub$ .                                                                  |

| $\uparrow m$                     | acceptance point in transmission of $m$ .                                                                                                   |

| $m \stackrel{t_1,t_2}{\leadsto}$ | post-acceptance phase of transmission of message $m$ with bounds $t_1,t_2$ on time to completion, $0 \le t_1 \le IB$ , $0 \le t_2 \le uB$ . |

Tab. 2.1: Transmission Status Notation.

dynamic components which are used to model the current transmission status and message queue as a system evolves.

The message queue modelled here represents a single shared queue for a whole network of nodes that are communicating using the same channel. It is assumed that a transmitting node only attempts to transmit its highest priority message. Additionally, a node that has a number of pending messages always attempts to transmit the highest priority message as soon as the channel becomes free. This implies that the channel can not become free between the transmission of messages if there are pending messages. It means that the CAN controller will arbitrate for the bus immediately after sending the previous message, and will only release the bus in case of lost arbitration. This is important to ensure that the transmission of a pending message is not deferred by beginning transmission of a lower priority message. Each CAN controller must have a suitable buffer management mechanism to respect these assumptions. This ideal behaviour of CAN was identified by Tindell et al. (Tindell and Burns, 1994; Tindell et al., 1994) for scheduling analysis of CAN network. If all nodes follow the same protocol to transmit messages, then the internal queue of all nodes can be viewed as one large queue for a whole network in which messages are placed in priority order, assuming that each message is assigned a unique priority number in a network.

A bCANDLE network is a set of channels in which each channel is given a unique identifier. Let K be a set of channel identifiers, then a network N over

K is an indexed set of channels which is expressed as follows:

$$N = ((M, \prec, \delta, s, u)_k \mid k \in K)$$

Let c be a channel, then the notation N[k:=c] denotes the network N', where  $N'_k = c$  and  $N'_{k'} = N_{k'}$  for all  $k' \in K \setminus \{k\}$ .

A channel c can act independently, by performing a discrete change in its transmission status or its message queue, to become c' which gives a new network N' = N[k := c']. Alternatively, the state of the whole network may be affected as time progresses. The relation  $N \xrightarrow{\lambda_{\mathsf{nt}}} N'$  represents a change of state from N to N' annotated with the label  $\lambda_{\mathsf{nt}}$  which ranges over  $A_{\mathsf{n}} \cup \mathbb{R}$ .  $A_{\mathsf{n}}$  is a set of network action labels used to annotate discrete state changes. Elements of  $\mathbb{R}$  are used to annotate state changes due to the passage of time.

Fig. 2.3 gives the network transition rules. The rules are expressed using the structural operational semantics (SOS) (Plotkin, 2004; Nielson and Nielson, 1991) style. SOS is the predominant approach for giving a meaning to programming and specification languages. It generates a labelled transition system, whose states are the terms of the language, and whose transitions between states are obtained inductively from a collection of transition rules of the form  $\frac{\text{premises}}{\text{conclusion}}$ . The validity of the premises of a transition rule, under a certain substitution, implies the validity of the conclusion of this rule under the same substitution (Aceto et al., 2001). The rules N.1, N.2, N.3 and N.4 give the transition rules due to discrete state changes of a network, whereas the rule N.5 gives the transition rule due to a time progress of a network. The function tcp(N) denotes the maximum time progress allowed for N.

N.1

$$\frac{N_{k} = (\downarrow, m : u)}{N \xrightarrow{k \leadsto m}_{\mathsf{n}} N[k := (\stackrel{\mathsf{lb},\mathsf{ub}}{\leadsto} m, u)]}$$

N.2

$$\frac{N_{k} = (\stackrel{\mathsf{0},\bar{}}{\leadsto} m, u)}{N \xrightarrow{k \uparrow m}_{\mathsf{n}} N[k := (\uparrow m, u)]}$$

N.3

$$\frac{N_{k} = (\uparrow m, u)}{N \xrightarrow{m \leadsto k}_{\mathsf{n}} N[k := (m \xrightarrow{\mathsf{lB},\mathsf{uB}}, u)]}$$

N.4

$$\frac{N_{k} = (\stackrel{\mathsf{0},\bar{}}{\leadsto}, u)}{N \xrightarrow{k \downarrow}_{\mathsf{n}} N[k := (\downarrow, u)]}$$

N.5

$$\frac{0 \le t \le \mathsf{tcp}(N)}{N \xrightarrow{\mathsf{h}}_{\mathsf{n}} N + t}$$

Fig. 2.3: Network Transition Rules.

#### Example of network behaviour

Assume a network that consists of a single channel which can transmit messages of type flow. The transmitted values of the flow sensor reading are abstracted, where 0 represents a reading at the low level, and 1 represents a reading at the high level. The network then can be defined as follows:

$$N = \{k \mapsto (M, \prec, \delta, \downarrow, \langle flow.1 \rangle)\}$$

Where  $I = \{flow\}$ ,  $V = \{0, 1\}$  and  $M = I \times V$ . As there is a single channel, then  $K = \{k\}$ . The function  $\delta$  gives the transmission latencies in  $\mu$ s, as follows:

|               | $flow{-}$ |

|---------------|-----------|

| $\delta^{lb}$ | 86        |

| $\delta^{ub}$ | 106       |

| $\delta^{lB}$ | 24        |

| $\delta^{uB}$ | 24        |

In the table, flow.\_ could be flow.0 or flow.1. It is assumed that the message

flow.1 has been already placed in the message queue; a possible trace of the network behaviour is shown in Fig. 2.4. The trace starts from the initial state  $(\downarrow, \langle flow.1 \rangle)$  in which the channel is free and the message is queued. Then, the time behaviour of the network progresses following the two-phase model. The network performs a discrete action first using one of the rules (N.1, N.2, N.3, and N.4) and then a time elapses using the rule (N.5) until the channel becomes free and the message queue becomes empty. After that, the network may progress using time transitions.

Fig. 2.4: Example of network behaviour.

#### 2.3.3 Process Model

bCANDLE uses a simple process-algebraic language to describe the behaviour of processes. A process is either a primitive process or a composition of other processes. There are four kinds of primitive processes in bCANDLE:

- 1.  $k!i.x non\text{-}blocking\ send$ : it causes the message i.v to be queued instantaneously for transmission on channel k, where i is the id of the message and v is the current value of x. Then it terminates immediately.

- 2.  $k?i.x blocking\ receive$ : it idles until an i-message reaches its acceptance point during transmission on channel k. Then it immediately assigns the

data value of the message to the variable x and terminates.

- 3.  $[\omega:t_1,t_2]$  time-bounded computation: it terminates not earlier than  $t_1$ , and not later than  $t_2$ , time units after beginning execution, and it atomically transforms the data state at the instant of termination as specified by the operation  $\omega$ .

- 4.  $\gamma \to P$  evaluate guard: it idles until the data environment satisfies the guard  $\gamma$  (which is a predicate on the data state), then it performs P.

These basic processes can be compounded using a small set of operators: sequential composition, choice, interrupt, parallel composition, and process recursion, in order to construct a larger process:

- P;Q (sequential composition) is a process that behaves as Q when P terminates.

- P + Q (choice) is a process that can behave either like P or like Q depending on which process can first perform an action.

- P[> Q (interrupt) it behaves as P until either Q performs an action or P terminates.

- P|Q is the parallel composition of P and Q.

- recX.P is a recursive process which has repetitive behaviour, where X is a process variable and P is a process term.

For details on the formal semantics of these process terms, one can refer to (Kendall, 2001b, p. 82).

#### 2.3.4 Example of bCANDLE

The bCANDLE model of the flow regulator example presented in Chapter 1 is shown in Fig 2.5. It consists of two processes: *Flow* and *Valve*. *Flow* models

a process which periodically reads a flow sensor and broadcasts its value in a flow message. Valve models a process which repeatedly waits to receive a flow message, executes a control algorithm to calculate a new value for the valve position, and instructs an actuator to move the valve to its new position. The time bounds given to each computation represent the lower and the upper bound on the time taken to execute the computation. For example, the execution time of the software to read the flow sensor may take between 85 to 100 time units.

Fig. 2.5: Flow regulator in bCANDLE.

Channel k models a CAN bus which transmits messages of type flow with a priority equals 1 and transmission latency of between 86 and 106 time units from start of a transmission to an acceptance point, and a latency of between 24 and 24 time units from the acceptance point to bus idle respectively. In the following we demonstrate how transmission latency function is calculated.

The CAN protocol employs a special technique, called bit stuffing. After every 5 consecutive transmitted bits of the same value, a stuff bit is inserted of the opposite value. This ensures that there are sufficient transitions in the bit stream to ensure that the nodes can remain synchronised. The equation of (Davis et al., 2007) gives the maximum transmission time of a message  $C_m$  containing n data bytes and including stuff bits:

$$C_m = \left(g + 8.n + 13 + \left\lfloor \frac{g + 8.n - 1}{4} \right\rfloor\right) t_{bit}$$

(2.1)

where g is 34 for the standard format or 54 for the extended format.  $t_{bit}$  is the transmission time of a single bit. The term  $\left\lfloor \frac{g+8.n-1}{4} \right\rfloor$  of equation 2.1 calculates the maximum number of stuff bits. The denominator of the fraction is 4 because bit stuffing includes also the stuffed bits in the frame. It is assumed for this particular example that the message acceptance point coincides with the leading edge of bit ACK0, see Fig. 1.2. In practice, the location of the acceptance point may vary from one type of CAN controller to another. In a CAN packet with n data bytes, there are g+8.n+1 bits from SOF up to, but not including, ACK0. Bit stuffing occurs from SOF up to, but not including, DEL. Therefore, the greatest number of bits is:  $\left\lfloor \frac{g+8.n-1}{4} \right\rfloor$  which are transmitted before the acceptance point. Therefore, the lower and upper bound of time taken during the pre-acceptance phase can be calculated by equation 2.2 and 2.3.

$$1b = (g + 8.n + 1) t_{bit} (2.2)$$

$$ub = \left(g + 8.n + 1 + \left\lfloor \frac{g + 8.n - 1}{4} \right\rfloor\right) t_{bit}$$

(2.3)

The remaining bits from ACK0 up to Int do not include stuff bits and so they equal 12 bits. Therefore, the lower and upper bound of time time taken during the post-acceptance phase can be calculated by:

$$1B = uB = 12.t_{hit}$$

(2.4)

Notice that  $ub + uB = C_m$  is always true.

For example, in a standard CAN packet, supposing a CAN bus operating at  $5 \times 10^5 bit/s$ , the transmission latency function  $\delta(m)$  for a message m with 1 byte size of data (i.e, n = 1) is:

•

$$1b = (34 + 8 + 1) t_{bit} = (43)5 \times 10^5 = 86 \mu s$$

•

$$ub = \left(34 + 8 + 1 + \left|\frac{34 + 8 - 1}{4}\right|\right) t_{bit} = (53)5 \times 10^5 = 106 \mu s$$

•

$$1B = uB = (12)5 \times 10^5 = 24 \mu s$$

Consequently, the transmission latency function  $\delta(m) = (86, 106, 24, 24)$  for the channel k.

# 2.4 The Net: The intermediate model of bCANDLE

The first stage in construction of a TA model from a bCANDLE model was performed (in (Kendall, 2001b)) by translating the bCANDLE model into an intermediate net representation which is similar to a Petri net (Murata, 1989). A similar approach was applied by Garavel in the translation of LOTOS (Garavel and Sifakis, 1990), and by Yovine in the translation of ATP (Yovine, 1993). The nets which are used in bCANDLE are similar to the extended nets of (Yovine, 1993). The aim of this work is to make use of the net representation developed by the TA translator to generate an executable code. This will be discussed in details in Chapter 3. In this section, we introduce the net and present its formal semantics.

The net, as usual, consists of a set of places and a set of transitions. The net is extended in two ways. First, each transition has an associated attribute which is used to determine whether the transition is fireable or not in a given system context, where a context consists of a network and data environment. Second, a transition is associated with a set of places vulnerable to the firing of the transition. When a transition fires, control is removed not only from the places in its source set but also from all those places which are vulnerable to

it. This extension allows a compact representation of the interrupt operator in particular.

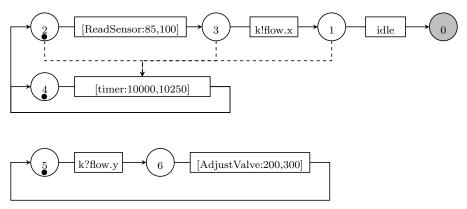

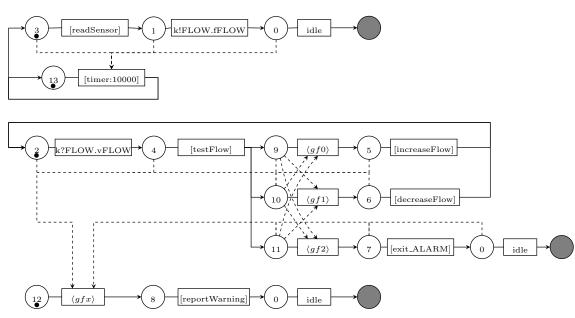

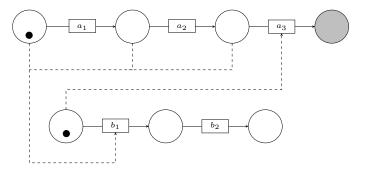

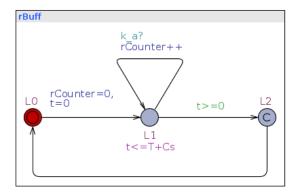

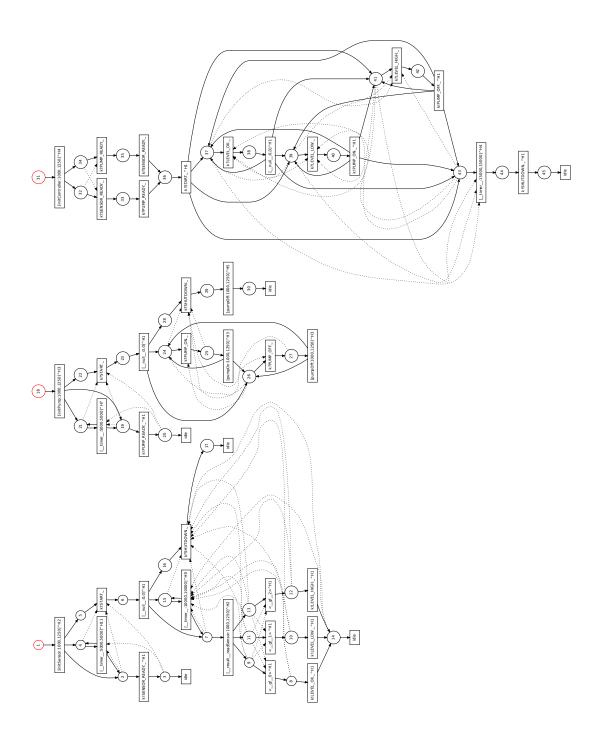

Fig. 2.6 shows the net representing the flow regulator example. Places of the net are shown as circles and transitions as boxes. The shaded circles represent a distinguished place, tick, modelling termination. A label inside a transition box refers to the transition attribute. The standard flow relation is shown using solid lines. The vulnerability relation is shown using dashed lines. A small black circle in a place shows that the place is marked. For example, transition 2 has associated attribute [ReadSensor: 85, 100]. The places: 2, 3 and 1 are vulnerable to the firing of transition 4. The places 2, 4 and 5 are initially marked in the net.

Fig. 2.6: Net of the flow regulator example.

#### 2.4.1 Definitions and Notation

A net is defined formally as a tuple  $\mathcal{R} = (W, \Theta, W^I)$  where:

- W is the set of places.

- $\bullet$   $\Theta$  is the set of transitions.

- $W^I$  is the set of initial marked places.

A transition  $\theta = (w, W^V, \alpha, W^T) \in \Theta$  where:

- $w \in W$  is the trigger of  $\theta$ , denoted • $\theta$ .

- $W^V \subseteq W$  is the set of places vulnerable to  $\theta$ , denoted  ${}^{\circ}\theta$ .

- $\alpha$  is the attribute of  $\theta$ , denoted  $\alpha\theta$ .

- $W^T \subseteq W$  is the target set of  $\theta$ , denoted  $\theta$ •

A place w is a trigger of exactly one transition. Transition attributes are just basic processes. The set Attribute is defined by the grammar:

$$\alpha ::= \widehat{\beta} |\langle \gamma \rangle| X$$

where  $\alpha \in Attribute$  is a transition attribute.  $X \in \chi$  is a process variable.  $\langle \gamma \rangle$  denotes a transition attribute which consists of the predicate  $\gamma \in \Gamma$ .  $\widehat{\beta}$  is a clocked basic process term  $(k!i.x, \, k?i.x, \, \text{or} \, [\omega:t_1,t_2]^h)$ . Timed automata use clock variables to model passing the time. At the first step in the translation of bCANDLE to timed automata, explicit clock variables are introduced into the process terms and the network channels of the bCANDLE model. A computation,  $[\omega:t_1,t_2]$ , and its associated clock variable, h, are written as  $[\omega:t_1,t_2]^h$ , and a process term, P, and network channel, N, when decorated with clock variables, are written as  $\widehat{P}$  and  $\widehat{N}$  respectively. The set of bCANDLE systems following clock allocation is written as  $\widehat{bCAN}$ . The set of clock variables is represented by H and h ranges over H.

The net of the flow regulator example shown in Fig. 2.6 is then defined formally as follows:

$$\mathcal{R} = (\{0, 1, 2, 3, 4, 5, 6\}, \{\theta_1, \theta_2, \theta_3, \theta_4, \theta_5, \theta_6\}, \{2, 4, 5\})$$

where

$$\theta_1 = \{1, \{\}, idle, \{0\}\}$$

$$\theta_2 = \{2, \{\}, [ReadSensor: 85, 100], \{3\}\}$$

$$\theta_3 = \{3, \{\}, k! flow.x, \{1\}\}\}$$