### Technical University of Denmark

### **Design of Integrated Circuits Approaching Terahertz Frequencies**

Yan, Lei; Johansen, Tom Keinicke

Publication date: 2013

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Yan, L., & Johansen, T. K. (2013). Design of Integrated Circuits Approaching Terahertz Frequencies. Kgs. Lyngby: Technical University of Denmark (DTU).

### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Design of Integrated Circuits Approaching Terahertz Frequencies

Lei Yan

September 21, 2012

### Abstract

In this thesis, monolithic microwave integrated circuits (MMICs) are presented for millimeter-wave and submillimeter-wave or terahertz(THz) applications. Millimeter-wave power generation from solid state devices is not only crucial for the emerging high data rate wireless communications but also important for driving THz signal sources. To meet the requirement of high output power, amplifiers based on InP double heterojunction bipolar transistor (DHBT) devices from the III-V Lab in Marcoussic, France are designed for the power generation at millimeter-wave frequency range. For future THz heterodyne receivers with requirements of room temperature operation, low system complexity, and high sensitivity, monolithic integrated Schottky diode technology is chosen for the implementation of submillimeterwave components. The corresponding subharmonic mixer and multiplier for a THz radiometer system are designed based on the monolithic membrane supported Schottky diodes, which is under development at Chalmers University of Technology, Sweden. To simplify the baseband circuitry, the received IF signal from the subharmonic mixer is further amplified and downconverted to the DC range with a low noise amplifier and an active mixer by using GaAs pseudomorphic high electron mobility transistor (pHEMT) technology available from OMMIC, France.

## Acknowledgments

I gratefully acknowledge the support and supervision by Associate Prof. Tom K. Johansen from Technical University of Denmark and my previous supervisor Prof. Viktor Krozer now with Goethe University of Frankfurt am Main. I also would like to thank my colleagues in the microwave technology group: especially to Chenhui Jiang, Thomas Jensen, Assistant Prof. Vitaliy Zhurbenko, Prof. Jens Vidkjær for many fruitful discussions regarding the investigations described in the thesis. For my external stay at Chalmers University of Technology in Sweden, I would like to acknowledge Prof. Jan Stake, Peter Sobis, Tomas Bryllert, and Huan Zhao for their hosting and valuable discussions. Last, but not least, I have to thank to my family, my parents, for their support. I greatly appreciate my wife, Tao Feng and my son Danny, being accompany with me.

Kgs. Lyngby, August 2012

Lei Yan

### **Publication List**

In the period of Ph. D. project, the following relevant papers were published or submitted:

- L.Yan and T.K.Johansen "Design and Modeling of InP DHBT Power Amplifiers at Millimeter-Wave Frequencies" *The European Microwave Integrated Circuits Conference*, accepted, 2012

- L.Yan, T.K.Johansen, and J.Kammersgaard "Stability Investigation for InP DHBT mm-wave Power Amplifier", *International Journal of RF and Microwave Computer-Aided Engineering*, accepted, 2012

- L.Yan, M.Tang, V.Krozer, V.Zhurbenko, C.Jiang, and T.K.Johansen "Filter designs based on coupled transmission line model for double split ring resonators ", *Microwave and Optical Technology Letters*, 2011

- L.Yan, M.Tang, V.Krozer, V.Zhurbenko, T.Jensen, C.Jiang, and T.K.Johansen, "Transmission line model for coupled rectangular double split-ring resonators ", *Microwave and Optical Technology Letters*, 2011

- T.K.Johansen and L.Yan, "Design of Mm-wave InP DHBT Power Amplifiers", SBMO/IEEE MTT-S International Microwave and Optoelectronics Conference, 2011

- L.Yan, V.Krozer, S.Delcourt, V.Zhurbenko, T.K.Johansen, and C.Jiang "GaAs Wideband Low Noise Amplifier Design for Breast Cancer Detection System", Asian Pacific Microwave Conference, 2009 Singapore

- L.Yan, T.K.Johansen, and V.Krozer, "Low Noise Design Strategy for Mixers and Amplifiers", Germany Microwave Conference, 2008 Hamburg

- J.Stake, H.Zhao, P.Sobis, A.Y.tang, V.Drakinskiy, A.Hülsmann, I.Kallfass, A.Tessman, A.Leuther, T.Bryllert, J.Hanning, T.Pelikka, A.Emrich, H.Richter, H.W.Hübers, L.Yan, T.K.Johansen, and V.Krozer, "Development of a compact 557GHz heterodyne receiver", 6th ESA Workshop on Millimeter-wave Technology and Applications and 4th Global Symposium on Millimeter Waves, 2011

- C.Jiang, V.Krozer, T.K.Johansen, H.G.Bach, G.G.Mekonnen, and L.Yan "Behavioral electromagnetic models of high-speed P-I-N photodiodes", *Microwave and Optical Technology Letters*, 2011

C.Jiang, T.K.Johansen, L.Yan, and B.Anja, "Cantilever-Based Microwave Biosensors: Analysis, Designs and Optimizations", Proceedings of the 27th Annual Review of Progress in Applied Computational Electromagnetics, 2011

# List of Figures

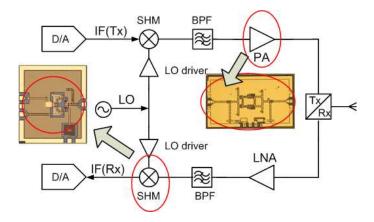

| 1.1 | Mm-wave RF transceiver system diagram.                           | 2  |

|-----|------------------------------------------------------------------|----|

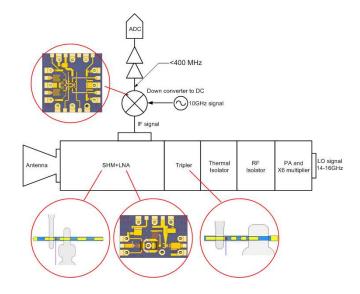

| 1.2 | System diagram of the THz heterodyne receiver at 557 GHz         | 4  |

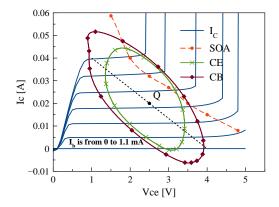

| 2.1 | Bias point selection for a InP DHBT single-finger device with    |    |

|     | emitter area: $0.7 \times 10 \ um^2$                             | 4  |

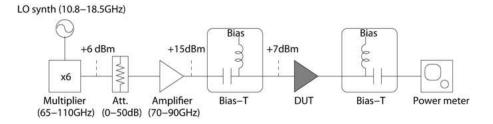

| 2.2 | Measurement setup for large-signal characterization              | 5  |

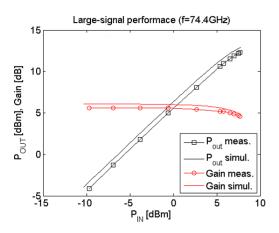

| 2.3 | Large-signal performance from power sweeping measurement         |    |

|     | for a single-finger common-emitter device at 74.4 GHz with       |    |

|     | 50 $\Omega$ terminations                                         | 5  |

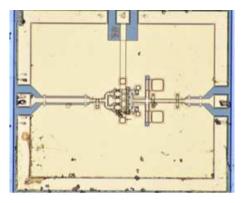

| 2.4 | Microphotograph of the four-way combined standard cascode        |    |

|     | power amplifier with chip dimension $1250 \times 1500 \ \mu m^2$ | 7  |

| 2.5 | Measured large-signal characteristics of the four-way combined   |    |

|     | standard cascode power amplifier                                 | 8  |

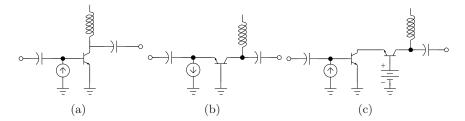

| 2.6 | Three standard circuit topologies: (a) common-emitter, (b)       |    |

|     | common-base, (c) cascode configurations.                         | 9  |

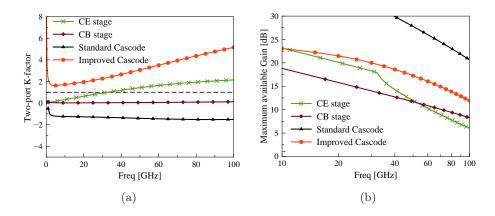

| 2.7 | Comparison of K-factor and maximum available $gain(G_{max})$     |    |

|     | for CE, CB and standard Cascode configurations. The im-          |    |

|     | proved K-factor of the inter-stage matched cascode configura-    |    |

|     | tion discussed later is also shown                               | 10 |

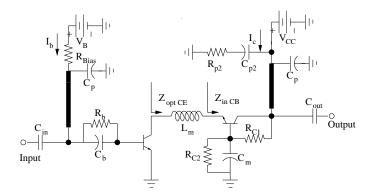

| 2.8 | Cascode configuration with inter-stage matching between common   | 1- |

|     | emitter and common-base devices.                                 | 11 |

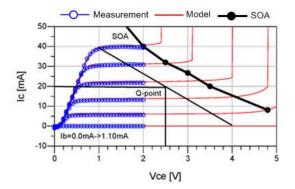

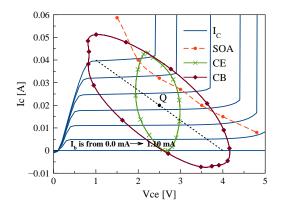

| 2.9 | Dynamic loading line of the CE and CB devices in the stan-       |    |

|     | dard cascode power cell are represented by the solid lines with  |    |

|     | symbols. The blue solid line represents the simulated output     |    |

|     | characteristic of a single-finger device model. The measured     |    |

|     | safe operation area(SOA) is indicated by the red dashed line.    | 12 |

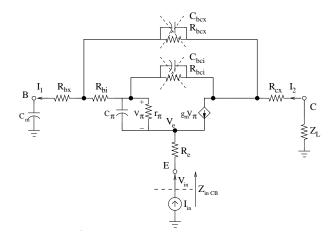

| 2.10 | Equivalent small-signal circuit of the CB device. The relevant                                                   |    |

|------|------------------------------------------------------------------------------------------------------------------|----|

|      | component values are extracted at $I_c=20$ mA and $V_{ce}=2.50$                                                  |    |

|      | V: $C_{\pi}$ =346.4 fF, $r_{\pi}$ =50.2 $\Omega$ , $R_{bi}$ =20.7 $\Omega$ , $R_{bx}$ =6.8 $\Omega$ , $R_e$ =4.0 |    |

|      | $\Omega$ , $R_{cx}=4.0 \ \Omega$ , $g_m=773 \ \text{mS}$ , $R_{bcx}=10.0 \ k\Omega$ , $R_{bci}=73.5 \ k\Omega$ , |    |

|      | $C_{bcx}=12$ fF, $C_{bci}=3.3$ fF, and $C_m$ is swept up to 200 fF                                               | 13 |

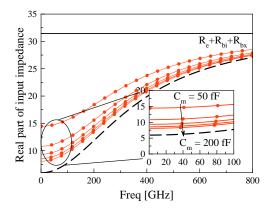

| 2.11 | Numerical response of the real part of the input impedance                                                       |    |

|      | for the simplified CB device shown in Fig.2.10.                                                                  | 14 |

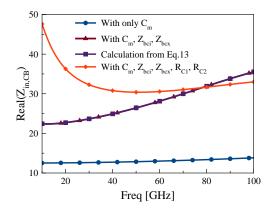

| 2.12 | Numerical influence on the real part of $Z_{in,CB}$ due to different                                             |    |

|      | feedback mechanisms.                                                                                             | 16 |

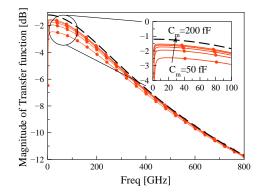

| 2.13 | Numerical response of the transfer function for the CB device                                                    |    |

|      | based on Eq.2.15                                                                                                 | 17 |

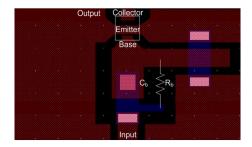

| 2.14 | Layout of CE stage with a base-ballasting network of $R_b/(1 +$                                                  |    |

|      | $j\omega R_b C_b$ ) and an open stub for interconnection of odd-mode                                             |    |

|      | stabilization resistor.                                                                                          | 19 |

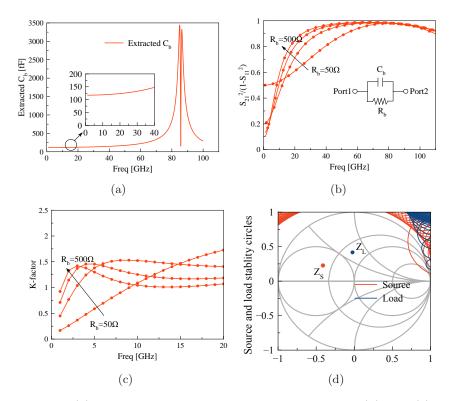

| 2.15 | (a) Extracted capacitance $C_b$ from the layout (b) and (c) is the                                               |    |

|      | transmission efficiency of the base-blasting network and the                                                     |    |

|      | associated low-frequency K-factor of the CE stage by sweeping                                                    |    |

|      | $R_b$ , respectively (d) source and load stability circles (1-110                                                |    |

|      | GHz) with fixed $R_b=250 \ \Omega$ and $C_b=117$ fF. $Z_S$ and $Z_L$ are                                         |    |

|      | from Table2.3                                                                                                    | 20 |

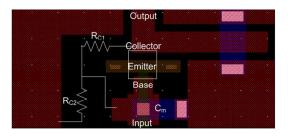

| 2.16 | Layout of CB stage with a self-biasing network of $R_{C1}$ , $R_{C2}$ ,                                          |    |

|      | an inter-stage matching capacitor $C_m$                                                                          | 21 |

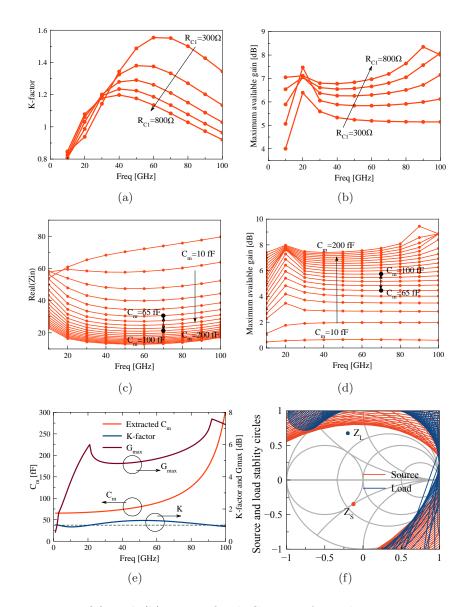

| 2.17 | (a) and (b) For a fixed $C_m=100$ fF and resistance ratio of                                                     |    |

|      | 0.4 between $R_{C1}$ and $R_{C2}$ , K-factor and $G_{max}$ is checked by                                         |    |

|      | sweeping $R_{C1}$ from 300 to 800 $\Omega$ respectively (c) and (d) real                                         |    |

|      | part of input impedance and $G_{max}$ of the CB device with                                                      |    |

|      | swept $C_m$ (e) extracted capacitance $C_m$ from Y-parameter                                                     |    |

|      | together with relevant K-factor and $G_{max}$ by fixing $R_{C1}=400$                                             |    |

|      | $\Omega$ and $R_{C2}$ =1000 $\Omega$ (d) source and load stability circles (1-100                                |    |

|      | GHz) with component values after optimization. $Z_S$ and $Z_L$                                                   |    |

|      | are from Table2.4.                                                                                               | 22 |

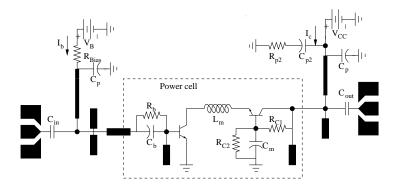

| 2.18 |                                                                                                                  |    |

|      | cascode power cell                                                                                               | 23 |

| 2.19 | Dynamic loading line of the CE and CB devices in the inter-                                                      |    |

|      | stage matched cascode power cell are represented by the solid                                                    |    |

|      | lines with symbols. The blue lines represent the simulated                                                       |    |

|      | DC characteristics from the device model. The measured safe                                                      |    |

|      | operation area(SOA) is indicated by the red dashed line                                                          | 24 |

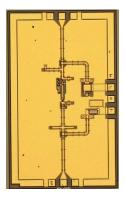

| 2.20 | Microphotography of designed single-branch interstage matched                                                    |    |

|      | cascode power amplifier with chip dimension of $1500^*2400 \ \mu m^2$ .                                          | 25 |

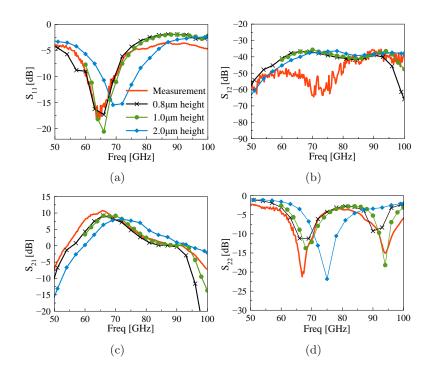

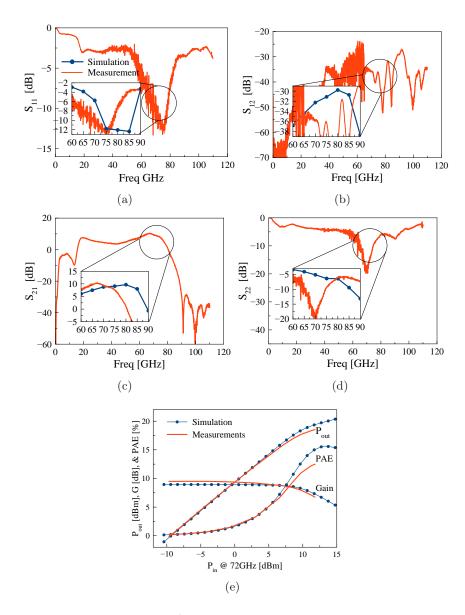

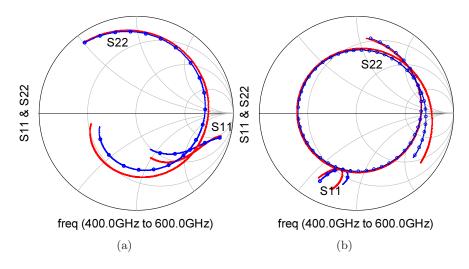

| 2.21 | Comparison of measured and simulated S-parameters with dif-                                                                                          |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | ferent dielectric thickness. The DC biasing points used for                                                                                          |     |

|      | measurement are: $V_{ce}=5.0$ V and $I_c=22$ mA                                                                                                      | 25  |

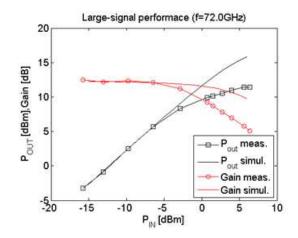

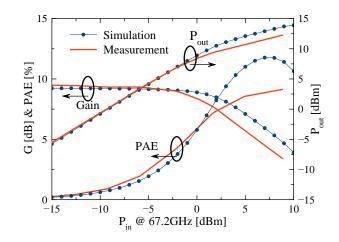

| 2.22 | Large-signal characterization of single-branch PA based on                                                                                           |     |

|      | single-finger devices. The comparison is done at 67.2 GHz                                                                                            |     |

|      | due to the downshifting of the designed PA: the red solid line                                                                                       |     |

|      | represents the measured output power, power gain, and effi-                                                                                          |     |

|      | ciency; the blue line with symbol represents the corresponding                                                                                       |     |

|      | simulated result.                                                                                                                                    | 26  |

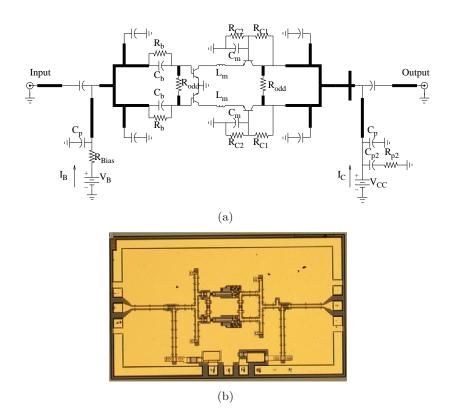

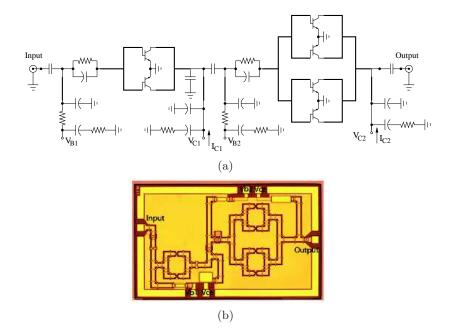

| 2.23 | (a) Schematic of two-way combined power amplifier based on                                                                                           |     |

|      | single-finger devices (b) Microphotography of the fabricated                                                                                         |     |

|      | chip with dimension of $1500^*2400 \ \mu m^2$ .                                                                                                      | 27  |

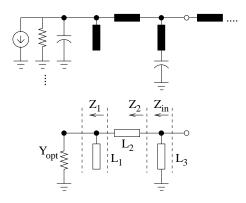

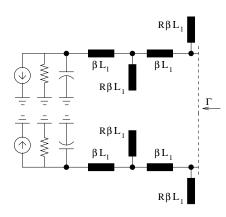

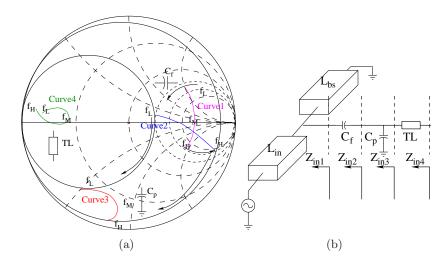

|      | Simplified half of the proposed power combining network                                                                                              | 28  |

| 2.25 |                                                                                                                                                      |     |

|      | and reflection on Smith chart with $Re(1/Y_{opt}) = Z_C = 50 \ \Omega$ and                                                                           |     |

|      | $\beta l$ =33° at 73.5 GHz                                                                                                                           | 31  |

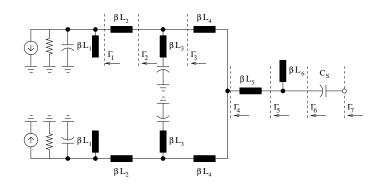

|      | Two-way output power combining and matching network                                                                                                  | 32  |

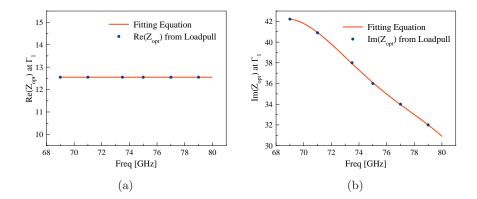

| 2.27 | Comparison of (a)real and (b)imaginary part of $Z_{opt}$ at $\Gamma_1$                                                                               |     |

|      | from load pull simulation with the numerical values from fit-                                                                                        |     |

|      | ting equation.                                                                                                                                       | 32  |

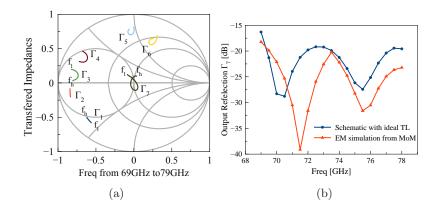

| 2.28 | (a) Reflections at different reference planes (b) numerical re-                                                                                      |     |

|      | sults from EM numerical and circuit simulator.                                                                                                       | 33  |

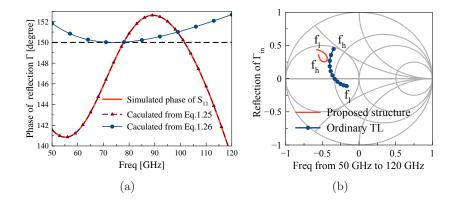

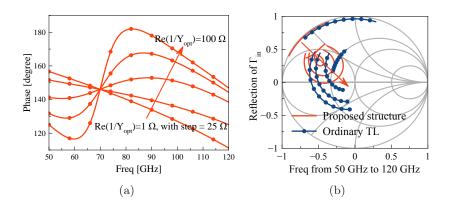

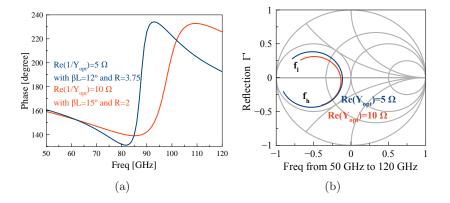

| 2.29 | (a,b) Phase responses and reflection from the proposed struc-                                                                                        |     |

|      | ture in Fig.2.24 and on Smith chart with different $Re(1/Y_{opt})$                                                                                   | 0.0 |

| 0.00 | and $\beta l = 33^{\circ}$ at 73.5 GHz.                                                                                                              | 33  |

| 2.30 | Two-way power combining network for large power devices $(1 - V_{1})^{-1}$                                                                           | 0.4 |

| 0.91 | with low $Re(1/Y_{opt})$ .                                                                                                                           | 34  |

| 2.31 | (a,b) Phase responses and reflection at $\Gamma$ with $Re(1/Y_{opt})=5$                                                                              | 25  |

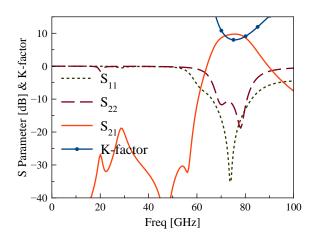

| า วา | or 10 $\Omega$ and $\beta l_1=12^\circ$ or $15^\circ$ and different ratio R at 73.5 GHz.<br>Small-signal performance of designed two-way combined PA | 35  |

| 2.02 | with the DC bias conditions: $V_{CC}=5$ V, $I_C=45.6$ mA and                                                                                         |     |

|      | with the DC bias conditions. $V_{CC}$ v, $T_{C}$ 45.0 mA and $V_{B}$ = 1.16 V, $I_{B}$ = 1.25 mA                                                     | 36  |

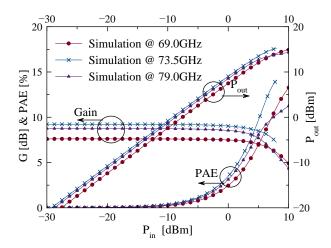

| 2 33 | Large-signal performance of the designed PA at 69 GHz, $73.5$                                                                                        | 50  |

| 2.00 | GHz, and 79 GHz with DC bias conditions: $V_{CC}$ =5V, $I_C$ =45.6                                                                                   |     |

|      | mA and $V_B$ =1.16 V, $I_B$ =1.25 mA                                                                                                                 | 36  |

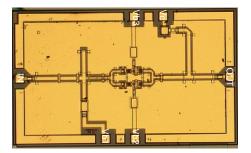

| 2.34 |                                                                                                                                                      | 00  |

| 2.01 | finger devices with the chip dimension of $1500^*2400\mu m^2$                                                                                        | 37  |

| 2.35 | Measured small/large-signal performance at DC bias condi-                                                                                            | - • |

| -    | tions of $I_{cc}$ =90mA and $V_c$ =5.0V: solid line represent the mea-                                                                               |     |

|      | surement results; the line with symbols is the simulation result.                                                                                    | 38  |

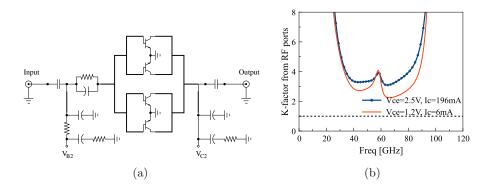

| 2.36 | (a) Schematic and (b) microphotography of the fabricated                                                                          |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------|------|

|      | two-stage common-emitter power amplifier with nominal DC                                                                          |      |

|      | biasing conditions: $I_{c1}=96$ mA, $I_{c2}=196$ mA, $V_c=2.5$ V                                                                  | 40   |

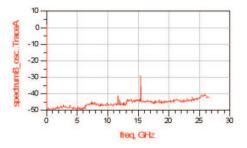

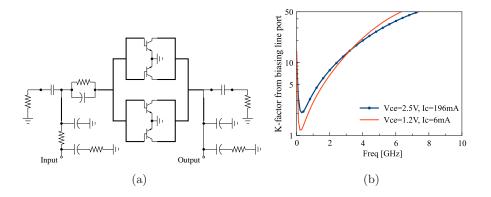

| 2.37 | Captured spectrum showing the oscillation around 15 GHz.                                                                          | 41   |

| 2.38 | RF Two-port K-factor analysis at the nominal and reduced                                                                          |      |

|      | DC biasing conditions.                                                                                                            | 42   |

| 2.39 | Stability analysis on biasing lines at the nominal and reduced                                                                    |      |

|      | DC biasing conditions. RF ports are terminated with 50 $\Omega_{\cdot}$ .                                                         | 43   |

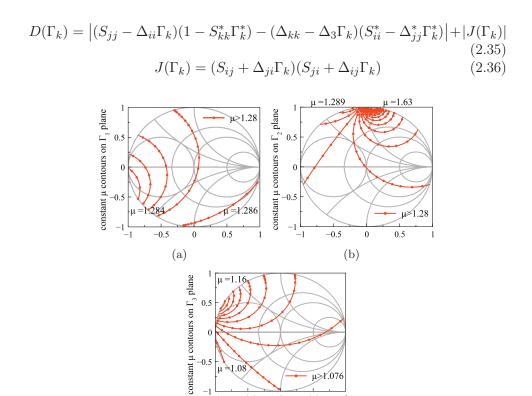

| 2.40 | Constant contours of $\mu_k$ calculated from three-port S-parameter                                                               |      |

|      | of the power stage with nominal DC bias operation conditions                                                                      |      |

|      | at 14 GHz: (a) viewed on the $\Gamma_1$ plane (b) viewed on the $\Gamma_2$                                                        |      |

|      | plane (c) viewed on the $\Gamma_3$ plane                                                                                          | 44   |

| 2.41 | Minimum $\mu_k$ for the frequency range from 1 to 40 GHz at the                                                                   |      |

|      | nominal DC operation conditions                                                                                                   | 45   |

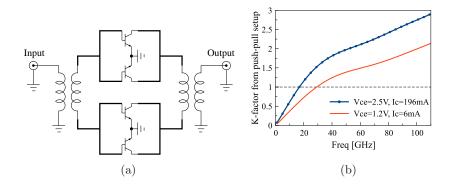

| 2.42 | Push-pull analysis at the nominal and reduced DC biasing                                                                          |      |

|      | conditions                                                                                                                        | 46   |

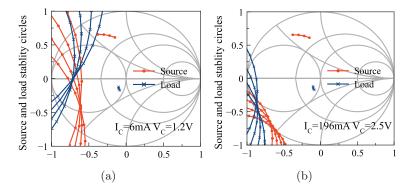

| 2.43 | Source and load stability circles for frequency range from 13                                                                     |      |

|      | to 16 GHz under the nominal (a) and reduced (b) DC biasing                                                                        |      |

|      | points                                                                                                                            | 46   |

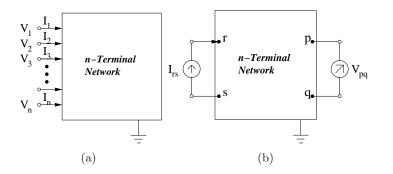

| 2.44 | (a) general symbolic representation of N-port network (b) sys-                                                                    |      |

|      | tem abstraction for the measurement of transimpedance                                                                             | 47   |

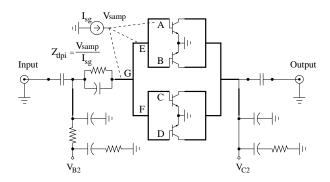

| 2.45 | Calculation of the driving point impedance with an auxiliary                                                                      |      |

|      | small-signal current source: $Z_{dpi}$ at different injection points                                                              |      |

|      | has different pole information due to the circuit symmetry                                                                        | 48   |

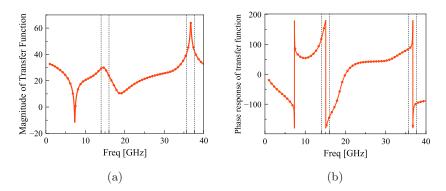

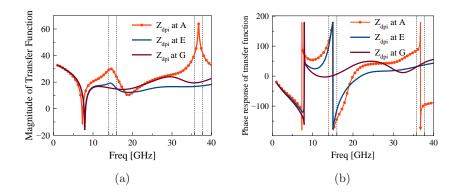

| 2.46 | Magnitude(a) and phase(b) response of the simulated driving                                                                       |      |

|      | point impedance at A point in Fig.2.45 with the reduced DC                                                                        |      |

|      | biasing conditions: $I_{c2}=6$ mA $V_{c2}=1.2$ V                                                                                  | 49   |

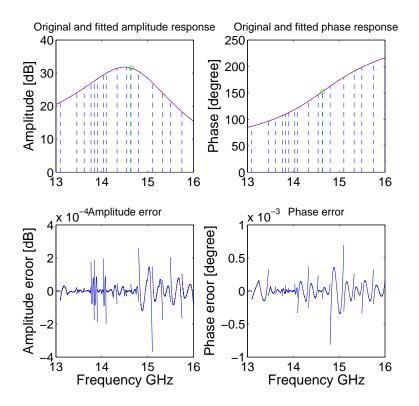

| 2.47 | Magnitude and unwrapped phase responses from the simula-                                                                          |      |

|      | tion (red solid line) and synthesized(blue dash line) transfer                                                                    |      |

|      | functions. One RHP between 14.5 to 15 GHz can be identified                                                                       | 50   |

| 0.40 | directly.                                                                                                                         | 50   |

| 2.48 | Magnitude(a) and phase(b) response of the calculated driving                                                                      |      |

|      | point impedance at A, E, and G point in Fig.2.45 with the                                                                         | F 1  |

| 9.40 | reduced DC biasing conditions.                                                                                                    | 51   |

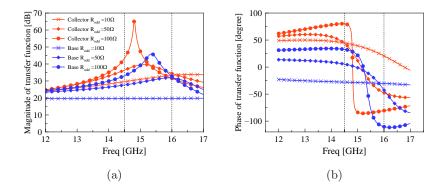

| 2.49 | Magnitude(a) and phase(b) response of the calculated driving                                                                      |      |

|      | point impedance at A point in Fig.2.45 with the reduced DC                                                                        |      |

|      | biasing conditions. Odd-mode stabilization resistors with the values of $10.0, 50.0$ and $100.0$ are inserted either at collector |      |

|      | values of 10 $\Omega$ , 50 $\Omega$ , and 100 $\Omega$ are inserted either at collector<br>or base of the devices                 | 51   |

|      |                                                                                                                                   | .) ( |

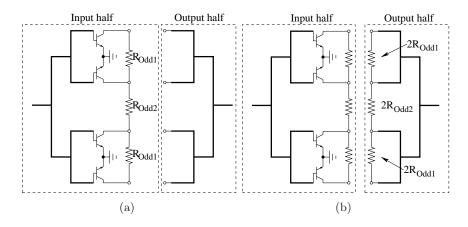

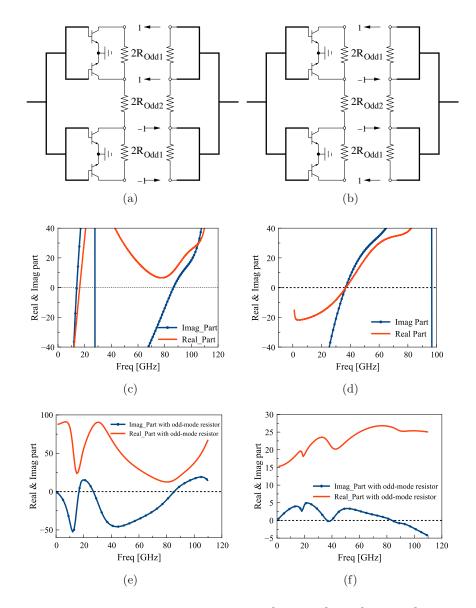

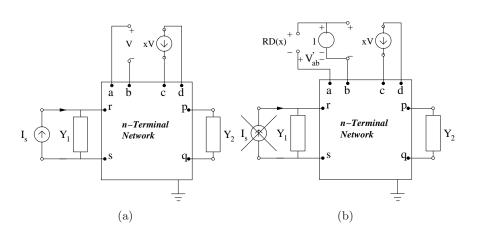

| 2.50 | Configuration for standard modal analysis(left) and extended modal analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

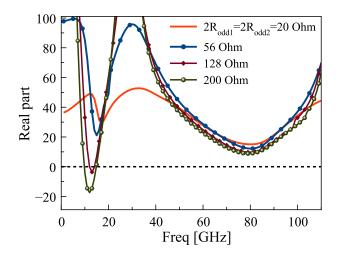

| 2.51 | Eigenvalue sums for modes of $[1 \ 1 \ -1 \ -1]$ and $[1 \ -1 \ -1 \ 1]$ under<br>the reduced DC biasing conditions of $I_{c2}=6$ mA and $V_{c2}=1.2$<br>V: (a,b,c) shows the circuit schematic with the assumed eigen-<br>vector mode of $[1 \ 1 \ -1 \ -1]$ , its corresponding eigenvalue sum<br>with infinite large $R_{odd1}$ and $R_{odd2}$ , and updated eigenvalue<br>sum with finite value of $2R_{odd1}$ and $2R_{odd2}=20 \ \Omega$ , respectively;<br>(d,e,f) shows the circuit schematic with the assumed eigenvec-<br>tor of $[1 \ -1 \ -1]$ , its corresponding eigenvalue sum with infinite<br>large $R_{odd1}$ and $R_{odd2}$ , and the updated eigenvalue sum with |    |

| 2 52 | finite value of $2R_{odd1}$ and $2R_{odd2}=20 \Omega$ , respectively Real part of eigenvalue sums for the mode of $[1 \ 1 \ -1 \ -1]$ with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

| 2.02 | different values of $2R_{odd1}$ and $2R_{odd2}$ at the reduced DC bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 2.53 | (a) A generalized feedback network with a dependent current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55 |

|      | source with a parameter of $x$ (b) physical significance of return difference $RD(x)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56 |

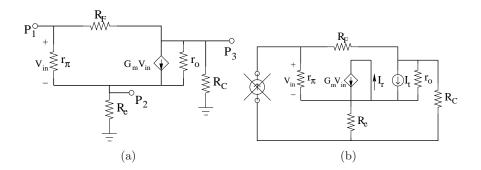

| 2.54 | RD analysis of a circuit with common-emitter configuration:<br>(a) the schematic for determinant calculation of the subject<br>network (b) RD calculation by disconnecting the dependent<br>source and injecting the small-signal tone                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58 |

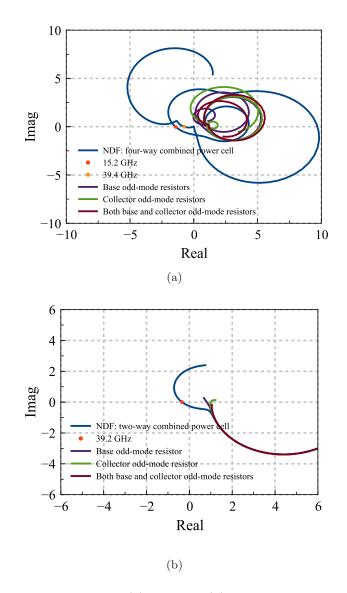

| 2.55 | NDF locus of the (a) four-way (b) two-way combined power<br>cells for the frequency range from 1 to 50 GHz. The blue curve<br>is the original NDF locus without stabilization resistors. The<br>other color solid line represents the case with stabilization                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

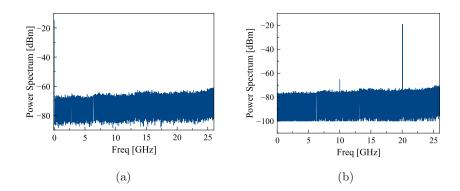

| 2.56 | resistors at only base, collector and both terminals respectively.<br>Captured frequency spectrum from the re-designed PA with<br>odd-mode stabilization resistors of 15 $\Omega$ for both $R_{odd1}$ and<br>$R_{odd2}$ : (a) power spectrum without incoming RF signal (b)<br>power spectrum with an injected tone from the network ana-                                                                                                                                                                                                                                                                                                                                            | 60 |

|      | lyzer into the PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61 |

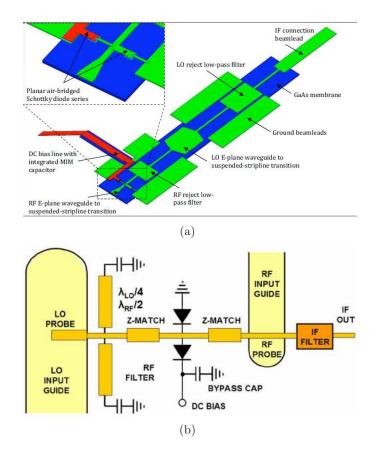

| 3.1  | SHM circuits based on the anti-parallel configuration: (a) low<br>noise SHM at 300 to 360 GHz [2] (b) balanced SHM design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

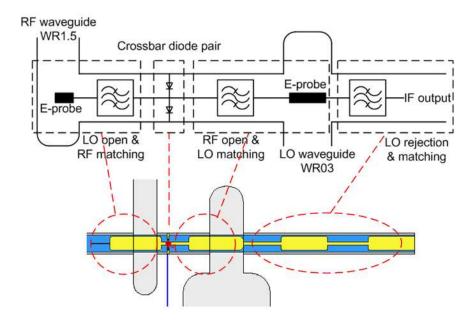

| 3.2  | with waveguide branch-line couplers at 340 GHz [3]<br>SHM circuits based on the crossbar diode configurations: (a) crossbar SHM design at 810 to 910 GHz [4] (b) crossbar SHM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70 |

|      | design at 520 to 590 GHz [5]. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71 |

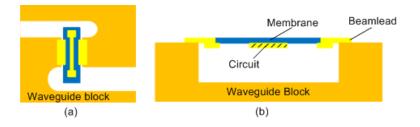

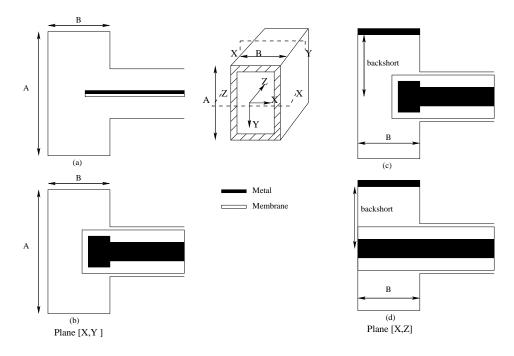

| 3.3  | Schematic pictures of the membrane circuits (a) top view (b)                                                                                                                                                                                                                                                                                            |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | cross section.                                                                                                                                                                                                                                                                                                                                          | 72 |

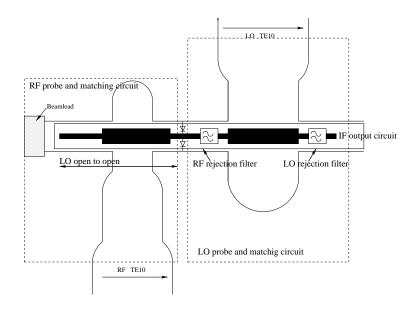

| 3.4  | Generalized SHM schematic at 557GHz                                                                                                                                                                                                                                                                                                                     | 73 |

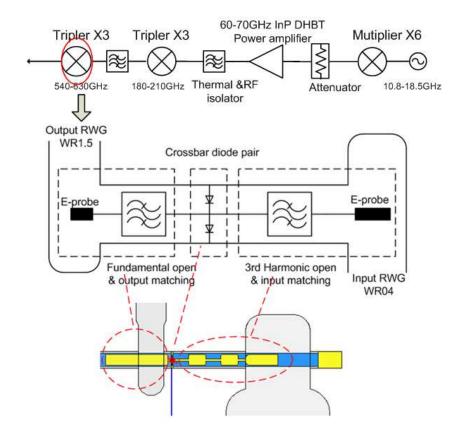

| 3.5  | RF signal generation chain by combining the designed tripler<br>and InP DHBT power amplifiers in this work. The inserted                                                                                                                                                                                                                                |    |

|      | figure shows the generalized schematic diagram of the tripler.                                                                                                                                                                                                                                                                                          | 74 |

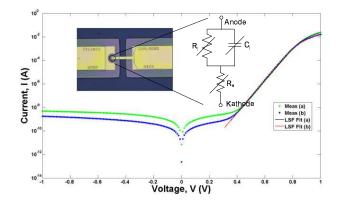

| 3.6  | Measured IV curve from the single finger diode. Inserted pic-<br>ture is the fabricated single device from Chalmers and its sim-<br>plified equivalent circuit model for the metal-semiconductor                                                                                                                                                        | 76 |

| 3.7  | contact [28]                                                                                                                                                                                                                                                                                                                                            |    |

|      | ear elements.                                                                                                                                                                                                                                                                                                                                           | 77 |

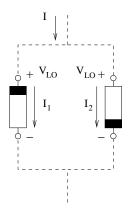

| 3.8  | Generic small-signal equivalent circuit of the crossbar SHM circuit.                                                                                                                                                                                                                                                                                    | 79 |

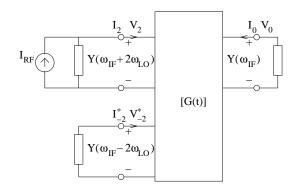

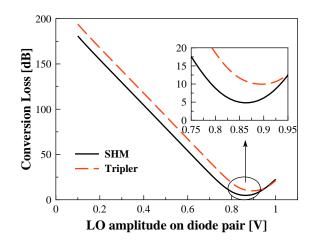

| 3.9  | Numerical results of the conversion loss by using the crossbar<br>diode pair (same as an antiparallel diode pair). The diode<br>parameter listed in Table 3.2 are used in the calculation of<br>large-signal conductance. The empirical impedance values for                                                                                            | 15 |

|      | RF and IF ports [29] are used for estimation.                                                                                                                                                                                                                                                                                                           | 80 |

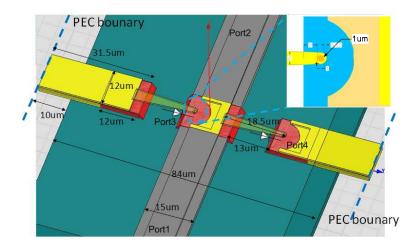

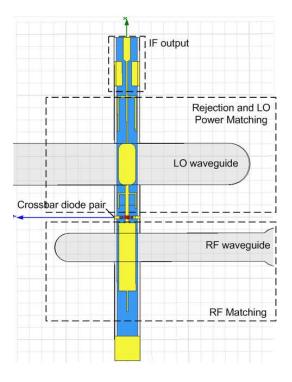

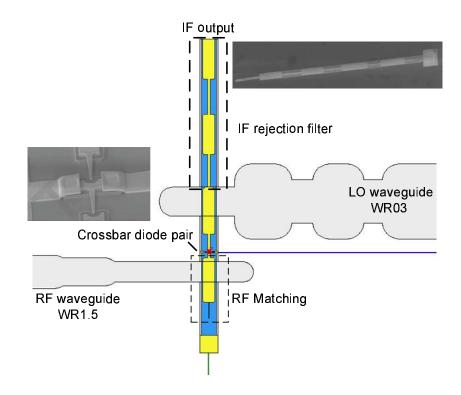

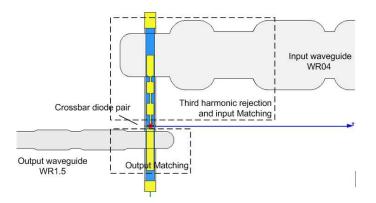

| 3.10 | SHM circuit configuration employed in this work                                                                                                                                                                                                                                                                                                         | 81 |

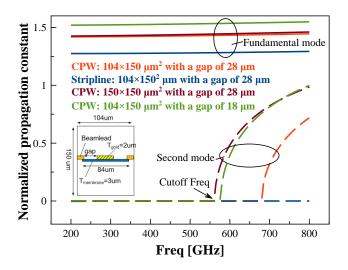

| 3.11 | The normalized propagation constant towards $\beta_0 = \omega / \sqrt{\mu_0 \epsilon_0}$<br>for different channel dimensions. The normalized fundamental<br>and second mode propagation constant of a specific channel<br>dimension are represented by solid and dashed lines with the<br>same color. The inserted figure shows the dimensions used for |    |

| 3.12 | the mode calculation                                                                                                                                                                                                                                                                                                                                    | 82 |

|      | tribution.                                                                                                                                                                                                                                                                                                                                              | 83 |

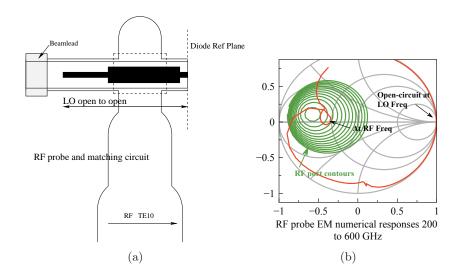

| 3.13 | EM model of the crossbar configuration inside of the metallic housing. The inserted figure shows the tapered finger geome-                                                                                                                                                                                                                              |    |

|      | try [28]                                                                                                                                                                                                                                                                                                                                                | 84 |

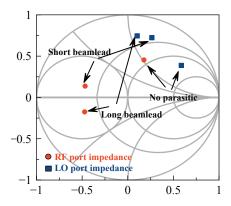

| 3.14 | Investigation of the beamlead parasitic influence. The RF<br>and LO optimum impedance are represented with red and<br>blue color respectively. The diode parameters used in the<br>load pull setup are listed in Table3.2. The SHM is simulated                                                                                                         |    |

|      | at $LO_{freq} = 283$ GHz, $RF_{freq} = 560$ GHz and $LO_{freq} = 6$ GHz.                                                                                                                                                                                                                                                                                | 85 |

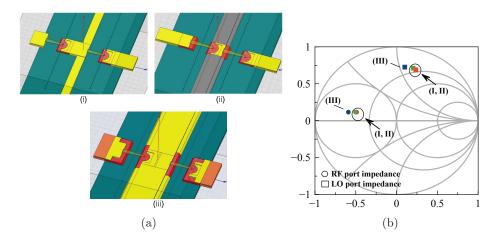

| 3.15 | symmetric about the central strip line [12] (ii) the finger struc-<br>ture is anti-symmetrical about the central strip line (iii) the                                                                                                                                                                                                                                                                           |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | larger dimensions of central mesa. (b) the corresponding op-<br>timum impedance on Smith chart.                                                                                                                                                                                                                                                                                                                 | 86 |

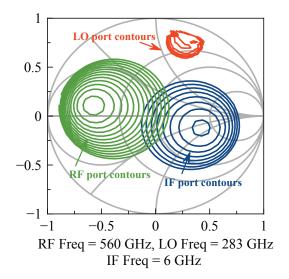

| 3.16 | Conversion loss contours for each port of the SHM. Numerical results are based on LO power level -1 dBm. The step of contours for LO port is 0.25 dB, the other ports are with a                                                                                                                                                                                                                                | ~  |

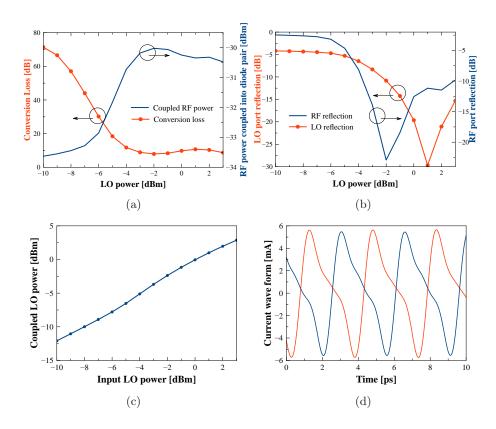

| 3.17 | step of 0.5 dB. All impedance are normalized to Z0=50 $\Omega$ SHM large-signal performance by sweeping the LO power levels with ideal filtering networks and terminations for all other mixing components and high order harmonics: (a) conversion loss and coupled RF power into the diodes (b) LO and RF port reflection (c) LO power coupled into the diodes (d) time do-                                   | 87 |

|      | main current waveforms for both diodes at -1 dBm LO power<br>level.                                                                                                                                                                                                                                                                                                                                             | 88 |

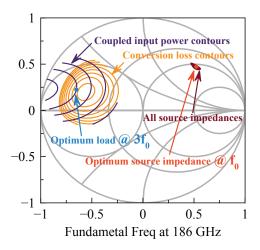

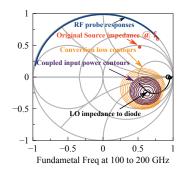

| 3.18 | Conversion loss contours with a step of 0.1 dB and coupled<br>fundamental input signal power contours with a step of 0.05<br>dB are shown. The corresponding source impedances at the<br>fundamental frequency are also indicated. The final optimum<br>load and reflected input impedance for circuit simulation are<br>noted. All impedance level are normalized to 50 $\Omega$                               | 89 |

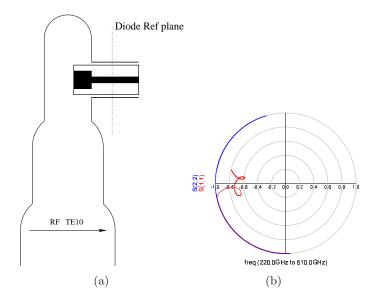

| 3.19 | Summary of the substrate orientation and probe types:(a) EM<br>energy is coupled into the circuit with the substrate perpendic-<br>ular to the broadside wall of the waveguide (b) the substrate<br>is parallel to the broadside wall of the waveguide (c) capaci-<br>tive E-probe with perpendicular orientation of the substrate<br>(d) inductive E-probe with perpendicular orientation of the<br>substrate. | 90 |

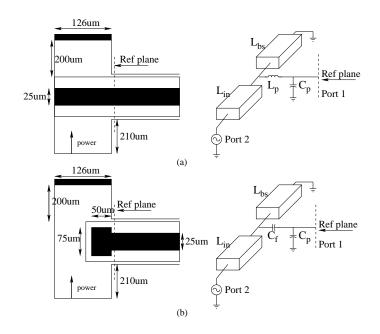

| 3.20 | Equivalent circuit models of (a) inductive E-probe and (b) capacitive E-probe.                                                                                                                                                                                                                                                                                                                                  | 92 |

| 3.21 | Comparison of frequency responses from EM numerical sim-<br>ulation and the corresponding equivalent circuit model: (a)                                                                                                                                                                                                                                                                                         |    |

| 3.22 | inductive E-probe (b) capacitive E-probe                                                                                                                                                                                                                                                                                                                                                                        | 92 |

|      | pacitive E-probe. The impedance at different reference planes corresponds to the different impedance curves on Smith chart.                                                                                                                                                                                                                                                                                     | 93 |

| 3.23 | Frequency responses of RF capacitive E-probe: (a) physical                                                      |     |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

|      | layout (b) the corresponding frequency responses. An open                                                       |     |

|      | stub (blue color)at fundamental LO frequency is used to fit                                                     |     |

|      | the low frequency response of the RF matching circuit(red                                                       |     |

|      | color).                                                                                                         | 95  |

| 3.24 | Frequency responses of the RF E-probe with half wavelength                                                      |     |

|      | transformer: (a) physical layout and (b) responses on the                                                       |     |

|      | Smith chart. The contours of conversion loss for RF port                                                        |     |

|      | is also shown.                                                                                                  | 95  |

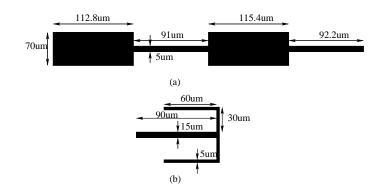

| 3.25 | Two types of RF rejection filters:(a) two-section step impedance                                                |     |

|      | rejection filter (b) folded open stubs filter                                                                   | 96  |

| 3.26 | Simulation results from circuit models and EM solver are com-                                                   |     |

|      | pared: (a) step-impedance rejection filter (b) OS rejection filter                                              | 97  |

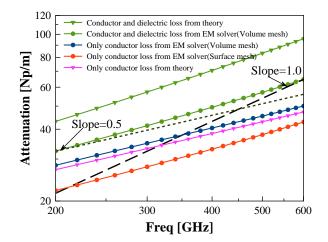

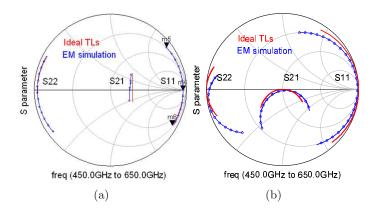

| 3.27 | Power loss comparison with surface and volume mesh for both                                                     |     |

|      | rejection filters.                                                                                              | 98  |

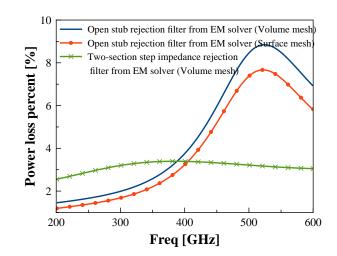

| 3.28 | Two types filters employed for LO & RF rejections: (a) Open                                                     |     |

|      | stubs (b) step-impedance (c) the transformed LO impedance                                                       |     |

|      | on Smith chart. The conversion loss contours of LO port is                                                      |     |

|      | also displayed.                                                                                                 | 99  |

| 3.29 | The proposed SHM layout.                                                                                        | 100 |

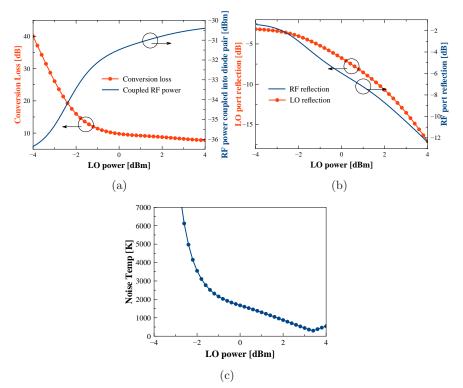

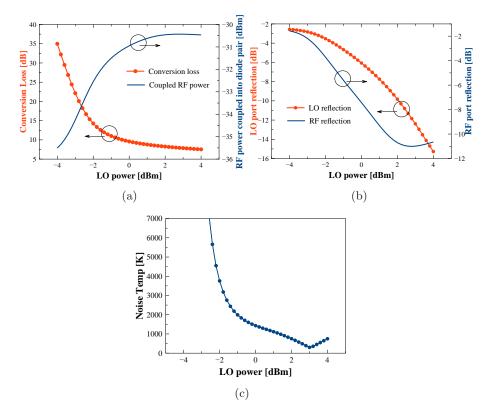

| 3.30 | SHM performance by sweeping the LO power from -4 dBm                                                            |     |

|      | to +4 dBm for a fixed $RF_{freq}$ at 560 GHz and $LO_{freq}$ at 283                                             |     |

|      | GHz: (a) conversion loss and coupled RF power (b) reflection                                                    |     |

|      | at RF& LO port (c) noise temperature.                                                                           | 101 |

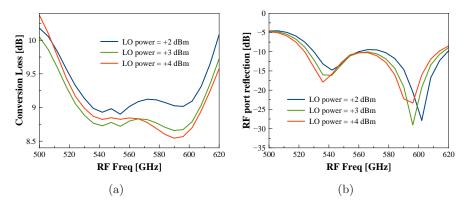

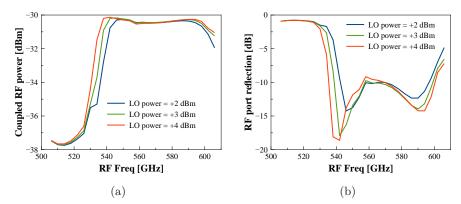

| 3.31 | RF bandwidth performance with different LO input power                                                          |     |

|      | levels from $+2$ to $+4$ dBm and a fixed $LO_{freg}$ at 283 GHz:                                                |     |

|      | (a) conversion loss (b) RF port bandwidth.                                                                      | 102 |

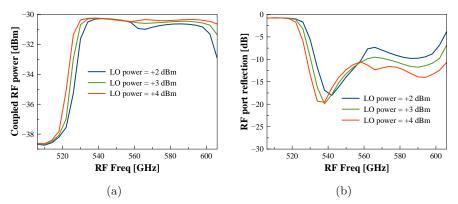

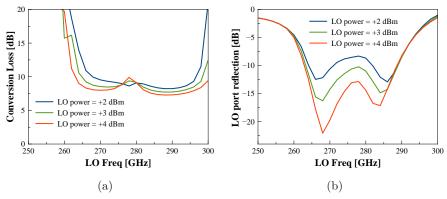

| 3.32 | RF port responses by sweeping $LO_{freq}$ from 250 to 300 GHz                                                   |     |

|      | with different LO power levels from $+2$ to $+4$ dBm. $IF_{freq}$                                               |     |

|      | is fixed at 6 GHz and $RF_{freq}$ is set to be the upper sideband                                               |     |

|      | signal at $2LO_{freq} + IF_{freq}$ : (a) coupled RF input power (b)                                             |     |

|      | The second se | 103 |

| 3.33 | LO RF port responses by sweeping $LO_{freq}$ from 250 to 300                                                    |     |

|      | GHz with different LO power levels from $+2$ to $+4$ dBm.                                                       |     |

|      | $IF_{freq}$ is fixed at 6 GHz and $RF_{freq}$ is set to be the upper                                            |     |

|      | sideband signal at $2LO_{freq} + IF_{freq}$ : (a) conversion loss (b)                                           |     |

|      |                                                                                                                 | 103 |

| 3.34 | Layout overview of the second SHM design                                                                        | 104 |

| 3.35 | SHM performance by sweeping the LO power from -4 dBm to +4 dBm for a fixed $RF_{freq}$ at 560 GHz and $LO_{freq}$ at 283 GHz: (a) conversion loss and coupled RF power (b) reflection |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | at RF& LO port (c) noise temperature                                                                                                                                                  | 05  |

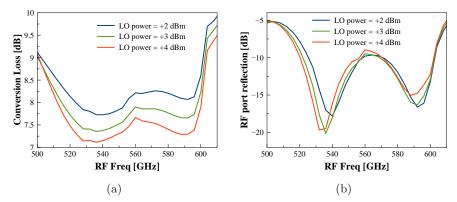

| 3.36 | RF bandwidth performance with different LO input power                                                                                                                                | 00  |

| 0.00 | from +2 to +4 dBm and a fixed $LO_{freq}$ at 283 GHz: (a)                                                                                                                             |     |

|      |                                                                                                                                                                                       | 06  |

| 3.37 | RF port responses by sweeping $LO_{freq}$ from 250 to 300 GHz                                                                                                                         | 00  |

| 0.01 | with different LO power levels from $+2$ to $+4$ dBm. $IF_{freq}$                                                                                                                     |     |

|      | is fixed at 6 GHz and $RF_{freq}$ is set to be the upper sideband                                                                                                                     |     |

|      | signal at $2LO_{freq} + IF_{freq}$ : (a) coupled RF input power (b)                                                                                                                   |     |

|      |                                                                                                                                                                                       | 06  |

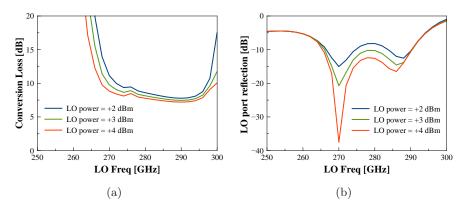

| 3 38 | LO RF port responses by sweeping $LO_{freq}$ from 250 to 300                                                                                                                          | 00  |

| 0.00 | GHz with different LO power levels from $+2$ to $+4$ dBm.                                                                                                                             |     |

|      | $IF_{freq}$ is fixed at 6 GHz and $RF_{freq}$ is set to be the upper                                                                                                                  |     |

|      | sideband signal at $2LO_{freq} + IF_{freq}$ : (a) conversion loss (b)                                                                                                                 |     |

|      |                                                                                                                                                                                       | 07  |

| 3.39 | Comparison of circuit model and full-wave EM simulation re-                                                                                                                           | · · |

|      | sults. The simulation conditions are the ones used in Fig.3.38                                                                                                                        |     |

|      | with LO pumping level of $+3$ dBm: (a) conversion loss (b)                                                                                                                            |     |

|      |                                                                                                                                                                                       | 08  |

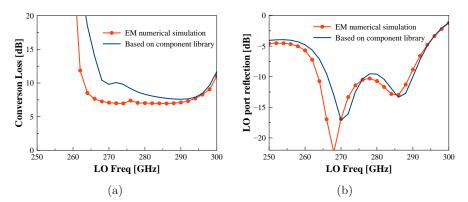

| 3.40 | Histogram of conversion loss and associated LO port reflection                                                                                                                        |     |

|      | for frequency range from 270 to 295 GHz: (a) collected conver-                                                                                                                        |     |

|      | sion loss from 2000 iterations (b) collected LO port reflection                                                                                                                       |     |

|      | from 2000 iterations (c) histogram of conversion loss at 282                                                                                                                          |     |

|      | GHz (d) histogram of LO port reflection at 282 GHz (e) his-                                                                                                                           |     |

|      | togram of conversion loss from 270 to 295GHz (f) histogram                                                                                                                            |     |

|      | of LO port reflection from 270 to 295 GHz                                                                                                                                             | 09  |

| 3.41 | Tripler layout with non-biased crossbar diode pair configuration.1                                                                                                                    | 10  |

| 3.42 | Tripler input matching responses. The output probe response                                                                                                                           |     |

|      | is also shown. The markers indicate the original optimum                                                                                                                              |     |

|      | source impedance at the beginning of the design procedure                                                                                                                             |     |

|      | and the new impedance due to the inductive output probe 1                                                                                                                             | 10  |

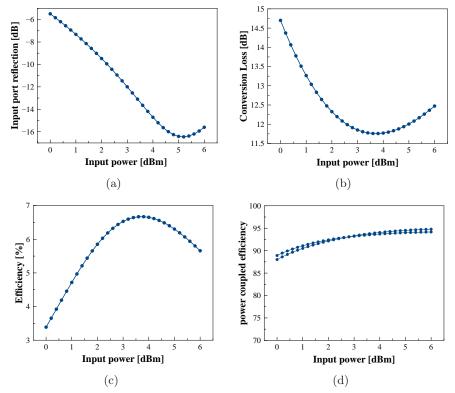

| 3.43 | Tripler large-signal performance by sweeping the input power                                                                                                                          |     |

|      | levels at a fixed input frequency at 190 GHz: (a) input re-                                                                                                                           |     |

|      | flection (b) conversion loss (c) efficiency (d) power coupled                                                                                                                         |     |

|      |                                                                                                                                                                                       | 11  |

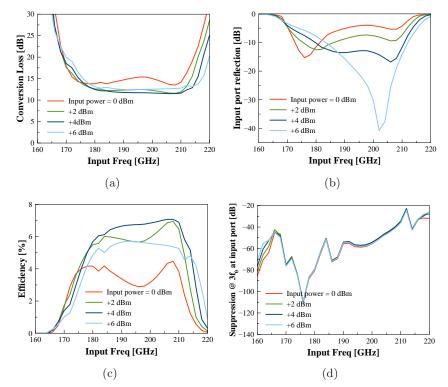

| 3.44 | Tripler bandwidth performance by sweeping the input fre-<br>quency from 120 to 220 GHz with the input power levels from<br>0 to $+6$ dBm: (a) conversion loss (b) input reflection (c) effi-<br>ciency (d) third order harmonic suppression at the input port. 112                                                                                                                                                                                                                          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

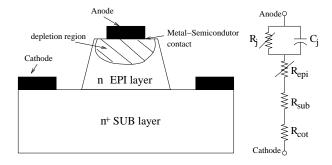

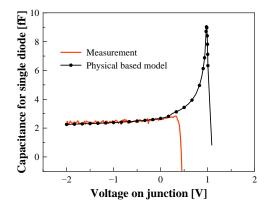

| 4.1  | Cross-section of the diode structure. The equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.2  | model is also shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

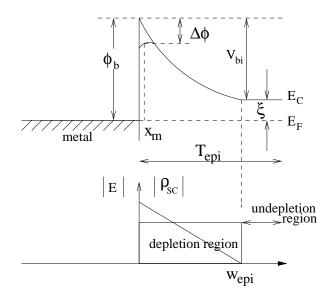

|      | is the space charge density. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                            |

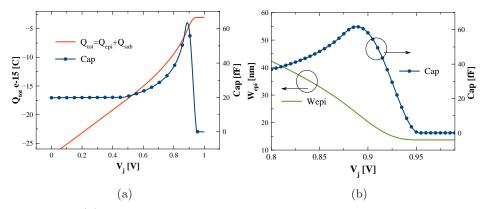

| 4.3  | (a) Calculated total charge $Q_{tot}$ and capacitance $C_{tot}$ in EPI<br>and SUB layers for different junction voltages $V_j$ . (b) deple-<br>tion width of EPI layer $w_{epi}$ under large forward bias. Calcu-<br>lation is based on the assumed values of $T_P=300$ K, $V_T=0.025$<br>V, $N_{epi}=1e23 m^{-3}$ , $N_{sub}=4e24 m^{-3}$ , $T_{epi}=80$ nm, $T_{sub}=5 \mu m$ ,                                                                                                           |

|      | $a=2.1 \ \mu m, \ Area=13.8 \ \mu m^2. \ldots 124$                                                                                                                                                                                                                                                                                                                                                                           |

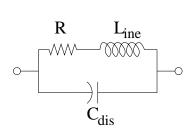

| 4.4  | The effect of displacement current and charge carrier inertia                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | are taken into account by a parallel network with a capaci-<br>tance of $C_{dis}$ and an inductance of $L_{ine}$ . R is the DC resistance                                                                                                                                                                                                                                                                                                                                                   |

| 4.5  | from EPI or SUB layer. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                  |

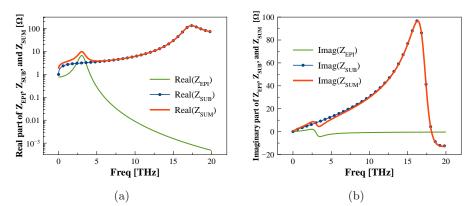

|      | $Z_{SUB}$ , and $Z_{SUM}$ . AC conductivity of the EPI and SUB<br>layer are considered by Eq.4.21. The total impedance is cal-<br>culated as $Z_{SUM} = Z_{EPI} + Z_{SUB}$ . The calculation procedure<br>are based on the assumed values of $T_P$ =300 K, $V_T$ =0.025 V,<br>$N_{epi}$ =1e23 $m^{-3}$ , $N_{sub}$ =3e24 $m^{-3}$ , $\mu_{epi}$ =4123 $cm^2/Vs$ , $\mu_{sub}$ =2068<br>$cm^2/Vs$ , $\omega_{s,epi}$ = 6.78e+12 rad/s, $\omega_{d,epi}$ = 5.69e+13 rad/s, $\omega_{s,sub}$ = |

|      | 1.36e+13 rad/s, and $\omega_{d,sub}$ = 8.57e+14 rad/s, $\epsilon$ =1.16e-10 F/m. 127                                                                                                                                                                                                                                                                                                                                                                                                        |

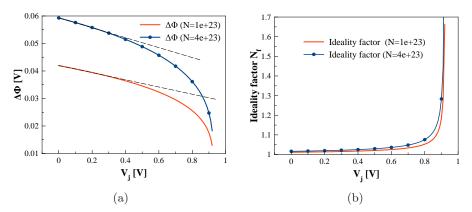

| 4.6  | (a) Barrier height lowering $\Delta \phi$ with different junction voltages $V_j$ and doping levels (b) the corresponding ideality factor $N_f$ .<br>Calculation is based on the assumed values of $T_P=300$ K, $V_T=25$ mV, $N_{epi}=1e+23$ $m^{-3}$ , $V_{bi}=0.953$ V, $\epsilon=1.16e-10$ F/m.<br>It is also assumed that the dependency of $V_{bi}$ on $N_{epi}$ is weak and can be ignored                                                                                             |

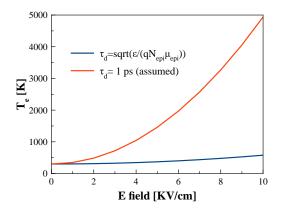

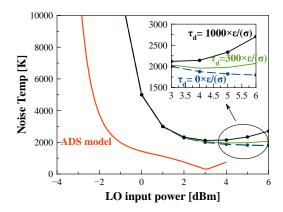

| 4.7  | Calculated equivalent noise temperature with different $\tau_d$ : one with assumed 1ps, the other is calculated based on Eq.4.19(b). |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | The parameters used in the calculation are $T_P=300$ K, $V_T=0.025$                                                                  |     |

|      | V, $N_{epi}=2e+22 m^{-3}$ , $\tau_s=2.3e-13$ s from Eq.4.19(a), $\tau_d=6.04e-$                                                      |     |

|      | 14 s from Eq.4.19(b), $\epsilon$ =1.16e-10 F/m, $\mu_{epi}$ =6000.0 cm <sup>2</sup> /Vs,                                             |     |

|      | $m^* = 0.068m_0$ , and $m_0$ is electron mass with 9.1e-31 kg                                                                        | 132 |

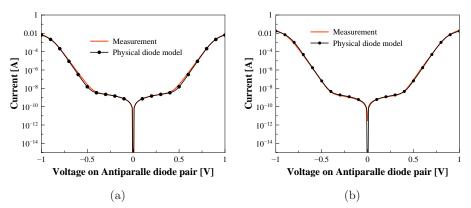

| 4.8  | The comparison of measured and simulated current-voltage                                                                             |     |

| -    | characteristics for two antiparallel diodes with (a) $a = 0.5 \ \mu m$                                                               |     |

|      | (b) $a = 1.0 \ \mu m.$                                                                                                               | 133 |

| 4.9  | The comparison of junction capacitance -voltage character-                                                                           |     |

| 1.0  | istics on a diode with $a=0.5 \ \mu m$ . Simulation results from                                                                     |     |

|      | physical diode model is shown.                                                                                                       | 134 |

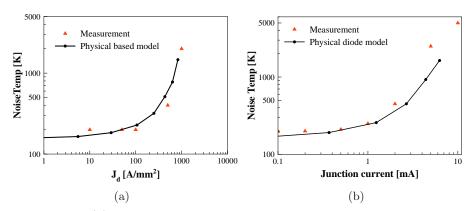

| 4 10 | (a) Noise temperature versus current density. The measured                                                                           | 101 |

| 1.10 | data is from [11] with diode parameters of $N_{epi}$ =2e+22 m <sup>-3</sup> ,                                                        |     |

|      | $a=1.5 \ \mu m$ , and $\phi_b=0.99 \ V$ . (b) noise temperature versus                                                               |     |

|      | current through the junction. The measured data is from                                                                              |     |

|      | [12] with diode parameters of $N_{epi}$ =4e+22 $m^{-3}$ , a=0.89 $\mu m$ ,                                                           |     |

|      | $T_{epi}$ =120 nm, and barrier height $\phi_b$ = 1.0 V                                                                               | 135 |

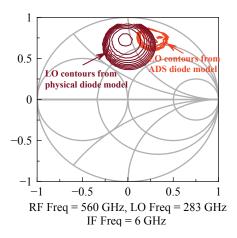

| 4 11 | Comparison of LO port contours with two different diode                                                                              | 100 |

|      | models.                                                                                                                              | 136 |

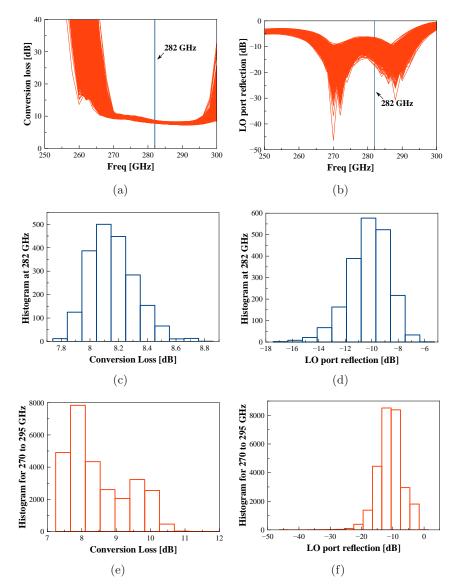

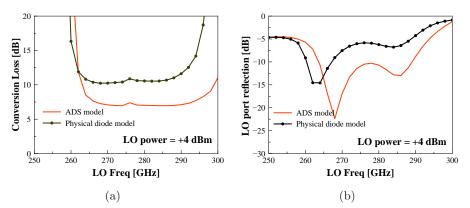

| 4.12 | Comparison of LO port responses by using different diode                                                                             |     |

|      | models with the same LO input power $+4 \text{ dBm}$ (a) conversion                                                                  |     |

|      | loss (b) LO port reflection.                                                                                                         | 136 |

| 4.13 | Comparison of simulated noise temperature for designed SHM                                                                           |     |

|      | by using ADS model and physical diode model. The simulated                                                                           |     |

|      | noise temperature with different factors are also compared.                                                                          |     |

|      | For the factor of zero, the hot electron noise is turned off                                                                         | 137 |

|      | ·                                                                                                                                    |     |

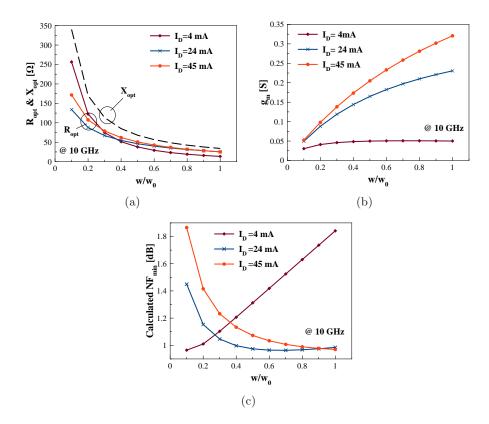

| 5.1  | (a) Calculated $R_{opt}$ and $X_{opt}$ (b) $g_m$ (c) $NF_{min}$ versus $w/w_0$                                                       |     |

|      | at 10 GHz for a common source configuration. The associated                                                                          |     |

|      | model parameters are based on the Eq.5.10. $\ldots$ $\ldots$ $\ldots$                                                                | 143 |

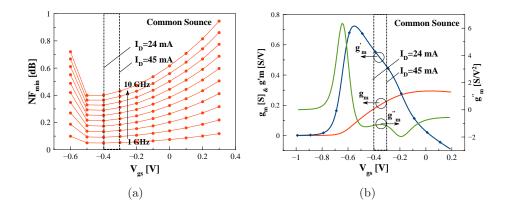

| 5.2  | (a) Simulated $NF_{min}$ with a 0.6 mm device up to 10 GHz for                                                                       |     |

|      | different bias point (b) $g_{m}$ , its first order derivative $g'_{m}$ , and                                                         |     |

|      | second order derivative $g''_m$                                                                                                      | 144 |

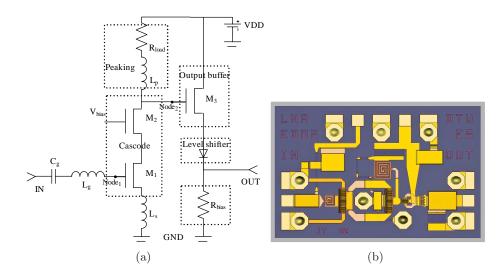

| 5.3  | (a) Circuit schematic of LNA with the relevant components                                                                            |     |

|      | values: $R_{load}$ =40 $\Omega$ , $R_{bias}$ =100 $\Omega$ , $L_g$ =0.33 nH, $L_p$ =1.5 nH,                                          |     |

|      | $C_g{=}6$ pF, 600 $\mu{\rm m}$ gate width for cascode devices (b) Mi-                                                                |     |

|      | crophotography of LNA MMIC                                                                                                           | 145 |

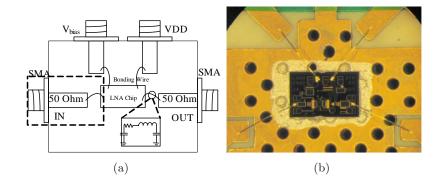

| 5.4 | (a) Evaluation board for noise characterization: the influence                                        |     |

|-----|-------------------------------------------------------------------------------------------------------|-----|

|     | of SMA connector, 50 $\Omega$ transmission line, and the bonding                                      |     |

|     | wire within the dashed line box has to be de-embedded (b)                                             |     |

|     | LNA chip is connected to the PCB evaluation board with long                                           |     |

|     | bonding wires.                                                                                        | 146 |

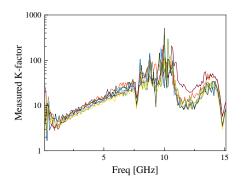

| 5.5 | Measured K-factor at various DC bias points from $I_D=30$ mA                                          |     |

|     | and $V_{CC}=3$ V to $I_D=60$ mA and $V_{CC}=5$ V                                                      | 146 |

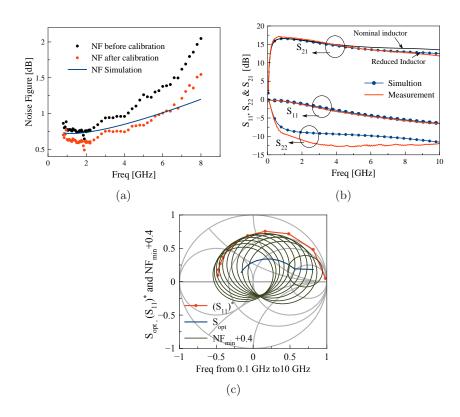

| 5.6 | (a) Measured and simulated noise figure from 0.8 to 8 GHz:                                            |     |

|     | discrete circles represent the measured noise figure before and                                       |     |

|     | after calibration; the solid line represents the simulation re-                                       |     |

|     | sult; (b) Measured and simulated input, output return loss,                                           |     |

|     | and power gain (c) simulated $S_{opt}$ , $(S_{11})^*$ , and constant noise                            |     |

|     | figure circles with predicted $NF = NF_{min} + 0.4$ dB from 0.1 to                                    |     |

|     | 10 GHz                                                                                                | 148 |

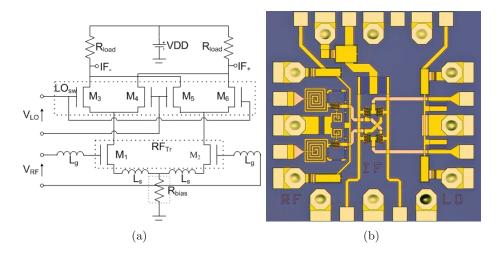

| 5.7 | (a) Circuit schematic of the active mixer with components                                             |     |

|     | values: $R_{load}$ =100 $\Omega$ , $R_{bias}$ =50 $\Omega$ , $L_s$ =0.25 nH, $L_g$ =1.5 nH,           |     |

|     | 112 $\mu \mathrm{m}$ gate width for devices in the transconductance stage,                            |     |

|     | and $90\mu m$ gate width for devices in the switching stage (b)                                       |     |

|     | Microphotography of the implemented Gilbert cell mixer with                                           |     |

|     | the chip dimension of $1200^*1200 \ \mu m^2$ .                                                        | 149 |

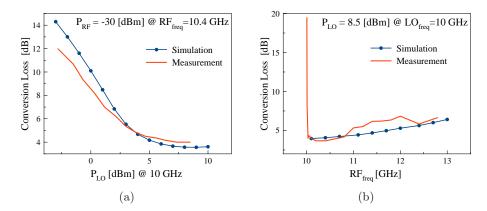

| 5.8 | (a) Measured and simulated conversion loss versus LO power                                            |     |

|     | levels at $LO_{freq}=10$ GHz and $RF_{freq}=10.4$ GHz (b) RF band-                                    |     |

|     | width performance with the fixed LO power of $+8.5$ dBm and                                           |     |

|     | $LO_{freq} = 10 \text{ GHz.} \dots \dots$ | 150 |

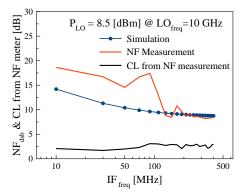

| 5.9 | Measured and simulated double sideband NF at different IF                                             |     |

|     | frequencies. The calculated conversion loss from NF meter                                             |     |

|     | are also shown                                                                                        | 151 |

## List of Tables

| 2.1 | Summary of reported power amplifiers based on InP DHBT                   |    |

|-----|--------------------------------------------------------------------------|----|

|     | and InP HEMT technologies. The sign $*$ represents the de-               |    |

|     | signs based on InP HEMT; N-way means n-way parallel power                |    |

|     | combining; G is the linear power gain; $P_{1dB}$ is the output 1dB       |    |

|     | compression point; $P_{sat}$ is the saturated output power; PAE          |    |

|     | represents the power added efficiency; $A_e$ is the emitter are;         |    |

|     | $L_g$ means the length of gate strip                                     | 2  |

| 2.2 | Comparison of three standard circuit topologies in term of $G$ ,         |    |

|     | $P_{1dB}$ , peak PAE, $P_{sat}$ , together with corresponding source and |    |

|     | load impedance. The large-signal simulation is performed at              |    |

|     | 73.5 GHz without stabilization resistors and layout parasitics.          |    |

|     | All devices are biased on $V_{ce}=2.5$ V, $I_c=20$ mA                    | 10 |

| 2.3 | Large-signal characteristics of CE stage including layout par-           |    |

|     | asitics at 73.5 GHz                                                      | 19 |

| 2.4 | Large-signal characteristics of the CB stage including layout            |    |

|     | parasitics at 73.5 GHz                                                   | 21 |

| 2.5 | Large-signal characteristics of the power cell from the dash-            |    |

|     | line box in Fig.2.18 at 73.5 GHz.                                        | 23 |

| 2.6 | Eigenvalues for two most common eigenvectors $[I_{half}]$                | 53 |

| 2.7 | Comparison of all instability detection methods in term of               |    |

|     | implementation, application circumstances, pre-knowledge of              |    |

|     | device models, and the ability of odd-mode instability detection.        | 63 |

| 3.1 | Sub-harmonic mixer specifications (Numbers in parenthesis                |    |

|     | are goals)                                                               | 75 |

| 3.2 | Extracted diode parameters from DC and capacitance mea-                  |    |

|     | surements                                                                | 75 |

| 3.3 | Summary of SHM performance for both antiparallel and cross-                                                                     |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

|     | bar configuration from the open literatures. SHM: Sub-Harmonic                                                                  |

|     | Mixer, CL: Conversion Loss, FBM: Fundamental Balanced                                                                           |

|     | Mixer, $N_T$ : Noise Temperature                                                                                                |