## NEUROMORPHIC APPLICATION OF OXIDE SEMICONDUCTORS

Mutsumi Kimura, Ryukoku University, Nara Institute of Science and Technology, mutsu@rins.ryukoku.ac.jp Tokiyoshi Matsuda, Ryukoku University Tomoya Kameda and Yasuhiko Nakashima, Nara Institute of Science and Technology

## Key Words: Neuromorphic application, Oxide semiconductor

Artificial intelligences are promising as key technologies in future societies. However, the conventional ones are executed using complicated software on high-specked hardware, and the machine size is very bulky and power consumption is unbelievably huge. Therefore, we are investigating "braintype integrated system", namely, neural network built only by hardware, which can be compact, low power, robust, and integrated on everything in future. In order to realize that system, simplification of the processing elements, such as neurons and

synapse, three-dimensional structure, and low cost fabrication are required. We have succeeded in that simplification and are trying to utilize oxide semiconductors for the neuromorphic application because they can be fabricated using low cost fabrication such as sputtering and printing, by which the three-dimensional structure can be obtained in future.

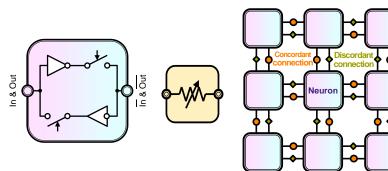

Figure 1 shows the structure of the neuron, synapse, and network [1]. We succeeded in simplifying the neuron circuit to a two-inverter and two-switch circuit and reducing the synapse device to a variable resistor. We adopted a cellar neural network, which is suitable for the integrated system because a neuron is connected only to the neighboring neurons. Instead, we prepared two-type synapses, concordant and discordant synapses, which tend to make the states of the connected neurons the same and different, respectively.

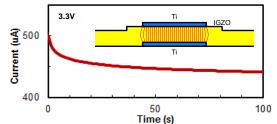

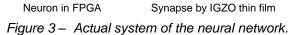

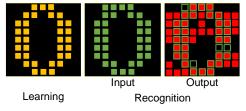

Figure 2 shows the characteristic of the In-Ga-Zn-O thin film [2]. Here, we sandwiched an In-Ga-Zn-O thin film of 70 nm thickness by Ti electrodes of 150x150 um area and applied 3.3 V. It is found that the conductance decreases as the time goes by. This characteristic is available to modified Hebbian rule, which is a learning rule we proposed for our network [3]. Figure 3 shows the actual system of the neural network. Here, we formed the neuron circuit in an FPGA and the synapse devices by an In-Ga-Zn-O thin film, where 80 horizontal and 80 vertical line electrodes formed 6400 synapses. We have already confirmed the learning of simple logic using smaller scale network. We are now trying to make this network learn number letters and came just around the corner of the success. It should be noted that the synapse devices are currently fabricated separately, but they can be stacked on LSI chip potentially.

[1] M. Kimura, Neurocomputing, in press [2] M. Kimura, IDW '16, 398 [3] M. Kimura, JJAP 54, 03CB02, 2015