# TECHNISCHE UNIVERSITÄT CHEMNITZ

# Evaluation of AXI-Interfaces for Hardware Software Communication

Master Thesis

Submitted in Fulfilment of the Requirements for the Academic Degree M.Sc. in Embedded Systems

Dept. of Computer Science Chair of Computer Engineering

Submitted by: Ankit Sharma Student ID: 425911 Date: 19.12.2018

Supervising tutor: Prof. Dr. W. Hardt Dipl. Inf. René Schmidt

# Abstract

A SoC design approach is implemented for the MERGE project which features Machine Learning (ML) interface for the hardware design. This setup deals with detection and localization of impact on a piezo metal composite. Development of the project is executed on Digilent ZYBO board. ZYBO incorporates Xilinx ZYNQ architecture. This architecture provides Processing System (PS) and Programmable Logic (PL) that communicate with each other via AMBA Standard AXI4 Interface.

Communication cost have major influence on the system performance. A optimized hardware software partitioning solution will reduce the communication costs. Therefore, best fitting interface for the provided design is needed to be evaluated to trade-off between cost and performance. High performance of AXI Interface will provide efficient localization of impact, especially for real-time scenario. In the thesis, the performance of three different AXI4 interface are evaluated. Evaluation is performed on the basis of the amount of data transferred and the time taken to process it.

Evaluation of interfaces are done through implementation of test cases in Xilinx SDK. Hardware design for AXI4-Interfaces is implemented in Vivado and later tested on Digilent ZYBO board. To test the performance of interfaces, read and write operations are initiated by PS on interface design. Each operation is performed for multiple data lengths. Average execution time is calculated that highlights time taken to transfer the corresponding input data length.

Through these tests, it is found that AXI4-Stream is the best choice for a continuous set of data. Preferably, it provides unlimited burst length which is useful for the current project. Among other two interfaces, AXI4-Full performed better in terms of execution time as compared to AXI4-Lite.

#### Keywords: AXI4-Full, AXI4-Lite, AXI4-Stream, Vivado, ZYNQ

# Contents

| Co  | onten                               | ts                                                                                                                                                                                                                                                                                                                     |

|-----|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lis | st of                               | Figures                                                                                                                                                                                                                                                                                                                |

| Lis | st of                               | Tables   7                                                                                                                                                                                                                                                                                                             |

| Lis | st of                               | Abbreviations                                                                                                                                                                                                                                                                                                          |

| Ac  | know                                | vledgments                                                                                                                                                                                                                                                                                                             |

| 1.  | <b>Intro</b><br>1.1.<br>1.2.        |                                                                                                                                                                                                                                                                                                                        |

| 2.  |                                     | The of the Art12Possible Communication Alternatives for FPGA122.1.1. Serial Peripheral Interface122.1.2. Inter-Integrated Circuit132.1.3. Controller Area Network152.1.4. Universal Serial Bus172.1.5. TIA/EIA Standards19                                                                                             |

|     | <ul><li>2.2.</li><li>2.3.</li></ul> | Outline of SoC Bus Standards       22         2.2.1. AMBA       22         2.2.2. CoreConnect       25         2.2.3. Wishbone       26         2.2.4. Avalon       28         2.2.5. Open Core Protocol       29         ZYNQ Architecture       29         2.3.1. Overview       30         2.3.2. Features       31 |

|     | 2.4.                                | 2.3.3. Communication Interfaces    32      Basis for Evaluation    36                                                                                                                                                                                                                                                  |

| 3.  | 3.1.                                | cept38Comparison of SoC Bus Standards38Approach for Evaluation of AXI Interfaces40                                                                                                                                                                                                                                     |

### CONTENTS

|     | 3.3.   | Evaluation Platform                         | 11         |

|-----|--------|---------------------------------------------|------------|

|     |        | 3.3.1. Hardware                             | 11         |

|     |        | 3.3.2. Software                             | 12         |

| 4.  | Impl   | ementation                                  | 15         |

|     | •      | Overview of FPGA Implementation             |            |

|     |        | 4.1.1. MERGE_PL FPGA IP                     |            |

|     | 4.2.   | Hardware and Software Design for Evaluation |            |

|     |        | 4.2.1. Hardware Design                      |            |

|     |        | 4.2.2. Software Design                      |            |

| 5.  | Resi   | Ilts and Discussion                         | 57         |

| -   |        | Read Operation                              |            |

|     | 5.2.   |                                             |            |

|     | 5.3.   | Comparison of Results                       |            |

| 6.  | Con    | clusion and Further Work                    | '6         |

| Bil | bliogr | raphy                                       | <b>'</b> 9 |

| An  | nex /  | A. Optimization level 2 flags               | 33         |

| An  | nex    | B. AXI4-Full Test Design                    | 84         |

| An  | inex ( | C. AXI4-Stream Clocking Wizard Design       | 85         |

| An  | nex    | D. AXI4-Full CDMA Design                    | 86         |

# **List of Figures**

| 1.1.  | Processing chain of Piezo Metal Composite[37]                                                                                      | 10 |

|-------|------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2.  | Block Diagram of the current design                                                                                                | 11 |

| 0.1   |                                                                                                                                    | 10 |

| 2.1.  | SPI Bus Topologies[3]                                                                                                              | 13 |

| 2.2.  | Typical Embedded Microprocessor System with an FPGA[2]                                                                             | 14 |

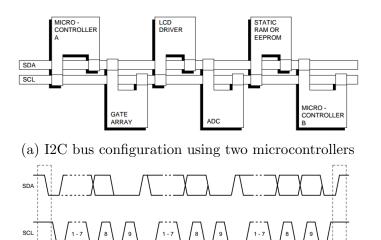

| 2.3.  | I2C Bus Configuration and Communication Frame[29]                                                                                  | 14 |

| 2.4.  | Inverted logic of a CAN bus[12]                                                                                                    | 15 |

| 2.5.  | $CAN frames[12] \dots \dots$ | 16 |

| 2.6.  | Relation between Baud rate and CAN bus length[34]                                                                                  | 16 |

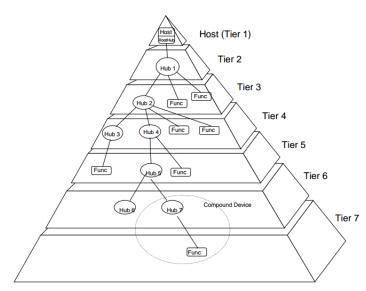

| 2.7.  | USB bus tiered-star topology $[e][9]$                                                                                              | 17 |

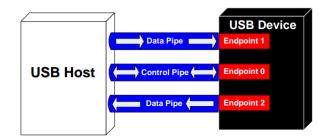

| 2.8.  | USB Pipe Model[28]                                                                                                                 | 18 |

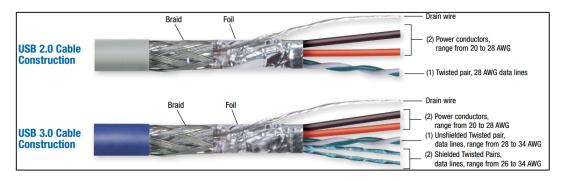

| 2.9.  | USB Cable[26]                                                                                                                      | 18 |

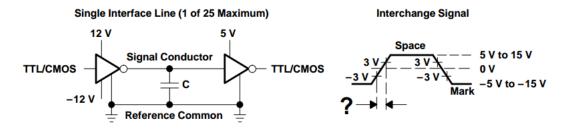

|       | $TIA/EIA-232-F Electrical Specification[20] \dots \dots \dots \dots \dots \dots \dots \dots$                                       | 19 |

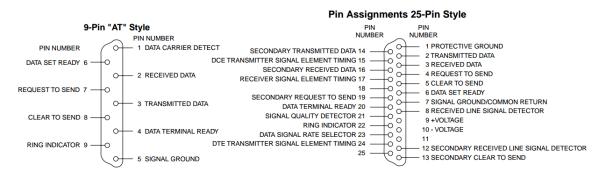

| 2.11. | $RS-232 \text{ connectors}[31]  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                   | 20 |

|       | RS-422 Balanced Voltage Circuit[22]                                                                                                | 20 |

|       | Comparison of cable length and data $rate[23]$                                                                                     | 21 |

| 2.14. | RS-485 Balance Voltage Circuit[22]                                                                                                 | 21 |

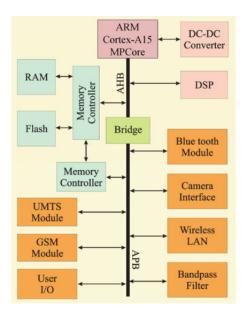

| 2.15. | AMBA-based mobile phone $SoC[35]$                                                                                                  | 23 |

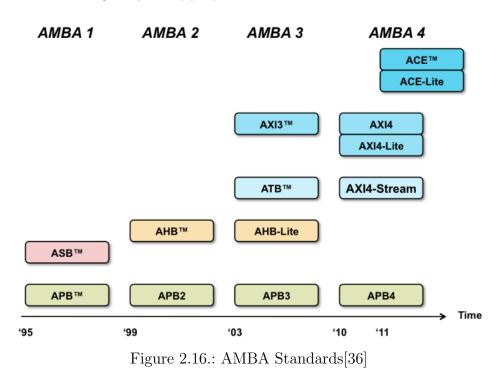

| 2.16. | AMBA Standards[36]                                                                                                                 | 24 |

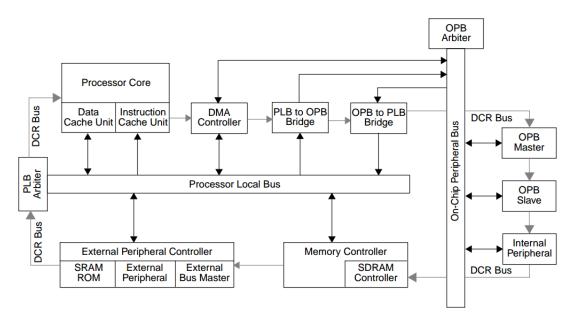

| 2.17. | CoreConnect Bus Architecture[19]                                                                                                   | 25 |

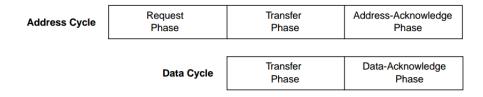

| 2.18. | PLB Address and Data Cycle [18]                                                                                                    | 26 |

| 2.19  | Various Wishbone Interconnection Scheme[27]                                                                                        | 27 |

| 2.20. | Avalon bus based system[5]                                                                                                         | 28 |

|       | System depicting Wrapped bus and OCP instances[27]                                                                                 | 29 |

|       | High-Level Block Diagram[51]                                                                                                       | 30 |

|       | Top View of ZYNQ Architecture[52]                                                                                                  | 31 |

|       | System-Level Address map[43]                                                                                                       | 32 |

|       | Read and Write Channels [42]                                                                                                       | 33 |

| 2.26. | Two-way VALID/READY Handshake[7]                                                                                                   | 34 |

|       | AXI4-Stream Transfer via Single Channel[41]                                                                                        | 35 |

|       | Overview of the design $[37]$                                                                                                      | 36 |

|       | View of Pre-processing Circuit used in the design[38]                                                                              | 37 |

| 2.20. | ten er rie breesend en en abed in ene deplen[oe]                                                                                   | 01 |

| 3.1.  | ZYBO ZYNQ-7000 Development Board[13]                                                                                               | 41 |

| 3.2.  | ZYBO clocking scheme[13]                                                                                                           | 42 |

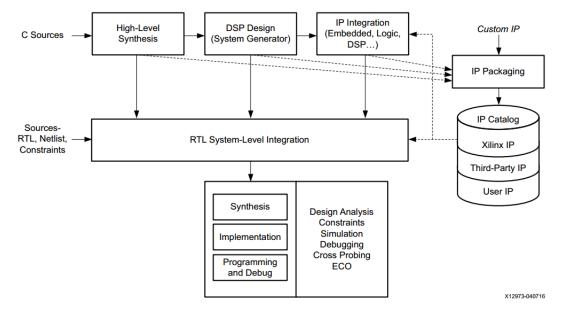

| 3.3.  | High-Level Design Flow in Vivado[46]                                                                                               | 43 |

### LIST OF FIGURES

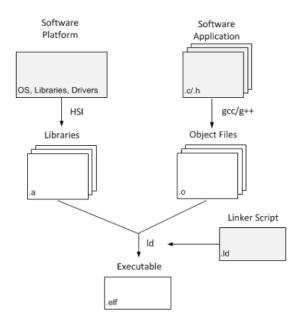

| 3.4.                                                                                                         | Software Workflow in SDK[40]                                                                                                                                                                                                            | 44                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

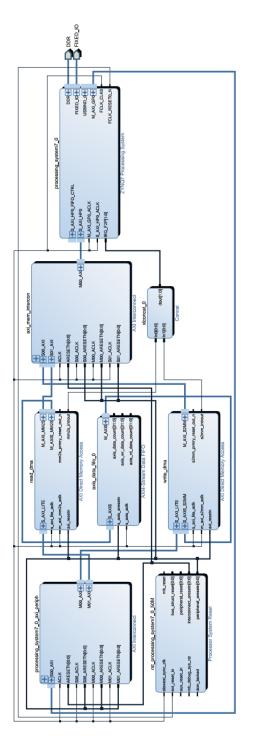

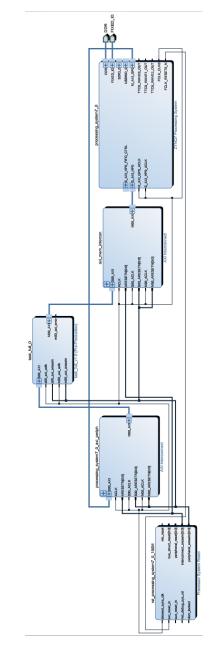

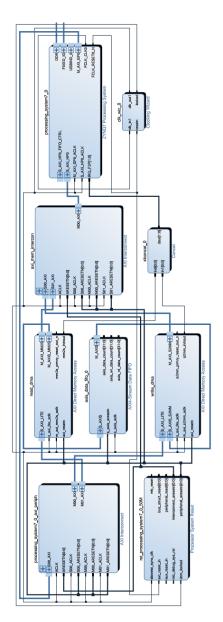

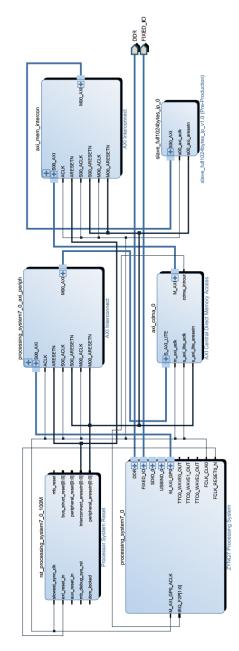

| $\begin{array}{c} 4.11.\\ 4.12.\\ 4.13.\\ 4.14.\\ 4.15.\\ 4.16.\\ 4.17.\\ 4.18.\\ 4.19.\\ 4.20. \end{array}$ | Block Diagram of Hardware Design                                                                                                                                                                                                        | $\begin{array}{c} 45\\ 46\\ 47\\ 48\\ 49\\ 50\\ 52\\ 53\\ 53\\ 54\\ 54\\ 55\\ 55\\ 56\\ 57\\ 57\\ 58\\ 59\\ 60\\ 66\end{array}$ |

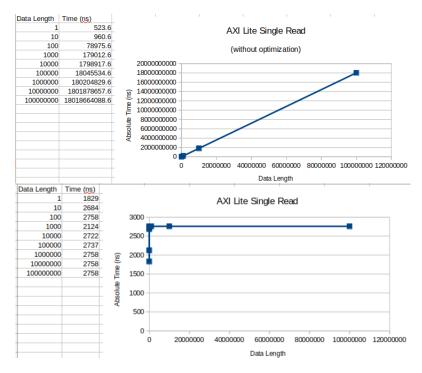

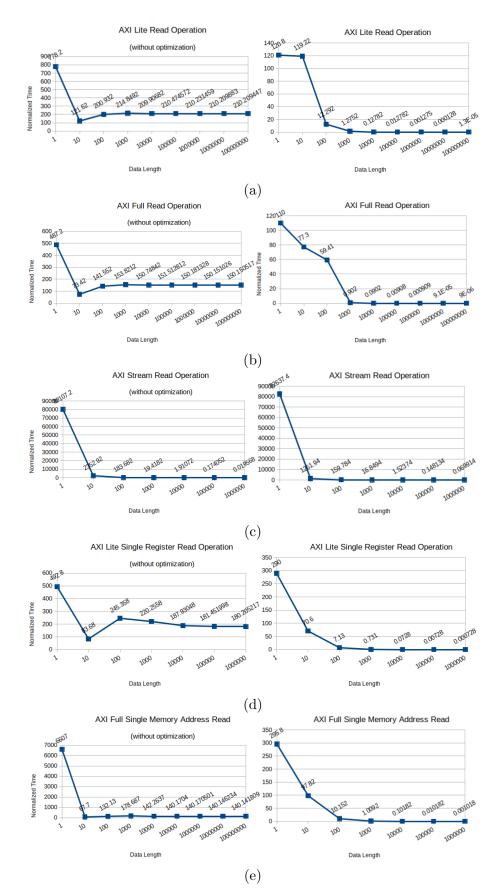

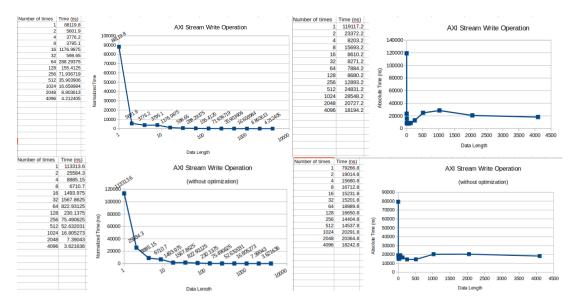

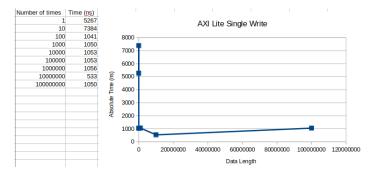

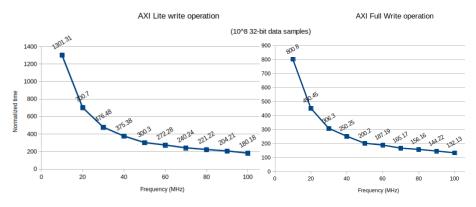

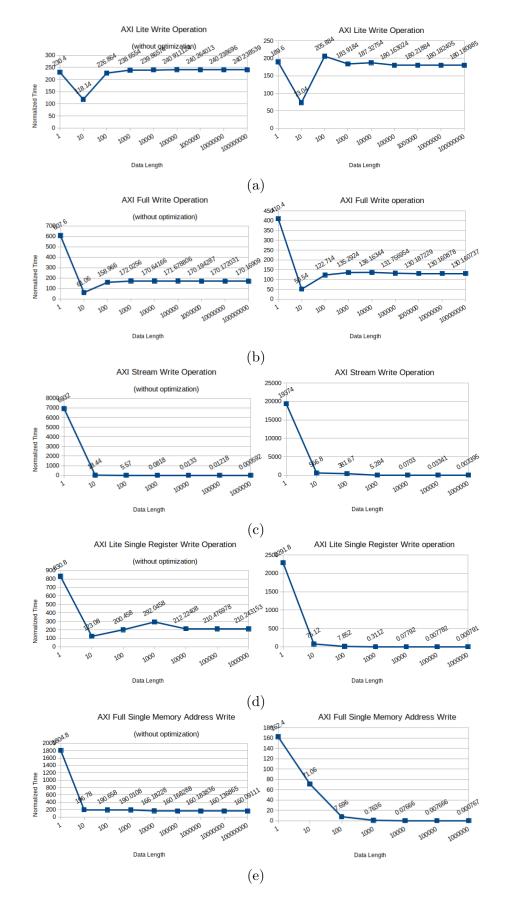

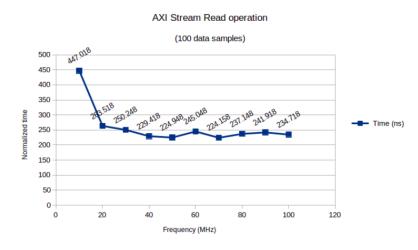

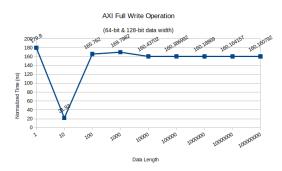

| $5.1. \\ 5.2. \\ 5.3. \\ 5.4. \\ 5.5. \\ 5.6.$                                                               | Optimization Effect on the ResultResults for Read OperationsComparison of Normalized and Absolute Time for AXI4 StreamAbsolute Execution Time for AXI4-Lite Write OperationPerformance based on PL FrequencyResults for Write Operation | 68<br>69<br>71<br>72<br>72<br>73                                                                                                |

|                                                                                                              | AXI4-Stream Performance Relative to PL Frequency                                                                                                                                                                                        | 77<br>78                                                                                                                        |

|                                                                                                              | AXI4-Full High-Performance Based Design                                                                                                                                                                                                 | 84                                                                                                                              |

| C.1.                                                                                                         | Clocking Wizard design for AXI4-Stream                                                                                                                                                                                                  | 85                                                                                                                              |

| D.1.                                                                                                         | AXI CDMA Based Hardware Design                                                                                                                                                                                                          | 86                                                                                                                              |

# List of Tables

| 2.1.         | AXI4 Feature Availability and IP Replacement[42] | 36       |

|--------------|--------------------------------------------------|----------|

| 3.1.         | Features of SoC Bus Standards                    | 39       |

| 4.2.<br>4.3. | Addresses of ADC Channel Registers[49]           | 61<br>62 |

|              | Configuration for Results                        |          |

# List of Abbreviations

| AHB | Advanced | High-Performance | Bus |

|-----|----------|------------------|-----|

| AHB | Advanced | High-Performance | Bus |

- **AMBA** Advanced Microcontroller Bus Architecture

- **APU** Application Processor Unit

- **APB** Advanced Peripheral Bus

**ARM** Advanced RISC Machine

- **ASB** Advanced System Bus

- ASIC Application-Specific Integrated Circuit

- **AXI** Advanced eXtensible Interface

- **CAN** Controller Area Network

- **DMA** Dynamic Memory Access

- **FPU** Floating Point Unit

- **I2C** Inter-Integrated Circuit

- **IP** Intellectual Property

- **MMU** Memory Management Unit

- NoC Network On Chip

- **OCM** On-Chip Memory

- **OP-AMP** Operational Amplifier

- **PLL** Phase Locked Loop

- **PL** Programmable Logic

- **PS** Processing System

- **ROM** Read Only Memory

- **SDK** Software Development Kit

- **SDIO** Secure Digital Input/Output

- SoC System on Chip

- **SPI** Serial Peripheral Interface

- **UART** Universal Asynchronous Receiver Transmitter

- **USB** Universal Serial Bus

# Acknowledgments

I would like to offer my gratitude towards Chair of Computer Engineering and people involved in the chair.

First and foremost, I am thankful to Prof. Dr. W. Hardt to provide me an opportunity to do master thesis in the Professorship of Computer Engineering.

I, sincerely, like to thank my supervisor, Dipl. Inf. René Schmidt, for supporting me throughout the journey. I am grateful to have him as my supervisor since I always felt motivated and happy while working under him.

# 1. Introduction

### 1.1. Motivation

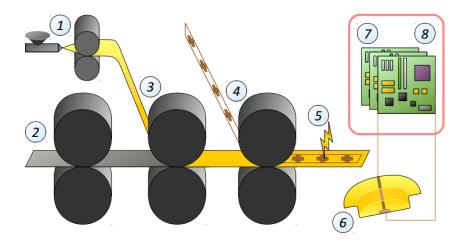

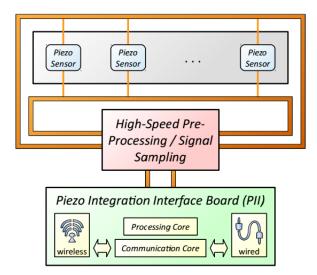

In context of MERGE technologies, "Technology Fusion for Lightweight Structures" aims to develop a novel touch-based user interface for a piezo metal composite. Overall concept of the project is illustrated in Figure 1.1.

Piezo foil is glued to a metal sheet with copper electrodes on it (step 3 and 4). These electrodes are polarized to amplify the resulting voltage from piezo film[37]. Afterwards, composite can be formed to give any required shape. This thesis is concerned with steps 7 and 8, highlighted in a rectangular box, that are responsible for detection and localization of impact on the composite.

Figure 1.1.: Processing chain of Piezo Metal Composite[37]

It requires embedded signal processing to process piezo signals and extract appropriate features for classifier to accurately localize the point of impact. Since composite is allowed to take multiple form, it is viable to use a Machine Learning (ML) interface. Classifier's accuracy depends on the type and amount of training data used for learning rather than geometry of the composite. Hence, it will eliminate dependency of the results on mechanical parameters such as changes in propagation of mechanical waves due to changes in physical shape of the composite[37].

Signal processing has been implemented on FPGA. However, it is not feasible to run ML part on FPGA, therefore, it demands a hardware/software co-design approach to run machine learning algorithm on the processor.

#### 1. Introduction

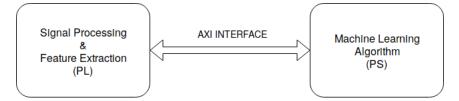

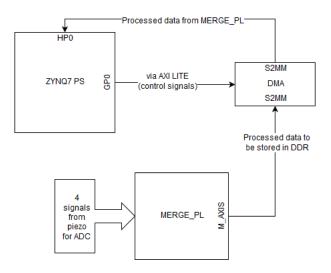

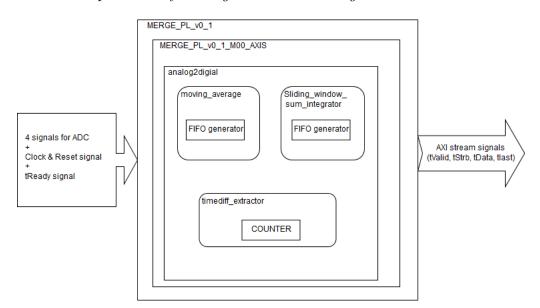

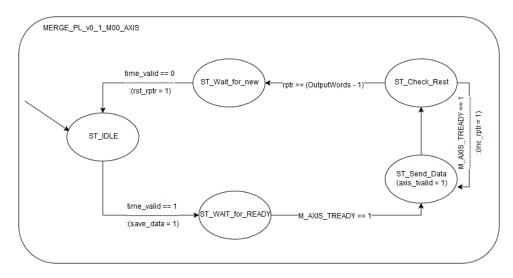

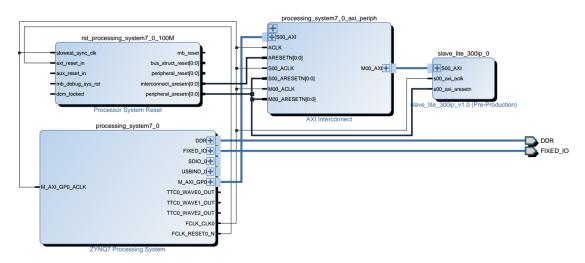

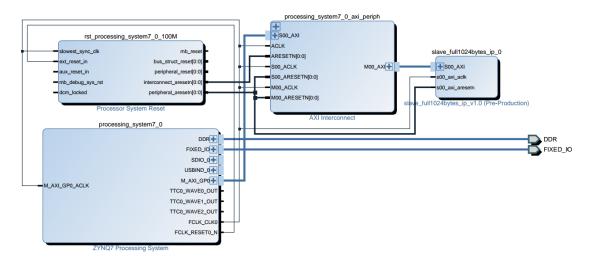

Current design as depicted in Figure 1.2 uses Digilent ZYBO (ZYnq BOard) board because of its inclusion of ARM-based processor with an FPGA on a Zynq Systemon-Chip (SoC). Moreover, for development purpose, for a low-cost it offers flexible design.

Figure 1.2.: Block Diagram of the current design

As seen from Figure 1.2, Zynq SoC comprise AXI Interface to link Programmable Logic (PL) and Processing System (PS). AXI Interface provides several configurations that can have impact on the overall speed of the design. In order to provide a optimized hardware software partitioning solution, the communication costs have a major influence on the system performance. Therefore, an analysis of the AXI-Interfaces representing the communication costs is mandatory.

### 1.2. Structure of the Thesis

Thesis is structured as follows:

**Chapter 2**, State of the Art, lists some of the communication protocols that are used in FPGA design. Since work in the thesis is done on SoC, therefore, various SoC communication standards are discussed. Among these, Zynq architecture is explained in detail because of its use in the implementation. Lastly, for the evaluation of AXI Interfaces, current hardware and software designs are mentioned.

**Chapter 3**, Concept, compares various SoC communication standards to provide an overview of features supported by such standards. In addition, approach taken to evaluate AXI-Interfaces and platform used for such purpose are discussed.

**Chapter 4**, Implementation, details FPGA implementation, provided in the thesis, for signal processing and feature extraction. It also explains implemented design, both hardware and software, for evaluation.

**Chapter 5**, Results and Discussions, highlights the performance of AXI Interfaces and examines their results to find the best fitting interface for given FPGA implementation and machine learning interface.

**Chapter 6**, Conclusion and Future Work, summarizes the thesis through its implemented design and evaluation results. Based on thesis's conclusion, possible ideas that can be implemented to improve the design are mentioned.

# 2. State of the Art

### 2.1. Possible Communication Alternatives for FPGA

There have been several communication protocols where are used in FPGA designs such as Universal Serial Bus (USB), I2C (Inter-Integrated Circuit), Serial Peripheral Interface (SPI), etc. In this chapter, some of the widely used communication protocols are discussed. These include: SPI, I2C, CAN, USB, and TIA/EIA standards. These protocols can be implemented within FPGA design as an IP Core. Some can be used to communicate with FPGA, for example, SPI.

These communication protocols uses serial communication. Through the discussion, it will be easier to have an outlook of the requirements for each protocols and complexity involved in using it. Moreover, it will provide an overview about features of various protocols.

Some of the well known standards which are used for the communication between FPGA and microprocessor are listed below:

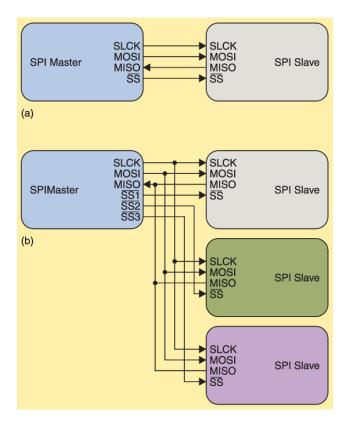

#### 2.1.1. Serial Peripheral Interface

Serial Peripheral Interface (SPI), developed by Motorola, is a synchronous serial bus that provides full duplex communication between the master and one or more slaves. It is well suited for communication between integrated circuits for low/medium data transfer speed with on-board peripherals. SPI bus consists of four wires as depicted in Figure 2.1. A separate Slave Select (SS) signal is needed for each slave which adds to extra wiring.

Functions of these four signals is as follows. Master drives the clock signal (SCLK) for the slaves. To send data from master to slave, MOSI (Master Output Slave Input) pin is used. For sending data from slave to master, slave uses MISO (Master Input Slave Output) pin. Master selects appropriate slave with the help of SS (Slave Select) pin and then sends/receives the data.

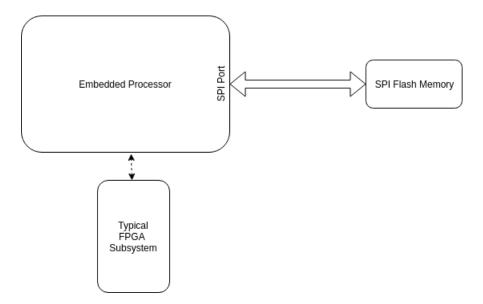

When used in full duplex mode, SPI Interface can achieve data rates of upto 1 Mbps. Therefore, it is well suited for low speed communications, for example, for configuring FPGAs where a microprocessor reads a bitstream file via SPI interface and sends it to FPGA over slave serial interface.

Figure 2.1.: SPI Bus Topologies[3]

#### 2.1.2. Inter-Integrated Circuit

Phillips introduced Inter-Integrated Circuit (I2C) protocol in 1982 for serial communication between ICs placed on a same board. I2C protocol, similar to UART (Universal Asynchronous Receiver Transmitter), supports two lines for communication, Serial Clock (SCL) and Serial Data (SDA), which handles multiple masters and slaves as depicted in Figure 2.3a.

In I2C bus configuration, SCL and SDL lines are connected to positive supply voltage using a pull-up resistor. Hence, a device on a I2C bus uses an open-drain approach, i.e., it can only drive a logic 0 (LOW) on a bus.

Master and slave communicate via 7-bit/10-bit address. Master sends address to slaves in a message frame coupled with control information as shown in Figure 2.3b. Communication starts and ends with special bits supported by I2C protocol. Each address is followed by a read/write information and an acknowledgment from the receiver.

I2C bus comes in various speeds as needed for the application. A unidirectionl bus supports Ultra Fast-mode with a bit rate up to 5 Mbps whereas a bidirectional bus supports:[29]

- Standard-mode (0 100 kbit/s)

- Fast-mode (0 400 kbit/s)

2. State of the Art

Figure 2.2.: Typical Embedded Microprocessor System with an FPGA[2]

- Fast-mode Plus (0 1 Mbit/s)

- High-speed mode (0 3.4 Mbit/s)

I2C protocol is mainly used for low speed communication and control applications such as in EEPROM (Electrically-Erasable Programmable Read-Only Memory), ADC (Analog-to-Digital Converter), microcontroller, LCD (Liquid Crystal Display) controllers [25]. Moreover, the bus is used in various control architectures such as System Management Bus (SMBus) and Power Management Bus (PMBus)[29].

(b) Communication frame in I2C data transfer

ACK

DATA

АСК

STOP

DATA

R/W ACK

ADDRESS

START

Figure 2.3.: I2C Bus Configuration and Communication Frame<sup>[29]</sup>

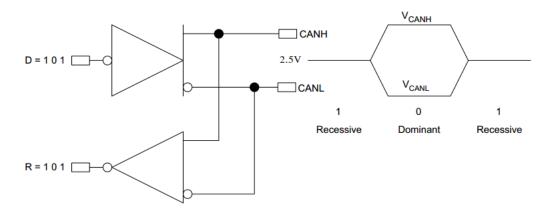

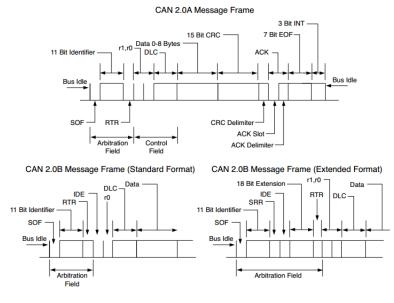

#### 2.1.3. Controller Area Network

In 1986 Robert Bosch GmBH, at the Society of Automotive Engineers (SAE) conference, publicly released a serial communication bus, Controller Area Network (CAN)[10]. Reason behind the development of serial network protocol was to have an efficient real-time based communication between various electronic devices in automotive applications.

CAN architecture replaced complex point-to-point wiring harness between various Electronic Control Units (ECUs) by a two-wire bus. These two wires, CANH and CANL, are configured in a twisted-pair cable which cancels out electromagnetic interference. CAN bus provides two logic states: a recessive state and a dominant state as illustrated in Figure 2.4. A dominant in a bus denotes a differential voltage between CANH and CANL of 2V (logical HIGH) whereas a recessive signifies a zero differential voltage.

Figure 2.4.: Inverted logic of a CAN bus[12]

CAN devices (or nodes) access CAN bus through carrier-sense, multiple-access protocol with collision detection and arbitration on message priority [12]. Prior to transmission of data, availability of bus is checked by a node. If multiple nodes transmit data at the same time, then bit-wise arbitration scheme is employed to resolve the conflict. Arbitration is performed on the value of message identifier stored in the arbitration field (Figure 2.5). Priority of a message is inversely proportional to the value of an identifier. So, among multiple frames, a node frame of lowest identifier wins the arbitration and, therefore, is transmitted on the bus. As depicted in Figure 2.5, CAN specification provides two different identifiers, 11-bit (standard) and 29-bit (extended), leading to an increase in the maximum number of nodes allowed on the bus. Message transfer between CAN devices is controlled by four frames[8]: a data frame, a remote frame, an error frame, and an overload frame. A data frame contains 0-8 bytes of data on the bus. Data can be requested from a specific node through a remote frame which contains no data. An error frame is transmitted by a node in case of an error in the bus. Overload frames provides additional delay between data or remote frames.

#### 2. State of the Art

Figure 2.5.: CAN frames [12]

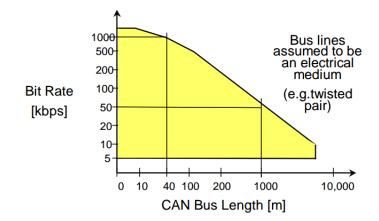

fig:canspeed it is seen that CAN bus allows a maximum speed of 1 M bits/s for a bus length of 40 m. Based on rate of transmission, CAN is divided into three types[11]

- High Speed CAN (Up to 1 M bits/s)

- Low Speed/Fault-tolerant CAN (Up to 125 K bits/s)

- Single Wire (Up to 83.3 K bits/s)

Figure 2.6.: Relation between Baud rate and CAN bus length[34]

Because of its low cost, robust noise immunity and real-time capabilities, CAN protocol is utilized in variety of applications apart from automotive. CAN finds its usage in textile machinery, medical devices, and as production line equipment[11].

#### 2.1.4. Universal Serial Bus

In 1990s, growing use of personal computer (PC) led to development of various peripherals such as mouse, keyboard, modem, printer etc. Separate interfaces such as serial and parallel port were used for the attachment of such peripherals to PC. From user's point of view, there was a need to replace different connectors by a single interface that can allow multiple devices to communicate with each other. Therefore, in 1994, Universal Serial Bus (USB) standard was developed through a joint effort of multiple industries: Compaq, IBM, DEC, Microsoft, Nortal, and NEC[28].

USB architecture consists of a host computer connected to wide range of peripherals through a cable bus. Attached peripherals share the bus bandwidth among them and are allowed to attach or detach while the bus is in operation[9]. These peripherals are connected to USB host in a tiered-star topology as depicted in Figure 2.7. USB protocol supports a maximum of 127 devices that can be attached to a single host controller. USB is a polled bus, that is, only the host controller can initiate a transfer in the bus.

Figure 2.7.: USB bus tiered-star topology[e][9]

Communication between host controller and USB device is done via pipes (Figure 2.8). An Endpoint in a USB device is used as a storage for data, which can be addressable by the host controller. From Figure 2.7, data pipes, as the name suggests, are unidirectional and carry data. Each USB device have a bidirectional control pipe to configure device or provide status and control information.

Each transaction in the bus is initiated by the host controller through the token packet. This packet contains information about the type and direction of transaction, the USB device address, and endpoint number[9]. After the token packet, host can send or receive data packets. USB device transmits a handshake packet to denote a successful transfer.

#### 2. State of the Art

Figure 2.8.: USB Pipe Model[28]

USB Specification provides four data transfer types[9]

- Control Transfers: Used for configuration of the device.

- Bulk Data Transfers: Used to transfer of large amount of data without guarantee on transfer speed or latency.

- Interrupt Data Transfers: Used to transfer small amount of data though in timely manner.

- Isochronous Data Transfers: Used for guaranteed data delivery rate through assurance of set amount of bus bandwidth and latency.

To carry out data transfers, USB cable uses differential signaling (Figure 2.9. The clock is encoded with the differential data and uses Non-Return-To-Zero Inverted (NRZI) scheme[9]. Bit stuffing is employed to maintain synchronization between sender and receiver, in cases where there are no transitions in the data.

Figure 2.9.: USB Cable[26]

From Figure 2.9 we see that there a two variants of cables used for USB bus communication. USB 2.0 supports three speeds: High-speed (480 Mbits/s), Full-speed (12 Mbits/s), and Low-speed (1.5 Mbits/s). USB 3.0 is back compatible with USB 2.0 devices and, in addition, provides a Superspeed bus that supports transfer rate of up to 5.0 Gbits/s[2]. A successor to 3.0, USB 3.1 scaled the Superspeed to 10.0 Gbits/s[2].

Availability of such transfer speeds allow USB to be employed in different applications than just being a way to connect peripherals to PCs. It enables faster performance in downloading data or video[26]. USB, as a protocol, is used in nontraditional application such as industrial automation[2]. Moreover, USB is used a power source for charging mobile devices.

#### 2.1.5. TIA/EIA Standards

Telecommunication Industry Association/Electronic Industries Association (TIA/EIA) defined physical layer standards intended for serial communication. These standards provide electrical and mechanical specification that can be utilized by a serial protocol.

For example, UART (Universal Asynchronous Receiver Transmitter) hardware is used in conjunction with these standards to facilitate serial communication. Another example is Modbus serial protocol used with RS-232 or RS-485 interfaces.

These standards are also referred with a prefix "RS" (Recommended Standard) such as RS-232, RS-422, and RS-485.

#### **RS-232 (TIA/EIA-232)**

RS-232 is a single-ended, full-duplex, communication interface between a driver and a receiver in the point-to-point configuration. This interface was introduced by EIA in 1962 to standardize communication between Data Transmission Equipment (DTE) such as a PC and Data Communication Equipment (DCE) such as a modem[20].

For communication purpose, RS-232 standard also defined a standard connector, named DB-25 (Figure 2.11). However, when IBM PC AT was released in 1984, it featured a 9-pin D type connector which later became common in use as an interface between data acquisition devices and computer systems.

Figure 2.10.: TIA/EIA-232-F Electrical Specification[20]

Voltage levels used by RS-232 are specified in Figure 2.10. Voltage levels between  $\pm 3V$  are undefined such that effect of noise at receiver's end is reduced. However, use of single-ended configuration is prone to common-mode noise. A shift in ground level at receiver's end can lead to unbalanced situation. Use of a common ground signal limits the maximum data throughput.

Figure 2.11.: RS-232 connectors[31]

RS-232 standard defines a maximum data rate of 20 kbits/s for a maximum cable length of about 15 to 20 meters[20]. It states that the cable is allowed to have a maximum capacitance of 2500 pF.

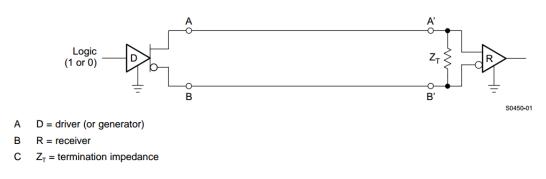

#### **RS-422 (TIA/EIA-422)**

RS-422 was introduced to overcome noise issue of RS-232 because of single-ended interface[23]. RS-422 standard provides electrical specification for employment of balanced data transmission over long distances.

It is a simplex multidrop standard, that is, on a shared bus only single driver and multiple receivers (up to 10) can exist. Similar to RS-232, it can also be used in point-to-point configuration.

Figure 2.12.: RS-422 Balanced Voltage Circuit[22]

An overview of the interface circuit is depicted in Figure 2.12. As per the specification, termination impedance is required to reduce reflection caused by mismatch of characteristic impedance of the line.

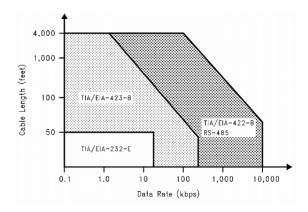

RS-422 allows a maximum cable length of 1200 meter, however, it would not result in maximum data rate as depicted in Figure 2.13. Voltage range for RS-422compliant driver lies in the range of  $\pm 6V$  whereas for receiver, it is  $\pm 10V$  with a threshold level of 200 mV[22].

Figure 2.13.: Comparison of cable length and data rate<sup>[23]</sup>

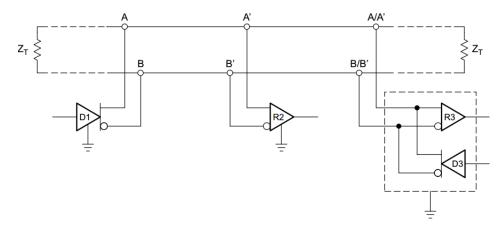

### **RS-485 (TIA/EIA-485)**

In comparison to RS-232 and RS-422, RS-485 is most widely used standard in industry owing to its balanced digital transmission line with an interconnection of multiple transmitters and receivers. RS-485 uses a half-duplex communication scheme in multi-point configuration as seen inFigure 2.14. It can transmit data over distances of several kilometers with fewer noise emission.

Figure 2.14.: RS-485 Balance Voltage Circuit[22]

RS-485 specification defines only electrical layer and its electrical specification is compliant with RS-422 drivers and receivers[22]. RS-485 compliant drivers and receivers voltage on the lines range from -7 V to 12 V. In contrast to RS-422, it requires termination impedance at both ends of the cable.

As per the specification, maximum cable length can be 1200 meter and a high signaling rate of up to 50 Mbits/s is achievable[21]. Variation of data rate with respect to length of the cable is depicted in Figure 2.13.

Due to its low noise coupling and various other advantages, various standards committees incorporated RS-485 as the physical layer specification for their com-

munication standard such as the Profibus standard and Small Computer Systems Interface (SCSI)[21].

## 2.2. Outline of SoC Bus Standards

Various computer components such as processor cores, on-chip memory, external memory interface, Digital Signal Processor (DSP), input/output devices, etc., are placed on a single chip called System-on-Chip (SoC). Compared to motherboards such arrangement leads to reduced board space and less power consumption. Owing to this they mainly find their use in mobile computing devices.

In the thesis, we will look into SoC that integrates FPGA (reconfigurable SoC) since implementation is performed on such system. In contract to Application-Specific Integrated Circuit (ASIC), rSoC provides more flexibility with short turn around time for testing the hardware design and is generally cost-effective. However, ASICs are aimed to comply with a particular purpose, hence, they acquire less space than FPGAs and have lesser power requirements.

IP (Intellectual Property) cores for SoC are designed with different interfaces and communication protocols. SoC needs minimal glue logic to integrate them in a chip and so it resulted in development of on-chip bus standards[27]. There have been several interconnect topology to interface various IPs in SoC such as point-to-point, bus system, crossbar switch, Network-on-Chip (NoC), etc. Among these, Network-on-Chip provides better design scalability and uses wires efficiently[16]. It makes use of data packets for communication between devices similar to TCP/IP (Transport Control Protocol/Internet Protocol) model.

To increase the overall speed of SoC designs, some emerging on-chip interconnect technologies such as optical interconnects, Radio Frequency (RF) based interconnect, and CNT (Carbon Nanotube) interconnect, are in experimental phase[33].

In this section, we will look into various on-chip bus standards which are flexible and robust enough to integrate numerous functional units on a single chip. Bus architecture is widely accepted integration technique for inter-module communication in SoC. It is based on traditional address and data buses used in computers to carry information across the system.

#### 2.2.1. AMBA

A SoC interconnect standard named Advanced Microcontroller Bus Architecture (AMBA) was introduced by ARM in 1996 to facilitate communication between various IPs (Intellectual Property)[6]. It employs two layer hierarchical bus topology to interface SoC components based on their performance requirements.

High performance bus connects processor cores, memories, and other highbandwidth components. Low performance bus provides interface to low bandwidth peripherals such as Ethernet, USB, UART, etc. It is a simple addressing bus with latched address and control signals for low-speed peripherals. These buses are adjoined by a bridge as illustrated in Figure 2.15.

ARM AMBA system consists of: masters, slaves, bus arbiter, and central decoder. Multiple masters can connect to high-bandwidth bus whereas slave peripherals communicate with the system using low-bandwidth bus. Bus arbiter implements arbitration scheme to allow only one master to initiate transfer at the same time. Decoder provides select signals for peripherals based on address provided by the master.

Figure 2.15.: AMBA-based mobile phone SoC[35]

The communications between IPs in an AMBA SoC is done in the form of transactions. A transaction, initiated by master, consists of securing the bus, commencing and completing read/write operation[35].

AMBA Specification version 1.0 released two buses: Advanced System Bus (ASB) and Advanced Peripheral Bus (APB). Advanced System Bus is used as the main system bus for high-bandwidth components such as processor, memory, DMA controller, and APB Bridge. APB Bridge acts as a cross-over between ASB and APB and handles the bus handshake[6]. It supports multiple data bus widths: 8, 16, and 32 bits. APB bus provides a simple addressing with latched address and control signals. It is suitable for connecting peripherals such as UART, USB, Ethernet, General purpose input/output ports. It supports data width of 8, 16, 32 bits.

Advanced High-Performance Bus (AHB) was included in second version of AMBA. Similar to ASB, it provides pipelined operation but also supports burst transfer and split transactions. Multiple data bus widths allowed in AHB are 32/64/128 bits. It incorporates access protection scheme to distinguish between privileged and nonprivileged access modes.

In third version (AMBA 3), AMBA added Advanced eXtensible Interface (AXI3)

which was later updated in fourth version to AXI4. AXI provides a point-to-point interconnect between master and slave which is advantageous over bus sharing. It enables higher bandwidth and lower latency in design. AMBA 3 also introduced Advanced Trace Bus (ATB) and AHB-Lite. ATB is part of CoreSight on-chip debug which is used for verification of an IP. AHB-Lite is a simplified version of AHB that allows only one master.

In addition to AXI3, AXI4 introduced two additional interfaces: AXI4-Lite and AXI4-Stream. AXI4-Lite is used for low-throughput memory mapped interface and provides powerful interface than APB. AXI4-Stream supports high-speed streaming of data[42]. AXI4 is discussed in greater detail in Section 2.3.

AMBA Specification version 4 (AMBA 4) released Advanced Coherency Extension (ACE) which is an extension to AXI4. It provides hardware management of cache memory across multiple cores. This removes the need of software to maintain coherency between caches, thereby, saving processor cycles and bus usage. A simplified version of ACE, ACE-Lite is introduced to provide one-way coherency for components that does not have their own cache memory like DMA (Direct Memory Access). Components with cache memory can also use ACE-Lite protocol when such cache is to be managed by an appropriate software.

In 2013, AMBA 5 released Coherent Hub Interface (CHI) which is a complete redesign of ACE to incorporate increasing number of coherent clusters. Instead of using ACE Interconnect, it introduced a packed based layered architecture.

Since its inception, AMBA has been the de facto standard for creating SoCs. It is used by industries such as NVidia, Qualcomm, Actel, etc[35].

#### 2.2.2. CoreConnect

IBM released on-chip bus standard named CoreConnect for interconnecting cores and enabling reuse of logical units in SoC through hierarchical bus system. It is composed of three buses for interconnecting cores, peripherals, and custom logic:

- Processor Local Bus (PLB)

- On-Chip Peripheral Bus (OPB)

- Data Control Register Bus (DCR)

Figure 2.17 illustrates the use of these buses in the architecture. PLB provides high-bandwidth and low latency with support for 16-, 32-, and 64-bits data transfers, extensible to 256-bits. PLB is intended to connect components that needs high throughput such as processor cores, DMA controllers, memories, etc. It is fully synchronous central arbitrated bus that supports up to 16 masters and unrestricted number of slaves. Both master and slave that are attached to PLB have separate bus for address, read data and write data. Hence, concurrent read and write transfers maximizes the bus utilization. Moreover, it features burst transfers, split transaction, and address pipelining which enhances bus throughput.

Figure 2.17.: CoreConnect Bus Architecture[19]

OPB reduces capacitive loading on PLB by providing independent support to low speed peripherals such as serial/parallel ports, USB, General purpose input/output ports, etc[c]. It uses separate 32-bit data and address bus. OPB features fully synchronous operation, burst transfers, single-cycle data transfers, multiple masters, and dynamic bus sizing. OPS supports multiple master devices through implementation of distributed multiplexer for both the address and data bus[19].

#### 2. State of the Art

From Figure 2.17 it can be seen that communication between PLB and OPB is done through bridges. PLB masters use PLB to OPB bridge to write data to slave peripherals or use OPB to PLB bridge to read data from master peripherals.

DCR is a low performance, fully synchronous bus to provide status and configuration data across the system. It consists of 10-bit address bus and 32-bit data bus. Read or write transfer on the bus need minimum two cycles. Similar to OPB, it off-loads PLB from lower performance transfers by providing a daisy-chained connection between processor core master and other SoC devices acting as slaves. It makes use of ring topology which is implemented as distributed multiplexer across the chip. Such connection of SoC devices minimizes silicon usage[1].

Bus transaction is started by PLB which consists of address and data cycles as shown in Figure 2.18. Master requests for the bus by driving address and transfer qualifier signals. When PLB Arbiter grants bus to the master, these signals are passed to the requested slave in the transfer phase. Address cycle terminates when slave latches these signals in the address acknowledge phase.

Figure 2.18.: PLB Address and Data Cycle[18]

Similarly master writes or reads data to/from slave in data cycle. Each data beat in data cycle consists: transfer phase where master drives write data or read data bus and data acknowledge phase which denotes end of the data cycle for the final beat of line transfer[1]. Maximum throughput occurs when data transfer and data acknowledge phases are concurrent.

CoreConnect finds its use in PowerPC400 family, for example, PowerPC 440 incorporates CoreConnect bus standard to interface components inside a PowerPC.

#### 2.2.3. Wishbone

Silicore Corporation released an on-chip interconnect architecture named Wishbone bus which is supported by OpenCores, an organization that provides open source IP cores. Main objective for development of Wishbone bus was to have a common interface between IP Cores so as to enhance portability and reliability of the system[32].

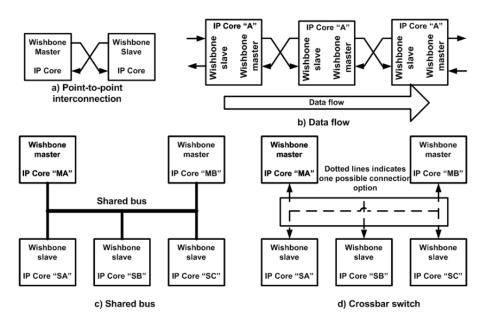

Wishbone is a general purpose interface which provides set of signals and bus cycles for a single level bus. To connect IP Cores to bus, it defines two types of interfaces, namely, Master and Slave. IP cores that acts as master can initiate bus cycles whereas the ones which receive bus cycles are classified as Slave interfaces. Major feature of Wishbone is the inclusion of possible interconnection architecture between Master and Slave interfaces as illustrated in Figure 2.19. These include: Point-to-Point, Data flow, Shared bus, and Crossbar switch.

Figure 2.19.: Various Wishbone Interconnection Scheme [27]

Point-to-Point is the simplest of all interconnection scheme and falls short for SoC design where multiple masters have to be interfaced with multiple slaves.

Data flow architecture exhibits parallelism where each IP Core has both Master and Slave interface to provide the movement of data from core to core. This results in pipelining similar to the use Fetch-Execute-Write functional blocks in computer systems. Dataflow topology can find its in DSP algorithms where linear systolic array architecture is implemented[32].

Shared bus architecture interconnects multiple master and slaves through a shared bus. It needs bus arbiter and decoder logic to allow only one master to use the bus at a time. Compared to other architectures, it uses fewer logic gates and routing resources to interconnect SoC components which makes it relatively compact[32].

Crossbar switch is valuable when multi core SoC is used since it can speed up data transfer rate by utilizing multiple cores concurrently. Thereby, compared to shared bus architecture, it is faster but incorporates more interconnection logic and routing resources[32]. Moreover, use of a cross-bar interconnect system results in limited scalibility because of the use of centralized arbiter to control the bus[32].

Each Wishbone interface have set of signals which supports three types of bus cycles[32]

- Single Read/Write: Only single data transfer at a time.

- Block Read/Write: Multiple single read/write cycles.

• Read-Modify-Write: Allows multiple masters to share common slave by using semaphore bit.

Wishbone supports multiple data widths: 8, 16, 32, or 64 bits and address bus width from 1 to 64 bits.

#### 2.2.4. Avalon

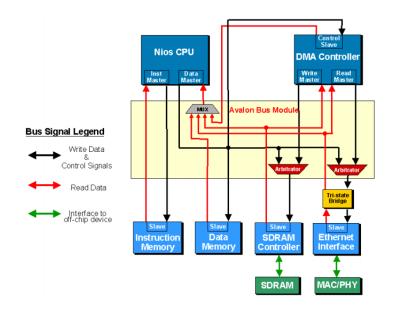

Altera Corporation, acquired by Intel, released Avalon bus architecture for Systemon-a-programmable-chip (SPOC). Avalon makes use of multiplexers to drive the signals to appropriate peripheral. Hence, output of peripherals switch between HIGH and LOW without existing in a high impedance state. Signals and timings are defined in the architecture to allow master and slave components to communicate with each other[5].

From Figure 2.20 we see that Avalon features data-path multiplexing and multiple master. Masters and slaves interact with each other without the intervention of bus. However, arbitration is needed when multiple masters access the same slave. Arbitration technique used in Avalon bus is called slave-side (distributed) arbitration. This proves advantageous for this architecture since it enables multiple masters to perform transactions concurrently when same slave is not accessed during the same bus cycle[[32]].

Figure 2.20.: Avalon bus based system[5]

Avalon bus stores logic and routing resources inside a Programmable Logic Device (PLD). It provides separate dedicated lines for address, data, and control. Therefore, there is no need of address or data decoder. Dynamic bus sizing is automatically implemented by Avalon bus. Avalon bus provides support for data width from 8 bits

up to 1024 bits[[24]]. High-bandwidth peripherals can use data streaming capability of Avalon bus.

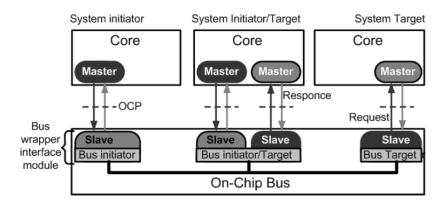

#### 2.2.5. Open Core Protocol

Accellera introduced Open Core Protocol (OCP) which defines a high performance and configurable interface for connecting IP Cores[a]. It is bus-independent, therefore, IP design with OCP interface can be reused. Its configurable interface enables IP core to use subsets of configuration features provided by OCP, thereby, optimizing die area.

From Figure 2.21 we see that OCP provides a point-to-point interface between IP cores and bus wrappers. In OCP system, master presents commands to slave and slave responds by accepting data from master or providing data to it.

Figure 2.21.: System depicting Wrapped bus and OCP instances [27]

Some features of OCP interfaces are[4]: Fully synchronous, configurable address and data width, pipelined transfers, optional burst transfers, concurrent transfers via threads, allows master or slave to control transfer rate.

OCP includes signals such as data flow, control, verification, and test, needed for IP core's communication[4]. Moreover, apart from basic OCP used for interoperability, it provides multiple extensions[30] Simple Extension, Sideband Extension, and Complex Extension. Simple and Complex Extension support burst transfers. Complex Extension provides concurrency support for threads. Sideband Extension utilizes core specific user defined signals. Moreover, it supports JTAG (Joint Test Action Group), structured test environments, and clock control.

## 2.3. ZYNQ Architecture

In the thesis, evaluation of the design is performed on Z-7010 which is from the family of Xilinx ZYNQ-7000 SoC architecture. Next sections will give details about the architecture and list its features.

#### 2. State of the Art

#### 2.3.1. Overview

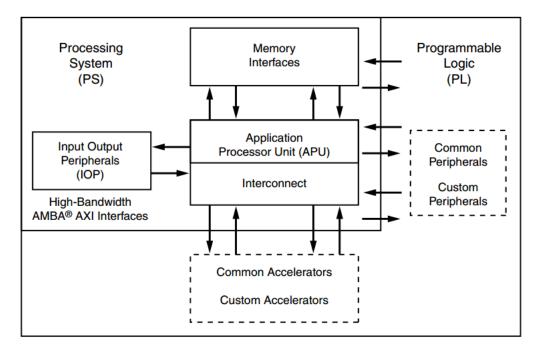

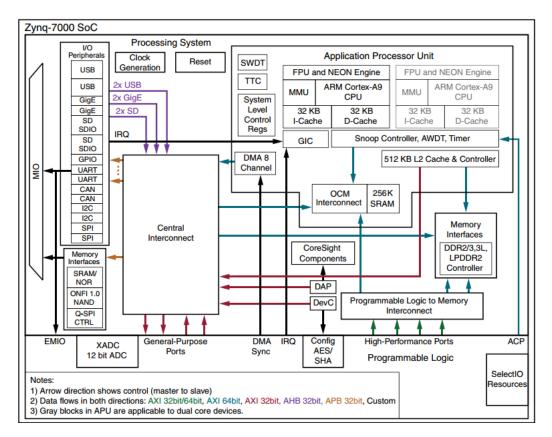

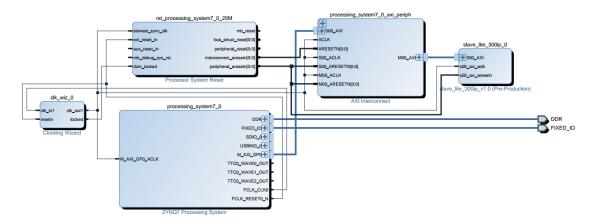

Xilinx ZYNQ-7000 SoC includes a Processing System (PS) and a Programmable Logic (PL) as displayed in Figure 2.23. PS consists of various functional blocks such as I/O peripherals, external memory interfaces, internal memory, and interconnect. Communication between PS and PL is performed through high-bandwidth AMBA AXI Interfaces.

Figure 2.22.: High-Level Block Diagram[51]

This architecture scheme enables ZYNQ to utilize re-configurable functionality with PS ASIC design. PL can be used to run data-intensive task that supports parallelism whereas PS can be allowed to handle sequential process. This results in overall high throughput.

High bandwidth connectivity, with the help of AMBA Standard AXI4 Interfaces, is provided between PS and PL and also within PS to allow functional units to communicate efficiently.

Hardware design is loaded into PL fabric only after PS is configured. As the system starts, a hard coded boot ROM is executed (Boot Stage-0) which then allows PS to load First Stage Boot Loader (FSBL) from On-Chip Memory (OCM). Afterwards, second-stage bootloader can be used to load the kernel to DDR memory. Later, if needed, a bitstream file can be used to program the PL fabric.

Zynq-7000 family PL uses Xilinx 7 Series FPGAs such as Zynq device Z-7010, used in the thesis, contains Artix-7 FPGA. The clock to PL can originate from external clock pin or from PS. PS uses three PLLs (Phase-Locked Loop) and provides four input clocks to PL. Synchronization of clocks between PS and PL is managed by the architecture. Zynq-7000 SoC devices are used in variety of fields such as Industrial motor control, Automotive and Medical diagnostics[52].

#### 2.3.2. Features

Functional units integrated into ZYNQ-7000 are displayed in Figure 2.23. It comprises of Processing System (PS) and Programmable Logic (PL).

Figure 2.23.: Top View of ZYNQ Architecture[52]

Processing System consists of Application Processor Unit (APU) that embeds dual core ARM-Cortex A9 processor which comes with 32 KB Level-1 cache memory. It also provides Floating Point Unit (FPU) to facilitate floating operations needed in applications such as DSP. NEON Engine is featured to support Single Instruction Multiple Data (SIMD) instructions to improve the system performance through data parallelism. Other componenets in APU are DMA Controller and Memory Management Unit (MMU). Automatic cache coherency between processor cores is implicit in the processor design[43].

Central interconnect links APU to multiple peripherals. It is based on ARM NIC301 (Network Interface Configuration) design and uses 64-bit AXI Interface[52].

For debugging and tracing the software design, PS includes CoreSight controller. PS communicates to PL through two AXI based 32-bit General Purpose ports. Different grade of ports are provided in the PL to communicate with the functional units in PS. Two 32-bit General Purpose ports are provided which are suitable for transfer of small amount of data such as control signals. There are two master and two slave GP ports. Four 64-bit High Performance ports which provides fast access to OCM and DDR memory. One Accelerator Coherency Port (ACP) is featured to access Snoop Control Unit (SCU) in APU. This enables PL to use OCM and Level-2 cache.

For processing Analog Mixed Signal(AMS), XADC (Xilinx Analog-to-Digital Converter) module is included in PL. It provides a dual 12-bit, 1 Mega sample per second ADC which is capable of accessing 17 external analog input channels[49].

Both PS and PL peripherals are mapped to System memory as shown in Figure 2.24. For unmapped peripherals in PS, Zynq features EMIO (Extended Multiplexed I/O) interface that allows these peripherals to use PL pins.

| FFFC_0000 to FFFF_FFFF | ОСМ                              |  |

|------------------------|----------------------------------|--|

| FD00_0000 to FFFB_FFFF | Reserved                         |  |

| FC00_0000 to FCFF_FFFF | Quad SPI linear address          |  |

| F8F0_3000 to FBFF_FFFF | Reserved                         |  |

| F890_0000 to F8F0_2FFF | CPU Private registers            |  |

| F801_0000 to F88F_FFFF | Reserved                         |  |

| F800_1000 to F880_FFFF | PS System registers,             |  |

| F800_0C00 to F800_0FFF | Reserved                         |  |

| F800_0000 to F800_0BFF | SLCR Registers                   |  |

| E600_0000 to F7FF_FFFF | Reserved                         |  |

| E100_0000 to E5FF_FFFF | SMC Memory                       |  |

| E030_0000 to E0FF_FFFF | Reserved                         |  |

| E000_0000 to E02F_FFFF | IO Peripherals                   |  |

| C000_0000 to DFFF_FFFF | Reserved                         |  |

| 8000_0000 to BFFF_FFFF | PL (MAXI _GP1)                   |  |

| 4000_0000 to 7FFF_FFFF | PL (MAXI _GP0)                   |  |

| 0010_0000 to 3FFF_FFFF | DDR(address not filtered by SCU) |  |

| 0004_0000 to 000F_FFFF | DDR(address filtered by SCU)     |  |

| 0000_0000 to 0003_FFFF | ОСМ                              |  |

|                        |                                  |  |

Figure 2.24.: System-Level Address map[43]

#### 2.3.3. Communication Interfaces

Zynq-7000 family uses ARM AMBA4 AXI Interfaces for its architecture. AXI Interface implements point-to-point protocol between a AXI master interface and a AXI slave interface. AMBA4 lists three AXI interfaces as:

• AXI4 Memory Mapped Interfaces:

- AXI4-Full Memory Mapped Interface

- AXI4-Lite Memory Mapped Interface

- AXI4-Stream Interface

Each AXI interface defines a protocol that differs from each other in terms of performance and functionality. Depending on the application, a developer can select the suitable AXI protocol. This increases the flexibility of the design.

#### **AXI4-Memory Mapped Interfaces**

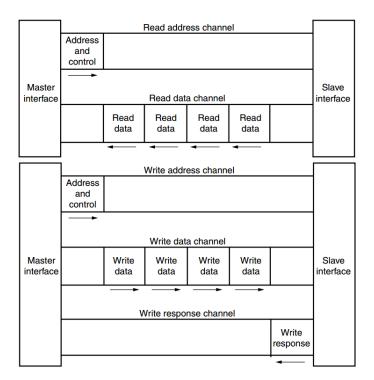

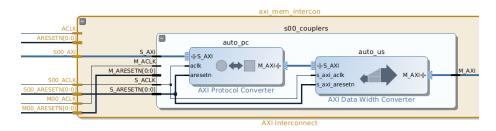

AXI4 Memory Mapped Interfaces use multiple channels to provide read/write access between the master and slave via AXI Interconnect. These channels are independent of each other and carry address, control, and data signals as illustrated in Figure 2.25.

Figure 2.25.: Read and Write Channels [42]

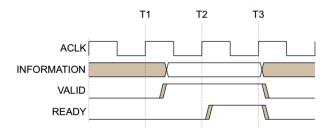

Each channel makes use of two-way VALID/READY handshake mechanism before transmitting address/control or data signals. In Figure 2.26, information is transmitted only when both VALID and READY signals are HIGH.

Dependencies can exist between channel handshake signals which can lead to a deadlock condition. Therefore, AMBA AXI Protocol Specification[7] details dependency rules to be observed while implementing a design.

Figure 2.26.: Two-way VALID/READY Handshake[7]

Due to separate address and data channels for read/write, data transfer can be concurrent and bidirectional[42]. These channels are used in two types of memory mapped interfaces:

#### **AXI4-Full Interface**

AXI4-Full implements a burst-based, point-to-point protocol which provides various options to achieve high data throughput. AXI Master initiates a data transaction by putting first address of the burst transaction on the address channel. Based on burst parameters (size and length), slave is required to calculate the following transaction addresses. Burst size indicates the width of a data beat whereas burst length states the number of beats in a burst.

Some of the key features are mentioned as follows[7]. Burst length of 1 to 256 beats is supported for incremental bursts and 1 to 16 beats for wrap bursts. Variable data widths, ranging from 32-bits to 256-bits, is supported. Data can be upsized or downsized as required.

Multiple outstanding addresses can be issued. Transactions such as out-of-order and unaligned transfers are applicable which provides better overall throughput. Security features are also added for the interface such as read and write access protection. To increase performance, it has an option for addition of register slices in pipeline stages.

#### **AXI4-Lite Interface**

AXI4-Lite protocol is similar to AXI4-Full, however, it does not support burst transfers. In other words, it supports only a burst length of 1. It is mainly used to transmit control signals since they require only few clock cycles.

PS uses AXI-Lite protocol to configure an IP (Intellectual Property) through mapping it to the system address. For instance, if General Purpose (GP) AXI Port 0 is used to interface the IP, then address space for Port 0 will be used.

It supports a fixed data width : 32-bit or 64-bit. However, Xilinx IP supports only 32-bit wide data bus[43].

### **AXI4-Stream Interface**

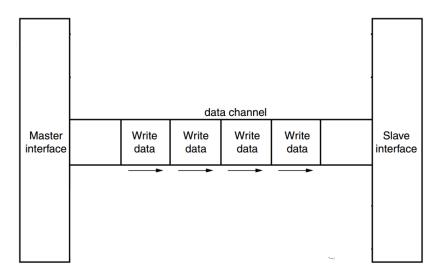

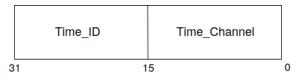

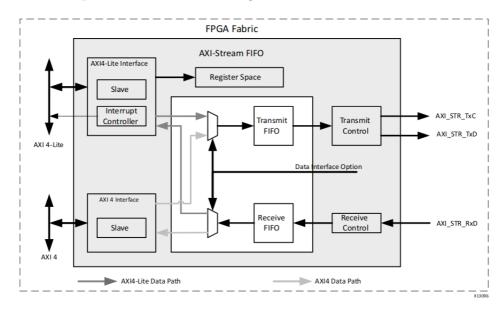

AXI4-Stream protocol defines a unidirectional flow of data from AXI master to AXI Slave without addresses (Figure 2.27. Instead of using addresses, it uses TID and TDEST signals to specify source and destination respectively[41]. It is mailny used for data-intensive applications where large amount of data has to be processed in the same manner such as in image processing, video streaming, etc.

Figure 2.27.: AXI4-Stream Transfer via Single Channel[41]

AXI4-Stream protocols provides three byte types: Data byte, Position byte, and Null byte. Data byte contains data whereas Position byte acts as a placeholder in a data stream. Null byte neither contains data nor position information. According to [7], TKEEP signal is asserted to indicate a Position byte whereas for Null byte it is deasserted. TKEEP signal allows current byte to be kept/discarded from the stream.

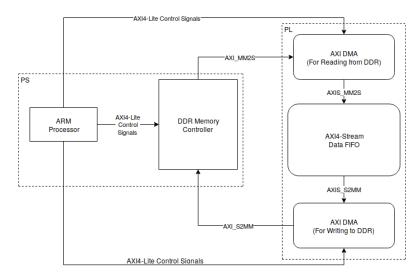

Zynq-7000 provides four 32/64-bit AXI High-Performance (HP) ports which is mainly used to read/write OCM and DDR memory via AXI4-Stream protocol. Some of the features provided by protocol[43]:

bolic of the leatures provided by prote

- Unlimited burst length.

- Sparse, continuous, aligned and unaligned streams.

- Transfer split, merge, interleave, upsize or downsize.

- Only ordered transfers allowed.

To layout a summary of AXI4 Interfaces, key differences in Table 2.1 are high-lighted.

| Interface   | Features                               | IP Replacement |

|-------------|----------------------------------------|----------------|

|             | • Memory mapped address/data interface | PLBv3.4/v4.6,  |

| AXI4        | $\circ$ Data burst support             | OPB, NPI,      |

|             |                                        | XCL            |

|             | • Memory based address/data interface  | PLBv4.6,       |

| AXI4-Lite   | $\circ$ Single data cycle only         | DCR,           |

|             |                                        | DRP            |

|             |                                        | Local Link,    |

| AXI4-Stream | $\circ$ Data-only burst                | DSP, TRN,      |

|             |                                        | FSL            |

Table 2.1.: AXI4 Feature Availability and IP Replacement[42]

## 2.4. Basis for Evaluation

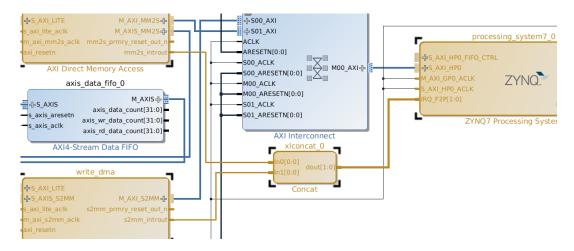

In the thesis, for the evaluation of AXI Interfaces, hardware and software designs are provided.

These designs are implemented on Digilent ZYBO board. ZYBO integrates Zynq Z-7010 SoC device and various peripherals such as Ethernet, USB, SD (Secure Digital) card interface, on-board memories, etc. Please refer to section 3.3 for an overview of the board.

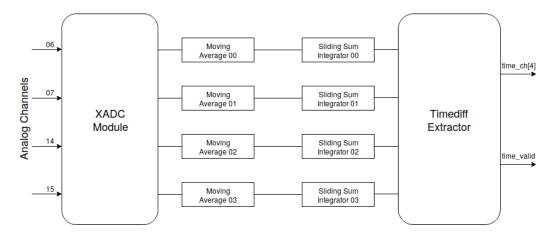

High level view of the design is illustrated in Figure 2.28. It is detailed as follows[[37], [38]]:

Figure 2.28.: Overview of the design[37]

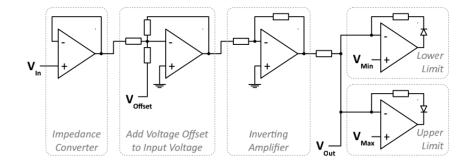

An electronic circuit is used to pre-process piezo voltage levels before passing it for sampling. This circuit is illustrated in Figure 2.29. It uses a series of Operational Amplifiers (op-amp) to provide useful voltage for XADC module to sample.

### 2. State of the Art

First op-amp acts as a buffer to isolate input source from the output so that loading affect on the source are reduced and, in addition, maintains the output voltage level. Second op-amp shifts the input voltage by adding a reference voltage for ADCs with non-symmetric input range. Third op-amp acts as an inverting amplifier to boost the voltage level so that it can be easily sampled. Lastly, fourth op-amp is used to keep the voltage within the limits of ADC input range.

Figure 2.29.: View of Pre-processing Circuit used in the design[38]

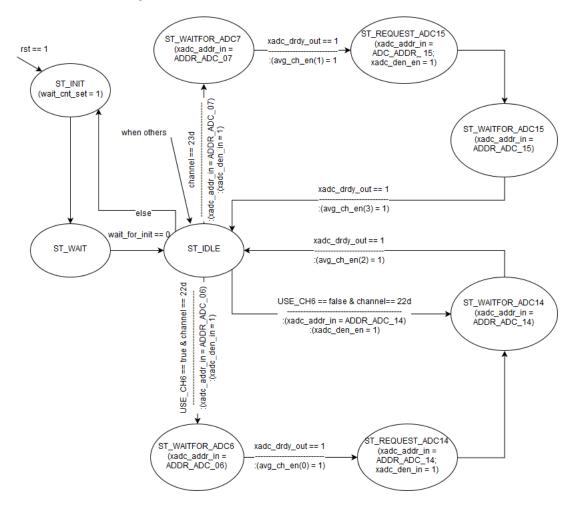

Piezo Integeration Interface board makes use of Zynq architecture. It uses PL to sample data via XADC module, then filter unwanted information using a threshold function, and, hence, extract features in terms of voltage-time values. Given FPGA implementation for PL is detailed in section 4.1.

Extracted features are passed to machine learning interface, which is running on PS, to detect and localize the impact.

In summary, basis for the master thesis is ZYBO evaluation board with a given FPGA implementation and a machine learning interface description.

# 3.1. Comparison of SoC Bus Standards

In section 2.2, various on-chip bus standards were introduced. These includes: ARM AMBA, IBM CoreConnect, Altera Avalon, OpenCores Wishbone, and Accellera Open Core Protocol (OCP). These bus standards are summarized in Table 3.1 in addition with several other standards that are not discussed in the thesis. An overview of comparison between standards, presented in section 2.2, is remarked below.

All standards, except for Avalon, have an open architecture. Avalon has partially open its architecture to public[32]. Among these, only Wishbone is truly freely, provided by OpenCores for public use. Other standards require registration or license agreement. OCP is openly licensed.

All the bus standards implement a synchronous bus system, that is, each communication in the bus is with reference to the bus clock.

Both AMBA and CoreConnect use hierarchical bus architecture, though difference lies in the number of layers. AMBA employs two bus layer: high-performance and low-performance bus, whereas CoreConnect utilizes three bus layer topology: PLB, OPB, and DRC. DRC bus uses ring topology for sharing status and control information. Therefore, CoreConnect makes usage two different topology schemes. Avalon and OCP incorporates similar architecture, point-to-point topology. Wishbone provides multiple choices: Point-to-Point, Ring type, Crossbar network, or Shared bus. It takes a single level bus approach and so does not support for hierarchical buses. For support for multiple buses, two separate Wishbone interfaces can be created: one for high speed, low latency and other for low speed components[27].

Single level bus approach severely limits the bus bandwidth because of increased load on the bus. For this reason, hierarchical bus offers better throughput due to division of high-bandwidth and low-bandwidth components on separate bus lines. Major disadvantage with shared bus system is that it limits design scalability and delay in sharing resources between SoC components[27].

AMBA and Wishbone offers flexibility in arbitration; they do not define any arbitration scheme. It is up to the user to utilize arbitration method according to the application's needs. CoreConnect uses static priority in a programmed fashion. Avalon connects masters and slaves in a point-to-point manner, making no use of bus for the transaction. Therefore, they use slave-side arbitration scheme in case multiple masters intend to access the same slave. OCP does not make use of arbitration. AMBA and CoreConnect have similar data transfer schemes: handshaking,

| Lotterybus | VCI | OCP | PI bus | Marble | Core Frame | Silicon Backplane | Wishbone   | Core Connect | Avalon | AMBA       | Name                    |             |

|------------|-----|-----|--------|--------|------------|-------------------|------------|--------------|--------|------------|-------------------------|-------------|

| •          | n/a | ×   | -      | ı      | $14^{*}$   | 1                 | ×          | •            | ×      | -          | Point-to-point          |             |

|            | n/a | -   | -      | ı.     | ı.         | ı.                | ×          | *1           | i.     | -          | Ring                    | T           |

|            | n/a |     | ×      | ı.     | 1          | ı.                | ×          |              | i.     | •          | Unilevel shared bus     | Topology    |

| ×          | n/a | •   | 1      | ×      | 1          | ı.                | •          | 1*           | i.     | ×          | Hierarchical bus        | gy          |

| •          | n/a | •   | ı      | ı.     | 1          | ×                 | ×          | ·            | i.     | -          | Interconnection network |             |

| S          | S   | S   | S      | A      | S          | S                 | S          | S            | S      | S          | Synchronous/Asinhronous |             |

|            | 3*  | •   | 3*     | ×      | 3*         | ı                 | *          | 4*           | 13*    | *L         | Static priority         |             |

| •          | 3*  | •   | 3*     | ı.     | 3*         | 6*                | 3*         | •            | 13*    | *          | TDMA                    |             |

| ×          | 3*  | •   | 3*     | ī      | 3*         | •                 | 3*         | •            | 13*    | *L         | Lottery                 | Arbi        |

| •          | 3*  | •   | 3*     | ı      | 3*         | 6*                | 3*         | •            | 13*    | 7*         | Round-robin             | Arbitration |

|            | 3*  | •   | 3*     | ī      | 3*         | 1                 | 3*         | •            | 13*    | <b>7</b> * | Token Passing           |             |

| •          | 3*  | •   | 3*     | ī      | 3*         | ı.                | 3*         | •            | 13*    | 7*         | CDMA                    |             |

| n/a        | n/a | n/a | 1-32   | n/a    | n/a        | 8,16,32,64        | 8,16,32,64 | *6           | 1-128  | *8         | Data bus width [bit]    | Bus width   |

| n/a        | n/a | n/a | 1-32   | n/a    | n/a        | n/a               | 1-64       | $10^*$       | 1-32   | 32         | Address bus width [bit] | lth         |

| n/a        | ×   | ×   | ×      | ×      | 2*         | ×                 | ×          | ×            | ī      | ×          | Handshaking             |             |

| n/a        | ×   | •   | •      | ×      | 1          | ×                 | n/a        | ×            | i.     | ×          | Split transfer          |             |

| n/a        | ×   | ×   | ×      | ×      | n/a        | ×                 | ı.         | ×            | ×      | ×          | Pipelined transfer      | Tran        |

| ×          | n/a | ×   | •      | ×      | ×          | ×                 | ×          | ×            | ×      | ×          | Burst transfer          | Transvers   |

| n/a        | ı   | ×   | ı      | ×      | ×          | ×                 | n/a        | n/a          | ı      | n/a        | Broadcast               |             |

| n/a        | n/a | •   | ı      | n/a    | n/a        | ×                 | n/a        | n/a          | i.     | n/a        | Multicast               |             |

| n/a        | n/a | n/a | n/a    | n/a    | n/a        | n/a               | $11^{*}$   | 12*          | n/a    | $11^{*}$   | Operating frequancy     |             |

3. Concept

Table 3.1.: Features of SoC Bus Standards[27]. Exceptions:1\* Data lines shared, control lines point-to-point ring; 2\* Palmbus uses handshaking, Mbus does not; 3\* Application specific, arbiter can be designed regarding to the application requirements; 4\* Programmable priority fairness; 5\* Two level arbitration, first level TDMA, second level static priority; 6\* Two level arbitration, first TDMA, second round-robin token passing; 7\* Application specific except for APB which requires no arbitration; 8\* For AHB and ASB bus width is 32, 64, 128 or 256 byte, for APB 8, 16 or 32 byte; 9\* For PLB bus width is 32, 64, 128 or 256 byte, for OPB 8, 16 or 32 byte and for DCR 32 byte; 10\* For PLB and OPB bus width is 32 byte, and for DCR 10 byte; 11\* User defined operating frequency; 12\* Operating frequency depending on PLB width; 13\* Slave side arbitration; 14\* System of buses, Palmbus and Mbus, both are point-to-point.

pipelining, split, and burst transfers. Wishbone supports handshaking and burst transfers. It can support pipelining if the architecture utilizes data flow interconnection scheme. Avalon makes no use of handshaking or split transactions since transfers take place without the intervention of bus. It employs pipelined and burst transfers. OCP does not support split transfers, however, it is the only one among others that provides broadcast transfers.

Among these, Wishbone is the only standard that offers read-modify-write transfer.

In conclusion, CoreConnect has similar feature set as AMBA. Compared to AMBA, Wishbone provides simpler design and better flexibility. However, Wishbone allows maximum data width of 64 bits whereas AMBA can provide data width of up to 256 bits. As mentioned in section 3.2, one of the evaluation criteria is the amount of data transferred between FPGA and processor. Hence, it is useful to have support for higher data widths. In terms of operating frequency, AMBA and Wishbone provide flexibility to user whereas CoreConnect's frequeny is limited to Processor Local Bus (PLB) width.

## 3.2. Approach for Evaluation of AXI Interfaces

The goal of the master thesis is to analyze best fitting AXI Interface for the given hardware and software design. AXI4 Interfaces have to be evaluated with different configurations resulting in quantification of best fitting AXI4 Interface. Hence, to satisfy such needs, an approach is outlined as follows.

- 1. Understanding of given FPGA implementation to derive the changes needed in the design to incorporate best-fitting interface.

- 2. Analysis of three different AXI4 Interfaces:

- 2.1. Hardware design for three AXI4 Interfaces

- 2.2. Implementation of several test cases to evaluate performance of each AXI4 Interface hardware design.

- 3. Based on test results, conclusion derived about the efficient usage of each AXI4 protocol.

Criteria for evaluation of the interfaces includes:

- Amount of data (input length) transferred between PS and PL

- Processing time for read/write operations

- PL Frequency

- Various interface configuration such as AXI4-Full provides different data widths and several burst configuration

The influence of PL frequency on the performance of read/write operation is to be included in the results. Moreover, AXI4-Full protocol provides several configuration for data widths and burst transfer. Performance of AXI4-Full Interface is to be evaluated with these configurations.

# 3.3. Evaluation Platform

### 3.3.1. Hardware

### Digilent ZYBO board

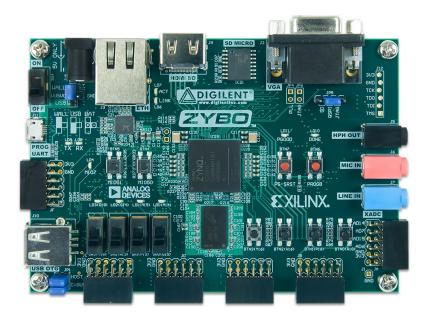

Digilent provides development platform for SoC (Figure 3.1) that features Xilinx Zynq Z-7010 All Programmable System-on-Chip (APSoC) architecture. Zynq architecture is discussed in section 2.3.

Figure 3.1.: ZYBO ZYNQ-7000 Development Board[13]

High-level view of the architecture can be seen in Figure 2.23. Some of the main features offered by ZYBO are listed as follows[13]:

- 650 MHz dual-core ARM Cortex-A9 processor

- Xilinx Artix-7 FPGA Programmable Logic

- 512 MB DDR3 memory

Functionality for On-board JTAG programming is featured by the board. It also includes dual analog/digital Pmod (Peripheral Module) interface. Four channels of

this interface are used in the MERGE project to connect ADC signals from piezo electrodes placed on the metal sheet. Various other interfaces are also supplied such as 1G Ethernet, USB 2.0, SPI, UART, CAN, I2C, SDIO, HDMI, etc.

ZYBO supports three different boot modes: microSD, Quad-SPI (QSPI) Flash, and JTAG. In the thesis, Linux based OS is used which is stored in microSD. ZYBO is configured to load Linux kernel from SD card into RAM via JP5 jumper[13].

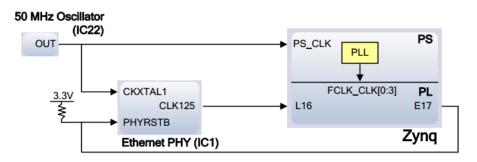

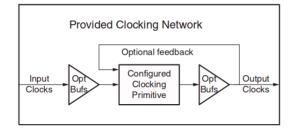

Figure 3.2 highlights clock usage for PS and PL. ZYBO provides 50 MHz clock to PS. This allows processor to run at maximum frequency of 650 MHz and DDR3 memory controller at maximum of 525 MHz[13]. PS incorporates four PLLs (Phase-Locked Loop) depicted as  $FCLK_CLK[0:3]$ . They provide reference clocks to PL. In addition, 125 MHz clock from Ethernet module provides an external clock input to PL.

Figure 3.2.: ZYBO clocking scheme[13]

ZYBO provides four pairs for analog input channels. In the given FPGA implementation, XADC module in PL reads piezo voltages through these analog channels.

### 3.3.2. Software

For SoC devices with FPGA, Xilinx offers Vivado Design Suite and Xilinx Software Development Kit (SDK). These tools have simplified embedded system design by providing a user-friendly interface, debug support, and verification of design.

In the thesis, Vivado v2015.4.2 is used to design hardware for different AXI4-Interfaces. To test the hardware design, several test cases were implemented in C using SDK.

### Vivado