#### University of Lethbridge Research Repository

| Ο | ΡΙ | JS |

|---|----|----|

Theses

http://opus.uleth.ca

Arts and Science, Faculty of

provided by OPUS: Open Uleth Scholarship - University of Lethbridge Re

2012

# Synthesis and testing of reversible Toffoli circuits

## Nayeem, Noor Muhammed

Lethbridge, Alta. : University of Lethbridge, Dept. of Mathematics and Computer Science, c2012

http://hdl.handle.net/10133/3309 Downloaded from University of Lethbridge Research Repository, OPUS

#### SYNTHESIS AND TESTING OF REVERSIBLE TOFFOLI CIRCUITS

NOOR MUHAMMED NAYEEM Bachelor of Science, University of Dhaka, 2008

A Thesis Submitted to the School of Graduate Studies of the University of Lethbridge in Partial Fulfillment of the Requirements for the Degree

#### **MASTER OF SCIENCE**

Department of Mathematics and Computer Science University of Lethbridge LETHBRIDGE, ALBERTA, CANADA

© Noor Muhammed Nayeem, 2012

To my beloved parents

## Abstract

Recently, researchers have been interested in reversible computing because of its ability to dissipate nearly zero heat and because of its applications in quantum computing and low power VLSI design. Synthesis and testing are two important areas of reversible logic. The thesis first presents an approach for the synthesis of reversible circuits from the exclusive-OR sum-of-products (ESOP) representation of functions, which makes better use of shared functionality among multiple outputs, resulting in up to 75% minimization of quantum cost compared to the previous approach. This thesis also investigates the previous work on constructing the online testable circuits and points out some design issues. A simple approach for online fault detection is proposed for a particular type of ESOP-based reversible circuit, which is also extended for any type of Toffoli circuits. The proposed online testable designs not only address the problems of the previous designs but also achieve significant improvements of up to 78% and 99% in terms of quantum cost and garbage outputs, respectively.

#### Acknowledgments

I owe a great debt of gratitude to my supervisor Dr. Jacqueline E. Rice for her continuous support, inspiration and guidance throughout my M.Sc. program. I owe sincere thanks to my committee members, Professor Shelly Wismath and Dr. Kevin Grant. I am grateful to them for taking the time to give me detailed comments on an earlier draft of this thesis, which helped to improve the thesis.

I would like to thank Professor Guan Zhijin, Dr. Ding Weiping, and Dr. Hang Yueqin of Nantong University, China for their suggestions. I would also like to thank Professor Gerhard W. Dueck at the University of New Brunswick, Canada for providing me the shared cube synthesis tool. Special thanks to Navid Farazmand of Northeastern University, USA for explaining me the simulation results of the dual rail coding approach. Also thanks to Md. Raqibur Rahman for his discussions on ternary logic.

Finally, I would like to thank my parents, sister and brother for their encouragement and support.

# Contents

| Ар  | prov    | al/Signature Page                                     | ii      |

|-----|---------|-------------------------------------------------------|---------|

| De  | dicat   | ion                                                   | iii     |

| Ab  | ostrac  | et                                                    | iv      |

| Ac  | knov    | vledgments                                            | v       |

| Ta  | ble of  | f Contents                                            | vi      |

| Lis | st of A | Acronyms                                              | ix      |

| Lis | st of [ | Tables                                                | X       |

| Lis | st of l | Figures                                               | xi      |

| 1   | Intr    | oduction                                              | 1       |

|     | 1.1     | Goals of the Thesis                                   | 2       |

|     | 1.2     | Organization of the Thesis                            | 2       |

| 2   | Bac     | kground                                               | 4       |

|     | 2.1     | Logic Function                                        | 4       |

|     | 2.2     | Reversible Logic                                      | 4       |

|     | 2.3     | Reversible Gates                                      | 6       |

|     |         | 2.3.1 Toffoli Gates                                   | 6       |

|     | 2.4     | 2.3.2 Fredkin Gates                                   | 8       |

|     | 2.4     | Reversible Circuit                                    | 9       |

|     | 2.5     | Cost Metrics                                          | 9<br>9  |

|     |         | 2.5.1       Gate Count                                | 9<br>10 |

|     |         | 2.5.2         Garbage Output                          | 11      |

|     | 2.6     | Synthesis Approaches of Reversible Logic              | 13      |

|     | 2.0     | 2.6.1 Transformation-based Synthesis                  | 13      |

|     |         | 2.6.2 PPRM-based Synthesis                            | 14      |

|     |         | 2.6.3 ESOP-based Synthesis                            | 14      |

|     |         | 2.6.4 Decision Diagram-based Synthesis                | 15      |

|     | 2.7     | Fault Models                                          | 15      |

|     |         | 2.7.1 Stuck-at Fault Model                            | 16      |

|     |         | 2.7.2 Bit Fault Model                                 | 16      |

|     |         | 2.7.3 Missing, Repeated and Reduced Gate Fault Models | 17      |

|     |         | 2.7.4 Crosspoint Fault Model                          | 18      |

| 3 | ESC  | DP-based Synthesis                                                      | 19 |

|---|------|-------------------------------------------------------------------------|----|

|   | 3.1  | Basic Approach                                                          | 20 |

|   | 3.2  | Optimization by Adding Not Gates                                        | 21 |

|   | 3.3  | Cube Ordering Heuristics                                                | 23 |

|   |      | 3.3.1 Alpha-beta Cost Metric                                            | 25 |

|   |      | 3.3.2 Autocorrelation Cost Metric                                       | 26 |

|   | 3.4  | Optimization by Using Negative-control Toffoli gates                    |    |

|   | 3.5  | Shared Cube Synthesis                                                   |    |

|   | 3.6  | Summary                                                                 |    |

| 4 | Imp  | roved ESOP-based Synthesis                                              | 33 |

|   | 4.1  | Utilization of Shared Functionality                                     | 33 |

|   | 4.2  | Our Approach                                                            | 35 |

|   | 4.3  | Experimental Results and Discussions                                    | 41 |

|   | 4.4  | Summary                                                                 | 43 |

| 5 | Test | ing of Reversible Circuits                                              | 45 |

|   | 5.1  | Offline Testing                                                         | 45 |

|   |      | 5.1.1 Testing of Stuck-at Faults                                        | 46 |

|   |      | 5.1.2 Testing of Missing Gate, Repeated Gate, and Reduced Gate Faults . | 47 |

|   | 5.2  | Online Testing                                                          | 47 |

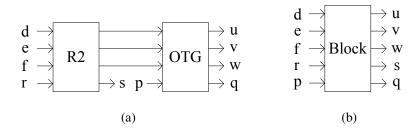

|   |      | 5.2.1 Testable Circuit Design Using R1, R2, and R Gates                 | 47 |

|   |      | 5.2.2 Testable Circuit Design Using Testable Reversible Cells (TRCs)    | 50 |

|   |      | 5.2.3 Testable Circuit Design Using Online Testable Gates (OTGs)        | 53 |

|   |      | 5.2.4 Dual Rail Coding Approach                                         | 54 |

|   |      | 5.2.5 Testable Circuit Design with Duplication of Gates                 |    |

|   | 5.3  | Summary                                                                 |    |

| 6 | Opt  | imized Approaches for Online Fault Detection                            | 57 |

|   | 6.1  | Testing of ESOP-based Circuits                                          | 57 |

|   |      | 6.1.1 Construction of a Testable Circuit from the ESOP-based Circuit    | 58 |

|   |      | 6.1.2 Analysis                                                          | 59 |

|   |      | 6.1.3 Experimental Results                                              | 64 |

|   |      | 6.1.4 Advantages of the Proposed Design                                 | 65 |

|   | 6.2  | Testing of Toffoli Circuits                                             | 67 |

|   |      | 6.2.1 Construction of a Testable Circuit from the Toffoli Circuit       | 67 |

|   |      | 6.2.2 Analysis                                                          | 68 |

|   |      | 6.2.3 Experimental Results                                              | 71 |

|   |      | 6.2.4 Comparisons with Our First Proposed Approach                      | 72 |

|   | 6.3  | Coverage of Fault Models                                                | 74 |

|   | 6.4  | Summary                                                                 |    |

|   |      |                                                                         |    |

| 7   | Con    | clusion       | 75 |

|-----|--------|---------------|----|

|     | 7.1    | Contributions | 75 |

|     | 7.2    | Future Work   | 76 |

| Bil | bliogr | raphy         | 78 |

## **List of Acronyms**

- BDD Binary decision diagram

- DFT Design-for-test

- DRG Deduced reversible gate

- ESOP Exclusive-OR sum-of-products

- ETG Extended Toffoli gate

- EXOR Exclusive-OR

- EXNOR Exclusive-NOR

- ILP Integer linear program

- M-S Muthukrishnan-Stroud

- MVL Multiple-valued logic

- OTG Online testable gate

- PPRM Positive polarity Reed-Muller

- TB Testable block

- TC Test cell

- TRC Testable reversible cell

## List of Tables

| Truth table of an arbitrary reversible function.                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Truth table of an AND gate.                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Truth table of the 3-bit Toffoli gate.                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Truth table of the 3-bit Fredkin gate                                            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Costs of <i>n</i> -bit Toffoli gates                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Cost calculation of input variables for the cube-list in Figure 3.4(a). $\ldots$ | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Experimental results.                                                            | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Experimental results.                                                            | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Comparison of different online testable approaches                               | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Improvements achieved by our approach.                                           | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Overhead calculation of the testable design over the non-testable design         | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Coverage of fault models                                                         | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                  | Truth table of an arbitrary reversible function.Truth table of an AND gate.Truth table of the 3-bit Toffoli gate.Truth table of the 3-bit Fredkin gate.Costs of <i>n</i> -bit Toffoli gates.Cost calculation of input variables for the cube-list in Figure 3.4(a).Experimental results.Comparison of different online testable approaches.Improvements achieved by our approach.Overhead calculation of the testable design over the non-testable design. |

# **List of Figures**

| 2.1        | (a) A NOT gate, (b) A CNOT gate, (c) an <i>n</i> -bit Toffoli gate, (d) a 3-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | negative-control Toffoli gate, and (e) an $(n+1)$ -bit ETG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7  |

| 2.2        | A Toffoli circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9  |

| 2.3        | Garbage output in a reversible circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

| 2.4        | A stuck-at fault.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16 |

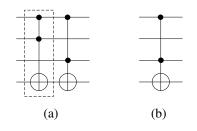

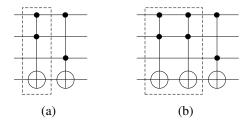

| 2.5        | (a) Before and (b) after the occurrence of a missing gate fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17 |

| 2.6        | (a) Before and (b) after the occurrence of a repeated gate fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17 |

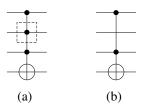

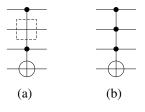

| 2.7        | (a) Before and (b) after the occurrence of a disappearance fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18 |

| 2.8        | (a) Before and (b) after the occurrence of an appearance fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18 |

| 3.1        | An ESOP cube-list.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

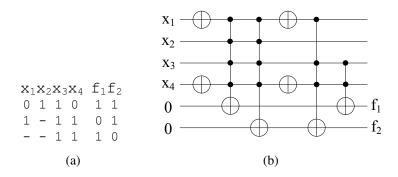

| 3.2        | (a) An ESOP cube-list and (b) a circuit generated by basic approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22 |

| 3.3        | a) An ESOP cube-list and (b) a circuit generated by basic approach with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|            | line optimization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24 |

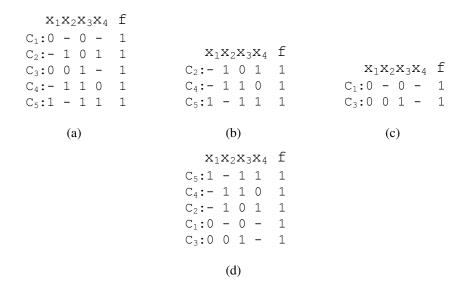

| 3.4        | (a) Initial ESOP cube-list, (b) list 1 containing positive polarity and don't care value of $x_3$ , (c) list 2 containing negative polarity of $x_3$ , and (d) final                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 3.5        | <ul><li>(a) Initial ESOP cube-list, (b) list 1 containing positive polarity and don't</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26 |

|            | care value of $x_1$ , (c) list 2 containing negative polarity of $x_1$ , and (d) final                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •  |

| 2.6        | reordered cube-list.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28 |

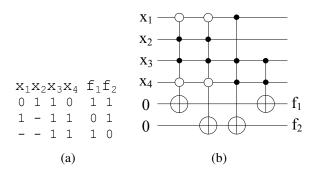

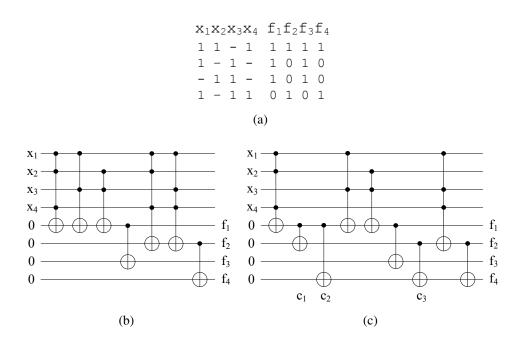

| 3.6<br>3.7 | <ul><li>(a) An ESOP cube-list and (b) a circuit using negative-control Toffoli gates.</li><li>(a) An ESOP cube-list, and circuits generated (b) by basic approach with</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29 |

|            | line optimization and (c) by shared cube synthesis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

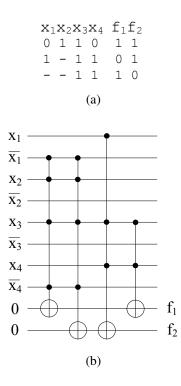

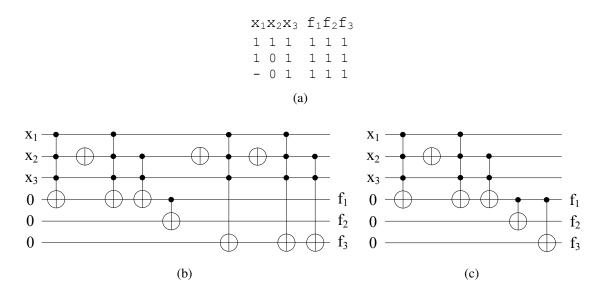

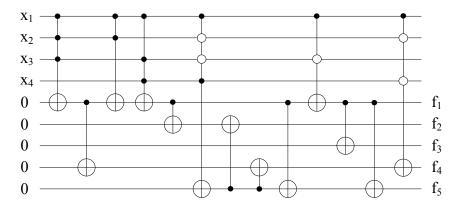

| 4.1        | (a) An example cube-list, (b) a Toffoli cascade generated by the approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|            | in [46, 47], and (c) an improved Toffoli cascade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34 |

| 4.2        | (a) An initial cube-list, (b) a Toffoli cascade generated by the approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|            | in [46, 47], and (c) an improved Toffoli cascade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35 |

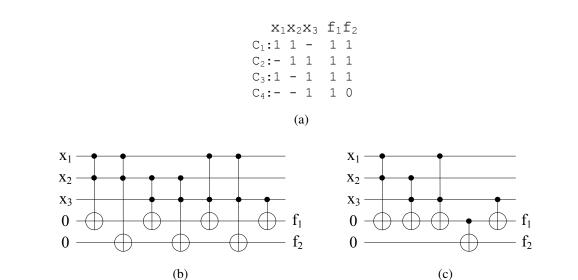

| 4.3        | Cube-list and its sub-lists.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38 |

| 4.4        | Improved shared cube synthesis process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 |

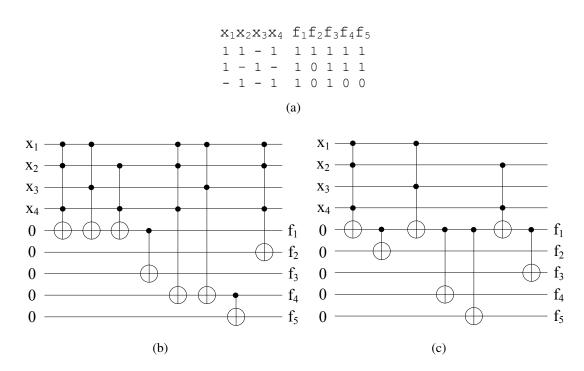

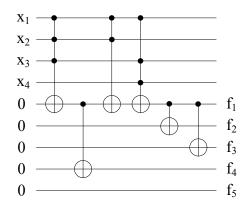

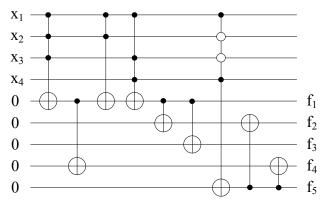

| 4.5        | (a) An example cube-list, (b) a Toffoli cascade generated by the approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|            | in [46, 47], and (c) a Toffoli cascade generated by our proposed approach. $% \left[ \left( {{{\bf{n}}_{\rm{c}}}} \right) \right] = \left[ {\left( {{{\bf{n}}_{\rm{c}}}} \right)_{\rm{c}}} \right]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44 |

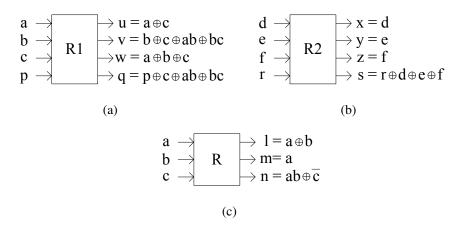

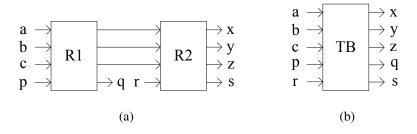

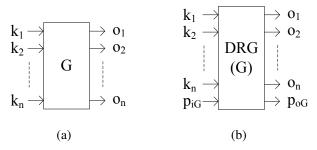

| 5.1        | (a) R1 gate, (b) R2 gate, and (c) R gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48 |

| 5.2        | (a) Construction of a testable block (TB), and (b) its block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48 |

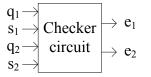

| 5.3        | A two-pair two-rail checker circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49 |

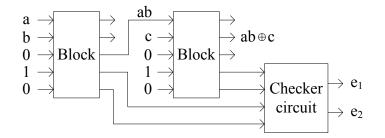

| 5.4        | Online testable circuit for $f = ab + \overline{c}$ , according to the design in [54, 53].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50 |

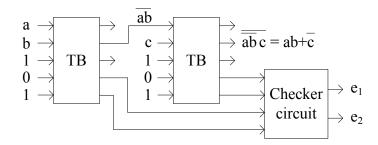

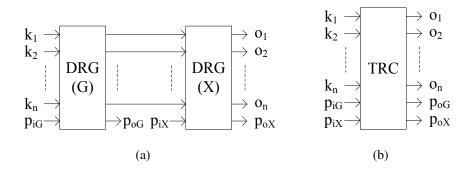

| 5.5        | (a) G gate and (b) $DRG(G)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50 |

| 5.6        | (a) Construction of a testable reversible cell TRC(G), and (b) its block dia-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|            | gram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

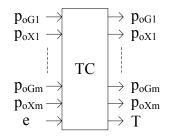

| 5.7        | Test cell (TC).       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 52 |

| 5.8  | (a) A Toffoli circuit for $f = ab \oplus a \oplus c$ , and (b) the corresponding testable |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | circuit according to the design in [21, 22]                                               | 52 |

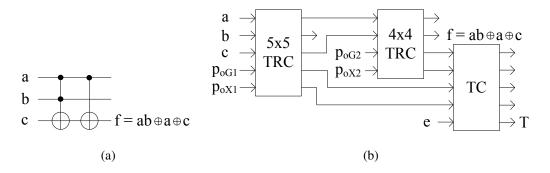

| 5.9  | Online testable gate (OTG)                                                                | 53 |

| 5.10 | (a) Construction of a testable block, and (b) its block diagram.                          | 53 |

| 5.11 | Online testable circuit for $g = ab \oplus c$ , according to the design in [52]           | 54 |

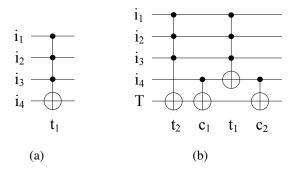

| 5.12 | (a) A Toffoli gate $t_1$ and (b) its corresponding testable circuit                       | 55 |

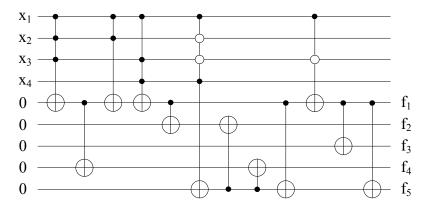

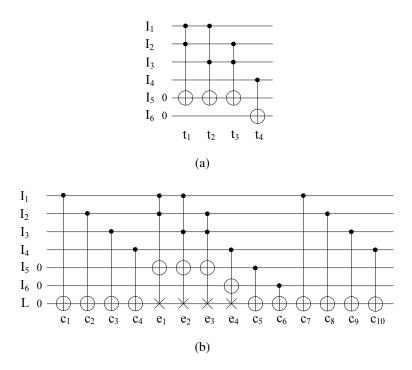

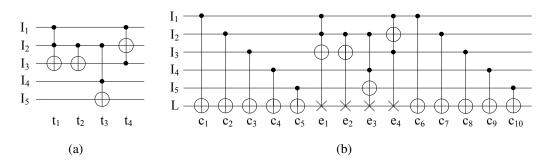

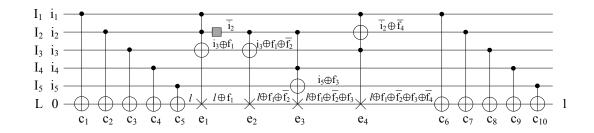

| 6.1  | (a) An ESOP-based circuit, (b) Online testable reversible circuit                         | 59 |

| 6.2  | Fault propagation in multiple lines.                                                      | 60 |

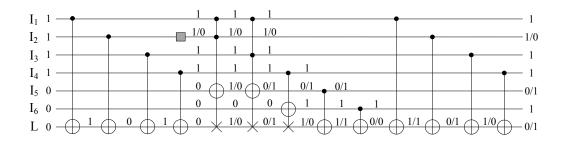

| 6.3  | A single fault on input line $I_2$                                                        | 64 |

| 6.4  | A single fault on output line $I_5$                                                       | 65 |

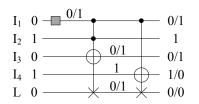

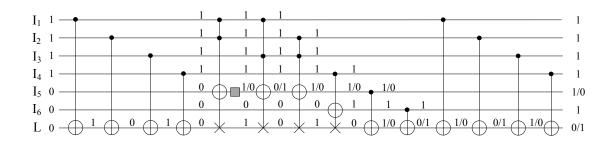

| 6.5  | (a) A Toffoli circuit and (b) an online testable circuit                                  | 68 |

| 6.6  | Fault detection in testable circuit.                                                      | 71 |

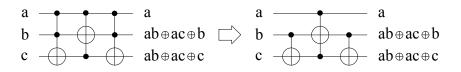

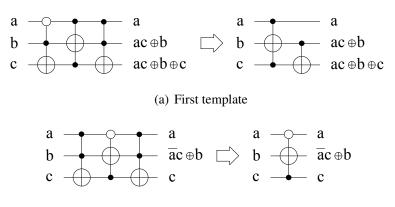

| 7.1  | A template for Toffoli gates with only positive controls [33]                             | 76 |

| 7.2  | Two templates for Toffoli gates with positive and negative controls                       | 76 |

# Chapter 1 Introduction

Traditional logic computation is irreversible since the outputs do not have enough information to reconstruct the inputs. In logic calculation, if there are *p* inputs and *q* outputs such that p > q, then at least p - q bits of information are lost [55]. As an example, a logic gate with two inputs and one output destroys at least one bit of information during computation. Landauer's principle [20] states that each bit of information that is disregarded results in dissipation of heat, regardless of underlying technology. The amount of dissipated heat is at least  $kT(\ln 2)$  joules for every bit of lost information, where *k* is the Boltzmann's constant and *T* is the absolute temperature. At room temperature, this amount becomes  $2.9 \times 10^{-21}$ joules.

According to [24], the problem of heat dissipation arises from (1) technological deviation from ideality of switches and materials and (2) Landauer's principle. Current technologies have addressed the first part of the problem by reducing heat loss. However, information loss in irreversible computation, which is the second part of the problem, will cause a considerable amount of heat generation in the near future due to increasing density of circuits. As an example [32], packing densities in excess of  $10^{17}$  logic devices in a cubic centimeter cause devices to dissipate at least  $kT(\ln 2)$ , which result in more than 3,000,000 watts while operating at room temperature at a frequency of 10 gigahertz.

Reversible logic is being considered as an alternative to traditional irreversible logic since reversible computing does not erase or lose any information. As a result, reversible logic has a theoretical potential to dissipate no energy. According to Frank [10], reversible logic can recover a fraction of energy that can reach up to 100%. As there is no limit in reducing the heat dissipation in reversible logic, the amount of dissipated heat will become very close to zero with the development of hardware.

Reversible logic is a vital part of quantum computing since quantum computation is reversible, and the physical reality of quantum logic can be illustrated by reversible logic [1]. Interested readers can refer to [41] for a detailed discussion of quantum computing. Reversible computing is also useful for other technologies including low power CMOS design [3], optical computing [43], nanotechnology [31], and bioinformatics.

#### **1.1** Goals of the Thesis

Reversible logic uses a different set of reversible gates rather than traditional AND or OR gates to realize circuits. Moreover, fan-outs and loops are prohibited in reversible circuits. These cause the synthesis of reversible logic to be different from that of traditional irreversible logic, making synthesis a challenging area of research. One goal of this thesis is to present an optimized reversible logic synthesis approach for functions, especially large ones, given in the form of exclusive-OR sum-of-products (ESOP).

Testing is important for circuit design. This thesis aims to thoroughly examine the prior work on online testable approaches and presents new online testable reversible designs which are efficient in different cost metrics and deal with the problems encountered in the prior work.

#### **1.2 Organization of the Thesis**

The rest of the thesis is organized as follows:

Chapter 2 introduces the reader to the world of reversible logic. The basics of reversible gates and cost metrics used for evaluating reversible circuits are covered. This chapter also provides an overview of various synthesis approaches and fault models for reversible circuits.

Chapter 3 begins with the representation of ESOP functions and then focuses on a particular type of synthesis which uses this representation. Algorithms and examples are given so that readers will gain a clear knowledge of ESOP-based synthesis.

In Chapter 4, we first provide the motivational examples for improving the ESOP-based synthesis. We then propose an optimized approach, followed by an example to illustrate the approach step-by-step. Experimental results are also tabulated to show the superiority of this approach. This chapter has been published in [37] and [39].

Starting in Chapter 5, the focus of the thesis turns to testing of reversible logic. For offline testing, the covered topics include test set generation and design-for-test (DFT) methods. A major part of this chapter is devoted to online testing. We look at different approaches in detail for designing testable circuits and also analyze the issues related to these designs with suitable examples. Part of this chapter has been published in [38].

In Chapter 6, we present in detail two approaches for constructing online testable reversible circuits. Analyses of the presented approaches along with proofs are provided. Experimental results for a number of benchmarks are compared to the previously reported approaches. This chapter has been published in [40] and [38].

Chapter 7 concludes the thesis by highlighting the major contributions of this thesis and describing the further research directions in the areas of both synthesis and testing.

#### Chapter 2

#### Background

#### 2.1 Logic Function

Let  $A = \{0,1\}$  be a set of binary or Boolean logic values. A logic function is simply a function of the form  $f : A^p \to A^q$  for two natural numbers p and q. Such a function can be expressed in terms of logical operations which are AND, OR, NOT, NAND, NOR, exclusive-OR (EXOR), and exclusive-NOR (EXNOR) operations. A logic gate implements a logical operation. In traditional irreversible logic, AND, OR, NOT, NAND, NOR, EXOR, and EXNOR gates are used as standard gates. Among all the logic gates, only NAND and NOR gates are universal since NAND gates alone (or alternatively NOR gates alone) can be used to implement any logic function. A circuit, which is an electronic representation of a function, is made from these gates by interconnecting the outputs of some gates to the inputs of others. Logic synthesis is the process of transforming a logic function into a circuit design in terms of gates. The resultant circuit is called a realization of the given function.

#### 2.2 Reversible Logic

A function is reversible if it is bijective (*i.e.*, one-to-one and onto) [49]. In other words, a reversible function has the same number of inputs as outputs (*i.e.*, p = q), and there is a one-to-one mapping between its input and output vectors. A reversible gate realizes a reversible function.

An example of a truth table for a particular reversible function with three inputs ( $k_1$ ,  $k_2$ , and  $k_3$ ) and three outputs ( $o_1$ ,  $o_2$ , and  $o_3$ ) is given in Table 2.1. The number of input vari-

ables and the number of output variables are the same. From the truth table, it can be seen that for any two input vectors, the corresponding output vectors are different. Similarly, for any two output vectors, the corresponding input vectors are different.

| $k_1$ | $k_2$ | $k_3$ | $o_1$ | <i>o</i> <sub>2</sub> | 03 |

|-------|-------|-------|-------|-----------------------|----|

| 0     | 0     | 0     | 0     | 0                     | 1  |

| 0     | 0     | 1     | 0     | 1                     | 1  |

| 0     | 1     | 0     | 0     | 0                     | 0  |

| 0     | 1     | 1     | 0     | 1                     | 0  |

| 1     | 0     | 0     | 1     | 0                     | 1  |

| 1     | 0     | 1     | 1     | 1                     | 1  |

| 1     | 1     | 0     | 1     | 0                     | 0  |

| 1     | 1     | 1     | 1     | 1                     | 0  |

Table 2.1: Truth table of an arbitrary reversible function.

In contrast, the AND gate (see truth table in Table 2.2) is not reversible for the following two reasons:

- it has two input variables but only one output variable, and

- for three different input vectors, the output vectors are the same.

If the output is 1, its input vector is [1,1] which can be uniquely identified. However, if the output is 0, unique identification of its input vector is not possible since there are three possible input vectors - [0,0], [0,1], and [1,0]. Other traditional logic gates such as OR, NAND, NOR, and EXOR are also not reversible. The only exception is the NOT gate which is reversible.

Table 2.2: Truth table of an AND gate.

| Inp | outs | Output |

|-----|------|--------|

| 0   | 0    | 0      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1    | 1      |

#### **2.3 Reversible Gates**

A different set of reversible logic gates is used to build reversible circuits, since traditional logic gates other than the NOT gate are not applicable in reversible logic. The two most popular reversible gates are the Toffoli gates and the Fredkin gates.

#### 2.3.1 Toffoli Gates

An *n*-bit Toffoli gate is a reversible logic gate that has *n* inputs and *n* outputs and that maps the input vector  $[k_1, k_2, ..., k_n]$  to the output vector  $[o_1, o_2, ..., o_n]$ , where  $o_j = k_j$  for j = 1, 2, ..., n - 1 and  $o_n = k_1 k_2 \cdots k_{n-1} \oplus k_n$ . Here, the symbol  $\oplus$  denotes the EXOR operation. The first n - 1 bits are known as controls, and the last  $(n^{th})$  bit is the target. This gate passes the input values at controls directly to the corresponding outputs without any change and toggles the target bit if and only if all input values at controls are 1.

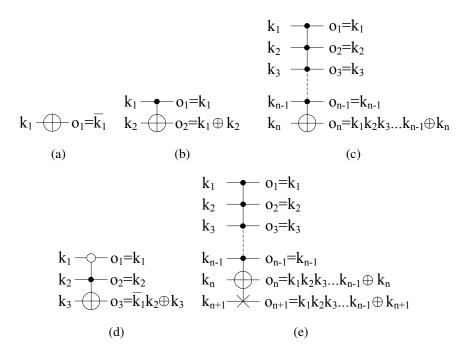

The NOT gate is a special case of a Toffoli gate with n = 1 and no controls. The 2-bit (that is, n = 2) Toffoli gate is also known as the CNOT gate or Feynman gate. A NOT gate, a CNOT gate and an *n*-bit Toffoli gate are shown in Figure 2.1(a), Figure 2.1(b) and Figure 2.1(c).

A negative-control Toffoli gate maps the input vector  $[k_1, k_2, ..., k_n]$  to the output vector  $[o_1, o_2, ..., o_n]$ , where  $o_j = k_j$  for j = 1, 2, ..., n - 1,  $o_n = \overline{k_1}k_2 \cdots k_{n-1} \oplus k_n$ ; here  $k_1$  is called a negative control. This gate may have one or more negative controls; in that case, the target bit is toggled if all positive controls have the value 1 and all negative controls have the value 0. A 3-bit Toffoli gate with a single negative control in its first input is shown in Figure 2.1(d).

The extended Toffoli gate (ETG) is a multi-target Toffoli gate proposed in [6]. In this thesis, we make use of an (n + 1)-bit ETG with two target outputs  $o_n$  and  $o_{n+1}$  as shown in Figure 2.1(e). This gate has the input vector  $[k_1, k_2, ..., k_n, k_{n+1}]$  and the output vec-

tor  $[o_1, o_2, ..., o_n, o_{n+1}]$ , where  $o_j = k_j$  for j = 1, 2, ..., n-1,  $o_n = k_1 k_2 \cdots k_{n-1} \oplus k_n$ , and  $o_{n+1} = k_1 k_2 \cdots k_{n-1} \oplus k_{n+1}$ . The first n-1 bits are controls and the last two bits are targets. Like a negative-control Toffoli gate, an ETG may have negative controls.

Figure 2.1: (a) A NOT gate, (b) A CNOT gate, (c) an *n*-bit Toffoli gate, (d) a 3-bit negativecontrol Toffoli gate, and (e) an (n+1)-bit ETG.

| $k_1$ | $k_2$ | $k_3$ | <i>o</i> <sub>1</sub> | <i>o</i> <sub>2</sub> | 03 |

|-------|-------|-------|-----------------------|-----------------------|----|

| 0     | 0     | 0     | 0                     | 0                     | 0  |

| 0     | 0     | 1     | 0                     | 0                     | 1  |

| 0     | 1     | 0     | 0                     | 1                     | 0  |

| 0     | 1     | 1     | 0                     | 1                     | 1  |

| 1     | 0     | 0     | 1                     | 0                     | 0  |

| 1     | 0     | 1     | 1                     | 0                     | 1  |

| 1     | 1     | 0     | 1                     | 1                     | 1  |

| 1     | 1     | 1     | 1                     | 1                     | 0  |

Table 2.3: Truth table of the 3-bit Toffoli gate.

The *n*-bit (n > 2) Toffoli gates including the negative-control Toffoli gates and ETGs are universal. For example, a 3-bit Toffoli gate has the mapping from  $[k_1, k_2, k_3]$  to  $[o_1 = k_1, o_2 = k_2, o_3 = k_1k_2 \oplus k_3]$ . Table 2.3 shows the truth table of this gate. When  $k_3 = 1$ , we

get  $(\overline{k_1k_2})$  which is the NAND operation of two inputs  $k_1$  and  $k_2$ . Since the NAND gate is universal and the 3-bit Toffoli gate can work like a NAND gate, it is also universal.

#### 2.3.2 Fredkin Gates

An *n*-bit Fredkin gate is a reversible logic gate that has *n* inputs and *n* outputs and that maps the input vector  $[k_1, k_2, ..., k_n]$  to the output vector  $[o_1, o_2, ..., o_n]$ , where  $o_j = k_j$  for  $j = 1, 2, ..., n-2, o_{n-1} = (\overline{k_1 k_2 \cdots k_{n-2}})k_{n-1} + k_1 k_2 \cdots k_{n-2} k_n$ , and  $o_n = (\overline{k_1 k_2 \cdots k_{n-2}})k_n + k_1 k_2 \cdots k_{n-2} k_{n-1}$ . In other words, the first n-2 input values are passed directly to the corresponding outputs without any change, and the last two inputs are swapped if and only if all the first n-2 inputs are 1. The 2-bit (that is, n = 2) Fredkin gate is also known as the swap gate.

Like the Toffoli gates, the Fredkin gates with n > 2 are also universal. A 3-bit Fredkin gate has the input vector  $[k_1, k_2, k_3]$  and the output vector  $[o_1 = k_1, o_2 = \overline{k}_1 k_2 + k_1 k_3, o_3 = \overline{k}_1 k_3 + k_1 k_2]$ . Its truth table is given in Table 2.4. By setting  $k_3 = 1$ , the OR operation of two inputs  $k_1$  and  $k_2$  can be realized from  $o_2$ .

| $k_1$ | $k_2$ | $k_3$ | <i>o</i> <sub>1</sub> | <i>o</i> <sub>2</sub> | 03 |

|-------|-------|-------|-----------------------|-----------------------|----|

| 0     | 0     | 0     | 0                     | 0                     | 0  |

| 0     | 0     | 1     | 0                     | 0                     | 1  |

| 0     | 1     | 0     | 0                     | 1                     | 0  |

| 0     | 1     | 1     | 0                     | 1                     | 1  |

| 1     | 0     | 0     | 1                     | 0                     | 0  |

| 1     | 0     | 1     | 1                     | 1                     | 0  |

| 1     | 1     | 0     | 1                     | 0                     | 1  |

| 1     | 1     | 1     | 1                     | 1                     | 1  |

Table 2.4: Truth table of the 3-bit Fredkin gate.

#### 2.4 Reversible Circuit

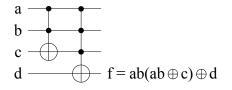

A reversible circuit consists of only reversible gates which are interconnected without fanout and feedback [49]. The fan-out refers to the maximum number of inputs that can be driven from one output of a gate. In a reversible circuit, the fan-out of a gate is at most one. If a reversible circuit is built using only Toffoli gates including NOT gates, CNOT gates and negative-control Toffoli gates, it is known as a Toffoli circuit. Figure 2.2 shows a Toffoli circuit where the three outputs of the 3-bit Toffoli gate are connected to the first three inputs of the 4-bit Toffoli gate. This circuit computes  $f = ab(ab \oplus c) \oplus d$ . It is noted that each of the three outputs of the first gate is connected to only one of the inputs of the second gate. Thus the first gate has a fan-out of 1.

Figure 2.2: A Toffoli circuit.

#### 2.5 Cost Metrics

A given function can be synthesized by several ways (see Section 2.6), resulting in different reversible circuits. This section outlines three cost metrics which are used to evaluate and compare different circuits realizing the same function.

## 2.5.1 Gate Count

Gate count is the simplest way to compare and evaluate different reversible circuits. It refers to the number of gates required to implement the circuit. It simply counts gates but

does not take into account the complexity of the gates. As a result, it can usefully compare different circuits only if the functionality (type) of the gates and the number of bits in the gates used in circuits are similar [36]. For example, consider two circuits where the first circuit consists of three 2-bit Toffoli gates and the second circuit consists of two 10-bit Toffoli gates. According to this measure, the second circuit is better. However, a 10-bit Toffoli gate is more complex than a 2-bit Toffoli gate. Since gates have different numbers of bits, this simple measure fails to provide meaningful information. Similarly, it cannot accurately evaluate circuits if one circuit contains only Toffoli gates and the other circuit contains both Toffoli and Fredkin gates.

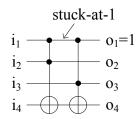

#### 2.5.2 Garbage Output

In reversible circuits, some outputs are required to maintain the reversibility property but do not behave as final results, nor are they used for further calculations. Such outputs are called garbage outputs. For example, a CNOT gate can be used to realize an EXOR operation as shown in Figure 2.3. The second output is  $o_2 = k_1 \oplus k_2$ , whereas the first output  $o_1 = k_1$  is a garbage output. Thus a circuit for generating an EXOR function with a CNOT gate produces a garbage output.

$$k_1 \rightarrow o_1 = k_1$$

(garbage output)

$k_2 \rightarrow o_2 = k_1 \oplus k_2$

Figure 2.3: Garbage output in a reversible circuit.

Garbage outputs increase the number of lines<sup>1</sup> in a circuit and hence increase the width of the circuit. For some circuits, however, it is impossible to remove all the garbage outputs. It is more important to reduce the garbage outputs than the number of gates [26, 53]. Thus

<sup>&</sup>lt;sup>1</sup>We refer to bits in reversible circuits as lines in this thesis. The correct term in quantum computing is qubits.

a challenging task in designing a reversible circuit is to minimize the number of required garbage outputs.

#### 2.5.3 Quantum Cost

The quantum cost is a very popular measure to compare reversible circuits. According to Maslov and Dueck [26], the quantum cost of a gate is defined as the number of basic quantum operations needed to realize the gate. Any reversible gate can be decomposed into basic quantum gates. The number of basic quantum gates is the quantum cost.

The quantum cost calculation of an *n*-bit Toffoli gate is presented in [4], and improved in [25] by adding CNOT gates, and further improved in [23] by applying templates [30]. The quantum costs of the NOT gate, CNOT (2-bit Toffoli) gate, and 3-bit Toffoli gate are 1, 1, and 5, respectively. The number of bits in a Toffoli gate increases the quantum cost. For example, a 4-bit Toffoli gate has a cost of 13, whereas a 6-bit Toffoli gate has a cost of up to 61 [23]. If the number of lines in a circuit is greater than the number of bits in the Toffoli gate, then the extra (garbage) lines can help reduce the cost of the gate. For example, the cost of a 6-bit Toffoli gate is 52 if one garbage line is used, but is reduced to 38 if three garbage lines are used [23].

The costs of an *n*-bit Toffoli gate and an *n*-bit negative-control Toffoli gate with at least one positive control are exactly the same [2]. However, for an *n*-bit negative-control Toffoli gate with all negative controls, an extra cost of 2 is required if either zero garbage lines are used [2] or (n-3) garbage lines are used [28, 2]. An additional cost of 4 is required if only one garbage line is used [28, 2].

The quantum costs for the Toffoli gates are given in Table 2.5. The first column indicates the number of bits in the Toffoli gates. The second column shows the number of garbage lines used to realize the gates. The third and fourth columns give the quantum costs for Toffoli gates with all positive and all negative controls, respectively. The first three columns are extracted from [23], while the last column is obtained based on the analysis given in [28, 2].

| Number        |              | Quantum Cost      |                   |  |

|---------------|--------------|-------------------|-------------------|--|

| of bits       | Garbage      | with all positive | with all negative |  |

| n             |              | controls          | controls          |  |

| 1             | 0            | 1*                | 1*                |  |

| 2             | 0            | 1                 | 3                 |  |

| 3             | 0            | 5                 | 6                 |  |

| 4             | 0            | 13                | 15                |  |

| 5             | 0            | 29                | 31                |  |

| 5             | 2            | 26                | 28                |  |

| 6             | 0            | 61                | 63                |  |

| 6             | 1            | 52                | 56                |  |

| 6             | 3            | 38                | 40                |  |

| 7             | 0            | 125               | 127               |  |

| 7             | 1            | 80                | 84                |  |

| 7             | 4            | 50                | 52                |  |

| 8             | 0            | 253               | 255               |  |

| 8             | 1            | 100               | 104               |  |

| 8             | 5            | 62                | 64                |  |

| 9             | 0            | 509               | 511               |  |

| 9             | 1            | 128               | 132               |  |

| 9             | 6            | 74                | 76                |  |

| 10            | 0            | 1021              | 1023              |  |

| 10            | 1            | 152               | 156               |  |

| 10            | 7            | 86                | 88                |  |

| n > 10        | 0            | $2^{n}-3$         | $2^{n} - 1$       |  |

| <i>n</i> > 10 | 1            | 24n - 88          | 24n - 84          |  |

| n > 10        | <i>n</i> – 3 | 12n - 34          | 12n - 32          |  |

Table 2.5: Costs of *n*-bit Toffoli gates.

\* 1-bit Toffoli gate (NOT gate) has no control.

The cost of an (n + 1)-bit ETG is two plus the cost of an *n*-bit Toffoli gate, since it can be simulated by an *n*-bit Toffoli gate and two CNOTs. Similarly, an (n + 1)-bit negativecontrol ETG has the cost of two plus the cost of an *n*-bit negative-control Toffoli gate. As given in [23], the cost of an *n*-bit Fredkin gate is computed as the cost of an *n*-bit Toffoli gate plus two. We have discussed the quantum costs of different Toffoli and Fredkin gates. To calculate the quantum cost of a reversible circuit, we sum the quantum costs of the gates used in the circuit. As described in [36], comparisons in terms of gate count are not meaningful if the reversible gates used in circuits have different functionalities and/or numbers of bits. The quantum cost is a good cost metric in this regard since it counts the number of elementary (quantum) gates required for the circuit.

### 2.6 Synthesis Approaches of Reversible Logic

There are a number of different approaches for synthesis of reversible logic circuits, including the transformation-based approach [33], the use of positive polarity Reed-Muller expressions (PPRM) [11], the use of ESOP expressions [9, 45], and the decision diagrambased approach [57].

#### 2.6.1 Transformation-based Synthesis

The transformation-based approach proposed in [33] involves examination of a truth table of a given reversible function, and identifies transformations that can be applied to the output side of the truth table to match the input and output patterns. The application of these transformations then can be translated into a cascade of gates; if the transformations are restricted to only those corresponding to Toffoli gates, then the resulting cascade will similarly consist only of Toffoli gates.

An improvement of the above approach is the bi-directional approach [33] which applies transformations both at the input side and output side of the truth table, resulting in a smaller number of gates in the circuit.