| http://opus.uleth.ca |

|----------------------|

|                      |

Theses Arts and Science, Faculty of

2005

## Design of a novel hybrid cryptographic processor

## Li, Jianzhou

Lethbridge, Alta.: University of Lethbridge, Faculty of Arts and Science, 2005

http://hdl.handle.net/10133/266

Downloaded from University of Lethbridge Research Repository, OPUS

# DESIGN OF A NOVEL HYBRID CRYPTOGRAPHIC PROCESSOR

Jianzhou Li ME., Hunan University, 2002

## A Thesis

Submitted to the School of Graduate Studies

of the University of Lethbridge

in Partial Fulfilment of the

Requirements for the Degree

MASTER OF SCIENCE

Department of Mathematics and Computer Science

University of Lethbridge

LETHBRIDGE, ALBERTA, CANADA

©Jianzhou Li, 2005

## Abstract

A new multiplier that supports fields GF(p) and  $GF(2^n)$  for the public-key cryptography, and fields  $GF(2^8)$  for the secret-key cryptography is proposed in this thesis. Based on the core multiplier and other extracted common operations, a novel hybrid crypto-processor is built which processes both public-key and secret-key cryptosystems. The corresponding instruction set is also presented. Three cryptographic algorithms: the Elliptic Curve Cryptography (ECC), AES and RC5 are focused to run in the processor.

To compute scalar multiplication kP efficiently, a blend of efficient algorithms on elliptic curves and coordinates selections and of hardware architecture that supports arithmetic operations on finite fields is required. The Nonadjacent Form (NAF) of k is used in Jacobian projective coordinates over GF(p); Montgomery scalar multiplication is utilized in projective coordinates over  $GF(2^n)$ . The dual-field multiplier is used to support multiplications over GF(p) and  $GF(2^n)$  according to multiple-precision Montgomery multiplication algorithms. The design ideas for AES and RC5 are also described.

The proposed hybrid crypto-processor increases the flexibility of security schemes and reduces the total cost of cryptosystems.

## Acknowledgments

I would like to express many thanks to my supervisor Dr. Hua Li, for his invaluable advice and ideas on the research and also for his devotion of time to me in the past two years. His support and expertise resolved many hurdles that I encountered throughout the research. I would also like to thank my co-supervisor, Dr. Jim Liu, for his kind encouragement and guidance.

I am also grateful to other committee members Dr. Jackie Rice and Dr. Rob Sutherland for their advice.

Finally, I would like thank my parents for their support of me.

## Table of Contents

| Si | gnatı | ure Pa | ge                                                       | i    |

|----|-------|--------|----------------------------------------------------------|------|

| A۱ | bstra | ct     |                                                          | ii   |

| A  | cknov | wledge | ments                                                    | iii  |

| Li | st of | Tables | 5                                                        | vii  |

| Li | st of | Figure | es                                                       | viii |

| 1  | Intr  | oducti | ion                                                      | 1    |

|    | 1.1   | Motiv  | ation                                                    | . 1  |

|    | 1.2   | Litera | ture Review                                              | . 2  |

|    |       | 1.2.1  | Hardware Speed-up of Secret-key Algorithms               | . 3  |

|    |       | 1.2.2  | Processor for Elliptic Curve Cryptography                | . 3  |

|    |       | 1.2.3  | Hardware Implementations for Both Public-key and Secret- |      |

|    |       |        | key Cryptosystems                                        | . 4  |

|    | 1.3   | Contr  | ibutions                                                 | . 5  |

|    | 1.4   | Thesis | S Outline                                                | . 5  |

| 2  | Mat   | thema  | tical Background                                         | 6    |

|    | 2.1   | Group  | os, Rings, and Fields                                    | . 6  |

|    | 22    | Finite | Fields                                                   | 8    |

|   |                             | 2.2.1 The Finite Field $GF(p)$                               | 8  |

|---|-----------------------------|--------------------------------------------------------------|----|

|   |                             | 2.2.2 The Finite Field $GF(2^n)$                             | 8  |

|   | 2.3                         | Summary                                                      | 1  |

| 3 | $\mathbf{Cry}_{\mathbf{j}}$ | ptography 1                                                  | 3  |

|   | 3.1                         | Terminology                                                  | 3  |

|   | 3.2                         | Secret-key System                                            | .4 |

|   | 3.3                         | Public-key System                                            | 5  |

|   | 3.4                         | Elliptic Curve Cryptography (ECC)                            | 7  |

|   | 3.5                         | Elliptic Curves over Finite Fields                           | 8. |

|   |                             | 3.5.1 Elliptic Curves over $GF(p)$                           | 8. |

|   |                             | 3.5.2 Elliptic Curves over $GF(2^n)$                         | 9  |

|   | 3.6                         | ECC Domain Parameters                                        | 20 |

|   | 3.7                         | Key Generation                                               | 21 |

|   | 3.8                         | Elliptic Curve Protocols                                     | 21 |

|   | 3.9                         | AES Algorithm                                                | 22 |

|   | 3.10                        | RC5 Algorithm                                                | 25 |

|   | 3.11                        | Comparison between Public-key and Secret-key Cryptosystems 2 | 27 |

|   | 3.12                        | Summary                                                      | 27 |

| 4 | $\mathbf{The}$              | Cryptographic Processor Architecture                         | 9  |

|   | 4.1                         | Coordinate Representation of Elliptic Curves over $GF(p)$    | 31 |

|   | 4.2                         | Elliptic Scalar Multiplication over $GF(p)$                  | 32 |

|   | 4.3                         | Elliptic Scalar Multiplication over $GF(2^n)$                | 34 |

|   | 4.4                         | Montgomery Multiplication                                    | 37 |

|   |                             | 4.4.1 Montgomery Multiplication over $GF(p)$                 | 37 |

|   |                             | 4.4.2 Montgomery Multiplication over $GF(2^n)$               | 11 |

|   | 4.5                         | Architecture of the Hybrid Processor                         | 14 |

|   |                             | 4.5.1 Data Path                                              | 15 |

|    |       | 4.5.2 Multiplier Design                              | 16 |

|----|-------|------------------------------------------------------|----|

|    |       | 1.5.3 Barrel Shifter                                 | 52 |

|    |       | 1.5.4 Adder/Subtracter                               | 53 |

|    |       | 1.5.5 Instruction Set                                | 53 |

|    | 4.6   | Performance Evaluation                               | 55 |

|    | 4.7   | Performance Comparison                               | 56 |

|    | 4.8   | Future Improvement                                   | 58 |

| 5  | Con   | lusions and Future Work                              | 31 |

|    | 5.1   | Conclusions                                          | 31 |

|    | 5.2   | Future Work                                          | 32 |

| Bi | bliog | aphy                                                 | 33 |

| A  | Par   | of Verliog HDL codes                                 | 70 |

|    | A.1   | Verilog HDL codes for multiplier                     | 70 |

|    | Δ 2   | Verilog HDL codes for the data path of the processor | 84 |

## List of Tables

| 2.1  | Properties of modular arithmetic operations in $GF(p)$      | 9          |

|------|-------------------------------------------------------------|------------|

| 4.1  | Projective coordinate representations over $GF(p)$          | 31         |

| 4.2  | Left-to-right NAF                                           | 34         |

| 4.3  | The core components in different cryptographic algorithms   | 45         |

| 4.4  | Instruction set                                             | <b>5</b> 4 |

| 4.5  | Codes for RC5                                               | 55         |

| 4.6  | Codes for Montgomery multiplication over $GF(p)$            | 56         |

| 4.7  | Usage of FPGA resources                                     | 56         |

| 4.8  | The performance for different cryptosystems                 | 57         |

| 4.9  | The performance comparison for RC5                          | 57         |

| 4.10 | The performance comparison for AES                          | 57         |

| 4.11 | The scalar multiplication comparison for ECC over $GF(2^n)$ | 58         |

| 4.12 | The hardware comparison for ECC over $GF(2^n)$              | 58         |

| 4.13 | The performance comparison for ECC over $GF(p)$             | 58         |

| 4.14 | Instruction set using pipeline technique                    | 59         |

| 1 15 | Codes for AFS                                               | 60         |

# List of Figures

| 3.1 | Model of secret-key cryptosystem                                     | 14 |

|-----|----------------------------------------------------------------------|----|

| 3.2 | Model of public-key cryptosystem                                     | 16 |

| 3.3 | ShiftRows operation for encryption in AES algorithm                  | 23 |

| 3.4 | AES algorithm flow for encryption/decryption                         | 24 |

| 4.1 | Hardware speeding-up of NAF                                          | 33 |

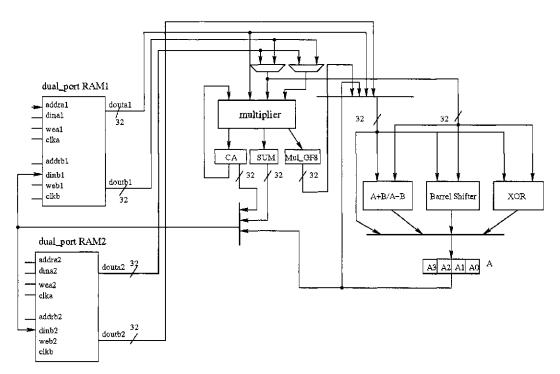

| 4.2 | The data path of the architecture: 32-bit part                       | 47 |

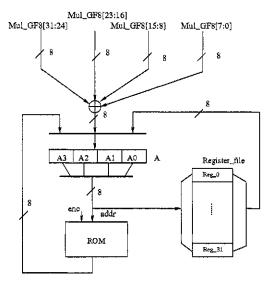

| 4.3 | The data path of the architecture: eight-bit part                    | 48 |

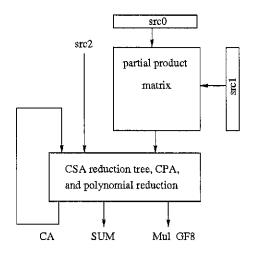

| 4.4 | The block diagram of multiple-precision multifunction multiplier     | 49 |

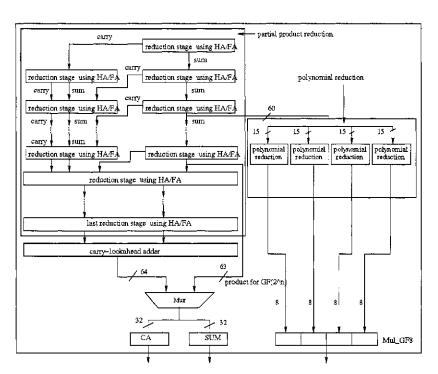

| 4.5 | Partial product reduction, CPA and polynomial reduction              | 50 |

| 4.6 | The dot diagram for partial product matrix of $32-bit \times 32-bit$ |    |

|     | multiplication                                                       | 51 |

| 4.7 | Example of an 8-bit barrel shifter                                   | 52 |

| 4.8 | Adder/subtracter                                                     | 53 |

## Chapter 1

## Introduction

#### 1.1 Motivation

The electronic world is increasingly influencing our lives. Every day hundreds of thousands of people interact electronically through e-mail, e-commerce (business conducted over the Internet), ATM machines, or cellular phones. This has led to an increased reliance on the security of information transmitted electronically. By far the most effective ways to ensure network and communication security are related to cryptography. Cryptography is the study of mathematical techniques related to aspects of information security such as confidentiality, data integrity, entity authentication, and data origin authentication. Cryptography is not the only means of providing information security, but rather a set of techniques [30]. Two types of cryptographic tools are commonly used: secret-key cryptography and public-key cryptography. For secret-key cryptography, RC5 and AES are two widely used important algorithms, while for public-key cryptography, the vast majority of the products and standards use RSA algorithm based on the integer factorization. Elliptic curve cryptography (ECC) is another approach to public-key cryptography based on the mathematics of elliptic curves. The primary advantage of elliptic curve cryptosystems over RSA is the absence of a sub-exponential-time algorithm that could solve the discrete logarithm problem (DLP) in the elliptic curve groups

CHAPTER 1 INTRODUCTION

[5]. Consequently, ECC can maintain the same level of security with a far smaller key size, therefore reducing processing overhead.

It is necessary to implement cryptographic algorithms in hardware due to the fact that software implementations are too slow to satisfy the real-time requirement. For efficiency reasons, usually hybrid encryption systems are used in practice; a key is exchanged using a public-key cipher, and the rest of the communication is encrypted using a symmetric-key algorithm (which is typically much faster). So it is necessary to design a chip that performs hybrid encryption systems for the user's convenience. Many hardware implementations of cryptosystems have been proposed to speed up the throughput while keeping the circuit area as small as possible. These designs can utilize the hardware resources and customize the architecture to maximize the efficiency of the implementations. However, most of the designs are dedicated to specific cryptographic algorithms. For example, many chips that only can perform AES algorithms have been discussed for secret-key cryptosystems, while others are proposed to speed up the public-key cryptosystems. Very little of the literature deals with hardware designs to implement both secret-key and public-key cryptosystems. A crypto-processor in [18] can perform secret-key algorithms AES and triple-DES, and public-key algorithms RSA and ECC. However, it uses dedicated coprocessor blocks for each algorithm, which consumes lots of hardware area. Also, it can only perform ECC over specific binary field  $GF(2^{146})$ . In this thesis, a processor that can flexibly deal with both secret-key algorithms for AES and RC5 and publickey algorithms for ECC over fields GF(p) and  $GF(2^n)$  with variable parameters is proposed.

#### 1.2 Literature Review

Many hardware implementations on Field-Programmable Gate Array (FPGA) and Application-Specific Integrated Circuit (ASIC) have been presented for elliptic curve

CHAPTER 1 INTRODUCTION

cryptosystems and for AES and RC5, respectively. A review of the previous work is given in this section.

#### 1.2.1 Hardware Speed-up of Secret-key Algorithms

Due to the simple computation compared with public-key cryptography and dedication to specific secret-key algorithm, chip designs used in the hardware speed-up of secret-key cryptography are much simpler. Since the invention of AES, many efficient hardware implementations on FPGA or ASIC are presented [50, 53, 29, 6, 24, 25]. References [26, 46] propose hardware architectures for the RC5 block cipher.

However there is little literature that deals with hardware implementations on several secret-key algorithms in one chip. A bulk encryption crypto-processor dedicated to smart cards was designed which could perform DES and 3DES algorithms [47].

#### 1.2.2 Processor for Elliptic Curve Cryptography

Many hardware implementations on elliptic curve cryptography have been proposed [2, 23, 10, 38, 36, 11, 39, 37, 4, 44, 12, 43, 9]. Binary field  $GF(2^n)$  arithmetic is more suitable for fast and compact hardware than a prime field GF(p), because elements over  $GF(2^n)$  are unsigned binary numbers and there is no need for carry propagation. However, conventional implementations for ECC over  $GF(2^n)$  have little flexibility due to dedicated field parameters. Some designs [2, 23, 10] are based on the fixed size Massey-Omura multiplier [37] using optimal normal bases. Some [38, 36] are based on the specific polynomial bases. On the other hand, conventional ECC hardware designs over GF(p) [38] support only the specific prime numbers. So the restrictions of the conventional approaches reduce the flexibility of hardware implementations and limit the application areas.

The Montgomery multiplication algorithm [32, 21] proposed by P.L Montgomery

Chapter 1 Introduction

in 1985 was for modular multiplication over GF(p) to avoid expensive division computation. The algorithm was then extended to binary field  $GF(2^n)$  [22]. This provides the guidance to unify the fields GF(p) and  $GF(2^n)$  into one computation component. Several contributions based on dual-field multipliers have been made to support field arithmetic on both GF(p) and  $GF(2^n)$ . One hardware architecture that uses carry-save adders to perform on dual-field operations is introduced in [44]. Processors based on a fully parallel multiplier that supports dual-field operations are presented in [43, 9], where n-bit operands need to be divided into m w-bit (word size) words to perform multiple-precision operations. This further provides the flexibility to accommodate elliptic curves with different key lengths.

## 1.2.3 Hardware Implementations for Both Public-key and Secret-key Cryptosystems

To our knowledge, very few hardware implementations of both public-key and secret-key cryptosystems exist. Reference [18] presents a crypto-processor that can perform secret-key algorithms AES and triple-DES, and public-key algorithms RSA and ECC. However, its design uses dedicated coprocessor blocks for each algorithm, which consumes lots of hardware area. Also, it can only perform ECC over specific binary field  $GF(2^{146})$ .

This section summarizes the previous hardware implementations of secret-key and public-key cryptosystems. They primarily focus on the specific algorithm or specific elliptic curve, thereby lacking certain flexibility. The processor based on a parallel dual-field multiplier makes it possible to perform elliptic curve cryptography on both GF(p) and  $GF(2^n)$  with variable parameters. However, the author is aware of very few hardware designs that implement algorithms for both secret-key and public-key systems.

CHAPTER 1 INTRODUCTION

#### 1.3 Contributions

The thesis presents a novel hybrid crypto-processor that can process not only publickey cryptography, such as ECC over GF(p) and  $GF(2^n)$  with random key length, but also secret-key algorithms, such as AES and RC5. The main contributions of my thesis are as follows.

- 1. The multiplier designed in this thesis is a novel 32-bit by 32-bit multiplication-accumulator that integrates multiplications over GF(p),  $GF(2^n)$  used in public-key cryptosystem and  $GF(2^8)$  used in secret-key cryptosystem.

- 2. Unlike previous work, the hybrid crypto-processor in this thesis has more flexibility that can perform not only public-key algorithms such ECC over fields GF(p) and  $GF(2^n)$ , but also secret-key algorithms AES and RC5.

- 3. The prime number p over GF(p) and the irreducible polynomial over  $GF(2^n)$  can easily be changed to improve the security of the processor.

#### 1.4 Thesis Outline

Chapter 2 introduces basic mathematical background which serves as the basis for discussions in later chapters.

In chapter 3, an introduction to cryptography is presented which includes secretkey and public-key cryptosystems.

Chapter 4 describes the architecture of the proposed processor and the implementation details of ECC, AES and RC5. The core arithmetic component such as multi-function multiplier and barrel shifter are presented. The related algorithms used for the ECC design are discussed. Finally, the performance analysis and comparison with previous work are made.

Conclusions and possible future work are given in Chapter 5.

## Chapter 2

## Mathematical Background

Cryptographic algorithms rely heavily on the base of mathematics. For example, the Advanced Encryption Standard (AES) and Elliptic Curve Cryptography (ECC) are built on properties of finite fields. In this chapter, we review some necessary mathematical background in abstract algebra, in particular finite fields, which are relevant to the work in this thesis.

## 2.1 Groups, Rings, and Fields

A group (G, \*) is a set together with a binary operation \* (called the multiplication) on G such that

- 1. Closure:  $g_1 * g_2 \in G$  for all  $g_1, g_2 \in G$ ;

- 2. Associative:  $g_1 * (g_2 * g_3) = (g_1 * g_2) * g_3$  for all  $g_1, g_2, g_3 \in G$ ;

- 3. Identity element: there is an element  $e \in G$  such that g \* e = e \* g for all  $g \in G$ ;

- 4. Inverse element: for each element  $g \in G$ , there exists an element g' such that g \* g' = g' \* g = e.

The element e is called the identity of the group G. The element g' is called the inverse of g, usually denoted by  $g^{-1}$ .

A group G is said to be abelian or commutative if  $g_1 * g_2 = g_2 * g_1$  for all  $g_1$ ,  $g_2 \in G$ . When G is an abelian group, the operation \* is denoted by +, which is called the addition. The identity element e is denoted by 0, which is called the zero element. The inverse of  $g \in G$  is denoted by -g, which is called the negative of g.

A ring  $(R, +, \times)$  is an nonempty set R with two binary operations + and  $\times$ , called addition and multiplication, such that

- 1. (R, +) is an abelian group.

- 2. Closure under multiplication:  $r_1 \times r_2 \in R$  for all  $r_1, r_2 \in R$ ;

- 3. Associative under multiplication:  $r_1 \times (r_2 \times r_3) = (r_1 \times r_2) \times r_3$  for all  $r_1, r_2, r_3 \in R$ ;

- 4. Multiplication is distributive over addition:  $r_1 \times (r_2 + r_3) = r_1 \times r_2 + r_1 \times r_3$  and  $(r_1 + r_2) \times r_3 = r_1 \times r_3 + r_2 \times r_3$  for all  $r_1, r_2, r_3 \in R$ .

A ring R is said to be a commutative ring if  $r_1 \times r_2 = r_2 \times r_1$  for all  $r_1, r_2 \in R$ .

A field  $(F, +, \times)$  is a set with two binary operations, called addition and multiplication, such that

- 1.  $(F, +, \times)$  is a commutative ring

- 2. Multiplicative identity: There exists an element 1 such that  $a \times 1 = 1 \times a = a$  for all  $a \in F$

- 3. No zero divisors: If  $a, b \in F$  and  $a \times b = 0$ , then a = 0 or b = 0;

- 4. Multiplicative inverse: For  $a \in F$  and  $a \neq 0$ , there exists an element  $a^{-1} \in F$  such that  $a \times a^{-1} = a^{-1} \times a = 1$

A ring  $(R, +, \times)$  is said to be an integral domain if it is a commutative ring with multiplicative identity and it contains no zero-divisors. A field is a set on which one can perform addition, subtraction, multiplication, and division. For this work, we

are only interested in fields with finite numbers of elements, which are called finite fields. More details about abstract algebra can be found in [13].

### 2.2 Finite Fields

A finite field  $(F, +, \times)$  [49, 14] consists of a finite set of elements. The number of elements q in the field is called the order of F. It can be shown that there exists a finite field of order q if and only if q is a prime power  $p^n$ , where n is a positive integer and p is a prime number. There is essentially only one finite field of order  $q = p^n$ , denoted by  $GF(q) = GF(p^n)$ . Here p is called the characteristics of  $GF(p^n)$  and p is called the extension degree. We are especially interested in two cases. For p = 1, and p = p ( $p \neq 2$ ), we have p = 2, and p = 2, we have p = 2.

#### **2.2.1** The Finite Field GF(p)

The finite field GF(p), where p is an odd prime, also called a prime finite field, is defined as the set of integers  $\{0, 1, \ldots, p-1\}$ , together with the modular arithmetic operations. Since GF(p) is a field, it should satisfy the conditions mentioned in Section 2.1. Table 2.1 lists the properties of modular arithmetic operations in GF(p).

#### **2.2.2** The Finite Field $GF(2^n)$

The finite field  $GF(2^n)$ , also called a binary finite field, can be viewed as a vector space of dimension n over GF(2). There exist n elements  $\{\alpha_0, \alpha_1, \ldots, \alpha_{n-1}\}$  such that for each element  $a \in GF(2^n)$ , a can be written uniquely as:

```

a=a_0\alpha_0+a_1\alpha_1+\ldots+a_{n-1}\alpha_{n-1}, where a_i \in \{0, 1\}

```

The set  $\{\alpha_0, \alpha_1, \ldots, \alpha_{n-1}\}$  is called a basis of  $GF(2^n)$  over GF(2). Given such a basis, an element a can also be represented as the bit string  $(a_0, a_1, \ldots, a_{n-1})$ .

Polynomial basis and normal basis are two kinds of commonly used bases (see Johnson et al [15] for more details).

|                                 | Y                                                                     |

|---------------------------------|-----------------------------------------------------------------------|

| Commutative laws                | $(w+x) \pmod{p} = (x+w) \pmod{p}$                                     |

|                                 | $(w \times x) \pmod{p} = (x \times w) \pmod{p}$                       |

| Associative laws                | $[(w+x) + y] \pmod{p} = [w + (x+y)] \pmod{p}$                         |

|                                 | $[(w \times x) \times y] \pmod{p} = [w \times (x \times y)] \pmod{p}$ |

| Distributive laws               | $[w \times (x+y)] \pmod{p} = [(w \times x) + (w \times y)] \pmod{p}$  |

|                                 | $[(x+y)\times w] \pmod{p} = [(x\times w) + (y\times w)] \pmod{p}$     |

| Identities                      | $(0+w) \pmod{p} = w \pmod{p}$                                         |

|                                 | $(1 \times w) \pmod{p} = w \pmod{p}$                                  |

| Additive inverse $(-w)$         | For each $w \in GF(p)$ ,                                              |

|                                 | there exists a z such that $w + z = 0 \pmod{p}$                       |

| Multiplicative inverse $w^{-1}$ | For each non-zero $w \in GF(p)$ ,                                     |

|                                 | there exists a value $a$ such that $a \times w = 1 \pmod{p}$          |

Table 2.1: Properties of modular arithmetic operations in GF(p)

#### Polynomial Basis

The finite field  $GF(2^n)$  can also be viewed as a set of polynomials over GF(2), together with polynomial arithmetics. The polynomials are defined modulo an irreducible polynomial f(x) whose highest power is integer n-1. A polynomial f(x) over field GF(2) is called irreducible if and only if f(x) cannot be factored as a product of polynomials in GF(2), with each highest degree less than n. An irreducible polynomial f(x) is also called a prime polynomial by analogy to primes in GF(p). Each f(x) defines a polynomial basis representation of  $GF(2^n)$ . The  $GF(2^n)$  can be expressed in the following form after the irreducible polynomial is determined:

$$GF(2^n) = \{a_{n-1}x^{n-1} + a_{n-2}x^{n-2} + \dots + a_1x + a_0 | a_i \in \{0, 1\}\},$$

or in the bit string form:

$$GF(2^n) = \{(a_{n-1}a_{n-2} \dots a_1a_0) | a_i \in \{0, 1\}\}.$$

The arithmetic operations on the elements in  $GF(2^n)$  are as follows.

- Additive identity is represented as (00...00).

- Multiplicative identity is represented as (00 ...01).

- Addition: Due to the coefficient over GF(2), the addition operation is bitwise

exclusive OR. Suppose  $a=(a_{n-1}a_{n-2}\ldots a_0)$  and  $b=(b_{n-1}b_{n-2}\ldots b_0)$  are elements of  $GF(2^n)$ , then  $a+b=c=(c_{n-1}c_{n-2}\ldots c_0)$ , where  $c_i=a_i\oplus b_i$ ,  $i=0,\ldots,n-1$ .

- Multiplication: Suppose  $a=(a_{n-1}a_{n-2}\dots a_0)$  and  $b=(b_{n-1}b_{n-2}\dots b_0)$  are elements in  $GF(2^n)$  and  $f(x)=f_{n-1}x^{n-1}+f_{n-2}x^{n-2}+\dots+f_1x+f_0$  is the irreducible polynomial, then the product  $r=(r_{n-1}r_{n-2}\dots r_0)=a\times b$  (mod f(x)).

- Inversion: Suppose  $a=(a_{n-1}a_{n-2}\dots a_0)$  is a nonzero element in  $GF(2^n)$ , then there exits a unique element  $c=(c_{n-1}c_{n-2}\dots c_0)$  to satisfy  $c\times a=1$  mod f(x).

#### Normal Basis

A normal basis of  $GF(2^n)$  is a basis of the form  $\{\beta, \beta^2, \beta^{2^2}, \ldots, \beta^{2^{n-1}}\}$ , where  $\beta \in GF(2^n)$ . The  $GF(2^n)$  can be expressed in the following form after a normal basis is determined:

$$GF(2^n) = \{a_0\beta + a_1\beta^1 + \dots + a_{n-2}\beta^{2^{n-2}} + a_{n-1}\beta^{2^{n-1}} | a_i \in \{0, 1\}\},$$

or in the bit string form:

$$GF(2^n) = \{(a_0a_1 \dots a_{n-2}a_{n-1}) | a_i \in \{0,1\}\}.$$

The arithmetic operations on the elements of  $GF(2^n)$  are described in the following.

- Additive identity is represented as (00...00).

- Multiplicative identity is represented as (11 ... 11).

- Addition: Due to the coefficients over GF(2), the addition operation is bitwise exclusive OR. Suppose  $a=(a_0a_1\ldots a_{n-1})$  and  $b=(b_0b_1\ldots b_{n-1})$  are elements of  $GF(2^n)$ , then  $a+b=c=(c_0\ c_1\ldots c_{n-1}),\ c_i=a_i\oplus b_i,\ i=0,\ldots,n-1.$

- Multiplication: Suppose  $a = (a_0 a_1 \dots a_{n-1})$  and  $b = (b_0 b_1 \dots b_{n-1})$  are elements of  $GF(2^n)$ , then

CHAPTER 2

$$c = a \times b = \left(\sum_{i=0}^{n-1} a_i \beta^{2^i}\right) \times \left(\sum_{i=0}^{n-1} b_i \beta^{2^i}\right)$$

=  $\sum_{i=0}^{n-1} \sum_{j=0}^{n-1} a_i b_j \beta^{2^i} \beta^{2^j} = \sum_{k=0}^{n-1} c_k \beta^{2^k}$ .

We can write

$$\beta^{2^i}\beta^{2^j} = \sum_{k=0}^{n-1} \lambda_{i,j}^{(k)}\beta^{2^k}$$

Substitution yields

$$c_k = \sum_{i=0}^{n-1} \sum_{j=0}^{n-1} a_i b_j \lambda_{i,j}^{(k)}$$

(2.1)

- Squaring: Suppose  $a = (a_0 a_1 \dots a_{n-1})$  is an element of  $GF(2^n)$ , then  $a^2 = (\sum_{i=0}^{n-1} a_i \beta^{2^i})^2 = \sum_{i=0}^{n-1} a_i (\beta^{2^i})^2 = \sum_{i=0}^{n-1} a_i \beta^{2^{i+1}} = \sum_{i=0}^{n-1} a_{i-1} \beta^{2^i}$ . The squaring is also represented in the string binary form:  $(a_0 a_1 a_2 \dots a_{n-1})^2 = (a_{n-1} a_0 a_1 \dots a_{n-2})$ .

- Inversion: Suppose  $a=(a_0a_1\ldots a_{n-1})$  is a nonzero element of  $GF(2^n)$ , then there exists a unique element  $c=(c_0c_1\ldots c_{n-1})$  to satisfy  $c\times a=1$ .

In normal basis representation, the squaring operation is only the simple left circular shift. However, multiplication can be cumbersome in general. For some special finite fields of  $GF(2^n)$ , there exist Optimal Normal Bases (ONB) to simplify the multiplication. An ONB [34] is one with the minimum number of nonzero terms in Equation 2.1.

## 2.3 Summary

In this chapter, the concept of finite fields is introduced. Two kinds of important finite fields GF(p) and  $GF(2^n)$  are discussed, which are the mathematical fundamental related to both public-key and secret-key cryptographic algorithms. Furthermore, the two bases representations of  $GF(2^n)$ , polynomial basis and normal basis, are explained. Even though the squaring in normal basis can be performed very efficiently, the arithmetic component for squaring is dedicated to a specific finite

#### CHAPTER 2

#### MATHEMATICAL BACKGROUND

field, which leads to lack of flexibility. Polynomial basis is chosen in this processor design, because finite fields with different parameters need to be accommodated.

## Chapter 3

## Cryptography

In this chapter, some basic terms used in cryptography are given. Two kinds of cryptosystems: the secret-key and public-key cryptosystems are discussed. The secret-key cryptographic algorithms: Advanced Encryption Standard (AES) and RC5, are introduced. Finally, details of public-key cryptographic algorithms focusing on Elliptic Curve Cryptography (ECC) are presented.

### 3.1 Terminology

Cryptography is the technique of converting data into a secret code for transmission over a public network. The original message, known as the plaintext, is converted into a coded message, called ciphertext. The process of converting from plaintext to ciphertext is called encryption, while the process of converting from ciphertext into plaintext is decryption. The theme used for encryption is called the cryptographic system or cipher. Encryption algorithms use a key, which is a binary secret number typically ranging from 40 to 256 bits in length, to control how the ciphertext is produced. At the receiving end, a key is also used to restore the plaintext. Cryptographic systems can be divided into two types according to the number of keys used. If both sender and receiver share the same key, the system is known as secret-key, symmetric-key, single-key, or conventional cryptography. Conversely, if the sender and receiver use different keys, the system is known as public-key, asymmetric-key,

or two-key cryptography. The secret-key cryptosystem can further be distinguished as block cipher and stream cipher. The block cipher processes the plaintext one block of elements at a time and produces the corresponding block of ciphertext elements. The stream cipher processes the elements of plaintext continuously and produces ciphertext one element at a time. The secret-key algorithms used in this thesis are all block ciphers.

#### 3.2 Secret-key System

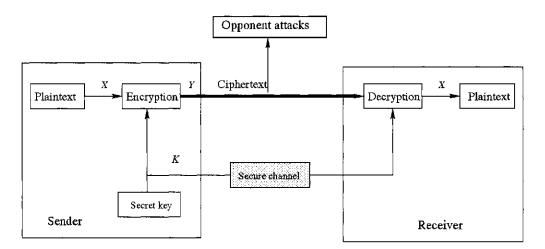

Figure 3.1: Model of secret-key cryptosystem

The model of secret-key cryptosystem shown in Fig. 3.1 gives the processes for encryption and decryption. The encryption algorithm can be written in the following form with plaintext X and secret key K as input and ciphertext Y as output.

$$Y = E_K(X) \tag{3.1}$$

From this formula we can see that the ciphertext Y is determined by both the encryption algorithm E and the key K. Similarly, the decryption inverts the transformation using the same secret key K and the corresponding decryption algorithm.

$$X = D_K(Y) \tag{3.2}$$

The security of the secret-key encryption depends on a strong encryption algorithm and the key size. The key is kept secret while the encryption algorithm is open. So the design of algorithm requires that the opponents cannot be able to decrypt ciphertext without knowing the secret key and to figure out the key even if they know a number of pairs of plaintext and ciphertext.

DES, AES and RC5 are three commonly used secret-key algorithms.

The main challenge in secret-key cryptosystems lies in how to have the sender and receiver share the secret key while keeping it secret without anyone else finding out. If the secret keys are in separate physical locations, a trusted third-party such as a courier, phone system, or some other transmission medium must be responsible for distributing the keys. The generation, transmission and storage of keys are called key management.

### 3.3 Public-key System

Whitfield Diffie and Martin Hellman introduced the concept of public-key cryptography in 1976 in order to solve the key management problem [8]. Public-key cryptosystems have two primary themes, encryption and authentication (digital signatures) as illustrated in Fig. 3.2. In the two systems, each participant gets a pair of keys, one referred to as the public key KU and the other referred to as the private key KR. The public key is published, while the private key is kept secret. The need for the sender and receiver to share secret information is eliminated; all communications involve only public keys, and no private key is ever transmitted or shared. In the encryption theme (Fig. 3.2a), the sender A uses receiver B's public key information  $KU_b$  to send confidential messages which can only be decrypted with B's private key,  $KR_b$ . This process can be expressed as follows for the sender A:

$$Y = E_{KU_h}(X) \tag{3.3}$$

Figure 3.2: Model of public-key cryptosystem

And for the receiver B, the inverted transformation is in the following formula.

$$X = D_{KR_b}(Y) \tag{3.4}$$

In the authentication theme (Fig. 3.2b), the sender A uses his or her private key  $KR_a$  to encrypt the message sent to B and B decrypts using A's public key  $KU_a$ . Because only sender A is in possession of the private key to encrypt the message X, the encrypted message Y serves as the digital signature of A. This process can be expressed as follows for the sender A:

$$Y = E_{KR_a}(X) \tag{3.5}$$

For the receiver B, the inverted transformation is given in the following formula.

$$X = D_{KU_a}(Y) \tag{3.6}$$

In a public-key cryptosystem, the private key is always linked mathematically to the public key. Therefore, it is always possible to attack a public-key system by deriving the private key from the public key. Typically, the defense against this is to make the problem of deriving the private key from the public key as difficult as possible. For instance, some public-key cryptosystems are designed such that deriving the private key from the public key requires the attacker to factor a large number. In this case it is computationally infeasible to perform the derivation. This is the idea behind the RSA public-key cryptosystem.

### 3.4 Elliptic Curve Cryptography (ECC)

The security of the public-key cryptography depends on the trap-door one-way function. A one-way function maps a domain into a range such that every function has a unique inverse with the property that it is easy to calculate in one direction and infeasible to calculate in the other direction unless certain additional information is known. This can be summarized as the following three formulas:

- 1.  $Y = f_K(X)$  easy to calculate, if key K and X are known;

- 2.  $X = f_K^{-1}(Y)$  easy to calculate, if key K and Y are known;

- 3.  $X = f_K^{-1}(Y)$  infeasible, if Y is known but K is not known.

Here the private key K is the trap-door.

Since the introduction of the public-key cryptography concept, only two cryptosystems have been invented, RSA and ECC. The RSA was published in 1978 by Rivest, Shamir and Adleman [41]. It uses exponentiation modulo a product of two large primes to encrypt and decrypt. Its security is based on the difficulty of factoring large integers. The introduction of Elliptic Curve Cryptography (ECC) independently by Neal Koblitz [19] and Victor Miller [31] in the mid' 80s has yielded a new family of analogous public-key algorithms. Although mathematically more

complex, elliptic curves appear to provide a more efficient way to leverage the discrete logarithm problem, particularly with respect to the key size.

Because a large number of elliptic curves are in use, it is necessary for an ECC processor to be able to handle different elliptic curves and the underlying fields.

The security of ECC relies on the discrete logarithm problem for the group of points on an elliptic curve defined over a finite field. The main advantage of ECC over systems based on the multiplicative group is the absence of a sub-exponential-time algorithm for solving the underlying hard mathematical problem in ECC, i.e. the Elliptic Curve Discrete Logarithm Problem (ECDLP). Consequently, a significantly smaller parameter can be used in ECC while maintaining the equivalent levels of security. It results in a smaller key size, bandwidth, and electrical power, and is especially attractive in applications where computational power and space are constrained, such as smart cards and wireless devices.

Good overviews of elliptic curve cryptography can be further found in [28, 20]

### 3.5 Elliptic Curves over Finite Fields

Elliptic curve cryptography is based on elliptic curves over finite fields. Two types of finite fields have been introduced in Section 2.2, Chapter 2. The Weierstrass equations for elliptic curves defined on these two fields GF(p) and  $GF(2^n)$  are described in the following subsections, respectively.

#### 3.5.1 Elliptic Curves over GF(p)

The elliptic curves over GF(p) (where p is an odd prime and p > 3) is defined by the equation

$$y^2 = x^3 + ax + b (3.7)$$

where the parameters  $a, b \in GF(p)$  and  $4a^3 + 27b^2 \neq 0 \pmod{p}$ . The set of solutions (or points)  $P = (x_p, y_p)$  where  $x_p, y_p \in GF(p)$ , together with a special point O (called

the point at infinity) constitute the set  $E_p(a,b)$ . A finite abelian group  $(E_p(a,b), +)$  is defined on the set  $E_p(a,b)$  with the O acting as its additive identity. According to the rule of abelian group, the addition operation in  $E_P(a,b)$  for all points  $P, Q \in E_p(a,b)$  in affine coordinate is as follows.

- 1. P + O = O + P = P

- 2. If  $P = (x_p, y_p)$ , then  $P + (x_p, -y_p) = O$ . The point  $-P = (x_p, -y_p)$  is called the negative of P

- 3. If  $P=(x_P,y_P)$  and  $Q=(x_Q,y_Q)$  and  $P\neq \pm Q$ , then  $R=P+Q=(x_R,y_R)$ , where

$$x_R = (\lambda^2 - x_p - x_Q) \pmod{p}$$

(3.8)

$$y_R = (\lambda(x_p - x_R) - y_P) \pmod{p} \tag{3.9}$$

where  $\lambda = (\frac{y_Q - y_P}{x_Q - x_P}) \pmod{p}$ .

4. If  $P = (x_P, y_P)$ , then  $R = P + P = 2P = (x_R, y_R)$ , where

$$x_R = (\lambda^2 - x_p - x_Q) \pmod{p}$$

(3.10)

$$y_R = (\lambda(x_p - x_R) - y_P) \ (mod \ p)$$

(3.11)

where  $\lambda = (\frac{3y_Q^2 + a}{2y_P}) \pmod{p}$ . This operation is referred to as the doubling of a point.

5. Scalar multiplication (or point multiplication) kP is defined as repeated addition of P to itself k times.

## **3.5.2** Elliptic Curves over $GF(2^n)$

Elliptic curves over  $GF(2^n)$  are defined by the equation

$$y^2 + xy = x^3 + ax^2 + b (3.12)$$

where the parameters  $a, b \in GF(2^n)$ . The set of solutions (or points)  $P = (x_p, y_p)$  where  $x_p, y_p \in GF(2^n)$  together with a special point O called the point at infinity constitute the set  $E_{2^n}(a, b)$ . A finite abelian group  $(E_{2^n}(a, b), +)$  is defined on the set  $E_{2^n}(a, b)$  with the a point at infinity O acting as its additive identity. According to the rule of abelian group, the addition operation in  $E_{2^n}(a, b)$  for all points  $P, Q \in E_{2^n}(a, b)$  in affine coordinate is as follows.

- 1. P + O = O + P = P.

- 2. If  $P = (x_p, y_p)$ , then  $P + (x_p, x_p + y_p) = O$ . The point  $-P = (x_p, x_p + y_p)$  is called the negative of P.

- 3. If  $P=(x_P,y_P)$  and  $Q=(x_Q,y_Q)$  and  $P\neq \pm Q$ , then  $R=P+Q=(x_R,y_R)$ , where

$$x_R = \lambda^2 + \lambda + x_p + x_Q + a \tag{3.13}$$

$$y_R = \lambda(x_p + x_R) + x_R + y_P \tag{3.14}$$

where  $\lambda = (\frac{y_Q + y_P}{x_Q + x_P})$ .

4. If  $P = (x_P, y_P)$ , then  $R = P + P = 2P = (x_R, y_R)$ , where

$$x_R = \lambda^2 + \lambda + a \tag{3.15}$$

$$y_R = \lambda(x_P + x_R) + x_R + y_v$$

(3.16)

where  $\lambda = (x_P + \frac{y_P}{x_P})$ . This operation is referred to as the doubling of a point.

5. Scalar multiplication (or point multiplication) kP is defined as repeated addition of P to itself k times.

#### 3.6 ECC Domain Parameters

Some definitions are required before the introduction of ECC domain parameters. The order of a point P on an elliptic curve is the smallest positive integer r such

that rP = O. kP = lP if and only if  $k = l \pmod{r}$  and  $k, l \in Z_n$ . The number of points of E(GF(q)), denoted by #E(GF(q)), is known as the *curve order* of the curve. Hasse's theorem states that #E(GF(q)) = q + 1 - t, where  $|t| \leq 2\sqrt{q}$ . ECC domain parameters over GF(q) are a septuple:

$$T = (q, FR, a, b, G, n, h)$$

(3.17)

where q specifies a prime power  $(q = p \text{ or } q = 2^m)$ , here m is denoted to distinguish the power of m from the ECC domain parameter n); FR (field representation) indicates the method used for representing field elements in GF(q); two field elements a and  $b \in GF(q)$  specify the equation of the elliptic curve E over GF(q);  $G = (x_G, y_G) \in E_q(a, b)$  is the base point on E(GF(q)); the prime number n is the order of G and the integer h is the cofactor h = #E(GF(q))/n. The ECC key length is defined to be the bit-length of n, because n is the primary security parameter.

### 3.7 Key Generation

An entity A's public and private key pair is associated with a particular set of elliptic curve domain parameters (q, FR, a, b, G, n, h). To generate a key pair, entity A does the following:

- 1. Select a random or pseudo-random integer d in the interval [1, n-1].

- 2. Compute Q = dG.

- 3. A's public key is a point Q in  $E_q(a,b)$  and A's private key is an integer d.

## 3.8 Elliptic Curve Protocols

Elliptic curve Diffie-Hellman (ECDH), the Elliptic Curve Digital Signature Algorithm (ECDSA) and the Elliptic Curve Authenticated Encryption Scheme (ECAES)

are three fundamental protocols based on elliptic curves. The ECDH is the elliptic curve analog of Diffie-Hellman key exchange; the ECDSA is the elliptic version of the DSA proposed by Scott Vanstone [52] in 1992; and the ECAES is a variant of the ElGamal public-key encryption theme proposed by Abdalla, Bellare and Rogaway [1] in 1999. Only the simple ECDH is described here and relevant references can be referred to for other protocols. Assume participants A and B share the same domain parameters D = (q, FR, a, b, G, n, h). The key exchange between A and B can be accomplished as follows:

- 1. A selects its private key  $d_A$  and generates a public key  $Q_A$  according to key generation procedure.

- 2. B selects its private key  $d_B$  and generates a public key  $Q_B$  according to key generation procedure.

- 3. A computes  $P_A = d_A Q_B = (x_A, y_A)$  and B computes  $P_B = d_B Q_A = (x_B, y_B)$ .

- 4. Check that  $P_A \neq O$ ,  $P_B \neq O$ .

- 5. The shared secret value is  $k = x_A = x_B$ .

### 3.9 AES Algorithm

The Advanced Encryption Standard (AES) [49, 35] is the new information protection standard defined by the US National Institute for Security Technologies (NIST) to replace the previous Data Encryption Standard (DES) to protect certain levels of federal information and communications. In 1997, NIST called for a new AES algorithm. The Rijndael algorithm was selected as the finalist and published in 2001.

AES performs four operations on a 128-bit block of data for a certain number of repetitions. All the intermediate results of the 128-bit block as well as the input

and the output block are called states. The most intuitive way to understand AES operation is to picture each state as a  $4 \times 4$  matrix of bytes which are filled in the matrix column by column from the most significant byte (indexed as 0) to the least significant byte (indexed as F). At each stage of the transformation between plaintext and ciphertext, the block of data is transformed from its current state to the next new state, depending on which operation is used. The four operations are SubBytes, ShiftRows, MixColumns and AddRoundKey.

The SubBytes operation is a nonlinear substitution that performs on each byte of the state using a substitution table (S-box) which contains a permutation of all possible 256 8-bit values. The inverse of this operation, InvSubBytes, consists of applying the inverse of the affine transformation followed by taking the same multiplicative inverse in  $GF(2^8)$ .

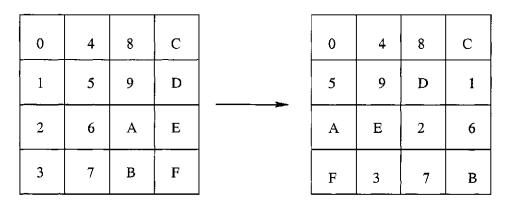

State before ShiftRows

State after ShiftRows

Figure 3.3: ShiftRows operation for encryption in AES algorithm

The ShiftRows operation (Fig. 3.3) is the cyclic shifting of each row of the state to the left over different numbers of bytes (offsets) on encryption, while the InvShiftRows shifts to the right on decryption.

The MixColumns operation treats each column of the state as a four-term polynomial over  $GF(2^8)$  and transforms each column to a new one by multiplying it with a constant polynomial  $a(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$  modulo

$x^4 + 1$ . The inverse MixColumns operation is a multiplication of each column with  $b(x) = a^{-1}(x) = \{0B\}x^3 + \{0D\}x^2 + \{09\}x + \{0E\} \mod x^4 + 1$ . The transformation can also be written in the following matrix multiplication given a 32-bit input word  $w = w_3w_2w_1w_0$  where each  $w_i$  has eight bits.

$$\begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \cdot \begin{bmatrix} w_3 \\ w_2 \\ w_1 \\ w_0 \end{bmatrix} = \begin{bmatrix} w'_3 \\ w'_2 \\ w'_1 \\ w'_0 \end{bmatrix}$$

(3.18)

The AddRoundKey operation is a simple logical XOR of the current state with a round key that is generated by the key expansion. The XOR operation is its own inverse.

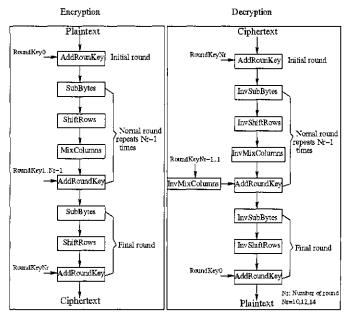

Figure 3.4: AES algorithm flow for encryption/decryption

In the key expansion algorithm, The initial Nk-word key corresponds to the cipher key and all subsequent Nk-word keys are derived recursively from their respective predecessors [49, 35]. Nk is the number of 32-bit words comprising the cipher key, which can be 4, 6 or 8. The same serial Nk-word keys are used in reversed order for decryption and all these keys can be derived from the last round of

Nk-word key using the inverse operations.

### 3.10 RC5 Algorithm

RC5 [49, 42, 17] is a fast block cipher designed by Ronald Rivest in 1994. The easy implementation and the security of heavily using data-dependent rotations and the mixture of different operations make it widely adopted in the area requiring high level strength for bulk encryption, such as wireless communications. A particular RC5 is exactly designated as RC5-w/r/b, where the variable parameters w, r, b denote the word size (in bits), the number of rounds and the length of secret key (in bytes), respectively. The allowable values of w are 16, 32 and 64; the allowable values of r and b range from 0 to 255. RC5-32/12/16 is commonly chosen.

There are three routines in RC5: key expansion, encryption, and decryption. These routines use three primitive operations (and their inverses): words addition modulo  $2^w$  (w is the word size parameter), bitwise XOR, and data-dependent left rotation of x by y denoted by x <<< y. Note that only the  $log_2(w)$  low-order bits of y affect this rotation. In the key-expansion routine, the user-provided secret key is expanded to fill a key table whose size depends on the number of rounds. The key table is then used in both encryption and decryption. The decryption follows the same scheme as encryption except that it requires words subtraction and rotation to the right. The description of the encryption algorithm is given in the following [42].

Input: Plaintext  $\{A, B\}$ , secret key array  $(S[0], \ldots, S[2r], S[2r+1])$ Output: Ciphertext  $\{A, B\}$

$$A = A + S[0]$$

$$B = B + S[1]$$

for  $i = 1$  to  $r$  do

$$A = ((A \oplus B) <<< B) + S[2i]$$

$$B = ((B \oplus A) <<< A) + S[2i + 1]$$

Algorithm 1: RC5 encryption algorithm

RC5 subkey generation is quite complex which generates a subkey array S of t = 2r + 2 words from b-byte secret key K. This includes three algorithm steps. First, the secret key array  $K[0, \ldots, b-1]$  in byte is copied into an array  $L[0, \ldots, c-1]$  in length of  $c = \lceil b/u \rceil$  words where u = w/8 is the number of bytes/word. Second, array S is initialized using an arithmetic progress modulo  $2^w$  determined by the predefined magic constants  $P_w$  and  $Q_w$ . At last, a mix in the secret key in three passes over the arrays S and L is performed as follows [42].

$$i = j = X = Y = 0$$

Do  $3* \max\{2r + 2, c\}$  times:

$$X = S[i] = (S[i] + X + Y) <<< 3$$

$$i = (i + 1) \pmod{t}$$

$$Y = L[j] = (L[j] + X + Y) <<< (X + Y)$$

$$j = (j + 1) \pmod{c}$$

## 3.11 Comparison between Public-key and Secretkey Cryptosystems

In this section, the advantages and disadvantages between public-key and secret-key cryptosystems are summarized. The advantages of public-key cryptosystem over secret-key cryptosystem are as follows:

- 1. Public-key cryptography has increased security and convenience since private keys never need to be transmitted or revealed to anyone. In a secret-key cryptosystem, by contrast, the secret keys must be transmitted.

- 2. Public-key cryptosystems can provide digital signatures that cannot be repudiated.

The disadvantages of public-key cryptosystem are listed as follows:

- 1. Many secret-key encryption algorithms are significantly faster than any currently available public-key encryption algorithm.

- 2. Public-key cryptography may be vulnerable to impersonation, even if users' private keys are not available.

In general, public-key cryptography is best suited for an open multi-user environment. It is not meant to replace secret-key cryptography, but rather to supplement it and to make it more secure. For efficiency reasons, a hybrid cryptosystem is used in practice; a key is exchanged using a public-key cipher, and the rest of the communication is encrypted using a secret-key algorithm.

## 3.12 Summary

In this chapter, an overview of public-key and secret-key cryptography is presented. The public-key Elliptic Curve Cryptography (ECC) and secret-key algorithms of CHAPTER 3 CRYPTOGRAPHY

AES and RC5 are discussed. These three algorithms are implemented in the proposed crypto-processor in this thesis. In the final section, comparisons between public-key and secret-key cryptography are given.

## Chapter 4

# The Cryptographic Processor Architecture

In this chapter, the algorithms used in the ECC are introduced, and the architecture of the processor with corresponding instruction set is described. The performance evaluation and comparison are given finally.

The implementation of ECC is more complicated than secret-key cryptosystems such as AES and RC5. So a majority of the work in this thesis focuses on the ECC design. In ECC, the computation of scalar multiplication kP involves three different levels:

- Selection of scalar multiplication algorithms. These algorithms include the double-and-add method using binary representation of k, addition-subtraction method using nonadjacent form of k, and Montgomery scalar multiplication. Montgomery scalar multiplication is a fast algorithm only for  $GF(2^n)$ .

- Elliptic arithmetics in different coordinate representations. These coordinates include affine coordinates, projective coordinates, Jacobian coordinates used in both GF(p) and  $GF(2^n)$  and López-Dahab [28] projective coordinates used only in  $GF(2^n)$ , etc. Different coordinate representations lead to different formulae for point addition and point doubling.

CHAPTER 4

• Field arithmetics. These include the basis selection, multiplier and squaring design, etc. In this thesis, the dual-field multipliers based on Montgomery multiplication are designed, which can perform multiplications both in GF(p) and  $GF(2^n)$  using polynomial bases. Furthermore, this multiplier design has been extended to implement four independent multiplications over  $GF(2^8)$  used in the secret-key cryptosystems such as AES.

In this thesis, algorithm combinations between selection of fast scalar multiplication algorithms and selection of coordinate representations are made in order to arrive at the best solution. Due to the different characteristics of GF(p) and  $GF(2^n)$ , the combinations are chosen separately. For GF(p), an addition-subtraction method using the NonAdjacent Form (NAF) of k in Jacobian projectives is chosen. For  $GF(2^n)$ , Montgomery scalar multiplication algorithm in projective coordinates is selected. In the finite field arithmetic level, the multiplication over GF(p) and  $GF(2^n)$  are unified using Montgomery multiplication algorithm.

In the following first two sections, the elliptic arithmetic over GF(p) of point addition and point doubling in modified Jacobian coordinates, and scalar multiplication using NAF are introduced. The Montgomery scalar multiplication algorithm over  $GF(2^n)$  in projective coordinates is described in the third section. Due to simple formulae for point addition and point doubling, the two parts are described in one section. In Section 4.4, the details of Montgomery multiplication algorithm over both GF(p) and  $GF(2^n)$  are introduced. In Section 4.5, the overall architecture of the processor is proposed and the details of important common components are described. Finally, the instruction set is given and the corresponding programs for AES, RC5, and multiplication in GF(p) are listed respectively. In Section 4.6 and Section 4.7, the performance evaluation and comparison are given.

| Coordinate Representation | Addition                         | Doubling                      |

|---------------------------|----------------------------------|-------------------------------|

| Projective                | $12 \mathcal{M} + 2 \mathcal{S}$ | $7\mathcal{M}+5\mathcal{S}$   |

| Jacobian                  | $12 \mathcal{M} + 4 \mathcal{S}$ | $4\mathcal{M}+6\mathcal{S}$   |

| Chudnovshky Jacobian      | 11 M+3 S                         | $5\mathcal{M}+6\mathcal{S}$   |

| Modified Jacobian         | $13 \mathcal{M} + 6 \mathcal{S}$ | $4\mathcal{M}{+}4\mathcal{S}$ |

Table 4.1: Projective coordinate representations over GF(p)

## 4.1 Coordinate Representation of Elliptic Curves over GF(p)

Since inversions are more expensive relative to multiplications, it is more efficient to represent points in projective coordinates. The inversion operation is traded for more multiplications and other less expensive finite field operations.

Several projective themes in GF(p) are described in [7]. Table 4.1 compares the themes for addition and doubling with respect to the number of multiplications  $\mathcal{M}$  and squarings  $\mathcal{S}$  in the underlying finite field. The inexpensive field addition operation is omitted. In this thesis, the modified Jacobian projective coordinates are chosen due to their fastest doubling operation. They are represented internally as the quadruple  $(X, Y, Z, aZ^4)$ . The formulae of addition and doubling in the modified Jacobian projectives are given as follows [7].

Let  $P=(X_1,\ Y_1,\ Z_1,\ aZ_1^4),\ Q=(X_2,\ Y_2,\ Z_2,\ aZ_2^4),$  and  $R=P+Q=(X_3,\ Y_3,\ Z_3,\ aZ_3^4).$  The addition formulae of R=P+Q  $(P\neq\pm Q)$  are the following:

$$\begin{split} U_1 &= X_1 \cdot Z_2^2, \quad S_2 = Y_2 \cdot Z_1^3, & X_3 &= -H^3 - 2U_1 \cdot H^2 + r^2, \\ U_2 &= X_2 \cdot Z_1^2, \quad H = U_2 - U_1, & Y_3 &= -S_1 \cdot H^3 + r(U_1 \cdot H^2 - X_3), \\ S_1 &= Y_1 \cdot Z_2^3, \quad r = S_2 - S_1, & Z_3 &= Z_1 \cdot Z_2 \cdot H, \ aZ_3^4 &= aZ_3^4. \end{split}$$

The doubling formulae of R = 2P are the following:

$$S = 4X_1 \cdot Y_1^2, \quad X_3 = -2S + M^2,$$

$$U = 8Y_1^4, \quad Y_3 = M \cdot (S - X_3) - U,$$

$$M = 3X_1^2 + (aZ_1^4), \quad Z_3 = 2Y_1 \cdot Z_1, \ aZ_3^4 = 2U \cdot (aZ_1^4).$$

## 4.2 Elliptic Scalar Multiplication over GF(p)

There are several methods known to compute kP. The basic method is the binary double-and-add method [30, 49] which requires k doublings and k/2 addition on average. The addition-subtraction method requires only k/3 additions on average with the same number of doubling [48]. It is based on NonAdjacent Form (NAF or sparse signed-digit representation) of the coefficient k where the redundant binary representation using  $\{-1, 0, 1\}$  is allowed. It is known that every integer has a unique NAF with the property that no two consecutive coefficients are nonzero. Also, the NAF has the minimum number of nonzero coefficients among all signed-digit representations, k/3 on average. Here gives an example of NAF:

$$NAF(29) = (1, 0, 0, -1, 0, 1), and 29 = 32 - 4 + 1.$$

(4.1)

The NAF of an integer is at most one bit longer than its binary expansion. The addition-subtraction method requires bit conversion left-to-right. An optimal NAF algorithm converted from the most significant bit is listed in Algorithm 2 [16].

```

Input: (e_t, e_{t-1}, \dots, e_1, e_0)

Output: (d_t, d_{t-1}, \dots, d_0)

b_t \leftarrow 0 \; ; \; e_t \leftarrow 0 \; ; \; e_{-1} \leftarrow 0 \; ; \; e_{-2} \leftarrow 0 \; ;

for i{=}t \; down \; to \; \theta \; do

b_{i-1} \leftarrow \lfloor (b_i + e_{i-1} + e_{i-2})/2 \rfloor \; ;

d_i \leftarrow e_i + b_{i-1} - 2b_i \; ;

end

```

Algorithm 2: Left-to-right NAF

CHAPTER 4

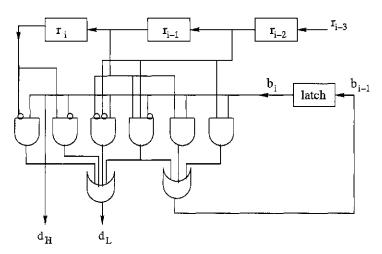

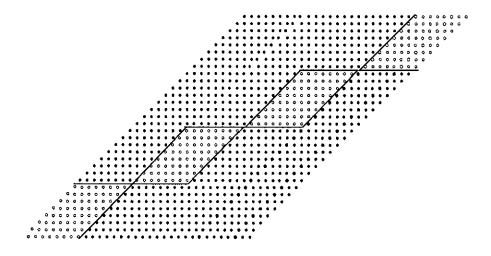

This algorithm can also be expressed as in Table 4.2 (X stands for don't care) [16]. Based on this table, a simple hardware speeding-up of NAF is proposed in [16].  $d_i$   $(d_i \in \{0, 1, \bar{1}\})$  can be encoded with two one-bit variables  $\{d_H, d_L\}$ . Let  $\{0 \rightarrow$  $(X,0)_2; 1 \rightarrow (0,1)_2; -1 \rightarrow (1,1)_2$ , and after simple logic reduction,  $b_{i-1}, d_H$ , and  $d_L$  can be expressed as follows.

$$\begin{cases} b_{i-1} = \overline{b_i} \cdot r_{i-1} \cdot r_{i-2} + b_i \cdot r_{i-1} + b_i \cdot r_{i-2} \\ d_H = b_i \\ d_L = \overline{b_i} \cdot r_{i-1} \cdot r_{i-2} + \overline{b_i} \cdot r_i + b_i \cdot \overline{r_i} + b_i \cdot \overline{r_{i-1}} \cdot \overline{r_{i-2}} \end{cases}$$

The logic diagram based on this equation is illustrated in Fig. 4.1. Initially, the shift-left registers  $\{r_i, r_{i-1}, r_{i-2}\}$  are loaded with  $\{0, r_{m-1}, r_{m-2}\}$  and the latch is reset to logic "0". At the end of each iteration, the output  $d_H$  and  $d_L$  are used to decide the value of the encoded  $d_i$ .

Figure 4.1: Hardware speeding-up of NAF

Given the NAF of  $n = \sum_{i=0}^{t} d_i 2^i$ , the elliptic scalar multiplication Q = nP is performed as follows [28, 48].

| $b_i$ | $r_i$ | $r_{i-1}$ | $r_{i-2}$ | $b_{i-1}$ | $d_i$ |

|-------|-------|-----------|-----------|-----------|-------|

| 0     | 0     | 0         | X         | 0         | 0     |

| 0     | 0     | 1         | 0         | 0         | 0     |

| 0     | 0     | 1         | 1         | 1         | 1     |

| 0     | 1     | 0         | X         | 0         | 1     |

| 1     | 0     | 1         | X         | 1         | Ī     |

| 1     | 1     | 0         | 0         | 0         | 1     |

| 1     | 1     | 0         | 1         | 1         | 0     |

| 1     | 1     | 1         | X         | 1         | 0     |

Table 4.2: Left-to-right NAF

```

Input: An integer k=(d_t,d_{t-1},\ldots,d_0), and a point P\in E(GF(q))

Output: Q=kP\in E(GF(q))

Set Q\leftarrow O;

for i=t\text{-}1 down to 0 do

Set Q\leftarrow 2Q;

if e_i=1 then

Set Q\leftarrow Q+P;

end

if e_i=-1 then

Set Q\leftarrow Q-P;

end

```

Algorithm 3: Addition-subtraction method using NAF

## 4.3 Elliptic Scalar Multiplication over $GF(2^n)$

A new scalar multiplication algorithm that was first proposed by Montgomery [33] and then modified by López and Dahab [27] proves to be the best algorithm for elliptic scalar multiplication in  $GF(2^n)$ . It is based on the binary expansion of k and the observation that the x-coordinate of the sum of two points whose difference is known can be computed in terms of the x-coordinates of the involved points. It

```

can be expressed in Algorithm 4.

Input: An integer k > 0, and a point P \in E(GF(2^n))

Output: Q = kP \in E(GF(2^n))

Set k \leftarrow (k_{t-1}, k_{t-2}, \dots, k_1, k_0)_2;

Set P_1 \leftarrow P, P_2 \leftarrow 2P;

for i=t-2 down to 0 do

if k_i = 1 then

Set P_1 \leftarrow P_1 + P_2, P_2 \leftarrow 2P_2;

else

Set P_2 \leftarrow P_1 + P_2, P_1 \leftarrow 2P_1;

end

end

Q = P_1;

```

Algorithm 4: The basic Montgomery scalar multiplication

As in GF(p), projective coordinates (X, Y, Z) are represented in order to avoid expensive inversions by x=X/Z and y=Y/Z from affine coordinates (x, y). The Montgomery scalar multiplication in projective coordinates is listed in Algorithm 5.

Input: An integer

$$k \geq 0$$

, and a point  $P \in E(GF(2^n))$

Output:  $Q = kP \in E(GF(2^n))$

if  $k=0$  or  $x=0$  then

output  $(0,0)$  and stop;

end

Set  $k \leftarrow (k_{t-1}, k_{t-2}, \dots, k_1, k_0)$ ;

Set  $X_1 \leftarrow x, \ Z_1 \leftarrow 1, \ X_2 \leftarrow x_4 + b, \ Z_2 \leftarrow x^2$ ;

for  $i=t-2$  down to 0 do

if  $k_i = 1$  then

$Z_3 \leftarrow (x_1 \cdot Z_2 + X_2 \cdot Z_1)^2, \ X_3 \leftarrow x \cdot Z_3 + (X_1 \cdot Z_2) \cdot (X_2 \cdot Z_1)$ ;

$Z_4 \leftarrow Z_2^2 \cdot X_2^2, \ X_4 \leftarrow X_2^4 + b \cdot Z_2^4$ ;

$Z_1 \leftarrow Z_3, \ X_1 \leftarrow X_3, \ Z_2 \leftarrow Z_4, \ X_2 \leftarrow X_4$ ;

else

$Z_3 \leftarrow (x_1 \cdot Z_2 + X_2 \cdot Z_1)^2, \ X_3 \leftarrow x \cdot Z_3 + (X_1 \cdot Z_2) \cdot (X_2 \cdot Z_1)$ ;

$Z_4 \leftarrow Z_1^2 \cdot X_1^2, \ X_4 \leftarrow X_1^4 + b \cdot Z_1^4$ ;

$Z_1 \leftarrow Z_4, \ X_1 \leftarrow X_4, \ Z_2 \leftarrow Z_3, \ X_2 \leftarrow X_3$ ;

end

end

return (The affine coordinates converted from projective coordinates of Q);

Algorithm 5: The Montgomery scalar multiplication algorithm using projective coordinates

The y-coordinates of kP can be computed from the x-coordinates of points involved in the last iteration in Algorithm 5, which is shown as follows.

$$if \ Z_1 = 0 \ then \ output \ (0,0)$$

$$if \ Z_2 = 0 \ then \ output \ (x, x + y)$$

$$x_k = \frac{X_1}{Z_1}$$

$$y_k = (\frac{X_1}{Z_1} + x) \cdot \frac{(\frac{X_1}{Z_1} + x)(\frac{X_2}{Z_2} + x) + x^2 + y}{x} + y$$

Using projective coordinates, Montgomery scalar multiplication requires  $6\lfloor log_2(k)\rfloor +$

9 multiplications,  $5\lfloor log_2(k)\rfloor + 3$  squarings,  $3\lfloor log_2(k)\rfloor + 7$  additions and 1 multiplicative inverse.

### 4.4 Montgomery Multiplication

Montgomery multiplication was first proposed by Montgomery in 1985 [32], as an efficient method for doing modular multiplication in prime fields GF(p). This method was extended to the binary finite field  $GF(2^m)$  by Koç and Acar in [21]. Several papers [12, 43, 9] have explored the similarity of hardware design between Montgomery multiplications in GF(p) and  $GF(2^m)$  and proposed unified or dual-field multipliers based on the Montgomery multiplication algorithm.

#### 4.4.1 Montgomery Multiplication over GF(p)

Given two integers A and B, and the prime number p, the Montgomery multiplication algorithm in GF(p) computes

$$C = MonMul(A, B) = A \cdot B \cdot R^{-1} \pmod{p} \tag{4.2}$$

where  $R=2^m$  and  $0 \le A$ , B and <math>p is an m-bit number. Before using Montgomery multiplication, the field element should be transformed into Montgomery domain by using the formula  $\bar{A} = A \cdot R \pmod{p}$  for  $A \in GF(p)$ . For any two elements in the Montgomery domain  $\bar{A}$  and  $\bar{B}$ , the result using equation 4.2 is still in the Montgomery domain.

$$\overline{C} = \overline{A} \cdot \overline{B} \cdot R^{-1} \pmod{p} = (A \cdot R) \cdot (B \cdot R) \cdot R^{-1} = C \cdot R \pmod{p} \tag{4.3}$$

The transformation operations between the two domains can be performed using the MonMul function as follows.

$$\bar{A} = MonMul(A, R^2) = A \cdot R^2 \cdot R^{-1} = A \cdot R \pmod{p}$$

$$\tag{4.4}$$

$$C = MonMul(\bar{C}, 1) = C \cdot R \cdot R^{-1} = C \pmod{p}$$

$$\tag{4.5}$$

The key idea of the Montgomery multiplication algorithm is to add an appropriate multiple of p to make the lowest m bits of  $A \cdot B$  equal to 0. The addition operation does not influence the equation 4.2 due to its modulo p arithmetic. In the following, we assume that the operation numbers have already been transformed to Montgomery domain and the overlines are omitted. For Montgomery reduction algorithm, an additional value N' is needed which satisfies the property  $R \cdot R^{-1} - N \cdot N' = 1$ . The integer  $R^{-1}$  and N' can be computed by the extended Euclidean algorithm. The Montgomery multiplication algorithm is given below:

```

Input: A, B, p \ (0 \le A, B \le p)

Output: C = AB2^{-m} mod \ p

1. T = A \cdot B;

2. M = T \cdot N' \mod 2^m;

3. C = (T + M \cdot p)/2^m;

4. if C \ge p then C = C - p;

```

For multiple-precision multiplication, the operands of m-bit length should be divided into s blocks of words  $(m = s \times w)$  in the form as  $A = (a_{s-1}, \ldots, a_1, a_0)$ , where w is the word size. This can also be expressed as follows:

$$A = a_{s-1}2^{w(s-1)} + \ldots + a_12^w + a_0$$

(4.6)

If one operand is in multiple-precision, while other operands are still in full-precision, the Montgomery multiplication algorithm is shown as Algorithm 6. In this algorithm, the division of  $2^w$  is trivial because the least significant word of the dividend is zero. This can be proved by the following argument:

$$c_0 + a_i b_0 + t_i p \mod 2^w$$

$$= c_0 + a_i b_0 + (c_0 + a_i b_0)(-p^{-1}) p \mod 2^w$$

$$= c_0 + a_i b_0 - (c_0 + a_i b_0) \mod 2^w$$

$$= 0$$

```

Input: A = (a_{s-1}, \dots, a_1, a_0), \ B, \ p, \ q = -p^{-1} \ mod \ 2^w = -p_0^{-1} \ mod \ 2^w

Output: C = AB2^{-m} \ mod \ p

C = 0;

for (i=0 \ to \ s-1) \ do

t_i = (c_0 + a_i b_0) q \ mod \ 2^w;

C = (C + a_i B + t_i p)/2^w;

end

if (C \ge p) then

C = C - p;

end

```

${\bf Algorithm~6:~Word~level~full~precision~Montgomery~multiplication}$

If all the operands are in multiple-precision form, the Montgomery multiplication is listed in Algorithm 7 based on the Coarsely Integrated Operand Scanning (CIOS) Method [22].

```

Input: A = (a_{s-1}, \ldots, a_1, a_0), B = (b_{s-1}, \ldots, b_1, b_0), p = (p_{s-1}, \ldots, p_1, p_0),

q = -p_0^{-1} \mod 2^w

Output: t = AB2^{-m} \mod p

for i=0 to s-1 do

C = 0;

for j=0 to s-1 do

(C,S) = t[j] + a[j] \times b[i] + C ;

t[j] = S ;

end

(C, S) = t[s] + C; t[s] = S;;

m = t[0] \times q \bmod 2^w ;

for j=0 to s-1 do

(C,S) = t[j] + m \times p[j] + C ;

if j \neq \theta then

t[j-1] = S ;

end

end

(C,S) = t[s] + C ;

t[s-1] = S; t[s] = C;

if t > p then

t = t - p;

end

```

**Algorithm 7:** Word level word level Montgomery multiplication over GF(p)

```

Input: A = (a_{s-1}, \ldots, a_1, a_0), p = (p_{s-1}, \ldots, p_1, p_0), q = -p_0^{-1} \mod 2^w

Output: t = AB2^{-m} \mod p

for i=0 to s-1 do

C = 0:

(C, S) = t[i] + a[i] \times a[i] + C; t[i] = S;

for j=i+1 to s-1 do

(C, S) = t[j] + 2 \times a[j] \times a[i] + C; t[j] = S;

end

(C,S) = t[s] + C ;

m = t[0] \times q \bmod 2^w ;

for j=0 to s-1 do

(C,S) = t[j] + m \times p[j] + C ;

if j \neq \theta then

t[j-1] = S ;

end

\quad \text{end} \quad

(C,S) = t[s] + C ;

t[s-1] = S; t[s] = C;

if t > p then

t = t - p;

end

end

```

**Algorithm 8**: Montgomery squaring over GF(p)

#### **4.4.2** Montgomery Multiplication over $GF(2^n)$

The Montgomery multiplication in  $GF(2^n)$  using the polynomial basis is very similar to the one in GF(p) [22]. The Montgomery multiplication of A(x) and B(x) with product C(x) is given as

$$C(x) = A(x) \cdot B(x) \cdot R(x)^{-1} \ (mod \ p(x))$$

(4.7)

where  $R(x) = x^m$  instead of  $R = 2^m$  as compared with equation 4.2. Furthermore, the representation of the elements of GF(p) and  $GF(2^n)$  are the same. An example in [44] is given as follows.

The elements of GF(7) for p=7 and the elements of  $GF(2^3)$  for  $p(x)=x^3+x+1$  are represented as  $GF(7)=\{000,001,010,011,100,101,110\}$  and  $GF(2^3)=\{000,001,010,011,100,101,110,111\}$ , respectively.

Similarly, the domain transformations are required: before Montgomery multiplication, the operands should be transformed into Montgomery domain and the computing result should be transformed back. The transformations are accomplished as follows:

$$\begin{split} \bar{A} &= MolMul(A, R^2) = A(x) \cdot R^2(x) \cdot R^{-1}(x) = A(x) \cdot B(x) \ (mod \ p(x)) \\ \bar{B} &= MolMul(B, R^2) = B(x) \cdot R^2(x) \cdot R^{-1}(x) = A(x) \cdot B(x) \ (mod \ p(x)) \\ \bar{C} &= MolMul(\bar{C}, 1) = C(x) \cdot R(x) \cdot R^{-1}(x) = C(x) \ (mod \ p(x)) \end{split}$$

However, the operations in  $GF(2^m)$  are much simpler without considering carry propagations.

The multiple-precision Montgomery multiplication algorithm for multiplication and squaring can be written based on the Coarsely Integrated Operand Scanning (CIOS) Method [22] as follows:

```

Input: A(x) = (a_{s-1}, \dots, a_1, a_0), B(x) = (b_{s-1}, \dots, b_1, b_0),

p(x) = (p_{s-1}, \dots, p_1, p_0), q(x) = p(x)^{-1} \mod x^w = p_0(x)^{-1} \mod x^w

Output: t(x) = A(x)B(x) \mod p(x)

for i=0 to s-1 do

C=0;

for j=0 to s-1 do

(C, S) = t[j] + a[j] \times b[i] + C; t[j] = S;

end

(C,S) = t[s] + C ;

m = t[0] \times n'[0] \bmod x^w ;

for j=0 to s-1 do

(C,S) = t[j] + m \times n[j] + C ;

if j \neq 0 then

t[j-1] = S ;

end

end

(C,S) = t[s] + C ;

t[s-1] = S; t[s] = C;

end

```

**Algorithm 9:** Montgomery multiplication over  $GF(2^n)$

```

Input: A(x) = a_{s-1}, \dots, a_1, a_0, p(x) = (p_{s-1}, \dots, p_1, p_0), q = p(x)^{-1} \text{ mod}

x^w = p_0(x)^{-1} \mod x^w

Output: t(x) = A(x)B(x) \mod p(x)

for i=0 to s-1 do

C = 0;

(C,S) = t[i] + a[i] \times a[i] + C ;

t[i] = S;

for j=i+1 to s-1 do

(C,S) = t[j] + 2 \times a[j] \times a[i] + C ;

t[j] = S ;

end

(C,S) = t[s] + C ;

m = t[0] \times p'[0] \mod x^w;

for j=0 to s-1 do

(C,S) = t[j] + m \times n[j] + C;

if j \neq \theta then

t[j-1] = S :

end

end

(C,S) = t[s] + C ;

t[s-1] = S; t[s] = C;

end

```

**Algorithm 10**: Montgomery squaring over  $GF(2^n)$

## 4.5 Architecture of the Hybrid Processor

The common arithmetic components in the three algorithms: ECC, AES, and RC5 are extracted as shown in Table 4.3. As the most important arithmetic component, a novel multiplier of 32 by 32 bits is proposed to perform multiplication over GF(p) and  $GF(2^n)$  in the ECC, and four independent multiplications over  $GF(2^8)$  in the

| components       | AES       | RC5 | ECC over $GF(p)$ | ECC over $GF(2^n)$ |

|------------------|-----------|-----|------------------|--------------------|

| multiplication   | $\sqrt{}$ |     | $\sqrt{}$        |                    |

| barrel shifter   |           |     |                  | $\sqrt{}$          |

| adder/subtracter |           |     |                  |                    |

| XOR              |           |     |                  | $\checkmark$       |

Table 4.3: The core components in different cryptographic algorithms

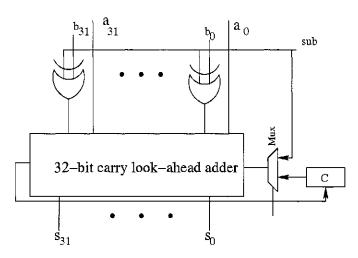

MixColumns operation of AES. An adder/subtracter is used for the modular addition/subtraction in RC5 and over GF(p) in ECC. In addition, a barrel shifter is embedded for data-dependent rotation in RC5. This barrel shifter can also be used for bit-shifts of parameter k in scalar multiplication kP over GF(p) and  $GF(2^n)$ .

In the following, the data path of the processor is described and followed by the details of core arithmetic components and the instruction set.

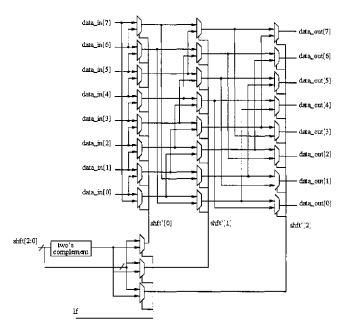

#### 4.5.1 Data Path

The main data path is 32-bit wide as shown in Fig. 4.2. The long operands of the ECC algorithm need to be broken up into multiple smaller words, and the arithmetic operations such as addition, subtraction, and multiplication, are implemented as multiple-precision operations [21]. The 32-bit data path is chosen considering that the word length in RC5 is 32-bit, and AES can also be processed in 32-bit processors. The two dual-port memories, which both have the capacity of  $256 \times 32$  bits, are used not only for passing parameters between the cryptographic processor and the host, but also for operands. The parameters for ECC or the expanded subkey array for secret-key cryptography are loaded into the dual-port RAMs from I/O ports. The operands of many instructions come from the dual-port RAMs. The formula of multiplication-accumulator operation is shown as  $(CA, SUM) = src0 \times src1 + src2 + CA$ , where CA is the carry vector, SUM is the sum vector, and src0, src1,

src2 are the three source operands which are accessed directly from the two dual-port RAMs with the ports douta1, doutb1 or douta2. The data in the dual-port RAMs can also be routed to register A through ports douta1 or doutb2. The results of barrel shifter, XOR and addition/subtraction operations are stored to register A, whereas the results of multiplications for ECC are written back to the dual-port RAMs.

In order to accommodate the eight-bit operations used in secret-key cryptographic algorithms, an eight-bit data path is also provided as shown in Fig. 4.3. The register A comprises of four eight-bit registers, i.e. A0, A1, A2, and A3. The sufficient Block RAMs provided by Xilinx FPGA devices are utilized to store the constants of the S-box and inverse S-box lookup tables operation used in AES algorithm. The ROM of  $512 \times 8$  bits is implemented by Block RAMs. The register file is composed of 32 eight-bit registers, of which four registers hold the indirect address for the dual-port RAMs and seven registers are used for the polynomial reduction for multiplication over  $GF(2^8)$ . The result of the multiplication over  $GF(2^8)$  is transmitted into A passing through multipliers as a 32-bit operation (Fig. 4.2) or the four independent bytes are XORed and the result is then stored into one of A3, A2, A1, A0 as an eight-bit operation (Fig. 4.3). For the MixColumns operation in AES, each element in the right column of the matrix in Equation 3.18 needs eight-bit XOR operations between the results of four eight-bit multiplications. For example,  $w_3' = (\{02\} \cdot w_3) \oplus (\{03\} \cdot w_2) \oplus (\{01\} \cdot w_1) \oplus (\{01\} \cdot w_0)$ . This special operation for MixColumns is supported directly in the design.

#### 4.5.2 Multiplier Design