## ON GRID CONVERTER RELIABILITY: PRESERVING THE LIFE OF POWER ELECTRONICS THROUGH ACTIVE THERMAL BOUNDARY CONTROL

by

Patrick T. Lewis

B.S. in Electrical Engineering, University of Pittsburgh, 2012

M.S. in Electrical Engineering, University of Pittsburgh, 2014

Submitted to the Graduate Faculty of

Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

2018

### UNIVERSITY OF PITTSBURGH

### SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Patrick T. Lewis

It was defended on

November 20, 2018

and approved by

Marius Rosu, PhD, Electromechanical Lead Product Manager, ANSYS Inc.

Robert Kerestes, PhD, Assistant Professor, Department of Electrical and Computer Engineering

Alexis Kwasinski, PhD, Associate Professor, Department of Electrical and Computer Engineering

Zhi Hong Mao, PhD, Associate Professor, Department of Electrical and Computer Engineering

Dissertation Co-Director: Gregory Reed, PhD, Professor, Department of Electrical and Computer Engineering

Dissertation Co-Director: Brandon Grainger, PhD, Assistant Professor, Department of Electrical and Computer Engineering Copyright © by P. T. Lewis

2018

# ON GRID CONVERTER RELIABILITY: PRESEVERING THE LIFE OF POWER ELECTRONICS THROUGH ACTIVE THERMAL BOUNDARY CONTROL

Patrick T. Lewis, Ph.D.

University of Pittsburgh, 2018

This dissertation proposes a method of preserving the lifetime of power electronic conversion systems through apt control design. Leading up to the inception of the contribution herein, this work involved exploring the impacts of advanced grid converter capabilities and control methods upon semiconductor device reliability. As distributed generation and loads are increasingly interfaced with the electric grid through power electronics, adverse challenges arise including voltage and frequency instability due to a reduction in system inertia. Said challenges incentivize various advanced grid converter features such as dynamic reactive compensation for grid voltage support, but such features can threaten to quicken the pace of device degradation, decreasing converter lifetime.

The reliability of power electronic conversion systems is correlated to the thermal stress experienced by the semiconductor device materials. The longevity of the device diminishes with high amplitudes of junction temperature fluctuations experienced by the device. This work introduces a control method designed to preserve converter life by minimizing thermal cycling amplitudes, particularly preventing the cooling of device materials when grid interactions would have situationally allowed cooling. The solution is based upon natural switching surface (NSS) control, previously applied in the literature to the dual active bridge for efficiency gains. Utilizing NSS control for the purpose of actively controlling thermal cycling behavior lays the foundational contribution of the work. In contrast to conventional pulse-width modulation strategies, this approach bears unique merit for the management of thermal behavior because of the unique ability to control the switching trajectories according to desired switching and conduction losses. With appropriate design measures this methodology is also applicable to various converter topologies.

This dissertation initially provides groundwork for the reliability of power electronics. Extensive case studies of electro-thermal performance assessments are presented for both reactive compensation and virtual synchronous machine control, evaluating the impacts of such advanced grid converter features upon device reliability. Theoretical foundation as well as an application case study are provided for natural switching surface control. The contributed work includes the development of active thermal boundary control for the dual active bridge operating under interval loading.

# **TABLE OF CONTENTS**

| AC  | KNO | WLED  | GEMENTS XXII                                       |

|-----|-----|-------|----------------------------------------------------|

| 1.0 |     | INTR  | ODUCTION1                                          |

|     | 1.1 | OBJ   | ECTIVE                                             |

|     | 1.2 | ORG   | GANIZATION                                         |

| 2.0 |     | BACH  | KGROUND ON DEVICE RELIABILITY AND MODELING         |

|     | 2.1 | ON F  | POWER ELECTRONICS RELIABILITY 8                    |

|     | 2.2 | ON H  | ELECTRO-THERMAL SEMICONDUCTOR DEVICE MODELING 17   |

| 3.0 |     | INVE  | STIGATING IMPACTS OF ADVANCED INVERTER FEATURES 24 |

|     | 3.1 | IMP   | ACT OF REACTIVE COMPENSATION GRID SUPPORT          |

|     |     | 3.1.1 | Smart DG Inverter Control Implementation27         |

|     |     | 3.1.2 | Case Results                                       |

|     |     | 3.1.3 | Conclusions                                        |

|     | 3.2 | IMP   | ACT OF VIRTUAL SYNCHRONOUS MACHINE GRID SUPPORT 39 |

|     |     | 3.2.1 | Virtual Synchronous Machine Implementation         |

|     |     | 3.2.2 | Case Results 47                                    |

|     |     | 3.2.3 | Conclusions                                        |

| 4.0 |     | NATU  | URAL SWITCHING SURFACE CONTROL THEORY FOR THE DAB. 51                  |

|-----|-----|-------|------------------------------------------------------------------------|

|     | 4.1 | CON   | TROL MODE WITH FOUR SWITCHING SURFACES                                 |

|     |     | 4.1.1 | Simulation Validation for the Four Trajectory Mode                     |

|     | 4.2 | CON   | TROL MODE WITH SIX SWITCHING SURFACES 67                               |

|     |     | 4.2.1 | Simulation Example for the Six Trajectory Mode77                       |

|     | 4.3 | DEG   | REES OF FREEDOM AND PARAMETER SELECTION                                |

|     | 4.4 | CAS   | E STUDY OF BOUNDARY CONTROL FOR EFFICIENCY                             |

|     |     | 4.4.1 | Efficient Burst Mode Design for Operation during Light Loading         |

|     |     | 4.4.2 | NSS Burst Mode Case Study Results91                                    |

| 5.0 |     | BOUN  | NDARY CONTROL AS ACTIVE THERMAL CONTROL                                |

|     | 5.1 | TRA   | JECTORY STRATEGY DESIGN FOR LIFE PRESERVATION                          |

|     |     | 5.1.1 | Degrees of freedom and transient performance specific to Life Mode 107 |

|     | 5.2 | ACT   | IVE THERMAL BOUNDARY CONTROL FOR BOOST MODE 124                        |

|     | 5.3 | IMP   | ACT ASSESSMENT OF ACTIVE THERMAL BOUNDRY CONTROL 127                   |

|     |     | 5.3.1 | System Design Selections 127                                           |

|     |     | 5.3.2 | Efficiency Case Study Comparison128                                    |

|     |     | 5.3.3 | Implementing Burst Mode for Interval Based Loading133                  |

|     |      | 5.3.4 | Implementing Conventional Control for Interval Based Loading 138   |

|-----|------|-------|--------------------------------------------------------------------|

|     |      | 5.3.5 | Implementing ATBC for Interval Based Loading148                    |

|     |      | 5.3.6 | Concluding Impact Assessment171                                    |

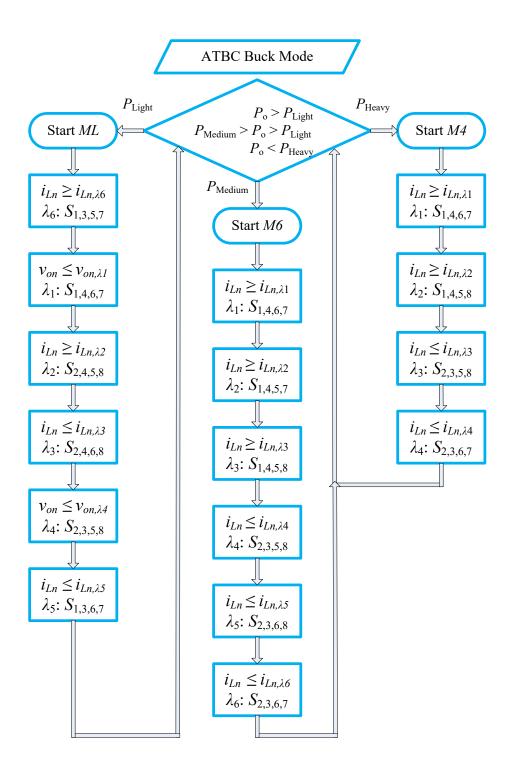

|     | 5.4  | ACT   | IVE THERMAL BOUNDARY CONTROL FOR BUCK MODE 174                     |

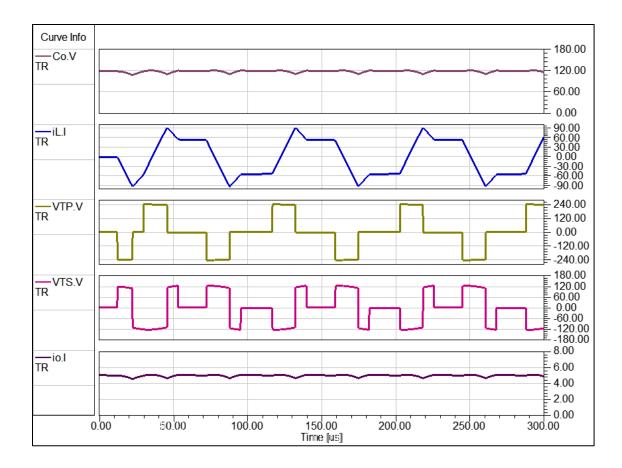

|     |      | 5.4.1 | Simulation Example of Life Preservation Mode in Buck Operation 180 |

| 6.0 |      | CONC  | CLUSIONS 182                                                       |

|     | 6.1  | RESI  | EARCH DIRECTIONS AND APPLICATIONS                                  |

| AP  | PEND | DIX A |                                                                    |

| BIB | BLIO | GRAPH | IY 189                                                             |

# LIST OF TABLES

| Table 1: Typical Lifetime Targets for Various Power Electronics Applications [3]2                      |

|--------------------------------------------------------------------------------------------------------|

| Table 2: Focus Points Matrix for Reliability of Power Electronic Components    3                       |

| Table 3: DG Inverter System Parameters for Reactive Compensation Implementation                        |

| Table 4: Filter Parameters for Various Inverter Switching Frequencies       34                         |

| Table 5: System Parameters for VSM Implementation    41                                                |

| Table 6: VSM Control Parameter Definitions    44                                                       |

| Table 7: VSM Control Parameter Values    44                                                            |

| Table 8: Four Natural Switching Surface Configurations    57                                           |

| Table 9: Parameters for Four Trajectory Validation Simulation    63                                    |

| Table 10: Six Natural Switching Surface Configurations for Buck Mode       70                          |

| Table 11: Six Natural Switching Surface Configurations for Boost Mode       70                         |

| Table 12: Parameters for Validation Simulation for Six Trajectory Mode    77                           |

| Table 13: Six Natural Switching Surface Configurations for M6    86                                    |

| Table 14: Six Natural Switching Surface Configurations for Burst Mode (MB)                             |

| Table 15: Modes of Natural Switching Surface Trajectories Summarized for Efficiency Case Study      87 |

|                                                                                                        |

Table 16: Parameters for Efficiency Case Study Simulation Implementing Three Strategic Modes

91

Table 17: Switching Surface Alterations for Initial Step in Designing Life Preservation Mode . 98 Table 18: Eight Natural Switching Surface Configurations for Life Preservation Mode (ML). 100 Table 19: Summarized Modes of NSS Control Operation when Prioritizing Life Preservation 104 Table 20: Simulation Parameters for Degrees of Freedom and Transient Performance Assessments Table 21: Life Preservation Mode of Control Degrees of Freedom Parametric Sensitivity Analysis Table 22: Base Parameters for Validation Simulations Implementing Various Control Modes 128 Table 23: Parameters for Efficiency Case Study Comparison Implementing ML ...... 129 Table 25: Parameters for Case 1 of Conventional Control in Thermal Cycling Assessment..... 138 Table 26: Parameters for Case 2 of Conventional Control in Thermal Cycling Assessment..... 138 Table 27: Simulation Parameters for ATBC Implemented during Interval Based Loading Table 28: Collected Worst Case Thermal Cycling Results for MOSFETS from Impact Assessment Table 29: Collected Worst Case Thermal Cycling Results for Schottky Diodes from Impact

Table 30: Percentage Improvements using ATBC for Corresponding Current Control Targets 174

| Table 31: Six Natural | Switching | Surface | Configurations | of Life | Preservation | Mode 1 | for Buck |

|-----------------------|-----------|---------|----------------|---------|--------------|--------|----------|

| Operation             | •••••     |         | ••••••         |         |              |        | 175      |

| Table 32: Summarized Design of NSS Control Operation when Prioritizing Li | fe Preservation in |

|---------------------------------------------------------------------------|--------------------|

| Buck Operation                                                            |                    |

# LIST OF FIGURES

| Figure 1: Economic Progress and Goals for the DOE SunShot Program [2]                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Critical reliability stressors for power electronic systems by application, an industry perception                                                                   |

| Figure 3: Defining the scope of (a) power electronics research according to William E. Newell in 1974 [17] and (b) power electronics reliability research trends today [13] 10 |

| Figure 4: Cross section of an IGBT module with highlighted physical points of contact relevant to device lifetime [14]                                                         |

| Figure 5: IGBT bond wire damage: (a) cracking and lift-off (b) bond wire lift-off [14] 12                                                                                      |

| Figure 6: Power cycling lifetime in relation to cycling amplitude and mean temperature for an IGBT module [14]                                                                 |

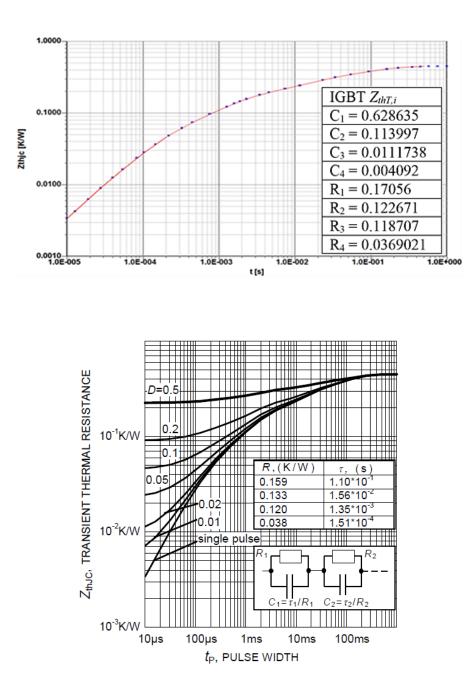

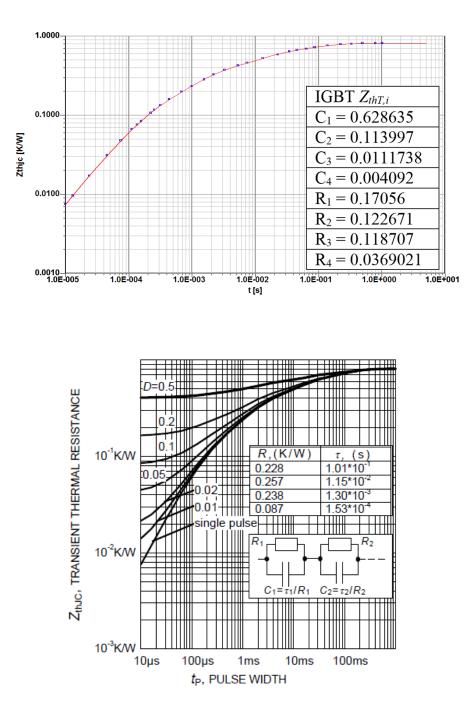

| Figure 7: Transient Thermal Impedance Foster Networks                                                                                                                          |

| Figure 8: Transient Thermal Impedance Model for the SiC MOSFET. Model (above) and<br>Manufacturer (below)                                                                      |

| Figure 9: Transient Thermal Impedance Model for Si IGBT. Simulation Model (above) and<br>Manufacturer Measurement (below)                                                      |

| Figure 10: Transient Thermal Impedance Model for Si Anti-parallel Diode. Simulation Model (above) and Manufacturer Measurement (below)                                         |

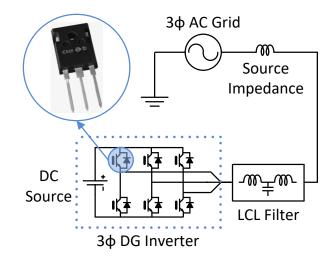

| Figure 11: Example Microgrid System (a) and Modeled System (b)                                                                                                                 |

| Figure 12: VSC Control System Implemented for Reactive Current Injection Control 30                                                                                            |

| Figure 13: Maximum Compensation according to Rated Inverter Capacity                                                                                                           |

| Figure 14: Control of Reactive Compensation for Voltage Instability Events with the injection<br>Ramp Rate Defined                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Figure 15: Junction Temperature on Phase A Upper SiC MOSFET with (above) and without (below) Reactive Compensation                      |

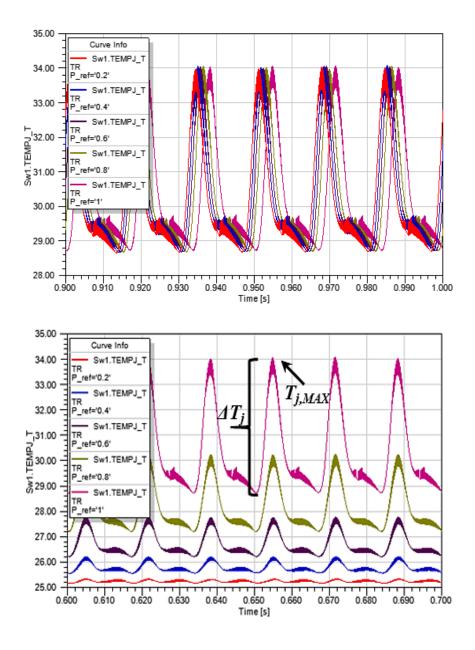

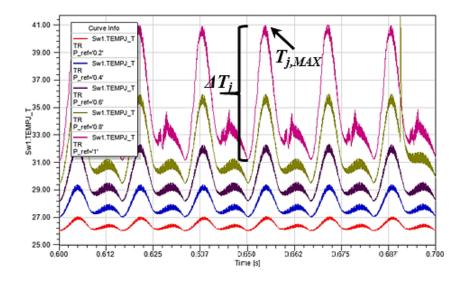

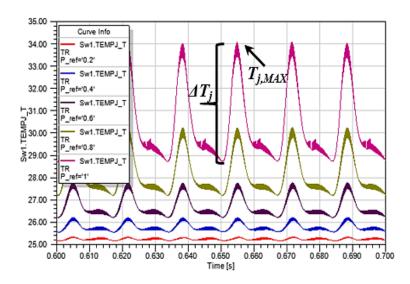

| Figure 16: Junction Temperature on Phase A Upper IGBT during steady state (Pref = 0.2 - 1.0 p.u.)                                       |

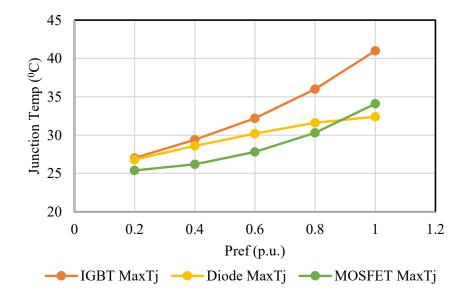

| Figure 17: Comparing Maximum Junction Temperature for SiC MOSFET and Si IGBT and Diode with respect to Reference Power                  |

| Figure 18: Modeled DG Inverter System                                                                                                   |

| Figure 19: Voltage source converter dq control interfaced with system                                                                   |

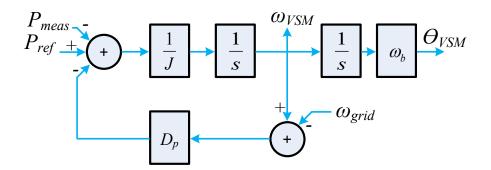

| Figure 20: Swing equation implemented into system control architecture                                                                  |

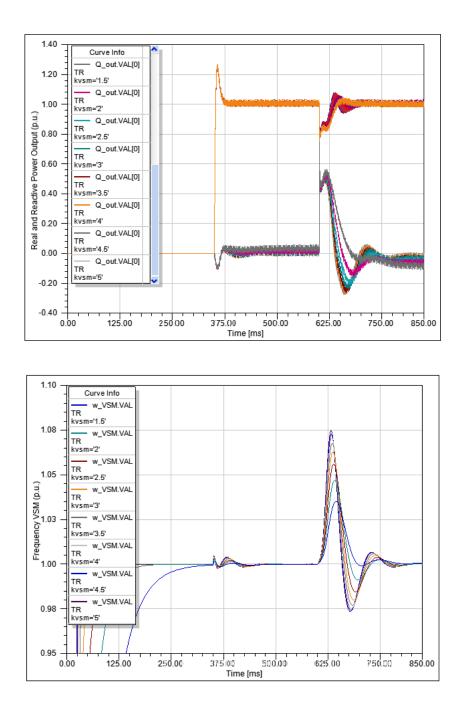

| Figure 21: Real and reactive power output of inverter (top) and associated change in VSM frequency (bottom) for varying values of Dp, J |

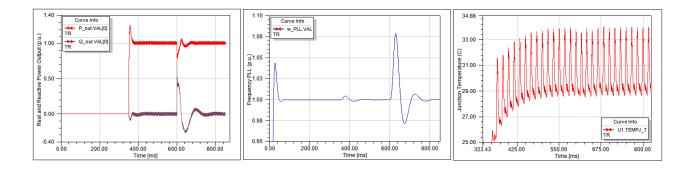

| Figure 22: The dq current regulated PLL power, frequency, and thermal responses with a 30 degree phase shift on grid                    |

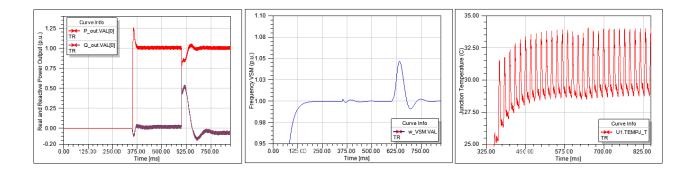

| Figure 23: The VSM power, frequency, and thermal responses with a 30 degree phase shift on grid $(Dp = 20, J = 2)$                      |

| Figure 24: Junction temperature on phase A Upper SiC MOSFET for varying load requirements                                               |

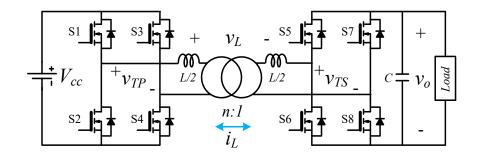

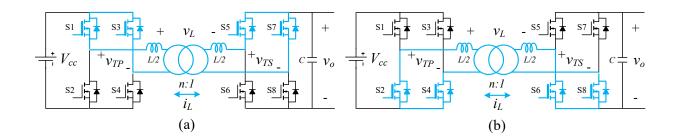

| Figure 25: DC/DC Isolated Bidirectional Power Converter the Dual Active Bridge (DAB) 52                                                 |

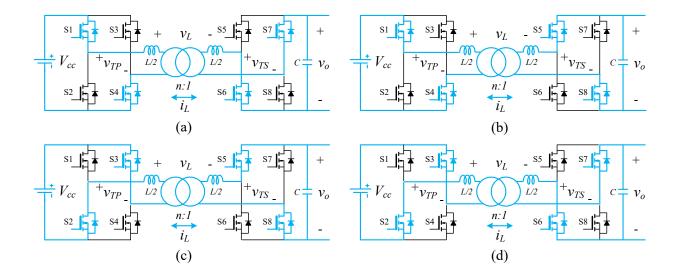

| Figure 26: Four switching structures of the dual active bridge for power delivery                                                       |

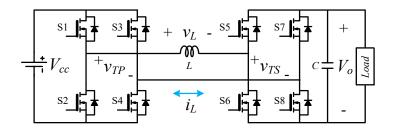

| Figure 27: Dual Active Bridge Circuit Considering only Leakage Inductance for Simplified<br>Analysis                                    |

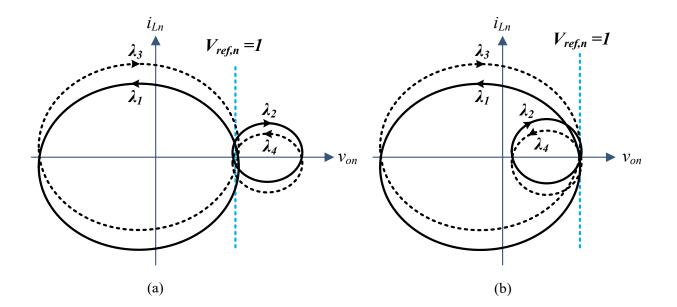

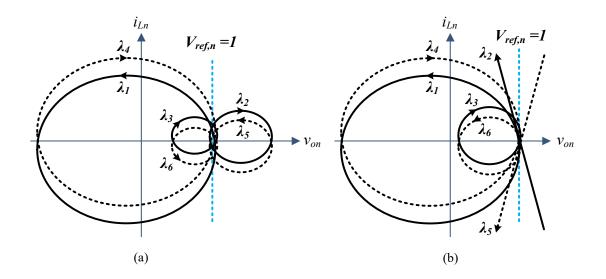

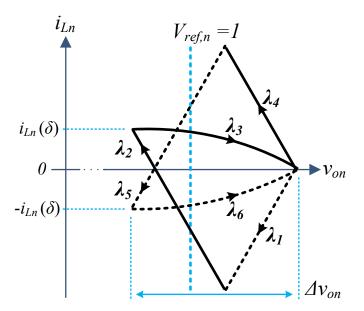

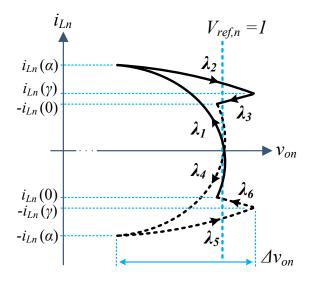

| Figure 28: Normalized natural switching surfaces of the DAB in the (a) buck and (b) boost modes of operation                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 29: Steady state conceptually of normalized natural switching surfaces for the DAB in the (a) buck and (b) boost modes of operation                                             |

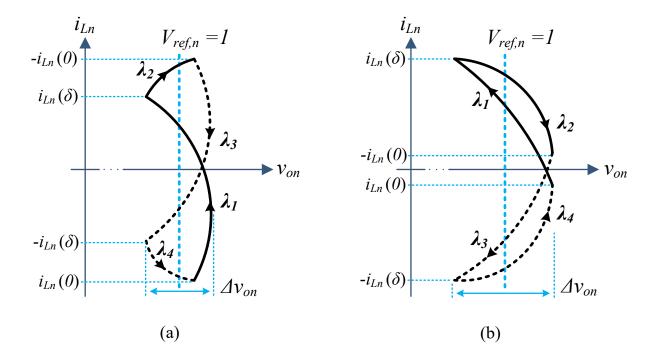

| Figure 30: Steady state operation of the DAB in boost mode showing (a) state plane and (b) corresponding waveforms                                                                     |

| Figure 31: Modification of natural trajectory $\lambda 2$                                                                                                                              |

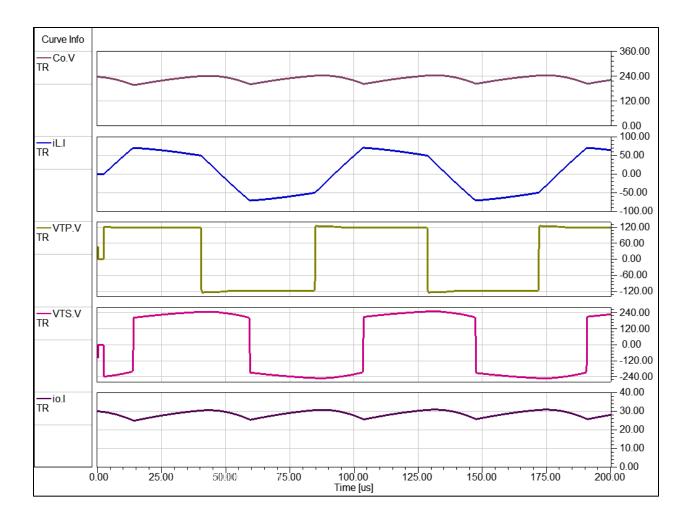

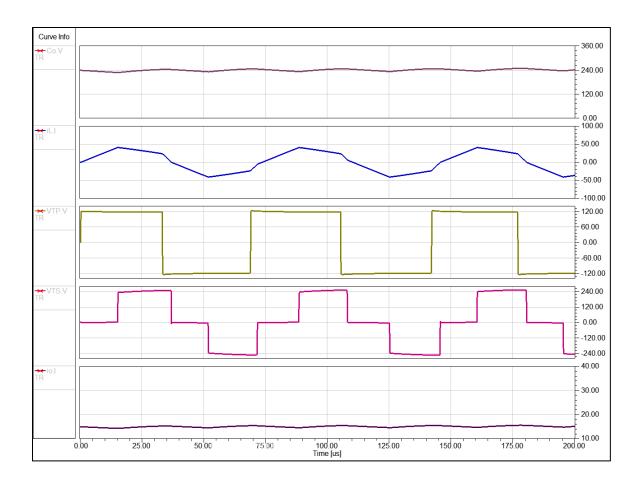

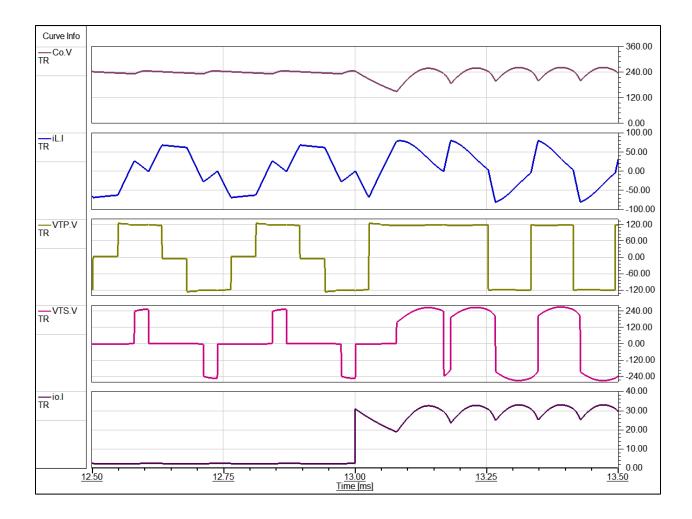

| Figure 32: Results of output voltage, transformer current, primary and secondary voltage, and output current for Validation of M4                                                      |

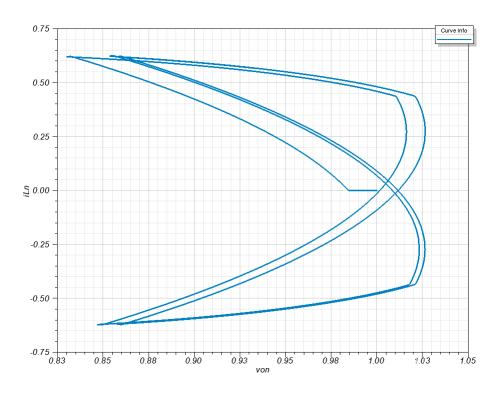

| Figure 33: Normalized state plane result for M4 operating under heavy loading 65                                                                                                       |

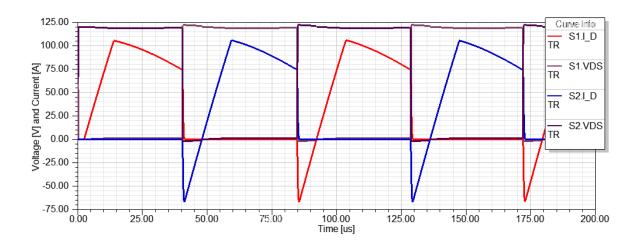

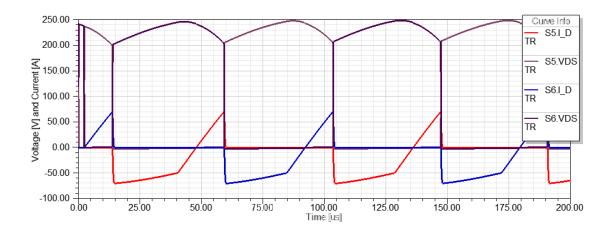

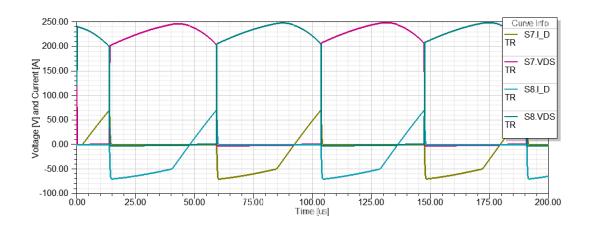

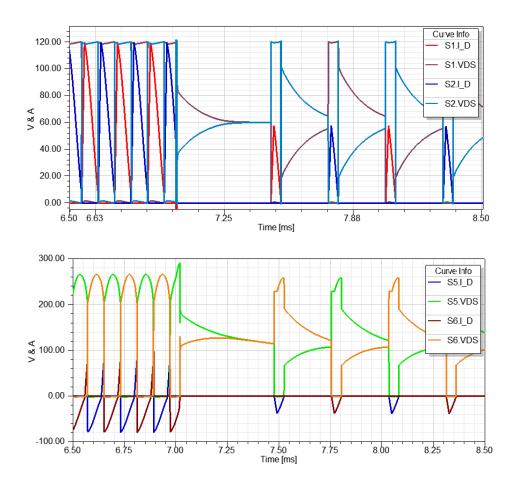

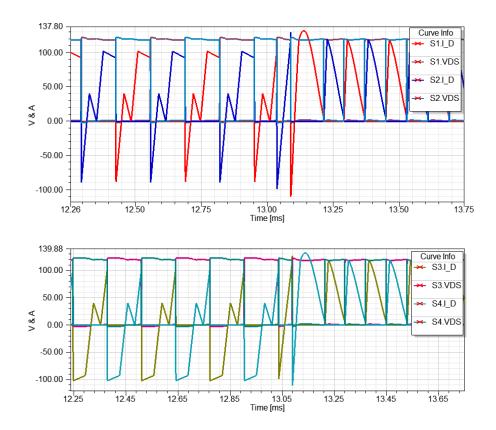

| Figure 34: Voltage VDS and Current ID for both S1 and S2                                                                                                                               |

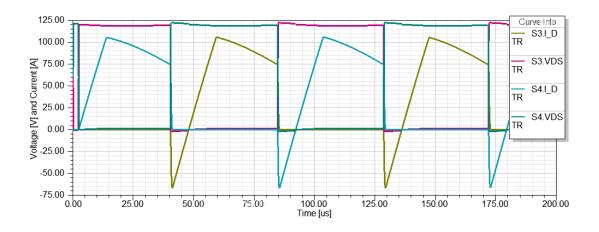

| Figure 35: Voltage VDS and Current ID for both S3 and S4                                                                                                                               |

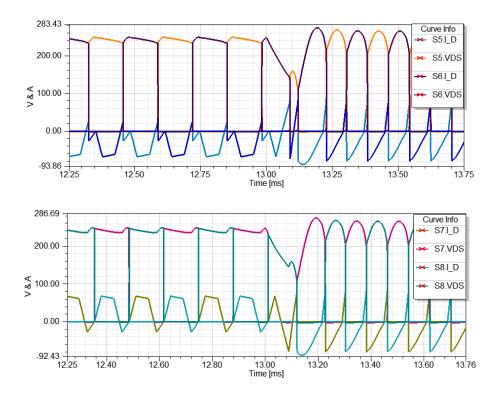

| Figure 36: Voltage VDS and Current ID for both S5 and S6                                                                                                                               |

| Figure 37: Voltage VDS and Current ID for both S7 and S8                                                                                                                               |

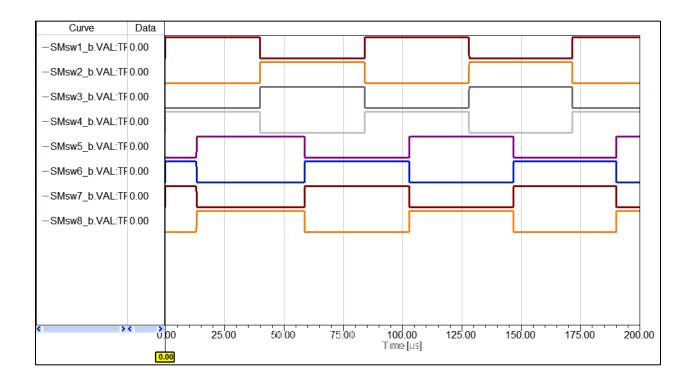

| Figure 38: Binary Gate Signals to all Devices Demonstrating Conventional Dual Active Bridge<br>Control with M4                                                                         |

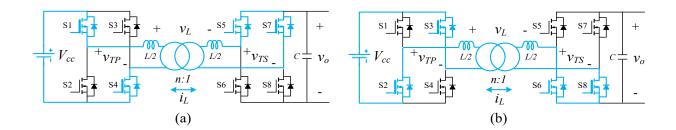

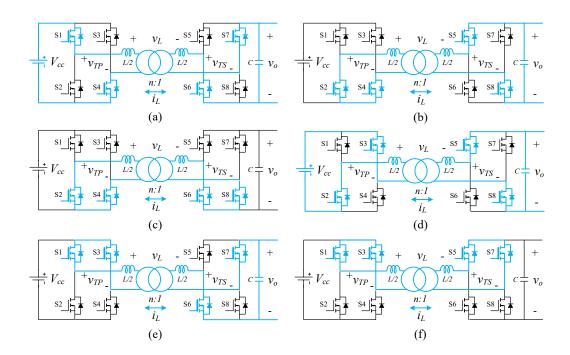

| Figure 39: Additional Switching Structures Used in a Mode of Six Strategic Trajectories (M6) 68                                                                                        |

| Figure 40: Normalized Natural Switching Surfaces of the Six Trajectory Strategy (M6) for buck (a) and boost (b)                                                                        |

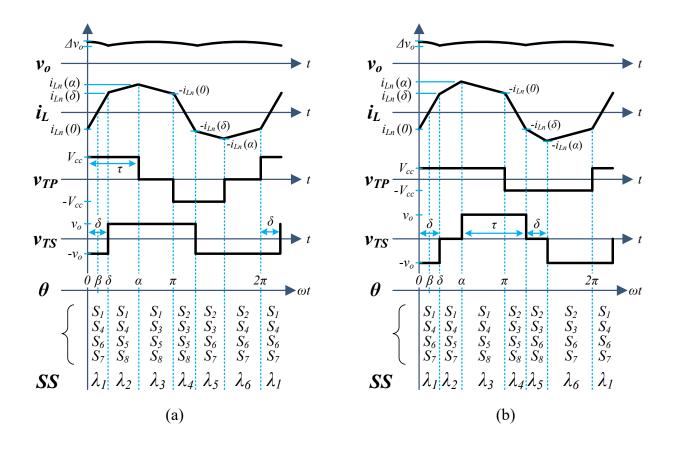

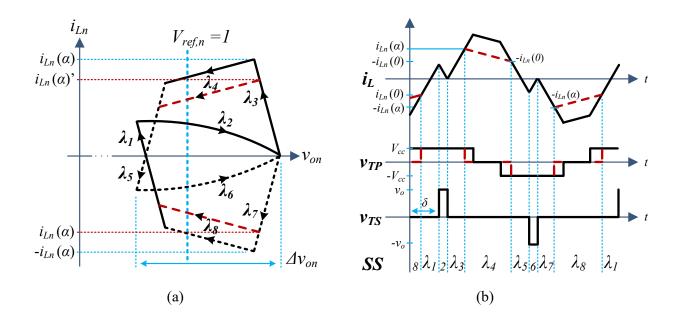

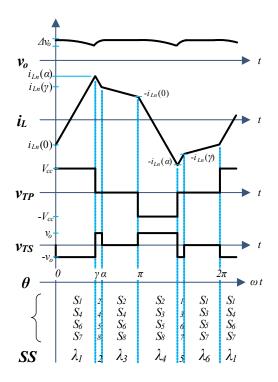

| Figure 41: Steady state operating waveforms for the strategic trajectory case study showing (a) buck and (b) boost modes, showing the conducting switches per switching surface (SS)71 |

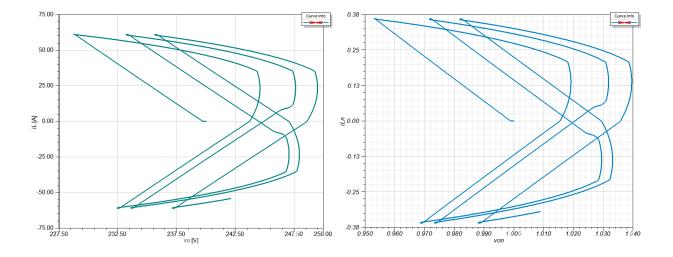

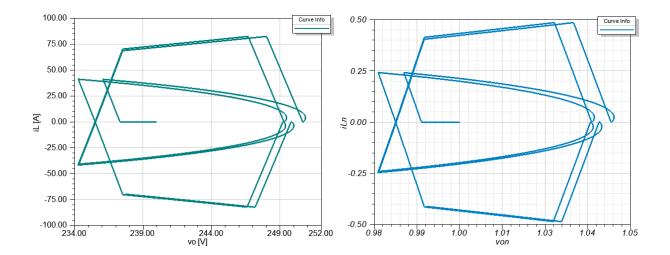

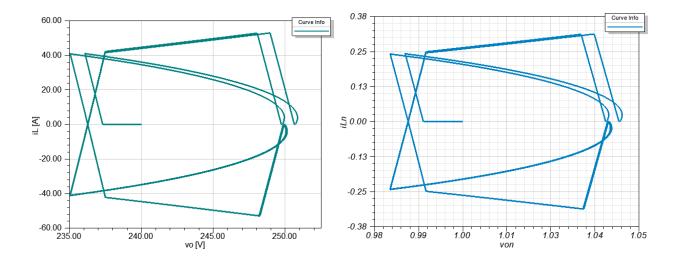

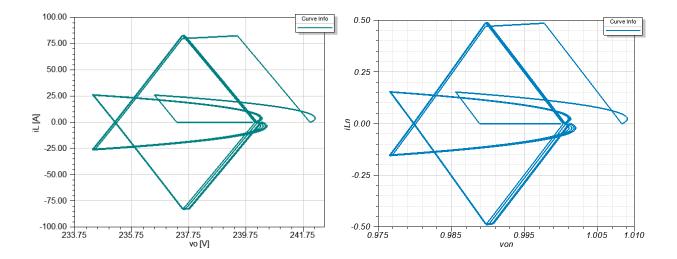

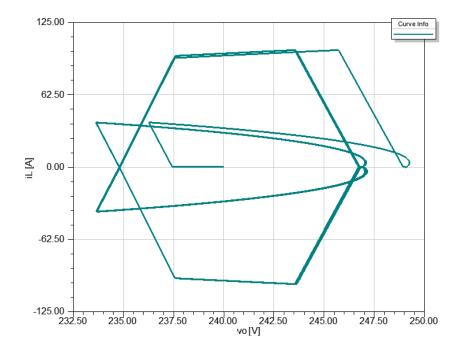

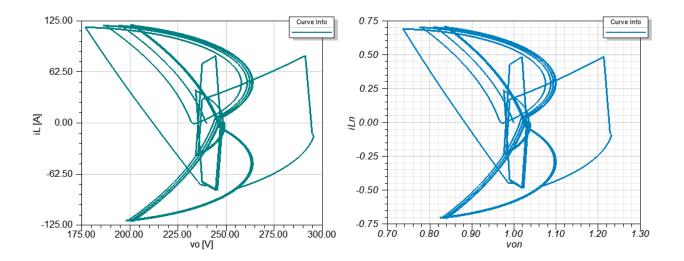

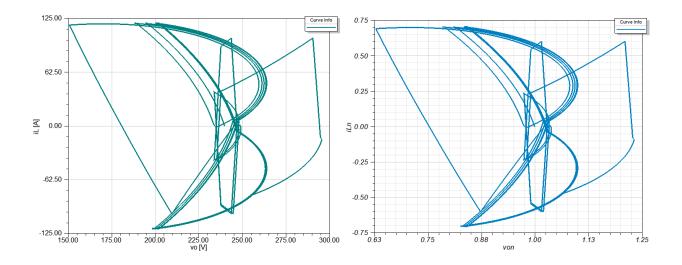

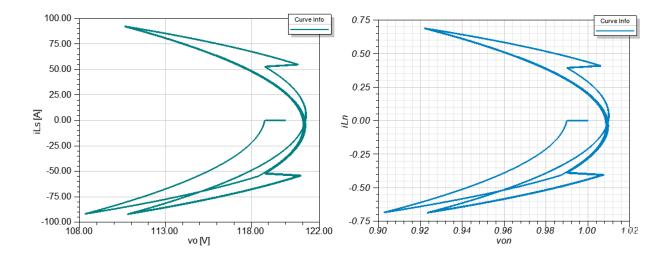

| Figure 43: State plane results, both normalized and not, for M6 operating under medium loading                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

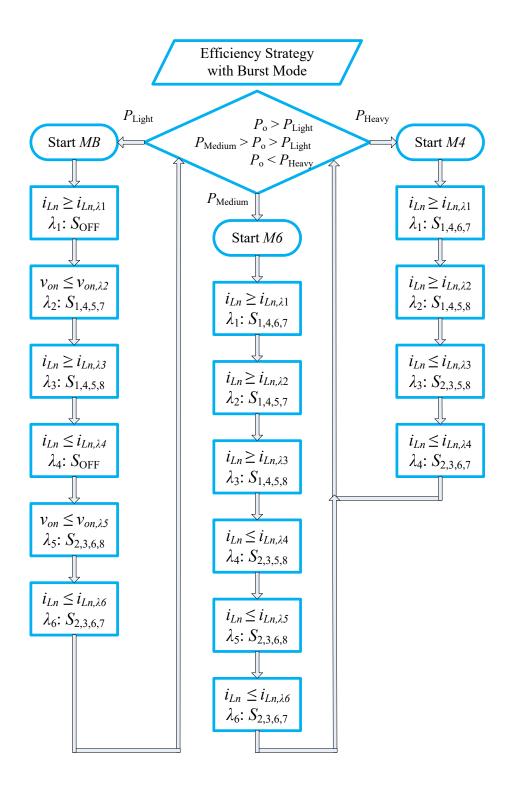

| Figure 44: Flowchart Summarizing the Control Operation of MB Coupled M4 and M6 for Efficient<br>Operation                                                            |

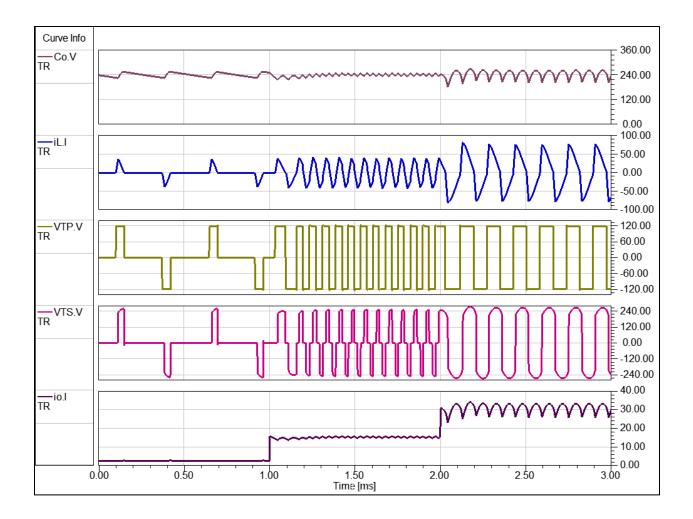

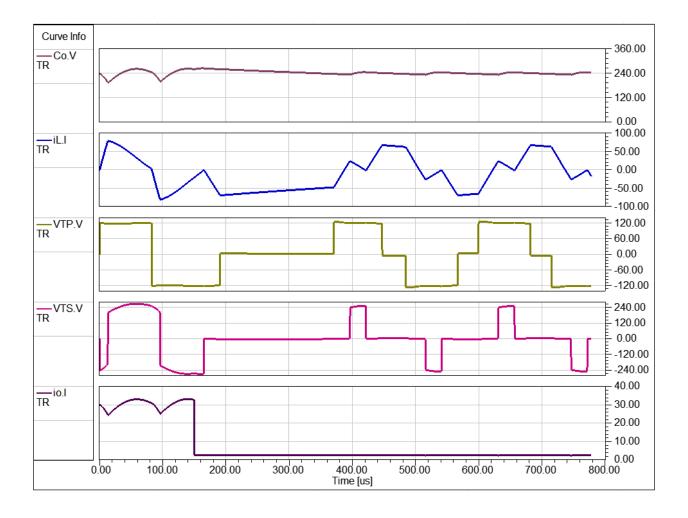

| Figure 45: Outputs of Efficiency Case Study Performing Three Strategic Modes for Three Levels<br>of Power Demand                                                     |

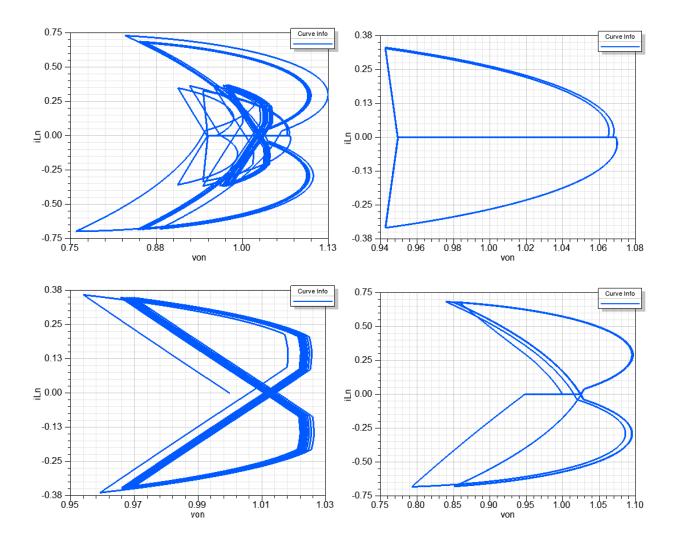

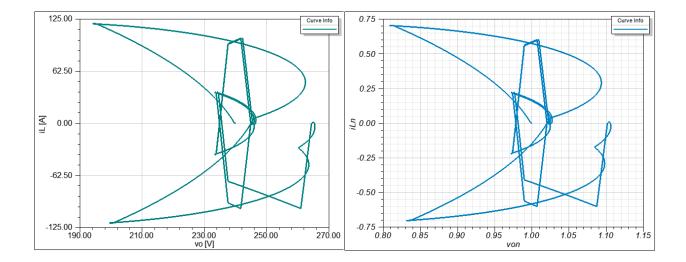

| Figure 46: State Plane for Efficiency Case Study, in total and divided into differing modes MB, M6, and M4                                                           |

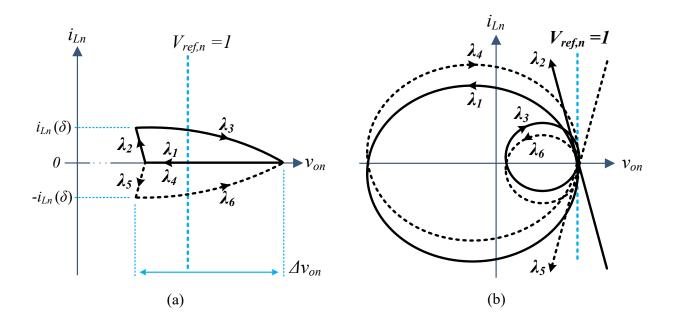

| Figure 47: Conceptual diagrams of MB in operation (a) and the natural switching surfaces of boost mode (b)                                                           |

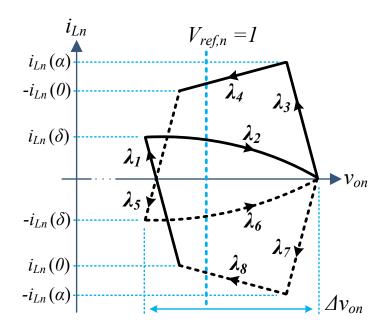

| Figure 48: Conceptual State Plane Result of Modified MB for Increased Conduction Loss 99                                                                             |

| Figure 49: Switching Configurations for λ4 (a) and λ8 (b) of Life Mode Design Realizing<br>Circulating Conduction                                                    |

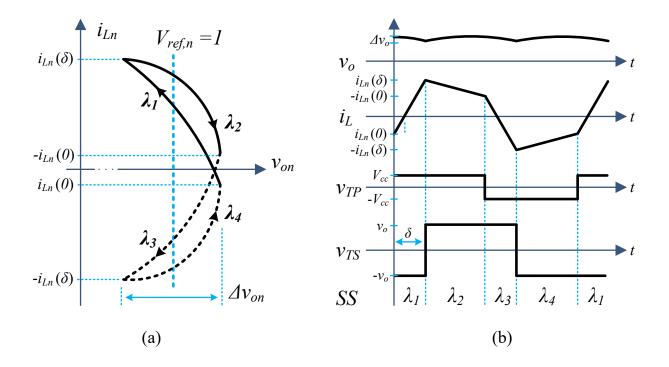

| Figure 50: Conceptual State Plane of Life Preservation Mode Final Design in Boost Operation                                                                          |

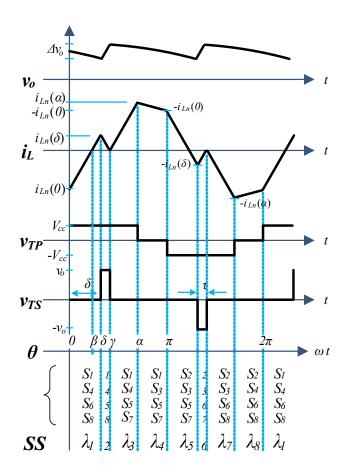

| Figure 51: Steady state operating waveforms for life preservation mode, showing the conducting switches per switching surface (SS) in the boost operation            |

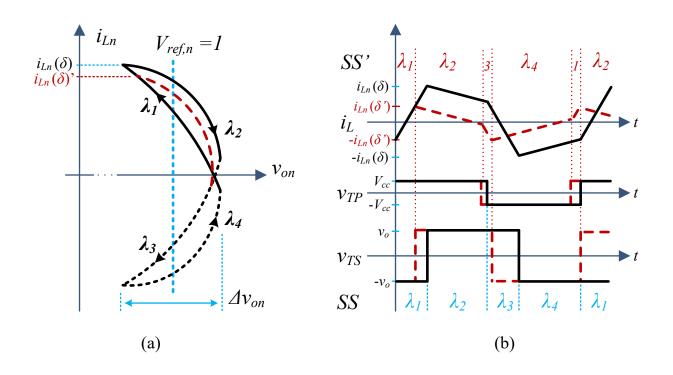

| Figure 52: Conceptual Modification to Life Preservation Mode with ILn,max as a Control Handle showing the Normalized State Plane and Associated System Waveforms 108 |

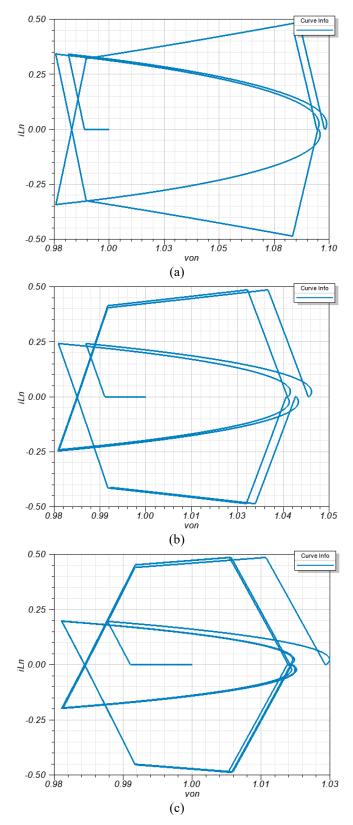

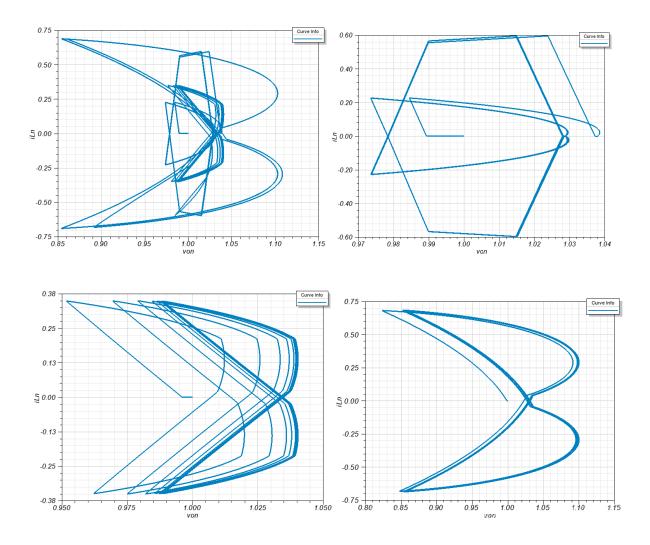

| Figure 53: Sensitivity state plane analysis of the impact of m variation where (a) m=0.1, (b) m=0.25, and (c) m=0.4                                                  |

| Figure 54: Transient performance of the life preservation mode showing a transition from M4 to ML at loading conditions of 7.2kW and 600W respectively               |

| Figure 55: State plane nominal and normalized associated with transient performance transitioning from M4 to ML |

|-----------------------------------------------------------------------------------------------------------------|

| Figure 56: Base Case of ML Parametric Analysis 112                                                              |

| Figure 57: Base Case State Plane Analysis both Nominal and Normalized 113                                       |

| Figure 58: Case 1 of ML Parametric Analysis with Maximum Current Increased to 100A 114                          |

| Figure 59: Case 1 State Plane Analysis both Nominal and Normalized with Maximum Current<br>Increased to 100A    |

| Figure 60: Case 2 of ML Parametric Analysis with Maximum Current Decreased to 50A 116                           |

| Figure 61: Case 2 State Plane Analysis both Nominal and Normalized with Maximum Current<br>Decreased to 50A     |

| Figure 62: Case 3 of ML Parametric Analysis with the Modulation Index at 0.1 118                                |

| Figure 63: Case 3 State Plane Analysis both Nominal and Normalized with the Modulation Index<br>at 0.1          |

| Figure 64: Case 4 of ML Parametric Analysis with the Modulation Index at 0.4 120                                |

| Figure 65: Case 4 State Plane Analysis both Nominal and Normalized with the Modulation Index<br>at 0.4          |

| Figure 66: Case 5 of ML Parametric Analysis with the Switching Frequency at 20kHz 122                           |

| Figure 67: Case 5 State Plane Analysis both Nominal and Normalized with the Switching<br>Frequency at 20kHz     |

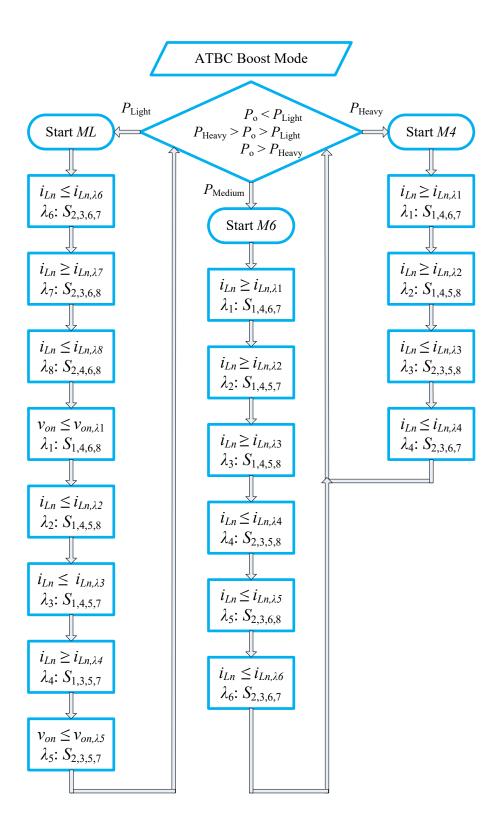

| Figure 68: Flowchart of Active Thermal Boundary Control in Boost Mode of Operation 126                          |

| Figure 69: Comparative Study between Burst Mode for the Efficiency Case Study and Life<br>Preservation Mode     |

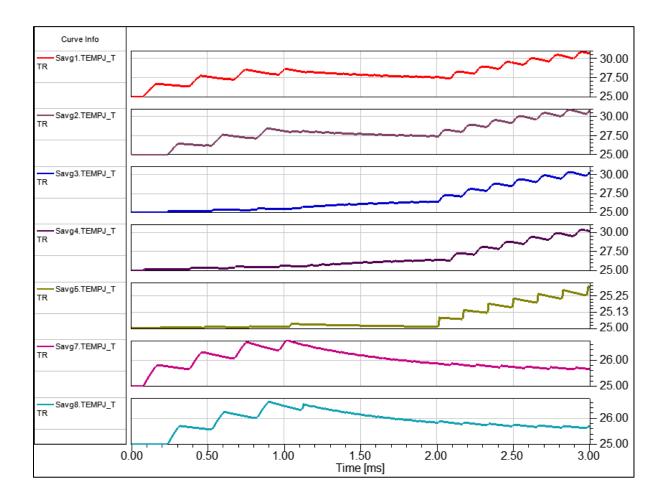

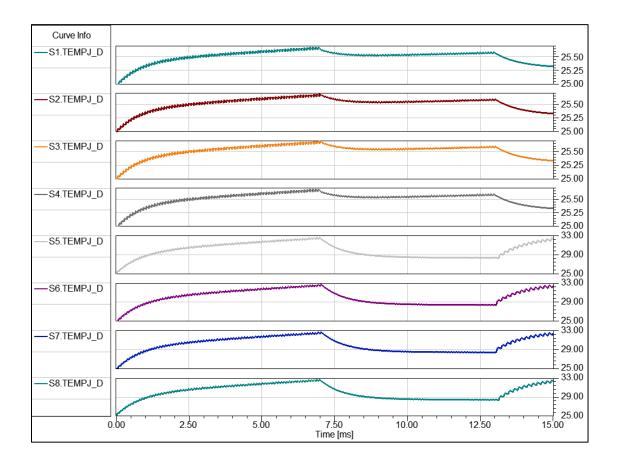

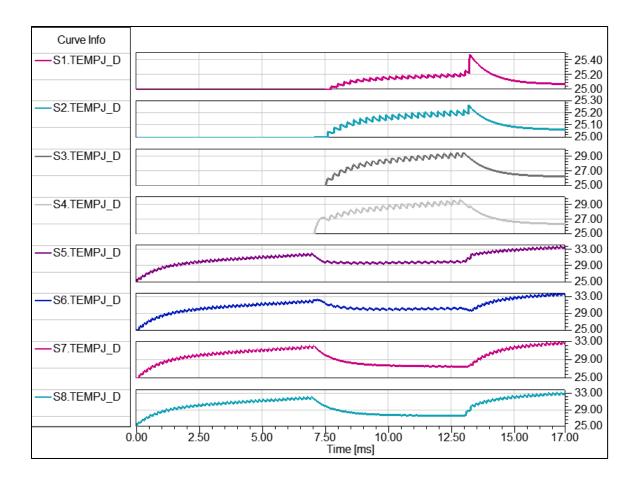

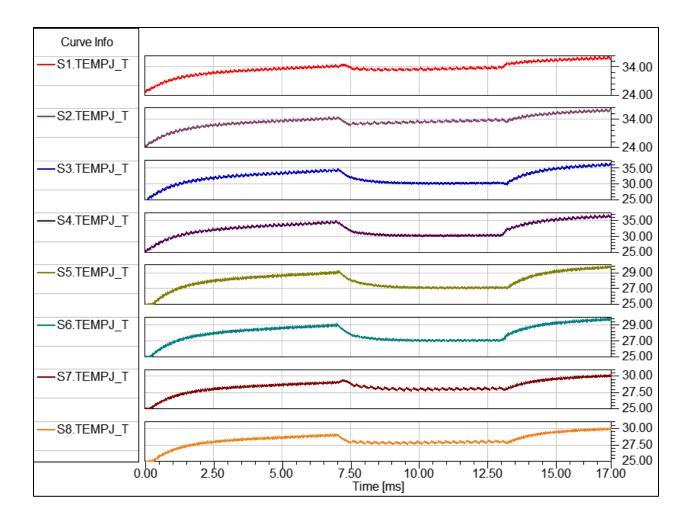

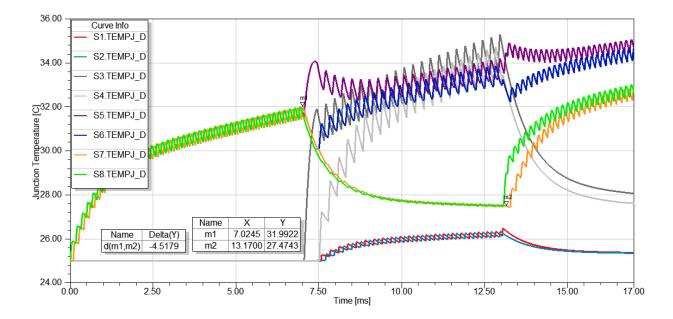

| Figure 70: Junction Temperature per MOSFET for Case Study Comparison Employing ML in<br>Light Loading                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 71: Binary Gate Signals for the Duration of the Case Study Comparison Employing ML in<br>Light Loading                                                                                                       |

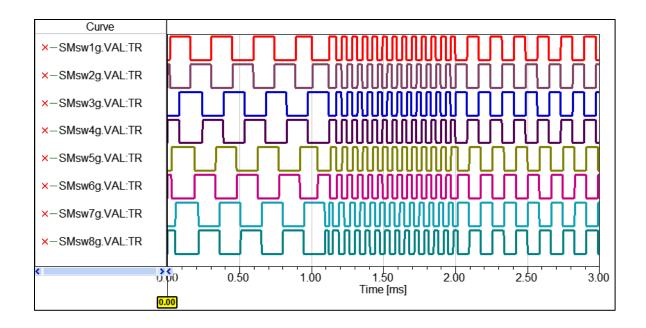

| Figure 72: Nominal State Plane of ML for Case Study Comparison Employing ML in Light<br>Loading                                                                                                                     |

| Figure 73: Normalized State Plane for Case Study Comparison Employing ML in Light Loading,<br>Including Entire Duration (top left) and Subdivided State Planes per Trajectory Mode (left<br>to right top to bottom) |

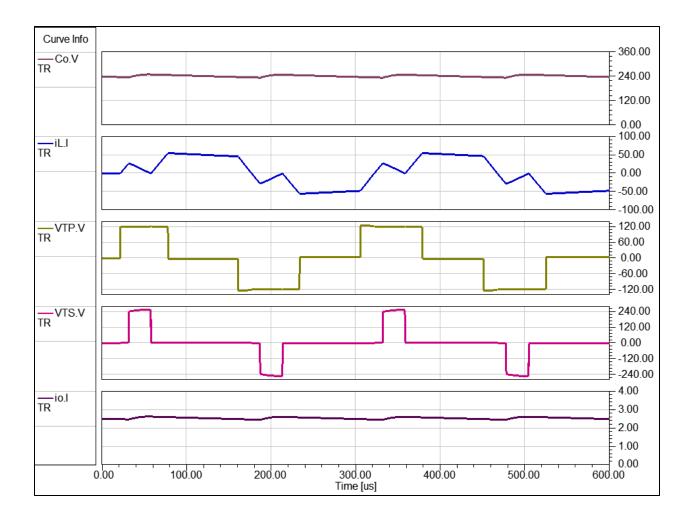

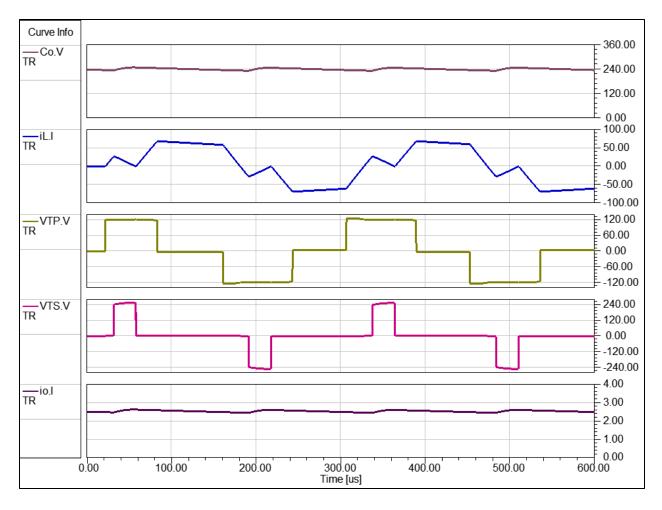

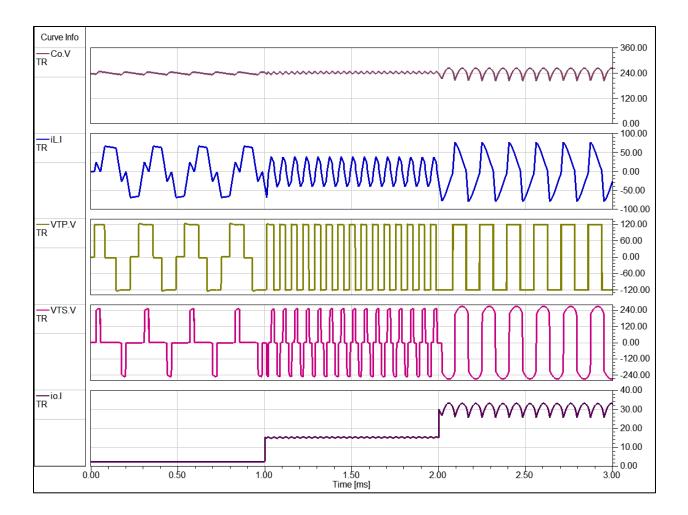

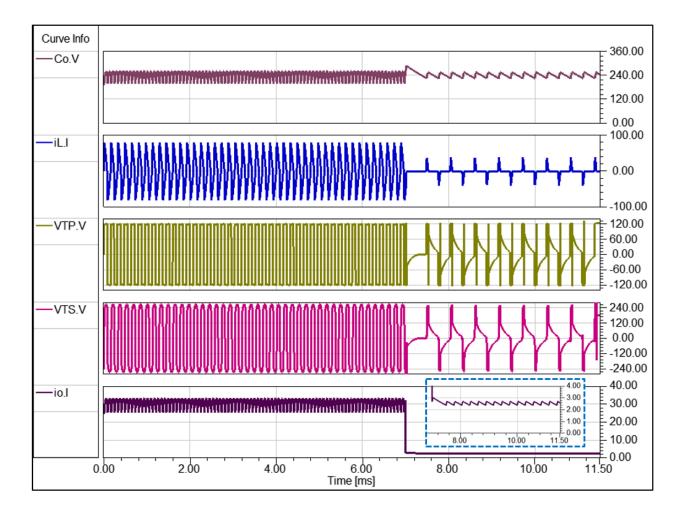

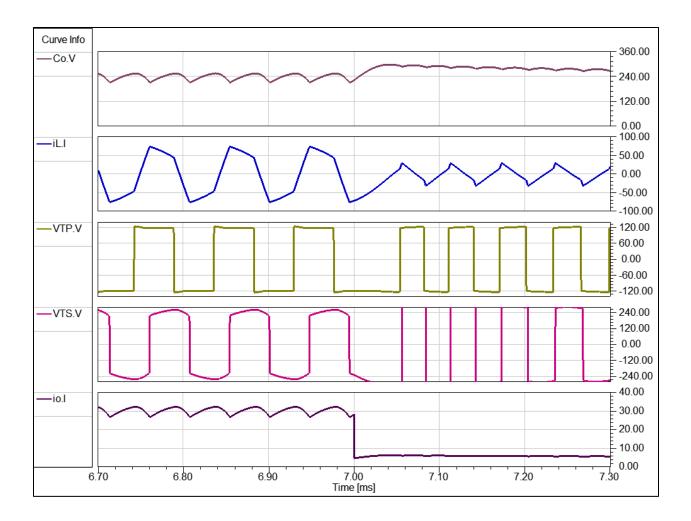

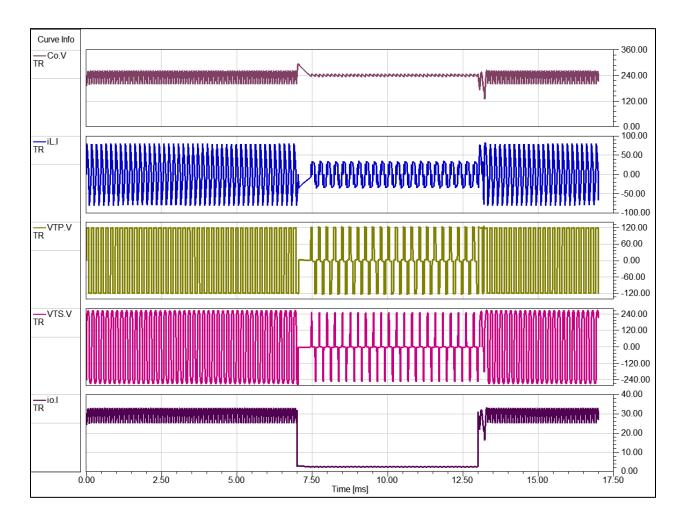

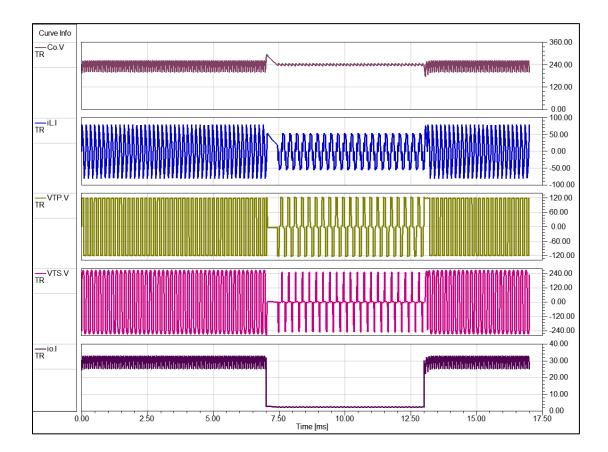

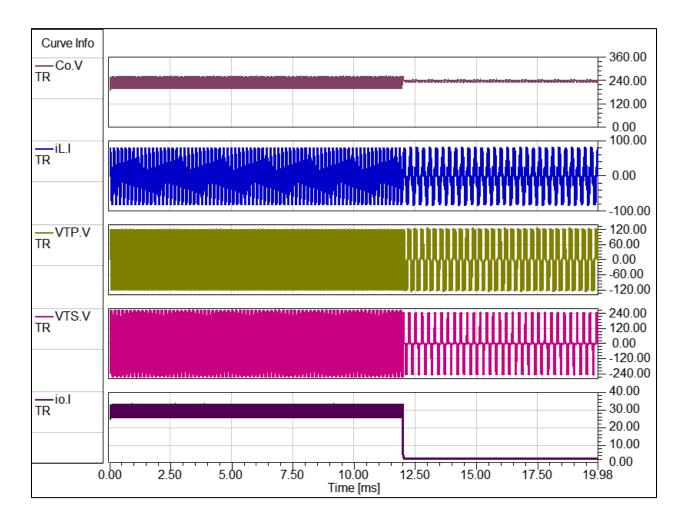

| Figure 74: System Waveforms during Interval Loading Employing MB during Light Load 135                                                                                                                              |

| Figure 75: Junction Temperatures for Each MOSFET during Interval Loading Employing MB in<br>Light Load                                                                                                              |

| Figure 76: Junction Temperatures for all MOSFETs and ΔTj during Interval Loading Employing MB in Light Load                                                                                                         |

| Figure 77: VDS and ID for switches S1, S2, S5, and S6 during MB operation 137                                                                                                                                       |

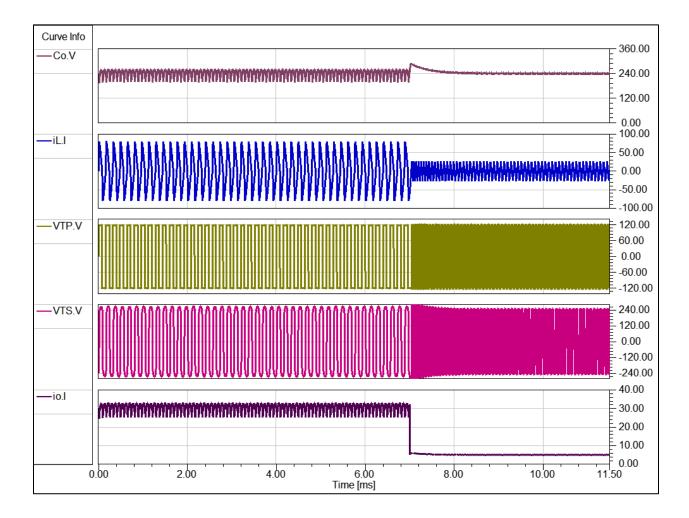

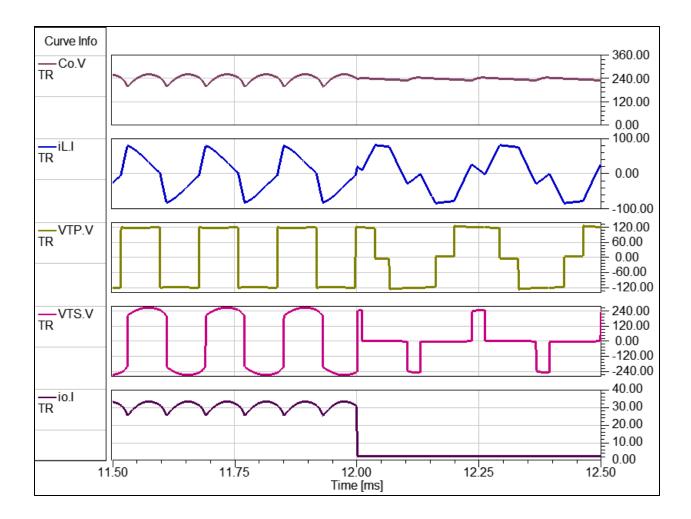

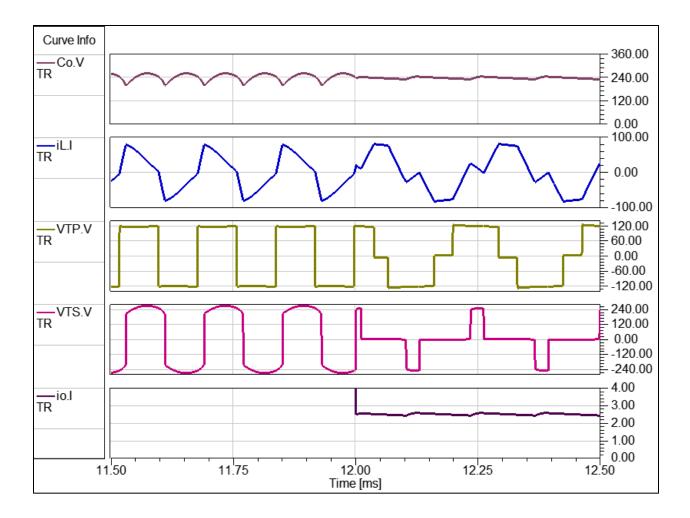

| Figure 78: System Waveforms during Interval Loading Employing Conventional Control for all Loads Case 1                                                                                                             |

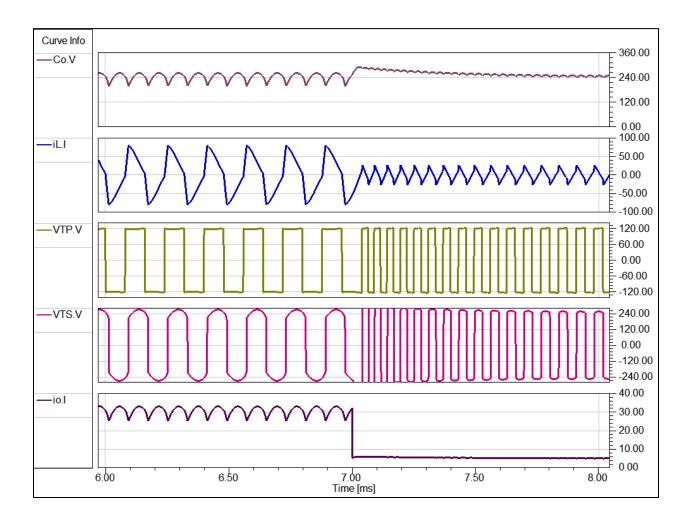

| Figure 79: System Waveforms Transient Performance using Conventional Control Case 1 140                                                                                                                             |

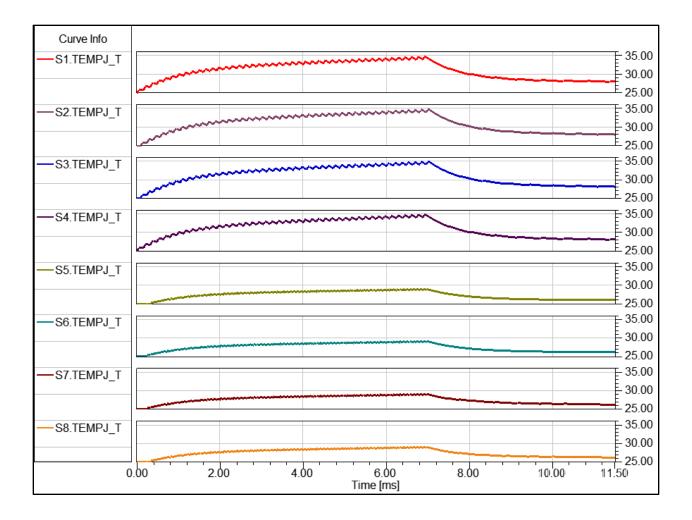

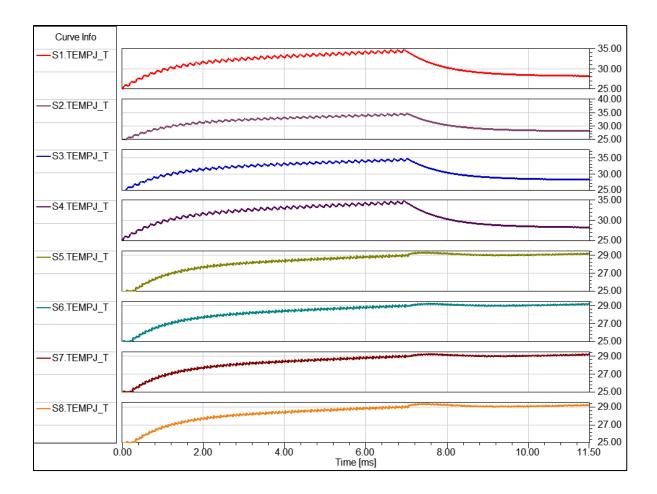

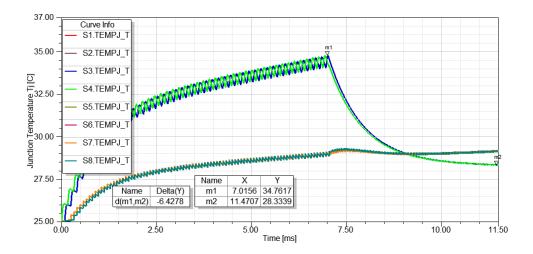

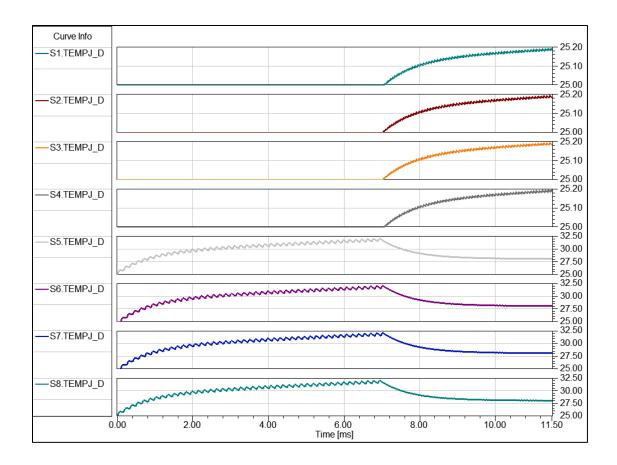

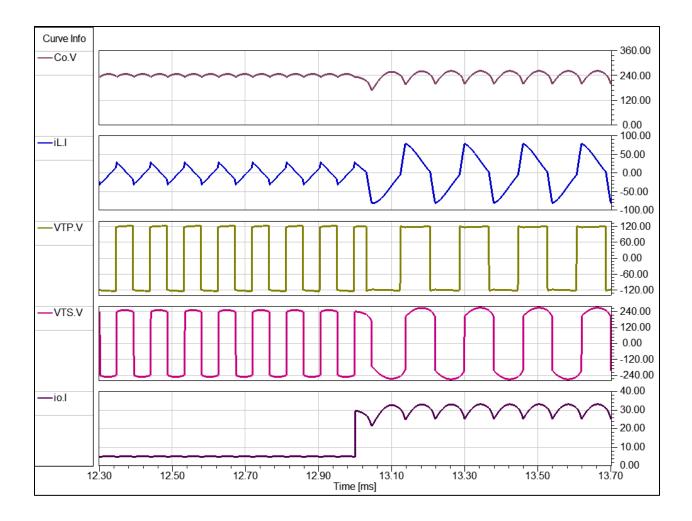

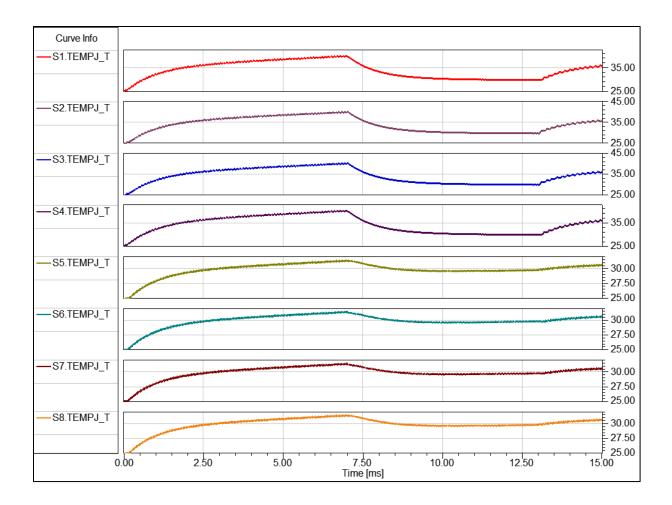

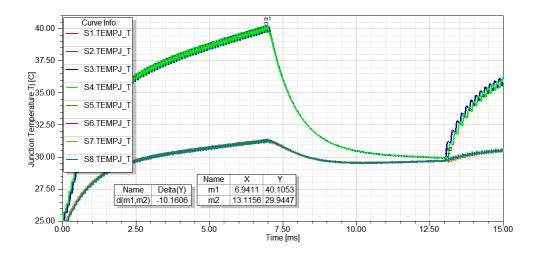

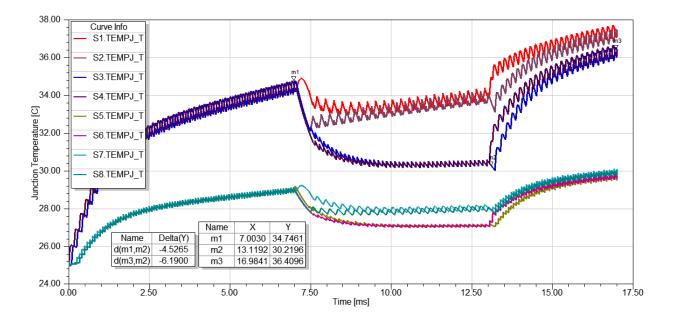

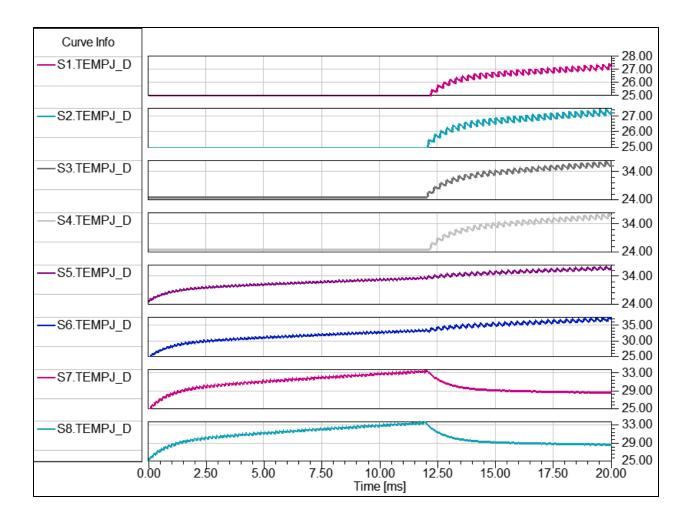

| Figure 80: Junction Temperatures for each MOSFET Employing Conventional Control Case 1                                                                                                                              |

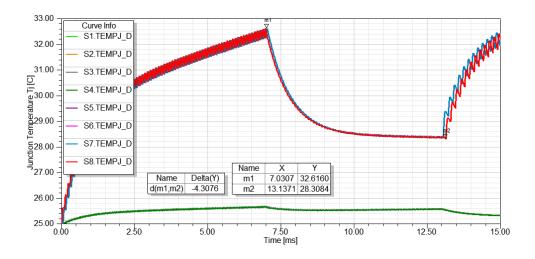

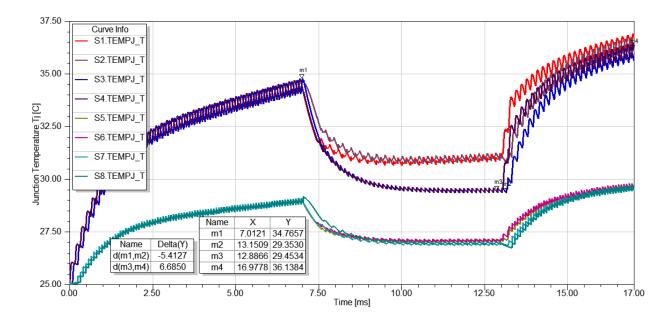

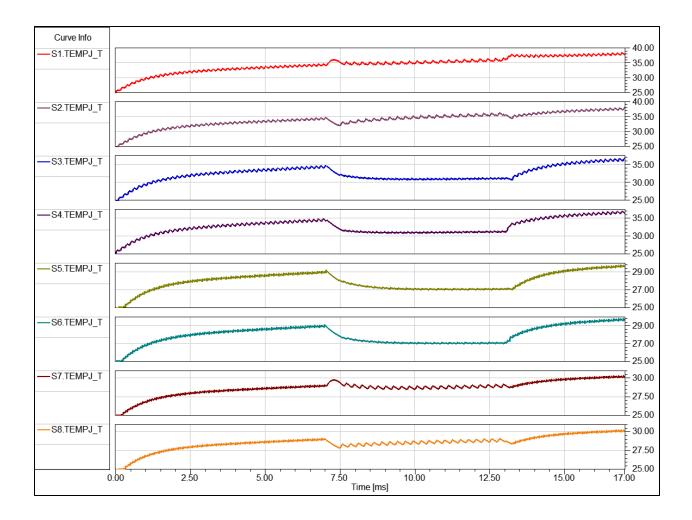

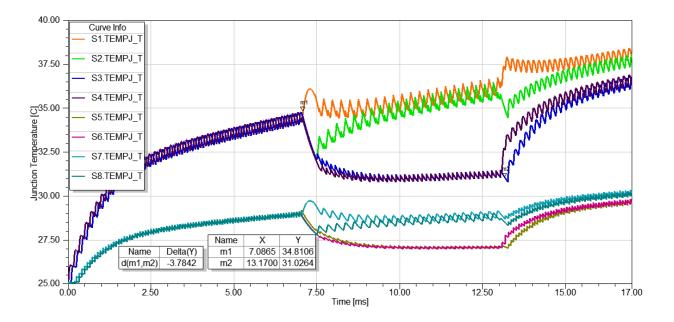

| Figure 81: Junction Temperatures for each MOSFET Superimposed with Delta Marker<br>Measurement Case 1                                                                                                               |

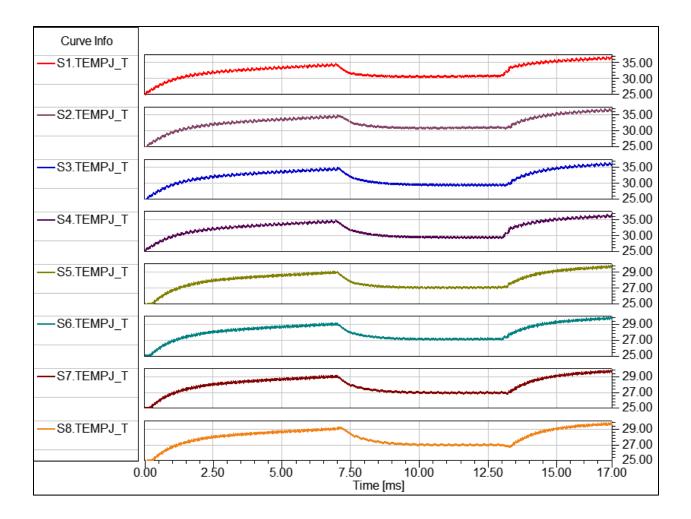

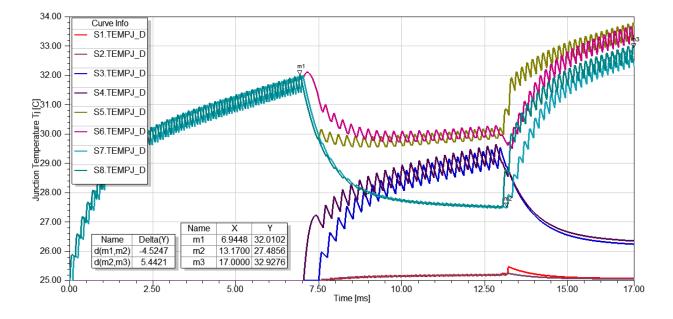

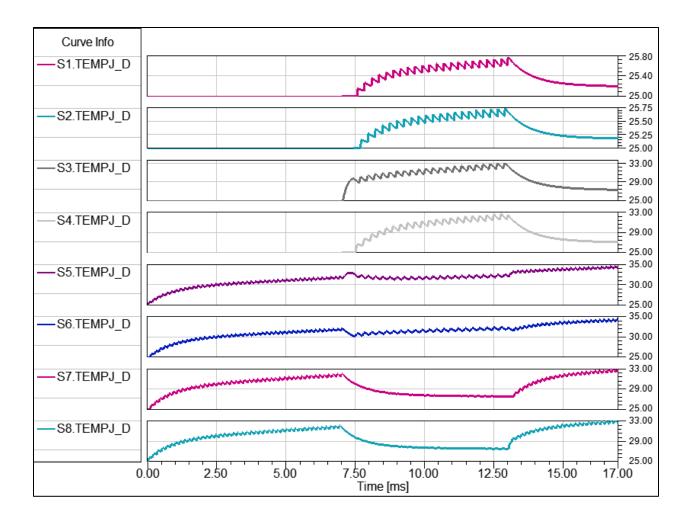

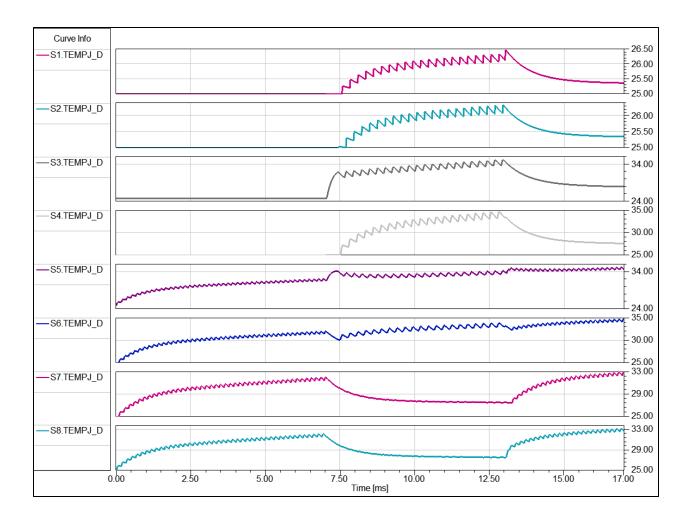

| Figure 82: Junction Temperatures for each Schottky Diode Employing Conventional Control Case 1                                                                                                                      |

| Figure 83: Junction Temperatures for each Diode Superimposed for Conventional Control Case 1<br>                  |

|-------------------------------------------------------------------------------------------------------------------|

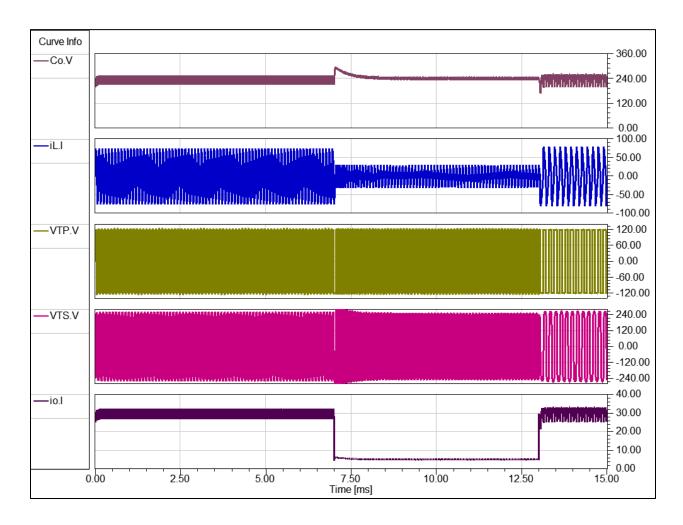

| Figure 84: System Waveforms during Interval Loading Employing Conventional Control for all<br>Loads Case 2        |

| Figure 85: System Waveforms Transient Performance from Heavy to Light Loading Conventional<br>Control Case 2      |

| Figure 86: System Waveforms Transient Performance from Light to Heavy Loading Conventional<br>Control Case 2      |

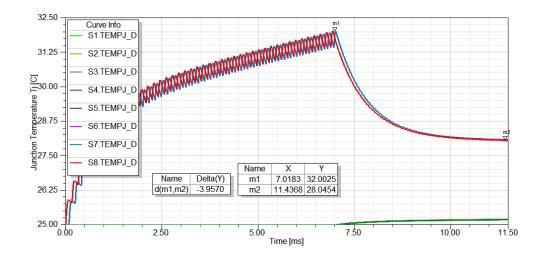

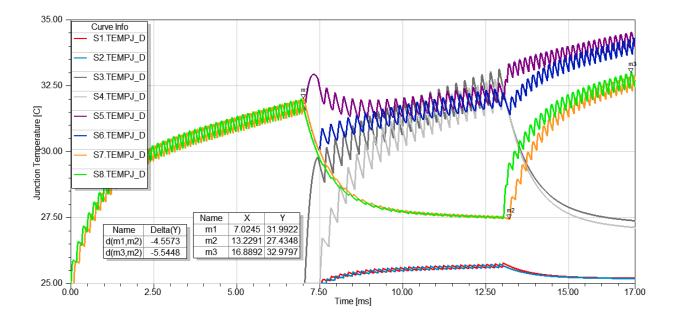

| Figure 87: Junction Temperatures for each MOSFET Employing Conventional Control Case 2                            |

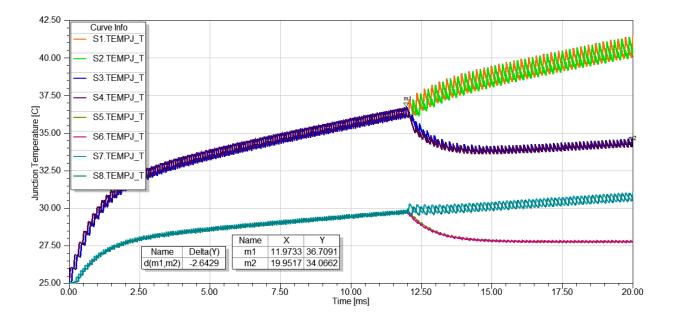

| Figure 88: Junction Temperatures for each MOSFET Superimposed with Conventional Control<br>Case 2                 |

| Figure 89: Junction Temperatures for each Schottky Diode Employing Conventional Control Case<br>2                 |

| Figure 90: Junction Temperatures for each Schottky Diode using Conventional Control Case 2                        |

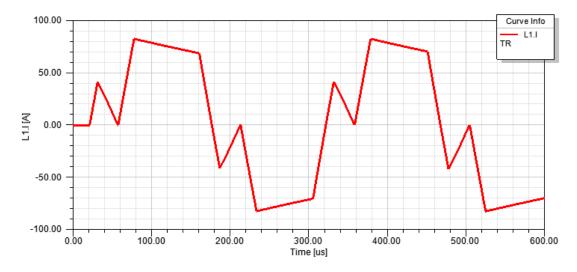

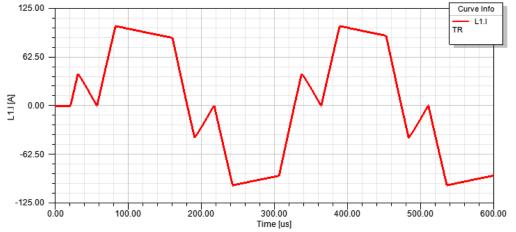

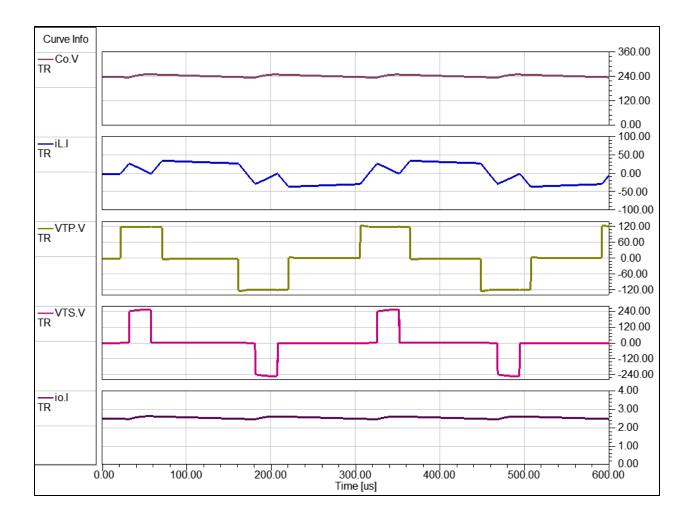

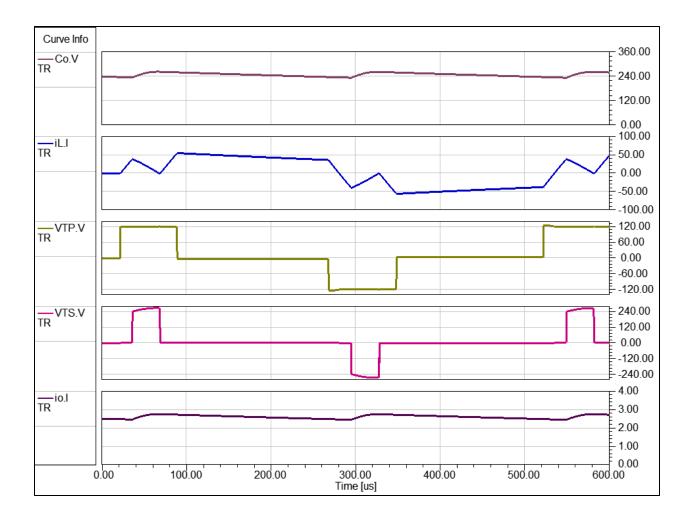

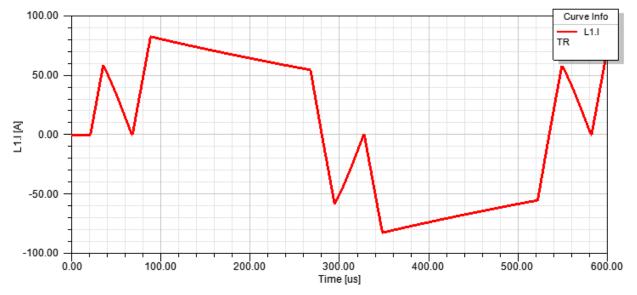

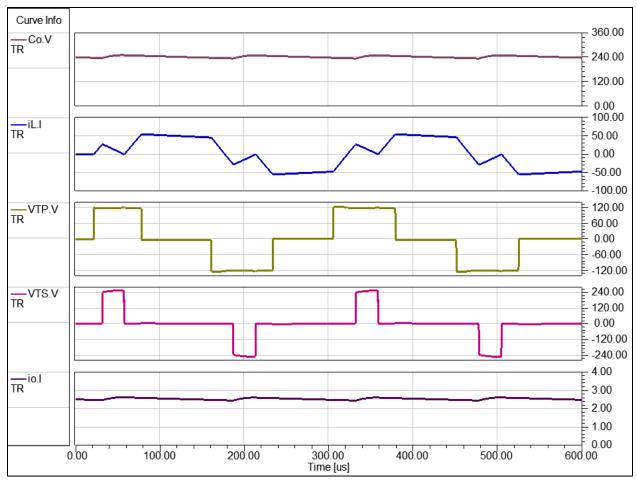

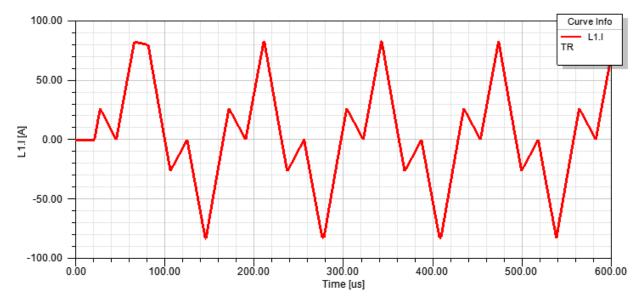

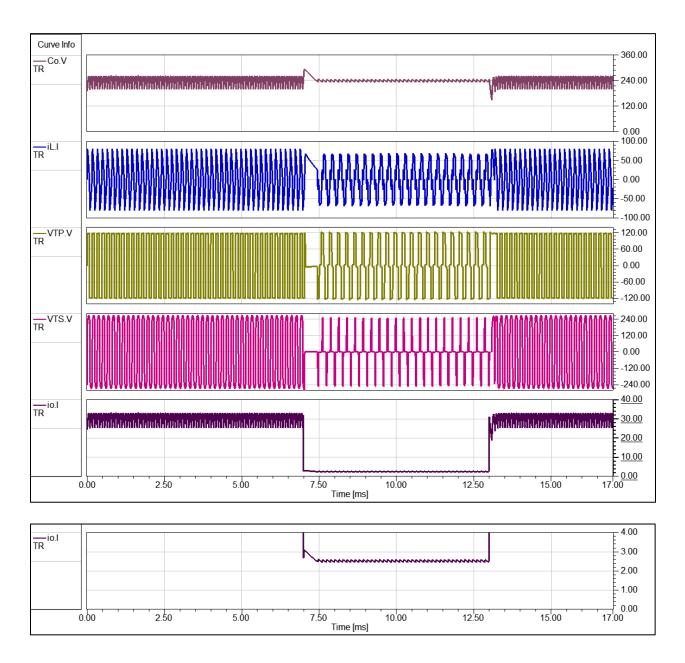

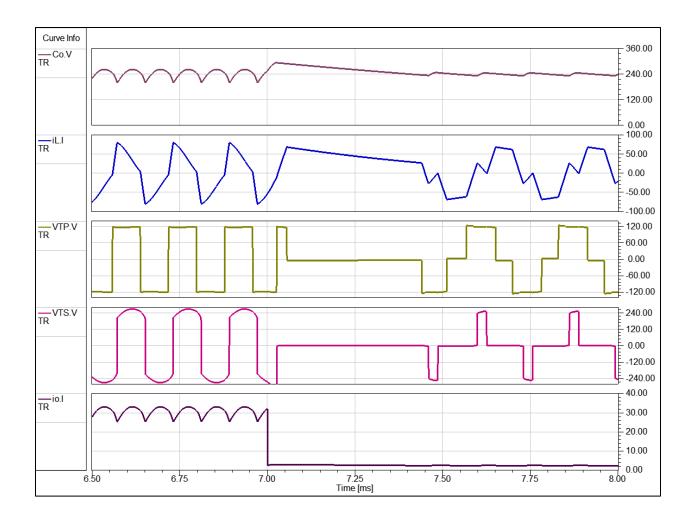

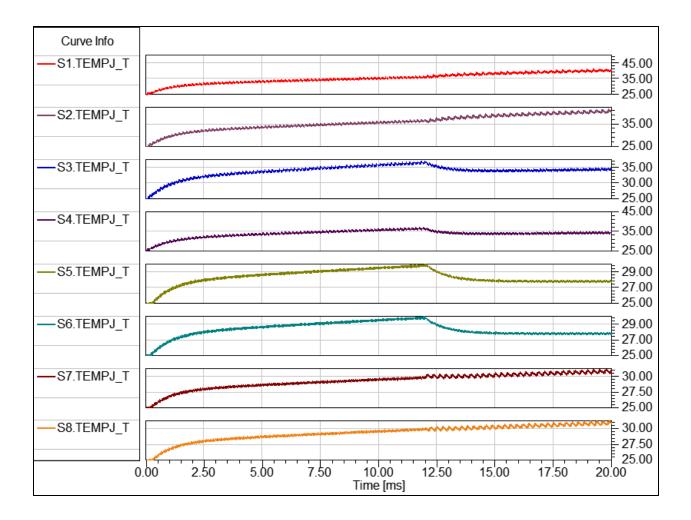

| Figure 91: System Waveforms during Interval Loading with ML Maximum Current at 50A 149                            |

| Figure 92: Junction Temperatures on each MOSFET during Interval Loading with ML Maximum<br>Current at 50A         |

| Figure 93: Junction Temperatures on each Schottky Diode during Interval Loading with ML<br>Maximum Current at 50A |

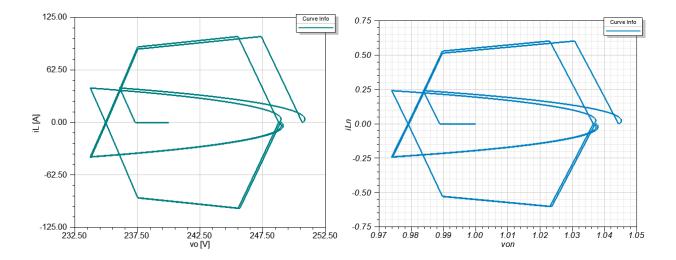

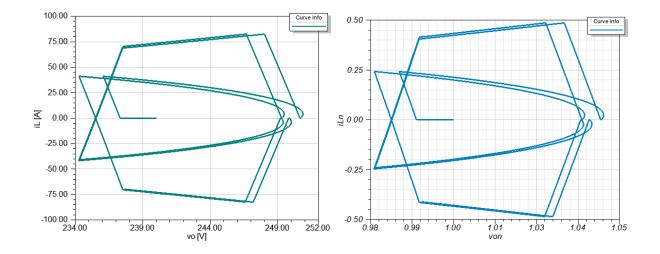

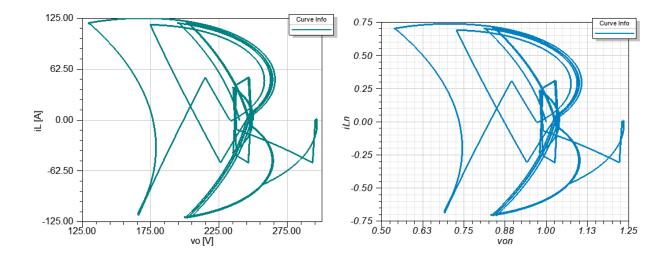

| Figure 94: Nominal and Normalized State Planes during Interval Loading with ML Maximum<br>Current at 50A          |

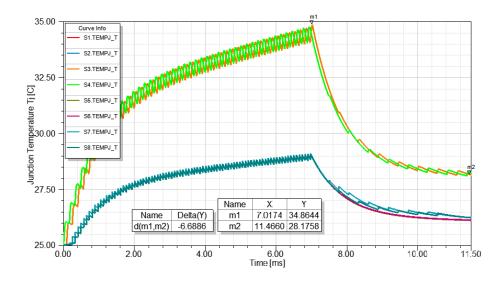

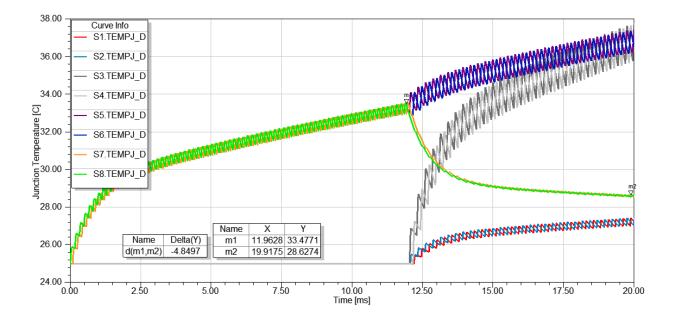

| Figure 95: Junction Temperatures on each MOSFET Superimposed with ML Maximum Current<br>at 50A                    |

| Figure 96: Junction Temperatures on each Schottky Diode Superimposed with ML Maximum<br>Current at 50A              |

|---------------------------------------------------------------------------------------------------------------------|

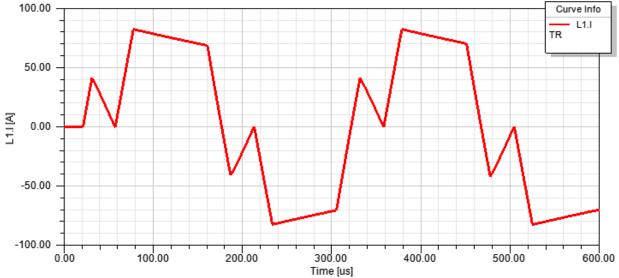

| Figure 97: System Waveforms during Interval Loading with ML Maximum Current at 80A 153                              |

| Figure 98: Nominal and Normalized State Planes during Interval Loading with ML Maximum<br>Current at 80A            |

| Figure 99: Junction Temperatures on each MOSFET during Interval Loading with ML Maximum<br>Current at 80A           |

| Figure 100: Junction Temperatures on each Schottky Diode during Interval Loading with ML<br>Maximum Current at 80A  |

| Figure 101: Junction Temperatures on each MOSFET Superimposed with ML Maximum Current<br>at 80A                     |

| Figure 102: Junction Temperatures on each Schottky Diode Superimposed with ML Maximum<br>Current at 80A             |

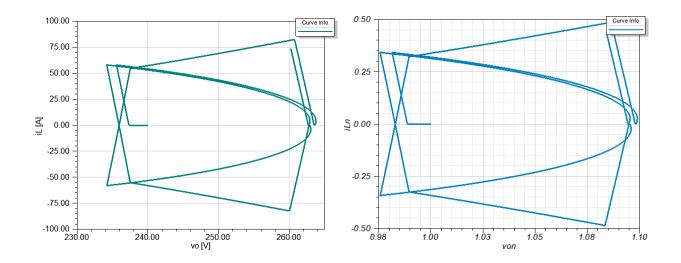

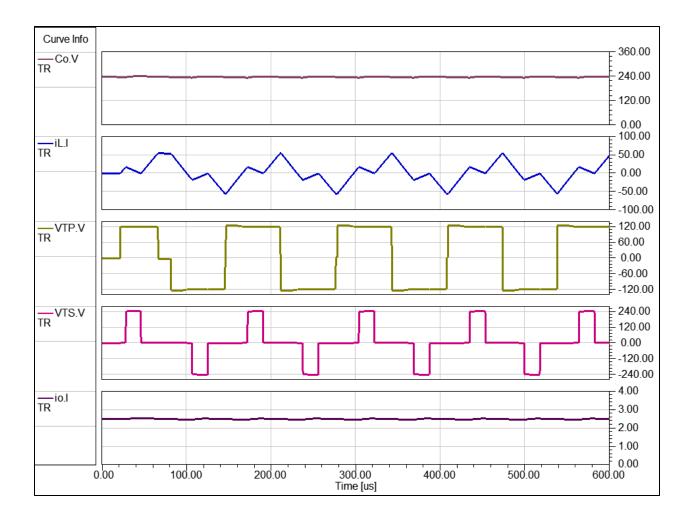

| Figure 103: System Waveforms during Interval Loading Employing ML in Light Load with Max<br>Current at 100A         |

| Figure 104: System Waveforms for Transient Performance from Heavy to Light Load with ML<br>Max Current at 100A      |

| Figure 105: System Waveforms for Transient Performance from Light to Heavy Load with ML<br>Max Current at 100A      |

| Figure 106: Junction Temperatures on each MOSFET during Interval Loading with ML Maximum<br>Current at 100A         |

| Figure 107: Junction Temperatures on each Schottky Diode during Interval Loading with ML<br>Maximum Current at 100A |

| Figure 108: Junction Temperatures on MOSFET during Interval Loading with ML Maximum<br>Current at 100A              |

| Figure 109: Junction Temperatures on Schottky Diode during Interval Loading with ML<br>Maximum Current at 100A      |

|---------------------------------------------------------------------------------------------------------------------|

| Figure 110: Nominal and Normalized State Planes during Interval Loading with ML Maximum<br>Current at 100A          |

| Figure 111: Voltage (DS) and Current (D) for all Devices during Interval Loading with ML<br>Maximum Current at 100A |

| Figure 112: System Waveforms during Interval Loading with ML Maximum Current at 120A in<br>Light Loading            |

| Figure 113: System Waveform Transient Performance from Heavy to Light Load with ML<br>Maximum Current at 120A       |

| Figure 114: System Waveform Transient Performance from Light to Heavy Load with ML<br>Maximum Current at 120A       |

| Figure 115: Junction Temperatures on each MOSFET during Interval Loading with ML Maximum<br>Current at 120A         |

| Figure 116: Junction Temperatures on each Schottky Diode during Interval Loading with ML<br>Maximum Current at 120A |

| Figure 117: Junction Temperatures on each MOSFET during Interval Loading with ML Maximum<br>Current at 120A         |

| Figure 118: Junction Temperatures on each Schottky Diode during Interval Loading with ML<br>Maximum Current at 120A |

| Figure 119: Conceptual Normalized State Plane of Life Preservation Mode for Buck Operation                          |

| Figure 120: Steady State Operating Waveforms for Life Preservation Mode in Buck Operation                           |

| Figure 121: Switching Configurations of ML in Buck Operation for Switching Surfaces 1 through 6                     |

Figure 122: Flowchart of Active Thermal Boundary Control in Buck Mode of Operation ...... 179

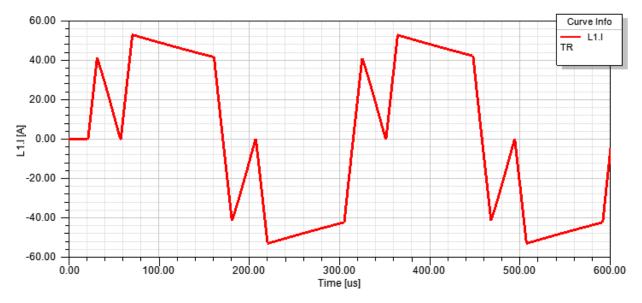

Figure 123: Steady State Waveforms of Life Preservation Mode Designed for Buck Operation 181

#### ACKNOWLEDGEMENTS

Here I gladly take a moment to express my gratitude to each of those who have been a part of my journey towards achieving this milestone. By the grace of God come to me through the many relationships acknowledged here, I have started from a fortunate vantage point from which most others have not. "I have learned that success is to be measured not so much by the position that one has reached in life as by the obstacles which he has overcome while trying to succeed" – Booker T. Washington. To whom much has been given, much is required. My pursuit of this advanced degree was motivated by my making the most of the opportunities given to me. In my work, may I continually give back to the Source and Sustainer of all things with thanksgiving and praise.

First of all, I want to thank my lovely wife, Heidi, for her devoted support, for her contagious drive for life and learning, and for the wonderful job she is doing as mother of our boys, Jack and Andrew. I thank Jack for his infectious wonder, joy, sweet spirit, and love of adventure. I thank Andrew for his peaceful company as I wrote substantial portions of this dissertation during the first few weeks of his life. His contributions have been invaluable. I thank my parents, William (Bill) and Mary Elizabeth (Lil) Lewis, who instilled in me the importance of education, wisdom, work ethic, humility, meekness, respecting others, faithfulness, and the list goes on. From my mom, I have received an artistic eye, the drive to do a job well, lessons in skillful composition, and perceptiveness in reading people. From my dad, I have received patience and endurance to work on something to perfection, active listening, and a model of humility. Additionally, I thank my dad for introducing me to engineering in general and specifically to naval engineering. I am now entering the naval engineering field myself with Hepburn and Sons LLC, trusted technology

advisors for the U. S. maritime industry. I thank Henry Rainone, a previous coworker and friend of my dad, for his integral role in landing this specific job opportunity. I want to thank Donald and Sally Lind, first of all for raising an incredibly thoughtful, diligent, and caring daughter. I am grateful to love them as an incredibly welcome expansion of family. I am grateful for their support and encouragement to Heidi and myself in all aspects of our life. I thank Sally (Mom) for her nurturing spirit, listening ear, and prayers. I thank Don (Dad) for his practical advice and for his quiet, sacrificial, behind-the-scenes support. I thank Dan Carnovale, Jon Daley, and Tim Lewis (brother) all of whom have inspired me to bravely experiment and tinker. I thank Andrew Weaver and Bill Lewis (brother) for being my notably first teachers in critical thinking, logical argument, and objective assessment of multiple perspectives. These have been exercised muscles that have served me well thus far.

Of those affiliated with the University of Pittsburgh, I begin by thanking those who have served on my PhD committee: Dr. Brandon Grainger, Dr. Gregory Reed, Dr. Zhi-Hong Mao, Dr. Alexis Kwasinski, Dr. Robert Kerestes, and Dr. Marius Rosu. I am grateful for all of the power engineering colleagues, classmates and professors that I have worked with along the way during my studies – mentors, peers, and mentees. I thank Zhi-Hong Mao for providing to me my foundation in control engineering. I thank Dr. Alexis Kwasinski for advancing my grasp of power electronics. As fellow third generation graduate students in electric power research at the University of Pittsburgh since the 2008 initiative, I particularly thank Hashim Al-Hassan, Ansel Barchowsky, and Alvaro Cardoza for the friendship and comradery as we pursued our doctorates together. I would also like to particularly thank those with whom I have had specific conversations that have helped lead to the contribution presented in this dissertation: Neal Clements, Rui Hu, Jacob Friedrich, and Brandon Grainger. I thank Shimeng Huang for her guidance and help with using ANSYS tools. I thank Jim Lyle, Bill McGahey, Danielle Ilchuk, Carrie Snell, and Sandy Weisburg for all of their technical and administrative support during my stay at the University of Pittsburgh. I thank the R. K. Mellon Foundation for their generous support of the Center for Energy and myself as a recipient of the R. K. Mellon Fellowship.

Lastly I take a moment to thank my PhD advisors, Dr. Gregory Reed and Dr. Brandon Grainger. I thank Dr. Reed for this educational opportunity made possible due to his vision and inspirational leadership. I am grateful for the unconventional educational environment he has initiated with the Electric Power Systems Laboratory (EPSL) in a way functioning more as a research consulting group than an academic program. Additionally, I am grateful for his example and encouragement in developing and exercising professional communication, networking, and community service skillsets, seeing them as critical to our education. To Brandon Grainger, I am incredibly grateful for his mentorship. His counsel has been invaluable. He has been my mentor, technical advisor, advocate, friend, life coach, and brother in Christ. I am grateful for his pressing me to exercise my inventive capacity, to learn new technical skillsets, to populate my engineering portfolio, to break down intimidation barriers, to dream big yet plan accordingly, and to get granular with the details. I thank Dr. Reed and Dr. Grainger for giving back as they have. I aspire to do the same. May God grant them and the many others mentioned here many years.

P. T. Lewis

#### **1.0 INTRODUCTION**

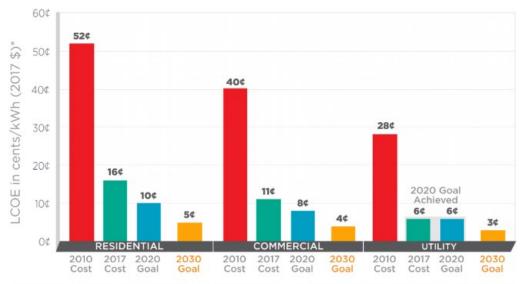

By 2030, as much as 80% of all U.S. electric power is predicted to be processed through power electronics between generation and consumption [1]. As of 2005, this statistic was approximately 30% of processed power in contrast to 80% [1]. Along with increased amounts of power electronics interfaced loads, a significant driver of this trend is the increasing adoption of renewable energy resources, particularly solar and wind power, for both environmental and economical motivations. Figure 1 provides a bar graph of the economic progress and goals associated with the DOE SunShot program arranged into residential, commercial, and utility subdivisions. Achieving three cents per kilowatt-hour would make utility scale solar power to be one of the least expensive sources of electricity generation, less expensive than most fossil-fueled generation [2]. This affordability will be one significant catalyst of the growing trend of power-electronics interfacing with the electric grid, moving beyond the 80% statistic in years and decades to come.

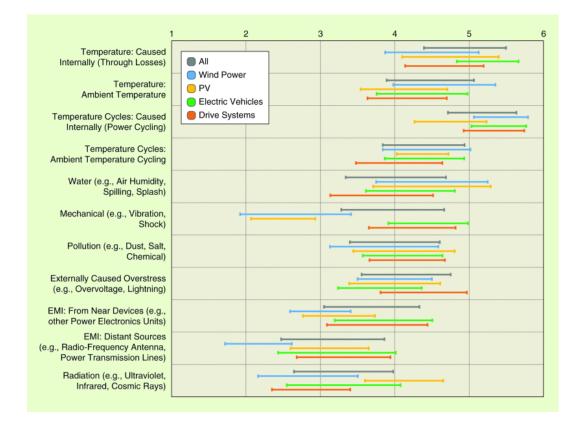

With this proliferation of power electronics, reliability becomes an increasingly important concern. How long would one expect the power electronics to last? Lifetime expectancy for power electronic systems vary per the application. For a few examples of such applications, Table 1 provides typical lifetime expectancies associated with each. The next question: what is the most critical factor that decreases the reliability of power electronic systems? On a component level, the power electronic device is the source of most frequent failures with electrolytic capacitors as a second. What are the more influential factors that decrease the lifetime of the device? Table 2 provides a form of an answer with a focus points matrix, presenting the factors that most critically impact the reliability of power electronic devices [3]. Additionally, a survey was performed among industry experts as to what was the critical reliability stressor for power electronic systems,

resulting with thermal cycling and magnitudes on the junction of a device as being the most critical as depicted in Figure 2 [4].

\*Levelized cost of electricity (LCOE) progress and targets are calculated based on average U.S. climate and without the ITC or state/local incentives. The residential and commercial goals have been adjusted for inflation from 2010-17.

Figure 1: Economic Progress and Goals for the DOE SunShot Program [2]

| Table 1: Typical Lifetime | Targets for | Various Power | Electronics . | Applications | [3]   |

|---------------------------|-------------|---------------|---------------|--------------|-------|

|                           |             |               |               | -FF          | L - 1 |

| Applications          | Typical design target of lifetime             |  |  |  |  |  |

|-----------------------|-----------------------------------------------|--|--|--|--|--|

| Aircraft              | 24 years (100,000 hours flight operation)     |  |  |  |  |  |

| Automotive            | 15 years (10,000 operating hours, 300,000 km) |  |  |  |  |  |

| Industry motor drives | 5–20 years (60,000 hours in at full load)     |  |  |  |  |  |

| Railway               | 20–30 years (73,000–110,000 hours)            |  |  |  |  |  |

| Wind turbines         | 20 years (120,000 hours)                      |  |  |  |  |  |

| Photovoltaic plants   | 30 years (90,000–130,000 hours)               |  |  |  |  |  |

| Load<br>Climate + Design ⇒ Stressor |                               |                              | Focus points               |      |           |                                |      |                                        |      |    |     |            |

|-------------------------------------|-------------------------------|------------------------------|----------------------------|------|-----------|--------------------------------|------|----------------------------------------|------|----|-----|------------|

|                                     |                               |                              | Active power<br>components |      |           | Passive<br>power<br>components |      | Control circuitry, IC, PCB, connectors |      |    |     |            |

| Ambient                             | Product design                | Stressors                    | Die                        | LASJ | Wire-bond | Cap.                           | Ind. | Solder joint                           | MLCC | IC | PCB | Connectors |

| Relative                            | – Thermal                     | Temperature swing $\Delta T$ | Х                          | Х    | X         |                                |      | X                                      |      |    |     |            |

| humidity                            | system                        | Average temperature $T$      | Х                          | Х    | Х         | Х                              |      | Х                                      | Х    | x  | х   | х          |

| -RH(t)                              | <ul> <li>Operation</li> </ul> | dT/dt                        | х                          | х    | х         | х                              |      |                                        |      |    |     |            |

| Temperature                         | point                         | Water                        |                            |      |           |                                |      |                                        |      | Х  | Х   | х          |

| -T(t)                               | - ON/OFF<br>- Power P(t)      |                              |                            |      |           |                                |      |                                        |      |    |     |            |

|                                     |                               | Relative humidity            | х                          | х    | х         | Х                              | х    | х                                      | х    | Х  | X   | х          |

| Pollution                           | Tightness                     | Pollution                    |                            |      |           |                                |      | х                                      |      |    | х   |            |

| Mains                               | Circuit                       | Voltage                      | х                          | х    | х         | Х                              | Х    |                                        | х    | х  | х   | х          |

| Cosmic                              | Circuit                       | Voltage                      | х                          |      |           |                                |      |                                        |      |    |     |            |

| Mounting                            | Mechanical                    | Chock/vibration              | х                          |      |           | х                              | х    | х                                      | х    |    |     | х          |

#### Table 2: Focus Points Matrix for Reliability of Power Electronic Components

LASJ - large area solder joint, MLCC - multi-layer ceramic capacitor, IC - integrated circuit, PCB - printed circuit board, Cap. - capacitor,

Ind. – inductor, level of importance (from high to low): X-X-X-x.

Figure 2: Critical reliability stressors for power electronic systems by application, an industry perception

With the evolution of the electric grid, the increase of converter-interfaced distributed generation (DG) results in grid voltage and frequency instability due to a reduction of inertia or system strength conventionally safeguarded by radially connected synchronous machines (SM) generation. This can be especially apparent for islanded microgrids. Resulting voltage instability can be addressed by reactive compensation as a grid support feature for smart inverters but not without added device degradation reducing system reliability [5]–[7]. Resulting frequency instability and the lack of desired SM inertial dynamics can be resolved by an increasingly popular solution, virtual synchronous machine (VSM) control also known as the synchronverter [8]–[10]. As distributed generation increases and as power electronics conversion technologies functionally advance in response to the challenges associated with increased penetration of power electronics power processing on the grid, advanced grid converter features threaten to quicken the pace of device degradation. Understanding and mitigating any negative impacts of such advanced grid converter solutions upon device lifetime is the purpose of this work.

The reliability of power electronic conversion systems is primarily correlated to the thermal stress experienced by the semiconductor device materials [11], [12]. Lifetime, the longevity of the power electronic semiconductor device, diminishes with high averages and more emphatically high amplitudes of device junction temperature thermal cycling dynamics experienced by the device [13]. For proper assessment of power electronic device reliability, electro-thermal semiconductor device models are created. Since wide bandgap materials are of particular interest in the power electronics community, reliability assessments include the comparison of conventional Si IGBT transistor and SiC power MOSFET models, based upon datasheets from the manufacturer for specific devices. All work is performed utilizing ANSYS Simplorer. Notably a reduction of thermal cycle amplitude preserves device reliability, and counter-intuitively this

reduction can be achieved by preventing junction temperatures from dropping to cooler temperatures.

The contribution proposed in this work is principally inspired by a control methodology previously applied to the dual active bridge, among others, based upon natural switching surfaces (NSS) applied for efficiency gain. Forms of NSS control are also known as boundary or trajectory control in the literature. Additionally, this work is inspired by the various active thermal control (ATC) methods that have been introduced in the literature. Utilizing NSS methodology for the purpose of actively controlling thermal cycling behavior lays the foundation of the proposed research. This approach bears unique merit for management of thermal behavior through designed electrical boundaries placed upon natural switching surfaces, influencing the thermal dynamics for lifetime preservation even while implementing advanced grid converter performance capability. The resulting method is autonomous, natural switching control with boundaries designed to accommodate improved device reliability.

First, this work provides a power electronic device reliability assessment utilizing electrothermal semiconductor device models for the enlightenment of the benefits of an interdisciplinary design perspective. Secondly and of primary contribution, this work proposes a means of device lifetime preservation leveraging natural switching surface control methodology as a means of active thermal control.

#### 1.1 **OBJECTIVE**

The objective of this work is to propose a method of converter control that actively mitigates decreased device lifetime that is related to adverse thermal performance. The methodology preferably would be applicable to various converter topologies.

More specifically, this work is dual-purposed in objective, 1) to enlighten electric power engineers with a more interdisciplinary perspective of power electronic converter system design accounting for electro-thermal behavior with regards to device reliability and 2) to provide a control methodology that minimizes the negative impacts of thermal behavior even while maintaining advanced converter performance benefits desired. Inherent to such an objective is a trade-off to be taken into account between reliability and performance.

#### 1.2 ORGANIZATION

This proposal is organized in order that any content can be placed into three primary categories: literature review, preliminary work, and proposed solution. Section 2 addresses a background literature review, concerning grid converter electrical performance features and the relationship between thermal performance and device reliability. Also addressed is the electro-thermal semiconductor device modeling necessary in order to observe impacts upon thermal performance. Sections 3 covers the preliminary work pertaining to the control features of distributed generation inverters including reactive compensation and virtual synchronous machine supporting grid voltage and frequency stability, respectively. Section 4 provides the theoretical background of natural switching surface control applied to the dual active bridge as well as a specific case study

design for efficient performance. Section 5 introduces the utilization of boundary or natural switching surface control to contribute a form of active thermal control for interval-based loads. The same control approach is proposed for future work to be developed for the distributed generation inverter accommodating the reliability cost of reactive compensation as a grid support feature. Section 6 concludes the work with a summary, suggested future research directions, and possible applications.

### 2.0 BACKGROUND ON DEVICE RELIABILITY AND MODELING

This background section provides the space for setting the scene, for primarily power electronic device reliability, but also for the electro-thermal semiconductor device modeling necessary for the validation of the proposed contribution. Device reliability requires an extensive background due to the proposed contribution being related to an improvement in such area. An appropriate understanding of device reliability is needed for a grasp of what is being proposed, as well as for a grasp of what is not being proposed. Integrally, background is given on the topic of active thermal control and how it can enable the preservation of power electronics reliability. The background and modeling details of electro-thermal device models are also provided, including model validation according to manufacturer datasheets for specific IGBT and MOSFET devices. The two advanced DG inverter functionalities explored in this work are dynamic reactive compensation and virtual synchronous machine control, supporting grid voltage and frequency instability, respectively. Background for each function is provided in their respective sections, 4 and 5. Lastly, the origin story of natural switching surface control in application to the dual active bridge is given coverage here, being the inspiration for the primary contribution of this work. Within the literature, this control methodology has existed outside the realm of active thermal control, until now.

#### 2.1 **ON POWER ELECTRONICS RELIABILITY**

Reliability for this work will be defined as "maintaining the characteristics relevant to operation over a defined period of time [14]," typically measured in terms of probability of survival or failure rate. The essence of reliability engineering in this sense is to preserve life or prevent failure. Reliability of a semiconductor device can correspondingly be defined as maintaining switched conduction for the expected lifetime of the device, and power electronics reliability engineering as preservation of the life of the component. Of power electronics more generally, the reliability of conversion systems are predominantly threatened by power semiconductor devices (e.g. Si and SiC IGBTs and MOSFETs, and GaN devices), but also by capacitors, connections, and fans [3]. This work addresses the reliability of power devices as they are a severe threat to converter system reliability on their own. All other said reliability vulnerabilities are outside the scope of this work.

Electronic reliability engineering has existed as a discipline in its own right since the early 1950s, with its origins in military electronics during World War II when the electronic tube was the most unreliable component in electronic systems [15]. This backdrop is the start of U.S. military handbooks on electronic reliability engineering. Such were the origins of the popularly utilized MIL-HDBK-217F titled "Reliability Prediction of Electronic Equipment" [16]. That said, the topic of electronic reliability engineering has come short of an exact science over the last seven decades. The cover page of this widely used handbook states its purpose to be guidance only and not to be cited as a requirement. The approach is that of documenting observed device failure data. This guide and many like it have been incredibly helpful, but they especially have limitations as power electronics technology advances and grid interconnection applications become more widespread. Additionally, advanced approaches seek to design for reliability proactively as much as possible. A paradigmatic shift exists nowadays towards a physics-of-failure approach for power electronics reliability engineering [3], [13]. This approach is being pioneered by prominent names in the power electronics engineering community, the likes of Dr. Huai Wang, Dr. Marco Liserre, Dr. Frede Blaabjerg, and Dr. Ke Ma among others. The physics-of-failure perspective takes a multi-disciplinary design for reliability (DFR) approach.

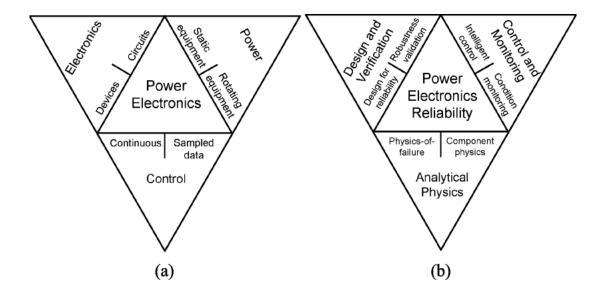

The broad and multi-disciplinary scope of power electronics research is effectively portrayed with the diagram in Figure 3 [13]. According to William E. Newell in 1974, the scope of power electronics research is subdivided into three primary disciplines of electrical engineering, the categories of power, electronics, and control as in Figure 3 (a) [17]. According to [13], the future trends of power electronics reliability can similarly be subdivided into primary disciplines of control and monitoring, design and verification, and analytical physics as seen in Figure 3 (b).

Figure 3: Defining the scope of (a) power electronics research according to William E. Newell in 1974 [17] and (b) power electronics reliability research trends today [13]

Where does this proposed research fall within the future disciplinary trends of power electronics reliability research? Within this multi-faceted topic, the contribution is primarily an intelligent control design, ensuring reliable field operation of grid converters from the start through means of control methodology. Secondarily, the contribution is an example of designing for reliability, building reliable operational dynamics into the design. Lastly, the proposed work is founded upon a physics-of-failure approach since previous research literature addressing how and why devices fail is the enlightenment of the controller contribution.

The relationship between device junction temperatures and device reliability is linked to the mechanical component physics. When the heterogeneous materials that make up a device module heat up and cool down at varying speeds, the life of the device diminishes. The reliability of a device is primarily correlated to this type of thermal stress experienced by the device module [11], [12]. The longevity of the functional life diminishes with high averages and more notably high amplitudes of device junction temperature fluctuations experienced by the device [13]. One rise and fall of temperature fluctuation on the junction of a power semiconductor device is known as one thermal cycle. Device failure ultimately results from stressed physical contacts between materials of differing thermal expansion coefficients, finally degrading into a crack at the maximum amount of thermal stress cycles that the contact could withstand.

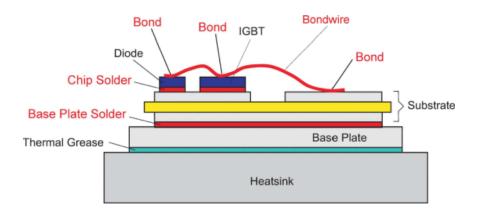

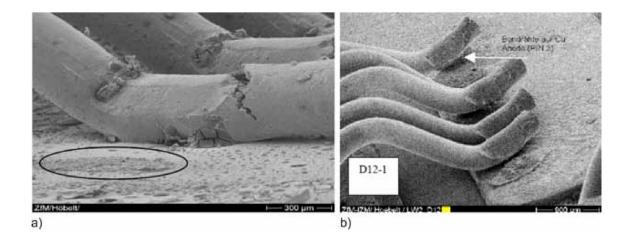

For an insulated gate bipolar junction transistor (IGBT) module, the material contacts relevant to reliability vulnerability include cracking of baseplate solder joints or chip solder joints and the lifting of wire bonds. A structural diagram of an IGBT is provided in Figure 4 with vulnerable points of contact highlighted in red. A helpful metaphor to conceptually grasp the physical cause of device failure is the repeated bending of a piece of metal wire. The wire will eventually snap from the cyclical bending. Cyclical temperature fluctuations on junctions of the power electronic device similarly result in device failure. Material junctions shifting on the order of 5 to 50  $\mu m$  is enough to cause such a failure [14]. For an example, a magnified picture of an actual failed IGBT caused by bond wire lifting and cracking is depicted in Figure 5. Note that power MOSFETs, whether they are based off of conventional Si or wide bandgap GaN materials, do not have bond wires due to having body diodes instead of anti-parallel diodes like IGBTs.

Nonetheless, reliability is an issue specifically with regards to cracking of baseplate solder joints or chip solder joints.

Figure 4: Cross section of an IGBT module with highlighted physical points of contact relevant to device lifetime

[14]

Figure 5: IGBT bond wire damage: (a) cracking and lift-off (b) bond wire lift-off [14]

An established mathematical approximation of power electronic device reliability, based upon thermal cycling, is the Coffin-Manson-based lifetime estimation model [11], [13], [18], [19].

Derived in [20], the remaining number of thermal cycles until device failure (N) can be calculated according to (1).

$$N = C \left( \Delta T_i - \Delta T_{i,0} \right)^{-n} \tag{1}$$

Where *N* is the number of cycles to failure and  $\Delta T_j$  is the range of temperature in the thermal cycle while *C* and *n* are constants determined empirically through simulation or experiment. The  $\Delta T_{j,0}$ is a thermal stress forgiveness region within which elasticity of material allows for a small amount of thermal cycling without causing added stress. When  $\Delta T_{j,0}$  is negligible in contrast to  $\Delta T_j$ , it can be dropped, resulting with the Coffin-Manson model of lifetime estimation, equation (2).

$$N = C \left( \Delta T_j \right)^{-n} \tag{2}$$

One more model that builds upon the work of Coffin and Manson is the Arrhenius life stress model, also known as the Arrhenius relationship. This relationship is likely the most commonly used lifestress relationships for accelerated life testing. My work is not geared towards accelerated life testing but simply to minimize the critical accelerators. Nonetheless, speaking of reliability would be incomplete without speaking of this relationship. It is derived from the Arrhenius equation, a reaction rate. In application to reliability of power electronics, the Arrhenius relationship is used to modify the Coffin-Manson model, resulting in the Coffin-Manson-Arrhenius model (3) [21].

$$N = D\left(\Delta T_j\right)^{-m} \left(e^{\frac{E_a}{k_B T_{j,m}}}\right)$$

(3)

Where  $k_{\rm B}$  is the Boltzmann constant,  $E_{\rm a}$  is the activation energy, and  $T_{\rm j,m}$  is the mean device temperature, while *D* and *m* are constants determined empirically. One can see that the average junction temperature is now incorporated into the Coffin-Manson, with added accuracy. Nevertheless, the Coffin-Manson is a foundational relationship because the thermal cycles are the dominant factor in the relationship between junction temperature and acceleration of degradation. That is as long as the magnitudes of the device are within rated thresholds provided within a datasheet.

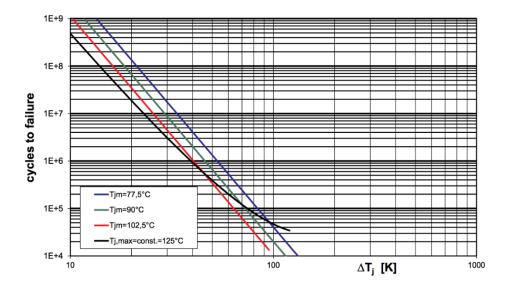

An example of these estimated cycles to failure calculations for an IGBT is depicted in Figure 6 with respect to both thermal cycling amplitude and mean temperature. The relationship between thermal cycling amplitude ( $\Delta T_j$ ) and mean junction temperature ( $T_{j,m}$ ) is defined in equation (4).

$$\Delta T_j = T_{j,m} - T_j \tag{4}$$

Where  $T_j$  represents the measured junction temperature in real time or the estimated junction temperature for given reliability engineering solutions. Beyond using the Coffin-Manson model

or even the Coffin-Manson-Arrhenius model, Miner's Rule is also a cumulative damage rule used for estimating device lifetime, provided in (5).

$$C = \sum_{i} \frac{n_i}{N_i} \tag{5}$$

Where C is the cumulative damage,  $n_i$  is the number of cycles within stress range, and  $N_i$  the number of cycles to failure in *i*th stress range [21]. Miner's Rule might be utilized for future validation of proposed research as is fitting.

Figure 6: Power cycling lifetime in relation to cycling amplitude and mean temperature for an IGBT module [14]

Note that some power electronics reliability research performs statistical analysis as in mission profiling or rainflow-counting analysis seeking to better predict the lifetime of the converter system by accelerated stress methods. This proposed work is not concerned with attempts to develop better estimations of device lifetime through statistical analysis. This work is interested in the lifetime prediction relationships described only for the purpose of recognizing the desired objective of reducing thermal cycling for lifetime preservation. Instead of predictions of lifetime, this work is involved with active reduction of junction temperature magnitudes and cycle amplitudes, as a form of what is coined as active thermal control (ATC) in the literature [22].

Numerous works have proposed various forms of ATC to improve converter reliability, utilizing various thermally-oriented control strategies, gate driver modification, and modulation methods as forms of ATC [21], [23]–[25]. Discontinuous pulse-width modulation, a well-known strategy for controlling device loading, reduces the amount of experienced losses and consequently temperatures due to intervals of discrete voltage output reducing switching actions [24], [26]. Active gate driver control provides the possibility of influencing both conduction and switching losses without hindering device functionality [27]. Additionally, a reduction of junction temperature variation can be achieved through proper switching frequency ( $f_{sw}$ ) variation per operating condition [21], [22]. The work in [22], takes this latter ATC approach and uniquely varies switching frequency to prevent excessive device cooling during power reductions, and the control design exploiting the switching frequency is informed by power loss estimations. Common among these ATC methods, is that either average or cycling amplitude junction temperature are reduced, and the savings are achieved due to reduced device loss. The device power loss ( $P_{loss}$ ), consisting of both switching ( $P_{sw}$ ) and conduction loss ( $P_{cond}$ ), is generally defined as in (6).

$$P_{loss} = P_{sw} + P_{cond} = \frac{I_{on}V_{off}}{a}f\Delta t_{sw} + I_{on}^2 R_{DS,on}$$

(6)

The work presented here is a form of ATC that reduces thermal cycling amplitudes particularly.

Where junction temperature averages and thermal cycling amplitudes can be minimized, device reliability is improved. Notably thermal cycle amplitude minimization, even if causing the devices to experience added loss and stay at higher temperatures, consequently extends device lifetime. This is consistent with the Coffin-Manson model and related estimations seen in equations (1) through (3). This form of active thermal control is a proven method of extending the lifetime of power electronic devices by limiting how far the devices cool down, effectively reducing the thermal cycling on the junction of a semiconductor device,  $\Delta T_i$ .

With all of this background, the narrowed scope of this work is related to the development of an active thermal control methodology, a form of intelligent control as seen in Figure 3 (b) within the larger scope of power electronics reliability. In order to validate the benefit of such a methodology, a means of assessing thermal cycling behavior is necessary. Electro-thermal semiconductor device modeling enters the scene, a physics-of-failure approach incorporating device physics into grid converter simulations for proper assessment of reliability engineering.

#### 2.2 ON ELECTRO-THERMAL SEMICONDUCTOR DEVICE MODELING

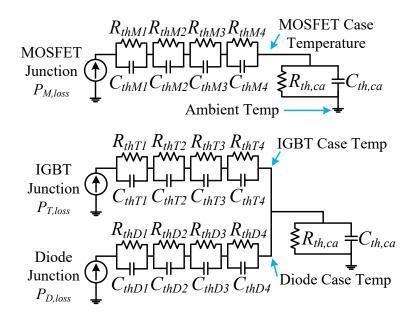

The thermal dynamics of the semiconductor devices are incorporated into CAD simulation by use of a thermal impedance network that is separate from yet coupled to the electrical device circuitry.

The impedance network is made up of parallel combinations of resistive and capacitive impedances, connected in series as shown in Figure 7 for a power MOSFET and for an IGBT with its associated anti-parallel diode. The physical layers of the device that are modeled include the following: device junction to device packaging case ( $Z_{th,jc}$ ), device case to the ambient temperature ( $Z_{th,ca}$ ), for which typical values for a heat sink thermal impedance are utilized in this work. The overall junction to ambient thermal impedance can be calculated as in (7) in units of degrees Celsius per Watt.

$$Z_{th,ja} = \frac{T_j - T_a}{P_{loss}} (°C/W)$$

<sup>(7)</sup>

Where  $T_a$  is the ambient temperature,  $T_j$  is junction temperature,  $P_{loss}$  is the total loss, and  $Z_{th,ja}$  is the total thermal impedance from junction to ambient. The thermal impedance from heat sink to ambient with intermediary layers of thermal impedance is calculated as shown in (8).

$$Z_{th,ja} = Z_{th,jc} + Z_{th,cs} + Z_{th,sa}$$

$$\tag{8}$$

Moving forward, the thermal impedance from casing to the heat sink,  $Z_{th,cs}$ , is lumped into a case to ambient thermal impedance,  $Z_{th,ca}$ . The junction temperature rises above ambient temperature by the amount of power loss dissipated across the described thermal impedances as in (9).

$$T_j = T_{ambient} + P_{diss}(Z_{th,jc} + Z_{th,ca})$$

(9)

Of the two popularly utilized thermal impedance networks, the Cauer and Foster models, the Foster network is implemented. The Foster network, also known as the partial fraction circuit, combines parallel combinations of thermal impedances that extrapolate manufacturer generated curves of transient thermal impedance. The Cauer network, also known as the continued fraction circuit, combines thermal impedances that specifically reflect the physical layers of the materials. Because material characteristics of the individual layers were not known for all device cases and because transient thermal impedance curves were available in datasheets, the Foster model was utilized.

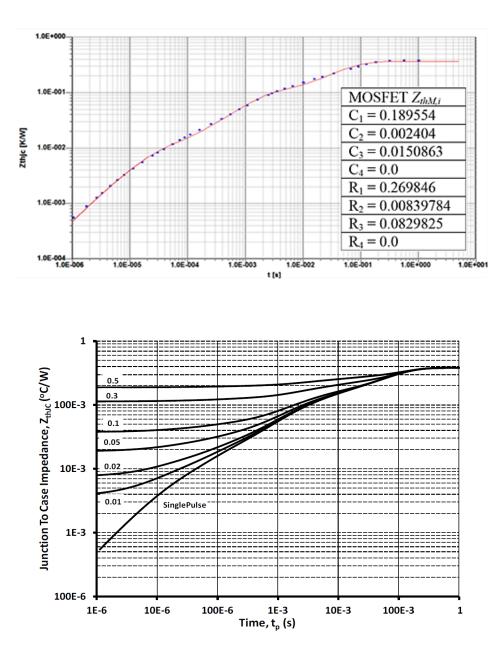

The four Foster thermal impedances ( $C_{\text{th,i-4}}$  and  $R_{\text{th,i-4}}$ ) for each device are mathematical approximations to map each correlating transient thermal impedance curve. The curves represent the thermal impedance between the *p-n* junction and device packaging case over the specified switching pulse time. Network models were created based upon datasheet characteristics, and the resulting thermal impedance values are listed for the SiC power MOSFET in Figure 6 and for the Si IGBT and its associated anti-parallel diode in Figure 7 and Figure 10, respectively. The IGBT and anti-parallel diode have different thermal characteristics and are hence modeled separately while the body diode of the MOSFET has inherently the same thermal characteristic as in Figure 8. For the purpose of validation, Figure 6, Figure 7, and Figure 8 also provide comparisons of the transient thermal impedance curves between the generated device model and its datasheet.

Figure 7: Transient Thermal Impedance Foster Networks

Figure 8: Transient Thermal Impedance Model for the SiC MOSFET. Model (above) and Manufacturer (below)

Figure 9: Transient Thermal Impedance Model for Si IGBT. Simulation Model (above) and Manufacturer

Measurement (below)

Figure 10: Transient Thermal Impedance Model for Si Anti-parallel Diode. Simulation Model (above) and Manufacturer Measurement (below)

# 3.0 INVESTIGATING IMPACTS OF ADVANCED INVERTER FEATURES

Included here are two in-depth studies (3.1 and 3.2) of the impacts that two advanced inverter features have upon power electronics systems reliability. These two features are reactive compensation and virtual synchronous machine control, grid support features for voltage and frequency stability, respectively.

#### 3.1 IMPACT OF REACTIVE COMPENSATION GRID SUPPORT

As advanced functionality is being demanded from distributed generation (DG) systems, smart inverters are being developed to provide reactive compensation to provide system support during grid disturbances. This compensation, however, leads to increased semiconductor device stress in the inverter. This work investigates the electro-thermal impacts of inverter grid support upon the longevity of SiC power MOSFET and Si IGBT products. This work is meant to inform the evolving standard development for smart inverter design.

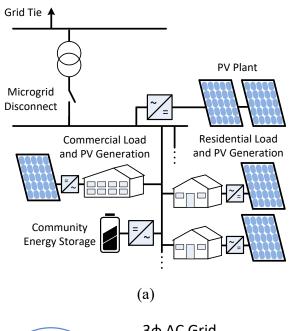

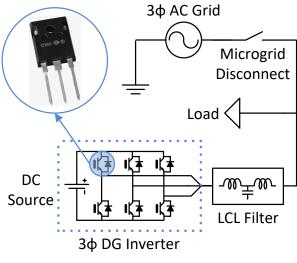

With increasing distributed generation (DG) on the grid, an expected paradigm shift is the requirement of DG inverters to provide grid support features, notably within microgrid systems, as depicted in Figure 11(a). A voltage sag that is experienced as result of system events, such as a grid fault or microgrid islanding, can be remedied through reactive power compensation. However, by performing reactive compensation with a smart inverter, additional device losses and stresses are created in the semiconductor switches [5], [13], [28], [29]. With this additional capability of voltage source converters (VSCs), there is a foreseen tradeoff: the grid voltage support added by the smart inverter and the reliability of the inverter (devices handling added stress).

(b)

Figure 11: Example Microgrid System (a) and Modeled System (b)

There is also a need to determine standards for advanced features required of smart inverters. The Electric Power Research Institute (EPRI) began such efforts in 2009 and documented the work "Common Functions for Smart Inverters Version 3," published in February 2014 [30] and updated in December 2016 [31], attempting to provide a common language for the subject of advanced inverter functions. Dynamic reactive current support is one of the discussed functions. Grid codes and evolving standards associated with advanced inverter features include IEEE 1547, CA Rule 21, UL 1741, and IEC 62109. Exploring the reliability of DG converters will help inform evolving requirements while maintaining balance between grid resiliency and converter reliability.

Mechanical reliability of a power electronics system is directly correlated with the thermal stress experienced within the semiconductor devices. This is dictated by increasing mean junction temperature and by junction temperature fluctuations experienced by each power electronic device. When p-n junction temperature magnitudes and fluctuations are minimized, reliability is improved. Numerous works have proposed various methods to improve converter reliability by such minimization utilizing various control strategies and modulation methods [23], [24], [32]. In [6], the optimization of reactive power flow is explored to achieve higher reliability of power converters interfacing doubly fed induction generators.

In this work a SiC power MOSFET and a Si IGBT, the CREE C2M0040120D [33] and the Infineon IKW40T120 [34], are characterized for a microgrid-based inverter system and modeled in ANSYS Simplorer. These models are used for comparison during a grid disconnect, in which the inverter control system must compensate for the voltage dip by injecting reactive current. The resulting temperature excursions experienced by the semiconductors in each inverter are examined, with analysis over a range of real and reactive power levels supplied by the inverter. These results demonstrate the mechanical impact of reactive power compensation on the longevity of power electronic devices in developing smart inverter systems. This work is organized into the following parts. Section II presents the implementation of smart inverter control capable of the reactive compensation support feature. Section III describes further modeling efforts associated with a switched converter model including device losses. Electrothermal device characterizations are presented and validated in Section IV. Lastly, Section V gives the results of various case scenarios, followed by observations and conclusions in Section VI.

#### 3.1.1 Smart DG Inverter Control Implementation

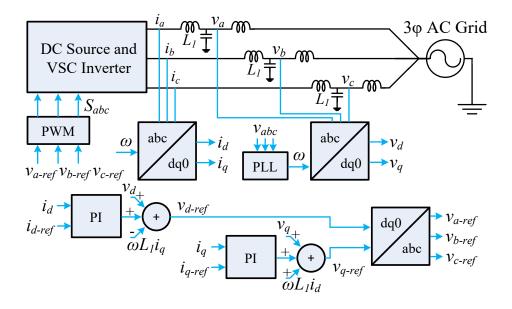

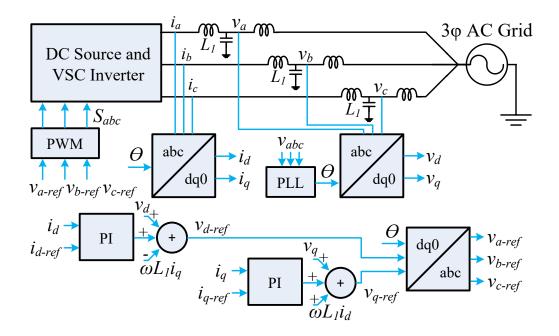

This section provides the model and controller implementation of the reactive compensation technique. The examined inverter is a commonly used VSC, two-level, three-phase, DG inverter with controllable reactive power injection. It is connected to the microgrid, as shown in Figure 11(b), via a LCL filter interface at the point of common coupling. The equivalent grid, modeled as an infinite bus, is disconnected from an islanded microgrid by a transfer switch. The system parameters, given in Table 3, are based upon typical values for a residential scale three-phase inverter. The VSC inverter control system performs standard inner current control regulation and outputs *d*-axis and *q*-axis voltage references for pulse width modulation control as seen in (1) and (2) [35]. Figure 12 presents this control structure and how it interfaces with the full system.

$$v_{d-ref} = v_d - \omega L_1 i_q + (K_P + K_I/s) (i_d - i_{d-ref})$$

(1)

$$v_{q-ref} = v_q + \omega L_1 i_d + (K_P + K_I/s) (i_q - i_{q-ref})$$

(2)

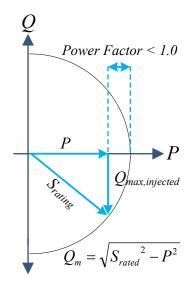

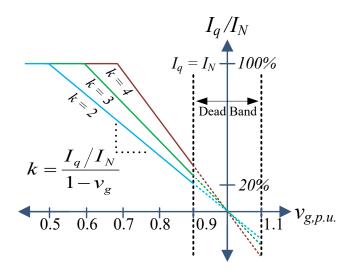

When injecting reactive current, the reference  $i_{q-ref}$  is altered according to the necessary amount of compensation for voltage recovery. As depicted in Figure 3, the maximum amount of possible reactive power compensation for a given event is limited by the rated capacity of the inverter. By adopting a constant active power strategy, the system achieves ramp rate control as defined in (3) and (4) [28], [36], [37].

$$i_{d-ref} = I_N / v_g \tag{3}$$

$$i_{q-ref} = k(1 - v_g)I_N \tag{4}$$

Here, k is the ramp rate of injection,  $I_N$  is the rated current of the inverter,  $i_{q-ref}$  is the injected reactive current reference, and  $v_g$  is the grid voltage measured at the point of connection.

The rate of current injection, k, is solved for from (13) and depicted within Figure 14. The German E.ON Grid Codes requires a minimum compensation of k = 2 [36]. The IEEE Standard 1547 is yet to determine such a code of implementation. The grid voltage measurement, calculated as a control input in (5), is the per unitized magnitude of the three phase grid voltages ( $v_a$ ,  $v_b$ , and  $v_c$ ) after conversion into the *d-q* reference frame.

$$v_g = \sqrt{v_d^2 + v_q^2} \tag{5}$$

Note that all calculations within the control system in Figure 12 are performed in per unit base, and the inverse park transform (with corresponding park transform) utilized in this control for both voltages and currents is provided here for clarity in (6).

$$\begin{bmatrix} v_d \\ v_q \\ v_0 \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos(\omega t) & \cos\left(\omega t - \frac{2\pi}{3}\right) & \cos\left(\omega t + \frac{2\pi}{3}\right) \\ -\sin(\omega t) & -\sin\left(\omega t - \frac{2\pi}{3}\right) & -\sin\left(\omega t + \frac{2\pi}{3}\right) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

(6)

Table 3: DG Inverter System Parameters for Reactive Compensation Implementation

| System Parameter                           | Value        |

|--------------------------------------------|--------------|

| AC Output Voltage (RMS)                    | $120 V_{LN}$ |

| DC Input Voltage ( $V_{DC}/2$ )            | 275 V        |

| Inverter Rated Power                       | 9 kVA        |

| Three Phase Load                           | 9 kW         |

| Grid Frequency f <sub>G</sub>              | 60 Hz        |

| Current Rating (RMS)                       | 25 A         |

| Filter Inverter-Side <i>L</i> <sub>1</sub> | 11.3 mH      |

| Filter Grid-Side L <sub>2</sub>            | 229.2 µH     |

| Filter $C_{\rm f}$                         | 26.52 μF     |

| Filter Damping $R_{\rm f}$                 | 0.97 Ω       |

| Switching Frequency f <sub>s</sub>         | 5 kHz        |

Figure 12: VSC Control System Implemented for Reactive Current Injection Control

Figure 13: Maximum Compensation according to Rated Inverter Capacity

Figure 14: Control of Reactive Compensation for Voltage Instability Events with the injection Ramp Rate

Defined

Provided here is further detail of implementing a system model that appropriately accounts for a detailed switched converter model including device losses. Particularly, this type of model needs to circumvent shoot-through phenomena and requires a LCL filter design due to harmonics generated. Also explained is the difference in inverter control between grid-connected and islanded modes of system operation.