T. Prov. 24/43 T10/52

# UNIVERSIDAD DE GRANADA FACULTAD DE CIENCIAS

BIBLIOTECA UNIVERSITARIA

GRANADA

N.º Documento 0/3376287

N.º Copia 1/6370796

Departamento de Electrónica y Tecnología de Computadores

# SIMULACIÓN Y MODELADO DE TRANSISTORES MOS DE DOBLE PUERTA

TESIS DOCTORAL

Pedro Cartujo Cassinello

2000

UNIVERSIDAD DE GRANADA

Facultad de Ciencias

Fecha ... 2% / 06 / 00.......

ENTRADA NUM. ... 2115......

Departamento de Electrónica y Tecnología de Computadores

D. Juan Antonio López Villanueva, Profesor Titular del Departamento de Electrónica

y Tecnología de Computadores de la Universidad de Granada.

#### **CERTIFICA:**

Que el trabajo de investigación que se recoge en la presente Memoria, titulada Simulación y Modelado de Transistores MOS de Doble Puerta, y presentada por **D. Pedro Cartujo Cassinello** para optar al grado de Doctor en Ciencias Físicas, ha sido realizado en su totalidad bajo su dirección en el Departamento de Electrónica y Tecnología de Computadores de la Universidad de Granada.

Granada, 13 de Junio, 2000

Fdo. D. Juan Antonio López Villanueva

Profesor del Departamento de Electrónica

Universidad de Granada

UNIVERSIDAD DE GRANADA

19 JUN. 2000

COMISION DE DOCTORADO

A mis padres

A Vanessa

### AGRADECIMIENTOS.

Quiero expresar mi más sincero agradecimiento a todas las personas que de alguna forma han contribuido en la realización de esta tesis doctoral.

A mi director, D. Juan Antonio López Villanueva, por su esfuerzo y dedicación. Por haberme propuesto este interesante trabajo. Por su inestimable ayuda que siempre me prestó. Por la confianza en mí depositada.

- A D. Pedro Cartujo Estébanez, mi padre, Catedrático de Electrónica y Director del Departamento de Electrónica y Tecnología de Computadores, por su continuo apoyo tanto en el plano personal como el profesional, por haber puesto a mi disposición todos los medios necesarios para la realización de este trabajo.

- A D. Juan Enrique Carceller Beltrán, Catedrático de Electrónica, por su apoyo y constante asesoramiento.

- A D. Francisco Gámiz Pérez, por su desinteresada ayuda y por proporcionarme muchos de los resultados que aparecen en este trabajo. Por las interesantes discusiones mantenidas.

- A D. Jesús Banqueri Ozaez, por haberme iniciado en la investigación. La experiencia adquirida en ese periodo ha sido luego fundamental a la hora de abordar este trabajo.

Al resto de componentes del Grupo de Investigación en Dispositivos Electrónicos (GRIDE) del Departamento de Electrónica: D. Juan Antonio Jiménez Tejada, D. Alberto Palma López, D. Juan Bautista Roldán Aranda, D. Andrés Godoy Medina, D. Salvador Rodríguez Bolívar, D. Francisco Jiménez Molinos, D. Valentín Tijeras García, D. Ignacio Melchor Ferrer y a D. Yassir Ghailan, por su ayuda y apoyo.

A mi madre, a mis familiares y amigos que siempre me han animado y ayudado durante tantos años.

## ÍNDICE

| • | INTRODUCCIÓN: PLANTEAMIENTO Y OBJETIVOS       | 1              |

|---|-----------------------------------------------|----------------|

|   | 1.1 EL MOSFET DE DOBLE PUERTA (DGMOST):       | 1              |

|   | DIFERENTES LABORATORIOS.                      | 9              |

|   | 1.2.1 MUESTRAS EXPERIMENTALES                 |                |

|   | 1.3 OBJETIVOS Y METODOLOGÍA:                  |                |

| 2 | LA ESTRUCTURA MOSOM (METAL-ÓXIDO-SEMICONDUCTO | ND_            |

|   | XIDO-METAL)                                   |                |

|   |                                               |                |

|   | 2.1 DESCRIPCIÓN DE LA ESTRUCTURA              | 25             |

|   | 2.1.1 INTRODUCCIÓN                            | 25             |

|   |                                               | 25             |

|   | 2.1.1 INTRODUCCIÓN                            | 25<br>27       |

|   | 2.1.1 INTRODUCCIÓN                            | 25<br>27<br>27 |

| 2.2 | RES   | SOLUC       | IÓN DE LAS ECUACIONES UNIDIMENSIONALES DE         |     |

|-----|-------|-------------|---------------------------------------------------|-----|

| POI | SSO   | N Y SC      | HRÖDINGER                                         | 41  |

|     |       |             |                                                   |     |

| 2   | .2.1  | <b>ECUA</b> | CIÓN DE POISSON CLÁSICA                           | 41  |

| 2   | .2.2  | ECUA        | CIÓN DE SCHRÖDINGER. CUANTIZACIÓN                 | 43  |

| 2   | .2.3  | MÉTO        | DOO DE RESOLUCIÓN                                 | 48  |

| 2   | .2.4  | NO PA       | ARABOLICIDAD                                      | 49  |

| 2   | .2.5  | RESUL       | LTADOS                                            | 51  |

|     |       |             |                                                   |     |

|     | 2.2.: | 5.1 SUE     | BBANDAS DE ENERGÍA Y FUNCIONES DE ONDA            | 52  |

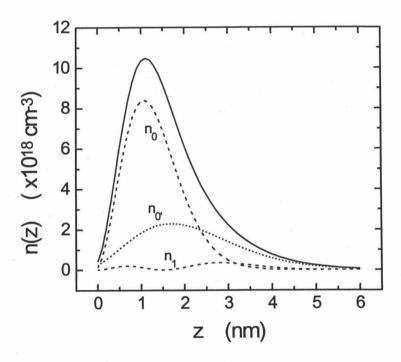

|     | 2.2.: | 5.2 DIS     | TRIBUCIÓN DE ELECTRONES CON Y SIN INVERSIÓN EN    |     |

|     | VO    | LUMEN       |                                                   | 54  |

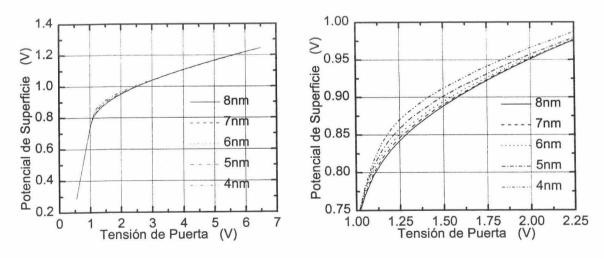

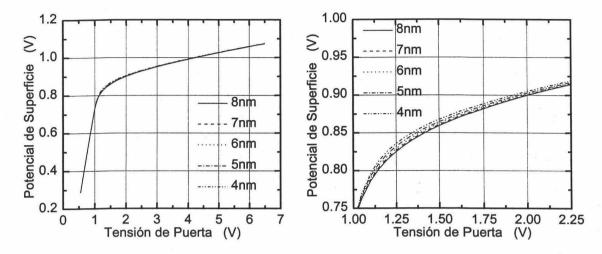

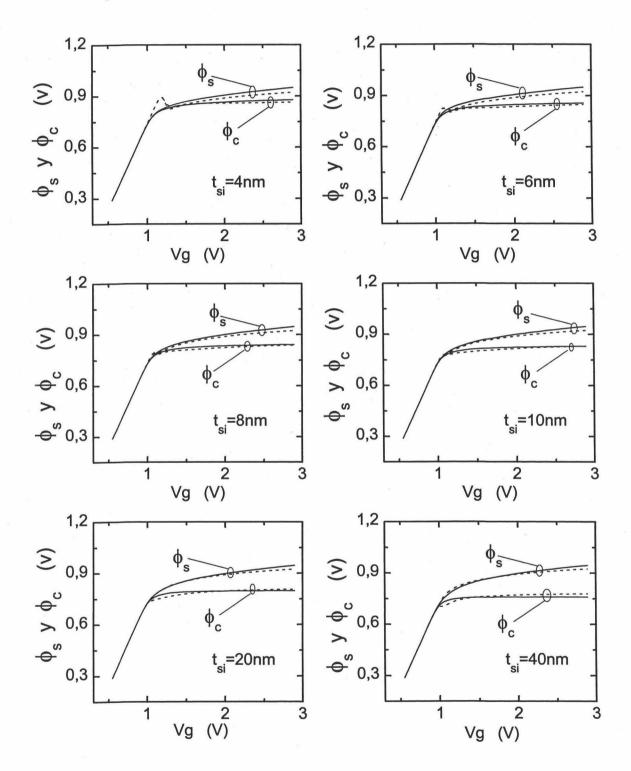

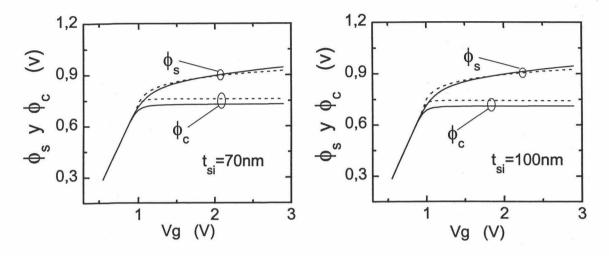

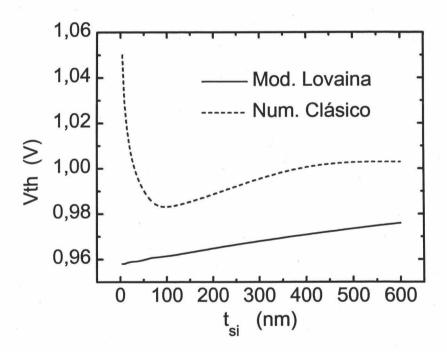

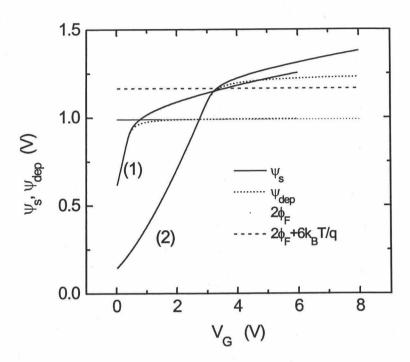

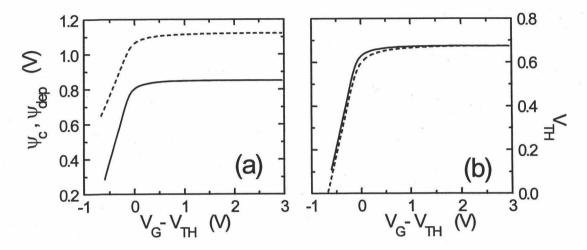

|     | 2.2.: | 5.3 POT     | TENCIALES CENTRAL Y DE SUPERFICIE. COMPARACIÓN EN | TRE |

|     | LOS   | S CASOS     | S CLÁSICO Y CUÁNTICO                              | 65  |

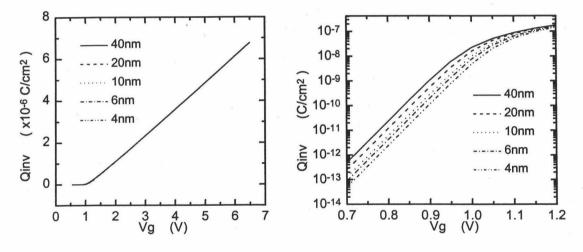

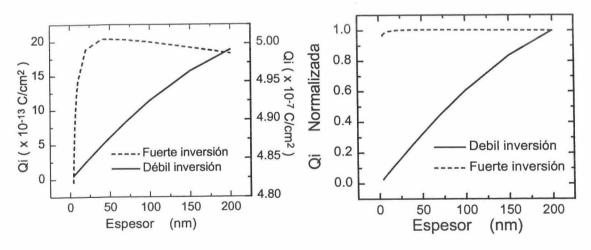

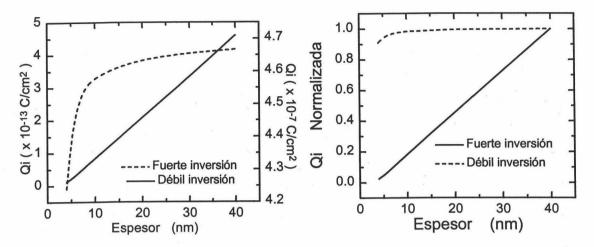

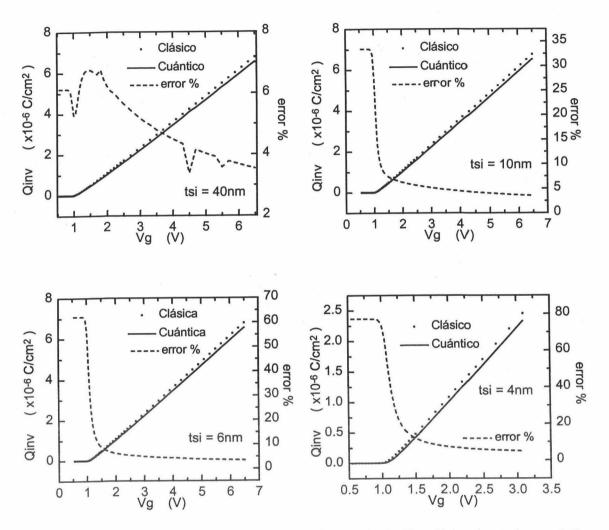

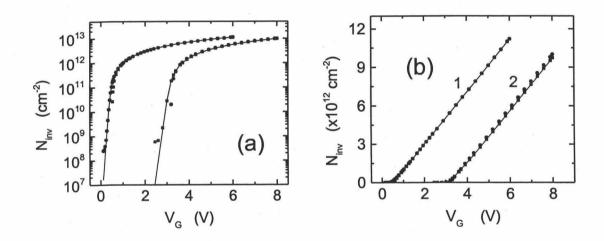

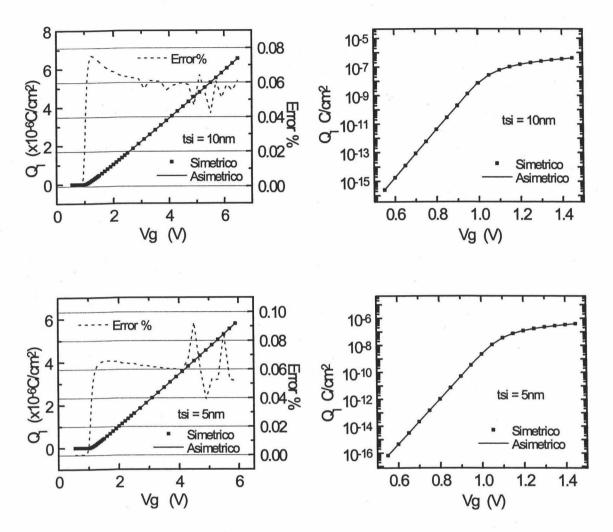

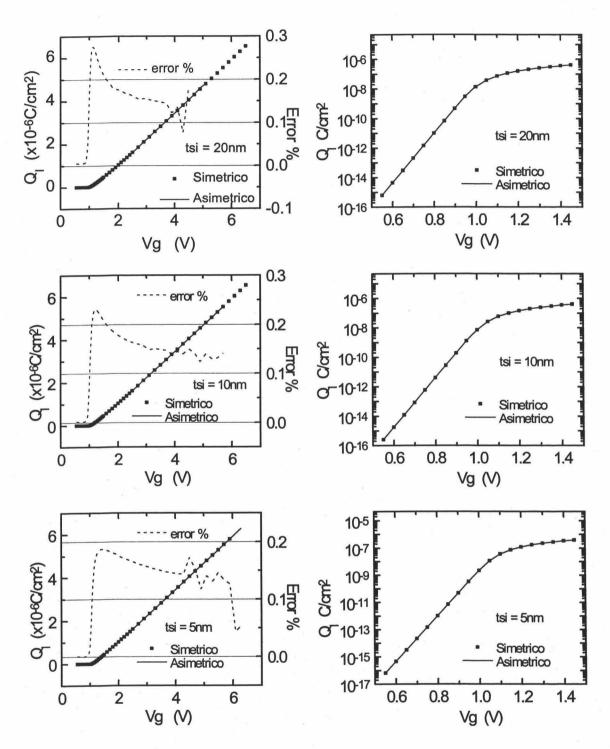

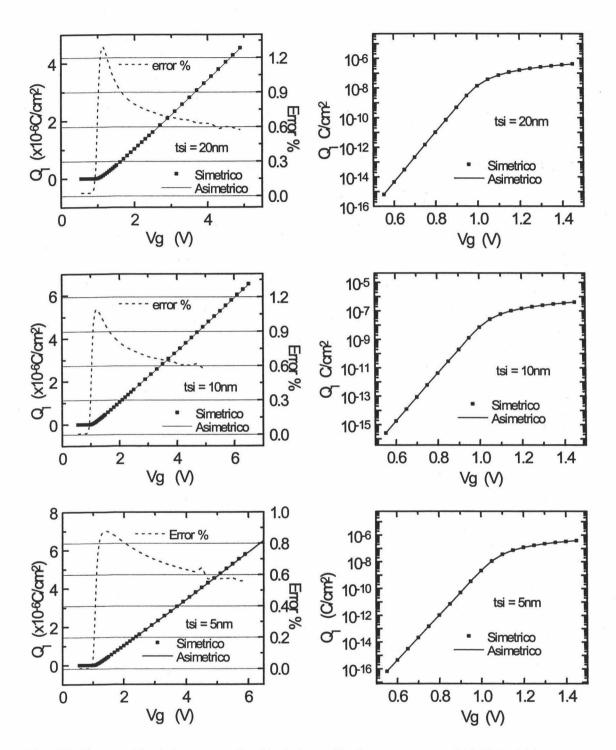

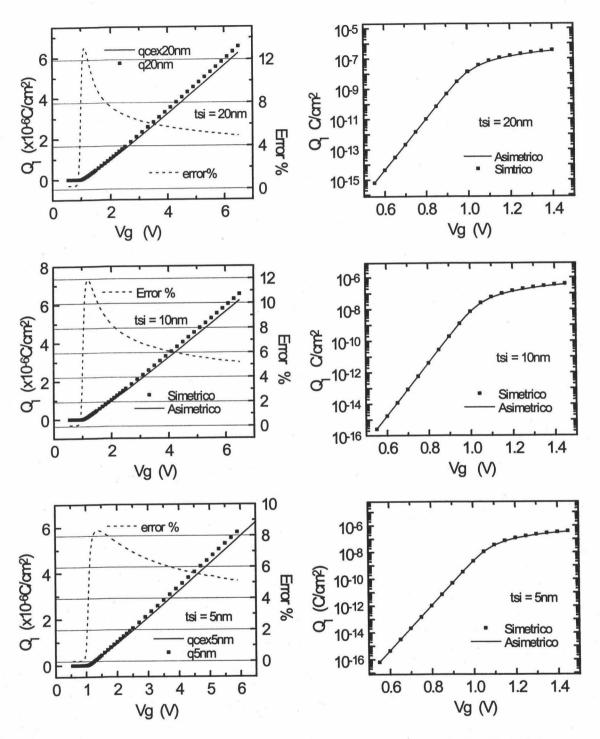

|     | 2.2.  | 5.4 CAF     | RGA EN INVERSIÓN. PENDIENTE SUBUMBRAL             | 69  |

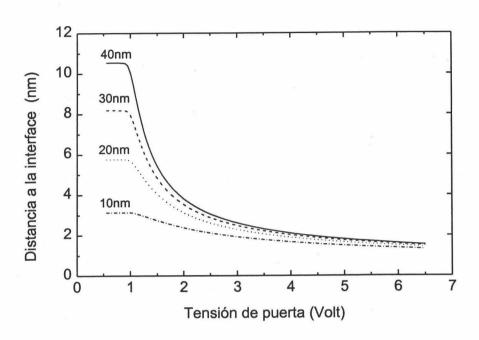

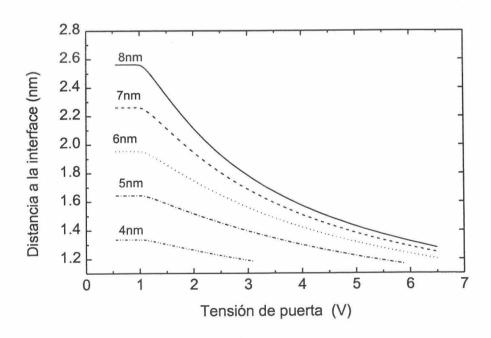

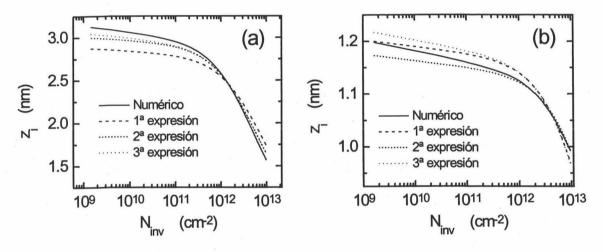

|     | 2.2.  | 5.5 CEN     | NTROIDE DE LA DENSIDAD DE CARGA                   | 74  |

|     |       |             |                                                   |     |

| 2.3 | LA    | TENSI       | ÓN UMBRAL                                         | 77  |

|     |       |             |                                                   |     |

| 2   | 2.3.1 | MÉTO        | DDOS DE DEFINICIÓN DE LA TENSIÓN UMBRAL           | 77  |

|     |       |             |                                                   |     |

|     | 2.3.  | 1.1 MO      | DELO DE FUJITSU                                   | 79  |

|     |       |             |                                                   |     |

|     | 2     | .3.1.1.1    | DESCRIPCIÓN BREVE DEL MODELO                      | 80  |

|     | 2     | .3.1.1.2    | HIPÓTESIS Y APROXIMACIONES                        | 81  |

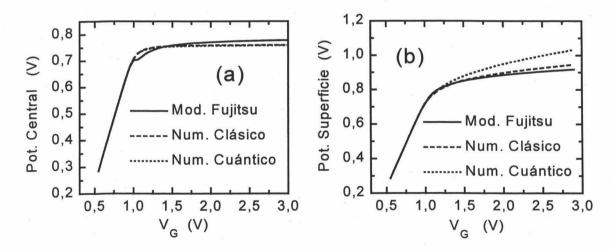

|     | 2     | .3.1.1.3    | POTENCIALES CENTRAL Y DE SUPERFICIE               | 82  |

|     | 2     | .3.1.1.4    | DEFINICIÓN DE TENSIÓN UMBRAL                      | 83  |

| 2.3.1.2 MODELO DE LOVAINA85                                            |

|------------------------------------------------------------------------|

| 2.3.1.2.1 DESCRIPCIÓN BREVE DEL MODELO85                               |

| 2.3.1.2.2 HIPÓTESIS Y APROXIMACIONES                                   |

| 2.3.1.2.3 DEFINICIÓN DE TENSIÓN UMBRAL                                 |

| 2.3.2 MÉTODOS DE DEFINICIÓN UTILIZADOS EN NUESTRO ESTUDIO.             |

| RESULTADOS89                                                           |

|                                                                        |

| 2.3.2.1 DEPENDENCIA CON EL ESPESOR DE LA LÁMINA DE SILICIO.            |

| DISTINTAS REGIONES91                                                   |

|                                                                        |

| 2.3.3 COMPARACIÓN CON OTROS MÉTODOS DE DEFINICIÓN DE LA                |

| TENSIÓN UMBRAL                                                         |

|                                                                        |

| 2.3.3.1 COMPARACIÓN CON EL MODELO DE FUJITSU94                         |

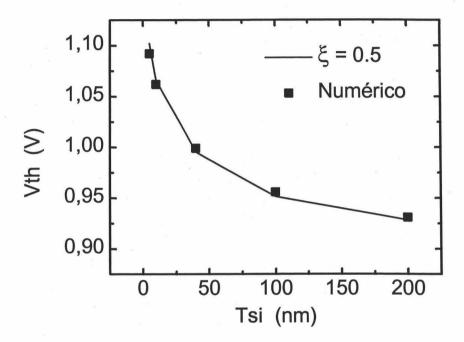

| 2.3.3.1.1 TENSIÓN UMBRAL EN FUNCIÓN DEL ESPESOR tsi PARA               |

|                                                                        |

| DISTINTOS ξ                                                            |

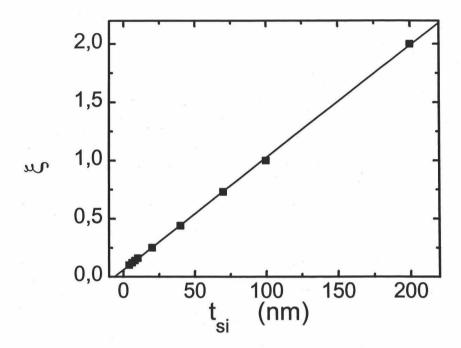

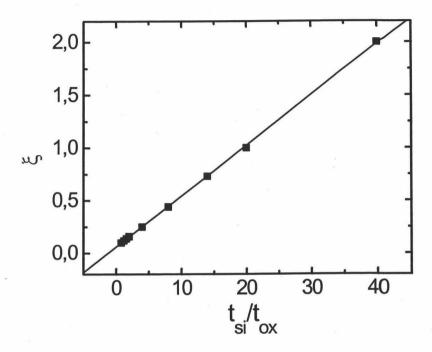

| 2.3.3.1.2 TENSIÓN UMBRAL EN EL CASO PARTICULAR $t_{si}/t_{ox} = 10$ 97 |

| EN FUNCIÓN DE tsi PARA AJUSTAR VALORES NUMÉRICOS99                     |

| 2.3.3.1.4 POTENCIAL DE SUPERFICIE Y CENTRAL102                         |

| 2.3.3.2 COMPARACIÓN CON EL MODELO DE LOVAINA105                        |

| L.J.J.L COMMINICATION CONTROL TO LANGUAGE                              |

| 3 COM   | PARACIÓN ENTRE UN MOSFET CONVENCIONAL Y UN MOS     | FET   |

|---------|----------------------------------------------------|-------|

| DE DOBL | E PUERTA. EFECTOS Y MODELADO DEL CENTROIDE DE LA   | 4     |

| LÁMINA  | DE INVERSIÓN                                       | 109   |

|         |                                                    |       |

| 0.1 D.W | ED ODLIGGIÓN                                       | 100   |

|         | TRODUCCIÓN                                         |       |

| 3.2 CA  | NALES INDEPENDIENTES                               | 111   |

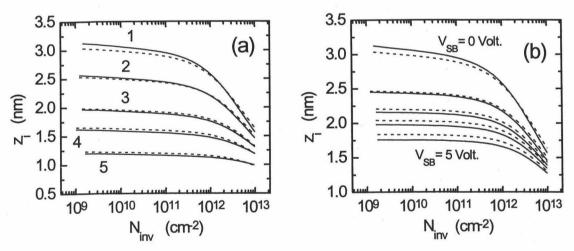

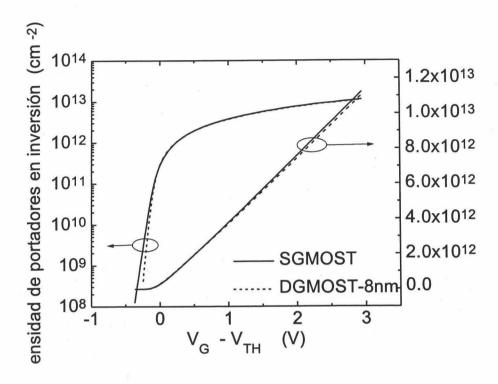

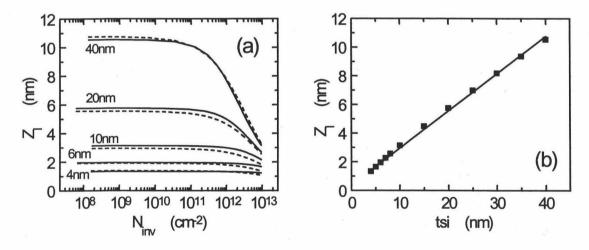

| 3.2.1   | EFECTOS DEL CENTROIDE SOBRE LA CURVA CARGA-TENSION | . 113 |

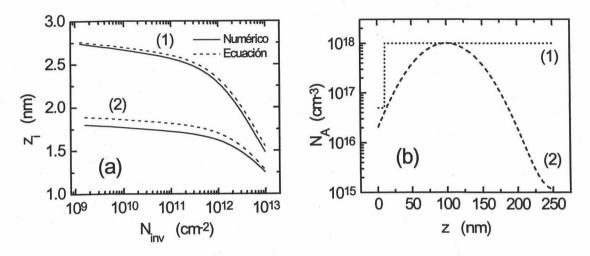

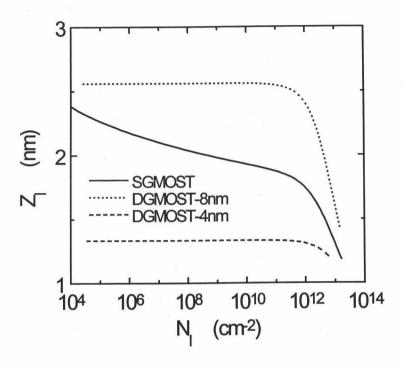

| 3.2.2   | MODELADO DEL CENTROIDE DE LA CAPA DE INVERSIÓN     | 120   |

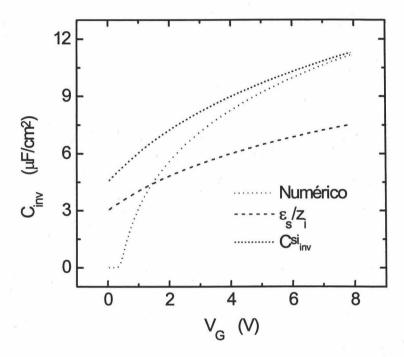

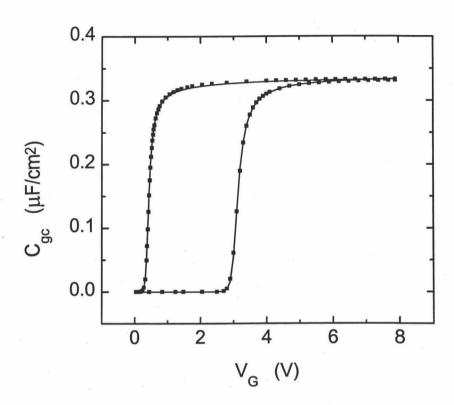

| 3.2.3   | EFECTOS DEL CENTROIDE SOBRE LA CURVA CAPACIDAD-    |       |

| TENS    | IÓN                                                | 128   |

| 3.3 CA  | NALES PRÓXIMOS: INVERSIÓN EN VOLUMEN               | 134   |

| 3.3.1   | EFECTOS DEL CENTROIDE SOBRE LA CARGA EN INVERSIÓN  | 134   |

| 3.3.2   | COMPARACIÓN ENTRE UN MOSFET DE PUERTA SIMPLE Y UN  |       |

| DGM     | OST EN INVERSIÓN EN VOLUMEN                        | 139   |

| 3.3.3   | MODELADO DEL CENTROIDE DE LA CAPA DE INVERSIÓN     | 146   |

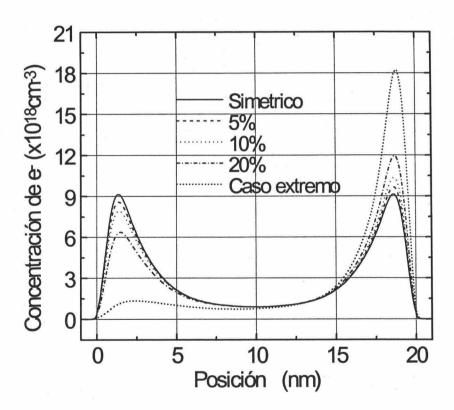

| 3.4 LA  | ESTRUCTURA MOSOM ASIMETRICA                        | 149   |

| 3.4.1   | ANALISIS DE LA ESTRUCTURA                          | 149   |

| 3.4.2   | ESTRUCTURA MOSOM CON DIFERENTES ESPESORES DE ÓXIL  | 0154  |

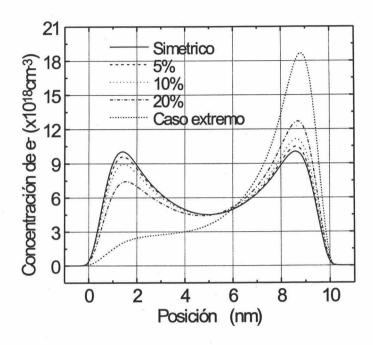

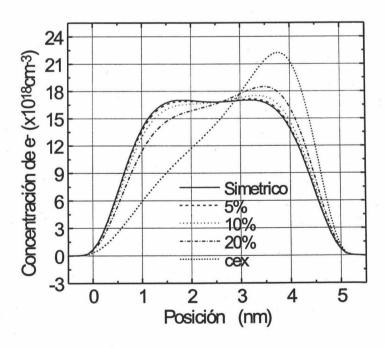

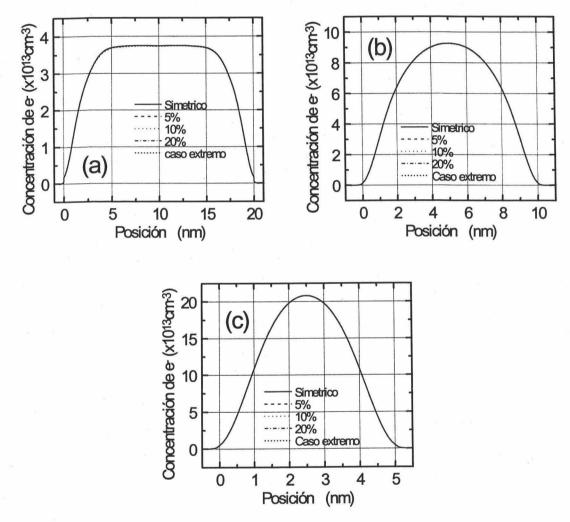

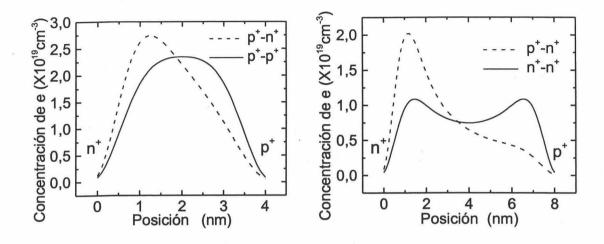

| 3.4.    | .2.1 DISTRIBUCIÓN DE ELECTRONES                    | 155   |

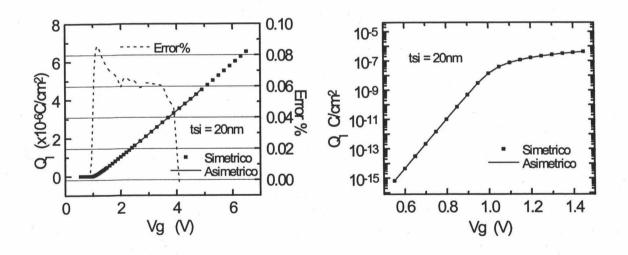

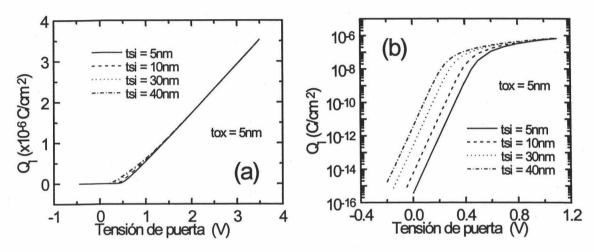

|         | .2.2 CARGA EN INVERSIÓN                            |       |

| 3.4     | .2.3 TENSIÓN UMBRAL                                | 164   |

| 3.4     | 2.4 CENTROIDE DE LA CAPA DE INVERSIÓN              | 165   |

| 3.    | 4.3   | ESTRUCTURA MOSOM CON DIFERENTES MA               | TERIALES DE PUERTA |

|-------|-------|--------------------------------------------------|--------------------|

|       |       |                                                  |                    |

|       |       |                                                  |                    |

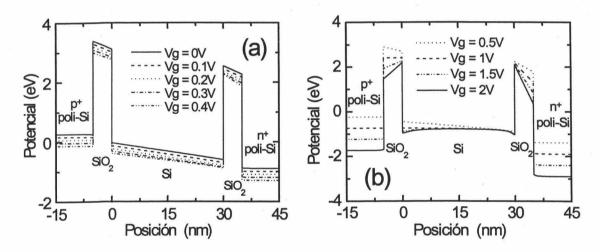

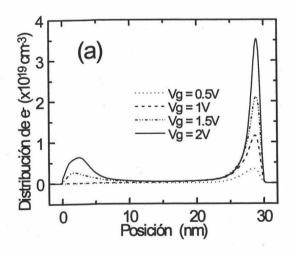

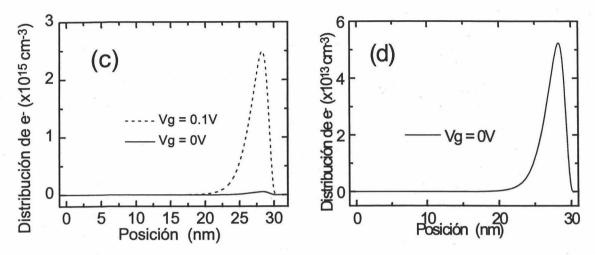

|       | 3.4.3 | .1 DISTRIBUCIÓN DEL POTENCIAL                    | 168                |

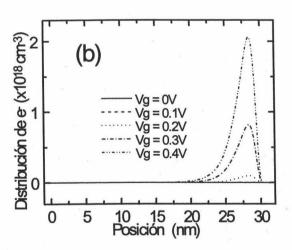

|       | 3.4.3 | .2 DISTRIBUCIÓN DE ELECTRONES                    | 169                |

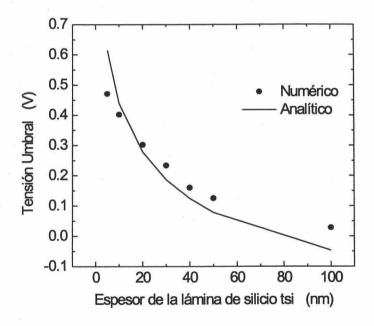

|       | 3.4.3 | .3 TENSIÓN UMBRAL                                | 171                |

|       |       | .4 CARGA EN INVERSIÓN                            |                    |

|       | 3.4.3 | .5 CENTROIDES                                    | 175                |

|       |       |                                                  |                    |

| 4 E   | L DC  | GMOST EN OPERACIÓN SUBUMBRAL. LO                 | NGITUD MÍNIMA DEL  |

| CANA  | L     | ••••••                                           | 177                |

|       |       |                                                  |                    |

| 4.1   | INT   | RODUCCIÓN                                        | 177                |

|       |       | ALADO DEL TRANSISTOR SOI DE PUERTA S             |                    |

|       |       | CALADO DEL DGMOST P <sup>+</sup> -P <sup>+</sup> |                    |

| 0.00  |       | CALADO DEL DGMOST P <sup>+</sup> -N <sup>+</sup> |                    |

| 4.4   | ESC   | ALADO DEL DOMOST F -N                            | 201                |

| 5 E   | STU:  | DIO DE LA MOVILIDAD DE LOS ELECTRO               | NES EN EL CANAL    |

| DE UN | N DG  | MOST                                             | 207                |

|       |       |                                                  |                    |

| 5.1   | INT   | RODUCCIÓN                                        | 207                |

| 5.2   | TRA   | ANSPORTE EN UNA LÁMINA DE INVERSIÓN              | SEMICONDUCTORA     |

|       |       |                                                  | 216                |

|       |       |                                                  |                    |

| 5.    | 2.1   | PROCESOS DE DERIVA                               | 216                |

| 5.    | 2.2   | PROCESOS DE DISPERSIÓN                           | 219                |

| 5     | 2.3   | DISPERSIÓN POR FONONES                           | 222                |

| 5.2.3.1 TRANSICIONES ACÚSTICAS INTRAVALLE                 | .222  |

|-----------------------------------------------------------|-------|

| 5.2.3.2 TRANSICIONES ÓPTICAS INTRAVALLE                   | .223  |

| 5.2.3.3 TRANSICIONES INTERVALLE                           | .223  |

|                                                           |       |

| 5.2.4 DISPERSIÓN CULOMBIANA                               | 224   |

| 5.2.5 DISPERSIÓN POR RUGOSIDAD SUPERFICIAL                | 225   |

|                                                           |       |

| 5.3 SIMULACIÓN POR EL MÉTODO DE MONTE CARLO               | 226   |

| 5.4 MODELO DE RUGOSIDAD SUPERFICIAL PARA DISPOSITIVOS SOI | . 229 |

| 5.5 RESULTADOS                                            | . 237 |

|                                                           |       |

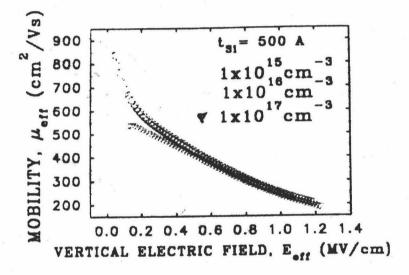

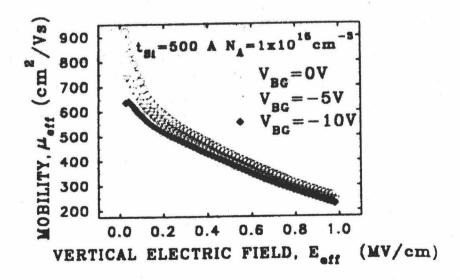

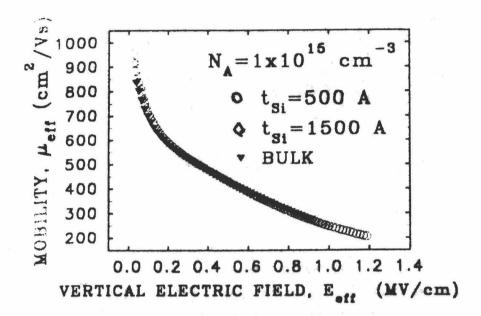

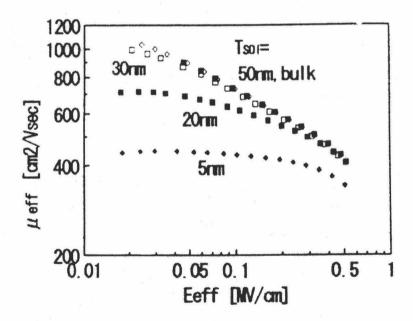

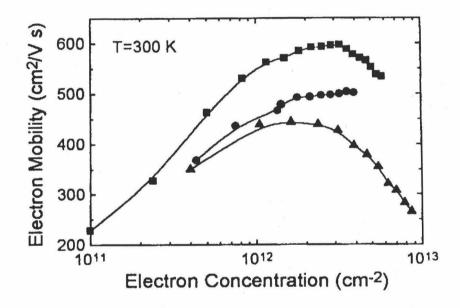

| 5.5.1 RESULTADOS PARA TRANSISTORES SOI DE PUERTA SIMPLE   | . 237 |

| 5.5.2 RESULTADOS PARA TRANSISTORES DE DOBLE PUERTA        | . 245 |

|                                                           |       |

| 5.5.2.1 MOVILIDAD LIMITADA POR LA DISPERSIÓN CULOMBIANA   | 245   |

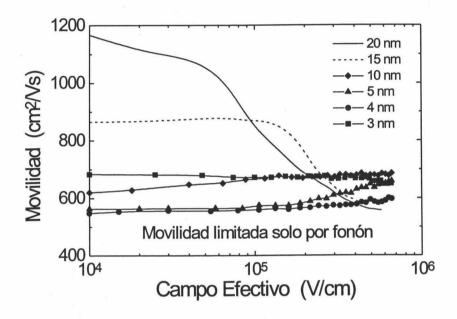

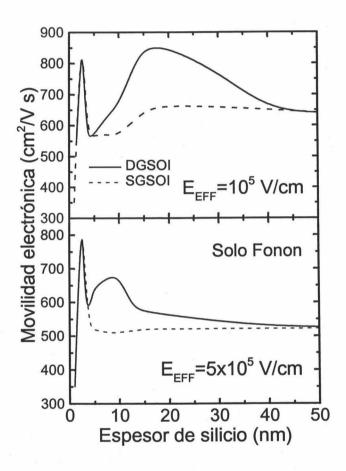

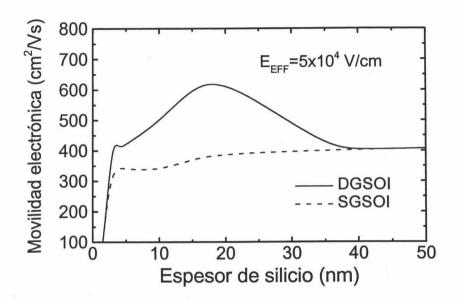

| 5.5.2.2 MOVILIDAD LIMITADA POR FONONES                    | 247   |

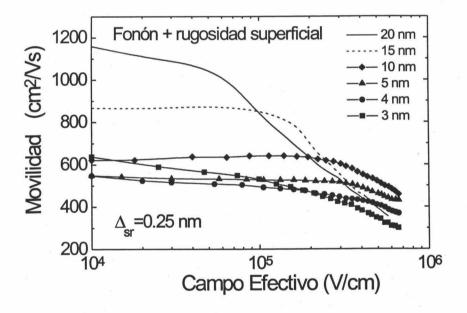

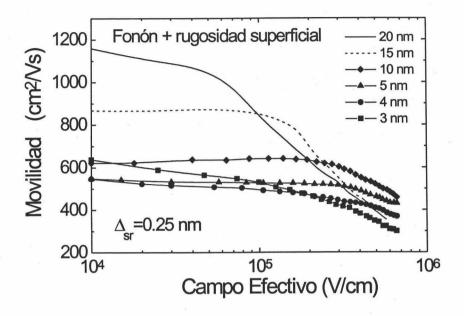

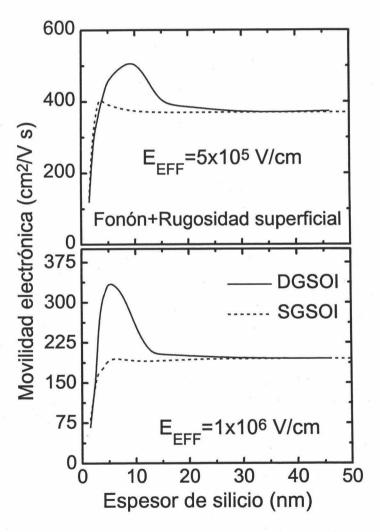

| 5.5.2.3 MOVILIDAD LIMITADA POR RUGOSIDAD SUPERFICIAL      | 250   |

| 5.5.2.4 MOVILIDAD TENIENDO EN CUENTA TODOS LOS EFECTOS DE |       |

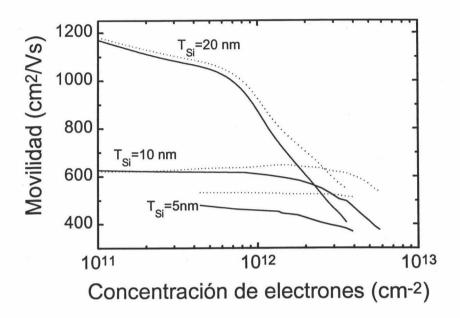

| DISPERSIÓN                                                | 254   |

| 5.5.2.5 COMPARACIÓN DE LA MOVILIDAD DE UN MOSFET DE DOBLE |       |

| PUERTA CON UN MOSFET SOI DE PUERTA SIMPLE                 | 258   |

| 5.5.2.6 COMPARACIÓN DE LA MOVILIDAD DE UN MOSFET DE DOBLE |       |

| PUERTA CON UN MOSFET CONVENCIONAL                         | 264   |

|                                                           |       |

| CONCLUSIONES                                              | 267   |

|                                                           |       |

| BIBLIOGRAFÍA                                              | 275   |

### **CAPÍTULO I:**

### 1 INTRODUCCIÓN: PLANTEAMIENTO Y OBJETIVOS

### 1.1 EL MOSFET DE DOBLE PUERTA (DGMOST):

A pesar del crecimiento exponencial continuo que se ha producido en la tecnología CMOS durante las tres últimas décadas, en las que se ha seguido cumpliendo la ley de Moore, existen muchos datos que hacen pensar que se alcanzarán límites físicos fundamentales en el futuro próximo [Wong et al., 99]. Las innovaciones tecnológicas que se han ido introduciendo hasta la fecha han permitido superar muchos obstáculos haciendo posible la fabricación de transistores con dimensiones características del orden de unos 100 nm, con prestaciones razonablemente buenas. Esto ha hecho que la tecnología CMOS sea, hoy día, la dominante en la industria electrónica. No obstante, aunque esta tendencia de perfeccionamiento tecnológico parece mantenerse en la actualidad, se han puesto de manifiesto nuevos problemas que amenazan el futuro de esta tecnología y que parecen predecir una reducción del ritmo de crecimiento hasta alcanzar una saturación en la próxima década. Entre estos inconvenientes podemos mencionar los siguientes:

- i) Dificultades en la aplicación de la litografía óptica, que utiliza luz de longitud de onda mínima de unos 193 nm, para tratar con dimensiones inferiores a 100 nm.

- ii) Corrientes túnel a través de los óxidos de puerta, una vez que éstos alcanzan espesores inferiores a 2 nm. De hecho se ha sugerido que el límite mínimo posible para un comportamiento aislante es de unos 1.2 nm [Muller et al, 99; Schulz, 99].

- iii) Excesiva concentración de impurezas en las regiones de carga espacial, que ha motivado la introducción de técnicas sofisticadas como el crecimiento de capas epitaxiales débilmente impurificadas sobre substratos altamente dopados.

- iv) Mantenimiento de la carga almacenada en las celdas de memoria, una vez que el área utilizada para las capacidades se ha hecho excesivamente pequeña al aproximarnos a la generación "gigabit", que plantea problemas incluso con las estructuras tridimensionales profundas o con los apilamientos conductor-dieléctrico.

- v) Fluctuaciones aleatorias de las propiedades del dispositivo, causadas principalmente por la dispersión del número de impurezas dopantes en las zonas de carga espacial, con consecuencias muy negativas sobre la tensión umbral, entre otros parámetros.

- vi) Dificultades para el uso de bajas tensiones de alimentación, necesarias para conseguir un bajo consumo de potencia, que se hace imprescindible si se desea integrar centenas de millones de transistores en un mismo "chip".

- vii) Y la excesiva proximidad de las impurezas de las regiones de drenador, fuente, e incluso de la propia puerta, a los portadores de carga en el canal, con la consiguiente reducción en la movilidad de éstos y en la transconductancia del dispositivo.

En este panorama, se han propuesto diversas estructuras que aprovechan el alto grado de desarrollo de la tecnología de silicio actual, pero que incorporan modificaciones significativas que podrían permitir la superación parcial de algunos de estos problemas, manteniendo así el avance en la complejidad de los circuitos integrados durante un periodo mayor de tiempo. Entre estas estructuras novedosas se

encuentran los transistores MOS de doble puerta.

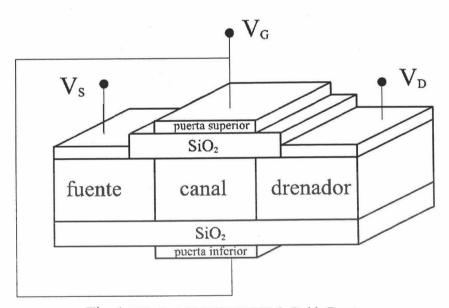

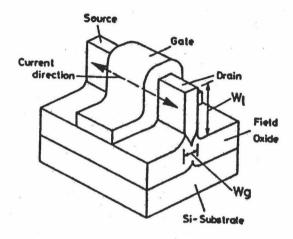

El transistor MOS de silicio de doble puerta (DGMOST), propuesto en 1984 [Sekigawa et al., 1984], consiste básicamente en una lámina delgada de silicio monocristalino, muy débilmente dopado, que conecta dos regiones de fuente y drenador situadas en sus extremos, y que está separado de dos puertas de control, una de ellas llamada frontal y la otra llamada posterior, por dos láminas delgadas de óxido de puerta. Un corte de esta estructura se representa en la Figura 1.

Fig. 1: Dibujo del MOSFET SOI de Doble Puerta.

En cierta forma se podría considerar al DGMOST como un tipo particular de transistor MOS en tecnología SOI ("Silicon On Insulator"), ya que en esta tecnología la lámina activa de silicio está separada del sustrato mediante una capa de óxido enterrado, con lo que el substrato podría desempeñar el papel de puerta posterior. Sin embargo, esta puerta posterior sería común para todos los dispositivos y, además, el óxido enterrado suele ser mucho más grueso que el óxido frontal de puerta, ejerciendo menor influencia en las propiedades de transporte del canal, mientras que en el DGMOST los dos óxidos tienen el mismo espesor, y las dos puertas suelen estar interconectadas entre sí e independientemente del resto de los dispositivos, lo que les confiere a los dos tipos

de transistores diferentes propiedades. No obstante, se puede afirmar que el DGMOST combina las características de un transistor SOI en deplexión total con las ventajas que aporta la disponibilidad de una segunda puerta de control, a cambio de una mayor complejidad tecnológica. Veamos esto en detalle:

Un transistor SOI en deplexión total consiste en una lámina delgada de silicio débilmente dopado, que conecta las regiones de fuente y drenador, y aislado por dos láminas de óxido. Una de ellas es el óxido de puerta, que separa la lámina de silicio que va a albergar al canal de la puerta frontal de control, y la otra es el óxido enterrado, que separa a la lámina de silicio del substrato. Para que opere en deplexión total es necesario que la lámina de silicio sea delgada, y poco dopada, de manera que la zona de carga espacial situada debajo del óxido de puerta llegue a alcanzar a la interface silicio-óxido posterior, quedando toda la capa de silicio vacía de portadores mayoritarios, lo que justifica la denominación "fully depleted" que se da a esta estructura.

Varias son las ventajas del transistor SOI en deplexion total. En este dispositivo no es necesario colocar una concentración de dopante precisa en el canal, ya que la extensión de la zona de carga espacial está limitada por el óxido posterior y no por la distribución de la concentración de impurezas. En particular, la densidad de impurezas en la región del canal puede ser muy baja con la consecuente reducción en la dispersión culombiana de los portadores de carga. Esto alivia el inconveniente (iii) antes mencionado. También reduce el problema de las fluctuaciones del número discreto de las impurezas dopantes, descrito en el punto (v). Finalmente, al estar fijada la carga de deplexión, también crece la pendiente de la curva de corriente en la región subumbral, alcanzándose un valor próximo al ideal [Colinge, 1986], lo que posibilita el diseño de dispositivos con tensiones umbrales inferiores, y, en consecuencia, con tensiones de alimentación más reducidas, solventándose el problema comentado en el punto (vi). La necesidad de un perfil lateral muy abrupto de la concentración de impurezas dopantes aún permanece en estas estructuras.

Los transistores MOS SOI en deplexión total disfrutan también de las cualidades de los dispositivos SOI en general, como son el aislamiento lateral y menores capacidades parásitas, que se traducen en una mayor velocidad, y su tolerancia a las radiaciones [Colinge et al, 1996], [Balestra et al, 1987]. No surge, en cambio, el problema del efecto "kink", que es uno de los principales inconvenientes de los transistores SOI que operan en deplexión parcial [Yoshimi et al, 1989], [Wang et al, 1994].

Pero no todo son ventajas: como contrapartida, el uso de una lámina de silicio delgada incrementa la resistencia serie parásita del dispositivo y plantea problemas de autocalentamiento al quedar la capa de silicio, en la que se genera el calor por efecto Joule, separada por dióxido de silicio, que tiene una menor conductividad térmica que el silicio. Este aumento de la temperatura produce, a su vez, una disminución en la movilidad [Roldán et al., 1999].

Todas las propiedades del transistor SOI de puerta simple "fully depleted" son compartidas por el DGMOST en deplexión total. Pero, además, la presencia de la segunda puerta de control aporta ventajas adicionales en la operación de estos dispositivos. Una de ellas se debe al mayor apantallamiento de la región de canal por ambas puertas, haciendo que la influencia del drenador sea inferior, al no penetrar en el interior del canal las líneas de fuerza con origen en el drenador tanto como lo hacen en las otras estructuras de transistor, incluidas los SOI de puerta simple. Esto produce una disminución importante en los efectos de canal corto, permitiendo el diseño de transistores con longitudes de canal más reducidas [Frank et al, 92; Wind et al, 96]. La reducción de la longitud del canal puede tener también consecuencias beneficiosas como es la entrada en el régimen de transporte balístico, en particular la aparición del fenómeno de sobredisparo ("overshoot") de la velocidad [Eaton et al., 1978]. Este efecto puede aumentar la transconductancia del transistor [Roldán et al., 1997], [Roldán et al., 1998], o, al menos, oponerse a los otros mecanismos físicos que tienden a reducirla, obteniéndose el beneficio de una mayor velocidad de conmutación

[El-Mansy et al., 1977], [Sasaki, 1981], [Lim et al., 1984]. Además, el DGMOST permanece en deplexión total a temperaturas más altas que los SOI de una sola puerta con el mismo espesor de silicio, y el aislamiento térmico es menor ya que los dos óxidos son delgados, siendo menos graves, por tanto, los efectos de autocalentamiento.

Otra ventaja aportada por la segunda puerta es el mayor flujo de corriente en el canal y, en consecuencia, el aumento de la transconductancia. Si la lámina de silicio es suficientemente delgada como para alcanzar la situación de deplexión total, pero no demasiado, de manera que las capas de inversión que se generan debajo de cada puerta son independientes, se conseguiría así un transistor con dos canales idénticos en paralelo. Este transistor es capaz de aportar el doble de corriente, o bien de aportar la misma corriente reduciendo a la mitad la anchura, pudiendo duplicar de esa manera el nivel de integración.

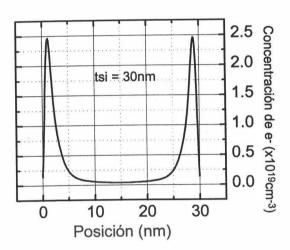

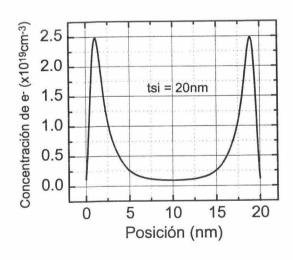

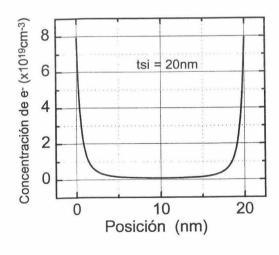

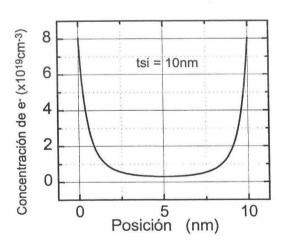

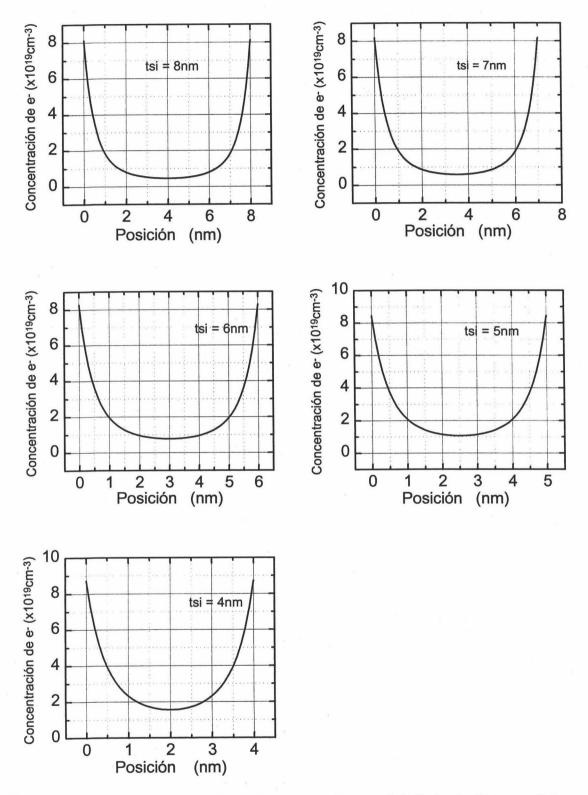

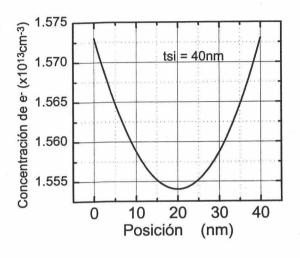

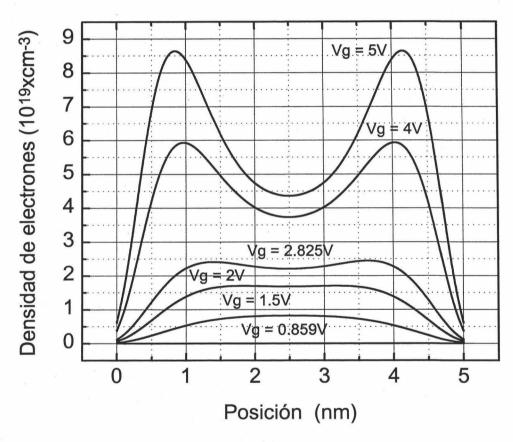

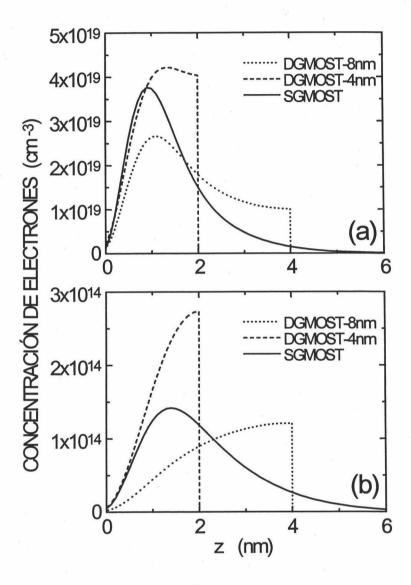

Se ha propuesto que es posible ganar aun más del doble en el incremento de corriente gracias a la llamada "inversión en volumen" [Balestra et al., 1987]. Esta situación se produce cuando la lámina de silicio es aun más delgada de manera que se solapan parcialmente las dos capas de inversión asociadas a las dos puertas. El confinamiento de los electrones en un pozo de potencial estrecho, impuesto por las dos interfaces óxido-silicio, hace que los electrones se distribuyan ocupando todo el volumen de la lámina de silicio. En una interpretación inicial demasiado simplificada, se sugirió que la distribución en toda la lámina en lugar de hacerlo en sólo las interfaces era ya causa de un mayor incremento en la corriente de estos dispositivos [Balestra et al, 1987]. No obstante, las ventajas que caben esperar de la inversión en volumen fueron ya fuente de controversia entre diferentes autores [Balestra et al., 1987; Venkatesan et al., 1992a; Balestra et al, 1992; Venkatesan et al, 1992b]: Balestra y colaboradores predijeron mejoras en un factor de 2.5 a 3 en la corriente de drenador y transconductancia de un transistor SOI de doble puerta en inversión en volumen en comparación con los resultados obtenidos para un transistor SOI de puerta simple. Sin embargo, [Venkatesan et al., 1992a] analizan el comportamiento de un transistor de doble puerta con una lámina de silicio de 100 nm de espesor mediante el simulador clásico "PISCES IIB", y únicamente predicen mejoras en la transconductancia y en la corriente inferiores al 10%. Argumentan que para comparar adecuadamente las dos estructuras hay que tener en cuenta también el desplazamiento de la tensión umbral de un transistor con respecto a la del otro, realizando la comparación para un mismo valor de la diferencia entre la tensión de puerta y la tensión umbral, V<sub>G</sub>-V<sub>TH</sub>. Además, razonan que aunque la movilidad en el centro de la lámina sea mayor que en las interfaces, aproximadamente el triple, la concentración de portadores minoritarios en fuerte inversión, en el centro, es tres ordenes de magnitud menor que en los extremos y por tanto la contribución de la corriente de los portadores de la zona central es muy pequeña, y concluyen que para que los efectos de la inversión en volumen sean notables se requerirían espesores de lámina de silicio menores o iguales a 20nm.

En cualquier caso, las conclusiones extraídas a partir de la distribución de portadores minoritarios calculada mediante un simulador clásico no deben ser aceptadas, al menos en fuerte inversión, ya que los resultados de estos simuladores no son válidos, ni siquiera desde un punto de vista cualitativo, como se pondrá de manifiesto a lo largo de la presente memoria. La relación entre la densidad de electrones en el centro de la lámina de silicio y en la proximidad de las interfaces, en función del espesor de dicha lámina, requiere un estudio más detallado de la distribución electrónica. Además, de la forma concreta de esta distribución dependen muchas de las propiedades esperables de la situación de inversión en volumen. En particular, la distancia de los electrones a las interfaces es decisiva en la determinación de los efectos de la dispersión culombiana debida a las cargas próximas a las interfaces óxido-silicio y de la dispersión por la rugosidad de dichas interfaces.

En resumen, las ventajas que cabría esperar de un DGMOST son: mayor transconductancia, menores efectos de canal corto, y menor tamaño. La mayor transconductancia sería debida al aumento de la movilidad esperado por la reducción del dopado en la lámina de silicio, por una parte, y al alejamiento de los electrones de las

interfaces disminuyendo así el efecto de las cargas presentes en las mismas y de la rugosidad superficial, por otra parte. Los menores efectos de canal corto se deben al efecto de apantallamiento producido por la segunda puerta, y permiten reducir más la longitud del canal aumentando de nuevo la transconductancia, más aun si se produce "overshoot" de la velocidad. El menor tamaño se debe, además de a la posible reducción de la longitud del canal, a la posibilidad de disminuir también su anchura, ya que la disposición de dos canales en paralelo permite hacerlo sin perder capacidad de aportar corriente. En contra de esto podríamos citar la tendencia a la disminución de la transconductancia extrínseca debido a los efectos de la mayor resistencia serie y al autocalentamiento, y, como principal inconveniente, las complicaciones tecnológicas que acarrean estas estructuras, que requieren pasos adicionales de proceso tecnológico, y las dificultades en la alineación de las dos puertas cuando se manejan dimensiones tan pequeñas.

# 1.2 RESULTADOS EXPERIMENTALES Y DE SIMULACIÓN EN DIFERENTES LABORATORIOS.

Desde su propuesta hasta la actualidad, el DGMOST ha despertado el interés de numerosos investigadores, y son ya varios los prototipos desarrollados en laboratorio que han demostrado una operación satisfactoria. Por otra parte, antes de desarrollar de forma masiva una tecnología con las complicaciones que presenta la fabricación de estos transistores, es muy conveniente asegurarse de cuáles son sus verdaderas ventajas, para lo que se requieren simulaciones numéricas lo más realistas y exactas que sea posible. En este apartado pretendemos presentar una visión panorámica de la situación actual, tanto en lo que se refiere al desarrollo de muestras experimentales como a los resultados de simulación.

### 1.2.1 MUESTRAS EXPERIMENTALES.

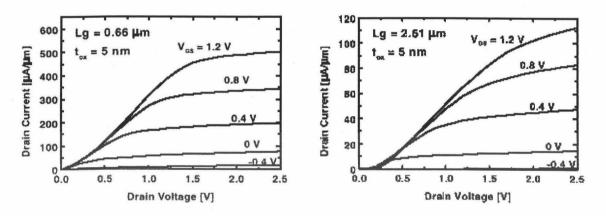

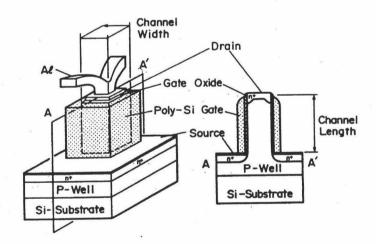

La estructura que permite conseguir láminas delgadas de silicio, con posibilidad de alcanzar el régimen de inversión en volumen, es el DGMOST horizontal realizado con diferentes variantes de la tecnología planar, bien con dos puertas independientes, aunque interconectadas, o con una metalización de puerta única que rodea a toda la lámina de silicio. Diferentes realizaciones prácticas de esta estructura se describen a continuación.

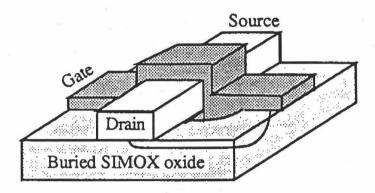

Uno de los primeros transistores MOS de este tipo, con excelentes propiedades, fue el GAA ("Gate-All-Around"), presentado en 1990 [Colinge et al, 1990]. Para la fabricación de este transistor se parte de una oblea SOI, en concreto, obtenida por el procedimiento SIMOX, en la cual se define una isla alargada de silicio sobre el óxido enterrado, mediante ataque del resto. Seguidamente se elimina parte del óxido enterrado debajo de la isla, definiendo una cavidad que se va a utilizar para crecer toda la puerta.

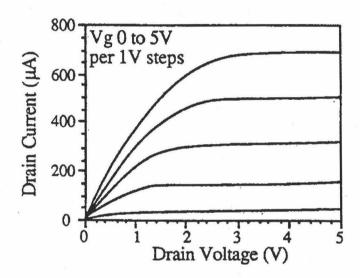

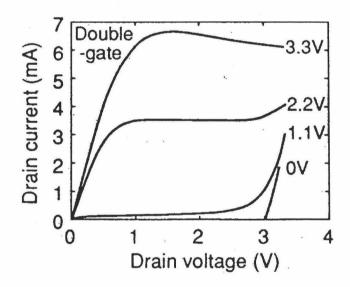

La estructura resultante se muestra en la figura 2, y sus curvas características en la figura 3:

Fig. 2: Vista del transistor GAA (Gate All Around) propuesto por [Colinge et al, 1990].

Fig. 3: Curvas características de salida I<sub>D</sub>-V<sub>D</sub> del transistor GAA.

En este dispositivo todo el óxido que rodea a la lámina de silicio es óxido de puerta, de alta calidad. Al no existir contacto con óxido de campo ni óxido enterrado, ofrecen una excelente dureza ante radiaciones y SEU ("Single Event Upset"), siendo la inevitable creación de estados de interface el único mecanismo de degradación observado. En cuanto a la fabricación, el proceso del GAA es sencillo (solo hay que

añadir dos pasos más con respecto al proceso del SOI convencional: un paso de litografía y una cavidad "etch"). Las curvas características muestran un buen comportamiento, con una transconductancia considerablemente mayor de la que se observa para un transistor SOI de puerta simple de la misma anchura. El problema de si la transconductancia es solamente el doble (lo que se obtendría con dos canales independientes) o es mayor, no se puede considerar totalmente resuelto, ya que es difícil hacer comparaciones experimentales manteniendo exactamente las mismas condiciones en los dos tipos de estructuras. Aunque los investigadores que desarrollaron el GAA ([Colinge et al., 1990]) afirman que se obtiene un factor tres de mejora en la corriente de drenador v entre 2.5 y 3.5 en la transconductancia, para la misma diferencia V<sub>G</sub>-V<sub>TH</sub>. con respecto a un transistor de puerta simple, [Venkatesan et al., 1992b] explican que esta comparación no es muy fiable ya que los espesores del transistor GAA y el de puerta simple utilizados no son iguales y sus anchuras tampoco (el GAA es más ancho, debido a las zonas laterales de la lámina de silicio que también conducen corriente), y, además, el transistor GAA esta en deplexión total mientras que el de puerta simple está en deplexión parcial, siendo parte de la mejoras debidas a la diferencia entre deplexión parcial y total [Sturm et al., 1988b]. Según esto, el incremento del 50% en la corriente y en la transconductancia no podría atribuirse totalmente a la inversión en volumen.

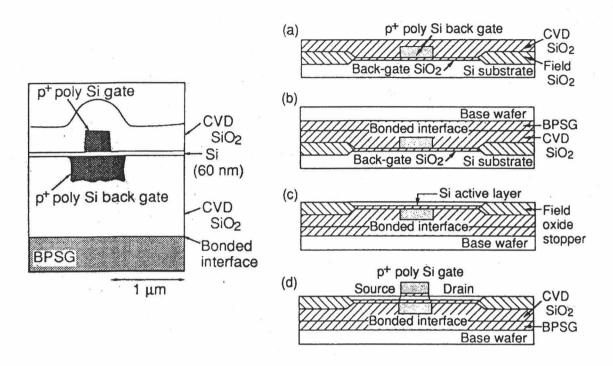

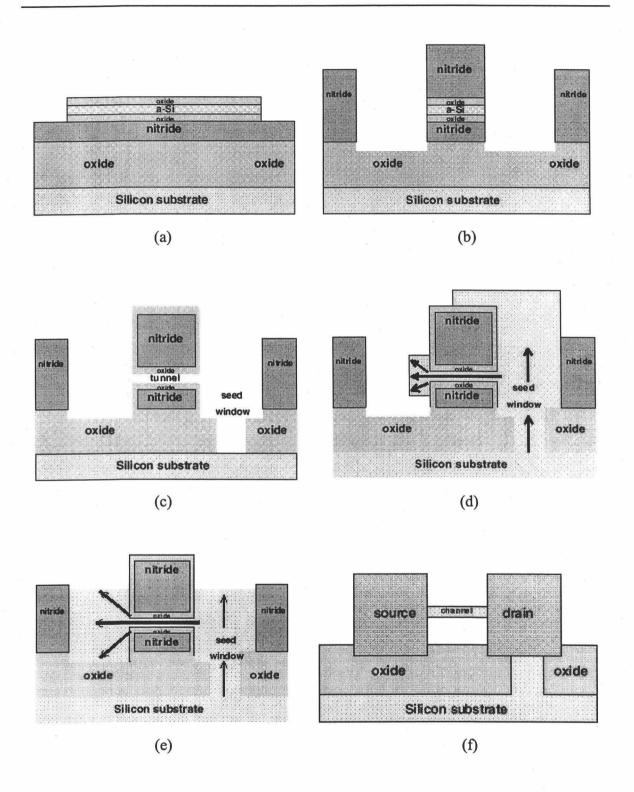

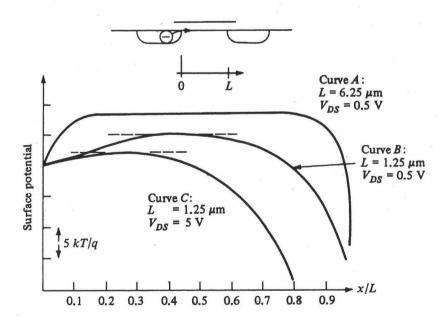

Investigadores de Fujitsu también presentaron en 1991 un transistor de doble puerta con buenas prestaciones [Tanaka et al., 1991]. En este caso se usó la técnica de "soldadura de oblea" con la que se consiguió un transistor con puertas de polisilicio p<sup>+</sup> con una longitud de puerta de 0.17µm y un espesor de la lámina de silicio de 60nm. La estructura resultante y detalles de su fabricación se muestran en la figura 4, y las curvas características conseguidas se representan en la figura 5.

Fig. 4: Estructura DGMOST propuesta por [Tanaka et al., 1991]. Detalle de su fabricación a la derecha.

Fig. 5: Curvas características de salida para el DGMOST propuesto por [Tanaka et al., 1991]

Aparte del buen comportamiento de las curvas características, el incremento conseguido en la transconductancia con respecto al factor 2 parece ser de sólo el 10%,

y, además, se aprecia un decrecimiento para altas tensiones de puerta, que ha sido explicado como un efecto del autocalentamiento [Su et al, 1997].

Estructuras similares han sido desarrolladas también por otros autores. [Vekatesan et al., 1992a] utilizan la técnica de sobrecrecimiento epitaxial lateral de silicio (ELO) sobre una puerta oxidada de polisilicio, y [Tanaka et al., 1994] utilizan la misma técnica de [Tanaka et al., 1991] para fabricar DGMOSTs con puertas de diferente material, una puerta de polisilicio tipo p<sup>+</sup> y otra tipo n<sup>+</sup> con un espesor de lámina de silicio de 40nm y una longitud de puerta de 0.19μm, con el fin de conseguir tensiones umbrales menores de un voltio, cuyo valor depende de la relación entre el espesor de óxido y de silicio que se elijan. Con estos transistores dicen haber conseguido una gran velocidad de operación, con retardos entre 20 y 40 picosegundos, inferiores a los de un MOSFET convencional de 0.15μm de puerta que se utiliza como referencia.

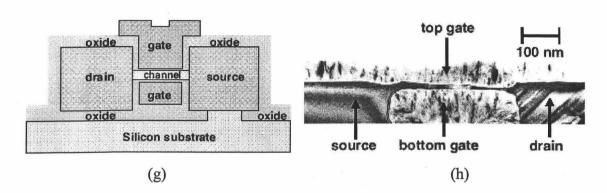

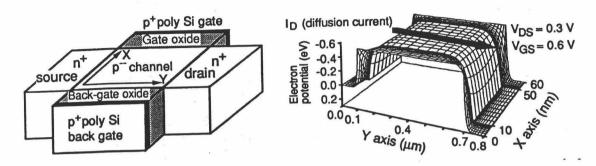

Más recientemente, investigadores de IBM ([Wong et al., 1997]) presentan una técnica de fabricación de DGMOSTs con las dos puertas autoalineadas, mediante crecimiento de un canal amorfo y recristalización posterior. Esta técnica puede resolver algunos problemas tecnológicos ya que la falta de alineamiento puede causar una capacidad de solapamiento puerta-fuente y puerta-drenador extra y pérdida de capacidad de corriente del dispositivo. El proceso de fabricación y la estructura resultante se muestran en la figura 6, y las curvas características conseguidas con esta estructura se presentan en la figura 7.

Fig. 6 (a)-(f): Proceso de fabricación del transistor DGMOST autoalineado propuesto por [Wong et al., 1997]. (g), (h): Estructura resultante.

Fig. 7: Curvas características de salida I<sub>D</sub>-V<sub>G</sub> del transistor DGMOST propuesto por [Wong et al., 1997] para dos longitudes de puerta. Lg es la longitud de canal de mascara.

Además de las estructuras horizontales descritas, se han diseñado también otros dispositivos, en cierta forma similares a los anteriores, en los cuales las puertas se disponen verticalmente, bien con el canal paralelo a la superficie de la oblea o bien con el canal perpendicular a la misma. El primer tipo de estructuras se conoce como DELTA, y consiste en una capa de silicio vertical rodeada por la puerta por encima y por los lados [Hisamoto et al., 1989, 1991]. Para aislar totalmente la lámina de silicio, se permite el crecimiento de algún óxido por debajo de la pared vertical por el efecto de pico de pájaro. La estructura resultante se muestra en la figura 8. Además de las buenas características correspondientes a un transistor de doble puerta hay que sumar las

ventajas de fabricación, ya que este dispositivo no necesita ninguna tecnología de recristalización o SIMOX, al formarse su estructura "tipo SOI" por simple oxidación selectiva (LOCOS), consiguiéndose así un cristal de gran calidad.

Fig. 8: Dibujo la estructura vertical DELTA propuesta por [Hisamoto et al., 1989, 1991]

Fig. 9: Estructura tipo pilar SGT propuesta por [Takato et al., 1988., 1991]

Los otros tipos de estructuras verticales definen pilares de silicio que tienen la fuente en la base y el drenador en el extremo superior, con la puerta rodeando todas sus paredes laterales después de haberlas oxidado. La primera estructura de este tipo, con un pilar rectangular, fué realizada por [Takato et al., 1988, 1991] para fabricar una celda

CMOS y le dieron el nombre de SGT ("Surrounding Gate Transistor"). Un esquema de esta estructura se muestra en la figura 9.

La principal ventaja del SGT es su nivel de integración: Se consigue con él la misma capacidad de conducción ocupando solo el 60% del área de la que ocupa el MOSFET planal convencional. [Sunouchi et al., 1989] utilizaron estos transistores para realizar una celda de memoria DRAM, y [Nitayama et al., 1991] proponen el dispositivo M-SGT ("Multi-Surrounding Gate Transistor"), que es simplemente una agrupación de pequeños SGTs de forma que se consigue reducir aun más el área que ocupa el transistor, llegando en este caso al 30% de lo que ocuparía un MOSFET convencional con la misma capacidad de corriente. La menor área del dispositivo y la estructura de malla del electrodo de puerta hacen que la capacidad de unión y el retardo RC de la puerta sea más pequeño que en el SGT y en el MOSFET convencional.

Otros investigadores que estudian este tipo de estructuras son [Miyano et al., 1992] que realizan un transistor con pilar circular al que dan el nombre de CYNTHIA. [Pein et al. 1993; 1995], que fabrican una celda de memoria EPROM, y [Maeda et al., 1995], que realizan una celda de memoria DRAM de un Gbit con estructura de pilar cilíndrico a la que llaman VΦT (Vertical Φ Shape Transistor).

En general, todas las estructuras verticales comparten la ventaja de permitir un alto nivel de integración, con un proceso tecnológico relativamente simple, siendo muy útiles para el desarrollo de memorias de muy alta capacidad. Y también comparten el inconveniente de definir la pared vertical, en cuya superficie se va a establecer el canal, mediante ataque ("etching") del silicio, en lugar de hacerlo mediante crecimiento epitaxial. Esto lleva consigo dos inconvenientes: Por una parte, la calidad de la superficie ha de ser necesariamente menor, y, en consecuencia, la interface óxido-silicio obtenida después del crecimiento del óxido de puerta también va a ser de menor calidad. Por otra parte, es mucho más difícil conseguir que la lámina o el pilar de silicio sea lo suficientemente delgada como para que se alcance inversión en volumen. Por estas

razones, desde el punto de vista utilizado en esta memoria, los transistores verticales no aportan nada nuevo a los transistores de puerta simple. El canal se puede considerar próximo a la interface óxido-silicio en todas las paredes, y el ancho del transistor será igual al perímetro de los pilares. La única precaución que habría que tener en su análisis sería resolver la ecuación de Poisson con la geometría apropiada si el dispositivo se encuentra en la situación de deplexión total. En esta memoria nos centraremos, pues, en el estudio de la estructura horizontal.

### 1.2.2 RESULTADOS DE SIMULACIÓN.

Los primeros cálculos que se realizaron con estas estructuras se basaron en modelos clásicos, sin tener en cuenta los efectos cuánticos debidos al confinamiento en un pozo de potencial [Balestra et al., 1987; Venkatesan et al., 1992a]. Con estos modelos no resultan válidas las conclusiones que se alcancen basadas en la forma de la distribución de portadores minoritarios, como hemos comentado en el apartado anterior, pero sí pueden considerarse válidas otras conclusiones sobre efectos de la longitud del canal, corriente en la región subumbral, etc. Desde este punto de vista, existen en la bibliografía resultados muy interesantes conseguidos sin tener en cuenta la cuantización en la dirección transversal.

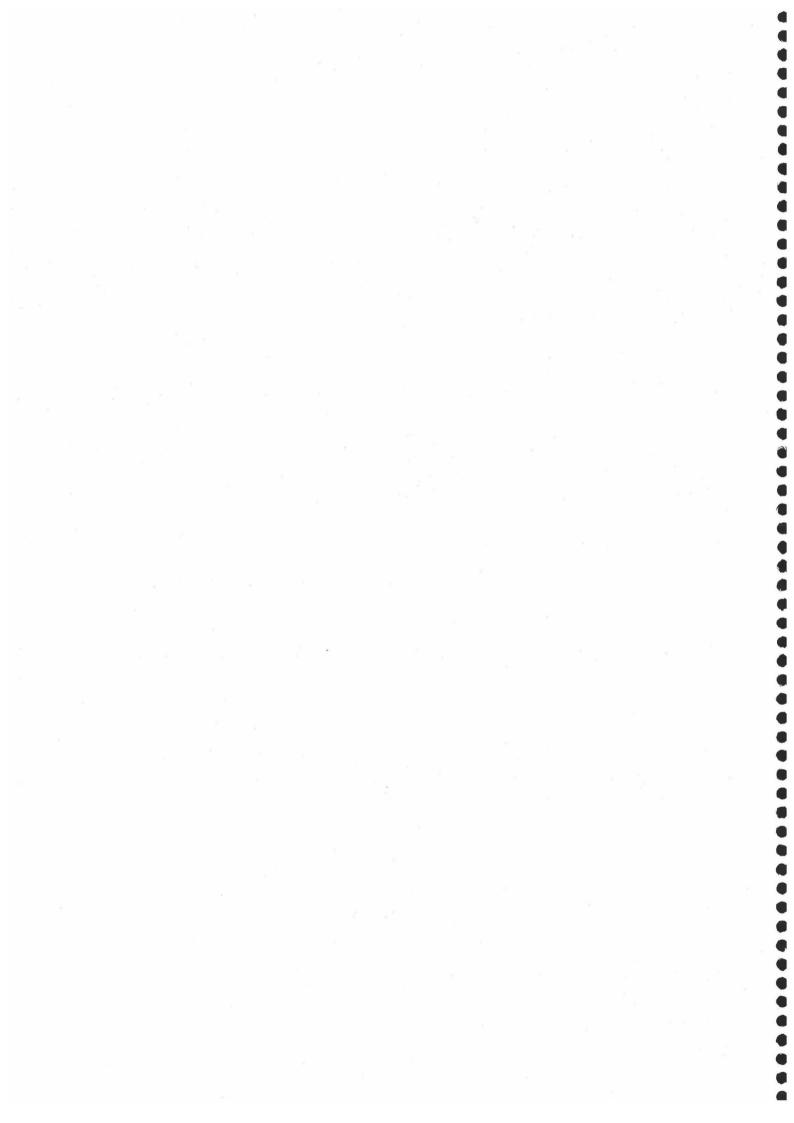

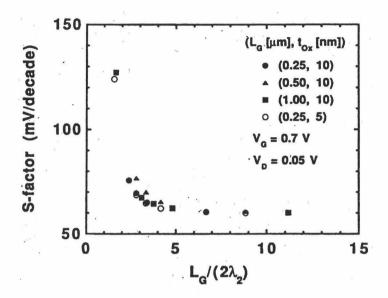

Como ejemplo pionero de estas simulaciones, [Fiegna et al., 1992] compararon, mediante simulación, distintos tipos de transistores en lo referente a efectos de canal corto y de portadores calientes. Concluyeron que con los MOSFET de doble puerta se podría llegar a una longitud de puerta inferior a 0.025 micras, mientras que con una sola puerta surgirían problemas por debajo de 0.05 micras. Comentaron, también, que una de las principales ventajas de los transistores SOI, los valores casi ideales de la pendiente subumbral, desaparece rápidamente a medida que la longitud de puerta decrece, debido al pobre control de la puerta posterior, sin embargo esto no ocurre con los transistores SOI de doble puerta.

También son muy interesantes los resultados de simulaciones mediante el método de Monte Carlo realizadas por investigadores de IBM ([Frank et al., 1992]), utilizando el programa DAMOCLES, con "full-band", acoplamiento dinámico a una resolución bidimensional de Poisson, y estadística de Fermi-Dirac. Utilizan el método de Monte Carlo para el estudio del transporte en fuerte inversión, aunque para el cálculo de la corriente subumbral, dominada por difusión, usan un modelo de difusión y deriva que dicen que proporciona resultados más exactos. De los resultados de esta simulación se deduce que el dispositivo de silicio más corto posible es un MOSFET SOI de doble puerta, con una longitud de puerta de 30 nm, un espesor de óxido de 3 nm y un espesor de lámina de silicio de 5 a 20 nm. Este dispositivo no muestra efectos de canal corto para longitudes mayores que 70 nm, proporciona valores de transconductancia hasta 2300mS/mm y un retardo estimado de oscilador en anillo de 1.1 picosegundos, (excelente para circuitos digitales). La tensión umbral tiene una incertidumbre proporcional a la del espesor de la capa de silicio. La tensión drenador-fuente límite puede ser V<sub>D</sub> = 1.2V (para impedir túnel banda a banda, limitar ionización por impacto, e impedir degradación por portadores calientes en el óxido), con una tensión umbral de 0.3±0.1V, quedando 0.2V para cortar el dispositivo. Consideran un 30% de decremento en la longitud del canal con respecto a la nominal, en el peor de los casos. En cuanto al espesor mínimo de la capa de silicio, atendiendo a limites físicos, consideran tres efectos: 1) La cuantización que desplaza la tensión umbral, siendo la causa principal de la incertidumbre en este parámetro debido a la inexactitud en el control del espesor de la lámina de silicio (suponiendo que se controla el espesor salvo un 20%, el espesor mínimo es entonces de 4nm), 2) la resistencia en serie, que limita el espesor a unos 5 nm con un dopado de  $10^{20}$  cm<sup>-3</sup> y 3) fluctuaciones estadísticas de los donantes discretos (éstas no imponen un limite si se deja el canal sin dopar, controlando la tensión umbral mediante la función trabajo de la puerta).

En lo referente al superior apantallamiento conseguido gracias a la doble puerta, [Wind et al, 1996] estudian las líneas de campo diferenciales que se obtienen cuando se incrementa la tensión de drenador, y concluyen que para que la tensión umbral no se vea

afectada por la polarización del drenador es necesario que estas líneas penetren lo mínimo posible hacia la fuente, y que eso se consigue con MOSFETs de doble puerta. Estas conclusiones se mantienen en [Taur et al, 1997], donde comparan también con otras estructuras como MOSFETs de SiGe.

•

Más adelante, se ha considerado que la forma de la distribución de electrones en la dirección perpendicular al canal puede ser importante, y que es necesario incluir los efectos de la cuantización. De acuerdo con esto, [Ouisse et al., 1994] estudiaron un DGMOST resolviendo autoconsistentemente las ecuaciones de Poisson y Schrödinger con la aproximación de Hartree y mostraron que la cuantización de la capa de inversión favorece la inversión en volumen. [Colinge et al., 1994] calcularon la transconductancia con un modelo cuántico que supone un pozo cuadrado con paredes infinitas y compararon con resultados experimentales a bajas temperaturas (menores de 2K), comprobando que los picos experimentales de la transconductancia coinciden con los esperados según los niveles del pozo. Para mayores tensiones de puerta, en fuerte inversión, la transconductancia decrece rápidamente. Mas tarde se han publicado cálculos autoconsistentes Poisson-Schrödinger similares al de [Ouisse et al., 1994], como el de [Majkusiak et al., 1998], que comparan los resultados del modelo cuántico y clásico para la densidad de portadores y el resultado que proporciona el modelo local de movilidad electrónica de MINIMOS, en función del espesor. Nosotros consideramos que el modelo local no es consistente con la hipótesis de "gas de electrones cuasibidimensional", por lo que revisaremos estos resultados en la presente memoria.

Finalmente, hemos de mencionar los resultados de [Pikus et al., 1997] que consideran el caso límite de un DGMOST con transporte totalmente balístico a lo largo del canal. Afirman que esta situación se presenta para longitudes de canal de 10nm y menores, como en el dispositivo propuesto por [Guo et al., 1997]. Llegan a la conclusión de que se pueden conseguir longitudes de hasta 10 nm para circuitos lógicos, y de hasta 4 nm para celdas DRAM. Para longitudes menores de canal habría que utilizar ideas físicas radicalmente diferentes.

### 1.3 OBJETIVOS Y METODOLOGÍA:

De todo lo expuesto en los dos apartados anteriores podemos deducir que, a pesar de que ya existe una gran cantidad de trabajo teórico y experimental realizado sobre los transistores MOS de doble puerta, quedan aún planteados múltiples interrogantes que requieren una solución para decidir si las ventajas que se pueden obtener con esta estructura van a compensar las complicaciones tecnológicas que plantea, antes de abordar el diseño y producción masiva de circuitos integrados basados en estos dispositivos. Muchas de las cuestiones planteadas se refieren a los verdaderos efectos de la inversión en volumen, ya que es en esta situación cuando los resultados de las simulaciones clásicas (que son las más detalladas realizadas con anterioridad) y cuánticas difieren más, y es también esta situación la que ha planteado una mayor controversia a lo largo de esta década. Concretamente, podríamos apuntar las siguientes:

- 1) ¿Es muy diferente un transistor MOS de doble puerta de un transistor MOS de puerta simple con doble anchura de canal?

- 2) ¿Cómo afecta la cuantización de los portadores minoritarios en la capa de inversión al comportamiento de parámetros importantes del dispositivo como es la tensión umbral?

- 3) ¿Se alejan realmente los electrones de las interfaces óxido-silicio?. Y si esto es así, ¿es este alejamiento suficientemente significativo como para apreciar una disminución en la dispersión culombiana por trampas cargadas en las interfaces y en el interior del óxido?

- 4) ¿Cómo afecta la inversión en volumen a la dispersión por rugosidad superficial?. ¿Consigue realmente hacerla disminuir?

- 5) ¿Cómo influye el espesor de la lámina de silicio, en conjunto, sobre las propiedades de transporte de los electrones, y sobre la movilidad en particular?. ¿Se compensa el efecto negativo de la reducción del espesor de esta lámina, debido a los fonones, con las ventajas que se obtienen en los otros mecanismos de dispersión?

- 6) ¿Cuál sería el espesor óptimo de la lámina de silicio?. ¿Cuáles serían los valores óptimos del resto de parámetros para este espesor?

El objetivo fundamental de esta Tesis es responder a todos estos interrogantes. Para ello se analizará una sección transversal de un transistor MOS de doble puerta de canal N, con el fin de examinar detalladamente las peculiaridades de la distribución de electrones con una amplia variedad de valores de todos los parámetros tecnológicos y condiciones de operación, y se estudiarán las propiedades de transporte en el canal.

Para la obtención de la distribución de electrones, se resolverán autoconsistentemente las ecuaciones de Poisson y Schrödinger en la estructura, dentro de las aproximaciones de Hartree y de masa efectiva. Para el estudio de las propiedades de transporte se calculará la movilidad de los electrones mediante el método de Monte Carlo. Los resultados de estas simulaciones se utilizarán también para verificar los efectos de los diferentes parámetros tecnológicos en parámetros utilizados en modelos analíticos para la simulación de circuitos.

Aunque sólo se tratan dispositivos con canal N en esta memoria, la mayor parte de los resultados serán aplicables también a transistores de canal P, al menos desde el punto de vista cualitativo. Los resultados cuantitativos con canal de huecos se podrían obtener mediante un análisis paralelo, pero incluyendo las peculiaridades de la banda de valencia, que conducirían a procedimientos de cálculo mucho más complejos. El análisis de un gas cuasibidimensional de huecos en un MOSFET convencional ha sido abordado ya en nuestro grupo de investigación [Rodríguez, 1999], y podría extenderse

también al estudio de transistores de doble puerta. No obstante, este tratamiento excede los límites que hemos impuesto a nuestro trabajo y podrá ser abordado en estudios posteriores.

A pesar de las limitaciones de nuestros resultados, impuestas por los modelos, aproximaciones y recursos computacionales empleados, esperamos que los resultados obtenidos por estos procedimientos, además de ayudar a la mejor comprensión de un problema de indudable interés científico, sean útiles para evaluar de forma realista y exacta las prestaciones de este tipo de transistores, pudiendo contribuir así al desarrollo de la tecnología electrónica de los años venideros.

### **CAPÍTULO II:**

LA ESTRUCTURA MOSOM (Metal-Óxido-Semiconductor-Óxido-Metal)

### 2.1 DESCRIPCIÓN DE LA ESTRUCTURA

### 2.1.1 INTRODUCCIÓN

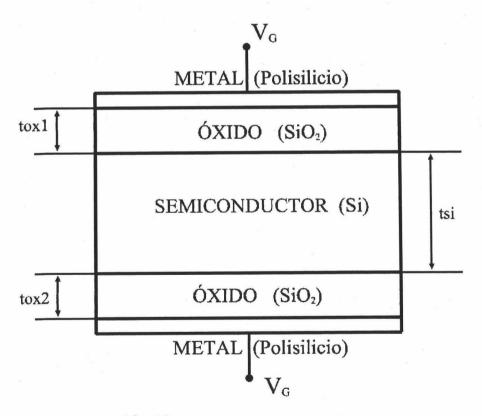

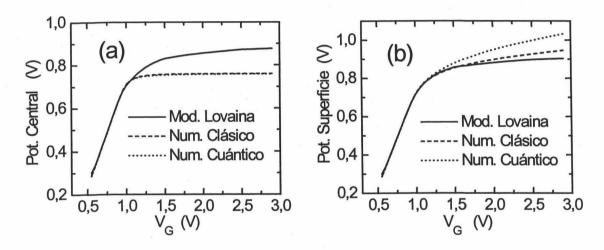

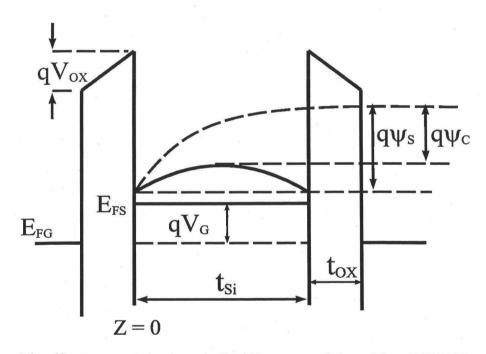

La estructura MOSOM es una parte fundamental del transistor de doble puerta, ya que es la que controla la conductividad del canal y, por consiguiente, el flujo de corriente a lo largo del dispositivo. Esta estructura está compuesta por cinco capas: una lámina de material semiconductor situada en el centro, dos capas de material aislante a ambos lados de la lámina semiconductora, y dos capas de un material altamente conductor en los dos extremos de la estructura que actúan como metalizaciones de puerta. La lámina semiconductora suele ser de silicio, las capas aislantes de dióxido de silicio y las capas conductoras de polisilicio, aunque también pueden incluir capas de siliciuros metálicos refractarios para aumentar su conductividad. En la Fig. 10 se representa esquemáticamente la estructura, que corresponde a un corte transversal del transistor de doble puerta en un plano perpendicular al canal.

Para realizar el estudio del MOSOM hemos escogido una estructura totalmente simétrica con una lámina de silicio tipo P de dopado uniforme, espesores de las dos capas de óxido iguales y puertas de polisilicio tipo P<sup>+</sup> con la misma concentración de impurezas.

Al aplicar una tensión positiva en ambas puertas de la estructura MOSOM se crean dos regiones de inversión, cada una de ellas próxima a una de las interfaces óxidosemiconductor. No obstante, como veremos más adelante en este mismo capítulo, en el caso de que la lámina de silicio sea muy estrecha, se puede producir la llamada inversión en volumen, en la cual la región de inversión ocupa toda la lámina de silicio. Igual que ocurre en el MOSFET, al situar dos regiones de silicio tipo n<sup>+</sup>, llamadas fuente y drenador, en ambos extremos de la lámina de silicio, y al aplicar una tensión entre ellas, se consigue que circule una corriente controlada por la tensión aplicada a las puertas, formando así la estructura completa del transistor.

Fig. 10: Dibujo de la estructura MOSOM.

## 2.1.2 REGIONES DE OPERACIÓN

A la hora de realizar el estudio de los distintos modos de operación del dispositivo MOSOM supondremos, por ahora, que se aplica la misma tensión a ambas puertas de la estructura, ya que ésta es la situación más usada en el transistor de doble puerta, y parece también que es la más ventajosa. Como en el MOSFET convencional, según sea la tensión aplicada a las puertas, el dispositivo podrá estar en la región de acumulación, de deplexión o de inversión, y dentro de esta región, en inversión débil, moderada o fuerte [Tsividis, 1993].

En la región de inversión, que es la de mayor interés, podemos diferenciar entre tres modos de funcionamiento del MOSOM dependiendo del espesor de la lámina de silicio: deplexión parcial, deplexión total e inversión en volumen. Analizamos estas tres situaciones a continuación:

### 2.1.2.1 DEPLEXIÓN PARCIAL. DOS CANALES INDEPENDIENTES

Estando en el modo de inversión, con lo cual suponemos que ya están formadas dos láminas delgadas de inversión junto a las dos interfaces óxido-silicio, la estructura MOSOM opera en deplexión parcial cuando se tienen además dos regiones de deplexión, una asociada a cada interface óxido-semiconductor, situadas a continuación de las láminas de inversión, pero separadas por una región en no deplexión dominada por portadores mayoritarios. Se trata de la misma situación que se observa en un MOSFET convencional, con la diferencia de que en este caso tendríamos dos MOSFETs con los substratos unidos. Las regiones de deplexión son independientes, estando cada una de ellas controlada por la puerta más cercana sin influencia de la puerta contraria. Como hemos mencionado, a todos los efectos es como si se tuvieran dos MOSFETs de puerta simple en paralelo.

#### 2.1.2.2 DEPLEXIÓN TOTAL

La estructura MOSOM opera en la región de deplexión total cuando toda la lámina de silicio se encuentra en deplexión, sin que exista zona neutra en el centro. Para que el dispositivo opere en esta situación, el espesor de la lámina de silicio "t<sub>si</sub>" tiene que ser inferior al espesor crítico "t<sub>sic</sub>", estando definido éste como:

$$t_{sic} = 2 \cdot \sqrt{\frac{4\varepsilon_{si}\phi_F}{q \cdot N_A}} \tag{1}$$

donde  $\epsilon_{si}$  es la permitividad dieléctrica del silicio, q la carga del electrón,  $N_A$  la concentración de la lámina de silicio y  $\phi_F$  el potencial de Fermi.

En este caso, el potencial en el centro de la capa de silicio esta influenciado por la tensión aplicada a las puertas y tiende a seguir a los potenciales de superficie.

#### 2.1.2.3 INVERSIÓN EN VOLUMEN

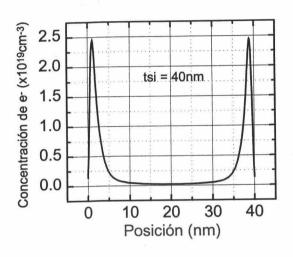

Cuando la estructura MOSOM alcanza la condición de inversión en volumen, se forma una sola región de inversión en vez de dos capas de inversión como en los anteriores casos. Los portadores minoritarios ocupan toda la lámina de silicio. La región física de inversión es mayor, y podríamos pensar que el número de portadores minoritarios también lo es comparado con el caso de que tengamos dos capas de inversión separadas. Las ventajas esperadas de esta forma de operación son, pues, el aumento de la corriente, la reducción de la influencia de los defectos de interface y los fenómenos de dispersión por cargas interfaciales, con el consiguiente aumento de la movilidad y de la transconductancia [Balestra et al., 1987].

La inversión en volumen del dispositivo MOSOM se produce para espesores

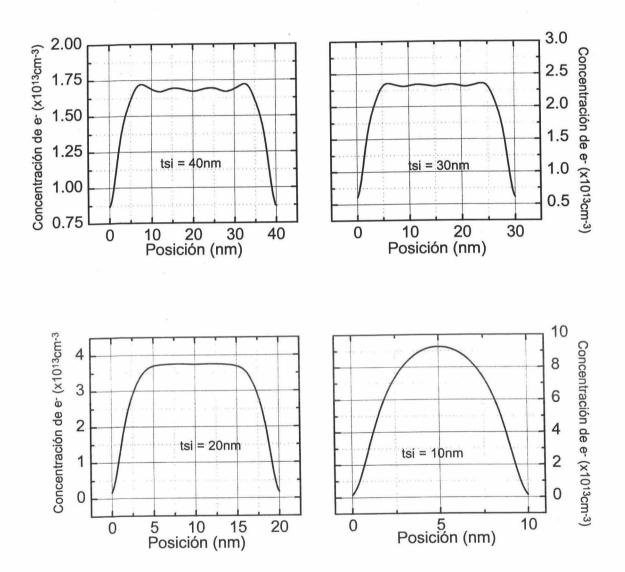

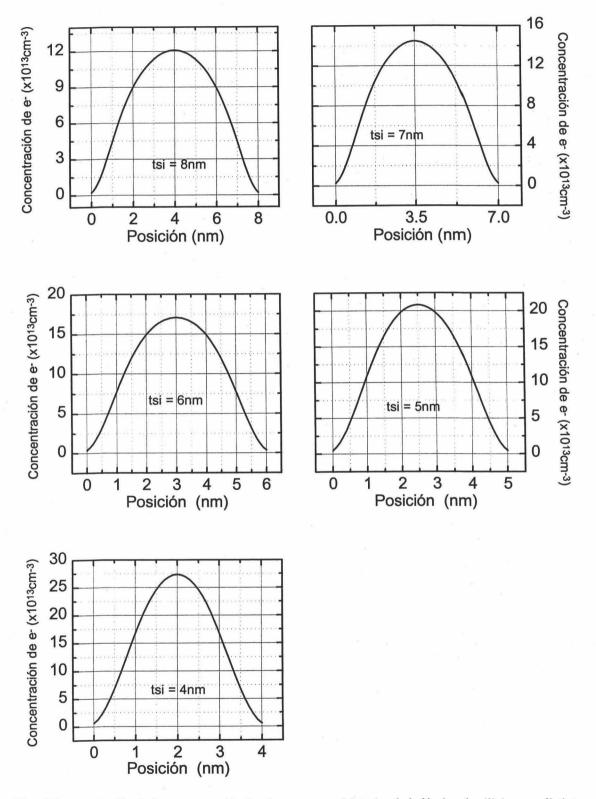

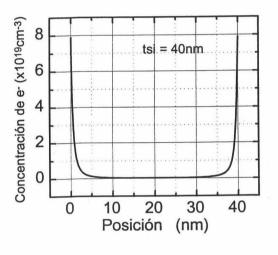

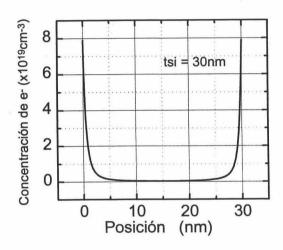

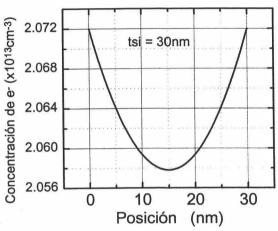

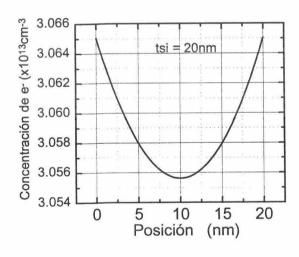

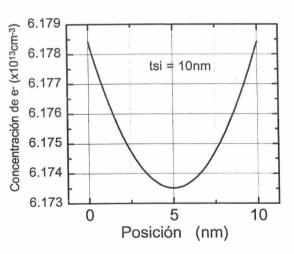

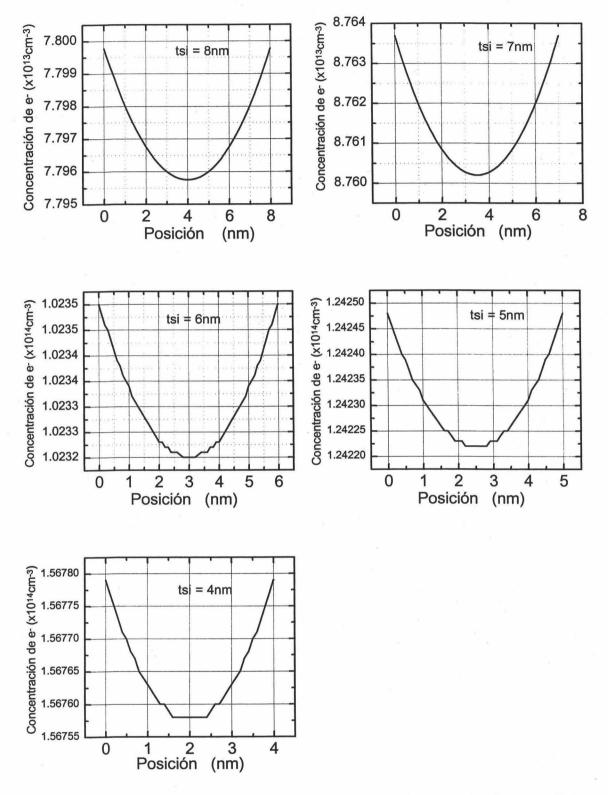

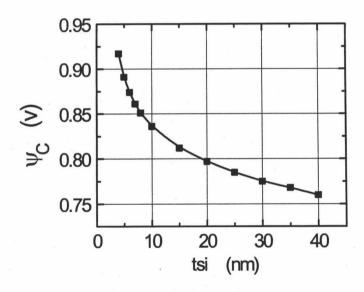

muy pequeños. [Balestra et al.,1987] definen la inversión en volumen como la situación en la cual la caída de potencial en el centro de la capa de silicio del MOSOM es mayor que dos veces el potencial de Fermi. Según nuestros cálculos, con esta definición se tendría inversión en volumen a partir de espesores de unos 500nm. Según [Suzuki et al., 1994] la inversión se produce para espesores de la capa de silicio menores de 5nm, y otros investigadores lo toman para espesores menores de 50nm [Majkusiak et al., 1998]. Este aparente desacuerdo se debe a que existen muchos casos en los que aparece una cierta concentración de portadores minoritarios en el centro de la lámina de silicio, con lo que estrictamente estaríamos ya en inversión en volumen, pero con concentración muy inferior a la existente cerca de las interfaces, por lo que a efectos prácticos la inversión en volumen puede ser despreciada. Como indican [Balestra et al.,1987], para un potencial central superior al doble del potencial de Fermi existe una cierta concentración de electrones, pero ésta es muy inferior a la que existe en las interfaces, y para poder hablar de inversión en volumen la concentración en el centro de la lámina debe ser comparable a la de los extremos o, de otra forma, la contribución a la corriente de los portadores de la zona central debe ser notable. Además, la distribución de portadores no sólo depende del espesor de la lámina de silicio, sino que está determinada también por la tensión aplicada a las puertas de la estructura. Así, en la región subumbral, la carga se distribuye por igual en toda la lámina de silicio independientemente de su espesor, mientras que en fuerte inversión, a medida que aumenta la tensión de puerta, los portadores tienden a concentrarse en las interfaces. A partir del espesor de 5nm, como indican [Suzuki et al., 1994], la carga se concentra en el centro de la lámina de silicio para cualquier tensión de polarización. Nosotros hemos estudiado la distribución de electrones para una estructura MOSOM con distintos espesores de la capa de silicio y llegamos a la conclusión de que la inversión en volumen comienza a partir de unos 40nm, para un valor del potencial central mayor o igual al doble del potencial de Fermi más seis veces el potencial térmico,  $\psi_c = 2\phi_F + 6\cdot U_t$ , que es una referencia ampliamente utilizada para el inicio de la inversión en los MOSFETs convencionales [Tsividis, 1993]. Estos resultados se mostrarán más adelante en este capítulo.

### 2.1.3 CURVATURAS DE BANDAS

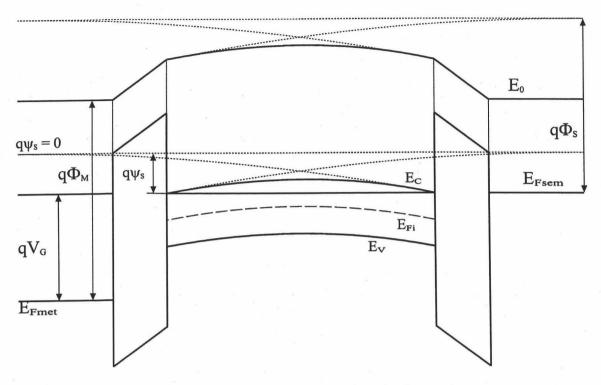

Para una mejor comprensión de la estructura mostramos en este apartado el diagrama de bandas para distintos espesores de la lámina de silicio y distintas tensiones de puerta. Tomamos, para este estudio, una estructura MOSOM totalmente simétrica, con lámina de silicio tipo P, uniformemente dopada, y puertas de polisilicio tipo P tales que la función trabajo del metal sea mayor que la del semiconductor,  $\Phi_{\rm M} > \Phi_{\rm S}$ . Analizaremos la estructura para tres casos, con diferentes espesores de la lámina de silicio, correspondientes a los tres tipos de operación del MOSOM: deplexión parcial, deplexión total e inversión en volumen.

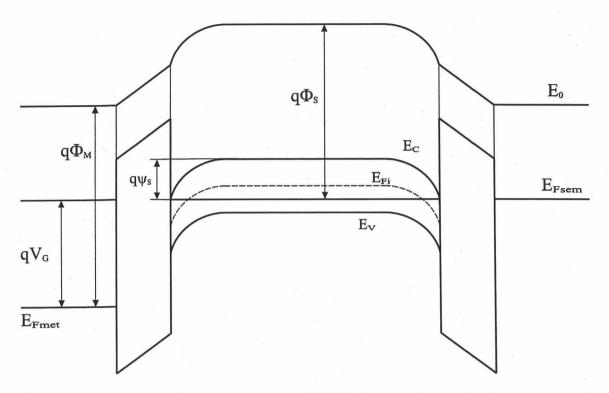

En el caso en que el espesor de la lámina de silicio sea mayor que el espesor crítico,  $t_{si} > t_{sic}$ , esto es, en deplexión parcial, el diagrama de bandas del MOSOM es igual que el de la estructura MIS (Metal, Aislante, Semiconductor), salvo por la presencia simultánea de dos puertas en el dispositivo. Se produce, pues, la curvatura de bandas en los dos extremos de la estructura, permaneciendo las bandas constantes en el centro de la misma. Se tiene la misma curvatura de bandas en los dos lados, ya que suponemos la estructura simétrica y las tensiones aplicadas a los dos puertas iguales.

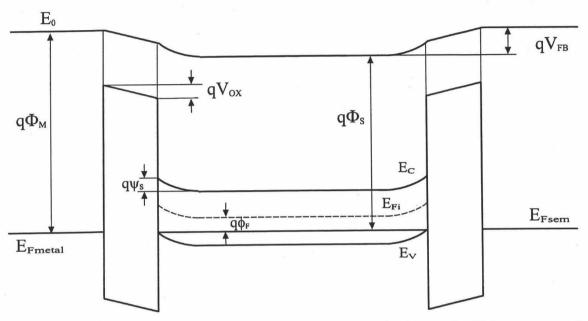

Si la tensión aplicada es nula, se produce acumulación de portadores mayoritarios en las dos interfaces óxido-semiconductor. En esta situación el diagrama de bandas tiene la forma que se detalla en la figura 11, donde  $\Phi_M$  es la función trabajo del metal,  $\Phi_S$  la función trabajo del semiconductor,  $V_{OX}$  la caída de potencial en el óxido,  $\psi_S$  el potencial de superficie que es igual a la caída de potencial en el semiconductor tomando como origen el mínimo de la banda de conducción de la zona neutra del semiconductor,  $\phi_F$  es el potencial de Fermi,  $V_{FB}$  la tensión de banda plana,  $E_0$  el nivel de energía del vacío,  $E_C$  la energía del fondo de la banda de conducción del semiconductor,  $E_{Fi}$  el nivel de Fermi intrínseco,  $E_V$  la energía de la cima de la banda de valencia y  $E_F$  el nivel de Fermi del semiconductor, que en este caso coincide con el

nivel de Fermi del metal al no haber aplicada ninguna tensión externa a la estructura.

Fig. 11: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio mayor que el espesor crítico  $t_{si} > t_{sic}$ , función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas  $V_G = 0$ .

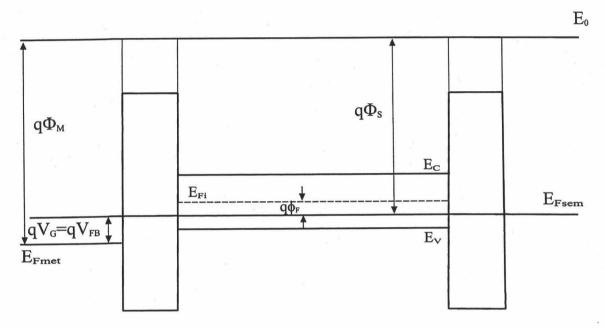

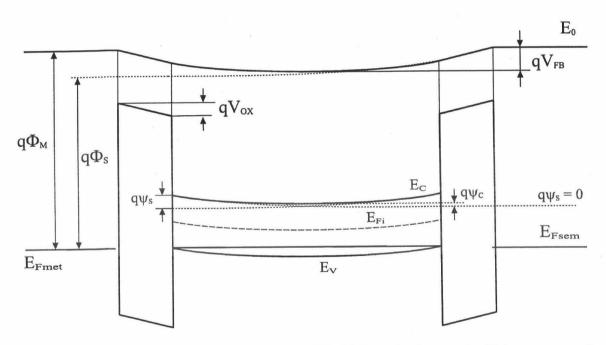

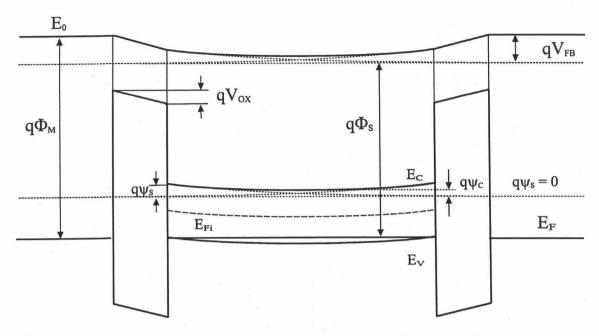

Al aplicar una tensión igual a la tensión de banda plana a las puertas, con respecto a la lámina central de silicio, (en este caso una tensión positiva), se consigue que las bandas no estén curvadas como se puede ver en la figura 12:

Fig. 12: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio mayor que el espesor critico  $t_{si} > t_{sic}$ , función trabajo del metal mayor que la del semiconductor ( $\Phi_M > \Phi_S$ ) y tensión aplicada a las puertas igual a la tensión de banda plana  $V_G = V_{FB}$ .

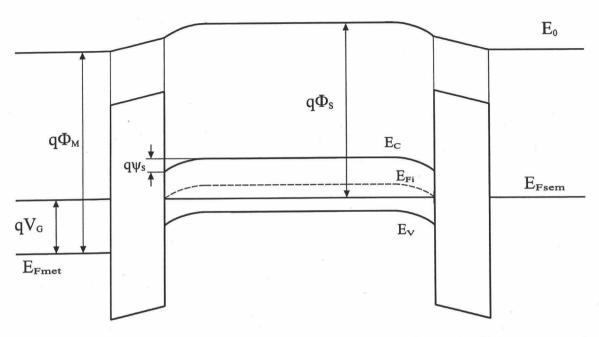

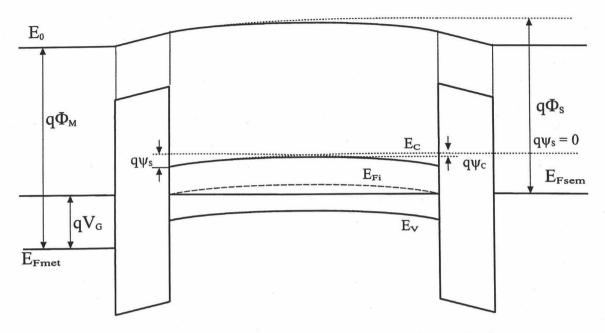

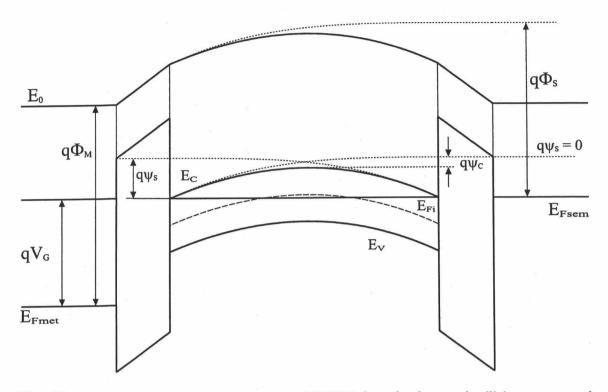

Si se aplica ahora una tensión superior a la de banda plana, las bandas se curvan hacia abajo, los portadores mayoritarios abandonan las zonas cercanas a las interfaces óxido-semiconductor y aumenta el número de portadores minoritarios en las zonas cercanas a las interfaces. Se forman dos regiones de deplexión separadas, como se puede ver en la figura 13.

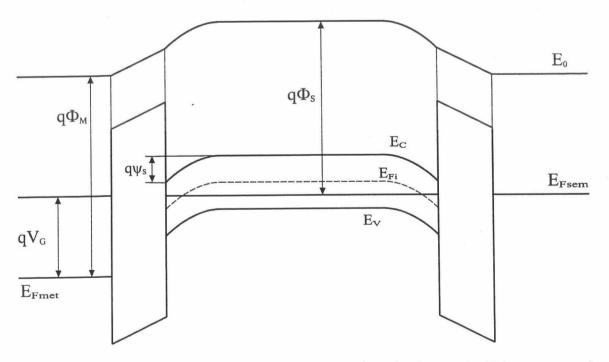

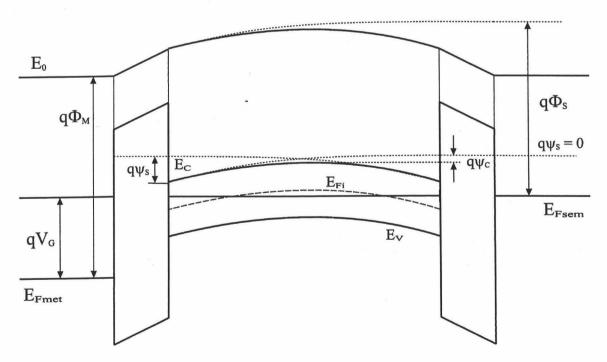

Y si se aplica una tensión de puerta lo suficientemente grande, la curvatura de las bandas en las interfaces es mayor que el potencial de Fermi,  $(\psi_s > \phi_F)$ . En este caso, se crean dos regiones de inversión en los dos extremos de la lámina semiconductora, como se muestra en las figuras 14 y 15:

Fig. 13: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio mayor que el espesor crítico  $(t_{si} > t_{sic})$ , función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas tal que el potencial de superficie es igual al potencial de Fermi.  $\psi_S = \phi_F$ .

Fig. 14: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio mayor que el espesor crítico  $(t_{si} > t_{sic})$ , función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas tal que el potencial de superficie es igual al doble del potencial de Fermi.  $(\psi_S = 2\varphi_F)$ .

Fig. 15: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio mayor que el espesor crítico  $(t_{si} > t_{sic})$ , función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas tal que el potencial de superficie es igual al triple del potencial de Fermi.  $(\psi_S = 3\varphi_F)$ .

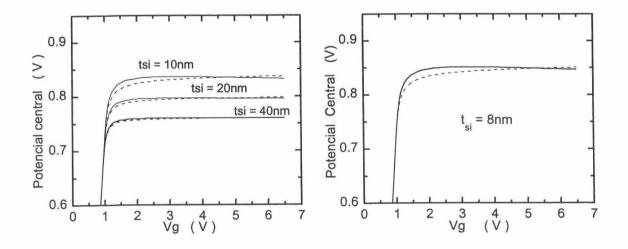

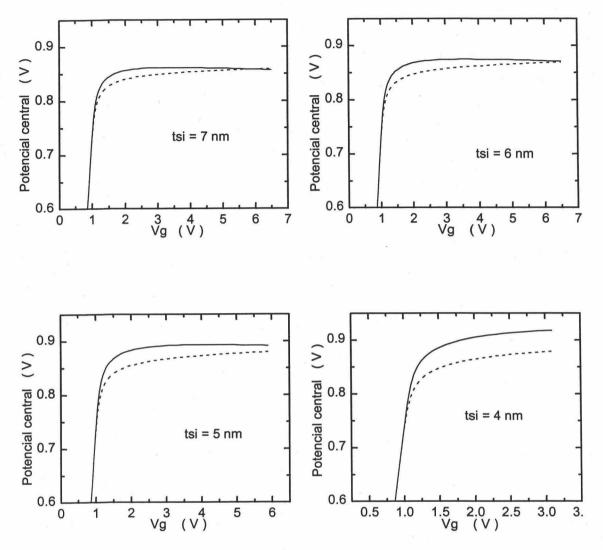

Como se puede ver, en la región central de la estructura MOSOM con capa de silicio de gran espesor, las bandas no están curvadas y mantienen siempre la misma distancia con respecto al nivel de Fermi del semiconductor, sea cual sea la tensión aplicada a las puertas. Esta región central no está, por consiguiente, afectada por las tensiones de puerta aplicadas. En cambio, cuando el espesor de la capa de silicio es inferior al espesor critico,  $t_{\rm si} < t_{\rm sic}$ , las bandas de energía se curvan a lo ancho de toda la capa semiconductora. En este caso, toda la estructura se encuentra afectada por la tensión aplicada a las puertas del dispositivo. Las bandas en el centro del semiconductor se desplazan en el mismo sentido en que se curvan las bandas en los extremos del semiconductor, y se define el potencial en el centro de la lámina de silicio, llamado aquí potencial central  $\psi_c$ , como la diferencia que existe entre el potencial en el centro de dicha lámina central en cada situación real, y el potencial que existiría en el punto central en caso de que la lámina fuera muy ancha, manteniendo el valor del resto de los

parámetros de la estructura, esto es, el potencial que existiría en el centro con neutralidad eléctrica. Por tanto, el potencial central, con deplexión total, no es nulo. El potencial de superficie también se define con respecto a este potencial de referencia, esto es, sería la diferencia entre el potencial en las interfaces óxido-silicio y el potencial de una región neutra lejana a dichas interfaces en un transistor convencional.

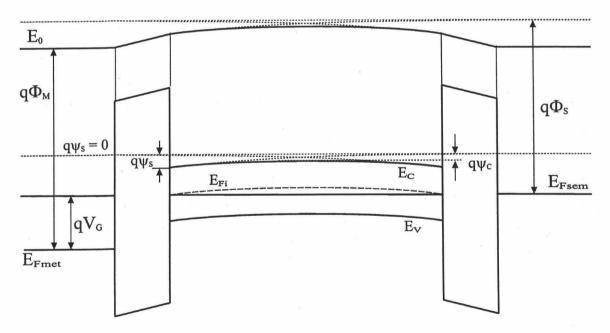

Los diagramas de bandas de la estructura para distintas polarizaciones de puerta, con espesor inferior al crítico, son los que se representan en las figuras siguientes:

Fig. 16: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que el espesor crítico  $(t_{si} < t_{sic})$ , función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas  $V_G = 0$ .

Fig. 17: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que el espesor crítico  $(t_{si} < t_{sic})$ , función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas tal que el potencial de superficie es igual al potencial de Fermi.  $\psi_S = \phi_F$ .

Fig. 18: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que el espesor crítico  $(t_{si} < t_{sic})$ , función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas tal que el potencial de superficie es igual al doble de potencial de Fermi.  $(\psi_S = 2\phi_F)$ .

Fig. 19: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que el espesor crítico ( $t_{si} < t_{sic}$ ), función trabajo del metal mayor que la del semiconductor ( $\Phi_M > \Phi_S$ ) y tensión aplicada a las puertas tal que el potencial de superficie es mayor que el doble del potencial de Fermi. ( $\psi_S = 3 \varphi_F$ ).

En las tres figuras anteriores se puede ver cómo la banda de conducción en el centro de la lámina se desplaza hacia abajo, lo que corresponde a un potencial positivo. La banda de valencia se aleja del nivel de Fermi de la lámina de silicio, disminuyendo la concentración de portadores mayoritarios y rompiéndose, en consecuencia, la neutralidad eléctrica en dicho punto central, y la banda de conducción se acerca a dicho nivel de Fermi, aumentando la concentración de portadores minoritarios, aunque suponemos que dicho incremento no es aún suficientemente significativo como para poder hablar de inversión en el centro de la lámina.

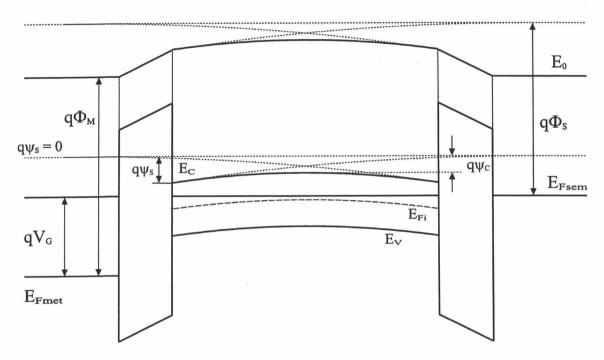

Finalmente, suponemos ahora que el espesor de la lámina de silicio es tan pequeño que se ha conseguido la situación de inversión en volumen. Los diagramas de bandas de la estructura MOSOM para distintas tensiones de polarización de puerta en estas condiciones se muestran en las figuras siguientes:

Fig. 20: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que 5nm, función trabajo del metal mayor que la del semiconductor ( $\Phi_M > \Phi_S$ ) y tensión aplicada a las puertas  $V_G = 0$ .

Fig. 21: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que 5nm, función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas tal que el potencial de superficie es igual al potencial de Fermi.  $\psi_S = \phi_F$ .

Fig. 22: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que 5nm, función trabajo del metal mayor que la del semiconductor ( $\Phi_M > \Phi_S$ ) y tensión aplicada a las puertas tal que el potencial de superficie es igual al doble del potencial de Fermi. ( $\psi_S = 2\varphi_F$ ).

Fig. 23: Diagrama de bandas para una estructura MOSOM de ancho de capa de silicio menor que 5nm, función trabajo del metal mayor que la del semiconductor  $(\Phi_M > \Phi_S)$  y tensión aplicada a las puertas tal que el potencial de superficie es mayor que el doble del potencial de Fermi.  $(\psi_S = 3\phi_F)$ .

La situación es cualitativamente similar al caso de deplexión total, pero el acercamiento de la banda de conducción al nivel de Fermi en la lámina de silicio es ahora considerablemente mayor, de manera que la concentración de portadores minoritarios sí se incrementa de forma significativa también en el centro de la lámina. Se puede decir que existe inversión también en ese punto central, y, por consiguiente, que la región de inversión ocupa toda la capa de silicio. Esto se pondrá de manifiesto más adelante, cuando se representen las concentraciones de portadores.

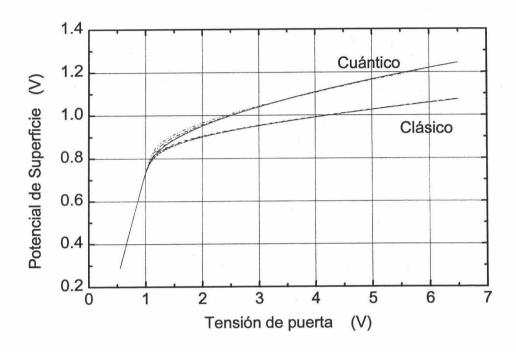

# 2.2 RESOLUCIÓN DE LAS ECUACIONES UNIDIMENSIONALES DE POISSON Y SCHRÖDINGER

Una vez mostrado de forma cualitativa el comportamiento de la estructura MOSOM en las diferentes regiones de operación, a través de la curvatura de bandas y de la posición de los extremos de las bandas con respecto al nivel de Fermi, nos planteamos una descripción cuantitativa del dispositivo. Nuestro objetivo es mostrar las distribuciones de portadores de carga para cada valor de la tensión de polarización externa y la dependencia del potencial de superficie y del potencial central en función de la tensión aplicada a las puertas. Nos proponemos realizar este estudio para diferentes valores de los parámetros tecnológicos relevantes, principalmente de la anchura de la lámina de silicio.

Si ya en un MOSFET convencional es importante considerar la cuantización del movimiento de los portadores minoritarios del canal en la dirección perpendicular a la interface silicio-óxido, debido a la modificación que produce en la distribución de dichos portadores, en el DGMOST esta modificación es más importante aun desde el punto de vista cualitativo, porque sin ella no se pueden apreciar los efectos de la inversión en volumen. Será necesario, pues, resolver autoconsistentemente las ecuaciones de Poisson y Schrödinger en la estructura. Con el fin de evaluar los efectos de la cuantización, también analizaremos la estructura con un modelo clásico, estudiando las diferencias. El procedimiento de solución se describe en los apartados siguientes.

## 2.2.1 ECUACIÓN DE POISSON CLÁSICA

En este apartado utilizamos un modelo clásico basado en la ecuación de Poisson y en una distribución continua de estados energéticos para los electrones, como se

obtendría en un trozo de semiconductor suficientemente ancho, no sometido a un pozo de potencial confinante. La distribución de electrones se obtiene a partir de la densidad continua de estados y la estadística de Fermi-Dirac, de manera que una vez resuelta la ecuación de Poisson en la dirección perpendicular a la interface se conoce también la distribución de carga en el dispositivo. A esta aproximación autoconsistente se le ha llamado "aproximación de Thomas-Fermi" en repetidas ocasiones en la bibliografía.

En el planteamiento de la ecuación de Poisson se han admitido las mismas simplificaciones que en la referencia [Gámiz et al., 1994a]. La ecuación de Poisson en el semiconductor es:

$$\frac{d^2\phi(z)}{dz^2} = -\frac{\rho(z)}{\varepsilon_{si}} \tag{2}$$

donde  $\phi(z)$  es el potencial eléctrico en todo punto de la estructura, que nos define la curvatura de bandas,  $\rho(z)$  es la densidad de carga y  $\epsilon_{si}$  la constante dieléctrica del silicio.

El potencial  $\phi(z)$  se relaciona con la curvatura de bandas mediante:

$$E_i(z) = E_{iB} - e\phi(z) \tag{3}$$

donde también se ha definido el origen de potenciales.  $E_i(z)$  es el nivel de Fermi intrínseco en todo punto y  $E_{iB}$  es el nivel intrínseco lejos de la interface, en una región neutra, si la hubiera.

La densidad de carga del silicio recibe tanto las contribuciones de portadores libres (huecos, p(z), y electrones, n(z), respectivamente) como de las impurezas ionizadas donadoras ( $N_D$ ) y aceptadoras ( $N_A$ ):

$$\rho(z) = q \cdot (p(z) - n(z) + N_D^+ - N_A^+)$$

(4)

Las concentraciones de electrones y huecos se han calculado por medio de la integración del producto de la densidad continua de estados en las bandas de conducción y valencia, respectivamente, y la función de ocupación de esos estados (calculada haciendo uso de la función de Fermi-Dirac).

La ecuación de Poisson se ha resuelto usando un procedimiento numérico iterativo utilizando el método de Newton-Raphson.

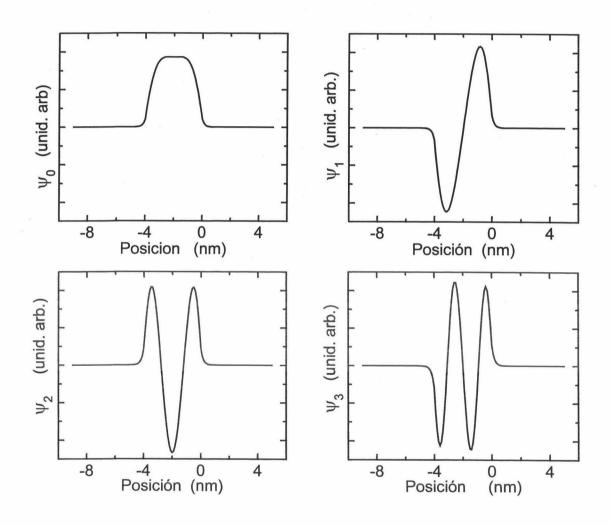

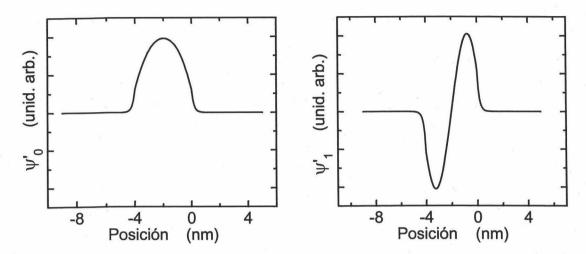

## 2.2.2 ECUACIÓN DE SCHRÖDINGER. CUANTIZACIÓN

Existen evidencias experimentales de que los portadores en una lámina de inversión muestran propiedades bidimensionales o cuasi-bidimensionales [Schrieffer 1957, Wheeler 1975, Gornik, 1976]. El pozo de potencial formado por la interface aislante-semiconductor es suficientemente estrecho para que los efectos cuánticos sean importantes: el movimiento de los electrones atrapados en este pozo de potencial está cuantizado en la dirección perpendicular a la interface. En el caso de un transistor de doble puerta con una lámina de silicio delgada, los efectos cuánticos se manifiestan experimentalmente de forma aun más evidente [Colinge, 1994].

Para incluir el comportamiento cuántico en el análisis de la estructura, habrá que calcular los niveles de energía posibles y las funciones de onda que los caracterizan resolviendo la ecuación de Schrödinger. Para su resolución se utilizan las mismas aproximaciones que en los trabajos de [Gámiz et al., 1994a y Madelung 1978]. Se supone también que el potencial que "ven" los electrones en inversión, es sólo función de la distancia a la interface, esto es,  $V(\vec{R}) = V(z)$ , siendo z la coordenada perpendicular a la interface.

En estas condiciones la función de onda del electrón,  $\psi(\vec{R})$ , puede escribirse como el producto de una función de Bloch, un factor envolvente que depende únicamente de z, y una onda plana que representa el movimiento libre del electrón en el plano paralelo a la interface,

$$\psi(x, y, z) = \xi(z) \cdot e^{(ik_1x + ik_2y)} \cdot u_{\alpha}(\vec{R})$$

(5)

$u_{\alpha}(\vec{R})$  es la función de onda de Bloch para el fondo del valle considerado en la banda de conducción, e incluye tanto la función periódica de la red, como la onda plana  $e^{i\vec{k}_{\alpha}\cdot\vec{R}}$ , donde  $\vec{k}_{\alpha}$  es el vector de onda en el mínimo de energía del valle  $\alpha$ -ésimo.

Con el fin de simplificar la expresión anterior y facilitar la resolución de la ecuación de autovalores resultante para la función envolvente, dependiente de la variable z, se transforma la expresión anterior obteniendo [Madelung 1978]:

$$\psi(x,y,z) = \zeta(z) \cdot e^{(ik_1x + ik_2y)} \cdot e^{-iz\left(\frac{\omega_{13}}{\varpi_{33}}k_1 + \frac{\omega_{23}}{\varpi_{33}}k_2\right)} \cdot u_{\alpha}(\vec{R})$$

(6)

Donde la forma concreta de los parámetros  $\omega_{ij}$  (componentes del tensor masa efectiva ) viene dada por la expresión:

$$\frac{1}{\hbar^2} \frac{\partial^2 E}{\partial k_i \partial k_j} = \frac{1}{m_{ii}} = \omega_{ij} \tag{7}$$

y donde la función  $\zeta(z)$  satisface la ecuación diferencial:

$$\frac{\hbar^2}{2m_z} \frac{d^2 \zeta}{dz^2} + [E'' - V(z)] \zeta(z) = 0$$

(8)

siendo m<sub>z</sub> el inverso de ω<sub>33</sub>, y E" igual a:

$$E'' = E(k_1, k_2) - \frac{\hbar^2}{2} \left[ \left( \omega_{11} - \frac{\omega_{13}^2}{\omega_{33}} \right) k_1^2 + 2 \left( \omega_{12} - \frac{\omega_{13}\omega_{23}}{\omega_{33}} \right) k_1 k_2 + \left( \omega_{22} - \frac{\omega_{23}^2}{\omega_{33}} \right) k_2^2 \right]$$

(9)

Dada la forma de V(z), deben existir estados ligados en la ecuación ( 8 ). Por tanto, sólo es posible un conjunto discreto de valores de E". Para cada uno de los valores discretos  $E_i$ " de energía, las componentes  $k_1$  y  $k_2$  del vector de onda varían de forma continua entre  $\pm \infty$ , de manera que para cada valor de  $E_i$ " se tiene un continuo de energías. A cada uno de estos continuos de energía se le denomina subbanda de energía, siendo  $E_i$ " el mínimo de dicha subbanda.

La ecuación de Schrödinger simplificada (8) depende de la orientación del mínimo de la banda considerado a través del valor de  $m_z$ . Para cada valor de  $m_z$  las soluciones  $E_i$ " constituyen una serie de subbandas. Por lo tanto, para diferentes orientaciones de las superficies isoenergéticas del substrato con respecto a la interface Si-SiO<sub>2</sub>, habrá diferentes conjuntos de subbandas. En el caso considerado en este estudio, de una superficie con orientación (100), dos de los seis elipsoides isoenergéticos del substrato corresponden a una masa perpendicular a la interface igual a la masa longitudinal,  $m_z = m_l$ , y dan lugar a un conjunto de subbandas que numeramos con los índices (0, 1, 2, ...); para los otros cuatro valles restantes, la masa perpendicular a la interface es la masa transversal  $m_z = m_t$ , y dan lugar a otro conjunto de subbandas que numeramos con los índices "primados" (0', 1', 2', ...). Dado que, en el caso del silicio,  $m_l$  es mayor que  $m_t$ , la solución i-ésima del conjunto (0, 1, 2, ...) corresponde a una energía transversal más pequeña que la solución i-ésima del conjunto (0', 1', 2', ...).

El potencial eléctrico V(z) vienen dado por la suma de varias contribuciones [Ando et al., 1982]:

$$V(z) = V_d(z) + V_s(z) + V_{im}(z) + V_{ex}(z)$$

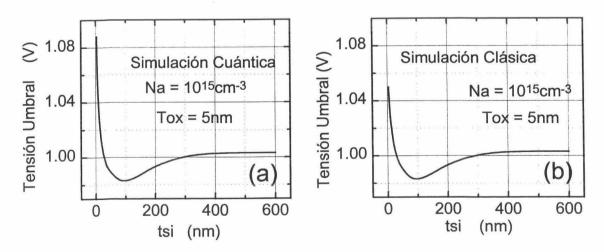

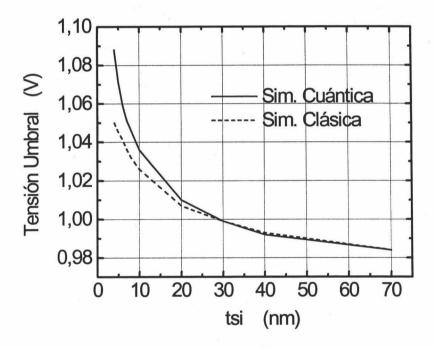

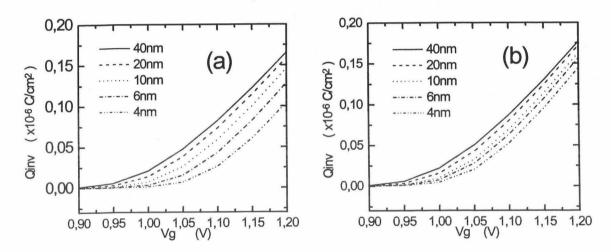

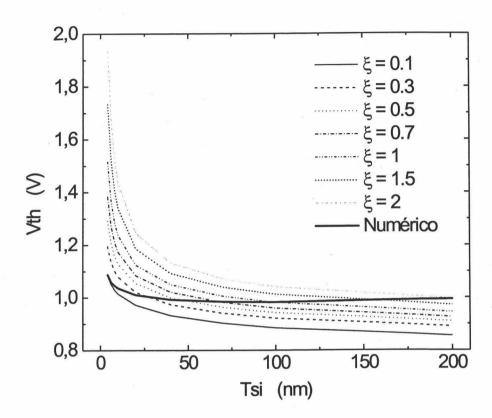

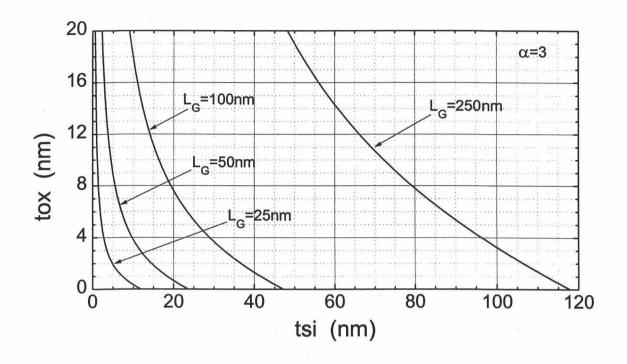

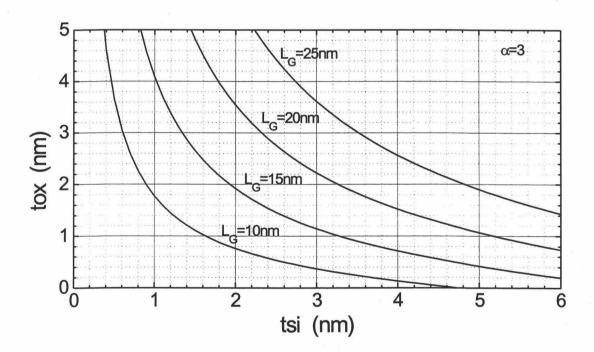

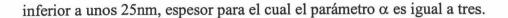

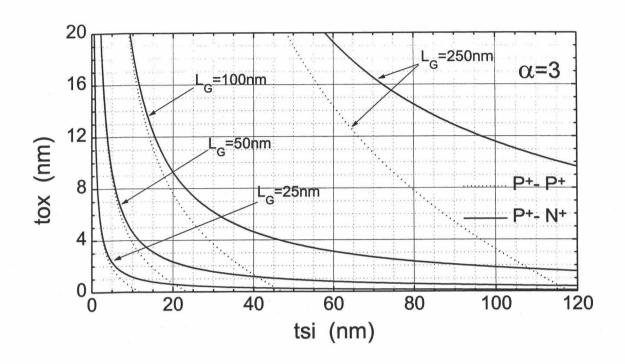

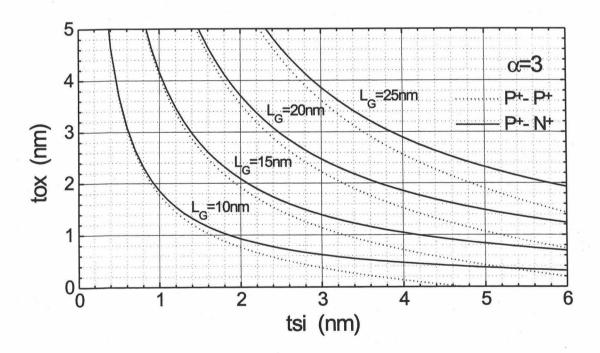

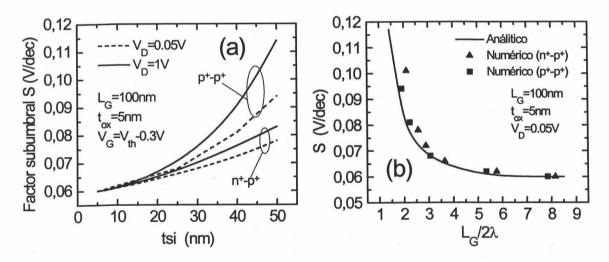

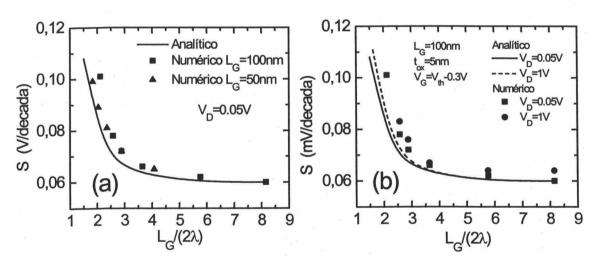

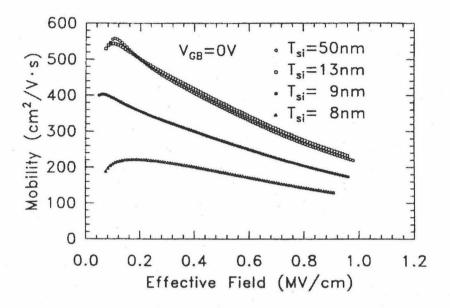

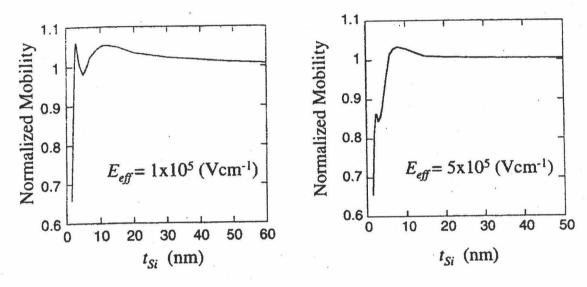

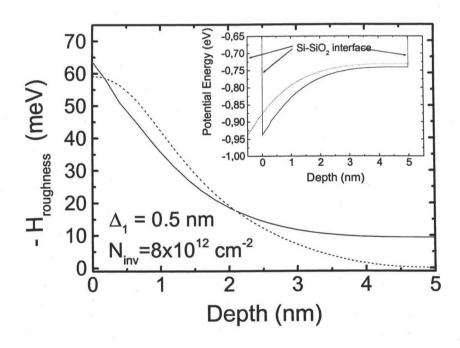

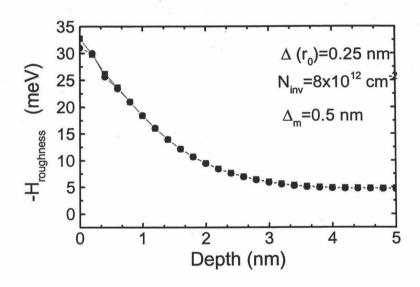

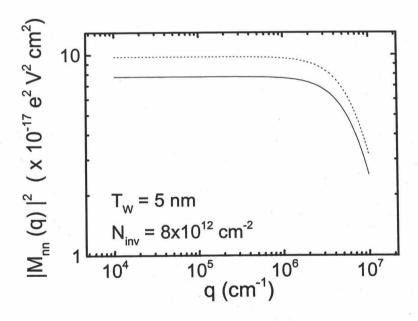

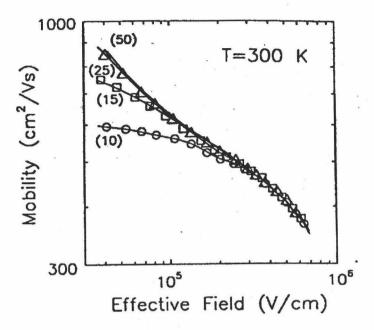

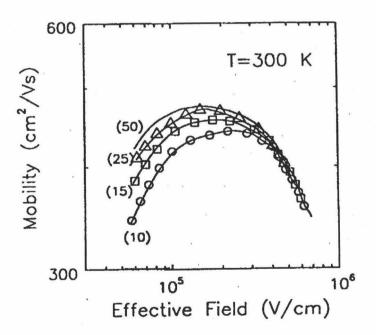

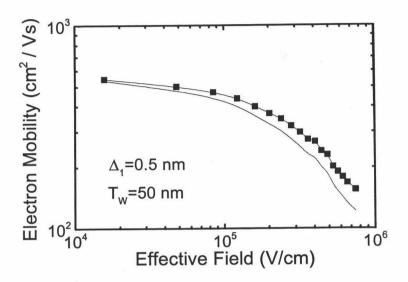

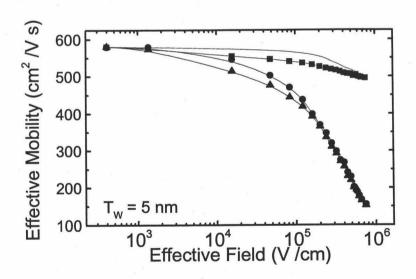

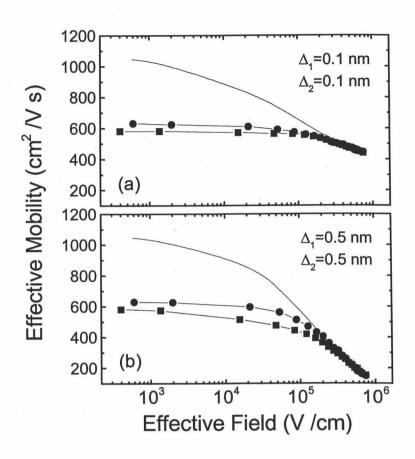

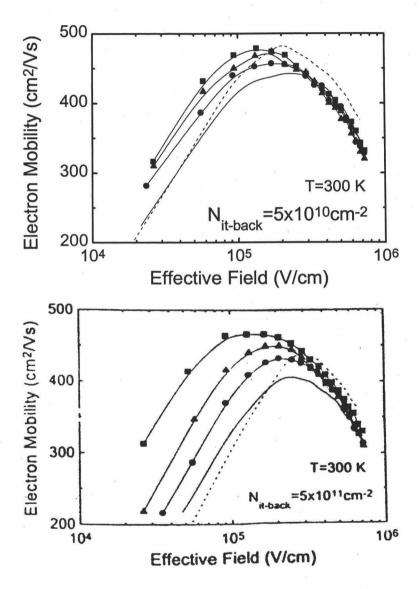

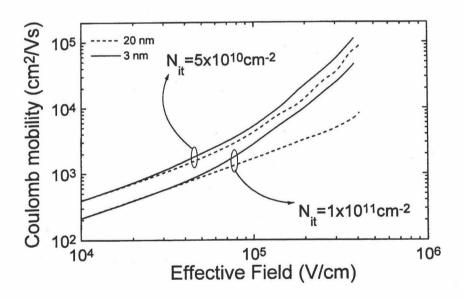

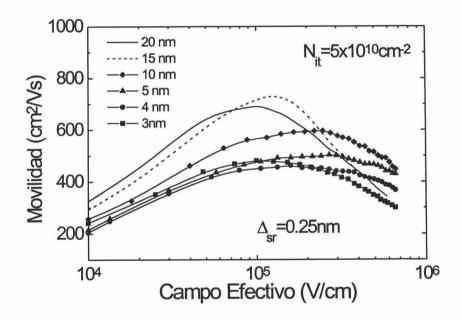

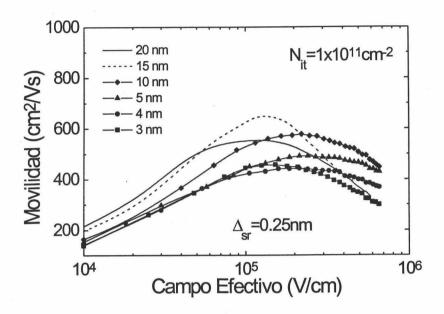

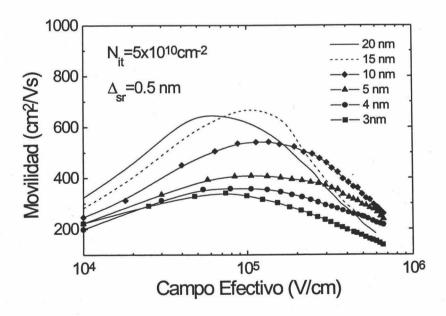

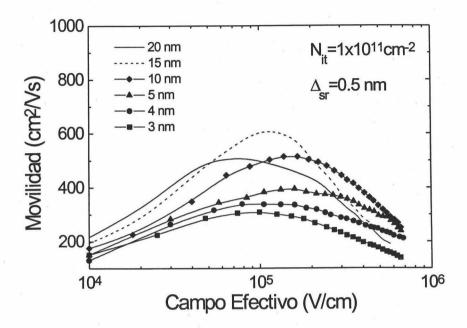

(10)