### Technical University of Denmark

## Towards a Formal Methods Body of Knowledge for Railway Control and Safety Systems

FM-RAIL-BOK Workshop 2013

Gruner, Stefan; Haxthausen, Anne Elisabeth; Maibaum, Tom ; Roggenbach, Markus

Publication date: 2013

Document Version Publisher's PDF, also known as Version of record

#### Link back to DTU Orbit

Citation (APA):

Gruner, S., Haxthausen, A. E., Maibaum, T., & Roggenbach, M. (Eds.) (2013). Towards a Formal Methods Body of Knowledge for Railway Control and Safety Systems: FM-RAIL-BOK Workshop 2013. Kgs. Lyngby: Technical University of Denmark (DTU). (DTU Compute-Technical Report-2013; No. 20).

## DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim. Technical University of Denmark

# Towards a Formal Methods Body of Knowledge for Railway Control and Safety Systems

FM-RAIL-BOK Workshop 2013 Madrid, Spain, September 2013 Proceedings

Stefan Gruner, Anne E. Haxthausen, Tom Maibaum, Markus Roggenbach (Eds.)

DTU Compute Technical Report-2013-20

Technical University of Denmark Department of Applied Mathematics and Computer Science Matematiktorvet, building 303B, 2800 Kongens Lyngby, Denmark Phone +45 4525 3031 compute@compute.dtu.dk www.compute.dtu.dk

ISSN: 1601-2321 ISBN: 978-87-643-1303-1

34}θφέρτυθιοπσδφγηξκλ

# Contents

| 1 | Introduction                                                                                                                                                                                             | 1  |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|   | Towards a Formal Methods Body Knowledge for Railway Control and Safety<br>Systems                                                                                                                        | 2  |  |

| 2 | Joint FMICS/FM-RAIL-BOK Keynote                                                                                                                                                                          | 3  |  |

|   | <b>Twenty-five Years of Formal Methods and Railways: What Next?</b>                                                                                                                                      | 3  |  |

| 3 | BoKs and Engineering Knowledge                                                                                                                                                                           | 4  |  |

|   | What IS a BoK?                                                                                                                                                                                           | 4  |  |

| 4 | Ontologies                                                                                                                                                                                               | 7  |  |

|   | An Ontology for Complex Railway Systems, Application to the ERTMS/ETCS<br>System                                                                                                                         | 7  |  |

| 5 | Verification of Data and Designs for Railway Control Systems                                                                                                                                             | 14 |  |

|   | <b>Verification of Scheme Plans using CSPB</b><br><i>Philip James, Faron Moller, Hoang Nga Nguyen, Markus Roggenbach, Steve Schneider, Helen</i><br><i>Treharne, Matthew Trumble, and David Williams</i> |    |  |

|   | Applied Bounded Model Checking for Interlocking System Designs                                                                                                                                           | 21 |  |

|   | Data Formal Validation of Railway Safety-Related Systems: Implementing the         OVADO Tool                                                                                                            | 27 |  |

| 6 | Verification of Interlocking Programs Expressed in Ladder Logic                                                                                                                                          | 33 |  |

|   | Validation of Railway Interlocking Systems by Formal Verification, a Case Study<br>Andrea Bonacchi, Alessandro Fantechi, Stefano Bacherini, Matteo Tempestini, and Leonardo<br>Cipriani                  | 33 |  |

|   | <b>Verification of Solid State Interlocking Programs</b>                                                                                                                                                 | 39 |  |

| 7 | ERMTS/ETCS Modelling                                                                                                                                                                                     | 46 |  |

|   | Modelling Functionality of Train Control Systems using Petri Nets                                                                                                                                        | 46 |  |

## Towards a formal methods body of knowledge for railway control and safety systems

Stefan Gruner University of Pretoria, South Africa

Anne Haxthausen Technical University of Denmark

Formal methods in software science and software engineering have existed at least as long as the term "software engineering" (NATO Science Conference, Garmisch, 1968) itself. Its various methods and techniques include algebraic specification, process-algebraic modelling and verification, Petri nets, fuzzy logics, etc. Especially in railway control and safety systems, formal methods have reached a considerable level of maturity. For example, the B-method has been used successfully to verify the most relevant parts of the Metro underground railway system of the city of Paris (France). Thus, it appears timely to begin the compilation of a so-called body of knowledge (BoK) dedicated to this specific area.

The FM-RAIL-BOK WORKSHOP 2013 (see also http: //ssfmgroup.wordpress.com), held on 23 September 2013 in Madrid, was a first successful step towards this aim. This international workshop was affiliated to the SEFM 2013, the 11th International Conference on Software Engineering and Formal Methods, Madrid. This volume compiles two abstracts and seven contributed papers of talks presented at the workshop.

As keynote, Alessandro Fantechi, Universita di Firenze, presents an overview "Twenty-Five Years of Formal Methods and Railways: What Next?". This keynote was shared with the 18th International Workshop on Formal Methods for Industrial Critical Systems (FMICS'13). Towards our aim of compiling a body of knowledge, Tom Maibaum, McMaster University, reflects upon "BoKs and Engineering Knowledge".

All contributed papers were reviewed by the workshop PC. They cover topics as varied as Ontologies, Verification of Data and Designs for Railway Control Systems, Verification of Interlocking Programs Expressed in Ladder Logic, and ECTS/ERTMS Modelling. Not necessarily presenting new scientific results, these papers compile case-based "best practice" knowledge in the spirit of classical engineering handbooks. A selection of these papers in improved and extended versions will appear in a volume of the Springer LNCS series.

As FM-RAIL-BOK co-chairs we would like to thank all authors who submitted their papers to our workshop, Alessandro Fantechi for accepting our invitation to present a keynote, the workshop participants, our Programme Committee, Manuel Nunez, Universidad Complutense de Madrid, Spain, and Steve Tom Maibaum McMaster University, Canada

Markus Roggenbach Swansea University, Wales, UK

Counsel, Brunel University, United Kingdom, for the smooth cooperation with SEFM'13, Linh Vu Hong for valuable help in preparing these proceedings, and Erwin R. Catesbeiana (Jr) for help with workshop organization on the fly.

The FM-RAIL-BOK co-chairs November 2013

#### FM-RAIL-BOK CO-CHAIRS

Stefan Gruner, University of Pretoria, South Africa Anne Haxthausen, Technical University of Denmark Tom Maibaum, McMaster University, Canada Markus Roggenbach, University of Swansea, Great Britain

#### FM-RAIL-BOK PC

Martin Brennan, British Rail Safety Standards Board Simon Chadwick, Invensys Rail, Great Britain Lars-Henrik Eriksson, Uppsala University, Sweden Alessandro Fantechi, University of Firenze, Italy Kirsten Mark Hansen, COWI A/S, Denmark Michaela Huhn, Technical University of Clausthal, Germany Kirsten Mark-Hansen, Cowi A/S, Danmark Hoang Nga Nguyen, University of Swansea, Great Britain Jan Peleska, University of Bremen, Germany Holger Schlingloff, Humboldt-University of Berlin, Germany Eckehard Schnieder, TU Braunschweig, Germany Kenji Taguchi, AIST, Japan Helen Treharne, University of Surrey, Great Britain Laurent Voisin, Systerel, France Kirsten Winter, University of Queensland, Australia

#### FM-RAIL-BOK EXTERNAL REVIEWER

Andrea Bonacchi, University of Firence, Italy

# Twenty-five years of formal methods and railways: what next?

(Invited Paper)

Joint FMICS/FM-RAIL-BOK Keynote Speaker.

Reprinted from C. Pecheur and M. Dierkes (eds.), Formal Methods for Industrial Critical Systems, LNCS 8187, page ix, Springer-Verlag, 2013, with permission of Springer-Verlag.

Alessandro Fantechi DINFO - University of Florence Via S. Marta 3 Firenze, Italy Email: fantechi@dsi.unifi.it

#### Abstract

Railway signaling is now since more than 25 years the subject of successful industrial application of formal methods in the development and verification of its computerized equipment.

However the evolution of the technology of railways signaling systems in this long term has had a strong influence on the way formal methods can be applied in their design and implementation. At the same time important advances had been also achieved in the formal methods area.

The evolution of railways signaling systems has seen railways moving from a protected market based on national railway companies and national manufacturers to an open market based on international standards for interoperability, in which systems of systems are providing more and more complex automated operation, but maintaining, and even improving, demanding safety standards.

The scope of the formal methods discipline has enlarged from the methodological provably correct software construction of the beginnings to the analysis and modelling of increasingly complex systems, always on the edge of the ever improving capacity of the analysis tools, thanks to the technological advances in formal verification of both qualitative and quantitative properties of such complex systems.

In spite of these advances, the verification of complex railway signalling systems is still a main challenge and an important percentage of the cost in the development of these systems. We will discuss a few examples of such systems that witness these difficulties.

The thesis we will put forward in this talk is that the complexity of future railway systems of systems can be addressed with advantage only by a higher degree of distribution of functions on local interoperable computers - communicating by means of standard protocols - and by adopting a multi-level formal modelling suitable to support the verification at design time and at different abstraction levels of the safe interaction among the distributed functions.

## What IS a BoK?

### - extended abstract -

Tom Maibaum McMaster Centre for Software Certification McMaster University 1280 Main St W, Hamilton, ON, Canada L8S 4K1 Email: tom@maibaum.org

#### I. MAIN POINTS

Software engineering is different from traditional engineering disciplines in certain crucial ways. But software engineering *is* an engineering discipline. However, software engineering fails to meet the requirements of an engineering discipline, as commonly conceived by conventional engineers. Software Engineering Books of Knowledge (BoKs) fail spectacularly in organising engineering knowledge as understood in classical engineering disciplines.

"The SWEBOK Guide:

- characterizes the contents of the software engineering discipline

- promotes a consistent view of software engineering worldwide

- clarifies software engineering's place with respect to other disciplines

- provides a foundation for training materials and curriculum development, and

- provides a basis for certification and licensing of software engineers."

We will "show" below that this is nothing like classical engineering knowledge and, in particular, like the so called cookbooks well known in engineering.

#### II. WHAT IS ENGINEERING?

So, what characterises classical engineering disciplines? The following books have been immensely helpful in understanding engineering:

- GFC Rogers, The Nature of Engineering, The Macmillan Press Ltd, 1983

- WG Vincenti, What Engineers Know and How They Know It, The Johns Hopkins University Press, 1990

We have also been inspired by various papers of Michael Jackson. [1] That software engineering is an engineering discipline is a simple consequence of the fact that: "engineering refers to the practice of organising the design and construction of any artifice which transforms the physical world around us to meet some recognised need" [2]. Vincenti [3] argues that engineering is different, in epistemological terms and, consequently, as praxis, from science or even applied science: "In this view, technology, though it may apply science, is

not the same as or entirely applied science". Rogers argues the same view on the basis of what he calls the teleological distinction concerning the aims of science and technology: "In its effort to explain phenomena, a scientific investigation can wonder at will as unforeseen results ... The essence of technological investigations is that they are directed towards serving the process of designing and constructing particular things whose purpose has been clearly defined." "We have seen that in one sense science progresses by virtue of discovering circumstances in which a hitherto acceptable hypothesis is falsified, and that scientists actively pursue this situation. Because of the catastrophic consequences of engineering failures - whether it be human catastrophy [sic] for the customer or economic catastrophy [sic] for the firm - engineers and technologists must try to avoid falsification of their theories. Their aim is to undertake sufficient research on a laboratory scale to extend the theories so that they cover the foreseeable changes in the variables called for by a new conception. The scientist seeks revolutionary change - for which he may receive a Nobel Prize. The engineer too seeks revolutionary conceptions by which he can make his name, but he knows his ideas will not be taken up unless they can be realised using a level of technology not far removed from the existing level." [2]

So, science is different from engineering. We can ask what the praxis of engineering is. Vincenti [3] defines engineering activities in terms of design, production and operation of artefacts. Of these, design and operation are highly pertinent to software engineering. In the context of discussing the focus of engineers activities, he then talks about normal design as comprising "the improvement of the accepted tradition or its application under new or more stringent conditions". He goes on to say: "The engineer engaged in such design knows at the outset how the device in question works, what are its customary features, and that, if properly designed along such lines, it has good likelihood of accomplishing the desired task." Jackson discusses this concept of normal design, although he does not use this phrase himself: "An engineering handbook is not a compendium of fundamental principles; but it does contain a corpus of rules and procedures by which it has been found that these principles can be most easily and effectively applied to the particular design tasks established in the field. The outline design is already given, determined by the established needs and products." "In this context, design innovation is exceptional. Only once in a thousand car designs does the designer depart from the accepted structures by an innovation like front-wheel drive or a transversely positioned engine. True, when a radical innovation proves successful it becomes a standard design choice for later engineers. But these design choices are then made at a higher level than that of the working engineer: the product characteristics they imply soon become well understood, and their selection becomes as much a matter of marketing as of design technology. Unsuccessful innovations - like the rotary internal combustion engine - never become established as possible design choices." "The methods of value are micro-methods, closely tailored to the tasks of developing particular well-understood parts of particular wellunderstood products."

Another important aspect of engineering design is the organising principle of hierarchical design: "Design, apart from being normal or radical, is also multilevel and hierarchical. Interesting levels of design exist, depending on the nature of the immediate design task, the identity of some component of the device, or the engineering discipline required." [3] It is quite clear from the engineering literature that engineering normally involves the use of multiple technologies. The observation that software engineering requires knowledge of other domains and that its teaching should be application oriented is not as perspicacious as its proponents would have us believe. This is part of the essence of engineering, whatever the discipline. An implied but not explicitly stated view of engineering design is that engineers normally design devices as opposed to systems, in the sense of Vincenti. A device, in this sense, is an entity whose design principles are well defined, well structured and subject to normal design principles. (See also Michael Polanyis operational principle of a device [4].) A system, in this sense, is an entity that lacks some important characteristics making normal design possible. "Systems are assemblies of devices brought together for a collective purpose." Examples of the former given by Vincenti are airplanes, electric generators, turret lathes; examples of the latter are airlines, electric-power systems and automobile factories. The software engineering equivalent of devices may include compilers, relational databases, PABXs, etc. Software engineering examples of systems may include air traffic control systems, automotive software, the internet, etc. It would appear that systems become devices when their design attains the status of being normal. That is, the level of creativity required in their design becomes one of systematic choice, based on well defined analysis, in the context of standard definitions and criteria developed and agreed by engineers.

#### III. ENGINEERING KNOWLEDGE

Is the knowledge used by software engineers different in character from that used by conventional engineers? The latter is underpinned by mathematics and some physical science(s), providing models of the physical universe in terms of which artefacts must be understood. What about software engineering? I would claim that logic (in its widest sense) fulfills these roles, although from different perspectives in computer science and software engineering. Software engineering is distinguished from conventional engineering because the artefacts constructed by the former are conceptual, while those built by the latter are physical. For the latter, the "real world" is a fixed constraint, whereas it is not clear that there are the same limitations on the "computational world". There is an existing track record of working with concepts and abstractions in mathematics and logic, particularly philosophical logic. What distinguishes software engineering is the day to day invention of theories (descriptions) by engineers and the problems of size and structure induced by the nature of the artefacts. Can we successfully apply the analogy between conventional engineering and its use of mathematical techniques and scientific analyses, on the one hand, and software engineering and its use of ideas from the relevant mathematics and logic based analyses, on the other?

An example that may be used in this context is program construction. The well understood underlying mathematics was developed over 25 years (in the sequential case), starting in the 1960s. Thus, we might have expected the SE equivalent of the engineering CAD tool to appear at the end of this time. Instead, we have CASE tools with no relation to the underlying mathematics, or formal methods, which offer a relaxation of the exhaustiveness requirement of the scientific/theoretical viewpoint. There is no equivalent of the conventional engineering disciplines available in industrial software engineering settings.

#### IV. CATEGORIES OF ENGINEERING KNOWLEDGE

Software engineering is distinct in character from conventional disciplines of engineering. However, it has enough in common with them to look for the same categories of knowledge [3]:

- 1) Fundamental design concepts

- 2) Criteria and specifications

- 3) Theoretical tools

- 4) Quantitative data

- 5) Practical considerations

- 6) Design instrumentalities

Fundamental design concepts include the operational principle of their device. According to Polanyi, this means knowing for a device "how its characteristic parts ... fulfill their special functions in combining to an overall operation which achieves the purpose". [4] A second principle taken for granted is the normal configuration for the device, i.e., the commonly accepted arrangement of the constituent parts of the device. These two principles (and possibly others) provide a framework within which normal design takes place. Criteria and specifications allow the engineer using a device with a given operational principle and normal configuration to "translate general, qualitative goals couched in[to] concrete technical terms". That the development of such criteria may be problematic is clear. However, the development and acceptance of such criteria is an inherent part of the development of engineering disciplines.

Engineers require theoretical tools to underpin their work, including intellectual concepts for thinking about design, as well as mathematical methods and theories for making design calculations. Both conceptual tools and mathematical tools may be devised specifically for use by the engineer and be of no particular value to a scientist/mathematician. "... the most useful context for the precision and reliability that formality can offer is in sharply focused micro-methods, supporting specialised small-scale tasks of analysis and detailed design." [1] Engineers also use quantitative data as well as tabulations of functions in mathematical models. (A good example in software engineering of this thoroughness in providing data useful for design is the work of Knuth on sorting and searching.)

There are also practical considerations in engineering. These are not usually subject to systematisation in the sense of the categories above, but reflect pragmatic concerns. For example, a designer will use various trade-offs which are the result of general knowledge about the device, its use, its context, its cost, etc. Design instrumentalities include "the procedures, ways of thinking, and judgmental skills by which it [design] is done" [3]. This is clearly what the Capability Maturity model has in mind when it refers to well defined and repeatable processes in software engineering.

According to Vincenti, as noted above, the day to day activities of engineers consist of normal design, as comprising "the improvement of the accepted tradition or its application under new or more stringent conditions". This is the combination of discipline and a little bit of creativity encapsulated in engineering cookbooks! He goes on to say: "The engineer engaged in such design knows at the outset how the device in question works, what are its customary features, and that, if properly designed along such lines, it has a good likelihood of accomplishing the desired task."

#### V. IN SUMMARY

"An engineering handbook is not a compendium of fundamental principles; but it does contain a corpus of rules and procedures by which it has been found that these principles can be most easily and effectively applied to the particular design tasks established in the field. The outline design is already given, determined by the established needs and products." [1]

Systems become devices when their design attains the status of being normal, i.e., the level of creativity required in their design becomes one of systematic choice, based on well defined analyses, in the context of standard definitions and criteria developed and agreed by the relevant engineers ([3], definition of normal design). This is exactly what engineering BoKs should be about!

#### REFERENCES

- [1] M. Jackson, "The operational principle and problem frames," in *Reflections on the Work of CAR Hoare*. Springer, 2010, pp. 143–165.

- [2] G. F. C. Rogers, *The nature of engineering: a philosophy of technology*. Macmillan Press, 1983.

- [3] W. G. Vincenti, What engineers know and how they know it: Analytical studies from aeronautical history. The Johns Hopkins University Press, 1990.

- [4] M. Polanyi, Personal Knowledge: Towards a Post-critical Philosophy. Routledge & Kegan Paul, London, 1958, reprinted by University of Chicago Press (1974).

# An ontology for complex railway systems, application to the ERTMS/ETCS system

Olimpia Hoinaru<sup>†</sup>, Georges Mariano<sup>†</sup>, Christophe Gransart<sup>‡</sup> \* Université Lille Nord de France French Institute of Science and Technology for Transport,

Development and Networks (IFSTTAR)

Évaluation des Systèmes de Transports Automatisés et de leur Sécurité <sup>‡</sup> LEOST

Laboratoire Électronique Ondes et Signaux pour les Transports

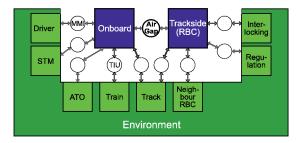

Abstract—We present hereafter our experimental work of building an ontology of the European Rail Traffic Management System (ERTMS) domain. ERTMS is a railway complex control system defined on the basis of publicly available specification documents, the System Requirements Specification (SRS). We will describe the methodology that we used to define an initial structure for an ERTMS ontology. The main goal of this work is to supply a first formalization of the ERTMS knowledge in order to provide the basis of a later development process i.e validating the specifications, developing the software/hardware components and finally validating the system.

Keywords—Ontologies, ERTMS/ETCS, railway systems

#### I. INTRODUCTION

ERTMS stands for the European Rail Traffic Management System. This is a European standard for the process control system and signalling and new lines for the replacement of existing systems for conventional lines. ERTMS contains two basic elements:

- GSM-R (Global System for Mobiles Railway): the communication component containing a voice communication network between vehicle drivers and line controllers. It provides routing and portability for ETCS data. It is based on the GSM public standard with specific features for railways.

- ETCS (European Train Control System): the signalling system component that includes control movement authorities, automatic train protection and interface with the interlocking.

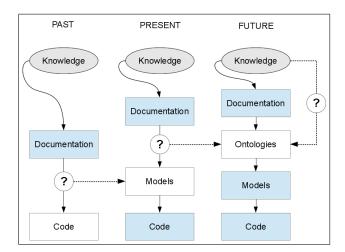

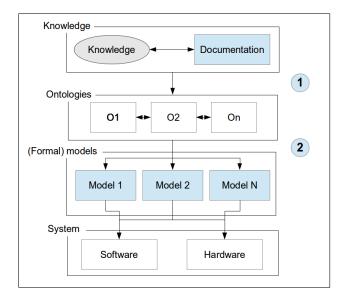

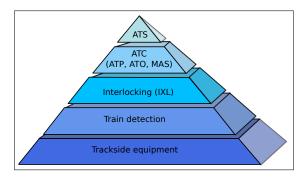

Developing such a complex structure is, of course, a real challenge. Only by considering the development of the corresponding software, we can observe on the figure 1 the general evolution of the technologies employed.

Roughly speaking, in the past, the challenge was to define a method to derive machine code from documentation (this documentation coming from the informal, and sometimes implicite "knowledge" of the system to be developed). To answer this challenge, (countless) modelling methods were defined and are now available. Thus we may now assert that the code is correct because it corresponds to previously established models (whether they are formal or not). Our problematics is how we can provide good models, preferably formal ones.

1

By doing this, we completely follow the paradigm stated in [1]: "Before software can be designed we must understand the requirements. Before requirements can be finalised we must have understood the domain". But where Dines Bjorner uses pure formal logic to tackle generic sample problems, we will experiment the use of ontological technologies (conceptualization, formalization, reasoning) to tackle a real and complex system.

#### II. GENERAL GOAL(S)

The work presented in this article is situated at the intersection of several domains i.e. knowledge management and Web semantics, knowledge representation and formalization, as well as system modelling. The knowledge of the ERTMS domain is considered and formalized for understanding and reuse issues.

Several methods (models) can be used to capture the different aspects of a railway complex system. Based on the fact that the same concept can have different meanings in different domains, the need for specification of these semantic differences was felt.

The ERTMS ontology aims at modelling and formalizing the System Requirements Specification documents of the ERTMS. These documents are written in natural language. The aim of this ontology is the formalization of these specifications in order to obtain a data structure that can be reusable in the framework of other research in the ERTMS field. A module of this ontology is the OSI (Open Systems Interconnection) [2] model and another one concerns the application of the OSI model to the ERTMS/ETCS subsystem dealing with the data transmission by means of radiocommunication.

#### III. ELABORATING ONTOLOGIES

Ontologies are formal representations of knowledge of a certain domain. Several definitions of the term "ontology" have been provided. [3] poses that "an ontology is an explicit specification of a conceptualization". According to the same author "the term is borrowed from philosophy, where an ontology is a systematic account of Existence".

Fig. 1. Ontologies for software-based systems

There are four types of information allowing us to precise what is that we represent in an ontology. These are the type of ontology (domain ontologies, generic ontology, ontology of a method of solving a problem, application ontology and representation ontology), the properties, the "is-a" relation and the other relations [4].

The knowledge of a domain is formalized using several notations with the aim of regrouping and creating a formal structure of the concepts of this domain into a web of knowledge.

We chose an ontology creation tool using the Web Ontology Language (OWL), i.e. the Protégé tool. Protégé-2000 was developed by Mark Musen's group at Stanford Medical Informatics. In this environment, concepts are formalized as classes together with their several types of properties and the relations among them. The so-called "rules" are created for the purpose of modelling requirements and certain "behaviors" of the system.

In the railway domain, documents describing the System Requirements Specifications were issued with the specific aim of explaining and clarifying the usage of a part of the terms/concepts used in this domain, and of the system itself.

#### A. Approaches

This paragraph presents some of the ontology development methodologies existing. "Methontology" is the term used to describe one of these methodologies for creating an ontology. It is among the more comprehensive ontology engineering methodologies as it is one for building ontologies either from scratch, reusing other ontologies as they are, or by a process of re-engineering them.

But methontology is not the only methodology of creating ontologies. Other methodologies like, for example, the corpusbased methodology exist. In this case, the ontology is derived from documents provided in natural language that can also contain diagrams, flow charts, or tables. It is the case of the ERTMS ontology whose creation we are presenting in this study.

• [5] is a publication dealing precisely with this subjectmatter. The authors describe here the reasons that can lead one to develop an ontology i.e. the usage of this kind of structure, its definition, several types of methodologies, as well as the composition and structure of an ontology. We found this article particularly interesting for its explicitness and pedagogical style. The example taken is a test ontology created by the Protege developers, a wine ontology.

#### IV. GLOBAL VIEW OF THE PROPOSED ERTMS ONTOLOGY

#### A. The chosen method

Our ontology is based on normative documentation, i.e. the System Requirements Specification [6] documents provided by the European Railway Agency (ERA). Other related documents are the "ERTMS Glossary" and the "ETCS Implementation Handbook" published by International Union of Railways (UIC). This is an ontology created as a semantic model and module extracted from the below mentioned documents. The extraction is based on the study, the comprehension of these documents, and on the transposition of the information conceptualized in the same documents. All this is being carried out manually by (some of) the authors of this article and not performed automatically as some software can do. As the study of these SRS within the framework of this research is at its beginnings, we chose to start it manually for a better usage of the comprehension of the human understanding. A perspective of this study is the automation of the information extraction from the SRS and other documents. This ontology is a way of formalizing the information provided by these documents. It is not the ultimate aim of this study, but just another more explicit form of the SRS documents.

The railway domain is an environment where numerous heterogeneous information sources exist. The ERTMS system basically relies on information exchange. Ontologies provide a number of useful features for intelligent systems, as well as for knowledge representation generally. The ERTMS ontology that we propose also aims at offering a solution for information exchange, and this for a better railway transportation world.

Train control is an important part of any railway operation management system. In the past a number of different Automatic Train Control (ATC) systems have evolved in different countries at different times. Due to the incompatibility and lack of interoperability among these systems, as well as to a significant increase in density of train traffic anticipated, many railways rethink their infrastructure strategy, in order to accommodate high levels of traffic, in which ATC systems play an important part. This and the fact that many railway systems would like to introduce standardized components to reduce system costs are, among others, the reasons of the existence of this system. In order to establish international standardization of ATC systems, the SRS document specifies the European Rail Traffic Management System/European Train Control System (ERTMS/ETCS).

The ERTMS System Requirements Specification is a set of documents written in natural language, English in this case. It specifies the European Rail Traffic Management System/ European Train Control System (ERTMS/ETCS) which is a control and signalisation innovative system of the railway vehicles and tracks. Also, system safety plays an important role in railway transport as it constitutes a challenging issue that has engaged strong and continuous research interest.

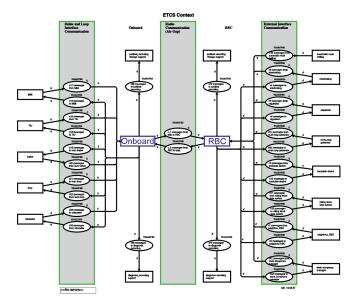

#### B. Ontology building from normative documentation

As mentioned before, in this ERTMS ontology, concepts are formalized as classes (terms). An ontology is not only the identification and classification of concepts, but also of their inherent characteristics that are here called "properties". Moreover the relations gather the concepts together. Primarily, we used the "is-a" relation which is a subsumption relation allowing the formal heritage of properties. The "has-a" relation, also known as composition, is used as well in this ontology, this time not for the class layer but for the instance layer. If, at the beginning, we had conceived our primary concept structure using the two relations for the classes, a differentiation became crucial as work proceeded. Then, other relations were established according to the system's syntax. These relations are created based on properties declaration and domain specification (tab allowing to select the class(es)) on which they take effect. Our ontology is structured into several modules.

- the Entity module, i.e. the superclass containing several entities like Driver, ERTMS, Procedure, describes entities that are used to define the required system behavior on a context level.

- the OSI\_Model is a sibling class of Entity, a module aiming at describing the Open Systems Interconnection (OSI) model. This is a conceptual model that characterizes and standardizes the internal functions of a communication system by partitioning it into abstraction layers. This module will be more thoroughly explained in section VI.

- another sibling class of the above mentioned one is Source. It formalizes information about the SRS and other ERTMS/ETCS documents used as corpus of these ontology.

- TrainCategories is also a child of the Entity superclass, containing information about the different types of rolling stock.

#### V. MODELLING ERTMS PROCEDURES

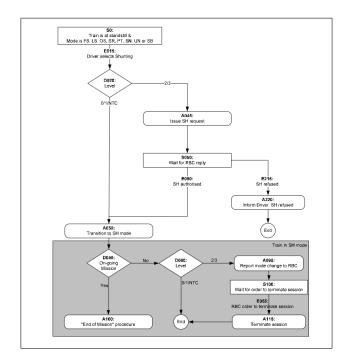

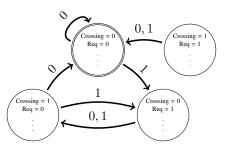

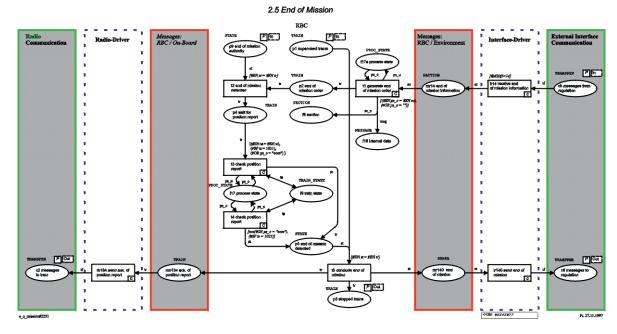

In figure 2, we present an example of a procedure defined in the SRS called "Entering SH mode". The "Shunting" mode is, by definition, a type of ERTMS/ETCS on-board equipment allowing a train to move without having the update train data.

There exist several ERTMS operating modes, as well as all operational modes and procedures necessary to ensure safe information exchange between the driver and the embedded subsystem. Each mode is associated with a specific configuration (train, track and conditions) defining the system state.

Transitions between modes require the establishment of different conditions required to perform the transition properly, i.e. safely. In the SRS, the procedures associated or involving mode transistions are defined by flowcharts linking conditions, decisions and states. The "shunting" flowchart is presented in figure 2.

Fig. 2. Flowchart for the "Shunting" procedure

In order to catch the semantics of these flowcharts in our ontology, we transformed the state transitions in each flowcharts into rules expressed in the SWRL language provided by the Protégé framework. SWRL stands for "Semantic Web Rule Language" and provides a syntax and a semantics to express rules upon the entities available in the ontology. SWRL rules have the form of an implication between an antecedent (body) and consequent (head). The intended meaning can be read as: whenever the conditions specified in the antecedent hold, then the conditions specified in the consequent must also hold.

Considering the flowcharts as state-transition machines, we derived a flowchart into a set of SWRL rules, each rule corresponding to a transition. By doing this, we intended to catch the dynamic behavior of ERTMS/ETCS control system.

#### VI. FOCUS ON THE RADIO-COMMUNICATION PART

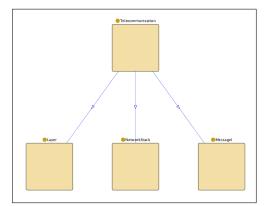

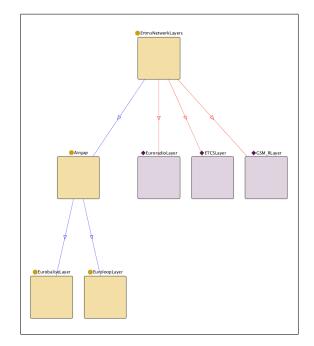

As mentioned in the sections before, this ontology is constructed by modules. One of these modules formalizes the OSI (Open Systems Interconnection) model and another sub-module deals with the application of the generic OSI model to the ERTMS system. This section presents the generic telecommunication model, followed by its instanciation with the OSI model and finally with the ERTMS telecommunication subsystem.

#### A. The radio telecommunication model

First, we defined a generic radio telecommunication model. This model/module is composed of several concepts<sup>1</sup>:

<sup>&</sup>lt;sup>1</sup>concepts defined in our ontology will be typesetted like this ConceptName

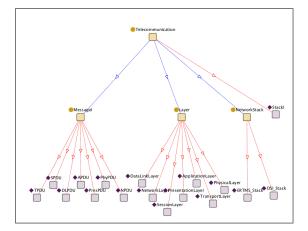

Fig. 3. Generic radio telecommunication concepts

Fig. 4. Hierarchy and instances for the OSI model

- the NetworkStack is the telecommunication stack which is composed of several Layers.

- the Layer is a part of the NetworkStack which is able to marshall and unmarshall some Messages. Each layer is linked to two other Layers: an upper layer and a down layer. The combination of this set of layers is a NetworkStack. A layer manipulates some Messages.

- the Message defines the data that will be sent and received on the network by the Layers.

- The Telecommunication concept references the concepts defined above.

Figure 3 presents graphically this set of concepts.

#### B. Feeding the ontology with the OSI model

Next, we populated the ontology with the concepts that describe the OSI model composed of 7 layers. This part of the work was usefull to see if the concepts defined into the radio telecommunication model were enough and to be sure that nothing was forgotten.

Figure 4 presents the hierarchy as defined previously and all the instances which represent the different layers of a classical OSI network stack. There is one important relation between

Fig. 5. Hierarchy and instances for the ERTMS radio subsystems

the layers. That relation describes the link between two consecutive layers. Its is notated hasUpperLayer between layer N and N+1 and its opposite hasDownLayer between N and N-1. The uppest layer does not have an hasUpperLayer, nor does the lowest layer have a hasDownLayer. These relations are not shown on the figure 4 to keep a clear schema.

#### C. Feeding the ontology with the ERTMS radio subsystem

We applied the same reasoning to represent the concepts of the ERTMS/ETCS radio subsystem. This radio subsystem is composed of three layers (from down layer to upper layer):

- the GSM\_RLayer is based on the GSM specification with some modifications to fit the railway industry needs. The goal of this layer is to transport data packets through a celullar network between the train and the Radio Block Center (RBC).

- the EuroradioLayer deals with the end to end communication between an embedded application into the train and an application on ground. This layer is also responsible for non functional properties like authentication and crytptography of the messages.

- the ETCSLayer manages the messages at the application level of ETCS. This layer permits the communication between the onboard EVC and the ground system RBC that gives the movement authority grant(s) to the train.

- AirGap, EurobaliseLayer and EuroloopLayer represent equipements put on the track. These equipements communicate with the train when it goes over the equipments.

Figure 5 shows the ERTMS Network layer stack with three instances that correspond to the layers described just before.

#### D. Current state

This ERTMS ontology is structured into several layers. The Thing superclass contains several classes like Entity, Source, OSIModel, etc which, in their turn, have several subclasses. For example, the Entity class reunites the subclasses Driver, ERTMS and Procedure. The ERTMS subsubclass contains ApplicationLevel, ERTMSNetworkLayer and ETCS. These are just a few examples of terms that we enterred in the surface levels of the class structure of this ontology.

Currently, the ERTMS ontology that we have been creating contains 112 classes, 193 instances, and 104 properties including object, datatype and annotation properties.

#### VII. RELATED WORKS

Due to the lack of space, we won't provide a huge panel of related works. With a few references, we will show that the main aspects of our work have already been studied and that there exist a solid background to tackle now with complex railway systems (like ERTMS/ETCS is) while involving several concerns like formalisation, requirements engineering, traceability, ...

#### A. Ontologies and software engineering

- In [7], an ontology called *OntoTest* is presented. This ontology is developed in order to promote organization, reuse and sharing of software testing knowledge. The main concepts and artefacts of testing are described (Process, phases, resources, procedures). The ontology itself is figured with UML class diagrams, W3C formalisms are not used in the paper but the ontology is now available in OWL format.

- The work presented in [8] is very close to the goals of our work. Starting from an industrial-use case (the Onboard Unit of ERTMS) a methodology to improve the testing process is provided. This methodology involves the analysis of the SRS specifications, the rewriting of the requirements into a "formal" language. The definition of this language is based on a previously established ontology classicaly defining the concepts, relations and axioms of the domain.

#### B. Ontologies and requirements engineering

[9] describes the expected benefits but also the challenges of using ontologies in requirements engineering (RE) activities. This is exactly the basis of our approach. The main statement is that such approach needs the definition of three ontologies: (1) an **application domain** ontology, (2) a **requirements** ontology and (3) a requirements specification **document** ontology. The **application domain** ontology calls itself a double-utility ontology i.e. a **domain** ontology that defines the necessary concepts for all training in the domain, and an **application** ontology which is one defining the concepts specific to a given application or méthod. The **requirements** ontology is used for representing requirements and their various relationships, as well as the relationships between requirements and systems. Whereas the requirements specification **document** ontology is a documentary ontology. The present paper deals with the creation of an ontology the first type presented above.

#### C. Ontologies and railway systems / applications

In [10], the authors present an ontology creation work conducted during the FP6 InteGRail project [11]. They used the same tools as us (OWL, Protege) to modelize an ontology that permits to check network statement for infrastructure operators. Using the ontology, they combine the network statements of different countries in different formats and analyse them in a transparent way. They modelized the network using concepts like network node, network line, track section, track node. All these concepts permit to the authors to represent the railway network as an object graph. In our work we could reuse such concepts.

#### VIII. CONCLUSIONS AND PERSPECTIVES

In the present paper, we presented an experimental approach aiming at establishing an ontology of a complex domain like the ERTMS/ETCS railway control system. This development is mainly based on the study of a set of referential texts. As an example of the benefits we expect to obtain, we presented the enrichment of the ontology with the consideration of OSI standard levels to define precisely the concepts regarding the radio communication aspects of ERTMS.

*SRS coverage:* Since we focused on a first feasibility of the approach, the current coverage of the available texts by our ontology is obviously reduced. This work shall be improved in order to make our "ontological product" actually usable. It would be a painstaking work that could possibly take advantages on techniques (and related tools) such as automatic language processing. For example, the following step of our experiment may be the use of the GATE framework [12], since it provides ontological and also machine learning facilities.

*Ontology quality:* The quality of the ontology, viewed as a product, can be twofold: first, the quality of the embedded knowledge (as a semantic object); and second, the quality of the ontology itself (as a syntactic object).

The second point can be treated by the use of experience feedback from the elaboration of other ontologies and, particularly by taking into account the best practices of the domain sometimes identified and integrated into dedicated static analysis tools (like OOPS! [13]).

Table I gives the results of the evaluation of the ERTMS ontology by the tool OOPS!, in its current state. These results are barely correct because this "syntactic" aspect of the assessment has not been taken into account yet. For example, the pitfall with the worst score should be easily corrected simply by using the correct "annotation property" attribute for the definitions.

It is also possible to improve the overall quality (structure) of the current ontology by studying aspects like modularity ([14]), thus improving the decomposition and the potential reuse of the knowledge. A better modularity should also make easier the reuse of other related ontologies like testing ontologies, RE ontologies (as stated in section VII-B).

| TABLE I. ONTOLOGY PITFALLS SCANNER OOPS | TABLE I. | ONTOLOGY P | PITFALLS | SCANNER | OOPS! |

|-----------------------------------------|----------|------------|----------|---------|-------|

|-----------------------------------------|----------|------------|----------|---------|-------|

|     | Pitfall                                         | Cases         |

|-----|-------------------------------------------------|---------------|

| P04 | Creating unconnected ontology elements          | 7             |

| P05 | Defining wrong inverse relationship             | 2             |

| P08 | Missing annotations                             | 244           |

| P11 | Missing domain or range in properties           | 35            |

| P13 | Missing inverse relationships                   | 33            |

| P19 | Swaping intersection and union                  | 38            |

| P21 | Using a miscellaneous class                     | 2             |

| P22 | Using different naming criteria in the ontology | ontology* (?) |

| P24 | Using recursive definition                      | 4             |

Fig. 6. Ontologies in the formalized developpement of safety critical systems

Usage of reasoners: The first point (knowledge quality) is essentially a matter of specific expertise to the considered field, but it can also be enhanced by the power of inference mechanisms used especially to detect semantic inconsistencies, incompleteness of relations, ...

All these criteria are not assessable by previous techniques (syntactic/structure level). As we study complex specification documents, it is even more important to implement these mechanisms earlier in the development process, so as to achieve a real "debugging" of the ontology before effective implementation of the system.

Linking ontology and external (formal) models: As a next step, when the ERTMS ontology will be rich enough to be usable, we will start to tackle the problem of deriving more concrete models (mainly formal ones). As described in figure 6, the current work (number one circled) deals with the analysis of available documentation and expert knowledge to derive one ontology (and probably several others in the future) which can be taken as a first step for an abstract formalization.

Formal methods are highly recommended for the development of safety-critical (railway) systems (cf. CENELEC 50128 Norm [15]). The ERTMS/ETCS is a system of this kind and, thus, a formalizable domain.

Indeed, in the openETCS project [16], a european large project involving the main actors of railway research, ERTMS/ETCS (semi-)formal models will be delivered (as well as the corresponding tool-chains). More than ten formalisms/approaches are studied. They range from ADA (the robust programming language), UML and/or sysML, to formal methods like SCADE, B or eventB, Petri nets, ...

The next step (number two circled) will be the derivation of more concrete models using available and well-known (semi-)formalisms like those used in the openETCS initiative. We intend to show that an initial formalization derived from an ontological conceptualisation will be helpful to define the architecture and the main properties for derived formal models.

Since the ontological support languages (OWL, SWRL, ...) used while elaborating our ontology are not too far from classical first order logic and set theory, one path to explore may be a model transformation from our ontology into formal specifications expressed within a "classical" formalism such as the B formal method [17].

Clearly, connecting our approach to the artefacts (formal models!) of the openETCS will be a real achievement.

#### A. Acknowledgements

The present research work is supported by the ICSIT (International Campus on Safety and Intermodality in Transportation) program and funded by the Nord Pas de Calais French Region and the ERDF (European Research and Development Funds). The authors gratefully acknowledge the support provided by these institutions.

#### REFERENCES

- D. Bjørner, "Rôle of domain engineering in software development—why current requirements engineering is flawed!" in *Perspectives of Systems Informatics*, ser. Lecture Notes in Computer Science, A. Pnueli, I. Virbitskaite, and A. Voronkov, Eds. Springer Berlin Heidelberg, 2010, vol. 5947, pp. 2–34. [Online]. Available: http://dx.doi.org/10.1007/978-3-642-11486-1\_2

- [2] A. S. Tanenbaum, Computer Networks. Prentice Hall, 1996.

- [3] G. Thomas R., "A translation approach to portable ontology specifications," *Knowledge acquisition*, vol. 5, pp. 199–220, 1993.

- [4] J. Charlet, B. Bachimont, and R. Troncy, "Ontologies pour le web sémantique," *Action spécifique*, vol. 32, pp. 43–63, 2003.

- [5] N. F. Noy and D. L. Mcguinness, "Ontology development 101: A guide to creating your first ontology," Online, 2001. [Online]. Available: http://www.ksl.stanford.edu/people/dlm/papers/ontology101/ ontology101-noy-mcguinness.html

- [6] E. U. G. UNISIG, System Requirements Specification (SRS) version 3.2.0, E. R. Agency, Ed., 2012. [Online]. Available: http://www.era. europa.eu

- [7] E. F. Barbosa, E. Y. Nakagawa, A. C. Riekstin, and J. Madonado, "Ontology-based Development of Testing Related Tools," 2008. [Online]. Available: http://www.labes.icmc.usp.br/moduloeducacional/ publicacoes/SK06Ellen.pdf

- [8] G. Bonifacio, P. Marmo, A. Orazzo, I. Petrone, L. Velardi, and A. Venticinque, "Improvement of processes and methods in testing activities for safety-critical embedded systems," in *Computer Safety, Reliability, and Security*, ser. Lecture Notes in Computer Science, F. Flammini, S. Bologna, and V. Vittorini, Eds. Springer Berlin Heidelberg, 2011, vol. 6894, pp. 369–382.

- [9] V. Castaneda, L. Ballejos, M. L. Caliusco, and M. R. Galli, "The use of ontologies in requirements engineering," *Global journal of researches in engineering*, vol. 10, no. Issue 6, Nov. 2010. [Online]. Available: http://www.engineeringresearch.org/index.php/GJRE/article/view/76/71

- [10] S. Verstichel, F. Ongenae, L. Loeve, F. Vermeulen, P. Dings, B. Dhoedt, T. Dhaene, and F. D. Turck, "Efficient data integration in the railway domain through an ontology-based methodology," *Transportation Research Part C: Emerging Technologies*, vol. 19, no. 4, pp. 617–643, 2011.

- InteGRail Consortium, "Integrail, intelligent integration of railway systems." InteGRail Consortium, 2009. [Online]. Available: http: //www.integrail.info

- [12] H. Cunningham, D. Maynard, K. Bontcheva, V. Tablan, N. Aswani, I. Roberts, G. Gorrell, A. Funk, A. Roberts, D. Damljanovic, T. Heitz, M. A. Greenwood, H. Saggion, J. Petrak, Y. Li, and W. Peters, *Text Processing with GATE (Version 6)*, 2011. [Online]. Available: http://tinyurl.com/gatebook

- [13] M. Poveda-Villalón, M. Suárez-Figueroa, and A. Gómez-Pérez, "Validating ontologies with oops!" in *Knowledge Engineering and Knowledge Management*, ser. Lecture Notes in Computer Science, A. Teije, J. Völker, S. Handschuh, H. Stuckenschmidt, M. d'Acquin, A. Nikolov, N. Aussenac-Gilles, and N. Hernandez, Eds. Springer Berlin Heidelberg, 2012, vol. 7603, pp. 267–281.

- [14] C. Bezerra, F. Freitas, J. Euzenat, and A. Zimmermann, "ModOnto: A tool for modularizing ontologies," in *Proc. 3rd workshop on ontologies and their applications (Wonto)*, Salvador de Bahia, Brésil, Oct. 2008, p. No pagination., bezerra2008a INRIA-CNPq-OntoCompo; IST-NeOn. [Online]. Available: http://hal.inria.fr/hal-00793533

- [15] CENELEC, "Railway applications communications, signalling and processing systems - software for railway control and protection systems," 2011.

- [16] openETCS, ITEA2 openETCS consortium, 2012. [Online]. Available: http://openetcs.org

- [17] J.-R. Abrial, *The B Book Assigning Programs to Meanings*. Cambridge University Press, Aug. 1996.

## Verification of Scheme Plans using CSP||B

Philip James<sup>\*</sup>, Faron Moller<sup>\*</sup>, Hoang Nga Nguyen<sup>\*</sup>, Markus Roggenbach<sup>\*</sup>, Steve Schneider<sup>†</sup>, Helen Treharne<sup>†</sup>, Matthew Trumble<sup>†</sup>, and David Williams<sup>‡</sup> \*Swansea University, Wales <sup>†</sup>Department of Computing, University of Surrey <sup>‡</sup>VU University, Amsterdam

Abstract—The paper presents a tool-supported approach to graphically editing scheme plans and their safety verification. The graphical tool is based on a Domain Specific Language which is used as the basis for transformation to a CSP||B formal model of a scheme plan. The models produced utilise a variety of abstraction techniques that make the analysis of large scale plans feasible. The techniques are applicable to other modelling languages besides CSP||B. We use the ProB tool to ensure the safety properties of collision, derailment and runthrough freedom.

#### I. INTRODUCTION

In a series of papers [11], [10], [12], [9], [14] we have been developing a new modelling approach for railway interlockings. This work has been carried out in conjunction with railway engineers drawn from our industrial partner. By involving the railway engineers from Invensys, we benefit twofold: they provide realistic case studies, and they guide the modelling approach, ensuring that it is natural to the working engineer.

We base our approach on CSP||B [16], which combines event-based with state-based modelling. This reflects the double nature of railway systems, which involves events such as train movements and – in the interlocking – state based reasoning. The formal models are by design close to the domain models. To the domain expert, this provides traceability and ease of understanding. The validity of this claim was demonstrated in particular in [11] where a non-trivial case study – a complex double junction – was provided, a formal model of which was understandable and usable by our industrial partners.

In [10], [14] we addressed how to *effectively* and *efficiently* verify safety properties within our CSP||B models. The properties of interest are collision, derailment and run-through freedom. To this end we developed a set of abstraction techniques for railway verification that allow the transformation of complex CSP||B models into less involved ones; we proved that these transformations are sound; and we demonstrated that they allow one to verify a variety of railway systems via model checking. The first set of abstractions reduces the number of trains that need to be considered in order to prove safety for an unbounded number of trains. Their correctness proof involves slicing of event traces. Essentially, these abstractions provide us with finite state models. The second set of abstractions simplifies the underlying track topology. Here, the correctness proof utilizes event abstraction specific to our application

domain similar to the ones suggested by Winter in [18]. These abstractions make model checking faster.

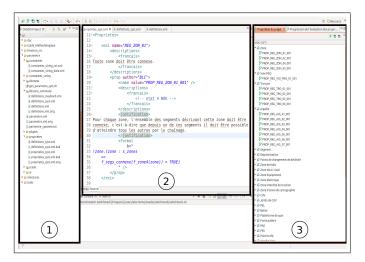

Still present in our approach from the aforementioned papers was the need to write the formal models by hand. In [8] we described our OnTrack toolset<sup>1</sup>, an open tool environment allowing graphical descriptions to be captured and supported by formal verification. This enables an engineer to visually represent the tracks and signals etc., within a railway network.

In this paper we continue the dissemination of our modelling approach which now also incorporates multi-directional tracks. We demonstrate that when changes are made to the models they are systematic and traceable; again this addition will be incorporated within our OnTrack tools.

The paper is organised as follows. In Section II we introduce our modelling language CSP||B so that we have the basis for discussing our workflow and provide examples. In Section III we describe the workflow for our CSP||B modelling approach and summarise where the different abstraction techniques fit into the workflow. In Section IV we introduce the modelling concepts of multi-directional travel and provide two illustrative examples. In Section V we put our work in the context of related approaches and finally conclude with future plans for the approach.

#### II. BACKGROUND TO CSP||B

The CSP||B approach [16] allows us to specify communicating systems using a combination of the B-Method [1] and the process algebra CSP (Communicating Sequential Processes) [6]. The overall specification of a combined communicating system comprises two separate specifications: one given by a number of CSP process descriptions and the other by a collection of B machines. Our aim when using B and CSP is to factor out as much of the "data-rich" aspects of a system as possible into B machines. The B machines in our CSP||B approach are classical B machines, which are components containing state and operations on that state. The CSP||B theory [16] allows us to combine a number of CSP processes Ps in parallel with machines Ms to produce  $Ps \parallel Ms$ which is the parallel combination of all the controllers and all the underlying machines. Such a parallel composition is meaningful because a B machine is itself interpretable as a CSP process whose event-traces are the possible execution sequences of its operations. The invoking of an operation of

<sup>1</sup>OnTrack available for download from http://www.csp-b.org.

a B machine outside its precondition within such a trace is defined as divergence [13]. Therefore, our notion of consistency is that a combined communicating system  $Ps \parallel Ms$  is *divergence-free*. We do not consider deadlock-freedom in this paper as it is concerned with liveness, and the focus of the paper is on safety.

A B MACHINE clause declares a machine and gives it a name. The VARIABLES of a B machine define its state. The INVARIANT of a B machine gives the type of the variables, and more generally it also contains any other constraints on the allowable machine states. There is an INITIALISATION which determines the initial state of the machine. The machine consists of a collection of OPERATIONS that query and modify the state. Besides this kind of machine we also define static B machines that provide only sets, constants and properties that do not change during the execution of the system.

The language we use to describe the CSP processes for B machines is as follows:

$$P ::= e?x!y \to P(x) | P_1 \Box P_2 | P_1 \Box P_2 |$$

if b then  $P_1$  else  $P_2$  end  $| N(exp) |$

$P_1 || P_2 | P_1_A ||_B P_2 | P_1 ||| P_2$

The process  $e?x!y \rightarrow P(x)$  defines a channel communication where x represents all data variables on a channel, and y represents values being passed along a channel. Channel e is referred to as a *machine channel* as there is a corresponding operation in the controlled B machine with the signature  $x \leftarrow e(y)$ . Therefore the input of the operation y corresponds to the output from the CSP, and the output x of the operation to the CSP input. Here we have simplified the communication to have one output and one input but in general there can be any number of inputs and outputs. The other CSP operators have the usual CSP semantics.

In this paper we omit a detail discussion of the semantic models used for reasoning of CSP||B models. In [14] we discuss that the traces models is enough to deal with the safety properties of railway interlockings.

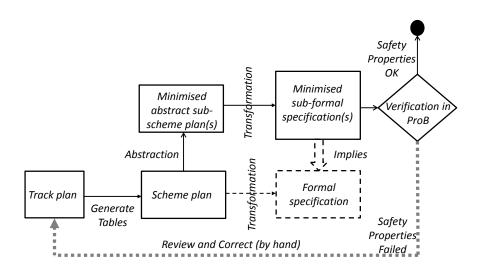

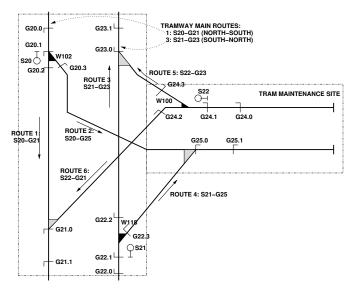

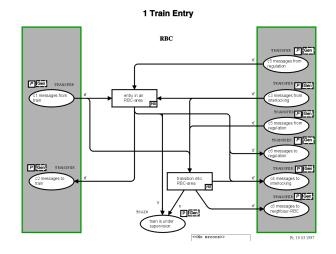

#### III. VERIFICATION WORKFLOW

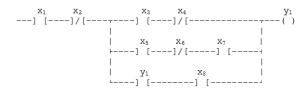

Figure 1 shows the workflow that we employ in our methodology. It makes use of two tools: OnTrack and the ProB model checker [15]. Initially, a user draws a Track Plan using the graphical front end in the OnTrack tool. Then the first transformation, Generate Tables leads to a Scheme Plan, which is a track plan and its associated control and release tables. Control tables contain information about when routes can be granted and release tables contain information about when points can be released, see [11] for details. Note in the paper we typically refer to tracks as being both linear tracks or points. Track plans and scheme plans are models formulated relative to our railway domain-specific language (DSL) meta-model [8]. A scheme plan is the basis for subsequent workflows that support its verification. Scheme plans can be captured as formal specifications. The simplest transformation, indicated by the Transformation dashed arrow, is to produce

one *Formal specification* that is a faithful representation of the scheme plan. This transformation is a mapping from the railway DSL meta-model to the CSP||B meta-model and its subsequent representation as CSP||B script files that can be inputted into ProB. This automated transformation makes use of the finitisation theory in order to be able to perform bounded model checking of the formal specification [10], [7]. The finitisation theory allows us to reduce the problem of verifying of scheme plans for safety (i.e., freedom from collision, derailment, and run-through) for any number of trains to that of a two-train scenario.

Nonetheless, even with the examining a reduced number of trains the formal specifications of realistic examples will inevitably contain too many states for safety analysis. Thus, our methodology enables us to carry out two forms of abstraction on a scheme plan:

(1) Covering Abstraction supports the decomposition of a scheme plan with a set of smaller sub-scheme plans. Any particular track in a scheme plan has a 'zone of influence': the other tracks which need to be considered to see what will happens on that track (e.g., when routes including it are enabled, when trains are approaching it, etc.). In particular, we only need to look at the zone of influence in order to see if a collision is possible on that track. To analyse if a collision, derailment or run-through is possible on that track, it is enough just to analyse the behaviour of trains within the zone of influence. We can do this for all the tracks, in each case just analysing for collisions, derailment or run-through within its zone of influence. This is called a covering. In general each zone of influence is much smaller than the overall track plan, so the analyses will be much quicker, and in practice can be done efficiently.

(2) **Topological Abstraction** supports the collapsing of tracks of a scheme plan to minimise the number of superfluous tracks in a plan, i.e., ones which do not impact on safety. Thus, for a particular track plan we take a sequence of tracks, and think of them as one single track. We do this for a number of sequences of tracks along the way. It is a topological abstraction if we can match moves around the original track plan with moves around the smaller one, so changes such as routes being enabled, points being released, trains being on particular routes, points being set, trains being at lights must still match for this collapsing to be a topological abstraction. If this is true then it means that we can analyse the behaviour of trains on the smaller scheme plan (which is easier because there are fewer positions to consider) and the results that we get will still be true for the original larger scheme plan.

We have proved the soundness of these abstractions in [10], [7]. In our methodology we first apply covering abstraction to generate sub-scheme plans and then apply topological abstraction to each of them. Using these abstractions we follow the *Abstraction* vertical workflow from the scheme plan to produce one or more *Minimised abstract sub-scheme plan(s)*. One or more such plans may be produced because as we shall see in our examples, in Section IV, it may not always be possible to perform covering, and in which case the only abstraction that

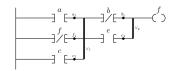

Fig. 1. CSP||B modelling and verification workflow.

may yield a reduction in the number of tracks in the plan will be topological abstraction. Applying these abstractions is done at the DSL level and is independent of the formalism being used to represent the abstract CSP||B specification. Currently, the covering abstraction is not fully automated but is ongoing development work within the OnTrack tool.

Following abstraction (top left box on the diagram) the *Transformation* workflow, described earlier, can be applied to the minimised abstract sub-scheme plans to produce corresponding sub-formal specifications. All of the transformations that are performed by the OnTrack tool are validated via manual review. The verification of all of these sub-formal specifications implies the safety of the formal specification, as illustrated by the *Implies* arrow workflow; this result has been formally proved [10], [7].

Once OnTrack produces the sub-formal specifications they are all systematically verified using the ProB model checker to ensure that the models are collision- and derailment-free and contain no run-throughs. Successful checks verify that the safety properties hold for the particular scheme-plan. The workflow has the potential for round-trip engineering where the counter examples produced from unsuccessful model checking are automatically fed back into the OnTrack tool. This has not, as yet, been incorporated into the tool but it would provide an improved tool-supported workflow; this is illustrated using the dotted *Review and Correct* arrow on the workflow.

## IV. MODELLING OF MULTI-DIRECTIONAL EXAMPLES OF CSP||B RAILWAY MODELS

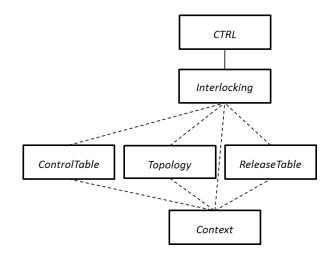

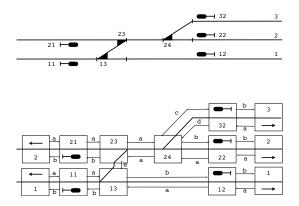

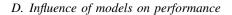

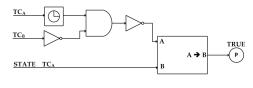

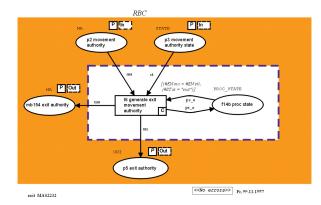

In this section we provide details of the architecture of the formal specifications that are produced by the OnTrack tool. The architecture of a CSP||B specification presented in [11] is restated in Figure 2. The centralised control logic is represented in the *Interlocking* machine, whereas the train

Fig. 2. CSP||B Architecture.

behaviour is controlled by CSP processes defined in the *CTRL* script. These process and machine synchronise on common events. Their definitions are independent of any particular scheme plan but contain the state of the railway interlocking model which changes as these events occur. The definitions are supported by generic domain definitions contained in the following stateless machines: *Topology, ControlTable, ReleaseTable* and *Context*. The sets, relations and functions in these stateless machines are automatically instantiated for a particular scheme plan. The definitions of the types in the *CTRL* script are also automatically instantiated to match the B instantiations. In the next sections we illustrate some aspects of the CSP processes and machines via examples <sup>2</sup> and focus on how multi-directional travel of trains on tracks is modelled.

<sup>&</sup>lt;sup>2</sup>Examples available for download from http://www.csp-b.org.

Fig. 3. Track plan for the tunnel example

| $TRAIN\_CTRL(t, pos) = \dots$                            |

|----------------------------------------------------------|

| $\Box \ pos \notin EXIT \land pos \notin SIGNALHOMES \&$ |

| $move!t.pos?newp \rightarrow TRAIN\_CTRL(t, newp)$       |

| □                                                        |

|                                                          |

Fig. 4. Fragment of the CSP control process for trains.

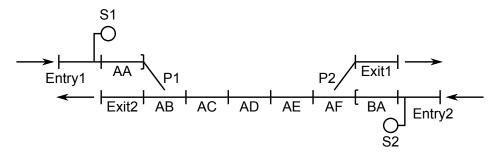

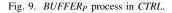

#### A. Tunnel Example

Consider the track plan in Figure 3 where tracks *AB*, *AC* and *AD* are bi-directional tracks. For route *R*1 associated with signal *S*1 their direction is left to right, whereas for route *R*2 associated with signal *S*2 their direction is right to left. The CSP process that controls the movement of trains is *TRAIN\_CTRL*. Figure 4 illustrates the fragment of it controlling the movement of a train from a track that is neither an *exit* one or one which has a signal on it. The *move* event is parameterised with the train identifier *t* and its current position *p*. This event is a synchronisation with a *move* B operation which returns its new position *newp*. Therefore, moving from track *AC* to *AD* corresponds to the event *move.t.AC.AD* for a particular train *t*.

Note, there is no information in the CSP event that corresponds to the direction of travel. All this information is contained in the *Topology* machine and used in the *move* operation within the *Interlocking* machine. In the *Topology* machine there are three relations which define the direction of tracks. For example, the relation *direction* shown in Figure 5 shows that the model needs to contain details of the way tracks are connected together, and this is explicitly done via the notion of identified *connectors* — the glue between tracks and points.

| 1 | <i>direction</i> $\in$ <i>TRACK</i> $\leftrightarrow$ <i>CONNECTOR</i> $*$ <i>CONNECTOR</i> $\land$ |

|---|-----------------------------------------------------------------------------------------------------|

| 2 | $direction = \{\ldots,$                                                                             |

| 3 | $AA \mapsto (C1, C2), \ldots,$                                                                      |

| 4 | $AC \mapsto (C3, C4), AC \mapsto (C4, C3),$                                                         |

| 5 | $AD\mapsto (C4,C5),\ldots\}$                                                                        |

Fig. 5. Fragment of the direction relation from Topology.

As we saw above the notion of a train's position in the CSP was captured using two parameters (t, pos). In the INVARIANT of the *Interlocking* machine a similarly named function *pos* also includes information about the connectors, as shown in

Figure 6. In its INITIALISATION  $pos := \emptyset$  since there are no trains on the tracks. The *move* operation updates the track and connectors related to train *t* in *pos* each time the train moves. (In earlier papers, e.g., [11], *pos* was simply a partial function between trains and tracks and *direction* was not required.)

$$\begin{array}{c|c} 1 \\ 2 \end{array} \begin{array}{c} \textit{pos} \in \textit{TRAIN} \twoheadrightarrow \textit{ALLTRACK}* \\ (\textit{ALLCONNECTOR} * \textit{ALLCONNECTOR}) \end{array} \end{array}$$

In addition to B operations which define the behaviour of movement, granting and releasing of route requests the OnTrack tool automatically produces B operations to support the verification of safety properties. Three B operations are produced, *collision*, *derailment* and *run-through*. Collision is encoded as follows:

| 1 | collision =                                           |

|---|-------------------------------------------------------|

| 2 | SELECT                                                |

| 3 | $\exists t_1, t_2 \in TRAIN \land t_1 \neq t_2 \land$ |

| 4 | $t1 \in dom(pos) \land t2 \in dom(pos)$               |

| 5 | $(dom(pos(t_1)) - (EXIT \cup ENTRY)) \cap$            |

| 6 | $(dom(pos(t_2))) - (EXIT \cup ENTRY)) = \emptyset$    |

| 7 | THEN skip                                             |

| 8 | END;                                                  |

|   |                                                       |

Here collision is detected when two different trains  $t_1$  and  $t_2$  occupy the same track segment (different from the *EXIT* and *ENTRY* tracks). The collision condition will be enabled when the two trains are at the same position.

Collision freedom can then be established by model checking the validity of the following CTL formula:

#### AG(not(e(collision)))

This formula is false if *collision* is enabled. In the CTL variant of PROB AG, stands for "on all paths it is globally true that", and e(a) stands for "event a is enabled". To achieve this the engineer would take the formal specification produced by OnTrack load it into the ProB tool and perform this check. A total of 1,516 distinct states were examined in order to determine that no collision was possible. Our methodology currently requires us to do this loading by hand but automating this as a batch process for all the safety properties could easily be done.

Fig. 7. Track plan for the buffer example

1

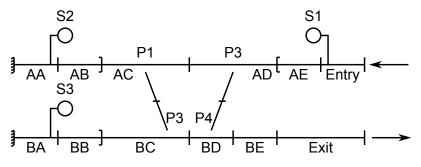

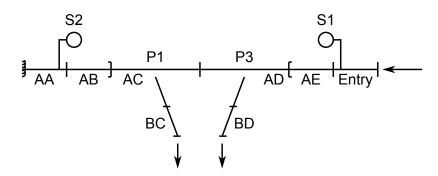

#### B. Buffer Example

Our next example is also multi-directional as shown in Figure 7. Interestingly, track BC has three directions, i.e.,  $\{BC\} \triangleleft direction = \{(C12, C11), (C11, C12), (C7, C12)\},\$ where C7 is the connector between tracks AC and BC, C11 is between BB and BC, and C12 is between BC and BD, respectively.