| ATISFACTION OF TH |

|-------------------|

| R THE DEGREE OF   |

| HILOSOPHY         |

| leer 1982         |

|                   |

|                   |

COMPUTER HARDWARE TO SUPPORT

CAPABILITY BASED ADDRESSING

IN A LARGE VIRTUAL MEMORY

Thesis

submitted for the Degree of

Doctor of Philosophy

Ъy

DAVID ANDREW ABRAMSON

B.Sc. (Hons)

Department of Computer Science

Monash University

August, 1982

# TABLE OF CONTENTS

| 1 | INTRODUCTION                                | 1  |

|---|---------------------------------------------|----|

|   | 1.1 The MONADS Project                      | 1  |

|   | 1.1.1 Aims of the MONADS Project            | 1  |

|   | 1.1.2 History of the Project                | 2  |

|   | 1.2 Objectives of the Thesis                | 3  |

|   | 1.3 Layout of the Thesis                    | 4  |

|   |                                             |    |

| 2 | CONVENTIONAL MEMORY ORGANIZATIONS           | 6  |

|   | 2.1 Software Environment                    | 6  |

|   | 2.1.1 User Programs                         | 6  |

|   | 2.1.2 The Operating System                  | 7  |

|   | 2.1.3 Compilers                             | 8  |

|   | 2.2 Conventional Memory Management Systems  | 8  |

|   | 2.2.1 Linear Memories                       | 8  |

|   | 2.2.1.1 Single User Systems                 | 9  |

|   | 2.2.1.2 Multi-user Systems                  | 9  |

|   | 2.2.1.2.1 Sharing Memory                    | 12 |

|   | 2.2.1.2.2 Protection between User Programs  | 13 |

|   | 2.2.2 Paged Virtual Memories                | 14 |

|   | 2.2.2.1 Single User Systems                 | 16 |

|   | 2.2.2.2 Multi-user Systems                  | 16 |

|   | 2.2.2.3 Address Translation                 | 16 |

|   | 2.2.2.3.1 Small Virtual Address Spaces      | 17 |

|   | 2.2.2.3.2 Small Physical Memories           | 18 |

|   | 2.2.2.3.3 Large Virtual Address Spaces      | 19 |

|   | 2.2.2.3.4 Very large virtual address spaces | 20 |

|   | 2.2.2.4 Protection                          | 20 |

|   | 2.2.2.5 Sharing                             | 21 |

|   | 2.2.2.6 Memory Allocation                   | 22 |

|   | 2.2.2.6.1 Page Replacement                  | 22 |

|   | 2.2.2.6.2 Internal Fragmentation            | 23 |

|   | 2.2.3 Segmented Memory Schemes              | 23 |

| 2.2.3.1 Address Translation                      | 23 |

|--------------------------------------------------|----|

| 2.2.3.1.1 Segment Lists                          | 24 |

| 2.2.3.1.2 Tagged Descriptors                     | 25 |

| 2.2.3.2 Memory Allocation                        | 25 |

| 2.2.3.2.1 Compaction                             | 26 |

| 2.2.3.2.2 External Fragmentation                 | 26 |

| 2.2.3.2.3 Segment Replacement                    | 27 |

| 2.2.3.2.4 Dynamic Segments                       | 27 |

| 2.2.3.3 Protection                               | 27 |

| 2.2.3.4 Sharing                                  | 28 |

| 2.2.3.4.1 Uniform Addressing                     | 29 |

| 2.2.3.4.2 Indirect Evaluation                    | 30 |

| 2.2.3.4.3 Multiple Segment Lists                 | 32 |

| 2.2.4 Segmented and Paged Memories               | 32 |

| 2.2.4.1 Address Translation                      | 33 |

| 2.2.4.2 Protection                               | 35 |

| 2.2.4.3 Sharing                                  | 35 |

| 2.2.4.4 Memory Allocation                        | 36 |

| 2.3 Conclusion                                   | 37 |

|                                                  |    |

| 3 COMPUTER MEMORY HARDWARE                       | 39 |

| 3.1 Introduction                                 | 39 |

| 3.2 Memory Building Blocks                       | 39 |

| 3.2.1 Registers                                  | 39 |

| 3.2.2 Fast Addressable Memories                  | 40 |

| 3.2.2.1 Serial Devices                           | 40 |

| 3.2.2.2 Random Access Devices                    | 41 |

| 3.2.?.2.1 Core Memories                          | 41 |

| 3.2.2.2 Modern Memory Devices                    | 41 |

| 3.2.3 Large Storage Devices                      | 42 |

| 3.2.4 Associative Memories                       | 42 |

| 3.2.4.1 True Content Addressable Memories        | 44 |

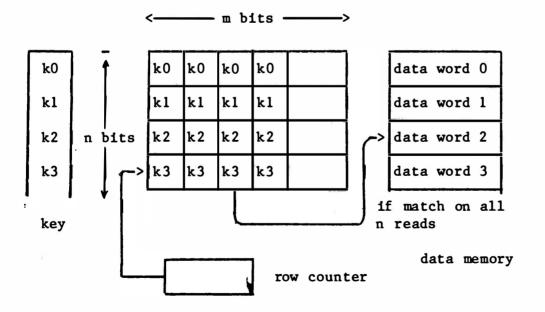

| 3.2.4.2 Linear Scan - Word serial - Bit parallel | 45 |

| 3.2.4.3 Linear Scan - Word parallel - Bit serial | 46 |

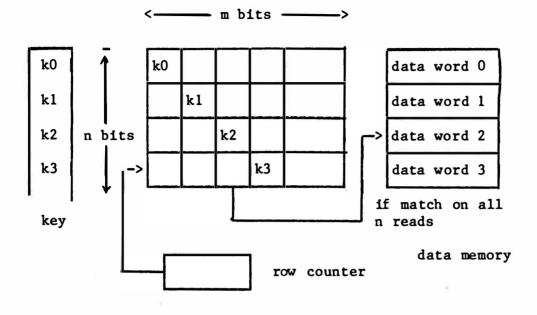

| 3.2.4.4 Skew Addressing                          | 47 |

| 3.2.4.5 Other Searching Algorithms               | 48 |

| 3.2.5 Cache Memories                             | 48 |

| 3.2.5.1 Memory Write Operations                           | ••• 49 |

|-----------------------------------------------------------|--------|

| 3.2.5.2 Inserting and Deleting Items                      | ••• 50 |

| 3.2.5.3 Data Caches and Address Translation Caches        | ··· 50 |

| 3.2.5.4 Implementing Cache Memories                       | ••• 50 |

| 3.2.5.4.1 The Freely Loadable Cache                       | ••• 51 |

| 3.2.5.4.2 Direct Mapping                                  | ••• 51 |

| 3.2.5.4.3 The Set Associate Cache                         | ••• 53 |

| 3.3 Implementing Memory Organizations                     | ••• 53 |

| 3.3.1 Linear Memory Schemes                               | ••• 54 |

| 3.3.1.1 Basic Scheme                                      | ••• 54 |

| 3.3.1.2 Relocation Registers                              | ••• 54 |

| 3.3.2 The Paged Memory Scheme                             | ••• 55 |

| 3.3.2.1 Small Virtual Address Spaces                      | ••• 55 |

| 3.3.2.2 Small Physical Memories                           | ••• 57 |

| 3.3.2.3 Large Virtual and Physical Memories               | ••• 58 |

| 3.3.2.4 Very Large Virtual Spaces                         | ••• 59 |

| 3.3.3 Segmented Memories                                  | ••• 60 |

| 3.3.4 Segmented-Paged Memories                            | ••• 60 |

| 3.4 Conclusions                                           | ••• 61 |

|                                                           |        |

| 4 CAPABILITY BASED ADDRESSING                             | ••• 62 |

| 4.1 The Properties of Capabilities                        | ••• 62 |

| 4.2 Capabilities and Objects                              | ••• 64 |

| 4.3 Implementing a Capability Addressing Scheme           | ••• 65 |

| 4.3.1 Protecting and Using Capabilities                   | ••• 65 |

| 4.3.1.1 Partitioned Segments                              | ••• 65 |

| 4.3.1.2 Tagging                                           | ••• 67 |

| 4.3.2 Names and Mapping Information                       | ••• 68 |

| 4.3.2.1 The Need for Mapping                              | ••• 68 |

| 4.3.2.1.1 Direct Mapping                                  | ••• 69 |

| 4.3.2.1.2 One Level Translation                           | ••• 70 |

| 4.3.2.1.3 Two Level Translation                           | ••• 71 |

| 4.3.2.2 Translating Names into Virtual Addresses          | 72     |

| 4.3.2.3 Translating Virtual Addresses into Real Addresses | •• 76  |

| 4.3.2.3.1 Linear Lists                                    | 76     |

| 4.3.2.3.2 Conventional Page Tables                        | ••• 77 |

| 4.3.2.3.3 Reusable Index Tables                           | 78     |

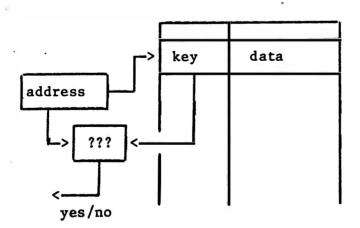

| 4.3.2.3.4 Hash Tables                            | 79   |

|--------------------------------------------------|------|

| 4.3.2.3.5 Active and Passive Segments            | 81   |

| 4.3.2.4 Efficient Address Translation            | 82   |

| 4.3.2.4.1 Visible Addressing Registers           | 82   |

| 4.3.2.4.2 Address Translation Caches             | 84   |

| 4.3.2.5 Logical Properties of Objects            | 84   |

| 4.4 Memory Segmentation                          | 85   |

| 4.4.1 Mapping Tables                             | 86   |

| 4.4.2 Memory Management                          | 87   |

| 4.5 Conclusion                                   | 89   |

|                                                  |      |

| 5 A NEW CAPABILITY BASED ADDRESSING MODEL        | 90   |

| 5.1 Aims of the Model                            | 90   |

| 5.1.1 Memory Management                          | 91   |

| 5.1.2 Address Translation Problems               | 91   |

| 5.1.3 Uniformity and Simplicity                  | 92 _ |

| 5.1.4 Efficiency                                 | 92   |

| 5.1.5 Flexibility                                | 92   |

| 5.2 Object Addressing                            | 93   |

| 5.3 Segment Addressing                           | 94   |

| 5.3.1 The Basic Form of a Capability             | 94   |

| 5.3.2 The Load-capability-register Instruction   | 97   |

| 5.3.3 Representation of a Capability             | 97   |

| 5.3.4 Refinement of Capabilities                 | 98   |

| 5.3.5 Summary                                    | 101  |

| 5.4 Virtual Memory                               | 102  |

| 5.4.1 Requirements of the Virtual Memory         | 102  |

| 5.4.2 A Small Segment Model                      | 103  |

| 5.4.2.1 Simple Real Memory Management            | 105  |

| 5.4.2.2 Simple Virtual Memory Management         | 105  |

| 5.4.2.3 Support for Small and Large Segments     | 105  |

| 5.4.3 Applying the Memory Management Model       | 106  |

| 5.4.4 Summary                                    | 107  |

| 5.5 Application of the Model                     | 107  |

| 5.5.1 The INTEL 1APX432                          | 108  |

| 5.5.1.1 The Intel Addressing Structure           | 108  |

| 5.5.1.2 Mapping the Intel iAPX432 onto the Model | 110  |

| 5.5.2 CAP-3                                                          | 111 |

|----------------------------------------------------------------------|-----|

| 5.5.2.1 CAP-3 Addressing Structure                                   | 111 |

| 5.5.2.2 Mapping CAP-3 onto the Model                                 | 113 |

| 5.5.3 MONADS                                                         | 113 |

| 5.5.3.1 The MONADS Addressing Structure                              | 113 |

| 5.5.3.2 Mapping the MONADS Software Structure onto the Model $\cdot$ | 115 |

| 5.5.4 Summary                                                        | 116 |

| 5.6 Evaluation of the Hardware Model                                 | 117 |

| 5.6.1 Model Aims                                                     | 117 |

| 5.6.1.1 Memory Management                                            | 117 |

| 5.6.1.2 Address Translation Problems                                 | 118 |

| 5.6.1.3 Uniformity and Simplicity                                    | 118 |

| 5.6.1.4 Efficiency                                                   | 118 |

| 5.6.1.5 Flexibility                                                  | 119 |

| 5.6.2 Comparison to Other Systems                                    | 119 |

| 5.6.2.1 The Use of Registers                                         | 119 |

| 5.6.2.2 The Capability Format                                        | 120 |

| 5.6.2.3 Refinement                                                   | 120 |

| 5.6.2.4 Real Store Management                                        | 120 |

| 5.6.2.5 Virtual Store Management                                     | 120 |

| 5.6.2.6 Small and Large Segments                                     | 121 |

| 5.6.2.7 Address Translation                                          | 121 |

| 5.7 Conclusion                                                       | 121 |

|                                                                      |     |

| 6 AN ARCHITECTURAL ENHANCEMENT TECHNIQUE                             | 122 |

| 6.1 Realizing a New Architecture                                     | 122 |

| 6.2 Using an Existing Computer System                                | 123 |

| 6.2.1 A Software Emulation                                           | 124 |

| 6.2.2 A Firmware Implementation                                      | 125 |

| 6.2.3 Modifying the Source Hardware                                  | 126 |

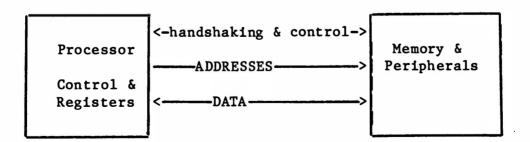

| 6.3 Hardware Modifications                                           | 127 |

| 6.3.1 Processor Configurations                                       | 127 |

| 6.3.2 Breaking the Address Bus                                       | 128 |

| 6.4 An Enhancement Model                                             | 129 |

| 6.5 Application of the Enhancement Model                             | 131 |

| 6.5.1 Dividing the Address Space into Areas                          | 131 |

| 6.5.2 Some Architectural Enhancements                                | 131 |

| 6.5.2.1 Adding New Registers                      | 132  |

|---------------------------------------------------|------|

| 6.5.2.2 Adding New Instructions                   | 132  |

| 6.5.2.3 Adding New Addressing Modes.              | 134  |

| 6.5.2.4 Adding a Virtual Memory.                  | 135  |

| 6.5.2.5 Expanding the Address Size                | 136  |

| 6.5.2.6 Detecting Errors.                         | 136  |

| 6.6 Conclusions                                   | 136  |

|                                                   |      |

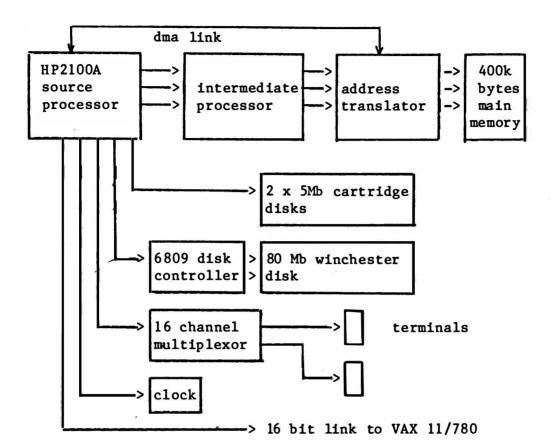

| 7 THE MONADS SERIES II SYSTEM - AN IMPLEMENTATION | 138  |

| 7.1 The MONADS SERIES II System - Primary Aims    | 138  |

| 7.2 The HP2100A Processor                         | 1 39 |

| 7.2.1 The View of Memory                          | 139  |

| 7.2.2 The Instruction Format                      | 140  |

| 7.2.3 The Input-Output (I/O) System               | 141  |

| 7.2.4 The Direct Memory Access System (DMA)       | 141  |

| 7.2.5 The Control System                          | 142  |

| 7.2.6 Interrupts                                  | 142  |

| 7.3 The Intermediate Processor                    | 142  |

| 7.3.1 Functionality                               | 142  |

| 7.3.1.1 Privilege Modes                           | 142  |

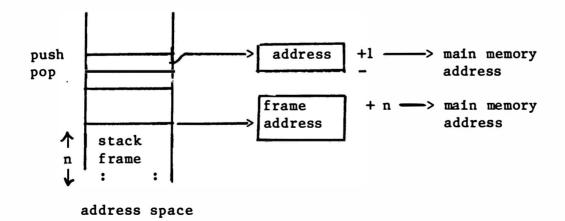

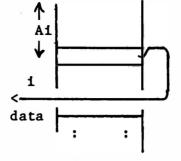

| 7.3.1.2 Addressing Structure                      | 143  |

| 7.3.1.2.1 The Capability Registers                | 143  |

| 7.3.1.2.2 The Modifier Registers                  | 144  |

| 7.3.1.2.3 The Counter Registers                   | 145  |

| 7.3.1.2.4 Extra Capability Registers              | 145  |

| 7.3.1.2.5 Summary                                 | 146  |

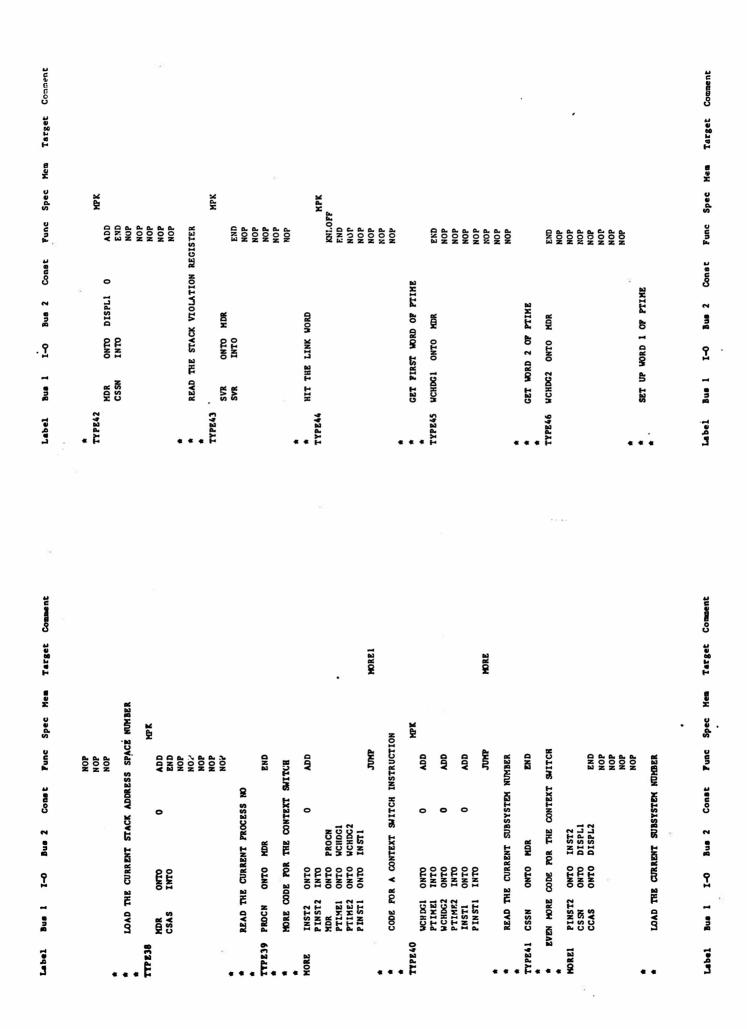

| 7.3.1.3 Process Changes                           | 147  |

| 7.3.1.4 The Kernel                                | 147  |

| 7.3.1.5 Control Registers                         | 147  |

| 7.3.1.6 Additional Features                       | 148  |

| 7.3.2 Address Mapping                             | 148  |

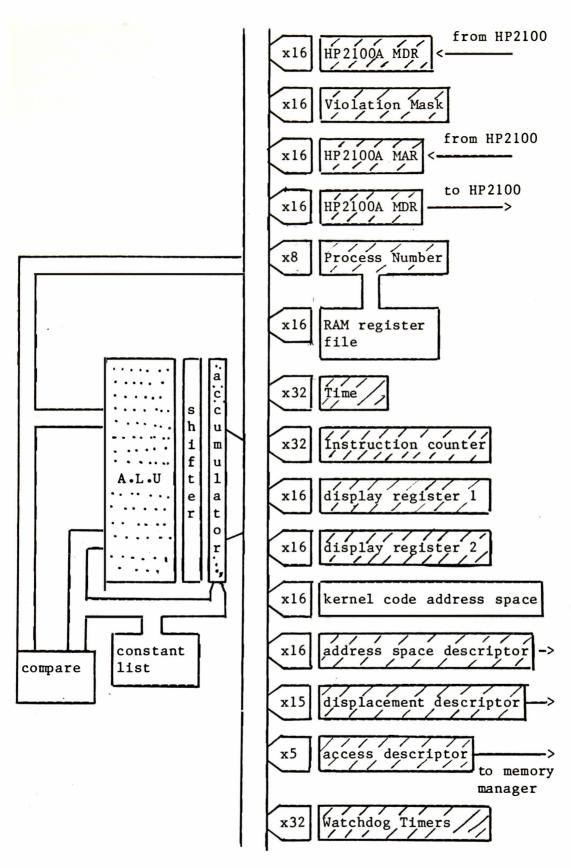

| 7.3.3 Implementation Details                      | 149  |

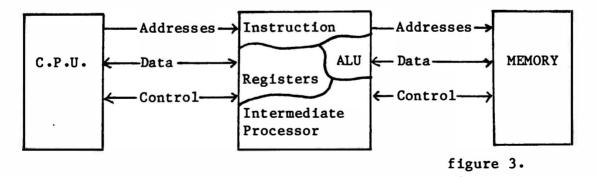

| 7.3.3.1 The Intermediate Processor Bus Structure  | 149  |

| 7.3.3.2 The Dedicated Registers                   | 151  |

| 7.3.3.2.1 The Descriptor Registers                | 151  |

| 7.3.3.2.2 The Watchdog Timer Registers            | 152  |

| 7.3.3.2.3 The Instruction Counters                | 152  |

| 7.3.3.2.4 The Display Registers                        | 152   |

|--------------------------------------------------------|-------|

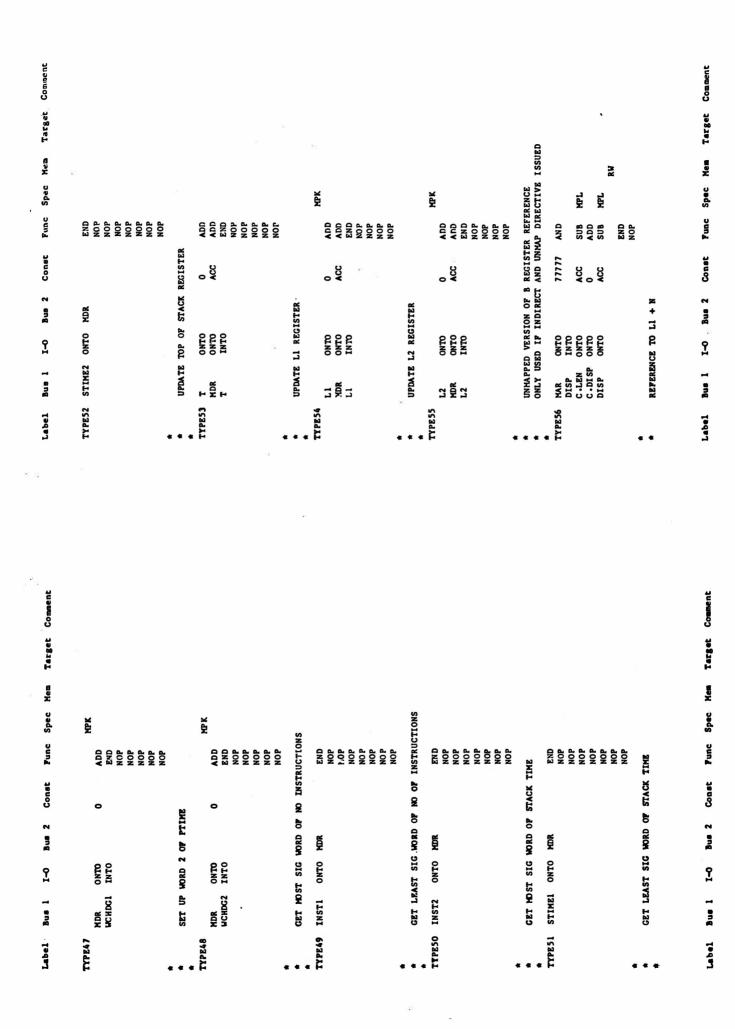

| 7.3.3.2.5 The Time Registers                           | 152   |

| 7.3.3.2.6 The Process Number Register                  | 152   |

| 7.3.3.2.7 The HP2100A Memory Address Register          | 152   |

| 7.3.3.2.8 The HP2100A Memory Data Register             | 153   |

| 7.3.3.2.9 The Violation Register                       | 153   |

| 7.3.3.3 The High Speed Arithmetic Unit and Accumulator | 153   |

| 7.3.3.4 The Register File                              | 153   |

| 7.3.3.5 The Control Unit                               | 154   |

| 7.3.3.6 Summary                                        | 154   |

| 7.4 The Memory Manager                                 | 154   |

| 7.4.1 Functionality                                    | 154   |

| 7.4.1.1 Nature of the Problem                          | 154   |

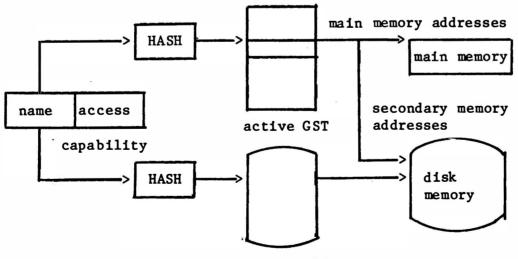

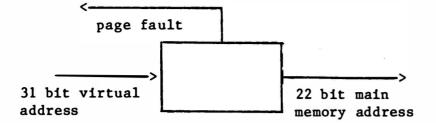

| 7.4.1.2 Aims of the MONADS II Address Translation      | 155   |

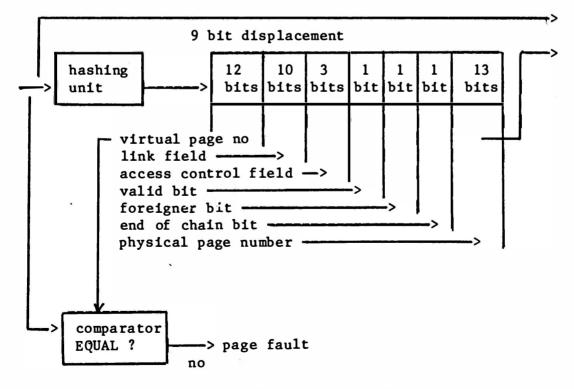

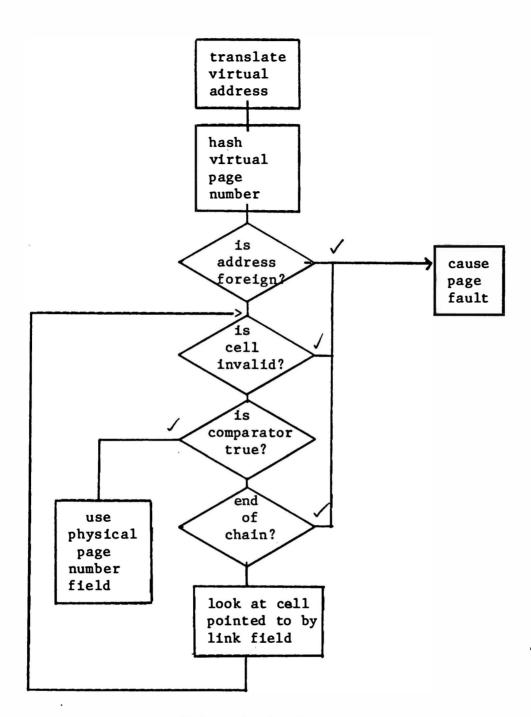

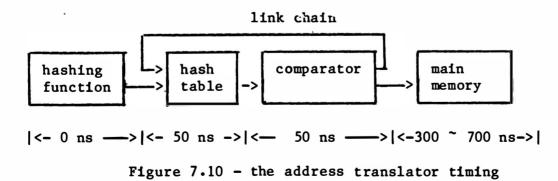

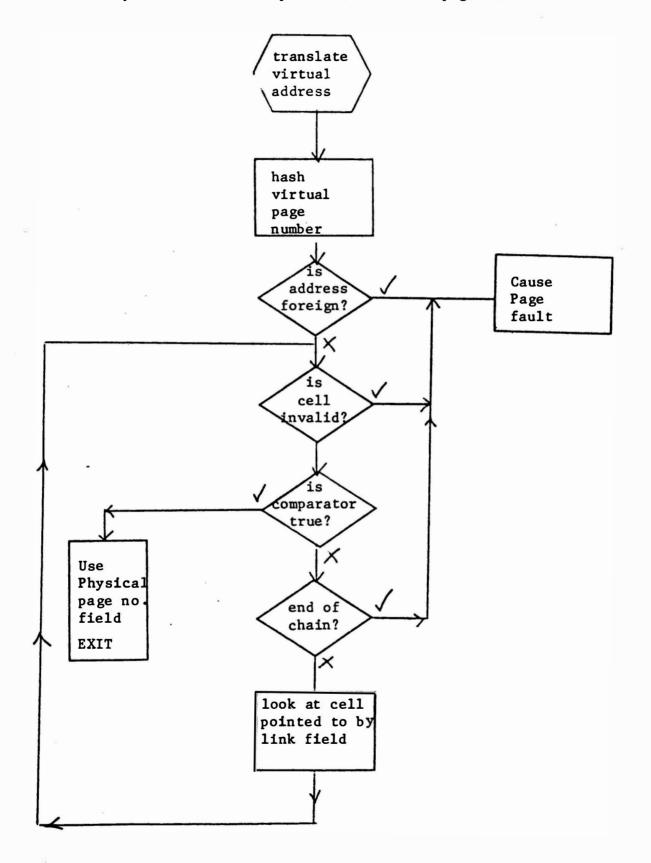

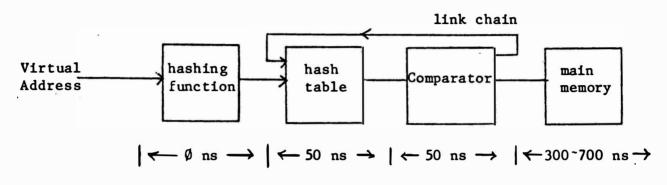

| 7.4.1.3 The MONADS II Address Translation Hardware     | 156   |

| 7.4.1.4 Retrieval                                      | 157 _ |

| 7.4.1.5 Insertion                                      | 157   |

| 7.4.1.6 Deletion Algorithm                             | 158   |

| 7.4.2 Implementation Details                           | 160   |

| 7.4.2.1 Internal Structure                             | 161   |

| 7.4.2.2 Hashing Unit                                   | 161   |

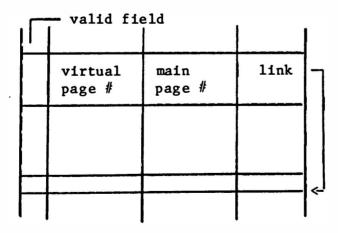

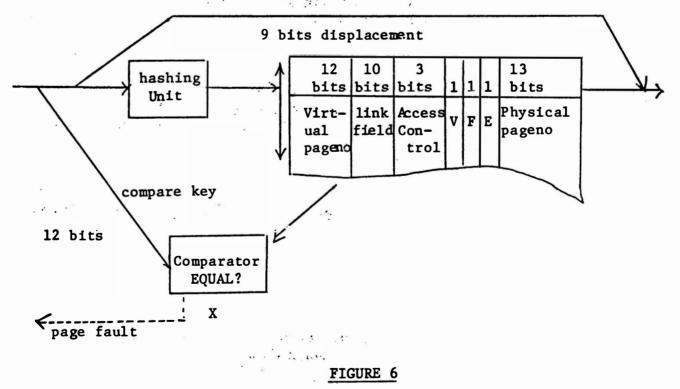

| 7.4.2.3 The Hash Table                                 | 162   |

| 7.4.2.3.1 The Virtual Address Identifier               | 162   |

| 7.4.2.3.2 The Physical Page Number                     | 162   |

| 7.4.2.3.3 Access Control Field                         | 162   |

| 7.4.2.3.4 Valid Field                                  | 163   |

| 7.4.2.3.5 The Link Field                               | 163   |

| 7.4.2.3.6 Foreigner Field                              | 163   |

| 7.4.2.3.7 End of Chain Field                           | 164   |

| 7.4.2.3.8 Summary                                      | 164   |

| 7.4.2.4 The Comparator                                 | 164   |

| 7.4.2.5 The Finite State Control Machine               | 164   |

| 7.4.2.6 The Software Algorithms                        | 164   |

| 7.4.2.7 Communicating with the Hash Table              | 166   |

| 7.4.2.8 Address Spaces 1, 2, 3 and 4                   | 166   |

| 7.4.2.9 The Peek Operation                             | 167   |

| 7.4.2.10 Performance of the Address Translator         | 167   |

|   | 7.4.3 Alternative Solutions                | 169   |

|---|--------------------------------------------|-------|

|   | 7.4.4 Conclusions                          | 170   |

|   | 7.5 Modifications to the HP2100A Hardware  | 170   |

|   | 7.5.1 The Memory Controller                | 171   |

|   | 7.5.2 DMA Logic                            | 171   |

|   | 7.5.3 More Writable Control Store          | 171   |

|   | 7.5.4 Mapping to Top Leaf                  | 171   |

|   | 7.5.5 Interrupt Logic                      | 172   |

|   | 7.5.6 Asynchronous Interface               | 172   |

|   | 7.5.7 Summary                              | 172   |

|   | 7.6 Software Packages                      | 172   |

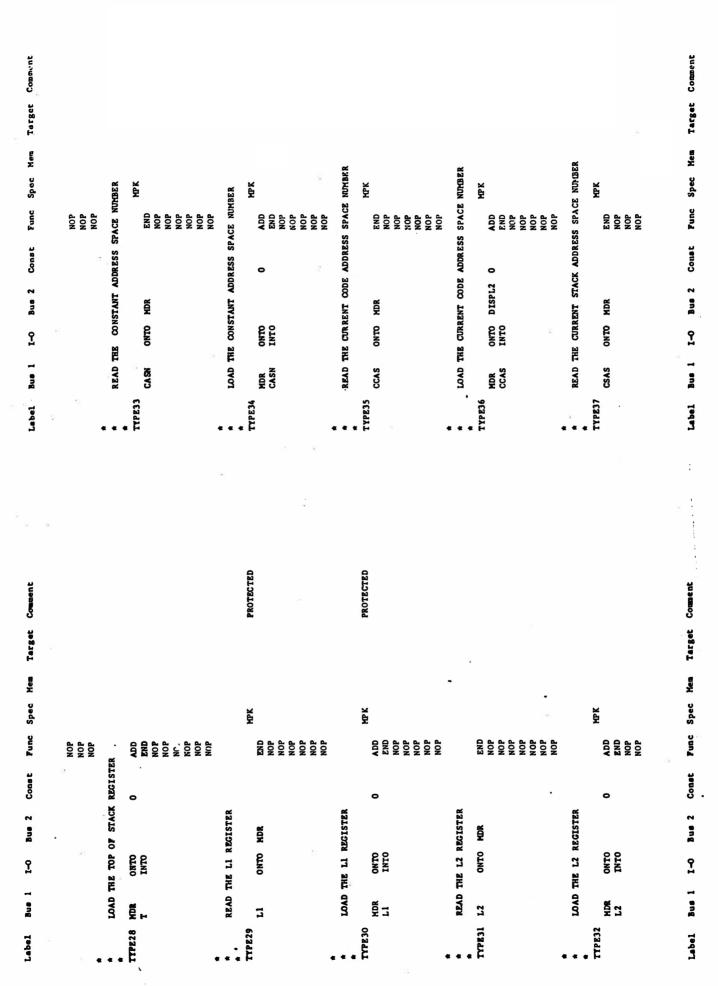

|   | 7.6.1 The Intermediate Processor Microcode | 172   |

|   | 7.6.2 The Microcode Assembler              | 173   |

|   | 7.6.3 The Bootstrap                        | 173   |

|   | 7.6.4 Utilities                            | 173   |

|   | 7.7 Conclusion                             | 173 _ |

|   |                                            |       |

| 8 | CONCLUSION                                 | 175   |

|   | 8.1 Limitations of the MONADS II System    | 175   |

|   | 8.1.1 The Address Size                     | 175   |

|   | 8.1.2 Special Capability Registers         | 176   |

|   | 8.1.3 The Hashing Function                 | 176   |

|   | 8.1.4 Processor Speed                      | 177   |

|   | 8.1.5 The HP2100A Instruction Set          | 177   |

|   | 8.1.6 Page Replacement                     | 177   |

|   | 8.1.7 Offsets from Capability Registers    | 178   |

|   | 8.2 Future Research                        | 178   |

|   | 8.2.1 MONADS III                           | 178   |

|   | 8.2.2 MONADS II/2                          | 179   |

|   | 8.2.3 Future Work                          | 179   |

|   | 8.3 Achievements and Significance          | 180   |

|   | 8.3.1 The Addressing Model                 | 180   |

|   | 8.3.1.1 Sharing of Data and Code           | 180   |

|   | 8.3.1.2 Protection of Information.         | 181   |

|   | 8.3.1.3 Flexibility                        | 181   |

|   | 8.3.1.4 Efficiency                         | 181   |

|   | 8.3.1.5 Uniformity                         | 182   |

| 8.3.2 The Enhancement Model  | 182 |

|------------------------------|-----|

| 8.3.3 Practical Achievements | 182 |

| 8.4 Final Remarks            | 183 |

APPENDIX A - Instruction Set ..... Al - 6 APPENDIX B - Mapping Details ..... Bl - 2 APPENDIX C - Microcode .... Cl - 18 APPENDIX D - Address Space Zero .... Dl - 3 APPENDIX E - Published Papers .... El - E39 BIBLIOGRAPHY .... BIBL - BIB9

#### SUMMARY

The research described in this thesis was undertaken with the aim of providing a suitable computer architecture for supporting the development and execution of large software systems decomposed into modules according to the information hiding principle. In the course of this work, the author developed two models relevant to the achievement of this aim.

The first model is framed in terms of a memory management and addressing scheme which bases protection on capabilities and overcomes the major memory management and address translation problems found in other capability-based architectures.

The second model arose from the author's practical work in modifying an existing computer (a Hewlett Packard HP2100A) to support this architecture. It proposes a general technique for upgrading relatively primitive computers to support more advanced features, in terms of addressing modes, additional registers, new instructions and virtual memory.

Chapter 1 provides background information which led the author to undertake this research, and explains the structure of the thesis.

Chapter 2 surveys the conventional memory management systems, and describes a number of the more common problems associated with them.

Chapter 3 describes the hardware used by most memory management systems.

Chapter 4 surveys current capability based addressing schemes and highlights their problems.

Chapter 5 describes the new architectural model and shows how it solves the problems raised in earlier chapters.

Chapter 6 addresses the problem of how to implement the new model both cheaply and quickly. In doing so, it develops a general technique which can be used to implement new computer architectures. Chapter 7 describes a practical implementation of the addressing scheme described in chapter 5 using the technique defined in Chapter 6.

The concluding chapter examines the extent to which the two models proposed in this thesis have been successful and practical.

The two major contributions of this research work are the new addressing model proposed in Chapter 5, and the architectural enhancement model proposed in Chapter 6.

The new addressing model avoids the two major problems of current capability based computers, namely memory management problems associated with small and large segments, and also address translation problems which arise in systems which make abundant use of segments. The model is shown to be more efficient than the addressing schemes used in other capability systems. Unlike other capability based and conventional computers, it is flexible enough to efficiently implement many different capability addressing structures. Consequently, the software ideas can change and evolve, without affecting the hardware.

The new enhancement technique allows many different architectural enhancements to be implemented and tested as an extension of an existing computer system, and thus allows a full scale evaluation of the ideas to be made. Because the technique allows complex structures to be constructed quickly, accurately and cheaply, it avoids the problems found in many theses which propose new architectures without coming to terms with their practical implications.

In addition to these contributions, during the course of the implementation work, a new address translation unit was devised which, whilst not significantly different in concept, is significantly different in implementation from many other units.

#### DECLARATION

This thesis contains no material which has been accepted for the award of any other degree or diploma in any other university, and to the best of my knowledge contains no material previously published or written by another person, except where reference has been made in the text of the thesis.

Signed:

David Abramage

David Abramson Department of Computer Science, Monash University, August, 1982.

#### ACKNOWLEDGEMENTS

I am most grateful to Dr Les Keedy, who has unofficially supervised my post-graduate work. He has always been ready to listen to my ideas and guide my research. Without his enthusiasm this thesis would never have been completed.

I am also grateful to my supervisor, Professor Chris Wallace. He has contributed greatly, particularly while I was designing the MONADS II hardware. Many complex problems and solutions became easier to understand because of his assistance.

Dr John Rosenberg has had a large influence on the direction of my research. I am not only thankful for his professional advice, but also his friendship. I also appreciate his time spent proof reading this manuscript.

The design of the MONADS II processor has been influenced greatly by the members of the MONADS project, particularly Mr. Peter Dawson, Dr. Ed Gehringer, Mr. Mark Halpern, Dr K. Ramamohanarao, Dr. Ian Richards, Mr. David Rowe, and Mr. John Wells.

I am indebted to the department technical officers, particularly Mr David Duke and Mr Steve Garrison, who constructed much of the MONADS II hardware.

Many of the bugs in the MONADS II system would not have been found without the help of Brian Wallis, who developed the hardware kernel for the system.

I would like to thank Ms. Lyn Winberg for typing part of the manuscript. Thanks are also due to Dr Ken McDonell, who helped with the text formatting.

During the first year of my candidature I was funded by a Commonwealth Post Graduate Award which I appreciate greatly.

Without the friendship and encouragement of my very close friends over the last four years this thesis would never have been completed. In particular, Heather has offered much support during the long process of writing. I am grateful for the love and patience of my family, who have put up with so much.

Finally, I appreciate the love and sacrifice of my parents. They created an environment in which it was pleasant to learn and study, often at their own expense. I only wish that my father had lived to see this work completed.

# DEDICATION

This thesis is dedicated to my loving father, Dr Phillip Abramson, who died shortly before it was completed. I miss his encouragement, love and friendship so much.

#### 1. Introduction

The research described in this thesis was conducted as part of the MONADS project in the Department of Computer Science at Monash University. The thesis topic is concerned with the development of computer hardware, in the form of the MONADS II system, but in addition to descriptions of the actual MONADS II development the thesis describes two general models which have more general applicability. The first of these is a model for building capability-based computer systems in a more flexible way than has hitherto been attempted. The second model describes a general approach which can be adopted to enhance existing relatively simple computers to support a wide variety of extensions, such as the addition of new addressing modes, new registers and support for a virtual memory.

#### 1.1. The MONADS Project

## 1.1.1. Aims of the MONADS Project

The MONADS project (Keedy, 1978, 1981; Keedy, Abramson, Rosenberg Rowe, 1982) began in 1976 with the intention of investigating and methods for developing large complex software systems. The techniques used in the project are based on the information hiding principle, as advocated by Parnas (1971, 1972) and others (Wirth, 1977; Liskov and Zilles, 1974; Keedy and Rosenberg, 1981; Keedy and Rosenberg, 1982b). Using this principle software systems are decomposed into small information hiding modules, each of which performs a specific task. The data structures and algorithms used by these modules are totally hidden from other modules which make use of their services, and communication between modules is by a procedural interface. Unlike many language based solutions (Liskov, Snyder, Atkinson, and Schaffert, 1977; Dahl, Myhrhaug and Nygaard, 1968; Wulf, London and Shaw, 1976), the MONADS project provides support for the information hiding module at an architectural level (Keedy, 1982b). Moreover, modules are used uniformly to represent all addressable objects, even those which conventionally have their own mechanisms for addressing, protection and sharing, such as files (Keedy and Richards, 1982).

From an implementation viewpoint, modules are constructed from segments of memory, each of which must be addressed from within the module and protected from access by other modules. For this reason, both modules and segments are addressed by capabilities (Fabry, 1974). Algorithms are implemented by code segments, and data structures can be held in data segments. Because the interface is strictly procedural the segments can only be directly addressed from within a module.

## <u>1.1.2.</u> <u>History of the Project</u>

The first phase of the project involved building an operating system (Keedy, 1978). The idea was to demonstrate that an operating system, and in fact any large software system, could be broken into small units, each of which is implemented by an information hiding module. During the system design it became clear that a conventional computer architecture was ill-suited to the new software methodology. The major area of concern was the way that information and modules are shared and protected. Consequently, the MONADS I processor was developed in about 1978 (Hagan and Wallace, 1979; Wallace, 1978; Hagan 1977) from a modified Hewlett Packard HP2100A. This processor provided a small virtual memory (4 x 32k word address spaces) and a number of previously unsupported addressing modes, such as process stack addressing and base and index register addressing. This new hardware was still unable to implement all of the required support functions, and the idea of a hardware kernel was developed in an attempt to bridge the hardwaresoftware gulf (Rosenberg and Keedy, 1978; Rosenberg, 1979). Much was learned from this preliminary implementation. Apart from the concept of hardware kernel, а process structuring model was designed а (Ramamohanarao and Keedy, 1978; Ramamohanarao, 1980; Keedy and Ramamohanarao, 1979), and a model was developed to describe the way that the information hiding modules should be addressed and protected (Richards and Keedy, 1978; Richards, 1982).

The MONADS I hardware presented a number of major implementation problems. First, the hardware was not totally secure. While individual user programs could be protected from each other, it was difficult to protect a program from corrupting sensitive information held on the process stack (e.g. linkage or parameter information), allowing security violations to occur. Second, user programs (and the associated data and stack space) could not be larger that 32k words, the size of one address space. This severely restricted the use of the system. Third, the hardware provided a paged addressing scheme, which presented sharing and protection problems. Fourth, the hardware could only support three concurrent user programs. Finally, because many of the important functions were implemented in the kernel (due to insufficient room in the microprogram control store) the system was quite inefficient.

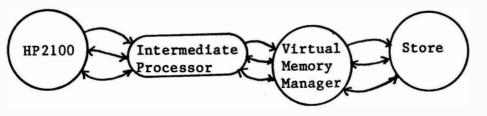

Because of these drawbacks, the author developed the MONADS II processor in 1980, again from a Hewlett Packard HP2100A minicomputer. However, this computer differed from MONADS I in two important respects. First, a different construction technique was used (Abramson, 1982a). Second, the MONADS II hardware was not specifically designed for the MONADS software methodology, but was a general capability based addressing processor able to implement many different software structures (Abramson, 1982b). At the same time as the new hardware was being designed, the MONADS software group was defining the addressing structure of the information hiding modules, which was then mapped onto the hardware. Following this, a new hardware kernel (Wallis, 1980) and a new operating system were designed. MONADS II removed some of the restrictions of MONADS I by providing a large virtual memory (Abramson, 1981), a uniform addressing mechanism and many new addressing modes (Abramson, 1980).

Whilst MONADS II demonstrated all of the principles of the new software structures, it was developed as a pilot system capable of supporting only a limited number of concurrent user programs. Thus, work began on a new processor, MONADS III (Keedy and Rosenberg, 1982), which built on the experience gained from the MONADS II system, but which would be powerful enough to provide a fast computer utility to a number of users. While MONADS II and MONADS III have many features in common<sup>-</sup> (Keedy, Rosenberg, Abramson and Rowe, 1982), and may be coupled to form a multi-computer system, they differ significantly at the implementation level.

#### 1.2. Objectives of the Thesis

This thesis contributes to the implementation of the MONADS software ideas by developing two general models, which are used in the MONADS II processor design. The first provides a hardware addressing unit, which allows information to be shared and protected in a uniform, flexible and efficient manner. This unit should be able to be used with a number of different software structures. The model draws a clear distinction between functions which should be supported in hardware (for efficiency reasons) and functions which should be implemented in software or firmware (for flexibility reasons). Because of this flexibility the hardware may be used in other capability projects as well as the MONADS project.

The second model defines a technique for implementing complex and different computer architectures quickly and cheaply. This not only enables a full scale evaluation of the new addressing model to be performed (in terms of supporting a real program development environment) but also serves as a general technique for evaluating many new architectural ideas. This scheme has many advantages over existing techniques, particularly in terms of efficiency and simplicity.

## 1.3. Layout of the Thesis

Chapter 2 describes the memory management models used by conventional computer systems, such as linear memories, paged memories, segmented memories and paged and segmented memories. By examining these systems in terms of their ability to protect and freely share information, we show that they do not provide an adequate addressing scheme. The chapter concludes that the segmentation scheme offers the best logical advantages, but acknowledges that it also has many implementation problems.

Chapter 3 examines the addressing hardware currently used in computer systems, and describes the common building blocks. These blocks are then used later in the thesis to implement a new addressing model.

Chapter 4 examines an addressing model based on the segmentation scheme, called capability based addressing, and shows how it solves some of the shortcomings of conventional architectures. The problems associated with the implementation are also discussed in detail.

Chapter 5 describes a new addressing model which is based on the capability addressing scheme, but which solves the outstanding problems and provides a flexible and uniform hardware addressing mechanism. A major design consideration is that the addressing hardware should not only be able to implement the MONADS software structures, but should be flexible enough to implement those of other capability based processors.

Chapter 6 examines the ways in which the new addressing model could be implemented, and shows that many conventional techniques are not suitable. Building a totally new computer is discarded because of lack of time and money, and other interpretive techniques (such as software and firmware implementations) are often too inefficient. The chapter then describes a general model for enhancing primitive computer architectures, and demonstrates some of the enhancements which are possible.

Chapter 7 describes the MONADS II computer system, and demonstrates the practically of the two new models proposed in this thesis.

Chapter 8 concludes the thesis, commenting on the relevance of this research and suggesting additional work which might be undertaken.

- 5 -

#### 2. Conventional Memory Organizations

This chapter examines the conventional memory management models used in many computer systems. First, we consider the types of requests which a memory system must be able to satisfy. These requests come from a number of different types of software. Second, we describe the conventional memory management models used in many current computer systems. These models can then be examined in terms of the different software requests, exposing the advantages and disadvantages of each scheme.

#### 2.1. Software Environment

From the viewpoint of the information storage system of a processor, memory demands come from three classes of software: user programs, the operating system and compilers.

#### 2.1.1. User Programs

User programs are designed to perform some task on behalf of a user. They require the information store to possess a number of attributes, namely:

- The store must be able to save and retrieve both high speed computational data (e.g. program variables) and permanent data (e.g. file data).

- User programs which share the central processor must be protected from corrupting data belonging to other users.

- User programs should be protected from corrupting their own code and read-only data.

- User programs should be able to share certain data with other users. This allows processes to cooperate with each other in performing one task.

- The information storage, sharing and protection system should be simple to use.

- The information storage system should be efficient in space and time.

- The store should be large enough to hold all computational and permanent data.

- The store should allow dynamic memory allocation for dynamic data structures.

A user program demands a number of functions from the memory system, and is not concerned with the way that the requests are implemented. As we shall see when we examine the various conventional memory management models in use, some of these basic requirements are not well supported.

## 2.1.2. The Operating System

The operating system has the task of controlling all the user programs which execute on the processor. With respect to the information storage system, the operating system must:

- allocate memory when a user program is loaded, or requires more memory;

- deallocate memory when a user program terminates, or releases memory;

- control the protection system;

- control the sharing system;

- control any address modification hardware;

- be able to share code modules between users, in order to save space (this form of sharing, unlike data sharing, is not visible to the user program).

Unlike user programs, which only use the memory, the operating system must also manage and control the memory system. These requirements demand that the memory system is easy to manage and control. Again, not all of these are well supported in conventional

- 7 -

memory management schemes.

#### 2.1.3. Compilers

Compilers are affected by the memory system in two respects. First, most compilers execute as a normal program (although they may have some extra privileges) on behalf of a user, and thus have the same needs as a Second, they are used to translate user programs from user program. high level languages into the machine code of the processor, and are expected to understand how to address memory. The main requirement that the compilers make on the memory system is that the addressing, sharing and protection systems are simple to use. This means that the code is easy to generate, and the compiler code generator is simple in design. The memory system should be able to represent and address the logical structures of a program, e.g. arrays and subroutines, rather than requiring the compiler to translate them into units which are meaningful to the memory.

## 2.2. Conventional Memory Management Systems

This section describes a number of conventional memory management models used for addressing the main, or computational, memory of a processor. Most conventional computer systems also use a secondary memory (such as a disk or drum) to hold permanent data. Whilst some also use the secondary store as part of their main memory storage system (as in virtual memory systems), the mechanisms for addressing secondary memory are not considered, because they only affect the operating system software, rather than the addressing hardware.

## 2.2.1. Linear Memories

The earliest memory management model used was the 'linear memory' model. In this scheme the main memory of a processor is viewed as a set of linearly arranged addressable storage locations, and each word (or location) of memory is accessed by supplying an address. These absolute addresses may be manipulated by a user program in order to access various data items. The way that linear memories are used varies depending on how many concurrent users the system must support.

## 2.2.1.1. Single User Systems

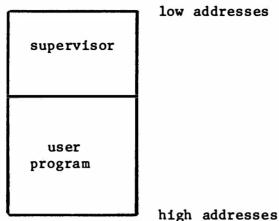

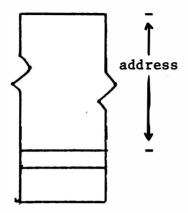

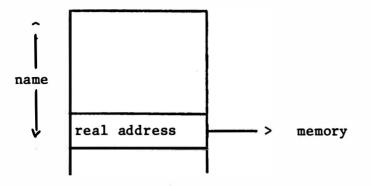

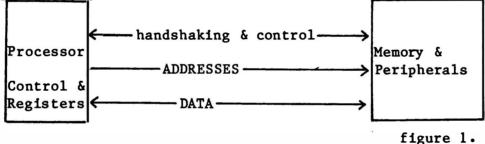

In the earliest computer systems, the central processor was allocated to a particular user when a job commenced, and was only relinquished when that job had terminated. In such systems, the program and associated computational data is loaded into the linear memory, and execution begins at the start of a program. The sequencing, loading and unloading of jobs is controlled by a supervisor program, which is loaded into the bottom of the memory. (In very early computer systems the supervisor was only capable of loading binary program tapes into memory.) User programs are then loaded into the memory above the supervisor. The 'linear memory' scheme, shown in Figure 2.1, has the advantage that it is simple. It also has a number of disadvantages. First, no program can be larger than the size of the main memory (although some systems use a manual overlaying scheme). Second, if a program starts a slow autonomous operation, such as an input-output transfer, the processor must remain idle until the transfer is completed. Third, there is no way of protecting the supervisor program from being corrupted by the user program. This problem was resolved by introducing a 'fence register' into the processor, which is loaded with the highest address of the monitor program. By preventing the user program from writing into memory below that address the supervisor can be protected. Fourth, because the supervisor program resides at the bottom of the memory, the user program no longer resides at address zero. Consequently, the start address, and the addresses of a11 variables and labels, must be adjusted so that the program begins at the top of the supervisor. This operation is called static relocation and can be quite expensive. The linear memory scheme has been used in many o'd single user systems, such as the HP2100A (Hewlett Packard, 1972).

## 2.2.1.2. Multi-user Systems

The linear addressing model can also support a multi-user environment. In this case the central processor is shared amongst many different user programs. Each program receives a slice of processor time, and is suspended either when the time slice expires or an input output transfer is started. Multi-user systems are able to use the processor more efficiently, because it is used to execute another job while other users are suspended, rather than being left idle.

#### CHAPTER 2

- 9 -

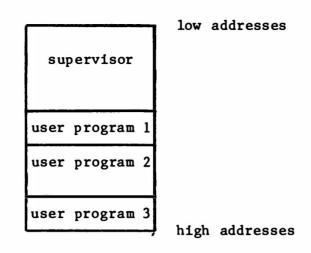

Figure 2.1 - a single user linear memory

The problem with constantly swapping the executing program is how allocate the main memory. Two main solutions have been used. First, to the entire memory is allocated to a program when it enters its time ' slice. All of the program code and data is loaded into memory (from a secondary storage device). When the time slice is over, the memory image is copied back into secondary memory, and the next program is loaded. This method has a number of disadvantages. While it may utilize the central processor better than in the single user system, the memory may still be under-utilized. A small program still uses the entire user area of main memory, wasting the rest of the space. Also, the time spent swapping code and data in and out of main memory is excessive, during which time the processor cannot be used. To avoid the load and unload operations every time slice, a second memory allocation scheme can be used, as shown in Figure 2.2. In this method all, or many, of the current programs are loaded into memory, each packed into the available space. When a program enters its time slice, the old register values are reloaded and the program is restarted. At the end of the time slice, the register values are saved and another program is restarted. This scheme avoids copying the code and data for a program into memory before it can be executed, and is thus much more efficient than the first solution. It also has a number of problems. First, because programs contain absolute addresses the code must be statically relocated before it can be loaded. In a single user system once the code has been relocated, it can be used repeatedly. However, in a multi-user system, the code must always be

Figure 2.2 - a linear memory multi user system

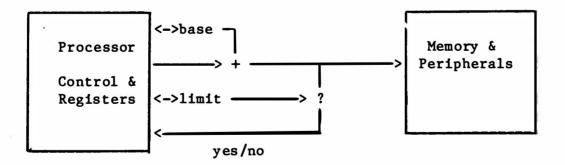

relocated before it is loaded, as its position may change each time the program is executed. This operation is expensive. Second, the simple fence register scheme cannot protect programs from corruption. A more elaborate protection scheme places a base register at the lowest address of a program, and a limit register at the top of the program. Addresses can then be restricted to a particular addressing region. Third, as programs are loaded and unloaded, the memory may become fragmented. This 'external fragmentation' complicates loading new programs, as insufficient free space may be available to hold an entire program. То simplify the problems of static relocation and memory management, a dynamic relocation scheme was devised.

In the dynamic relocation scheme each program assumes that it is loaded at address zero, and the processor augments each address by the contents of a base register before it reaches the memory. This new address can also be validated against a limit register, thereby protecting other programs from corruption. These dynamic relocation registers also assist with memory management. A statically relocated program cannot be moved in memory once it has been loaded, because it may have absolute addresses in data variables. Thus, if insufficient contiguous space is available, it may be impossible to load a program into memory. Dynamic relocation registers, however, allow a program to be moved; thus the memory may be periodically reorganized. Unfortunately the cost of moving programs in memory is quite high, and it may be more efficient to waste some of the main memory.

Another solution aimed at simplifying the external fragmentation problem is the partitioned scheme, used in the ICL System 4 (ICL, 1971) and some of the IBM 360 range (Belady, Parmelee and Scalzi, 1981). In this scheme the main memory is divided by the operating system into a number of fixed size partitions. When a program is loaded into memory it is placed in a free partition. Because memory is allocated in fixed size units, the task of memory management becomes much simpler, and external Unfortunately internal fragmentation fragmentation is eliminated. occurs, as programs which are smaller than a partition will waste space. Thus, while memory management may be simpler, the fixed partition scheme may waste even more space than a variable space allocation scheme. Also, large programs must be manually overlayed so that they fit in a partition. The effect of internal fragmentation may be diminished by using small partitions; however, this limits the maximum size of a program (unless it is broken down into overlays).

Another problem with the linear memory model is that from the compilers' viewpoint the memory image is totally unstructured. It must allocate space within the address space for all of the data structures and code of a program without any assistance form the memory management system.

## 2.2.1.2.1. Sharing Memory

It is often desirable to share access to areas of memory between user programs. In the swapping scheme sharing is awkward. The supervisor program must allocate an area of shared memory at a reserved address, and as programs are loaded and unloaded this area must remain unaltered. In this way many programs can share access to a statically defined set of data items. In the scheme which loads all programs into memory at the same time, data items may be shared by using the absolute address of the item. This procedure does not work if base and limit registers are used to protect a program, or if dynamic relocation registers are used. Sharing of code is extremely difficult in a linear memory scheme. Because of the problems, very few linear memory computers allow sharing at all.

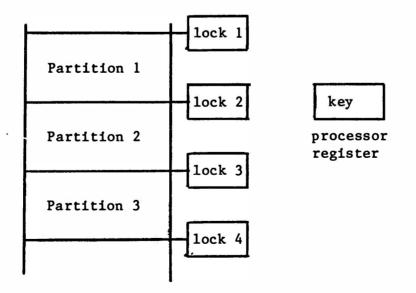

## 2.2.1.2.2. Protection between User Programs

We have already shown that user programs may be protected from corruption by base and limit registers. This scheme has been used in many linear memory computers, such as the ICL1900 series (ICL, 1976). The partition scheme can also provide inter-program protection, as shown in Figure 2.3. In this scheme the hardware recognizes a number of fixed size areas (in the IBM 360 range this was 2k words in size), and associated with each area is a protection lock which holds the identity of the program. (If the partition size chosen by the operating system is larger than the area size recognized by the hardware then a number of protection locks may be assigned to the same partition.) The central processor has a current-protection-key register, which holds the identity of the currently executing program. When a program enters its time slice the current-protection-key register is loaded with the identity of the program. Each time memory is addressed, this value is compared to the protection lock for the area being addressed. If they differ, then a protection violation has occurred, and the program is aborted. Consequently, a program can only address areas which it owns. Whilst it is conceptually possible to dynamically change the values held in the protection locks to facilitate controlled sharing, this has not been implemented. Thus, it is very difficult to share memory between

Figure 2.3 - the protection key system

programs. None of the protection systems discussed protect a program from corrupting its own code. Most of these schemes make the sharing of memory extremely difficult.

## <u>2.2.2</u>. <u>Paged Virtual Memories</u>

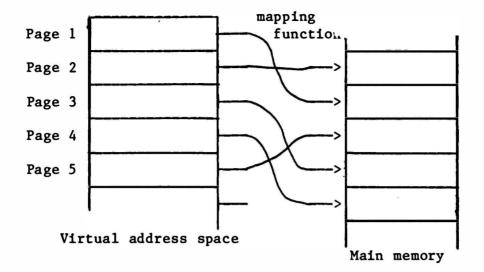

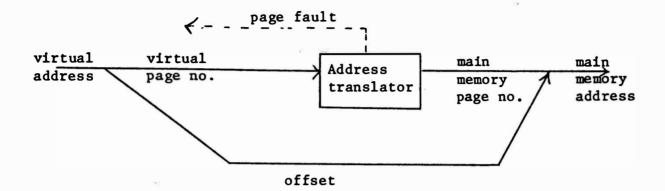

The concept of a paged virtual memory was first proposed and implemented by the Atlas design team in the late 1950s (Fotheringham, 1961; Kilburn, Edwards, Lanigan and Sumner, 1962). The scheme consists of detaching the logical view of memory as seen by a program from the physical organization of the main memory. The logical memory, or virtual memory, is mapped onto the main memory by a mapping function. The implementation of this addressing structure requires that both the virtual and physical memories are divided into a number of fixed size pages. Consequently, an address (either virtual or physical) consists of two portions, a page number field and a within page displacement field, as shown in Figure 2.4. A mapping unit can then map pages of virtual memory onto pages of physical memory as shown in Figure 2.5. The within page displacement from the virtual address is used as a within page displacement for the physical page.

The paged scheme has a number of general advantages. First, the type of reference applied to a page of virtual memory may be controlled. Associated with each page of virtual memory may be some access rights, which determine whether the page may be read from, written into, or executed as code. With this information, the processor can monitor every memory reference and report addressing errors. Unlike a linear memory, the paged memory organization can protect a user program from modifying its own code, and pages of constants can be protected from being modified. Second, a contiguous area of virtual memory need not be allocated contiguously in main memory. The mapping function can map

displacement page number

Figure 2.4 - a paged virtual address

Figure 2.5 - a paged virtual memory

pages of virtual memory arbitrarily onto main memory, allowing large contiguous areas of virtual memory to be created. This makes memory management easier and eliminates the external fragmentation experienced in the linear memory scheme. Third, the virtual space may be larger than the physical space. Any pages of virtual memory which are not mapped onto a page of physical memory can be tagged absent. A reference to these pages causes an addressing error, called a page fault, which is similar to an access rights violation. Because the virtual address space may be very large, programs larger than the main memory may be loaded. If an absent page of virtual memory is addressed, a supervisor program may fetch a copy of the page required from secondary memory, find a free page in main memory, place it in main memory, and update the mapping function. When the reference is attempted again, the processor will address the correct page of physical memory. This operation is called demand paging, as pages are only fetched into main memory on demand. Some systems have experimented with prepaging, i.e. attempting to fetch pages before they are required. Unfortunately, it is very difficult to determine the access patterns of a program, and because the overheads of moving unneeded pages into main memory are high, prepaging is not commonly used. Fourth, as we will see shortly, user programs may be protected from interference from each other.

The paged scheme also has some disadvantages. Because memory is allocated in fixed size units, some space will be wasted in the last page of the virtual address space. This internal fragmentation is the same problem experienced in the partitioned linear memory. We shall examine some more serious disadvantages later, in terms of the logical properties of pages.

## 2.2.2.1. Single User Systems

In a single user system, the program executing on the processor is loaded into the virtual address space. To the user program, the memory appears to be linearly arranged. However, unlike the linear memory model, the pages may be allocated randomly from main memory. In addition, pages may be protected from inadvertent corruption. When the program terminates, the virtual address space can be loaded with a new user program.

## 2.2.2.2. Multi-user Systems

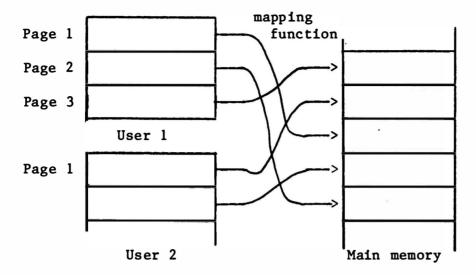

Most paged computers support a multi-user facility by creating a number of virtual address spaces. Each user program is loaded into a different address space and the main memory is composed of pages of many different programs. Each of the virtual spaces is then mapped onto the main memory by its own mapping function, as shown in Figure 2.6. When a program enters its time slice, the appropriate mapping function is selected so the program can only address its own pages. When the time slice is over, a new mapping function is selected. This arrangement is similar to the swapping technique used in the linear memory scheme. However, only the mapping function is altered after each time slice (which can be performed very quickly), rather than copying each address space to and from secondary memory. The demand paging system allows a program to load its pages into main memory as they are required.

## 2.2.2.3. Address Translation

So far we have assumed a mapping function between virtual addresses and physical addresses, without considering how this function can be implemented. This translation operation is performed each time the processor accesses memory. The virtual address may either be translated into a main memory address, in which case the reference can proceed, or

Virtual address spaces

Figure 2.6 - a paged multi-user system

a secondary memory address, in which case the page is fetched into main memory. The implementation of the mapping function depends on the size of the virtual memory and the size of the main memory, and four categories can be identified: small virtual address spaces, small main memories, large virtual address spaces with large main memories and very large virtual address spaces. These categories will be examined again in the next chapter, which deals with the hardware necessary to translate addresses. Here we briefly consider the implementation of these different categories from the view of the operating system software.

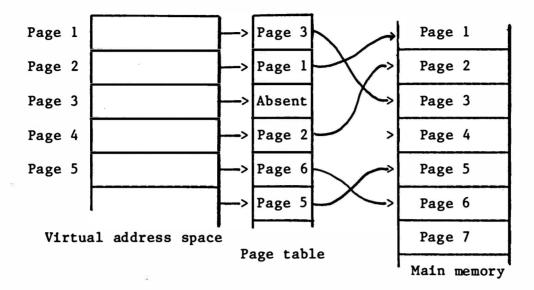

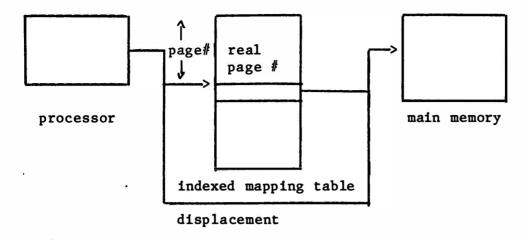

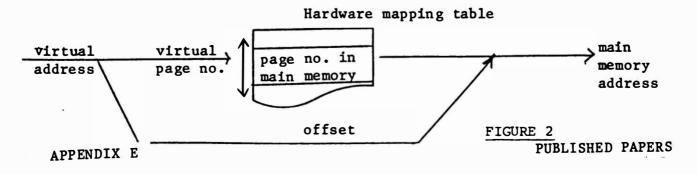

#### 2.2.2.3.1. Small Virtual Address Spaces

When the virtual address space is comparatively small the virtual page numbers can be translated into physical page numbers by a directly indexed table held in main memory, as shown in Figure 2.7. The virtual page number is used as an index to a page table entry. The page table entry contains the physical page number, the access rights for the page, and an absent/present flag, which is set if the page is present in main memory. If the page is not present, then the physical page number field can be used to hold the secondary memory address of the page. When this table is small enough, it may be held in a special address translation memory, rather than in main memory, and this is discussed in more detail

Figure 2.7 - a small virtual address space

in the next chapter. The size of the main memory has little effect on the size of the mapping table, and only influences the width of each page table entry. The size of the virtual memory affects the length of the table, and the scheme is thus only viable for small virtual address spaces.

In a single user system only one page table is required. In a multi-user system, a page table is required for each virtual address space. A register is often used to hold the address of the current page table. When a user program enters its time slice, this register can be modified to point to the new page table, thus changing the mapping function. Similar address translation schemes have been successfully used in processors such as the HP21MX (Hewlett Packard, 1974), Data General Eclipse (Data General, 1974).

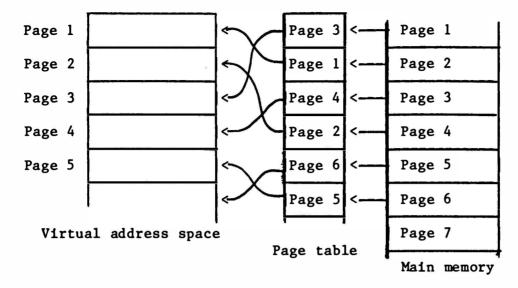

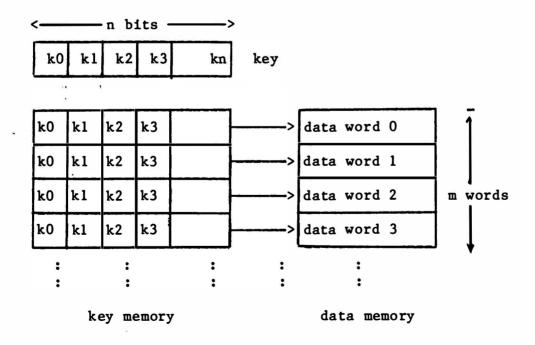

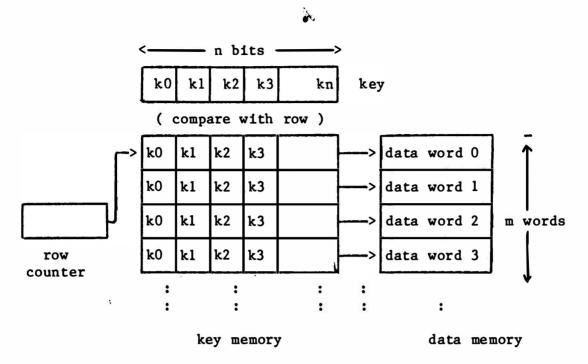

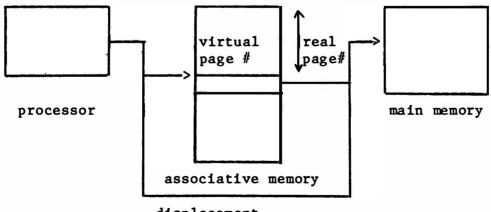

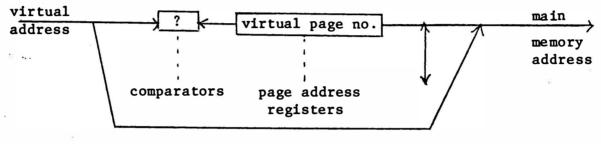

## 2.2.2.3.2. Small Physical Memories

If the main memory has a limited number of pages, a different translation technique can be used. Rather than indexing the page table on virtual page number, this method uses the main memory page number as an index value, as shown in Figure 2.8. Each page table entry contains a virtual page number, some access rights and an invalid flag. When a virtual address is translated into a main memory address, the page table

Figure 2.8 - a small main memory

is searched associatively for the virtual page number. If found, the index value of the page table entry is used as the main memory page number. If not found, then the virtual page is not present in main memory, and is fetched from secondary memory. If a page of main memory is not mapped to a page of virtual memory, then the invalid flag must be set. Special hardware is required to search the page table, and this is described in Chapter 3. This technique is sensitive to the size of the main memory, as this affects the length of the page table, and is only used when the main memory is small. In a single user system there is only one page table. Those pages of main memory which do not pertain to a user program, must have their page table entries flagged invalid.

# 2.2.2.3.3. Large Virtual Address Spaces

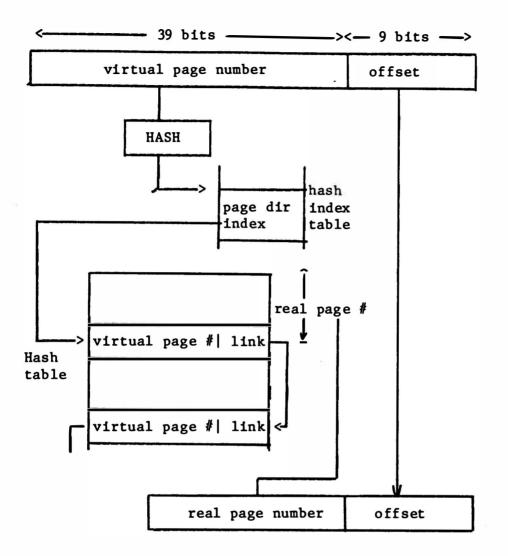

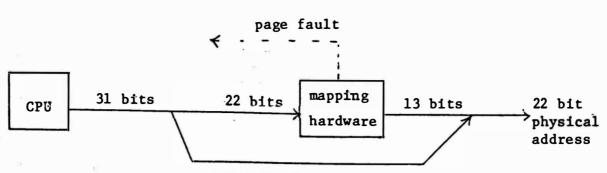

When both the virtual address space and the main memory become large the techniques discussed above become infeasible. A large virtual address space makes the directly indexed page tables too large to be placed permanently in main memory, or in a special hardware table. Similarly, because of poor hardware an associative search becomes difficult. (In the next chapter we will examine some associative schemes which are effective.) One solution places directly indexed tables in main memory (which can be addressed by a special processor register), and swaps them between memory and disk as they are required. In some systems the page tables may be placed in virtual memory themselves, as in the VAX 11/780 computer (Digital Equipment Corp., 1979), and the paging mechanism can be used to address the page tables. Consequently, the page tables are mapped onto main memory by page tables, which may then be small enough to place permanently in main memory. When an address is translated, the virtual page number is used to form a virtual address of a page table entry. This virtual address is then translated into a main memory address by the page table for the page tables. At any stage, either of these translations may cause a page fault, i.e. the page table entry is not present in main memory at the time. Each address translation may cause a number of page faults to be generated. Further page faults may be generated when a page is removed from main memory (possibly to find room for a page which has already caused a fault), as the present/absent bit must be updated in the page table entry. To prevent an endless loop of page faults, this scheme must always have a pool of free pages. In this way a page may be brought into memory without having to remove another page, and thus cause further page faults. The scheme requires special hardware to assist in address translation, and this is discussed in the next chapter.

#### 2.2.2.3.4. Very large virtual address spaces

This class of virtual memory is typically used to hold file data as well as computational data. The only processor which has attempted this operation (namely MULTICS (Organick, 1972)) did not use a very large virtual address, and could use normal page tables. In this class of address space the page tables would certainly be placed in virtual memory, and would be very large indeed. Consequently it requires special hardware to translate addresses. Such hardware is discussed in Chapters 3, 4 and 7.

# 2.2.2.4. Protection

A paged virtual memory offers a multi-user system a number of levels of protection. First, programs are protected from corruption by each other. Because each program is loaded into its own virtual address space, and has its own mapping function, it is impossible for a program to inadvertently address the pages of another. Second, a program may be prevented from corrupting pages of code, or non-modifiable data. In this way a program is partially protected from itself. Third, the operatingsystem (or supervisor program) is treated as another user program, and is loaded into its own address space. Thus, fence register schemes are not needed to protect the operating system from corruption.

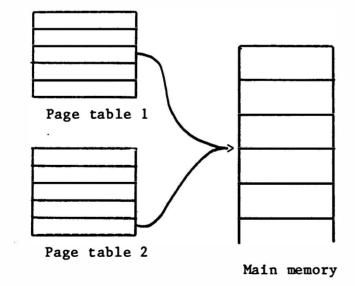

# 2.2.2.5. Sharing

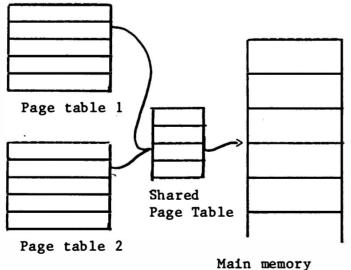

Whilst enforcing an effective protection mechanism, a paged memory scheme also allows controlled sharing of data and code. The page table structure allows a page of main memory to appear in more than one virtual address space, as shown in Figure 2.9. Moreover, each address space can have different access rights for the page. Thus, one program may be allowed to read from a shared page, whilst another may be allowed to read from and write to the page.

Because the operation of removing a page from main memory may become complicated by the need to locate and update all page table entries which refer to it, a variation of this sharing scheme may be used. To simplify this problem, some systems maintain an additional table, located between the page table entries and the main memory, as shown in Figure 2.10. Each page table entry which addresses a shared

Figure 2.9 - shared pages

page contains an index into the additional table. This table entry then contains the main memory page number. If the page is banished from memory, only one entry needs to be adjusted.

### 2.2.2.6. Memory Allocation

Memory allocation in the paged scheme is much simpler than in the linear model. Because memory is allocated in fixed size units, there will always be an area of the correct size available when space is required, even if some other pages must be removed from main memory.

# 2.2.2.6.1. Page Replacement

When a page is brought into main memory from secondary memory, it is often first necessary to remove another page. The choice of which page to remove may have a significant effect on the efficiency of the computer system, i.e. if the wrong page is discarded then it may need to be fetched again soon afterwards, leading to an inefficient situation known as 'thrashing'. Many different discard algorithms have been devised (Denning, 1970), the most common being Random, First In First Out (FIFO), Least Recently Used, Atlas Loop Detection (Kilburn, Edwards, Lanigan and Sumner, 1962) and Working Sets (Denning, 1968, 1980); these often require hardware assistance (Morris, 1972) and will not be

Figure 2.10 - shared pages

discussed further.

### 2.2.2.6.2. Internal Fragmentation

Because memory is allocated in fixed size units, namely pages, each address space will totally occupy an integral number of pages, and only partly occupy the last page of the address space. Consequently, each address space will waste, on average, half a page of memory. This internal fragmentation is also experienced in the partitioned linear memory, and is a major disadvantage of the paged memory scheme. It has been shown that a significant proportion of memory may be wasted from internal fragmentation (Randell, 1969).

# 2.2.3. Segmented Memory Schemes

The segmented memory scheme is similar to the paged memory model. Both map a logical view of memory onto the main memory of the processor, and both allow information to be protected and shared amongst users. However, pages are an inappropriate unit of protection and sharing as many unrelated structures may be placed in the same page. Also, the compiler must place the logical structures of a program into the pages of a linear address space, which both hides the logical structure of programs from the architecture and requires more address calculation by the compiler. To avoid these problems the segmented scheme divides the virtual memory into a number of variable length segments, instead of fixed length pages. Each logical component of a program, such as a code data array, and scalar variable, is loaded into a segment of procedure, memory, rather than being arbitrarily decomposed into fixed length pages. Each segment is protected by a set of access rights, in the same way as pages may be protected.

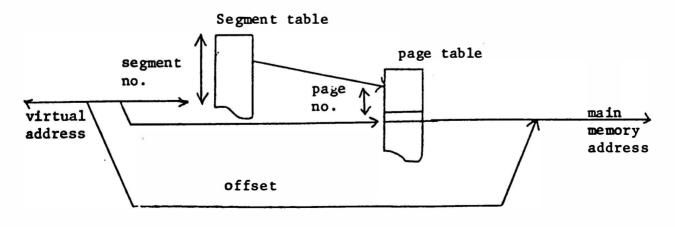

Each process has access to a set of segments. Typically, a segmented address consists of a segment number (which is usually numbered relative to the segments of a program or process) and an offset within the segment. This address, as shown in Figure 2.11, is then translated into a main memory address before the reference can proceed.

### 2.2.3.1. Address Translation

For each segment address, the main memory base address of the segment, and the size of the segment must be determined. Also, to allow

| segment number                                                                                                  | displacement |

|-----------------------------------------------------------------------------------------------------------------|--------------|

| the second se |              |

Figure 2.11 - a segmented address

segments to be removed from main memory and fetched on demand (in the same way as demand paging) it must be possible to flag a segment as absent from main memory, and to supply its secondary memory address instead. There are two common methods of address translation, segment lists and tagged absolute descriptors.

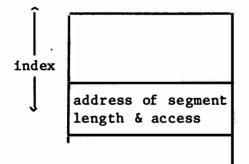

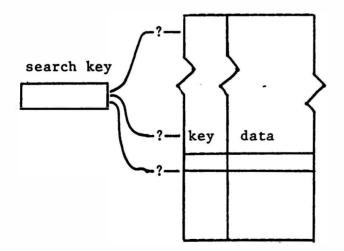

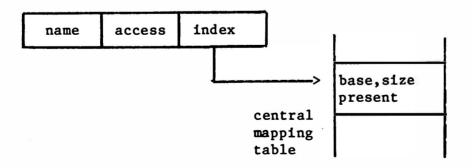

# 2.2.3.1.1. Segment Lists

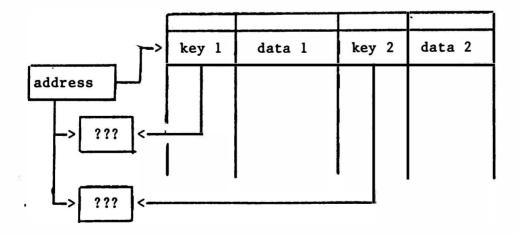

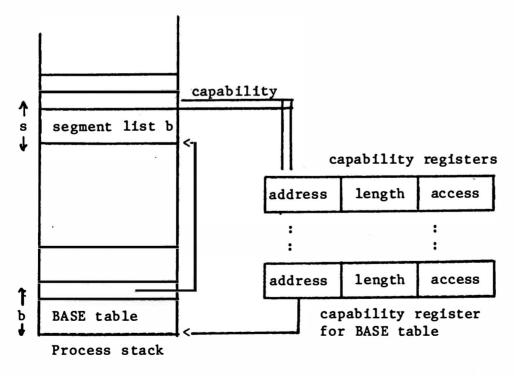

In this scheme, each process has access to a list of segments, as shown in Figure 2.12. Memory reference instructions can address segments by supplying a segment number relative to the process (i.e. starting at zero) and a within segment offset. The segment number, which forms an index into the process segment list, must then be translated into a main memory base address. Contained in each entry of the segment list is the main memory base address of the segment, the size of the segment (or the main memory limit address), a set of access rights and a present/absent flag. The word in memory address is calculated by adding the base address to the offset.

Figure 2.12 - a segment list

The current segment list is usually held in main memory, and may be located by a special processor register, in much the same way as a page table. The segment list is protected from corruption by the user program in the same way as other segments may be protected, as we will see later.

# 2.2.3.1.2. Tagged Descriptors

An alternative address translation system is the tagged absolute descriptor mechanism, as used in the B6700 family of computers (Organick, 1973). In this scheme, each segment descriptor, consisting of main memory base address, segment size, access rights and а present/absent flag, is placed in the data area of a process, e.g. the process stack, and is possibly intermixed with program variables. These descriptors are then used as pointers to segments. A segment cannot be addressed without the correct descriptor. So that descriptors cannot be modified, and used to address other segments of memory, it is possible to protect them by using tag bits (Feustal, 1972; Myers, 1978a, 1978b). Each word of main memory has a tag field attached to it. A word which is tagged as a descriptor cannot be modified by a normal user program. (Although the B6700 hardware allows a program to modify descriptors, the compilers prevent high level language programs from changing them.) The tags are also used for detecting the difference between integer variables, character variables etc. Absolute descriptors have the disadvantage that they are not always easy to find when they must be updated (e.g. if a segment is removed from memory, the segment address and present flag must be updated). An illustration can be found in the B6700 computer, which provides a special instruction for finding all descriptors for a particular segment. This process is not only time consuming, but also means that the stack segments can never be removed from main memory, as they may hold active descriptors. Segment list entries, unlike descriptors, are always held in a well known place and can be easily found.

# 2.2.3.2. Memory Allocation

In the paged memory scheme, memory is allocated in fixed size units. Consequently, memory allocation is relatively easy. When space is required, a page frame must be found in main memory which, in the worst case, may mean that another page may need to be removed from memory. In the segmentation scheme, each segment is of a different size, and must occupy a contiguous area of main memory. Moreover, it must either be totally loaded into memory, or totally absent. This may mean that a large segment cannot ever be loaded into memory because there is not enough space. (The B6700 uses a modified segmentation scheme and allows very large segments to be divided into a number of 'pages'. This will be discussed later). A number of allocation policies have been used to try and allocate space in the most efficient manner such as Best Fit, First Fit and the Buddy system (Knuth, 1978). Often these policies are augmented by a compaction scheme, in an attempt to waste as little main memory as possible. Compaction can also be used when no particular allocation policy is used. Space is simply used up sequentially until there is none left, and then the memory space is compacted.

# 2.2.3.2.1. Compaction

Often the main memory may undergo some data compaction to try to remove areas which are too small to be of any use. During this time, all the processes executing on the processor are stopped, and a special operating system routine packs all the segments together. This scheme has two important drawbacks. First, the compaction operation is expensive in time. It must be performed by the central processor, during which time no other process can run. Second, all the segment table entries must be updated to reflect the new segment addresses. While this operation is possible, it also is extremely expensive. Moreover, if the B6700 type of absolute descriptors are used, these must also be updated. Unfortunately, such descriptors are very difficult to locate, as they may be mixed with data variables.

# 2.2.3.2.2. External Fragmentation

Regardless of the allocation policy, unless memory compaction is used frequently (which would be far too expensive) a large amount of memory space will be wasted, because very few areas will be exactly the same size as the segments. This is called external fragmentation, and is also experienced in the linear memory model in which memory is allocated in variable size units. It has been shown that this space loss can add up to a significant proportion of the available main memory space (Randell, 1969). External fragmentation is, however, often less serious than the internal fragmentation found in paged memories.

# 2.2.3.2.3. Segment Replacement

If sufficient space in main memory cannot be found for a segment, an already loaded segment may need to be removed. This operation is similar to the removing a page from a paged main memory. It is possible to apply the same kind of algorithms used in the paged model, such as Random, Least Recently Used, etc. However, in the segmented scheme the segment which is removed from memory must leave sufficient space to hold the new segment. Consequently, algorithms such as Least Recently Used can only be applied to those segments which are large enough (or to groups of contiguous segments).

# 2.2.3.2.4. Dynamic Segments

One form of segment which complicates the task of memory management is the dynamic segment. These segments are initially allocated a fixed amount of space, like all other segments. However, during the lifetime the segment it may grow in size. Examples of such segments include of stacks, queues, lists and heaps. Space for dynamic segments may be allocated in two ways. First, extra space may be found contiguously in main memory, which may mean that a segment must be removed. Unfortunately, this may not always be possible. Second, the segment may need to be copied from its current place in memory, to a new contiguous area large enough to hold the entire segment. This is an expensive operation, and is avoided if possible. If the data structure has embedded link pointers, such as in a heap, and if the pointers are absolute memory addresses, then contiguous space need not be allocated. However, this organization is impractical because it complicates memory management significantly, as these pointers must be updated when the memory is rearranged.

# 2.2.3.3. Protection

Because it is impossible for user programs to modify segments which are not addressed by the process segment list, users may be protected from corruption by other users. To ensure that the segment list entries only point to the correct segments, the list itself (and any descriptor) is protected from being modified by a user program. Also, a program can be protected from inadvertently modifying its own code or constant data by setting the access rights for each segment to prevent modification. In the paging model information is randomly packed into pages of memory. Because there is no logical link between the access rights of objects in a page and the access rights of a page (unless this has been specifically arranged by the compiler), pages form the wrong unit of protection. Segments, however, are used to represent logical objects, and thus form the correct unit of protection. They also form the best unit of sharing.

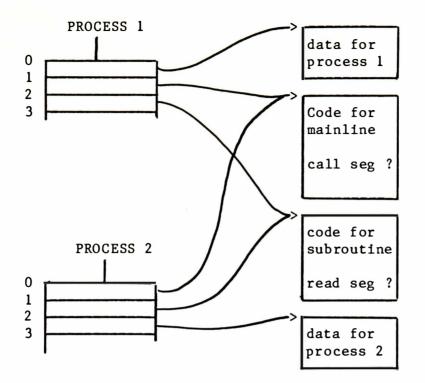

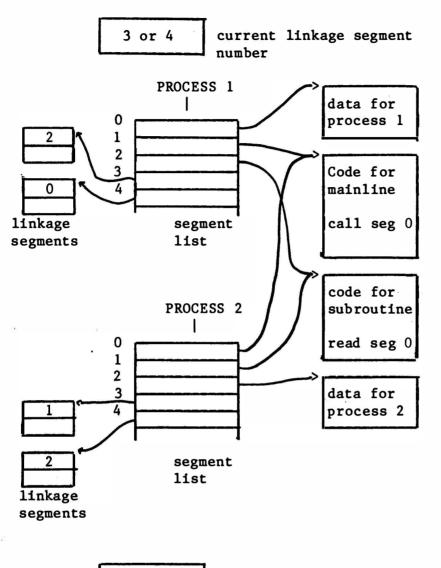

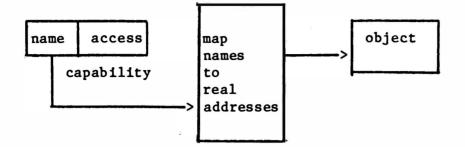

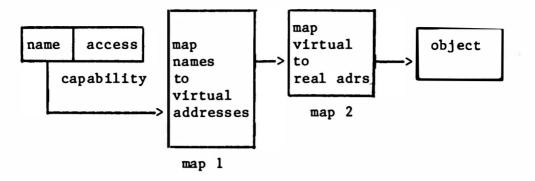

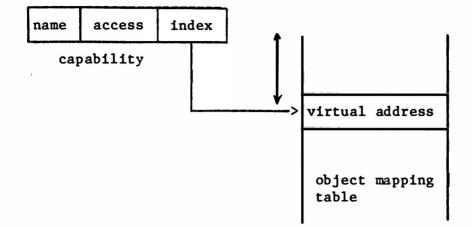

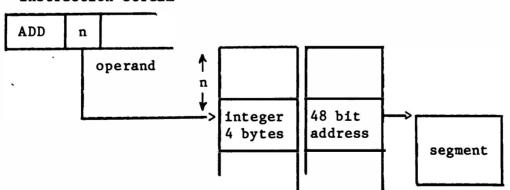

# 2.2.3.4. Sharing

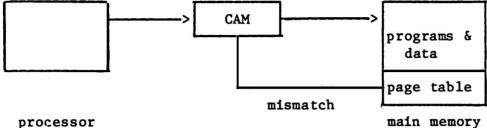

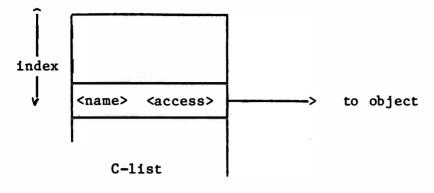

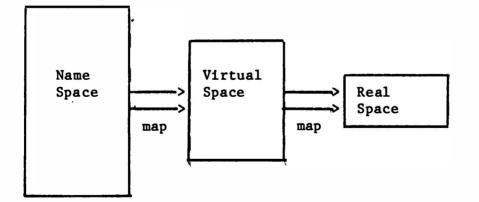

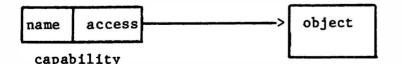

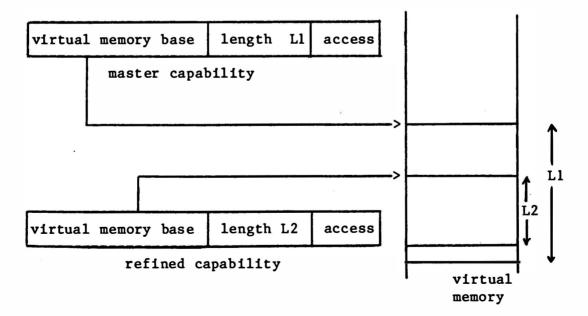

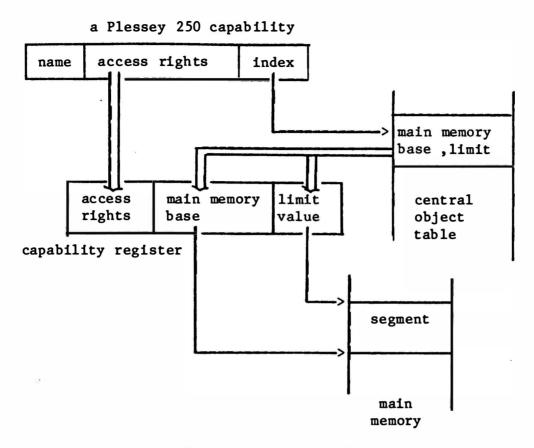

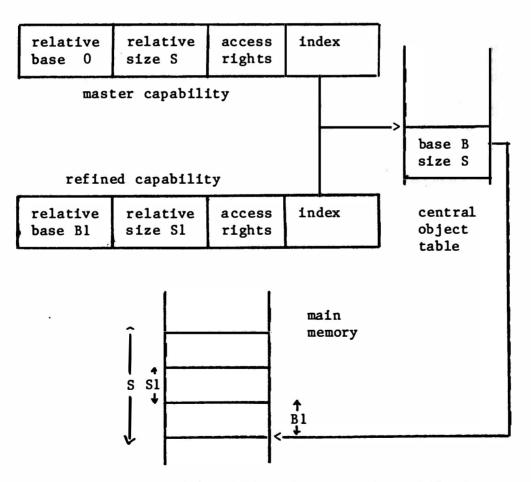

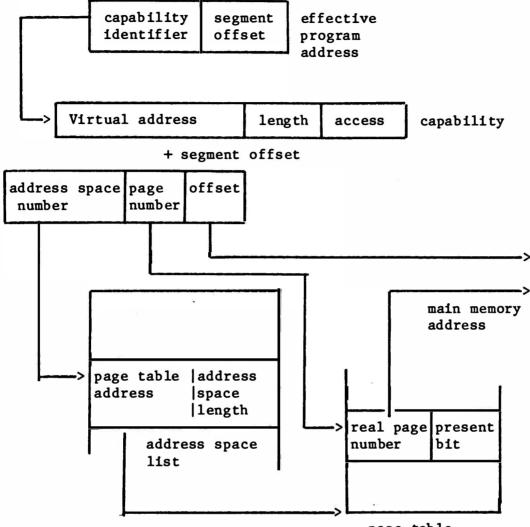

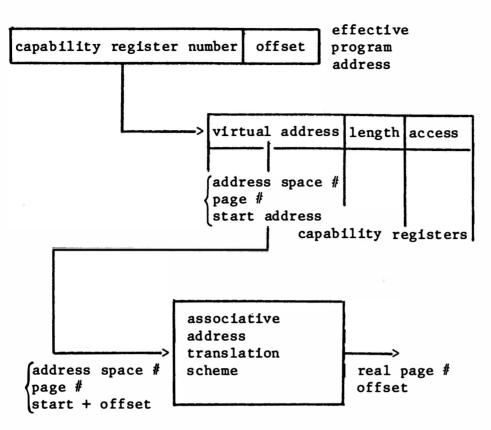

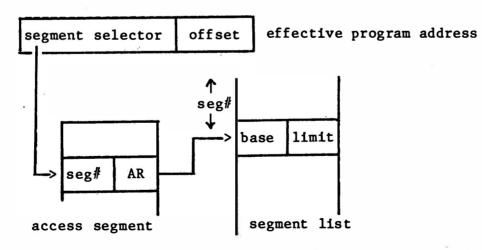

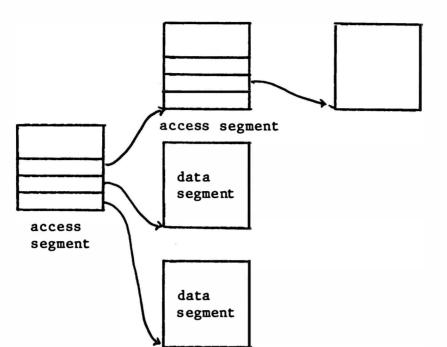

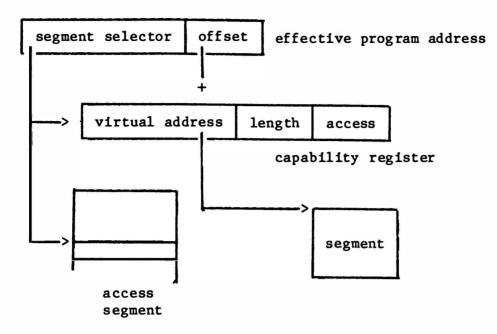

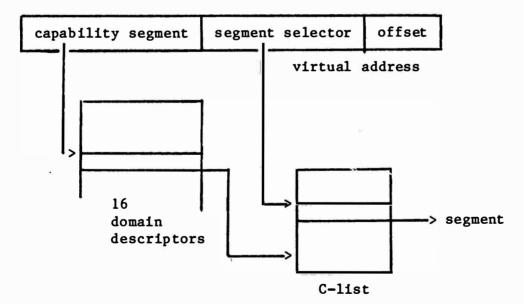

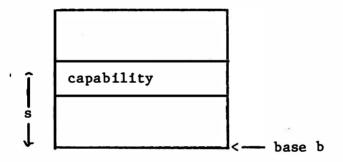

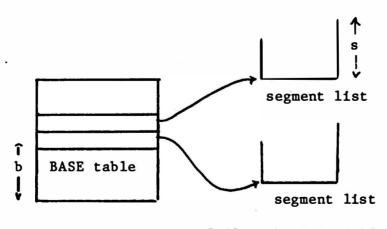

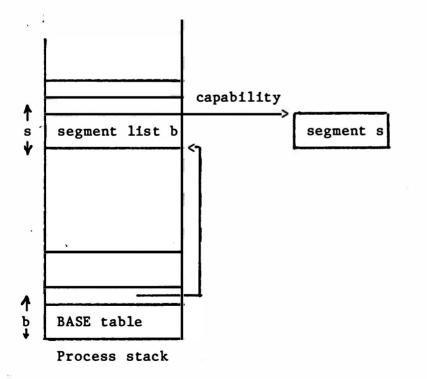

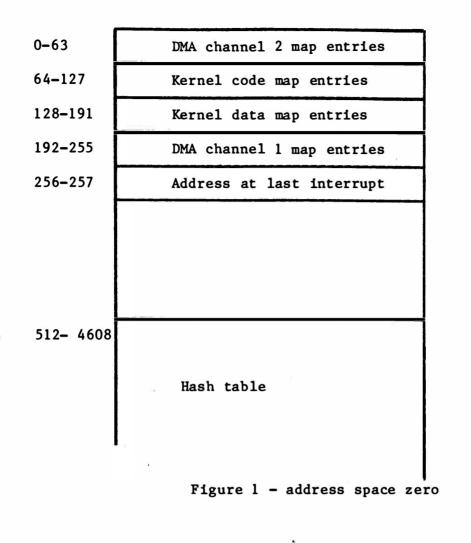

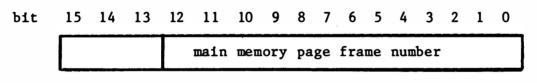

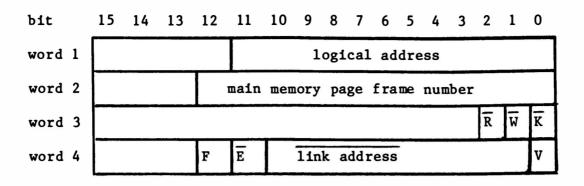

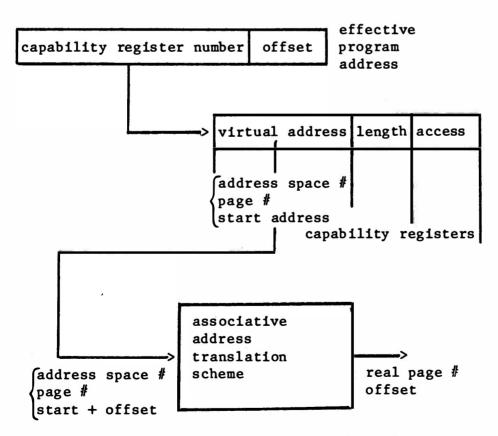

An important feature of the segmentation scheme is that many users may share access to a single segment. Again, unlike pages, segments are used to hold individual objects. Two users may wish to share access to an object, such as an array, but may not wish to share all of the objects held in a page of memory, unless the page holds only one object. A number of different schemes have been devised which allow programs to share segments. The simplest implementation is achieved by loading the same memory base and limit addresses into more than one segment list. Thus, any process with the same segment list entry will automatically address the correct segment, regardless of the segment number chosen. Furthermore, each segment list entry may use different access rights to address the segment. This simple implementation causes two problems when a code procedure is shared amongst a number of user processes, and is illustrated by the example shown in Figure 2.13 (Fabry, 1974), where the code addresses a shared subroutine and a process-own data segment.