### University of Nebraska - Lincoln Digital Commons@University of Nebraska - Lincoln

**CSE Journal Articles**

Computer Science and Engineering, Department of

1982

## Fault Coverage Requirement in Production Testing of LSI Circuits

Vishwani D. Agrawal Bell Laboratories, Murray Hill, NJ

Sharad C. Seth University of Nebraska - Lincoln, seth@cse.unl.edu

Prathima Agrawal Bell Laboratories, Murray Hill, NJ

Follow this and additional works at: http://digitalcommons.unl.edu/csearticles

Part of the Computer Sciences Commons

Agrawal, Vishwani D.; Seth, Sharad C.; and Agrawal, Prathima, "Fault Coverage Requirement in Production Testing of LSI Circuits" (1982). CSE Journal Articles. 39.

http://digitalcommons.unl.edu/csearticles/39

This Article is brought to you for free and open access by the Computer Science and Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in CSE Journal Articles by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

# Fault Coverage Requirement in Production Testing of LSI Circuits

VISHWANI D. AGRAWAL, SENIOR MEMBER, IEEE, SHARAD C. SETH, MEMBER, IEEE, AND PRATHIMA AGRAWAL, MEMBER, IEEE

Abstract—A technique is described for evaluating the effectiveness of production tests for large scale integrated (LSI) circuit chips. It is based on a model for the distribution of faults on a chip. The model requires two parameters, the average number  $(n_0)$  of faults on a faulty chip and the yield (y) of good chips. It is assumed that the yield either is known or can be calculated from the available formulas. The other parameter,  $n_0$ , is determined from an experimental procedure. Once the model is fully characterized, it allows calculation of the field reject rate as a function of the fault coverage. The technique implicitly takes into account such variables as fault simulator characteristics, the feature size, and the manufacturing environment. An actual LSI circuit is used as an example.

#### I. Introduction

THE reasons for the practical impossibility of obtaining a complete functional test for a large scale integrated (LSI) circuit may be found among the following attributes: 1) imperfect fault modeling: an actual fault may not correspond to a modeled fault or vice versa [1]; 2) data dependency of faults: it may not be enough to exercise all the functions on a chip since execution of certain functions may be sensitive to data or, worse, to data sequences [2, p. 46]; 3) testability limitations: some LSI circuits may be harder to test because of the pin limitation resulting in the lack of direct access to subcircuits. Thus, if the circuit passes the test, one still cannot guarantee that it is free from faults.

Test designers consider fault coverage as a measure of a test's capability to isolate a faulty circuit. Most present-day simulators that are used to determine the fault coverage can simulate single logical (line-stuck type) faults but cannot evaluate the coverage of actual physical faults (shorts or breaks in metallization or diffusion runs, shorting of substrate with metallization or diffusion [1], [2]-[4]). Multiple logical faults are also frequent in the production environment, but the exact relationship between single- and multiple-fault coverage is not well understood [5, p. 21]. Also, different simulators may employ different criteria to detect fault-induced races and oscillations.

Detection of some faults may never be possible, or may be quite irrelevant because of redundancies. If a test could be generated for the complete design verification of a circuit, then the faults that are not detected by the test could be ig-

Manuscript received March 2, 1981; revised June 2, 1981.

nored as redundant. Even when only single stuck type faults are targeted, the cost of test development and test application increases very rapidly with an increasing fault coverage requirement.

Since stuck type faults represent only a sample of all possible faults, the coverage of such faults can be regarded as a figure of merit for a test. In this paper we try to answer the question: how is this figure of merit related to the quality of the tested product? It is assumed that the desired value of the stuck-type fault coverage would depend upon the circuit implementation, technology, manufacturing environment, and, of course, the required quality level of the tested product. The method developed is based upon a model of fault distribution on the chip. The parameters of this distribution are determined experimentally by examining an actual production lot of chips. The analysis then gives the value of fault coverage required for a given quality (field reject rate [6]) of the tested chips. A previous attempt in this direction [6] was based upon a more restrictive model for the distribution of faults. It produced satisfactory results for chips with high yield (typically, SSI and MSI), but predicted too pessimistic fault coverage values for larger chips with lower yield. Our analysis is not restricted to any particular type or size of chips and can be applied to all scales of integration.

#### II. DEFINITION OF SYMBOLS

| chip area                                                                                 |

|-------------------------------------------------------------------------------------------|

| defect density                                                                            |

| fault coverage                                                                            |

| number of faults covered by tests                                                         |

| number of faults present on a chip                                                        |

| average number of faults on a defective chip                                              |

| average number of faults on a chip                                                        |

| total number of possible faults on a chip                                                 |

| probability of exactly $n$ faults being present on a chip                                 |

| probability of a chip being found faulty when tested to a fault coverage f                |

| probability of detecting exactly $k$ faults when the chip has $n$ faults present          |

| field reject rate for fault coverage f                                                    |

| yield of chips (probability of a manufactured chip                                        |

| being good)                                                                               |

| probability of a faulty chip being tested as good when the fault coverage of tests is $f$ |

|                                                                                           |

a parameter depending upon the variance of  $D_0$ .

V. D. Agrawal and P. Agrawal are with Bell Laboratories, Murray Hill,

S. C. Seth is with the Department of Computer Science, University of Nebraska, Lincoln, NE 68588.

#### III. THE MODEL

Assume that an integrated circuit chip has n faults. Although there can be several types of faults on the chip, we assume that the faults on the chip are equivalent to n single stuck type of faults. In other words, the faults present on our chip are such that they can be detected by tests that detect n stuck type of faults. We further assume that the yield of good chips is y and that the number of faults n on a faulty chip has a Poisson distribution [7, p. 156]:

prob {number of faults = n}

=

$$p(n) = (1 - y) \frac{(n_0 - 1)^{n-1}}{(n-1)!} e^{-(n_0 - 1)}, \quad n = 1, 2, 3, \cdots$$

$$p(0) = y, \tag{1}$$

where  $n_0$  is the average number <sup>1</sup> of faults on a faulty chip. In the above expression, the Poisson's density function has been shifted to the right by one unit since it is used for the probability of the number of faults on a defective chip, i.e.,  $n \neq 0$ ,  $n = 1, 2, 3, \cdots$ . From (1), the average number of faults is obtained as

$$n_{\text{av}} = \sum_{n=0}^{\infty} n \, p(n) = (1 - y) n_0.$$

(2)

Indeed, the number of terms in the above summation should be equal to the maximum number of faults N. In practice, however, the value of  $n_0$  is much smaller than the maximum number of faults and the use of the infinite sum, which allows a simple result, is numerically quite accurate. The distribution of faults, as given by (1), is characterized by the two parameters y and  $n_0$ .

Furthermore, we assume that the yield y of the chip is known, at least approximately. In fact, the yield of integrated circuits has been widely studied in the past [8]-[14]. The following formula is often used for calculating chip yield [12], [13]:

$$y = (1 + \lambda D_0 A)^{-(1/\lambda)} \tag{3}$$

where [13]

A = chip area

$D_0$  = average number of defects per unit area

and

$D_0^2$   $\lambda$  = variance of  $D_0$ .

The parameters  $D_0$  and  $\lambda$  can be determined either experimentally as described in [11] or from the results on previously manufactured chips that came off the same processing system.

The estimation of the remaining parameter  $n_0$  will be discussed later.

#### IV. FIELD REJECT RATE

Let us assume that the total number of possible faults on a chip is N, where  $N >> n_0$ . We test these chips by the tests that detect m faults. The fault coverage is then f = m/N. Let  $q_k(n)$  be the probability of detecting exactly k faults when a chip has n faults present on it. The,  $q_k(n)$  is given by the hypergeometric density function [7, pp. 43-44]

$$q_k(n) = \frac{\binom{n}{k} \binom{N-n}{m-k}}{\binom{N}{m}}.$$

(4)

The probability of passing the chip, having n faults, as good is

$$q_0(n) = \frac{\binom{N-n}{m}}{\binom{N}{m}} \simeq (1-f)^n \tag{5}$$

where f = m/N is the fault coverage of tests. The above approximation is quite accurate for  $n << \sqrt{N(1-f)/f}$  and it will be used in the following analysis. For larger values of n, a better closed form expression is derived in [15] where the accuracy of (5) is also discussed.

Now, since the number of faults n on a bad chip is a random number, the probability (or yield) of a bad chip being tested as good is given by

$$Y_{bg}(f) = \sum_{n=1}^{N} q_0(n) p(n).$$

(6)

On substituting from (1) and (5), and simplifying, we get

$$Y_{bg}(f) \simeq (1 - f)(1 - y)e^{-(n_0 - 1)f}.$$

(7)

The field reject rate r(f) is defined as the ratio of the number of bad chips tested as good and the number of all chips that are tested as good [6]. Therefore,

$$r(f) = Y_{bg}(f)/[y + Y_{bg}(f)]$$

and, upon substituting from (7), we obtain

$$r(f) = \frac{(1-f)(1-y)e^{-(n_0-1)f}}{y+(1-f)(1-y)e^{-(n_0-1)f}}.$$

(8)

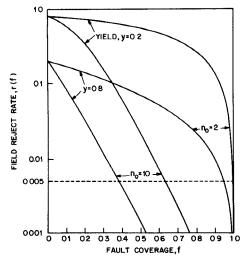

Fig. 1 shows a plot of (8) for two different yields, y = 0.80 and 0.20. In each case, two curves corresponding to  $n_0 = 2$  and 10, respectively, are drawn. This graph illustrates the dependence of test result on the parameter  $n_0$ . Consider the yield of 80 percent (say, for an MSI chip). If we wish to test the chip for a field reject rate below 0.5 percent, then the fault coverage should be 95 percent for  $n_0 = 2$  or 38 percent for  $n_0 = 10$ . Similarly, for a yield of 20 percent (which is closer to LSI) one would require a fault coverage of 99 or 63 percent, depending upon whether  $n_0$  is taken as 2 or 10. As pointed out earlier, the parameter  $n_0$  not only depends upon the chip size, but may also be a function of technology, design rules, processing environment, etc. We will, therefore, use an experimental procedure for determining this parameter.

<sup>&</sup>lt;sup>1</sup> Notice that the parameter  $n_0$  is different from the average number of physical defects  $(D_0A)$ , which is used for calculating the chip yield. In a highly dense circuit, a physical defect can produce several logical faults.

Fig. 1. Field reject rate for two chips with yields of 80 and 20 percent.

#### V. EXPERIMENTAL CHARACTERIZATION OF MODEL

Consider the fraction of chips that have been rejected by tests having a fault coverage f. This fraction is equal to the following probability

$$P(f) = 1 - y - Y_{bg}(f)$$

.

Upon substitution from (7), we get

$$P(f) = (1 - y) \left[ 1 - (1 - f) e^{-(n_0 - 1)f} \right]. \tag{9}$$

For a given chip, the yield y can be calculated from (3). In order to determine  $n_0$ , we start with a set of test patterns which need not have a high fault coverage. These patterns are evaluated on a fault simulator in the same order as they would be applied to the chip. A cumulative fault coverage as a function of the number of test patterns is thus obtained. Next, the patterns are used for testing the chips that are being produced in the processing line. A chip is rejected at the first pattern that it fails. A sufficiently large number of chips (say 100-200) are tested so that the cumulative fraction of rejected chips can be plotted as a function of the fault coverage. The calculated yield P(f), as computed from (9), is also plotted on the same graph for various values of  $n_0$ . The value of  $n_0$  that is closest to the experimental curve is then selected for use in the calculation of the required fault coverage.

Experience has shown that in LSI testing a large proportion of the chips is rejected by the first few test patterns. Thus, the graphs of the fraction of rejected chips and the function P(f) exhibit a steeply rising straight-line behavior near the origin. The experimental value of this slope can also be used for determining  $n_0$  since from (9)

$$P'(f) = \frac{dP(f)}{df} = (1 - y) [1 + (1 - f) (n_0 - 1)] e^{-(n_0 - 1)f}$$

and

$$P'(0) = (1 - y)n_0. (10)$$

Notice that the slope P'(0) is equal to the average number  $(n_{av})$  of faults as given by (2). One can determine an experimental value of P'(0) by applying a relatively small number of test

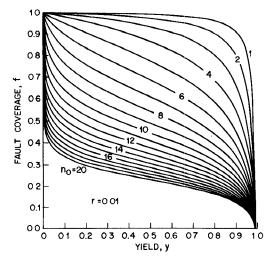

Fig. 2. Fault coverage required for a field reject rate of one in 100.

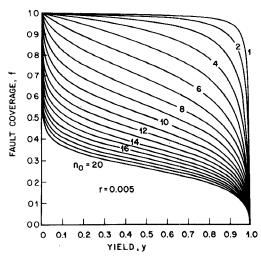

Fig. 3. Fault coverage required for a field reject rate of one in 200.

patterns to the chips. Also, when the yield is not known,  $n_0 \simeq P'(0)$  can be used as an estimate. Notice that P'(0) will be a close approximation for  $n_0$  for low-yield chips. Since, for a nonzero yield,  $P'(0) < n_0$ , use of P'(0) in place of  $n_0$  will give a pessimistic (or safe) value of fault coverage; in Fig. 1, a lower value of  $n_0$  means a higher fault coverage for a given field reject rate.

The procedures for determining  $n_0$  as outlined here will be illustrated by an example in a later section.

#### VI. FAULT COVERAGE REQUIREMENT

Once  $n_0$  has been evaluated for a chip, the required fault coverage for any specified field reject rate can be computed from (8). It is, however, not very convenient to solve (8) for f. If the required field reject rate is r, then from (8) we get

$$y = \frac{(1-r)(1-f)e^{-(n_0-1)f}}{r+(1-r)(1-f)e^{-(n_0-1)f}}.$$

(11)

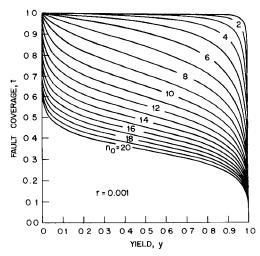

This result is plotted in Figs. 2-4 for r = 0.01, 0.005, and 0.001, respectively. One can easily obtain the fault coverage from these graphs. For example, if the field reject rate was specified as 1 in 1000, i.e., r = 0.001, then from Fig. 4 for

Fig. 4. Fault coverage required for a field reject rate of 1 in 1000.

yield y = 0.3 and  $n_0 = 8$ , the fault coverage should be about 85 percent.

#### VII. AN LSI EXAMPLE

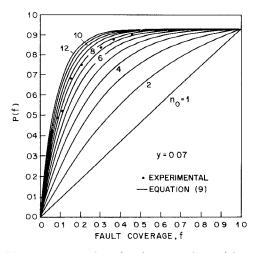

In this example, we consider an LSI chip containing about 25 000 transistors for which test patterns had been evaluated on the LAMP fault simulator [16]. The results used here were obtained from the testing of wafers on the Fairchild Sentry test system [17]. The yield for this chip was estimated to be about 7 percent. For each chip, the test pattern number on which the chip first failed was recorded. The cumulative number of failing chips as a function of the fault coverage is shown in Table I. The procedure for obtaining the entries in this table can be understood by examining the first line. After the initialization sequence, on the first pattern at which the tester strobed the chip output, 113 of 277 (i.e., 41 percent) chips failed. From fault simulation, the fault coverage on this pattern was obtained as 5 percent. The results of Table I are plotted in Fig. 5, where a family of curves, P(f) versus f for  $n_0 = 1-12$ , is also plotted. The experimental points closely match the curve corresponding to  $n_0 = 8$ . Also, if we approximate the slope of P(f) at the origin from the data in the first line in Table I, we get P'(0) = 0.41/0.05 = 8.2. Now from (10),  $n_0 = 8.2/0.93 = 8.8$ .

Taking  $n_0 = 8$ , we notice from Fig. 2 that for a 1 percent field reject rate, the fault coverage should be about 80 percent. As Fig. 4 indicates, the fault coverage should be improved to 95 percent in order to achieve a field reject rate of 1 in 1000.

The above conclusions differ significantly from those obtained in [6] where the field reject rate was obtained as

$$r = (1 - y)(1 - f)$$

.

From this formula, for r = 0.01, y = 0.07, we get f = 99 percent and for r = 0.001, f = 99.9 percent. These fault coverages are significantly higher than those obtained by the analysis presented here and, in fact, represent almost unachievable numbers for LSI circuits. Our analysis would have given similar results for  $n_0 = 3$  or 4. But  $n_0 = 3$  or 4 produces a P(f) versus f curve which significantly disagrees with the experimental result (see Fig. 5).

TABLE I

RESULT OF CHIP TEST

YIELD  $\simeq 0.07$ TOTAL NUMBER OF CHIPS = 277

| Fault Coverage (percent)                   | Cumulative<br>Number of<br>Chips Failed                     | Cumulative<br>Fraction of<br>Chips Failed                    |

|--------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|

| 5<br>8<br>10<br>15<br>20<br>30<br>36<br>45 | 113<br>134<br>144<br>186<br>209<br>226<br>242<br>251<br>256 | 0.41<br>0.48<br>0.52<br>0.67<br>0.75<br>0.82<br>0.87<br>0.91 |

| 50<br>65                                   | 257                                                         | 0.93                                                         |

Fig. 5. Determination of  $n_0$  from experimental data.

A large chip can be considered as composed of several smaller chips and thus the average number of faults on a large faulty chip would be higher. Also, for a given chip area, one would expect the average number of logical faults to be higher for greater circuit density (e.g., in the case of fine-line technology). The strength of our model lies in the experimental process by which the model parameter  $(n_0)$  is determined for the actual chip being studied. The influence of the fault model used in determining the fault coverage (e.g., stuck type faults) also influences the value of  $n_0$ . For instance, let us assume that the tests that detect the stuck type faults detect only very few of the actual fault modes of the chip. As the tests are applied, the chips will be rejected at a slower rate and (see Fig. 5) we will get a smaller value of  $n_0$ . This would mean (see Figs. 2-4) that the fault coverage (as measured in terms of stuck type faults) will have to be higher.

#### VIII. CONCLUSION

Besides finding the fault coverage requirement for a chip processing line, there are other applications of the technique presented here. One such application is in prediction of the influence of fine-line technology on the testing problem. A given circuit, when implemented with finer design rules, occupies a smaller area. The yield, which largely depends upon the chip area, would be higher. In Figs. 2-4, a higher yield indicates a lower fault coverage requirement if  $n_0$  was kept fixed. However, when the circuit is shrunk into finer features, one should expect many logical faults to be produced by a physical defect. This phenomenon could result in a higher

value of  $n_0$ , thereby further reducing the fault coverage requirement.

In our theory, we have introduced a new parameter  $n_0$ , the average number of faults on a defective chip. No attempt has been made to relate  $n_0$  to the yield. Yield, which has been extensively studied in the past, is known to depend upon the chip area and the defect density. The average number of faults also depends upon the chip area and defect density. Further work should establish at least an empirical relationship between yield and the average number of faults.

Since the completion of this work, the authors have learned of similar work being pursued elsewhere [18].

#### ACKNOWLEDGMENT

The cooperation of J. Kumar, J. H. Lee, and R. D. Taft in providing the Sentry test data, the assistance of R. Seth with the compilation of statistical data, and the assistance of E. Edelman in the preparation of this manuscript are much appreciated.

#### REFERENCES

- [1] J. Galiay, Y. Crouzet, and M. Vergniault, "Physical versus logical fault models in MOS LSI circuits: Impact on their testability," *IEEE Trans. Comput.*, vol. C-29, pp. 527-531, June 1980.

- [2] C. Mead and L. Conway, Introduction to VLSI Systems. Reading, MA: Addison-Wesley, 1980.

- [3] G. R. Case, "Analysis of actual fault mechanisms in CMOS logic gates," in *Proc. 13th Design Automation Conf.*, San Francisco, CA, June 28-30, 1976, pp. 265-270.

- [4] R. L. Wadsack, "Fault modeling and logic simulation of CMOS and MOS integrated circuits," *Bell Syst. Tech. J.*, vol. 57, pp. 1449-1474, May-June 1978.

- [5] M. A. Breuer and A. D. Friedman, Diagnosis and Reliable Design of Digital Systems. Rockville, MD: Computer Science Press, 1976.

- [6] R. L. Wadsack, "Fault coverage în digital integrated circuits," Bell Syst. Tech. J., vol. 57, pp. 1475-1488, May-June 1978.

- [7] W. Feller, An Introduction to Probability Theory and Its Applications, vol. I, 3rd ed. New York: Wiley, 1968.

- [8] B. T. Murphy, "Cost-size optima of monolithic integrated circuits," Proc. IEEE, vol. 52, pp. 1537-1545, Dec. 1964.

- [9] R. B. Seeds, "Yield, economic and logistic models for complex digital arrays," in 1967 IEEE Int. Conv. Rec., Part 6, pp. 60-61.

- [10] J. E. Price, "A new look at yield of integrated circuits," Proc. IEEE, vol. 58, pp. 1290-1291, Aug. 1970.

- [11] C. H. Stapper, "Defect density distribution for LSI yield calculations," *IEEE Trans. Electron Devices*, vol. ED-20, pp. 655-657, July 1973.

- [12] J. Sredni, "Use of power transformation to model the yield of ICs as a function of active circuit area," in *Proc. Int. Electron Devices Meeting*, Washington, DC, December 1975, pp. 123-125.

- Devices Meeting, Washington, DC, December 1975, pp. 123-125.

[13] C. H. Stapper, "On a composite model to the IC yield problem,"

IEEE J. Solid-State Circuits, vol. SC-10, pp. 537-539, Dec. 1975.

- [14] A. B. Glaser and G. E. Subak-Sharpe, *Integrated Circuit Engineering*. Reading, MA: Addison-Wesley, 1978, pp. 746-799.

- [15] V. D. Agrawal, S. C. Seth, and P. Agrawal, "LSI product quality and fault coverage," in *Proc. 18th Design Automation Conf.*, Nashville, TN, June 29-July 1, 1981 pp. 196-203.

- [16] H. Y. Chang, G. W. Smith, Jr., and R. B. Walford, "LAMP: System description," Bell Syst. Tech. J., vol. 53, pp. 1431-1499, Oct. 1974.

- [17] Sentry 600 User's Manual, Part No. 67095498, Fairchild Systems Technology, Palo Alto, CA, Dec. 1973.

- [18] D. Griffin, "Estimation of DC stuck-fault quality levels through application of a mixed Poisson model," in *Proc. Int. Conf. Cir*cuits Comput. (ICCC), Port Chester, NY, Oct. 1-3, 1980, pp. 1099-1102.

Vishwani D. Agrawal (S'68-M'70-SM'80) received the B.Sc. degree from Allahabad University, Allahabad, India, in 1960, the B. E. degree from Roorkee University, Roorkee, India, in 1964, the M. E. degree from the Indian Institute of Science, Bangalore, India, in 1966, and the Ph. D. degree from the University of Illinois, Urbana, in 1971.

His experience includes teaching (1966-67) in the Department of Electrical Engineering Indian Institute of Technology, New Delhi, India;

antenna research (1967-70) at the Antenna Laboratory, University of Illinois, Urbana; digital test technique development (Illiac IV Project, 1970-71) at the Automation Technology, Inc., Champaign, IL; wideband antenna design (1971-72) at E.E. and G., Inc., Albuquerque, NM; teaching and research (1972-75) at the School of Radar Studies, Indian Institute of Technology, New Delhi, India; and spacecraft antenna design (1975-78) at TRW Defense and Space Systems Group, Redondo Beach, CA. Since 1978 he has been at Bell Laboratories, Murray Hill, NJ, working on computer-aided design and testing of LSI circuits.

Dr. Agrawal was awarded the Best Applications Paper Award from the IEEE Antennas and Propagation Society in 1979.

Sharad C. Seth (S'66-M'70) received the B. E. degree in electronics and telecommunications from Jabalpur University, Jabalpur, India, in 1964, the M. Tech. degree in electrical engineering from the Indian Institute of Technology, Kanpur, India in 1966, and the Ph. D. degree in electrical engineering from the University of Illinois, Urbana, in 1970.

Since 1970 he has been on the faculty of the Department of Computer Science, University of Nebraska, Lincoln, and is currently an As-

sociate Professor. He held a Visiting Position at the Indian Institute of Technology, Kanpur, India, during the year 1974-75 and was a Member of Technical Staff at Bell Laboratories, Murray Hill, NJ, during the Summer of 1980. His current research interests are in the area of VLSI testing and design.

Dr. Seth is a member of the Association for Computing Machinery.

Prathima Agrawal (S'74-M'78) received the B.E. and M.E. degrees in electrical communication engineering from the Indian Institute of Science, Bangalore, India, in 1964 and 1967, respectively. She received the M.S. degree in electrical engineering from the University of Rochester, Rochester, NY, in 1968, and the University of Southern California, Los Angeles, in 1977.

From 1964 to 1968 she held teaching assignments at the Indian Institute of Science, Bangalore, and later at the University of Rochester. From 1968 to 1970 she worked on digital simulation and design diagnostics of the Illiac IV computer at the Department of Computer Science, University of Illinois, Urbana, and continued this work through 1970-71 at Automation Technology, Inc., Champaign, IL. During 1973-74, she worked at the Computer Center of the Indian Institute of Technology, New Delhi, India, on design automation and diagnosis of digital systems. From 1974-77, as a Research Assistant in the Electrical Engineering Department, University of Southern California, Los Angeles, she worked on routing algorithms for circuits. During the fall of 1977 she was an Assistant Professor of Electrical Engineering at California State University, Northridge. Since 1978 she has been with Bell Laboratories, Murray Hill, NJ, where she is currently working in the microprocessor design department. Her research interests include several areas of design automation: automated layout algorithms, testing, simulation, and design verification.