### **Computers Working at the Speed of Light**

#### David R. Selviah

Department of Electronic and Electrical Engineering,

University College London, UCL, UK,

d.selviah@ee.ucl.ac.uk

Tel: 020 7679 3056

### Moore's Law

- Gordon Moore was a co-founder of Intel.

- In 1965 he said that the number of transistors in an integrated circuit will increase exponentially, almost doubling every two years in an article in Electronics, Volume 38, Number 8, April 19, 1965

- Moore's law has been obeyed since the invention of the integrated circuit in 1958 to now

- The smaller the transistor the faster the switching speed can be giving faster computers.

2

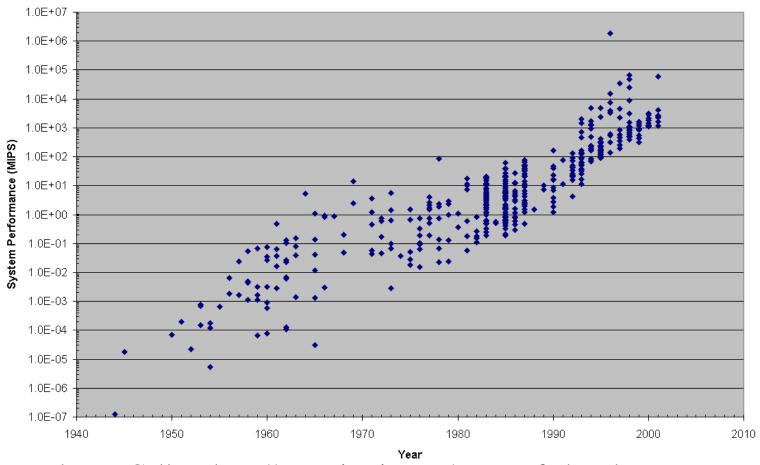

### **Computer CPU Performance Trend**

#### **Computer System Performance**

Thanks to John McCallum http://www.jcmit.com/cpu-perf-chart.htm

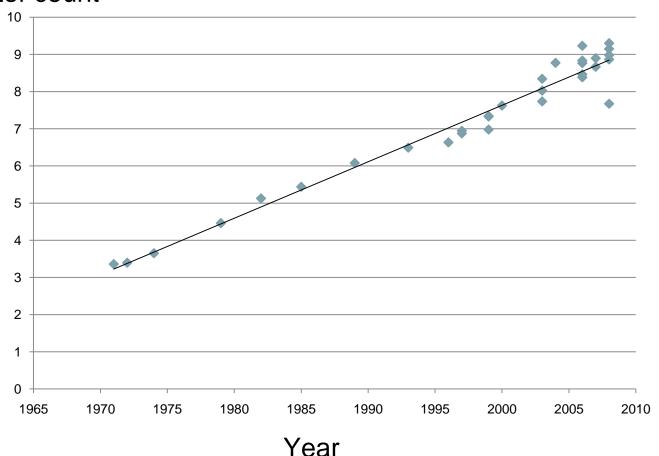

### **Computer Processor Transistor Count Trend**

# Logarithm to base 10 of Transistor count

#### **Transistor count**

- Intel 4004 with 2300 transistors

- Quad-Core

Itanium Tukwila

with 2 trillion

transistors

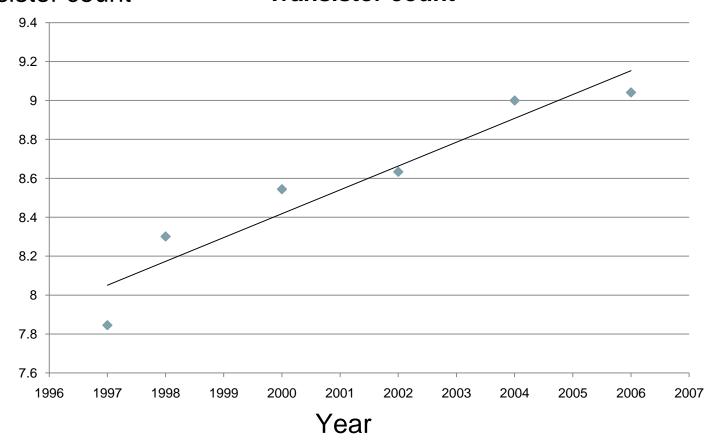

### Field Programmable Gate Arrays, FPGA Transistor count for Xilinx Series

Logarithm to base 10 of Transistor count

#### Transistor count

- Virtex with 70 million transistors

- Virtex E

- Virtex II

- Virtex II Pro

- Virtex 4

- Virtex 5 with 1.1 trillion transistors

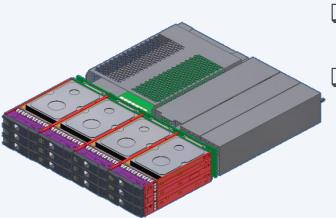

# IBM's Blue Gene/L: world's fastest supercomputer in 2005

The 65,536-processor machine can sustain 280.6 trillion calculations per second, called 280.6 teraflops

# IBM's Blue Gene/L supercomputer simulated half a mouse brain 2007

- University of Nevada with IBM Almaden Research Lab, ran a "cortical simulator that was as big and as complex as half of a mouse's brain on the BlueGene L,"

- It had 8,000 neurons and 6,3000 synapses

- It ran for 10 seconds at a speed "ten times slower than real-time"

### **Top 10 Fastest Computers in December 2008**

| Roadrunner - BladeCenter QS22/LS21 Cluster, PowerXCell 8i                       |

|---------------------------------------------------------------------------------|

| 3.2 GHz / Opteron DC 1.8 GHz , Voltaire Infiniband                              |

| Jaguar - Cray XT5 QC 2.3 GHz                                                    |

| Pleiades - SGI Altix ICE 8200EX, Xeon QC 3.0/2.8 GHz                            |

| BlueGene/L - eServer Blue Gene Solution                                         |

| Blue Gene/P Solution                                                            |

| Ranger - SunBlade x6420, Opteron QC 2.3 GHz, Infiniband                         |

| Franklin - Cray XT4 QuadCore 2.3 GHz                                            |

| Jaguar - Cray XT4 QuadCore 2.1 GHz                                              |

| Red Storm - Sandia/ Cray Red Storm, XT3/4, 2.4/2.2 GHz                          |

| dual/quad core                                                                  |

| Dawning 5000A - Dawning 5000A, QC Opteron 1.9 GHz, Infiniband, Windows HPC 2008 |

|                                                                                 |

# IBM Roadrunner Supercomputer at Los Alamos National Laboratory in June 2008 is worlds fastest

- 1.105 petaflop/s

- Second fastest is the Cray XT5 supercomputer at Oak Ridge National Laboratory called Jaguar.

- The system, is the second to break the petaflop/s barrier

- One petaflop/s represents one quadrillion floating point operations per second.

### Data storage systems increasing in complexity, density and speed

### Storage demand increasing Data rates increasing

**Disk sizes decreasing**

- Manage more storage

- ☐ Data access speeds:

$\square$  3.5"  $\rightarrow$  2.5"  $\rightarrow$  1.8"  $\rightarrow$  1"

- Increased complexity

- $3 \text{ Gb/s SAS} \rightarrow 6 \text{ Gb/s SAS} \square$  Increased system density

- □ 10 Gb/s Gigabit Ethernet

- 12 Gb/s SAS

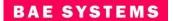

# **On-board Platform Applications**

### **On-board Platform Applications**

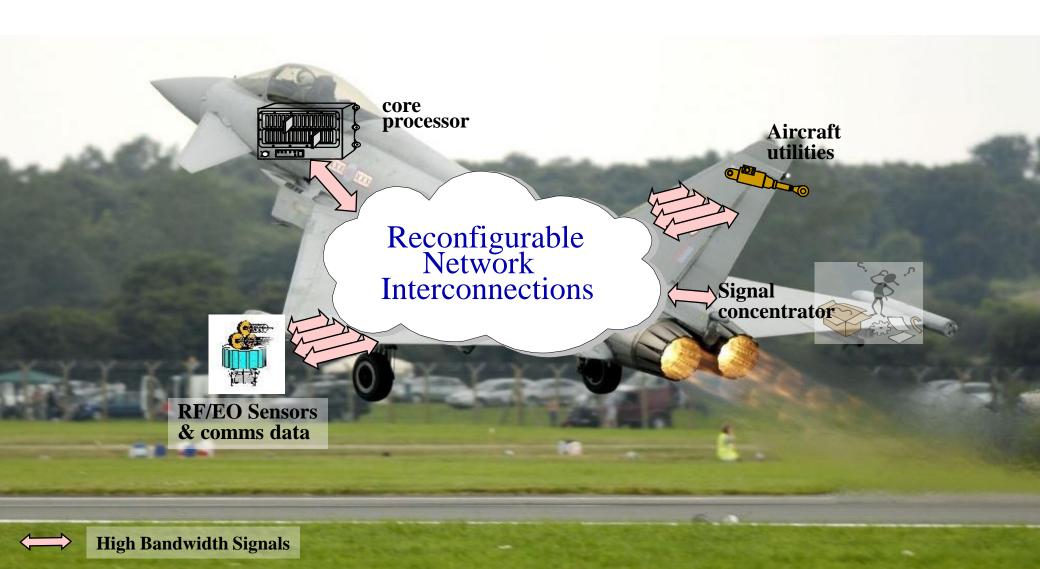

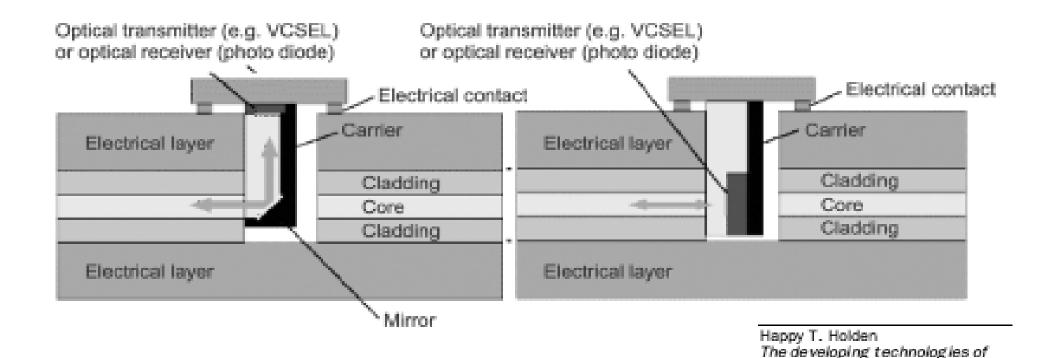

# **JIEP Optical Packaging Roadmap 2002**

Happy T. Holden The developing technologies of integrated optical waveguides in printed circuits

Circuit World 29/4 [2003] 42-50

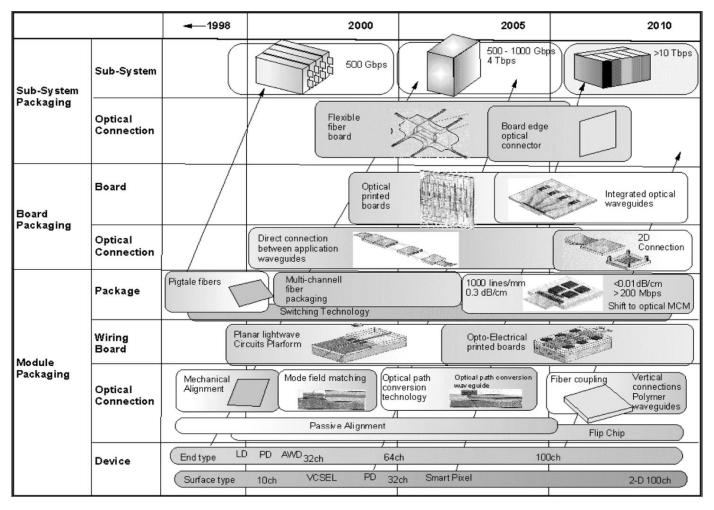

### **Backplane Motherboards**

# Copper Tracks versus Optical Waveguides for High Bit Rate Interconnects

- Copper Track

- EMI Crosstalk

- Loss

- Impedance control to minimize back reflections, additional equalisation, costly board material

- Optical Waveguides

- Low loss

- Low cost

- Low power consumption

- Low crosstalk

- Low clock skew

- WDM gives higher aggregate bit rate

- Cannot transmit electrical power

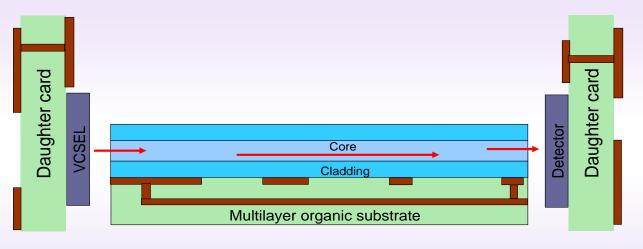

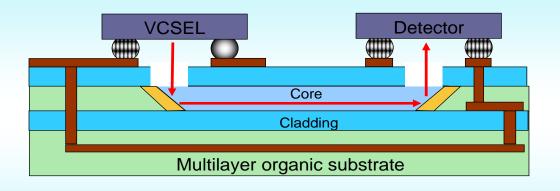

### Integration of Optics and Electronics

- Backplanes

- Butt connection of "plug-in" daughter cards

- In-plane interconnection

- Focus of OPCB project

- Out-of-plane connection

- 45 mirrors

- Chip to chip connection possible

integrated optical waveguides in

printed circuits Circuit World

29/4 [2003] 42-50

# **Optical Connectors (Griese, 2002)**

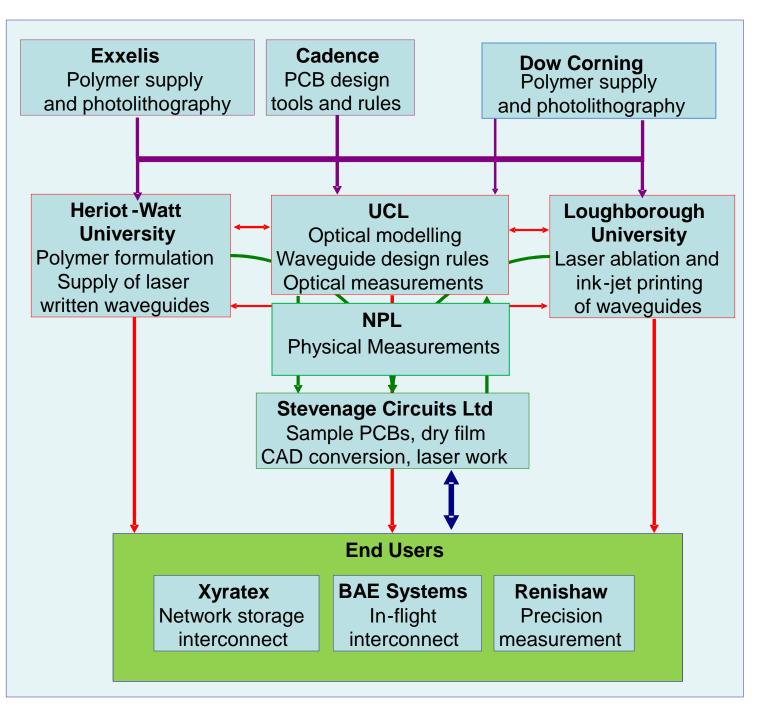

# The Integrated Optical and Electronic Interconnect PCB Manufacturing (OPCB) project

- Hybrid Optical and Electronic PCB Manufacturing Techniques

- 8 Industrial and 3 University Partners led by industry end user

- Multimode waveguides at 10 Gb/s on a 19 inch PCB

- Project funded by UK Engineering and Physical Sciences Research Council (EPSRC) via the Innovative Electronics Manufacturing Research Centre (IeMRC) as a Flagship Project

- 2.5 years into the 3 year, £1.3 million project

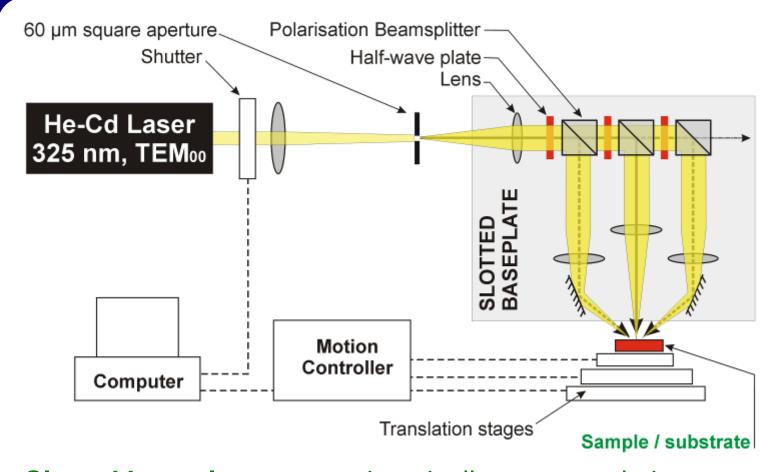

# **Direct Laser-writing Setup: Schematic**

- Slotted baseplate mounted vertically over translation, rotation & vertical stages; components held in place with magnets

- By using two opposing 45° beams we minimise the amount of substrate rotation needed

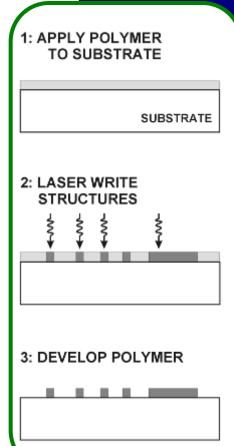

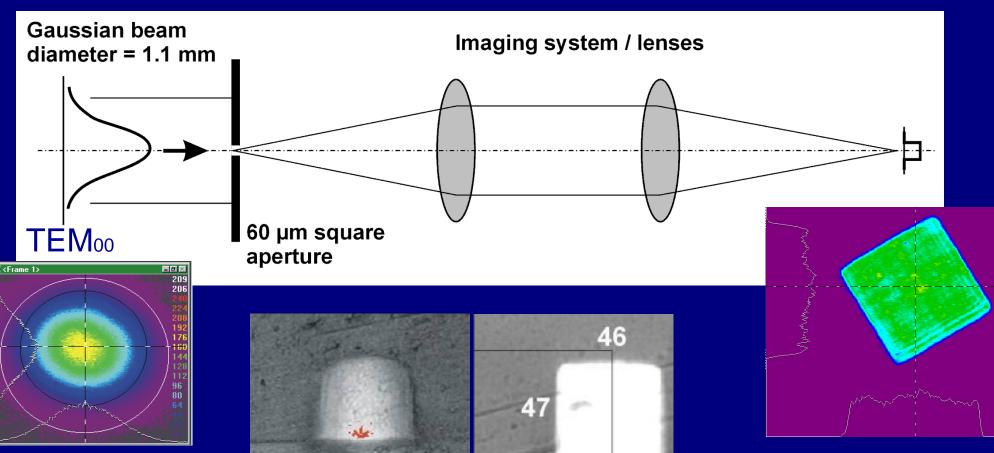

# Writing sharply defined features

- flat-top, rectangular laser spot

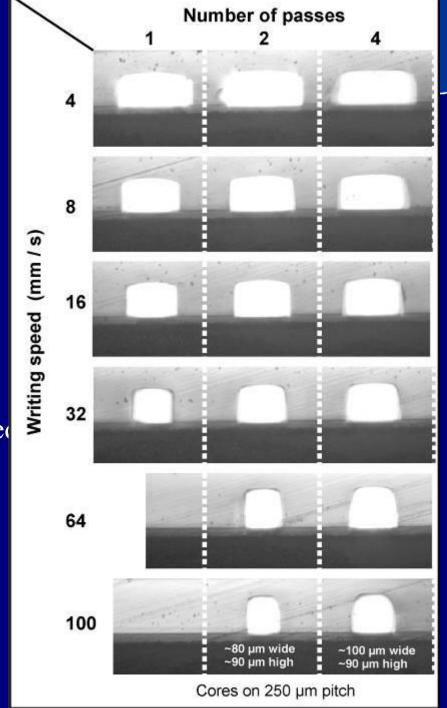

Images of the resulting waveguide core cross-sections

**Imaged aperture**

**Gaussian Beam**

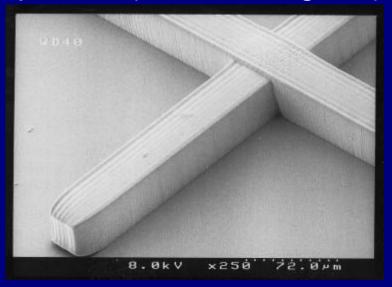

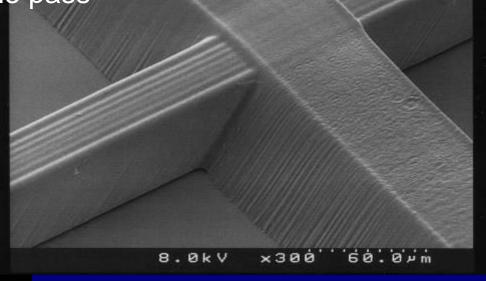

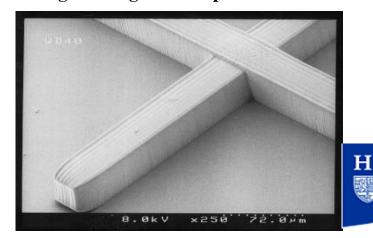

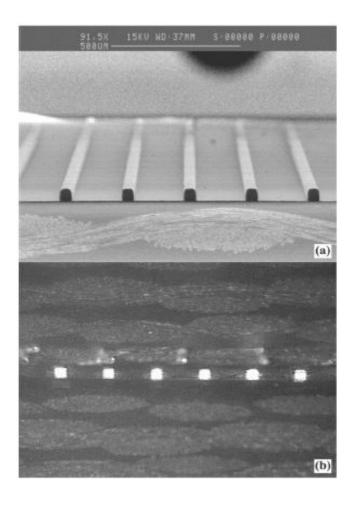

# Laser written polymer structures

HERIOT WATT UNIVERSITY

SEM images of polymer structures written using imaged 50 µm square aperture (chrome on glass)

- Writing speed: ~75 μm / s

- Optical power: ~100 μW

- Flat-top intensity profile

- Oil immersion

- Single pass

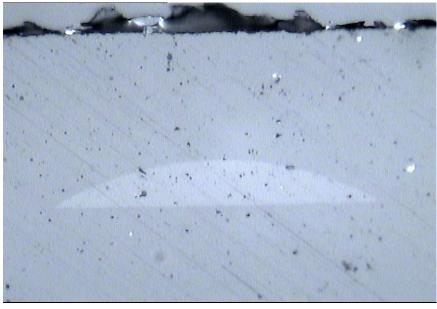

Optical microscope image showing end on view of the 45° surfaces

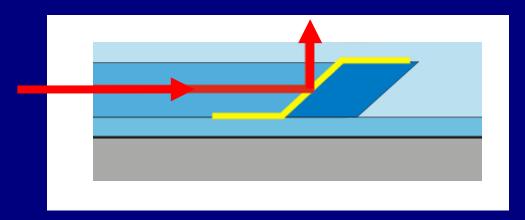

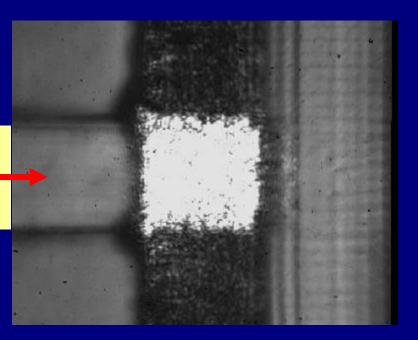

# Waveguide terminated with 45-deg mirror

Out-of-plane coupling, using 45-deg mirror (silver)

Microscope image looking down on mirror coupling light towards camera

**OPTICAL INPUT**

### **Current Results**

### **Laser-writing Parameters:**

- Intensity profile: Gaussian

- Optical power: ~8 mW

- Cores written in oil

### **Polymer:**

- Custom multifunctional acrylate photo-polymer

- Fastest "effective" writing speed to date: 50 mm/s

(Substrate: FR4 with polymer undercladding)

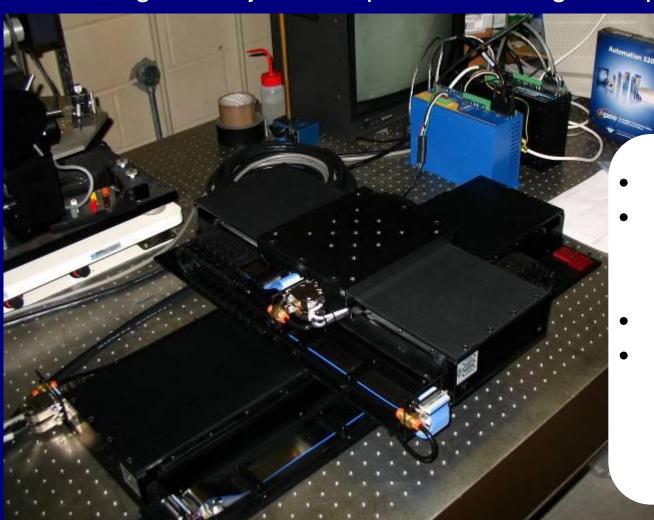

# **Large Board Processing: Writing**

HERIOT WATT UNIVERSITY

- Stationary "writing head" with board moved using Aerotech sub-µm precision stages

- Waveguide trajectories produced using CAD program

600 x 300 mm travel

Requires a minimum of 700 x 1000 mm space on optical bench

Height: ~250 mm

Mass:

300 mm: 21 kg

• 600 mm: 33 kg

Vacuum tabletop

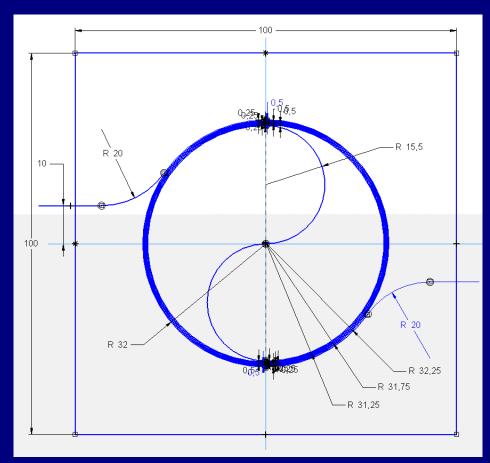

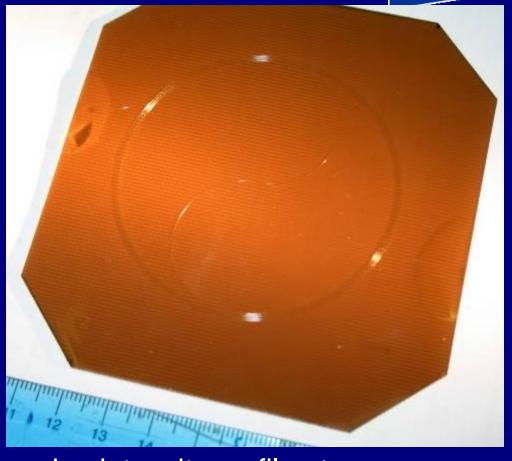

# **Large Board Processing: Writing**

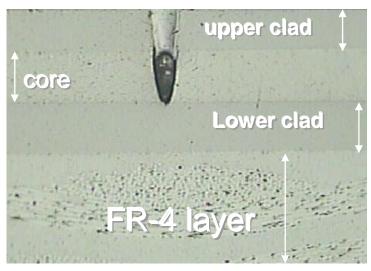

The spiral was fabricated using a Gaussian intensity profile at a writing speed of 2.5 mm/s on a 10 x 10 cm lower clad FR4 substrate. Total length of spiral waveguide is  $\sim 1.4$  m. The spiral was upper cladded at both ends for cutting.

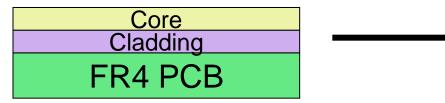

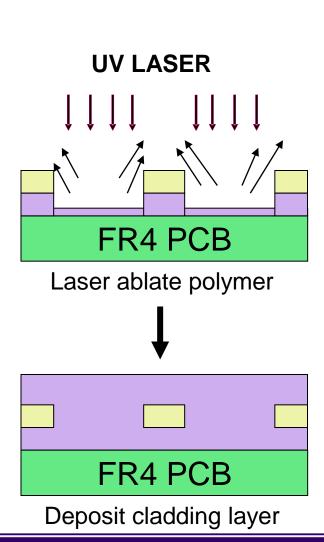

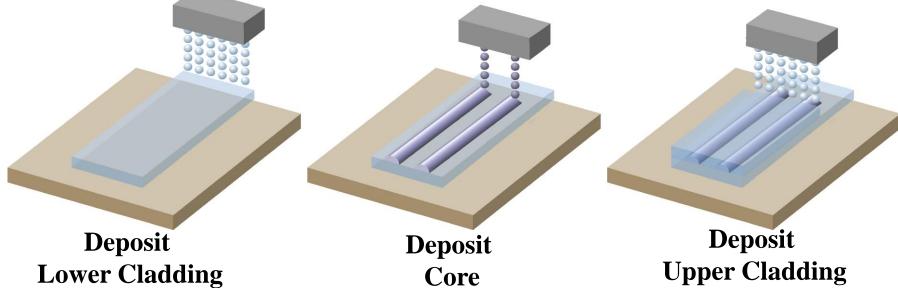

### Laser Ablation for Waveguide Fabrication

- Ablation to leave waveguides

- Excimer laser Loughborough

- Nd:YAG Stevenage Circuits

Deposit cladding and core layers on substrate

**SIDE VIEW**

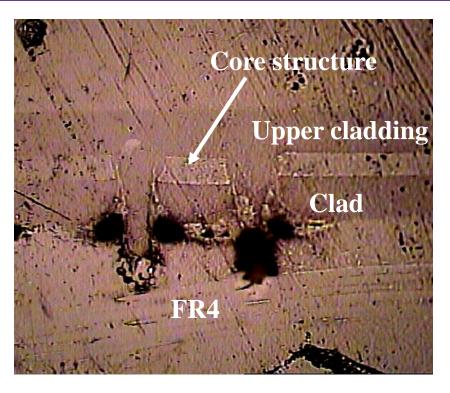

### **Nd:YAG Ablation**

- Nd:YAG laser based at Stevenage Circuits

- Grooves machined in optical polymer and ablation depth characterised for machining parameters

- Initial waveguide structures prepared

### **Excimer Laser Ablation**

- Straight structures machined in polymer

- Future work to investigate preparation of curved mirrors for out of plane interconnection

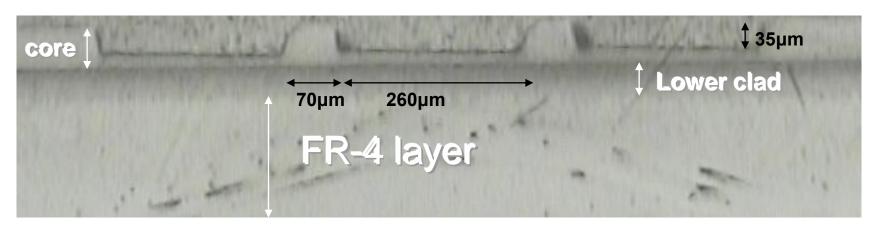

### Cross-section

Plan View

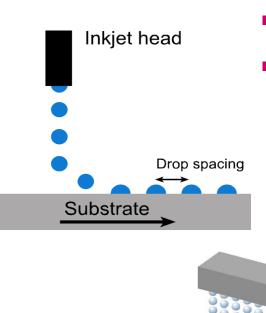

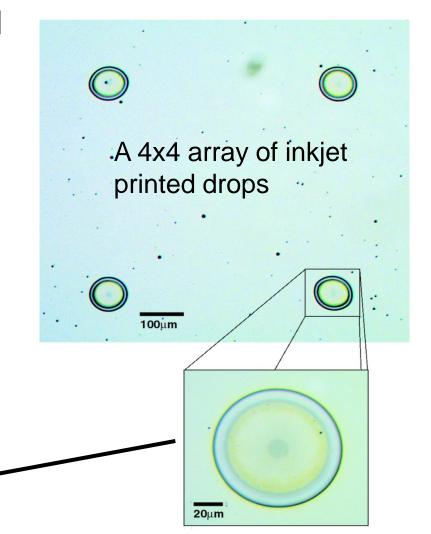

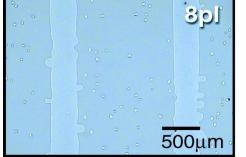

### Inkjetting as a Route to Waveguide Deposition

- Print polymer then UV cure

- Advantages:

- controlled, selective deposition of core and clad

- less wastage: picolitre volumes

- large area printing

- low cost

### **Challenges of Inkjet Deposition**

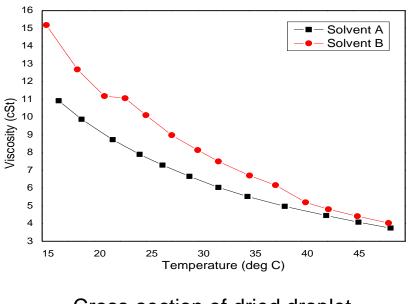

- Viscosity tailored to inkjet head via addition of solvent

- "Coffee stain" effects

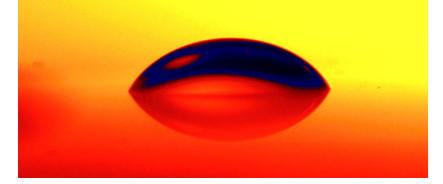

Cross-section of dried droplet "coffee-stain" effect

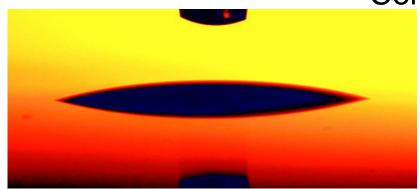

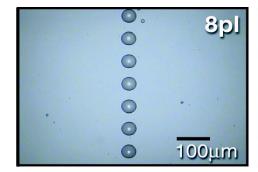

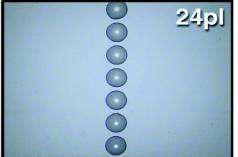

### **Changing Surface Wettability**

**Contact Angles**

Core material on cladding

24pl

Large wetting - broad inkjetted lines

Core material on modified glass surface (hydrophobic)

Reduced wetting – discrete droplets

Identical inkjetting conditions - spreading inhibited on modified surface

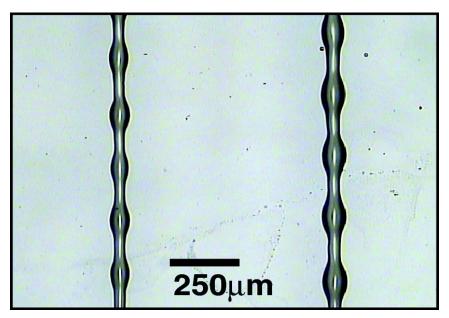

### **Towards Stable Structures**

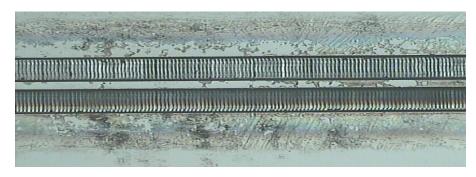

Stable line structures with periodic features

Cross section of inkjetted core material surrounded by cladding (width 80 microns)

A balance between wettability, line stability and adhesion

# Waveguide components and measurements

- Straight waveguides 480 mm x 70 µm x 70 µm

- Bends with a range of radii

- Crossings

- Spiral waveguides

- Tapered waveguides

- Bent tapered waveguides

- Loss

- Crosstalk

- Misalignment tolerance

- Surface Roughness

- Bit Error Rate, Eye Diagram

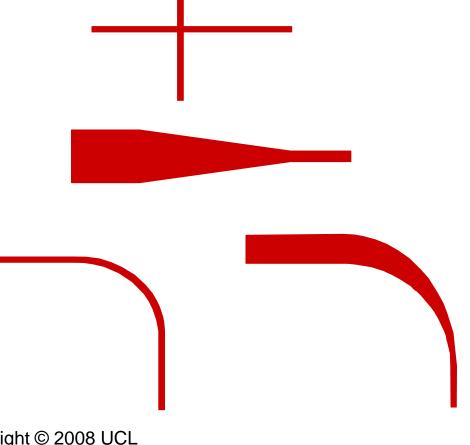

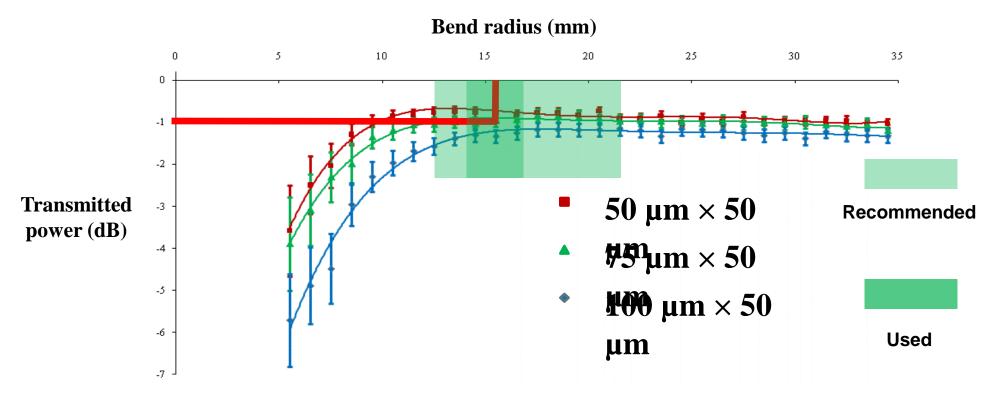

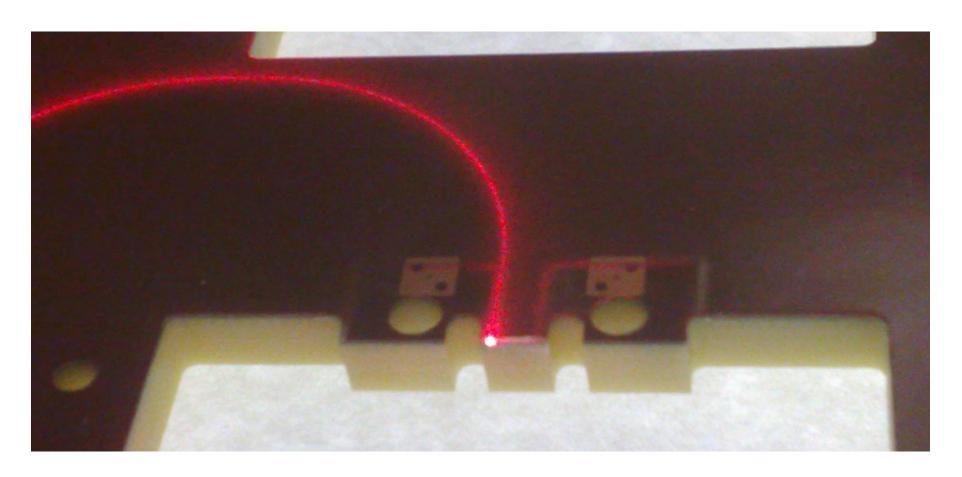

# Optical Power Loss in 90 Waveguide Bends

Schematic diagram of one set of curved waveguides.

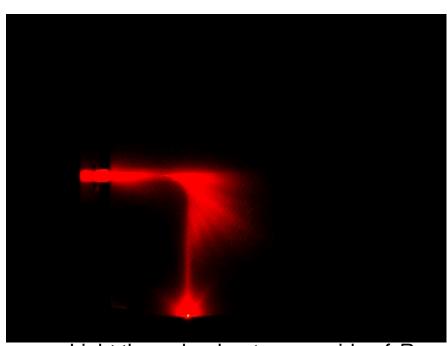

Light through a bent waveguide of R = 5.5 mm - 34.5 mm

- Radius R, varied between 5.5 mm < R < 35 mm,  $\Delta R = 1$  mm

- Light lost due to scattering, transition loss, bend loss, reflection and backscattering

- Illuminated by a MM fiber with a red-laser.

Copyright © 2008 UCL

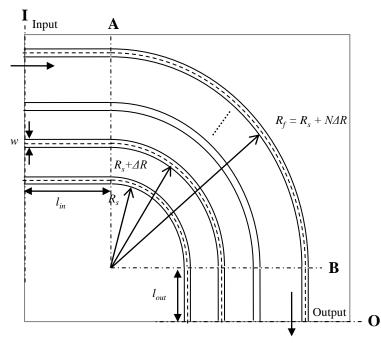

# BPM, beam propagation method modeling of optical field in bend segments

$w = 50 \ \mu m$ ,  $R = 13 \ mm$  (left picture) in the first segment (first 10°). (right picture) in the 30° to 40° degree segment. Copyright © 2008 UCL

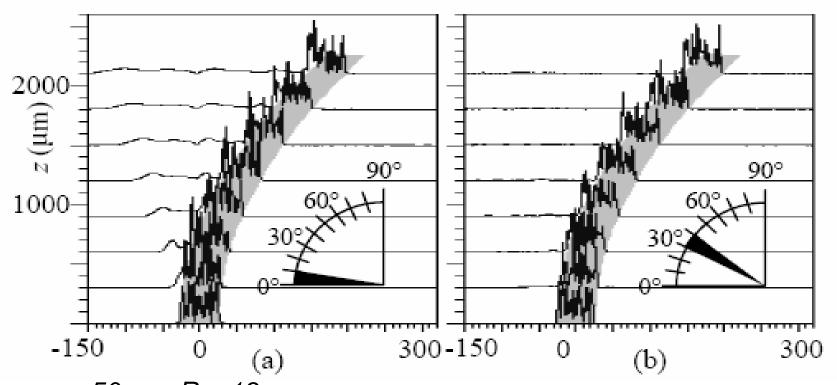

# Differences in misalignment tolerance and loss as a function of taper ratio

- Graph plots the differences between a tapered bend and a bend

- There is a trade off between insertion loss and misalignment tolerance Copyright © 2008 UCL

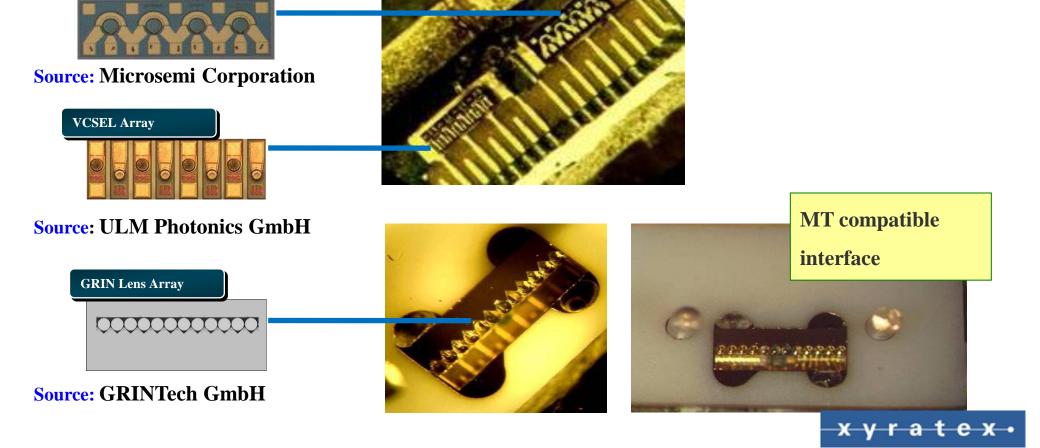

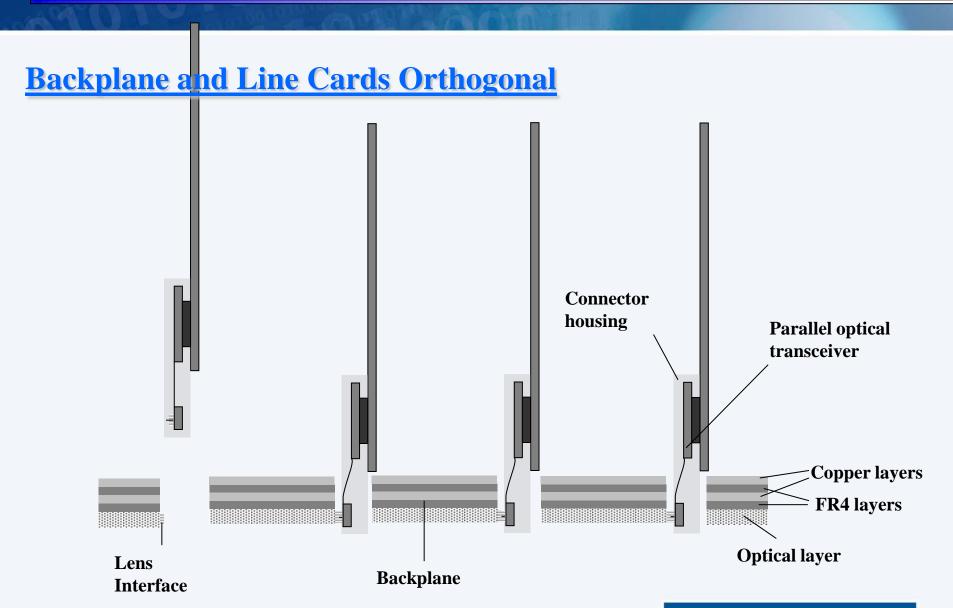

## Crosstalk in Chirped Width Waveguide Array

## 100 μm 110 μm 120 μm 130 μm 140 μm 150 μm

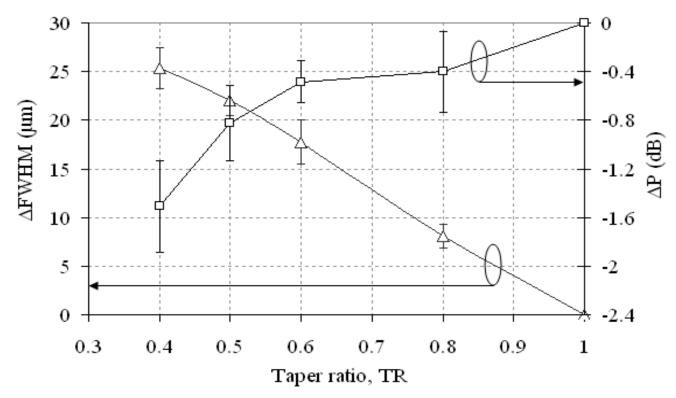

- Light launched from VCSEL imaged via a GRIN lens into 50 µm x 150 µm waveguide

- Photolithographically fabricated chirped with waveguide array

- Photomosaic with increased camera gain towards left

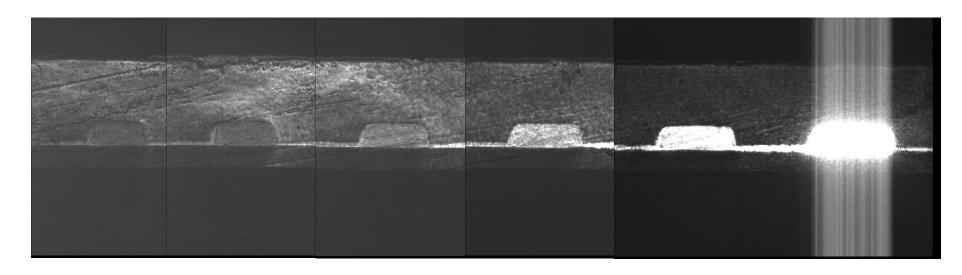

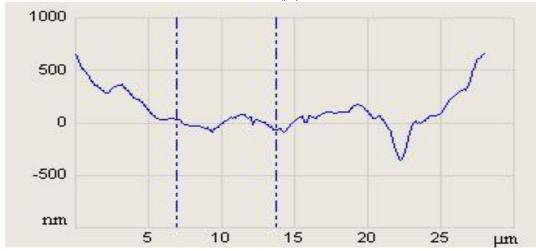

## **Surface roughness**

RMS side wall roughness: 9 nm to 74 nm

RMS polished end surface roughness: 26 nm to 192 nm.

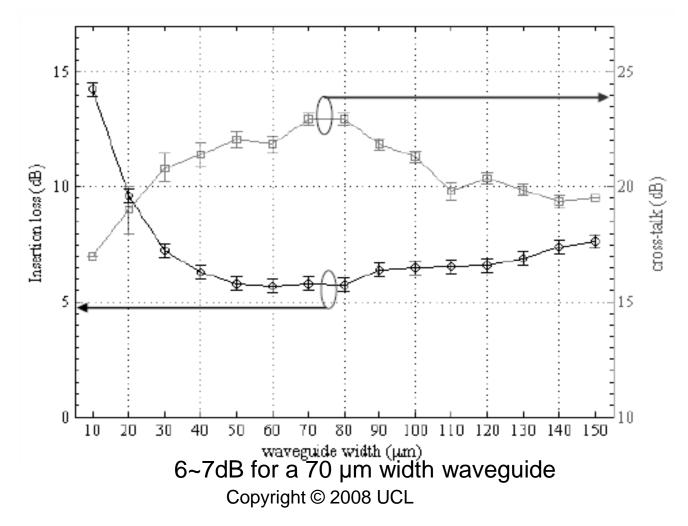

# Design rules for waveguide width depending on insertion loss and cross-talk

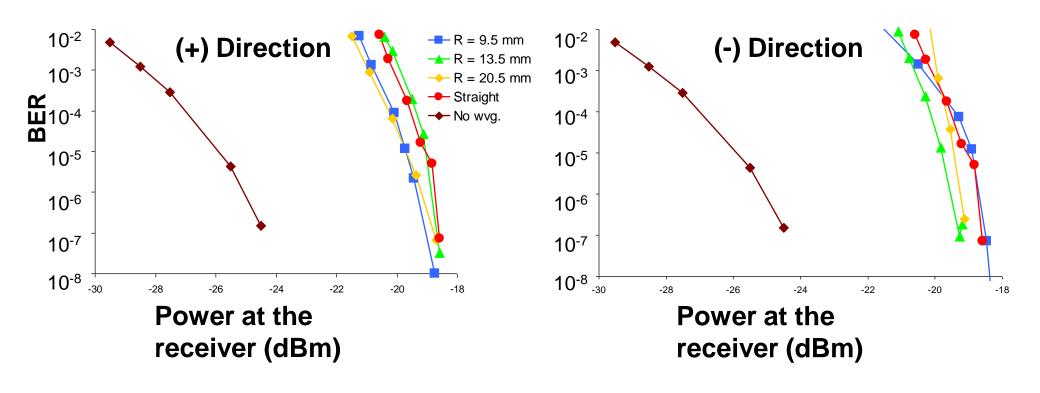

# Bit error rate for laterally misaligned 1550 nm 2.5 Gb/s DFB laser

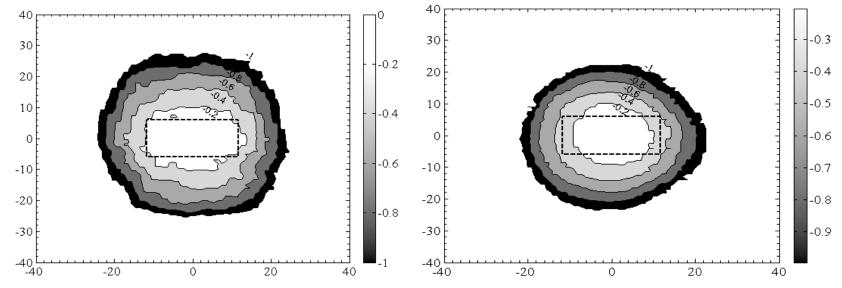

## Contour map of VCSEL and PD misalignment

- (a) Contour map of relative insertion loss compared to the maximum coupling position for VCSEL misalignment at z = 0.

- (b) Same for PD misalignment at z = 0. Resolution step was  $\Delta x = \Delta y = 1 \mu m$ .

- Dashed rectangle is the expected relative insertion loss according to the calculated misalignments along x and y.

- The minimum insertion loss was 4.4 dB, corresponded to x = 0, y = 0, z = 0Copyright © 2008 UCL

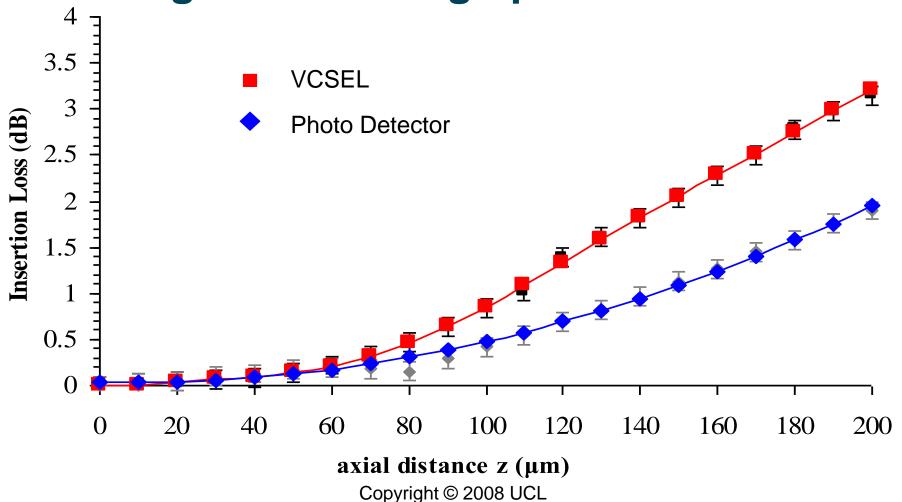

# Coupling Loss for VCSEL and PD for misalignments along optic axis

### Fabrication Techniques and Waveguides Samples

**Straight waveguides – Optical InterLinks**

90° Crossings – Heriot Watt University

90° Crossings – Dow Corning

50° Crossings – Exxelis

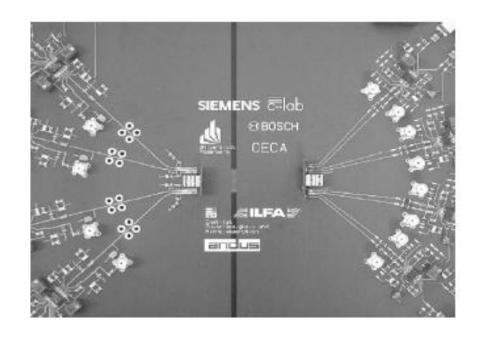

## Siemens C-Labs Test Board (Griese, 2002)

Happy T. Holden The developing technologies of integrated optical waveguides in printed circuits

Circuit World 29/4 [2003] 42-50

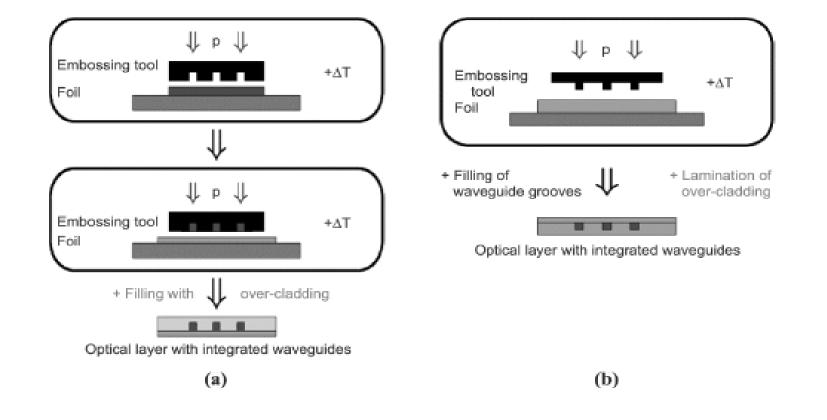

# Waveguide Fabrication by Two Hot Embossing Methods (Griese, 2002)

# TOPCat Polymer optical waveguide cores with overcladding (Watsun 2001)

Happy T. Holden The developing technologies of integrated optical waveguides in printed circuits

Circuit World 29/4 [2003] 42-50

## **TOPCat optical waveguide fabrication process**

Coat tool with core pre-polymer

Strike off excess, cure

Overcoat with clad

Lift out cores

Happy T. Holden

The developing technologies of integrated optical waveguides in printed circuits

Circuit World 29/4 [2003] 42-50

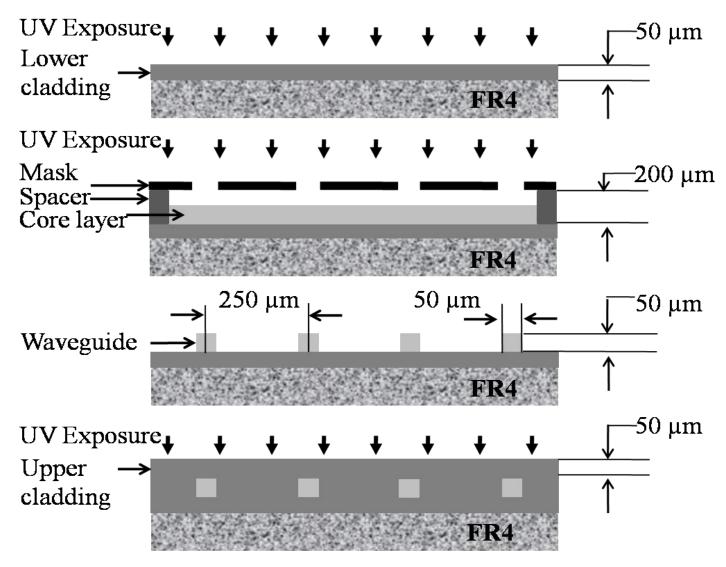

### Photolithographic Fabrication of Waveguides

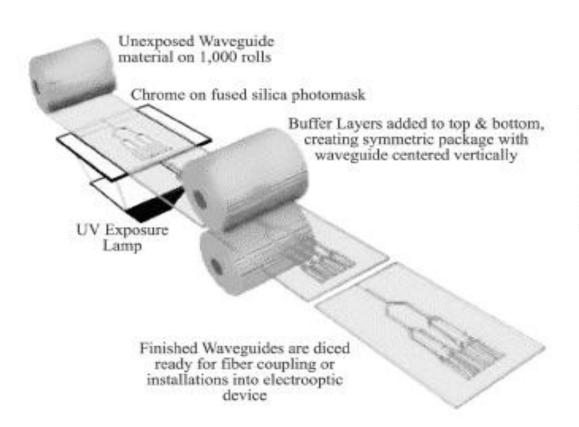

# Polymer waveguides formed by Photolithography in Truemode® polymer

Happy T. Holden The developing technologies of integrated optical waveguides in printed circuits

Circuit World 29/4 [2003] 42-50

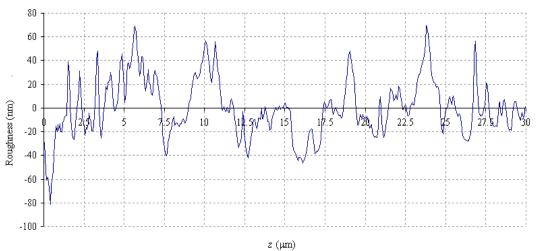

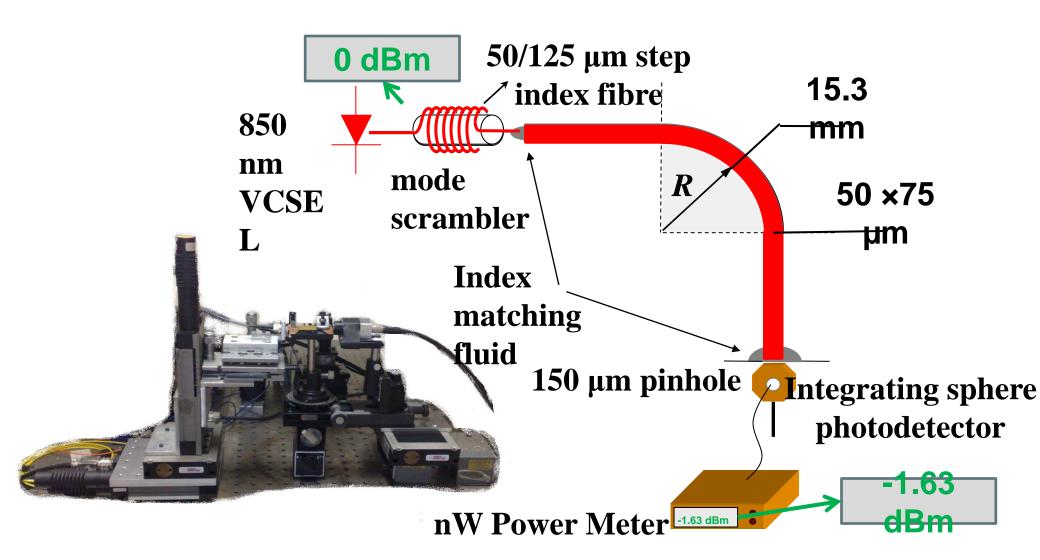

### **Optical Loss Measurement**

## **VCSEL Array for Crosstalk Measurement**

**PIN Array**

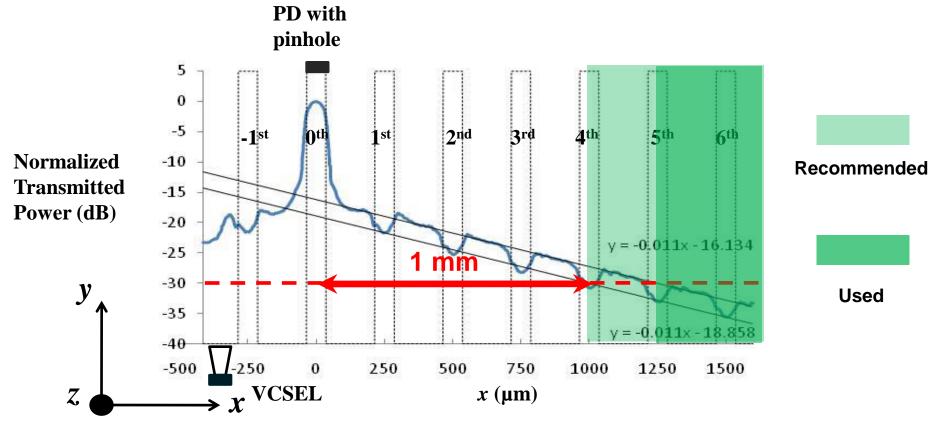

## Design Rules for Inter-waveguide Cross Talk

- 70  $\mu m \times 70~\mu m$  waveguide cross sections and 10 cm long

- In the cladding power drops linearly at a rate of 0.011 dB/µm

- Crosstalk reduced to -30 dB for waveguides 1 mm apart

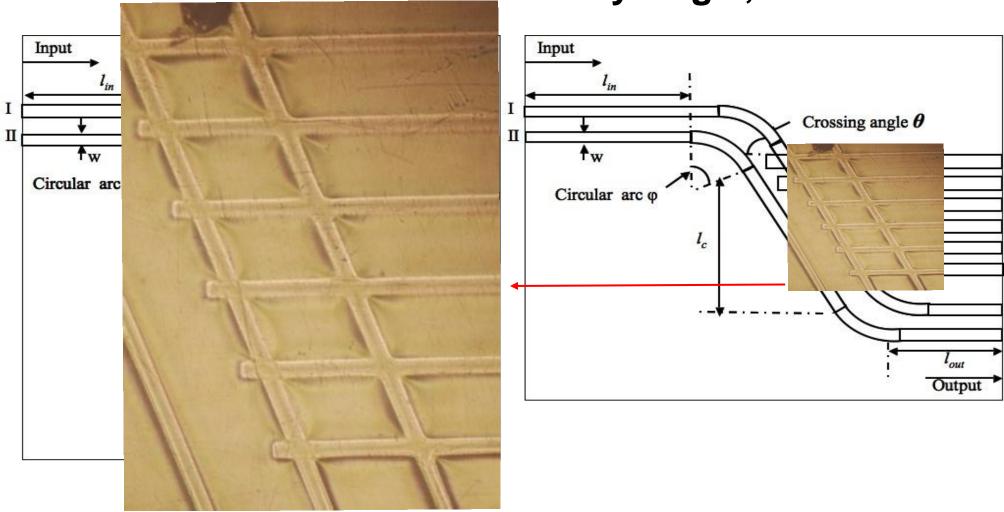

# Schematic Diagram Of Waveguide Crossings at 90° and at an Arbitrary Angle, θ

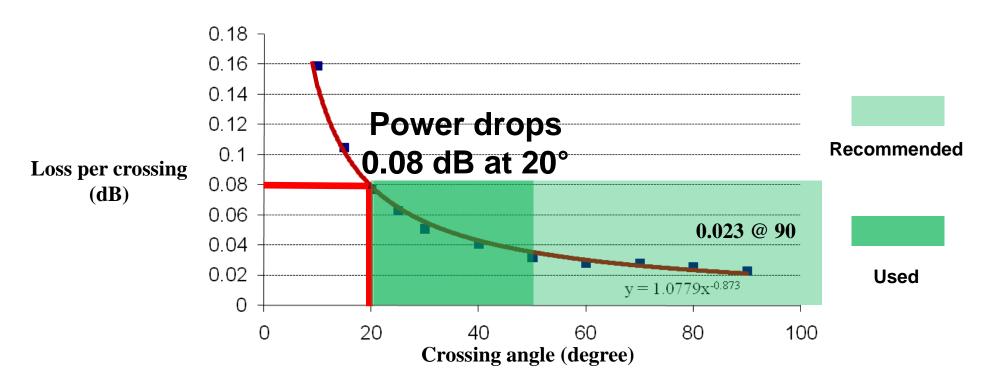

### Design Rules for Arbitrary Angle Crossings

- Loss of 0.023 dB per 90° crossing consistent with other reports

- The output power dropped by 0.5% at each  $90^{\circ}$  crossing

- The loss per crossing ( $L_c$ ) depends on crossing angle ( $\theta$ ),  $L_c$ =1.0779  $\theta$  -0.8727.

## **Loss of Waveguide Bends**

| Width (µm) | <b>Optimum Radius (mm)</b> | Maximum Power (dB) |

|------------|----------------------------|--------------------|

| 50         | 13.5                       | -0.74              |

| 75         | 15.3                       | -0.91              |

| 100        | 17.7                       | -1.18              |

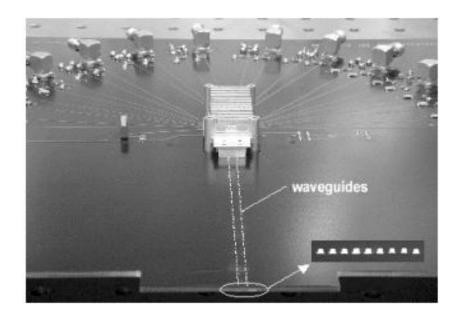

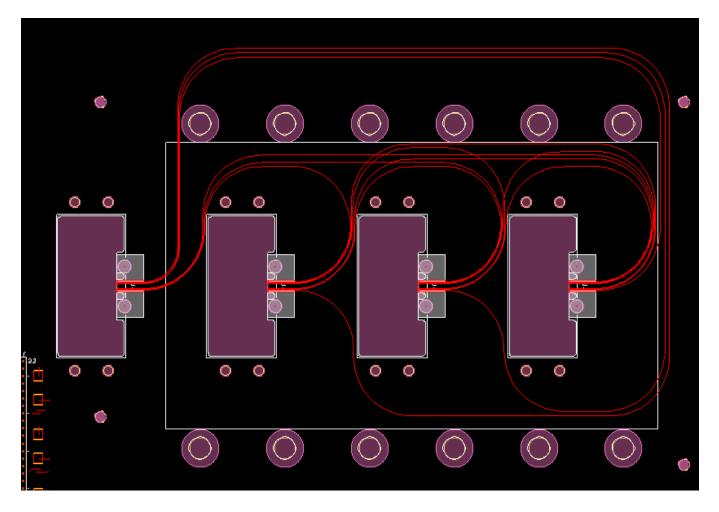

## **System Demonstrator**

Fully connected waveguide layout using design rules

Copyright © 2008 UCL

# **Power Budget**

| Input power (dBm/mW)                   |                        | -2.07 / 0.62011 |      |       |       |              |       |       |       |      |       |      |

|----------------------------------------|------------------------|-----------------|------|-------|-------|--------------|-------|-------|-------|------|-------|------|

| Input coupling loss (dB)               |                        | 2.3             |      |       |       |              |       |       |       |      |       |      |

| 90° Bends                              | Radii (mm)             | 16.5            | 17.5 | 18    | 3.5   | 19.5<br>0.89 |       | 20.5  | 22.5  | 23.5 |       | 24.5 |

|                                        | Loss per bend (dB)     | 0.94            | 0.83 | 0.8   | 85    |              |       | 0.95  | 0.97  | 0.99 |       | 1.03 |

| Propagation                            | loss (dB/cm)           | /cm) 0.06       |      |       |       |              |       |       |       |      |       |      |

| Crossing                               | Crossing angles (°)    | 22.27 29.45     |      | 36.23 |       | 42.10        |       | 47.36 |       |      |       |      |

|                                        | Loss per crossing (dB) | 0.07            | '8   | 0     | 0.056 |              | 0.047 |       | 0.041 |      | 0.037 |      |

| Output coupling loss (dB)              |                        | 2.3             |      |       |       |              |       |       |       |      |       |      |

| Min. power no bit error rate (dBm/mW)  |                        | -12 / 0.06      |      |       |       |              |       |       |       |      |       |      |

| Sensitivity of photo detector (dBm/mW) |                        | -15 / 0.03      |      |       |       |              |       |       |       |      |       |      |

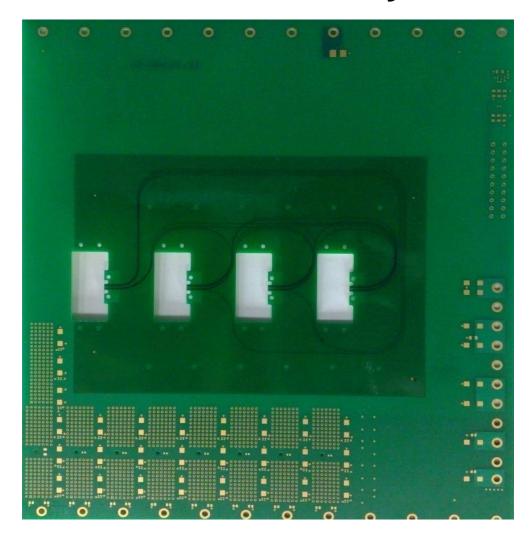

## **Demonstrator Dummy Board**

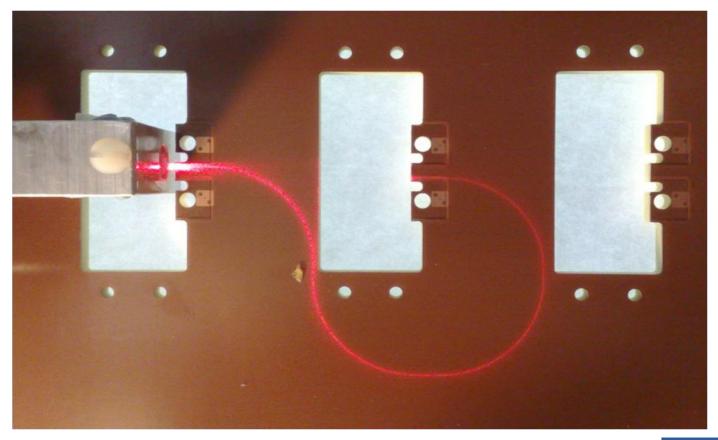

# The Shortest Waveguide Illuminated by Red Laser

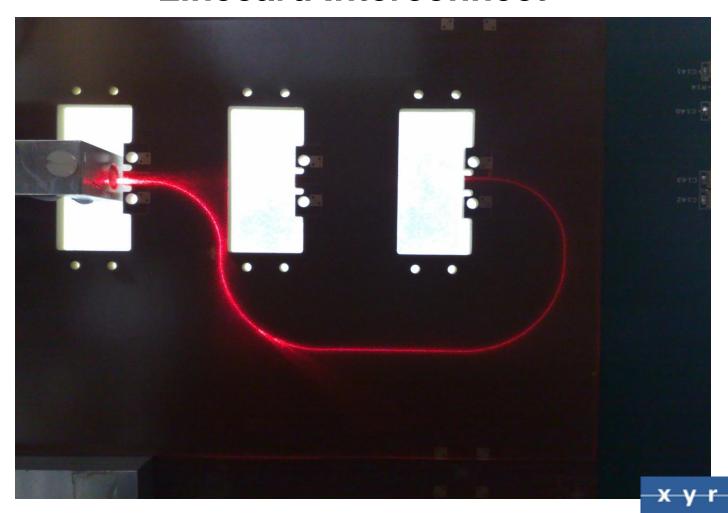

# Waveguide with 2 Crossings Connected 1<sup>st</sup> to 3<sup>rd</sup> Linecard Interconnect

## **Output Facet of the Waveguide Interconnection**

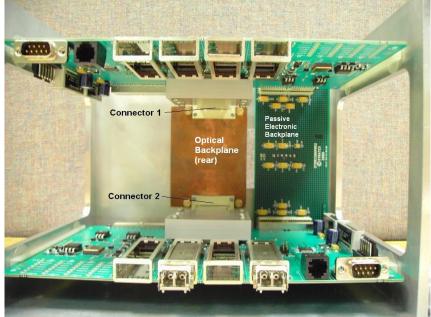

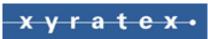

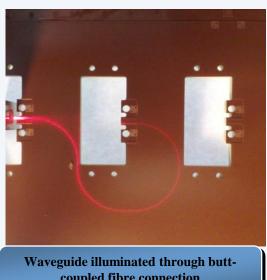

### Butt-coupled connection approach without 90° deflection optics

coupled fibre connection

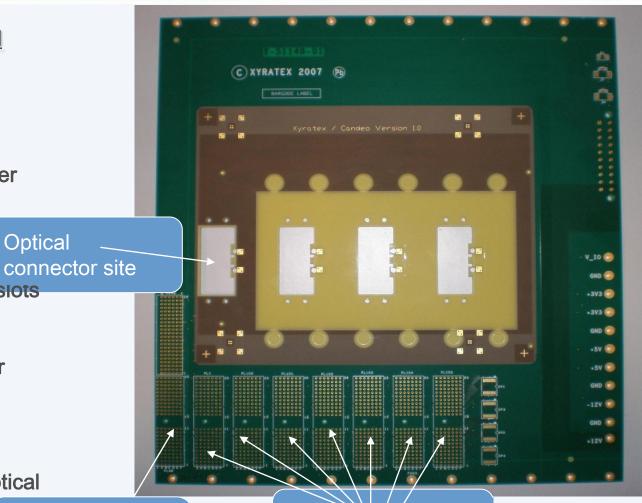

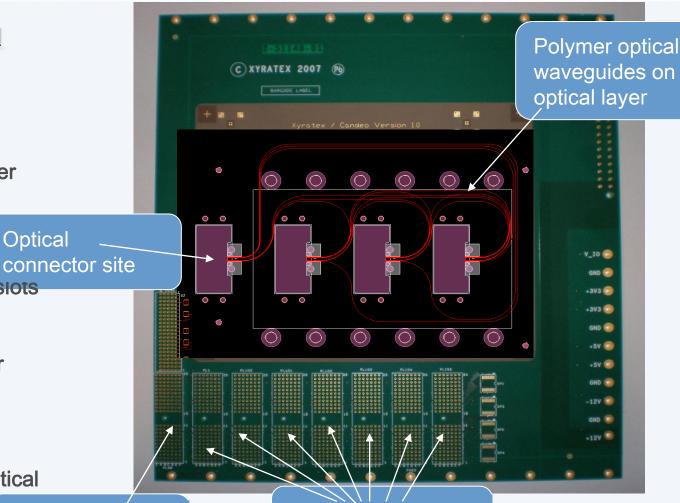

#### **ELECTRO-OPTICAL BACKPLANE**

#### **Hybrid Electro-Optical Printed Circuit Board**

☐ Standard Compact PCI

backplane architecture

☐ 12 electrical layers for power

and C-PCI signal bus and

peripheral connections

□ Electrical C-PCI connector slots

for SBC and line cards

☐ 1 polymeric optical layer for

high speed 10 GbE traffic

☐ 4 optical connector sites

☐ Dedicated point-to-point optical

waveguide architecture

Compact PCI slot for single board computer

**Optical**

Compact PCI slots for line cards

#### **ELECTRO-OPTICAL BACKPLANE**

#### **Hybrid Electro-Optical Printed Circuit Board**

☐ Standard Compact PCI

backplane architecture

☐ 12 electrical layers for power

and C-PCI signal bus and

peripheral connections

□ Electrical C-PCI connector slots

for SBC and line cards

☐ 1 polymeric optical layer for

high speed 10 GbE traffic

☐ 4 optical connector sites

☐ Dedicated point-to-point optical

waveguide architecture

Compact PCI slot for single board computer

**Optical**

Compact PCI slots for line cards

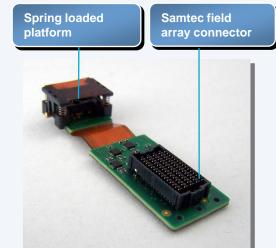

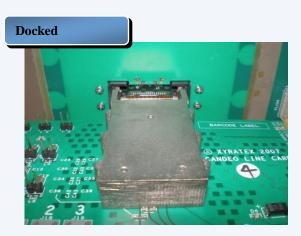

#### PARALLEL OPTICAL PCB CONNECTOR MODULE

#### Parallel optical transceiver circuit

- ☐ Small form factor quad parallel optical transceiver

- ☐ Microcontroller supporting I<sup>2</sup>C interface

- □ Samtec "SEARAY™" open pin field array connector

- ☐ Spring loaded platform for optical engagement mechanism

- ☐ Custom heatsink for photonic drivers

#### Backplane connector module

- ☐ Samtec / Xyratex collaborate to develop optical PCB connector

- ☐ 1 stage insertion engagement mechanism developed

- □ Xyratex transceiver integrated into connector module

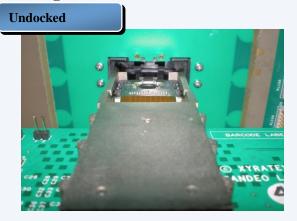

### Active Pluggable Optical Connector

#### **Engagement process**

☐ Optical transceiver interface floats

Cam followers

- ☐ Backplane receptacle "funnels" connector

- ☐ Cam followers force optical interface up

- ☐ Optical transceiver lens butt-couples to

Cam track

### backplane lens

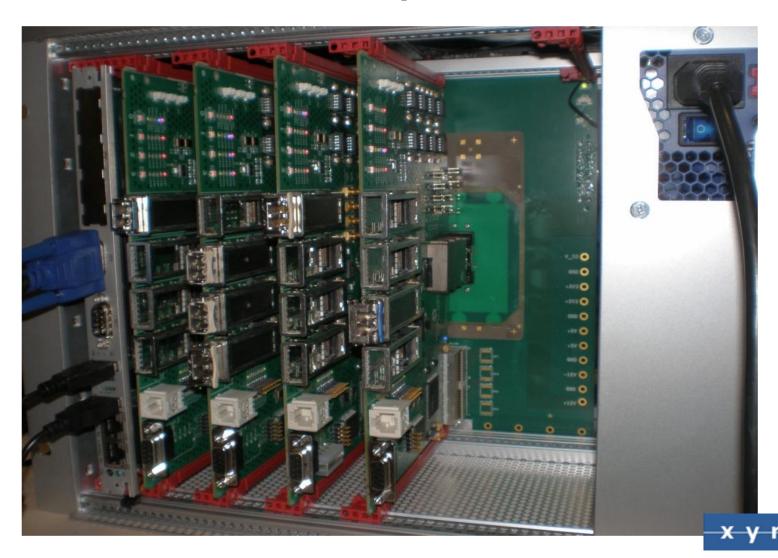

### HIGH SPEED SWITCHING LINE CARD

## **Demonstrator with Optical Interconnects**

### Demonstration Assembly

Electro-optical backplane

Pluggable optical backplane connectors

**Compact PCI chassis**

High speed switch line cards

XFP front end

Single board computer

## Acknowledgments

- University College London, UK

- Kai Wang, Hadi Baghsiahi, F. Aníbal Fernández, Ioannis Papakonstantinou (now at Sharp Labs of Europe Ltd)

- Loughborough University, UK

- David A. Hutt, Paul P. Conway, John Chappell, Shefiu S. Zakariyah

- Heriot Watt University

- Andy C. Walker, Aongus McCarthy, Himanshu Suyal

- BAE Systems, UK

- Henry White

- Stevenage Circuits Ltd. (SCL), UK

- Dougal Stewart, Jonathan Calver, Jeremy Rygate, Steve Payne

- Xyratex Technology Ltd., UK

- Dave Milward, Richard Pitwon, Ken Hopkins

- Exxelis Ltd

- Navin Suyal and Habib Rehman

- Cadence

- Gary Hinde

- EPSRC and all partner companies for funding