University of Warwick institutional repository: http://go.warwick.ac.uk/wrap

#### A Thesis Submitted for the Degree of PhD at the University of Warwick

http://go.warwick.ac.uk/wrap/54844

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

## Library Declaration and Deposit Agreement

#### 1. **STUDENT DETAILS**

| Places complete the following: |  |

|--------------------------------|--|

| Please complete the following: |  |

| Full name:            | Hui Huang |  |

|-----------------------|-----------|--|

| University ID number: | 0756774   |  |

#### 2. THESIS DEPOSIT

2.1 I understand that under my registration at the University, I am required to deposit my thesis with the University in BOTH hard copy and in digital format. The digital version should normally be saved as a single pdf file.

2.2 The hard copy will be housed in the University Library. The digital version will be deposited in the University's Institutional Repository (WRAP). Unless otherwise indicated (see 2.3 below) this will be made openly accessible on the Internet and will be supplied to the British Library to be made available online via its Electronic Theses Online Service (EThOS) service.

[At present, theses submitted for a Master's degree by Research (MA, MSc, LLM, MS or MMedSci) are not being deposited in WRAP and not being made available via EthOS. This may change in future.]

2.3 In exceptional circumstances, the Chair of the Board of Graduate Studies may grant permission for an embargo to be placed on public access to the hard copy thesis for a limited period. It is also possible to apply separately for an embargo on the digital version. (Further information is available in the *Guide to Examinations for Higher Degrees by Research*.)

2.4 If you are depositing a thesis for a Master's degree by Research, please complete section (a) below. For all other research degrees, please complete both sections (a) and (b) below:

(a) <u>Hard Copy</u>

I agree that my thesis may be photocopied.

YES /<del>NO</del> (*Please delete as appropriate*)

#### (b) Digital Copy

I hereby deposit a digital copy of my thesis to be held in WRAP and made available via EThOS.

Please choose one of the following options:

EITHER My thesis can be made publicly available online. YES / NO (Please delete as appropriate)

OR My thesis can be made publicly available only after.....[date] (Please give date) <u>YES</u> / NO (*Please delete as appropriate*)

OR My full thesis cannot be made publicly available online but I am submitting a separately identified additional, abridged version that can be made available online.

YES / NO (Please delete as appropriate)

OR My thesis cannot be made publicly available online. YES / NO (Please delete as appropriate)

#### 3. **GRANTING OF NON-EXCLUSIVE RIGHTS**

Whether I deposit my Work personally or through an assistant or other agent, I agree to the following:

Rights granted to the University of Warwick and the British Library and the user of the thesis through this agreement are non-exclusive. I retain all rights in the thesis in its present version or future versions. I agree that the institutional repository administrators and the British Library or their agents may, without changing content, digitise and migrate the thesis to any medium or format for the purpose of future preservation and accessibility.

#### 4. **DECLARATIONS**

- (a) I DECLARE THAT:

- I am the author and owner of the copyright in the thesis and/or I have the authority of the authors and owners of the copyright in the thesis to make this agreement. Reproduction of any part of this thesis for teaching or in academic or other forms of publication is subject to the normal limitations on the use of copyrighted materials and to the proper and full acknowledgement of its source.

- The digital version of the thesis I am supplying is the same version as the final, hardbound copy submitted in completion of my degree, once any minor corrections have been completed.

- I have exercised reasonable care to ensure that the thesis is original, and does not to the best of my knowledge break any UK law or other Intellectual Property Right, or contain any confidential material.

- I understand that, through the medium of the Internet, files will be available to automated agents, and may be searched and copied by, for example, text mining and plagiarism detection software.

- (b) IF I HAVE AGREED (in Section 2 above) TO MAKE MY THESIS PUBLICLY AVAILABLE DIGITALLY, I ALSO DECLARE THAT:

- I grant the University of Warwick and the British Library a licence to make available on the Internet the thesis in digitised format through the Institutional Repository and through the British Library via the EThOS service.

- If my thesis does include any substantial subsidiary material owned by third-party copyright holders, I have sought and obtained permission to include it in any version of my thesis available in digital format and that this permission encompasses the rights that I have granted to the University of Warwick and to the British Library.

#### 5. **LEGAL INFRINGEMENTS**

I understand that neither the University of Warwick nor the British Library have any obligation to take legal action on behalf of myself, or other rights holders, in the event of infringement of intellectual property rights, breach of contract or of any other right, in the thesis.

Please sign this agreement and return it to the Graduate School Office when you submit your thesis.

Student's signature: ...... Date: .....

# Lifetime Prediction for Power Converters

Hui Huang School of Engineering University of Warwick

Dissertation submitted for the degree of Doctor of Philosophy July 2012

# Declaration

The work presented in this thesis was carried out in the School of Engineering, University of Warwick, during the period October 2007 to August 2011 under the supervision of Prof. Philip Mawby.

The author wishes to declare that apart from commonly understood and accepted ideas, or where reference is made to the work of others, the work in this thesis is his own. It has not been submitted in part, or in whole, to any other university for a degree, diploma or other qualification.

H. Huang July, 2012

"To my loving parents, who offered me unconditional love and provided me with the foundation to stand upon to reach for success"

"To Yao, who has been a great source of motivation and inspiration, for her love which I cannot live without, for her patience and support which I will forever grateful"

## Acknowledgements

Firstly, I would like to my supervisors Prof. Philip Mawby for his guidance and support through out my PhD studies. His advice, encouragement and feedback is invalueable for me and I shall be forever grateful.

I would also thank Engineering and Physical Sciences Research Council (EPSRC) for their financial support of this project.

I must thank my colleagues within the PEATER group, especially Benedict Donnellan for his numerous help with my writing, Dr. C.F. Tong for his useful advices and overall help, Dr. K. K. Leong for his help on proofreading of this work and daily chat, Dr. Shaoyong Yang for his cooperation on building the power cycling rig, Dr. M. R. Jennings for his cooperation on building the gate oxide reliability test rig, Dr. D. Hamilton for his useful discussion and advices on power module packaging and reliability, Dr. Nii-Adotei Parker-Allotey for his help in the Matlab simulation. I would also like to thank Stewart Edris and his fellow technicians for their helpful advices and excellent workmanship.

Finally, I would like to thank all my friends both within the University of Warwick and elsewhere, for their support and making them an invalueable experience.

## Abstract

Renewable energy is developing rapidly and gaining more and more commercial viability. High reliability of the generation system is essential to maximize the output power. The power inverter is an important unit in this system and is believed to be one of the most unreliable parts. In the case of wind power generation, especially in off-shore wind, when the system reliability requirement is high, a technique to predict the inverter lifetime is invaluable as it would help the inverter designer optimize his design for minimal maintenance.

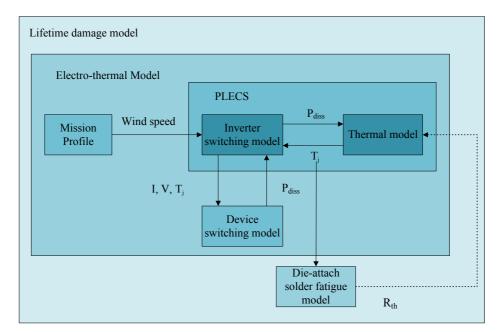

Previous researchers studying inverter lifetime prediction, focus either at device level such as device fatigue damage models, or at system level which require experimental data for their selected device. This work presents a new method to estimate the inverter lifetime from a given mission profile within a reasonable simulation time. Such model can be used as a converter design tool or an on-line lifetime estimation tool after being configured to a real converter system.

The key contribution of this work is to link the physics of the power devices to a large scale system simulation within a reasonable framework of time. With this technique, the system down time can be reduced and therefore more power can be generated. Also, the failure damage to the system is avoided which reduces the maintenance cost. A power cycling test is designed to gather the lifetime data of a selected IGBT module. Die-attach solder fatigue is found out to be the dominant failure mode of this IGBT module. The accuracy of widely accepted Miner's rule, which accumulates damage linearly, is discussed and a nonlinear accumulation method is promoted to predict the lifetime of power inverters.

# Contents

### Nomenclature

| 1        | Intr | oducti  | on                                                              | 1  |

|----------|------|---------|-----------------------------------------------------------------|----|

|          | 1.1  | Energy  | y Security and Low-carbon Society                               | 1  |

|          | 1.2  | The R   | ole of Power Electronics in Energy Efficiency                   | 4  |

|          | 1.3  | Overvi  | iew of Reliability Problems                                     | 6  |

|          | 1.4  | Scope   | of the Thesis                                                   | 10 |

| <b>2</b> | Pow  | ver Ele | ctronics Physics and Modelling Technique                        | 14 |

|          | 2.1  | Basic I | Physics of Power Electronic Devices                             | 14 |

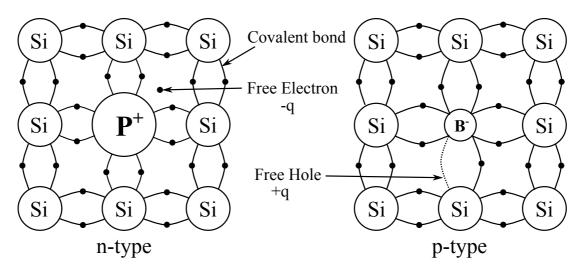

|          |      | 2.1.1   | Conduction Processes in Silicon                                 | 15 |

|          |      |         | 2.1.1.1 Free carriers: Holes and Electrons                      | 15 |

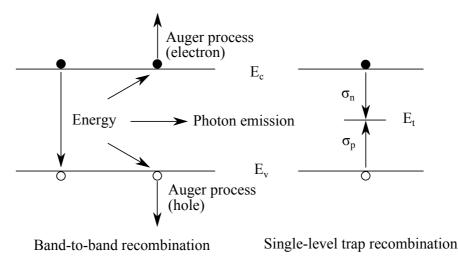

|          |      |         | 2.1.1.2 Recombination                                           | 18 |

|          |      |         | 2.1.1.3 Drift and Diffusion                                     | 22 |

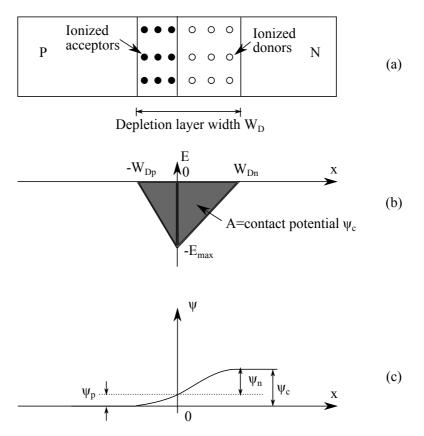

|          |      | 2.1.2   | PN Junction                                                     | 24 |

|          |      |         | 2.1.2.1 Thermal Equilibrium                                     | 24 |

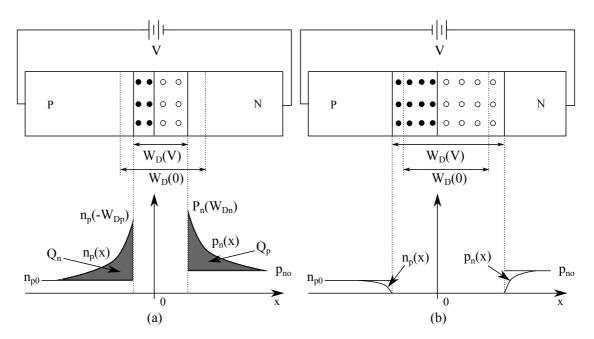

|          |      |         | 2.1.2.2 Forward and Reverse Bias                                | 27 |

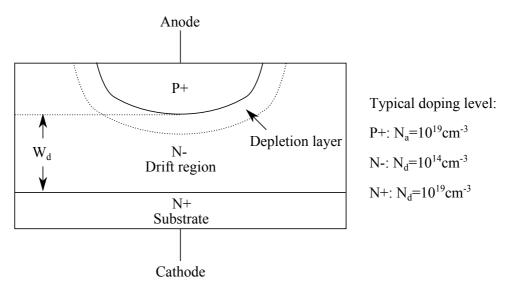

|          |      | 2.1.3   | Power Diode Structure and Operation                             | 32 |

|          |      |         | 2.1.3.1 Basic Structure and Principles of Power Diode           | 32 |

|          |      |         | 2.1.3.2 Switching characteristics of Power Diode                | 36 |

|          |      | 2.1.4   | IGBT Structure and Operation                                    | 39 |

|          |      |         | 2.1.4.1 Basic Structure and Principles of IGBT                  | 39 |

|          |      |         | 2.1.4.2 Switching characteristics of IGBT                       | 43 |

|          | 2.2  | Physic  | s Based IGBT and Diode Model                                    | 48 |

|          |      | 2.2.1   | Review of Device Modelling Technique                            | 48 |

|          |      | 2.2.2   | Fundamentals of the ADE model based on Fourier series solutions | 50 |

|          |      | 2.2.3   | Temperature Effects                                             | 54 |

| 3        | Phy  | sics of | Power Module Package Failures                                   | 59 |

|          | 3.1  | Introd  | uction to Packaging Technology for Power Modules                | 59 |

|          | 3.2  | Reliab  | ility Estimation via Physics of Failure Approach                | 64 |

|          |      | 3.2.1 Basic Physics of Bond Wire Lift Off                    |

|----------|------|--------------------------------------------------------------|

|          |      | 3.2.2 Basic Physics of Solder Fatigue                        |

|          | 3.3  | Brief Introduction to Other Power Module Failures            |

| <b>4</b> | Inve | erter Electrothermal Model 74                                |

|          | 4.1  | Parameterisation of Device Switching Model                   |

|          |      | 4.1.1 Inductive Switching Test                               |

|          |      | 4.1.2 Initial Parameter Extraction of Device Switching Model |

|          |      | 4.1.3 Optimisation of the Extracted Parameters               |

|          |      | 4.1.4 Look Up Tables for IGBT and Diode Power Loss           |

|          | 4.2  | Thermal Network Extraction for IGBT Module and Heatsink 90   |

|          |      | 4.2.1 Principles of Heat Propagation                         |

|          |      | 4.2.2 Initial Thermal Network Extraction                     |

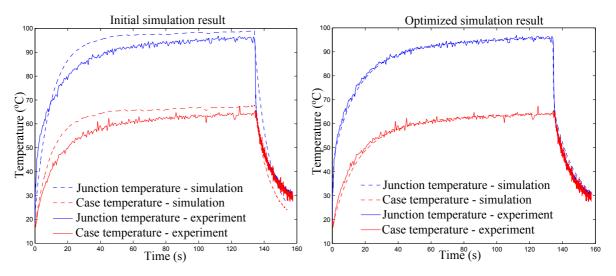

|          |      | 4.2.3 Optimisation of Extracted Thermal Network              |

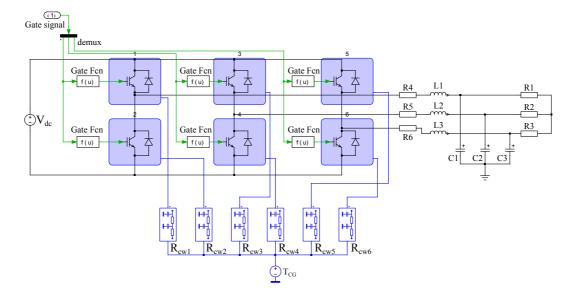

|          | 4.3  | Inverter Electrothermal Model in PLECS                       |

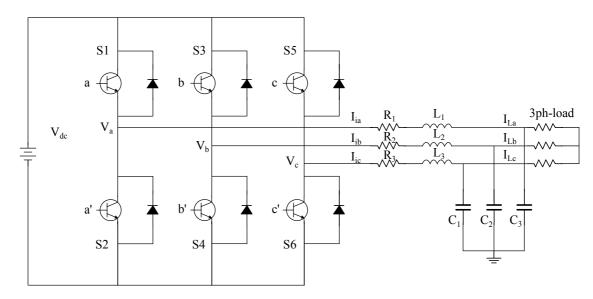

|          |      | 4.3.1 Main Electrical and Thermal Circuit                    |

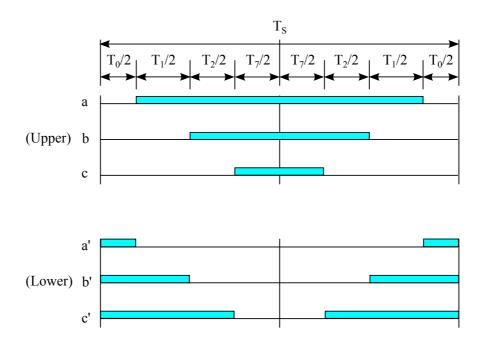

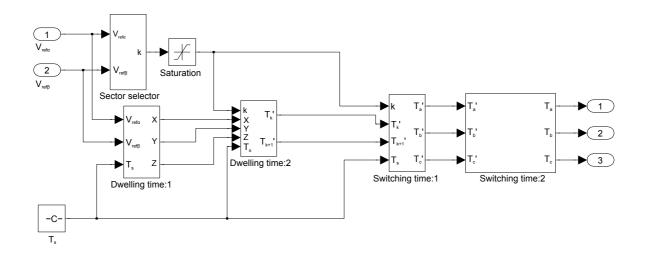

|          |      | 4.3.2 Gate Drive Control: Space Vector PWM                   |

| <b>5</b> | Des  | ign of the Power Cycling Rig and Test 108                    |

|          | 5.1  | System Configuration of Power Cycling Test                   |

|          |      | 5.1.1 Main Electrical System                                 |

|          |      | 5.1.2 Water Cooling System                                   |

|          |      | 5.1.3 Control and Data Acquisition System                    |

|          | 5.2  | System Calibration and Preparation Before Test               |

|          |      | 5.2.1 Calibration of Junction Temperature Measurement        |

|          |      | 5.2.2 Calibration of Thermocouples                           |

|          | 5.3  | Design of Power Cycling Test and Data Processing             |

|          | 5.4  | Conclusions                                                  |

| 6        | Inve | erter lifetime Damage Model 134                              |

|          | 6.1  | Thermomechanical models of the IGBT module                   |

|          | 6.2  | Cycle counting method                                        |

|          | 6.3  | Fatigue damage accumulation method                           |

|          | 6.4  | Conclusions                                                  |

| 7        | Cas  | e Study: Wind Power Application 160                          |

|          | 7.1  | Inverter Electrothermal Modelling for Wind Power Application |

|          |      | 7.1.1 Wind Power Generation System                           |

|          |      | 7.1.2 Inverter Current Control Technique                     |

|          |      | 7.1.3 Inverter Electrothermal Simulation                     |

|          | 7.2  | Inverter Lifetime Prediction                                 |

#### CONTENTS

|              | 7.3   | 7.2.1<br>7.2.2<br>7.2.3<br>Conclu | Rainflow Cycle Counting of the Temperature Profile       | $\begin{array}{c} 173 \\ 176 \end{array}$ |

|--------------|-------|-----------------------------------|----------------------------------------------------------|-------------------------------------------|

| 8            | Con   | clusio                            | ns and Future work                                       | 180                                       |

|              | 8.1   | Conclu                            | sions                                                    | 180                                       |

|              | 8.2   | Sugges                            | stions for Further Work                                  | 183                                       |

|              |       | 8.2.1                             | Obtain More Power Cycling Data                           | 183                                       |

|              |       | 8.2.2                             | Inverter Model Validation                                |                                           |

|              |       | 8.2.3                             | Optimum Wind Turbine Control                             | 184                                       |

| A            | Pub   | olicatio                          | n                                                        | 185                                       |

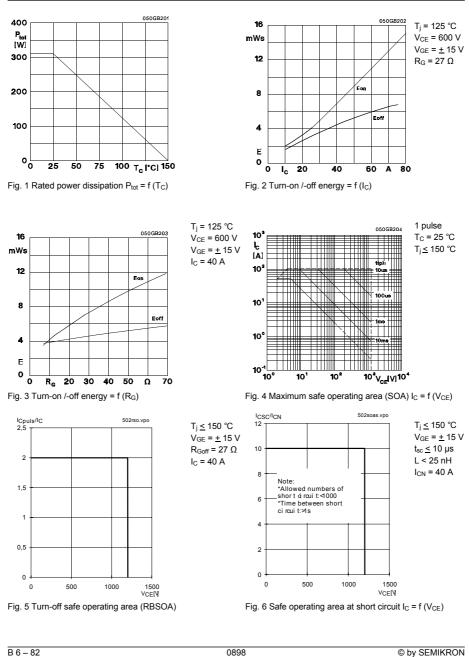

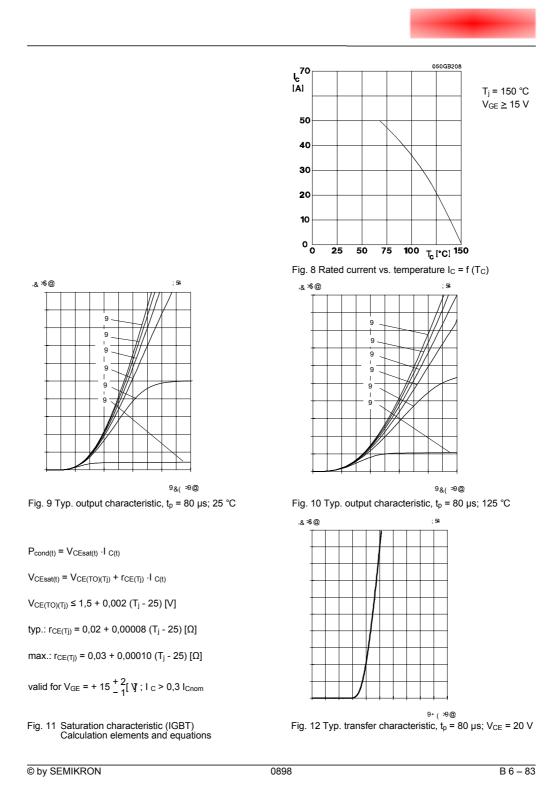

| В            | Dat   | a Shee                            | et of Selected IGBT Module                               | 186                                       |

| $\mathbf{C}$ | Mat   | tlab Co                           | odes                                                     | 193                                       |

|              | C.1   | Find H                            | Extreme Points                                           | 193                                       |

|              | C.2   | Locate                            | e Switching Start/End Point                              | 196                                       |

|              | C.3   | Rainfl                            | ow Cycle Counting Code                                   | 201                                       |

|              | C.4   | Nonlir                            | hear Damage Accumulation Code                            | 205                                       |

| D            | Pow   | ver Cy                            | cling Rig                                                | 208                                       |

|              |       | •                                 | ol Flow Chart Diagram of Thermal Network Extraction Test | 208                                       |

|              |       |                                   | ist of Data Acquisition System                           |                                           |

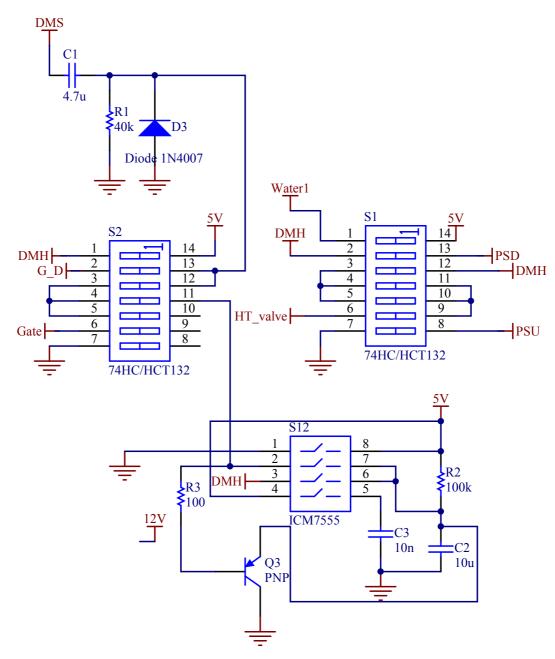

|              |       |                                   | t Diagram for the DMH                                    |                                           |

| Re           | efere | nces                              |                                                          | 212                                       |

# List of Figures

| 1.1  | Energy consumption from different sources in 2008                                               | 2  |

|------|-------------------------------------------------------------------------------------------------|----|

| 1.2  | Examples of renewable energy power plant                                                        | 3  |

| 1.3  | IGBT module and different layers of packaging                                                   | 5  |

| 1.4  | Typical example of power electronics and their applications.                                    | 6  |

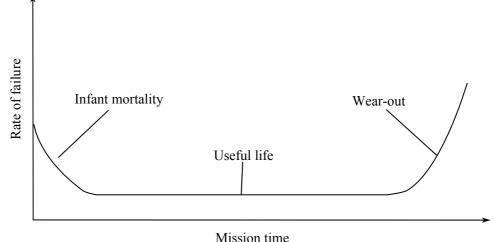

| 1.5  | Idealized bathtub curve.                                                                        | 7  |

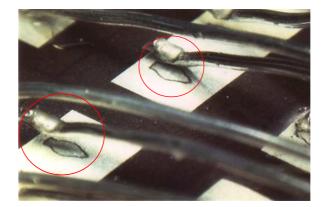

| 1.6  | Two common failure mechanisms.                                                                  | 10 |

| 1.7  | Framework of lifetime damage model                                                              | 11 |

| 2.1  | Silicon lattice dope with phosphorous (n-type) and boron (p-type).                              | 17 |

| 2.2  | Recombination mechanisms.                                                                       | 18 |

| 2.3  | PN junction in thermal equilibrium. (a) Space charge distribution. (b) Elec-                    |    |

|      | tric field distribution. (c) Potential distribution                                             | 25 |

| 2.4  | PN junction and its minority carrier densities in each side when it is (a)                      |    |

|      | forward biased and (b) reverse biased                                                           | 28 |

| 2.5  | Cross section view of a typical p-i-n diode. $W_d$ indicates the drift region width.            | 33 |

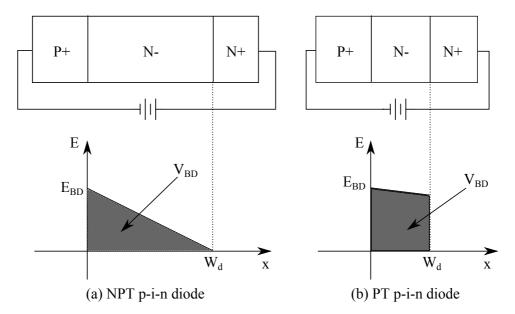

| 2.6  | The distribution of depletion layer in (a) NPT and (b) PT p-i-n diode. $\ldots$                 | 34 |

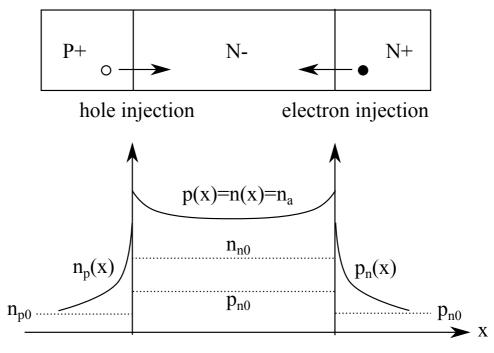

| 2.7  | Conductivity modulation.                                                                        | 35 |

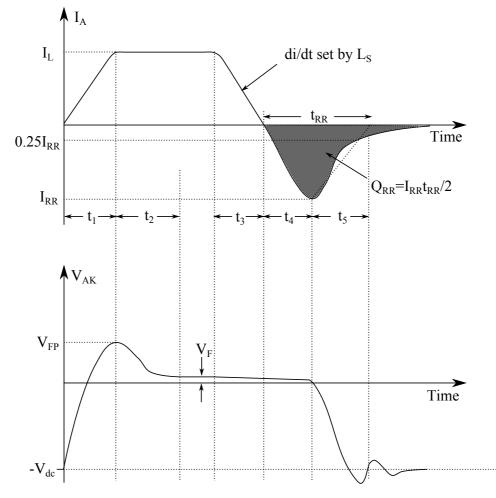

| 2.8  | Power diode switching waveforms                                                                 | 37 |

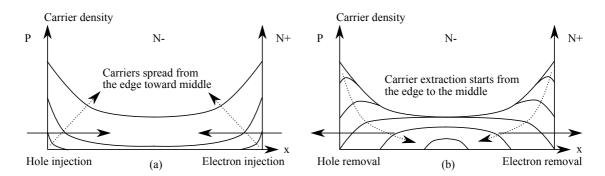

| 2.9  | Carrier distribution in the drift region during (a) turn-on and (b) turn-off.                   | 38 |

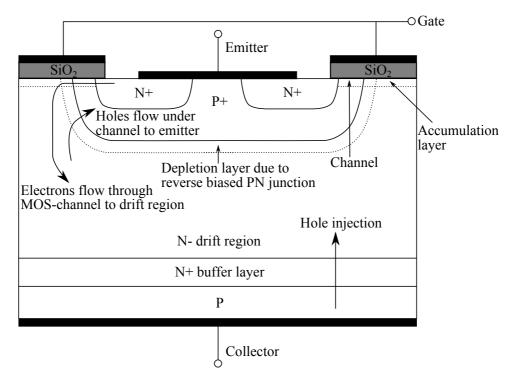

| 2.10 | Basic IGBT structure and its behavior in the on-state.                                          | 40 |

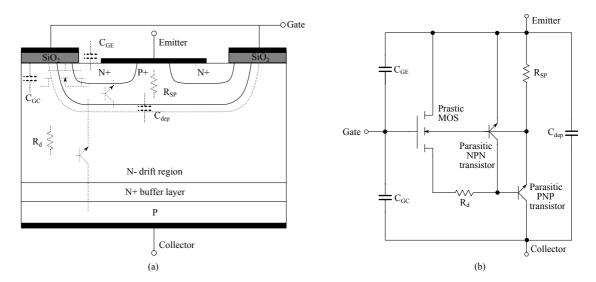

| 2.11 | (a) IGBT structure with parasitic components and (b) accurate IGBT equiv-                       |    |

|      | alent circuit.                                                                                  | 42 |

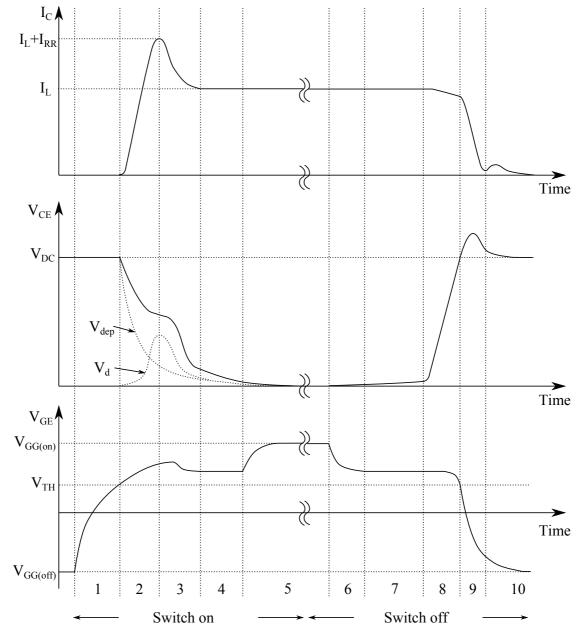

|      | Detailed IGBT switching waveforms under inductive load condition                                | 44 |

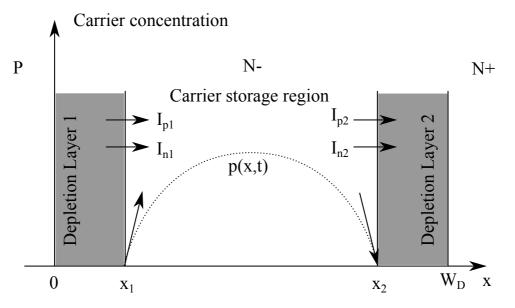

|      | General arrangement of the depletion layers and CSR in the drift region                         | 52 |

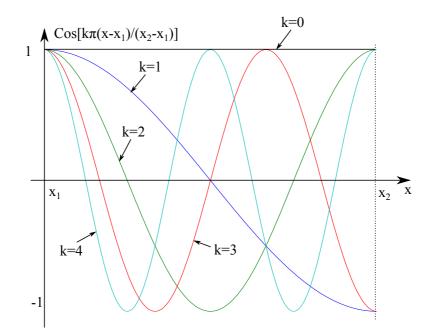

|      | Carrier density profiles for odd and even term in the Fourier series                            | 53 |

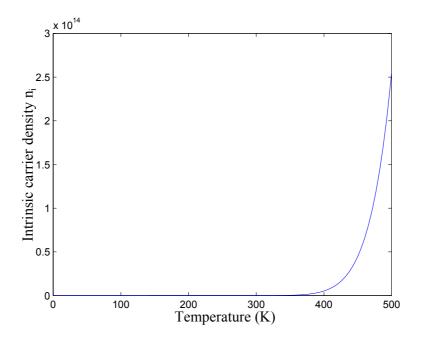

|      | Intrinsic carrier density changes with temperature                                              | 55 |

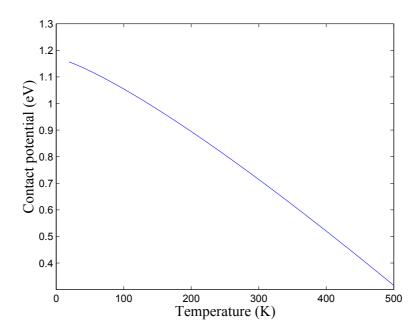

|      | Contact potential changes with temperature                                                      | 56 |

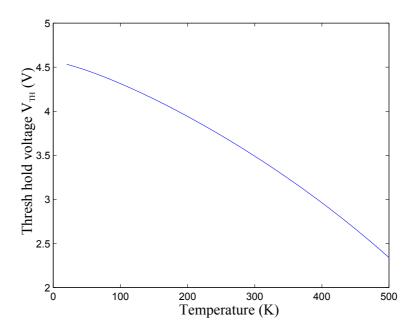

| 2.17 | Threshold voltage changes with temperature                                                      | 58 |

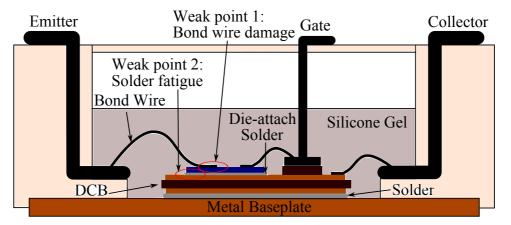

| 3.1  | Cross section view of a conventional power module. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 60 |

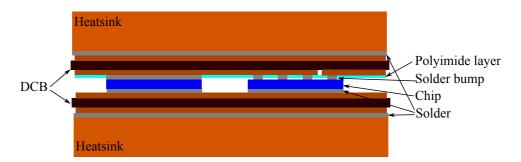

| 3.2  | Cross section view of the double sided cooling IGBT module                                      | 62 |

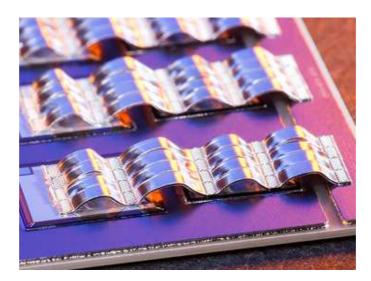

| 3.3  | Ribbon bonds $[1]$ .                                                                 | 63  |

|------|--------------------------------------------------------------------------------------|-----|

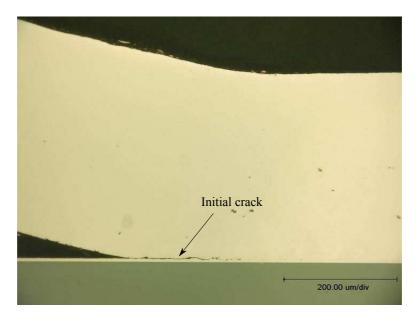

| 3.4  | Initial crack at the heel of bond wire [2]                                           | 65  |

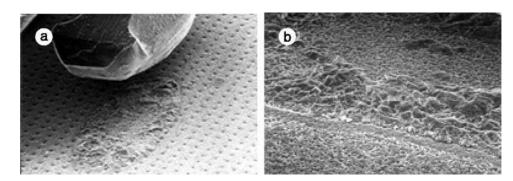

| 3.5  | Crack propagation by ductile tearing [3]                                             | 66  |

| 3.6  | (a) Scanning electron microscope (SEM) image of bond wire lift off, (b) foot-        |     |

|      | print of Al bond wire after lift off [4]                                             | 67  |

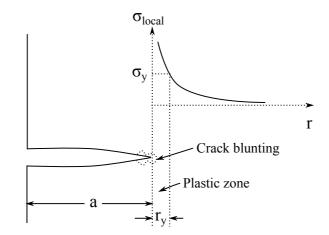

| 3.7  | Illustration of fatigue crack propagation.                                           | 69  |

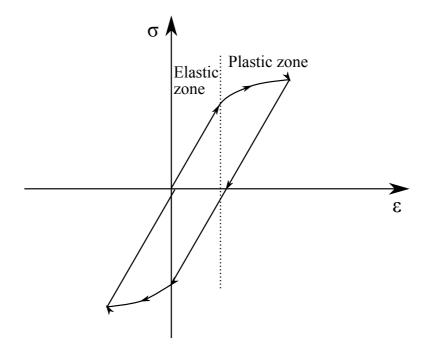

| 3.8  | Hysteresis loop for the solder fatigue process for one stress cycle                  | 70  |

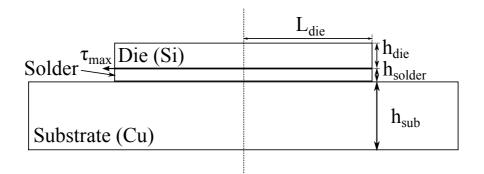

| 3.9  | Three layer structure of the electronic device assembly                              | 70  |

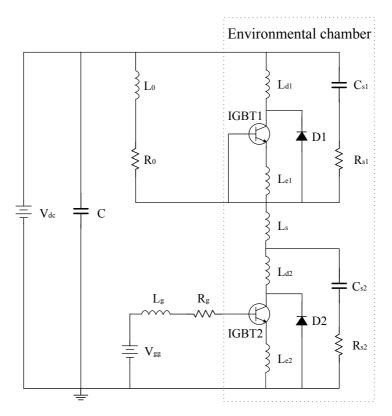

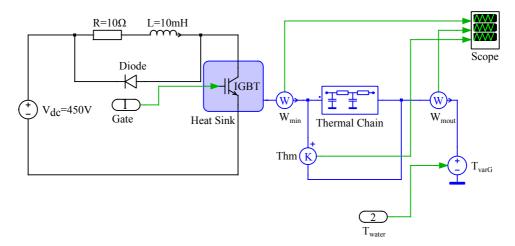

| 4.1  | Circuit diagram for the inductive switching test                                     | 76  |

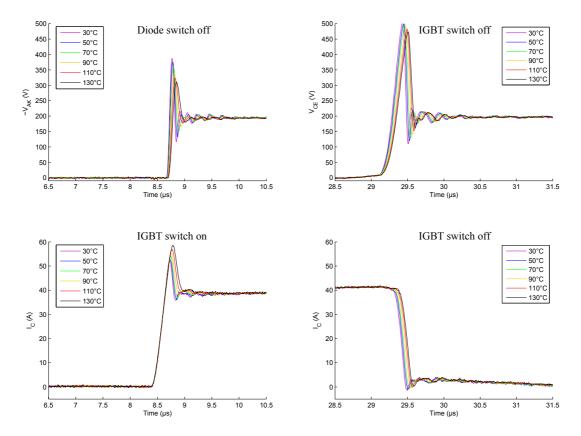

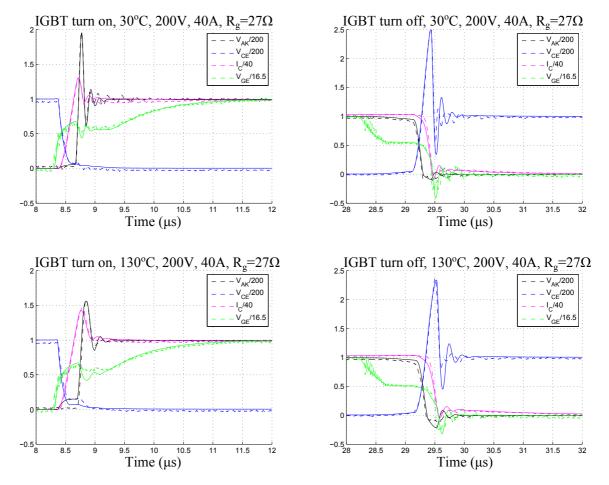

| 4.2  | Inductive switching waveforms at 30 $^{\circ}$ C (left) and 130 $^{\circ}$ C (right) | 77  |

| 4.3  | Comparison of switching waveforms at different temperatures                          | 78  |

| 4.4  | Forward V-I characteristics of IGBT for parameter extraction                         | 83  |

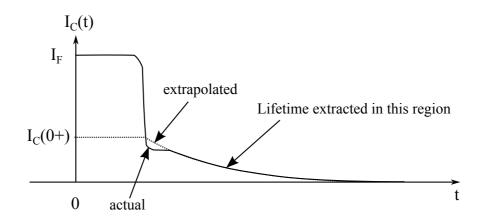

| 4.5  | IGBT turn off current waveform                                                       | 83  |

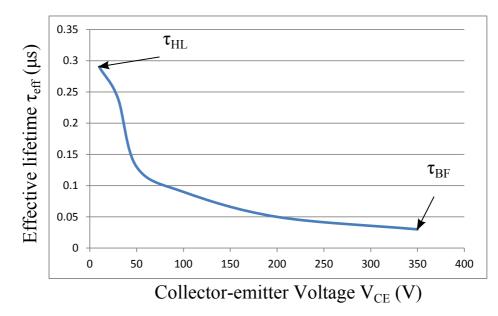

| 4.6  | Effective lifetime extraction under different clamped voltage for PT IGBT.           | 84  |

| 4.7  | Comparison of simulation and experimental switching waveforms at different           |     |

|      | temperatures                                                                         | 86  |

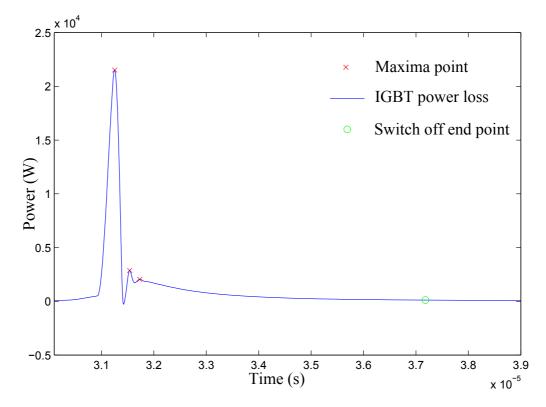

| 4.8  | Demonstration of the algorithm for determine the switching region                    | 88  |

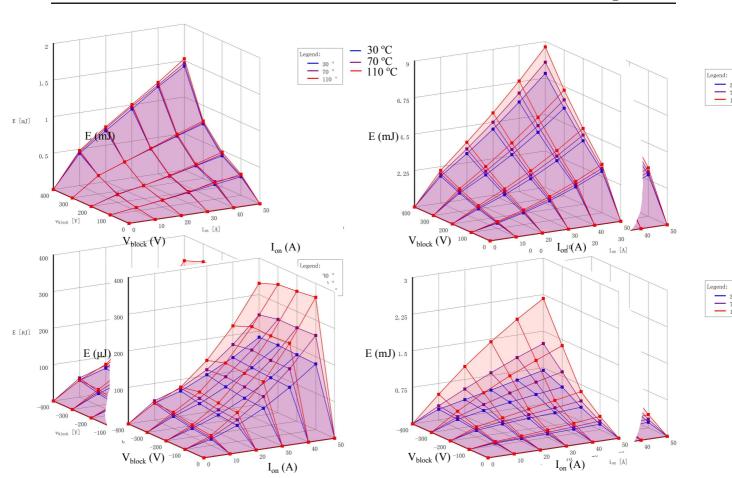

| 4.9  | IGBT and diode switching loss LUTs. Top-left: IGBT turn-on loss; top-right:          |     |

|      | IGBT turn-off loss; bottom left: diode turn-on loss; bottom right: diode turn-       |     |

|      | off loss                                                                             | 89  |

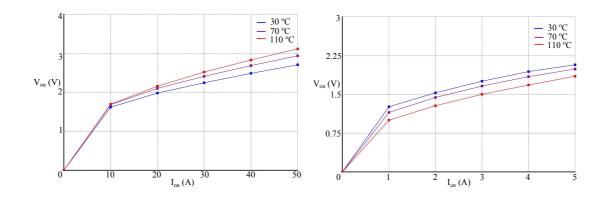

|      | IGBT (left) and diode (right) on-state power loss LUTs                               | 90  |

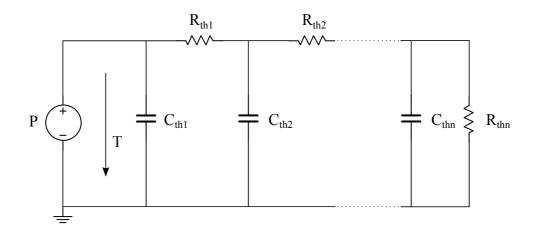

| 4.11 | Electrical transmission line equivalent circuit diagram (Cauer network) for          |     |

|      | modeling heat conduction properties                                                  | 91  |

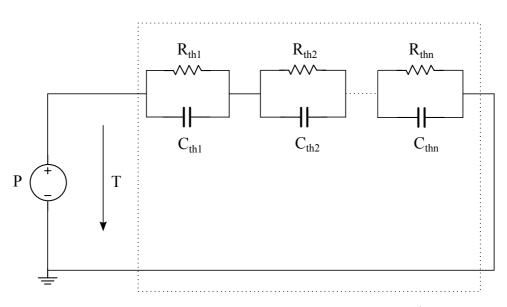

| 4.12 | Electrical transmission line equivalent circuit diagram (Foster network) for         |     |

|      | modeling heat conduction properties                                                  | 93  |

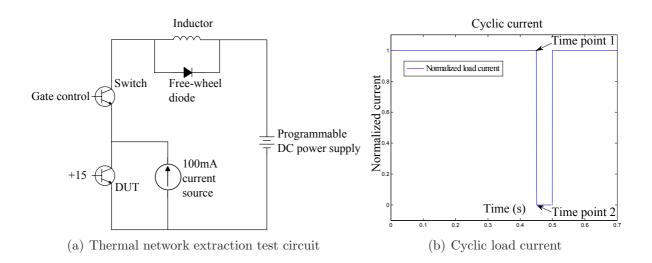

|      | Thermal network extraction                                                           | 94  |

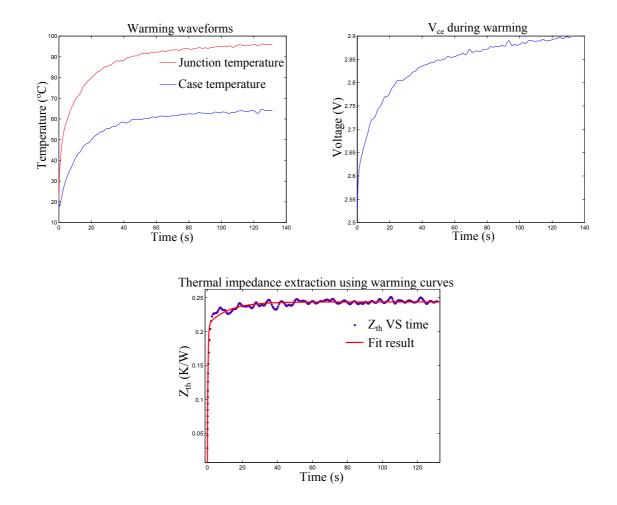

| 4.14 | Junction to case thermal impedance extraction: heating curves (up two) and           |     |

|      | fitting result (down).                                                               | 95  |

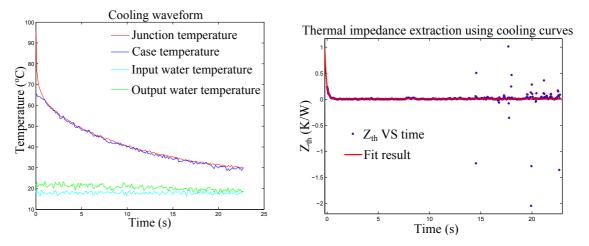

| 4.15 | Junction to case thermal impedance extraction: cooling curves (left) and fit-        |     |

|      | ting result (right)                                                                  | 96  |

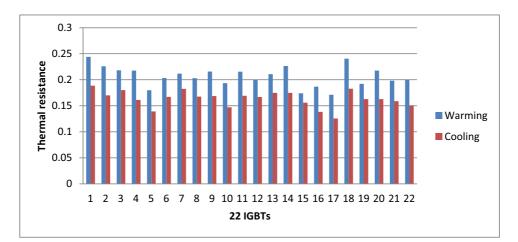

|      | Comparison of two thermal impedance extraction methods                               | 97  |

| 4.17 | 1                                                                                    | 98  |

|      | Simulation of thermal impedance extraction test                                      | 98  |

|      | 1 0                                                                                  | 100 |

| 4.20 | 1                                                                                    | 101 |

| 4.21 | 8                                                                                    | 103 |

| 4.22 |                                                                                      | 104 |

|      | 01                                                                                   | 106 |

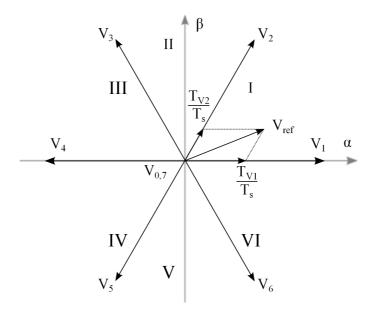

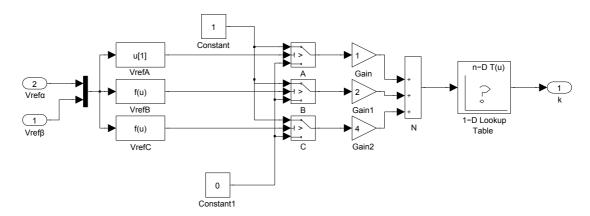

| 4.24 | SVPWM generator model                                                                | 107 |

#### LIST OF FIGURES

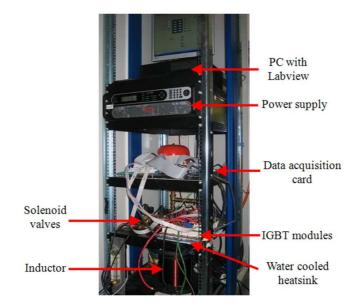

| 5.1  | Power cycling rig designed to investigate the temperature effects on IGBT                                       |     |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

|      | module lifetime                                                                                                 | 110 |

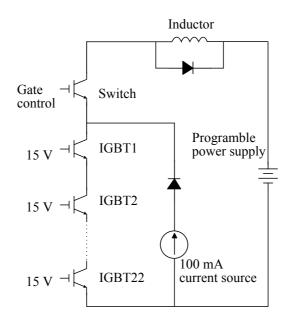

| 5.2  | Main electrical circuit diagram of the power cycling rig                                                        | 111 |

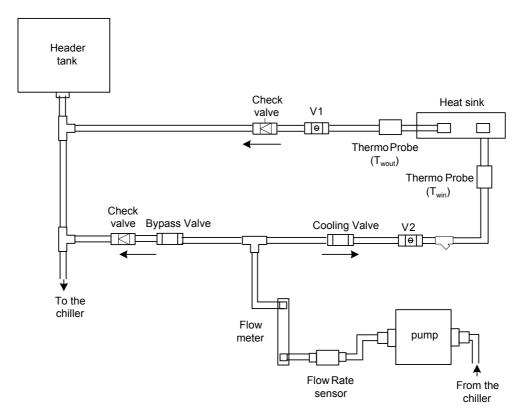

| 5.3  | The configuration of water cooling system                                                                       | 112 |

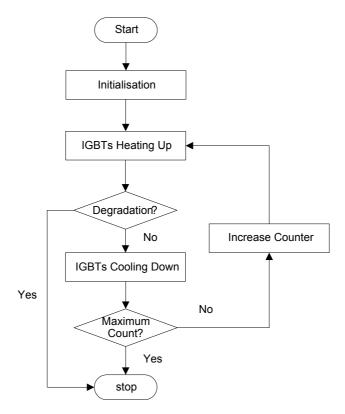

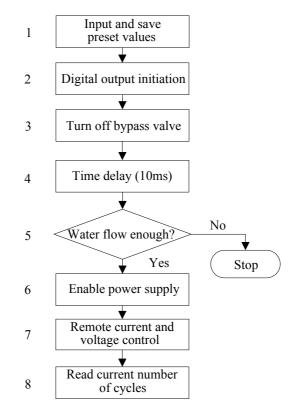

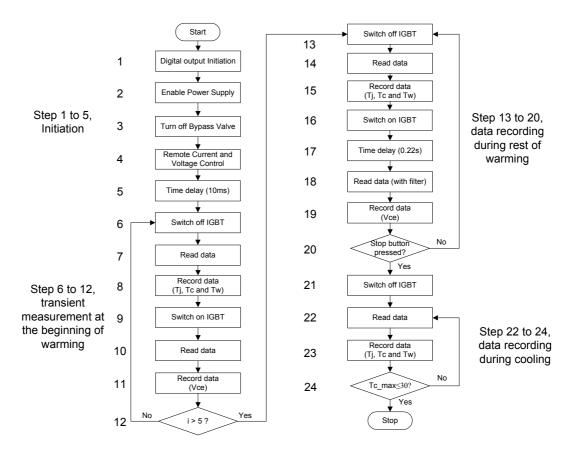

| 5.4  | Simplified control algorithm of power cycling test                                                              | 113 |

| 5.5  | Detailed flow chart for initialisation                                                                          | 114 |

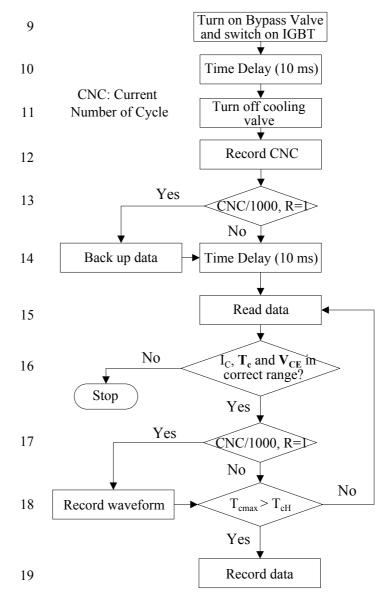

| 5.6  | Detailed flow chart for IGBT heating phase.                                                                     | 115 |

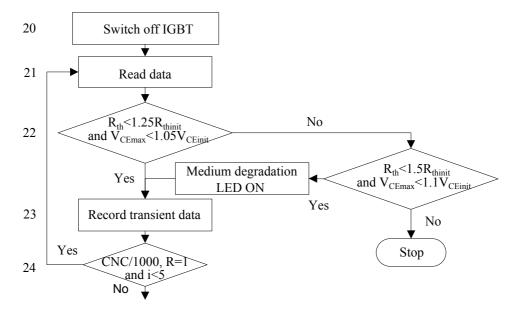

| 5.7  | Detailed flow chart for IGBT degradation check.                                                                 | 117 |

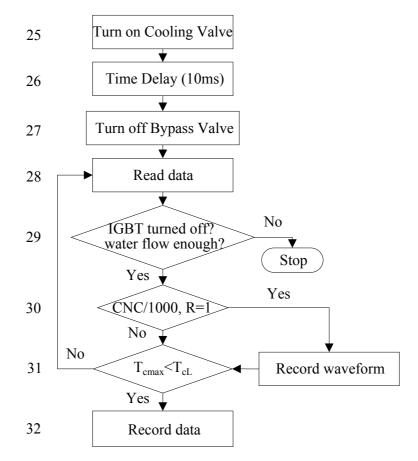

| 5.8  | Detailed flow chart for IGBT cooling phase.                                                                     | 119 |

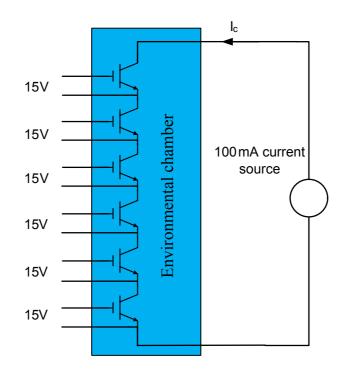

| 5.9  | Test configuration of junction temperature measurement calibration                                              | 121 |

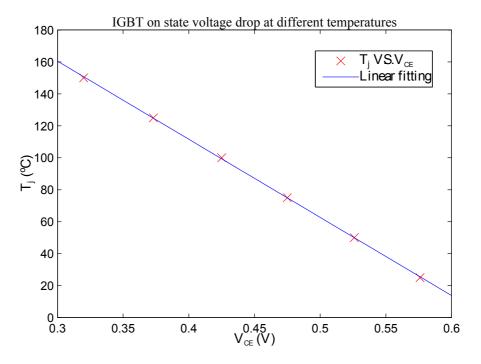

| 5.10 | Calibration result of junction temperature measurement                                                          | 122 |

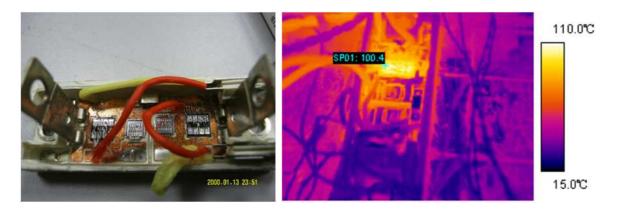

|      | IGBT module under test                                                                                          | 123 |

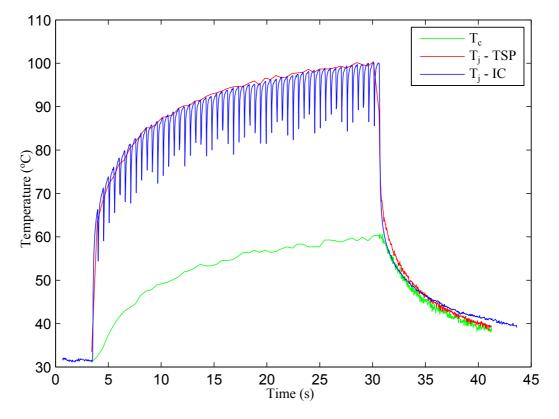

|      | Comparing the $T_j$ measured by TSP and IC                                                                      | 124 |

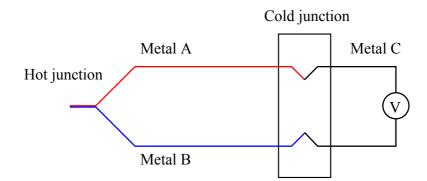

|      | Principle of thermocouple.                                                                                      | 124 |

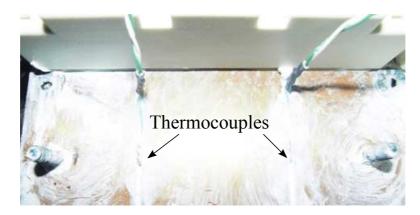

|      | Thermocouple placement.                                                                                         | 125 |

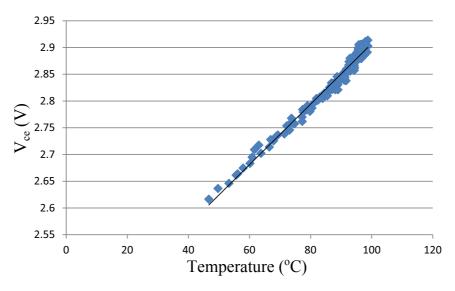

|      | Calibration of $V_{CE}$ versus $T_j$ at 50 A                                                                    | 127 |

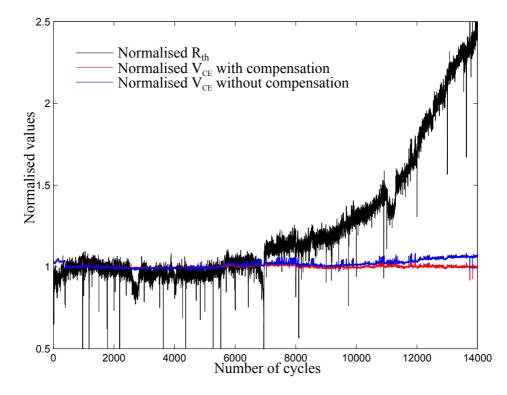

|      | Comparison of $V_{CE}$ measurement with and without temperature compensation                                    |     |

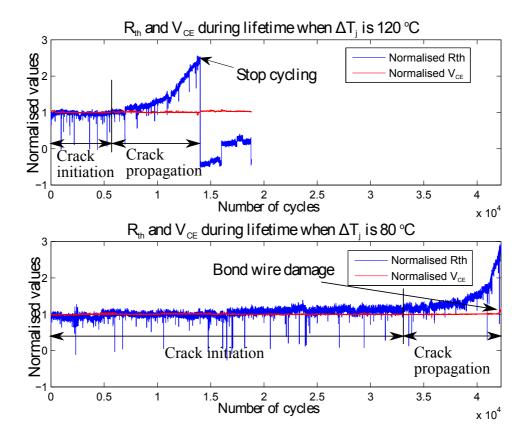

|      | Typical results of power cycling test1 (lower) and test2 (upper)                                                | 130 |

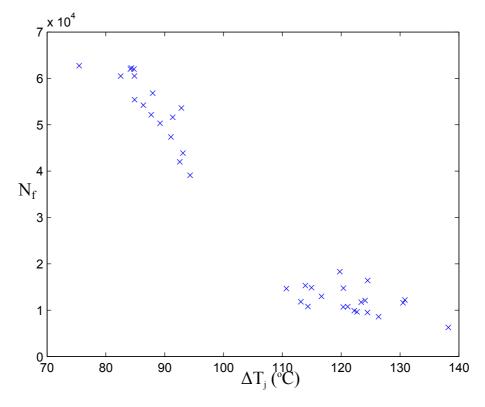

| 5.18 | Lifetime data of all IGBTs with different $\Delta T_j$                                                          | 132 |

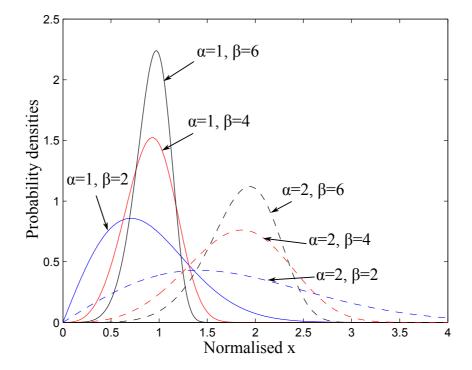

| 6.1  | Weibull probability density distribution variation due to the change of param-                                  |     |

| 0.1  | eters                                                                                                           | 136 |

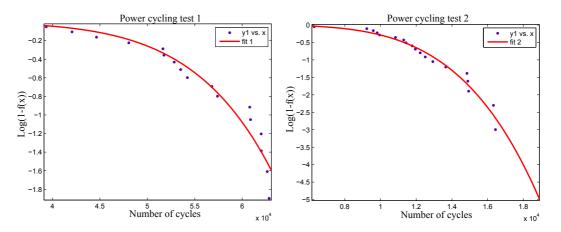

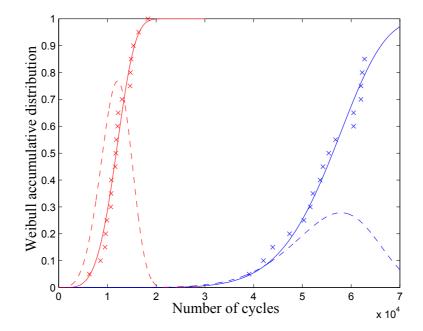

| 6.2  | Fitting results for the modified Weibull accumulative distribution.                                             | 137 |

| 6.3  | Fitted results for the Weibull accumulative and probability density distribu-                                   |     |

|      | tion, blue indicates the results for power cycling test 1 and red indicates the                                 |     |

|      | results for power cycling test 2.                                                                               | 138 |

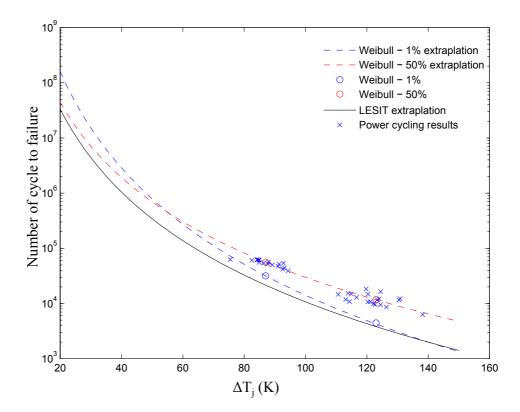

| 6.4  | Comparison of the power cycling results with LESIT results                                                      | 140 |

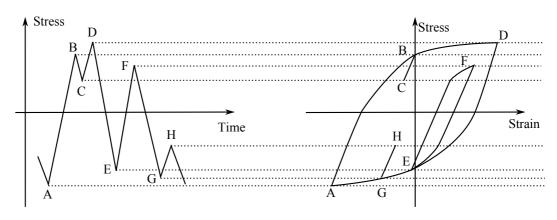

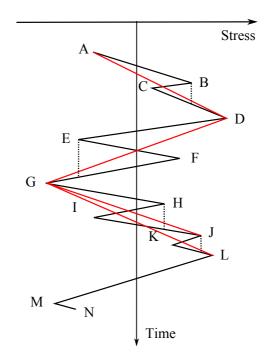

| 6.5  | Rainflow cycle counting method based on hysteresis loops                                                        | 142 |

| 6.6  | Original algorithm of rainflow cycle counting method, where red indicates the                                   |     |

|      | flow from valley and blue indicates the flow from peak                                                          | 143 |

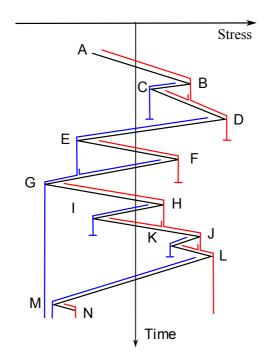

| 6.7  | Illustration of practical rainflow algorithm.                                                                   | 147 |

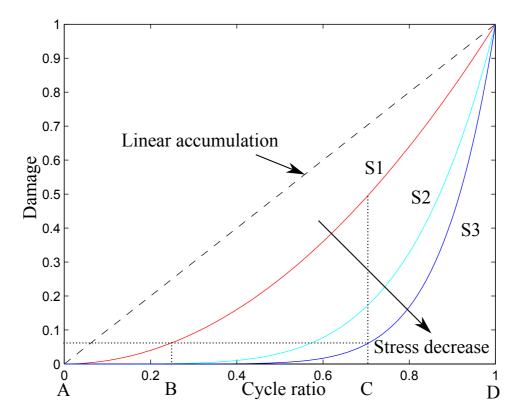

| 6.8  | Comparison of D-r curves for the linear and nonlinear rule for damage accu-                                     |     |

|      | mulation. Where, S1, S2 and S3 indicates the nonlinear damage accumulation                                      |     |

|      | under different stress levels, while A, B, C and D indicates different lifetime                                 |     |

|      | point                                                                                                           | 149 |

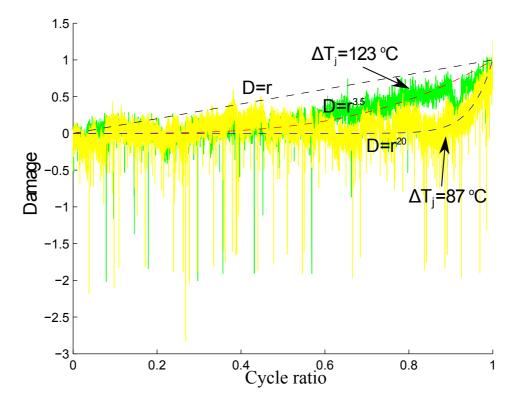

| 6.9  | Typical D-r curves of both sets of power cycling tests                                                          | 150 |

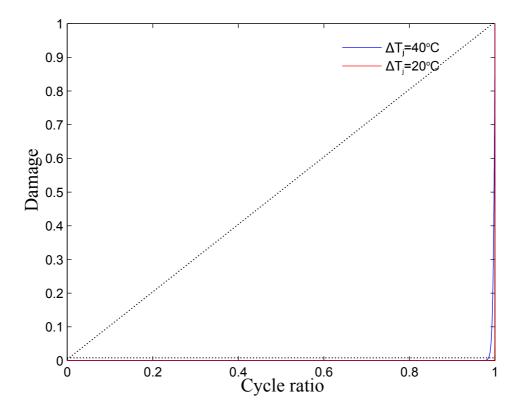

| 6.10 | D-r curves for small temperature cycles.                                                                        | 154 |

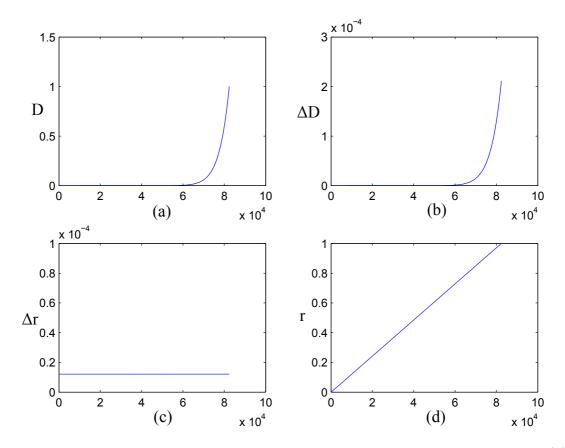

| 6.11 | Validation of nonlinear accumulation method with constant stress, (a) accu-                                     |     |

|      | mulated damage during lifetime, (b) damage per cycle during lifetime, (c) $\Delta r$                            |     |

|      | per cycle during lifetime, (d) accumulated $r$ during lifetime. x axis indicates                                |     |

|      | the number of cycles. $\ldots$ | 155 |

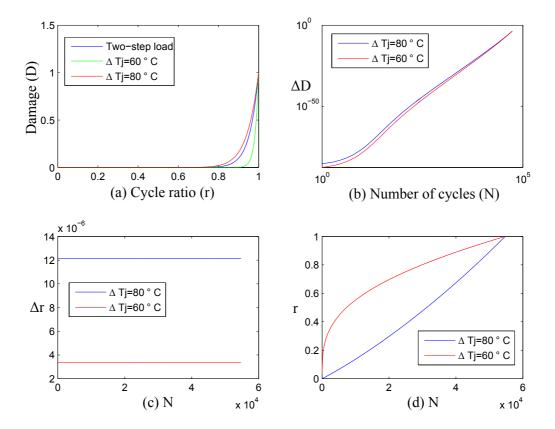

| 6.12        | Validation of nonlinear accumulation method with two-step stress, (a) D-r curves for the nonlinear accumulated two-step load, $\Delta T_j = 80$ °C, and $\Delta T_j = 60$ °C, (b) damage per cycle during lifetime, (c) $\Delta r$ per cycle during lifetime, (d) accumulated r during lifetime. | 157        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

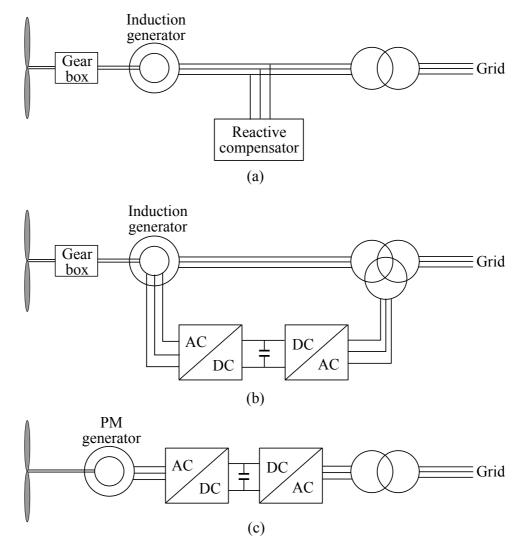

| 7.1         | Different topologies of wind power generation system. (a) topology without power electronics, (b) topology with partially rated power electronics, (c) topology with fully rated power electronics.                                                                                              | 162        |

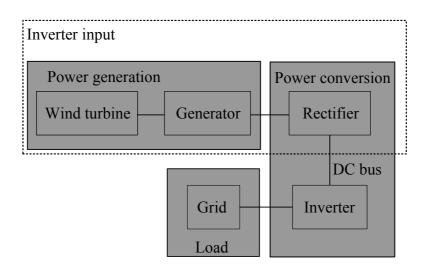

| 7.2         | Basic structure of wind power generation system.                                                                                                                                                                                                                                                 | 163        |

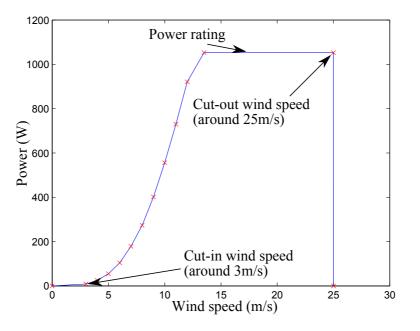

| 7.3         | Inverter input power curve.                                                                                                                                                                                                                                                                      | 164        |

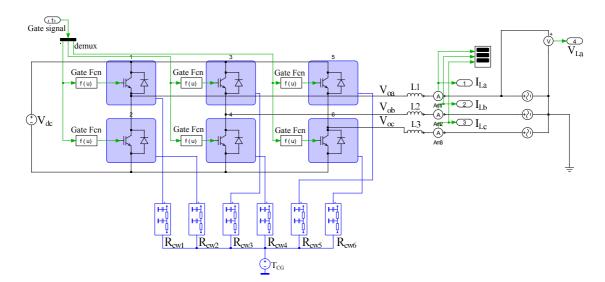

| 7.4         | PLECS model of the grid connected voltage source inverter.                                                                                                                                                                                                                                       | 165        |

| 7.5         | Linear assumption of predictive current control.                                                                                                                                                                                                                                                 | 168        |

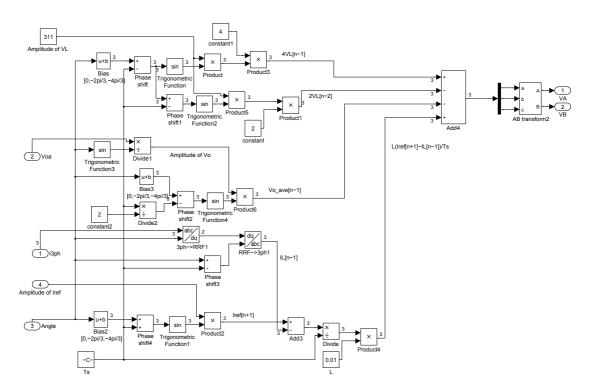

| 7.6         | Block diagram of the predictive controller build in Matlab Simulink                                                                                                                                                                                                                              | 169        |

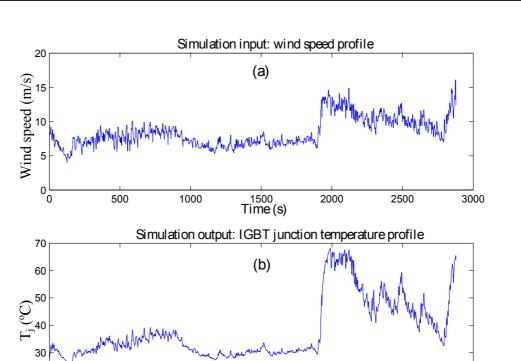

| 7.7         | Simulation (a) input and (b) output.                                                                                                                                                                                                                                                             | 170        |

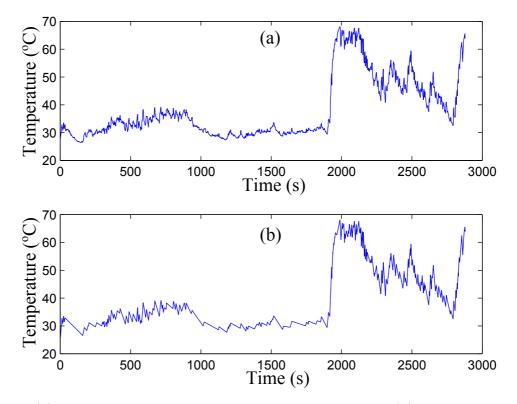

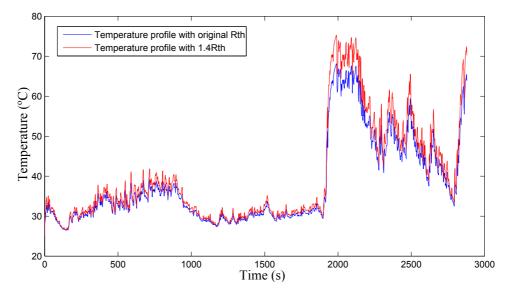

| 7.8         | (a) Original IGBT junction temperature profile and (b) extreme points of the                                                                                                                                                                                                                     |            |

|             | temperature profile                                                                                                                                                                                                                                                                              | 172        |

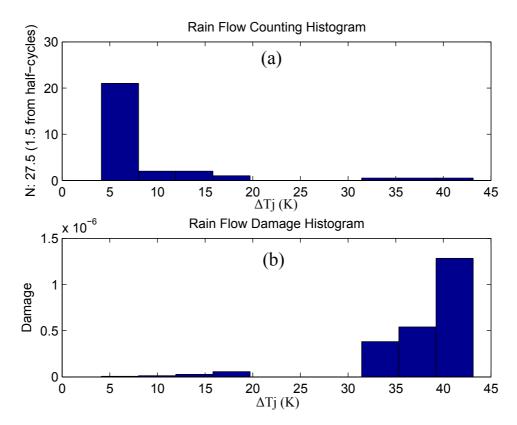

| 7.9         | (a) Rainflow cycle counting results for one temperature profile and (b) the                                                                                                                                                                                                                      |            |

|             | damage caused by the temperature cycles within one profile                                                                                                                                                                                                                                       | 173        |

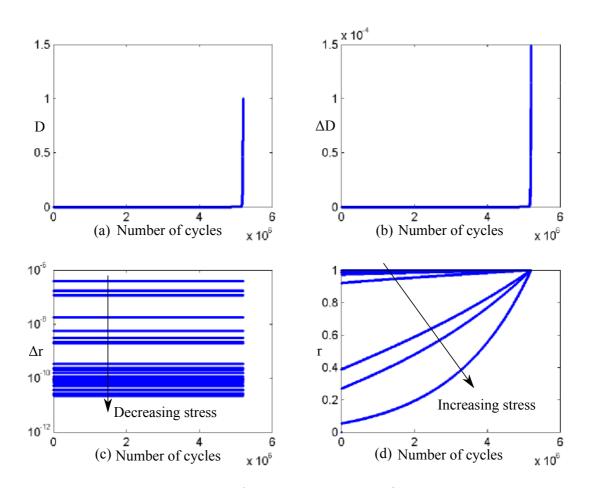

| 7.10        |                                                                                                                                                                                                                                                                                                  |            |

|             | (a) damage accumulation, (b) damage per cycle, (c) $\Delta r$ per cycle, (d) variation                                                                                                                                                                                                           | 1 -        |

| <b>₽</b> 11 | of $r$ during the lifetime                                                                                                                                                                                                                                                                       | 175        |

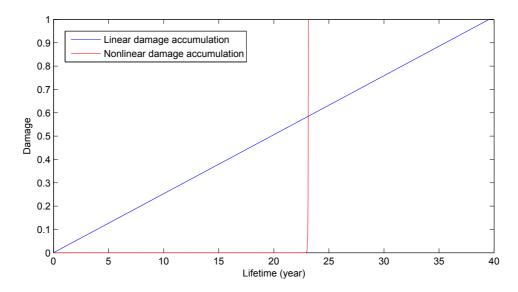

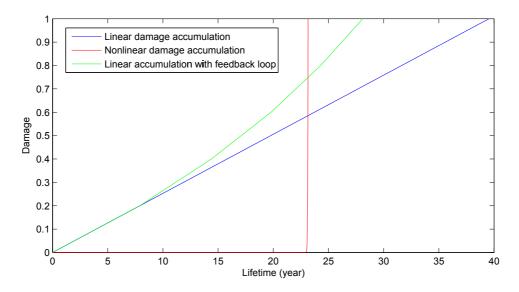

|             | Damage accumulation throughout lifetime by the linear and nonlinear methods.                                                                                                                                                                                                                     |            |

|             | Temperature profile with the initial and increased thermal resistance Comparison of the estimated lifetime with and without feedback loop                                                                                                                                                        | 177<br>178 |

| 1.15        | Comparison of the estimated metime with and without feedback loop                                                                                                                                                                                                                                | 170        |

| B.1         | IGBT module SKM50GB123D datasheet page 1                                                                                                                                                                                                                                                         | 187        |

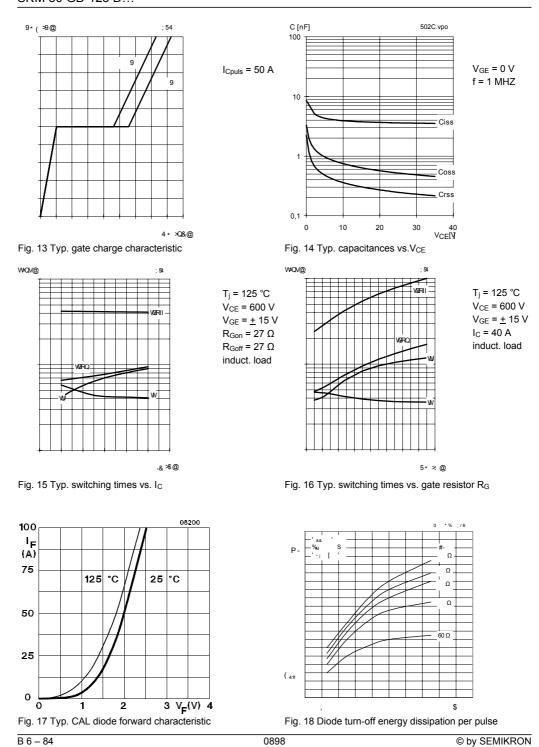

| B.2         | IGBT module SKM50GB123D datasheet page 2                                                                                                                                                                                                                                                         | 188        |

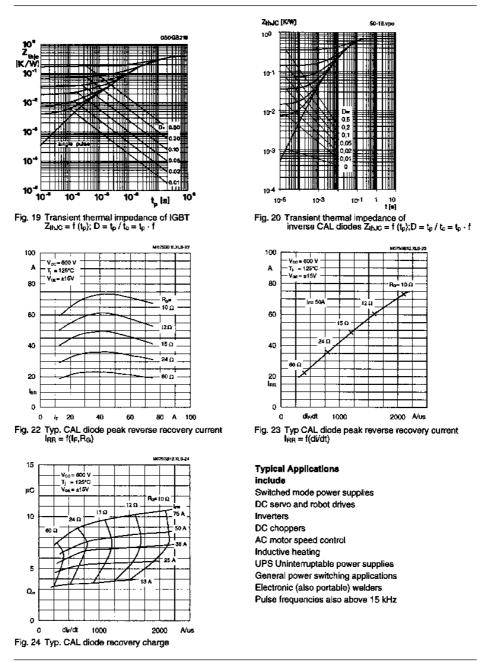

| B.3         | IGBT module SKM50GB123D datasheet page 3                                                                                                                                                                                                                                                         | 189        |

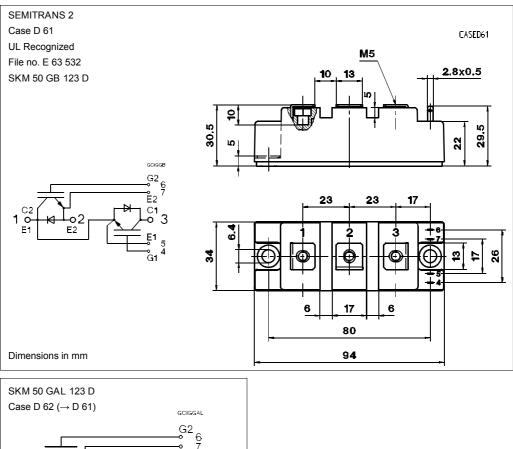

| B.4         | IGBT module SKM50GB123D datasheet page 4                                                                                                                                                                                                                                                         | 190        |

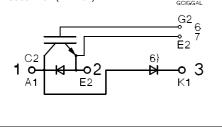

| B.5         | IGBT module SKM50GB123D datasheet page 5                                                                                                                                                                                                                                                         | 191        |

| B.6         | IGBT module SKM50GB123D datasheet page 6                                                                                                                                                                                                                                                         | 192        |

| D.1         | Control flow chart diagram of thermal network extraction test                                                                                                                                                                                                                                    | 209        |

|             | Circuit diagram of the DMH.                                                                                                                                                                                                                                                                      | 205        |

|             |                                                                                                                                                                                                                                                                                                  |            |

# List of Tables

| $3.1 \\ 3.2$                                                                               | Materials and their CTE used for each layer of the conventional power module<br>Materials and their CTE used for each layer of the conventional power module                                                                                             |                                                        |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \end{array}$ | Initial parameter extraction of diode                                                                                                                                                                                                                    | 80<br>80<br>84<br>92<br>98<br>101<br>103<br>105<br>107 |

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5$                                                          | General diagnose of system failure by measured data $\dots \dots \dots \dots \dots \dots$<br>Failure criteria for power cycling test $\dots \dots \dots$ | 116<br>118<br>122<br>126<br>131                        |

| 6.1<br>6.2                                                                                 | Die-attach solder fatigue lifetime model for $1\%$ and $50\%$ Weibull accumulative failure                                                                                                                                                               | 139<br>152                                             |

| 7.1                                                                                        | Lifetime estimation with feedback loop. N indicates the number of cycles in one profile and D indicates upper damage limit.                                                                                                                              | 178                                                    |

| 8.1                                                                                        | The designed test conditions to investigate the effects of both temperature cycle and mean temperature                                                                                                                                                   | 183                                                    |

| D.1                                                                                        | I/O list of data acquisition system                                                                                                                                                                                                                      | 210                                                    |

# Nomenclature

| ADE                  | Andringlan Differences Exception                  |

|----------------------|---------------------------------------------------|

| ADE                  | Ambipolar Diffusion Equation                      |

| AF                   | Accelerated factor                                |

| Al                   | Aluminum                                          |

| CJC                  | Cold junction compensation                        |

| CNC                  | Current number of cycle                           |

| $\operatorname{CSR}$ | Carrier storage region                            |

| CTE                  | Coefficient of thermal expansion $(ppm/K)$        |

| DCB                  | Direct copper bonding                             |

| DFIG                 | Doubly-fed induction generator                    |

| DMH                  | Dead man's handle                                 |

| GaN                  | Gallium nitride                                   |

| HVDC                 | High voltage direct current                       |

| IC                   | Infrared camera                                   |

| IGBT                 | Insulated-gate bipolar transistor                 |

| Κ                    | Kelvin                                            |

| MOSFET               | Metal-oxide semiconductor field effect transistor |

| MTBF                 | Mean time between failure                         |

| MTTR                 | Mean time to repair                               |

| NPT                  | Non-punch-through                                 |

| PDEs                 | Partial differential equations                    |

| PM                   | Permanent magnet                                  |

| $\mathbf{PT}$        | Punch-through                                     |

| PV                   | Photovoltaics                                     |

| Si                   | Silicon                                           |

| SiC                  | Silicon carbide                                   |

| SPWM                 | Sin-triangle pulse width modulation               |

| SSE                  | Sum of squared error                              |

| SVPWM                | Space vector pulse width modulation               |

| TDDB                 | Time dependent dielectric breakdown               |

| 1000                 |                                                   |

| TSP                | Temperature sensitive parameter                                                                                                                                           |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USD                | United State dollar                                                                                                                                                       |

|                    |                                                                                                                                                                           |

| α                  | Weibull scale parameter                                                                                                                                                   |

| $lpha_{Al}$        | CTE of Al $(ppm/K)$                                                                                                                                                       |

| $\alpha_{Si}$      | CTE of Si (ppm/K)                                                                                                                                                         |

| $\beta$            | Weibull shape parameter                                                                                                                                                   |

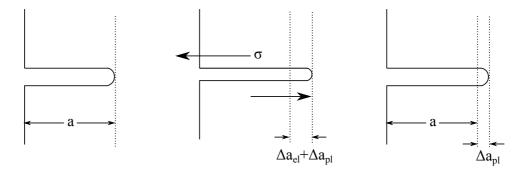

| $\Delta a_{el}$    | Elastic deformation (m)                                                                                                                                                   |

| $\Delta a_{pl}$    | Plastic deformation (m)                                                                                                                                                   |

| $\Delta n$         | Excess electron density $(cm^{-3})$                                                                                                                                       |

| $\Delta p$         | Excess hole density $(cm^{-3})$                                                                                                                                           |

| $\epsilon$         | Permittivity of silicon $(1.04 \times 10^{12} \ F \cdot cm^{-1})$                                                                                                         |

| $\epsilon_{el}$    | Elastic strain                                                                                                                                                            |

| $\epsilon_{pl}$    | Plastic strain                                                                                                                                                            |

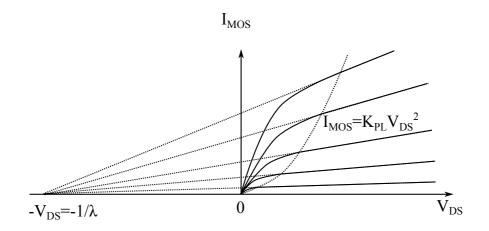

| $\lambda$          | Short channel parameter $(V^{-1})$                                                                                                                                        |

| $\lambda_{th}$     | Heat conductance                                                                                                                                                          |

| E                  | Electric filed $(V/m)$                                                                                                                                                    |

| $\mathscr{E}_d$    | Electric field in drift region $(V/m)$                                                                                                                                    |

| $\mathscr{E}_{BD}$ | Breakdown electric filed $(V/m)$                                                                                                                                          |

| $\mu_i$            | Mobility due to ionized impurities scattering $(m^2/(V \cdot s))$                                                                                                         |

| $\mu_l$            | Mobility due to acoustic phonon scattering $(m^2/(V \cdot s))$                                                                                                            |

| $\mu_n$            | Electron mobility $(m^2/(V \cdot s))$                                                                                                                                     |

| $\mu_p$            | Hole mobility $(m^2/(V \cdot s))$                                                                                                                                         |

| $\psi_c$           | Contact potential (eV)                                                                                                                                                    |

| $\rho$             | Density of the material                                                                                                                                                   |

| ho(x)              | Total charge density distribution along x coordinate $(cm^{-3})$                                                                                                          |

| $\rho_{water}$     | Density of water                                                                                                                                                          |

| $\sigma$           | Stress (N/m)                                                                                                                                                              |

| $\sigma_n$         | Electron capture cross section $(cm^2)$                                                                                                                                   |

| $\sigma_p$         | Hole capture cross section $(cm^2)$                                                                                                                                       |

| $\sigma_y$         | Yeild strength (MPa)                                                                                                                                                      |

| $	au_{BF}$         | Carrier lifetime in N buffer layer (PT) $(\mu s)$                                                                                                                         |

| $	au_{bHL}$        | High-level injection lifetime due to band-to-band recombination (s)                                                                                                       |

| $	au_{bn}$         | Electron lifetime due to band-to-band recombination (s)                                                                                                                   |

| $	au_{bp}$         | Hole lifetime due to band-to-band recombination (s)                                                                                                                       |

| $	au_{tHL}$        | High-level injection lifetime due to bulk trap recombination (s)                                                                                                          |

| $	au_{tn}$         | Electron lifetime due to bulk trap recombination (s)                                                                                                                      |

| $	au_{tp}$         | Hole lifetime due to bulk trap recombination (s)<br>$\mathbf{P}$ : $\mathbf{h}$ + $\mathbf{h}$ = $\mathbf{h}$ = $\mathbf{h}$ = $\mathbf{h}$ = $\mathbf{h}$ = $\mathbf{h}$ |

| ε                  | Dielectric constant of Si $(1.04 \times 10^{-12} \text{ F/cm})$                                                                                                           |

| С                  | Thermal capacitance                                                                                                                                                       |

|                    |                                                                                                                                                                           |

| ~              |                                                                                |

|----------------|--------------------------------------------------------------------------------|

| $C_{dep}$      | Depletion layer capacitance (F)                                                |

| $C_{GC}$       | IGBT gate-collector capacitance / Miller capacitance (F)                       |

| $C_{GE}$       | IGBT gate-emitter capacitance (F)                                              |

| $C_{ies}$      | IGBT input capacitance (nF)                                                    |

| $C_{oes}$      | IGBT output capacitance (nF)                                                   |

| $C_{OX}$       | Gate oxide capacitance (F)                                                     |

| $C_{res}$      | IGBT reverse capacitance $(nF)$                                                |

| $C_{th}$       | Thermal capacitance                                                            |

| $C_{water}$    | Thermal capacitance of water                                                   |

| D              | Damage                                                                         |

| D              | Duty ratio of cyclic load current                                              |

| $D_n$          | Electron diffusion constant $(m^2/s)$                                          |

| $D_p$          | Hole diffusion constant $(m^2/s)$                                              |

| E              | Youngs modulus (GPa)                                                           |

| $E_a$          | Activation energy (eV)                                                         |

| $E_c$          | Conduction bands J                                                             |

| $E_c$          | Critical electrical field value for silicon (V/m)                              |

| $E_g$          | Bandgap J                                                                      |

| $E_i$          | Fermi level energy (J)                                                         |

| $E_t$          | Bulk trap energy in Si (J)                                                     |

| $E_v$          | Valence bands J                                                                |

| $E_{Fn}$       | Electron quasi Fermi level (J)                                                 |

| $E_{Fp}$       | Hole quasi Fermi level (J)                                                     |

| $E_{off}$      | IGBT turn-off loss (mJ)                                                        |

| $E_{on}$       | IGBT turn-on loss (mJ)                                                         |

| $f_s$          | Sampling frequency                                                             |

| $f_e$          | Error figure between simulation results and experimental waveforms             |

| $\overline{G}$ | Shear modulus (GPa)                                                            |

| $G_{th}$       | Thermal generation rate                                                        |

| $h_n$          | Electron recombination coefficient $(cm^4 \cdot s^{-1})$                       |

| $h_p$          | Hole recombination coefficient $(cm^4 \cdot s^{-1})$                           |

| $I_F$          | PN junction forward current (Å)                                                |

| $I_g$          | IGBT gate current (A)                                                          |

| $I_L^{j}$      | Load current (A)                                                               |

| $I_L[n]$       | Instantaneous load current at sampling point $[n]$ (A)                         |

| $I_s$          | Reverse saturation current (A)                                                 |

| $I_{cH}$       | Defined upper limit of load current during heating phase in power cycling test |

| $I_{cL}$       | Defined lower limit of load current during heating phase in power cycling test |

| $I_{CM}$       | Peak collector current from the RBSOA curve given in the datasheet (A)         |

| $I_{ref}[n]$   | Instantaneous reference current at sampling point [n] (A)                      |

| $I_{RR}$       | Reverse recovery current (A)                                                   |

| 1010           | v X /                                                                          |

| $I_{sne}$     | Minority carrier saturation current (PT) (A)                  |

|---------------|---------------------------------------------------------------|

| $J_c on$      | Conduction current density $(A/m^2)$                          |

|               | Diffusion current density $(A/m^2)$                           |

| $J_d rift$    | Drift current density $(A/m^2)$                               |

| $J_n$         | Electron current density $(A/m^2)$                            |

| $J_p$         | Hole current density $(A/m^2)$                                |

| $J_s$         | Reverse saturation current density $(A/m^2)$                  |

| k             | Boltzmann's constant, $1.38 \times 10^{-23} J/K$              |

| $K_{PL}$      | MOS transconductance coefficient $(A/V^2)$                    |

| $L_d$         | Diode series inductance (H)                                   |

| $L_e^a$       | IGBT Kelvin emitter inductance (mH)                           |

| $L_n^{\circ}$ | Electron diffusion length (cm)                                |

| $L_p^n$       | Hole diffusion length (cm)                                    |

| $L_S^P$       | Circuit stray inductance (H)                                  |

| $\tilde{m_c}$ | Conductivity effective mass (kg)                              |

| $m_{water}$   | Mass of water                                                 |

| n             | Electron density $(cm^{-3})$                                  |

| $n_0$         | Thermal equilibrium electron density $(cm^{-3})$              |

| $N_a$         | Ionized acceptor density $(cm^{-3})$                          |

| $N_B$         | Drift region width $(\mu m)$                                  |

| $N_d$         | Ionized donor density $(cm^{-3})$                             |

| $N_f$         | Number of cycle to failure                                    |

| $n_i$         | Intrinsic carrier density $(cm^{-3})$                         |

| $N_P$         | Weibull percentile                                            |

| $N_t$         | Bulk trap density in Si $(cm^{-3})$                           |

| $N_H$         | Doping concentration of N buffer layer (PT) $(cm^{-3})$       |

| $n_{p0}$      | Thermal equilibrium electron density in p-type Si $(cm^{-3})$ |

| $n_p$         | Electron density in p-type Si $(cm^{-3})$                     |

| p             | Hole density $(cm^{-3})$                                      |

| $p_0$         | thermal equilibrium hole density $(cm^{-3})$                  |

| $P_{jc}$      | Heat conducts from IGBT junction to case                      |

| $p_{n0}$      | thermal equilibrium hole density in n-type Si $(cm^{-3})$     |

| $p_n$         | Hole density in n-type Si $(cm^{-3})$                         |

| $P_{water}$   | Heat extracted by water                                       |

| q             | Magnitude of the electron charge, $1.6 \times 10^{-19} C$     |

| $Q_d$         | Stored charge in the drift region (C)                         |

| $Q_F$         | Total excess carrier charge in the drift region $(C)$         |

| $Q_n$         | Total excess carrier charge in n-side $(C)$                   |

| $Q_p$         | Total excess carrier charge in p-side Si (C)                  |

| $Q_{RR}$      | Reverse recovery charge $(C)$                                 |

| R             | Resistance per unit length                                    |

|               |                                                               |

| ~                    | Crucle motio                                                                  |

|----------------------|-------------------------------------------------------------------------------|

| r<br>D               | Cycle ratio<br>Rend to hand recombination rate                                |

| $R_b$                | Band-to-band recombination rate                                               |

| $R_g$                | Gate resistance $(\Omega)$                                                    |

| $r_y$                | Plastic zone width (m)                                                        |

| $R_{bc}$             | Recombination coefficient due to band-to-band recombination                   |

| $R_{jc}$             | Thermal resistance between IGBT junction and case                             |

| $R_{SP}$             | Resistance of the P-well $(\Omega)$                                           |

| $R_{th}$             | Thermal resistance                                                            |

| T<br>T               | Absolute temperature (K)                                                      |

| $T_c$                | IGBT case temperature                                                         |

| $t_c$                | Time between collision (s)                                                    |

| $T_j$                | IGBT junction temperature                                                     |

| $T_m$                | Mean IGBT junction temperature in power cycling test                          |

| $T_{cH}$             | Defined upper limit of IGBT case temperature in power cycling test            |

| $T_{cL}$             | Defined lower limit of IGBT case temperature in power cycling test            |

| $t_{RR}$             | Reverse recovery time (s)                                                     |

| $T_{varG}$           | Average water temperature (°C)                                                |

| $T_{win}$            | Water temperature before flow into the heatsink                               |

| $T_{wout}$           | Water temperature after flow out of the heatsink                              |

| $U_b$                | Net band-to-band transition rate                                              |

| $U_t$                | Net bulk trap transition rate                                                 |

| $V_d$                | Carrier drift velocity $(m/s)$                                                |

| $V_d$                | Voltage across the drift region $(V)$                                         |

| $V_F V_L$            | PN junction forward voltage drop (V)<br>Load voltage $(V)$                    |

|                      | Load voltage $(V)$                                                            |

| $V_O$                | Inverter output voltage (V)<br>Diode anode-cathode voltage (V)                |

| $V_{AK}$<br>$V_{}$   | Breakdown voltage (V)                                                         |

| $V_{BD}$<br>$V_{BR}$ | Breakdown voltage from datasheet plus 150 to 200 V typical margin for general |

| VBR                  | IGBTs (V)                                                                     |

| $V_{ce}$             | IGBTs (V)<br>IGBT on-state voltage drop                                       |

| $V_{CM}^{ce}$        | Peak IGBT collector voltage during turn-off (V)                               |

| $V_{DC}^{CM}$        | DC supply voltage (V)                                                         |

| $V_{GE}$             | IGBT gate-emitter voltage (V)                                                 |

| $V_{GG(off)}$        | IGBT off-state gate voltage (V)                                               |

| $V_{GG(on)}$         | IGBT on-state gate voltage (V)                                                |

| $V_{L\_ave}[n]$      | Average grid voltage over the switching period $[n, n+1]$ (V)                 |

| $V_{O\_ave}[n]$      | Average inverter output voltage over the switching period $[n, n+1]$ (V)      |

| $V_{ref}$            | Reference voltage vector                                                      |

| $V_{TH}$             | IGBT threshold voltage (V)                                                    |

| $v_{th}$             | Thermal velocity $(m/s)$                                                      |

|                      | $\mathbf{v}$ $\mathbf{v}$ $\mathbf{v}$ $\mathbf{v}$ $\mathbf{v}$              |

| $V_{water}$ | Speed of water flow                         |

|-------------|---------------------------------------------|

| $W_D$       | Depletion layer width (cm)                  |

| $W_d$       | Drift region width (cm)                     |

| $W_{Dn}$    | Depletion layer width in n-type region (cm) |

| $W_{Dp}$    | Depletion layer width in p-type region (cm) |

| $W_H$       | Width of N buffer layer (PT) $(\mu m)$      |

| $x_{meas}$  | Experimentally measured waveforms           |

| $x_{sim}$   | Simulated results                           |

| $Z_{th}$    | Thermal impedance                           |

# Chapter **1** Introduction

## 1.1 Energy Security and Low-carbon Society

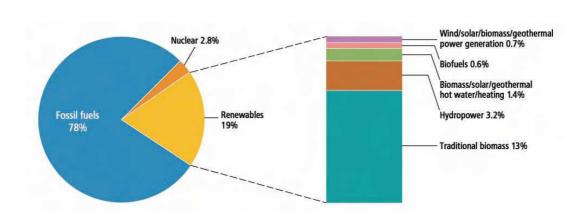

The development of human society is highly reliant on energy. Fig. 1.1 shows that in 2008, 78% of the worlds total energy consumption was generated from fossil fuels [5]. Throughout recent history, the demand and consumption of fossil fuels has lead to many problems, such as air pollution and global warming. Furthermore, fossil fuels are finite resources which eventually will dwindle and become too expensive. The key to overcome these problems is to find alternative energy sources which are inexhaustible and environmentally friendly.

Nuclear as an alternative option is becoming more and more important. 439 nuclear power plants were installed in 31 countries upto and including 2008 and generate 2.8% of the worlds energy [6]. Nuclear power plants use the controlled nuclear fission rods to heat water and produce steam to drive the turbine. However, the debate about whether nuclear should be used as an energy source grows with installed capacity. Proponents suggest that nuclear power is a sustainable energy source which produces no conventional air pollution, such as green-house gases. They claim that the risk of the nuclear leakage is small and can be reduced by improving the technology. Opponents believe that nuclear power plants

Figure 1.1: Energy consumption from different sources in 2008.

bring many threats to the people who live around them. In fact, there have been a number of serious nuclear accidents, for example the Chernobyl disaster in 1986, which caused a great deal of damage to the global environment and human health. The most recent nuclear accident is the Fukushima disaster in Japan on the  $11^{th}$  March 2011, which cause huge damage to Japan's environment and economy. These accidents support the opponents' view and have caused a global recession in nuclear power.

Renewable energy is the energy which comes from natural sources, such as sunlight, wind, geothermal and tide which are naturally replenished. Therefore renewable energy does not have a generation limit and so are environmentally friendly. Furthermore, these energy sources could supply enough power for human society if they can be harnessed efficiently. Globally, about 1700TW of solar power is theoretically available over land for Photovoltaics (PV), which means even the capture of 1% of this power would supply more power than we currently need [6]. The available wind power globally is about 72TW, which is 5 times the worlds total power production [7]. However, the installed solar PV capacity was only 21GW and wind power capacity was 159GW in 2009 [5]. Fig. 1.2 shows some examples of renewable energy power plant. Clearly, renewable power plant can be built in desert or ocean where the environment is too severe for mankind to live. Therefore they will not affect the human's living space. In this case, high system reliability is required since the maintenance

(a) Solar energy power plant

(b) Offshore wind farm

Figure 1.2: Examples of renewable energy power plant

cost will be relevantly high, due to limited access.

Although the market share of solar and wind energy only accounts for 0.7% of the total power consumption, it is growing very rapidly and gaining more and more attention from both researchers and business. Grid connected solar PV has grown by an average of 60% each year for the past decade while wind power capacity has grown at 27% annually for the past 5 years. The annual global investment in new renewable capacity reached 150 billion United State dollars (USD) in 2009 [6]. After the Kyoto summit in 1997, most of the worlds major countries committed to change the ways they used and supplied energy to limit the emission of green-house gases. Acts were passed by governments to legally constrict greenhouse gas emission, for example, UK's climate change act in 2008. However, the development of renewable energy is still highly government driven because the cost of energy generated from renewable sources is still higher than that from fossil fuels. Clearly, increasing the reliability of energy generation systems is a direct method of reducing the operation and maintenance cost. After all, the development potential of renewable energy is huge and more technical efforts is required.

## **1.2** The Role of Power Electronics in Energy Efficiency

The electrical energy from renewable sources normally cannot be despatched by the grid directly. In the case of wind power system, the frequency and voltage of the electricity generated by wind turbine changes as the wind speed varies. Energy conversion is required to modify the generated electricity to the grid frequency and voltage. Power converters are installed to accomplish this task because of their high efficiency, normally higher than 90%. Unlike classical electronics, power electronics process power rather than information. Nowadays, power electronic devices can be found in almost all electrical applications like mobile phone, traction, satellite, wind turbines and so on. At least 25% of all generated power passes through some form of power electronic system before being utilised [8].

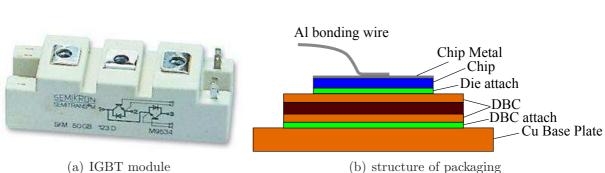

Power electronic technology was originally developed at the beginning of 20<sup>th</sup> century when the mercy arc valve, the first high power electronic device, was invented. Mercury arc valves were widely used to convert AC to DC until the 1960s when high voltage semiconductor devices like silicon diode and thyristor were developed. Metal Oxide Semiconductor Field-Effect Transistor (MOSFET) has become commercially available in 1976. With the advantage of both high switching frequency and controllable turn-off, they are widely used in many electrical applications. However, MOSFET is a unipolar device which faces the tradeoff between voltage blocking capability and on-state resistance. The insulated Gate Bipolar Transistor (IGBT) was invented to overcome this limitation. The voltage rating of an IGBT module, which is commercially available now, is up to 6500V. Fig. 1.2 shows the example of current available IGBT module and its basic structure.

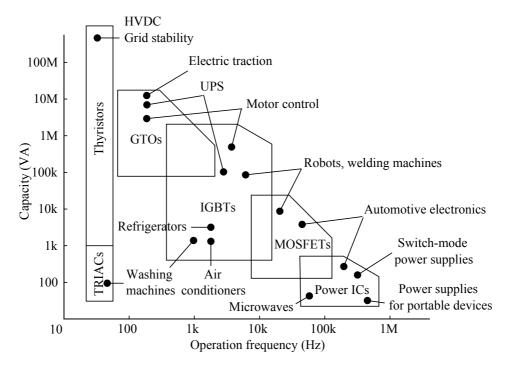

After 100 years of development, the family of power electronic device contains a range of products, as shown in Fig 1.4. Thyristors are used in high power and low switching frequency applications such as the high voltage direct current (HVDC) Grid. It can be seen that the switching frequency of an IGBT is much higher than that of the thyristor therefore it is widely used in motor control applications. MOSFETs, whose switching frequency is even

#### 1.2 The Role of Power Electronics in Energy Efficiency

(a) IGBT module

Figure 1.3: IGBT module and different layers of packaging

higher, are typically used in the power supply for portable devices. In the case of renewable energy, higher switching frequency and power capacity devices are preferred to limit the harmonics and convert higher power levels. Due to these requirements, IGBT is preferred device for renewable applications.

Figure 1.4: Typical example of power electronics and their applications.

## 1.3 Overview of Reliability Problems

Reliability is often defined as the ability of a device to fulfill its intended function during an interval of time [9]. Today, reliability engineering is applied to many products as failure can causes catastrophic consequences such as aircraft accidents. Even some small failures, such as the failure of a mobile phone, are a nuisance and could give the company that produces it a bad reputation. According to an industry based survey in 2009 [10], the converter is one of the most unreliable parts of an electrical system operating in a harsh environment, such as wind turbine. The cost of converter failure and maintenance is high in the case of off-shore operation due to the inaccessibility of the system. The system reliability can be greatly increased by replacing devices before they fail. Therefore the reliability of the converter is a critical issue.

The reliability of most products has often been represented by an idealised plot called a

Figure 1.5: Idealized bathtub curve.

bathtub curve shows in Fig. 1.5. This curve consists of three regions: infant mortality, useful life and wear out. In the first region, failure is mainly caused by manufacturing defects or poor workmanship. The defective products tend to fail early, so the failure rate decreases with time. The failure rate reaches a constant level in the useful life region, where the failures observed are considered as random failures. In the last region, the products start wearing out and consequently the failure rate begins to rise as they experience more stresses.