## Increasing Experiment Velocity in a Production Environment

By Shafali Rastogi

B.S. Electrical Engineering and Computer Science Minor, University of Calgary, 1995

Submitted to Sloan School of Management and the Department of Electrical Engineering and Computer Science in partial fulfillment of the degrees of

> Master of Science in Management And Master of Science in Electrical Engineering and Computer Science

At the Massachusetts Institute of Technology May 1999

© Massachusetts Institute of Technology, All rights reserved Signature of Author Department of Electrical Engineering and Computer Science Sloan School of Management  $\wedge$ 1 Certified by Stan Gershwin Senior Research Scientist, Thesis Advisor Department of Mechanical Engineering Certified by Professor Larry Wein, Thesis Advisor Sloan School of Management Accepted by Professor Arthur C. Smith, Chairman EECS Department Committee on Graduate Students Accepted by Lawrence S. Abeln, Director of Master's Program Sloan School of Management MASSACHUSETT OF JUI LIBRARIES

This Page is intentionally left blank.

Shafali Rastogi

## Increasing Experiment Velocity in a Production Environment

By Shafali Rastogi

Submitted to Sloan School of Management and the Department of Electrical Engineering and Computer Science in partial fulfillment of the degrees of

> Master of Science in Management And Master of Science in Electrical Engineering and Computer Science

## Abstract

Intel Corporation's D2 semiconductor fabrication facility (fab) is the smaller of Intel's two development facilities. The primary purpose of this facility is to bring new processes from early development to the point where they are ready to be transferred to a full scale fab. In conjunction with their charter, D2 also runs an aggressive production schedule. These two goals conflict with each other, in the sense that while production runs in large volumes with low cycle times, experiments run less often but bring more variation to the line and require more time to run. This thesis explores ways to improve the cycle times of technical development (TD) lots while minimizing the impact on production flow.

Two approaches are taken to looking at this challenge. The first is to improve TD setup and running procedures. To this end it is shown that the current experiment setup procedures at D2 are cumbersome, requiring much communication and signing for small changes. Where these gaps exist is highlighted. Focusing next on photolithography (litho), standards for running experiments for different processes and different litho tool sets are created, in order to ease the flow and reduce the confusion created by incoming experiments to the area.

The second approach is to improve the scheduling and prioritization of TD in the fab. The DUV toolset in litho, which runs the five critical layers for all processes, is the focus of this study. TD is characterized into three phases:

- 1. Process Development The earliest phase, this is where parameters are just being set.

- 2. Process Characterization and Improvement

- Here, the experimental aim is to ramp up the process to large volume manufacturing 3. Sustainment Development

These lots are already in production, but experiments are being done to tweak the process.

With the three phases of TD and production as inputs, a simulation model was created to determine some rules for optimally running TD on the photolithography toolset.

The simulation study led to following conclusions:

- 1. Process Development TD is more complex than the other types of TD and production. It should be given more consideration than regular production.

- 2. Prioritizing TD is a key lever. TD should be given high priority. Deprioritizing TD will not have a large impact on production queue times, but will have a large impact on TD queue times.

- 3. There is a negative impact to holding lots to reduce set up or processing times.

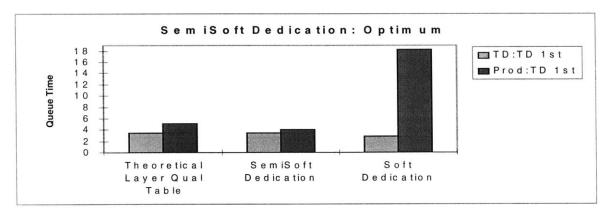

- 4. Of the scenarios tried, semi-soft dedication running TD first gave the best results. The semi-soft dedication result is confirmed by a pilot conducted independently on these tools. There is an optimum where tools are most fully utilized while set up times are minimized, which further experimentation should lead to.

Thesis Advisors: Larry Wein, Sloan School of Management Stan Gershwin, Department of Mechanical Engineering

## Acknowledgements

The author gratefully acknowledges the support and resources made available to her through MIT Leaders for Manufacturing Program, a partnership between MIT and major U.S. manufacturing companies.

This work was made possible through the help and support of people at Intel's D2 site and LFM. I would like to thank my supervisor, Rob Edmondson, for helping me outline and solve the TD-Production issues presented in this thesis. I would like to thank Melinda Manente, who got me involved in the photolithography area, a central focus of my thesis. I would like to thank Laura Whitaker for taking the time to help me with the simulation and provide the necessary input data and Arena manual. This paper was greatly assisted by the people I worked with in Integration -especially Linda Erlich-, Automation, and the Photolithography group. Finally, I would like to thank the other Intel Santa Clara LFM's (SCILI's): Gary Tarpinian, Ajay Amar, and Manish Bhatia who helped me structure my project throughout the internship and patiently watched my simulation grow.

I would like to thank my two advisors: Larry Wein from the Sloan School of Management and Stan Gershwin form the Department of Mechanical Engineering, who helped me focus and improve the quality of this thesis.

This thesis is dedicated to my mom and dad, for the quarter century of hard work they put into getting me here and to my sister, who helped me solve my research problem and even provided the software and the manual.

This page is intentionally left blank.

Shafali Rastogi

## **Table of Contents**

| Abstract                                                       | 3  |

|----------------------------------------------------------------|----|

| Acknowledgements                                               | 5  |

| Table of Contents                                              | 7  |

| List of Figures                                                |    |

| List of Tables                                                 |    |

| Chapter 1 Introduction                                         |    |

| 1.1 Overview                                                   |    |

| 1.2 Problem Statement                                          |    |

| 1.3 Research Description                                       |    |

| 1.4 Thesis Objective                                           | 13 |

| 1.5 Thesis Structure                                           |    |

| Chapter 2 Introduction to the Semiconductor Industry and Intel | 14 |

| Chapter 3Intel's D2 Site                                       |    |

| 3.1 TD Lot Set Up                                              |    |

| 3.2 Running the Lot in the Factory                             |    |

| 3.3 Ongoing Issues                                             |    |

| Chapter 4The Setting up of Experiments                         | 21 |

| Chapter 5 Standardization of Photolithography Experiments      |    |

| Chapter 6 Simulation Model Description                         |    |

| 6.1 Inputs                                                     |    |

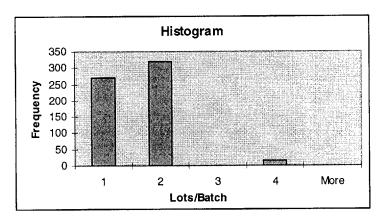

| 6.1.1 Arrival Distribution                                     | 28 |

| 6.1.2 Lots/Batch Distribution6.1.3 Layer Distribution          | 29 |

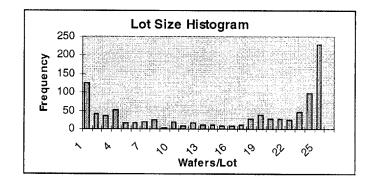

| 6.1.4 Lot Size Distribution                                    | 29 |

| 6.1.5 Layer Identification                                     | 30 |

| 6.2 Tool Parameters                                            | 20 |

| 6.2.1 Layer Qualification Tables                               | 30 |

| 6.2.2 Machine down and repair times                            | 30 |

| 6.2.3 Layer Change and Setup Times                             | 31 |

| 6.2.4 Processing Times                                         |    |

| 6.3 Model Assumptions                                          |    |

| 6.4 The Model                                                  |    |

| Chapter 7 Simulation Model - The Experiments                   | 37 |

Shafali Rastogi

| Chapter 8 - Model Validation                                        | 38     |

|---------------------------------------------------------------------|--------|

| Chapter 9 Simulation Model - Results                                | 4      |

| Chapter 10 - Conclusions                                            |        |

| Bibliography                                                        |        |

| Appendix A: Definitions                                             |        |

| Appendix B: Description of Process Flow Steps for Experiment Setups | 52     |

| DESIGN OF EXPERIMENT                                                | 5      |

| D2 START REQUEST                                                    | 5      |

| DOE/SPLIT TABLE                                                     |        |

| EXPERIMENT CHANGE REQUEST                                           | 5      |

| ROUTE/LOTSPEC SETUP                                                 | 5      |

| SPECS FOR NEW OPERATIONS                                            | ><br>5 |

| SCRIPTS UPDATED                                                     | 5      |

| ROUTE/LOTSPEC WRITTEN AND SIGNED OFF BY LOT OWNER                   | 5      |

| SPC++ REQUEST IN                                                    | 5      |

| RETICLE SET UP                                                      |        |

| Change Integration Management (CIM)                                 | 5      |

| ROUTE/LOTSPEC AND PAPERWORK IN TO CIM                               | 5      |

| WALK THE ROUTE                                                      | 3<br>5 |

| SPC++ SET-UP                                                        | 5      |

| LRTA DONE, CHECKED, TO ERC                                          | 5      |

| EXPERIMENT REVIEW COMMITTEE (ERC)                                   | 5      |

| ERC APPROVAL/WTR DONE                                               | 5      |

| POST ERC                                                            | 5      |

| PRODUCT ATTACHED TO RT                                              | 5      |

| HOLDS ATTACHED<br>ROUTE/LOTSPEC MAILED TO STATION OWNERS            | 5      |

| TARGET LOT LIST UPDATED                                             | 3<br>5 |

| WAFER START                                                         |        |

| Appendix C: Input Data for Simulation Model                         |        |

| Appendix D: Layer Qualification Tables for Tools                    |        |

| Appendix E: Output Data                                             |        |

| Appendix F: Model Validation Data Input File                        |        |

# List of Figures

| Figure 1: Product Life Cycle Curve                                                | 11 |

|-----------------------------------------------------------------------------------|----|

| Figure 2: TD System Overview                                                      | 18 |

| Figure 3: FAST 3-2-1 System                                                       |    |

| Figure 4: Setting Up a TD Experiment for the D2 Fab                               | 22 |

| Figure 5: Standardized Format for Photolithography Lots                           |    |

| Figure 6: Example of Lots Per Batch Distribution Histogram                        | 29 |

| Figure 7: Example of Layer Distribution Histogram                                 | 30 |

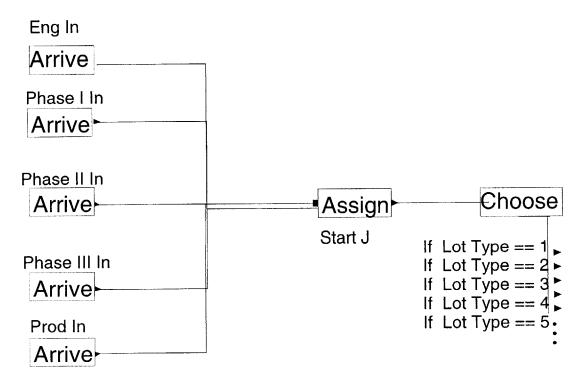

| Figure 8: The Creation of Lots                                                    | 33 |

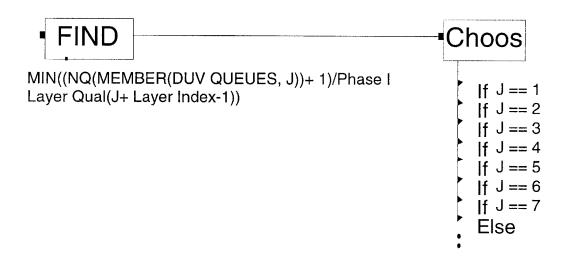

| Figure 9: Choosing a Tool                                                         |    |

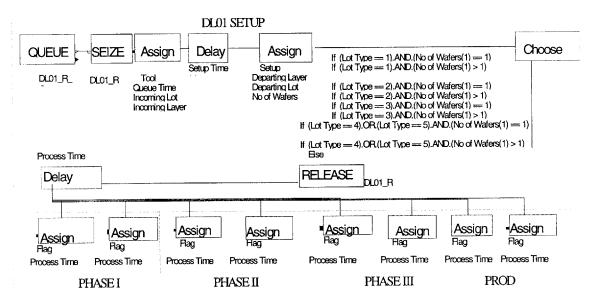

| Figure 10: Processing a Lot                                                       | 35 |

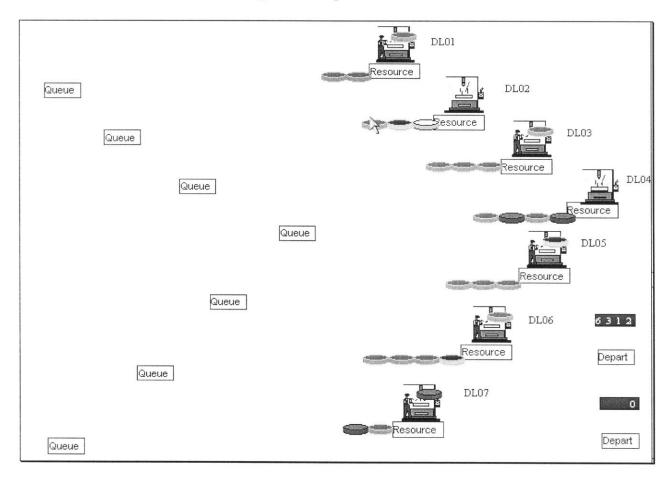

| Figure 11: Sample Simulation                                                      | 36 |

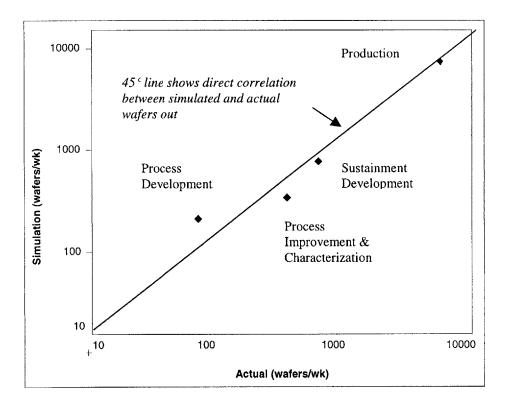

| Figure 12: Proportionality in Wafers Out Between Actual and Simulation            | 39 |

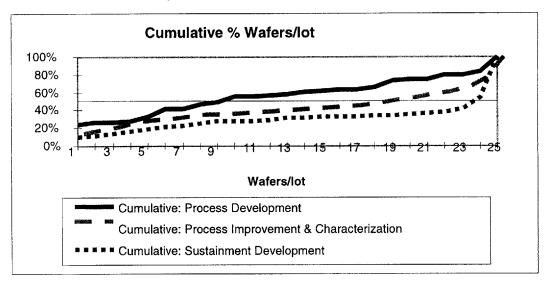

| Figure 13: The Number of Wafers In a Lot                                          | 41 |

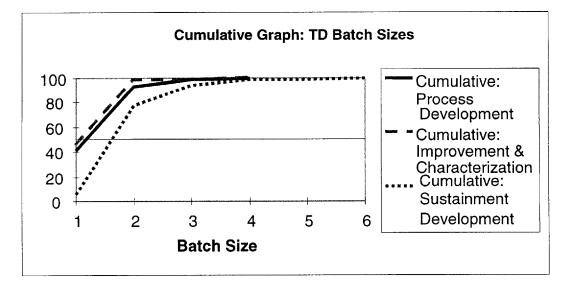

| Figure 14: Number of Lots Arriving Simultaneously                                 | 41 |

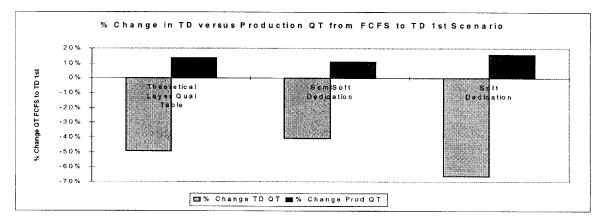

| Figure 15: To a Change in TD priority, TD queue times change more than Production | 42 |

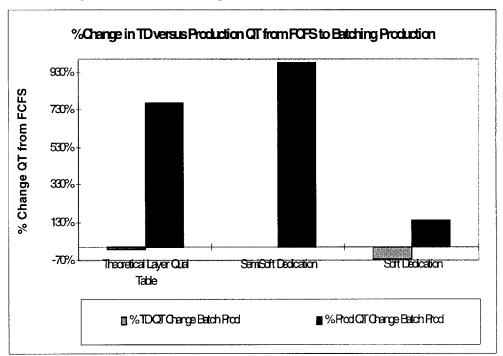

| Figure 16: Queue Time Impact when Batching Production                             | 43 |

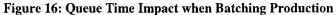

| Figure 17: Queue Time Impact of Running Process Development Only During the Day   | 44 |

| Figure 18: The Optimal Scenario                                                   |    |

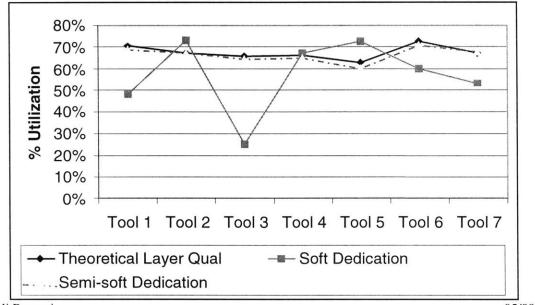

| Figure 19: Tool Utilization FIFO Strategies                                       | 45 |

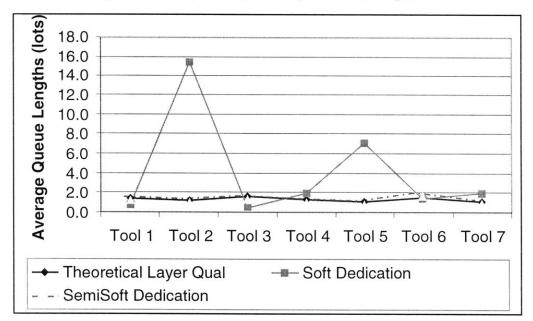

| Figure 20: Average Tool Queue Lengths FIFO Strategies                             | 46 |

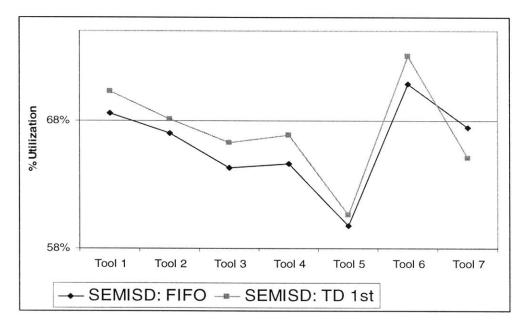

| Figure 21: Tool Utilization - TD 1st versus FIFO for Semisoft Dedication          |    |

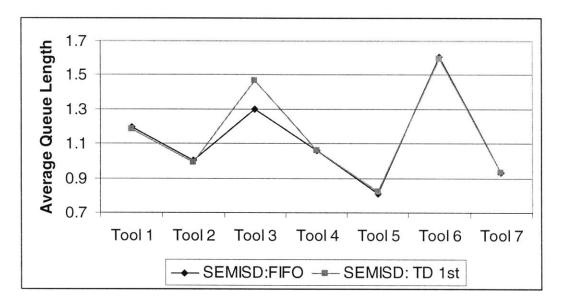

| Figure 22: Tool Queues - TD 1st versus FIFO                                       | 47 |

## List of Tables

| Table 2: Basic Steps in Photolithography16Table 3: Lot Prioritization19Table 4: Input Characteristics For Three Phases28Table 5: Machine Down and Repair Times31Table 6: Original Layer Change and Setup Time Matrix31Table 7: Averaged Layer Change and Setup Time Matrix32Table 8: Lot Processing Times32Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63Table 20: Sample Input Data File Used in Model Validation64 | Table 1: Process Flow Steps to Make a Chip                |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|

| Table 4: Input Characteristics For Three Phases28Table 5: Machine Down and Repair Times31Table 6: Original Layer Change and Setup Time Matrix31Table 7: Averaged Layer Change and Setup Time Matrix32Table 8: Lot Processing Times32Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                              | Table 2: Basic Steps in Photolithography                  | . 16 |

| Table 5: Machine Down and Repair Times31Table 6: Original Layer Change and Setup Time Matrix31Table 7: Averaged Layer Change and Setup Time Matrix32Table 8: Lot Processing Times32Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                    |                                                           |      |

| Table 6: Original Layer Change and Setup Time Matrix31Table 7: Averaged Layer Change and Setup Time Matrix32Table 8: Lot Processing Times32Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                                                            | Table 4: Input Characteristics For Three Phases           | . 28 |

| Table 7: Averaged Layer Change and Setup Time Matrix32Table 8: Lot Processing Times32Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                                                                                                                  |                                                           |      |

| Table 8: Lot Processing Times32Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                                                                                                                                                                        | Table 6: Original Layer Change and Setup Time Matrix      | . 31 |

| Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                                                                                                                                                                                                       | Table 7: Averaged Layer Change and Setup Time Matrix      | . 32 |

| Table 9: Experiments Run37Table 10: Model Validation Data38Table 11: Simulation Model Results40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                                                                                                                                                                                                       | Table 8: Lot Processing Times                             | . 32 |

| Table 11: Simulation Model Results.40Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 9: Experiments Run                                  | . 37 |

| Table 12: Arrival Rate Data57Table 13: Theoretical Layer Qualification Table58Table 14: Soft Dedication Qualification Table59Table 15: Semisoft Dedication Qualification Table60Table 16: Raw Output Data61Table 17: Lot Statistics62Table 18: Average Lot Statistics62Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production63                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                           |      |

| Table 13: Theoretical Layer Qualification Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |      |

| Table 14: Soft Dedication Qualification Table       59         Table 15: Semisoft Dedication Qualification Table       60         Table 16: Raw Output Data       61         Table 17: Lot Statistics       62         Table 18: Average Lot Statistics       62         Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production       63                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |      |

| Table 15: Semisoft Dedication Qualification Table       60         Table 16: Raw Output Data       61         Table 17: Lot Statistics       62         Table 18: Average Lot Statistics       62         Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           |      |

| Table 16: Raw Output Data       61         Table 17: Lot Statistics       62         Table 18: Average Lot Statistics       62         Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 14: Soft Dedication Qualification Table             | . 59 |

| Table 17: Lot Statistics       62         Table 18: Average Lot Statistics       62         Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 15: Semisoft Dedication Qualification Table         | . 60 |

| Table 18: Average Lot Statistics       62         Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production       63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |      |

| Table 19: Sample of Data from Cumulative Frequency of Queue Times for TD and Production                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |      |

| Table 20: Sample Input Data File Used in Model Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Table 20: Sample Input Data File Used in Model Validation | . 64 |

This page is intentionally left blank.

Shafali Rastogi

## **Chapter 1 Introduction**

## 1.1 Overview

This thesis looks at how to reduce experiment cycle times in a joint production-development semiconductor fabrication facility (fab). It looks first at how to make more efficient the setting up of experiments. It then focuses solely on the Photolithography functional area<sup>1</sup>, exploring first how to make the worker process more efficient, and then how to reduce cycle times for lots<sup>2</sup> going through the area by scheduling and prioritization changes.

## 1.2 Problem Statement

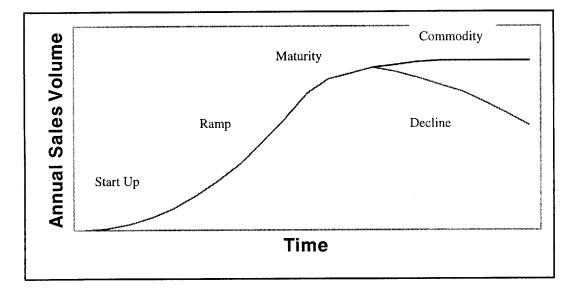

The high tech industry can be characterized as one of fast paced product development and exponentially decreasing margins on a given product. Indeed, product life cycles tend to follow the curve shown in Figure 1.

#### **Figure 1: Product Life Cycle Curve**

This curve definitely holds true for the semiconductor industry. One of the founders of this industry, Gordon Moore, coined Moore's law which states that approximately every 18 months, the speed of a microprocessor will double and its cost will halve. Furthermore, in almost any high tech development, the highest margins can be achieved in the beginning of the product's life cycle. The problem of short product life cycles are confounded in the semiconductor industry by the expense of R&D and the approximately \$2B that must be spent every time a new fab is built. However, it can also take in the range of two years to develop a new semiconductor chip process. There occurs, then, a dilemma between wanting to recoup

<sup>&</sup>lt;sup>1</sup> Photolithography (shortened to litho for the rest of this paper) is a process in which a mask is applied on a silicon wafer and a pattern is placed on the wafer using electromagnetic radiation such as ultraviolet light or X-rays.

$<sup>^{2}</sup>$  A lot is a set of wafers in a box. In general the lot travels through the fab in the box as a group, though sometimes the lot is temporarily split up. Wafers are round discs of single crystal silicon. Currently they are 8" in diameter with thicknesses in the range of 0.5 mm. Many chips are built on one wafer. 05/09/99 Shafali Rastogi

development expenses by ramping up as quickly as possible and maintaining maximum possible production while trying to go forward with development at maximum speed in order to stay at the front of the technology curve.

The purpose of this thesis is to look at the balance between doing development and production on the same line in a fab. It takes the slant of trying to maximize experiment velocity through the fab with minimum impact on production. Velocity, in this paper, refers to the speed at which experiments and production lots can make it through the fab. It is equivalent to the term WIPturns<sup>3</sup> used at Intel. When looking at organizational improvements, increasing experiment velocity means cutting down the time taken to set up and run the experiments. In the simulation model built as part of the research, increasing the velocity means minimizing queue times in front of the tools, which in turn reduces overall cycle times for those tools.

## 1.3 Research Description

This research was conducted at Intel Corporation's Santa Clara D2 fab. At the time of this project D2 was facing a number of challenges. In 1999 they anticipated an increase in production and development work coming into the facility. They were also in the midst of a massive cost reduction program, which in part meant a focus on reducing head count in the fab.

Through the 6 months time period the research was conducted, D2 produced Pentium II chips for sale, was transferring their first generation of flash memory from pure development to send to another fab for production, and began development work on their second generation of flash memory. This research uses 6 months worth of data from these three processes. It also treats the three processes as representative of the different phases of development and production in a typical fab. Historically, D2 had not expended a great deal of effort analyzing technical development (TD) work. This was changing a little, as the industrial engineering group looked for ways to better analyze the capacity needed to run TD. This research takes a stab at an in depth characterization of TD and its affects on one area, photolithography. Photolithography was focused on because at this time they were having the largest cycle time problems and they tend to be the designed bottleneck of the fab. At the time of this research, photolithography was just bringing on line seven new tools to run their five most critical layers on. The simulation model built to emulate these tools assumes that all seven tools are available.

Organizationally, D2 had long been set in how experiments were being set up and run in the fab. It was recognized, however, that the current methodology was too cumbersome and slow. In fact, one development deadline was missed in this time. There was a real drive to change the organization and procedures of setting up development to increase experimental set up speed, and to make smoother the running of experiments in the fab. In particular, the photolithography group was concerned about being able to cross train their workers on two different tool sets. They wanted standardized procedures for the running of experiments to help them achieve this goal. In part this goal was driven by the need to reduce head count in that area. The organizational research conducted in this paper set the groundwork for reducing experimental set up times and for helping photolithography smooth out the running of experiments in their area.

<sup>3</sup> WIPturns at Intel are a measure of how quickly the work in process moves through the fab. Shafali Rastogi

Conducting this research meant working closely with different groups at D2. In particular, it was necessary to involve the Integration group that set up all the experiments in the fab; the Automation group that ran the automation software used in the fab; the photolithography technicians and engineers; and the industrial engineers who did the capacity, scheduling, and prioritization work for the fab. The customers for this work were the Technical Development (TD) Operations Manager, whose job it was to coordinate experiments in the fab with the rest of the operations people, and the Photolithography Area Manager, who was concerned about the running of experiments in photolithography. The inputs and outputs of the model were delivered to the Industrial Engineering group.

## 1.4 Thesis Objective

Specific objectives of the research were to:

- 1. Provide a framework for TD set up procedures as they existed in order to show where gaps were theat were leading to long experiment set up times.

- 2. Provide a basis on which to standardize photolithography experiment running procedures.

- 3. Characterize TD at D2.

- 4. Show through the use of a simulation model the cycle time impacts of various scenarios under which they can run TD leading to some general do's and don'ts for running TD.

## 1.5 Thesis Structure

This thesis is broken up as follows:

Chapter 2 gives an overview of Intel and the semiconductor fabrication industry. Chapter 3 moves on to focus on Intel's D2 site and the photolithography group at D2. With this background, Chapter 4 goes into details on the work that was done to flowchart how experiments are set up at D2. It highlights the delays that are caused as people chase signatures and paperwork sits in queues. Chapter 5 goes into details on the standardization of photolithography experiments. The rest of the thesis is dedicated to the simulation study conducted for the Deep Ultra Violet (DUV) tools in photolithography. Chapter 6 details the model. Chapter 7 discusses the scheduling policies that were run on the model. Chapter 8 talks about the model validation and Chapter 9 is a discussion of the results. Chapter 10 explains the conclusions reached from the model. Chapter 11 is a summary of what was learned overall through the research.

## Chapter 2 Introduction to the Semiconductor Industry and Intel

Semiconductor technology began in 1875 when it was observed that selenium exhibited rectification and photoconductivity<sup>4</sup>. By 1935 rectifiers, photodetectors, and diodes were on the market. In 1947 the first transistor was invented at Bell Telephone Laboratories. By 1966 840 million transistors were sold a year. In the early 1960's, the integrated circuit was developed. As processes and equipment became more sophisticated, scientists were able to reduce the feature sizes on chips. They went from 10 mils in 1957 to 0.024 mils in 1990. Along with decreasing feature sizes, equipment costs rose. By 1990 equipment cost per machine ranged from \$500,000 to \$3,000,000<sup>5</sup>. Thus, increasing capital expenditures and increasing sophistication have been the main characteristics of the semiconductor industry. Since the late 1980's there has also been ever growing competition in the semiconductor industry. The Japanese entered the memory and device markets in the late 1980's, continuously bringing down prices. Japanese entry into the semiconductor industry led to the formation of Sematech in the early 1990's to help American firms compete with the Japanese. The last couple of years have shown growing competition even within the United States. Companies like AMD have been able to lower chip costs to the point where PC's are now available for less than \$1000. Firms have found themselves either competing on cost or on advanced technology, and today they find themselves competing on both fronts. This is certainly true for Intel, which is for the first time in a situation of cost competition coupled with a need to push the technology curve.

Intel designs, develops, makes and markets advanced microcomputer components and related products. Its principal components are silicon-based semiconductors etched with complex patterns of transistors<sup>6</sup>. With a market capitalization of \$191B, Intel is arguably the most powerful company in the United States.

Intel was founded in 1968 by Robert Noyce and Gordon Moore. Andy Grove, employee number 4, became their most famous CEO, writing such books as *Only the Paranoid Survive*. His successor, Craig Barrett, is the current CEO. Since developing their first microprocessor in 1971<sup>7</sup>, Intel has worked to design, develop, and bring new logic and memory technologies to high volumes as quickly as possible; and to proliferate the Intel name. Their *copy exactly* methodology has given them this ability to rapidly ramp up production on new technologies, and their *Intel Inside* campaign made a chip that no one can see and few understand, a household name. In short, Intel is a business and a technical success.

Intel is composed of two technical development (TD) and a number of production semiconductor fabrication (fab) facilities. Processes, such as logic or memory chips, are made in what Intel calls its *virtual factory*. A virtual factory is a combination of production facilities and a development facility. The development facility does the work necessary to bring a new chip design to full scale production. The process is then handed off to the production facilities. At this point, any change made to the process must be approved by everyone in the virtual factory. This is what is known as the copy exactly method. The method has the advantage of consistency and speeding up ramp up between all the fabs, but the disadvantage of not allowing local optimization and slowing down change in the process. For example, once a process has been established, a fab cannot buy a different type of equipment without approval from everyone in the virtual factory.

<sup>&</sup>lt;sup>4</sup> Rectification refers to the diode like characteristic of Selenium allowing it to either invert the negative or chop off the negative part of a sinusoidal wave. Photoconductivity means Selenium is a better conductor of electricity when exposed to light.

<sup>&</sup>lt;sup>5</sup> Campbell, Stephan A.. *The Science and Engineering of Microelectronics Fabrication*, New York: Oxford University Press, 199, Chapter 1.

<sup>&</sup>lt;sup>6</sup> http://quicken.excite.com/investments/snapshot/?symbol=INTC

<sup>&</sup>lt;sup>7</sup> http://www.intel.com/intel/museum/25anniv/index.htm Shafali Rastogi

A given fab is split up into seven functional areas. These areas are Diffusion/Implant, Etch, Litho, Planar & Yield, Thin Films, and Fab Support Group (FSG). All the areas except yield and FSG are grouped to correspond to one of the steps in the process flow of making a chip. The process steps are outlined in Table 1. Definitions for many of the technical terms are given in Appendix A.

| Process Step                                                                                          | Functional Area                          |

|-------------------------------------------------------------------------------------------------------|------------------------------------------|

| 1. Thermally grow starting oxide                                                                      | Diffusion/Implant                        |

| 2. Use Low Pressure Chemical Vapour Deposition                                                        | Diffusion/Implant                        |

| (LPCVD) to deposit nitride                                                                            |                                          |

| <ol><li>Pattern isolation mask (isolates n and p well</li></ol>                                       | Lihography - coat photoresist, expose to |

| transistors from each other)                                                                          | patterned reticle using UV light, and    |

|                                                                                                       | develop resist                           |

| 4. Nitride Etch - transfers the pattern from the resist to                                            | Etch                                     |

| the nitride                                                                                           | Little attender Etable                   |

| 5. Mask the p well area, leaving the n well area                                                      | Litho then Etch                          |

| exposed                                                                                               | Diffusion/Implant                        |

| 6. Implant phosphorus ions into p-well                                                                | Diffusion/Implant                        |

| 7. Grow another layer of field oxide and drive in Ph                                                  | Dinusion/impiant                         |

| ions in diffusion furnace                                                                             | Litho for mask, Etch, then               |

| <ol> <li>Mask n-well, implant Boron in p well, drive in<br/>positives in diffusion furnace</li> </ol> | Diffusion/Implant for ion implantation   |

| positives in diresion remace                                                                          | and drive-in of ions.                    |

| 9. Preclean wafer surface with hydrogen flouride and                                                  | Diffusion/Implant                        |

| grow a layer of oxide called gate oxide                                                               |                                          |

| 10. Use LPCVD to depositoin a layer of polysilicon.                                                   | Deposit in Diffusion/Implant, mask in    |

| This will be patterned into the transistor gates                                                      | litho, transfer patter in Etch           |

| 11. Grow a layer of side oxide to seal gate against                                                   | Diffusion/Implant                        |

| possible contaminants                                                                                 |                                          |

| 12. Implant a pattern of Boron to suppress runaway                                                    | Boron Lightly Doped Drain (LDD) mask     |

| electrons                                                                                             | in litho then Etch, Implant Bron in      |

|                                                                                                       | Diffusion/Implant                        |

| 13. Phosphorus LDD Mask and Implant                                                                   | Litho, Etch, Diffusion/Implant           |

| 14. Deposit nitride to create spacers that separate the                                               | Diffusion, Litho, Etch                   |

| gate from the source and the drain                                                                    |                                          |

| 15. Grow a layer of oxide to protect wafer from                                                       | Diffusion/Implant                        |

| damage                                                                                                | Mark in lithe transfer nottorn in stab   |

| 16. Heavily dope the n and p-channel source and                                                       | Mask in litho, transfer pattern in etch, |

| drains. A channel is simply the well referred to                                                      | implant in diffusion/implant             |

| earlier.                                                                                              | High temperature diffusion               |

| <ol> <li>Anneal source and drain - meaning integrate<br/>dopant into Si lattice</li> </ol>            | Thigh temperature diffusion              |

| 18. Add first metal interconnects between layers                                                      | Deposit in diffusion, Mask in litho,     |

| 10. Add mat metal merconneolo between hayero                                                          | transfer pattern in etch                 |

| 19. Deposit interlayer dielectric (ILD) to insulate                                                   | Use CVD in diffusion, pattern openings   |

| between metal layers                                                                                  | in litho and etch                        |

| 20. Add second metal interconnects                                                                    | Deposit in diffusion, Mask in litho,     |

|                                                                                                       | transfer pattern in etch                 |

| 21. Add a passivation layer to protect chip from                                                      | Diffusion                                |

| moisture or cracking                                                                                  |                                          |

| Table 1: | Process | Flow | Steps | to | Make | a | Chip |

|----------|---------|------|-------|----|------|---|------|

|----------|---------|------|-------|----|------|---|------|

Shafali Rastogi

| 22. Add bond pads, which is metal used as conduction paths for the tests | Litho Etch               |

|--------------------------------------------------------------------------|--------------------------|

| 23. Add polyimide for insulation                                         | Diffusion, Litho, Etch   |

| 24. Backgrind wafer to remove built up layers and                        | Planar                   |

| contaminants                                                             |                          |

| 25. Add gold to back of wafer to provide and ohmic                       | Sputter on in Thin Films |

| contact                                                                  |                          |

| 26. Test wafer                                                           | Yield                    |

The key point to notice in this complex process flow is that it is cyclic. Layers of chemicals are added on and patterned by running repeatedly through diffusion/implant, litho, and etch.

Of the functional areas, Intel tries to keep photolithography the bottleneck if possible. This is because the equipment in this area is the most expensive and technically complicated. Table 2 breaks down the steps that happen in photolithography:

| Step                                                        | Description                                                                                 |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1. Spin coat photoresist                                    | Spin a layer of an organic photosensitive chemical                                          |

| 2. Expose the wafer with resist on it to UV                 | This transfers the pattern from the mask onto the                                           |

| light, shining through a mask<br>3. Develop the photoresist |                                                                                             |

| 3. Develop the photoresist                                  | The resist that was exposed to UV light has been altered. You can now wash away the altered |

|                                                             | photoresist.                                                                                |

**Table 2: Basic Steps in Photolithography**

Intel breaks up its semiconductor work into what are called *processes* and *products*. A process is the series of steps that a given type of semiconductor, whether it be a logic or a memory chip, must go through to come out as say a Pentium II processor. Within a process there can be multiple products (also called dot processes since a process is given a number like 856, and then a product within that process is given a '.number ' like 856.7), which go through the same steps, but have some parameters that are unique to just that product. The series of steps that are performed in a process are called a *route*.

## Chapter 3 Intel's D2 Site

Intel's D2 site is the smaller of Intel's two development facilities. The two sites split up the product development for the various processes that Intel is developing. D2's charter is to ramp a process from design to full scale manufacturing; or as one engineer put it, from 'wiggle' to high volume. The experimentation necessary to bring up a process and ramp it to large volume is called technical development (TD). TD is one of Intel's technical competencies. TD is a silicon based competence - it is a determination and tweaking of the physical steps necessary to put multiple layers of masks on a chip<sup>8</sup>. At the time of my internship, D2 was running 0.25 micron technology<sup>9</sup>. They were running one Pentium II logic processor and two generations of flash memory.

There are many groups within Intel responsible for TD. Engineers from one of the functional groups design experiments. The Integration group takes the experiments and decides which experiments will be run, how many wafers an experiment will receive, and then makes sure that the proper paper work and communication has been done to allow the experiment to run smoothly. The automation group makes sure that the Workstream automation system they use in the fab has been appropriately updated. D2 limits the number of experimental wafers allowed in the fab at any one time, which means choosing the experiments is important. The running of experiments is a complicated procedure because there are really two goals in running TD:

- 1. To collect information from running experiments.

- 2. To not bring down equipment on the line or delay the production process.

The second goal is mainly due to the fact that D2 runs production and development on the same lines. They can do this, because the one logic and two memory processes they are running were designed to be able to use the same equipment. The fab runs production for a number of reasons, including:

- 1. To most closely simulate a production environment for development. They want to do this because the goal of the experiments run at D2 is to bring the new process into a production environment.

- 2. To keep the factory heavily loaded. Again, this is to help simulate a real production facility and to keep people challenged to behave as though it is a production environment.

- 3. To remain competitive with the other fabs. Fabs at Intel are rated by their cost per wafer, their wafer starts, and their die and line yields<sup>10</sup>. Being a smaller fab, D2 has struggled to keep their cost per wafer down. Increasing wafer starts is one way to do this.

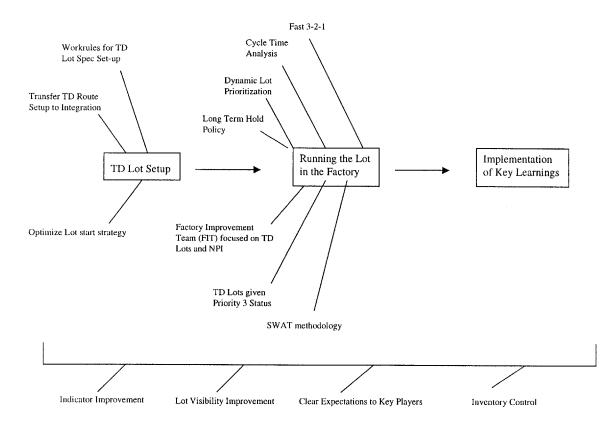

The relationship between TD and production is of paramount importance at D2. Despite a charter focused on TD, TD is not the primary driver at D2. Many people at D2 focus on production as the main importance of the fab. In fact, last year, 75% of the people in the fab did production work. This thesis focuses on TD as the primary job of the fab, but the relationship between production and TD plays a key role in the analysis presented. Figure 2 is a D2 TD System Overview drawn up by the TD Operations Manager responsible for managing the interface between TD and the factory operations. Following is an explanation of some of the issues he outlined as facing TD, and then a narrowing in on the thesis focus.

<sup>&</sup>lt;sup>8</sup> Burgelman, Robert A.. Fading Memories: A Process Theory of Strategic Business Exit in Dynamic Environments. Stanford University: Administrative Science Quarterly, p. 32, 1994.

<sup>&</sup>lt;sup>9</sup> 0.25 micron refers to the minimum width of a line that can be put on a chip. The semiconductor industry is continuously working to drive this down.

<sup>&</sup>lt;sup>10</sup> Line yield is a measure of how many wafers per lot make it through the process. Die yield is a measure of the number of good chips on a wafer.

#### Figure 2: TD System Overview

#### 3.1 TD Lot Set Up

This is the front end of experimentation. Issues at this point include:

- Workrules for TD Lot Spec Set-Up: Each lot has a lot spec attached to it. This lot spec details the route that the lot will be travelling. For TD the lot spec may have steps that are modified, added or deleted. The work rules are necessary to prevent confusion on the floor caused by the changes in the normal or *Plan of Record* (POR) lot spec.

- Transfer TD Route Setup to Integration: It is the job of Integration to set up the routes that TD lots follow and to make sure that the fab is able to handle the changes. This is a complex process and D2 still struggles with misprocessing and lots being put on hold because they cannot be processed by the technicians.

- Optimize Lot Start Strategy: D2 has a maximum limit on how many TD wafers can be in the fab at one time. Integration and Production Control must figure out which experiments they will allow to enter the fab so as not to exceed this limit.

#### 3.2 Running the Lot in the Factory

When TD lots are in the fab, they are tracked as they make there way through the process. Some important considerations in running the lots are:

Fast 3-2-1: Fast 3-2-1 is the generic method used at Intel to decide which type of lot to look at next. Each lot is put into a quadrant as illustrated in Figure 3. The highest priority is given to Quadrant 1,

Shafali Rastogi

05/09/99 Page 18 then 2, 3, and lastly 4. Based on the queue at the next step and the queue at the current step, a lot is prioritized as to when it can run. While this method works quite well, it is also being evaluated to make sure that it is the best method.

| 1. Short queue at next   | 2. Short queue at  |

|--------------------------|--------------------|

| step, long queue at this | next step, short   |

| step                     | queue at this step |

| 3. Long queue at         | 4. Long queue at   |

| next step, long          | next step, short   |

| queue at this step       | queue at this step |

Figure 3: FAST 3-2-1 System

Cycle Time Analysis: The Industrial Engineering group at Intel is responsible for doing cycle time analyses. They look at what the cycle time should be based on tool availability and cycle time goals. Last year cycle time goaling went through a major revamp to better meet factory needs. This group continues to look at cycle time goaling algorithms and how to figure out cycle times. This is especially challenging for TD work, which tends to have a lot more uncertainty as to what will be required when it hits the floor.

Dynamic Lot Prioritization: Lots are prioritized according to Table 3.

| Priority | Description                                              |

|----------|----------------------------------------------------------|

| 1        | Will hold a tool open for this lot. Highest WIPturn goal |

| 2        | Second highest WIPturn goal                              |

| 3        | Most TD                                                  |

| 4        | Monitor wafers                                           |

| 6        | Production wafers. Lowest WIPturn goal                   |

**Table 3: Lot Prioritization**

This prioritization is periodically revisited especially for TD, where they would like to lower the prioritization. Lot prioritization is linked to the fab's main measured called *WIPturns*. WIPturns are the average number of activities<sup>11</sup> a wafer goes through per day. The higher the

<sup>&</sup>lt;sup>11</sup> An activity is an irreversible step a wafer goes through. For example, after a wafer has been etched it is difficult or impossible to undo the work. On the other hand, just patterning a mask on photoresist in litho can be undone fairly easily.

WIPturn goal the greater the priority of the wafer. This priority supercedes FAST 3-2-1 priority.

- Long Term Hold Policy: This is an interesting problem at Intel. Lots that are put on long term hold are taken off the wafer count for TD wafers. Thus, engineers can increase the number of experiments they have running in the fab by putting some lots on hold. These lots are then outside the system and at some level defeat all the work that is put into controlling TD lots. This is because putting lots on long term hold complicates the measuring of the real cycle times for the wafers and the planning of experiments. For example, when a lot has been put on long term hold, should they stop the clock on that lot as far as cycle time goes? Does that lot still count towards the experimental wafer limit at D2? At the moment it does not count towards the cycle time of the lot and it does not count towards the limit, but whether this is proper is still being considered. Another issue is that engineers can take lots off of long term hold and insert them in the system. This disrupts the scheduling efforts and the smooth experimental set up system that Integration is trying to maintain. In a sense, the long term hold policy is a loop hole in the experimental set up system that, though it may be necessary, disrupts the systematic running of experiments.

- TD lots given P3 status: D2 is still experimenting with how to weight priorities. In 1998 a Priority 3 lot could not sit in queue for more than six hours. If this limit was encroaching, the lot had to be moved to the front of the queue. They have been experimenting with increasing that wait to 12 hours.

### 3.3 Ongoing Issues

Indicator Improvement: Are they using the right metrics to measure success of TD?

Lot Visibility Improvement: TD lots continued to be misprocessed or put on hold. How can this be prevented?

Clear expectations to key players: The entire TD process takes cooperation and communication between many different groups, including engineering, the functional areas, and integration. Improving

the process so that it is more efficient and so that mistakes do not happen is an ongoing effort. Inventory control: How do they deal with long term holds and what is the best use of the wafer limitation?

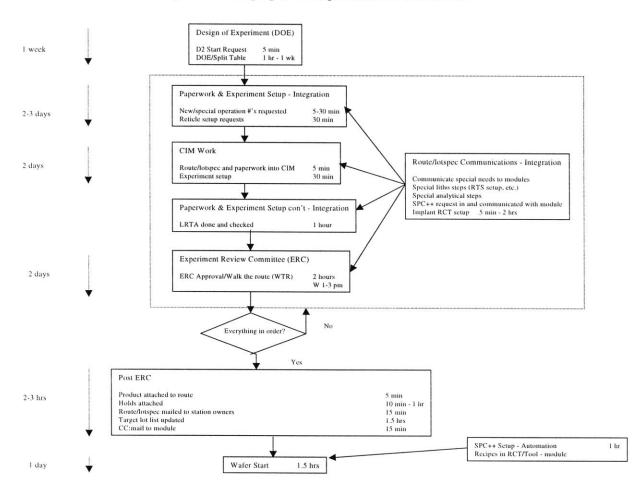

## Chapter 4 The Setting up of Experiments

The first part of the thesis project to help D2 reduce experiment cycle times was to look at the setting up of an experiment. This is what is called the front end of an experiment. At D2, one of the primary goals in the setting up of an experiment is that it does not negatively impact production<sup>12</sup>. This could happen, if for example, a measurement device shut down a tool because it mistook a change caused by an experiment for a tool error. Another part of the effort of setting up an experiment is to make sure that the experiment is properly integrated into the fab system and that the experiment runs smoothly while it is in the fab. Now, it takes about 8 weeks to make a chip. The setting up of an experiment only takes two days to a week. Even though this is just a small percentage of the overall cycle time for a wafer to leave the fab, it is a completely person made and beaurocratic addition to the cycle time. That is, while all the paperwork is being completed to get the experiment into the fab, the actual experiment is not being advanced at all. Also, every time an engineer wants to make a change to an experiment, the entire set up procedure is repeated. Thus, for a given experiment, the setup procedures may have to be repeated multiple times.

It is understood that a disciplined set up procedure is necessary at D2 to prevent unnecessary confusion or machine failures in the fab. The question was, given the set up procedure is as it is, what causes the delays? To answer this, the procedure to set up an experiment was flowcharted and comparison made between how long the actual steps took to the 'window' people wanted or needed to do the job. The window could be required because of queues, because people are multitasking, or because they are waiting for someone else to finish their part before they can go. The flowchart is shown in Figure 4.

<sup>&</sup>lt;sup>12</sup> This goal is part of an overriding issue at D2, which is that of conflicting missions. As a development facility, D2 should emphasize TD, but instead, it is put more in the role of a necessary activity that should not impact the more important goal of producing sellable chips. There is no easy resolution to this conflict, nor is D2 planning to change this goal. Shafali Rastogi 05/09/99

Figure 4: Setting Up a TD Experiment for the D2 Fab

Appendix B explains in detail what the different steps are. Most of the technical and Intel specific jargon is defined in Appendix A. The main driver of this process is Integration. The experiments are sent to them, they start the paperwork, and submit the package to ERC for approval.

The key learning from this study was that paperwork spent a great deal of time waiting for signatures and in queues. Consider these parts of the process from the perspective of Integration:

- Communicate special operations to litho

- Get signatures from litho for special steps

- Talk to module engineers about special analytical steps

- Signatures required for new lot specs can require signatures from entire virtual factory

- Litho must return the RTS table

- LRTA sits in queue at CIM group waiting to be put into Workstream

- If ERC approval is not received, certain steps must be redone

Every time a step goes to another group, the progress of the lot is taken out of the hands of Integration, yet they are considered responsible for getting experiments into the fab. This creates a great deal of stress for this group. They spend a lot of their time chasing and hounding people, that they could spend working on Shafali Rastogi 05/09/99

Page 22

setting up other experiments. At the same time, the process is very paper and signature intensive. Since there are many experiments being set up or changed every week, people build up queues.

Using this flowchart, one finds that the main box to attack is the large dotted box. It is the CIM queue and the communication done by integration that is adding all the extra time. Things D2 is looking at changing to improve this are:

- Eliminate unnecessary signatures! The paperwork and corresponding signature work that currently exists in the system is the result of years of patchwork solutions to problems that occurred in the fab. They aim to spread the blame for possible failures, when it would be more efficient, and according to people who work in the system, more desirable, to give people full responsibility for their part of the process.

- Move to a more web based system. This will speed up the paperwork process.

To really improve the system, D2 needs to look at each part of the procedure in detail, and ask the question: Why are we doing this? What would happen if we eliminate this step or this signature? They should try a green field approach, where Integration, Automation, and the TD operations people figure out what they really need to ensure that experiments run smoothly. One of the key problems with this system is that it is really complex and cumbersome. If it can be simplified, the next step would be to aim towards getting engineers inputting more of their own experiments. If this can be done, the advantages will be:

- The process will speed up

- It will prevent engineers from trying to go around the system, which will help from a system accounting point of view

- The Integration group will not be under as much stress

- Automation can shift more focus on improving systems than entering data

## Chapter 5 Standardization of Photolithography Experiments

In the next stage of my analysis of cycle time reduction in experiments at D2, I focussed on photolithography. As Campbell explains in *The Science and Engineering of Microelectronic Fabrication*,

Lithography is the most complicated, expensive, and critical process in mainstream microelectronic fabrication...Lithography accounts for nearly one third of the total fabrication cost, a percentage that is rising.<sup>13</sup>

As such, Intel is conscientious to try and make photolithography the bottleneck of the fab. The purpose of this project was, again, to increase experiment velocity by improving the TD process. Photolithography was a natural choice to focus on in looking experimentation in the fab because:

- It is the designed fab bottleneck

- There are 20 layers on a given chip that must all go through photolithography. This reentrant flow means that any improvement is very important in the overall process.

This project, done with the photolithography group, was one that had been of concern for months. The project was to standardize the format of experiments that entered the fab. Litho wanted to do this for a few reasons:

- 1. There was a real drive to make experiments look like production in the fab. The thinking was that if one can make experiments almost invisible to the technicians on the floor, they will run more smoothly.

- 2. Litho had two different toolsets and three different processes running through it. The way experiments were coming into the area across the different tool sets and the different processes was not consistent. This meant confusion on the floor that led to holds and misprocessing.

- 3. As part of their cost reduction effort, they wanted to cross train technicians across the two tool sets.

The most challenging part of creating the standards was achieving consensus among all the involved parties. This included Integration, Automation, and litho engineers for both tool sets. Integration was further divided because a different group set up the flash processes and a different group did logic. They were also split by who did the front end and who did the back end of the processes<sup>14</sup>.

The final outcome of the standardization work is shown in Figure 5.

<sup>&</sup>lt;sup>13</sup> Campbell, p. 152.

<sup>&</sup>lt;sup>14</sup> The front end of a process are all the steps up to Metal 1 shown in Table 1. The back end is the metal interconnects onwards. Shafali Rastogi

| PROCESS                                 | Standard                                                              | Non-stand <b>a</b> rd                          | Short term Special processing                                                                                                                              | Processing                                                                                                                 | Trouble Shooting<br>Special Processing                                                                                                                 | Owner                      |

|-----------------------------------------|-----------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| EXAMPLES                                | POR                                                                   | Test wafers, Blind Steps,<br>Production builds | Splits, processing of<br>one or two lots                                                                                                                   | Pilots, TD baseline                                                                                                        | excursions, special<br>measurements                                                                                                                    |                            |

| REQUIREMENTS                            |                                                                       |                                                |                                                                                                                                                            |                                                                                                                            |                                                                                                                                                        |                            |

| Operation number                        |                                                                       | 4 numbers                                      | 2 or 3 numbers                                                                                                                                             | 2 or 3 numbers                                                                                                             | POR number                                                                                                                                             | Integration/<br>Automation |

|                                         | func area+F(if flash)+'/-+3(if<br>803)+layer + desc (max 10<br>chars) | 803)+layer + desc (max 10                      | func area+F(if flash)+*/-+3(if<br>803)+layer + desc (max 10<br>chars)                                                                                      |                                                                                                                            | func area+F(if<br>flash)+*/-+3(if<br>803)+layer + desc                                                                                                 | Integration/<br>Operations |

| Operation<br>Description                | e.g. Flash Litho S/E/D FL6<br>803                                     | e.g. Flash Litho S/E/D FL6<br>803              | e.g. Flash Litho S/E/D<br>FL6 804                                                                                                                          |                                                                                                                            | e.g. Flash Litho<br>S/E/D FL6 804                                                                                                                      | Integration/<br>Operations |

| Lot Spec                                | yes                                                                   | yes                                            | yes                                                                                                                                                        | no                                                                                                                         | no                                                                                                                                                     | Integration                |

| Lot attrib (SPR) flag                   | No                                                                    | No                                             | Yes                                                                                                                                                        | yes                                                                                                                        | Yes                                                                                                                                                    | Integration                |