| 997 Y.,     | SAC.<br>T      | (1)<br> |       | 904<br>197      | IUI  |

|-------------|----------------|---------|-------|-----------------|------|

|             | a tang da sa s |         |       | <br>· · · · · · |      |

| 1.76        | Å.             | R       |       | 4               |      |

| -12 Core 2* | ~ ()           | · • •   | · ·-· |                 | 1411 |

# Automated Wavelength Recovery for Silicon Photonics

by

Erman Timurdogan

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

Master of Science

## at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

## FEBRUARY 2013

©2013 Massachusetts Institute of Technology. All rights reserved.

Signature of Author:\_\_\_\_\_

Department/of Electrical Engineering February 1, 2013

Certified by:\_\_\_\_\_

Michael R. Watts Professor of Electrical Engineering Thesis Supervisor

Accepted by:\_\_\_\_\_

Leslie A. Kolodziejski Professor of Electrical Engineering Chair, Committee for Graduate Students

## Automated Wavelength Recovery for Silicon Photonics

by

Erman Timurdogan

Submitted to the Department of Electrical Engineering and Computer Science on February 1, 2012 in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering and Computer Science

## ABSTRACT

In 2020, 1Tb/s on-/off-chip communication bandwidth and ~100fJ/bit total energy in a point to point link is predicted by Moore's law for high performance computing applications. These requirements are pushing the limits of on-chip silicon CMOS transistors and off-chip VCSELs technology. The major limitation of the current systems is the lack of ability to enable more than a single channel on a single wire/fiber. Silicon photonics, offering a solution on the same platform with CMOS technology, can enable Wavelength Division Multiplexed (WDM) systems. However, Silicon photonics has to overcome the wafer level, fabrication variations and dynamic temperature fluctuations, induced by processor cores with low-energy high-speed resonators.

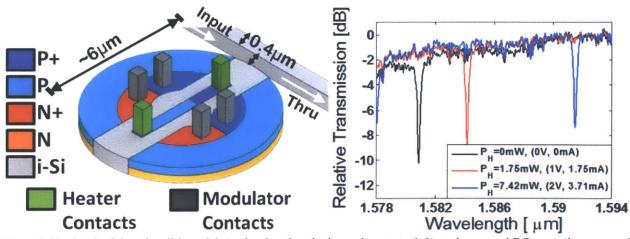

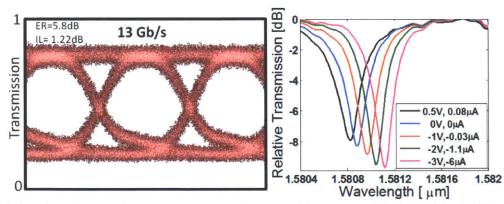

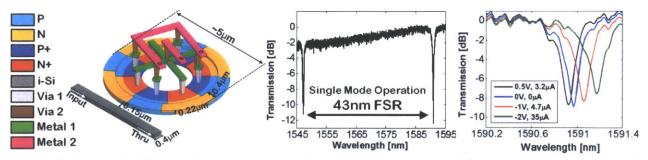

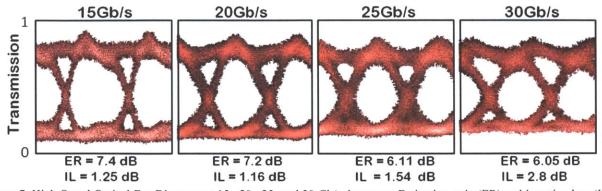

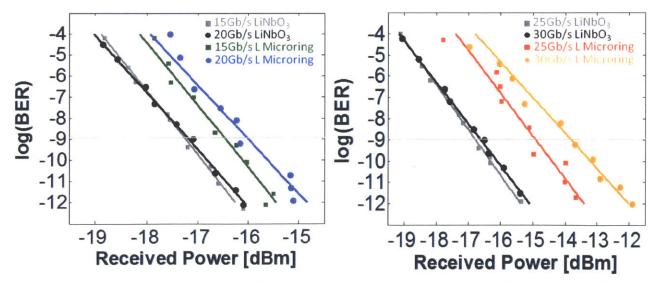

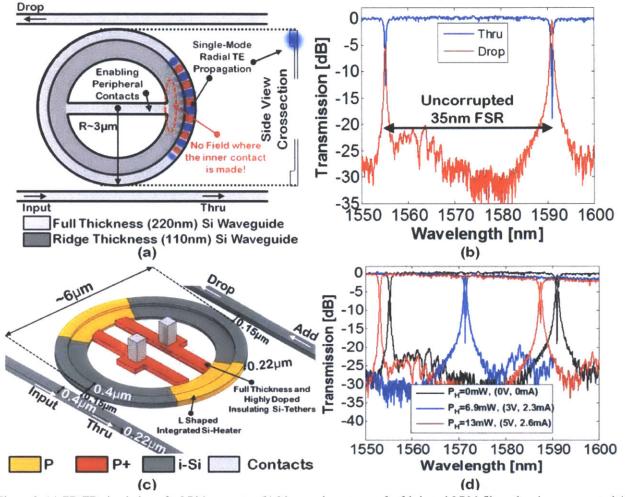

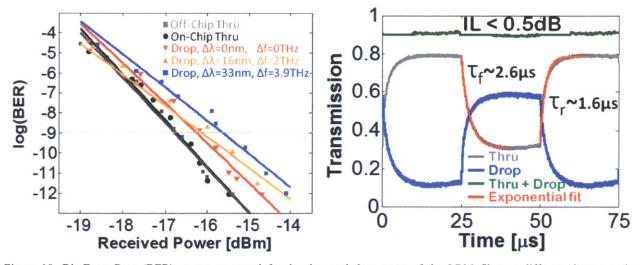

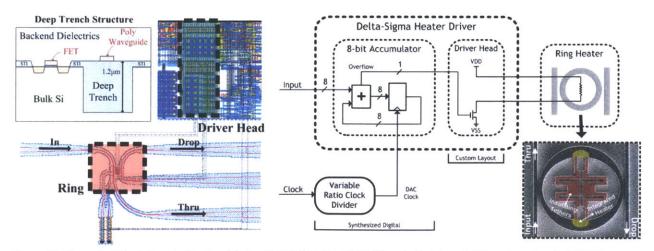

In this work, we offer a solution, called as Automated Wavelength Recovery (AWR), to these limitations. In order to demonstrate AWR, we design and demonstrate high performance active silicon resonators. A microdisk modulator achieved open eye-diagrams at a data rate of 25Gb/s and error-free operation up to 20Gb/s. A thermo-optically tunable microdisk modulator with Low power modulation (11fJ/bit) at a data rate of 13-Gb/s, a 5.8-dB extinction ratio, a 1.22-dB insertion loss and a record-low thermal tuning  $(4.9-\mu W/GHz)$  of a high-speed modulator is achieved. We demonstrated a new L-shaped resonant microring (LRM) modulator that achieves 30 Gb/s error-free operation in a compact (< 20  $\mu$ m<sup>2</sup>) structure while maintaining single-mode operation, enabling direct WDM across an uncorrupted 5.3 THz FSR. We have introduced heater elements inside a new single mode filter, a LRM filter, successfully. The LRM filter achieved high-efficiency (3.3 $\mu$ W/GHz) and high-speed ( $\tau_f \sim 1.6 \mu s$ ) thermal tuning and maintained signal integrity with record low thru to drop power penalty (<1.1 dB) over the 4 THz FSR and <0.5dB insertion loss. We have integrated a heater driver and adiabatic resonant microring (ARM) filter in a commercial bulk CMOS deep-trench process for the first time. The proposed AWR algorithm is implemented with an ARM multiplexer. An advanced method for AWR is also introduced and demonstrated with passive resonators.

Thesis Supervisor: Michael R. Watts Title: Professor of Electrical Engineering

#### ACKNOWLEDGMENTS

There are many people that have contributed in the completion of this thesis. Working with my colleagues at MIT over the last 2.5 years has been a valuable experience in many ways. The formal collaborations and random discussions have lead to many innovative ideas. The research environment at MIT provided the freedom to investigate and learn things in many aspects. Friends, family have made the experience outside of campus enjoyable throughout consecutive trials-errors and tapeouts.

I owe many thanks for information and assistance to spend their time to give an extra hand or incentive to finalize this work. I would like to start with off-campus collaborations. Douglas D. Coolbaugh, Gerald Leake from CNSE, helped to fabricate my exotic designs and tried to offer solutions for making things work. They also provided insight to limitations of the process. It has been a great pleasure to work and discuss with Roy Meade, Ofer Tehar-Zahav and many others from our collaboration with Micron Technology. This work has been funded the Defense Advanced Research Project Agency (DARPA) through POEM program. On campus, Jason Orcutt was the key person that helped me with infinite patience to submit a CMOS design for fabrication under tight deadlines and high stress. He also helped me to get familiar with experiments on POEM runs. Aleksander(Sasha) Biberman guided me to perform experiments in the right way, gave insights about my infinite ideas and listened and perfected my presentations before my conference talks. Jie Sun and Ami Yaacobi have been great officemates and combination of our ideas have resulted great discoveries. Cheryl Sorace-Agaskar taught Sentaurus and process simulations. I have spent sleepless nights to meet deadlines working alongside a great team of photonic designers; Zhan Su, Ehsan S. Hosseini, Michele Moresco, Brad G. Cordova, Purnawirman and circuit designers; Michael Georgas, Ben Moss, Jonathan Leu and Chen Sun. It has been a great opportunity to work closely with Prof. Vladimir Stojanovic, who has served as the project lead on POEM effort and has great insight about electronic and photonics. His motivation and dedication to make things work inspired in many ways.

Prof. Michael R. Watts has provided me with an active academic environment in Photonic Microsystems Group. I learnt a lot about Silicon Photonics in a short time from his expertise. Mike has provided brilliant insights in 5 to 10 minutes meetings. His advices and ideas in general pushed me to become a better person in many ways. He is also a considerate person who has been valuable over the bad times. It will be a great pleasure to pursue my studies further in his group.

# **Table of Contents**

| 1. Introduction                                                                       | 9 |

|---------------------------------------------------------------------------------------|---|

| 1.1 Electrical on-/off-chip communications                                            | 9 |

| 1.2 Optical on-/off-chip communications2                                              | 1 |

| 1.3 Data Storage Scaling2                                                             | 5 |

| 1.4 Energy per bit scaling on a chip2                                                 | 6 |

| 1.5 Silicon Photonics2                                                                | 7 |

| 1.6 Wafer Level and Process Variations3                                               | 1 |

| 1.7 Thermal Fluctuations                                                              | 2 |

| 1.8 Available Solutions3                                                              | 3 |

| 1.9 Electro-optic tuning/modulation3                                                  | 5 |

| 1.10 Thermo-optic tuning                                                              | 7 |

| 1.11 Automated Wavelength Recovery Architecture3                                      | 8 |

| 1.12 Conclusions                                                                      | 2 |

| 1.13 References                                                                       | 3 |

| 2 Active Silicon Photonic Resonators4                                                 | 8 |

| 2.1 Resonant Modulators4                                                              | 8 |

| 2.2 Vertical Junction Microdisk Modulator at 25 Gb/s4                                 | 9 |

| 2.2.1 Device characterization and demonstrated results5                               | 0 |

| 2.3 Vertical Junction Microdisk Modulator with Integrated Heater5                     | 3 |

| 2.3.1 Device characterization and demonstrated results5                               | 4 |

| 2.4 L-Shaped Resonant Microring Modulator5                                            | 6 |

| 2.4.1 Device characterization and demonstrated results5                               | 7 |

| 2.6 Active Resonant Filters5                                                          | 9 |

| 2.7 L-Shaped Resonant Microring Filter with Thermal Tuner5                            | 9 |

| 2.7.1 Device characterization and demonstrated results6                               | 0 |

| 2.8 Monolithically Integrated Adiabatic Resonant Microring Filter with Thermal Tuner6 | 2 |

| 2.8.1 System Overview and Experimental Results6                                       | 3 |

| 2.9 Conclusions                                                                       | 5 |

| 2.10 References                                                                       | 7 |

| 3 Automated Wavelength Recovery Demonstration                                         | 9 |

| 3.1 Device fabrication and characterization                                           |   |

| 3.2 Automated Wavelength Recovery (AWR) Algorithm            | 73 |

|--------------------------------------------------------------|----|

| 3.3 Thermal and Laser Frequency Drifts                       | 76 |

| 3.4 AWR Speed and Stability Optimization                     | 77 |

| 3.5 Laser intensity dependence                               |    |

| 3.6 Conclusion                                               |    |

| 3.7 References                                               |    |

| 4 Advanced Automated Wavelength Recovery                     |    |

| 4.1 Integrated Amplitude to Phase Converter Theory           |    |

| 4.2 Integrated Amplitude to Phase Converter Design           |    |

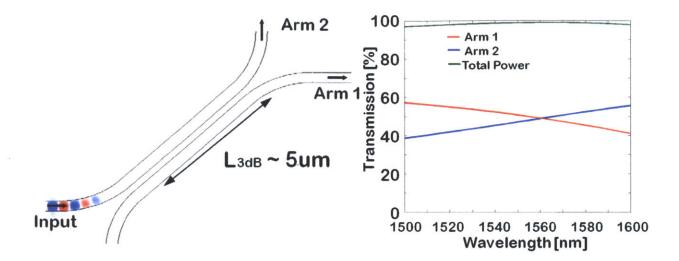

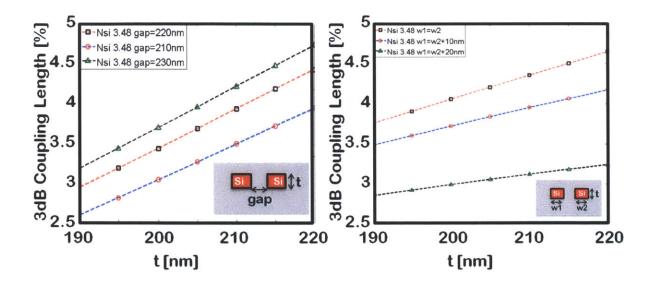

| 4.2.1 Arbitary Coupler Design                                |    |

| 4.2.2 The 3dB Coupler Design                                 |    |

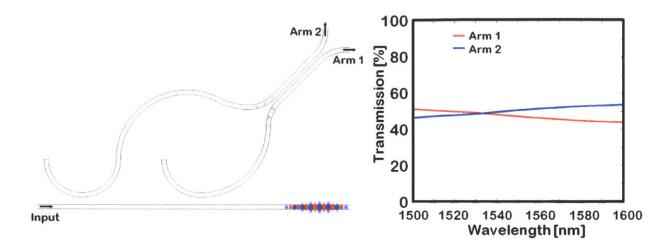

| 4.2.3 FDTD-3D Simulation of the Amplitude to Phase Converter | 94 |

| 4.3 Advanced AWR with Amplitude to Phase Converter           |    |

| 4.4 Conclusions and Future Work                              |    |

| 4.5 References                                               |    |

| 5 Conclusions and Future Work                                |    |

## 1. Introduction

Over the course of first chapter, on-/off-chip electrical and optical communications will be introduced with a focus on realization of Wavelength Division Multiplexed (WDM) Silicon Photonics. The roadmap of WDM Silicon Photonics will be summarized and an overview of ways to overcome the challenges of silicon photonics will be given. The need for automated wavelength recovery (AWR) will be justified and the architecture of AWR will be proposed.

#### 1.1 Electrical on-/off-chip communications

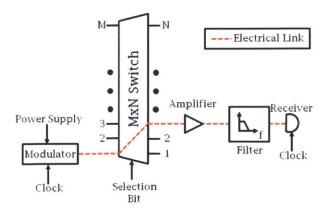

Since the digital era started with Complementary Metal Oxide Semiconductor (CMOS) technology, the data storage, transmission bandwidth boomed up and the communication technologies scaled the clock frequency, power efficiency, on- and off-chip bandwidth and hard disk capacity. Gordon E. Moore predicted that the number of integrated components (especially transistors) will be doubled at every two year in 1965 [1]. His statement is true since 1965 and it is often called as Moore's Law. P-type and N-type metal oxide semiconductor field effect transistors (NMOS and PMOS) are the building blocks of on-chip communications. Off-chip communications utilized high speed electrical interconnects before the fiber optics and VCSEL technology. The off-chip short distance communication is still dominated with electrical interfaces. Definitions might vary for an electrical link but a simple electrical point to point link should have electrical modulator, switch, filter, amplifier and receiver (Fig. 1).

Figure 1. Point to point electrical Link with distributed clock

Digital modulators need to transmit two distinct logic levels; "1"s and "0"s at the local clock frequency. Data at the output of the modulator will be fed to a router or switch. The switch will pass the data to the desired node. The data will be amplified and filtered before it reaches the receiver. The data will be received and sampled using the clock at the end and signal integrity of this transmission will be determined with bit error rate (BER). BER of less than  $1 \times 10^{-12}$ , is considered error-free as a communication standard.

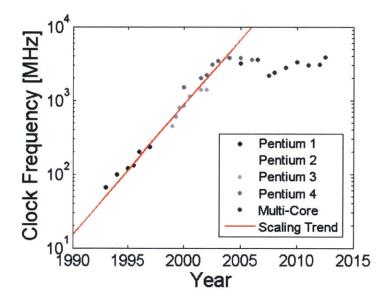

On-chip communications is dominated with electronics only due to cost effectiveness and scaling of transistor technology. Clock frequency scaled significantly from 66 MHz (1993, Pentium) to 3.9GHz (2012, Core i7 Extreme). Intel chipset x86 clock frequency is shown in Figure 2 and the clock frequency scaling trend is in good agreement with Moore's Law from 1993 to 2004.

Figure 2. Clock frequency scaling for Intel chipset x86

After 2004, the clock frequency is kept similar to Pentium 4 and the number of cores is increased. Microprocessor area kept same to preserve high yield through the wafers. [2] Instead, the transistor density scaled to improve on-chip performance. This is enabled with research on advanced materials and Silicon fabrication [3-5], low voltage signaling (LVS) [6], memory architecture [7] and multicore design and performance validation [8,9]. These developments targeted to keep the scaling computer

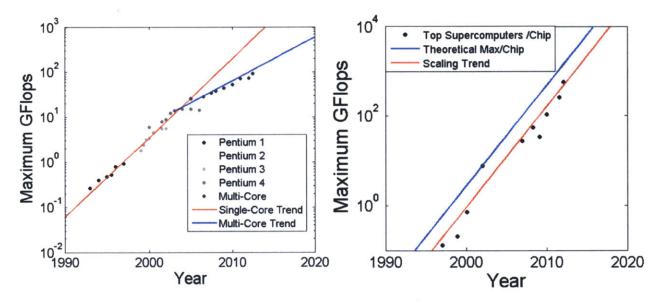

performance. The number of floating-point operations per second (FLOPs) is widely used as a measure of computer performance. Theoretical maximum FLOPs can be calculated as follows [39];

$$FLOPs = N_{core} f_C \frac{Operations}{Core \times Clock \ Cycle}$$

Where,  $N_{core}$  is the number of cores and  $f_C$  is the clock frequency. Commodity microprocessors can currently at least perform 4 operations whereas supercomputers can perform more than 12 operations per core in single clock cycle. Since this assumes each core is fetching the maximum number of operations, it predicts a theoretical maximum FLOPS. Computer performance is plotted in Figure 3. Commodity computer performance is still increasing with a rate similar to Moore's Law after 2004. Even at this scaling rate, we expect to reach around ~1 TFLOPs by 2020. However, multicore processing does not

Figure 3. Maximum FLOPs for commodity (left) and supercomputer (right) microprocessor scaling as a measure of computer performance and memory bandwidth. Top Supercomputer FLOPs per chip (right) is calculated based on TOP500.org data. Theoretical maximum FLOPs per chip (right) is calculated using the FLOPs equation.

necessarily boost the performance linearly since some tasks cannot be handled in all cores at the same time. Amdahl has foreseen the future of computing in 1967 [23] and based on his predictions, Amdahl's Law of scaling has been formulated as follows [24];

Speedup <sub>parallel</sub> =

$$\frac{1}{r_{seq} + \frac{1 - r_{seq}}{N_{core}}}$$

Where,  $r_{seq}$  is the ratio of the sequential part of the program,  $1 - r_{seq}$  is the ratio of the parallel executable part of the program. Here the program is assumed to be a combination of sequential and parallel part. If program execution is all parallel, then speedup is linear with number of cores. However, if the tasks are sequential, then there is no speedup due to parallel computing. Therefore, asymmetric multicore chips that combine one or more powerful core and standard cores inside a package and dynamic microprocessors which can arbitrarily interchange between sequential and parallel mode, have been proposed [24]. Both approaches have maximized the parallel computation Speedup than symmetric multicore chips that involve identical cores.

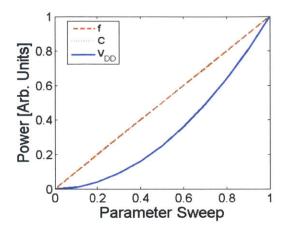

At this point, it is important to understand the trend for how to keep low power at higher clock frequency and having multiple cores. Power of a single transistor can be calculated as the following;

$$P_{tr} = N_{core} \,\alpha \, f_C \, C_{tr} \, V_{DD}^2$$

Where,  $P_{tr}$  is the transistor power,  $\alpha$  is the encoding scheme related multiplier,  $C_{tr}$  is the transistor capacitance and  $V_{DD}$  is the supply voltage. For non-return to zero on-off keying (NRZ-OOK) pseudorandom bit sequence (PRBS), there are equal number of 0-0, 0-1, 1-0, 1-1 transitions and the power is only consumed in 0-1 transition. Therefore,  $\alpha$  is equal to 1/4. The  $C_{tr}$ ,  $V_{DD}$ ,  $f_C$  is swept from 0 to 1 to show dependence of transistor power (Fig. 4).

Figure 4. Normalized on-chip power scaling as a function of transistor capacitance, voltage supply and clock frequency

The power consumption will be constant if the transistor capacitance and voltage supply can be lowered while the clock frequency is rising. That is the reason the fabrication processor node is dwarfed from 0.8µm (1993) to 22nm (2012). While the transistor area is scaled down to achieve low power devices, the power density increased significantly. Power and heat density limited the scaling of transistor technology and the multi-core era has started in 2004. The methods for diminishing voltage supply ( $V_{DD}$ ) up to a factor of 2 has been demonstrated recently [10, 11] and it might be an enabler for power and performance scaling.

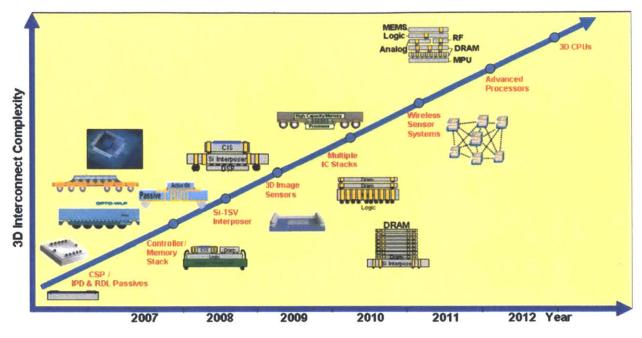

Before moving from the on-chip to off-chip communications, one must discus about the memory access which is bridging the on- and off-chip communications. On-chip performance is measured by FLOPs and memory or data storage is indicated with bytes per second. The relation between byte (b) and FLOP are reported as 1 b/FLOP [12] for commodity and 0.5 b/FLOP [10] for supercomputers. 1 b/FLOP is regularly quoted for memory bandwidth. Therefore, we expect to reach around 1 Tb/s memory bandwidth in 2020 (Fig. 3). High bandwidth operation will be enabled by 3D CPU and it is predicted to be available by 2013 in 3D integration roadmap (Fig. 5) [33]. The on-/off-chip bandwidth will be bridged using an intermediate vertical connection between board to chip or chip to chip in 3D integration.

Figure 5. 3D integration complexity and roadmap predicted by Fraunhofer IZM

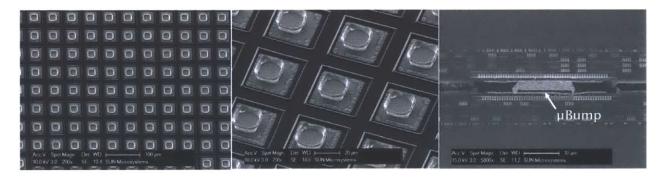

Ball grid array is being used to achieve high speed interconnects between CMOS chips [26]. Microballs are squeezed by the top and bottom chips to achieve microbump/solder structures (Fig. 6). It can be utilized for CMOS and photonic chip interconnects as well. However, standard pitch is ~50µm and allows

Figure 6. Micgrographs of high density microbump array (left), closeup on microbump array (middle), flip-chip bonding of two CMOS chips (right)

low density interconnects. Therefore, reaching high density interconnects and high off-chip bandwidth requires new methods of chip to chip interconnect.

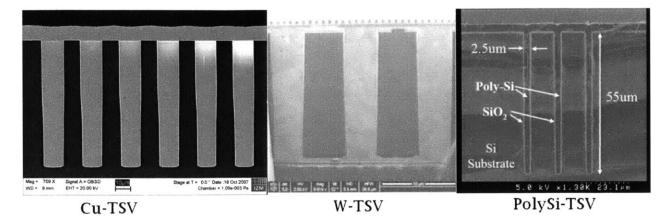

On the other hand, Through Silicon Via (TSV) is a key alternative since it is an extension of convential via technology implemented in process design kits [22]. TSV is slightly taller than the existing

via on a microprocessor which can provide high speed and low latency off-chip interconnects and access to memory compared to existing technologies. TSV is currently formed by Cu, W and Poly-Si (Fig. 7).

Figure 7. Cu-TSV (Fraunhofer IZM), W-TSV and Poly-si TSV

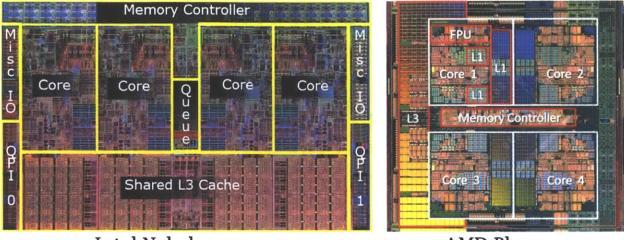

The common limitations of TSV are increased on-chip heat dissipation and density as well as threshold voltage shifts on transistors. The heat and power consumption problem might be alleviated by running at low clock frequencies [30]. RC time constant of the dense TSV interconnection will be dominated by high resistance due to thin cores or wires and via to via or wire to wire capacitance and inductance. TSVs are modeled into lumped electrical lines [28, 29] and estimated resistance and capacitance is agreeing with detailed simulation [31]. Due to the bandwidth limitation, TSV pitch is expected to be 16µm and pin density of TSVs is ~  $4 \times 10^3$ /mm<sup>2</sup> in 2011-2014 time frames [14]. Each pin is capable of supporting data rates up to 3 Gb/s [27]. Intel Nehalem and AMD Phenom Quad-core processors are shown in Figure 8 and 731 and 463 million of transistors arranged into a 263 and 283 mm<sup>2</sup> die area, respectively [32]. TSVs will most likely cover only 1-5% of the microprocessor chip [29]. Utilizing only 1% of the quad-core die area, cumulative off-chip bandwidth with these estimated numbers will be ~ 32 Tb/s. For the same chip the cumulative off-chip bandwidth will be ~0.7 Tb/s with microbump array.

## Intel Nehalem

## AMD Phenom

Figure 8. Intel Nehalem quad-core die (left) and AMD Phenom quad-core die (right) (images are not to scale) On-chip to off-chip bandwidth is handled using low voltage signaling (LVS) which refers to wide range of differential signaling technologies with low voltage operation. Intel and AMD are using QuickPath Interface (QPI) and HyperTransport Interface (HPI) architecture, respectively. Intel's QPI improved the uni-directional front side bus and provides high speed, packetized, point to point links with differential signaling since 2008 [35]. This allowed high bandwidth up to 204.8 Gb/s and low latency utilizing 84 pins (data rates up to 2.5 Gb/s per pin). Although QPI or HPI is not designed for memory interconnects, it is the state of the art technology to estimate the current on-chip to off-chip electrical signaling capacity. Recently, a 1cm CMOS link with 356 and 463 fJ/link at 4 and 5.2 Gb/s has been demonstrated, respectively [36]. This Link is provided with 90nm process and integration to advanced CMOS process can double the bandwidth of QPI. Additionally, ball grid pitch scaling down to 35 μm will enable off-chip bandwidth of ~3.2 Tb/s.

For off-chip communications, the commodity computers and data centers, supercomputers have established different standards. The focus will be first in commodity interconnect technologies and later the rise of photonics in the supercomputers, data centers and long distance communications will be addressed. The coaxial cable, patented by O. Heaviside in 1880 [13], is revolutionary for electrical interconnects. It is really started to be widely used for transmission of many telephone carriers with a

single cable since 1930. Characteristic impedance of a coaxial line depends on the dielectric constant filling and the ratio of the inner and outer diameter.

$$Z_0 = \frac{1}{2\pi} \sqrt{\frac{\mu_R \mu_0}{\varepsilon_R \varepsilon_0}} \ln \frac{R_{in}}{R_{out}} \approx \frac{138\Omega}{\sqrt{\varepsilon_R}} \log_{10} \frac{R_{in}}{R_{out}}$$

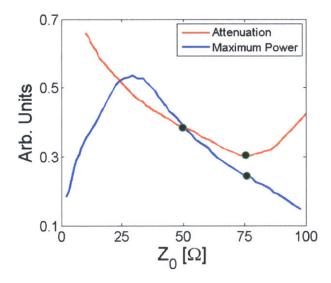

Where,  $Z_0$  is the characteristic impedance,  $\mu_R$  is the relative magnetic permeability,  $\mu_0$  is the vacuum magnetic permeability,  $\varepsilon_R$  is the relative electric permittivity,  $\varepsilon_0$  is the vacuum electric permittivity,  $R_{out}$  is the outer radius of the coaxial cable and  $R_{in}$  is the inner radius of the coaxial cable. Typical maximum power handling and attenuation is shown in Figure 9 [14]. Maximum power handling occurs for characteristic impedance of ~30 $\Omega$ . Characteristic impedance of 52 $\Omega$  is chosen as a compromise between minimum attenuation and maximum power by US Navy in World War 2. It is rounded to 50 $\Omega$  later and widely accepted. Television broadcasts are matched to 75 $\Omega$  to minimize attenuation through air.

Figure 9. Maximum power and attenuation of a typical coaxial cable. Widely used characteristic impedances are shown with black dots.

SubMiniature A, B, C and K (SMA, SMB, SMC and SMK) are widely used coaxial radio frequency (RF) connectors and cables from DC to 17, 4, 10 and 45 GHz bandwidth range, respectively (Fig. 10). At high frequencies even optimized rigid, semi-rigid or flexible coaxial cables tend to have high loss.

Figure 10. RF coaxial cable standards; SMA, SMB, SMC, SMK.

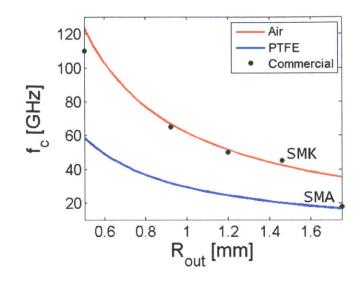

It is important to understand where the losses are originated at this point. For minimizing the propagation losses, the coaxial cable has to be designed as large as possible to minimize mode overlap with lossy media. However, if we consider high bandwidth cables on the market, the diameter of the cable is shrank from 3.5mm to 2.9mm, 2.4mm and down to 1mm as the bandwidth increases. The main reason for this decrease is that the coaxial cables support the fundamental transverse electric mode (TEM) as well as higher order modes if the cut off frequency is lower than the excitation frequency. Each perturbation on the cable including bend, twist or imperfections induced the coupling to the higher order modes which travel at different speed and lowers the voltage standing wave ratio (VSWR). Therefore, cables shrank down to 1mm diameter to support single mode at high frequencies. The cut off frequency of the RF coaxial cable can be modeled accurately using the finite difference modesolver. An approximation can be made to the cut off frequency using metallic boundary conditions;

$$f_c = \frac{c}{\pi \sqrt{\mu_R \varepsilon_R} (R_{out} + R_{in})}$$

Where,  $f_c$  is the cut off frequency, c is the speed of light. Cut off frequency approximation is compared with commercially available cables in Figure 11.

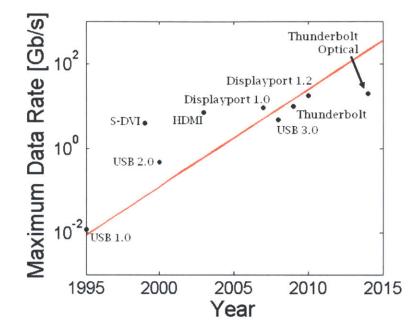

Figure 11. Comparison of the cut off frequency of commercially available cables and approximation For local or short distance off-chip communications, PC interface standards; Universal Serial Bus (USB), Digital Visual Interface (DVI), High Definition Multimedia Interface (HDMI), Apple/Intel Thunderbolt and Displayport have been introduced (Fig. 12). There are mostly based on microstrip and stripline RF cables. Off-chip short distance communication bandwidth, shown in Figure 13, increased

Figure 12. High speed recent PC interface standards

from 12 Mb/s (1995) to ~18 Gb/s (2010). It is likely to have PC interfaces at 100 Gb/s or more in 2015 and 1 Tb/s or more in 2020. Display resolution standards; High Definition (HD) (1366x768), HD+ (1600x900), FullHD (1920x1080), WQXGA (2560x1600), QFHD (3480x2160), 4K×2K (4096x2160) will need high bandwidth interfaces in the near future. Video data rate can be calculated as follows; *Video Data Rate = refresh rate × # of pixels × bits per pixel*

24 and 36 bits per pixel (bpp) is considered as low and high end color depth, respectively. Standard refresh rates are 60, 120 Hz. HDMI 1.4a cable supports 120Hz and 24bpp FullHD signal. However, Displayport 1.2 can support 4K×2K video at 60Hz and 30bpp. A 4K×2K video at 120Hz and 36bpp will

require 40 Gb/s interface. For a 3D display capability, two separate high quality images will be received by the user/s which doubles the bandwidth of transmission. This type of a 3D display technology does not provide motion parallax. In other words, user is observing the same 3D video independent of position with respect to screen which is different than real perception. Holographic displays or dynamic 3D

Figure 13. Short distance off-chip bandwidth scaling

content designed for each user can achieve 3D display with motion parallax. Such a display technology will require much more bandwidth than what have been discussed previously.

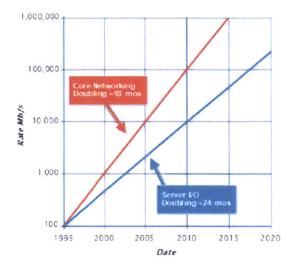

The most commonly used off-chip interface, Ethernet, for computer networking technology for local area networks (LANs) has introduced in 1980 with coaxial cables. Electrical cables induced high loss for off-chip long distance communications and the data needs to be amplified, filtered, received, and transmitted again using repeaters. The cables are replaced later with low loss twisted pair cables and fiber optic links. The Ethernet bandwidth is increased even at a rate faster than Moore's law (Fig. 14). It is expected to reach 1 Tb/s in 2015 by core network and 0.4 Tb/s in 2020 by server network.

Figure 14. Ethernet bandwidth scaling according to IEEE 802.3 Ethernet Working Group Communication

#### 1.2 Optical on-/off-chip communications

Since we summarized the on-/off-chip communications above, it is important to discuss where the optical interconnects (especially silicon photonics interconnects) are being used and will be used in the near future. Data centers or high performance computing machines (HPCs) are already utilizing the vertical cavity surface emitting lasers (VCSEL) as the optical interconnect since 2004 (Blue Gene L [10]). VCSELs handle communication between server cabinets in HPCs and gradually support communication between blades, boards and chips. VCSELs currently carry single channel per fiber similar to an electrical interconnect that carries single channel per wire. Recently, a 980nm VCSEL at 35 Gb/s data rate is demonstrated with as low as 268 fJ/bit [40]. At lower data rates, the 980nm VCSEL can achieve lower energy per bit. A 1060 nm VCEL at 10 Gb/s is also demonstrated with only 140 fJ/bit [41]. The 1060nm VCSEL showed reliable performance and the output power dimmed less than 10% of its original over 5000 hours of operation under thermal and humidity stress.

Today's top two fastest supercomputer, Sequoia (Blue Gene/Q) and the K have 1.572 million and 700 thousand cores and works at a peak performance of ~10 and ~16 PFLOPs, respectively. In order to achieve a EFLOPs machine with VCSELs we can start from the single chip with TSVs and we can determine the number of VCSELs and fibers for this system. We estimated the cumulative off-chip bandwidth of a single chip will be ~ 32 Tb/s or 20 TFLOPs above with TSVs. We can expect the VCSEL

technology will be advanced to 50 Gb/s in the same time frame. Even at this bandwidth, 640 VCSELs are needed to integrate on a single chip with 20 TFLOPs. Currently, IBM Blue Waters is using 40 VCSELs per 4 chip hub. Achieving 640 VCSELs on a chip is far beyond the current technology since VCSEL integration with CMOS on the optical chip has not been demonstrated. This also requires multiplexing and demultiplexing of many TSVs to achieve 50 Gb/s per VCSEL which increases the power consumption and complexity of the transmit and receive circuitry. If the 3D integration will be realized, VCSEL will limit the CMOS design since it is based on vertical cavity and can only integrated on top of the chip.

Even if the 20 TFLOPs on a single microprocessor is realized with 640 VCSELs, we will need 50,000 microprocessors for a super computer running at EFLOPs. With 640 optical fiber per chip at 50 Gb/s per fiber, we will need 32 million fibers and VCSELs in an EFLOPs machine. Although VCSEL was the current choice for optical interconnect, the scalability to exascale computing in dense 3D integration is technologically challenging and not cost effective. Therefore, wavelength division multiplexed (WDM) systems with large scalability and bandwidth will take place in off-chip communications. It is also addressed by International Technology Roadmap for Semiconductors (ITRS) in 2011 [14].

The WDM system proposed in this thesis will be silicon photonics. A silicon photonic WDM system that operates in C band (1530 - 1565nm) with a single channel carrying 50 Gb/s and 100 GHz channel spacing will provide 38 wavelength multiplexed channels and will be transmitted with a single mode fiber. This reduces the number of fibers 38 times compared to VCSELs. If the signal needs to be amplified, C and L band Erbium Doped Fiber Amplifier (EDFA) is available and widely used. Therefore, L band (1565 – 1625nm) can also be covered with additional WDM channels and double the number of channels to 75. All 75 channels can be still transmitted through a SM fiber. For a EFLOPs machine, the required number of fibers is 426 thousand with WDM system compared to 32 million fibers with VCSELs. The integration can be achieved on the same substrate utilizing monolithic integration with CMOS or on a 3D chip with flip chip bonding of CMOS and photonic chips.

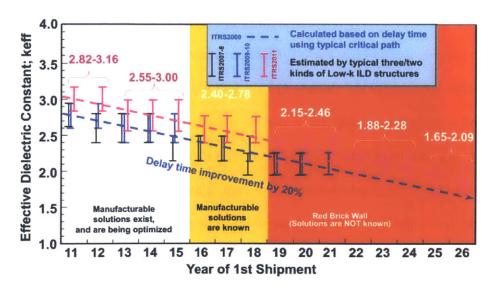

Although integration of Silicon photonics with CMOS is encouraging and enabling technology, it is a major change for the process design kits. Based on ITRS roadmap [14], on-chip electronics have already determined ways to leverage the bandwidth and energy requirements until 2020. Simply, on-chip wire capacitance can be minimized with lower dielectric constant oxides. Process design kits are expensive to develop. Only minor changes are allowed to minimize the cost. Silicon photonics integration with current CMOS standards is a major change than lowering dielectric constant of conventional oxides. Moreover, ways to achieve Low-k dielectrics have been understood and demonstrated (Fig. 15). Dielectric constant <2.0 oxides becomes mechanically unstable and damaged from plasma etching. It is foreseen that dielectric constant will achieve around 2.15 in 2018. After 2018, a major change is expected in process design kit which can enable Air-Gap [15-17] or another technology such as on-chip silicon photonics. However, ITRS roadmap claimed the backend optically low loss materials such as Poly-Si that requires high temperatures [37] or SiN which is not a semiconductor or active material [38]. However, this is not completely true. Monolithic integration is realizable by tweaking the parameters of CMOS and photonic process. A monolithic integration of a microdisk modulator up to 2 Gb/s has demonstrated at Sandia National Laboratories [42]. Monolithic integrated 2<sup>nd</sup> order 4 channel thermally tunable microring filter bank has been demonstrated at MIT [43].

Figure 15. Low-k dielectric progression from ITRS roadmap. It is possible to achieve Low-k dielectrics until 2018.

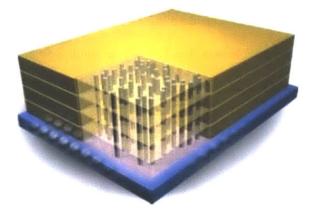

Local memory communication, governed by electronics, is the next to discuss. Dynamic random access memory (DRAM) is currently limited by the bus between the memory and chip. Micron identifies this as the "memory wall" problem. 3D System-on-Chip (3D-SOC) that uses multiple stacked dies, 3D Wafer-Level-Packaging (3D-WLP) that is established by flip-chip bonding, and 3D-Stacked-Integrated-Circuit (3D-SIC) that utilizes direct interconnects between circuit blocks in different layers, are interconnect technologies that involve TSVs in ITRS roadmap. Chip to memory 3D integration (Hybrid Memory Cube), can be achieved vertically integrated by TSV technology instead of side by side or off-chip [18-21]. Conceptual drawing of Hybrid Memory Cube is shown in Figure 16.

Figure 16. Hybrid Memory Cube proposed by Micron. Package, Logic and DRAM level is shown with pink, purple and gold colors, respectively. TSVs are shown in between DRAM and logic level.

On-chip cache is also occupying half of the chip size in order to save bandwidth of writing and reading from an off-chip memory (see Fig. 8). Therefore, it can leverage the access to DRAM and makes the current on-chip cache (SRAM) obsolete [25]. Additionally, the 3D memory cube will double the computation space since the on-chip cache can be placed on top of the microprocessor instead of occupying same physical layer. This requires short TSVs to be enabled on chip as well as accurate alignment between the memory and microprocessor chip. It has been demonstrated repeatable alignment tolerances within 3µm [26]. IBM has a roadmap to integrate photonics next to electronics for 2015 and includes vertical memory cube for 2020 [24]. Conceptual drawing of these integrations is shown in Figure 17. A recent study compared monolithically integrated 41 stage ring oscillators and identical ring

oscillators bounded between chips using TSVs. Results are surprising since there was no degradation in speed or increase in power consumption on the integrated chip with TSV connections. Moreover, data rates up to 3Gb/s per pin are already demonstrated using TSVs in 2008 [27]. However, these key developments still might not allow silicon photonics to take place in local memory communication for some time. Off-chip communications will stay optical (VCSELs) for HPCs and commodity PC interface standards with optical power supply and data transmission will likely to emerge.

2015 Roadmap

2020 Roadmap

Figure 17. IBM 2015 and 2020 roadmap for photonics integration

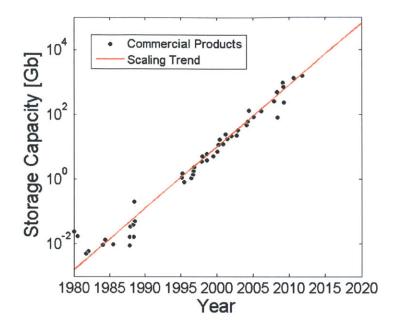

### 1.3 Data Storage Scaling

High bandwidth off-chip communications such as Ethernet, computing and displays will require the data storage capacity to scale in parallel. Hard drive capacity, shown in Figure 18, scaled from 1 Gb (1995) to 4 Tb (2012) and it is even increasing at a rate higher than Moore's Law. The capacity scaling is referred as Kryder's Law [34]. It is predicted that a two-platter hard drive capacity will be 14 Tb on a 2.5" disk drive and cost ~40\$ in 2020. However, speed of reading and writing the data is ~ 160 Mb/s for the state of the art hard disk drive with electromagnetic storage [45]. On the other hand, solid state drives are using flash access memory which is considerably faster up to ~ 390 Mb/s and 8 times more expensive per byte than the electromagnetic counterpart [46]. We can easily predict that data storage will be handled with a method different than photonics and it has other solutions for future [34].

Figure 18. Storage capacity scaling

## 1.4 Energy per bit scaling on a chip

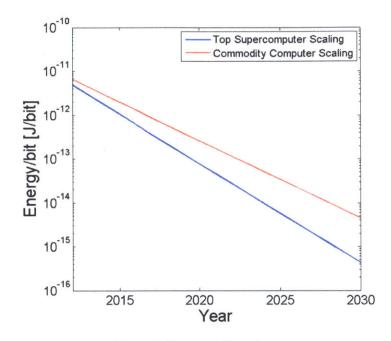

We have concentrated above on computer performance and bandwidth roadmap and ways to achieve those targets. Power handling on a microprocessor is also important because power density will increase in parallel with computing performance. Most chip architectures are limited to 1 W/mm<sup>2</sup>. So, for a quad core chip with a die area of ~270 mm<sup>2</sup> (estimated based on Nehalem and Phenom chips) could handle maximum power consumption of 270 W and 20% of this power will be devoted to off-chip communications [44]. If the transmit and receive power is assumed to be equal, the maximum transmit or receive power will be 27 W. We can calculate the maximum bits per chip from the FLOPs per chip (Figure 3) by using 6 bits/FLOPs. 6 bits can be decomposed into 2 and 4 bits for off-chip and memory communication. Energy per bit, shown in Figure 19, is calculated by dividing the maximum transmit or receive power to number of bits. Top Supercomputers will reach the 100, 10 and 1 fJ/bit limit by 2020, 2025 and 2030, respectively. On the other hand, commodity computers will reach 100, 10 fJ/bit limit by 2025, 2030, respectively. This constraint is fundamental and derived basically the density of components in the chip area for high bandwidth operation. Transmit or receive energy per bit for 100 fJ/bit has not been demonstrated using VCSEL. However, silicon photonic resonant modulators with as low as 3 fJ/bit

Figure 19. Energy per bit scaling

at 10 Gb/s and 13fJ/bit at 25Gb/s has been demonstrated [47,48]. This is only including an electro-optic modulator energy performance. With integrated circuitry and laser source, cumulative energy per bit will raise to  $\sim$ 100 fJ/bit. However, the resonant microdisk needs to be aligned in wavelength to an external or on-chip laser line. This is not necessarily true due to process/wafer variations and dynamic temperature fluctuations and this thesis is devoted to offer solutions and understand the reasons for this mismatch.

## 1.5 Silicon Photonics

Although photonics is commonly recognized by researchers, there are few commercially available devices utilizing the benefits of it. It may be partially due to challenging and sophisticated photonic system design requirements or challenges in integration of the photonics with electronics on the same platform. Silicon photonics is the effort of utilizing CMOS processes and CMOS compatible materials to form photonic components on the same platform. Silicon is an ideal platform for photonics since it is optically transparent or low loss above 1.1  $\mu$ m and has a high refractive index around 3.48, allowing highly confined waveguides and tight bends (radius of curvature <1.75 $\mu$ m) as opposed to sophisticated fibers that allow bends in the order of millimeters.

Although older CMOS nodes match well with silicon photonic thickness requirements (~100-250nm), the current nodes are too thin for supporting highly confined optical modes. In order to increase the confinement factor central wavelength is shifted from 1550 to 1280nm for monolithic integration of electronics and photonics [43], which necessitates new design of each element on-chip and expensive amplifiers. It also requires the integration of Poly-Si or Amorphous-Si waveguides and extensive control of the process to lower the losses based on edge roughness and multi grain structure instead of C-si. A customized CMOS process have been demonstrated Photonics chip fabricated with an older node CMOS and state of the art electronics chip can be 3D integrated utilizing TSVs. Through my MIT studies, I was lucky to experience both monolithic integration at 1280nm with IBM and Micron processes and flip-chip bonding at 1550nm with CNSE Albany process. High performance devices can be achieved by bonding III-V materials on silicon layer. However, yield lowers significantly due to voids in the integration process.

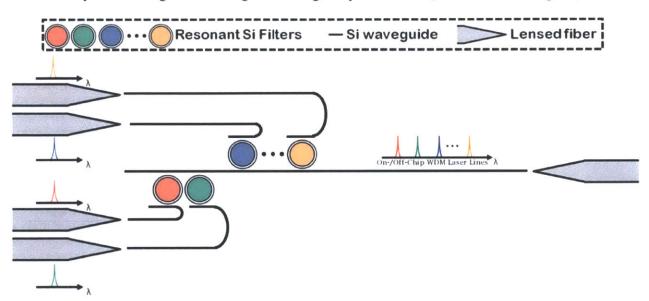

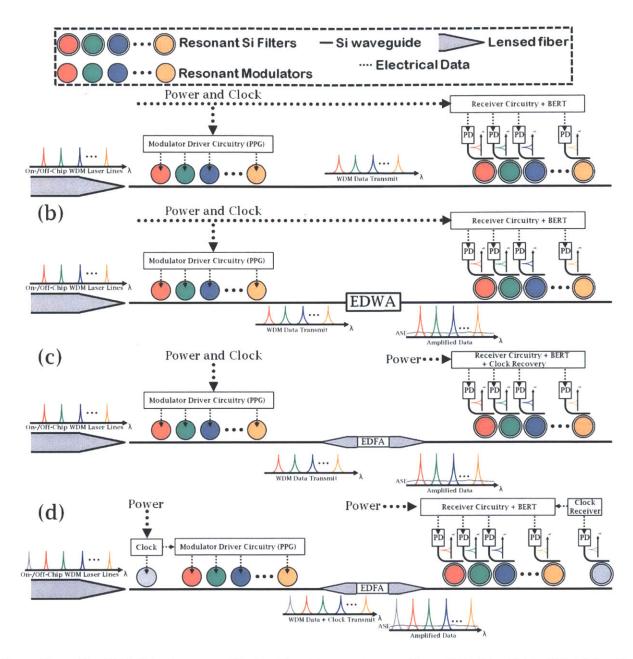

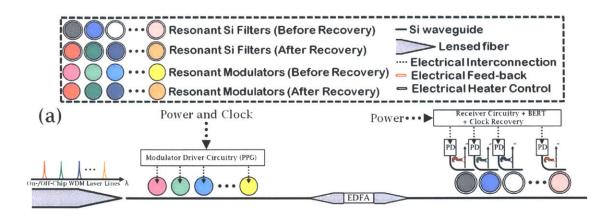

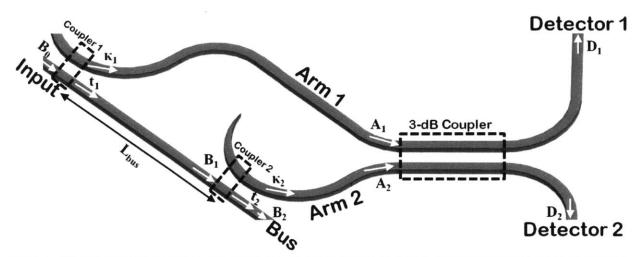

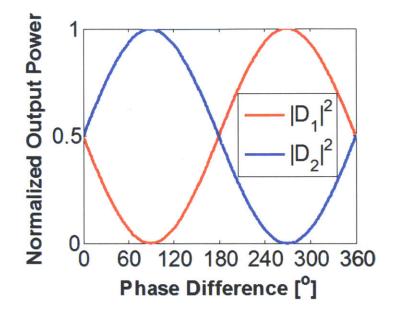

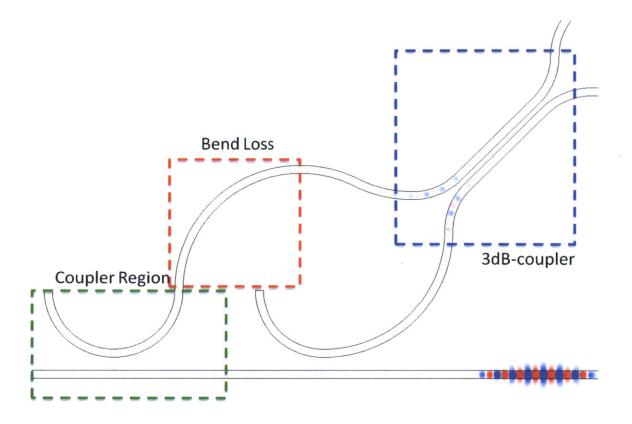

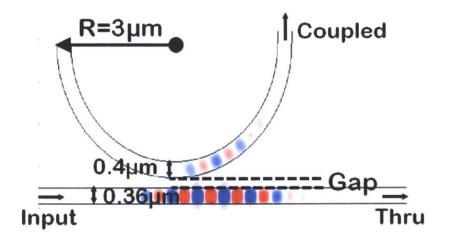

WDM based silicon photonics with microdisk/ring resonators will be the main focus of this thesis. Silicon Mach-Zender modulators are not going to be discussed in this thesis but the transfer matrix of a Mach-Zender will resemble the solution in chapter 3. The most simple single channel point to point silicon photonic link is composed of a CW laser source, a resonant modulator, modulator driver and a detector and receiver circuit. For a multi channel WDM link, a single photonic bus waveguide can guide all channels and all external and/or on-chip laser sources need to be multiplexed to a single fiber or a waveguide. A multiplexer with microring filters is illustrated in Fig. 20. Each channel will require a CW laser source, a resonant modulator and a detector as well as a resonant filter prior to detection (Fig. 21, a).

Our team at MIT has measured the intrinsic loss of C-Si as low as 2.7dB/m and the ridge waveguide design is allowing a microring resonator with a quality factor of  $2.2 \times 10^7$  [49]. Therefore, the on-chip transmission can be short enough that the signal will not require amplification. However, if the amplification is required, erbium doped gain medium or waveguide amplifier (EDWA) can be integrated on-chip [50] (Fig. 21, b). For off-chip communication, the amplification can be achieved by external erbium doped fiber amplifier (EDFA) for C and L bands (Fig. 21, c).

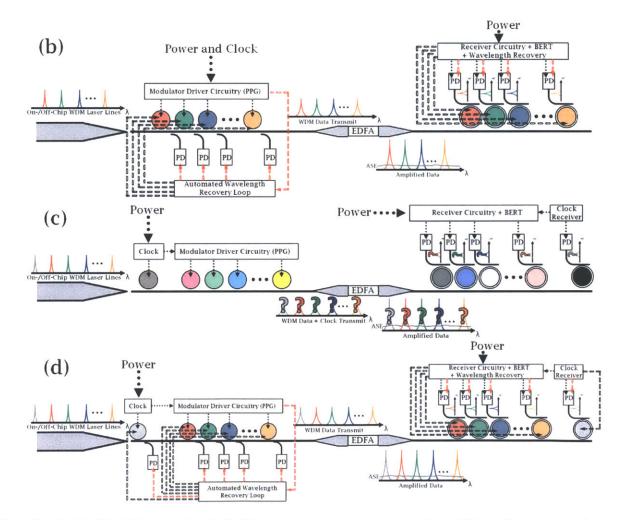

For receiving the signal, clock frequency and phase has to be determined. On-chip transmitter and receiver can share an additional electrical clock wire to receive data properly (Fig. 21, a-b). However, when the transmission is received data, clock has to be recovered with a clock recovery circuitry (Fig. 21, c) [51]. Electrical clock recovery will dissipate additional power and occupy additional chip area. However, it is a widely used control layer of an electrical link. In a WDM link, clock recovery can be eliminated by transmitting and receiving clock using an optical channel, as illustrated in Fig. 21, d.

Figure 20. on-chip WDM multiplexer of laser sources, color coding is used to indicate the resonance of the filters. Each resonator resonance corresponds to the color coded laser lines.

Figure 21. on-chip WDM link with no amplification (a) and integrated waveguide amplifier (b), off-chip WDM link with amplification between transmitter and receiver chips (c), off-chip WDM link with optical clock transmitter and receiver (d). Color coding is used to indicate the resonance of filters and modulators. Each resonance corresponds to the color coded laser lines.

We have introduced a WDM link, which is composed of an optical multiplexer, a transmitter and a receiver (Fig. 20-21) which includes multiple silicon resonant filters and modulators. In such a WDM link, laser sources are required to be aligned in wavelength to the resonances of silicon resonant filters and modulators in the multiplexer and transmitter, respectively and transmitted data on each channel is also assumed to be aligned with resonance of the filters in the receiver. The alignment is distorted by process and wafer imperfections and dynamic temperature fluctuations due to processor core activity which will be explained in detail in the following section.

### 1.6 Wafer Level and Process Variations

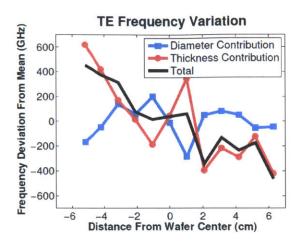

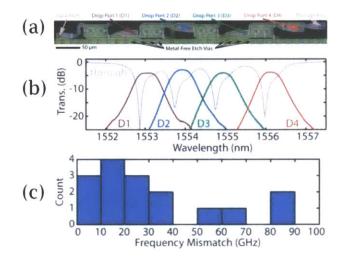

High confinement waveguides, which is enabled by high index contrast of Si, can be formed into compact (~3.5µm diameter) micro-ring/-disk resonators at the expense of susceptibility to the fabrication imperfections or wafer thickness variations. Fundamental TE and TM resonances of a micro-disk resonator experience frequency offsets to only thickness and diameter variations. The width and diameter imperfections can be extracted from the response of the two orthogonal polarizations [52]. Using a cylindrical modesolver, the microdisks with different diameters are designed around 1550nm in wavelength. Frequency offset due to thickness and diameter dependence is determined to be 140, 52 GHz/nm for fundamental TE radial mode, and 330 GHz/nm, 36 GHz/nm for fundamental TM radial mode, respectively. Microdisks at different location on a wafer have been fabricated on a thick SOI, respectively. A resonance frequency shift of  $\pm 400$  GHz has been observed in a 6cm radius around the wafer center Fig. 22. A 4 channel second-order silicon microring filter bank have been demonstrated on a customized CMOS run with a post-fabrication undercut process (Fig. 23,a) [43]. Drop ports and thru port of the second-order microring filters have been measured at different positions on wafer to determine frequency mismatch between two resonators (Fig. 23,b-c). A frequency mismatch of ±45 GHz is achieved, which implies a tight process control compared to thick SOI process can be realized on a customized CMOS run. Therefore, a  $\pm 50$  GHz frequency offset has to be compensated.

Figure 22. Fundamental TE resonance frequency deviation with respect to the distance from wafer center [52].

Figure 23. (a) Optical micrograph of a four-channel second-order filter bank, (b) Measured transmission normalized to offresonance through port transmission for the four-channel second-order filter bank without thermal tuning or post-fabrication trimming, (c) histogram of resonant frequency mismatch between the two rings in the second-order filters from four die from different wafer locations [43].

## 1.7 Thermal Fluctuations

Silicon is a thermally and electrically active material. Electrical conductivity of Si can be controlled precisely with implantation and activation of p-/n-type doping species. This has been utilized to create transistors family and active photonic structures. On the other hand, thermal conductivity of Si is weakly dependent on doping concentration and can only be controlled by sophisticated rough nanostructures that engineer phonon scattering [53-57]. Although some of the offered solutions to control thermal conductance are CMOS compatible, they require complex processing and there is no silicon

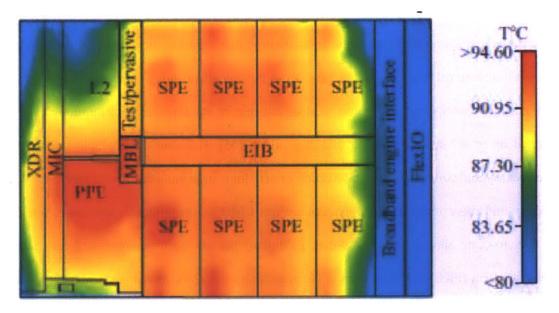

resonator with specially engineered thermal conductance. Therefore, the Si waveguides and resonators are not thermally insulated and Si has a high thermo-optic coefficient that corresponds to  $\sim 10$ GHz/<sup>0</sup>C resonance shifts [91]. It becomes a major problem in a processor core with dynamic temperature variations, as illustrated in Fig. 24 [58]. Furthermore, a 3D-integrated or a monolithically integrated photonic chip can have a dynamic temperature variation of  $\pm 10^{\circ}$ C, that corresponds to a  $\pm 100$ GHz frequency mismatch.

Figure 24. IBM microprocessor thermal map, showing a temperature variation of ~±7.3°C [58].

### 1.8 Available Solutions

In section 1.6 and 1.7, we have summarized the main factors that induce frequency mismatch. From these sections, we can predict that a total frequency mismatch of  $\pm 150$ GHz has to be compensated, including fabrication imperfections and dynamic temperature fluctuations. In this section, we will explain available solutions to resolve this problem. The passive methods include athermal, high-order box and SiN filters and active methods include electro-optic or thermo-optic tuning.

Athermal waveguides is formed with Si waveguides buried or covered with a polymer that has a negative thermo-optic coefficient [59-65]. Width of the Si waveguide can be scaled down to lower confinement factor and fundamental waveguide mode will overlap with the polymer to compensate the

thermo-optic coefficient. Additionally, the low confinement of silicon waveguide limits the radius of the current athermal microrings is >10µm. The confinement can be maximized with a large negative thermooptic coefficient polymer, thus minimize bend radii. Compact devices lead to large free spectral range that allows large number of WDM channels and minimize the electrical power consumption of active devices. Therefore, the performance of athermal devices is limited to material engineering. We have explained how the athermal waveguides can be a solution for on-chip temperature fluctuations. However, the fabrication imperfections need post-trimming of the athermal resonators. The refractive index can be tuned by curing the polymer to compensate the fabrication induced frequency mismatch. The polymer can be cured with an external laser source and can store the refractive index change up to couple months. Although, curing process dissipates power, it does not require static power consumption. This has been demonstrated up to 4<sup>rd</sup> order microring add-drop filters [65]. However, no scalable method has been offered to identify and compensate the fabrication offsets for a large number of resonators in a WDM link automatically and more importantly, polymers are not CMOS compatible. Furthermore, integration of athermal electro-optic silicon micro-ring/-disk modulator has not been demonstrated into this system. Franz-keldysh effect (FKE) has been used in Ge modulators that show robust performance in a thermally volatile environment [66]. However, FKE occurs at a small range of frequencies and limits the WDM capacity of the silicon photonic system.

Another passive solution will be using CMOS compatible thick SOI process to form high order microring filters. First order microring response has a lorentzian shape that distorts the signal significantly if there is a frequency mismatch between microring resonance and the data carrier center wavelength. High order microring exhibits a flat-top or box filter response with sharp cut-off, that allows the multiple WDM channels. A high order microring filter with a >300GHz 1-dB bandwidth will require no compensation with  $\pm 150$ GHz frequency drift [67]. The drawback is the electro-optic resonant silicon modulators are single micro-ring/-disk based devices. Therefore, modulators will require active control.

SiN can be used a material platform since the thermo-optic coefficient much smaller than Si and high order SiN has been demonstrated on thick SOI [68,69]. However, SiN is not likely to be a complete

solution due to three reasons. First, SiN is a low-index ( $\sim$ 2) contrast material, thus increases size of the structures. The SiN thickness needs to be  $\sim$ 400nm to minimize substrate leakage on a SOI wafer, which requires tight process control to achieve low side-wall roughness. Second, the thickness of the Si is being decreased and density of transistors increased with the next generation of processor node. Therefore, even SiN microrings are fabricated with an older node; the pitch of the electrical wires will limit the performance of the hybrid photonic-electronic chip. Third, SiN is not electrically active (insulating) and fabrication imperfections need to be fixed with external control, which becomes a power hungry solution.

If any of the solutions offered above can be realized in a large-scale integration platform, it will definitely have an impact on the research and commercialization of Silicon photonic products. However, we should focus on a more general solution without limitations of passive methods. Active compensation methods; electro-optic and thermo-optic tuning have been optimized and energy per bit performance is dwarfed significantly in the last decade [71-74]. Active compensation methods will be explained in the following two sections.

#### 1.9 Electro-optic tuning/modulation

This section will focus on PN junction resonant switches and modulators since the PN junction based devices have few demonstrations of electro-optic tuning [75]. The speed of the tuning will be limited by the bandwidth of electro-optic tuners, thus a faster device can be utilized for a reconfigurable network. Injection or depletion of the carriers from a PN diode formed inside a resonator exhibits the plasma-dispersion effect [70], which in turn changes the refractive index of the silicon waveguide. The electro-optic refractive index change alters the resonance frequency of the resonator. Using this principle, many variations of compact silicon modulators are formed and the first resonant modulator was an injection-based device [71].

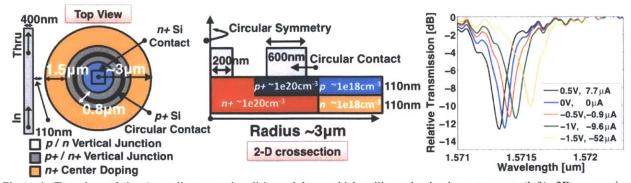

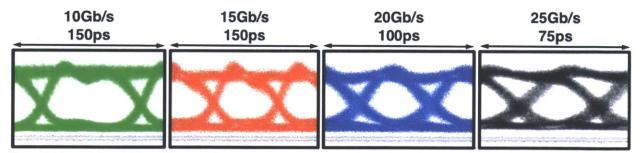

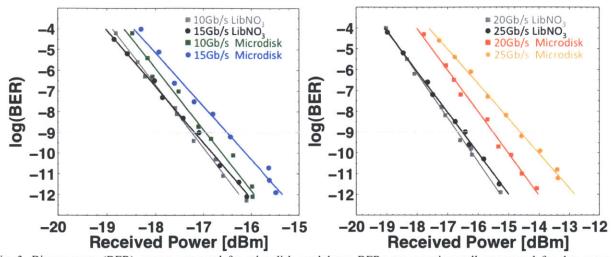

Depletion based devices improve on this early injection-based device, enabling efficient highspeed operation of silicon microring and microdisk modulators. Recent work has yielded depletion-based modulators leveraging lateral-junction configurations capable of operating beyond 25 [76–78], and even 40 Gb/s [79-81]. Methods to interleave PN junctions have been utilized to increase the electro-optic efficiency by enhancing the carrier-light overlap, which reduces the voltage-length product  $V_{\pi}L_{\pi}$ , achieving 25-Gb/s operation of a 30-µm-radius device with 4.5-dB extinction ratio at 2-V driving voltage [76], and 25-Gb/s operation of a 250-µm-circumference device with about 3.6-dB extinction ratio at 1.6-V driving voltage and 41-fJ/bit power consumption [77]. Another demonstration has achieved 25-Gb/s operation of a 7.5-µm-radius device with about 5-dB extinction ratio at 1-V driving voltage and about 7-fJ/bit power consumption [78]. By reducing the radius of the latter device to 5 µm, reducing the junction capacitance and the RC time constant, a similar device was demonstrated to operate at 40 (44) Gb/s, with 7- (2.3-) dB extinction ratios at 2-V driving voltages [79]. Leveraging PN-junction-interleaved cascaded microring resonators, 40-Gb/s operation was demonstrated with a 20-µm-radius device with 3.9-dB extinction ratio at 5-V driving voltage [80]. Lastly, a method to zigzag the PN junction has been employed to achieve 44-Gb/s operation with 3.01-dB extinction ratio at 3-V driving voltage [81]. Injection-based devices can be used as an electro-optic tuner, but the efficiency (~4.4µW/GHz [73]) will be quite low since it dissipates static power due to current.

Depletion-based devices leveraging vertical-junction configurations provide the added advantage to the drive voltage, power consumption, size, and speed [73]. The vertical junction maximizes the overlap of the depletion region with the radial TE mode, reducing the drive voltage and power consumption for modulation. It also enables direct electrical contacts to be made at the interior of the silicon microdisk or microring resonator, forming a hard outer wall that minimizes radiation, resulting in a significant size reduction of the device. This reduction in size also reduces the capacitance and increasing the speed. For example, depletion-based vertical-junction silicon microdisk modulators have enabled 12.5-Gb/s modulation of a 1.75-µm-radius device with 3.2-dB extinction ratio at 1-V driving voltage and 3-fJ/bit power consumption [73]. This device occupies less than one-tenth the area of traditional microring modulators, and maintains entirely-interior electrical contacts. Depletion based devices do not shift more than ~50GHz with CMOS compatible voltage range, thus it is not enough for an electro-optic tuner until today. However, if there will be a solution to the shift, depletion-based devices will have low static power, which is dominated by the leakage current.

However, one major limitation of microdisk resonators is that they support higher-order spatial modes that corrupt the free spectral range (FSR) by introducing undesired resonances. To combat this, several demonstrations have utilized adiabatic microring resonators, which leverage single-mode coupling regions and adiabatic tapering to enable contact regions and maintain single-mode operation [82–85]. These devices preserve most of the benefits of microdisk resonators, with the added advantage of enabling uncorrupted FSRs [82]. A single-mode adiabatic resonant microring (ARM) modulator has been demonstrated with comparable performance to the microdisk modulator [84,85].

### 1.10 Thermo-optic tuning

Refractive index of Si waveguides can be tuned by a heater. Optimized external heaters placed over the oxide cladding achieve 28- $\mu$ W/GHz with a 6.4 $\mu$ s thermal time constant [72]. Recently, the heaters have been integrated within resonators which offer the best optimization of tuning efficiency and speed on thick SOI. One demonstration has directly integrated heaters within adiabatic microring resonators, achieving 4.4- $\mu$ W/GHz tuning efficiency and 1- $\mu$ s thermal tuning speed of a second-order filter [74]. The resonant modulators also require thermo-optic tuning to align with the WDM multiplexer and receiver. Unfortunately, heaters are usually integrated within resonant modulators at the expense of area and/or performance. A large ridge microring modulator (400 $\mu$ m<sup>2</sup>) with ~42 $\mu$ W/GHz tuning efficiency and 50% junction area coverage around the periphery [86] and a compact microdisk modulator (50 $\mu$ m<sup>2</sup>) with 7 $\mu$ W/GHz tuning efficiency and 50% junction area coverage around the periphery [86] have been demonstrated in the literature. Junction area coverage limits the modulation efficiency and leads to an insertion loss of >5dB [5] and >3db [87]. For a normal distribution of  $\pm 10^{0}$ C temperature fluctuations and a ~100GHz resonance frequency offset due to fabrication/wafer variations, the total modulation and heater energy was >322fJ/bit [86] and >200fJ/bit [87]. Therefore, the total modulator efficiency is dominated by heater power.

## 1.11 Automated Wavelength Recovery Architecture

In section 1.5, we have shown the idealized WDM multiplexer, transmitter and receiver. Through section 1.6 to 1.10, we have stated the frequency mismatch due to fabrication/wafer imperfections and dynamic temperature fluctuations and between resonators and the on-/off-chip lasers. We also explained the available methods that can fix that frequency mismatch. Thermo-optic tuning is considered as the most realistic approach. We will offer a solution that we call as automated wavelength recovery (AWR), to fix a WDM silicon photonic link. This is a control layer that is required for a large scale WDM link that supports >1Tb/s bandwidth.

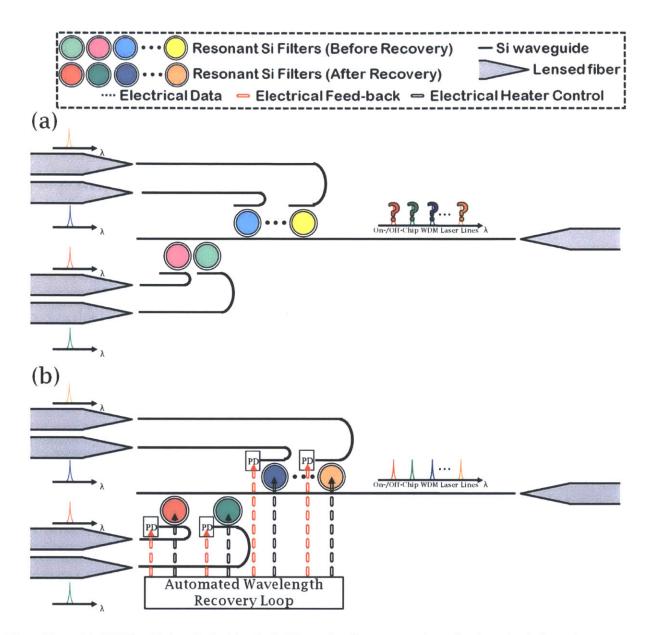

A realistic WDM link multiplexer before and after AWR is shown in Fig. 25, a-b. AWR loop is implemented to use the feedback from the integrated photodetector (PD) at thru port of each resonant filter and sending the control voltage to the integrated heaters. Minimizing the received signal at the detector will align the laser to the filter. The performance will be limited with the receiver sensitivity. The underlying algorithm and demonstration of such a loop will be explained in Chapter 3.

Figure 25. on-chip WDM multiplexer before(a) and after(b) wavelength recovery, color coding is used to indicate the resonance of the filters. Automated wavelength recovery loop is using the feedback from the integrated detector at thru port of each resonant filter and sending the control voltage to the integrated heaters. Each resonance corresponds to the color coded laser lines after recovery.

Figure 26. off-chip WDM link before(a) and after(b) automated wavelength recovery with amplification between transmitter and receiver chips, off-chip WDM link with optical clock transmitter and receiver (d). Color coding is used to indicate the resonance of filters and modulators.

A realistic WDM link transmitter and receiver with off-chip amplification, before and after AWR is shown in Fig. 26, a-b. This link requires clock recovery and a WDM channel can be used to transmit and receive the clock to eliminate clock recovery circuitry (Fig. 26,c-d). Thru port of the resonant modulators can be observed by adding an evanescently coupled PD after each modulator. The data received by each PD and the electrical data will be used as a feedback signal for the AWR loop and integrated heater within the modulator will be used to align the laser line (Fig. 26, c). For a 1-MHz thermal tuner bandwidth, and a data rate of 10-Gb/s, every 32<sup>th</sup> bit from the electrical data can be compared to the data received by the PD at a loop with a bandwidth of ~312GHz. Another approach is to measure the average intensity in the PD and selecting a bias point based on the optical true one and zero. A loop bandwidth ~10-20MHz can be used for this approach which minimizes the power consumption of the driver circuitry. Power consumption of the heater driver have been measured on a monolithically integrated platform and at a clock frequency >20MHz a significant power is consumed by the driver head [87]. So far, all modulator recovery demonstrations [89,90] include a calibration data which is not a realistic solution considering optical performance fluctuations due to fabrication/wafer imperfections.

The transmitted data need to be demultiplexed before the receiver. A PD integrated to the drop port of each resonant filter is already being utilized for receiving the data. Therefore, the AWR loop can be implemented to use the feedback from this PD and sending the control voltage to the integrated heaters (Fig. 26, d). Maximizing the received signal at the detector will automatically align the data to the filter. The performance will be limited with the receiver saturation and/or sensitivity, depending on the input laser power and the insertion loss of the filter. The underlying algorithm of such a loop will be explained in Chapter 3.

The laser power fluctuations and frequency drifts are excluded up to this point since it is not directly related to silicon photonics except possible thermal crosstalk between the lasers and silicon photonic chip. However, laser is the key component of WDM link and AWR loop required to compensate laser power fluctuations and frequency drift. AWR algorithm offered in Chapter 3 is designed to handle this problem and minimizes the power required to stabilize the lasers.

# 1.12 Conclusions

In the first chapter, on-/off-chip electrical and optical communications introduced. The roadmap for bandwidth, clock frequency, energy, data storage and photonic integration discussed. The off-chip bandwidth (>1Tb/s in 2020) and energy scaling (<100fJ/bit in 2020 for HPC machines) obviously requires new technologies other than single channel per wire/fiber. WDM based Silicon Photonics is offered as an enabling technology that can reach those goals. However, there are challenges, wafer level and process variations and thermal fluctuations, ahead that silicon photonics need to overcome. The frequency drifts due to those challenges can be  $\sim\pm150$ GHz ( $\sim\pm50$ GHz from wafer/process imperfections and  $\pm10^{0}$ C from dynamic temperature fluctuations). The most of the available methods to compensate frequency drifts have limitations. Thermo-optic tuning can be used as a general solution at the expense of static power consumption. Integration of heaters to each resonator and using a feedback loop that constantly check for the frequency drifts is proposed which is called as automated wavelength recovery (AWR).

•

1.13 References

- [1] Moore, G.E., "Cramming More Components Onto Integrated Circuits," *Proceedings of the IEEE*, vol.86, no.1, pp.82-85, Jan. 1998.

- [2] Ferris-Prabhu, A.V., "Introduction to Semiconductor Device Yield Modeling", 1992, New York: Artech House.

- [3] Chen, F., et al. "Line edge roughness and spacing effect on low-k TDDB characteristics," in Reliability Physics Symposium, 2008. IRPS 2008. IEEE International. 2008.

- [4] Chen, X., et al. "A cost effective 32nm high -K/ metal gate CMOS technology for low power applications with single-metal/gate-first process" in VLSI Technology, 2008 Symposium on. 2008.

- [5] Jan, C.H., et al. "A 32nm SoC platform technology with 2<sup>nd</sup> generation high k/metal gate transistors optimized for ultra low power, high performance, and high density product applications" in Electron Devices Meeting (IEDM), 2009 IEEE International . 2009.

- [6] Wang, X., L. Wu, and Y. Liu, "Low -power LVD S I/O interface for above 2Gb/s -per-pin operation" Journal of Electronics (China), 2009. 26(4): p. 525-531.

- [7] Zhang, W., N.K. Jha, and L. Shang, "Design space exploration and data memory architecture design for a hybrid nano/CMOS dynamically reconfigurable architecture" J. Emerg. Technol. Comput. Syst., 2009. 5(4): p. 1-27.

- [8] Sinharoy, B. "POWER7 multi-core processor design in Microarchitecture", 2009. MICRO-42. 42nd Annual IEEE/ACM International Symposium on. 2009.

- [9] Howard, J., et al., "A 48-Core IA-32 Processor in 45 nm CMOS Using On -Die Message-Passing and DVFS for Performance and Power Scaling. Solid-State Circuits," IEEE Journal of, 2011. 46(1): p. 173-183.

- [10] Kogge, P., The Tops in Flops (vol 48, pg 48, 2011). Ieee Spectrum, 2011. 48(3): p. 8-8.

- [11] Kwong, J. and A.P. Chandrakasan, "Advances in Ultra -Low -Voltage Design. Solid-State Circuits Newsletter," IEEE, 2008. 13(4): p. 20 -27.

- [12] Daniel E. Atkins, K.K.D., Stuart I. Feldman, Hector Gacia-Molina, Michael L. Klein, David G. Messerschmitt, Paul Messina, Jeremiah P. Ostriker, Margaret H. Wright, "Revolutionizing Science and Engineering Through Cyberinfrastructure. Report on the National Science Foundation Blue-Ribbon Advisory Panel on Cyberinfrastructure", 2003.

- [13] Nahin, Paul J. (2002). "Oliver Heaviside: The Life, Work, and Times of an Electrical Genius of the Victorian Age".

- [14] International Technology Roadmap for Semiconductors 2011 Edition Interconnect.

- [15] Watanabe, T., et al "Self-Formed Barrier Technology using CuMn Alloy Seed for Cu Dual-Damascene Interconnect with Porous-SiOC/ Porous-Par Hybrid Dielectric," IITC, 2007, p. 7

- [16] Saito, T., et al., "A Reliability Study of Barrier-Metal-Clad Copper Interconnects With Self-Aligned Metallic Caps," IEEE Trans. Electron Devices, 48, p. 1340.

- [17] Hu, C.K., et al., "A Study of Electromigration Lifetime for Cu Interconnects Coated with CoWP, Ta/TaN, or SiCxNyHz," Proceedings of AMC, 2003, p. 253.

- [18] http://www.xbitlabs.com/news/memory/display/20111102133147\_Samsung\_Plans\_to\_Manufacture\_ Hyper\_Memory\_Cube\_Solutions\_in\_2013\_2014.html.

- [19] http://www.bit-tech.net/news/hardware/2012/05/09/microsoft-hmc-tech/1.

- [20] http://www.electroiq.com/articles/ap/2011/12/ibm-fabs-micron-memory-cube-with-tsv-tech.html.

- [21] http://www.i-micronews.com/news/Micron-reveals-%C3%A2%E2%82%AC%C5%93Hyper-Memory-Cube%C3%A2%E2%82%AC%20-3DIC-Technology,6472.html.

- [22] Xie, Y., et al., "Design space exploration for 3D architectures" J. Emerg. Technol. Comput. Syst., 2006. 2(2): p. 65 -103.

- [23] Amdahl, G.M., "Validity of the single processor approach to achieving large scale computing capabilities," AFIPS Joint Computer Conference, 1967.

- [24] Coteus, P.W., Krickerbocker J.U., Lam C.H., Vlasov Y. A., "Technologies for exascale systems," IBM Journal of Research and Development 55(5), 14-1, IBM, 2011

- [25] Facchini, M., et al., An RDL -configurable 3D memory tier to replace on-chip SRAM, in Proceedings of the Conference on Design, Automation and Test in Europe 2010, European Design and Automation Association: Dresden, Germany. p. 291-294. 42

- [26] Krishnamoorthy, A.V., et al., Computer Systems Based on Silicon Photonic. Interconnects. Proceedings of the IEEE, 2009. 97(7): p. 1337 -1361.

- [27] Kawano, M., et al. A 3D Packaging Technology for 4 Gbit Stacked DRAM with 3 Gbps Data Transfer. in Electron Devices Meeting, 2006. IEDM '06. International. 2006.

- [28] Weldezion, A.a.W., Roshan and Pamunuwa, Danesh B. and Zheng, Li-Rong and Tenhunen, Hannu (2009) Bandwidth optimization for through silicon via (TSV) bundles in 3D integrated circuits. In: Workshop Notes, Design, Automation and Test in Europe

- [29] Koyanagi, M., T. Fukushima, and T. Tanaka, High-Density Through Silicon Vias for 3 -D LSIs. Proceedings of the IEEE, 2009. 97(1): p. 49 -59

- [30] Facchini, M., et al., An RDL -configurable 3D memory tier to replace on-chip SRAM, in Proceedings of the Conference on Design, Automation and Test in Europe 2010, European Design and Automation Association: Dresden, Germany. p. 291-294.

- [31] Savidis, I. and E.G. Friedman, Closed -Form Expressions of 3-D Via Resistance, Inductance, and Capacitance. Electron Devices, IEEE Transactions on, 2009. 56(9): p. 1873 -1881.

- [32] http://techreport.com/review/15818/intel-core-i7-processors

- [33] Philip Garrou, Christopher Bower, Peter Ramm, "Handbook of 3D Integration," John Wiley & Sons, (2011)

- [34] Kryder, Mark H. et al., "After Hard Drives What Comes Next?", IEEE Transactions on Magnetics 45 (10) October 2009.

- [35] An Introduction to the Intel QuickPath Interconnect, 2009.

- [36] Byungsub, K. and V. Stojanovic "A 4Gb/s/ch 356fJ/b 10mm equalized on-chip interconnect with nonlinear charge -injecting transmit filter and transimpedance receiver in 90nm CMOS". in Solid-State Circuits Conference - Digest of Technical Papers, 2009. ISSCC 2009. IEEE International . 2009.

- [37] Preston, K., B. Schmidt, and M. Lipson, "Polysilicon photonic resonators for large-scale 3D integration of opti cal networks," Opt. Express, 2007. 15(25): p. 17283-17290.

- [38] Young, I.A., et al. "Integration of nano-photonic devices for CMOS chip-to -chip optical I/O," in Lasers and Electro -Optics (CLEO) and Quantum Electronics and Laser Science Conference (QELS), 2010 Conference on . 2010.

- [39] Samuel Williams, K.D., Jonathan Carter, Leonid Oliker, John Shalf, Katherine Yelick, David Bailey, "PERI - auto-tuning memory-intensive kernels for multicore," Journal of Physics, 2008. 125.

- [40] Chang, Y.C., C.S. Wang, and L.A. Coldren, High-efficiency, high-speed VCSELs with 35 Gbit=s error-free operation. Electronics Letters, 2007. 43(19): p. 1022 -1023.

- [41] Imai, S., et al. Recorded low power dissipation of 0.14 mW/Gbps in 1060 nm VCSELs for "Green" optical interconnection. in Semiconductor Laser Conference (ISLC), 2010 22nd IEEE International. 2010.

- [42] Zortman, W.A., et al. "Monolithic integration of silicon electronics and photonics". in Winter Topicals (WTM), 2011 IEEE. 2011.

- [43] J. S. Orcutt, A. Khilo, C. W. Holzwarth, M. A. Popovi, H. Li, J. Sun, T. Bonifield, R. Hollingsworth, F. X. Kärtner, H. I. Smith, V. Stojanovi, and R. J. Ram, "Nanophotonic integration in state-of-the-art CMOS foundries," Opt. Express, vol. 19, pp. 2335-2346, 2011.

- [44] Miller, D.A.B., "Device Requirements for Optical Interconnects to Silicon Chips," Proceedings of the IEEE, 2009. 97(7): p. 1166 -1185.

- [45] http://www.tomshardware.com/charts/hdd-charts-2012/-01-Read-Throughput-Average-h2benchw-3.16,2901.html

- [46] http://www.tomshardware.com/charts/ssd-charts-2012/AS-SSD-4K-Q64-Random-Read,2786.html

- [47] M. R. Watts *et al.*, "Vertical junction silicon microdisk modulators and switches", *Opt. Exp.* 19, 21989–22003 (2011).

- [48] E. Timurdogan et al., "Vertical Junction Silicon Microdisk Modulators at 25Gb/s," OFC, 2013.

- [49] A. Biberman, M. Shaw, E. Timurdogan, J. Wright, and M. Watts, "Ultralow-loss silicon ring resonators," Opt. Lett. 37, 4236-4238 (2012).

- [50] L. Agazzi, J. Bradley, M. Dijkstra, F. Ay, G. Roelkens, R. Baets, K. Wörhoff, and M. Pollnau, "Monolithic integration of erbium-doped amplifiers with silicon-on-insulator waveguides," Opt. Express 18, 27703-27711 (2010).

- [51] Zerbe, J.; Werner, C.; Stojanovic, V.; Chen, F.; Wei, J.; Tsang, G.; Kim, D.; Stonecypher, W.; Ho, A.; Thrush, T.; Kollipara, R.; Yeh, G.-J.; Horowitz, M.; Donnelly, K.; , "Equalization and clock recovery for a 2.5-10Gb/s 2-PAM/4-PAM backplane transceiver cell," *Solid-State Circuits Conference, 2003. Digest of Technical Papers. ISSCC. 2003 IEEE International*, vol., no., pp. 80-479 vol.1, 2003

- [52] W. Zortman, D. Trotter, and M. Watts, "Silicon photonics manufacturing," Opt. Express 18, 23598-23607 (2010).

- [53] J.H. Kiely, D.V. Morgan, and D.M. Rowe, Meas. Sci. Technol. 5, 182 (1994)

- [54] J. Xie, C. Lee, M. F. Wang, Y. H. Liu and H. H. Feng, Journal of Micromechanics and Microengineering 19, 125029 (2009).

- [55] Jang M, Park Y, Jun M, Hyun Y, Choi S, Zyung T. The characteristics of Seebeck coefficient in silicon nanowires manufactured by CMOS compatible process. Nanoscale Res Lett. 2010;5:1654. doi: 10.1007/s11671-010-9690-2.

- [56] Faiz Salleh, Kiyosumi Asai, Akihiro Ishida and Hiroya Ikeda. Appl. Phys. Express 2 (2009) 071203

- [57] Hochbaum, A. I. *et al.* Enhanced thermoelectric performance of rough silicon nanowires. *Nature* **451**, 163–167 (2008)

- [58] M. W. Riley, J. D. Warnock and D.F. Wendel, "Cell Broadband Engine Processor: Design and Implementation," *IBM J. Res. & Dev.* Vol. 51 No. 5 (2007).

- [59] V. Raghunathan, J. Yagüe, J. Xu, J. Michel, K. Gleason, and L. Kimerling, "Co-polymer clad design for high performance athermal photonic circuits," Opt. Express 20, 20808-20813 (2012).

- [60] B. J. Eggleton, B. Luther-Davies, and K. Richardson, "Chalcogenide photonics," *Nat. Photon.* 5, 1–8 (2011).

- [61] V. Raghunathan, T. Izuhara, J. Michel, and L. Kimerling, "Stability of polymer-dielectric bi-layers for athermal silicon photonics," Opt. Express 20, 16059-16066 (2012).

- [62] A. Canciamilla, F. Morichetti, S. Grillanda, P. Velha, M. Sorel, V. Singh, A. Agarwal, L. Kimerling, and A. Melloni, "Photo-induced trimming of chalcogenide-assisted silicon waveguides," Opt. Express 20, 15807-15817 (2012).

- [63] Andrea Melloni ; Stefano Grillanda ; Antonio Canciamilla ; Carlo Ferrari ; Francesco Morichetti ; Michael Strain ; Marc Sorel ; Vivek Singh ; Anu Agarwal ; Lionel C. Kimerling; Photo-induced trimming of chalcogenide-assisted silicon photonic circuits. Proc. SPIE 8266, Silicon Photonics VII, 82660A (February 9, 2012)

- [64] V. Raghunathan, S. Grillanda, V. Singh, A. Canciamilla, F. Morichetti, A. Agarwal, J. Michel, A. Melloni, and L. Kimerling, "Trimming of Athermal Silicon Resonators," in Integrated Photonics Research, Silicon and Nanophotonics, OSA Technical Digest (online) (Optical Society of America, 2012), paper IW4C.5.

- [65] A. Melloni, A. Canciamilla, C. Ferrari, S. Grillanda, F. Morichetti, P. Velha, M. Sorel, J. Hu, J. Musgraves, B. Zdyrko, I. Luzinov, K. Richardson, V. Singh, A. Agarwal, and L. Kimerling, "Exploiting photosensitivity in chalcogenide-assisted integrated optics," in Integrated Photonics Research, Silicon and Nanophotonics, OSA Technical Digest (CD) (Optical Society of America, 2011), paper IMB1.

- [66] J. Liu, M. Beals, A. Pomerene, S. Bernardis, R. Sun, J. Cheng, L. C. Kimerling, and J. Michel, "Waveguide-integrated, ultralow-energy GeSi electroabsorption modulators," Nature Photonics 2, 433-437 (2008).

- [67] Y. Vlasov, W. M. J. Green, and F. Xia, "High-throughput silicon nanophotonic wavelengthinsensitive switch for on-chip optical networks," Nature Photonics 2, 242 - 246 (2008)

- [68] M. Popovíc, T. Barwicz, M. Watts, P. Rakich, L. Socci, E. Ippen, F. Kärtner, and H. Smith, "Multistage high-order microring-resonator add-drop filters," Opt. Lett. 31, 2571-2573 (2006).

- [69] T. Barwicz, H. Byun, F. Gan, C. Holzwarth, M. Popovic, P. Rakich, M. Watts, E. Ippen, F. Kärtner, H. Smith, J. Orcutt, R. Ram, V. Stojanovic, O. Olubuyide, J. Hoyt, S. Spector, M. Geis, M. Grein, T. Lyszczarz, and J. Yoon, "Silicon photonics for compact, energy-efficient interconnects [Invited]," J. Opt. Netw. 6, 63-73 (2007).

- [70] Soref, R.; Bennett, B.; , "Electrooptical effects in silicon," *Quantum Electronics, IEEE Journal of*, vol.23, no.1, pp. 123-129, Jan 1987 doi: 10.1109/JQE.1987.1073206.

- [71] Q. Xu, B. Schmidt, S. Pradhan, and M. Lipson, "Micrometre-scale silicon.electro-optic modulator", Nature, Vol. 435, pp. 325-327, 19 May 2005

- [72] Gan, F.; Barwicz, T.; Popovic, M.A.; Dahlem, M.S.; Holzwarth, C.W.; Rakich, P.T.; Smith, H.I.; Ippen, E.P.; Kartner, F.X.; , "Maximizing the Thermo-Optic Tuning Range of Silicon Photonic Structures," *Photonics in Switching, 2007*, vol., no., pp.67-68, 19-22 Aug. 2007

- [73] M. R. Watts et al., "Vertical junction silicon microdisk modulators and switches," Opt. Express 19, 21989–22003 (2011).

- [74] M. R. Watts *et al.*, "Adiabatic Resonant Microrings (ARMs) with directly integrated Thermal Microphotonics," *CLEO*, 2012.

- [75] S. Manipatruni, C. B. Poitras, Q. Xu, and M. Lipson, Opt. Lett. 33, 1644.2008.

- [76] X. Xiao, H. Xu, X. Li, Y. Hu, K. Xiong, Z. Li, T. Chu, Y. Yu, and J. Yu, "25 Gbit/s silicon microring modulator based on misalignment-tolerant interleaved PN junctions," *Opt. Express* 20, 2507–2515 (2012).

- [77] J. C. Rosenberg, W. M. J. Green, S. Assefa, D. M. Gill, T. Barwicz, M. Yang, S. M. Shank, and Y. A. Vlasov, "A 25 Gbps silicon microring modulator based on an interleaved junction," *Opt. Express* 20, 26411–26423 (2012).

- [78] G. Li, X. Zheng, J. Yao, H. Thacker, I. Shubin, Y. Luo, K. Raj, J. E. Cunningham, and A. V. Krishnamoorthy, "25Gb/s 1V-driving CMOS ring modulator with integrated thermal tuning," *Opt. Express* 19, 20435–20443 (2011).

- [79] G. Li, X. Zheng, H. Thacker, J. Yao, Y. Luo, I. Shubin, K. Raj, J. E. Cunningham, and A. V. Krishnamoorthy, "40 Gb/s thermally tunable CMOS ring modulator," Proc. International Conference on Group IV Photonics (GFP), 1–3 (2012).

- [80] Y. Hu, X. Xiao, H. Xu, X. Li, K. Xiong, Z. Li, T. Chu, Y. Yu, and J. Yu, "High-speed silicon modulator based on cascaded microring resonators," *Opt. Express* 20, 15079–15085 (2012).

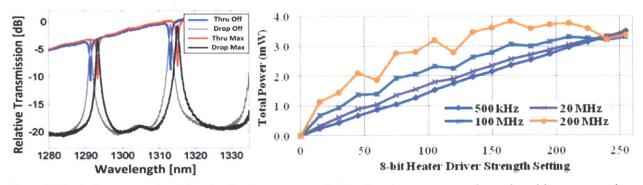

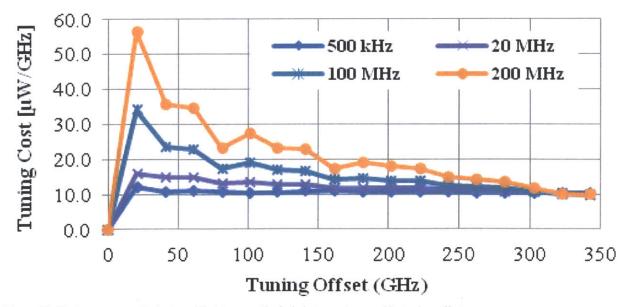

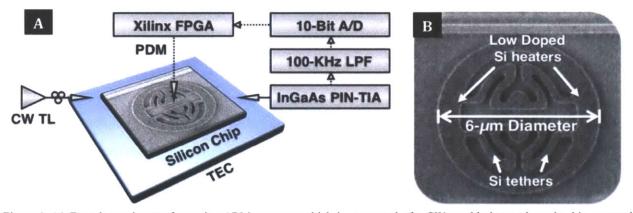

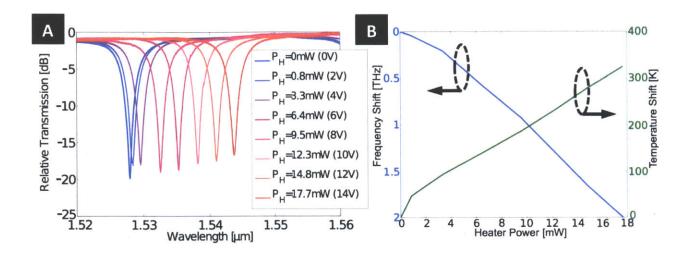

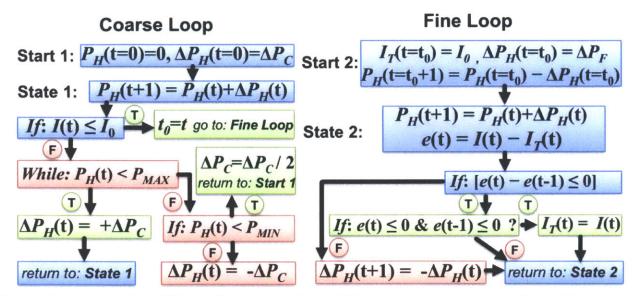

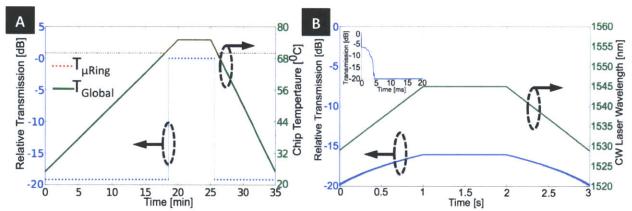

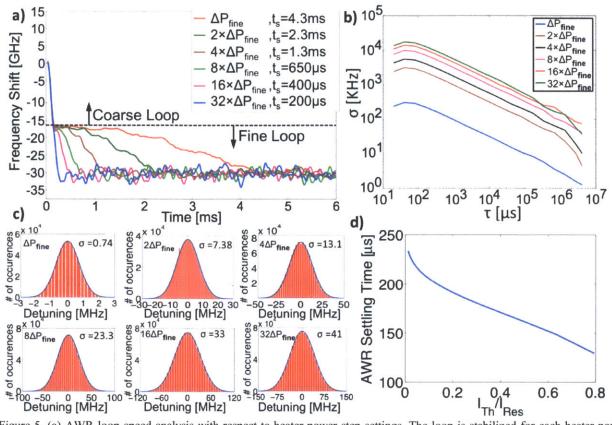

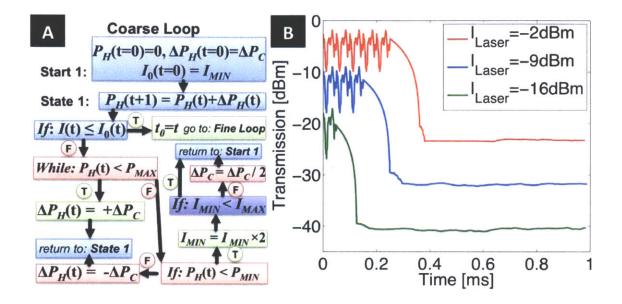

- [81] X. Xiao, X. Li, H. Xu, Y. Hu, K. Xiong, Z. Li, T. Chu, J. Yu, and Y. Yu, "44-Gb/s silicon microring modulators based on zigzag PN junctions," *IEEE Photon. Technol. Lett.* 24, 1712–1714 (2012).