# A Configurer for Parallel Programs

## AUTHOR NASSER SULEIMAN KARABASH

SUBMITTED FOR THE AWARD OF MASTER OF ENGINEERING

SUPERVISOR Sean Marlow Ph D

School of Electronic Engineering Dublin City Unievsity

**MARCH 1991**

The contents of this thesis are based on my own research

# **CONTENTS**

| Acknowledgments                      | V  |

|--------------------------------------|----|

| Abstract                             | 1  |

| Introduction                         | 2  |

| Chapter 1 : Processor Networks       | 5  |

| 1-1 Introduction                     | 5  |

| 1-2 Static connection topologies     | 6  |

| 1-2-1 Rings                          | 7  |

| 1-2-2 Meshes                         | 7  |

| 1-2-3 Binary trees                   | 7  |

| 1-2-4 Fully connected                | 8  |

| 1-2-5 Hypercubes                     | 8  |

| 1-3 Routing algorithms               | 9  |

| 1-3-1 Rings                          | 9  |

| 1-3-2 Meshes                         | 9  |

| 1-3-3 Binary trees                   | 10 |

| 1-3-4 Fullly connected               | 10 |

| 1-3-5 Hypercubes                     | 10 |

| 1-4 Dynamic connection topologies    | 11 |

| 1-4-1 Switching networks             | 11 |

| 1-4-2-1 Crossbar networks            | 11 |

| 1-4-2-2 Single and multistage        |    |

| interconnection networks             | 12 |

| 1-5 Transputer networks              | 14 |

| 1-5-1 The Occam programming language | 14 |

| 1-5-2 The transputer                 | 15 |

| 1-5-3 Message passing techniques 1                  | .7         |

|-----------------------------------------------------|------------|

| 1-5-3-1 Through routing 1                           | .7         |

| 1-5-3-2 Channel multiplexing 1                      | . 8        |

| 1-5-3-3 Dynamic link reconfiguration 1              | . 9        |

| 1-5-4 Transputer networks topologies 1              | . 9        |

| 1-5-4-1 Static topologies 2                         | 0 :        |

| 1-5-4-1-1 Rings 2                                   | 0 1        |

| 1-5-4-1-2 Meshes 2                                  | 1:1        |

| 1-5-4-2 Dynamic topologies                          | 22         |

| 1-5-4-3 Mixed topologies 2                          | 24         |

| Chapter 2 : Configuring Parallel Programs 2         | 29         |

| 2-1 Introduction 2                                  | ≥9         |

| 2-2 Parallel program configuring stages 2           | ≥9         |

| 2-2-1 Parallelism spotting (partitioning) 2         | 29         |

| 2-2-3 Process assigning 2                           | 29         |

| 2-2-4 Communication channels assigning 3            | 31         |

| 2-2-5 Interprocessor connection implementation 3    | 31         |

| 2-3 Configuring parallel programs under the TDS 3   | 31         |

| 2-3-1 TDS2 transputer development system 3          | 31         |

| 2-3-2 TDS configuring procedure                     | 32         |

| 2-3-3 MMS2 module motherboard software 3            | 33         |

| 2-3-3-1 Using the MMS2 3                            | 34         |

| 2-3-4 Case study 3                                  | 3 <b>4</b> |

| Chapter 3 : A Configurer for Programs Running Under |            |

| the TDS2 on the IMS B008 3                          | 38         |

| 3-1 Introduction 3                                  | 38         |

| 3-2 The environment                                 | 38         |

| 3-3 Implementing message passing techniques on |            |

|------------------------------------------------|------------|

| the IMS B008                                   | 38         |

| 3-3-1 Through routing                          | 38         |

| 3-3-2 Channel multiplexing                     | 39         |

| 3-3-3 Dynamic links reconfiguration            | 39         |

| 3-4 The configurer                             | 42         |

| 3-4-1 What is requisted from the configurer    | <b>4</b> 2 |

| 3-4-2 The configurer general description       | 43         |

| 3-4-3 The general algorithm                    | 45         |

| 3-4-4 The configurer requirements in the       |            |

| input program                                  | 45         |

| 3-4-5 Special cases                            | 47         |

| 3-4-5-1 Three non-neighbouring processes       | 47         |

| 3-4-5-2 All the processes need four links      | 48         |

| 3-4-5-3 No loading route from the Root TRAM    | 48         |

| 3-4-6 The configurer program                   | 49         |

| 3-4-6-1 Network detecting                      | 49         |

| 3-4-6-1-1 The program on T2 (controller) .     | 49         |

| 3-4-6-1-2 Network detecting procedure          |            |

| (Host)                                         | 51         |

| 3-4-6-2 Searching for the program source       |            |

| fold                                           | 54         |

| 3-4-6-3 Reading the program source             | 54         |

| 3-4-6-4 Processes and channels mapping and     |            |

| placing                                        | 58         |

| 3-4-6-4-1 Phase I                              | 58         |

| 3-4-6-4-2 Phase II                             | 61         |

# Contents

| 3-4-6-4-3 Phase III                                 |

|-----------------------------------------------------|

| Chapter 4: Using the Configurer 80                  |

| 4-1 Introduction 80                                 |

| 4-2 A program requiring a hypercube topology 80     |

| 4-3 A program requiring a mesh topology 81          |

| 4-4 A program requiring a binary tree topology . 82 |

| 4-5 A program requiring a user defined topology 83  |

| 4-6 Configuring the network 85                      |

| Chapter 5: Improvements and Further development 87  |

| 5-1 Introduction 87                                 |

| 5-2 Improvements on the configurer program 87       |

| 5-2-1 Handle larger number of processes and         |

| processors 87                                       |

| 5-2-2 Handle replicated PLACED PAR construct . 88   |

| 5-2-3 Mixed transputer types                        |

| 5-2-4 Unlimited number of processes 88              |

| 5-2-5 Use the configurer instead of the MMS2 . 90   |

| 5-2-6 Channels protocols check 90                   |

| 5-2-7 User friendly 90                              |

| Conclusions 91                                      |

| <b>References</b> 92                                |

| Appendix A                                          |

| Appendix B                                          |

| Appendix C                                          |

| Appendix D                                          |

| Appendix E                                          |

# **Acknowledgment:**

I would like to thank Dr. S. Marlow for his support and encouragement, which helped me to complete this work.

My gratitude to the Scientific Studies and Research Centre (SSRC) in Syria for it's guidance and sponsorship.

#### Abstract:

Making parallel systems easy to use, and parallel programs easy to write and run, are two major aims for parallel systems designers.

This work describes an automatic configurer which attempts to lessen the effort a user should put to configure and run a parallel program on a network of parallel processors

The configurer configures the program, as required by the operating system and produces the configured source of the program

The network is also configured by the configurer to meet the communication requirements of the configured program

#### Introduction:

Developments on parallel programming languages are directed to help the programmer to write a parallel program without having to know how the concurrent processes are going to be distributed on the processors or how they are going to communicate with each other.

Parallel architectures provide a high level of computing power although ordinary processing elements are used [1]. Different topologies are being used in parallel architectures but no single one has proved to be better than all the others. Each topology is good for a specific type of problems but may be bad for others.

Performance problems, possibly caused by bad partitioning of a program, result in a very big amount of communication between the different partitions (concurrent processes). In the worst case, running problems like long waiting times or even deadlocks may occur.

The maximum performance is got if all the processors are kept busy as much as possible. To achieve that, a balance in the computational and communication load between all the processors should be achieved, which is not an easy task. Predicting or estimating the required computation time of a process is not an easy task [21].

To configure a program to run on a processor network is to assign the concurrent processes of the partitioned program to the processors and assign the communication channels between the processes to the processors' links.

Information about how many processors there are in the network, how the processors are connected, how the messages are passed between the processors, how many parallel processes there are, and the communication requirements between these processes should be known to enable the configurer to distribute the processes in an efficient way.

This project addresses the detection of the processors in the network and the parallel processes in the program, the generation of the communication map between the processes, the assigning of the parallel processes to the processors (transputers) in the network, the creation of the required interconnections between the processors to meet the interprocess communication needs, and generates a new source program with all the correct configuration data added.

In Chapter One, different interconnection methods used in parallel processing machines are discussed to show the relationship between the applications and the processor network topology. A general idea about the Occam programming language and the transputer is then given. Different message passing techniques used in transputer networks are discussed. Some transputer based systems of different types of topologies are described.

In Chapter Two the procedure of configuring a program to run on a processor network is discussed, and then the TDS configuring procedure is described followed by a case study to clarify the problem the project is trying to

solve.

Chapter Three discusses the design of the configurer in detail.

Chapter Four contains the results of configuring programs requiring different types of topologies by the configurer program. This chapter shows how to use the configurer and demonstrates the facilities it provides.

In Chapter Five suggested improvements and further work are mentioned followed by the conclusions.

# **Processor Networks**

#### 1-1 Introduction:

Partitioning a program into parallel processes and defining the communication pattern between the processes are the steps which come before the configuring step.

Different types of interconnection schemes used in parallel machines are described to show the relationship between the machine architecture and the application program partitions. Selected transputer based architecture examples are mentioned separately to show the variety of network architectures that could be build using the transputer as the basic processing block.

This chapter gives parallel programs designers information which will help them in chosing algorithms, processor network topologies and communication techniques.

Two categories of topologies could be distinguished:

- 1 Static connection topology.

- 2 Dynamic connection topology.

Static topologies are suitable for applications whose communication pattern can be reasonably predicted. Dynamic topologies, although they are more expensive, are suitable for a wider class of applications.

Static topologies machines are special purpose because high performances on these machines are achieved when dealing with specific problems depending on the match between the topologies and the algorithms being used in

solving these problems.

## 1-2 Static connection topologies:

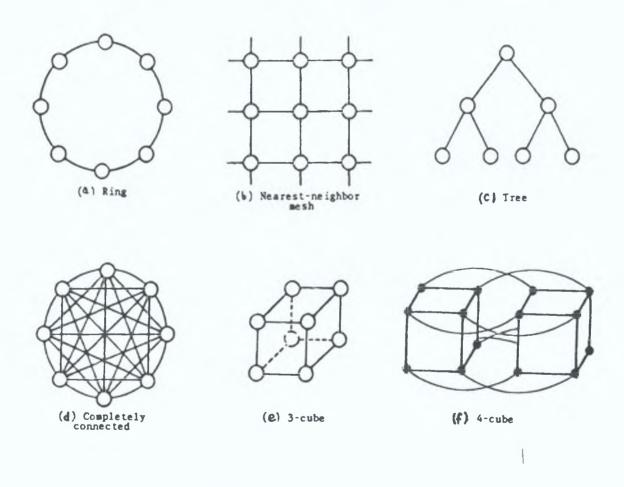

A static network topology is one in which none of it's connections can be changed after the machine is built. The simplest connecting scheme is a ring (Figure 1-1-a). On the other hand, the most complicated but powerful and ideal connecting scheme is the all-to-all scheme Figure (1-1-d).

Figure (1-1 a-h) [7]

Different static configurations have been used in parallel systems with an intermediate number of nearest neighbours taking into consideration that the choice of the connection scheme is compromise between wireability and

performance [9].

Special purpose systems with a relatively large number of computing nodes are expected to give good performance results when dealing with problems which could be divided into parts which have light and predictable communication patterns, normally data exchanges among neighbouring nodes.

# 1-2-1 Rings:

The nodes are arranged in a closed line "Necklace" where adjacent nodes are connected. Nodes are of degree 2, Figure (1-1-a) illustrates this scheme. Ring topology is used in systems like the ZMOB [13], which was designed to support image processing [14] and artificial intelligence [15] applications.

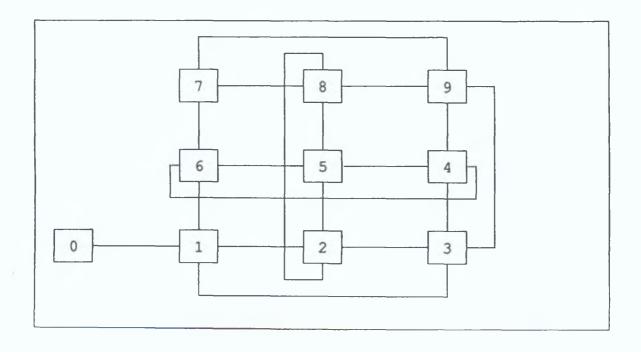

#### 1-2-2 Meshes:

The nodes are arranged in a mesh of N dimensions. The interior nodes are of 2N degree and the degree(s) of the nodes at the edges and the corners differs from machine to another. Figure (1-1-b) illustrates a 2-dimensional mesh scheme. Array processors like the MPP and DAP [3] provide a large computing power required for massive computing applications, e.g large matrix operations.

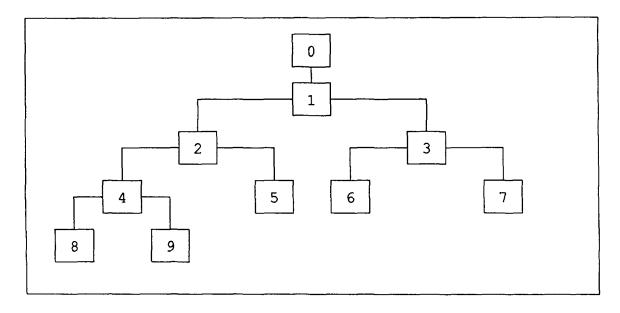

#### 1-2-3 Binary Trees:

The nodes in the basic binary tree are arranged in levels, each level contains double (or half depending on the direction) the number in the previous level. The interior nodes are of degree 3, the root nodes are of degree 2 and the leaves are of degree 1. Figure (1-1-c)

illustrates this scheme for three levels. The scheme is used in Reduction machines like FFP [16] and expert systems machines like DADO [17].

## 1-2-4 Fully connected:

Each node is directly connected to all the others in the network which means all the nodes are of degree N-1 in a network containing N nodes. The total number of connections needed in this scheme is N(N-1)/2 connection.

Figure (1-1-d) illustrates an all-to-all network for N=8.

## 1-2-5 Hypercubes:

has a special a mesh scheme but connecting and numbering the nodes. An n-dimensional Hypercube will contain number of nodes N=2 where n is the node degree also. If the nodes are numbered starting from 0 to N-1, by using the binary representation of the nodes numbers and connecting the nodes whose numbers differ by a power of 2, the result will be dimensional Hypercube. Figure (1-1-e,f) illustrates a 3D and a 4D cubes respectively. The Connection Machine which uses a 12-dimensional hypercube [18] is suitable for a broad class of computational problems and knowledge processing.

Many other schemes are used like the Linear Array, the Systolic Array, the Chordal Ring, Shuffle-Exchange and many others. New schemes are always expected to appear trying to increase the performance of the machines and to meet the

requirements of new applications.

# 1-3 Routing algorithms:

Packet switching is used in all of the topologies mentioned above. A routing algorithm will be suggested to find a path between node A and node B for data routing.

#### 1-3-1 Rings:

In a ring of N node clockwise numbered from 0 to N-1 the minimal length path from A to B could be found depending on the table:

| Conditions                                                               | Length   | CW/CCW |

|--------------------------------------------------------------------------|----------|--------|

| (A>B) AND (( B-A )>N/2)                                                  | N -  B-A | CCW    |

| (A>B) AND (( B-A ) <n 2)<="" td=""><td> B-A </td><td>CW</td></n>         | B-A      | CW     |

| (A <b) (( b-a )="" and="">N/2)</b)>                                      | N -  B-A | CW     |

| (A <b) (( b-a )<n="" 2)<="" and="" td=""><td> B-A </td><td>CCW</td></b)> | B-A      | CCW    |

| B-A  = N/2 (N is even)                                                   | B-A      | SAME   |

## 1-3-2 Meshes:

Routing on a mesh of K dimension is performed one dimension at a time. In a 3D mesh suppose A has the coordinates (a,b,c) and b has the coordinates (x,y,z), a path from A to B is constructed from three paths each of these paths is parallel to one of the dimensions so the route will move along the first dimension to reach the node coordinated at (x,b,c) then it will move along the second dimension to reach the node coordinated at (x,y,c) and then the last part of the path is to move along the third dimension to reach the destination B at (x,y,z).

#### 1-3-3 Binary Trees:

The simplest way is to start from A and then up the tree until the first ancestor of B is found, then down to B. This algorithm can be implemented simply depending on the numbering system of the nodes.

One way of numbering is to assign a number to the node, say (n), and assign the numbers (2n) to it's left child and (2n+1) to it's right child and the root is given the number (1). The path from A to B due to the above algorithm depends on finding an ancestor of B starting from A. Using the binary representation of the numbers of A and B, the number of the first ancestor of B (starting from A) is the result of a chain of logical shift right operations on both A and B until they are equal. Going down to B, after reaching the ancestor, is easy by ignoring the ancestor number in B (from the MSBs) and going down one level for each bit left. Going Right or left depends on the bit; if it is 1 go right and if it is 0 go left. When all the bits are used B will be reached.

#### 1-3-4 Fully connected:

All the nodes have direct paths with all the others, Figure (1-1-d).

## 1-3-5 Hypercubes:

Since the hypercube is a special case of mesh where each dimension contains only two nodes, the binary numbers of the nodes are actually the coordinates of the

node and each bit represents a dimension. In order to make use of this property, performing an Exclusive OR between the numbers A and B will result in a number which contains a 1 in precisely the dimensions along which the data must move.

## 1-4 Dynamic connection topologies:

which all A dynamic topology network is one in connections can be changed after the machine is built. goal of using a dynamic topology is to provide the possibility of connecting any node to any other one directly, using circuit switching, without the need to pass through other nodes which have nothing to do with the data being transferred.

# 1-4-1 Switching networks:

Multiple segments communication path interconnected by switches are used to make complete paths between the nodes, these paths are changed as necessary to cope with the communication traffic among the nodes.

## 1-4-2-1 Crossbar networks:

A crossbar network enables any node to have a direct path with any other non-busy node at any time with a constant delay which is basically the switching time of one switching element. Crossbar networks advantage over the all-to-all network in that the connections it needs are of order N not N. The difficulty with crossbar networks is the number of the crosspoint switches. N crosspoint switches are needed for a network of N nodes and that complicates the design of the crossbar and makes the producing cost high rather than putting limits on the size of the crossbar.

Using current technology, designing large systems with large number of nodes is not yet feasible [10].

#### 1-4-2-2 Single and Multistage interconnection networks:

In order to solve the problem of providing fast, reliable and efficient communications in large parallel processing systems at a reasonable cost many different networks were designed to replace the crossbar. The replacement can be constructed from single or multiple stages of small and cheap crossbar switches.

In a single-stage network data (messages) may have to be passed through the switches several times before reaching their final destinations. In a multistage network only one pass through the stages is needed, the function of a multistage network can be performed by a single-stage network and the delay will still be the same but in the single-stage network a new wave of messages could not be accepted before the preceding wave has done all the needed passes which is not the case in the multistage networks where a new wave is accepted each time the preceding wave has moved on to the next stage.

The Omega network is an example of the multistage networks based on the shuffle-exchange permutations [19].

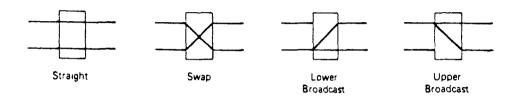

The network consists of 2X2 crossbar switches, each of the crossbars can perform four passing functions:

- 1) Straight-through, Figure (1-2-a).

- 2) Criss-cross (swap), Figure (1-2-b).

- 3) Upper broadcast, Figure (1-2-c).

- 4) Lower broadcast, Figure (1-2-d).

Figure (1-2) [11]

The switches are arranged in an array of N/2 rows by Log<sub>2</sub> N columns and are interconnected in a perfect shuffle. The switching method is packet switching where messages are sent through the network in the form of data plus an address which is read by each switch and then the packet is forwarded to the next appropriate switch according to some control scheme until it arrives at it's destination.

The Omega network uses a distributed control scheme that takes advantage of simple message routing а algorithm which is suitable for both SIMD (synchronous) operation because many different permutations could be performed in a short tıme and MIMD (asynchronous) operation in which connection requests are dynamically.

Many other networks are discussed in [11] and [12] in

some detail.

## 1-5 Transputer networks:

#### 1-5-1 The Occam programming language:

Occam is a high level programming language designed to support concurrent programming [30].

As a concurrent programming language an Occam program is built from a number of processes running sequentially, concurrently or in parallel. In the case of concurrent and parallel processes inter-process communications are done through Occam channels.

Occam has three primitive processes :

| Process function                                                              | Operator | Process Format |

|-------------------------------------------------------------------------------|----------|----------------|

| Assignment                                                                    | =:       | var. := exp.   |

| Output to channel                                                             | 1        | chn. 'exp.     |

| Input from channel                                                            | ?        | chn. ? exp.    |

| Where var. is a variable name. exp. is an expression. chn. is a channel name. |          |                |

To form constructs Occam processes could be combined in three different ways depending on the execution timing relationship between the processes, these ways are:

| Timing Relationship | Operator |

|---------------------|----------|

| Sequentially        | SEQ      |

| In Parallel         | PAR      |

| Alternatively       | ALT      |

Parallel processes could be executed in parallel if

they are assigned (placed) to different processors otherwise they will be executed concurrently on the same processor (pseudo-parallel execution).

Alternative execution performs one process out of a number of processes guarded by inputs. This process is the one guarded by the ready input.

Inter-process communication in Occam is synchronous, and can only be done through channels as shared memory is not allowed in Occam. The communication will only take place if both the sender and the receiver are ready to communicate; other-wise the ready to communicate process will be suspended till the other process is ready to communicate [31].

Concurrent programming languages have two categories of applications. The first is designing multitasking programs for single processor systems. The second is designing programs for multi-processor systems where the program processes will run in parallel. Occam supports both categories and is used in the implementation of parallel algorithms [32], [33] in many fields like FFT, signal processing, image processing and display, industrial control, process automation, and simulation.

#### 1-5-2 The transputer:

The transputer is a programmable VLSI device designed to support the Occam model of concurrency.

To run an Occam program which could be constructed

from concurrent processes, the transputer has to provide concurrency run-time functions like process scheduling, queue manipulation, context switching, process suspending and releasing. These functions are directly supported by the transputer's hardware and microprogram.

Concurrency is achieved on a single transputer by sharing the processor time between the concurrent processes.

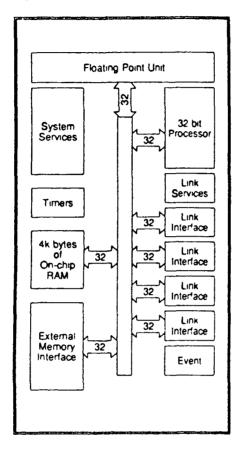

The IMS T800 (Figure 1-3) integrates a 32-bit microprocessor, a 64-bit floating point unit, four standard transputer communications links, 4K Bytes of onchip RAM, a memory interface and peripheral interfacing on a single chip using a 1.5 CMOS process [22].

The 64-bit floating point unit provides single and double length operations according to the ANSI-IEEE 754-1985 standard for floating point arithmetic and is able to perform it's operations concurrently with the processor. The transputer uses a DMA block transfer mechanism to transfer messages between the memory and another transputer product via an INMOS link. The link interfaces and the processor all operate concurrently allowing the processing to continue while data is being transferred. The 4K Bytes of on-chip RAM provide a maximum data rate of 80 MBytes/Sec with access from both the processor and the links. The external data address buses are multiplexed on one bus and provides data at rate up to 26.6 MBytes/Sec.

The IMS T800 has a microcoded graphics capabilities for block moving at the speed of memory.

Figure (1-3) Transputer architecture [22]

#### 1-5-3 Message passing techniques:

#### 1-5-3-1 Through routing:

This way of message routing would allow processes running on non-neighbouring processors to communicate.

A routing process is allocated on each processor in the network and has the map of the whole network to be able to forward the messages on the right route.

Buffering is essential for this method because the messages are not being received by the destination. In the Occam model, sending and receiving are synchronous

events between the source process and the destination process, while here the sending process can proceed without the message being received by the real destination because the message is received by the routing process. How long the message will take to arrive to the destination, depends on how much the routing processes along the route from the source to the destination are loaded.

To avoid the proceeding of the sender before the message being received by the destination, the sender is blocked waiting for an acknowledgment message to come from the destination. The time the sender speds waiting for this message to come is obviously wasted and still the synchronization is not restored [37] because the destination will proceed.

## 1-5-3-2 Channel multiplexing:

In the cases where the four channel-pairs of the transputer are not enough and more channels are needed, channels could be multiplexed onto transputer links.

A multiplexing process and a demultiplexing process are required for each link. This method is useful when more than one independent process is running on the same transputer and have to communicate with other processes on another neighbour transputer. The problem of losing synchronization is still there because the messages are still being received by a process other than the destination. The acknowledgment technique

could be used to guarantee message arrival.

#### 1-5-3-3 Dynamic link reconfiguration:

Synchronization is only granted when the sender and the receiver are communicating directly.

A solution to the problem created by the limited number of transputer links and the communication between processes on non-neighbour processors is the dynamic topology [24],[28] where the processes can request from the topology controller to create a connection with the other process on the other transputer. This technique enables any process on any transputer to communicate with any other process within the Occam model.

Routing algorithms should always avoid deadlocks by providing the required precautions. Deadlocks are out of the focus of this thesis; refer to [20] for a detailed design of deadlock free networks.

#### 1-5-4 Transputer network topologies:

A transputer network consists of a number of

transputers interconnected via the serial links of the transputers. Transputer networks need less hardware to be implemented because the communication links are serial and need only two wires (tracks on PCBs) one for input and one for output. Also transputers can be directly connected via the links without any additional hardware (driving or interfacing).

As a powerful processor and very suitable for

parallel architectures, Transputer based parallel processing systems are being used in a wide range of applications.

Transputer based systems with all types of topologies, Static, Dynamic, and Mixed are available.

## 1-5-4-1 Static topologies:

## 1-5-4-1-1 Rings:

#### - Kilonode:

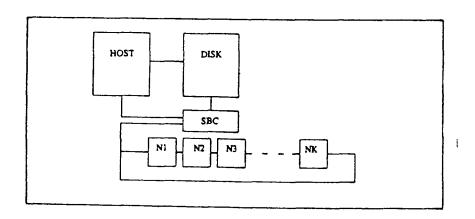

The Kilonode system [4] is expandable modular and the maximum configuration contains up to 1000 transputer based modules. The interconnection scheme used in the Kilonode is a ring where all the nodes (modules) are connected via the links of the transputers. The system consists of a host computer running the application, a large disk, an SCSI or ethernet interface to the host and the Kilonode.

Figure (1-4) [4]

Figure (1-4) shows the architecture of the

System where SBC is a very fast Single Board Computer which accesses the disk to read the data and automatically apportion it among the nodes. The data is passed to the nodes from the SBC through the links. Through routing technique is used for data exchange. The system supports ultra-large computing problems like matrix inversion, FFT, circuit analysis.

#### 1-5-4-1-2 Meshes:

#### - IBM Vector multi-processor:

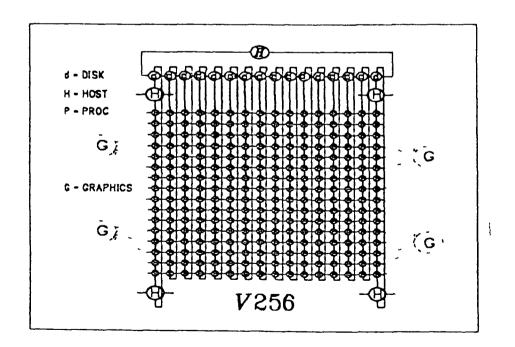

The interconnection scheme used in the Vector family of transputer based multi-processor systems is 2D mesh. Figure (1-5) shows the overall architecture of the system.

Figure (1-5) [23]

The V16 is the smallest containing 16 nodes

and V256 is the largest in the family containing 256 nodes and a total of 1G Bytes of memory. The

V256 is partitionable. Four concurrent users and a superuser could share the system each has his own isolated partition. A user can own a host, an arbitrary shaped multi-processor piece of the network and one graphics node. Special hardware is used to prevent users interfering with each other. The 16 disk nodes are owned by the superuser and act as servers, handling all file-system requests from the users [23]. The nodes are built around the IMS T800 transputer and communicate with each other via the transputers' links. Messages are passed using the through routing. Large knowledge bases is one of the system's applications.

# 1-5-4-2 Dynamic topologies:

All the interprocessor connection can be changed in this type of topology. The network may be configured for a certain application before the execution of the program onto the network starts and during the execution the topology may remain as it was configured or changes may occur during execution (Run-time) to meet the communication requirements at the different stages execution.

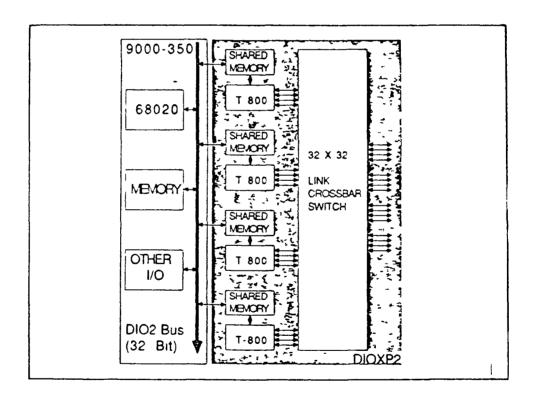

#### - DIOXP2 card:

A transputer based add-in board was designed to work as an accelerator to the HP 9000-300 series of engineering workstations to increase the capabilities of three dimensional modeling of solid objects (computationally intensive task). Figure (1-6) shows the DIOXP2 card and its relation with the workstation [24].

Figure (1-6) [24]

Algorithms being used for the modeling require different operations to be done on identical copies

of the object data which is primarily expressed as double precision floating point numbers. decrease the time consumed in sending the data to provides the processors the design broadcasting facility which is able to send the data to some or all the transputers simultaneously. The broadcasting of the data is achieved by using dual ported memory for each transputer and the host has access to all these memories and can only write to all or some of them at the same address. Communications between the processes running on the transputers are done via the transputers' links which are connected to a crossbar switch controlled by the workstation through special circuity.

Messages could be passed between the transputers using packet switching as well as circuit switching because the system allows runtime topology reconfiguration of the transputer network by enabling the user's application to access the crossbar switch control circuity.

#### 1-5-4-3 Mixed topologies:

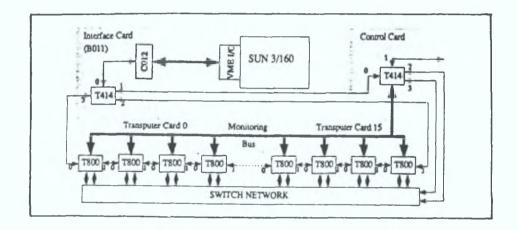

#### - The ParSiFal system:

The ParSiFal (Parallel Simulation Facility) has a modular architecture, a fully configured system contains to 1024 transputers each of it with 1M or 2M Bytes of external RAM. The transputers are installed on boards each contains four IMS T800.

Sixteen of these boards comprise one module called the T-Rack machine which was designed as a step in the ParSiFal project [27], Figure (1-7). The T-Rack machine has 64 transputers connected together by links 0 and 1 to form a processor pipe, Link0 of the first transputer is connected to Link3 of the Root transputer (IMS T414) on the interface board

Figure (1-7) [27]

with the host computer (Sun 3/160) and Link1 of the last (which could be connected to Link0 from another T-Rack) is connected to Link2 of the Root transputer. The rest of the links (2,3) are taken to a crossbar switch controlled by a separate board called the Control board. The user program can control the crossbar switch via a Link connects the interface transputer to the control transputer. The T-Rack has a Byte-wide monitoring bus appearing as a register in the address space of each transputer

and as an array of registers in the address space of the switch control transputer, this bus provides the mean of communication between the application transputers and the crossbar control transputer (the dynamic topology control transputer). During the Run-Time a process running on a transputer may need to communicate with another process running on a non-neighbour transputer. A message is sent to the control transputer, through the monitoring bus, asking for the required connection [28]. The system is used for parallel architectures simulation.

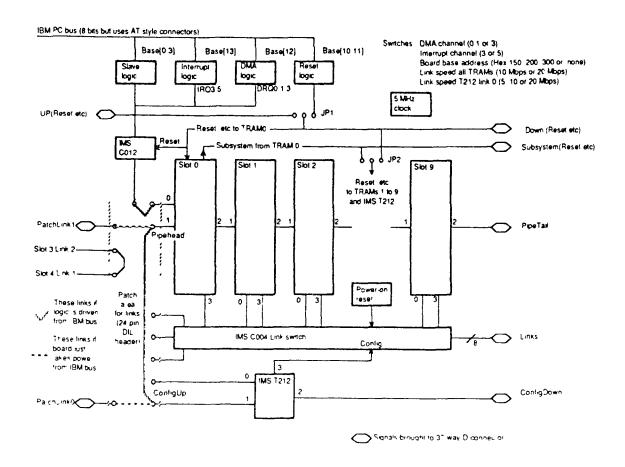

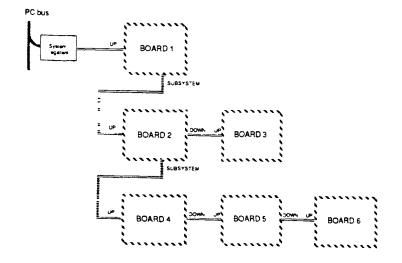

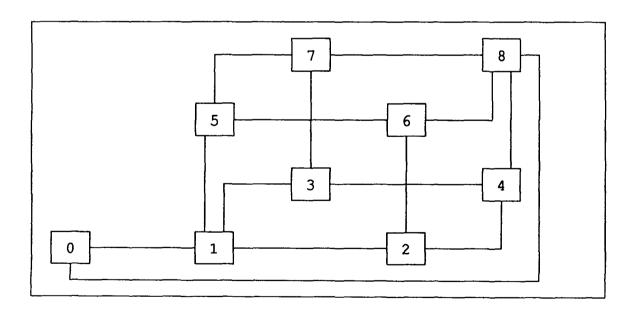

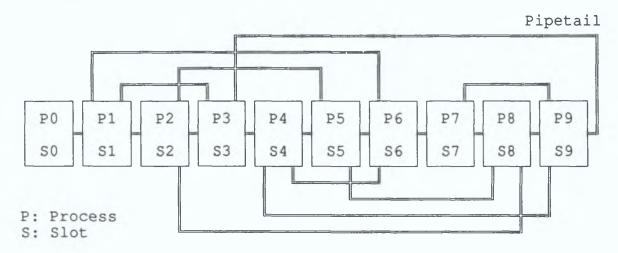

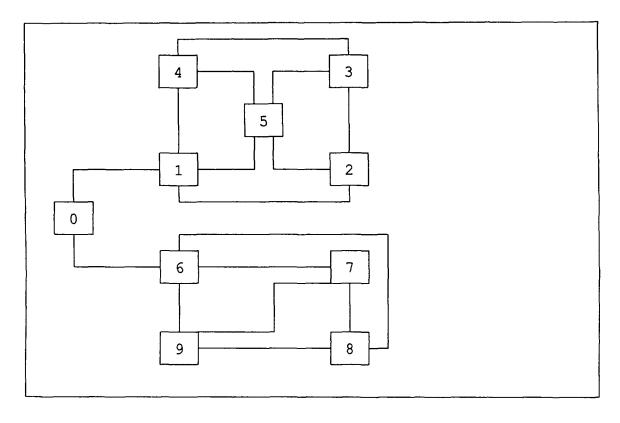

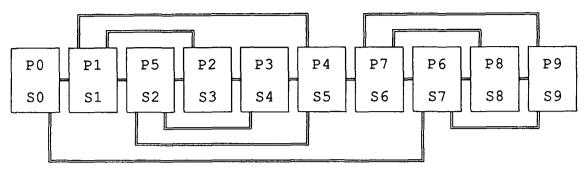

#### - IMS B008 module motherboard:

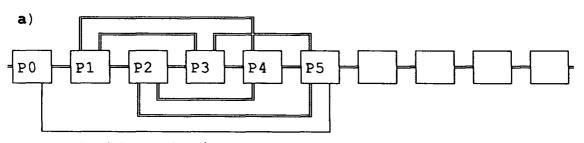

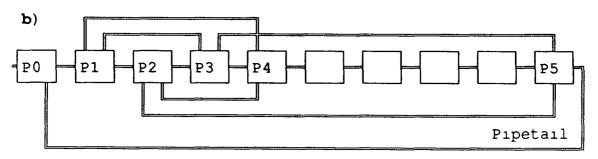

The IMS B008 is an IBM-PC plug-in Transputer Module motherboard, Figure (1-8). It provides the interface between the PC and the transputer based system. The board can accommodate 10 transputer modules (TRAMs). A processor pipe is formed by connecting Links 1 and 2 of each TRAM. The rest of the links (0,3) are taken to a software controlled 32X32 crossbar switch, the IMS C004 [22], to allow a variety of topologies to be implemented. The board is cascadable to allow a multimotherboard system to be built, Figure (1-9).

The structure of the IMS B008 is similar to the structure of the T-Rack with a major difference which is the absence of the monitoring bus.

Figure (1-8) [29]

Figure (1-9) [22]

For more details please refer to [29], [36].

The transputer efficiency and the simplicity of implementing transputer based architectures give transputer systems an advantage on other processors based parallel architectures.

As we have seen static topologies are special purpose and to get high performances on such machines, restrictions should be imposed on the programs structures to achieve a kind of match between the program and the machine. Dynamic topologies flexibility allow a wide range of topologies, message passing techniques to be implemented (chapter 4) and that makes it more general purpose.

In the next chapter the procedure of configuring parallel programs to be fitted onto the parallel processor network is described, then the configuring procedure of the TDS (Transputer Development System) to run a program on a transputer network is discused in detail.

# Configuring Parallel Programs

#### 2-1 Introduction:

The design of parallel programs passes through several stages before it could be compiled and run. Configuration is last where the processes are located at the processors and the communication links are located at the interprocessor connections.

#### 2-2 Parallel program configuring stages:

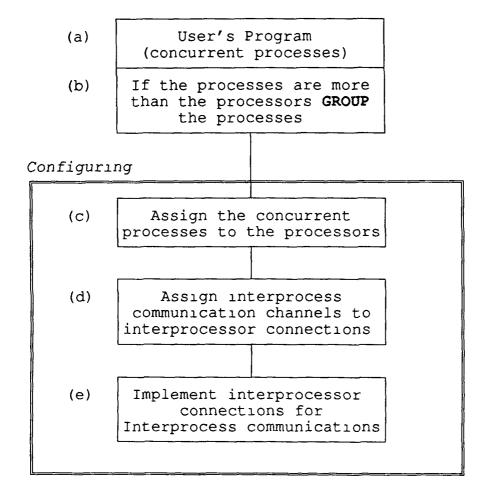

Figure (2-1) represents the configuring procedure.

## 2-2-1 Parallelism spotting (Partitioning):

This stage is extremely important because the next stages are strongly depend on its results.

In fact most of the computing applications (e.g. real-time systems) are inherently parallel in nature. An application behavior could be described by a collection of concurrent processes, each describing the behavior of a particular aspect of the implementation. Running these processes in parallel and enabling them to communicate together will give an actual representation and better response to the events in real-time. A match between the program structure and the target parallel processor network architecture should be made to achieve high performances.

## 2-2-3 Processes assigning:

Each concurrent processes is assigned to an individual processor if possible. Often there will be

Figure (2-1)

more processes than the available processors. In such cases groups of processes are assigned to individual processors. Processes are grouped according to their expected computation time, and communication relations.

The balance of the computational load between the processors increases the system performance, but it is not the only factor. In some applications where the communication traffic is heavy, the communication system efficiency determine the overall system performance.

Computational load balance, and short paths between

heavily communicating processes are major factors in process distributing [21].

#### 2-2-4 Communication channels assigning:

After the processes are assigned the communication channels between the processes could be assigned to the interprocessor connections depending on the processes places and the routing algorithm.

#### 2-2-5 Interprocessor connection implementation:

If the system has a dynamic or mixed (dynamic and static) topology, the processor network is configured to meet the previous stages requirements.

# 2-3 Configuring parallel programs under the TDS:

# 2-3-1 TDS2 The transputer development system:

The TDS2 is an integrated development system designed to support the development of Occam programs for transputer networks applications. The TDS2 consists of two parts; one contains the editor, the compiler and other utilities. This part runs on a transputer based plug-in board like the IMS B004 or IMS B008. The other part provides the access to the host filling system and the console (screen, keyboard). This part runs on the host system.

Occam programs can be edited, compiled, and run from within the TDS2. Programs to run on a transputer network could be developed as well. The TDS2 has many other utilities like parallel programs debugger, transputer networks tester, mathematical library, Input/Output

functions library, and others [34].

#### 2-3-2 TDS configuring procedure:

In order to configure a program constructed from a number of parallel processes under the TDS, a number of steps should be done. These steps are [34]:

- 1: Each process to be allocated to a transputer should be contained within a fold of type SC.

- 2: All the SC folds should be collected into a fold of type PROGRAM.

- 3: Configuration statements are added to the PROGRAM fold, these statements place the processes each at a transputer and describe the interconnections between the processes by mapping the external channels onto the links of the transputers using special constructs.

- 4: Compile the program and then extract all the code produced by the compiler into on code fold.

- 5: Before the network could be loaded with the executable code of the configured program the connections between the transputers should be implemented (Dynamic topology) using the proper hardware or software (if the network can be configured by software).

The programmer needs to know some details about the target network to be able to configure a program and to implement the required topology.

In our case where the target hardware is the IMS B008

[29], configuring a program passes through the same steps using the MMS2 [35] for step 5.

#### 2-3-3 MMS2 The module motherboard software:

This package is supplied by INMOS to enable users of the IMS B008 module motherboard to configure the transputer network to meet their programs communication requirements. The MMS2 requires two files as input files, one to describe the new connections the user wants to create, and one to describe the hardwired connections of the board, this file is supplied by INMOS [29]. To write the softwired connections description file, the programmer has to know at which slots, on the board, the TRAMS (Transputer Module) are installed.

The MMS2 runs independently from the TDS2 and from outside the TDS2. If the TDS is suspended and the MMS2 is run, the system can't return back to the TDS. That means the network should be configured before running the TDS and then run the TDS and load the network with the code of a configured program. The whole process must be repeated to run another program which requires a different topology.

The MMS2 is able to create bootable files to configure the network without the need to run the MMS2 every time the network needs to be configured [35]. This file should be used to configure the network before running the TDS.

#### 2-3-3-1 Using the MMS2:

The following steps describes the use of the MMS2 to configure a transputer network on the IMS B008:

- 1: Draw the topology and name (number) the links.

- 2: Write the softwired connections description file.

- 3: Run the MMS2 using his file as the first input file and the hardwired connections description file as the second input.

- 4: If the topology is going to be frequently used, it's better to produce a bootable file. Reset the subsystem, and initialize the C004s (the crossbar switch), before setting the C004.

- 5: The TDS could be run now and the network could be loaded with the program code.

# 2-3-4 Case study (Configuring an example program):

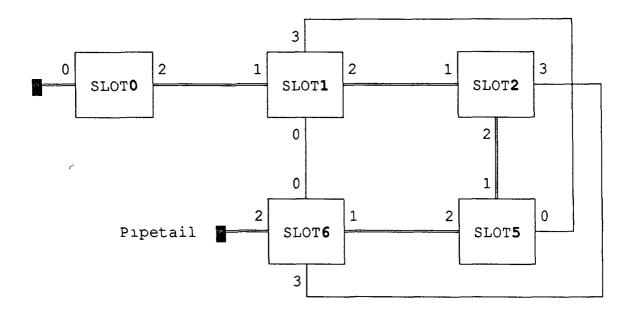

Suppose a program of five parallel processes, is be configured to run on a network of five transputers, (stages a & b, Figure (2-1), are already done).

The processes external channels are as in Table 2-1, and the required network topology to run the program is illustrated in Figure (2-2). The first step is to place (assign) the concurrent processes to the available processors (transputers), Figure (2-1,c). Under the TDS special configuring instructions are added to the program source to place the processes at the transputers. Numbers are given to the transputers, but they have no relation

| with the | he | actual | numbers | of | the | TRAMs | they | represent. |

|----------|----|--------|---------|----|-----|-------|------|------------|

|----------|----|--------|---------|----|-----|-------|------|------------|

| Process name | Input channels name                                      | Output channels name                                     |  |  |  |

|--------------|----------------------------------------------------------|----------------------------------------------------------|--|--|--|

| process.0    | from.1.to.0                                              | from.0.to.1                                              |  |  |  |

| process.1    | from.0.to.1<br>from.2.to.1<br>from.3.to.1<br>from.4.to.1 | from.1.to.0<br>from.1.to.2<br>from.1.to.3<br>from.1.to.4 |  |  |  |

| process.2    | from.1.to.2<br>from.3.to.2<br>from.4.to.2                | from.2.to.1<br>from.2.to.3<br>from.2.to.4                |  |  |  |

| process.3    | from.1.to.3<br>from.2.to.3<br>from.4.to.3                | from.3.to.1<br>from.3.to.2<br>from.3.to.4                |  |  |  |

| process.4    | from.1.to.4<br>from.2.to.4<br>from.3.to.4                | from.4.to.1<br>from.4.to.2<br>from.4.to.3                |  |  |  |

Table (2-1)

The external channels are placed at the transputers' links using a supposed placing of the processes at the SLOTs (the process placed at PROCESSOR 0 in the previous step is placed at the first occupied SLOT after SLOT 0).

After the external channels are placed the softwired links description file is written to be used by the MMS2 to configure the network. The following is the contents of the softwired file:

```

SOFTWIRE

SLOT 1, LINK 3 TO SLOT 6, LINK 0

SLOT 1, LINK 3 TO SLOT 5, LINK 0

SLOT 5, LINK 3 TO SLOT 6, LINK 3

END

-Softwire description file for Figure (2-2) topology

```

Now the program is configured and could be compiled and extracted. The network should be configured before loading it with program executable code.

Appendix A contains the configured program listing.

: Softwired links

: Hardwired links

Figure (2-2)

For a network of small number of transputers this procedure could done by the programmer, but for larger networks it will become complicated and will consume a long time.

These difficulties are not faced when working on a sequential machine or developing a sequential program which we are accustomed to. I believe that the job of parallel machines users should end after writing their

programs, which are parallel processes communicate with each other. The lesser the restrictions put on programs writing, the closer to a user friendly easy to use parallel machine we are.

Why not have the configuration done by the computer? The next chapter describes a configurer for programs developed under the TDS and will run on the IMS B008.

# A Configurer for Programs Running Under the TDS2 on the IMS B008

#### 3-1 Introduction:

Attempts to design a transparent parallel machine and to make the already available ones transparent to the programmer are on going, and the need for that is growing as the number of such machines' users is becoming bigger and bigger.

The IMS B008 is made transparent to the users by the configurer described below. All hardware related work is carried out by the configurer.

#### 3-2 The environment:

The program was designed and tested on the IMS B008 under the TDS2 operating system, hosted by an IBM PC-AT.

# 3-3 Implementing message passing techniques on the IMS B008: 3-3-1 Through routing:

This technique is applied to a static topology network. A communication handling process (router) should be placed at each transputer either by adding the process to the program before the compilation or by designing a general routing process. This process is placed at each transputer. Before loading the network with any program code, the routing processes should be fed with the processes map and their links, this maybe done by another process running on the host. After that the network could be loaded with the executable code of the program.

The "neighbours identification" operation should be done at first by all the routers and each routing process should have complete information about which process is running on which transputer. Packet switching is used so each message should contain information about it's length, source identity, and destination. The router will accept any message on any link and then the message will be redirected to another transputer via the proper link according to the process map of the network.

#### 3-3-2 Channel multiplexing:

Similar to the Through-routing from the implementation point of view except that communication handling processes multiplex and demultiplex channels on the appropriate link. In this technique each process should know its neighbours only, unless both techniques, Through-routing and Channel multiplexing, are used together where it becomes necessary for the communication processes to know the process map of the whole network.

## 3-3-3 Dynamic links reconfiguration:

The IMS B008 is very similar to the T-Rack machine but on a small scale and with a very important difference which is the absence of the monitoring bus.

The monitoring bus plays the major role in the runtime link-switching in the T-Rack machine where it carries the processes requests for links switching to the controller where it is dealt with. Something else should play the role of the monitoring bus in the T-Rack machine

on the IMS B008. In the IMS B008 two links from each TRAM are connected to software controlled crossbar switch, and two are used to form the processor pipeline. To configure the network, the configuration data are sent on the configure input of the crossbar switch (IMS C004) via Link3 of the IMS T212 (refer to [29] for more details).

Each TRAM has two links connected to the crossbar switch (Link0 and Link3) except TRAMO where Link3 only is connected to the crossbar switch. By sacrificing one of these links of each TRAM, say Link0 and lets call it "configure link", this link will take the place of the monitoring bus of the T-Rack machine. The other link, Link3, of each TRAM is called "flexible link".

A process is allocated at each TRAM and called the "Organizer", its job will be described later, and another process running on the IMS T212 is also needed. This process acts like a telephone exchange operator. The process is called the "Controller".

Any process, no matter on which TRAM it is running, wanting to communicate with any process which is not running on a neighbour TRAM (processes running on neighbour TRAMs are accessible via Link1 and Link2), will send a message to the organizer of it's TRAM. The message contains information about the channel the process wants to communicate on and the direction (send or receive). In the case of receiving, the organizer keeps the channel number (channels are numbered to ease the searching task)

and the process is then blocked on a message from the organizer to resume. In the case of sending, the organizer sends a message to the controller (on T212) via the configure link requesting a linkage with the TRAM on which there is a process waiting to receive a message on the same channel.

scans all the configure The controller links continuously, and on receiving a message from organizer it sends searching messages to all the organizers looking for the process waiting to receive on the wanted channel (blocked on a message from the local organizer). If the process is found, the organizer on the TRAM on which the process waiting to receive was found, sends a message to the controller. Then the controller connects the flexible links of both TRAMs (if not already in use) and inform both organizers. Both organizers will then send a resume message to both processes and the communication take place in the conventional way. After the message is sent the sending process should inform the organizer that it finished and the organizer in it's turn informs the controller which disconnects the flexible links. The organizer process is identical on all TRAMs.

This design was tried on a simple example which contains four processes running on four TRAMs excluding the Host.

As we saw, this method requires some modifications on the processes to insert the handshaking between the processes and the organizers. Another problem is caused by the size of the controller process which should fit in the internal memory of the T212 because it has no external memory on the IMS B008. For these reasons and specially the first one this technique, dynamic link reconfiguring, was not used in the configurer.

The choice of which technique to use is left to the user. The configurer adds no new restrictions on programs to be configured (other) than the TDS restrictions.

# 3-4 The configurer:

#### 3-4-1 What is requisted from the configurer?

The configurer should be able to do the following:

- 1: Discover the target transputer network.

- 2: Discover the structure of the program (parallel processes).

- 3: Map and place the processes at the transputers and then place the channels at the links.

- 4: Configure the network (set the crossbar switch) to meet the required topology.

- 5: Produce the configured output as an acceptable input to the TDS compiler.

This version of the configurer is able to configure a program constructed from a number of processes less than or equal to the number of the available TRAMs on one IMS B008.

Each process could have a number of external channels

less than or equal to the number of the available links of the TRAM of both input and output. The configurer does not support the replicated PAR instruction in this version.

The program deals with one IMS B008, but with some modifications on some parts of it, the program would be able to deal with a number of cascaded IMS B008 boards.

## 3-4-2 The configurer general description:

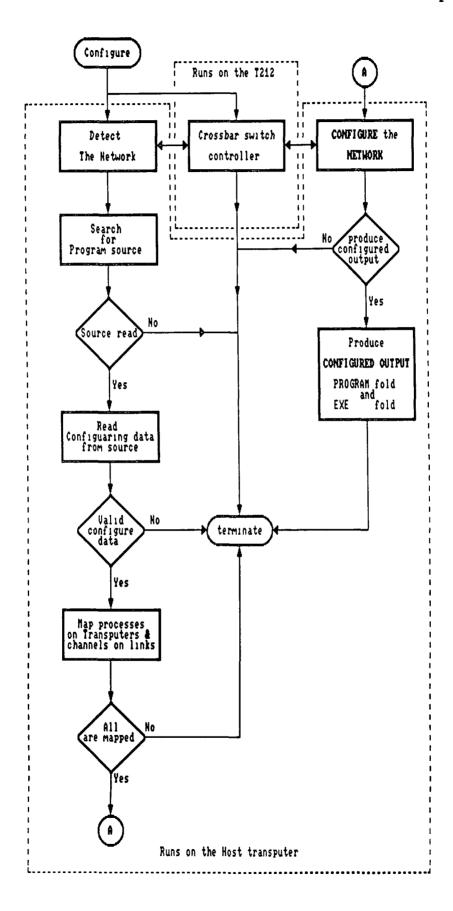

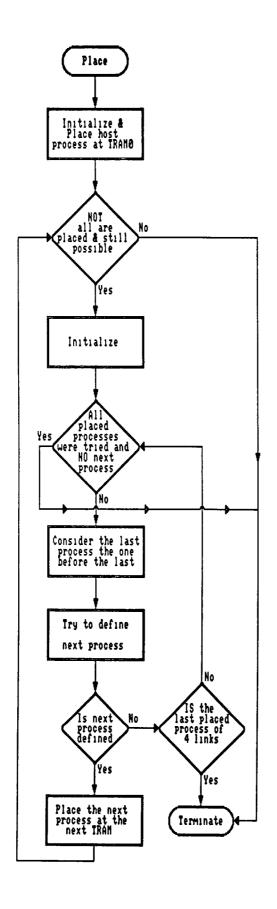

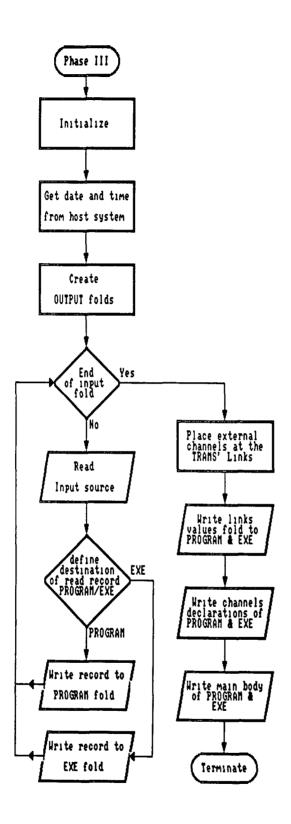

The program consists of two programs running in parallel. The first runs on TRAMO, and accesses the file system of the host computer (PC) and does the most of the job. The second runs on the IMS T212 (T2) controls the crossbar switch according to messages sent by the first, Figure (3-1) shows the major flowchart of the configurer.

The program starts with discovering the network to define the number of the installed TRAMs and the slots they occupied using the crossbar switch.

After that the configurer searches for the source of the input program (the program to be configured). If the source was found, the program reads the information required in the configuration process. This information in addition to the network information is then used to configure the program.

The configurer has three phases. In the first phase the configuring data is checked. If the data is valid, the next phase is performed through which the processes and their external channels are mapped on the network.

The network is then configured if the mapping was

Figure (3-1), Configurer general flowchart

successful. At this point the configurer program could be stopped if the configured output is not required (the configurer could be used to configure the network to run a pre-configured program). The configurer outputs have all the required configuring instructions added.

#### 3-4-3 The general algorithm:

The general algorithm is actually the summary of the previous paragraph.

Begin;

Detect the available TRAMs in the network.

Search the program source for processes.

FOR each found process

DO:

Get the process name.

Read the external channels information.

Check the channels declarations.

Check the number of the channels.

Check input and output channels matching.

Place the processes at the TRAMs.

Place the channels at the links.

Configure the network.

If required

Produce the configured output.

End;

## 3-4-4 The configurer requirements in the input program:

The input program should be a foldset of type PROGRAM and fulfil the following points:

- 1: A fold literally called "EXTERNAL CHANNELS

PROTOCOLS" which contains the declarations of all

protocols of the external channels.

- 2: Each process should be contained within an SC type foldset including the process which will run on the host.

- 3: Each process should contain a fold of type COMMENT and literally called "PROCESS <the process name> EXTERNAL CHANNELS" contains the declarations of the external channels of the process. This fold should preced the outer PROC statement of the process.

- 4: External channels should be declared, in the previous fold, using the same format of Occam, but with an addition which is the direction of the channel (input or output) using the format:

5: A fold literally called "CONFIGURE" contains a PLACED PAR instruction and the process's calling statements starting with the call statement of the host process (the process which has access to the system). The indentation of all the above folds should be zero relative to the PROGRAM fold (please refer to [27] for details about the folds types and indentation).

## 3-4-5 Special cases:

Sometimes the conditions of the configurer are fulfilled by the program but the configuration failed. If that happened it will be caused by the IMS B008 design as will be discussed.

Because of the hardwired links on the board some difficulties may be encountered while configuring a program and sometimes the required topology could not be implemented on the IMS B008.

# 3-4-5-1 Three non-neighbouring processes:

Figure (3-2-a) shows the required topology for a program, but because two links of each TRAM are hardwired the topology could not be implemented using this distribution of processes.

-- : Could not be implemented.

- : Possible links.

P : Process.

Figure (3-2)

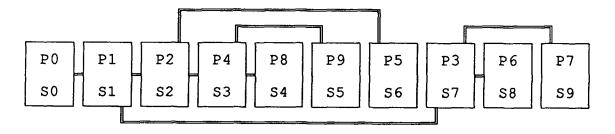

In Figure (3-2-b) P5 has been shifted to the end of the pipe to make use of the pipetail link through the edge connector. This solution is avoided by the program because of the complexity of it's implementation if cascaded boards are used. The program makes use of the pipetail link in the case where the number of the processes is equal to the number of the TRAMs number.

#### 3-4-5-2 All the processes need four links:

In the case where all the processes need four links and the number of the processes is **less** than the number of the TRAMs the topology is impossible on the IMS B008. A channel at least should be cancelled to make the topology implementable.

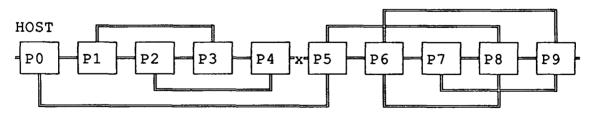

#### 3-4-5-3 No loading route from the root TRAM:

The loader sends all the code to the root TRAM to be distributed from there. In some cases like the one illustrated in Figure (3-3) the network could not be loaded and a loader failure message will be sent.

x : No channels are placed at these links.

Figure (3-3)

In such cases the configurer adds a channel and places it at the proper links to connect the loading

route, this channel is called "JUST.FOR.LOADING". That could happen once in the topology because the host TRAM has two links only.

#### 3-4-6 The configurer program:

The configurer design tries to minimize the work the the programmer has to do to configure a program. All the programmer has to do before configuring a program (apart from writing the processes) is to add the external channels declaration folds to each process in the way described above, and after the configuration is done he (she) has to make the output folds as foldsets, all the other requirements are TDS requirements.

#### 3-4-6-1 Network detection:

This task is carried out by the two parallel parts of the configurer.

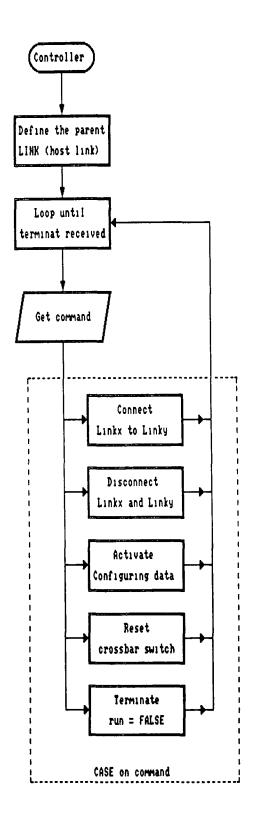

#### 3-4-6-1-1 The program on T2 (controller):

The program runs on the T2 controls the crossbar switch which is connected to the T2 via Link3 refer to Figure (2-1).

The controller receives messages from the program running on the host via Link1 and sends control data (configure data) to the crossbar switch via Link3.

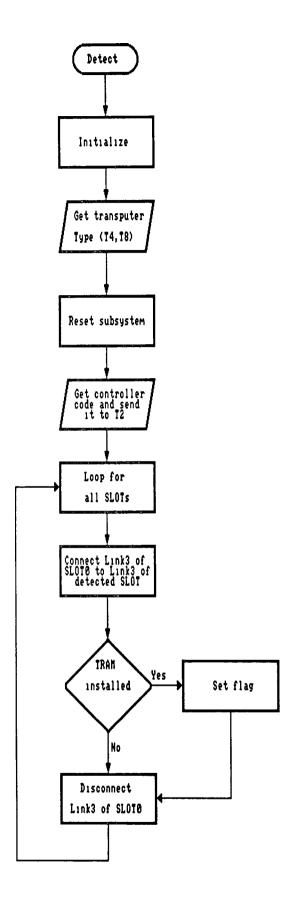

The controller could be easily modified to act as a worm program for applications where cascaded IMS B008s are used. Figure (3-4) is the general flowchart of the controller program.

At the beginning, the program on the host resets

Figure (3-4), Crossbar switch controller flowchart

Chapter 3

the subsystem which includes T2 and the crossbar switch, then it boots T2 with the controller code.

When the controller starts to run it waits for a number to be sent on any link, this link will be defined as the host link. After that the controller enters a loop which is the body of the program. This loop starts with receiving a command from the host and then a CASE construct on the command is executed.

No processing is done by the controller to keep it's size as small as possible to fit in the internal memory of T2. The program is needed twice for the configuration, firstly to discover the network, and secondly to set the crossbar switch (configure the network).

The program supports all the IMS C004 commands except the enquiry command, but only four commands are actually used:

- 1: Connect Link<x> to Link<y>.

- 2: Disconnect Link<x> and Link<y>.

- 3: Activate the configuring data.

- 4: Reset, all the outputs are disconnected.

- x,y are IMS C004 links numbers [14].

When the configuration is done, the host sends a terminating command to terminate the controller.

#### 3-4-6-1-2 Network detecting procedure (Host):

The configurer starts by calling this procedure "network" to define the number of the available TRAMs

Figure (3-5), Network detector flowchart

in the network and the slots they are occupying, Figure (3-5). The number of the TRAMs is kept in the variable "nTransputers" and the occupied slots are kept in the Boolein array "slots".

The procedure starts with initializations and then gets the transputer type from the user (T4 or T8). After that the subsystem (network) is reset and the code of the controller is got from a file called "C004byT2.cpr" by the local procedure "read.T2.code". Then T2 is booted with the controller code. If everything goes well, the length of the controller is sent to T2 to enable the controller to identify the host link on which the communication will take place. A trial command is then sent to the controller to assure that every thing there is OK, the local procedure "is.loaded" is used for that. Then the network discovering process starts with resetting the crossbar switch to cancel any previous connections.

The slots are then scanned by connecting Link3 of the host (slot0) to Link3 of each slot in turn, by sending the appropriate commands and data to the controller. A poke operation trying to write anything in the internal memory of the transputer at a certain address is then performed followed by a peek operation to read the contents of the same address. If the read value is the same written value a TRAM is

Chapter 3

known to be installed at that slot, "nTransputers" is incremented and the corresponding item of "slots" is set to TRUE. After that the links are disconnected (Link3 of slot0 and Link3 of the tested slot) and a connection is done with Link3 of the next slot and so on until the whole slots are tested. Then the number of TRAMs found is displayed on the screen and the network discovering phase is finished.

#### 3-4-6-2 Searching for the program source fold:

The program looks for the source in the first fold of the bundle which should be a foldset of type PROGRAM. Procedure "search.for.source" is used for that.

At first the procedure gets the number of the folds in the bundle to check if there is any or not. If the number is one or more the attributes of the fold are read and checked where the acceptable attributes are:

TYPE : foldset or voidset.

CONTENT : fc.occam2.prg.

If the attributes are accepted then the attributes of the first fold are read to check it's contents which should be "fc.source.text". If it is, then "prog.source.found" is set to TRUE and the search process succeeded, otherwise the procedure report on the screen with an error message.

# 3-4-6-3 Reading the program source:

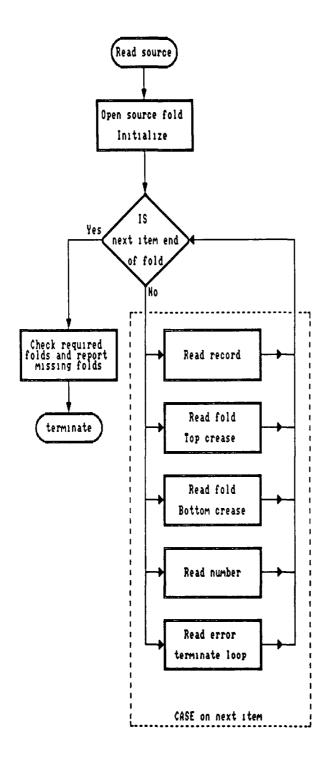

The program requires special information folds to

Figure (3-6), Input program source read

be added by the programmer to the program in order to decrease the needed amount of processing. The program only reads the folds which contain the information necessary for configuring, which is found in the added external channels folds and the configure fold. Missed folds, if any, are reported and the programs stops.

Procedure "source.read" is used to read the required information from the source of the program to be configured, Figure (3-6).

The procedure tries at first to open the first fold for reading, if it failed an error message is sent to screen and the program stops. If it passed, some initializations are done and the program enters the reading loop contains a CASE construct which forms the core of the procedure. The reading loop ends on reaching the end of the opened fold, or an error occurred during the reading. Using some library procedures for folds reading, the program source is read. Special processing is done when a "top crease" or a "bottom crease" and if a record is the next item to be read.

On reaching a "top crease" the comment of the fold is read and checked to see whether this fold contains configuration data or not.

If the fold is an external channels fold, the process name of which the external channels fold was found is obtained from the comment using the local

procedure "get.proc.name" which keeps the process name in the byte array "proc.names" and the length of the name in bytes in the integer array "proc.names.lens". The Boolean "comment.read" is set to TRUE to indicate to "read.record" procedure to put the contents of the current fold into the buffer. The current value of the buffer pointer is saved in the integer array "ext.chn.ptr" to indicate the offset of the start of the external channels information of the current process in the buffer.

If the fold is the configure fold (the fold contains the processes calling statements), the Boolean "configure.read" is set to TRUE to indicate to "read.record" procedure to put the contents of the current fold into the buffer. The current value of the buffer pointer is saved in the integer array "ext.chn.ptr" to indicate the offset of the start of the calling statements in the buffer.

If the fold is the external channels protocols declaring fold, the boolean "ext.protocol.read" is set to TRUE to indicate the availability of the fold.

On reaching a "bottom crease" a check is done to find out if the end of a configuring data fold is reached or not depending on the depth of the fold, which is increased on entering a fold and decreased on exiting. If an end is reached the appropriate boolean is set to FALSE and the current value of the buffer

pointer is saved in the integer array "ext.chn.ptr" to indicate the offset of the end of the external channels information of the current process or the calling statements. If the end was of an external channels fold the processes counter "sc.number" is incremented.

The procedure "read.record" is used to read record items from the source, but it adds the record to the buffer only if "comment.read" or "configure.read" is TRUE and the record itself is not a comment record.

The procedure "source.read" will report any missed configuring fold. Any process does not have an external channels fold will not be regarded by the configurer.

# 3-4-6-4 Processes and channels mapping and placing:

The configurer divided this job into three tasks, each task is carried out by a special procedure called Phase.

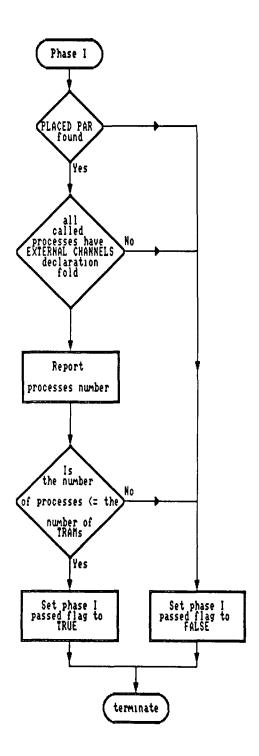

#### 3-4-6-4-1 Phase I:

After the available configuration data is read from the program source, the configurer enters a new phase which includes checking major points in the read data. These points are checked by the procedure "phase.I" which itself is consisted of a number of procedures each checks a different point, Figure (3-7).

The points checked during this phase are:

- 1: "PLACED PAR" instruction.

- 2: For each called process there is an

Figure (3-7)

external channels fold which holds the same process name.

3: The number of the called processes with the number of the available TRAMs.

The procedure starts with checking the number of the SC type folds found during the reading operation as there is no point to go on if there is nothing to place. After that the procedure "CONFIGURE.inst" is used to look for the "PLACED PAR" instruction in the data read from the fold called "CONFIGURE". If the instruction was found (step 1) the names of the called processes (to be placed) are obtained from the calling statements by the procedure "get.called.sc.name" and then compared to previously got while reading the source by procedure "match.sc.name". The names matching operation is done for each calling statement in turn. During the names matching the number of the called processes is updated every time a called process passed the check, this number is then compared with the number of the available TRAMs, and the order in which the processes are called is also saved. Error messages are issued on each error to help the user to identify the error. These error messages are specific as possible. Phase one according to the configurer is now over and data required for phase two to be executed is available (but not checked).

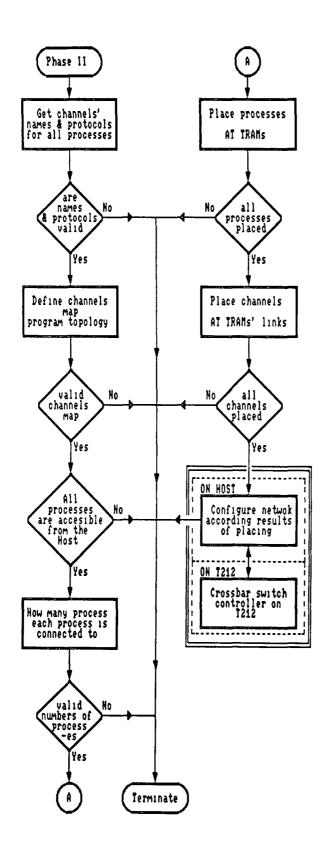

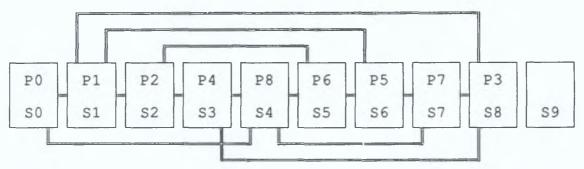

#### 3-4-6-4-2 Phase II:

This phase is the major phase in the program and most of the job is done here, Figure (3-8). At first the channels definition information of each process are got from the read data, then the channels map of the processes is produced, then the possibility of accessing all the processes from the host is checked. After that the processes map is produced to be used in the next step which is placing the processes followed by mapping the channels on the TRAMs links and the last step is configuring the network according to the results of the previous two steps.

Phase two starts with getting the channels' names, protocols, and directions for each process from the external channels data of that process. The input channels and the output channels are separated and counted for checking. A process could have up to four input and four output channels (except the host process can have two of each) and should have one of each at least (what is the point of a parallel process without input or output?). The procedure "channels.names" does all the checking channels in addition to some syntax checking on the channels declaration statements.

After that the procedure "10.or.1.or.0" is called to produce the channels map. The procedure tries to find the match input channel for each output channel,

Figure (3-8)

and checks that the channels are not already used to match different channels, either the input or the output channel. If the output channel is already used for another input channel, the procedure reports a duplicated input channel and a duplicated output channel.

The last check before the channel is mapped or put in the channels map is that the channel is not connected to the same process it belongs to (I could not find a reason to connect two links of the same TRAM, together).

After passing all the previous checks the channel is mapped and after the procedure "io.or.i.or.o" finishes, the channels map is ready unless there is a mistake of some kind in the external channels data.

Figure (3-9)

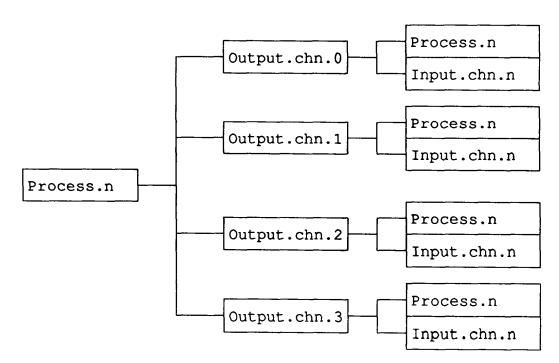

The channels map "chn.map" is a three dimensional array and could be seen in the way illustrated in Figure (3-9) which shows the part of the array of process number <n>. The output and the input channels are numbered within the processes from 0-3.

Another three dimensional array is also used to keep the destinations (for the output channels) and the sources (for the input channels) for each process. The array called "connected.to" is used, the array structure is similar to the one of the array "chan.map" but each process has eight elements (the first four are used for the output channels and the last four are used for the input channels of the process) instead of the four in "chan.map". Figure (3-10) shows one element of the array which describes the channels of process <n>.

Depending on the channels map, the procedure "loading.route" detects inaccessible processes (processes which could not be accessed from the host TRAM). These processes's channels will pass all the previous checks without being discovered that they are isolated. The procedure starts with the host process and marks it as an accessible process, then depending on the channels map, it marks each process connected to the host process (by any output) as an accessible process.

Figure (3-10)

After that the processes are scanned and all the processes connected to a marked process are marked as well. At the end a check is done to see if there is any unmarked process which is, if found, reported.

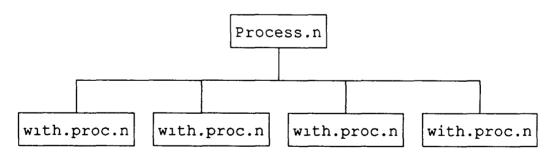

The next step which is the last step before placing the processes is producing the channels map and defining the number of processes each process is connected to and the number of links it needs.

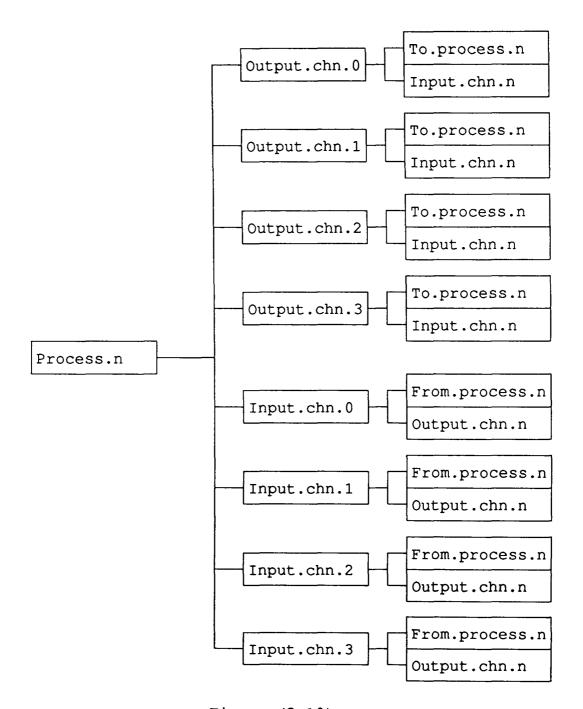

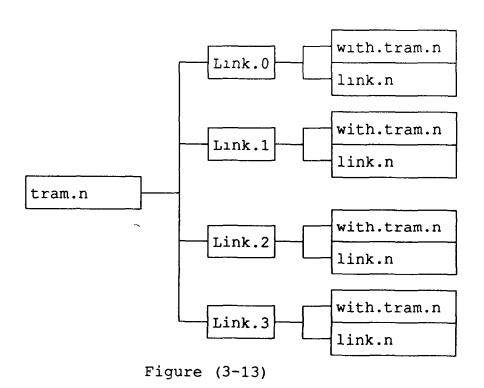

The procedure "num.proc.conn.to" is now executed to produce the processes map "proc.proc.map" which is a two dimensional array and during that another two dimensional array "processes.n.links.n" is used to keep the number of the different processes connected to each process and the number of links it uses. An element of the processes map array (for one process) can be seen as in Figure (3-11) where (-1) is the initial value of all "with.proc.n".

Figure (3-11)

The procedure uses the array "connected.to" created with the channels map. At first the outputs of the process are scanned, and for each used output all the inputs (of the same process) are scanned trying to find an input from the same process to which the output is connected. By this means the input and the output of each link between two

# with Compliments

Professor M. Elizabeth C. Hull, B.Sc., Ph.D., C.Eng., F.B.C.S. Head of Department of Computing Science

processes will be used if possible. If an input was found, both the output and the input are marked (cancelled from the array) and a link is reserved. The array "link.with.proc" is used to keep the number of the required links between all the processes. The structure of "link.with.proc" is identical to structure of "chan.map" replacing the outputs with the links. After all the outputs of the process are scanned, the inputs are scanned looking for any input left. A link is reserved in the three possible cases, input and output, output only, or input only. Each time a link is needed (for input, output, or both) the processes number is updated (incremented) if this is the first link with this process. After the channels of a process are scanned, the procedure checks the number of the different processes to which the current process is connected, and the number of links required. If any of these numbers exceeds the allowed number an error message is issued.

The data required for placing the processes are now ready and correct and there should be no problem in placing the processes unless a special case (like the one mentioned above) occurred.

#### Processes placing algorithm:

The processes placing algorithm, which is the core of the configurer, was designed to suit the IMS B008 design and the extensibility of the

system.

In a fully dynamic (reconfigurable) topology system where all the links are flexible, the needed processes placing algorithm is simple. The complexity of the algorithm grows as the restrictions on processes placing grow. As described earlier, any topology to be implemented on the IMS B008 should consider the hardwired links between the TRAMs.

The algorithm is relatively simple and could be used for placing a large number of processes at a similar number of TRAMs. The processes are placed one after another to form a chain "necklace" of processes similar to the processors chain on the board(s). Starting with the Host process (the process which access the system) placed on the Host TRAM (TRAMO on the first IMS BOO8, which has two free links only) and then the other processes are placed on the other TRAMs which have four free links each.

The algorithm depends on the number of links needed by each process. Processes needing larger number of links are placed at first in the proper place to make the processes chain as long as possible.

The terms "last process" indicates the last placed process, "next process" indicates the next

process to be placed, and "N links process" indicates a process which uses N links. At the beginning the host process is the last process. The next process is chosen from the processes connected to the last process according to the number of links it needs and to the position of the TRAM, at which it will be placed, in the processor chain.

A cut in the processes chain could happen if two processes are neighbours but they have no connections between them, in this case the next process could not be a four links process. A cut in the processes chain is discovered by checking the processes connected to the last process, if all of them are placed, then there is a cut in the processor chain.