# **Switching Techniques for Broadband ISDN**

a thesis presented for the award of

**Doctor of Philosophy**

by

Martin Collier, BEng, MEng, School of Electronic Engineering, Dublin City University.

Supervisor: Dr. Tommy Curran.

July, 1993.

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of PhD in Electronic Engineering is entirely my own work and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

Signed: Nortin Collier Date: 6/33

## **Acknowledgements**

I hereby acknowledge the invaluable advice and assistance of my supervisor, Dr. Tommy Curran, during the course of this research. I also thank Prof. Charles McCorkell for his continual support.

Mention is also due to the many people in the School of Electronic Engineering who provided help along the way, and in particular, to Karen, who typed much of Chapters Four and Five, Dave, Peter and John, who sorted out many difficulties with equipment, and to Aengus, who endured three years of sharing an office with a member of the telecommunications research group.

Lastly, I would like to thank my family, for their constant encouragement.

## **Table of Contents**

| 1. SWITCHING IN BROADBAND ISDN                            | 1  |

|-----------------------------------------------------------|----|

|                                                           |    |

|                                                           |    |

| 1.1 Introduction                                          |    |

| 1.2 Objectives                                            |    |

| 1.3 Summary                                               | 3  |

|                                                           |    |

| References                                                | 4  |

|                                                           |    |

|                                                           |    |

|                                                           |    |

| 2. BROADBAND SWITCH ARCHITECTURES                         | 6  |

|                                                           |    |

|                                                           | _  |

| 2.1 Introduction.                                         |    |

| 2.2 Delta networks.                                       |    |

| 2.3 Self-routing networks based on 2x2 switches.          |    |

| 2.3.1 Principles of self-routing networks                 |    |

| 2.3.2 A notation to describe self-routing networks.       |    |

| 2.3.3 Some link permutations.                             |    |

| 2.3.3.1 The perfect shuffle.                              |    |

| 2.3.3.2 The inverse perfect shuffle                       |    |

| 2.3.3.3 The swap permutation.                             |    |

| 2.3.3.3 The bit-reversal permutation                      |    |

| 2.3.4 Network definitions.                                |    |

| 2.3.4.1 Baseline network.                                 | 14 |

| 2.3.4.2 Omega network                                     | 14 |

| 2,3.4.3 Indirect binary n-cube                            | 16 |

| 2.3.4.4 The GL-banyan                                     | 16 |

| 2.3.4.5 The P-banyan                                      |    |

| 2,3.4.6 The S-banyan,                                     |    |

| 2.3.5 Inverse networks                                    | 19 |

| 2.3.6 Topological equivalence.                            | 21 |

| 2.4 Sorting networks.                                     | 22 |

| 2.4.1 Principles of sorting networks                      |    |

| 2.4.2 The Batcher sorter.                                 | 22 |

| 2.5 Switch architectures based on the banyan network      | 24 |

| 2.5.1 Banyan switches.                                    | 24 |

| 2.5.2 Switches with multiple paths.                       | 26 |

| 2.5.3 Switches with multiple banyans.                     |    |

| 2.5.4 Concluding remarks concerning banyan-based switches |    |

| 2.6 Switch architectures based on sort-banyan networks.   |    |

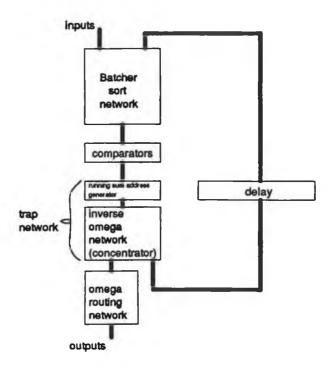

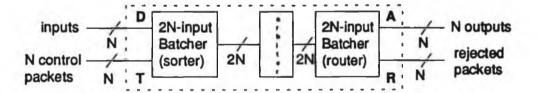

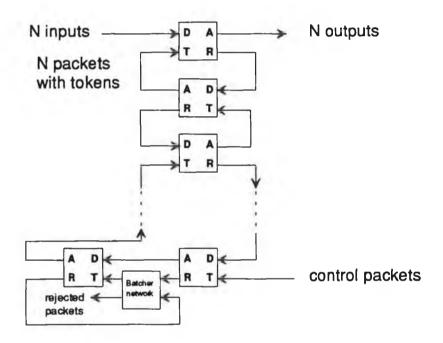

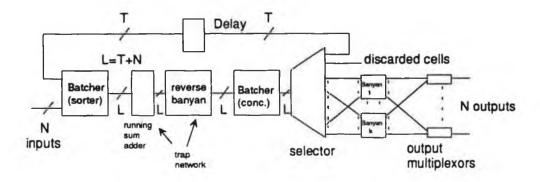

| 2.6.1 The Starlite switch                                 |    |

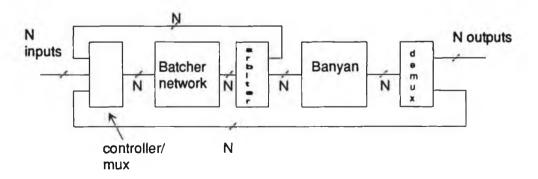

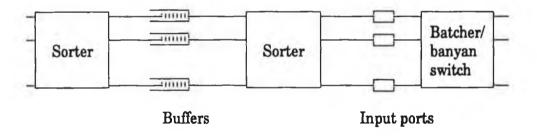

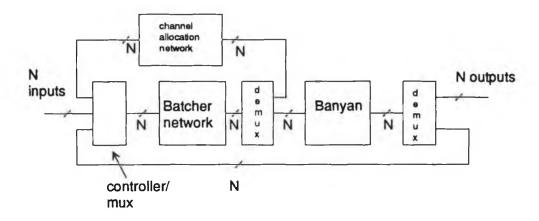

| 2.6.2 Switching with sorters.                             |    |

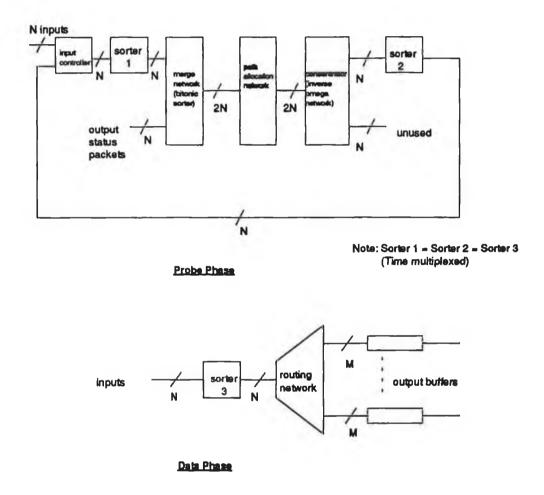

| 2.6.3 Input-buffered switches.                            |    |

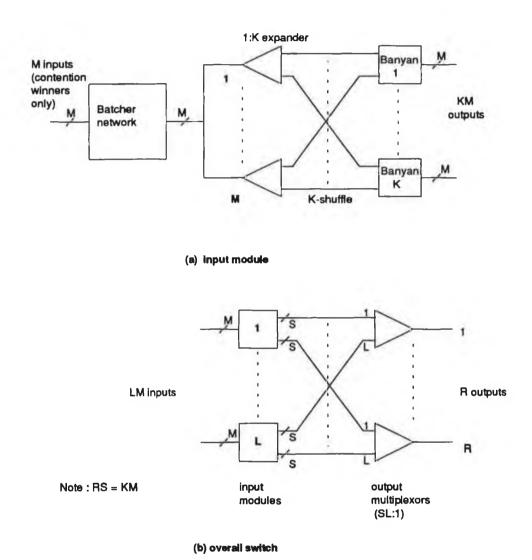

| 2.6.4 Multiple servers and channel grouping.              | 41 |

| 2.6.5 Scaling difficulties in sort-banyan switches.       |    |

| 2.6.6 Conclusions regarding sort-banyan switches.         |    |

| 2.7 Memory-hased and shared-medium switch architectures   |    |

| 2.8 Other output-buffered switch architectures.  2.9 Remarks concerning output-buffered switches.  2.10 Multi-stage switches. | 55  |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| References                                                                                                                    | 61  |

| 3. PERFORMANCE EVALUATION OF ATM SWITCHES                                                                                     | 65  |

| 3.1 Introduction.                                                                                                             | 65  |

| 3.2 Performance of internally blocking switches.                                                                              |     |

| 3.3 Classification of internally non-blocking switches.                                                                       | 67  |

| 3.4 Output queuing switches                                                                                                   | 68  |

| 3.4.1 Homogeneous arrivals.                                                                                                   |     |

| 3.4.2 Correlated arrivals - Markov-modulated sources.                                                                         |     |

| 3.4.3 Non-Markovian models.                                                                                                   |     |

| 3.4.4 Mixing of traffic types.                                                                                                |     |

| 3.4.5 Shared-buffer switches                                                                                                  |     |

| 3.5 Throughput analysis of input-queuing switches.                                                                            |     |

| 3.5.1 Homogeneous traffic.                                                                                                    |     |

| 3.5.2 Geometric burst lengths                                                                                                 |     |

| 3.6 Queuing analysis of input-queuing switches                                                                                |     |

| 3.6.1 Homogeneous traffic.                                                                                                    |     |

| 3.6.2 Non-uniform traffic.                                                                                                    |     |

| 3.7 Fairness in Batcher-banyan switches                                                                                       |     |

| 3.7.1 Implementing fair access in Batcher-banyan switches                                                                     |     |

| 3.7.2 Homogeneous traffic                                                                                                     | 89  |

| 3.7.3 Bursty Traffic.                                                                                                         | 93  |

| References                                                                                                                    | 104 |

| 4. EQUIVALENCE AND BLOCKING IN ATM SWITCHES                                                                                   | 107 |

| 4.1 Equivalence in binary self-routing networks.                                                                              | 107 |

| 4.1.1 Establishing topological equivalence                                                                                    |     |

| 4.1.2 The equivalence between the S-banyan and the omega network                                                              | 113 |

| 4.1.3 The equivalence between the S-banyan and the baseline network                                                           |     |

| 4.1.4 The equivalence between the S-banyan and the inverse S-banyan                                                           |     |

| 4.1.5 Exact equivalence of the baseline and inverse baseline networks                                                         |     |

| 4.1.6 The general case.                                                                                                       | 121 |

| 4.2 Local addresses in binary self-routing networks.                                                                          |     |

| 4.2.1 Definition of local address.                                                                                            |     |

| 4.2.2 Dependence on source address.                                                                                           |     |

| 4.2.3 Dependence of local address on destination address.                                                                     |     |

| 4.2.4 Local address as a function of both source and destination addresses                                                    |     |

| 4.2.5 The routing strategy in sen-routing networks.  4.2.6 Input equivalence and the $g(k)$ function.                         |     |

| 4.3. Blocking properties of binary self-routing networks.                                                                     |     |

| 4.3.1 Bernabei's condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 4.3.2 Collisions as a function of source address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| 4.3.3 Collisions as a function of the destination address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |

| 4.3.4 Calculation of the distance function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| 4.3.5 Blocking and equivalence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| 4.4 Non-blocking conditions for the S-banyan and its inverse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

| 4.4.1 The S-banyan.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |

| 4.4.2 The inverse S-banyan.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| 4.5 Synthesis of binary self-routing networks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| 4.5.1 An example of network synthesis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

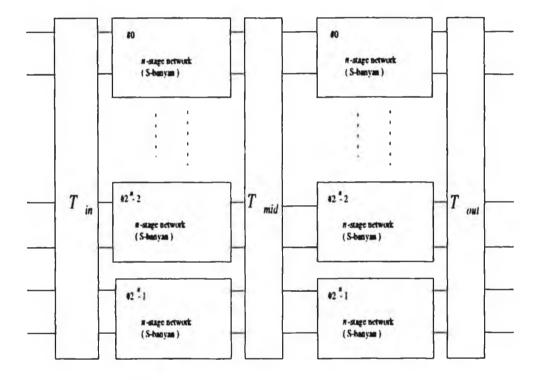

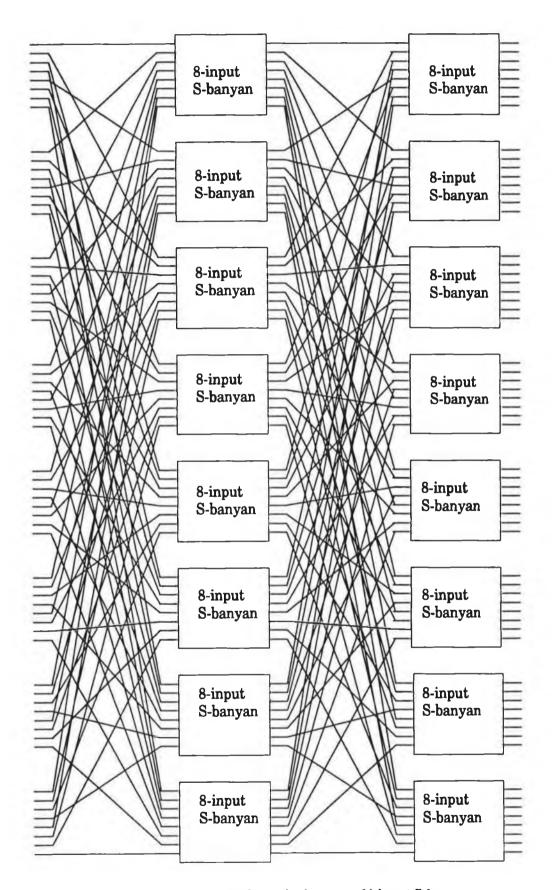

| 4.5.2 Constructing a $2^{2n}$ -input S-banyan from $2^{n+1}$ $2^n$ -input S-banyans                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 147                                           |

| 4.6 The re-routing banyan.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |

| 4.6.1 Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| 4.6.2 Routing in the rerouting banyan.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| 4.6.3 Equivalence in the B <sub>r</sub> network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

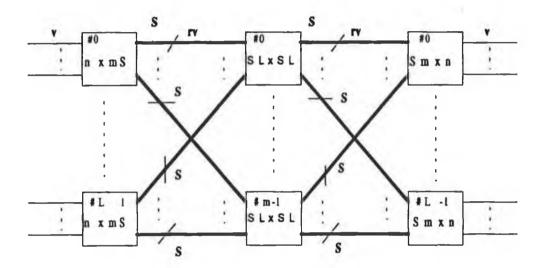

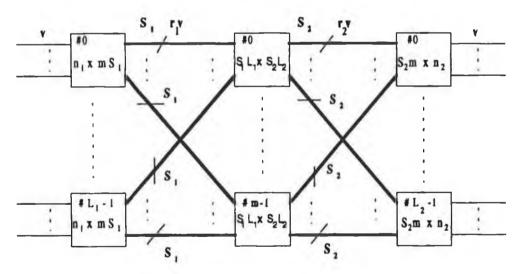

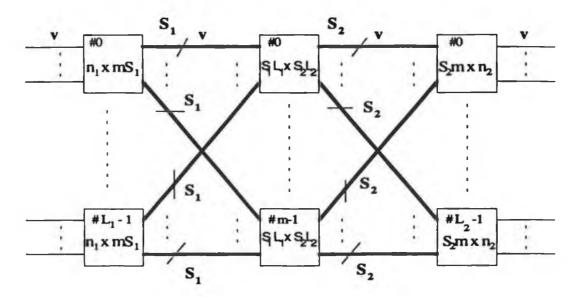

| 4.7. Blocking properties of three-stage networks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| 4.7.1. Existing conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| 4.7.2 A new non-blocking condition for circuit-switched networks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| 4.7.3 Special cases of the non-blocking condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| 4.7.4 Asymmetric switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103                                           |

| 4.7.5 Non-blocking conditions for ATM networks with call-level path allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| 4.7.6 The non-blocking condition for a three-stage ATM switch with cell-level                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

| path allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 166                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10/                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 150                                           |

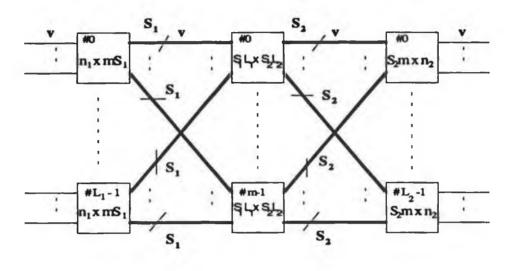

| 5. A NEW THREE-STAGE BROADBAND SWITCH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 168                                           |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168                                           |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169                                    |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>169                             |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>169<br>170                      |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>169<br>170                      |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>170<br>171                      |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>170<br>171<br>173               |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>170<br>171<br>173<br>178        |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>170<br>171<br>173<br>178<br>178 |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168<br>169<br>170<br>171<br>173<br>178<br>178 |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170171173178178                         |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170171173178178178                      |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170171173178178179183                   |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169171173178178179183189                   |

| 5.1 Introduction 5.2 An algorithm for path allocation at cell level 5.2.1 The objectives of a path allocation algorithm. 5.2.2 Existing algorithms for cell-level path allocation. 5.2.3 A new algorithm for path allocation. 5.2.4 Synchronisation of the algorithm. 5.2.5 Modular growth of the switch. 5.3 Implementation of the processing element. 5.3.1 Design requirements. 5.3.2 A bit-serial implementation. 5.3.3 A faster bit-serial implementation. 5.3.4 Bit-parallel implementations. 5.3.5 Processor implementation in CMOS. | 168169170173178178179183189                   |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170173178178179183189191                |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170173178178179183189191                |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170171178178179183189190191191          |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169171173178178179183189191191             |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169171173178178179183190191191191          |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170173178178179183190191191192192       |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 168169170173178178179183190191191192196196    |

| 5.6.1 Advantages of eliminating control packets.2125.6.2 Request counting without control packets.2125.6.3 Elimination of control packets in routing tag assignment.2205.6.4 Hardware counts associated with synthetic control packets.2235.7 Choice of switch modules.2255.7.1 Input stage modules.2255.7.2 Intermediate stage modules.2265.7.3 Output stage modules.2265.8 Fault tolerance.2275.9 Implementation of loss priority.2285.10 Implementation of input queuing.2305.11 A design example.231 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

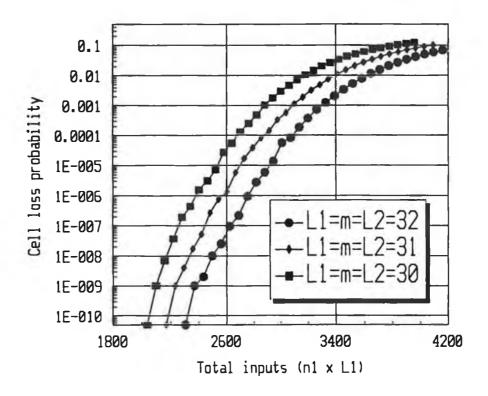

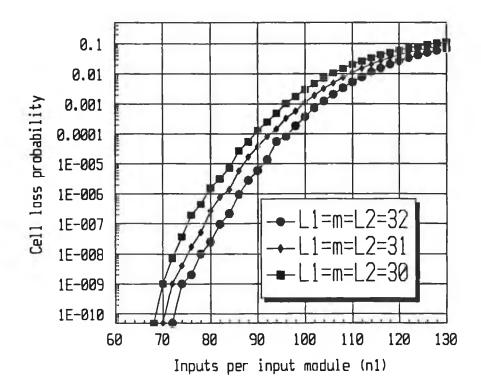

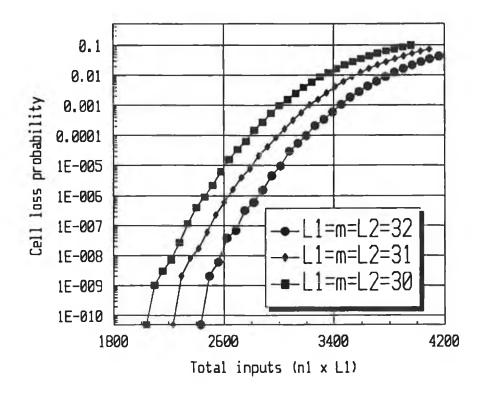

| 6. PERFORMANCE OF THE THREE-STAGE ATM SWITCH237                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7. CONCLUSIONS254                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| APPENDIX A: Discrete-time queuing models                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PUBLICATIONS arising from this research                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GLOSSARY of acronyms used in the text                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### **Abstract**

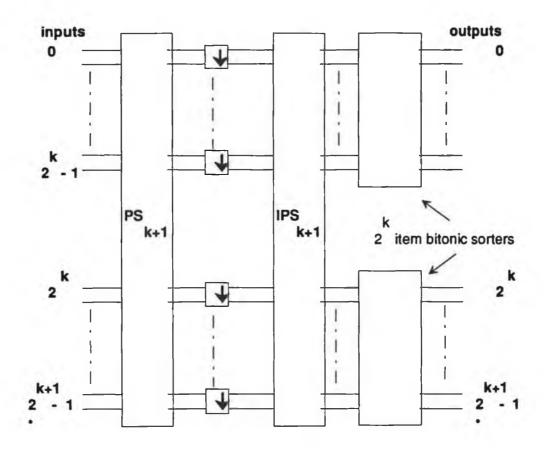

The properties of switching techniques suitable for use in broadband networks have been investigated. Methods for evaluating the performance of such switches have been reviewed. A notation has been introduced to describe a class of binary self-routing networks. Hence a technique has been developed for determining the nature of the equivalence between two networks drawn from this class. The necessary and sufficient condition for two packets not to collide in a binary self-routing network has been obtained. This has been used to prove the non-blocking property of the Batcher-banyan switch. A condition for a three-stage network with channel grouping and link speed-up to be nonblocking has been obtained, of which previous conditions are special cases.

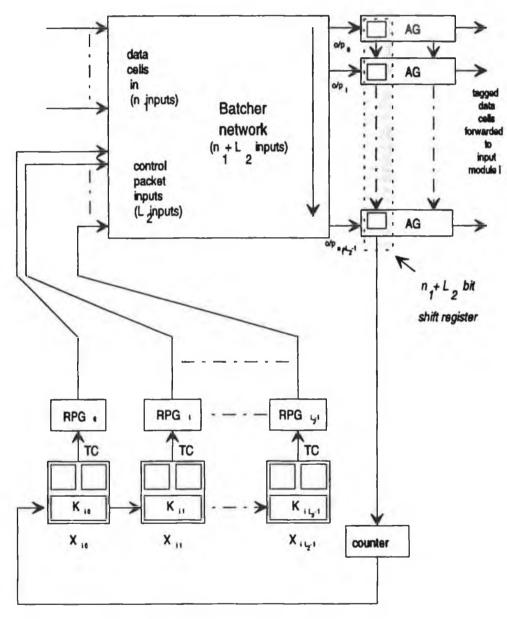

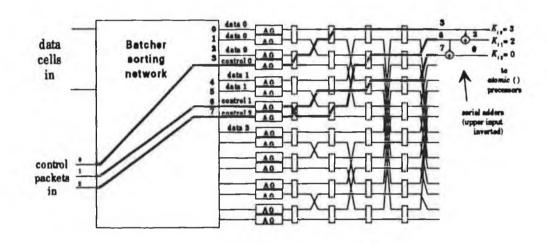

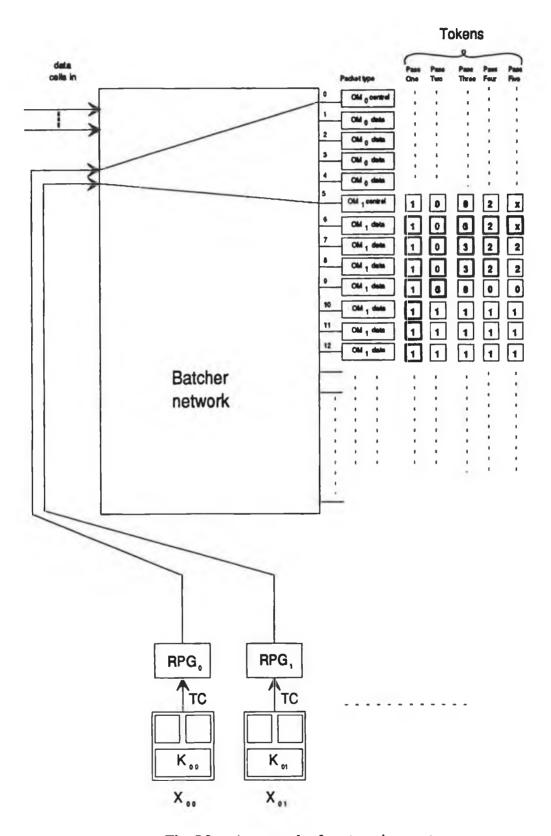

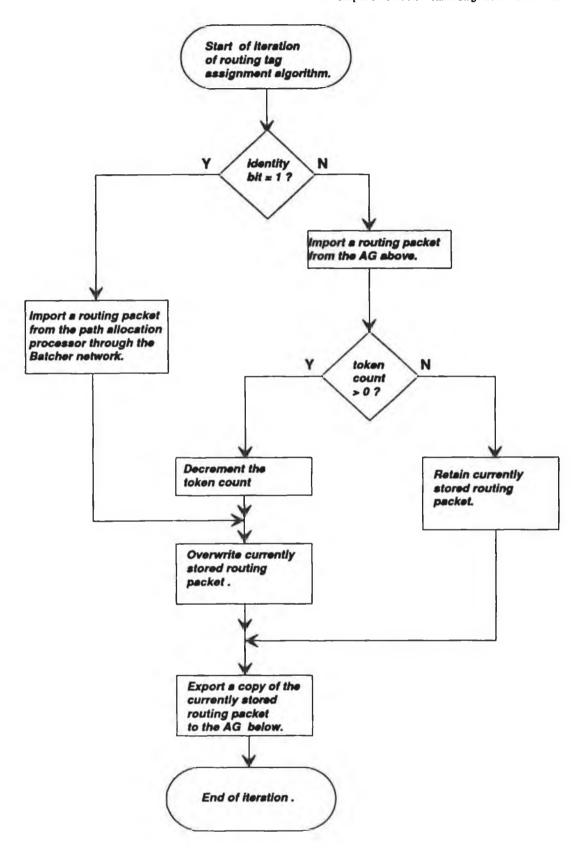

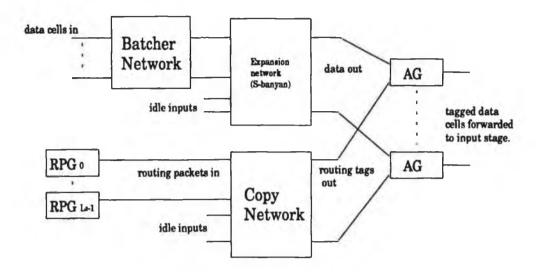

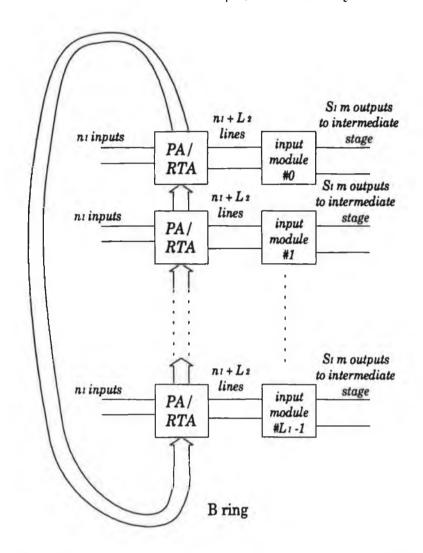

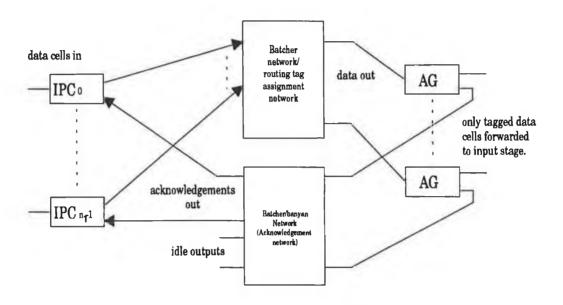

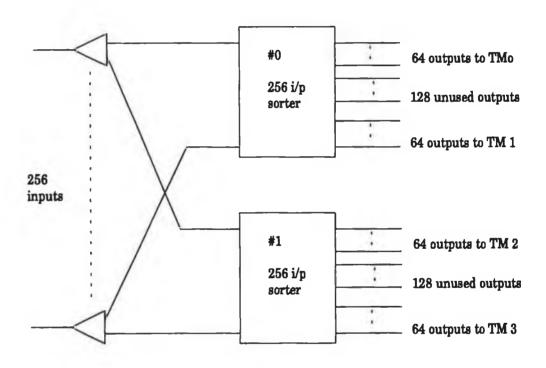

A new three-stage switch architecture has been proposed, based upon a novel cell-level algorithm for path allocation in the intermediate stage of the switch. The algorithm is suited to hardware implementation using parallelism to achieve a very short execution time. An array of processors is required to implement the algorithm. The processor has been shown to be of simple design. It must be initialised with a count representing the number of cells requesting a given output module. A fast method has been described for performing the request counting using a non-blocking binary self-routing network. Hardware is also required to forward routing tags from the processors to the appropriate data cells, when they have been allocated a path through the intermediate stage. A method of distributing these routing tags by means of a non-blocking copy network has been presented.

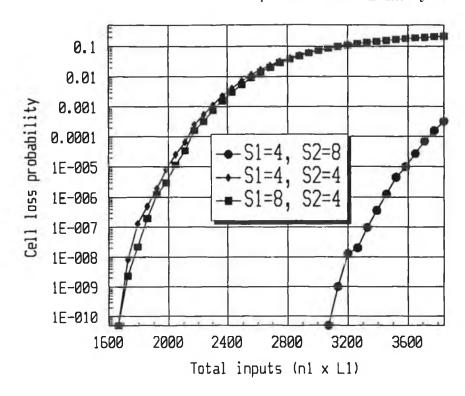

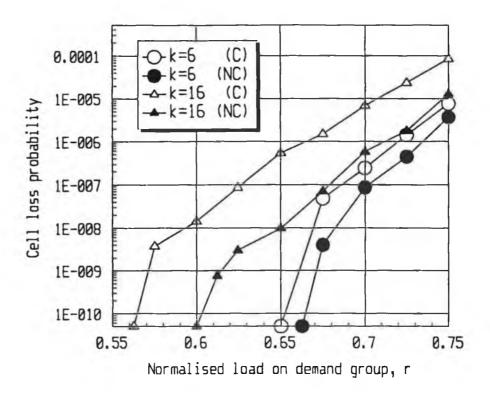

The performance of the new path allocation algorithm has been determined by simulation. The rate of cell loss can increase substantially in a three-stage switch when the output modules are non-uniformly loaded. It has been shown that the appropriate use of channel grouping in the intermediate stage of the switch can reduce the effect of non-uniform loading on performance.

#### 1. SWITCHING IN BROADBAND ISDN.

#### 1.1 Introduction.

Recent advances in fibre optic communications make a broadband public network, which will replace or augment the existing public switched telephone network, a practical goal. The deployment of narrowband ISDN (Integrated Services Digital Network) is a step towards achieving this goal, allowing as it does the integration of voice and data signals [1].

The evolution to a broadband network will be accompanied by the introduction of new services, which may include digital HDTV (high definition television), video conferencing of high quality, multimedia communications, and distributed computing [2]. The precise mix of services which will be provided is still uncertain.

It follows that a key requirement of broadband ISDN is that it must support the flexible provision of services. This means, in particular, that access must be supported at multiple bit rates. An obvious method of providing a choice of bit rate is to employ packet switching, whereby the principle of demand multiplexing allows variable rate access. However, existing packet switching techniques are unsuitable for broadband networks.

The alternative approach is to use multi-rate circuit switching. This has the advantage that the quality of service can be more readily assured, since the bandwidth available to a connection is fixed, and is not subject to statistical fluctuations.

The respective merits of two approaches to broadband communications have been studied by the CCITT. These were STM (synchronous transfer mode, which corresponds to multi-rate circuit switching, and ATM (asynchronous transfer mode, which is equivalent to fast packet switching). ATM was chosen as the method for the transport of data in broadband ISDN [3,4]. The key features of ATM are:

- demand multiplexing. Data is transmitted in the form of fixed-length packets called cells. Each cell is 53 octets (i.e., 424 bits) long. Cells queue to gain access to network resources.

- high bit rate. Cells are transmitted at a bit rate of 155.52 Mb/s. Each cell occupies a time slot of approx.  $2.5 \mu s$  duration.

- connection-oriented operation. Routing is based on a virtual channel identifier (VCI) or virtual path identifier (VPI). When the connection is established, a virtual channel must be set up through the network from source to

destination, and a unique virtual channel identifier must be associated with that virtual channel on every link traversed by the data. Alternatively, the connection can be routed through a pre-allocated bundle of virtual channels known as a virtual path.

The 53 octet cell contains 48 octets of data and a 5 octet header. The structure of the cell header is shown in Fig. 1.1. It contains the virtual path identifier and virtual channel identifier, a cell loss priority (CLP) bit and error control bits. Also included in the header are bits for generic flow control (which are included only at the user-network interface) and a two-bit payload type field. A review of the CCITT recommendations as of August 1991 was given in [5].

| bit     | 7   | 6       | 5 | 4  | 3    | 2     | 1   | 0 |  |

|---------|-----|---------|---|----|------|-------|-----|---|--|

| octet 0 |     | GFC/VPI |   |    |      | VPI   |     |   |  |

| octet 1 | VPI |         |   |    | VCI  |       |     |   |  |

| octet 2 | VCI |         |   |    | VCI  |       |     |   |  |

| octet 3 | VCI |         |   | PT | Rese | erved | CLP |   |  |

| octet 4 | HEC |         |   |    |      |       |     |   |  |

GFC: Generic flow control VPI: Virtual path identifier VCI: Virtual channel identifier

PT: Payload type

HEC: Header error control CLP: Cell loss priority

Fig. 1.1: The ATM cell header.

The combination of high bit rates and demand multiplexing means that special techniques are required in the design of ATM switches. Some connections may require a cell loss probability below 10<sup>-10</sup> [6]. This will require stringent control of cell loss within the switch.

## 1.2 Objectives.

The objectives of this research are as follows:

- · to review techniques for broadband switching;

- to investigate the topologies of binary self-routing networks;

- to determine conditions for the avoidance of blocking in three-stage and multi-stage networks;

- to evaluate numerical and analytical techniques for predicting the performance of ATM switches;

- to design an ATM switch of high throughput, and low loss, capable of expansion to several thousand inputs and outputs.

## 1.3 Summary.

Chapter Two contains a survey of switch designs which have been proposed for broadband switching. These designs are classified according to the basic principles of their operation, such as the use of multi-stage networks, or the use of broadcasts on a shared medium. These switch designs are critically compared, and recommendations are made concerning their suitability for use in ATM networks. A notation is introduced in Chapter Two for the compact description of binary self-routing networks. This facilitates the comparison of various designs of binary self-routing network, for which purpose the notation will be used in Chapter Four.

Chapter Three contains a description of techniques from discrete-time queuing theory and the theory of Markov chains which have been applied to model ATM switches. Methods for the analysis of multi-stage switches, input-buffered switches and output-buffered switches are discussed. Methods are also considered which allow variants on these switch types, such as shared-buffer switches, and switches with both input and output buffers, to be analysed. Models of source traffic used include homogeneous (Bernoulli) traffic, and bursty traffic. Bursty traffic is modelled by geometrically distributed burst and silence lengths at the input side of the switch, and by Markov-modulated sources at the switch outputs. The issue of fairness of access to the output ports in Batcher-banyan switches is considered in some detail. Recommendations are made concerning mechanisms to ensure fair access, and simulation results are presented to evaluate the effectiveness of these mechanisms.

Chapter Four considers the topological equivalence between binary self-routing networks. Three stronger types of equivalence are introduced, namely input equivalence, output equivalence, and exact equivalence. Attention is restricted to that class of binary self-routing networks where the interconnections between stages are drawn from a set termed the set of binary permutations. This restriction allows a powerful method to be developed for investigating the equivalence between two networks. The method is used to investigate routing strategies in binary self-routing networks, and is also applied to obtain the necessary and sufficient condition for two cells not to collide in a binary self-routing network. An elegant proof is given that the sorting operation in the Batcher-banyan switch is

sufficient to ensure that the above condition is satisfied by the cells entering the banyan network. Previous authors have presented proofs that the Batcher-banyan switch is internally non-blocking, but they did not relate their proof to the necessary and sufficient condition for cells not to collide in the banyan network.

The condition for a three-stage switch to be non-blocking has been obtained in Chapter Four for the case where the inputs and outputs of the intermediate stage modules feature channel grouping and link speedup. Special cases of this condition are obtained which apply to multi-rate and single-rate circuit switching. Hence it is shown that a different non-blocking condition applies to a three-stage ATM switch where routing through the intermediate stage is performed at cell level, than to the corresponding switch with call-level routing.

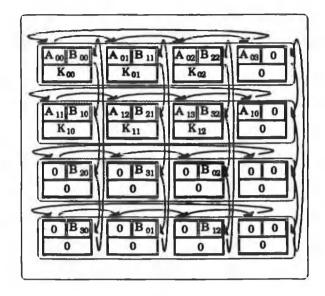

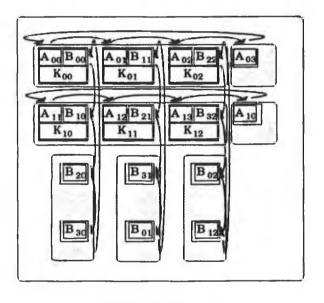

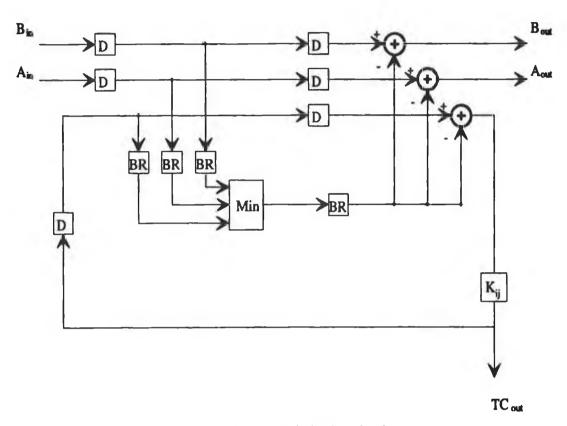

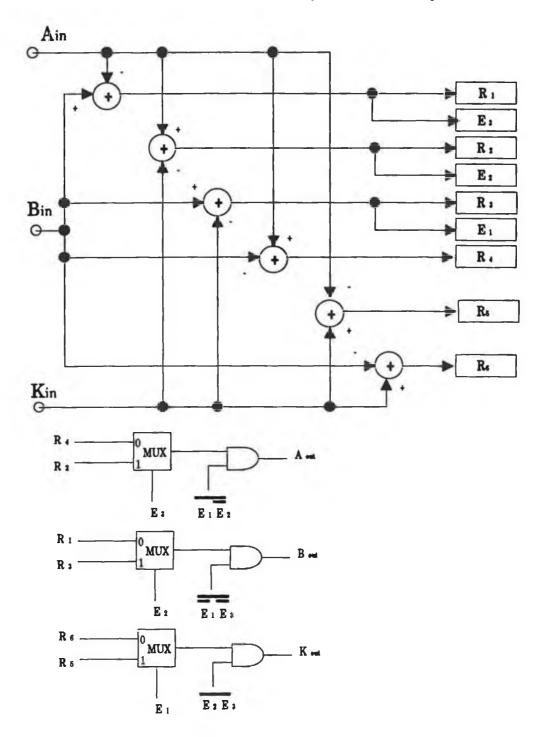

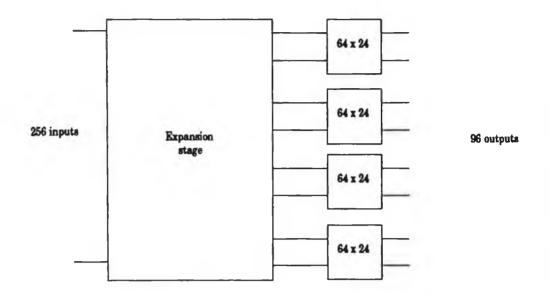

A new design of three-stage ATM switch is described in Chapter Five. The design supports the use of channel grouping in the intermediate stage. Routing through this stage is performed at cell level. The new design requires a lower operating speed for the circuitry which implements the cell level path allocation than would be the case for previously published algorithms. This benefit is obtained at the expense of an increase in the amount of hardware required. The key component of the switch is an array of processors which try to reserve a path through the intermediate stage of the switch for every incoming cell. The logic required to implement the processor is described, so as to demonstrate that the processors are of low complexity, and so can be operated at the required clock rate. Additional hardware is required to initialise the processor array at the start of each time slot, and to forward routing tags to the cells indicating the available path through the intermediate stage. This hardware makes extensive use of non-blocking banyan networks, so as to ensure high-speed operation.

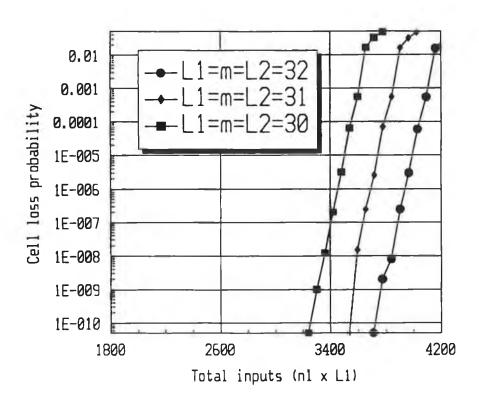

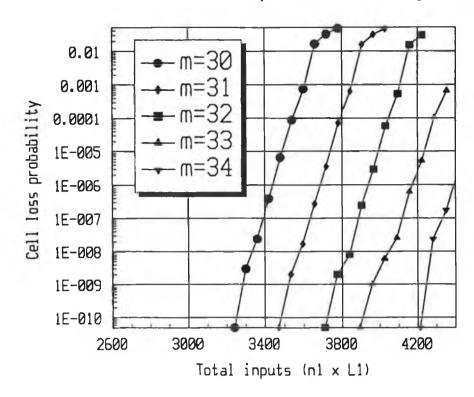

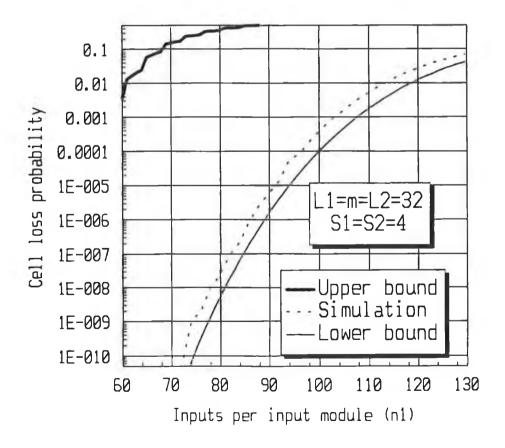

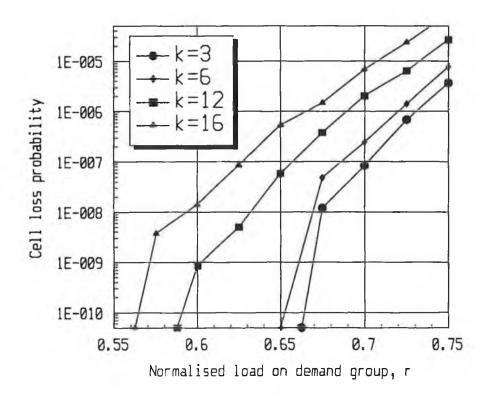

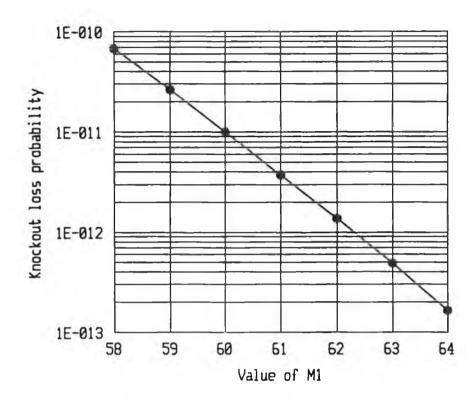

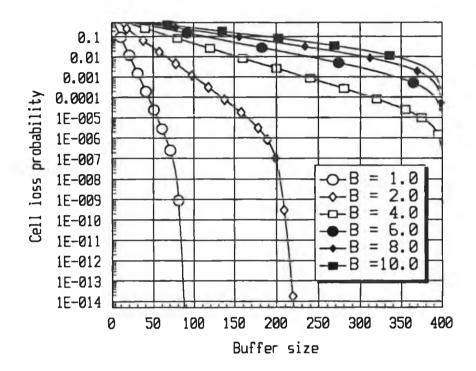

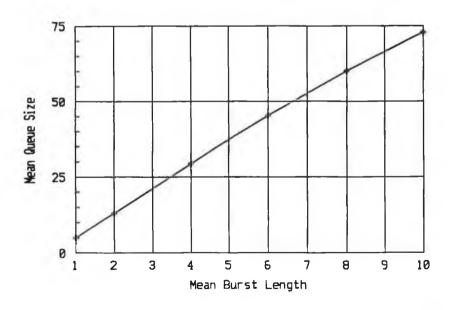

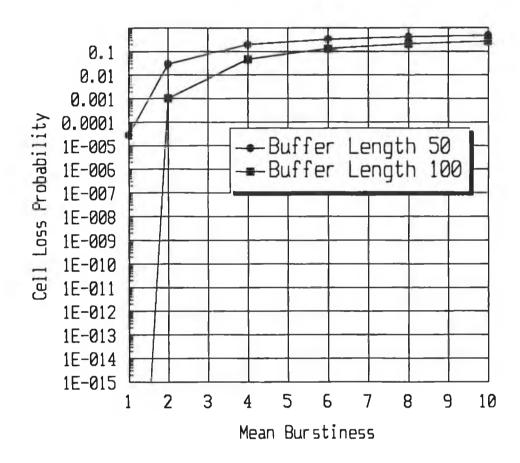

The performance of the new switch is evaluated in Chapter Six. Simulation techniques are used to determine the cell loss probability, due to loss of contention for a path through the intermediate stage, for an output-buffered switch. The advantages of channel grouping are demonstrated by the results obtained. It is also shown that the switch is relatively insensitive to non-uniform loading of the outputs. The performance of the output stage of the switch is evaluated analytically, using one of the methods described in Chapter Three.

The results of the above research are summarised in Chapter Seven.

#### References

<sup>[1]</sup> L. Kleinrock, "ISDN - the path to broadband networks", Proc. IEEE, vol. 79, no. 2, pp. 112-117, Feb. 1991.

<sup>[2]</sup> CCITT Recommendation I.211, "B-ISDN service aspects", 1990.

<sup>[3]</sup> CCITT Recommendation 1.121, "Broadband aspects of ISDN", 1990.

<sup>[4]</sup> CCTTT Recommendation I.361, "B-ISDN ATM layer specification", 1990.

- [5] M. Kawarasaki and B. Jabbari, "B-ISDN architecture and protocol", Journal Of Select. Areas Commun., vol. 9, no. 9, pp. 1405-1415, Dec. 1991

- [6] CCITT Draft Recommendation I.35B, "B-ISDN ATM layer cell transfer performance".

#### 2. BROADBAND SWITCH ARCHITECTURES.

#### 2.1 Introduction.

A wide range of switch designs has been proposed for use in ATM networks [1-4]. Most broadband switches adopt one of a small number of basic techniques in order to achieve the high switching rates required whilst accommodating the unscheduled nature of cell arrivals. These basic techniques are investigated in detail below, and their strengths and weaknesses are assessed. Methods for evaluating the performance of ATM switches will be considered in Chapter Three.

The term ATM is of recent origin. Prior to its adoption, switches of the type appropriate for an ATM network were typically referred to as fast packet switches. Two of the earliest such switches proposed were the Starlite switch [5] and Turner's Fast Packet Switch [6].

Both of these switch designs achieved high speed operation by employing self-routing networks of the type first proposed for use as interconnection networks in a parallel processing environment [7]. These interconnection networks include the Omega network [8], the indirect binary n-cube [9], the baseline network [10] and the SW-banyan [11]. The above networks have been shown to be topologically equivalent [10]. The self-routing property is achieved by employing digit-controlled switch elements, and so these switches are all examples of delta networks [12]. The Starlite switch in addition employs a sorting network, of the type first proposed by Batcher [13].

#### 2.2 Delta networks.

The definition of delta networks given by Patel [12] was as follows:

A delta network is an  $a^n \times b^n$  switching network with n stages consisting of (for stage  $1 \le i \le n$ ),  $a^{n-i}b^{i-1}$  crossbar modules. Each crossbar module has a inputs and b outputs and is digit-controlled, i.e. an input is connected to an output d ( $0 \le d < b$ ) if a control digit (base b) supplied by the input is d. The module can arbitrate among conflicting requests for output d. The digit is chosen from the destination address of the input data. All inputs and outputs of the crossbar modules are connected. The link pattern between stages is such that a unique path of constant length exists between any source and any destination in the network.

From this definition, it can be seen that the class of banyan networks [11] has much in common with delta networks. In particular, an SW-banyan is an example of a delta network, if the 'cross-bars' of which it is composed are digit-controlled. Also, the interconnection networks mentioned above (such as the Omega network) are examples of delta networks where the crossbar modules are 2x2 switches.

## 2.3 Self-routing networks based on 2x2 switches.

## 2.3.1 Principles of self-routing networks.

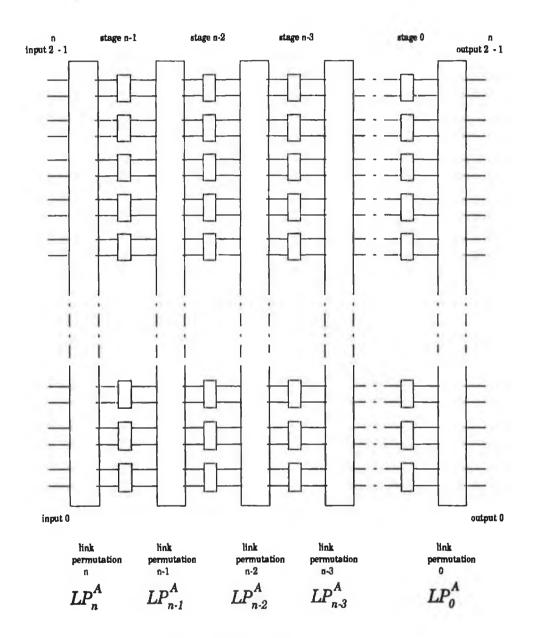

Many self-routing switches have been proposed by different authors, and a variety of notations, terminologies, etc., are in use to describe such switches. A consistent method for the description of these switches, which is similar to that adopted by Wu and Feng [10], is described in the following. This method will be used in Chapter Four to analyse the conditions under which blocking occurs in an arbitrary binary self-routing network.

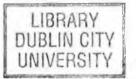

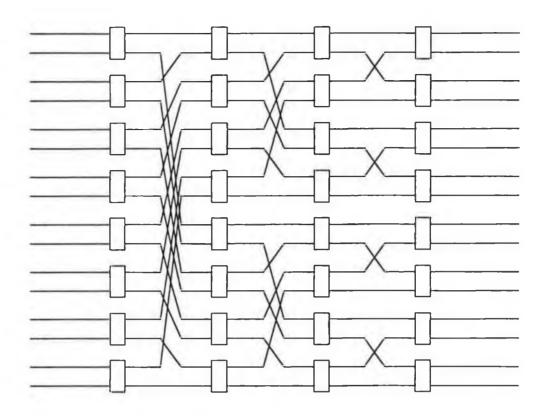

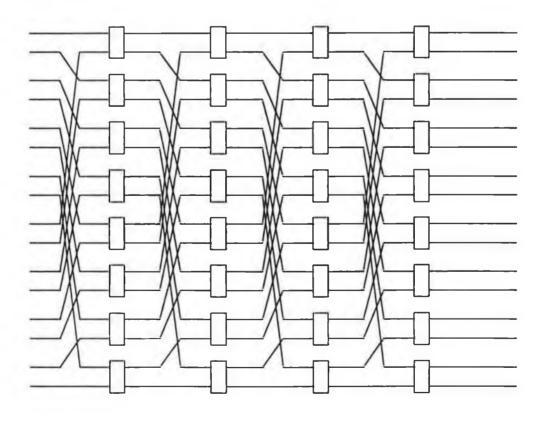

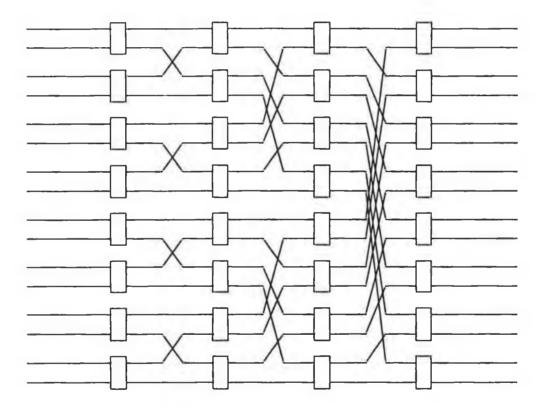

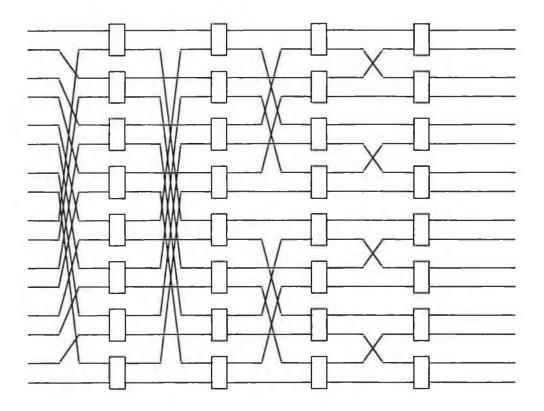

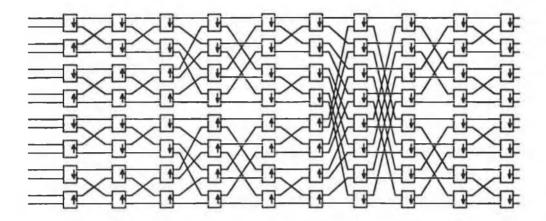

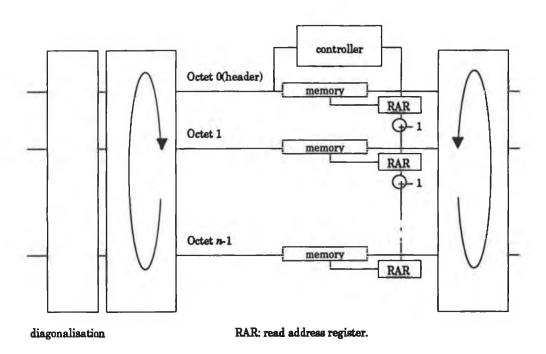

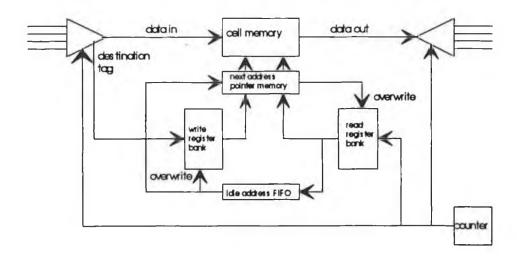

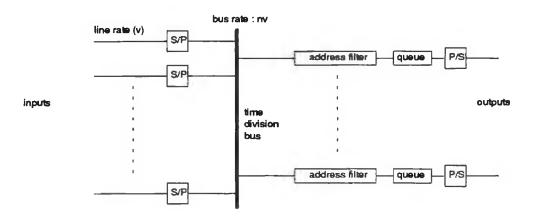

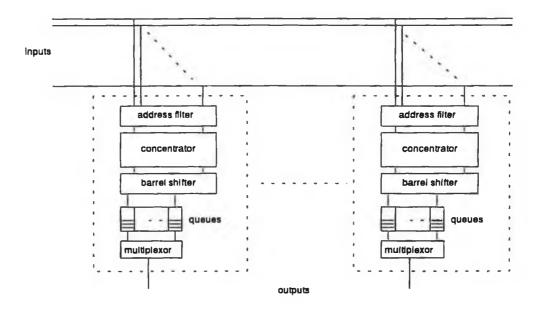

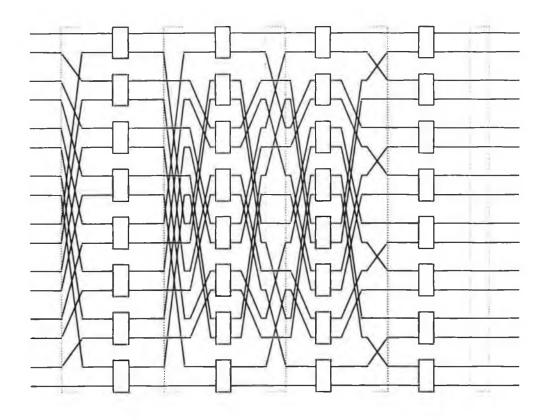

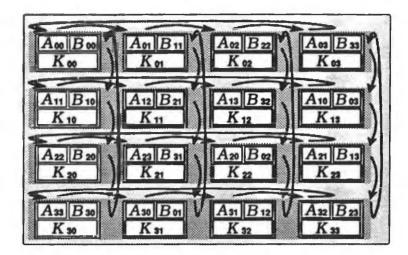

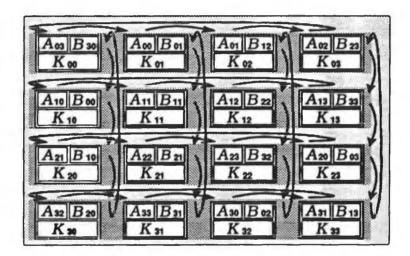

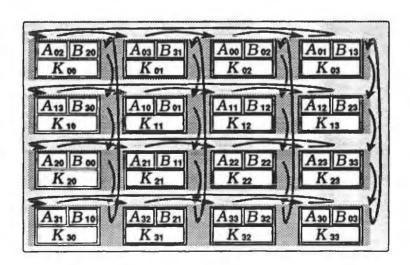

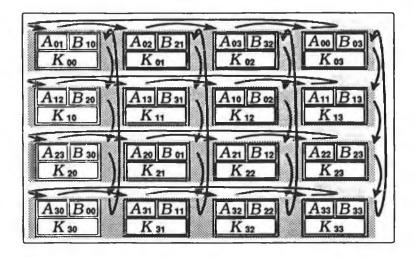

Most self-routing networks considered for use in ATM may be represented as shown in Fig. 2.1. It can be seen that the switch has  $2^n$  inputs and  $2^n$  outputs, and comprises n stages of  $2^{n-1}$  switch elements. These switch elements are bit-controlled as follows. The input cells are transmitted serially through the network, with an n-bit destination tag  $(d_{n-1}d_{n-2}.....d_1d_0)$  as prefix; the switch elements present in stage k of the switch route their input cells to the upper or lower output according to the value of one of the routing tag bits, which is typically  $d_k$ ; the cell is routed to the higher output if  $d_k = 1$ , and otherwise is routed to the lower output. A difficulty arises when both cells present at the switch element inputs have the same value for  $d_k$ , i.e., when they are contending for the same output. Methods of dealing with this contention shall be considered later.

If the link permutations (which are simply hard-wired re-arrangements of the order in which the outputs of one stage are connected to the inputs of the succeeding stage) are appropriately chosen, then a cell with a given destination tag will be routed to the same output port, irrespective of the input port at which it arrives, having passed through n switch elements, each of which routes it on the basis of a single (unique) bit of its destination tag. It is because of this property that such networks are described as self-routing.

#### 2.3.2 A notation to describe self-routing networks.

The link permutations are what distinguish among these self-routing switch designs. Thus, to uniquely describe a particular network of the type in Fig. 2.1 it is sufficient to define the n link permutations  $LP_0,...,LP_n$ . A notation to describe the permutations of interest will be described below.

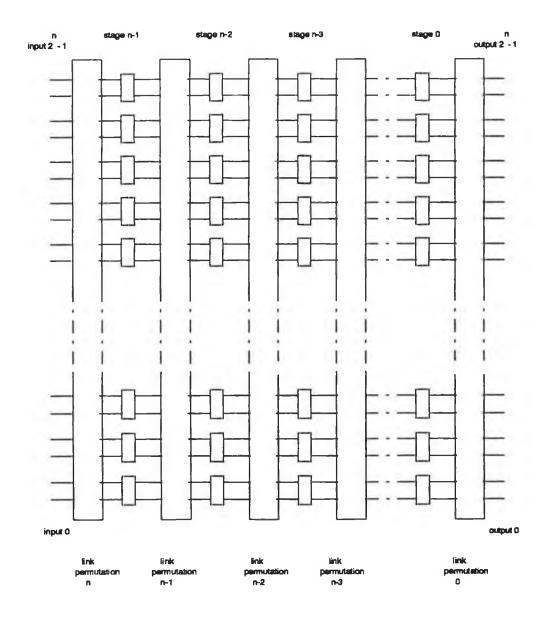

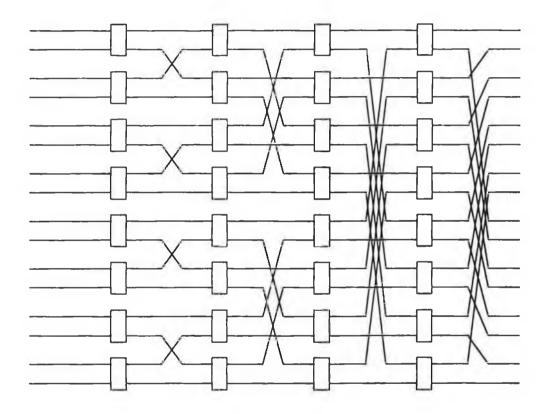

Two possible permutations of eight links are illustrated in Fig. 2.2. The simplest possible permutation is shown in Fig. 2.2(a), and is here called the straight-through (ST) permutation. In this permutation, input line 0 is linked to output line 0, input line 1 to output line 1, etc. In other words the ST permutation is a null permutation. Typically, at least one from the n-th link permutation ( $LP_n$ ) and link permutation zero ( $LP_0$ ) will be an ST permutation. Another common

permutation is the perfect shuffle [14] of Fig. 2.2(b). The outputs labelled 0,1,....,7 are connected to inputs labelled 0,4,1,5,2,6,3,7 respectively. Thus, the upper four inputs and the lower four inputs have been interleaved at the outputs. This is termed a perfect shuffle by analogy with the permutation produced by cutting a deck of cards in the middle and interleaving each half.

A link permutation can be regarded in mathematical terms as a transformation from the set of input line numbers to the set of output line numbers. Evidently, the transformation must be bijective (one-to-one and onto) if an input line is not to be linked to two output lines or *vice versa*. Let the set  $I_n$  denote the set of integers  $\{0,1,2,\ldots,2^{n-1}\}$ . Then, in a permutation of  $2^n$  lines, the output port labelled Y is connected to the input port labelled X if

$$Y = \tau(X)$$

where  $\tau:I_n \to I_n$  is a bijective transformation.

One permutation  $(\tau_a)$  can be immediately followed by another  $(\tau_b)$ , to produce a third permutation  $(\tau_c)$ , i.e., one where the output lines from the permutation defined by  $\tau_a$  are connected as input lines to the link permutation defined by  $\tau_b$ . The output port Y connected to input port X is then given by

$$Y = (\tau_b \circ \tau_a) (X) \Delta \tau_b (\tau_a (X)).$$

It follows that  $\tau_c = \tau_a \tau_b$  by analogy with matrix multiplication.

An alternative representation of a link permutation involves the use of a  $2^n$  x  $2^n$  matrix M, whose entries are defined by

$$M_{ij} = \frac{1}{0}$$

, if a link connects input *i* to output *j* otherwise.

Since only one link can be connected to each input or output, it follows that

$$\sum_{0 \le i < 2^n} M_{ij} = 1$$

and

$$\sum_{0 \le i < 2^n} M_{ij} = 1.$$

Evidently, if one permutation  $(\mathbf{M}_a)$  is followed by another  $(\mathbf{M}_b)$  to produce a third  $(\mathbf{M}_c)$ , then

$$M_c = M_c M_b$$

In order to identify the output link k to which input link i is connected via a link permutation represented by the matrix M, the following is calculated:

$$e_{out} = e_i M$$

,

where  $e_i$  is a row vector containing  $2^n$  entries defined by:

$$(\mathbf{e}_i)_i = \delta_{ij}$$

(where  $\delta_{ij}$  is the Kronecker delta function)

and where eout is a similar row vector defined by

$$(\mathbf{e}_{out})_i = \delta_{ik}$$

.

The scalar value of j can be recovered using

$$j = \mathbf{e}_{OUt} \cdot \mathbf{v},$$

where v is a column vector with  $2^n$  entries defined by

$$\mathbf{v}_k = k, \, 0 \le k < 2^n.$$

The transformation notation shall be used henceforth because of its greater simplicity. However, it is apparent, from the analogy developed here, that the rules of matrix multiplication and inversion apply to operations involving consecutive or inverse link permutations. These rules shall be applied in Chapter Four to elucidate some of the properties of self-routing networks.

In general, a complete description of  $\tau$  would require an ordered listing of the set of output link numbers, i.e.  $\{\tau(0),\tau(1),\ldots,\tau(2^{n}-1)\}$ . However, most of the permutations of interest in self-routing networks can be described more compactly, if the values of X and Y are represented in binary notation. Suppose that  $X = b_{n-1} 2^{n-1} + b_{n-2} 2^{n-2} + \ldots + b_0$  and  $Y = c_{n-1} 2^{n-1} + c_{n-2} 2^{n-2} + \ldots + c_0$ , where  $\tau(X) = Y$ . The transformation  $\tau($ ) will be referred to as a binary permutation if, for arbitrary X and Y.

$$c_{\tau'(i)} = b_i, 0 \le i < n$$

where

$$0 \le \tau'(i) < n$$

,

and where

$$\tau'(i) = \tau'(j) \Leftrightarrow i = j$$

.

In other words,  $\tau'()$  is a permutation of the integers from 0 to n-1. A binary permutation is thus simply a re-ordering of bits. This means, in particular, that the number of binary 1's in X and Y must be the same. An example of a binary link permutation is the perfect shuffle of eight lines depicted in Fig. 2.2(b). This can be defined by:

$$0 \xrightarrow{r'} 1$$

$$1 \xrightarrow{r'} 2$$

$$2 \xrightarrow{r'} 0$$

or

$$b_0 \xrightarrow{\tau} b_1$$

$$b_1 \xrightarrow{\tau} b_2$$

$$b_2 \xrightarrow{\tau} b_0.$$

Fig. 2.1: A binary self-routing network.

More compactly, this may be written as

$$\tau (b_2b_1b_0) = b_1b_0b_2.$$

It shall be shown in section 2.3.4 that the link permutations used in many popular self-routing networks belong to the class of binary permutations. An example of a link permutation which falls outside this class is the crossover permutation [15].

Fig. 2.2: Some link permutations.

The names chosen for the permutations of interest, and their definition using the notation introduced above, are as follows. It is assumed that the permutations are of  $2^n$  lines, so that n bits are required to identify a line.

## 2.3.3 Some link permutations.

#### 2.3.3.1 The perfect shuffle.

The perfect shuffle of all  $2^n$  inputs is represented by the transformation  $\mathbf{PS_n}$ , which corresponds to a cyclic shift *left* of the input port number, i.e.

$$PS_n(b_{n-1}b_{n-2}....b_0) = b_{n-2}.....b_0b_{n-1}$$

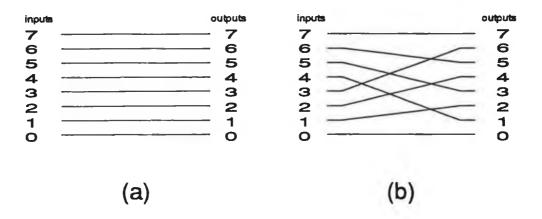

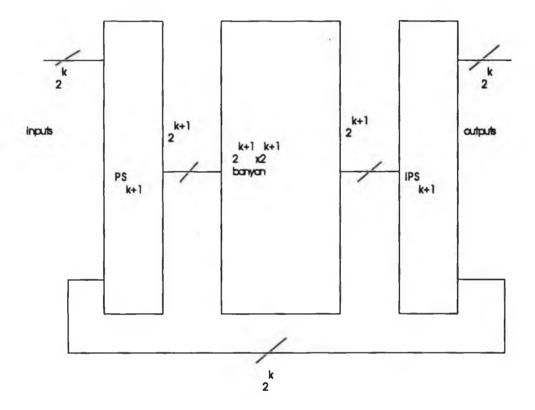

Often, the perfect shuffle is performed on equal-sized subsets of inputs, e.g., separately on the upper and lower  $2^{n-l}$  lines. Thus, the  $PS_k$  transformation is defined by:

$$PS_k(b_{n-1}b_{n-2}....b_0) = b_{n-1}b_{n-2}....b_kb_{k-2}...b_0b_{k-1}$$

This is a cyclic shift left performed on the least significant k bits of the input line number only. It is equivalent to grouping the inputs into  $2^{n-k}$  contiguous groups, and performing a full perfect shuffle on each group individually. The four

possible perfect shuffles for sixteen lines are shown in Fig. 2.3. Evidently, the  $PS_1$  transformation is equivalent to the ST transformation.

Fig. 2.3: The perfect shuffle.

## 2.3.3.2 The inverse perfect shuffle.

Another family of permutations is obtained from the inverse perfect shuffle, i.e. when the perfect shuffle is performed on the output lines to obtain the input lines, rather than *vice versa*. The IPS<sub>k</sub> transformation is defined as a cyclic shift *right* of the least significant k bits of the input port number, i.e.,

$$IPS_k(b_{n-1}b_{n-2}....b_0) = b_{n-1}b_{n-2}....b_kb_0b_{k-1}...b_1$$

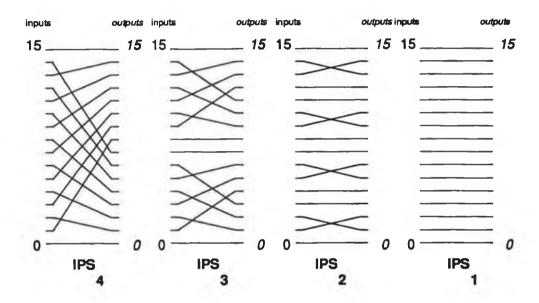

A  $PS_k$  permutation followed by an  $IPS_k$  permutation reduces to a ST permutation, hence the name *inverse* perfect shuffle. Example inverse perfect shuffles are shown in Fig. 2.4. Note that the  $IPS_2$  and  $PS_2$  transformations are identical.

#### 2.3.3.3 The swap permutation.

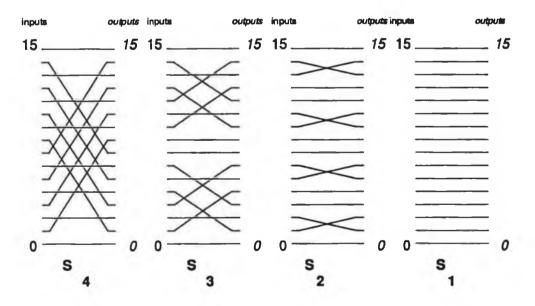

Another permutation, which is here called the swap permutation, is obtained by following an  $IPS_k$  permutation by a  $PS_{k-1}$  permutation. This gives the transformation  $S_k$  defined by

$$\begin{split} S_{k}(b_{n-1}b_{n-2}.....b_{0}) &= &PS_{k-1}(IPS_{k}(b_{n-1}b_{n-2}.....b_{0})) \\ &= &PS_{k-1}(b_{n-1}b_{n-2}.....b_{k}b_{0}b_{k-1}...b_{1}) \\ &= &b_{n-1}b_{n-2}....b_{k}b_{0}b_{k-2}...b_{1}b_{k-1}. \end{split}$$

Using the shorthand notation introduced earlier, this result may be written as

$$S_k = IPS_kPS_{k-1}$$

The transformation is so called because the least significant bit  $(b_0)$  and the k-th least significant bit  $(b_{k-1})$  exchange places. Evidently, the swap permutation is its own inverse, i.e.  $S_k(S_k(X)) = X$ . The swap permutation is illustrated in Fig. 2.5.

Fig. 2.4: The inverse perfect shuffle.

Fig. 2.5: The swap permutation.

## 2.3.3.3 The bit-reversal permutation.

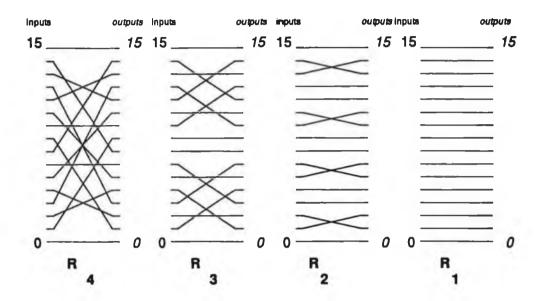

The bit-reversal permutation Rk is defined by

$$R_k(b_{n-1}b_{n-2}....b_0) = b_{n-1}b_{n-2}....b_kb_0b_1b_2...b_{k-1}$$

In other words, it consists of a bit reversal on the k least significant bits of the link address. The bit-reversal permutation is illustrated in Fig. 2.6.

Fig. 2.6: The bit-reversal permutation.

#### 2.3.4 Network definitions.

#### 2.3.4.1 Baseline network.

The baseline network [10] is of the form shown in Fig. 2.1, with  $2^n$  input and output lines, and with the link permutations defined by

$$LP_n = LP_0 = ST$$

,

$LP_k = IPS_{k+1}$ ,  $0 < k < n$ ,  $k$  integer.

A 16x16 baseline network is shown in Fig. 2.7.

## 2.3.4.2 Omega network.

The omega network [8] is of the form shown in Fig. 2.1, with  $2^n$  input and output lines, and with the link permutations defined by

$$LP_0 = ST$$

,

$LP_k = PS_n$ ,  $0 < k \le n$ ,  $k$  integer.

A 16x16 omega network is shown in Fig. 2.8.

Fig. 2.7: The baseline network.

Fig. 2.8: An omega network.

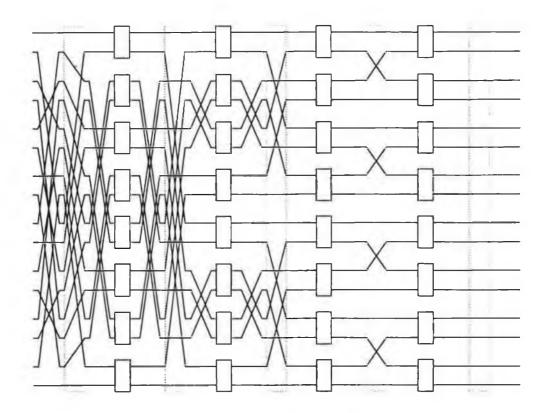

## 2.3.4.3 Indirect binary n-cube.

The indirect binary n-cube [9] is a network of the form shown in Fig. 2.1, with  $2^n$  input and output lines, and with the link permutations defined by

$$LP_n = ST$$

,

$LP_0 = IPS_n$

$LP_k = S_{n-k+1}$ ,  $0 < k < n$ ,  $k$  integer.

A 16x16 indirect binary n-cube network is shown in Fig. 2.9.

Fig. 2.9: The indirect binary n-cube.

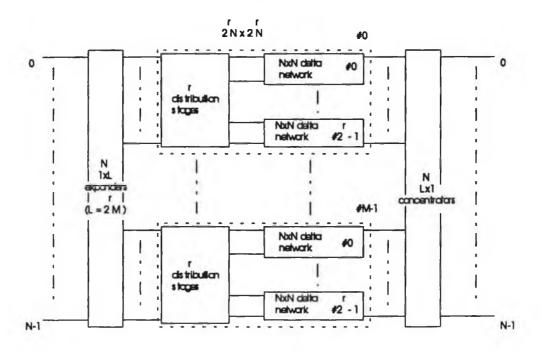

#### 2.3.4.4 The GL-banyan.

Goke and Lipovski presented definitions of general banyan networks, and of specific banyan structures [11]. The focus here shall be on those banyan structures that can be represented by Fig. 2.1. In the terminology of Goke and Lipovski, the number of stages in this switch is referred to as the number of levels, i.e., an L-level banyan has L stages of switching. The number of inputs and outputs of each switch element is referred to as the fanout(F) and the spread(S) respectively. If the values for fanout and spread are the same for each switch element, the resulting structure is referred to as a regular banyan. Thus, using this terminology, Fig. 2.1

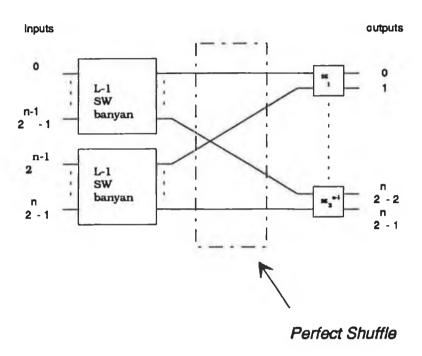

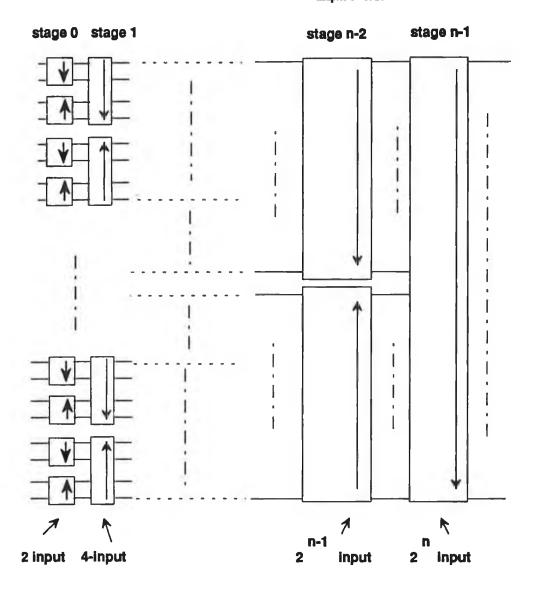

depicts a regular (n-level) banyan with S=F=2. Goke and Lipovski described a recursive technique for synthesising a specific regular banyan called the SW banyan. Applying this technique in the special case where S=F=2, it is found that a 1-level SW banyan is equivalent to a 2x2 switch element, and that an L-level SW banyan may be synthesised by interconnecting two (L-1)-level banyans and  $2^{L-1}$  2x2 switch elements as shown in Fig. 2.10.

Fig. 2.10: Recursive rule for banyans.

Fig. 2.10 is an interpretation of Fig. 8 of [11] for the special case where 2x2 switches are used. The interconnection pattern used must be such that, if the upper input port of  $SE_k$  is connected to output port j of the upper (L-1)-level SW banyan, then the lower input port of  $SE_k$  must be connected to output port j of the lower (L-1)-level SW banyan. Thus, allowable link permutations include the  $PS_L$  and the  $S_L$ . The  $PS_L$  transformation is implied by Fig. 8 of [11], which illustrates the recursive rule, but two other examples of SW banyans presented in that paper used the swap permutation. Accordingly, other authors, in reporting on the SW banyan, have implicitly accepted the swap permutation as the one to be used. Accepting this convention, the resulting banyan shall be referred to as the GL-banyan. This is a network of the form shown in Fig. 2.1, with  $2^n$  input and output lines, and with the link permutations defined by

$$LP_n = LP_0 = ST,$$

$$LP_k = S_{n-k+1}, \ 0 < k < n, k \text{ integer.}$$

A 16x16 GL-banyan network is shown in Fig. 2.11. It is evident that the GL-banyan is identical to the indirect binary n-cube, with the exception that the inverse perfect shuffle of the output port lines is not performed.

#### 2.3.4.5 The P-banyan.

If, instead of using the swap permutation in recursively constructing the GLbanyan, the perfect shuffle had been used, the resulting banyan would be defined by

$$LP_n = LP_0 = ST$$

$$LP_k = PS_{n-k+1} \qquad 0 < k < n, k \text{ integer.}$$

This network is referred to as a P-banyan. A 16x16 example of such a network is shown in Fig. 2.12.

Fig. 2.11: The GL-banyan.

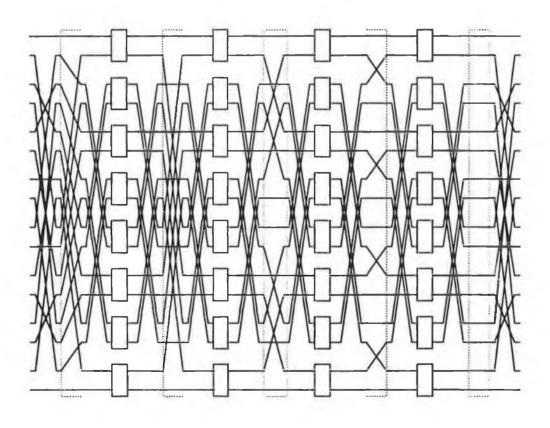

#### 2.3.4.6 The S-banyan.

A certain amount of confusion exists in the literature regarding banyan networks, because of the generality of the definition of the banyan, as introduced by Goke and Lipovski [11]. Thus, all of the structures considered above can be regarded as banyan networks. An attempt has been made in this discussion to

avoid confusion by always using the more specific title for a particular network (e.g. the baseline network) where it exists, and by inventing titles for networks without specific names (e.g., the GL-banyan, which would otherwise need to be described as 'a regular L-level banyan, with S=F=2, synthesized recursively using the swap permutation', in order to describe it completely). Unfortunately, the term 'banyan', without further qualification, is often used by the switching community to refer to the structure defined by:

$$LP_n = PS_n$$

$$LP_0 = ST$$

$$LP_k = S_{k+1}, \quad 0 < k < n, k \text{ integer.}$$

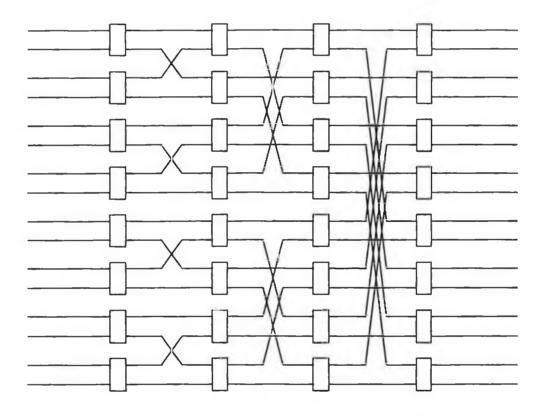

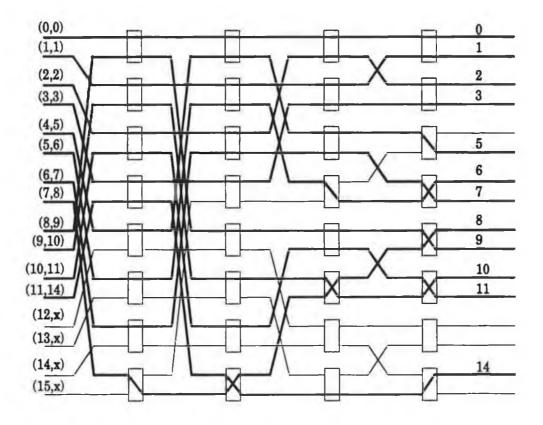

This is referred to as the S-banyan. A 16x16 S-banyan is shown in Fig. 2.13.

Fig. 2.12: The P-banyan.

#### 2.3.5 Inverse networks.

The inverse of a permutation may be defined as that permutation which arises when the input and output lines are interchanged. It is apparent that a permutation, immediately followed by its inverse permutation, is equivalent to the straight-through permutation, i.e.,

$$ST = \tau \tau^{-1}$$

.

OL

$$\tau^{-1}(\ \tau(X)\ )=X.$$

It has already been noted that the swap permutation is its own inverse, and that the  $IPS_k$  permutation is the inverse of  $PS_k$ .

Fig. 2.13: The S-banyan.

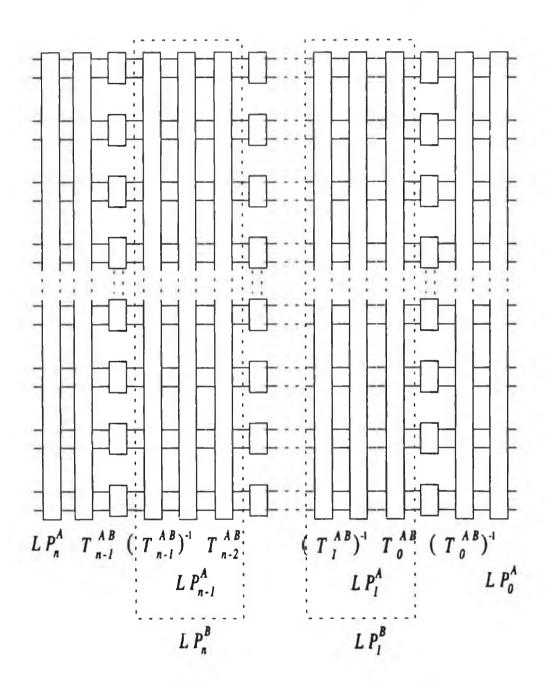

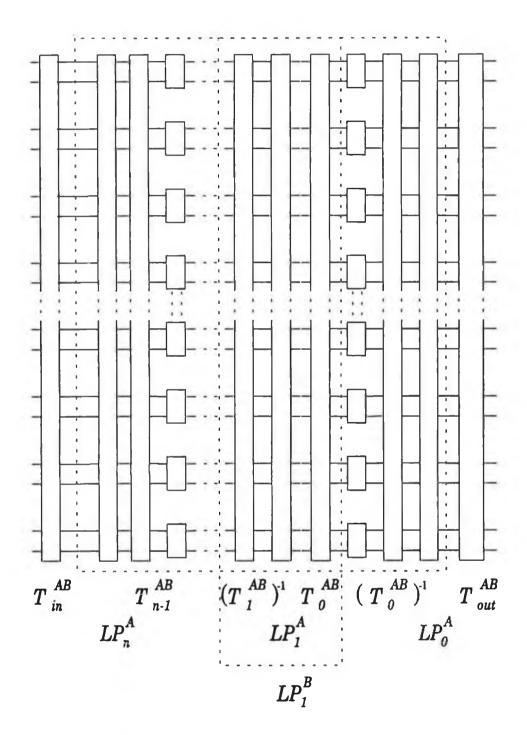

The inverse network is obtained, assuming bi-directional switching elements, simply by applying the inputs at the right hand side of Fig. 2.1, and reading the outputs at the left hand side, i.e. by 'turning around' the network. More formally, the network defined by the transformations  $\{LP'_0,LP'_1,....,LP'_n\}$  is said to be the inverse network of that defined by  $\{LP_0,LP_1,....,LP_n\}$  if and only if

$$LP'_{0} = [LP_{n}]^{-1}$$

$$LP'_{n} = [LP_{0}]^{-1}$$

$$LP'_{k} = [LP_{n-k}]^{-1}, \qquad 0 < k < n.$$

Thus it may be seen that the inverse of the S-banyan is the indirect binary ncube. New networks can be obtained simply by inverting other networks using the above formula.

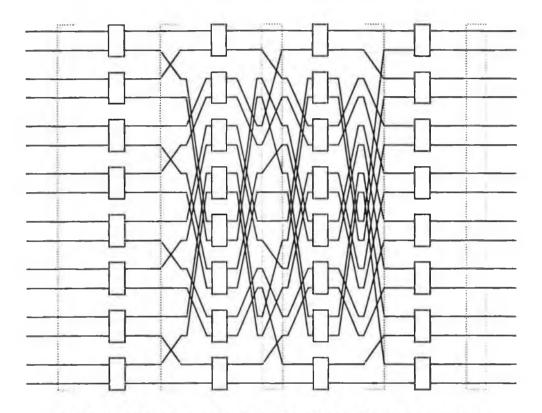

#### 2.3.6 Topological equivalence.

It would appear, at first sight, that a bewildering range of multi-stage interconnection networks is possible, each network with its own unique properties. In fact, it has been shown by Wu and Feng [10] that many of these networks are topologically equivalent. Their method was to renumber the switches in each stage (so that each switch was given a logical number, in addition to its physical number, which represents its position in the stage), and the input and output lines, of a multi-stage interconnection network. The network was then shown to be equivalent to a baseline network by appropriate choice of the logical numbers. The choice of logical numbers was such that the logical numbers of the switch elements linked to any given switch element (say the switch in stage k with logical number h) were the same as the physical numbers of the switches, in a baseline network, linked to the switch element in stage k whose physical number is j. Thus, to prove topological equivalence using this method, it sufficed to discover a mapping rule which mapped the physical numbers of the switch elements in a network into appropriate logical numbers. Using this method, Wu and Feng have shown the following networks to be equivalent to the baseline network:

- i) the Omega network;

- ii) the GL-Banyan;

- iii) the flip network in STARAN [16] this is equivalent to an inverse Omega network, although it is intended for use as a permutation network, rather than a self-routing network;

- iv) the modified data manipulator this is equivalent to an S-Banyan, but with the  $LP_0$  permutation modified to be straight-through (the original data manipulator of [17] used 3x3 switch elements and thus cannot be represented by Fig. 2.1);

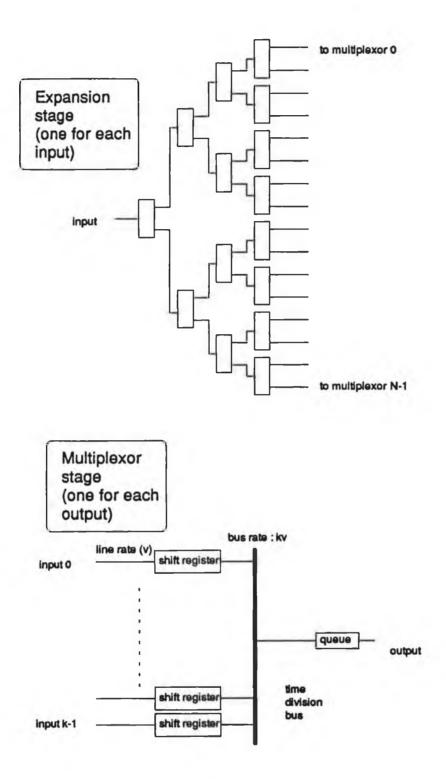

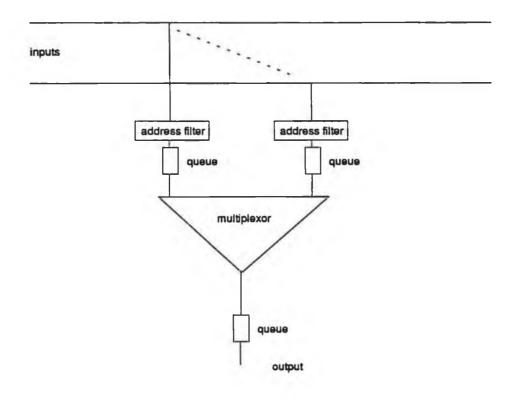

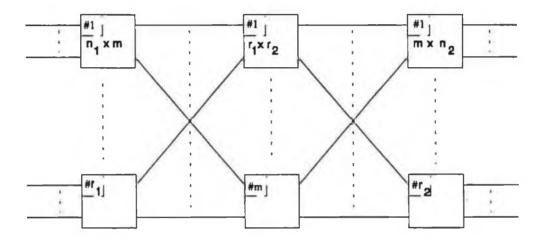

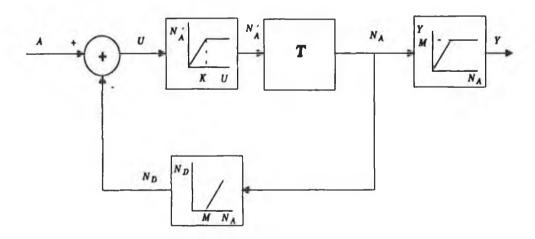

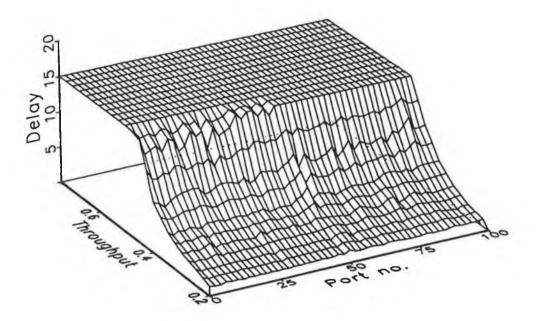

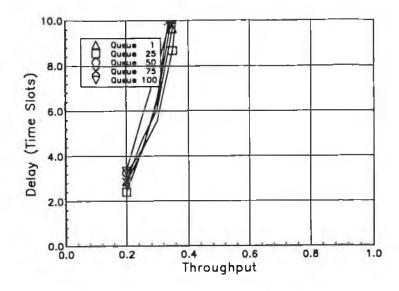

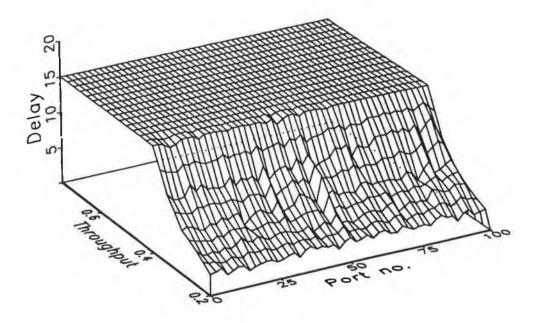

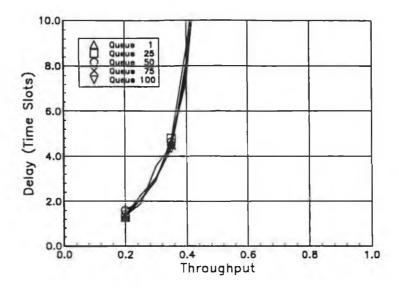

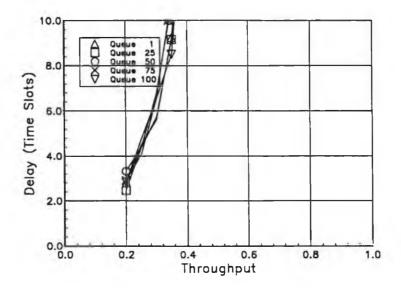

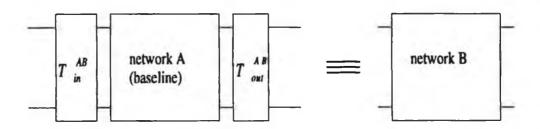

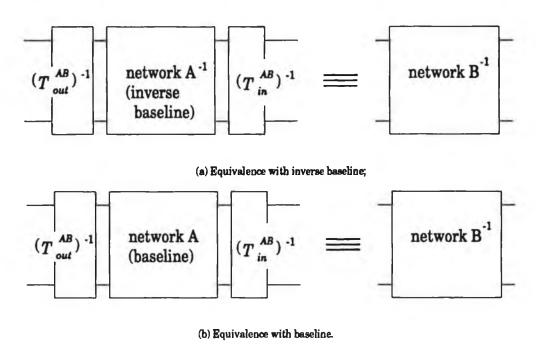

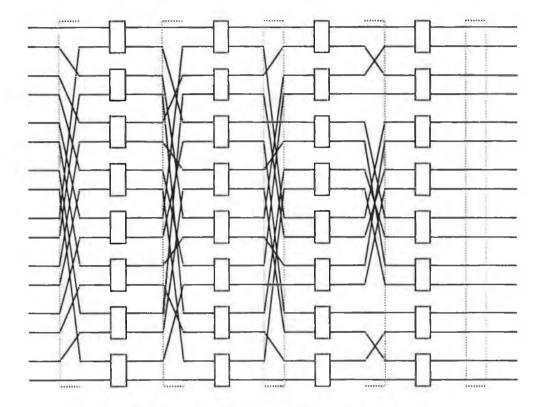

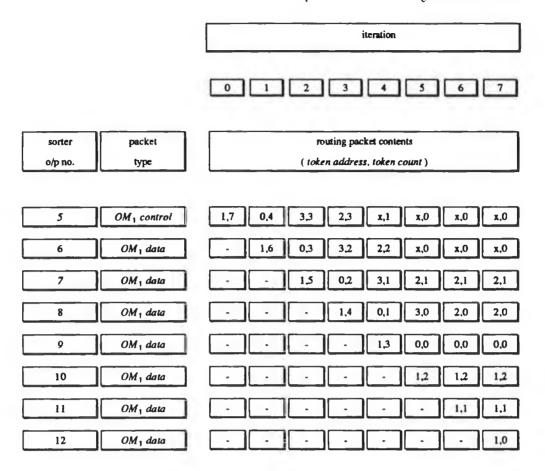

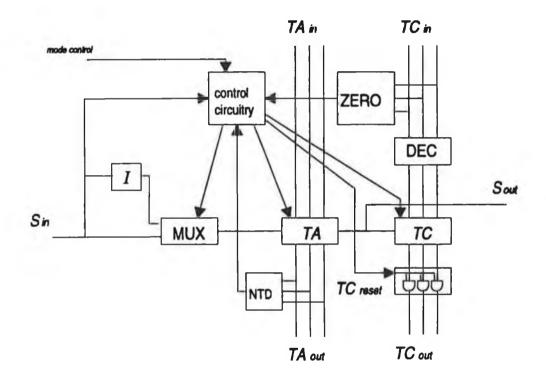

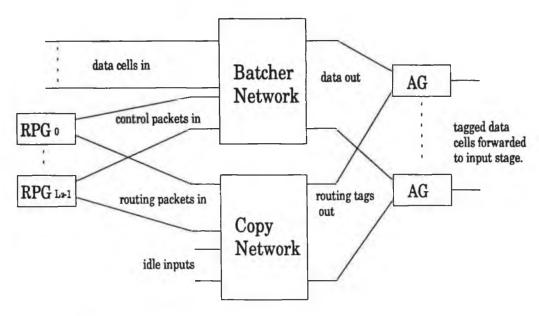

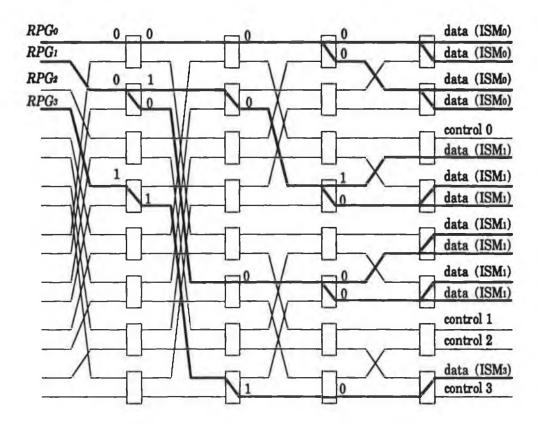

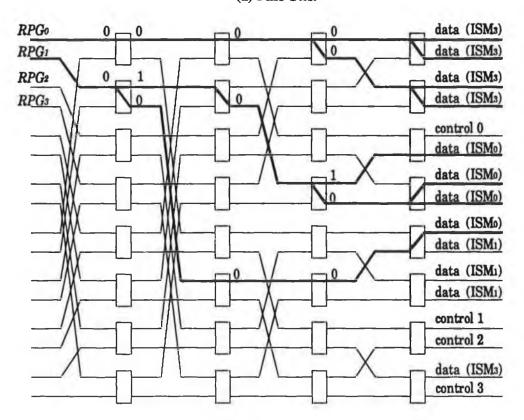

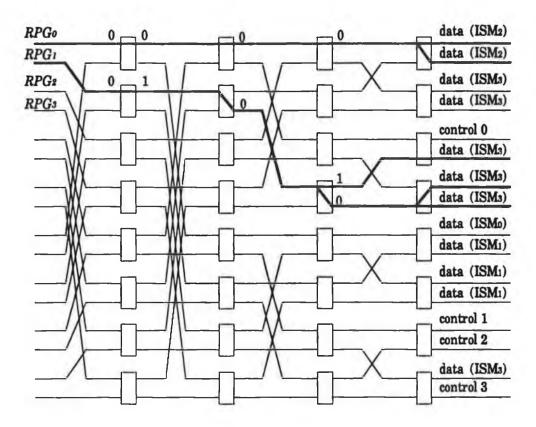

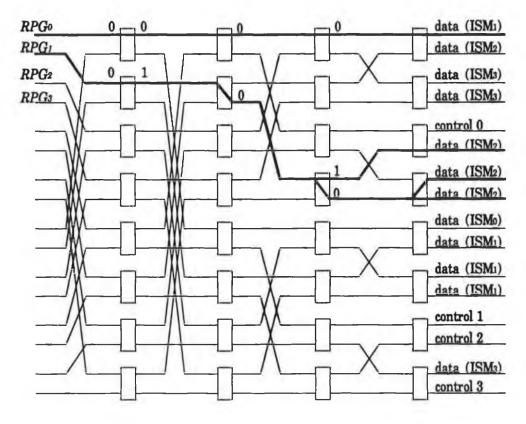

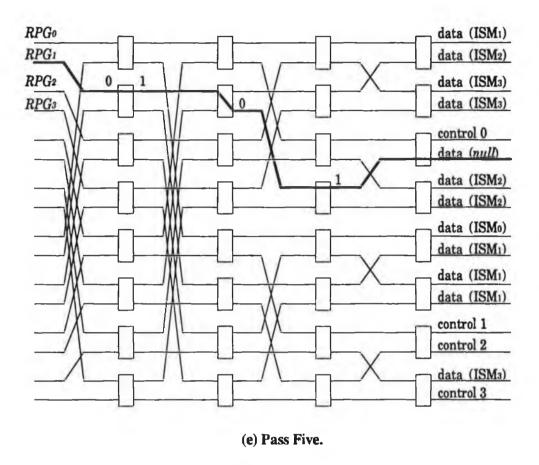

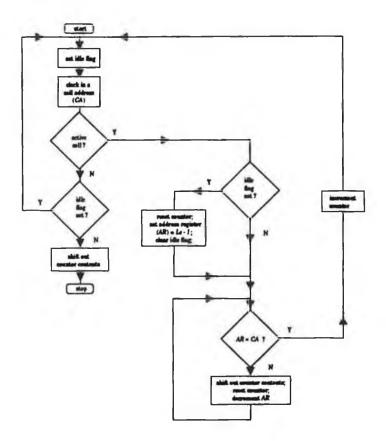

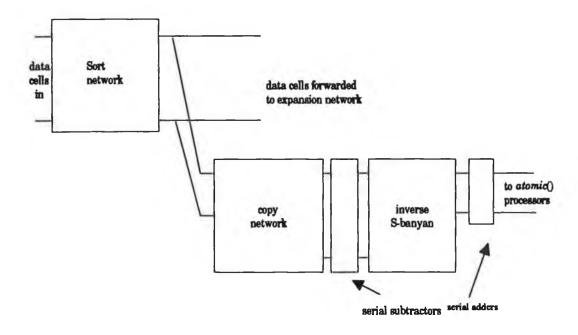

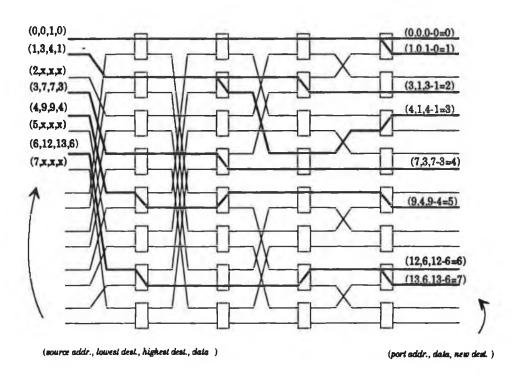

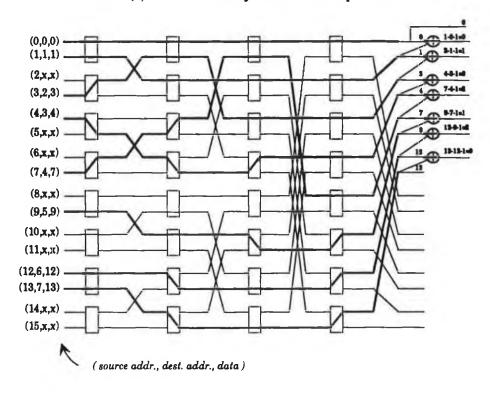

- v) the inverse baseline network Wu and Feng referred to this as the reverse baseline network.