### RICE UNIVERSITY

## Lightweight Silicon-based Security Concept, Implementations, and Protocols

by

### Mehrdad Majzoobi

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

**Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Farinaz Koushanfar, Chair Associate Professor of Electrical and Computer Engineering

Richard Baraniuk

Victor E. Cameron Professor of Electrical and Computer Engineering

Dan Wallach Professor of Computer Science

Houston, Texas

March, 2012

#### ABSTRACT

Lightweight Silicon-based Security Concept, Implementations, and Protocols

by

#### Mehrdad Majzoobi

Advancement in cryptography over the past few decades has enabled a spectrum of security mechanisms and protocols for many applications. Despite the algorithmic security of classic cryptography, there are limitations in application and implementation of standard security methods in ultra-low energy and resource constrained systems. In addition, implementations of standard cryptographic methods can be prone to physical attacks that involve hardware level invasive or non-invasive attacks.

Physical unclonable functions (PUFs) provide a complimentary security paradigm for a number of application spaces where classic cryptography has shown to be inefficient or inadequate for the above reasons. PUFs rely on intrinsic device-dependent physical variation at the microscopic scale. Physical variation results from imperfections and random fluctuations during the manufacturing process which impact each device's characteristics in a unique way. PUFs at the circuit level amplify and capture variation in electrical characteristics to derive and establish a unique device-dependent challenge-response mapping.

Prior to this work, PUF implementations were unsuitable for low power applications and vulnerable to wide range of security attacks. This doctoral thesis presents a coherent framework to derive formal requirements to design architectures and protocols for PUFs. To the best of our knowledge, this is the first comprehensive work that introduces and integrates these pieces together. The contributions include an introduction of structural requirements and metrics to classify and evaluate PUFs, design of novel architectures to fulfill these requirements, implementation and evaluation of the proposed architectures, and integration into real-world security protocols.

First, I formally define and derive a new set of fundamental requirements and properties for PUFs. This work is the first attempt to provide structural requirements and guideline for design of PUF architectures. Moreover, a suite of statistical properties of PUF responses and metrics are introduced to evaluate PUFs.

Second, using the proposed requirements, new and efficient PUF architectures are designed and implemented on both analog and digital platforms. In this work, the most power efficient and smallest PUF known to date is designed and implemented on ASICs that exploits analog variation in sub-threshold leakage currents of MOS devices. On the digital platform, the first successful implementation of Arbiter-PUF on FPGA was accomplished in this work after years of unsuccessful attempts by the research community. I introduced a programmable delay tuning mechanism with pico-second resolution which serves as a key component in implementation of the Arbiter-PUF on FPGA. Full performance analysis and comparison is carried out through comprehensive device simulations as well as measurements performed on a population of FPGA devices.

Finally, I present the design of low-overhead and secure protocols using PUFs for integration in lightweight identification and authentication applications. The new protocols are designed with elegant simplicity to avoid the use of heavy hash operations or any error correction. The first protocol uses a time bound on the authentication process while second uses a pattern-matching index-based method to thwart reverseengineering and machine learning attacks. Using machine learning methods during the commissioning phase, a compact representation of PUF is derived and stored in a database for authentication. "Dedicated to my parents"

## Contents

|          | Abst | tract    |                                      | ii        |

|----------|------|----------|--------------------------------------|-----------|

|          | List | of Illus | trations                             | viii      |

|          | List | of Tabl  | les                                  | XV        |

| 1        | Int  | roduc    | etion                                | 1         |

|          | 1.1  | Focus    |                                      | 4         |

|          | 1.2  | Thesis   | Organization                         | 7         |

| <b>2</b> | Ba   | ckgro    | und                                  | 8         |

| 3        | Re   | lated    | Literature                           | 16        |

|          | 3.1  | Vulner   | ability analysis and countermeasures | 18        |

|          | 3.2  | Hardw    | vare True Random Number Generation   | 20        |

| 4        | PU   | Fs ba    | ased on timing variations            | <b>23</b> |

|          | 4.1  | Delay    | Signature Extraction                 | 23        |

|          |      | 4.1.1    | Signature extraction system          | 27        |

|          |      | 4.1.2    | Characterization accuracy            | 29        |

|          |      | 4.1.3    | Parameter extraction                 | 30        |

|          | 4.2  | Timin    | g PUF                                | 31        |

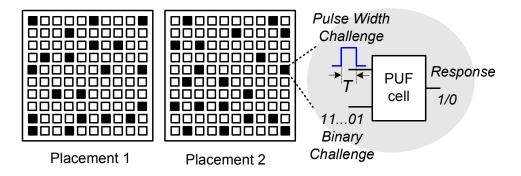

|          |      | 4.2.1    | Pulse challenge                      | 32        |

|          |      | 4.2.2    | Binary challenge                     | 33        |

|          |      | 4.2.3    | Placement challenge                  | 34        |

|          | 4.3  | Respo    | nse robustness                       | 35        |

|          |     | 4.3.1  | Linear Calibration                                          | 36        |

|----------|-----|--------|-------------------------------------------------------------|-----------|

|          |     | 4.3.2  | Differential Structure                                      | 38        |

|          | 4.4 | Exper  | imental evaluations                                         | 41        |

|          | 4.5 | Arbite | er PUF on FPGA                                              | 49        |

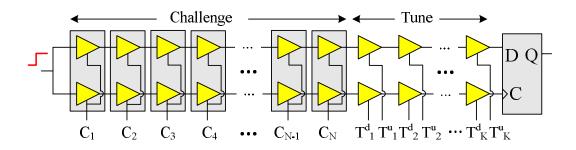

|          |     | 4.5.1  | Tuning with Programmable Delay Lines                        | 51        |

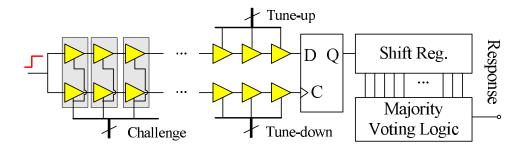

|          |     | 4.5.2  | PDL-based Symmetric Switch                                  | 52        |

|          | 4.6 | Precis | ion Arbiter                                                 | 54        |

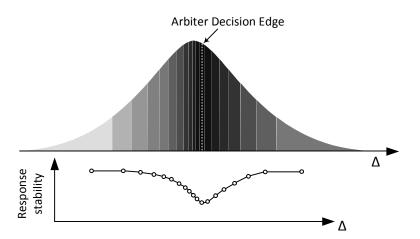

|          | 4.7 | Robus  | t responses                                                 | 55        |

|          | 4.8 | Robus  | tness versus Entropy                                        | 57        |

|          | 4.9 | Exper  | imental Evaluation                                          | 58        |

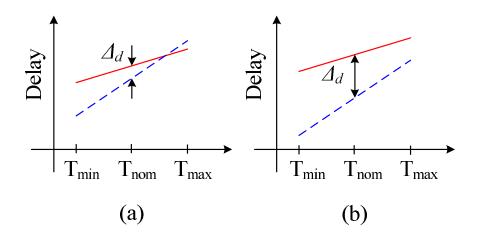

|          |     | 4.9.1  | Programmable delay line                                     | 58        |

|          |     | 4.9.2  | Arbiter-based PUF evaluation                                | 60        |

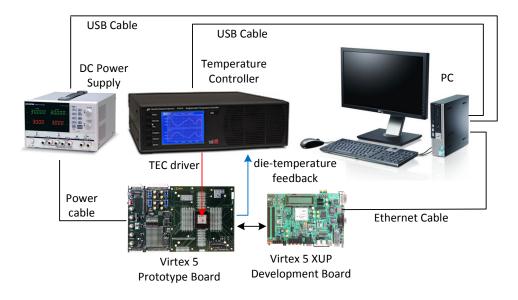

|          |     | 4.9.3  | Measurement setup                                           | 60        |

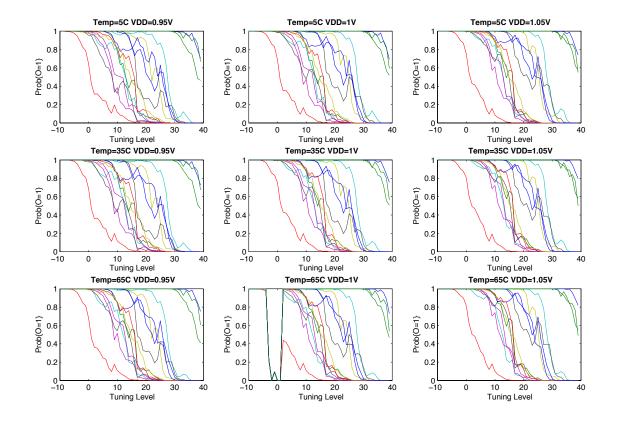

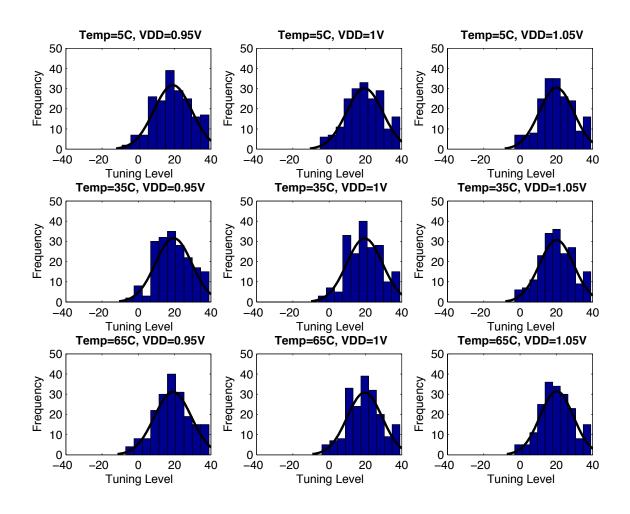

|          |     | 4.9.4  | Tuning the PUF                                              | 61        |

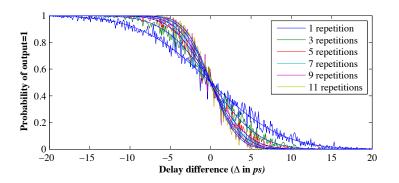

|          |     | 4.9.5  | Majority Voting                                             | 62        |

|          |     | 4.9.6  | Robust response classification                              | 63        |

|          |     | 4.9.7  | Robustness versus entropy                                   | 64        |

|          |     | 4.9.8  | Correlation between effects of temperature and power supply |           |

|          |     |        | variations                                                  | 65        |

| <b>5</b> | PU  | Fs ba  | ased on current variations                                  | <b>74</b> |

|          | 5.1 | Conce  | pt and circuit realization                                  | 74        |

|          | 5.2 | Exper  | imental results                                             | 78        |

| 6        | Au  | thent  | ication Protocols                                           | 86        |

|          | 6.1 | Authe  | ntication Protocol                                          | 86        |

|          |     | 6.1.1  | Classic Authentication                                      | 86        |

|          |     | 6.1.2  | Time-bounded Authentication Using Reconfigurability         | 87        |

|          | 6.2 | Attack | as and Countermeasures                                      | 90        |

vi

|              | 6.3 | Slende | er PUF Protocol                           |   | 91  |

|--------------|-----|--------|-------------------------------------------|---|-----|

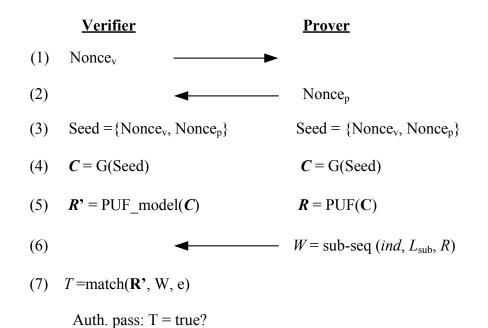

|              |     | 6.3.1  | Slender PUF protocol steps                |   | 93  |

|              |     | 6.3.2  | Secret sharing                            | • | 95  |

|              | 6.4 | Analy  | rsis of attacks                           |   | 96  |

|              |     | 6.4.1  | PUF modeling attack                       |   | 96  |

|              |     | 6.4.2  | Random guessing attack                    |   | 99  |

|              |     | 6.4.3  | Compromising the random seed              |   | 100 |

|              |     | 6.4.4  | Substring replay attack                   |   | 101 |

|              |     | 6.4.5  | Exploiting non-idealities of PRNG and PUF |   | 102 |

|              | 6.5 | Exper  | rimental evaluation                       |   | 104 |

|              | 6.6 | Hardv  | vare implementation                       | • | 112 |

|              |     |        |                                           |   |     |

| 7            | Co  | nclus  | ion                                       | - | 117 |

| $\mathbf{A}$ | TR  | NG     |                                           | - | 119 |

|              | A.1 | TRNO   | G System Design                           |   | 119 |

|              | A.2 | Exper  | rimental results                          |   | 126 |

| В            | Plo | ots    |                                           | - | 134 |

|              | Bib | oliogr | aphy                                      | - | 160 |

vii

# Illustrations

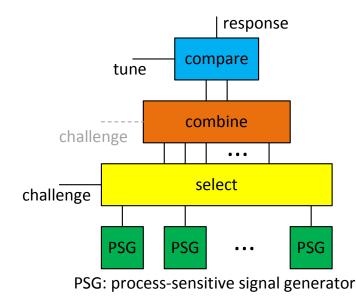

| 2.1 | The conceptual architecture of Strong PUF                            | 10 |

|-----|----------------------------------------------------------------------|----|

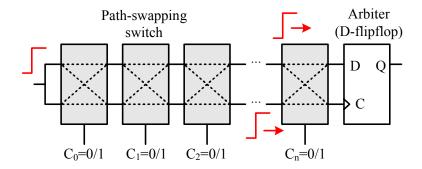

| 2.2 | Arbiter-based PUF introduced in [1]                                  | 11 |

| 2.3 | Optional caption for list of figures                                 | 13 |

| 2.4 | Optional caption for list of figures                                 | 15 |

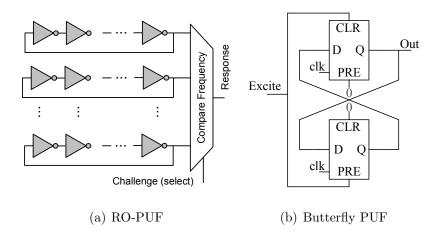

| 3.1 | Delay-based PUF                                                      | 17 |

| 3.2 | TRNG based on sampling the ring oscillator phase jitter              | 21 |

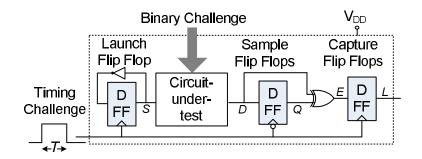

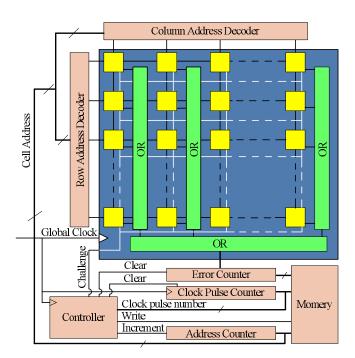

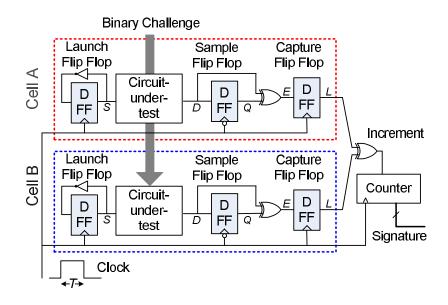

| 4.1 | The timing signature extraction circuit                              | 24 |

| 4.2 | The probability of observing timing failure as a function of clock   |    |

|     | pulse width, $T$                                                     | 27 |

| 4.3 | The architecture for chip level delay extraction of logic components | 28 |

| 4.4 | Two random placement of PUF cells on FPGA.                           | 31 |

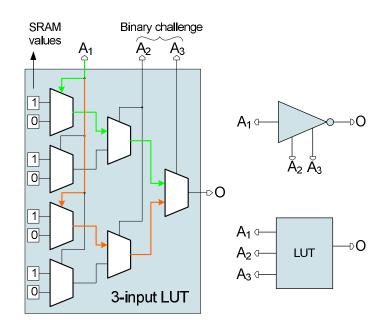

| 4.5 | The internal structure of LUTs. The signal propagation path inside   |    |

|     | the LUTs change as the inputs change.                                | 33 |

| 4.6 | The differential signature extraction system.                        | 38 |

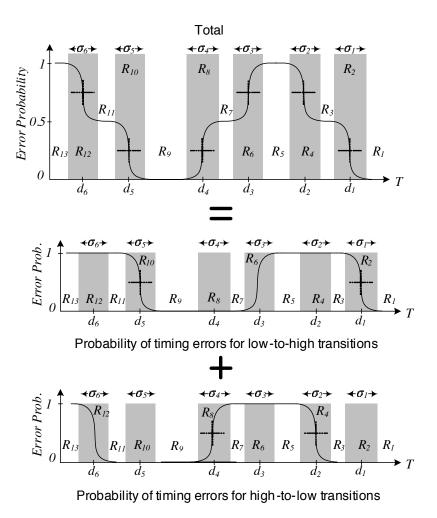

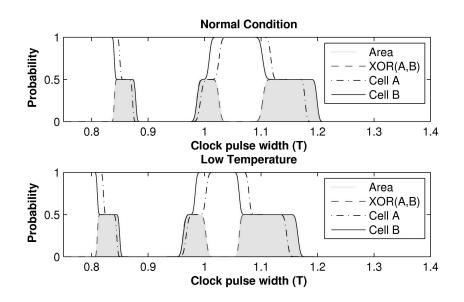

| 4.7 | The timing error probability for two sample PUF cells and the        |    |

|     | resulting XOR output probability under (a) normal operating          |    |

|     | condition and (b) low operating temperature of $-10^{\circ}C$        | 39 |

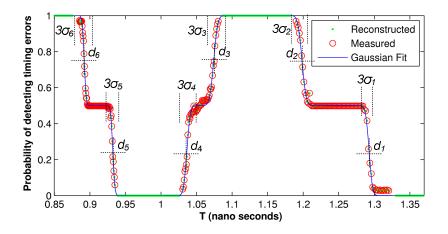

| 4.8 | The probability of detecting timing errors versus the input clock    |    |

|     | pulse width $T$ . The solid line shows the Gaussian fit to the       |    |

|     | measurement data.                                                    | 43 |

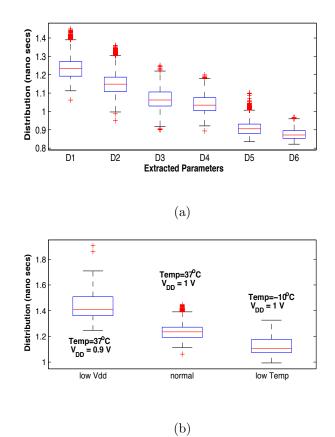

| 4.9 Optional caption for list of figures                                            | 44 |

|-------------------------------------------------------------------------------------|----|

| 4.10 (a) Distribution of delay parameters $d_i$ . (b) The distribution of $d_1$ for |    |

| normal, low operating temperature, and low core voltage. $\ldots$ .                 | 47 |

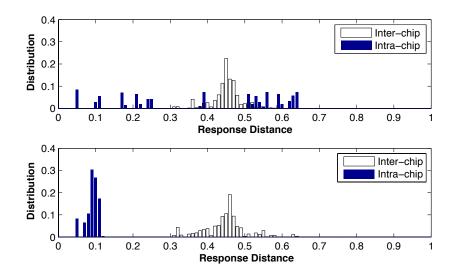

| 4.11 The inter-chip and intra-chip response distances for $T = 0.95 \ ns$ and       |    |

| $N_c = 2$ before (top) and after (bottom) calibration against changes in            |    |

| temperature                                                                         | 48 |

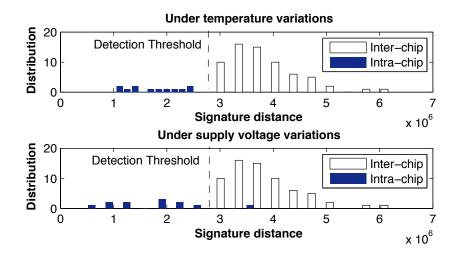

| 4.12 The distribution of the intra- and inter-chip signature ${\cal L}_1$ distances | 50 |

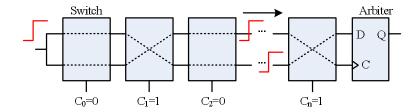

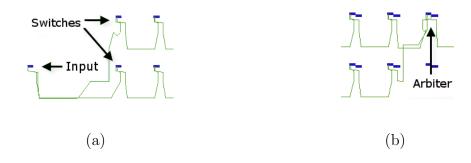

| 4.13 Arbiter-based PUF with path swapping switches                                  | 50 |

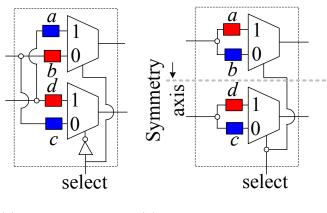

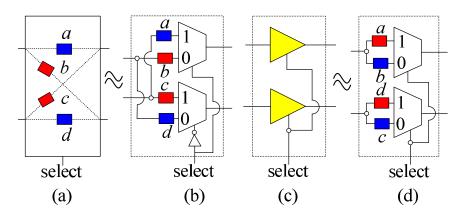

| 4.14 (a),(b) path swapping switch and its delay abstraction (c),(d)                 |    |

| PDL-based switch and its delay abstraction                                          | 53 |

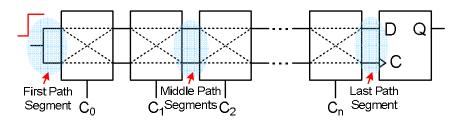

| 4.15 The new arbiter-based PUF structure                                            | 54 |

| 4.16 Reducing the response instability due to arbiter metastability by              |    |

| using majority voting.                                                              | 55 |

| 4.17 Signal propagation delay as a function of temperature                          | 56 |

| 4.18 The distribution of $\Delta_d$ and stability of responses in the corresponding |    |

| partitions.                                                                         | 57 |

| 4.19 The delay measurement circuit. The circuit under test consists of              |    |

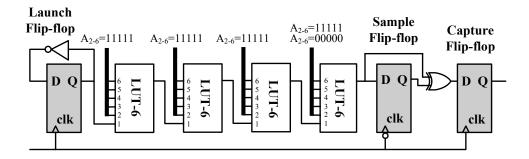

| four LUTs each implementing a PDL                                                   | 59 |

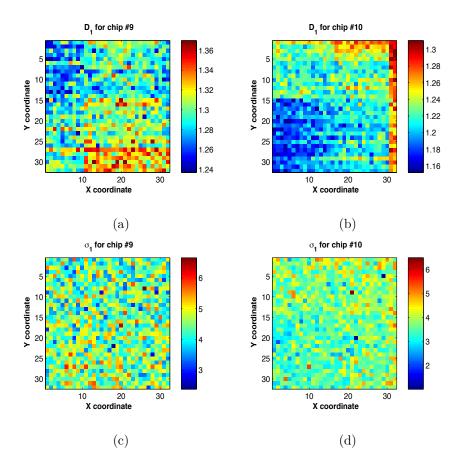

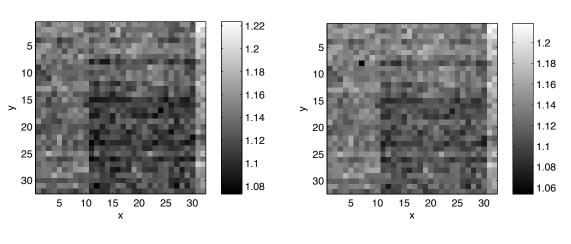

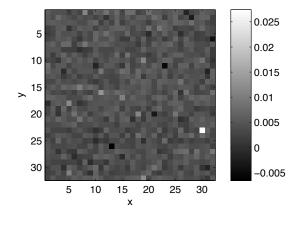

| 4.20 The measured delay of $32 \times 32$ circuit under tests containing a PDL      |    |

| with PDL control inputs being set to (a) $A_{2-6} = 00000$ and (b)                  |    |

| $A_{2-6} = 11111$ respectively. The difference between the delays in these          |    |

| two cases is shown in (c)                                                           | 67 |

| 4.21 Routing and placement of the PUF (a) first segment (b) last segment.           | 67 |

| 4.22 Measurement system setup diagram                                               | 68 |

| 4.23 Lab setup                                                                      | 68 |

| 4.24 Number of '1's in responses (normalized) as a function of tuning level         |    |

| for the PUF on FPGA 6                                                               | 69 |

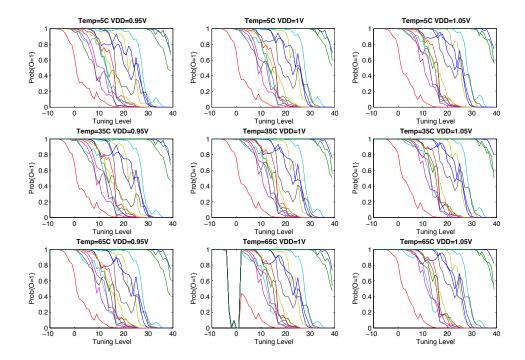

| 4.25 | Distribution of the tuning levels across all PUF rows on all FPGAs          |    |

|------|-----------------------------------------------------------------------------|----|

|      | for different operating conditions.                                         | 70 |

| 4.26 | The probability of majority voting system output being equal to 1 as        |    |

|      | a function of the delay difference                                          | 70 |

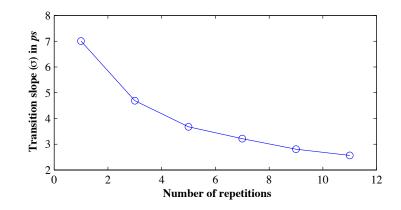

| 4.27 | The sharpness $(\sigma)$ of the transition slope versus the number of       |    |

|      | repetitions for majority voting                                             | 71 |

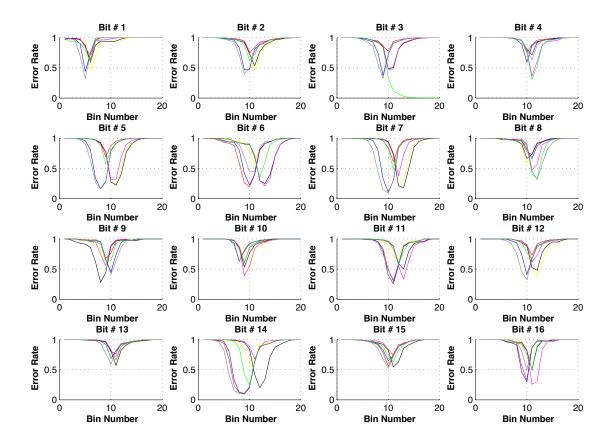

| 4.28 | Response stability measured across different challenge partitions with      |    |

|      | reference to eight operating condition corner cases for FPGA 6. $\ . \ .$ . | 71 |

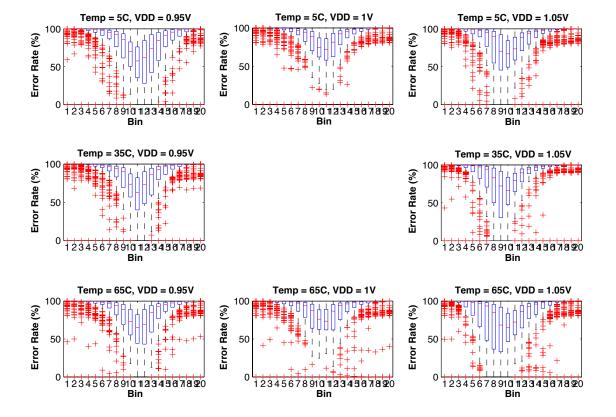

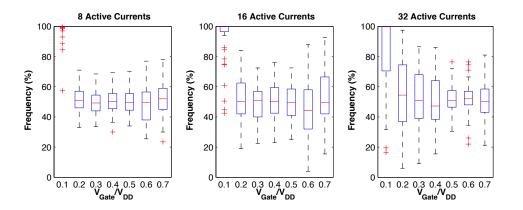

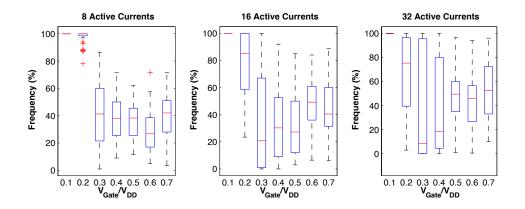

| 4.29 | Boxplot showing the distribution of error rates for a given operating       |    |

|      | condition corner and challenge partition                                    | 72 |

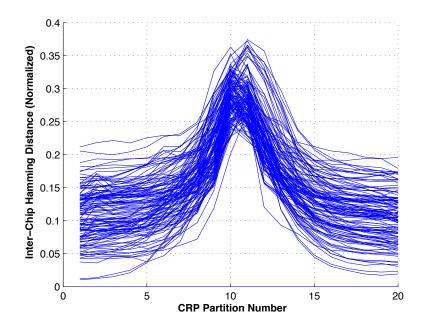

| 4.30 | Entropy of the response to the challenges at each robustness partition.     | 73 |

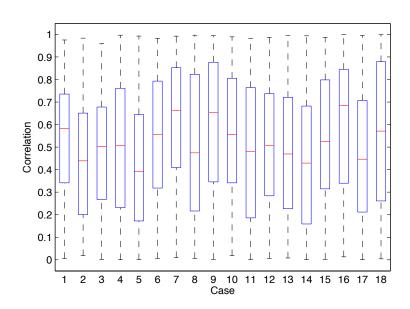

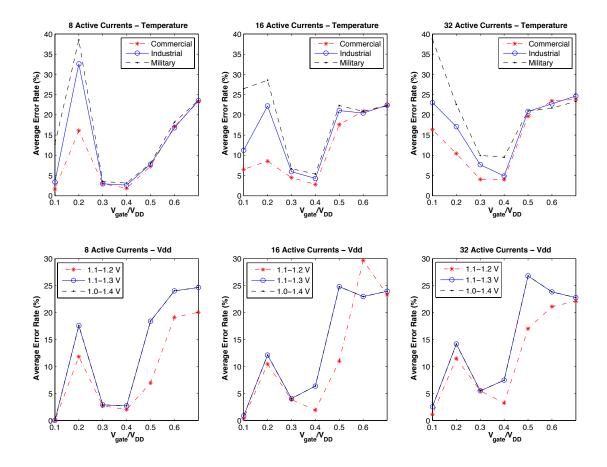

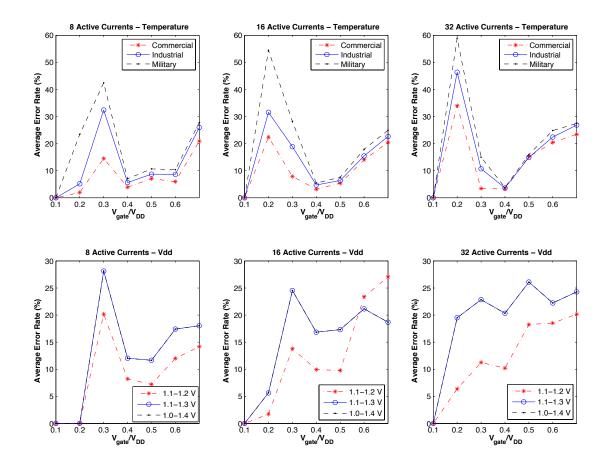

| 4.31 | The correlation between effect of temperature and power supply              |    |

|      | variations on responses for 18 different scenarios. Each box plot is        |    |

|      | made of response correlation values across 12x16 PUFs. $\ldots$ .           | 73 |

|      |                                                                             |    |

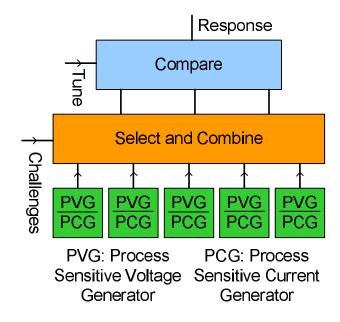

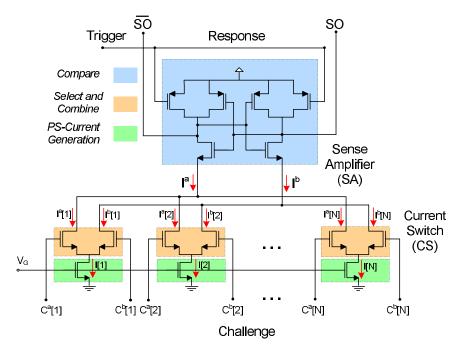

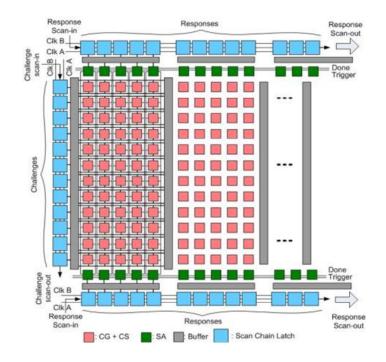

| 5.1  | The conceptual block diagram of the proposed PUF structure                  | 75 |

| 5.2  | The proposed current based PUF system                                       | 76 |

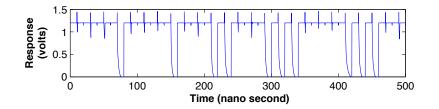

| 5.3  | The sense amplifier output response waveform to a set of random             |    |

|      | challenges                                                                  | 78 |

| 5.4  | The distribution of number of '1's in responses to 100 challenges over      |    |

|      | 100 PUFs obtained from pre-layout monte-carlo simulation                    | 79 |

| 5.5  | The distribution of number of '1's in responses to 100 challenges over      |    |

|      | 100 PUFs obtained from post-layout monte-carlo simulation $\ . \ . \ .$     | 80 |

| 5.6  | The average response error rate as a function of the current generator      |    |

|      | transistor gate voltage obtained from pre-layout monte-carlo simulation.    | 82 |

| 5.7  | The average response error rate as a function of the current generator      |    |

|      | transistor gate voltage obtained from pre-layout monte-carlo simulation.    | 83 |

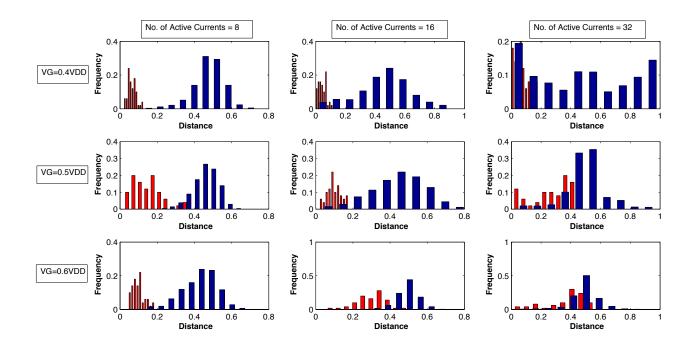

| 5.8  | The inter-die and intra-die response distance distribution under                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | different usage scenarios.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84  |

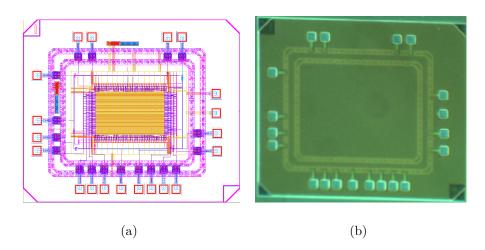

| 5.9  | The floor planning of the PUF components on the die                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84  |

| 5.10 | (a) The PUF chip layout. (b) taped-out chip micrograph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

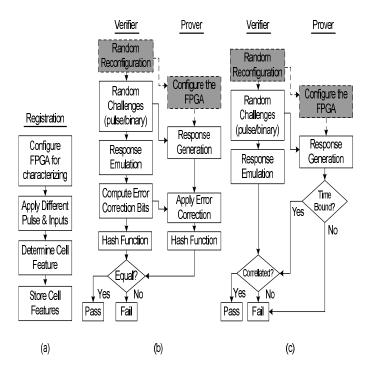

| 6.1  | (a) FPGA registration (b) Classic authentication flow (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|      | Time-bound authentication flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88  |

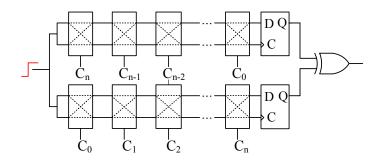

| 6.2  | Two independent linear arbiter PUFs are XOR-mixed in order to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | implement an arbiter PUF with better statistical properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92  |

| 6.3  | The 7 steps of the SlenderPUF lightweight protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94  |

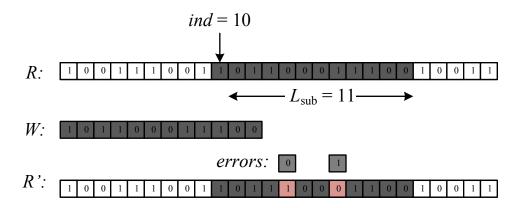

| 6.4  | Top: random selection of an index; Middle: extracting a substring of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | a predefined length; Bottom: the verifier matches the received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|      | substrings to its estimated PUF response stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95  |

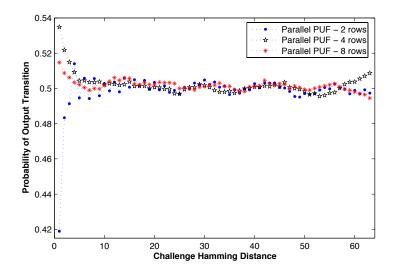

| 6.5  | The probability of the arbiter PUF output flipping versus the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | Hamming distance between two challenge sequences for $2, 4, and 8$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|      | independent XOR-mixed PUFs [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 103 |

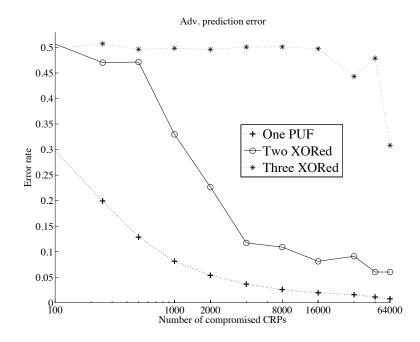

| 6.6  | The modeling error rate for arbiter-based PUF, and XOR PUFs with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|      | 2 and 3 outputs as a function of number of train/test CRPs. $\hfill \hfill \hf$ | 110 |

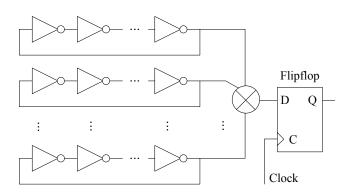

| 6.7  | True random number generation architecture based on flipflop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|      | metastability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114 |

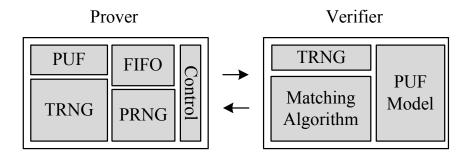

| 6.8  | Resource usage on prover and verifier sides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 115 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

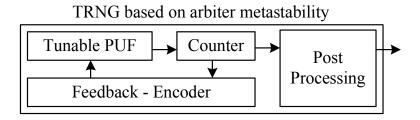

| A.1  | The TRNG system model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 119 |

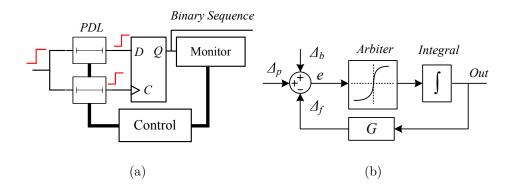

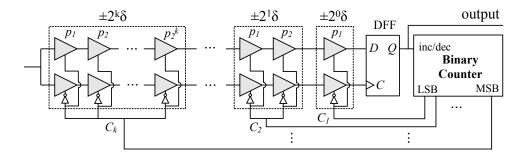

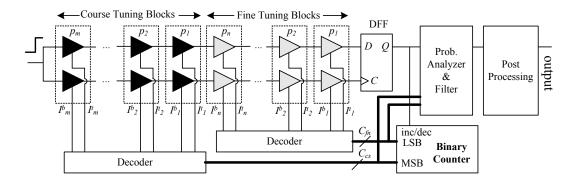

| A.2  | The TRNG system implementation with a PI controller on FPGA. $\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 121 |

| A.3  | Decoding operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 122 |

| A.4  | The complete TRNG system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 124 |

xi

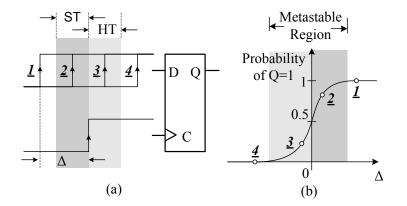

| A.5  | (a) Flip-flop operation under four sampling scenarios, (b) probability     |     |

|------|----------------------------------------------------------------------------|-----|

|      | of output being equal to '1' as a function of the input signals delay      |     |

|      | difference ( $\Delta$ ). The numbers on the probability plot correspond to |     |

|      | each signal arrival scenario.                                              | 125 |

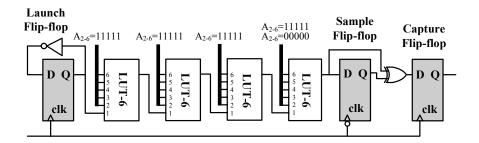

| A.6  | The delay measurement circuit. The circuit under test consists of          |     |

|      | four LUTs each implementing a PDL                                          | 127 |

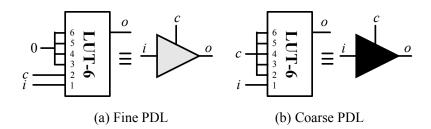

| A.7  | Coarse and fine PDLs implemented by a single 6-input LUT                   | 128 |

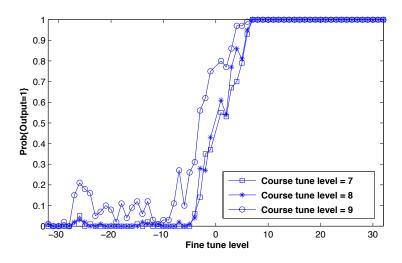

| A.8  | The probability of flip-flip generating a '1' output as a function of the  |     |

|      | fine and coarse tuning levels                                              | 129 |

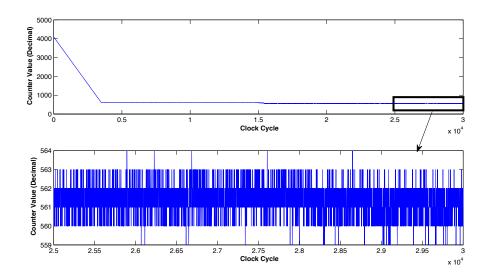

| A.9  | The transient counter value (decimal) versus the clock cycles              | 130 |

| A.10 | Distribution of the steady state counter values and associated bit         |     |

|      | probabilities.                                                             | 131 |

|      |                                                                            |     |

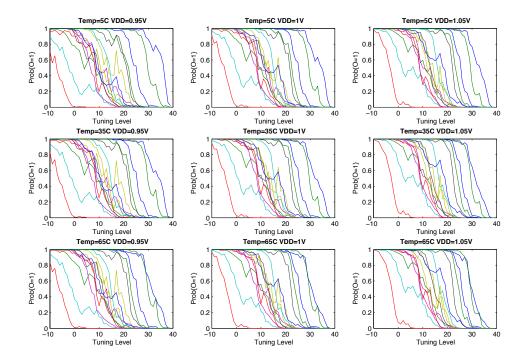

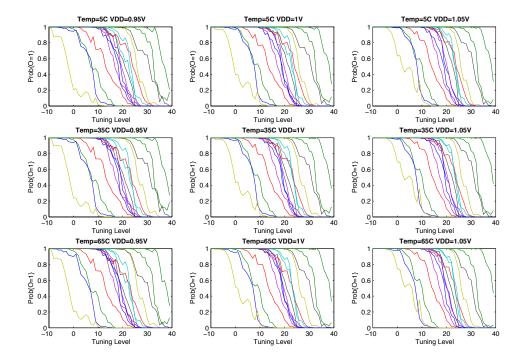

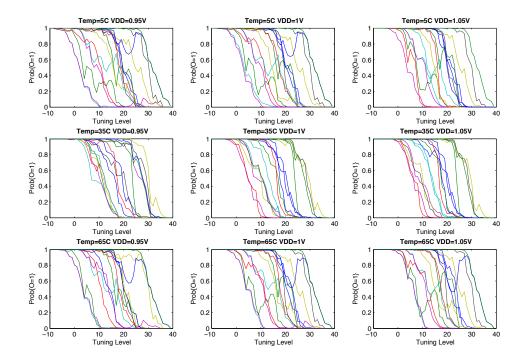

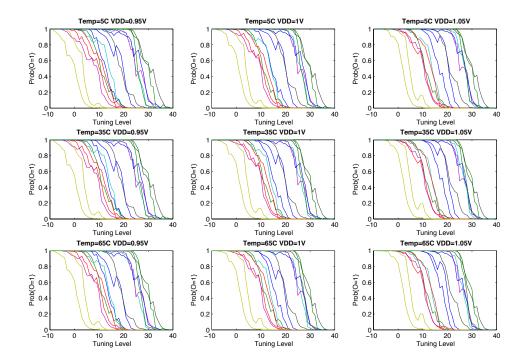

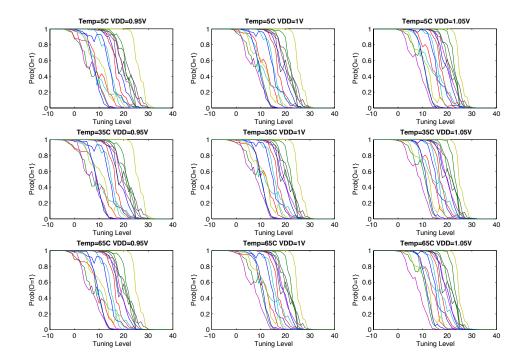

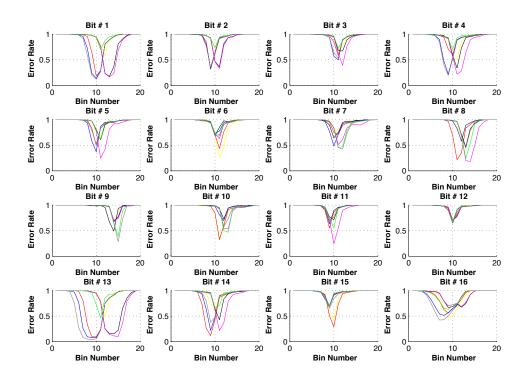

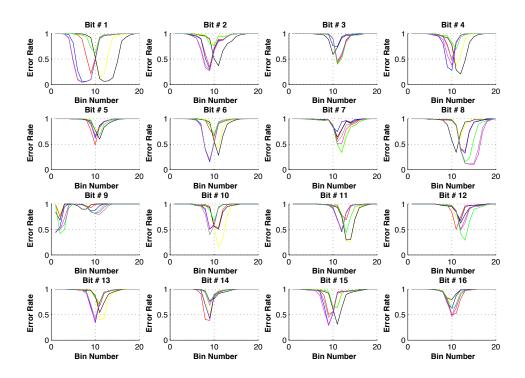

| B.1  | Number of '1's in responses (normalized) as a function of tuning level     |     |

|      | for the PUF on FPGA 6                                                      | 136 |

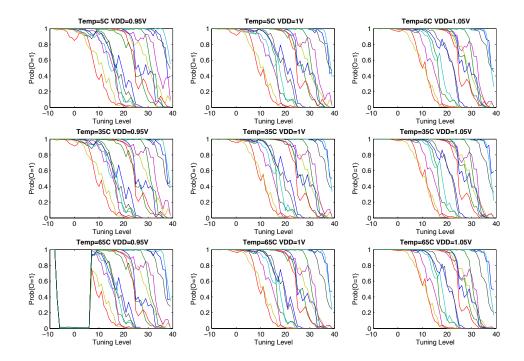

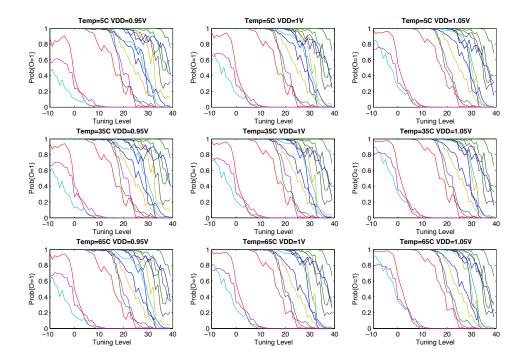

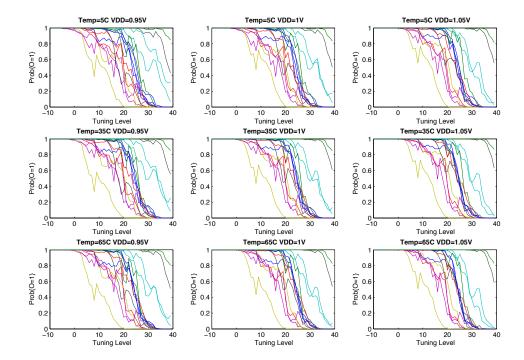

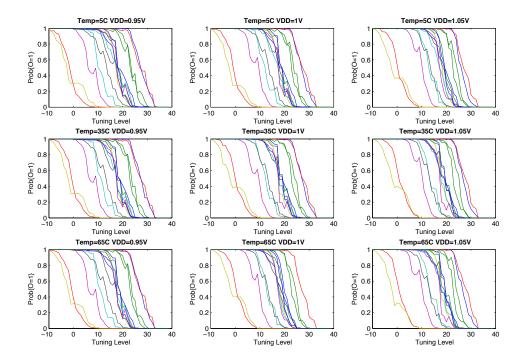

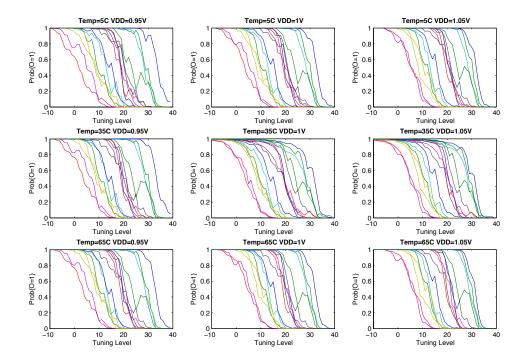

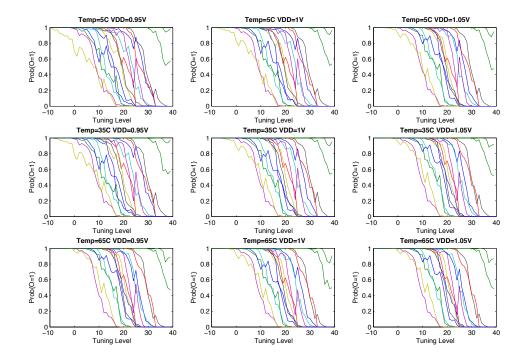

| B.2  | Number of '1's in responses (normalized) as a function of tuning level     |     |

|      | for the PUF on FPGA 7                                                      | 137 |

| B.3  | Number of '1's in responses (normalized) as a function of tuning level     |     |

|      | for the PUF on FPGA 8                                                      | 138 |

| B.4  | Number of '1's in responses (normalized) as a function of tuning level     |     |

|      | for the PUF on FPGA 9                                                      | 139 |

| B.5  | Number of '1's in responses (normalized) as a function of tuning level     |     |

|      | for the PUF on FPGA 10                                                     | 140 |

| B.6  | Number of '1's in responses (normalized) as a function of tuning level     |     |

|      | for the PUF on FPGA 11                                                     | 141 |

| B.7  | Number of '1's in responses (normalized) as a function of tuning level     |     |

|      | for the PUF on FPGA 12                                                     | 142 |

| B.8 Number of '1's in responses (normalized) as a function of tuning level  |     |

|-----------------------------------------------------------------------------|-----|

| for the PUF on FPGA 13                                                      | 143 |

| B.9 Number of '1's in responses (normalized) as a function of tuning level  |     |

| for the PUF on FPGA 14                                                      | 144 |

| B.10 Number of '1's in responses (normalized) as a function of tuning level |     |

| for the PUF on FPGA 15                                                      | 145 |

| B.11 Number of '1's in responses (normalized) as a function of tuning level |     |

| for the PUF on FPGA 16                                                      | 146 |

| B.12 Number of '1's in responses (normalized) as a function of tuning level |     |

| for the PUF on FPGA 17                                                      | 147 |

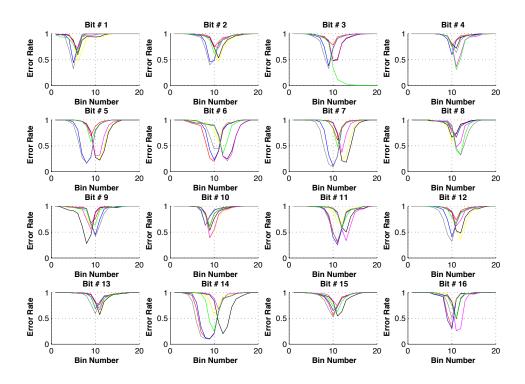

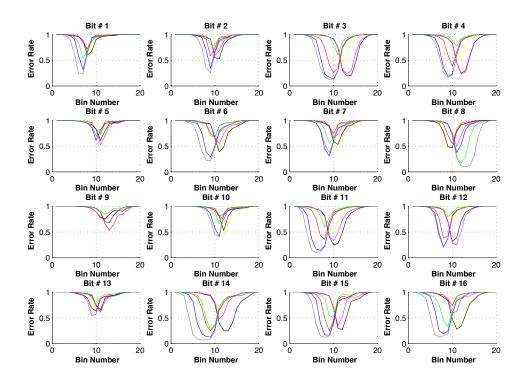

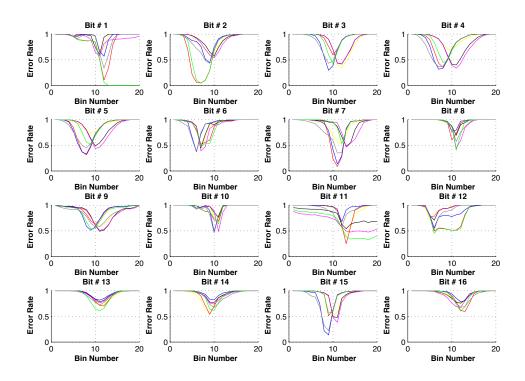

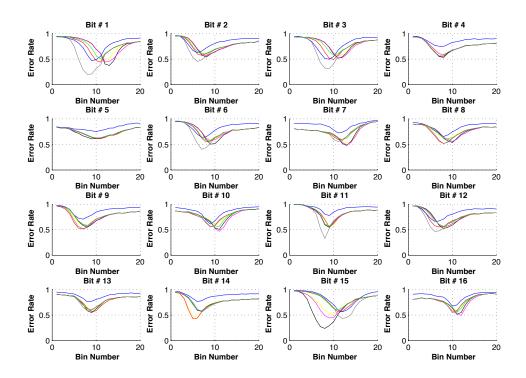

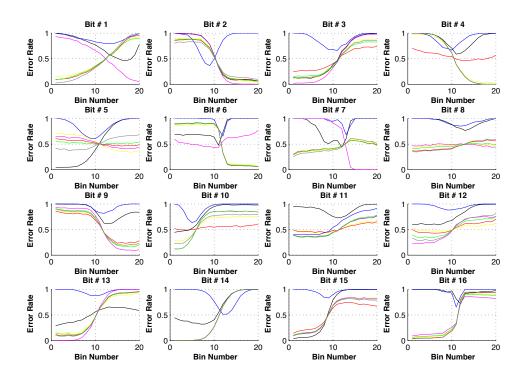

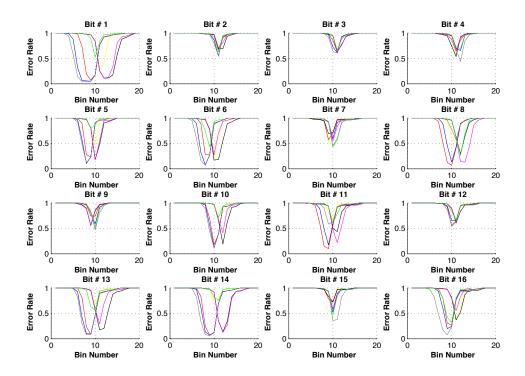

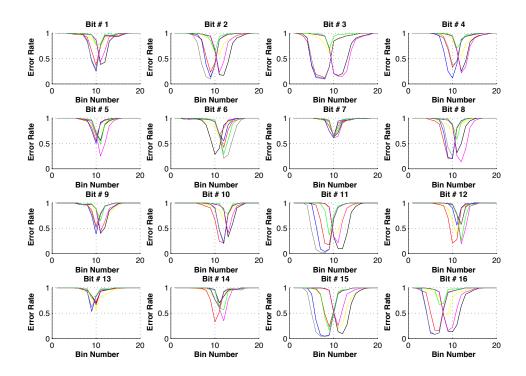

| B.13 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 6. $\ldots$    | 148 |

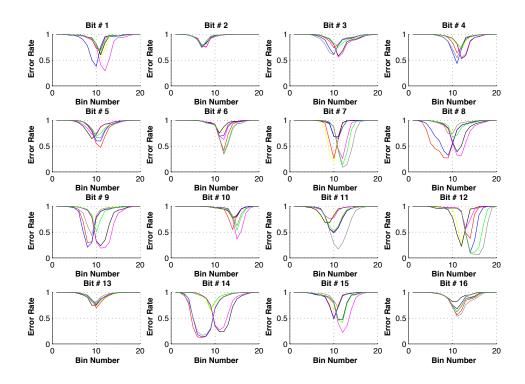

| B.14 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 7. $\ldots$    | 149 |

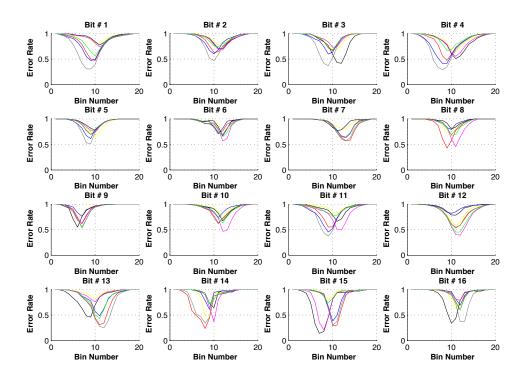

| B.15 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 8. $\ldots$    | 150 |

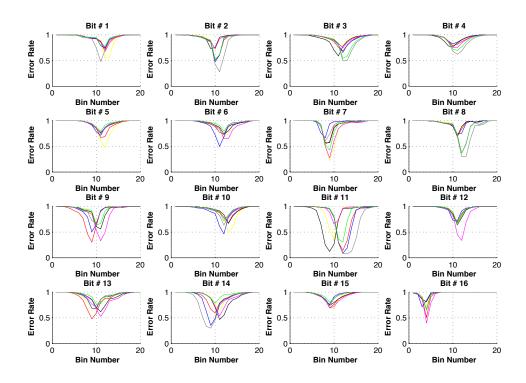

| B.16 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 9. $\ldots$    | 151 |

| B.17 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 10             | 152 |

| B.18 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 11             | 153 |

| B.19 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 12             | 154 |

| B.20 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 13             | 155 |

| B.21 Response stability measured across different challenge partitions with |     |

| reference to eight operating condition corner cases for FPGA 14             | 156 |

- B.22 Response stability measured across different challenge partitions with reference to eight operating condition corner cases for FPGA 15. . . . 157

- B.23 Response stability measured across different challenge partitions with reference to eight operating condition corner cases for FPGA 16. . . . 158

- B.24 Response stability measured across different challenge partitions with reference to eight operating condition corner cases for FPGA 17. . . . 159

# Tables

| 4.1 | (a) probability of false alarm (b) probability of detection        | 45  |

|-----|--------------------------------------------------------------------|-----|

| 4.2 | The probability of detection and false alarm before and after      |     |

|     | performing calibration on the challenge pulse width in presence of |     |

|     | variations in temperature and core voltage                         | 49  |

| 4.3 | 18 correlation cases studies for various increments/decrements on  |     |

|     | temperature and power supply                                       | 66  |

| 6.1 | List of design parameters                                          | 97  |

| 6.2 | Average bit error rate of PUF in different voltage and temperature |     |

|     | conditions in comparison with the ideal PUF output at nominal      |     |

|     | condition.                                                         | 106 |

| 6.3 | Average bit error rate of the Verifiers PUF model against the PUF  |     |

|     | outputs in different voltage and temperate conditions.             | 106 |

| 6.4 | 2-input XOR                                                        | 108 |

| 6.5 | 3-input XOR                                                        | 109 |

| 6.6 | 4-input XOR                                                        | 109 |

| 6.7 | False rejection and acceptance error probabilities for different   |     |

|     | protocol parameters.                                               | 111 |

| 6.8 | Implementation overhead on Virtex 5 FPGA                           | 115 |

| 6.9 | SHA-2 implementation overhead as reported in [3]                   | 116 |

| A.1 | NIST Statistical Test Suite results.                               | 133 |