### Strathprints Institutional Repository

Fletcher, Steven (2013) *Protection of physically compact multiterminal DC power systems.* PhD thesis, University Of Strathclyde.

Strathprints is designed to allow users to access the research output of the University of Strathclyde. Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. You may not engage in further distribution of the material for any profitmaking activities or any commercial gain. You may freely distribute both the url (http:// strathprints.strath.ac.uk/) and the content of this paper for research or study, educational, or not-for-profit purposes without prior permission or charge.

Any correspondence concerning this service should be sent to Strathprints administrator: mailto:strathprints@strath.ac.uk

### University of Strathclyde Department of Electronic and Electrical Engineering

# Protection of Physically Compact Multiterminal DC Power Systems

by

Steven Fletcher

A thesis presented in fulfilment of the requirements for the degree of

Doctor of Philosophy

2013

This thesis is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of a degree.

The copyright of this thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.51. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

#### Abstract

The use of DC for primary power distribution has the potential to bring significant design, cost and efficiency benefits to microgrid, shipboard and aircraft applications. The integration of active converter technologies within these networks is a key enabler for these benefits to be realised, however their influence on an electrical network's fault response can lead to exceptionally demanding protection requirements. This represents a significant barrier to more widespread adoption of DC power distribution. The principle challenge within the field is to develop protection solutions which do not significantly detract from the advantages which DC networks offer. This objective leads the thesis to not only consider how the protection challenges may be overcome but also how this can be achieved in a manner which can benefit the overall design of a system, inclusive of various system design objectives. The thesis proposes that this objective can be achieved through the operation of network protection within the initial transient period following the occurrence of a fault.

In seeking to achieve this aim, the work presented within this thesis makes a number of contributions. The thesis categorises converter type based on the components which influence their fault response and then presents an analysis of the natural fault response of compact multiterminal DC power distribution networks containing these converters. Key factors such as the peak magnitudes and formation times of fault current profiles are determined and quantified as a function of network parameters, enabling protection system operating requirements to be established. Secondary fault effects such as voltage transients are also identified and quantified to illustrate the impact of suboptimal protection system operation. The capabilities of different protection methods and technologies for achieving the proposed operating requirements are then analysed. Significant conclusions are: solid state breaking technologies are essential to achieving operating targets and severe limitations exist with the application of protection methods available within literature for this application. To overcome these shortfalls, novel fault detection approaches are proposed and analysed. These approaches enable fault detection time targets to be met as well as aid with the effective integration of future circuit breaking technologies.

### Contents

| $\mathbf{A}$ | Abstract |                                                                                                                       |           |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------|-----------|

| 1            | Intr     | roduction                                                                                                             | 1         |

|              | 1.1      | Summary of key contributions                                                                                          | 6         |

|              | 1.2      | Dissemination of research outcomes                                                                                    | 8         |

|              |          | 1.2.1 Publications                                                                                                    | 8         |

|              | 1.3      | Thesis outline                                                                                                        | 11        |

|              | 1.4      | Bibliography for Chapter 1                                                                                            | 13        |

| <b>2</b>     | DC       | power networks: architectures, technologies and protection                                                            | 17        |

|              | 2.1      | DC power network design                                                                                               | 17        |

|              |          | 2.1.1 Power system design objectives                                                                                  | 17        |

|              |          | 2.1.2 Review of current and state of the art DC power system                                                          |           |

|              |          | architectures                                                                                                         | 19        |

|              | 2.2      | DC power network protection fundamentals                                                                              | 23        |

|              |          | 2.2.1 Protection system objectives                                                                                    | 23        |

|              |          | 2.2.2 Protection philosophies and their application to DC systems                                                     | 24        |

|              |          | 2.2.3 Protection devices                                                                                              | 31        |

|              | 2.3      | DC power network converter technologies                                                                               | 39        |

|              |          | 2.3.1 Review of active converter topologies and types                                                                 | 39        |

|              |          | 2.3.2 Impact of converter interface type on the protection re-                                                        |           |

|              |          | $quirements \ldots \ldots$ | 46        |

|              | 2.4      | Assessment of significant literature                                                                                  | 51        |

|              |          | 2.4.1 BS EN/IEC 61660-1:1997                                                                                          | 51        |

|              |          | 2.4.2 The status of DC micro-grid protection                                                                          | 53        |

|              |          | 2.4.3 Overcurrent protection on voltage-source-converter-based                                                        |           |

|              |          | multiterminal DC distribution systems                                                                                 | 54        |

|              |          | 2.4.4 Protection of low-voltage DC microgrids                                                                         | 55        |

|              | 2.5      | Areas identified for research                                                                                         | 56        |

|              | 2.6      | Chapter 2 summary                                                                                                     | 57        |

|              | 2.7      | Bibliography for Chapter 2                                                                                            | 59        |

| 3            | DC       | system transient response during faulted, fault clearance and                                                         |           |

|              | post     | t fault conditions                                                                                                    | <b>67</b> |

|              | 3.1      | Analysis of compact DC networks fault response                                                                        | 68        |

|              |          | 3.1.1 Analysis of capacitor discharge                                                                                 | 70        |

|              |          | 3.1.2 Contribution from converter interfaced sources                                                                  | 80        |

|   | 3.2 | Analysis of system behaviour during circuit breaker operation 8                                                                     |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.2.1 Calculation of circuit breaker energy dissipation 8                                                                           |

|   |     | 3.2.2 Calculation of circuit breaker voltage and fault clearance                                                                    |

|   |     | time                                                                                                                                |

|   |     | 3.2.3 Calculation of fault energy let through                                                                                       |

|   | 3.3 | Analysis of post-fault clearance network voltage transient behaviour 8                                                              |

|   | 3.4 | Validation of DC fault analysis                                                                                                     |

|   |     | 3.4.1 Validation of calculated RLC circuit natural response 8                                                                       |

|   |     | 3.4.2 Validation of calculated RLC circuit response including diode                                                                 |

|   |     | $conduction path \dots 9$           |

|   |     | 3.4.3 Validation of post fault clearance transient calculations 9                                                                   |

|   | 3.5 | Chapter 3 summary                                                                                                                   |

|   | 3.6 | Bibliography for Chapter 3                                                                                                          |

| 4 | Det | cermination of protection system requirements for DC elec-                                                                          |

|   |     | al power networks 10                                                                                                                |

|   | 4.1 | Optimising protection system to match design criteria 10                                                                            |

|   | 4.2 | Impact of current response on protection system requirements 10                                                                     |

|   |     | 4.2.1 Impact of peak fault current and time to peak on protection                                                                   |

|   |     | system requirements                                                                                                                 |

|   |     | 4.2.2 Impact of an upper current threshold on the protection                                                                        |

|   |     | system requirements                                                                                                                 |

|   | 4.3 | Impact of voltage response on protection system requirements 10                                                                     |

|   | т.0 | 4.3.1 Undervoltage protection                                                                                                       |

|   |     | 4.3.2 Impact of converter voltage reversal on protection system                                                                     |

|   |     | requirements                                                                                                                        |

|   |     | 4.3.3 Impact of overvoltage transients on protection system re-                                                                     |

|   |     | quirements                                                                                                                          |

|   | 1 1 | Impact of circuit breaker performance on protection system re-                                                                      |

|   | 4.4 | quirements                                                                                                                          |

|   |     | 1                                                                                                                                   |

|   |     | 4.4.1 Impact on circuit breaker energy dissipation                                                                                  |

|   |     | 4.4.2 Impact on circuit breaker voltage and fault clearance time 11                                                                 |

|   |     | 4.4.3 Impact on fault energy let through                                                                                            |

|   |     | 4.4.4 Discussion of results                                                                                                         |

|   | 4.5 | Analysis of networks containing addition filter or current limiting                                                                 |

|   |     | components                                                                                                                          |

|   |     | 4.5.1 Consideration of converters containing series inductive fil-                                                                  |

|   |     | ters or current limiters                                                                                                            |

|   |     | 4.5.2 Effect of including resistive FCLs                                                                                            |

|   |     | 4.5.3 Discussion on use of addition filter or current limiting com-                                                                 |

|   |     | ponents $\ldots \ldots 12$ |

|   | 4.6 | Impact of operating requirements on protection system implemen-                                                                     |

|   |     | tation $\ldots \ldots 12$  |

|   |     | 4.6.1 Implications for circuit breaker technologies                                                                                 |

|   |     | 4.6.2 Implications for fault detection and location methods 12                                                                      |

|   | 4.7 | Chapter summary                                                                                                                     |

|          | 4.8               | Bibliography for Chapter 4                                                                                                         | .30             |

|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>5</b> |                   | timising the roles of unit and non-unit protection methods for the future DC networks 1                                            | 33              |

|          | 5.1               | Non-unit protection implementation within compact DC networks 1<br>5.1.1 Impact of fault resistance on non-unit methods of protec- | 34              |

|          |                   | tion discrimination                                                                                                                | .35             |

|          |                   | 1                                                                                                                                  | 45              |

|          | 5.2               |                                                                                                                                    | 53<br>54        |

|          |                   | ·                                                                                                                                  | 55              |

|          |                   | · · · · · ·                                                                                                                        | .60             |

|          | 5.3               | Optimising the roles of unit and non-unit protection methods within                                                                | .65             |

|          |                   | 5.3.1 Impact of unit protection implementation on overall pro-<br>tection scheme                                                   | .65             |

|          | 5.4               |                                                                                                                                    | .67             |

|          | 5.5               | Bibliography for Chapter 5                                                                                                         | .68             |

| 6        |                   | vel methods of unit protection implementation within DC net-                                                                       | <b>-</b> 1      |

|          | <b>wor</b><br>6.1 |                                                                                                                                    | <b>71</b><br>71 |

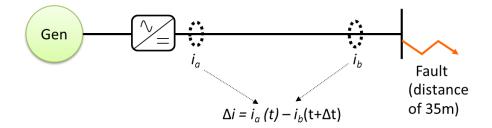

|          | 0.1               | 6.1.1 Current differential scheme with synchronised measurements 1                                                                 |                 |

|          |                   | 6.1.2 Current differential scheme with non-synchronised inputs . 1                                                                 | .78<br>.81      |

|          | 6.2               | Alternative use of threshold currents to overcome the synchronisa-                                                                 | .82             |

|          | 6.3               |                                                                                                                                    | .82             |

|          | 6.4               | Bibliography for Chapter 6                                                                                                         | 84              |

| 7        | Fau               | It detection and location in DC systems from initial $\frac{di}{dt}$ mea-                                                          |                 |

|          |                   |                                                                                                                                    | 85              |

|          | 7.1               | Concept analysis                                                                                                                   | .86             |

|          | 7.2               | Potential application areas and method implementation 1                                                                            | .88             |

|          | 7.3               | Practical limiting aspects and initial assumptions                                                                                 | 90              |

|          |                   | 7.3.1 Fault resistance/impedance                                                                                                   | 90              |

|          |                   | 7.3.2 Internal component resistance and inductance 1                                                                               | .90             |

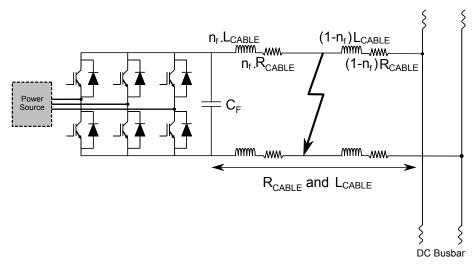

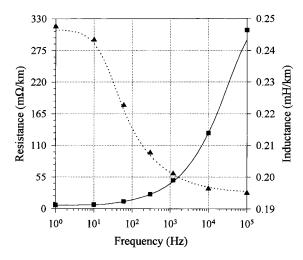

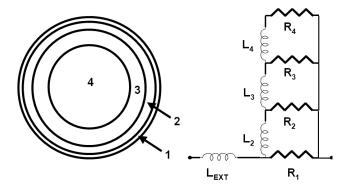

|          |                   | 7.3.3 Varying conductor parameters                                                                                                 | 92              |

|          |                   | 7.3.4 Maximum $\frac{di}{dt}$ from the capacitor                                                                                   | 92              |

|          | 7.4               | <i>ut.</i> -                                                                                                                       | .95             |

|          |                   |                                                                                                                                    | 95              |

|          |                   |                                                                                                                                    | .95             |

|          |                   |                                                                                                                                    | .98             |

|          |                   |                                                                                                                                    | 200             |

|          |                   |                                                                                                                                    |                 |

|     | 7.4.5        | Initial response with parallel capacitors and common branch                                 |             |

|-----|--------------|---------------------------------------------------------------------------------------------|-------------|

|     |              | fault location                                                                              | 201         |

|     | 7.4.6        | Impact of circuit breaking transients on initial $\frac{di}{dt}$ response                   | 203         |

| 7.5 | Impler       | mentation and measurement requirements of an initial $\frac{di}{dt}$                        |             |

|     | based        | protection scheme                                                                           | 204         |

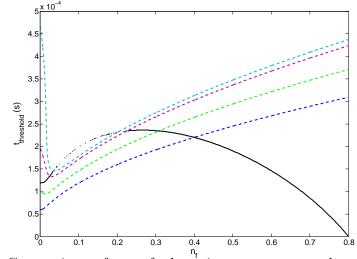

|     | 7.5.1        | Initial $\frac{di}{dt}$ fault detection with variable zone coverage due to                  |             |

|     |              | parameter and measurement uncertainty                                                       | 205         |

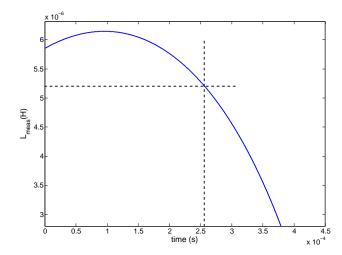

|     | 7.5.2        | Variable zone coverage due to exponential decay of $\frac{di}{dt}$                          | 206         |

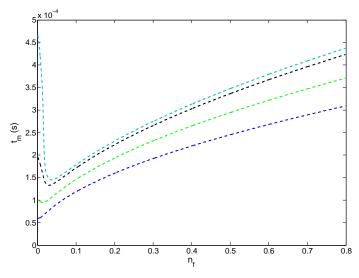

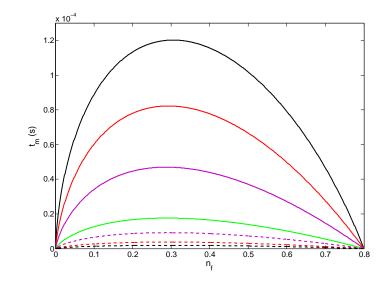

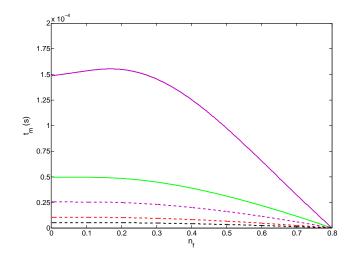

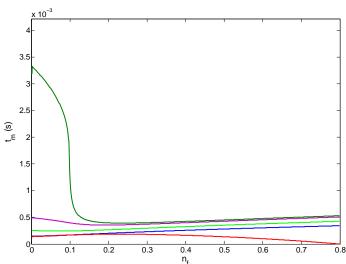

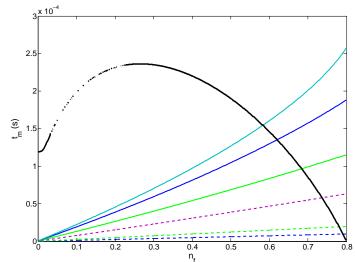

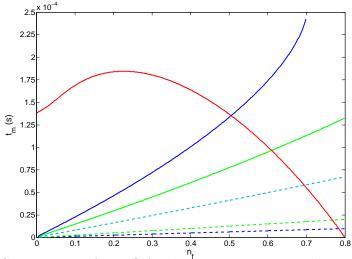

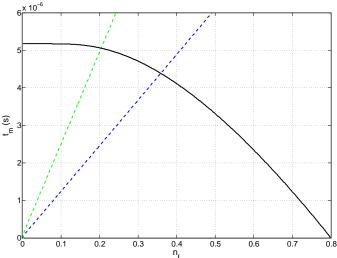

|     | 7.5.3        | Use of Newton's method to define $n_f - t_m$ characteristic for                             |             |

|     |              | multiple fault conditions                                                                   | 208         |

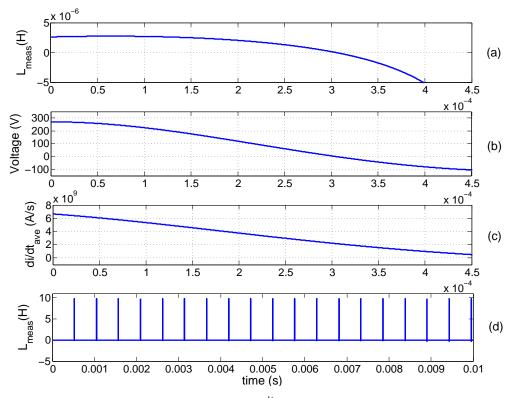

|     | 7.5.4        | Impact of practical measurement conditions                                                  | 210         |

|     | 7.5.5        | Comparison of measurement requirements for discrimina-                                      |             |

|     |              | tion and other protection operation criteria                                                | 222         |

|     | 7.5.6        | Discussion of results                                                                       | 227         |

| 7.6 |              | ional operating schemes, considerations and applications                                    | 229         |

|     | 7.6.1        | Integration of instantaneous over<br>current and initial $\frac{di}{dt}$ pro-               |             |

|     |              | tection                                                                                     | 229         |

|     | 7.6.2        | Addition of a blocking zone for distant faults using initial                                | 220         |

|     |              | $\frac{di}{dt}$ measurement                                                                 | 230         |

|     | 7.6.3        | Compensation of initial line voltage drop                                                   | 232         |

|     | 7.6.4        | Measurement of second derivative                                                            | 234         |

|     | 7.6.5        | Detection of earth faults                                                                   | 235         |

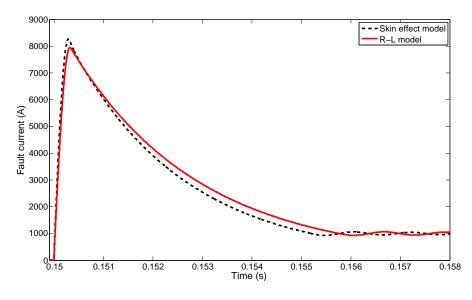

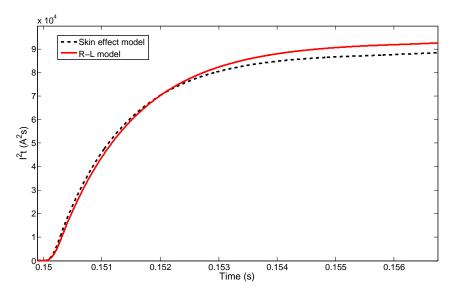

|     | 7.6.6        | Impact of incorporating skin effect on the analysis of fault response                       | 236         |

|     | 7.6.7        | Impact of varying mutual inductance within compact and                                      | 230         |

|     | 1.0.1        | power dense networks                                                                        | 242         |

|     | 7.6.8        | Impact of means of fault onset/inception and changing fault                                 | 414         |

|     | 1.0.0        | conditions                                                                                  | 242         |

|     | 7.6.9        | Application in HVDC and AC transmission systems                                             | 243         |

|     | 7.6.10       |                                                                                             | 243         |

|     | 7.6.11       | Integration with converter protection systems                                               | 243         |

| 7.7 | Chapt        | er summary                                                                                  | 244         |

| 7.8 | Biblio       | graphy for Chapter 7                                                                        | 245         |

| C   |              |                                                                                             | <b>a</b> 40 |

|     |              | ns, contributions and future work                                                           | 249         |

| 8.1 |              | w of chapter conclusions and contributions                                                  | 249         |

| 8.2 | Rey al 8.2.1 | reas of future work                                                                         | 252         |

|     | 0.2.1        | Optimisation of protection system design through combi-<br>nation of operating requirements | 252         |

|     | 8.2.2        | Quantification of the impact of protection system operation                                 | 253         |

|     | 0.2.2        | on overall system design                                                                    | 253         |

|     | 8.2.3        | Demonstration of microprocessor based current differential                                  | 200         |

|     | 0.2.0        | schemes                                                                                     | 254         |

|     | 8.2.4        | Development and demonstration of $\frac{di}{dt}$ based protection scheme                    |             |

| 8.3 |              | uding remarks                                                                               | 254         |

|     |              |                                                                                             |             |

8

## List of Figures

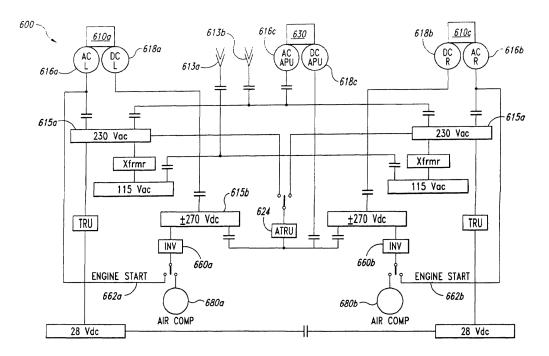

| 2.1  | Single line diagram of Boeing 787 electrical system architecture [11]                            | 19 |

|------|--------------------------------------------------------------------------------------------------|----|

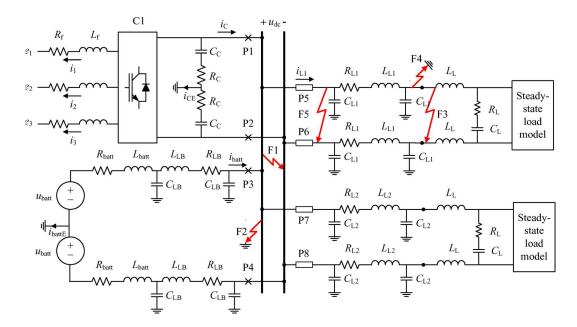

| 2.2  | Example of a DC microgrid network section [12]                                                   | 21 |

| 2.3  | Example of a proposed shipboard electrical system architecture                                   |    |

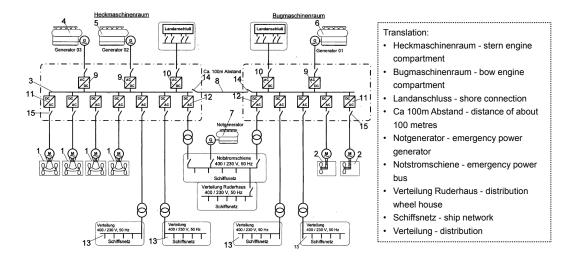

|      | based on interconnected DC busbars [13]                                                          | 22 |

| 2.4  | Example of a DC ring electrical power system architecture for a                                  |    |

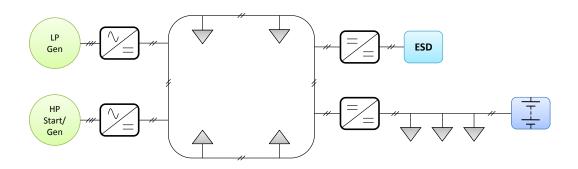

|      | UAV                                                                                              | 22 |

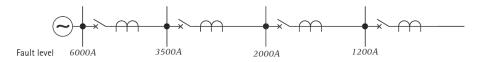

| 2.5  | Radial current distribution line with reducing fault level [17]                                  | 25 |

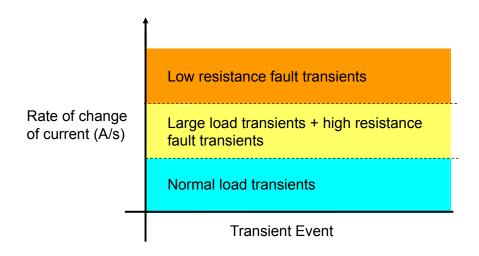

| 2.6  | Fault detection regions for $\frac{di}{dt}$ protection systems                                   | 26 |

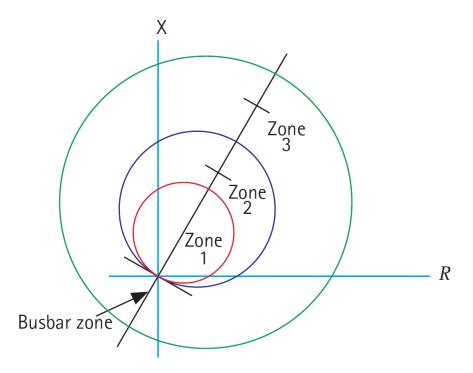

| 2.7  | Mho characteristic with zones of protection [23]                                                 | 27 |

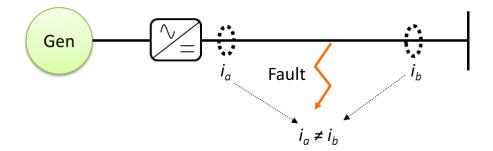

| 2.8  | Current differential scheme with fault external to the protected zone                            | 29 |

| 2.9  | Current differential scheme with fault within the protected zone .                               | 29 |

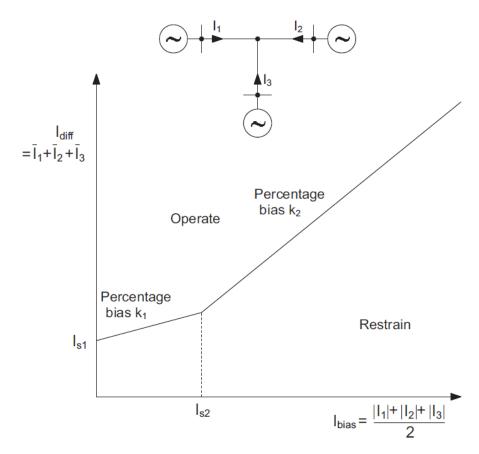

| 2.10 | Typical bias characteristic of a relay [28]                                                      | 30 |

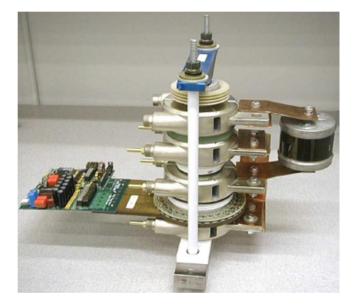

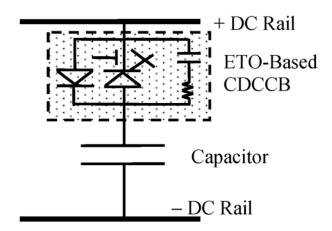

| 2.11 | Prototype of an ETO based DCCB [36]                                                              | 32 |

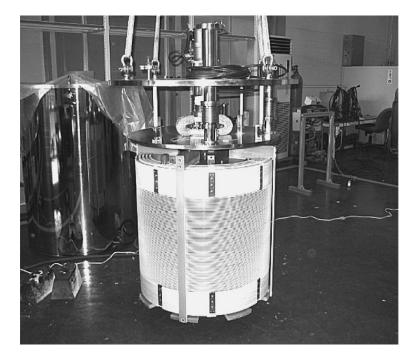

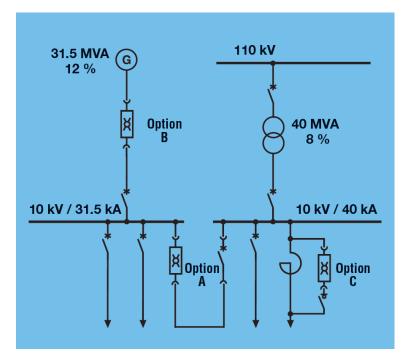

| 2.12 |                                                                                                  | 34 |

| 2.13 | Application of Is-limiters [47]                                                                  | 35 |

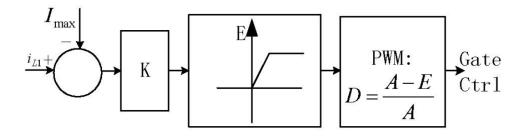

| 2.14 | Pulse by pulse current limiting switch control circuit block dia-                                |    |

|      | gram [48]                                                                                        | 36 |

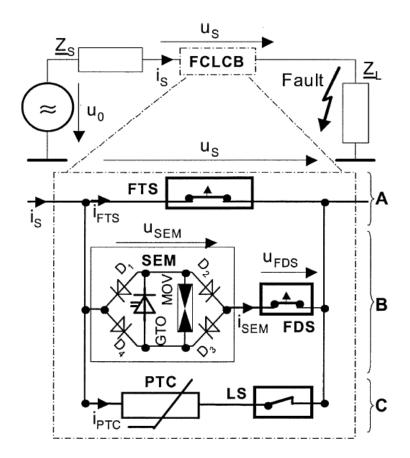

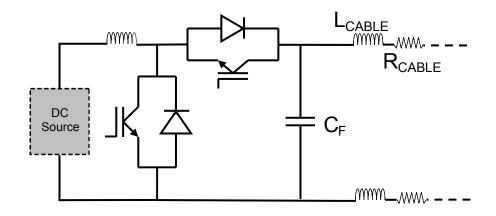

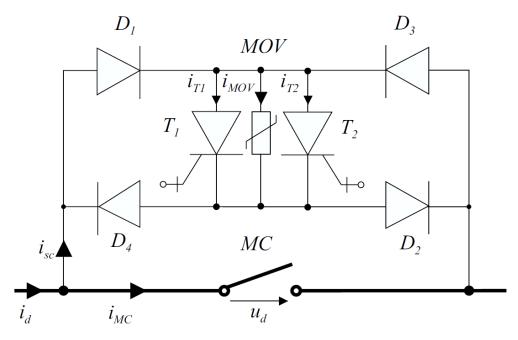

| 2.15 | Hybrid fault current limiting circuit breaker [38]                                               | 37 |

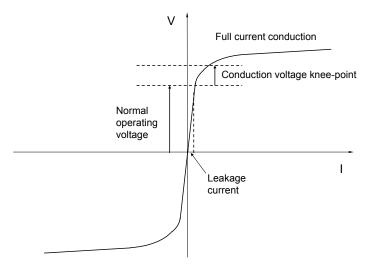

|      | Typical surge arrestor V/I response                                                              | 38 |

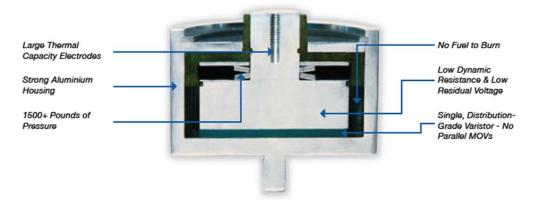

|      | Cross Section of a Raycap StrikeSorb surge arrestor [55]                                         | 39 |

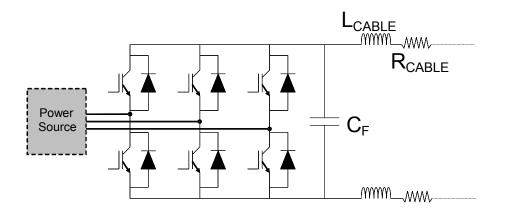

| 2.18 | Standard six switch VSC converter                                                                | 40 |

| 2.19 | Simplified circuit highlighting the antiparallel diode conduction                                |    |

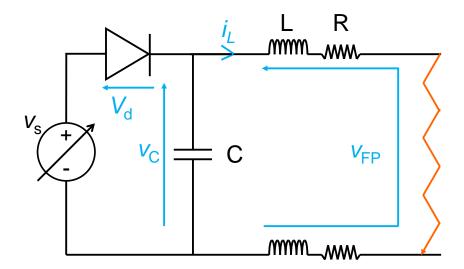

|      | path and back biasing voltages for a VSC                                                         | 41 |

| 2.20 | Two switch buck-boost DC/DC converter topology [63,64]                                           | 42 |

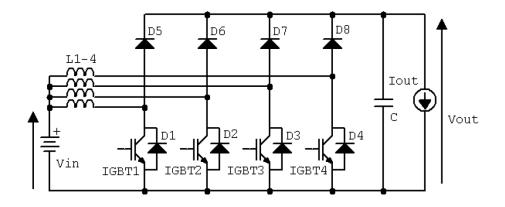

| 2.21 | Interleaved 4-channel boost DC/DC converter [66]                                                 | 43 |

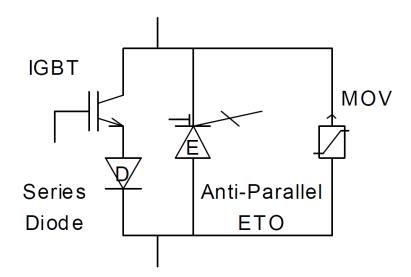

| 2.22 | Switch realisation with IGBT and anti-parallel ETO device [67] .                                 | 43 |

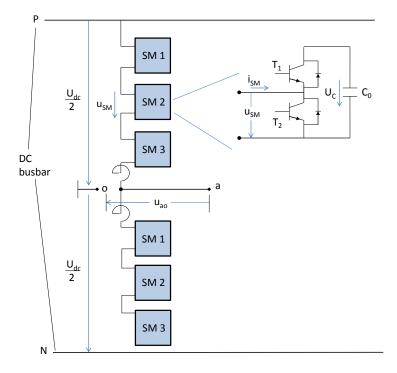

| 2.23 | Single phase diagram of the modular multilevel VSC [71]                                          | 44 |

| 2.24 | BS-EN/IEC 616660-1 standard equivalent circuit for fault current                                 |    |

|      | calculation                                                                                      | 51 |

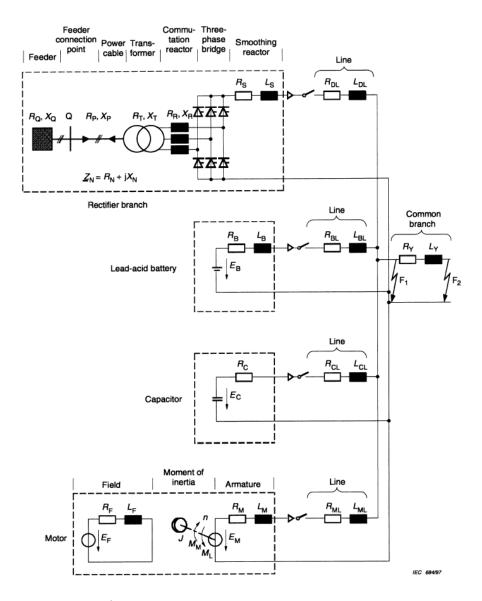

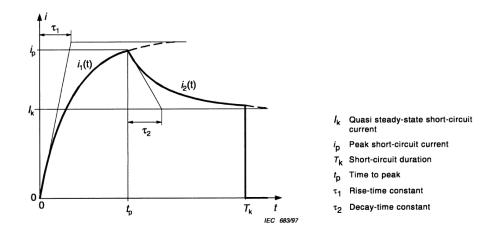

| 2.25 | $\operatorname{BS-EN}/\operatorname{IEC}$ 616660-1 standard fault current approximation function | 52 |

| 2.26 | ETO based capacitive discharge circuit breaker $[14]$                                            | 54 |

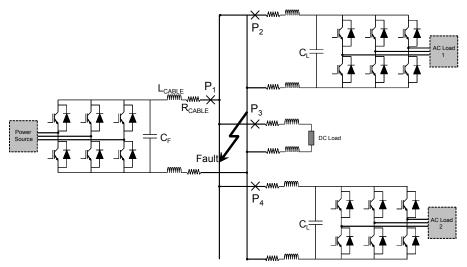

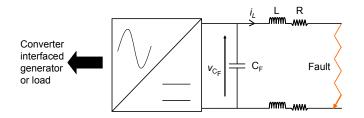

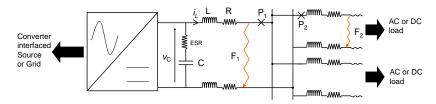

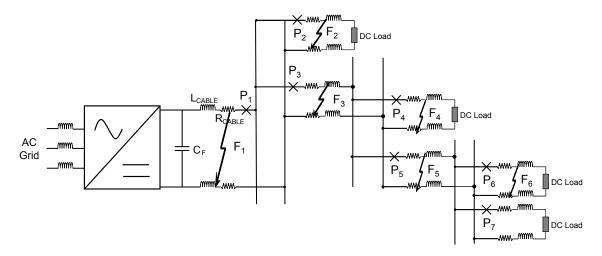

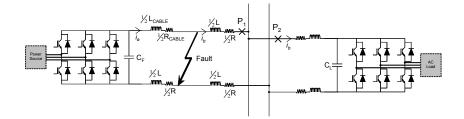

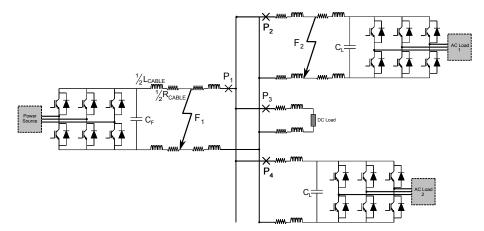

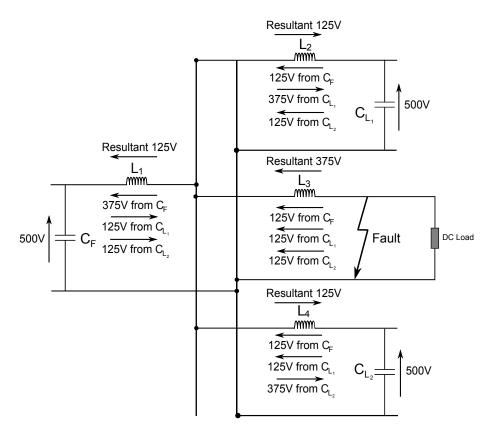

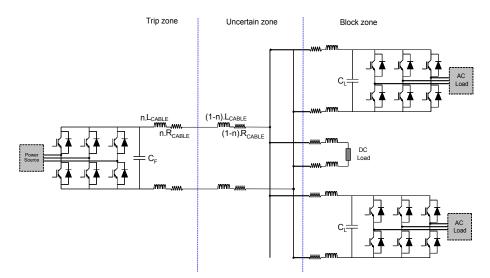

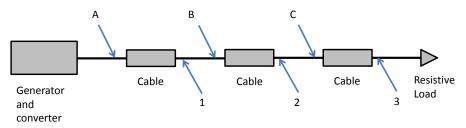

| 3.1  | Example multiterminal DC network                                                                 | 68 |

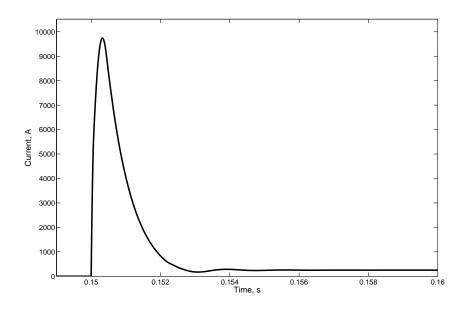

| 3.2  | Simulated fault current for a short-circuit fault on the busbar at                               |    |

|      | 0.15s                                                                                            | 69 |

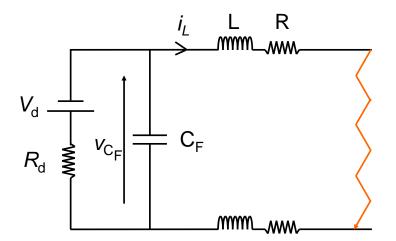

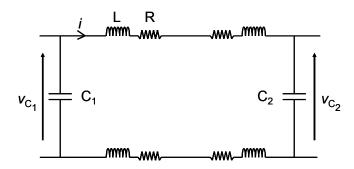

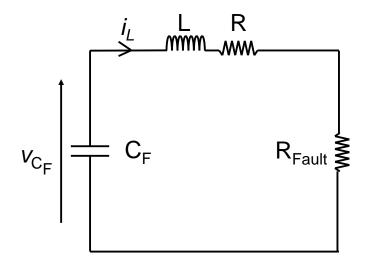

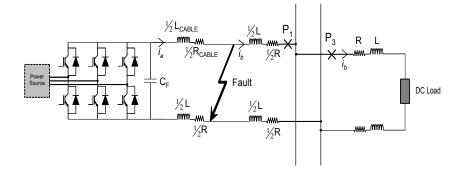

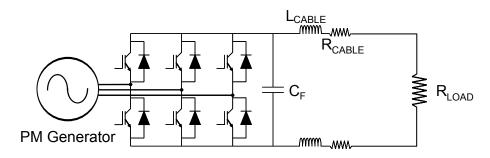

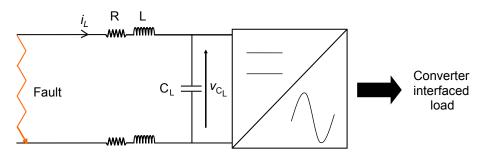

| 3.3  | Equivalent circuit for the faulted network                                                       | 71 |

| 3.4  | Equivalent circuit of the faulted circuit with conducting freewheel-                                 |      |

|------|------------------------------------------------------------------------------------------------------|------|

|      | ing diodes $\ldots$ | 77   |

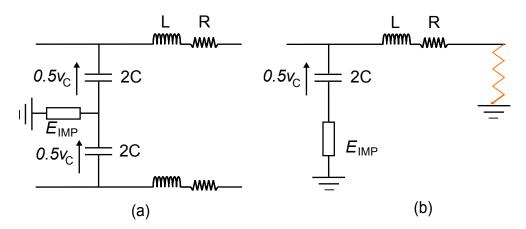

| 3.5  | (a) Mid-point earthing of converter output filter capacitors (b)                                     |      |

|      | Equivalent circuit for a rail to earth fault                                                         | 80   |

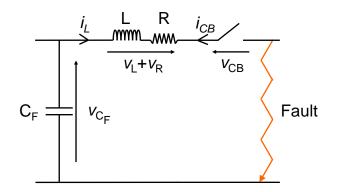

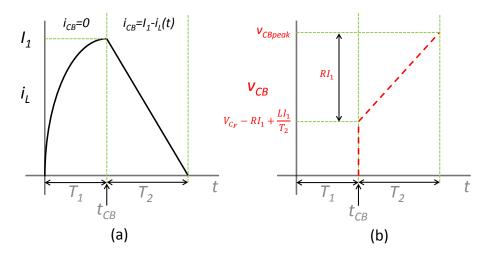

| 3.6  | Equivalent circuit for the faulted network with CB operation                                         | 83   |

| 3.7  | Simplified fault current (a) and circuit breaker voltage (b) response                                |      |

|      | before and after circuit breaker operation                                                           | 83   |

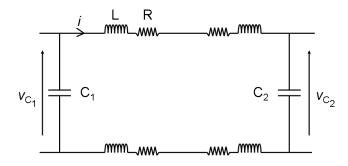

| 3.8  | Equivalent circuit for the post fault clearance network                                              | 88   |

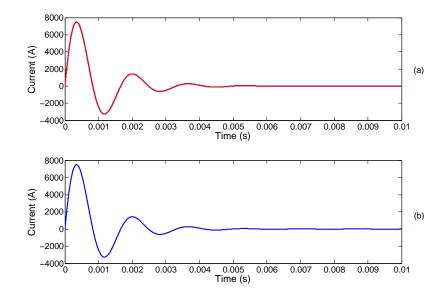

| 3.9  | Simulated RLC circuit                                                                                | 89   |

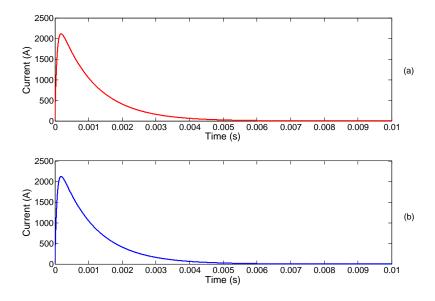

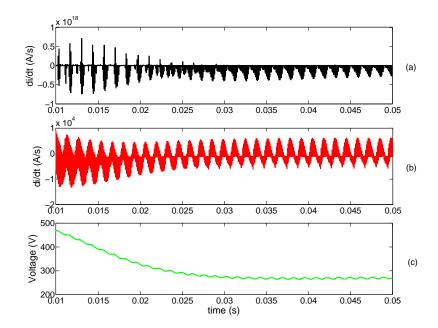

| 3.10 | Comparison of simulated (a) and calculated (b) underdamped RLC                                       |      |

|      | $circuit\ current\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                           | 90   |

| 3.11 | Comparison of simulated (a) and calculated (b) overdamped RLC                                        |      |

|      | circuit current                                                                                      | 91   |

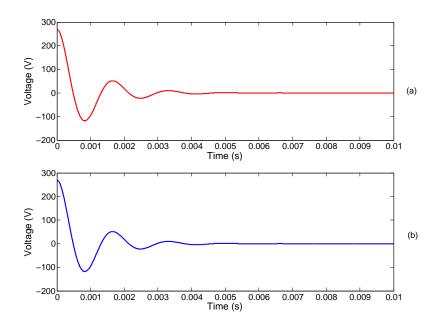

| 3.12 | Comparison of simulated (a) and calculated (b) underdamped RLC                                       |      |

|      | circuit voltage                                                                                      | 91   |

| 3.13 | Comparison of simulated (a) and calculated (b) overdamped RLC                                        |      |

|      | circuit voltage                                                                                      | 92   |

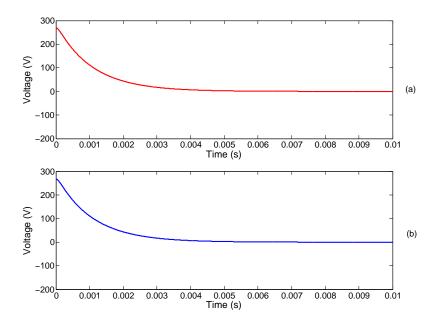

| 3.14 | Comparison of simulated (a) and calculated (b) underdamped RLC                                       |      |

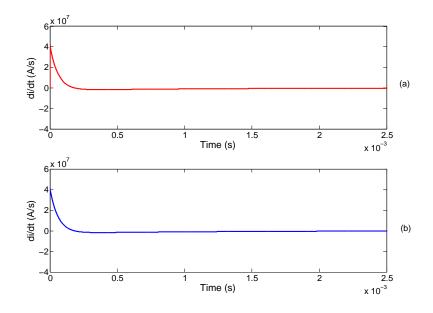

|      | circuit $\frac{di}{dt}$                                                                              | 92   |

| 3.15 | Comparison of simulated (a) and calculated (b) overdamped RLC                                        |      |

|      | circuit $\frac{di}{dt}$                                                                              | 93   |

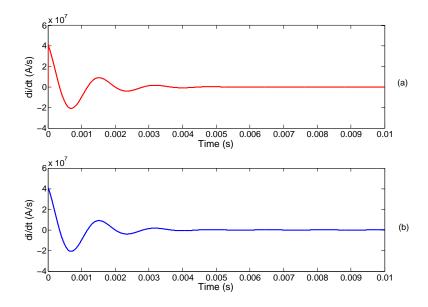

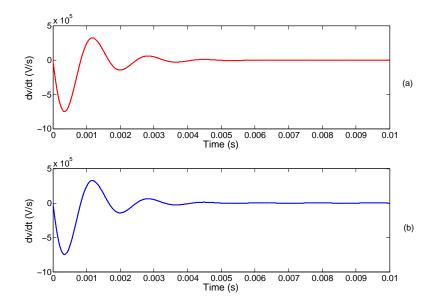

| 3.16 | Comparison of simulated (a) and calculated (b) underdamped RLC                                       |      |

|      | circuit $\frac{dv}{dt}$                                                                              | 93   |

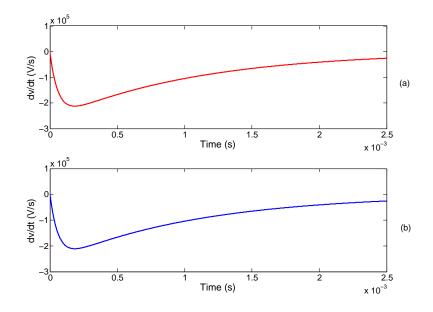

| 3.17 | Comparison of simulated (a) and calculated (b) overdamped RLC                                        |      |

|      | circuit $\frac{dv}{dt}$                                                                              | 94   |

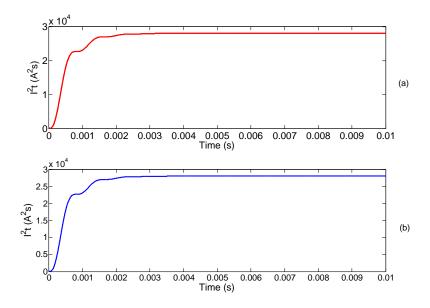

| 3.18 | Comparison of simulated (a) and calculated (b) underdamped RLC                                       |      |

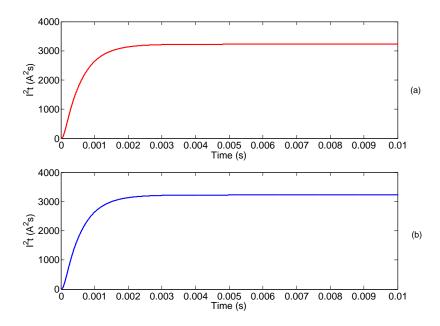

|      | circuit $I^2 t$ response                                                                             | 94   |

| 3.19 | Comparison of simulated (a) and calculated (b) overdamped RLC                                        |      |

|      | circuit $I^2 t$ response                                                                             | 95   |

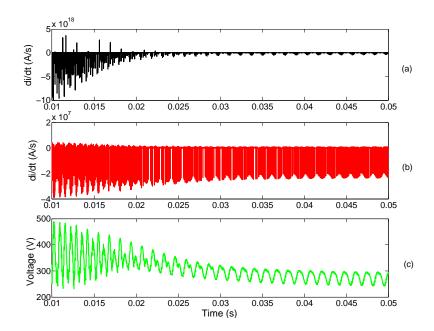

| 3.20 | Comparison of simulated (a) and calculated (b) RLC circuit cur-                                      |      |

|      | rent with diodes conducting following voltage reversal                                               | 96   |

| 3.21 | Comparison of simulated (a) and calculated (b) RLC circuit cur-                                      |      |

|      | rent with diodes conducting following voltage reversal                                               | 96   |

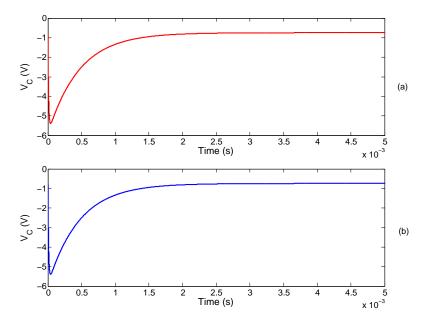

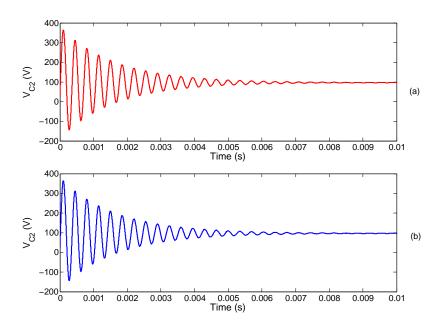

| 3.22 | Comparison of simulated (a) and calculated (b) post fault clearance                                  |      |

|      | equivalent circuit voltage transient                                                                 | 97   |

|      |                                                                                                      |      |

| 4.1  | Line protection with variable zone coverage and fault detection area                                 | s107 |

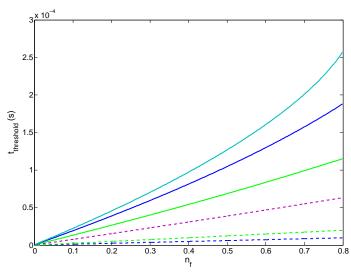

| 4.2  | Comparison of calculated time to current threshold for a range of                                    |      |

|      | fault locations                                                                                      | 107  |

| 4.3  | Comparison of calculated time to voltage threshold for a range of                                    |      |

|      | fault locations and voltage thresholds                                                               | 109  |

| 4.4  | Calculated: (a) Voltage across a converter freewheeling diode and                                    |      |

|      | (b) subsequent current through the diode                                                             | 110  |

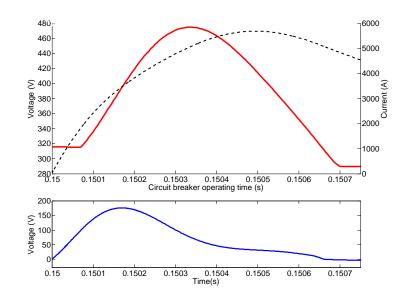

| 4.5          | Simulated maximum voltage caused by circuit breaker operation<br>(upper plot - solid line) after a short circuit fault occurs at 0.15s                                                                      |                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

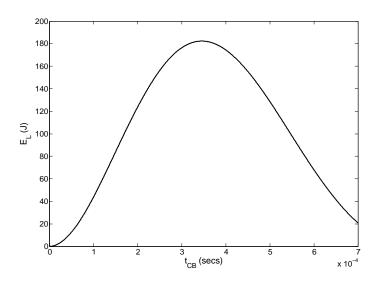

| 4.6          | compared to varying initial conditions. Potential fault current (up-<br>per plot - dashed line), capacitor voltage difference (lower plot)<br>Calculated inductive stored energy to be dissipated in the CB | 112               |

| 4.0          | against operating time                                                                                                                                                                                      | 113               |

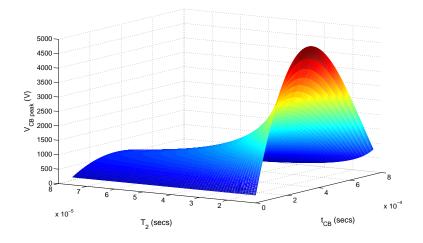

| 4.7          | Calculated impact of CB operation time and fault clearance time<br>on required circuit breaker voltage                                                                                                      | 114               |

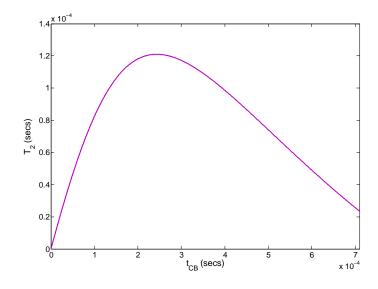

| 4.8          | Calculated example $T_2$ against $t_{CB}$ plot for a peak CB voltage of 540V                                                                                                                                | 115               |

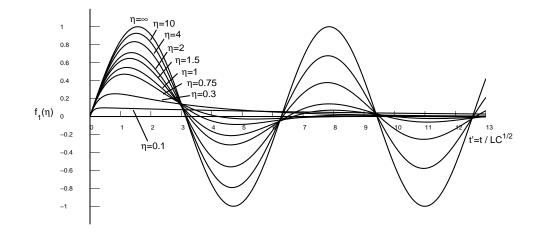

| 4.9          | Generalised damping plots for series RLC circuits based on the                                                                                                                                              |                   |

| 4.10         | ratio of surge impedance to resistance                                                                                                                                                                      | 122               |

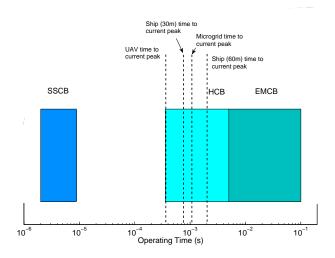

| 4.11         | peak in different applications                                                                                                                                                                              | $\frac{125}{126}$ |

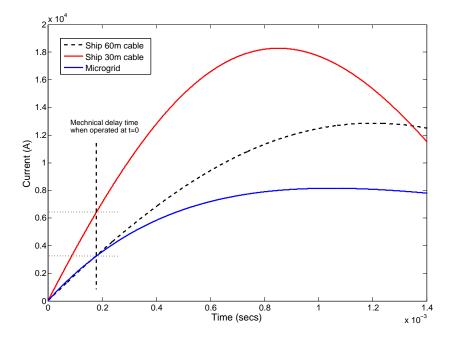

|              | Calculated fault current profile for the microgrid and ship systems described in table 4.1                                                                                                                  |                   |

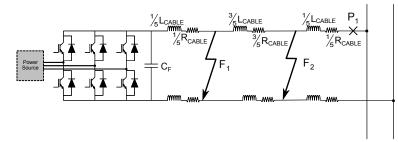

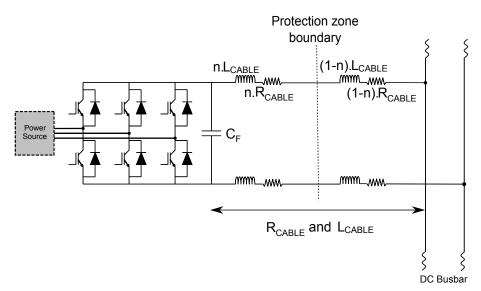

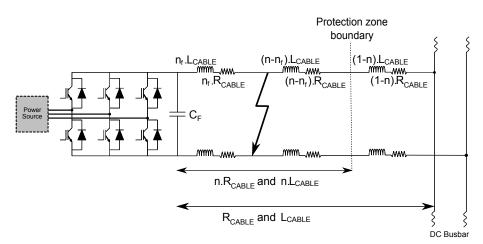

| 5.1          | Equivalent circuit for the faulted network                                                                                                                                                                  | 126<br>136        |

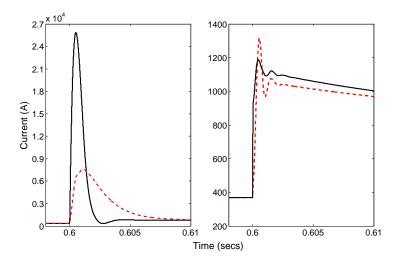

| $5.1 \\ 5.2$ | Simulated network current response for $1m\Omega$ (left) and $500m\Omega$                                                                                                                                   |                   |

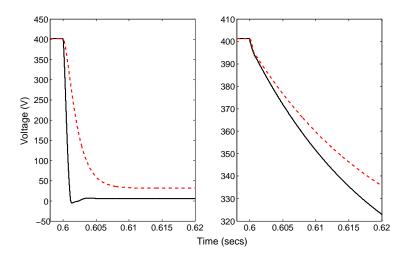

| 5.3          | (right) faults at $F_1$ (solid) and $F_2$ (dotted)                                                                                                                                                          | 137               |

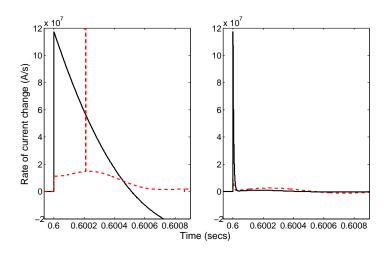

| 5.4          | (right) faults at $F_1$ (solid) and $F_2$ (dotted)                                                                                                                                                          | 139               |

|              | faults at $F_1$ (solid) and $F_2$ (dotted)                                                                                                                                                                  | 141               |

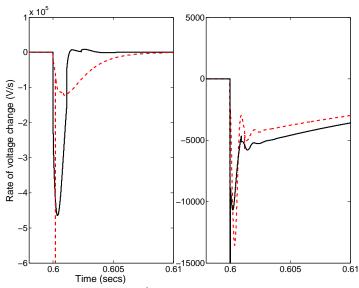

| 5.5          | Simulated network $\frac{dv}{dt}$ response for $1m\Omega$ (left) and $500m\Omega$ (right) faults at $F_1$ (solid) and $F_2$ (dotted)                                                                        | 142               |

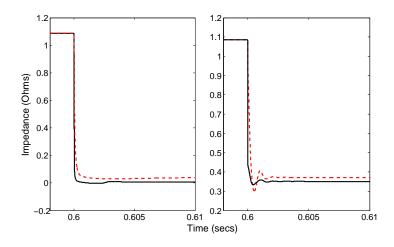

| 5.6          | Simulated network impedance response for $1m\Omega$ (left) and $500m\Omega$ (right) faults at $F_1$ (solid) and $F_2$ (dotted)                                                                              | 144               |

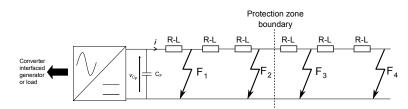

| $5.7 \\ 5.8$ | Network diagram                                                                                                                                                                                             | 146               |

|              | and $500m\Omega$ (right) faults at $F_1$                                                                                                                                                                    | 150               |

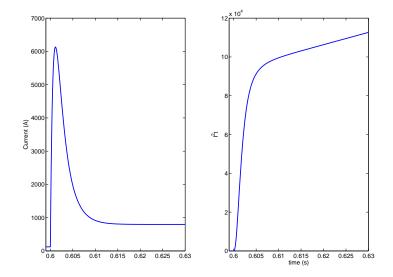

| 5.9          | Simulated current (left) and $i^2t$ (right) response for $1m\Omega$ fault at $F_2$ and $F_3$                                                                                                                | 151               |

|              | Current differential scheme with passive load connected                                                                                                                                                     | 155               |

|              | Current differential scheme with active load connected                                                                                                                                                      | 157               |

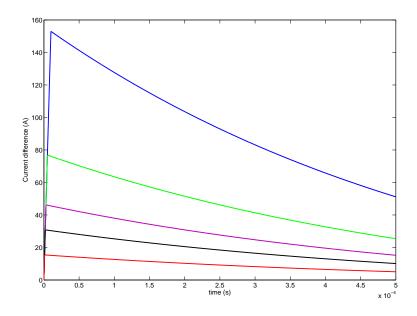

| 0.12         | Calculated comparison of current difference resulting from non-<br>synchronisation of current differential zone measurements. From                                                                          |                   |

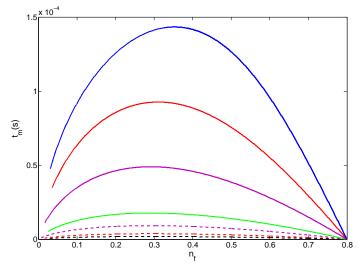

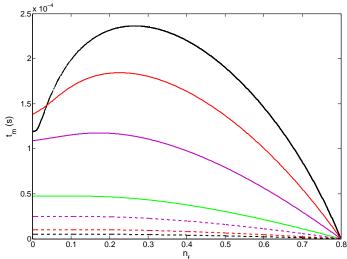

|              | bottom to top the time synchronisation error is $1\mu s$ (Red), $2\mu s$ (Black), $3\mu s$ (Purple), $5\mu s$ (Green), $10\mu s$ (Blue)                                                                     | 164               |

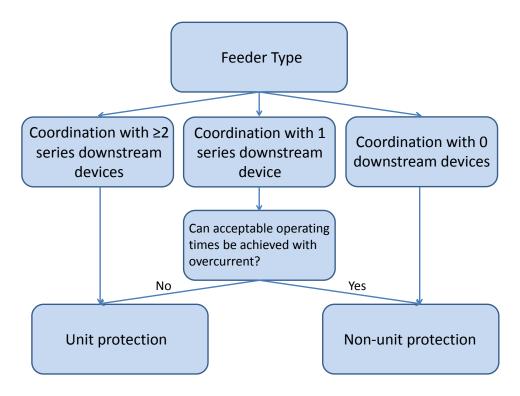

| 5.13         | Protection scheme approach decision tree                                                                                                                                                                    | $164 \\ 166$      |

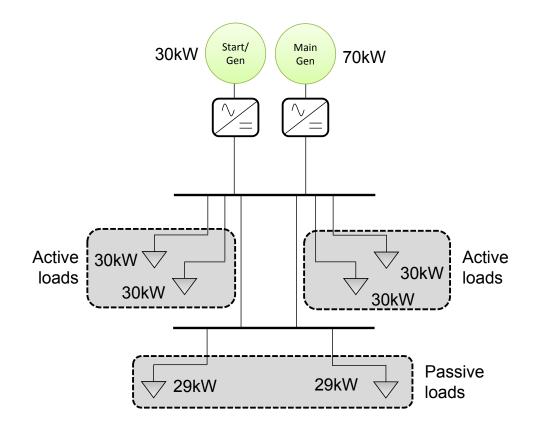

| 6.1          | Representative UAV electrical system architecture                                                                                                                                                           | 173               |

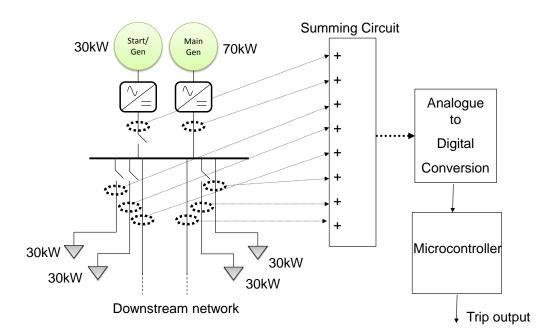

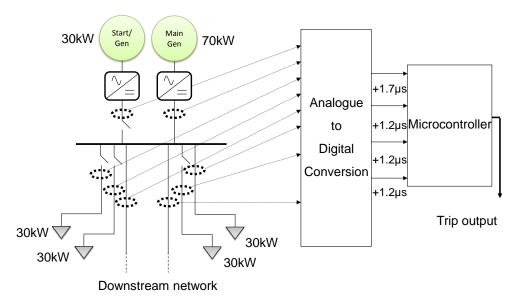

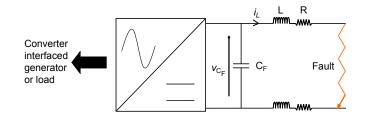

| 6.2          | Proposed current differential scheme with physically summed currents and central microcontroller                                                                                                            | 173               |

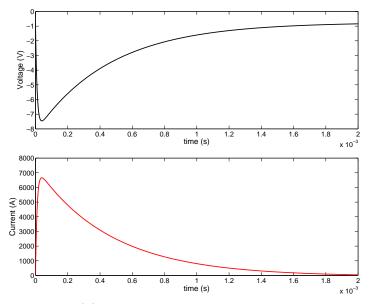

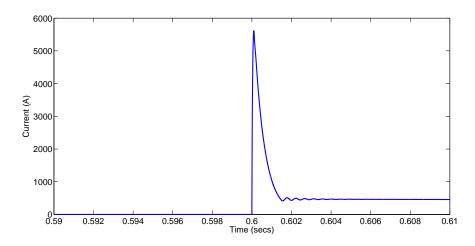

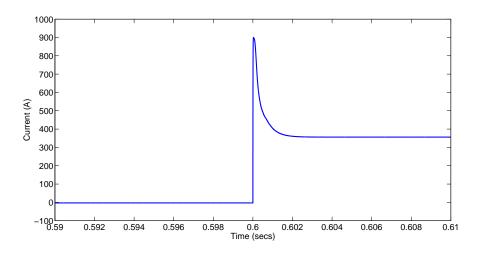

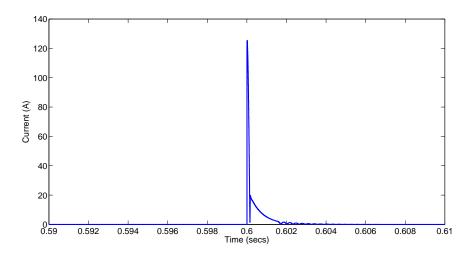

| 6.3          | Simulated fault current for a low impedance busbar fault                                                                                                                                                    | 175               |

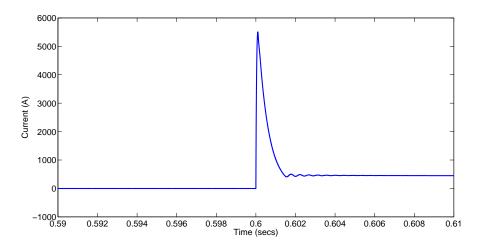

| 6.4        | Simulated current sum less applied threshold current for a low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|            | impedance busbar fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 176          |

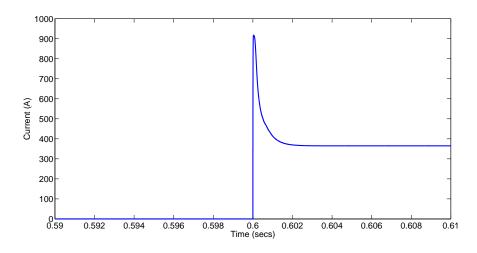

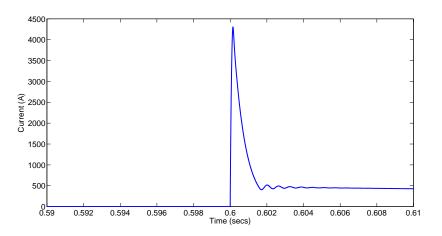

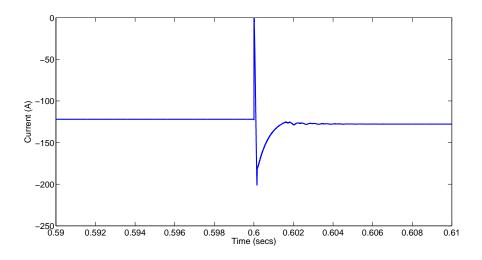

| 6.5        | Simulated fault current for a high impedance busbar fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 176          |

| 6.6        | Simulated current sum less applied threshold current for a high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

|            | impedance busbar fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 177          |

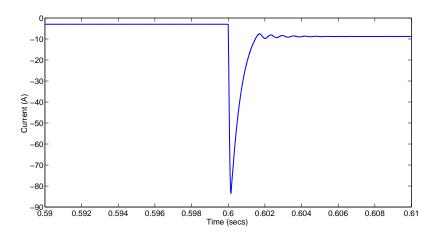

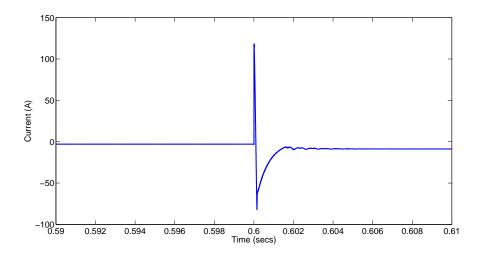

| 6.7        | Simulated fault current for a low impedance external zone fault .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 177          |

| 6.8        | Simulated current sum less applied threshold current for a low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

|            | impedance external zone fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 178          |

| 6.9        | Proposed current differential scheme with individually sampled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

|            | currents digitally summed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 178          |

| 6.10       | Simulated current sum for a low impedance external zone fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 179          |

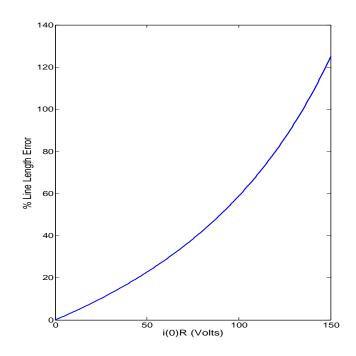

| 6.11       | Simulated current sum less applied threshold current for a low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |