## UNIVERSITÀ DI PISA

Scuola di Dottorato in Ingegneria "Leonardo da Vinci"

# Corso di Dottorato di Ricerca in INGEGNERIA DELL'INFORMAZIONE SSD ING-INF/01

Tesi di Dottorato di Ricerca

# Design and validation of key components for the readout electronics of future PET scanners

| Autore:                  |  |

|--------------------------|--|

| Nahema Marino            |  |

|                          |  |

|                          |  |

|                          |  |

| Relatori:                |  |

| Prof. Luca Fanucci       |  |

| Prof. Alberto Del Guerra |  |

| Prof. Roberto Roncella   |  |

Anno 2013

#### **SOMMARIO**

Il presente lavoro di tesi tratta il progetto e la validazione di due componenti circuitali utilizzati nell'elettronica di lettura di scanner per tomografia a emissione di positroni (PET) per applicazioni biomedicali: un discriminatore a frazione costante (CFD) ed un convertitore tempo-digitale (TDC) CMOS integrato.

Il primo è utilizzato per la lettura di uno scanner PET a due teste precedentemente realizzato dal gruppo di fisica medica presso l'Istituto Nazionale di Fisica Nucleare (INFN) di Pisa per il monitoraggio non invasivo della dose somministrata in adroterapia. L'obiettivo del lavoro è stato l'ottimizzazione del front-end realizzato su PCB in termini di prestazioni temporali al fine di ridurre il tempo morto e la risoluzione del sistema. È stata così realizzata una nuova scheda CFD e le misure sperimentali hanno dimostrato un significativo miglioramento delle caratteristiche temporali che hanno permesso l'acquisizione di dati PET durante l'irraggiamento del fascio, fondamentale per il trattamento in adroterapia.

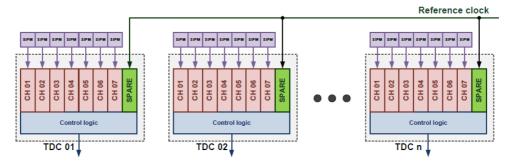

Il secondo argomento della tesi riguarda il progetto di un TDC CMOS integrato da impiegare nella misura del tempo di volo in un rivelatore PET compatibile con i campi magnetici. Al fine di definire la migliore topologia circuitale, sono stati analizzati diversi fattori derivanti dalle specifiche di progetto, tra i quali la risoluzione temporale, la linearità e il tipo di comunicazione con gli altri elementi del sistema di lettura. Simulazioni eseguite con Cadence e Verilog hanno dimostrato che è possibile ottenere un passo di misura di 100 ps mediante combinazione di una tecnologia sub micrometrica (UMC 65 nm LLLVT) con un approccio sistolico basato su un contatore a 10 bit accoppiato ad una linea ad aggancio di ritardo (DLL) a 4 stadi. Ciò si traduce in una risoluzione nominale di 29 ps. Inoltre, l'uso di una DLL costituita da pochi elementi di ritardo garantisce un comportamento lineare, particolarmente determinante nelle misure di tipo PET. Sebbene in letteratura siano documentate risoluzioni più spinte ottenibili con topologie di TDC differenti, risulta spesso difficile la realizzazione di buone prestazioni sia in termini di risoluzione temporale che di linearità. Il convertitore è anche dotato di un algoritmo di validazione in tempo reale che permette la reiezione degli ingressi di rumore generati dal fotorivelatore senza influire sulla capacità di acquisizione del sistema. È stata, inoltre, progettata una sezione a celle standard che si occupa dell'immagazzinamento dei dati e dell'invio degli stessi alle schede di lettura esterne in forma seriale. Tale stadio fornisce in uscita una parola di 47 bit ad una velocità selezionabile tra 31.25 MHz e 62.5 MHz con una risoluzione di doppio evento pari a 170 ns. A marzo 2013 è stato sottomesso un prototipo ad 8 canali di 1.875 x 1.875 mm² al fine di validare i dati simulati con risultati sperimentali.

#### **ABSTRACT**

This thesis work discusses the design and validation of two circuit components used in the electronic readout of positron emission tomography (PET) scanners for biomedical applications: a constant fraction discriminator (CFD) and an integrated CMOS time to digital converter (TDC).

The former is used in the read out of a double-head PET scanner already developed by the group of medical physics at INFN Pisa for non-invasive dose delivery monitoring in hadrontherapy. The goal of the work has been the optimization of the front-end PCB in terms of timing performances so as to reduce the dead time and resolution at system level. A new CFD board has been implemented and experimental results have shown a significant enhancement of the timing characteristics which have enabled performing in-beam PET data acquisition which is fundamental in hadrontherapy treatment.

The design of an integrated CMOS TDC to be used for the time of flight measurement in a magnetic field-compatible PET block detector is the second topic of the thesis. The required time resolutions, linear behaviour as well as the communication with other readout elements have been taken into account in the definition of the circuit topology. Cadence and Verilog simulations have shown that a bin size of 100 ps can be obtained with the combination of a submicron technology (UMC 65 nm LLLVT) and a pipeline approach where a 10 bit systolic counter coupled to a 4 stage delay locked loop (DLL) are exploited. This translates into a nominal resolution of 29 ps. In addition, the use of a short DLL leads to a high linearity which is an issue in PET measurements. Despite lower resolutions are obtained in literature with different TDC topologies, achieving good performances in terms of both time resolution and linearity is not straightforward. The converter also features a real-time validation algorithm which is capable to reject noise inputs generated by the photodetector without impairing the acquisition capability of the system. A standard-cell unit has been also designed which is in charge of data buffering and serial communication with external readout boards. A 47 bit output word is provided by the semi-custom stage at a measurement rate which is selectable between 31.25 MHz and 62.5 MHz with a double hit resolution of 170 ns. An 8 channel prototype of 1.875 x 1.875 mm<sup>2</sup> has been submitted in March 2013 in order to validate simulated data with experimental results.

#### **ACKNOWLEDGMENTS**

This theses would not have been possible without the contribution of several people I have worked with during the last three years. Firstly, I wish to thank my tutors, professor Luca Fanucci and professor Alberto Del Guerra, for having welcome me in Pisa and provided me with interesting subjects to work on.

I am indebted to professor Roberto Roncella who has guided me through the development of my second project with precious suggestions and ideas. I also want to thank doctor Federico Baronti for the valuable help and discussions which have been fundamental for the accomplishment of the theses goals. A special acknowledgment is due to professor Maria Giuseppina Bisogni who has believed in me and supported my work in both bad and good times.

I also acknowledge the help of doctor Nicola Belcari for his guidance in the physics field during my experience at INFN and of professor Valeria Rosso for involving me in several group works after my period at the physics department.

Of course, I wish to thank all people from the TPS project and 4DMPET project who have contributed to my professional growth with stimulating conversations.

I am also indebted to Tony Bacchillone for his help with software tools and to professor Sergio Saponara for his guidance with the publication works. I wish to thank professor Francesco Corsi and professor Cristoforo Marzocca from Polytechnic of Bari for their encouragement even from far away and after so many years have passed by.

Special thanks are due to Stefano, Katrin, Gianluca and Nicola who have supported me and made me feel at home: you will be my best memories from these times in Pisa. I also thank the guys from the engineering lab for the funny lunch breaks and all my friends in Bari whose affection gives me strength and joy every time things get tough.

Finally, mom and dad: I wish I could find the most appropriate words to say but nothing can explain my feelings better than "I love you". This theses is dedicated to you both.

# **CONTENTS**

| SOMMARIO                                                           | l        |

|--------------------------------------------------------------------|----------|

| ABSTRACT                                                           | II       |

| ACKNOWLEDGMENTS                                                    | ا        |

| LIST OF FIGURES                                                    | VII      |

| LIST OF TABLES                                                     | XI       |

| LIST OF SYMBOLS                                                    | XII      |

| 1. INTRODUCTION                                                    | 1        |

| 1.1. The role of electronics in medical physics                    | 1        |

| 1.2. Positron emission tomography                                  | 4        |

| 1.2.1. Performance parameters of PET                               | 5        |

| 1.2.2. Photodetectors                                              | 8        |

| 1.2.3. History and state of the art of PET                         |          |

| 1.2.3.2. Combined PET/CT                                           | 13<br>15 |

| 1.2.4. Some new trends in PET                                      |          |

| 1.3. Goals and organization of the thesis                          | 21       |

| 2. OPTIMIZATION OF A CONSTANT FRACTION DISCRIMINATOR               |          |

| 2.1. The TPS project                                               | 23       |

| 2.2. PET system at INFN                                            |          |

| 2.2.1. Electronic readout performances                             | 26       |

| 2.2.1.1. Symmetric charge division                                 | 26       |

| 2.2.1.2. Pulse shaping preamplifier                                |          |

| 2.2.1.3. Constant fraction discriminator2.3. Proposed CFD topology |          |

| 2.3.1. Experimental results                                        |          |

| 2.4. Conclusions and future work                                   |          |

| 3. DESIGN OF A MULTICHANNEL TIME TO DIGITAL CONVERTER              |          |

| 3.1. The 4DMPET project                                            | 45       |

| 3.1.1. TOF PET/MRI block detector                                  |          |

|                                                                    |          |

| 3.1.2. Time to digital converter requirements                      |          |

| 3.1.2. Time to digital converter requirements                      | 47       |

|                                                                    | 47<br>49 |

| 3.3.1.1. Ring oscillator and all-digital delay locked loop | 60 |

|------------------------------------------------------------|----|

| 3.3.1.2. Systolic counter                                  | 67 |

| 3.3.1.3. Data sampling                                     | 68 |

| 3.3.1.3.1. Input validation                                |    |

| 3.3.1.3.2. Hit registers                                   | 74 |

| 3.3.1.4. Other features                                    | 77 |

| 3.3.2. Semi-custom unit                                    | 79 |

| 3.3.3. Chip assembly                                       | 83 |

| 3.4. Conclusions and future work                           |    |

| 4. CONCLUSIONS                                             | 89 |

| PUBLICATIONS                                               | 90 |

| BIBLIOGRAPHY                                               | 93 |

|                                                            |    |

# **LIST OF FIGURES**

| Figure 1.1 – Physical phenomena of annihilation (left) and PET scanner scheme [22]4                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 – Coincidence detection probability does not depend on the annihilation point but on the object size only (left). Nonuniformity in different sections of the body arises form different values of probability (right) |

| Figure 1.3 – Illustration of the TOF principle. Without TOF information (A) annihilation is equiprobable along the LOR. With TOF (B), the annihilation point can be estimated with restriction to a smaller region [33]          |

| Figure 1.4 – Data collection and reconstruction in conventional PET (a) and TOF PET (b) (Adapted from [35])                                                                                                                      |

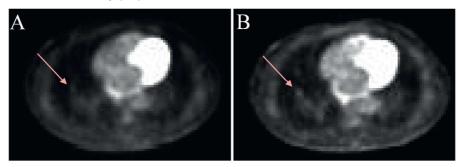

| Figure 1.5 – Transverse slices showing lung lesion (arrows) with non-TOF PET (a) and TOF PET (b) acquisitions [36]                                                                                                               |

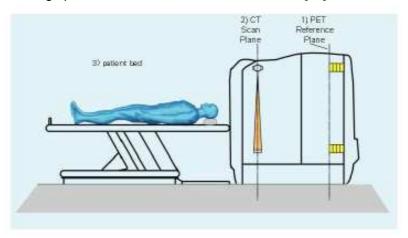

| Figure 1.6 – Design of a combined PET/CT scanner [45] 16                                                                                                                                                                         |

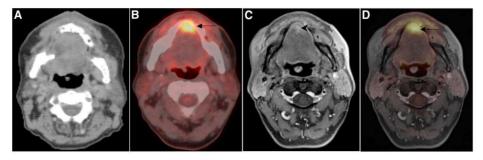

| Figure 1.7 – Squamous cell carcinoma of tongue (arrow) scanned with CT (A), PET/CT (B), MRI (C), PET/MRI (D) [52]                                                                                                                |

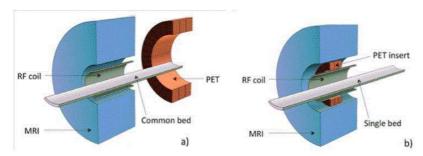

| Figure 1.8 – PET/MRI tandem configuration (a) and hybrid PET/MRI (b) (Adapted from [50])                                                                                                                                         |

| Figure 2.1 – Dual-head PET system developed at INFN (a). Each head can house up to 4 block detectors (b)                                                                                                                         |

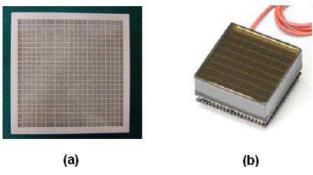

| Figure 2.2 – LYSO:Ce scintillator crystal (a) and PMT H8500 (b) employed in the PET system                                                                                                                                       |

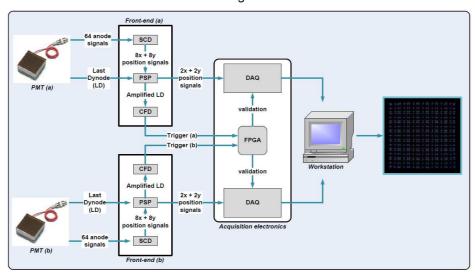

| Figure 2.3 – Schematic representation of the readout process in a PET acquisition with the facility developed at INFN. Reconstructed image of the crystal pixel matrix is also shown (right)                                     |

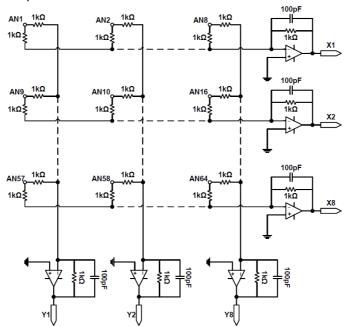

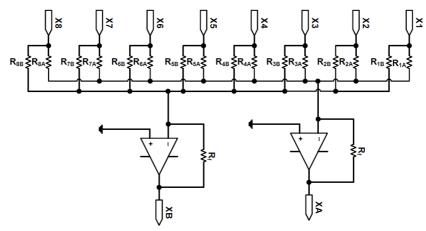

| Figure 2.4 – Symmetric charge division network [65]                                                                                                                                                                              |

| Figure 2.5 – Weighted resistive network for signal reduction along the x axis. The same scheme is implemented for the y direction. The value of the feedback resistor is $1.74 \text{ k}\Omega$ and the opamps used are AD805827 |

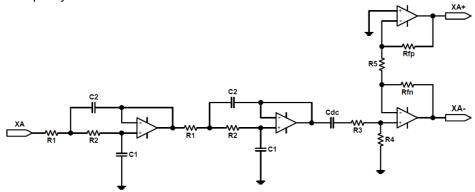

| Figure 2.6 – 2 stage Sallen-Key low-pass filter coupled to a single-ended to differential converter for position signal processing before sending data to the DAQ boards. All opamps are AD805829                                |

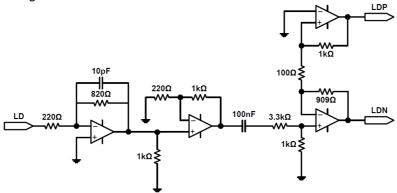

| Figure 2.7 – LD preamplification stage on PSP board. After shaping and amplification, single-ended to differential conversion is performed                                                                                       |

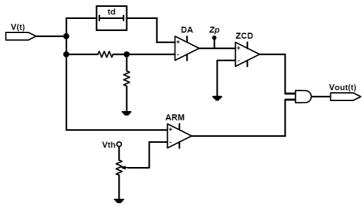

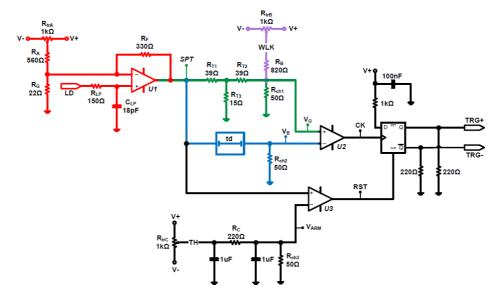

| Figure 2.8 – CFD scheme: the input signal $V(t)$ is split into 3 branches in order to minimize both amplitude and rise time fluctuations as well as to discard noise 31                                                          |

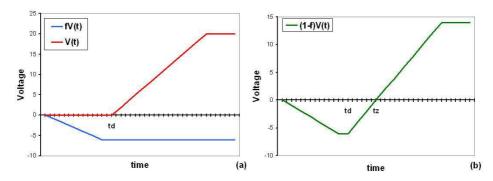

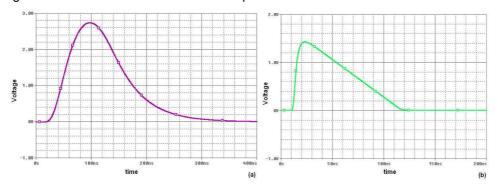

| Figure 2.9 – Delayed and attenuated signals at the input of the differential amplifier (a) and waveform resulting at node $Z_p$ (b) when $t_d > t_r$                                                                             |

| Figure 2.10 – Delayed and attenuated signals at the input of the differential amplifier (a) and waveform resulting at node $Z_p$ (b) when $t_d < t_r$                                                                            |

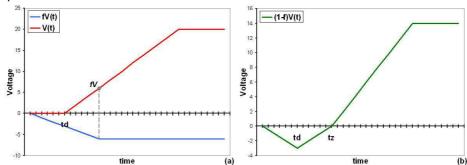

| Figure 2.11 – CFD implementation in the multi-board front-end of the PET scanner.                                                                                                                                                |

|                                                                                                                                                                                                                                  |

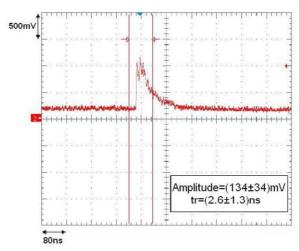

| Figure 2.12 – LD signal measured at the output of the PMT                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

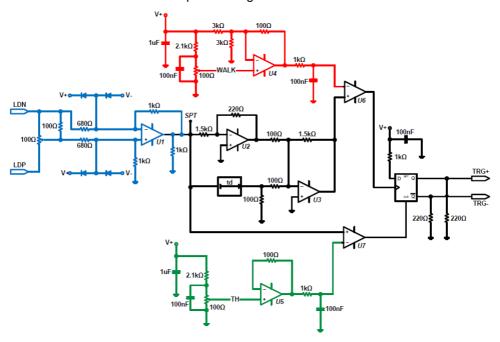

| Figure 2.13 – New CFD circuitry. All resistors are 0603-size with 5% tolerance 35                                                                                                                                                                  |

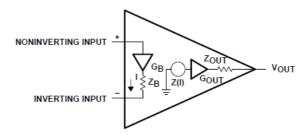

| Figure 2.14 – Model of a current feedback amplifier [71]                                                                                                                                                                                           |

| Figure 2.15 – CFA in non-inverting configuration                                                                                                                                                                                                   |

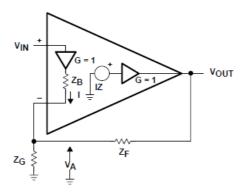

| Figure 2.16 – Simulated V <sub>SPT</sub> in the old (a) and new (b) CFD                                                                                                                                                                            |

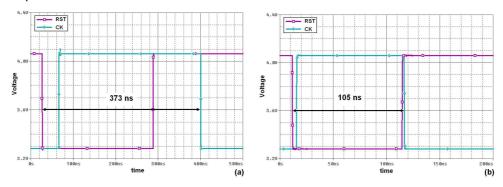

| Figure 2.17 – Simulated dead time in the old (a) and new (b) CFD. The latter exhibits a significant reduction down to one third with respect to the old circuit 38                                                                                 |

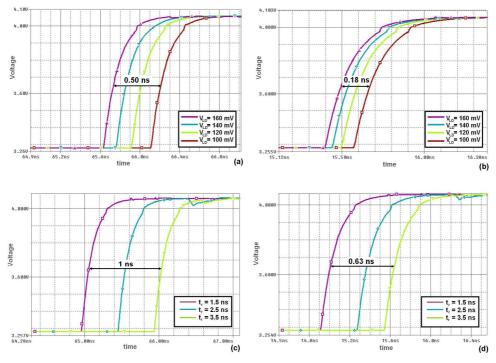

| Figure 2.18 – Effect of amplitude and rise time variation on CK generation in the old (a-c) and new (b-d) CFD                                                                                                                                      |

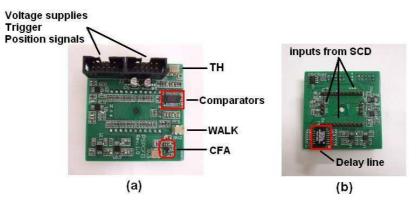

| Figure 2.19 – Front (a) and back (b) sides of the new PA-D board 40                                                                                                                                                                                |

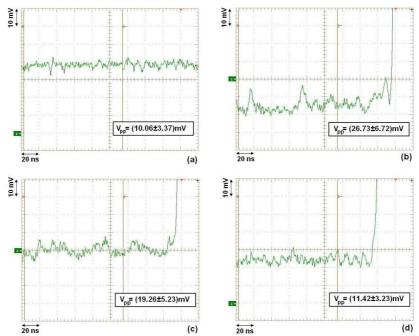

| Figure 2.20 – Peak to peak noise at nodes $V_{ARM}$ (a), $V_{SPT}$ (b), $V_{B}$ (c) and $V_{G}$ (d) for setting TH and WALK thresholds (cf. figure 2.13)                                                                                           |

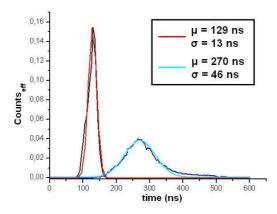

| Figure 2.21 – Dead time distribution in the OB (blue) and NB (black). Gaussian fits are superimposed (light blue for the OB and red for the NB). Counts are normalized to the total number of events                                               |

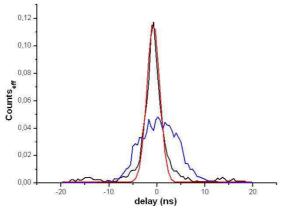

| Figure 2.22 – Time delay distribution in the OB (blue) and NB (black). Gaussian fit of the NB is superimposed (red). Counts are normalized to the total number of events                                                                           |

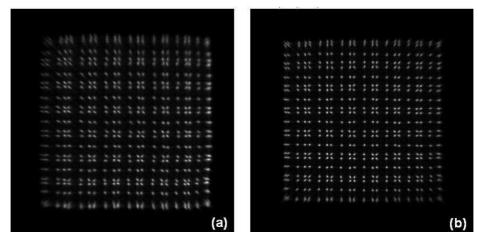

| Figure 2.23 – Reconstructed images of the crystal scintillator pixel matrix acquired with the old electronics (a) and PA-D (b)                                                                                                                     |

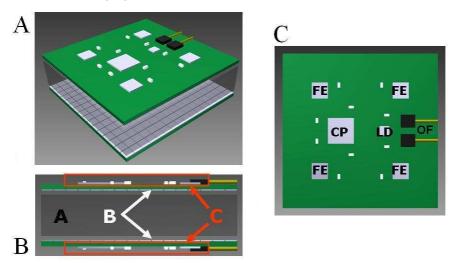

| Figure 3.1 – Block detector layout: 3D view (a), side view (b) and top view (c) 46                                                                                                                                                                 |

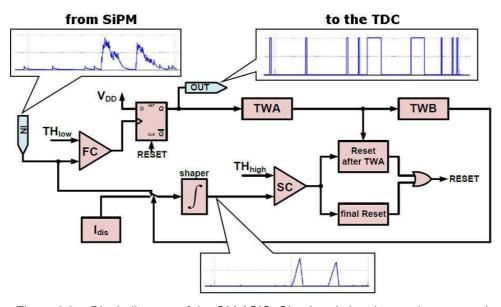

| Figure 3.2 – Block diagram of the CM ASIC. Simulated signals are also reported.47                                                                                                                                                                  |

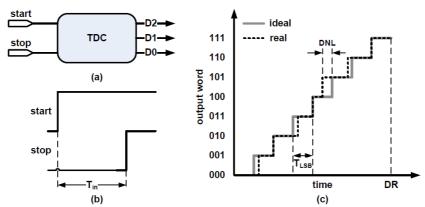

| Figure 3.3 – Working mechanism (a-b) and characteristic transfer curve (c) of a 3 bit TDC. Component mismatches and noise cause the real transfer curve to deflect from the ideal condition, generating quantization errors (adapted from [91]) 49 |

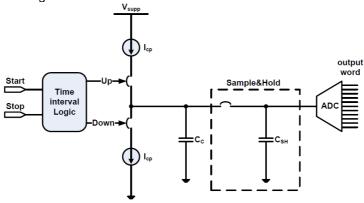

| Figure 3.4 – Schematic of the analogue approach for TDC (adapted from [91]) 51                                                                                                                                                                     |

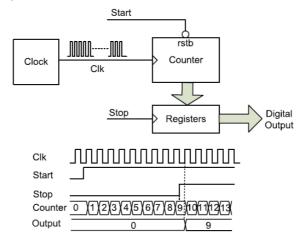

| Figure 3.5 – Counter-based TDC. The counter runs at the clock frequency and is reset by the start signal. The output bits are sampled by the stop pulse [91] 52                                                                                    |

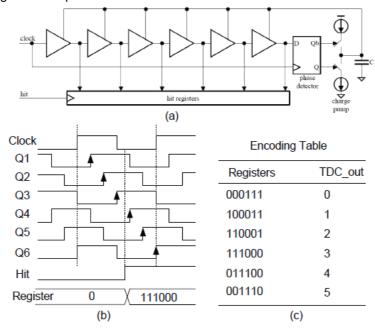

| Figure 3.6 – DLL-based TDC. Schematic analogue implementation (a), sampling diagram (b) and encoding table (c) [91]53                                                                                                                              |

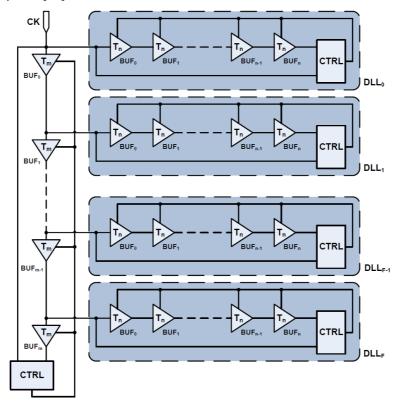

| Figure 3.7 – ADLL-based TDC 54                                                                                                                                                                                                                     |

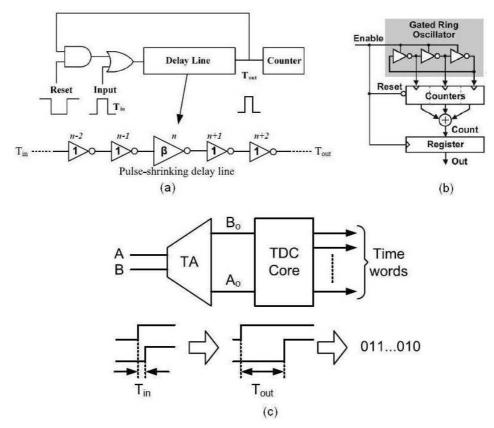

| Figure 3.8 – Sub-picosecond TDCs. Cyclic TDC using pulse shrinking DL (a), GRO-TDC (b), TA-based TDC (c) (adapted from [91])                                                                                                                       |

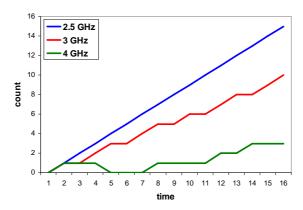

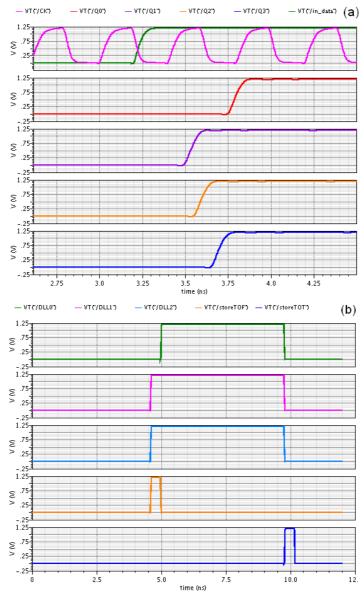

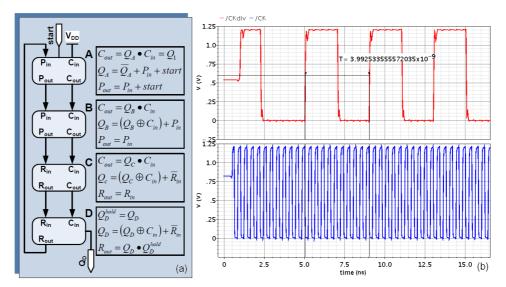

| Figure 3.9 – Post-layout simulations of the 4 bit systolic counter in UMC 65 nm at 90% $V_{DD}$ , 40°C and slow process                                                                                                                            |

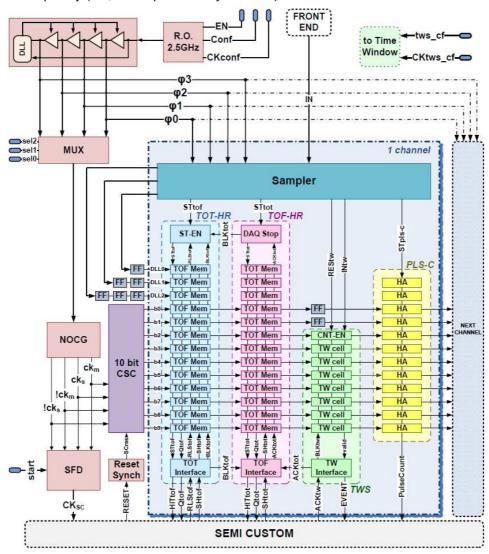

| Figure 3.10 – Block diagram of the FCU. Red blocks are common to the 8 channels of the TDC whereas the systolic counter feeds 4 channels only in pipeline fashion.                                                                                 |

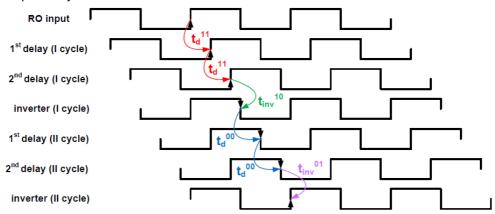

| Figure 3.11 – Delayed waveforms at the outputs of a 5 inverter stage R0. Inverters 1-2 are grouped together as $1^{st}$ delay, inveters 3-4 form the $2^{nd}$ delay 61                                                                             |

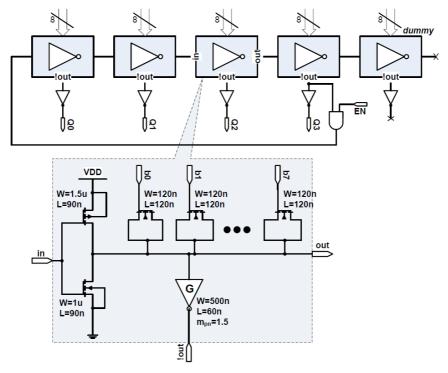

| Figure 3.12 – 5-stage RO implementation (up) and detail of the delay cell (down).                                                                                                                                                                  |

| 62                                                                                                                                                                                                                                                 |

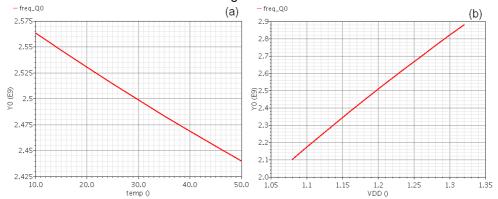

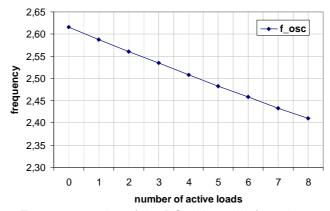

| Figure 3.13 – Variation of the RO frequency over temperature (a) and voltage range 10% -110% $V_{\rm DD}$ (b) in half-loaded configuration and typical process cond (post-layout simulations)                                                                            |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 3.14 – Frequency tuning of the RO delay cells (post-layout simulations)                                                                                                                                                                                           | 63           |

| Figure 3.15 – ADDLL and RO locking for typical (a), slow (b) and fast process(c                                                                                                                                                                                          | :).64        |

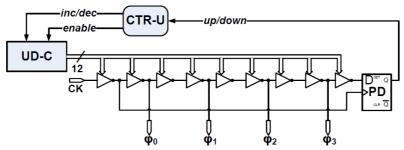

| Figure 3.16 – Block diagram of the ADDLL                                                                                                                                                                                                                                 | 65           |

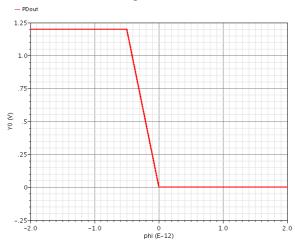

| Figure 3.17 – PD phase error vs. input delay (post-layout simulation in type conditions).                                                                                                                                                                                |              |

| Figure 3.18 – Block diagram of the up/down counter                                                                                                                                                                                                                       | 66           |

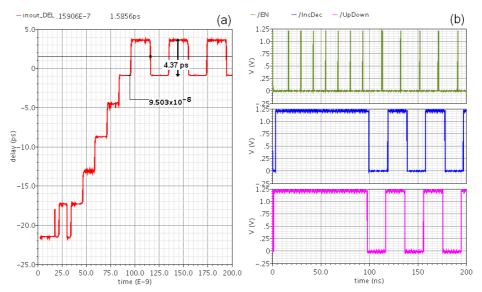

| Figure 3.19 – ADDLL behaviour from the starting to the locking condition. In output delay (a) and control loop waveforms (b)                                                                                                                                             |              |

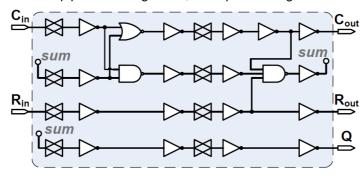

| Figure 3.20 – Systolic implementation of the half-adder function                                                                                                                                                                                                         | 67           |

| Figure 3.21 – Skewed output (orange and blue) of a 4 bit systolic counter. $S_i$ an are sum and carry at the output of the i-th half-adder (a). Simulated output bits                                                                                                    | (b).         |

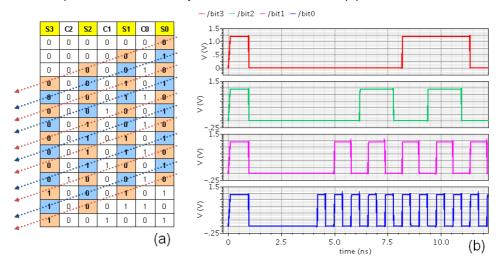

| Figure 3.22 – Event sampling with the four ADDLL phases (a) and rise/fall education at systolic level (b).                                                                                                                                                               | edge         |

| Figure 3.23 – Input signal sampled with the 4 phases of the ADDLL (a); s signals and DL status at the input arrival time (b) (post-layout simulations)                                                                                                                   |              |

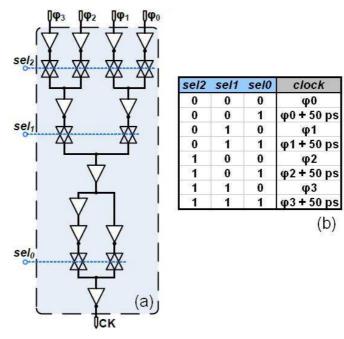

| Figure 3.24 – Multiplexer for clock selection (a) and configuration table (b)                                                                                                                                                                                            | 71           |

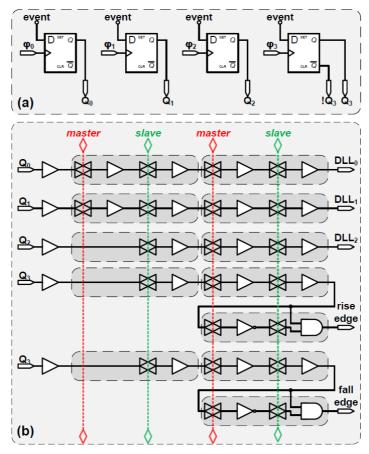

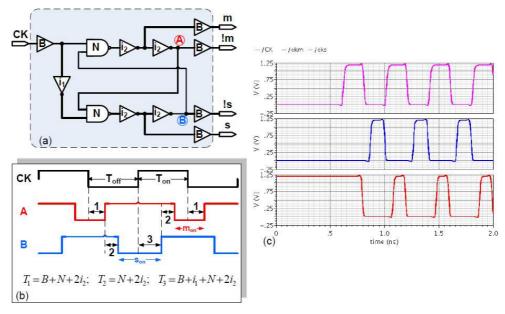

| Figure 3.25 – Schematic block of the NOCG (a) and timing diagram of the c master/slave generation (b)                                                                                                                                                                    |              |

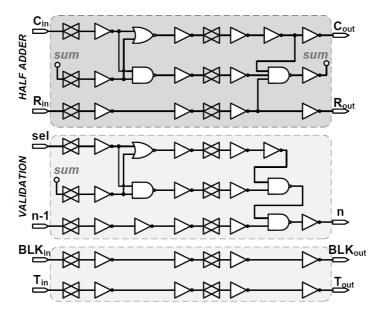

| Figure 3.26 – Configuration of the TWS cell. The validation section performs xnor between the configured bit (sel) and the calculated sum; if the two bits equal and the comparison has been true at the previous cell as well (signal not logic 1 is generated at pin n | are<br>1), a |

| Figure 3.27 – Input and output signals of the time window stage. Both noise valid input (red) is simulated                                                                                                                                                               | and          |

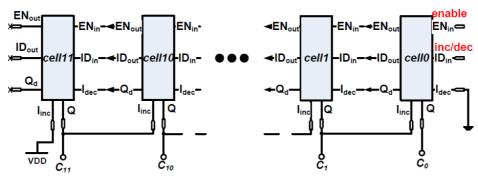

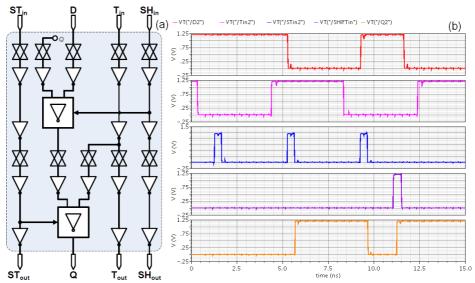

| Figure 3.28 – Schematic implementation of the store/shift process within mencells (a). Waveforms at the input/output of a single cell in typical conditions (b).                                                                                                         |              |

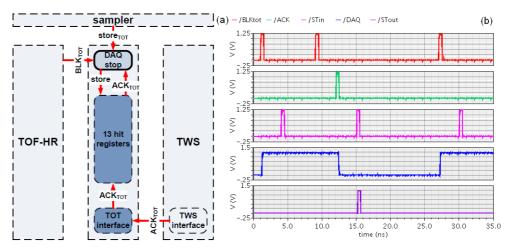

| Figure 3.29 – Signals feeding the DAQ stop stage (a) and waveforms result from simulations in typical conditions (b)                                                                                                                                                     | _            |

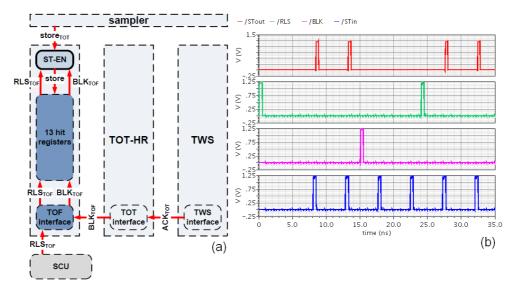

| Figure 3.30 – Signals feeding the store enable unit (a) and waveforms resufrom simulations in typical conditions (b)                                                                                                                                                     | 77           |

| Figure 3.31 – Systolic implementation of the frequency divider by 10 (a) and playout simulation of the output clock (b)                                                                                                                                                  |              |

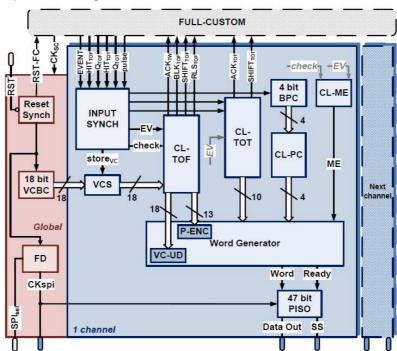

| Figure 3.32 – Block diagram of the semi-custom unit. The red section is share the 7 channels of the SCU                                                                                                                                                                  |              |

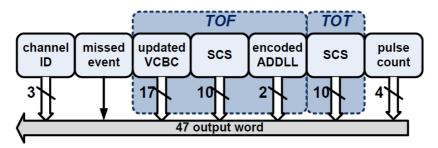

| Figure 3.33 – Output word generation                                                                                                                                                                                                                                     | 81           |

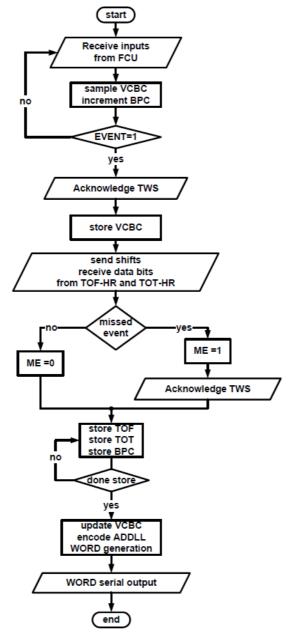

| Figure 3.34 – Flow chart of the SCU algorithm                                                                                                                                                                                                                            |              |

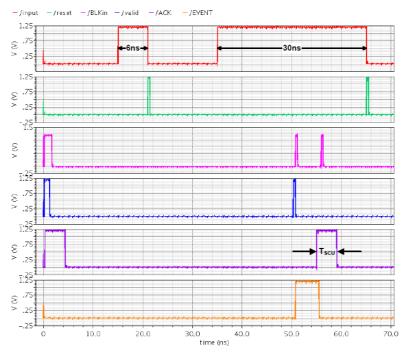

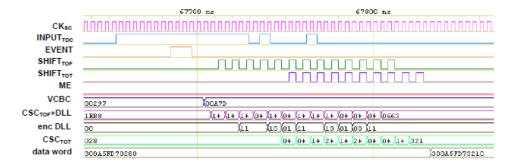

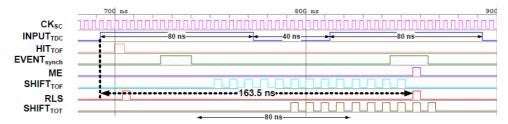

| Figure 3.35 – Verilog simulation of one channel of the TDC                                                                                                                                                                                                               | 83           |

| Figure 3.36 – DHR evaluation with a time threshold of 6 ns                                                                                                                                                                                                               |              |

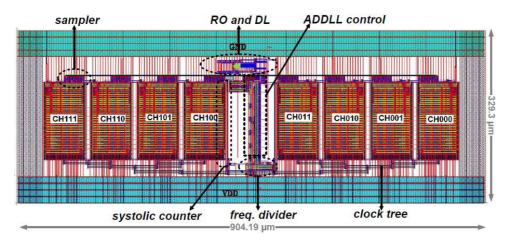

| Figure 3.37 – Layout of the full-custom unit.                                                                                                                                                                                                                            | 84           |

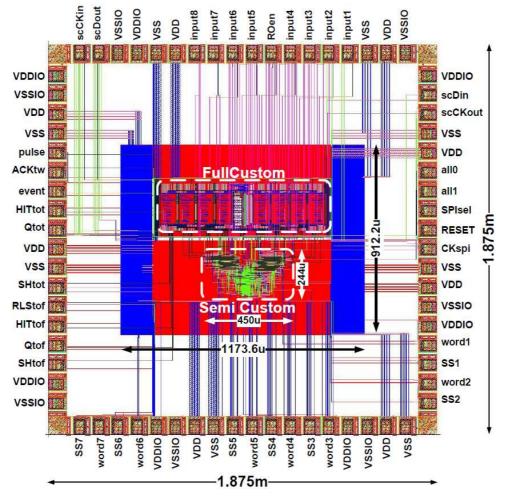

| Figure 3.38 – Chip layout                                                 | 85 |

|---------------------------------------------------------------------------|----|

| Figure 3.39 – Spare channel used in the TDC chip for off-line calibration | 87 |

# LIST OF TABLES

| Fable 1.1 – Performance characteristics of the main photodetectors used in<br>scanners |    |

|----------------------------------------------------------------------------------------|----|

| Table 1.2. – Some physical properties of common PET scintillators [26]                 | 12 |

| Fable 1.3 – Merits of different medical imaging technique [51]                         | 17 |

| Fable 2.1 – Main characteristics of Hamamatsu H8500 [63]                               | 25 |

| Fable 2.2 – Main characteristics of AD8009 [72]                                        | 37 |

| Fable 2.3 – Performance comparison between the old and the new front-end               | 43 |

| Fable 3.1 – Design requirements for the TDC ASIC                                       | 48 |

| Fable 3.2 – Features and performances of the three UMC technologies conside            |    |

| Fable 3.3 – RO cell delays in ideal conditions (post-layout values)                    | 62 |

| Fable 3.4 – Algorithm implemented by the VC-UD                                         | 81 |

| Fable 3.5 – TDC performances from post-simulation results.                             | 86 |

#### LIST OF SYMBOLS

ADC Analogue to Digital Converter

ADDLL All Digital DLL ADLL Array of DLL

APD Avalanche Photo Diode

ARC CFD Amplitude and Rise Time Compensation CFD

ARM Arming Discriminator

ASIC Application Specific Integrated Circuit

BaF<sub>2</sub> Barium Fluoride **BGO** Bismuth Germanate BPC Binary Pulse Counter Charge Sensing Amplifier CSA Common Systolic Counter CSC Current Feedback Amplifier CFA CFD **Constant Fraction Discriminator** CL-ME Control Logic for Missed Event Control Logic for Pulse Count CL-PC

CL-TOF Control Logic for TOF

CL-TOT Control Logic for TOT

CM ASIC Current Mode ASIC

CsF Caesium Fluoride

CT Computed Tomography

CTR-U Control Unit D-FF D-Flip Flop

DAQ Data Acquisition Board DHR Double Hit Resolution

DL Delay Line

DLL Delay Locked Loop

DNL Differential Non Linearity

DOI Depth Of Interaction

DR Dynamic Range

FCU Full Custom Unit

FDG Fludeoxyglucose

FIFO First In First Out register

FOV Field Of View

FPGA Field Programmable Gate Array

FWHM Full Width at Half Maximum

GRO Gated Ring Oscillator

GSO Gadolinium Silicate

INL Integral Non Linearity

LaBr3 Lanthanum Bromide

LD Last Dynode

LED Leading Edge Discriminator

LOR Line Of Response

LSB Least Significant Bit

LSO Lutetium Oxyorthoslicate

XII

LVDS Low Voltage Differential Signalling LYSO Lutetium Yttrium Oxyorthosilicate

ME Missed Event

MRI Magnetic Resonance Imaging

MSB Most Significant Bit

Nal(Tl) Thallium-activated Sodium Iodide

NECR Noise Equivalent Count Rate

NOCG Non Overlapping Clock Generator

PA-D Position Amplification and Discriminator

PCB Printed Circuit Board PD Phased Detector

PECL Positive Emitter Coupled Logic

PET Positron Emission Tomography

PISO Parallel Input Serial Output register

PLL Phased Locked Loop

PLS-C Pulse-Counter

PMMA Poly Methyl Methacrylate

PMT Photo Multiplier Tube

PSP Pulse Shaping Preamplifier

PVT Process Voltage Temperature variation

RF Radio Frequency

RO Ring Oscillator

RT Radiation Therapy

SCD Symmetric Charge Division

SCU Semi Custom Unit SF Scatter Fraction

SFD Systolic Frequency Divider

SiPM Silicon Photo Multiplier

SNR Signal to Noise Ratio

SPAD Single Photon Avalanche Detector

SPECT Single Particle Emission Computed Tomography

SPI Serial Peripheral Interface

SyC Systolic Counter TA Time Amplification

TAC Time to Amplitude Conversion

TOF Time Of Flight

TOF-HR Time Of Flight-Hit Register TOT Time Over Threshold

TOT-HR Time Over Threshold-Hit Register

TWA Time Window A

TWB Time Window B

TWS Time Window Stage

UD-C Up Down-Counter

UT Ultra Transmitting

VCBC Very Coarse Binary Counter

VC-UD Very Coarse-Updater

VDL Vernier Delay Line

VFA Voltage Feedback Amplifier ZCD Zero Crossing Discriminator

#### 1. INTRODUCTION

## 1.1. The role of electronics in medical physics

Medical physics is the combination of applied physics, electronics and computing for the diagnosis and treatment of human disease. The subject is further divided into many branches, including diagnostic radiology, nuclear medicine, which uses radioactive materials for diagnosis of disease, ultrasound, magnetic resonance imaging (MRI) and radiotherapy, which employs radiation to destroy cancerous tissue. All of these applications need or provide an imaging tool for health care. The demand for better image quality entails continuous research to improve instrumentation and techniques. Furthermore, shorter examination times, shift to outpatient testing and non-invasive imaging are required while saving costs. Studies in the fields of detector technologies, circuit design techniques, materials and system approach have led to significant progress in ultrasound, MRI, X-ray, computed tomography (CT) and nuclear medicine. Despite significant differences in the principle of operation, all of these imaging tools require readout electronics, usually referred to as front-end, to perform signal processing such as signal amplification, filtering, multiplexing and analogue to digital conversion [1].

X-ray imaging is based on the analysis of attenuation data of the patient who undergoes the ray exposure. Indeed, since internal organs have different matter composition, they experience different levels of X-ray absorption. This makes it possible to reconstruct a 2D image of the area under investigation. Main drawbacks of this technique are reduced image contrast due to collapsing 3D structures into bi-dimensional images and poor resolution capability in soft tissues given the small differences in attenuation coefficients. A 3D extension of X-ray technology is computer tomography (CT) where a large number of X-ray images is taken at multiple angles so as to elaborate a 3D view of the structures. In general, X-ray detection is based on the use of materials which absorb the incoming radiation and transform the corresponding photon energy into an electrical signal. The latter must be further processed by dedicated electronics in order to be amplified, filtered and then converted into digital form for reconstruction purposes. Most of the improvements in CT have attempted to provide faster acquisition times, better spatial resolution and shorter computer reconstruction times. At the beginning, the use of a single semiconductor CT detector required a single readout channel system. Nowadays, modern X-ray detectors make use of large-scale arrays of active picture elements (pixels) each one to be readout by an independent electronic channel. This solution improves image quality as it concentrates more pixels in a given detector volume. The implementation of such novel layouts has been possible thanks to the technology progress. The use of VLSI electronics along with advanced techniques of IC design makes it possible to integrate a large number of channels within a single chip. Thus, each pixel on the detector array can be readout individually. This leads to good spatial resolution in the final image and large dynamic range. The measurement resolution of the X-ray system strongly depends on the properties of the readout unit, which influences both time and noise profiles of the overall system itself. A primary example of VLSI electronics used for X-ray detection is Medipix which is a CMOS pixel detector readout chip designed to be connected to a segmented semiconductor sensor

[2,3]. One of the main drawbacks of the increasing level of integration between analogue and digital parts in mixed-signal systems is on-chip noise coupling. Noise currents caused by switching digital circuits are spread to the sensitive analogue components via the power distribution network and through the substrate by current injection. This is especially true in radiation pixel detectors where an extreme level of integration is required to read out the array. A dedicated circuit design can improve the noise performance [4]. A further issue in X-ray detection is related to the high count rate of the system. Thus, special attention must be paid in the front-end design in order to maximize the throughput while keeping a high resolution. This problem can be addressed with the use of dedicated strategies in the ASIC design [5]. Area occupancy of readout channels must also be considered in order to accommodate the large number of channels required by novel block layouts. Thus, innovative architectures must be introduced [6]. Finally, image contrast can also be improved by setting an energy window in the low energy range which can be selectable by hardware [7].

As opposed to X-ray imaging which provides morphological information of the body, nuclear medicine techniques inform about the functional activities inside the tissues. Two major imaging modalities can be considered: positron emission tomography (PET) and single particle emission computed tomography (SPECT). In both the two techniques no external radiation is used to scan the object as in X-ray imaging. Instead, radiotracers are injected inside the body and accumulate in the region of interest. Then, radiation is detected to recover the distribution of the isotopes and 2D or 3D images are elaborated through computer analysis. Mapping of emitted radiation is performed either by collimator (SPECT) or by electronic coincidence using two opposite detectors (PET). Currently, almost all commercially available scanners employ scintillation crystals with photodetectors coupled to readout electronics. The latter must measure the photon energy so as to discriminate true events from background and scattered photons. Then, the number of detected photons and the coordinates of each interaction in the detectors are recorded in order to inform about the amount of radiation and the directions of photons' arrivals. Additionally, PET systems record the timing information of photons to detect coincidence pairs. The accuracy and resolution of nuclear imaging tools are severely restricted by both physical effects, such as photon attenuation and scatter, and deficiencies of the equipment which limit the system capability in reconstructing the tracer distribution. As in X-ray technology, reading out the signals from both SPECT and PET sensors requires highly specialized electronics with stringent requirements in terms of signal to noise ratio (SNR), dynamic range, linearity and stability. The use of novel pixelated photodetectors with high rate of events per pixel causes the demand for high density, high rate, multichannel ASICs. Each channel processes the charge signals coming from the associated pixel by performing amplification, filtering, discrimination, measurement and storage. Pixel amplification can be performed by providing either charge to voltage [8], charge to charge or current to current amplification [9]. Shaping is another important step in pixel readout as it limits the bandwidth to maximize SNR and shorten the pulse width to minimize dead time and avoid pile up. Different approaches to implement optimal shapers are reported in literature [10,11]. The last step in the readout chain is the extrapolation of energy and timing information from data. Accurately extracting such information requires employing specialized circuits such as peak detectors and digitizers [12,13].

Magnetic resonance imaging (MRI) is a relatively new medical imaging technique which is able to generate images with excellent soft tissue contrast. It does not use ionizing radiation and therefore is considered safer than CT, PET and SPECT. MRI systems are based on superconducting magnets that produce a highly uniform static field inside a cylindrical bore. Hydrogen nuclei present in biological structures tend to align with the field. This results in a small bulk magnetization which is subsequently tilted from its equilibrium position of alignment; this gives rise to the magnetic resonance phenomenon which consists of the precession of the individual nuclear moments around the field vector. As a consequence of the return to an equilibrium stage, radio-frequency (RF) magnetic fields are generated that can be detected with pickup loop coils. The rates at which the longitudinal and transverse components of the magnetization return to their respective equilibrium values create contrast between different biological tissues. The tilting of the magnetization is provided by the energy of a short, intense pulse of RF magnetic field produced by a large transmission coil. Spatial encoding is performed after the excitation pulse generation by driving time-variant currents in the gradient field coils, during which the RF signal induced by the magnetization in receiver coil is acquired. This measurement procedure can be repeated several times so as to acquire enough data to produce an image [1,14]. The acquisition of signals detected by the receiver coil is performed by the spectrometer, whose function is also to generate the precisely timed gradient and RF pulses that are required to excite and encode spatial information into the nuclear magnetization. Initially, a single receiver coil was used with a size covering the area of interest. The drawback of this approach is that for the large regions positioned far away from the surface, field of the coil is weak and results in a poor SNR. This problem has been overcome by using an array of surface coils whose individual noise is not correlated, thus improving the overall SNR [15]. In these array structures, each resonating loop must be connected to a low-noise preamplifier through a matching network for SNR optimization [16]; moreover, preamplifier decoupling must be implemented in order to avoid coupling among the coil loops [17]. These techniques make it possible the design of coil arrays with a large number of independent channels. In order to exploit the use of such multichannel receivers, new approaches are currently being investigated in order to address issues related to the construction and acquisition of data (i.e., RF interferences among cables and data volume). Advances in semiconductor technology such as photonics, wireless high-speed communications, large-scale integration and MEMS are fundamental for planning new solutions, such as the use of fibre-optic based cabling [18,19], wireless communication [20] and pre-processing hardware [21].

According to what stated so far, it is evident that electronics play a fundamental role in the implementation of imaging tools for medical applications. Indeed, each technique makes use of a transducer apparatus (scintillator plus photodetector in X-ray, CT, PET, SPECT and receiver coil in MRI) which translates physical phenomena into an electrical signal. Therefore, the information required for image reconstruction must be extrapolated by means of signal processing. Improvements in detector layouts and procedures demand for further innovation of readout techniques. Currently, the trend in most of medical imaging fields is shifting from a single large transducer to arrays of small structures which allow for image quality enhancement. It follows that a very small area is available for readout electronics, thus requiring the development of VLSI multichannel front-ends. In this scenario,

main challenges in ASIC design include power limitation, low noise levels, crosstalk prevention and good matching performance among channels. Physicists, engineers and doctors are working together in order to increase medical imaging performances, thus allowing a better quality of life.

#### 1.2. Positron emission tomography

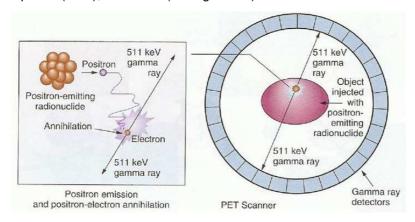

Positron emission tomography is a molecular imaging technique that provides images of physiological processes inside the body. After  $\beta^+$  decay of a radiotracer injected into the tissues, a positron is released which annihilates with an atomic electron, thus producing two 511 keV photons (*event*). These pairs of gamma rays are emitted in almost exactly opposite directions within the PET scanner. Coincidence detection of the two photons is exploited to provide projection data used for image reconstruction. Production of the radionuclides requires the use of a cyclotron, which must be near the testing centre due to the short half-lives of the radioisotopes.

A PET scanner is made up of an array of detectors surrounding the object to be imaged. Each time a detector is hit by a gamma ray, opposite detectors are checked for detection of a second photon. If this happens within a given coincidence time window (typically ranging from 5 ns up to 10 ns), an event is counted and the straight line connecting the centres of the two detectors, called the line of response (LOR), is created (see figure 1.1).

Figure 1.1 – Physical phenomena of annihilation (left) and PET scanner scheme [22].

Each detector element is connected by a coincidence circuit with the time window to a set of n opposite detector elements. The n fan-beam projections available for each detector form an angle of acceptance in the transaxial plane; the angles of acceptance for all detectors in the ring form the transaxial field of view (FOV). Combining all counts from the detectors produces a single projection; several projections are needed to reconstruct an image of the area of interest. Nowadays, PET cameras consist of a large number of detectors and a real time check of detector pairs is impractical. Instead, each hit is associated to a timestamp and buffered into a digital coincidence processor that compares all data in order to identify true coincidence events. Next, the pulse height of the detected photons is

checked if it is within the pulse energy window set for 511 keV (~20-30% FWHM centred on the 511 keV photopeak) and the position of the LOR is determined by a weighted centroid algorithm to store the event in the computer memory for reconstruction purposes. Data storage should be organized so that the spatial information carried by each LOR is preserved. Two storage methods are available. A first approach is based on binning the acquired data into projection representation of the data also known as sinograms. Events are accumulated into a 3D sinogram array, where each element is identified by a radial position, a transaxial angle and an axial position (with polar angle) with respect to the centre of the scan field [23]. A second approach is listmode reconstruction in which data are stored as a list of detected events each one associated to its position, energy and detection time [24].

#### 1.2.1. Performance parameters of PET

PET technology makes use of solid scintillation detectors to sense gamma pairs. Several materials have been investigated in order to find the most performing one according to some characteristics such as stopping power of the detector for 511 keV photons, scintillation decay time, light output per keV of photon energy, energy resolution and detection efficiency. The stopping power of the detector is related to the mean distance the photon travels until it stops after complete deposition of its energy and depends on the density and effective atomic number (Z) of the detector material. The scintillation decay time derives from interactions between gamma rays and atoms of the detector material. This results in the atoms being excited to a higher energy level and then decaying to the ground state with emission of visible light. This time of decay is called the scintillation decay time and depends on the detector material. A shorter decay time leads to a higher efficiency of the detector at high count rates. Light output is responsible of a well-defined pulse, thus resulting in better energy resolution. The intrinsic energy resolution is affected by inhomogeneities in the crystal structure of the detector and random variations in the production of light in it. Usually detectors in PET scanners have relatively poor energy resolution (from 10% up to 25%). Finally, the detection efficiency depends on the linear attenuation coefficient ( $\mu$ ) which determines the fraction of incident gamma rays which experience either photoelectric absorption or Compton scattering when passing through the detector material.

Unfortunately, detector properties may vary from block to block. This is an issue in large PET scanners where thousands of detectors are assembled. Along with such a problem, variations in the gain of the photodetectors and detector block misalignments determine nonuniformity in the PET ring. This affects the integrity of the acquired projection data, thus requiring calibration procedures. Other problems are related to photon attenuation, random coincidences, scatter coincidences, dead time and parallax error.

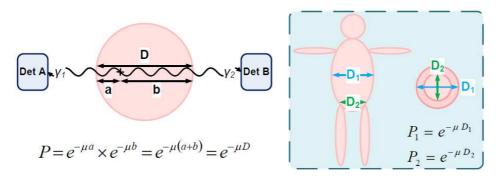

Photon attenuation by tissues arises from variation of the thicknesses and distance of tissues from the detector pair in coincidence. Indeed, if photons travel through organs and tissues with uniform density (thus having the same  $\mu$ ), the probability P of coincidence detection is independent of the position of the annihilation site along the line of response, but is only related to the attenuation coefficient and to body size. In addition, when non-uniform organs and tissues are passed through, the attenuation coefficient and thickness of each of them influences the detection probability P. This leads to nonuniformity in the images since more coincidence

events are lost from the largest sections of the body, as depicted in figure 1.2; furthermore, the two photons may travel through different organs along the LOR. As such, correction is required to take into account this phenomenon.

Figure 1.2 – Coincidence detection probability does not depend on the annihilation point but on the object size only (left). Nonuniformity in different sections of the body arises form different values of probability (right).

Random coincidences occur when two unrelated 511 keV photons from two separate positron annihilation locations are detected by a detector pair within the time window. This causes artefacts and loss of image contrast. A common method of correcting random events is to employ two coincidence circuits, one with the standard time window and another with a delayed time window both windowed in the same energy range. The counts in the standard time window include both random and true events, whereas the delayed time window contains the random ones only. Given that random events in both time windows are the same within statistical variations, correction is made by subtracting the delayed window counts from the standard window counts.

Scatter coincidences are related to radiations incurring in Compton scattering with energy within the acceptance window. These scattered radiations increase the background of the image, thus degrading the image contrast. Moreover, two Compton scattered photons are likely to sum up simultaneously in a detector. If the resultant peak falls within the energy window, an event will be counted but mispositioned because of the unrelated events involved, thus causing image distortion at high count rates. The scatter contribution increases with the density and depth of the body tissue, the density of the detector material, the activity in the patient and the energy window width.

Dead time is the time interval during which the system processes a gamma ray pair. It begins with the photon interaction with the detector and lasts until the end of event recording. During this interval the detection system is unable to process a second event, which is lost. This undesired effect can be reduced by using detectors with shorter scintillation decay time and high speed electronics components in the PET scanners.

Parallax error is due to coincidence events occurring at off-centre points with respect to the FOV. In this condition, the photons can strike tangentially at the backside of the detector pair with unknown depth of interaction. The resulting coincidence event blurs the image. This effect can be corrected by measuring the

light in the front and back of the detector and using the difference to estimate the depth of photon interaction in the detector.

In commercial PET scanners, where more adjacent rings are arranged, coincidences between detectors in different rings can be processed in either two possible modalities: 2D and 3D acquisition mode. The former is performed in scanners where annular shielding rings called septa are placed between the crystal rings so as to absorb photons travelling along large oblique angles. This allows coincidences to take place between neighbouring rings only, thus significantly reducing contributions from scattered photons and photons from radioactivity outside the FOV of the scanner from 30% to 40%. In 3D mode acquisition, no septa are used so that coincidences between all detectors in any ring are allowed. This results in increased sensitivity but in poorer spatial resolution due to random coincidences as well as in a larger amount of data to be stored.

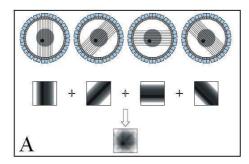

Projection data acquired in 2D or 3D mode are further processed for reconstruction. The quality of the image and the accuracy of the resulting data strongly depend on the method used. Two reconstruction techniques are available: filtered backprojection and iterative methods. The former is the most commonly used in clinical environment as it is fast and simple although the generated images lack quantitative accuracy and often contain significant artefacts. It is based on the assumption that the number of photons recorded in any given detector bin represents the sum of contributions from the activity located along a line perpendicular to the detector surface. In iterative methods, an initial estimate of an image is made and the projections are computed from the image and compared with the measured projections. If there is a difference between the estimated and measured projections, corrections are made to improve the estimated image and a new iteration is performed to assess the convergence between the estimated and measured projections. Iterations are continued until a reasonable agreement between the two sets of projections is achieved. The main drawback of this technique is the reconstruction time which could be an issue especially for very large 3D data sets.

Image quality is also associated to several scanner parameters including spatial resolution, sensitivity, noise, scattered radiations and contrast [25,26].

Spatial resolution of a PET scanner is a measure of the ability of the device to faithfully reproduce the image of an object. It is empirically defined as the minimum distance between two points (sources) in an image that can be clearly distinguished by a scanner. It is influenced by the following factors.

- Detector size: Intrinsic resolution of the scintillation detectors significantly

affects the spatial resolution. For multi-detector PET scanners, the intrinsic

resolution is related to the detector size. For continuous single detectors,

however, the intrinsic resolution strongly depends on the number of photons

detected.

- Positron range: The positron is emitted with a kinetic energy conceiving to an energy spectrum between 0 and E<sub>max</sub> (usually around 1 MeV for most of the positron emitters used in PET). The positron travels a distance in tissue, losing most of its energy and then annihilates after capturing an electron, i.e., forming a "positronium" atom. Since coincidence detection is related to the location of annihilation, an error occurs in the localization of true position of the positron emission, thus resulting in the degradation of spatial resolution.

- Non-colinearity: Non-colinearity arises from the deviation of the two annihilation

photons from the exact 180° position; in a first ap proximation, this arises from

some small residual momentum of the positron at the end of the positron

range. Therefore, the observed LOR between the two photons is somewhat

displaced from the annihilation site due to the *Lorentz boost*.

- Other factors which influence image quality are the reconstruction method used and the correct localization of the detector.

Sensitivity of a PET scanner is defined as the number of counts per unit time detected by the device for each unit of activity present in a source. It depends on the geometric efficiency, detection efficiency, energy window settings and the dead time of the system. The higher the sensitivity, the better the SNR achieved in the reconstructed image.

Image noise is mainly due to the random variation in pixel counts across the image and can be reduced by increasing the total counts in the image. Another source of noise arises from non-random or systematic addition of counts due to imaging devices or procedural artefacts. The image noise is characterized by a parameter called the *noise equivalent count rate (NECR)* which is related to true, random and scatter coincidence count rates.

Scatter fraction (SF) is often used to compare the performances of different PET scanners. It is defined as that fraction of the total coincidences recorded in the photopeak window which have been scattered.

*Image contrast* is a measure of the detectability of an abnormality relative to normal tissue. It arises from the relative variations in count densities between adjacent areas in the image of an object and can be influenced by count density, scattered radiation, size of the lesion and patient motion.

#### 1.2.2. Photodetectors

In a PET scanner, the role of the photodetector is to translate the light emitted by the scintillator into an electrical signal. Generally, the photodetectors used in PET can be divided into two categories, the photomultiplier tubes (PMT) and the semiconductor-based photodiodes, which include avalanche photodiodes (APD) and silicon photomultipliers (SiPM).

Photomultiplier tubes are the most common photosensors used in PET. They consist of a vacuum enclosure with a thin photocathode layer at the entrance window. An incoming scintillation photon deposits its energy at the photocathode and triggers the release of a photoelectron. Depending upon its energy, the photoelectron can escape the surface potential of the photocathode and in the presence of an applied electric field accelerate to a nearby dynode which is at a positive potential with respect to the photocathode. Upon impact with the dynode, the electron, with its increased energy, will result in the emission of multiple secondary electrons. The process of acceleration and emission is then repeated through several dynode structures with increasing potentials, leading to a gain of more than a million at the final dynode (anode). This high gain leads to a very good SNR for low light levels and is the primary reason for the success and applicability of PMTs in PET detectors. The main drawback of a PMT is the low efficiency in the emission and escape of a photoelectron from the cathode after the deposition of energy by a single scintillation photon. This property is called the *quantum*

efficiency (QE) of the PMT and it is typically 25% [26]. Furthermore, PMTs are bulky, require very high bias voltages and are not magnetic field compatible.

Photodiodes are based on semiconductor technology and have high sensitivity in the detection of the low energy of scintillation photons. These detectors typically are in the form of inversely-biased PIN diodes where the incoming photons produce electron-hole pairs, thus resulting in a charge flow after the application of an electric field. In particular, APDs have a built-in avalanche region which generates a gain depending on the applied voltage. If operating below the breakdown, the total output current is proportional to the amount of incoming radiation (linear mode behaviour). Unfortunately, in these conditions the mean gain per photon is low so that the low output signal cannot be easily distinguished from noise. On the other hand, if the applied voltage is slightly above the breakdown (10% - 20%), a gain in the order of 10<sup>2</sup> is obtained. The APD is said to work in Geiger mode and exhibits a "digital" behaviour. Arrays of such APDs, called single photon avalanche detectors (SPAD), have been thought suitable for PET scanners in the early 2000s, given their compactness and IC technology and magnetic field compatibility. Some problems in SPADs are related to the increase of dark pulses (avalanches independent of the incident light) and recovery time with increased area [27].

Silicon photomultipliers overcome these limits by exploiting a dense array of SPADs connected in parallel on the same substrate. SiPMs combine the advantages of both PMTs, such as high gain and total QE, and APDs, like the small dimensions which permit extremely compact, light and robust mechanical design and magnetic field compatibility. The use of SiPM-based detectors is very promising for the implementation of high performance PET scanners [28,29]. Table 1.1 summarizes the main characteristics of PMTs, APDs and SiPMs.

Table 1.1 – Performance characteristics of the main photodetectors used in PET scanners.

|                      | PMT       | APD     | SiPM  |

|----------------------|-----------|---------|-------|

| Gain                 | 108       | 102     | 106   |

| Bias voltage (V)     | 1000-2000 | 100-200 | 30-70 |

| Output response (ns) | 5-10      | >1      | <1    |

| MRI compatibility    | No        | Yes     | Yes   |

| Compactness          | No        | Yes     | Yes   |

#### 1.2.3. History and state of the art of PET

Although modern PET technology has taken approximately thirty years to develop, the history of molecular imaging is strictly connected to several inventions and discoveries which took place since the early 1920s such as Rutherford experiments, the design of the first cyclotron and the positron discovery [30].

Furthermore, the application of modern biology and medicine to molecular medicine has been fundamental in making PET an essential tool in health care. In 1951 William H. Sweet exploited for the first time the positron concept for medical purposes by implementing a simple brain probe where coincidence was used to localize brain tumours. Based on this idea, he collaborated with Gordon L. Brownell and a physics group at Massachusetts General Hospital to develop the first brain probe using two opposing sodium iodide (NaI(TI)) detectors which detected photons when radiation passed through them. Photomultiplier tubes were placed to measure the amount of released light, which was proportional to the amount of radiation produced. The patient's head had to be placed between the two detectors and the circuitry was designed to detect the coincidence photons from the annihilation products. The idea of coincidence detection with mechanical motion in two dimensions used in these studies was the underlying principle of modern PET. Brownwell and Sweet performed the initial studies with positron emitters by changing Polaroid films in rapid succession. Electronic formatters increased the rate of obtaining images and image quality. In the same year, Wrenn, Good and Handler published studies on positron annihilation for localizing brain tumours. In their work, they presented the technique of simultaneous detection of the annihilation product photons to localize positron emission. They also discussed the principles behind the earliest cameras in positron studies. These two independent papers represent the first attempts to record positron data for use in a medical application.

In the early 1960s, Kuhl and Edwards were developing image reconstruction techniques for single photon tomography. Although this algorithm was not a true computed tomography approach, it did employ the principle of superimposition of back projections. About a decade later, Chesler introduced the filtered back projection technique whereas Hounsfield and Cormack reported their results on iterative techniques.

In the mid 1960s, Allan Cormack published papers where he demonstrated a bench top X-ray computerized tomograph scanner. Image reconstruction was based on a decomposition algorithm of a function in a set of projections, known as Radon transform (J. Radon, 1917). A few years later, Godfrey Hounsfield directed a project to combine X-ray and digital computer technology. This effort gave birth to computerized tomography.

In 1973, James Robertson of Brookhaven National Laboratory built the first ring tomograph, which consisted of 32 detectors. However, he was unable to obtain true reconstructed cross sectional images due to limited sampling, lack of attenuation correction and lack of a proper image reconstruction algorithm. In the same year, Michael E. Phelps built the first PET tomograph, known as PETT I (Positron Emission Transaxial Tomography). Later he reduced the name to PET because transaxial was not the only plane in which images could be reconstructed. Limited sampling, attenuation problems and bad collimators interfered with a successful transverse back projection.

From this moment on, ten fundamental steps paved the way to the development of modern PET [31].

Event 1: In 1973, Mike Phelps and Ed Hoffman of Washington University joined EG&G ORTEC, a spin-off company of the Oak Ridge National Laboratory, and developed PETT II and PETT II ½ These tomographs were

used to establish the mathematics and physics of PET, as well as to perform imaging of blood flow and metabolism in animals. The principles of PET, as they are known today, were published from studies performed on these tomographs developed by Phelps and his team. At the end of 1974, Phelps and Hoffman constructed PET III for human studies. This system was a hexagonal array with excellent sampling by a combination of linear movement of detectors and a 60-degree rotation of the gantry. The system had its own computer for controlling the motion of the detectors, gantry and bed, as well as performing image reconstruction. Nizar Mullani developed the coincidence logic while EG&G ORTEC designed the electronics. The first images of blood flow, oxygen and glucose metabolism and F-18 bone scans from this tomograph represented the first published human PET images using the filtered back projection algorithm. Soon after, the first commercial PET scanner named ECAT II (Emission Computed Axial Tomograph) was designed at EG&G ORTEC. This tomograph used a total of 96 3.75cm NaI(TI) crystals, had a PDP-11 computer with 32Kbytes of memory for a console and was sold for approximately \$600,000 in 1978.

- Event 2: During 1970s, the only detector used in PET was Nal(TI), which was difficult to manufacture because of its hygroscopic nature. Also, the Nal(TI) scintillator had medium/low density and effective atomic number that limited the efficiency for the high energy photons (i.e., 511 keV). On the other hand, it had a high light yield and reasonably fast decay time to provide good coincidence time resolution. The use of another crystal, the bismuth-germanate (BGO), was considered after studies made by Cho and Derenzo so that in 1978 EG&G ORTEC produced the NeuroECAT, the first commercial tomograph to use BGO.

- Event 3: In the years 1978-80, fludeoxyglucose (FDG), a positron-emitting radiopharmaceutical, was used for PET imaging for the first time.

- Event 4: Between 1984 and 1986, CTI, Inc. built the first PET medical cyclotron; in the same years, Satyamurthy, Barrio and Padgett at UCLA developed the first automated chemistry module for synthesizing FDG, as well as other molecular probes. Nowadays, several companies (General Electric, Siemens, IBA) provide cyclotrons with various forms of automated chemistry for producing molecular imaging probes. Additionally, other companies sell automated chemistry modules for PET without the cyclotron.

- <u>Event 5</u>: During 1984-85, the idea of a block detector was introduced by Casey and Nutt, where thirty-two crystals for four photomultipliers were arranged, thus making possible the implementation of high-resolution PET tomographs. In 1983-84, the Computer Technology and Imaging, Inc. (CTI) a spin-off company of EG&G ORTEC dedicated to the ECAT design, paved the way to the commercial commitment of PET.

- Event 6: From 1985 to 1990, Schelbert, Schwaiger and Phelps developed and validated the match/mismatch principle for determining cardiac viability, which proved to be very important in the process of making clinical PET a reality.

- Event 7: Between 1987 and 1990, the entrance of the two major imaging companies (Siemens and General Electric) in PET design gave birth to a commercial focus on developing and supplying PET products for clinical service.

- Event 8: In 1991, Phelps presented the first whole-body oncology images obtained by using a technique developed by himself, Hoffman and Dahlbom. This started the evolution to detect primary and metastatic disease, differentiate benign from malignant lesions and assess therapeutic responses by being able to image all organs of the body in a single examination. These applications formed the basis of the Food and Drug Administration's (FDA) approval of FDG and the Medicare reimbursement of several oncology indications.

- Event 9: In the years 1997-98, the FDA Reform Bill was signed into law and government reimbursement for PET was finally announced.

- Event 10: The introduction, in the years 1990-2000, of cerium-doped lutetium oxyorthosilicate (LSO) revolutionized PET imaging. LSO has a slightly greater density, slightly lower effective atomic number and has five times more light output than BGO. Also, LSO has 7.5 times faster scintillation decay time. This LSO performance results in a combination of speed and light output improvement of 37.5 over BGO (see table 1.2). The first LSO PET tomograph, microPET, was designed and fabricated by Simon Cherry for small animals, whereas the first human LSO tomograph was delivered to the Max Planck Institute, Köln, Germany, in February 1999.

Table 1.2. – Some physical properties of common PET scintillators [26].

| Parameter                             | Nal(TI) | BGO  | LSO  | GSO  | BaF <sub>2</sub> |

|---------------------------------------|---------|------|------|------|------------------|

| Effective atomic number (Z)           | 50.6    | 74.2 | 65.5 | 58.6 | 52.2             |

| Density (g/cm3)                       | 3.67    | 7.13 | 7.4  | 6.71 | 4.89             |

| Attenuation length                    | 2.88    | 1.05 | 1.16 | 1.43 | 2.2              |

| Scintillation decay time (ns)         | 230     | 300  | 40   | 60   | 0.6              |

| Light output (photons/keV)            | 38      | 6    | 29   | 10   | 2                |

| Wavelength λ (nm)                     | 410     | 480  | 420  | 440  | 220              |

| Relative light output                 | 100     | 15   | 75   | 25   | 5                |

| Linear attenuation coefficient (cm-1) | 0.35    | 0.96 | 0.87 | 0.70 | 0.44             |

| Energy resolution (% at 511 keV)      | 6.6     | 10.2 | 10   | 8.5  | 11.4             |

#### 1.2.3.1. Time of flight PET

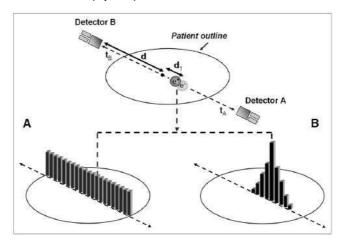

In clinical applications, PET image quality benefits from the time of flight (TOF) feature either using analytical or iterative reconstruction algorithms. By measuring the photons arrival time on the detectors, the annihilation point can be estimated, thus leading to better noise level, contrast and clarity of detail in the reconstructed images [32]. In conventional PET, each time positron annihilation is registered, its position along the LOR is unknown. However, in TOF PET, faster detectors are used to measure the difference in the arrival time of the two gamma rays, thus narrowing the position of the annihilation along the LOR. This added information enables the reconstruction algorithm to provide the final image with fewer iterations and less image noise.

Figure 1.3 illustrates the principle of TOF PET [33]. Named d the radius of the detector ring and  $d_1$  the distance between the annihilation site and the centre of the FOV, the distance of the two detectors in coincidence and the annihilation point is  $\left(d+d_1\right)$  and  $\left(d-d_1\right)$ , respectively. Then, the arrival time difference between the two photons travelling at the speed of light c at the detectors is  $2\cdot \left(d_1/c\right)$ . Clearly, photons originating from the centre of the FOV arrive at the detectors at the same time, since in this case it is  $\left(d_1=0\right)$ .

Figure 1.3 – Illustration of the TOF principle. Without TOF information (A) annihilation is equiprobable along the LOR. With TOF (B), the annihilation point can be estimated with restriction to a smaller region [33].

In a conventional PET (figure 1.3A) all voxels along the LOR are assigned equal probability in the generation of the annihilation site. Instead, in TOF PET the most probable location of the annihilation is at the centre of the uncertainty distribution (figure 1.3B).

Therefore, the TOF information is incorporated directly into the reconstruction algorithm, leading to an improvement in SNR given by [34]:

$$\frac{\sigma_{nonTOF}}{\sigma_{TOF}} = \sqrt{\frac{2D}{c\,\Delta t}}\tag{1}$$

where  $\sigma_{nonTOF}$  and  $\sigma_{TOF}$  are the standard deviation of the image SNR without and with TOF measurement, D is the size of the object to be imaged and  $\Delta t$  is the TOF time resolution. Then, it is clear that the time resolution plays a key role in improving the image quality.

Figure 1.4 illustrates conventional PET and TOF PET in filtered backprojection [35].

Figure 1.4 – Data collection and reconstruction in conventional PET (a) and TOF PET (b) (Adapted from [35]).

In conventional PET, the system just records the fact that an event took place somewhere along the lines connecting the detectors. In figure 1.4a, only four measurement angles are considered with a low resolution along the lines and a high resolution perpendicular to the lines. From these measurements four estimates are obtained (figure 1.4a, middle) and added to form the final estimate (figure 1.4a, bottom). The TOF information in figure 1.4b allows the placement of the events along the LORs thus defining 7 regions (figure 1.4b, top). In this case, the four estimates resulting from the measurement angles are closer to the original image (figure 1.4b, middle). Consequently, the quality of the final estimate given by the sum is much better than the conventional case (figure 1.4b, bottom). This can be observed in a real situation from figure 1.5, where both non-TOF PET and TOF PET acquisitions of a lung lesion are reported: the lesion is more easily discernible in the TOF PET study [36].

Figure 1.5 – Transverse slices showing lung lesion (arrows) with non-TOF PET (a) and TOF PET (b) acquisitions [36].

The potential benefits of TOF were understood in the early 1980s, thus leading to the development of the first TOF PET scanners at Washington University, CEA