# EFFICIENT SYNCHRONIZATION FOR GPGPU

by

# Jiwei Liu

B.S., Zhejiang University, 2010

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of **Ph.D. in Electrical Engineering**

University of Pittsburgh

2018

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Jiwei Liu

It was defended on

June 12, 2018

and approved by

Jun Yang, Ph.D., Professor, Department of Electrical and Computer Engineering Rami Melhem, Ph.D., Professor, Department of Computer Science

Youtao Zhang, Ph.D., Associate Professor, Department of Computer Science

Kartik Mohanram, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Heng Huang, Ph.D., Professor, Department of Electrical and Computer Engineering

Wei Gao, Ph.D., Associate Professor, Department of Electrical and Computer Engineering

Dissertation Director: Jun Yang, Ph.D., Professor, Department of Electrical and Computer

Engineering

# EFFICIENT SYNCHRONIZATION FOR GPGPU

Jiwei Liu, PhD

University of Pittsburgh, 2018

High-performance General Purpose Graphics processing units (GPGPUs) have exposed bottlenecks in synchronizations of threads and cores. The massively parallel computing cores and complex hierarchies of threads present new challenges for synchronizations at different granularities. Performance of GPU is hindered by inefficient global and local synchronizations. I propose hardware-software cooperative frameworks for efficient synchronization of GPGPU to address the following issues.

To provide efficient global synchronization (Gsync), an API with direct hardware support is proposed. The GPU cores are synchronized by an on-chip Gsync controller. Partial context switch is employed to guarantee deadlock-free execution. The proposed Gsync avoids expensive API calls and alleviates data thrashing. Prioritized warp scheduling is used to increase the overlap of context switch with kernel execution.

To efficiently exploit the inherent parallelism of producer-consumer problems, a flexible wait-signal scheme is proposed at thread-block level. I propose dedicated APIs to express fine-grained static and dynamic dependencies with hardware support. The proposed scheme can accelerate wavefront, graph and machine learning applications. The architectural design of on-chip wait-signal controller eliminates busy wait loop and long-latency memory operations. I also propose thread block dispatch scheduling to address the problem of load imbalance and large context switch overhead.

To reduce stall due to synchronizations, a synchronization-aware warp scheduling is proposed to coordinate multiple warp schedulers upon synchronization events. Both performance and hardware utilization are improved by resolving the barrier sooner.

# TABLE OF CONTENTS

| 1.0 | IN' | <b>TRODUCTION</b>                                                           | 1  |

|-----|-----|-----------------------------------------------------------------------------|----|

|     | 1.1 | THE CHALLENGES FOR GPGPU SYNCHRONIZATION                                    | 4  |

|     |     | 1.1.1 Inefficient Global Synchronization                                    | 4  |

|     |     | 1.1.2 Lack of Wait-Signal Support                                           | 4  |

|     |     | 1.1.3 Synchronization Oblivious Warp Scheduling                             | 5  |

|     | 1.2 | THESIS OVERVIEW                                                             | 6  |

|     | 1.3 | CONTRIBUTIONS                                                               | 9  |

|     |     | 1.3.1 Efficient GPU Global Synchronization with Light Weight Context Switch | 9  |

|     |     | 1.3.2 Accelerate RNNs with software Wait-Signal                             | 9  |

|     |     | 1.3.3 Thread Block Level Wait and Signal in GPU with Hardware support .     | 10 |

|     |     | 1.3.4 Synchronization Aware GPGPU Warp Scheduling                           | 11 |

|     | 1.4 | THESIS ORGANIZATION                                                         | 12 |

| 2.0 | BA  | SICS OF GPGPU                                                               | 13 |

|     | 2.1 | GPGPU ARCHITECTURE                                                          | 13 |

|     | 2.2 | STREAMING MULTIPROCESSOR ARCHITECTURE                                       | 13 |

|     | 2.3 | WARP SCHEDULING                                                             | 14 |

|     | 2.4 | GPU SYNCHRONIZATION PRIMITIVES                                              | 15 |

|     |     | 2.4.1 Global Synchronization                                                | 15 |

|     |     | 2.4.2 Within-TB synchronization                                             | 15 |

| 3.0 | RE  | LATED WORKS                                                                 | 21 |

|     | 3.1 | ADDRESSING GLOBAL SYNCHRONIZATION                                           | 21 |

|     |     | 3.1.1 Dynamic Parallelism                                                   | 21 |

|     |     | 3.1.2 Atomic Operations and Memory Flags        | 22 |

|-----|-----|-------------------------------------------------|----|

|     |     | 3.1.3 Persistent threads                        | 22 |

|     |     | 3.1.4 Cooperative Kernels                       | 23 |

|     |     | 3.1.5 Occupancy Discovery Protocol              | 23 |

|     | 3.2 | ADDRESSING PRODUCER CONSUMER PROBLEMS           | 24 |

|     |     | 3.2.1 Asynchronous Task Management Interface    | 25 |

|     |     | 3.2.2 Specialized Warps                         | 25 |

|     |     | 3.2.3 Case Study: RNN Acceleration Techniques   | 26 |

|     |     | 3.2.3.1 Accelerating Single Layer RNNs          | 29 |

|     |     | 3.2.3.2 Accelerating Multi-Layer RNNs           | 30 |

|     |     | 3.2.3.3 Stream implementations of RNNs          | 30 |

|     |     | 3.2.3.4 Persistent implementations of RNNs      | 34 |

|     | 3.3 | ADDRESSING WARP SCHEDULING                      | 34 |

|     |     | 3.3.1 Round Robin Warp Scheduling               | 34 |

|     |     | 3.3.2 Greedy Then Oldest Warp Scheduling        | 35 |

|     |     | 3.3.3 CTA-aware two-level warp scheduling       | 35 |

| 4.0 | EF  | FICIENT GLOBAL SYNCHRONIZATION                  | 36 |

|     | 4.1 | MOTIVATIONS FOR EFFICIENT GSYNC                 | 36 |

|     | 4.2 | GPU-SIDE GLOBAL SYNCHRONIZATION API             | 38 |

|     | 4.3 | MICROARCHITECTURE DESIGN FOR GSYNC              | 40 |

|     | 4.4 | MANAGING CONTEXT SWITCH                         | 43 |

|     |     | 4.4.1 Memory Allocation for Context Saving      | 43 |

|     |     | 4.4.2 Reducing Context Switch Overhead          | 44 |

|     |     | 4.4.3 Reducing Memory Congestion                | 46 |

|     |     | 4.4.4 Using Other Context Switch Techniques     | 46 |

|     | 4.5 | Experimental Results for Global Synchronization | 47 |

|     |     | 4.5.1 Experiment Setup and Methodology          | 47 |

|     |     | 4.5.1.1 Stencil applications                    | 50 |

|     |     | 4.5.1.2 Graph Traversal                         | 51 |

|     |     | 4.5.2 Performance Overhead and Scalability      | 52 |

|     |     | 4.5.3 Hardware Overhead Analysis                        | 54 |

|-----|-----|---------------------------------------------------------|----|

| 5.0 | AC  | CELERATING RNN WITH SOFTWARE WAIT-SIGNAL                | 55 |

|     | 5.1 | ALGORITHM                                               | 55 |

|     |     | 5.1.1 Fine-grained Parallelism within a layer           | 56 |

|     |     | 5.1.2 Implementing Wait Signal with memory flags        | 58 |

|     |     | 5.1.3 Workload Assignment                               | 59 |

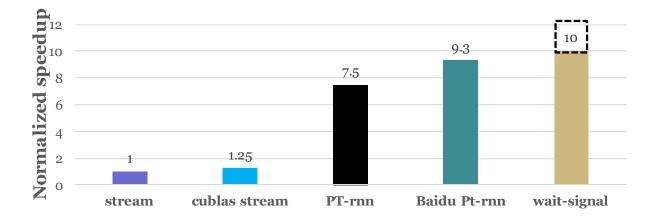

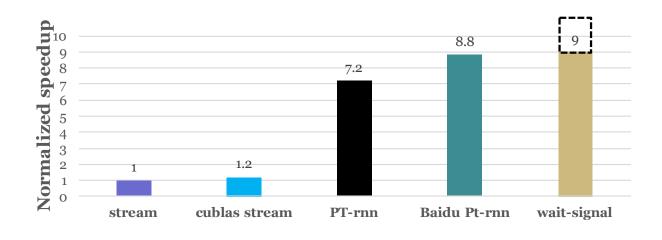

|     | 5.2 | Experimental Results for evaluation RNN                 | 61 |

|     |     | 5.2.1 Benchmarks                                        | 64 |

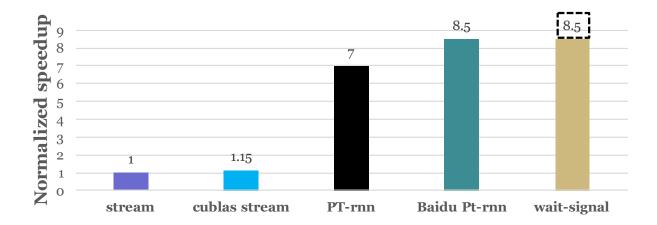

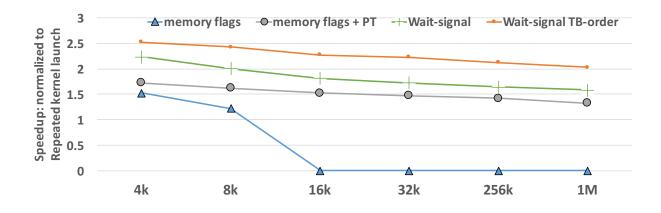

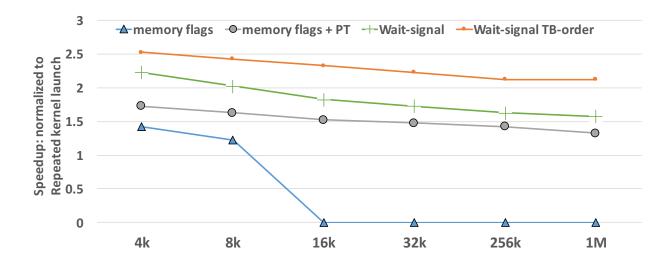

|     |     | 5.2.2 Speedup Comparison                                | 65 |

| 6.0 | TH  | READ-BLOCK LEVEL WAIT SIGNAL WITH HARDWARE SUP-         |    |

|     | PO  | <b>RT</b>                                               | 69 |

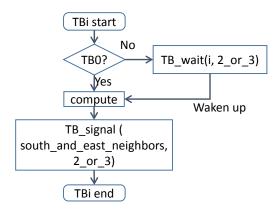

|     | 6.1 | SYNTAX AND USAGE OF WAIT AND SIGNAL IN GPU              | 69 |

|     |     | 6.1.1 Developing Usage for Static Dependencies          | 70 |

|     |     | 6.1.2 Developing Usage for Dynamic Dependencies         | 74 |

|     | 6.2 | COMBINING KERNELS TO AVOID GLOBAL SYNCHRONIZATION       | 75 |

|     | 6.3 | ARCHITECTURE DESIGN                                     | 76 |

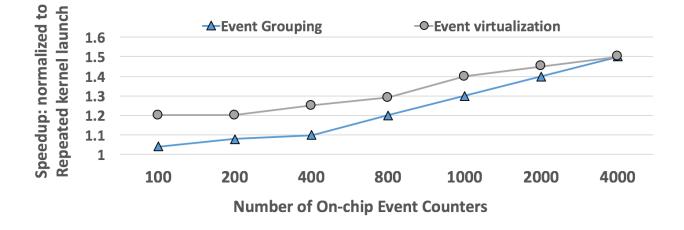

|     |     | 6.3.1 Virtualizing Event Counters                       | 77 |

|     |     | 6.3.2 Integration with Partial Context Switching        | 78 |

|     |     | 6.3.3 Specifying the order of TB Dispatching            | 80 |

|     | 6.4 | Experimental Results of the proposed Wait-Signal Scheme | 82 |

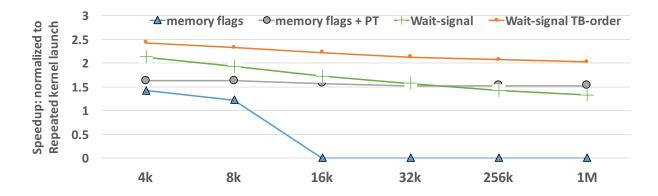

|     |     | 6.4.1 Experimental Methodology                          | 82 |

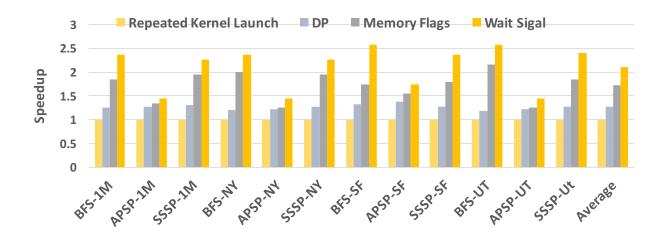

|     |     | 6.4.2 Results for Graph Applications                    | 82 |

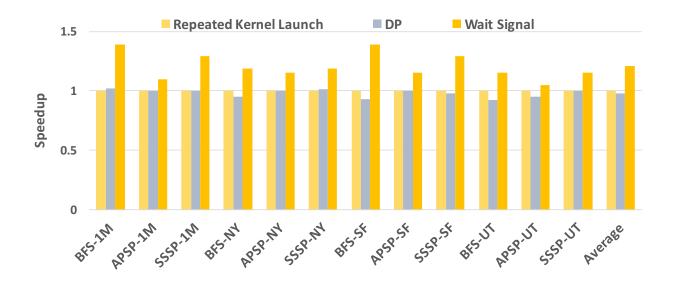

|     |     | 6.4.3 Results for Wavefront Applications                | 83 |

|     |     | 6.4.4 Overhead Analysis                                 | 85 |

| 7.0 | SY  | NCHRONIZATION AWARE GPGPU WARP SCHEDULING               | 93 |

|     | 7.1 | KEY OBSERVATIONS OF SAWS                                | 94 |

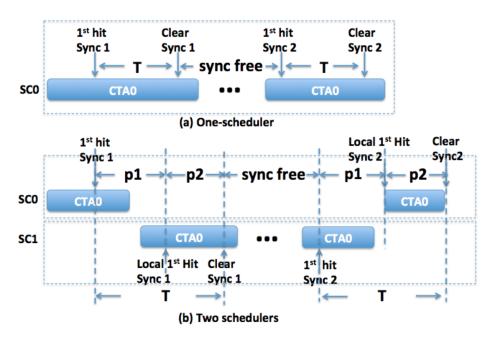

|     |     | 7.1.1 The Anatomy of Synchronization Events             | 95 |

|     |     | 7.1.2 Reducing Intra-CTA Interference                   | 96 |

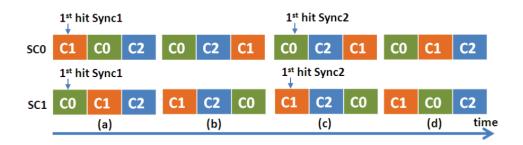

|     |     | 7.1.3 Removing Barriers at the Same Rate                | 97 |

|     | 7.2 | SAWS ALGORITHM                                          | 98 |

|     | 7.3 INTEGRATING WITH PRIOR WARP SCHEDULER                   | 99  |

|-----|-------------------------------------------------------------|-----|

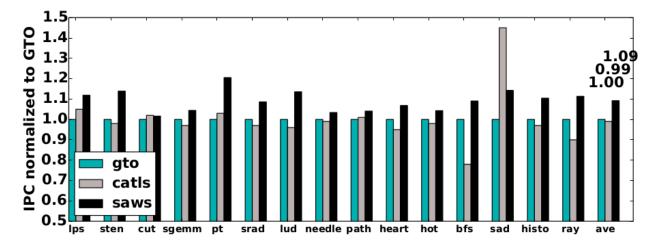

|     | 7.4 Warp Scheduling Experimental Results                    | 100 |

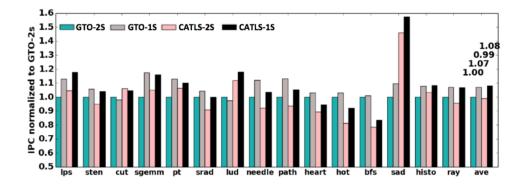

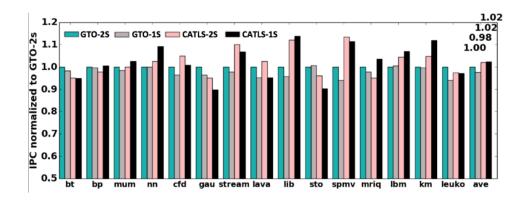

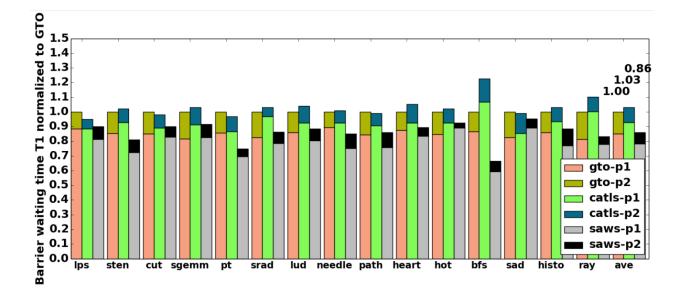

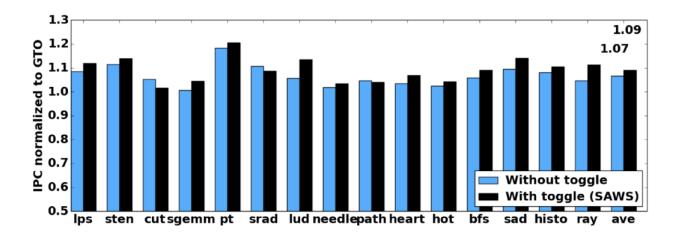

|     | 7.4.1 Performance Improvement, SAWS vs. GTO and CATLS       | 101 |

|     | 7.4.2 SAWS Reduces Barrier Waiting Time                     | 101 |

|     | 7.4.3 SAWS Ensures Uniform Barrier Clearing Rate among CTAs | 102 |

| 8.0 | FUTURE RESEARCH DIRECTIONS                                  | 104 |

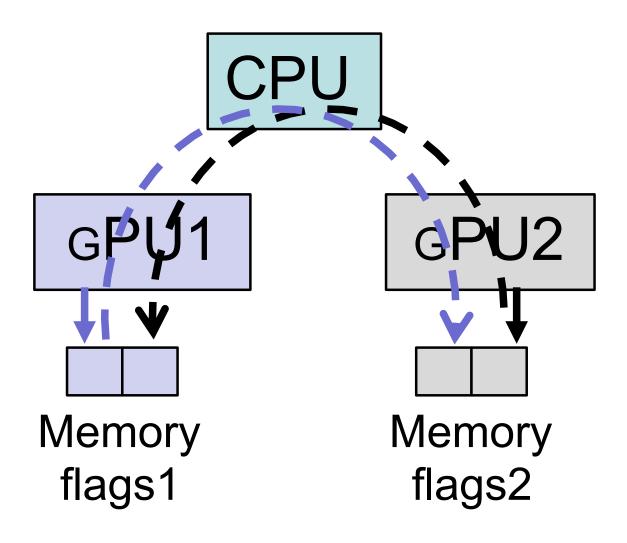

|     | 8.1 SINGLE-NODE MULTI-GPU SYNCHRONIZATION                   | 105 |

|     | 8.2 Multi-NODE MULTI-GPU SYNCHRONIZATION                    | 107 |

| 9.0 | CONCLUSION                                                  | 108 |

| BIE | BLIOGRAPHY                                                  | 110 |

# LIST OF TABLES

| 1 | Overview of proposed schemes and challenges                              | 7             |

|---|--------------------------------------------------------------------------|---------------|

| 2 | Configurations of GPGPU-Sim for evaluation of global synchronization     | 48            |

| 3 | Configurations of GPU devices for RNN speedup comparison                 | 63            |

| 4 | Communication for multiple GPUs. P2P: peer-to-peer GPU communication. [1 | <b>l</b> ]104 |

# LIST OF FIGURES

| 1  | Thread hierarchy of GPU programs                                                                             | 2  |

|----|--------------------------------------------------------------------------------------------------------------|----|

| 2  | General GPGPU architecture. SM: Streaming Multiprocessor                                                     | 3  |

| 3  | Problem overview: (a) global synchronization (b) wait-signal support (c) Syn-                                |    |

|    | chronization oblivious scheduling                                                                            | 7  |

| 4  | GP100 Pascal GPU architecture [2]                                                                            | 17 |

| 5  | Architecture of Streaming Multiprocessor.                                                                    | 18 |

| 6  | Warp scheduling: warps from the same TB are split.                                                           | 19 |

| 7  | Host code examples of CPU driven synchronizations through repeated kernel                                    |    |

|    | launch. (a) stencil computation. (b) convolutional neural network                                            | 19 |

| 8  | Programming patterns with the within-TB synchronization.                                                     | 20 |

| 9  | (a) barrier (wavefront) synchronization vs (b) wait-signal synchronization. Com-                             |    |

|    | puting each tile only depends on the upper and left tiles                                                    | 24 |

| 10 | A basic single recurrent neural network cell                                                                 | 27 |

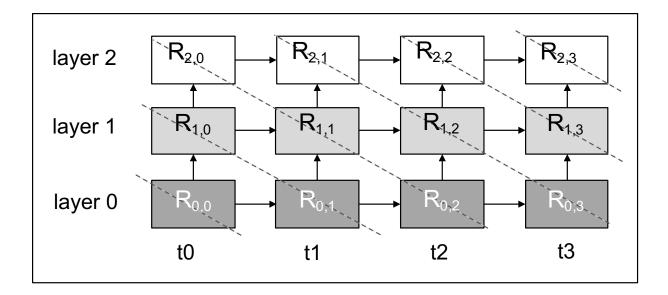

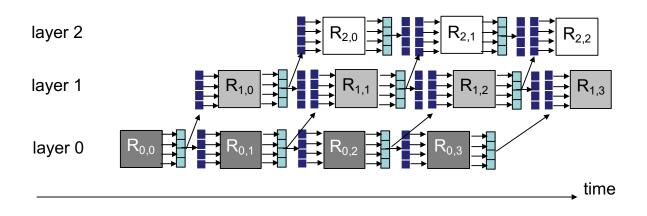

| 11 | Multi-layer RNNs. The dashed line indicates potential wavefront parallelism.                                 |    |

|    | $R_{i,t}$ represents a RNN cell at layer <i>i</i> and time step <i>t</i> . The RNN cells of the              |    |

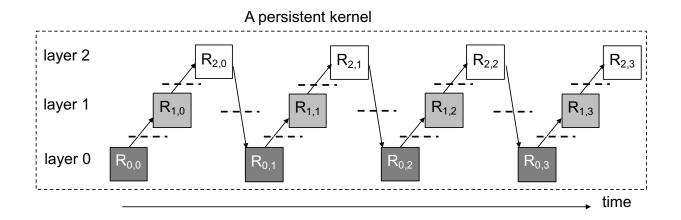

|    | same layer (same shades) share the same weights                                                              | 31 |

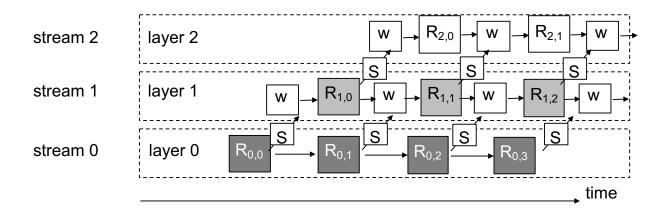

| 12 | Stream Implementation of wavefront parallelism. $W$ : wait event. $S$ : signal                               |    |

|    | event. $R_{i,t}$ represents a <b>kernel</b> to compute a RNN cell at layer <i>i</i> and time step <i>t</i> . | 32 |

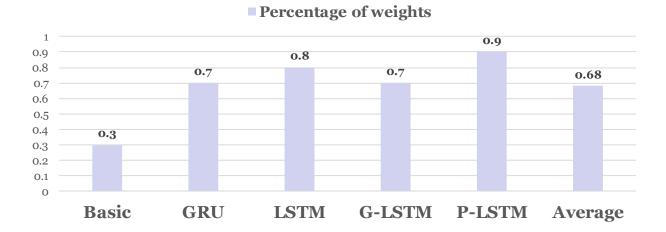

| 13 | Percentage of reused weights in RNNs with batch size $= 4 \dots \dots \dots \dots$                           | 32 |

| 14 | Persistent RNN. The dashed line indicates global barrier. Each $R_{i,t}$ is com-                             |    |

|    | puted by all TBs sequentially.                                                                               | 33 |

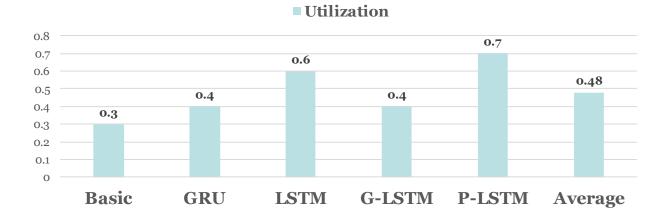

| 15 | GPU utilization with persistent RNN                                                                          | 33 |

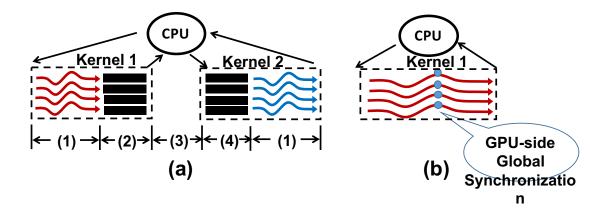

| 16       | Global synchronization through (a) CPU-side API and repeated kernel launch-                                                                                                                             |          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|          | ing: $(1)$ kernel execution, $(2)$ data flushing, $(3)$ kernel launch overhead, $(4)$ data                                                                                                              |          |

|          | reload; (b) the proposed GPU-side synchronization.                                                                                                                                                      | 37       |

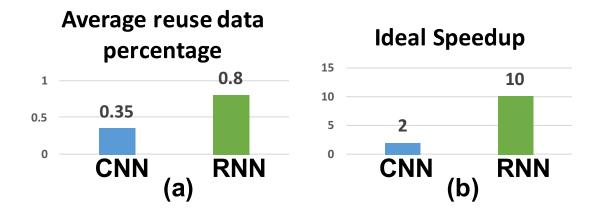

| 17       | (a) Percentage of reused data across global barrier. (b) ideal speedup over                                                                                                                             |          |

|          | repeated kernel launching if there is no data thrashing                                                                                                                                                 | 38       |

| 18       | Code examples of using $\globalSync()$ : (a) stencil computation; (b) CNN                                                                                                                               |          |

|          | application.                                                                                                                                                                                            | 39       |

| 19       | Architecture support for Global Synchronization with Partial Context Switch                                                                                                                             |          |

|          | and meta data for swapped-out TBs                                                                                                                                                                       | 41       |

| 20       | Breakdown of context size reduction                                                                                                                                                                     | 45       |

| 21       | Scheduling swap instructions when TB0 & TB1 are swapped out and TB2 &                                                                                                                                   |          |

|          | TB3 are swapped in (to/from global memory). (a) Baseline. (b) Proposed                                                                                                                                  | 47       |

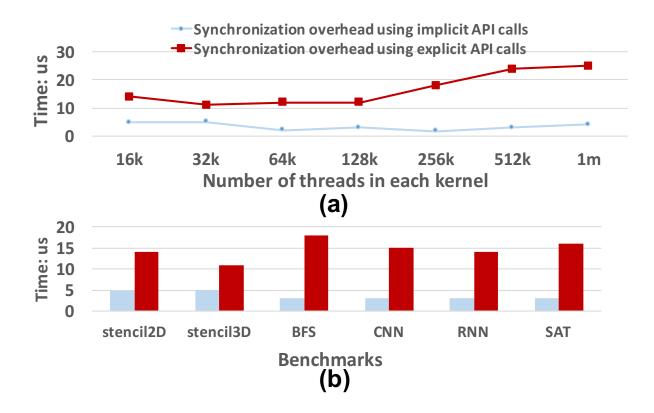

| 22       | API call latency for different data size and applications                                                                                                                                               | 49       |

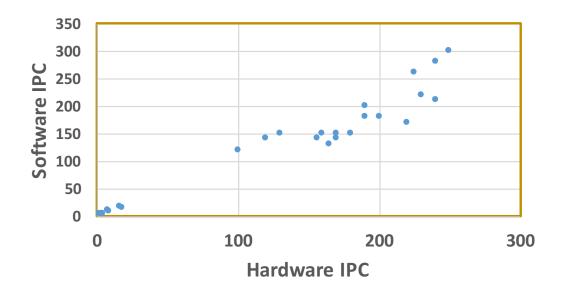

| 23       | Correlation between simulated and real device execution on GTX 970                                                                                                                                      | 49       |

| 24       | Speedup for stencil 2D.                                                                                                                                                                                 | 50       |

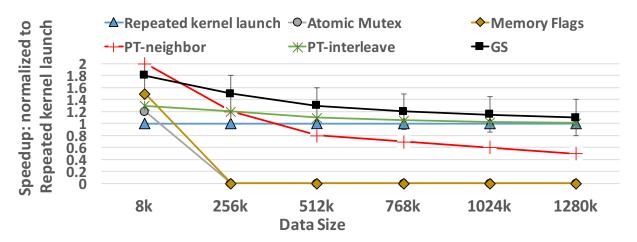

| 25       | Speedup for BFS.                                                                                                                                                                                        | 53       |

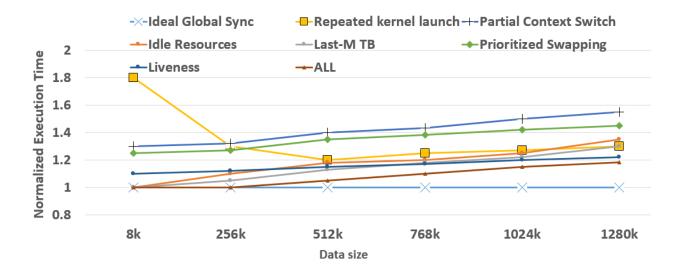

| 26       | Performance overhead of partial context switch normalized to an ideal GS                                                                                                                                | 54       |

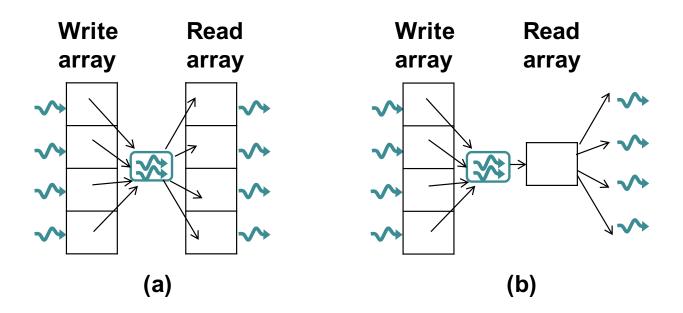

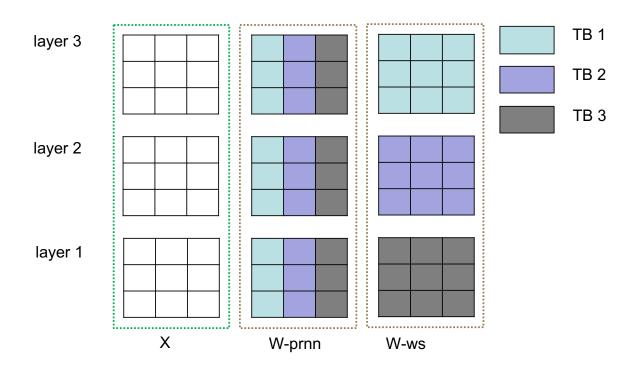

| 27       | The proposed TB-level wait-signal. The light/dark blue arrays are write/read                                                                                                                            |          |

|          | memory flag arrays. The entire network is computed by one kernel and for                                                                                                                                |          |

|          |                                                                                                                                                                                                         |          |

|          | each <i>i</i> , the cells $R_{i,t}$ , $t = 0, 1,$ are computed by a subset of TBs                                                                                                                       | 56       |

| 28       | each <i>i</i> , the cells $R_{i,t}$ , $t = 0, 1,$ are computed by a subset of TBs Fine-grained Parallelism within an RNN cell. $\mathbf{S}_{i,t-1}\mathbf{W}$ and $\mathbf{O}_{i-1,t}\mathbf{U}$ run in | 56       |

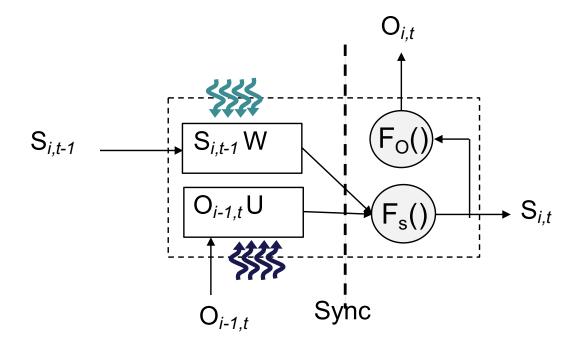

| 28       |                                                                                                                                                                                                         | 56<br>57 |

| 28<br>29 | Fine-grained Parallelism within an RNN cell. $\mathbf{S}_{i,t-1}\mathbf{W}$ and $\mathbf{O}_{i-1,t}\mathbf{U}$ run in                                                                                   |          |

|          | Fine-grained Parallelism within an RNN cell. $\mathbf{S}_{i,t-1}\mathbf{W}$ and $\mathbf{O}_{i-1,t}\mathbf{U}$ run in parallel by different threads.                                                    |          |

|          | Fine-grained Parallelism within an RNN cell. $S_{i,t-1}W$ and $O_{i-1,t}U$ run in parallel by different threads                                                                                         |          |

|          | Fine-grained Parallelism within an RNN cell. $S_{i,t-1}W$ and $O_{i-1,t}U$ run in<br>parallel by different threads                                                                                      | 57       |

| 29       | Fine-grained Parallelism within an RNN cell. $S_{i,t-1}W$ and $O_{i-1,t}U$ run in<br>parallel by different threads                                                                                      | 57       |

| 29       | Fine-grained Parallelism within an RNN cell. $S_{i,t-1}W$ and $O_{i-1,t}U$ run in<br>parallel by different threads                                                                                      | 57<br>60 |

| 29<br>30 | Fine-grained Parallelism within an RNN cell. $S_{i,t-1}W$ and $O_{i-1,t}U$ run in<br>parallel by different threads                                                                                      | 57<br>60 |

| 33 | Speedup comparison for GRU RNN                                                  | 67  |

|----|---------------------------------------------------------------------------------|-----|

| 34 | Speedup comparison for LSTM RNN.                                                | 67  |

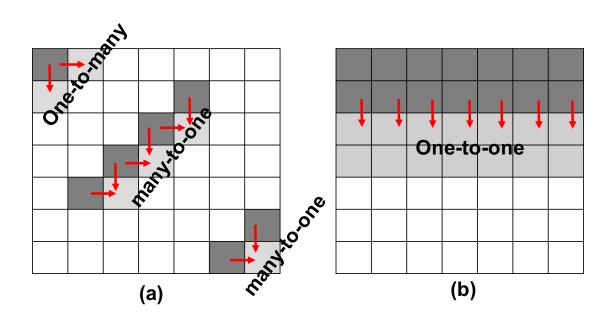

| 35 | (a) Summed area table (SAT) with static one-to-many and many-to-one de-         |     |

|    | pendencies. (b) SAT using PT produces one-to-one dependencies                   | 71  |

| 36 | The use of local synchronization in one-pass SAT.                               | 72  |

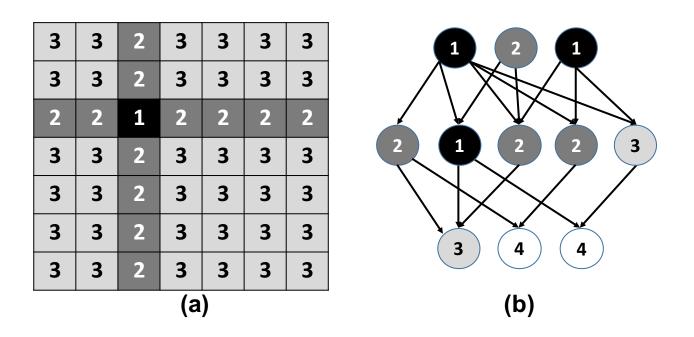

| 37 | (a) All pair shortest path (APSP) with static many-to-many dependencies. (b)    |     |

|    | Breadth first search (BFS) with dynamic dependencies (the number in each        |     |

|    | node indicates the TB that is processing that node)                             | 86  |

| 38 | The use of wait and signal primitives to enforce dynamic dependencies in the    |     |

|    | BFS algorithm.                                                                  | 87  |

| 39 | TB dependencies in the LUD application.                                         | 87  |

| 40 | Skeleton of LUD (a) Global synchronization through repeated kernel launch.      |     |

|    | (b) wait-signal using a combined kernel                                         | 88  |

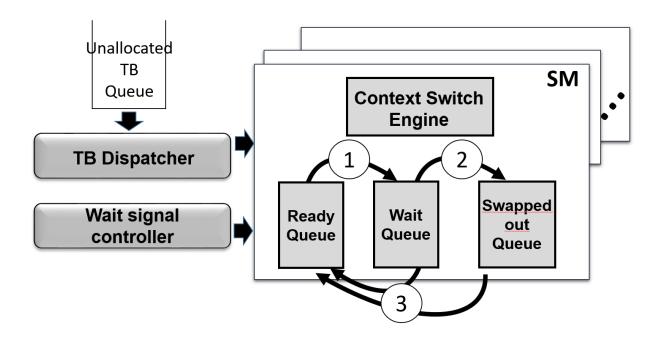

| 41 | Microarchitecture support for Wait and Signal                                   | 88  |

| 42 | Integration with context switch engines.                                        | 89  |

| 43 | Comparing graph applications with sampled data sets (40k nodes)                 | 89  |

| 44 | Comparing graph applications with the original data sets (1M nodes). $\ldots$   | 90  |

| 45 | Comparing SAT with varied data size                                             | 90  |

| 46 | Comparing SOR with varied data size                                             | 91  |

| 47 | Comparing LUD with varied data size                                             | 91  |

| 48 | Measuring the effect of event grouping and counter virtualization using the     |     |

|    | LUD application.                                                                | 92  |

| 49 | Performance of single vs. two<br>scheduler SMs for synchronization-rich kernels | 94  |

| 50 | Performance of single vs. twoscheduler SMs for synchronization-free kernels     | 95  |

| 51 | Timing of synchronization events                                                | 96  |

| 52 | CTA promotion could cause nonuniform barrier-clearing rate.                     | 97  |

| 53 | Performance comparisons for synchronization-rich benchmarks.                    | 100 |

| 54 | Breakdown of barrier waiting time.                                              | 102 |

| 55 | SAWS with and without promotion toggling.                                       | 103 |

| 56 | Single node Multiple GPU global synchronization via memory flags enabled by |     |

|----|-----------------------------------------------------------------------------|-----|

|    | unified virtual memory and demand paging. Dashed arrow: read and write.     |     |

|    | Solid arrow: write                                                          | 106 |

# 1.0 INTRODUCTION

Graphics Processing Units (GPUs) were originally designed to accelerate computer graphics and vision related tasks such as texture mapping [3], ray tracing [4], vertex shading [5] and etc, which are commonly used in video games and 3D rendering [6]. Dating back to 1995, the first GPU was introduced as a 3D graphics add-in chip [7]. During the early 2000s, the major goal of GPU design is how to deliver more polygons with high frame rates to increase the realism of 3D rendering [6]. The nature of geometric and graphics computation is highly parallel and heavily floating-point intensive. The raw throughput requirement of such operations impose a vast pressure on the traditional general-purpose CPU processors. Inspired by the good performance of GPU, scientific researchers and software developers started looking for ways to apply GPUs beyond computer graphics to more general purpose computing.

Programming GPUs used to be notoriously difficult for any simple tasks other than graphics applications [6]. Programmers have to be aware of the low-level hardware details such as the fixed graphics pipelines. Programming languages and interfaces were also limited to graphics-centered APIs such as OpenGL [8], DirectX [9], C for Graphics (CG) [10].

Numerous efforts have been made in the research and industry community to improve GPU programmability. The most successful projects include Compute Unified Device Architecture (CUDA) [11] form NVIDIA and Open Computing Language (OpenCL) [12]. Both CUDA and OpenCL are general-purpose programming models for parallel computing. CUDA is vendor-specific model which is available only to NVIDIA GPUs and accelerators while OpenCL is an open cross-platform standard for all vendors which supports not only GPUs but also CPUs, digital signal processors (DSPs), field-programmable gate arrays (FP-GAs) and other hardware accelerators [12, 13]. CUDA and OpenCL support C as well as other high level programming languages. With widely uptake of CUDA and OpenCL within the academic and industry community, GPU is turned from graphics-centric platform into general-purpose usage, hence the term general-purpose GPU (GPGPU) computing.

Nowadays GPGPU is becoming increasingly popular for a wider range of applications including machine learning, data mining, computational biology and many more scientific and commercial applications. Deep learning and deep neural networks (DNNs) have recently gained attention due to their superior performance and ground-breaking results in various application domains such as computer vision [14], speech recognition [15], and natural language processing [16]. GPGPU is the most successful hardware to accelerate DNN applications [14, 17, 18, 19], including both training and inference, thanks to its tremendous compute horsepower and highly optimized software libraries such as cuDNN [17], tensorflow [20], caffe [21] and so on.

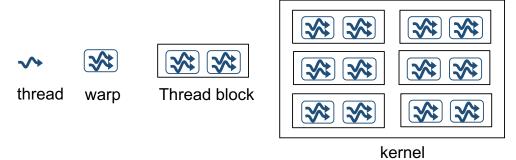

Figure 1: Thread hierarchy of GPU programs

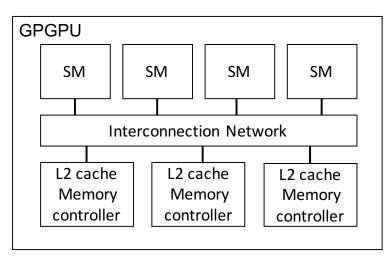

A typical GPU program consists of multiple kernels of thousands of threads. The thread hierarchy is shown in Figure 1. These threads are organized in thread blocks, or TB in short [11, 22] (also known as work groups [23]). A kernel is simply a grid of TBs. Within a TB, a group of threads that are executed in lockstep and scheduled as a unit is referred to as a warp or a wavefront. A warp consists of 32 threads on NVIDIA hardware [11] and a wavefront consists of 64 threads in AMD hardware [23]. As shown in Figure 2, a GPU consists of Streaming Multiprocessors (SM) (also known as Compute Units) with their own shared memories and L1 data caches. Each SM has one or more independent warp schedulers that can quickly switch contexts between threads and issue instructions from different ready

warps. To initialize a kernel, the TB dispatcher dispatches TBs to SMs until all SMs reach their maximum capacities [22]. Then the warp scheduler within a SM picks a ready warp to execute in each cycle. The warp is selected based on a warp scheduling policy such as the round robin policy (RR).

Figure 2: General GPGPU architecture. SM: Streaming Multiprocessor

In efficient parallel algorithms, threads cooperate and share data to perform collective computations. To share data, the threads must synchronize. The granularity of sharing varies from algorithm to algorithm, so thread synchronization should be flexible. Historically, programming models for GPU, including CUDA and OpenCL, have provided a single and simple construct for synchronizing cooperating threads: a barrier across all threads of a thread block, as implemented with the *synchreads* or *barrier* function. Such barrier synchronization is a point in a program where a thread may not proceed further until other parallel threads, in this case threads from the same TB, reach this point. On the other hand, synchronization of TBs or threads from different TBs are not allowed within the kernel. The only operation to achieve such synchronization is to terminate the current kernel and launch the kernel again. All threads of the kernel are synchronized at the kernel boundary hence a global synchronization of all threads are realized. This shows a fundamental design philosophy of current GPU synchronization. By not allowing threads in different TBs to perform barrier synchronization with each other, GPU run-time system does not need to deal with any constraint while executing different TBs. In other words, TBs can execute in any order relative to each other since none of them need to wait for each other. This flexibility enables transparent scalability [11, 22]. Without changing the code, the performance of the program scales naturally with different hardware configurations (different number of cores).

However, programmers often need to define and synchronize groups of threads larger or smaller than thread blocks in order to enable greater performance, design flexibility, and exploit finer parallelism. Therefore hardware and architectural modifications are necessary for efficient, flexible and reliable synchronization mechanisms.

# 1.1 THE CHALLENGES FOR GPGPU SYNCHRONIZATION

# 1.1.1 Inefficient Global Synchronization

Current GPU global synchronization (Gsync) across the entire grid of threads is inefficient. Gsync is typically achieved by slicing a kernel at the synchronization points, often leading to repeated kernel launches [11, 12]. Such an approach incurs overhead due to API calls and data thrashing. Previously, these overhead are deemed acceptable since many parallel processing have long-latency kernels which outweighs those overheads. However, with the recent development of real-time deep learning applications such as image recognition in self-driving cars [24] and speech recognition [15] in instantaneous speech to text (STT), the response time of inferring one image or one sentence (not training) is crucial. In those scenarios, each kernel finishes in several hundreds of microseconds, which makes kernel launch Gsync-related overhead more pronounced. Existing software workarounds such as atomic operations and memory flags may lead to deadlock when the GPU cannot simultaneously host all the threads [25].

## 1.1.2 Lack of Wait-Signal Support

GPU performance on applications with irregular parallelism and producer-consumer dependencies has suffered from a limited support for synchronization primitives. For these problems, global synchronization unnecessarily involves all the thread blocks. Existing software partial synchronization across thread blocks use atomic operations or memory flag-arrays, which rely on busy-wait loops that can cause underutilization of hardware resources and may lead to deadlock for large data sizes [26]. Specialized Warps [27] present a hardware solution that achieves partial synchronization among the warps of a thread block but do not extend to synchronization between thread blocks. Cooperative groups [28] can also synchronize thread blocks but are not flexible and efficient enough to express fine-grained dependencies. Heterogeneous system architecture (HSA) and Asynchronous Task Management Interface (ATMI) [13, 29] implement wait-signal at kernel level with dedicated APIs and task queues, which is less effective utilizing GPU hardwares compared to thread block (TB) level wait-signal schemes. Dynamic parallelism [11, 13] is also a kernel-level optimization for data dependent workloads but is not efficient for applications with static dependencies due to excessive launching of children kernels for small tasks.

One classic application to demonstrate the importance of wait-signal mechanism is Recurrent neural network (RNN). RNNs are an important family of deep learning models which can learn the sequential pattern of input data. Multi-layer RNNs have two unique properties: 1) wavefront parallelism across layers and time steps and 2) reusing weights over multiple time steps during inference. Previous GPU-accelerated RNNs exploit these two optimization opportunities separately. Specifically, the wavefront synchronization is realized with kernel-level APIs such as *hsa\_signal\_wait\_acquire* or *cudaStreamSynchronize*. Preserving the weights using on-chip registers are achieved by persistent thread models at the thread block level which rely on global synchronization barriers to enforce the dependencies.

# 1.1.3 Synchronization Oblivious Warp Scheduling

Traditional warp scheduling policies of GPGPU have been optimized to increase memory latency hiding capability [30], improve cache behavior [31], and alleviate branch divergence [32]. However, warp scheduling policies do not account for the synchronization behavior among warps under the presence of multiple warp schedulers. A warp may stall the cores due to a thread incurring a long latency operation. Hence, GPGPU SMs can switch to different warps to continue execution and stay active. On every cycle, a scheduler makes the decision on which warp to issue next. An uninformed execution order of warps may create unnecessary scheduling stalls and SM idle times. Barrier synchronizations, which are used to coordinate execution among threads, are adopted in a wide range of general purpose applications. The most common barrier is the TB-level barrier, where all threads of a TB have to arrive at a single point before any of them can proceed. A TB is assigned entirely to one SM. I made a key observation that the warps within a TB are distributed evenly to each scheduler of an SM to balance the load. Hence, each scheduler only sees part of one TB, and performs scheduling independently of other schedulers. Their scheduling decisions and order are also entirely different. When synchronization barriers are present, hitting the same barrier on different schedulers could be very far apart in time, causing earlier warps to stall for a long time waiting for the latest warp to clear out the barrier. None of the existing warp schedulers address this issue due to their synchronization unawareness.

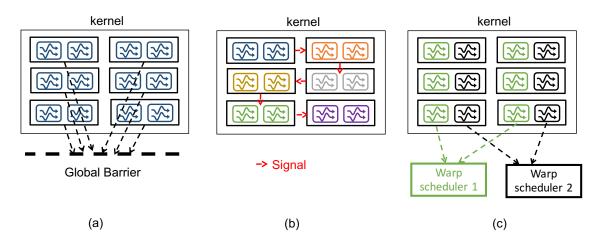

# 1.2 THESIS OVERVIEW

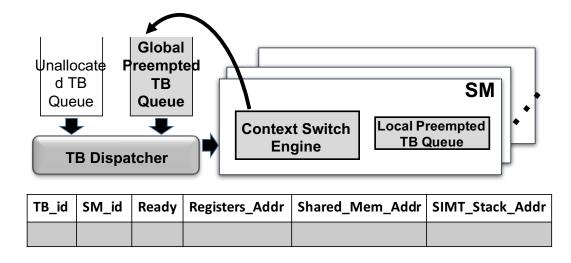

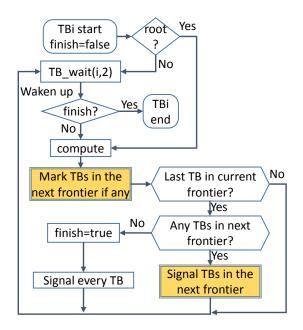

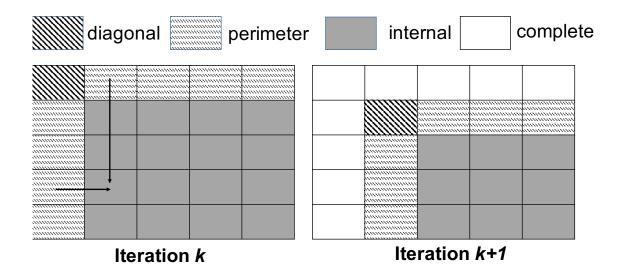

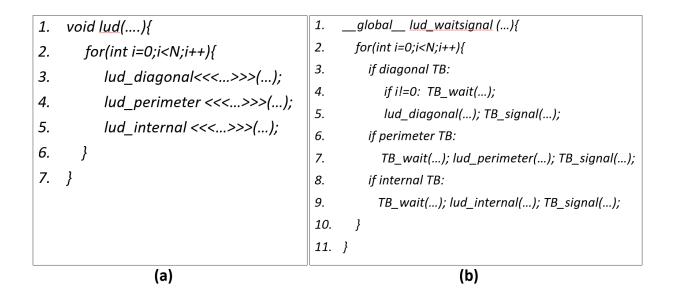

The problems to be solved are summarized in Figure 3. Figure 3(a) shows the global synchronization where all threads and TBs are synchronized at a global barrier. Since the number of TBs can exceed the capacity of GPU, synchronizing all TBs requires marking the status of each TB and context switch out and in TBs appropriately. Figure 3(b) shows the problem of implementing wait-signal scheme at TB level. Producers and consumers are placed in different TBs. Consumer TBs should be blocked until a signal is received from the producer TB it depends on (the red arrow in Figure 3(b)). Figure 3(c) shows the problem of synchronization oblivious warp scheduling. The warps of the same TB are split and distributed to each warp scheduler. If a within-TB barrier is used in the kernel, the barrier will introduce additional delay since the two warp schedulers do not communicate with each other. To solve these problems, I propose several architectural techniques as summarized in Table 1 with the major challenges for each scheme. For global synchronization, I propose an efficient hardware support to synchronize thread blocks globally within the kernel. A

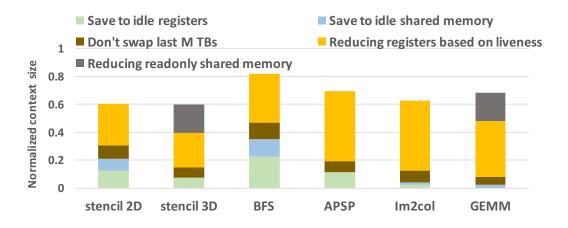

hardware counter is used to manage a global barrier across thread blocks and partial context switch is leveraged to avoid deadlock. Moreover, we design several techniques to reduce the context switch overhead which is critical to performance improvement. The proposed scheme outperforms repeated kernel launch when 1) data reuse is significant across synchronization points and/or 2) the latency of the API calls is relatively long.

Figure 3: Problem overview: (a) global synchronization (b) wait-signal support (c) Synchronization oblivious scheduling

| # | Scheme                               | Challenges                         |

|---|--------------------------------------|------------------------------------|

| 1 | Global Synchronization               | Large contexts to save             |

| 2 | TB-Level Wait-Signal                 | Complex producer-consumer patterns |

| 3 | Synchronization-Aware Warp Scheduler | No cooperation of warp schedulers  |

Table 1: Overview of proposed schemes and challenges

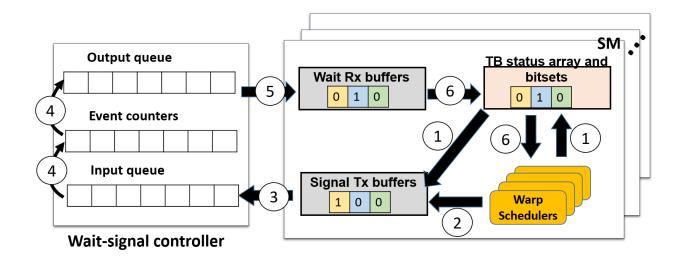

For wait-signal support, I propose a hardware-software cooperative framework to achieve Wait-Signal mechanism between thread blocks in GPGPUs to efficiently exploit the inherent parallelism of producer-consumer problems. The proposed scheme guarantees deadlock-free execution and improves load balancing. The global thread block dispatcher is augmented with a wait-signal controller to manage event counters and synchronization of thread blocks. To avoid busy wait loops, the "Wait" instruction blocks a TB and releases its computing resources for use by other TBs. The happen-before relationships of "Signal" and "Wait" is resolved by allowing both wait and signal instructions to increment an event counter while only wait instructions are blocking. The proposed wait-signal mechanism is flexible to support both static and dynamic producer consumer dependencies. In order to achieve load balancing and avoid unnecessary context switch, we propose a kernel configuration extension to initialize the order of TB dispatching based on the dependencies implied by the applications.

To accelerate RNNs as a representation of producer-consumer problems, we propose a novel wait-signal mechanism at the thread block (TB) level to accelerate multi-layer RNNs. The multi-layer RNN is launched in a single kernel where weights are loaded in registers only once and persist for all the unfolded time steps. The weights of each layer are statically allocated to a specific group of TBs that collaborate to accomplish one computing task for the current time step (namely matrix multiplication). After synchronizing using a local barrier, the TB group assigned to a given layer signals the TB groups assigned to the next layer and waits for the results from the previous layer before proceeding with the computation for the next time step. The local barrier and the wait signals are implemented by lock-free memory flags. With the proposed TB-level wait-signal mechanism, the wavefront parallelism is achieved and unnecessary memory reloading of weights is avoided. We implemented the proposed wait-signal mechanisms on the latest GPUs and evaluated the speedups using a number of widely used RNNs. On average, the proposed scheme achieves 37% speedup over the state-of-the-art persistent RNNs.

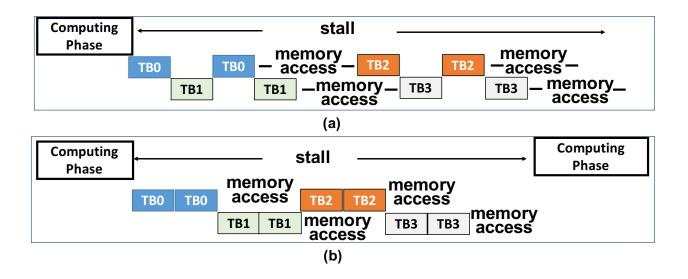

To improve performance of within-TB synchronization in the context of multiple warp schedulers, I propose a warp scheduling algorithm that is synchronization aware. The key observation is that excessive stall cycles may be introduced due to synchronizing warps residing in different warp schedulers. We propose that schedulers coordinate with each other to avoid warps from being blocked on a barrier for overly long. Such coordination will dynamically reorder the execution sequence of warps so that they are issued in proximity when a barrier is encountered.

# 1.3 CONTRIBUTIONS

# 1.3.1 Efficient GPU Global Synchronization with Light Weight Context Switch

I propose a new global synchronization (Gsync) function at the GPU-side, which applies to both conventional SPMD and persistent programming styles. The existing SM and TB dispatcher is augmented to manage GS and partial context switches of the TBs. I also propose effective techniques for reducing the overhead of context switching to achieve scalability. The experimental results show that the proposed scheme outperforms existing software approaches in three typical type of applications with up to 2x speedup over CPU-driven synchronization. I make the following contributions.

- An extensive study on the effectiveness and trade-offs of the existing software approaches for Gsync in both CUDA and OpenCL

- efficient approach to explicitly support global synchronization using partial context switch to avoid deadlocks. The proposed approach improves both performance and programmability.

- Case studies of representative applications, including scientific computing, graph traversal and machine learning, to demonstrate how to use the proposed Gsync function call and benefit from its performance advantages.

### 1.3.2 Accelerate RNNs with software Wait-Signal

I propose a novel wait-signal mechanism at the thread block (TB) level to accelerate multilayer RNNs. First, we implement the *wait()* and *signal()* functionality via lock-free memory flags [25]. A TB that calls a *wait()* function will be stalled until its dependent TBs execute a *signal()* function. With such fine-grained synchronization, the theoretical maximum wavefront parallelism can be achieved. The proposed scheme also improves the computation efficiency and the reuse of shared memory. Specifically, in the proposed scheme, the weights of a certain layer are partitioned among TBs, which is different from the state-of-the-art persistent RNN scheme[33], where the weights of the entire neural network are partitioned among TBs. I make the following contributions:

- A study of the potential for accelerating RNNs with both wavefront parallelisms and on-chip storage of weights.

- The design of an efficient wait-signal functionality at the TB-level using memory flags. This increases both parallelism and hardware occupancy for RNN implementations.

- Experimentation with different representative RNN applications to demonstrate the impact of key hyper parameters such as number of layers, feature dimensions and sequence length on the proposed design.

# 1.3.3 Thread Block Level Wait and Signal in GPU with Hardware support

I propose a Wait-Signal mechanism with hardware support for local synchronization of thread blocks in GPGPUs. Each Streaming Multiprocessor is augmented with wait and signal buffers and extend the global thread block dispatcher with a wait-signal controller to manage event counters. The proposed scheme can be integrated with context switch engines that were previously proposed for swapping TBs when all the TBs of a kernel cannot fit simultaneously on the GPU. I also propose a mechanism that allows applications to control the order of TB dispatching, thus eliminating the need for context switching in single pass wavefront application kernels as long as the TBs constituting an active front can fit on the GPU.

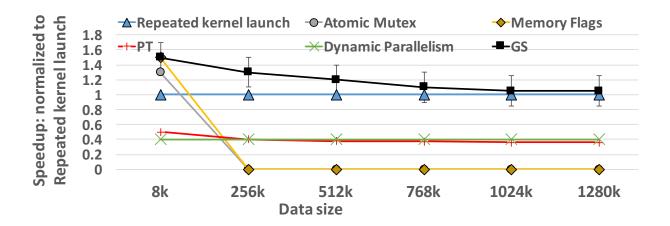

The proposed mechanism can support one-to-one, one-to-many, many-to-one, and manyto-many producer consumer dependencies. Cycle-accurate simulation shows that, on average, the proposed scheme achieves 2.0x speedup over repeated kernel launch and 31% speedup over the best-known software memory flags techniques. I make the following contributions.

- An extensive study of the effectiveness and trade-offs of the existing approaches for producer-consumer relationships.

- An efficient approach to explicitly support Wait and Signal in hardware to exploit finegrained parallelism, guarantee deadlock-free execution and improve load balancing.

- Case studies of representative applications executing wavefront and graph algorithms.

# 1.3.4 Synchronization Aware GPGPU Warp Scheduling

I propose Synchronization Aware GPGPU Warp Scheduling (SAWS) to tackle warp scheduling to mitigate performance loss due to synchronization events in SMs with multiple schedulers. Current designs treat each scheduler independently, which works well without synchronization barriers, but exposes deficiency with barriers. I find that multiple schedulers, when operating independently, will delay the clearance of barriers and create excessive stall cycles to the warps. Hence, I propose to coordinate among multiple schedulers and prioritizes warps as a reaction to synchronization events. In addition, I find that maintaining a uniform barrier-clearing rate during prioritization brings additional performance benefit.

Our proposed scheme SAWS is so simple that integrating it with existing scheduler does not require much additional hardware. The evaluation shows that SAWS can speed up barrier clearance by 15% and total execution by 10% on average, when compared with the state-of-the-art warp scheduler. Finally, SAWS shows its increasing effectiveness when the number of scheduler grows, proving that it is a scalable design. Specifically I make the following contributions.

- A detailed analysis of performance loss due to mishandling of synchronization barriers with multiple warp schedulers.

- A simple synchronization aware warp scheduling algorithm that coordinates multiple schedulers to minimize barrier waiting time and synchronization-induced stalls.

- A design that can be seamlessly integrated with existing warp scheduler so that synchronizationrich kernels can be well handled while not harming synchronization-free kernels.

- A simulation evaluation of performance advantages of the proposed scheduler over existing well-studied warp schedulers.

# 1.4 THESIS ORGANIZATION

The rest of this thesis is organized as follows. Chapter 2 presents preliminary information of GPGPU. Chapter 3 discusses the related work. The efficient global synchronization is described in Chapter 4. Software implementation of wait-signal to accelerate RNNs are introduced in Chapter 5. Chapter 6 illustrates the thread-block level wait-signal scheme. The synchronization-aware warp scheduling is explained in Chapter 7. Chapter 8 describes the future research directions. Chapter 9 concludes the thesis.

# 2.0 BASICS OF GPGPU

# 2.1 GPGPU ARCHITECTURE

General Purpose Graphic Processing Units (GPGPUs) have been evolved actively in recent years with increasing number of cores, higher clock frequency and high-bandwidth highcapacity on-board GPU memory. For example, the state-of-the-art Nvidia Pascal GPU architecture is shown in Figure 4 [2]. The SMs are grouped into Texture Processing Clusters (TPCs) and Graphics Processing Clusters (GPCs). The global GigaThread controller manages TB dispatching, application context switching and also provides a pair of streaming data-transfer engines, each of which can fully saturate GPU's PCI Express host interface.

Each memory controller is attached to 512 KB of L2 cache, and each High Bandwidth Memory (HBM) DRAM stack is controlled by a pair of memory controllers. The full GPU includes a total of 4096 KB of L2 cache. L1 cache can serve as a texture cache depending on workload. The unified L1/texture cache acts as a coalescing buffer for memory accesses, gathering up the data requested by the threads of a warp prior to delivery of that data to the warp.

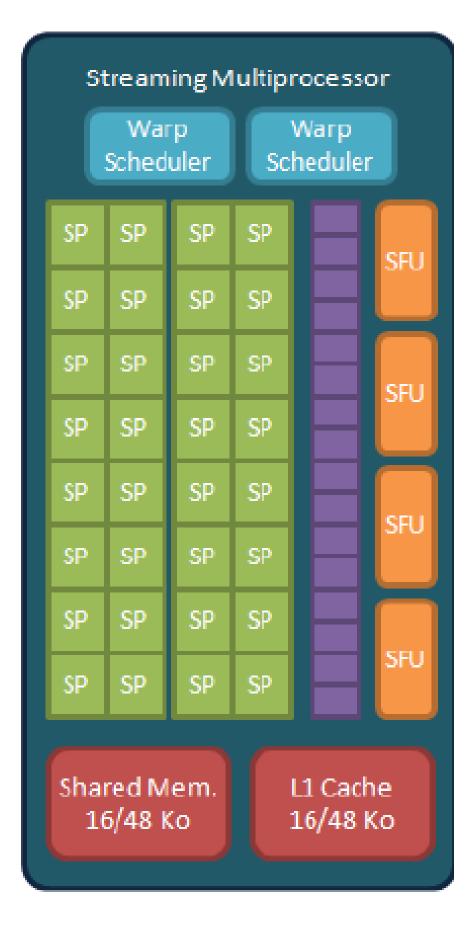

### 2.2 STREAMING MULTIPROCESSOR ARCHITECTURE

The most critical component of GPU is the streaming multiprocessor, or SM in short. As shown in Figure 5, Each SM consists of many simple scaler processors (SP) for common simple calculations such as addition and several special function units (SFUs) for complex calculations such as exponential operations. There are abundant of registers on the SM private to each thread. There is also a L1 data cache which can cache global memory access shared by all threads on the SM. Different from CPU, the capacity of registers (96 KB) on the SM is larger than that of the L1 cache (48 KB). The shared memory is a special scratch memory that is programmable and to be shared by threads from the same TB. In previous GPU architecture, shared memory and L1 cache are physically the same device and can be configured/split by programmers. Recent GPU architecture provides dedicated independent shared memory and L1 cache.

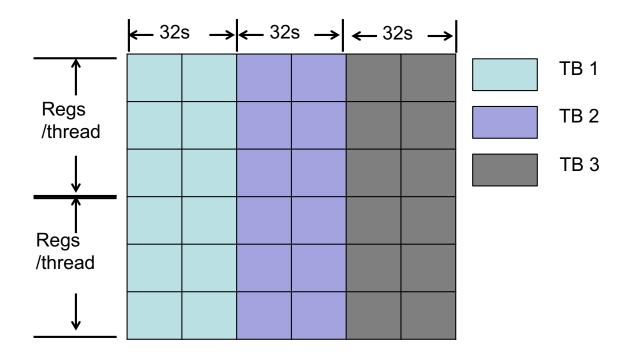

# 2.3 WARP SCHEDULING

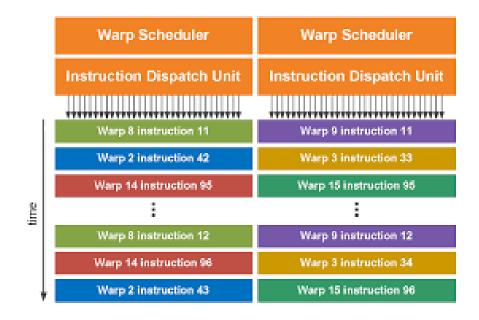

As shown in Figure 5, there are multiple warp schedulers in one SM. The number of warp schedulers range from two to four.

When a kernel is dispatched to a GPGPU, a global TB dispatcher assigns TBs to SMs until all SMs are saturated. An SM may be assigned more than one TB at a time, since the size of a kernel and its TBs may vary. An SM which finishes a TB will get a new one from the global dispatcher, until all TBs of a kernel finish. Hence, the execution latency of a kernel is dependent on how quickly the SMs complete their TBs.

As the core count increases in the latest generations of GPGPUs, each SM may contain one, two or four warp schedulers. When a TB is assigned to an SM, its warps are further assigned to those warp schedulers in a round robin fashion in order to balance the warp distribution, as shown in Figure 30. During execution, each warp scheduler selects a ready warp to execute, allowing one, two or four warps to issue and execute concurrently. A warp can become blocked due to a long latency operation such as a load from the memory or a barrier synchronization. The warp scheduler switches context to another ready warp, if such warp can be found, to mask the stalled cycles due to long latency operations. If no such warps can be found, the scheduler stalls, causing resource underutilization. In fact, how the warps are selected to execute determines the resulting number of stalled cycles. Hence, effort has been put on optimizing the scheduler to mask or reduce stall cycles.

# 2.4 GPU SYNCHRONIZATION PRIMITIVES

#### 2.4.1 Global Synchronization

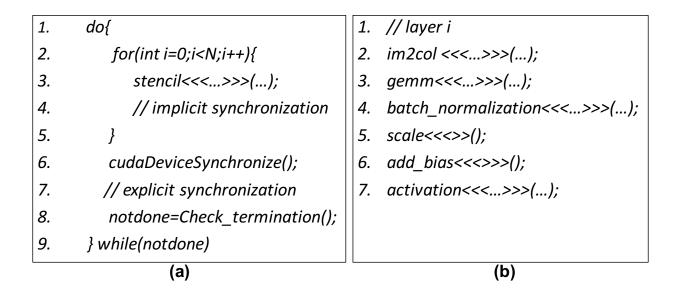

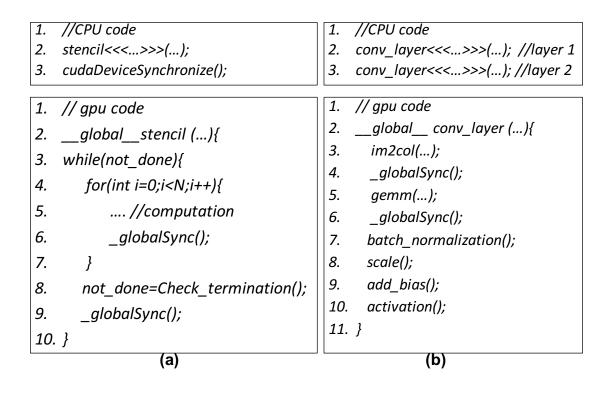

Figure 7 shows host (CPU) code examples where kernels are sequentialized by either implicit or explicit CPU-driven synchronizations. As such programming style typically puts kernels and synchronizations in loop bodies, we term this synchronization method "repeated kernel launching". In Figure 7(a), the kernel **stencil** is invoked N times (line 3) within the inner for loop and then the termination condition (convergence in this case) is checked in line 8 of the outer while loop[34]. Each kernel launch calculates the new values for all data points based on the results of the previous kernel. Other stencil-like applications, such as solving Laplace differential equations, also follow a similar coding style [34].

Global synchronization is needed between kernel launches, and before the convergence check. In the *for* loop, since no CUDA streams are specified, all kernels launched belong to a default NULL stream [11]. Kernels in the NULL stream are guaranteed to execute sequentially, which is one of the most common type of implicit global synchronization [11]. Explicit CPU-driven synchronization is also used in this example, by invoking cudaDeviceSynchronize() at line 6. This call is necessary because kernel launch is asynchronous with respect to host code [11]. If cudaDeviceSynchronize() is not used, the convergence checking at line 8 will be executed immediately after launching N kernels and before the kernels finish execution, thus giving incorrect results.

#### 2.4.2 Within-TB synchronization

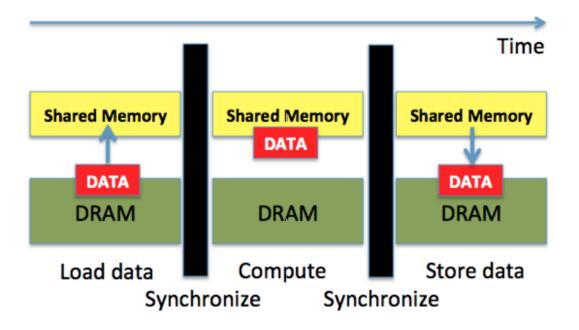

GPU programming models also provide explicit within-TB synchronization instructions such as *syncthreads()* in CUDA or *barrier()* in OpenCL. This instruction is used to synchronize all the threads in the same TB.

Many applications, including graphic and general purpose applications, adopt synchronizations to coordinate among multiple threads and guarantee execution correctness when parallelized onto a GPGPU. Within a TB, threads may operate on shared data but make progress at different rate and arrive at different phases, e.g. read or write phases, at different times. The synchronization barrier ensures that all threads in the same TB complete one phase before moving on to the next. In the CUDA programming model, for example, shared data may be first loaded into the fast on-chip shared memory of each TB, which is the read phase. Then, computing starts by accessing the shared memory, which is the compute phase. Finally, the shared data is written back to the main memory, which is the write phase. Within-TB synchronization barriers must be used between adjacent phases to guarantee that the read and write sequence of the shared data is correct. Figure 8 illustrates such a common programming paradigm.

| Host Interface                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                     | ead Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| GPC<br>Raster Engine<br>SM SM SM SM                                 | GPC Raster Engine + + + + + + + + + + + + + + + + + + +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Polymorph Engine Polymorph Engine Polymorph Engine Polymorph Engine | Polymorph Engline Polymorph En |  |

| vertoo troo<br>SM SM S             | Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

Figure 4: GP100 Pascal GPU architecture [2].

Figure 5: Architecture of <sup>18</sup>Streaming Multiprocessor.

Figure 6: Warp scheduling: warps from the same TB are split.

Figure 7: Host code examples of CPU driven synchronizations through repeated kernel launch. (a) stencil computation. (b) convolutional neural network.

Figure 8: Programming patterns with the within-TB synchronization.

### 3.0 RELATED WORKS

#### 3.1 ADDRESSING GLOBAL SYNCHRONIZATION

Many applications require global synchronization (Gsync) to coordinate among parallel tasks, which is typically a point (barrier) in a program where a thread may not proceed further until all other parallel threads reach this point. Currently, GPUs do not support explicit implementation of Gsync. There are mainly two workarounds that have been commonly used: 1) split the program into separate kernels where Gsync is needed [11, 25], which we term "repeated kernel launching" as the Gsync and split kernels are typically in loop bodies; 2) use atomic operations or memory flags similar to those used in a CPU [25]. However, both workarounds could degrade performance or lead to deadlock.

## 3.1.1 Dynamic Parallelism

One variant of repeated kernel launching introduced before is *dynamic parallelism* (DP) [35, 36, 37] which differs from repeated kernel launching in that kernels are launched from within the GPU. A master kernel launches a sequence of children kernels with in-GPU cudaDeviceSynchronize() in between. Hence, DP doesn't yield control from the GPU to the CPU. The overheads of DP include kernel queuing, dispatching and context setup when launching thread blocks [35, 36]. Further, when DP launches many small children kernels, serious slowdown occurs due to low hardware utilization and limitation of call stacks, as well as other factors [35, 38]. Such overhead can be mitigated by kernel aggregation [35, 38]. Heterogeneous System Architecture (HSA) with support of OpenCL 2.0 also implements an efficient dynamic parallelism which does not suffer from call stack limitations [39].

## 3.1.2 Atomic Operations and Memory Flags

Using atomic mutex at the GPU side is one way to avoid splitting a kernel. An atomic function performs a read-modify-write operation on a variable residing in global memory [11, 40]. The basic idea is to use a global mutex variable to count the number of TBs that invoke global synchronization. All TBs busy-check this counter in the memory until it reaches a predefined value. Global memory atomics are long latency operations which are at least 10x slower than atomic operations using on-chip local memory on AMD Radeon GPU [40]. More efficient atomic operations are available. For example, Global Data Share (GDS) of AMD GCN [41] is a special global memory which can utilize atomic operation to implement a fast global barrier. Another option is to implement a lock-free global barrier with memory flag arrays to achieve the same purpose but with better performance than global memory atomics [25].

In either implementation, the kernel is launched once and iterates at the GPU side with one global synchronization at the end of each iteration. Hence, the CPU API call and data thrashing overheads are removed. However, those mechanisms are prone to deadlocks because they require that all TBs of the kernel be dispatched to the GPU. Otherwise, executing TBs that reach the Gsync point are kept busy checking the global counter and never release their resources. In turn, pending TBs never get a chance to execute and progress to the Gsync point. Thus, executing and pending TBs deadlock waiting for each other causing deadlock [42].

## 3.1.3 Persistent threads

Persistent thread (PT) is a programming approach where the kernel is persistent on the GPU until no work remains. When input data size increases, the number of TBs in a PT kernel stays the same and more workload is processed by each thread. Therefore, PT style code is fundamentally different from the general parallel programming style where one thread maps to certain data points statically. A PT kernel also uses atomic operations or memory flags to implement Gsync. PT relies on programmers to correctly define the kernel dimension to achieve full occupancy, balance load and avoid deadlock [43, 42]. Since occupancy depends on

the available resource, PT code is not portable from device to device unless the programmer uses careful device profiling and kernel configuration routines. PT also prohibits independent progress of kernels from different streams or queues [13].

Advanced PT programming techniques to optimize the task-flow graph are proposed for specific synchronization problems, usually with compiler design to automatically optimize dependency graphs of the workload at thread block level. Free launch is such a compiler design to realize global synchronization for dynamic irregular workloads [38]. Peer Wave proposed a program model to manually map wavefront problem to regular PT tiles [26]. PT RNN [33] also manually optimize the programming by transforming the computing graph with global barrier only. Although achieving great performance improvement, in general these methods are limited to one specific type of applications. The PT programming style is also difficult and time-consuming to implement and understand. We argue that with architectural design and APIs, a comparable level of performance improvement can be achieved with simple conventional CUDA programming style for a more broad group of applications.

#### 3.1.4 Cooperative Kernels

CUDA Cooperative kernels [11] simplifies the profiling by providing auxiliary APIs to calculate occupancy for a given kernel. *cudaLaunchCooperativeKernel* accepts the number of SMs or maximum number of TBs on an SM as input arguments to guarantee co-residency of TBs. After a kernel is launched, the *grid.sync()* is called for global synchronization. Furthermore, such synchronization doesn't invalidate registers and shared memory [28]. Although the underlying implementation has not been made public, the documentation implies that context switch is not supported and the number of TBs in the kernel is statically determined.

# 3.1.5 Occupancy Discovery Protocol

Alternatively, an occupancy discovery protocol is proposed to dynamically discover a safe occupancy for a given GPU and kernel, allowing for a deadlock-free inter-TB barrier by restricting the number of TBs/workgroups according to this estimate [42]. On the one hand, this solution only applies to the kernel which is agnostic to the number of TBs and can

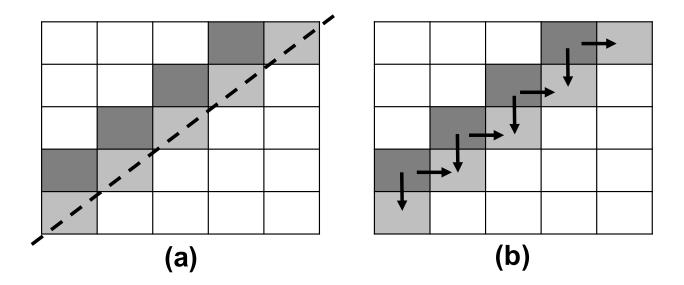

Figure 9: (a) barrier (wavefront) synchronization vs (b) wait-signal synchronization. Computing each tile only depends on the upper and left tiles.

distribute workloads to TBs dynamically like the PT model [42]. On the other hand, it is likely that the occupancy detected is less than the maximum occupancy [42] and underutilizes GPU resources.

# 3.2 ADDRESSING PRODUCER CONSUMER PROBLEMS

Repeated kernel launch is the most common strategy which enforces dependencies by putting producers and consumers in separate kernels, thus realizing global synchronization at the boundary of kernels [11, 25]. Cooperative groups [28, 11] implements a barrier synchronization for a subset of threads either in the same TB or across different TBs in the same kernel. Both repeated kernel launch and cooperative groups are not flexible enough to express fine-grained producer-consumer dependencies and exploit fine-grained parallelization opportunities like Figure 9.

A barrier synchronizes the current wavefront (darker tiles) before executing any of the lighter tiles. Clearly, a more efficient synchronization should allow each light tile to only wait for its upper and left neighbors. Previous works showed that even an optimized barrier synchronization implementation can result in at least 20% slowdown compared to wait-signal synchronization [26].

#### 3.2.1 Asynchronous Task Management Interface

Heterogeneous system architecture (HSA) defines wait-signal APIs such as *hsa\_signal\_wait\_acquire* [13]. Asynchronous Task Management Interface (ATMI) is a low-level realization on top of HSA for kernel-level wait-signal on HSA-compatible GPUs [29]. ATMI utilizes HSA waitsignal API calls, barrier packets and the underlying hardware support to execute asynchronous tasks of producer-consumer problems. Independent kernels are pushed in separate HSA task queues and executed in parallel. Dependencies are specified by inserting a special barrier packet into the task queue which can have signals associated with it [29]. ATMI achieves 1.6 to 3.3 speedup over repeated kernel launch.

Despite the kernel launch overhead, there are some potential limitations of ATMI. First, Independent kernels have to be in separate task queues to run in parallel. The number of such queues are limited. For instance, there are 24 in AMD FX-8800P APU [29] and 32 in the Nvidia GK110 architecture [36]. This limits the parallelism it could exploit. Second, the number of signals attached to a packet is 5 [29]. To support more than 5 signals, hierarchical barrier packets have to be used which cause additional delay.

### 3.2.2 Specialized Warps

Specialized warps have been implemented with CUDA named barrier to specify dependencies among warps of a TB [11, 27]. Specifically, two assembly functions are used, bar.sync and bar.arrive, corresponding to wait and signal between a TB's warps. Both functions take two arguments, a barrier\_name and a target value (multiple of 32). Each named barrier is associated with a hardware counter in the SM. When a warp issues bar.arrive or bar.sync, the corresponding counter is incremented by 32 (each thread in the warp increment the counter by 1). Bar.sync is a blocking function while bar.arrive is non-blocking. This design has two important implications: 1) signals are not lost, which means that a signal must be called exactly when it is needed. Issuing more or fewer signals than can be matched with waits will leave the barrier unresolved or incorrectly resolved. 2) happen-before relationships between waits and signals are not necessary. In CUDA, bar.sync and bar.arrive can be issued in any order without affecting correctness as long as the number of issued bar.sync and bar.arrive match. This design is necessary for GPU SIMT execution where warps can be issued in arbitrary orders.

The fine-grained synchronization enabled by named barriers is very expressive for complex dependencies. However, named barriers are only defined within a thread block. Kernelwide synchronization can only be expressed for a kernel consisting of one TB. This leads to very low SM occupancy since one TB is dispatched to a single SM. In addition, one TB can have no more than 1024 threads which also limits parallelism. In fact, named barrier is mainly used for accelerating sub-tasks such as loading from or storing to memory. They are not meant to be used as the main synchronization mechanism for producer-consumer applications.

## 3.2.3 Case Study: RNN Acceleration Techniques

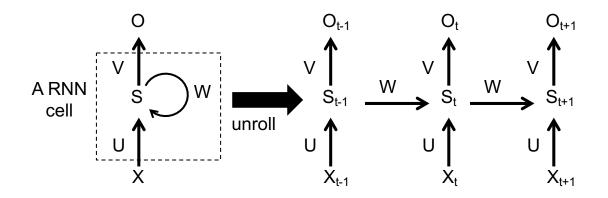

Recurrent Neural Networks (RNNs) have shown great performance in many sequential modeling tasks. Different from a traditional neural network, where all inputs and outputs are independent of each other, RNNs are used to model a sequential dependency. For example, if the task is to predict the next word in a sentence, the model must utilize information about words that appeared earlier in the sentence. RNNs are recurrent because they compute every element of a sequence based on the previous computations. Hence RNNs have a "memory" which captures information about what has been calculated so far. The building block of RNN is called a "cell", which is basically a function that takes in an input and a state, and returns an output and the next state [44]. Figure 32 shows how a single RNN cell is unfolded for each time step. The formulas that govern the computation happening in a RNN are described as follows:

Figure 10: A basic single recurrent neural network cell.

$$S_t = f(\mathbf{S_{t-1}W} + \mathbf{X_tU}) \tag{3.1}$$

$$O_t = g(\mathbf{S}_t \mathbf{V}) \tag{3.2}$$

where  $\mathbf{X}_t \in \mathbf{R}^{\mathbf{B}\times\mathbf{P}}$ ,  $\mathbf{S}_t \in \mathbf{R}^{\mathbf{B}\times\mathbf{H}}$  and  $\mathbf{O}_t \in \mathbf{R}^{\mathbf{B}\times\mathbf{K}}$  are an input matrix, a hidden state matrix and an output matrix at time step t, respectively. B, P, H, K represent batch size, number of input features, number of hidden units and number of output features, respectively.  $\mathbf{S}_t$  is the memory of the RNN which is calculated based on the previous hidden state and the input at the current step as shown in formula (3.1). The function f is usually nonlinear, such as tanh (the hyperbolic tangent function) or relu (the rectified linear unit function). The initial state,  $\mathbf{S}_{-1}$ , is typically initialized to all zeros or a random number. An important property of the RNN is the reuse of the weights over the time steps. For example, as shown in Figure 32, the weights  $\mathbf{W} \in \mathbf{R}^{\mathbf{H}\times\mathbf{H}}$ ,  $\mathbf{U} \in \mathbf{R}^{\mathbf{P}\times\mathbf{H}}$  and  $\mathbf{V} \in \mathbf{R}^{\mathbf{H}\times\mathbf{K}}$  are reused multiple times.

We use **U** and **W** to represent the weights corresponding to inputs and previous hidden states, respectively. The basic RNN has several downsides including vanishing gradients [45] and degraded performance for long sequences [46]. The most successful advancement of RNN is Long short-term memory (LSTM) networks. LSTM is designed to combat vanishing gradients through a gating mechanism [46] that is governed by the following equations:

$$i_t = \sigma(\mathbf{S_{t-1}}\mathbf{W}^{\mathbf{i}} + \mathbf{X_t}\mathbf{U}^{\mathbf{i}}) \tag{3.3}$$

$$f_t = \sigma(\mathbf{S_{t-1}W^f} + \mathbf{X_tU^f}) \tag{3.4}$$

$$o_t = \sigma(\mathbf{S_{t-1}W^o} + \mathbf{X_tU^o}) \tag{3.5}$$

$$g_t = tanh(\mathbf{S_{t-1}W^g} + \mathbf{X_tU^g}) \tag{3.6}$$

$$S_t = \mathbf{S_{t-1}} \circ \mathbf{f_t} + \mathbf{g_t} \circ \mathbf{i_t}$$

$$(3.7)$$

$$O_t = \mathbf{S}_t \circ o_t \tag{3.8}$$