# ANCHOR: ARCHITECTURE FOR SECURE NON-VOLATILE MEMORIES

by

# Shivam Swami

B. Tech., Guru Gobind Singh Indraprastha University, 2012M. Tech., Indian Institute of Technology, Kharagpur, 2014

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

# **Doctor of Philosophy**

University of Pittsburgh

2018

#### UNIVERSITY OF PITTSBURGH

#### SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Shivam Swami

It was defended on

June 12, 2018

and approved by

Kartik Mohanram, Ph.D., Associate Professor Department of Electrical and Computer Engineering

Jun Yang, Ph.D., Professor Department of Electrical and Computer Engineering

Zhi-Hong Mao, Ph.D., Professor Department of Electrical and Computer Engineering

Natasa Miskov-Zivanov, Ph.D., Assistant Professor Department of Electrical and Computer Engineering

> Rami Melhem, Ph.D., Professor Department of Computer Science

Yiran Chen, Ph.D., Associate Professor Department of Electrical and Computer Engineering, Duke University

Dissertation Director: Kartik Mohanram, Ph.D., Associate Professor Department of Electrical and Computer Engineering Copyright © by Shivam Swami 2018

#### **ANCHOR: ARCHITECTURE FOR SECURE NON-VOLATILE MEMORIES**

Shivam Swami, PhD

University of Pittsburgh, 2018

Computing systems that integrate advanced non-volatile memories (NVMs) are vulnerable to several security attacks that threaten (i) data confidentiality, (ii) data availability, and (iii) data integrity. This dissertation presents ANCHOR, which integrates 4 low overhead, high performance security solutions SECRET, COVERT, ACME, and STASH to thwart these attacks on NVM systems.

SECRET is a low cost security solution for data confidentiality in multi-/triple-level cell (i.e., MLC/TLC) NVMs. SECRET synergistically combines (i) smart encryption, which prevents reencryption of unmodified or zero-words during a write-back with (ii) XOR-based energy masking, which further optimizes NVM writes by transforming a high-energy ciphertext into a low-energy ciphertext. SECRET outperforms state-of-the-art encryption solutions, with the lowest write energy and latency, as well as the highest lifetime.

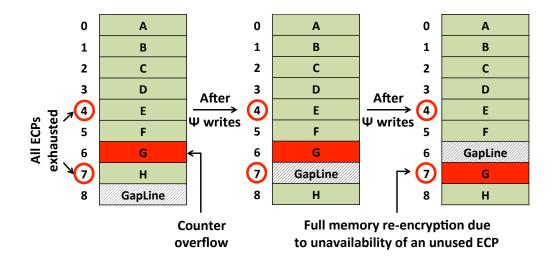

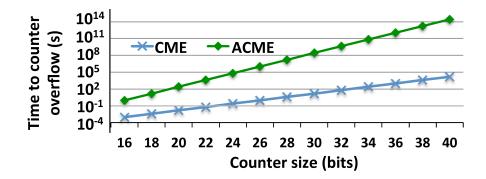

COVERT and ACME complement SECRET to improve system availability of counter mode encryption (CME). COVERT repurposes unused error correction resources to dynamically extend time to counter overflow of fast growing counters, thereby delaying frequent full memory reencryption (system freeze). ACME performs counter write leveling (CWL) to further increase time to counter overflow, and thereby delays the time to full memory re-encryption. COVERT+ACME achieves system availability of 99.999% during normal operation and 99.9% under a denial of memory service (DoMS) attack. In contrast, conventional CME achieves system availability of only 85.71% during normal operation and is rendered non-operational under a DoMS attack.

STASH is a comprehensive end-to-end security architecture for state-of-the-art smart hybrid memories (SHMs). STASH integrates (i) CME for data confidentiality, (ii) page-level Merkle Tree authentication for data integrity, (iii) recovery-compatible MT updates to withstand power/system

failures, and (iv) page-migration friendly security meta-data management. For security guarantees equivalent to state-of-the-art, STASH reduces memory overhead by  $12.7\times$ , improves system performance by 65%, and increases NVM lifetime by  $5\times$ .

This dissertation thus addresses the core security challenges of next-generation NVM systems. Directions for future research include (i) holistic architectures for both security and reliability of smart memories, (ii) applications of ANCHOR to reduce security overhead of Internet-of-Things, and (iii) secure non-volatile processors, especially in the light of advanced attacks like Spectre and Meltdown.

## TABLE OF CONTENTS

| PRI | EFA( | <b>CE</b>                               |

|-----|------|-----------------------------------------|

| 1.0 | IN   | <b>TRODUCTION</b>                       |

|     | 1.1  | Contributions                           |

|     |      | 1.1.1 SECRET                            |

|     |      | 1.1.2 COVERT                            |

|     |      | 1.1.3 ACME                              |

|     |      | 1.1.4 STASH                             |

|     | 1.2  | Future work                             |

|     | 1.3  | Dissertation organization               |

| 2.0 | BA   | <b>CKGROUND</b>                         |

|     | 2.1  | NVM basics                              |

|     |      | 2.1.1 PCM basics                        |

|     |      | 2.1.2 RRAM basics                       |

|     |      | 2.1.3 STT-RAM basics                    |

|     | 2.2  | <b>NVM</b> security                     |

|     |      | 2.2.1 Threat model                      |

|     |      | 2.2.2 Data confidentiality attacks      |

|     |      | 2.2.3 Data availability attacks         |

|     |      | 2.2.4 Data integrity attacks            |

|     |      | 2.2.5 Counter mode encryption           |

|     |      | 2.2.6 Merkle Tree authentication        |

|     |      | 2.2.7 Bonsai Merkle Tree authentication |

|     | 2.3 | Relate | ed work                          | 17 |

|-----|-----|--------|----------------------------------|----|

| 3.0 | SEC | CRET   |                                  | 19 |

|     | 3.1 | SECF   | RET: Motivation                  | 19 |

|     | 3.2 | SECF   | RET: Contributions               | 21 |

|     |     | 3.2.1  | Smart encryption                 | 21 |

|     |     | 3.2.2  | Energy masks                     | 23 |

|     |     | 3.2.3  | Flag-bit encryption              | 25 |

|     |     | 3.2.4  | SECRET: Architectural design     | 26 |

|     |     |        | 3.2.4.1 Write operation          | 26 |

|     |     |        | 3.2.4.2 Read operation           | 27 |

|     |     | 3.2.5  | Hardware overhead                | 28 |

|     | 3.3 | SECF   | RET: Evaluation and results      | 28 |

|     |     | 3.3.1  | Evaluated techniques             | 28 |

|     |     | 3.3.2  | Summary                          | 29 |

|     |     | 3.3.3  | MLC RRAM NVM                     | 30 |

|     |     |        | 3.3.3.1 Energy and latency       | 30 |

|     |     |        | 3.3.3.2 Memory lifetime          | 31 |

|     |     | 3.3.4  | TLC RRAM NVM                     | 31 |

|     |     |        | 3.3.4.1 Energy and latency       | 32 |

|     |     |        | 3.3.4.2 Memory lifetime          | 33 |

|     | 3.4 | SECF   | RET: Conclusions                 | 33 |

| 4.0 | CO  | VERT   | 2                                | 34 |

|     | 4.1 | COV    | ERT: Motivation                  | 34 |

|     | 4.2 | COVI   | ERT: Contributions               | 35 |

|     |     | 4.2.1  | COVERT: Dynamic counter (DYNAMO) | 36 |

|     |     |        | 4.2.1.1 DYNAMO design            | 36 |

|     |     | 4.2.2  | Memory operations                | 38 |

|     | 4.3 | COVI   | ERT: Evaluation and results      | 39 |

|     |     | 4.3.1  | Simulation framework             | 39 |

|     |     | 4.3.2  | Summary of results               | 40 |

|     |     | 4.3.3 Re-encryption rate                     | 40 |

|-----|-----|----------------------------------------------|----|

|     |     | 4.3.4 Lifetime improvements                  | 41 |

|     | 4.4 | COVERT: Conclusions                          | 41 |

| 5.0 | AC  | ME                                           | 43 |

|     | 5.1 | ACME: Motivation                             | 43 |

|     | 5.2 | ACME: Contributions                          | 44 |

|     |     | 5.2.1 ACME: Observation                      | 44 |

|     |     | 5.2.2 ACME: Design                           | 45 |

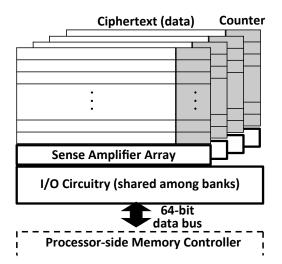

|     |     | 5.2.3 ACME: Memory organization              | 48 |

|     |     | 5.2.4 ACME: Memory operations                | 50 |

|     |     | 5.2.5 ACME: Security                         | 51 |

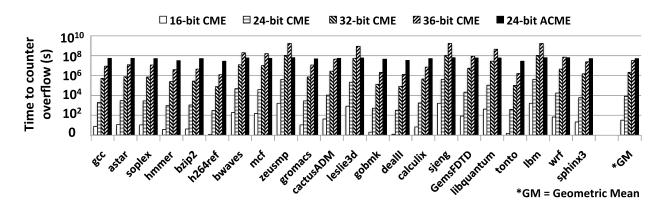

|     | 5.3 | ACME: Evaluation and results                 | 52 |

|     |     | 5.3.1 System availability                    | 53 |

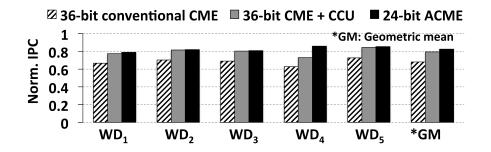

|     |     | 5.3.2 System performance                     | 54 |

|     |     | 5.3.3 Denial of memory service (DoMS) attack | 55 |

|     | 5.4 | Related work                                 | 56 |

|     | 5.5 | ACME + state-of-the-art in NVM security      | 57 |

|     | 5.6 | ACME: Conclusions                            | 57 |

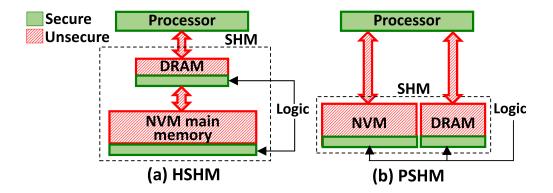

| 6.0 | STA | <b>NSH</b>                                   | 58 |

|     | 6.1 | STASH: Motivation                            | 58 |

|     | 6.2 | Smart hybrid memories (SHMs)                 | 59 |

|     | 6.3 | STASH: Threat model                          | 60 |

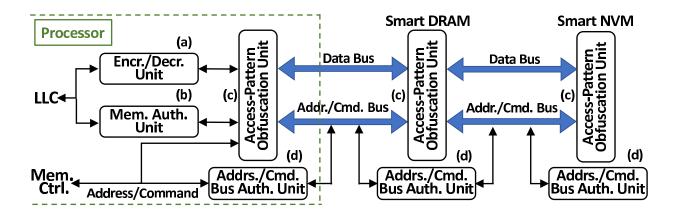

|     | 6.4 | Strawman security architecture (SSA)         | 60 |

|     |     | 6.4.1 Security primitives of SHM-SSA         | 60 |

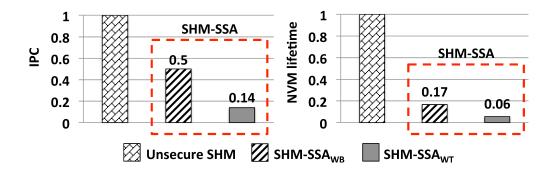

|     | 6.5 | SHM-SSA overheads                            | 62 |

|     |     | 6.5.1 Security                               | 63 |

|     |     | 6.5.2 Instant data recovery                  | 63 |

|     |     | 6.5.3 Page migration                         | 64 |

|     | 6.6 | STASH: Contributions                         | 64 |

|     |     | 6.6.1 STASH: PMT                             | 64 |

|     |           | 6.6.2 STASH: RECOUP                              | 66 |

|-----|-----------|--------------------------------------------------|----|

|     |           | 6.6.3 STASH: PACT                                | 68 |

|     |           | 6.6.4 STASH: Security                            | 69 |

|     | 6.7       | STASH: Evaluation and results                    | 69 |

|     |           | 6.7.1 Summary                                    | 71 |

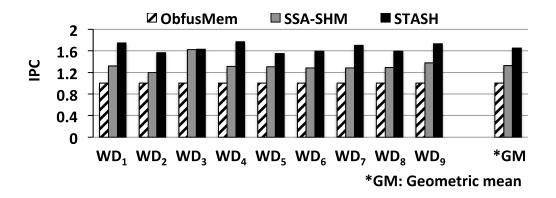

|     |           | 6.7.2 System performance                         | 72 |

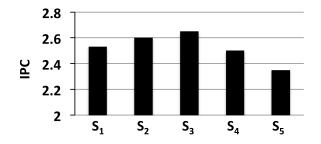

|     |           | 6.7.3 Counter cache and PMAC cache sizing        | 73 |

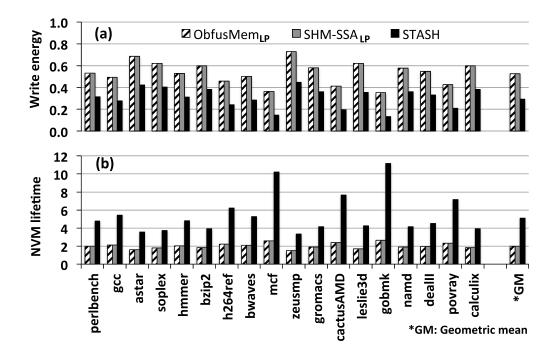

|     |           | 6.7.4 NVM write energy and lifetime              | 74 |

|     | 6.8       | STASH: Conclusions                               | 74 |

| 7.0 | <b>FU</b> | <b>ΓURE WORK</b>                                 | 76 |

|     | 7.1       | Security and reliability of smart memory systems | 76 |

|     | 7.2       | Security of Internet-of-Things                   | 77 |

|     | 7.3       | Security of non-volatile processors              | 78 |

| BIB | LIO       | GRAPHY                                           | 80 |

### LIST OF TABLES

| 1 | Write energy and latency for TLC RRAM       | 19 |

|---|---------------------------------------------|----|

| 2 | SECRET: Summary of results                  | 29 |

| 3 | COVERT: Summary of results                  | 40 |

| 4 | COVERT: Full-memory re-encryption frequency | 42 |

| 5 | ACME: Workloads                             | 53 |

| 6 | STASH: Workloads                            | 71 |

| 7 | STASH: Summary of results                   | 71 |

### LIST OF FIGURES

| 1  | PCM cell                                                    | 10 |

|----|-------------------------------------------------------------|----|

| 2  | RRAM cell                                                   | 11 |

| 3  | STT-RAM cell                                                | 12 |

| 4  | Counter mode encryption                                     | 15 |

| 5  | Impact of encryption on cell flips and write energy of NVMs | 20 |

| 6  | Smart encryption                                            | 22 |

| 7  | State transition in MLC NVM                                 | 23 |

| 8  | SECRET: Energy masking module                               | 24 |

| 9  | SECRET: Energy masking operation                            | 25 |

| 10 | SECRET: Architecture                                        | 27 |

| 11 | SECRET: MLC energy/latency comparison                       | 30 |

| 12 | SECRET: MLC lifetime comparison                             | 31 |

| 13 | SECRET: TLC energy/latency comparison                       | 32 |

| 14 | SECRET: TLC lifetime comparison                             | 33 |

| 15 | Impact of counter cache on counter mode encryption          | 35 |

| 16 | COVERT: DYNAMO design                                       | 37 |

| 17 | COVERT: Wear leveling                                       | 38 |

| 18 | ACME: Access locality                                       | 45 |

| 19 | ACME: Address translation                                   | 46 |

| 20 | ACME: Known-plaintext attack                                | 47 |

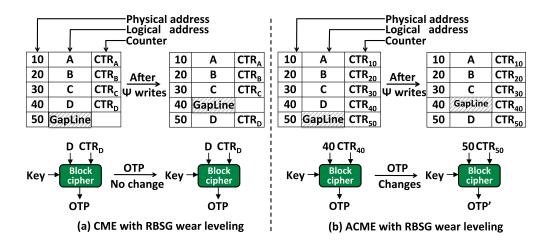

| 21 | ACME: OTP generation                                        | 48 |

| 22 | ACME: Memory organization                                   | 50 |

| 23 | ACME: Time to counter overflow                              | 53 |

|----|-------------------------------------------------------------|----|

| 24 | ACME: IPC                                                   | 55 |

| 25 | ACME: DoMS attack                                           | 55 |

| 26 | STASH: SHM architectures                                    | 59 |

| 27 | STASH: Strawman security architecture for SHM               | 61 |

| 28 | STASH: Overheads of strawman security architecture for SHM  | 62 |

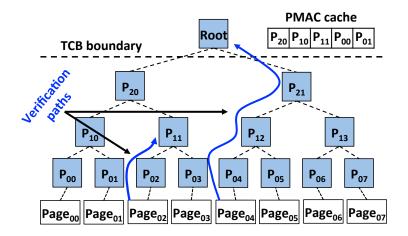

| 29 | STASH: PMT                                                  | 65 |

| 30 | STASH: PMAC caching                                         | 68 |

| 31 | STASH: IPC results                                          | 72 |

| 32 | STASH: Sensitivity analysis of counter cache vs. PMAC cache | 73 |

| 33 | STASH: NVM Energy and lifetime results                      | 75 |

#### PREFACE

Firstly, I would like to express my sincere gratitude to my Ph.D. advisor, Prof. Kartik Mohanram, for his support, patience, and motivation throughout this journey. Kartik's immense knowledge, high research standards, and professionalism have not only shaped this dissertation, but also my personality in these past 4 years. I could not have imagined having a better advisor and mentor for my Ph.D study.

I am also grateful to my Ph.D. committee – Prof. Rami Melhem, Prof. Yiran Chen, Prof. Jun Yang, Prof. Zhi-Hong Mao, and Prof. Natasa Miskov-Zivanov – for their encouragement and valuable input on my work. Without their blessings, this dissertation could not have seen the light of day. I am equally grateful to the department of Electrical and Computer Engineering at the University of Pittsburgh and all the people therein, especially Sandy Weisberg, for the help and cooperation in these past 4 years.

No thanks can do justice to the support and help extended to me by my labmate and housemate, Joydeep, who has been an integral part of this journey from day 1. I am also thankful to my senior labmate, Poovaiah, for providing highly collegial atmosphere and getting me started at Pitt. I consider myself privileged to have been a part of this research group.

Last but not the least, I acknowledge the support and encouragement of my parents, who have always motivated me to go the extra mile and achieve excellence in my pursuits. I am also thankful to my life partner, Gunjan, and my brother, Arjun, for providing me the much needed emotional support during difficult times. And to conclude, I dedicate my doctorate to my grandparents, whose love and blessings have turned this dream into reality.

#### **1.0 INTRODUCTION**

The high power consumption and poor potential for technology scaling below 22nm of DRAM [1] has spurred research in emerging resistance-class non-volatile memories (NVMs) such as phase change memory (PCM) [2,3], resistive RAM [4,5], spin-transfer torque RAM (STT-RAM) [6], and 3D X-Point [7]. These NVMs store data by modulating the resistance (PCM/RRAM/3D X-Point) and magnetoresistance (STT-RAM) of the storage material, with data persistence on power down. Due to a large separation between the lowest and the highest resistance state, PCM, RRAM, 3D X-Point, and STT-RAM also support multi-level/triple-level cell (MLC/TLC) operation, which is the ability to store 2/3 logical bits per physical cell. Whereas these NVMs offer several advantages over DRAM, computing systems that integrate these advanced NVMs are vulnerable to several security attacks that threaten (i) data confidentiality, (ii) data availability, and (iii) data integrity. Data confidentiality attacks aim to obtain secret data stored in the system [8–13]. Data availability attacks seek to make the memory system unavailable for authorized users [14, 15]. Finally, data integrity attacks refer to any adversarial corruption or tampering of data [14, 16–18].

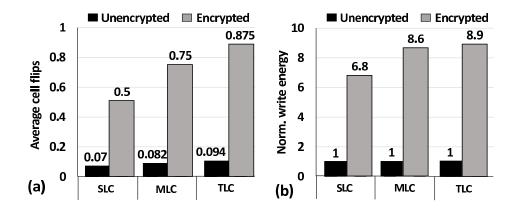

A broad class of memory encryption techniques have been proposed in the literature [8–12] to protect NVMs against data confidentiality attacks. Encryption algorithms demonstrate strong diffusion characteristics that ensure that a single bit change in the plaintext (i.e., unencrypted data) results in several bit changes in the ciphertext (i.e., encrypted data). Due to strong diffusion characteristics, the theoretical average cell flips per write for encrypted SLC/MLC/TLC NVM is 0.5/0.75/0.875. This renders cell flip reduction techniques like data comparison write (DCW, i.e., classical read-modify-write) [19] and flip-n-write (FNW) [20] ineffective in practice, increasing the write energy/latency and reducing the lifetime of NVMs.

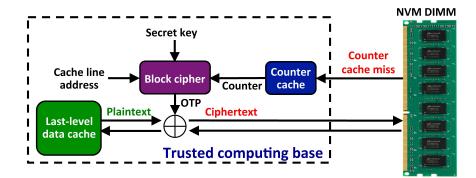

Furthermore, state-of-the-art encryption techniques [8, 11, 12] are based on the principles of counter mode encryption (CME). CME associates a counter with each cache line and uses this

counter along with the memory address of the cache line and a secret key to encrypt the cache line on a memory write. To reduce on-chip memory overhead in CME, the counters are stored in main memory and cached on-chip in a counter cache to improve performance [11,21–23]. However, CME suffers from the counter overflow problem, in which a counter overflow mandates full memory re-encryption with a new secret key, causing the system to freeze for the duration of full memory re-encryption. Counter overflow renders CME vulnerable to the denial of memory service (DoMS) attack, which threatens system availability. In a DoMS attack, a malicious application can render the memory system unavailable to other applications by forcing frequent full memory re-encryption due to counter overflow. A DoMS attack can be easily engineered using cache eviction and ordering instructions (like clflush and mfence) that can be executed in non-administrator mode to constantly write to the same cache line in main memory, forcing its counter to overflow. Whereas system availability can be improved by employing large counters, this increases the memory overhead of CME and results in poor performance due to frequent counter cache misses (for a fixed counter cache size).

Although CME ensures data confidentiality, it does not guarantee data data integrity, which refers to ability to detect any adversarial corruption or tampering of data. For data integrity, memory authentication is performed using the Merkle Tree (MT) authentication [16–18,24–27]. In MT authentication, a logical tree – obtained by recursively computing message authentication codes (MACs, i.e., keyed hash values) over memory blocks – is maintained in the main memory [16,21]. The integrity of the fetched data is verified by computing the corresponding chain of MACs up to the MT root, which is maintained on the processor-side memory controller. Due to its hierarchical structure, MT significantly increases memory overhead and memory accesses, negatively impacting performance.

In addition to these direct attacks on data confidentiality, availability, and integrity, memory systems are also vulnerable to side-channel attacks that exploit memory access patterns to obtain secret encryption/authentication keys [28–30]. Concealing the true memory access patters by employing techniques like Oblivious RAM [31] thwarts access-pattern based side-channel attacks; however, it increases memory traffic by  $10 \times$  and deteriorates performance by  $4 \times$  [28, 29, 31].

This dissertation presents ANCHOR, which integrates 4 low overhead, high performance security solutions SECRET, COVERT, ACME, and STASH to thwart these attacks on NVM systems. SECRET synergistically integrates smart encryption with energy masking to reduce write energy/latency of CME. COVERT complements SECRET to improve system availability of CMEbased secure NVMs. ACME further complements COVERT to thwart DoMS attacks on NVMs. Finally, STASH is a comprehensive end-to-end security architecture for smart hybrid memories that integrates (i) CME for data confidentiality, (ii) low overhead page-level Merkle Tree (MT) authentication for data integrity, (iii) recovery-compatible MT updates to withstand power/system failures, and (iv) page-migration-friendly security meta-data management. The rest of this introduction summarizes the core contributions of SECRET, COVERT, ACME, and STASH and also outlines directions for future research.

#### **1.1 CONTRIBUTIONS**

#### 1.1.1 SECRET

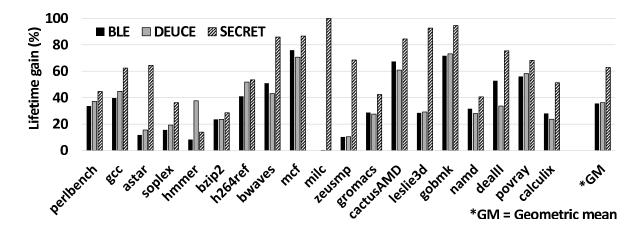

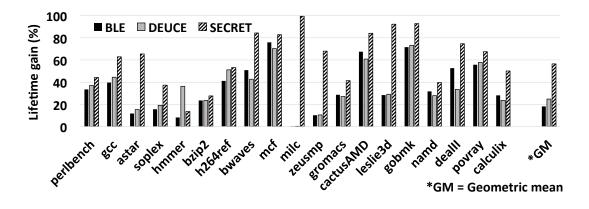

Smartly EnCRypted Energy efficienT (SECRET) NVMs synergistically integrate zero-based partial writes with XOR-based energy masking to realize low-overhead CME for MLC/TLC NVMs. Smart encryption integrates word-level re-encryption and zero-based partial writes in order to reduce memory writes. Word-level re-encryption modifies classical CME—which is used at cache line granularity—by allocating separate counters for each word, allowing data encryption at granularities smaller than a cache line. Zero-based partial writes leverages the fact that a significant fraction of the plaintext written to the memory is zero for real-life workloads [32–36]. SECRET uses a one-bit zero-flag per word to track zero-words (i.e., words with only zeros) in a cache line and maintain zero-words in their last encrypted states, saving the write overhead of re-encrypting zero-words. Following smart encryption, SECRET performs write optimization by filtering the encrypted words (i.e., the ciphertext) through *energy masks*. For an overhead of one bit (energy-flag) per word, XOR-based energy masks transform high energy states in the ciphertext into low energy states, reducing the overall write energy of the cache line. Both the zero-flag and the energy-flag are stored in encrypted state in the memory in order to ensure the security of the data. SECRET is evaluated on MLC/TLC RRAM architectures using the NVMain [37] memory simulator on memory traces from the SPEC CPU2006 benchmark suite [38]. SECRET considers advanced encryption standard-based (AES-based) CME as the baseline. SECRET is compared to state-of-the-art encryption techniques, namely BLE [11] and DEUCE [12], which perform cache line encryption at a granularity of 128 bits and 16 bits, respectively. Simulations on MLC RRAM show that BLE, DEUCE, and SECRET reduce write energy (latency) by 40% (23%), 40% (17%), and 80% (37%) over the baseline. The lifetime evaluations show that BLE, DEUCE, and SECRET reduce write energy (latency) by 33% (31%), 40% (23%), and 63% (49%), respectively, over the baseline. The lifetime improvements for TLC RRAM from BLE, DEUCE, and SECRET are 18%, 24%, and 56%, respectively, over the baseline.

Thus, by integrating smart encryption with energy masking, SECRET reduces CME overheads for MLC/TLC NVMs. SECRET outperforms BLE and DEUCE, with the lowest write energy/latency, as well as the highest lifetime.

#### **1.1.2 COVERT**

*Counter OVErflow ReducTion (COVERT)* is an encryption solution that addresses the counter overflow problem in CME by performing on-demand memory allocation to the fast-growing counters, while also retaining the area/performance benefits of small counters. ANCHOR integrates COVERT with SECRET to provide a holistic platform to improve the system availability, performance, lifetime, and reduce the write energy/latency of CME-based secure NVMs. At its core, COVERT employs dynamic counters (DYNAMO henceforth) to reduce frequent full memory re-encryption due to small-sized counters. DYNAMO leverages the fact that a significant fraction of memory provisioned for error correction remains unutilized till very late in memory lifetime [39, 40]. DYNAMO repurposes unused error correction memory cells to the overflowing counters, thereby delaying the mandatory full memory re-encryption on a counter overflow and improving system availability. COVERT is a drop-in replacement for classical CME, and does not compromise the security of the underlying CME (i.e., COVERT preserves CME requirements of (i) encryption inside a secure processor and (ii) spatial/temporal exclusivity of the OTP). COVERT is evaluated on a phase change random access memory (PCRAM) architecture [41] using the MARSS full-system simulator [42] on both integer and floating-point workloads from the SPEC CPU2006 benchmark suite [38]. COVERT employs 16-bit CME as the underlying encryption technique. The results show that for equivalent overhead and no impact to performance, COVERT improves system availability from 85.71% (of classical 16-bit CME [8]) to 99.3%. Thus, COVERT provides an effective solution to address the counter overflow problem in CME without compromising its security.

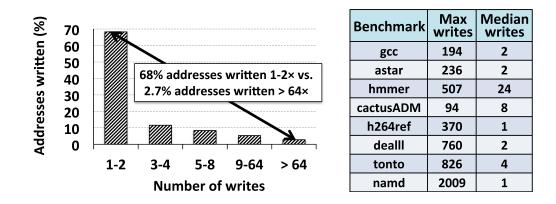

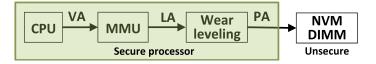

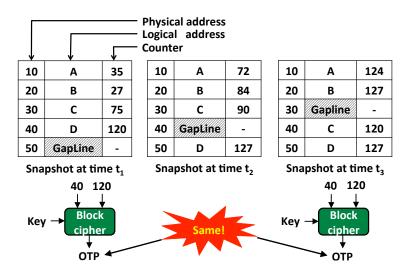

#### 1.1.3 ACME

Advanced Counter Mode Encryption, i.e., ACME, complements COVERT to realize low overhead, high performance NVM security solution that is robust to both data confidentiality and system availability attacks. At its core, ACME leverages the underlying wear leveling architecture employed to improve NVM endurance [2,43,44]—to perform counter write leveling (CWL). CWL associates counters with physical addresses (PAs) instead of logical addresses (LAs) such that when a frequently written cache line is translated from one PA to another PA for wear leveling, its associated counter is also remapped, leading to a distribution of writes across counters. Multiple counters together track the number of writes seen by a frequently written cache line, thereby delaying counter overflow; delaying counter overflow improves system availability due to delayed full memory re-encryption. ACME incurs no logic overhead, since it enables CWL by leveraging the existing wear leveling architecture that is integrated with the secure processor. ACME is a drop-in replacement for CME, and does not compromise the security of the underlying CME, i.e., ACME preserves CME requirements of (i) encryption inside a secure processor and (ii) spatial as well as temporal exclusivity of the OTP.

ACME is evaluated on a PCRAM architecture using (i) a trace-driven memory simulator that integrates the Intel Pin [45] binary instrumentation tool and (ii) the MARSS [42] full-system simulator on SPEC CPU2006 benchmarks [38]. Results show that for the system availability of 99.999%, ACME not only requires 50% lower counter memory overhead, but also improves system performance by 20% in comparison to classical CME. Further, When subject to a DoMS attack in the form of an unprivileged Linux process that sidesteps all levels of cache to constantly write to

the same memory address to precipitate counter overflow, the ACME-based system provides 99.9% system availability in contrast to a classical CME-based system that is rendered non-operational. Finally, upon integration with COVERT, ACME improves COVERTs system availability from 99.3% to 99.999% for no overhead.

#### 1.1.4 STASH

Smart hybrid memories (SHMs) that integrate NVM, DRAM, and processor logic can provide high bandwidth, low memory latency, and high memory density to meet the needs of future high-performance computing systems. However, the unsecure DRAM, NVM, and/or memory buses in SHMs are vulnerable to data confidentiality attacks (e.g., memory scanning and bus snoop-ing) [10, 12, 14, 26], data integrity attacks (spoofing/splicing/replay attacks) [17, 27–29], and side-channel attacks (e.g., access-pattern based attacks) [28,29] that must be addressed prior to commercialization. *SecuriTy Architecture for Smart Hybrid memories (STASH)* is the first comprehensive end-to-end security solution that makes the following three core contributions.

Low-cost page-level MT authentication (PMT) that replaces classical cache-line-level authentication to secure the SHM from data integrity attacks. PMT leverages page granularity data migration between DRAM and NVM to reduce Merkle Tree (MT) authentication overheads for thwarting data tampering attacks. Bonsai MT (BMT) [17] framework is the norm for memory authentication that is adopted by all state-of-the-art memory security techniques [26,27,29]. BMT requires a 128bit data message authentication code (DMAC) per 512-bit cache line along with an MT constructed over encryption counters (counters henceforth). In contrast, PMT maintains a 128-bit MAC per 4kB page and constructs an MT by recursively hashing these page-level MACs (PMACs), providing equivalent security guarantees for significantly lower memory and performance overheads.

Recovery-compatible MT updates (RECOUP) is an IDR solution that performs selective metadata (counters, MT root, etc.) updates to tolerate power/system failures in SHMs. To improve performance, it is common practice to employ an on-chip write-back counter cache to delay security meta-data updates in memory [17, 26]. This renders the meta-data residing in the SHM partially stale and unsynchronized with the ciphertext. As a result, the SHM cannot reliably decrypt and/or authenticate the ciphertext in the event of a power/system failure. Extending BMT [17] to support IDR in SHMs significantly increases NVM writes, since every cache line write also requires multiple consistent MT updates. RECOUP leverages a key observation that IDR can be supported by consistently updating only (a) the MT root in the trusted computing base (TCB) of the smart DRAM and (b) the modified MT leaf (i.e., data/counter) in the smart NVM, thereby eliminating unnecessary MT re-computations and reducing high overhead NVM writes.

Page-migration-friendly security meta-data management (PACT) supports low overhead page migration is SHMs. Since state-of-the-art security solutions [16, 17, 26, 28, 29] are designed to operate at only cache-line granularity, the meta-data overhead (>1kB per 4kB page) of these solutions on page migration from smart NVM to smart DRAM increases memory traffic and reduces effective DRAM capacity. PACT addresses this problem by (i) transferring only the required PMT meta-data (16 bytes per 4kB page) to DRAM and (ii) caching the PMT meta-data of the migrated page in a PMAC cache on the logic layer of the smart DRAM. By eliminating bulk meta-data migration to DRAM, PACT reduces memory traffic and improves DRAM utilization in SHMs.

STASH is evaluated on an SHM that integrates a 2GB HMC [46] as the DRAM cache and a 32GB smart triple-level cell (TLC) PCM [47] as the main memory. NVMain memory simulator [37] and the MARSS [42] full system simulator are used for trace-based and system-level evaluations of STASH, respectively. STASH is compared to (i) state-of-the-art ObfusMem [29] and (ii) a strawman security architecture for SHMs (SSA-SHM henceforth). Results show that in comparison to ObfusMem (SSA-SHM), STASH reduces memory overhead by  $12.7 \times (12.7 \times)$ , improves system performance by 65% (25%), and increases NVM lifetime by  $5 \times (5 \times)$ .

Hence, for security guarantees equivalent to state-of-the-art, STASH achievies the best system performance, the highest NVM lifetime and the lowest memory overhead.

#### **1.2 FUTURE WORK**

Directions for future research include (i) exploration of holistic architectures that ensure both security and reliability of smart memory systems, as well as extending ANCHOR to further reduce the overheads of instant data recovery in smart NVMs. (ii) Investigating applications of ANCHOR to reduce security overhead of Internet-of-Things (IoT). IoT security involves secure data acquisition by the front-end devices, secure data forwarding on the network, and secure data processing in the back-end cloud. (iii) Extending ANCHOR to safeguard emerging non-volatile processors (NV-processors), especially in the light of advanced attacks like Spectre and Meltdown, which can be launched from the user space without invoking any administrative privileges.

#### **1.3 DISSERTATION ORGANIZATION**

The rest of this dissertation is organized as follows. Chapter 2 covers basic concepts of NVMs, describes various security vulnerabilities of NVM-based systems, and presents related work in NVM security. Chapter 3 describes the theory and architecture of SECRET, along with evaluation and results. Chapter 4 describes the theory and architecture of COVERT, along with evaluation and results. Chapter 5 describes the theory and architecture of ACME, along with evaluation and results. Chapter 6 describes theory and architecture of STASH, along with evaluation and results. Finally, Chapter 7 presents directions for future research.

#### 2.0 BACKGROUND

This chapter is divided into two sections. The first section covers background material related to emerging NVMs to motivate NVM integration in modern computing systems. The second section discusses various security challenges that must be addressed prior to commercialization of these advanced memory technologies.

#### 2.1 NVM BASICS

#### 2.1.1 PCM basics

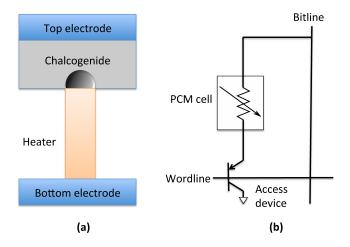

A PCM storage element consists of a resistive heater and a phase change material (chalcogenide) placed between two metal electrodes (refer figure 1 (a)). A PCM cell is a one resistor, one transistor device comprising of a PCM storage element and an access transistor (refer figure 1 (b)). PCM stores data by altering the resistance of its phase change material (e.g.,  $Ge_2Sb_2Te_5$  (GST)) between the fully amorphous state with high resistance (reset state) and the fully crystalline state with low resistance (set state) [2, 48]. To reset a PCM cell, a high amplitude reset pulse is applied to melt the GST and then abruptly cutoff to quench the molten GST into the amorphous state. To set a PCM cell, a small amplitude set pulse heats the GST above its crystallization temperature for a sufficiently long duration to transform the GST into the crystalline state. The information stored in a PCM cell is read by measuring the resistance of the cell.

#### 2.1.2 RRAM basics

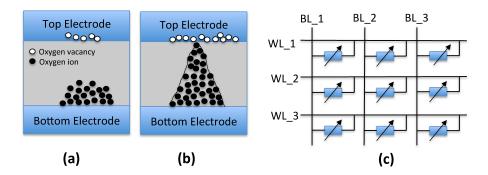

An RRAM cell consists of a transition metal oxide (TMO) that acts as an insulator, sandwiched between two metal electrodes, forming a Metal-Insulator-Metal (MIM) structure. Information is stored by switching the resistance of the TMO between the high resistance state (HRS, logic '0')

Figure 1: (a) Physical structure of PCM (b) 1-bit PCM cell with a storage element and an access transistor [2]

and the low resistance state (LRS, logic '1'). Applying an external voltage of specified polarity, magnitude, and duration results into the formation/destruction of one or more conductive filaments (CF) made out of oxygen vacancies [4, 5, 49]. Formation of the CFs establishes a conductive path between the top and the bottom electrode, bringing the cell into the LRS. In contrast, destruction of the CFs removes the conductive path, bringing the cell into the HRS (refer figure 2(a) and (b)). Based on the switching behavior, RRAM can be classified into two categories: bipolar and unipolar RRAM. For a unipolar RRAM cell, the magnitude and the duration of the external voltage applied across the cell alone controls the RRAM resistance switching. In contrast, for a bipolar RRAM cell, LRS to HRS switching (i.e., reset operation) and HRS to LRS switching (i.e., set operation) occur at different voltage polarities.

Two types of memory structures have been proposed in the literature for RRAM array: conventional MOSFET-accessed structure and crosspoint structure. Due to the large size of a MOS-FET access device in comparison to an RRAM cell, the conventional MOSFET-accessed structure ceases the RRAM's area advantage. Therefore, architects prefer the area-efficient crosspoint RRAM array [4, 44]. In the crosspoint structure, each RRAM cell is sandwiched between a top electrode and a bottom electrode at each crosspoint of the array without an access device. In this structure, each cell only occupies an area of  $4F^2$  (F is the feature size in fabrication technology), which is in theory the smallest cell area for a single-layer memory structure.

Figure 2: Physical structure of an RRAM cell in (a) high resistance state (HRS) (b) low resistance state (LRS). (c) Schematic view of crosspoint RRAM array (WL = wordline, BL = bitline) [49]

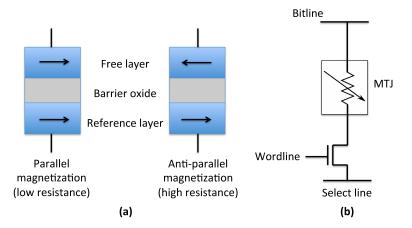

#### 2.1.3 STT-RAM basics

An STT-RAM cell comprises of a magnetic tunnel junction (MTJ) connected in series with an access transistor. MTJ is basically an oxide layer sandwiched between two ferromagnetic layers [6, 50,51]. As shown in figure 3(a), the magnetic orientation of one of the ferromagnetic layers is fixed (*reference layer (RL)*), while the magnetic orientation of the other layer (*free layer (FL)*) is changed by applying an external field. Parallel magnetization of FL and RL results in a low resistance state of the MTJ and corresponds to logic '0'. In contrast, anti-parallel magnetization of FL and RL results in a high resistance state of the MTJ and corresponds to logic '1'. Figure 3(b) shows an STT-RAM bit cell. There are two approaches of reading an STT-RAM bit cell (i) parallel reading and (ii) anti-parallel reading. In parallel reading, select line (SL) is grounded and a small bias is applied to the bit line (BL). In anti-parallel reading, the voltage polarity of SL and BL are opposite and the current flows in reverse direction from SL to BL.

#### 2.2 NVM SECURITY

This section covers the NVM threat model, the role of memory encryption and authentication in NVM security, and also discusses state-of-the-art NVM security solutions.

Figure 3: (a) STT-RAM storing device (MTJ) (b) Structure of an STT-RAM cell with a storage element and an access transistor [6, 50]

#### 2.2.1 Threat model

The security of modern computing systems is based on the three cornerstone properties of confidentiality, availability, and integrity [14]. Since it is neither practically feasible, nor desirable, to design a system that can guarantee complete protection from all possible attacks to these security requirements, systems are designed only for a subset of attacks, with certain security assumptions to eliminate the possibility of other attacks that are not a part of the threat model [14, 21]. As in prior studies on memory security, the trusted computing base (TCB) consists of the processor and core parts of the operating system (e.g., security kernels); external memory and peripherals are assumed to be untrusted [8,9,11,12]. This threat model is extended to include on-module processing logic on smart hybrid memories (discussed in detail in section 6.3).

#### 2.2.2 Data confidentiality attacks

Past research [8–12] on NVM security has recognized the stolen DIMM and bus snooping attacks as the two most common security attacks to data confidentiality in NVMs. Unlike DRAM, where only specialized cold boot attacks [52] can potentially retrieve data after power down, data retrieval from powered-down NVMs is much easier due to data persistence. In the stolen DIMM attack, the attacker has physical access to the NVM DIMM, enabling them to stream data from the DIMM.

Data persistence of NVMs exposes data in the plaintext to attackers on power down. A similar problem has been addressed in disk storage through encryption, motivating encryption of NVMs. In the bus snooping attack, the attacker can acquire data by monitoring unsecured off-chip communications. Again, it is widely accepted that such attacks can be thwarted by implementing data encryption in the secure processor.

Data encryption for NVMs is generally achieved by applying a block cipher (e.g., AES) to the plaintext to transform it into the ciphertext using a secret key. However, direct encryption of data is vulnerable to dictionary-based attacks where an attacker can compare encrypted data to figure out which lines store the same content. Hence, recent research [12,21,22,26,53] advocates the use of counter mode encryption (CME) as a secure memory encryption technique that is robust against dictionary-based attacks.

#### 2.2.3 Data availability attacks

With the advent of row-hammer-like attacks [54–56], NVM-based main memories have also become vulnerable to denial of memory service (DoMS) attacks that threaten system availability. In a DoMS attack, a malicious application can render the memory system unavailable to other applications by forcing frequent full memory re-encryption due to counter overflow (a well-known limitation of CME [16, 17]). DoMS attacks can be easily engineered using cache eviction and ordering instructions (like clflush and mfence) that can be executed in non-administrator mode to constantly write to the same cache line in main memory, forcing its counter to overflow. Splitcounter mode encryption (split-CME) [16] protects DRAM-based main memories against DoMS attacks; however, directly extending split-CME to NVM-based main memories undermines the ability of NVMs to ensure data recovery in the face of power/system failures. Past work, e.g., MECU [8] and i-NVMM [10], has motivated that preserving the data recovery property of NVMs is an important design goal for any NVM security solution.

#### 2.2.4 Data integrity attacks

Data integrity attacks (spoofing/splicing/replay) refer to the tampering of data in order to compromise the security of the computing system on which the data is stored [11, 14, 16, 18, 21, 21, 26]. **Spoofing attacks:** Arbitrary data tampering by adversary constitute spoofing attacks. These attacks can potentially disrupt the normal system operation or reveal confidential information stored in the system.

**Splicing or relocation attacks:** Unauthorized copying (also swapping) of data from one memory address to another constitute splicing attacks. Such an attack may be viewed as a spatial permutation of memory blocks.

**Replay attacks:** Replacing a memory block's data with a valid older value constitute replay attacks. A memory block located at a given address is recorded and inserted at the same address at a later point in time. Such an attack may be viewed as a temporal permutation of a memory block, for a specific memory location.

#### 2.2.5 Counter mode encryption

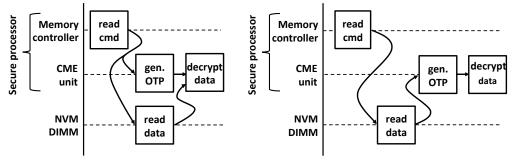

In counter mode encryption (CME), a block cipher is used to encrypt a seed with a secret key (stored on the processor) to produce a one-time pad (OTP). This OTP is bitwise XORed with the plaintext to generate the ciphertext. During decryption, the same OTP is XORed with the ciphertext to obtain the plaintext. The spatial and temporal exclusivity of the OTP is critical for the security of CME and requires that (i) the OTPs should be unique for different cache lines and (ii) the OTPs for a particular cache line should be unique for every write. These unique OTPs are generated from unique seeds that have two components: (i) the cache line address (to ensure spatial exclusivity) and (ii) a counter, which is incremented on each write (to ensure temporal exclusivity).

To reduce on-chip memory overhead in CME, the counters are stored in main memory and cached in an on-chip counter cache to improve performance [12, 22, 26]. Figure 4 shows CME in the presence of a counter cache. To increase the counter cache hit rate, small counters are preferred in practice, since a fixed size counter cache can store more counters if each counter is small. However, small counters can quickly overflow in the presence of high memory write traffic. Conventionally, a counter overflow is handled by changing the secret key to prevent reuse of OTPs [16]. However, since the same secret key is shared by every cache line, a change of secret key requires the entire memory to be re-encrypted, causing the system to freeze for the duration of full memory re-encryption. Whereas large counters can be employed to delay counter

Figure 4: This figure depicts counter mode encryption, which uses a counter, line address, and secret key to generate a one-time pad (OTP). During encryption (decryption), the OTP is XORed with the plaintext (ciphertext) to generate the ciphertext (plaintext).

overflow, large counters increase the memory overhead of CME and result in poor performance due to frequent counter cache misses. Thus, CME imposes heavy overheads on memory, performance, and availability in practice.

To address CME overheads, the authors in [16] proposed split-counter mode encryption (split-CME). Split-CME is a 2-level counter based encryption that employs a 7-bit minor counter per 512-bit cache line and a 64-bit major counter per 4kB page (i.e., net memory overhead is 1.56% per cache line). For OTP generation, both major and minor counters are concatenated. A minor counter is incremented on every write to its cache line and a minor counter overflow is handled by: (i) resetting all the minor counters in a 4kB page to 0 (ii) increasing the pages major counter by 1 and (iii) re-encrypting the entire 4kB page using the new counter values. Whereas split-CME improves system availability by reducing the cost of a counter overflow from full memory re-encryption to a 4kB page re-encryption, it requires special support from the operating system to prevent OTP reuse for cache lines with the same virtual address (if the virtual address is used for OTP generation); if the physical address is used for OTP generation, split-CME needs bookkeeping for reliable decryption of the pages that are moved between main memory and the disk.

To eliminate the dependence of the OTP on the cache line memory address, the authors in [17] proposed address-independent seed encryption (AISE). AISE repurposes split- CME's 64-bit major counter per page to a logical page identifier (LPID) that is unique for every page. While generating the OTP for a cache line, AISE uses the LPID and the cache line page offset within a page as

the memory address. On a minor counter overflow, similar to split-CME, AISE re-encrypts the corresponding page by assigning it a new LPID and resetting all the minor counters. Thus, AISE retains the performance and availability benefits of split-CME for no hardware/software overhead to support cache line memory address (physical/virtual).

#### 2.2.6 Merkle Tree authentication

Merkle Tree (MT) authentication is the most widely used scheme for main memory authentication [14, 16, 17, 26]. In MT authentication, a message authentication code (MAC) generated by a cryptographic hash function (e.g., NIST-approved SHA-1/2/3) using a secret key is computed for each cache line and stored along with the cache line in the main memory. For protection against spoofing (arbitrary data tampering) and splicing (replacing a cache line with another cache line) attacks, MAC generation includes the cache line data and memory address, respectively. On every read, the MAC is computed for the fetched data and compared with the stored MAC value. If the stored MAC is equal to the recomputed MAC, fetched data integrity is established; else, tampering is detected and the system raises an exception.

Although single-level MACs are robust against spoofing and splicing attacks, they are ineffective against replay attacks wherein an adversary replaces the data and counter with their older values. To protect memory from replay attacks, MT maintains a hierarchical tree structure of MACs, with the data and counter as its leaf nodes. The root of this tree is stored on the secure processor. A cache line write/read propagates MAC update/verification up the tree to the root. Since the on-chip MAC root is the cryptographic signature of the entire memory, a replay attack by an adversary is always detected.

#### 2.2.7 Bonsai Merkle Tree authentication

Due to its hierarchical structure, MT significantly increases memory overhead and memory accesses, negatively impacting performance. To reduce memory and performance overheads of MT, the authors in [17] proposed Bonsai Merkle Tree (BMT). In BMT authentication, an MT is maintained only for counters instead of both data (cache lines) and counters; a cache line is protected by only a single-level MAC, which is computed using the ciphertext (i.e., cache line data), cache

line memory address, and its counter value. BMT significantly reduces memory/performance overhead of MT authentication without compromising security. As in CME (which caches counters in the on-chip counter cache), the BMT nodes (i.e., counter hashes) are also cached in the on-chip counter cache to further improve system performance [17, 26, 57].

#### 2.3 RELATED WORK

Initial proposals to protect data confidentiality, e.g., execute-only memory (XOM) [58] used direct encryption that incurred high encryption/decryption latency. Early tamper-evident systems like AEGIS [59] incurred high authentication overhead due the use of hash trees. To reduce the performance overhead of memory encryption/decryption, the authors in [21,22] proposed OTP-based CME, which removes the encryption/decryption process from the critical path of LLC miss handling (as explained in section 2.2.5). The authors in [53] proposed a counter prediction and OTP pre-computation mechanism to improve CME performance without employing a counter cache. The performance and availability of CME were further improved by state-of-the-art split-CME [16] and AISE [17] by using a 2-level counter design (explained in detail in section 2.2.5).

Memory authentication architectures have evolved from performance-intensive and memoryintensive integrity trees like Merkle Tree [24, 25], Parallelizable Authentication Tree (PAT) [60], and Tamper-Evident Counter tree (TEC-Tree) [61] to state-of-the-art Bonsai Merkle Tree [17], which significantly reduces memory/performance overhead of authentication. Furthermore, to remove the integrity verification process from the critical path of LLC miss handling, PoisonIvy [57] proposes safe speculative execution while performing integrity verification in the background.

In addition, several NVM-centric encryption solutions, e.g., incremental NVMM encryption (i-NVMM) [10], block-level encryption (BLE) [11], and dual-counter encryption (DEUCE) [12] have been proposed to account for high write energy and latency, and low endurance of NVMs. Techniques like i-NVMM perform memory-side (i.e., encryption unit is placed in memory) incremental encryption by keeping only the frequently accessed memory pages in unencrypted form in the memory and securing rest of the memory in encrypted form. However, these techniques suffer from security vulnerabilities due to partial memory encryption and unencrypted off-chip communi-

cations. Processor-side encryption techniques like BLE [11] and DEUCE [12] have been proposed to address the security vulnerabilities of i-NVMM by placing the encryption unit in the secure processor. Additionally, in order to reduce the encryption penalty (i.e., high write energy/latency and cell flip rate), these techniques encrypt only the modified words in a cache line and allow the unmodified words to remain in their last encrypted state (word-level read-modify-write). Whereas state-of-the-art security solutions have focused on reducing the encryption penalty (increased write energy/latency and reduced memory lifetime) in single-level cell (SLC) NVMs, the realization of low encryption penalty solutions for multi-/triple-level cell (MLC/TLC) secure NVMs as well as protecting NVMs against data availability and side-channel attacks remain areas of active research and development.

# 3.0 SECRET: SMARTLY ENCRYPTED ENERGY EFFICIENT NON-VOLATILE MEMORIES

#### 3.1 SECRET: MOTIVATION

Encryption algorithms demonstrate strong diffusion characteristics that ensure that a single bit change in the plaintext results in several bit changes in the ciphertext. Due to strong diffusion characteristics, encryption renders cell-level write reduction techniques like FNW [20] and cell-level DCW [19] ineffective in practice, increasing the average cell flips per write operation. As shown in figure 5(a), average cell flips per write in encrypted SLC NVM is 0.5, and it increases to 0.75 (0.875) in encrypted MLC (TLC) NVM. High average cell flips per write results in increased write energy/latency and reduced memory lifetime.

Furthermore, writing to an MLC/TLC requires configuring the cell into a target resistance range by using state-of-the-art program-and-verify (P&V) [5, 36, 62, 63]. Typically, P&V requires several iterations of read-verify-write to bring an MLC/TLC to the desired state. The main draw-back of P&V is that programming an MLC/TLC to intermediate states consumes more write energy and latency in comparison to programming it to the terminal states. Table 1 shows that the energy/latency required to configure an RRAM TLC to states 3 and 4 are  $10 \times$  in comparison to the terminal states.

Table 1: Latency/energy for TLC RRAM program-and-verify [5, 63]

| State        | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

|--------------|------|------|------|------|------|------|------|------|

| Latency (ns) | 15.2 | 46.8 | 98.3 | 143  | 150  | 101  | 52.7 | 12.1 |

| Energy (pJ)  | 2.0  | 6.7  | 19.3 | 35.1 | 35.6 | 19.6 | 6.1  | 1.5  |

Figure 5(b) illustrates the impact of encryption on write energy of MLC/TLC RRAM NVMs. Simulations on SPEC CPU2006 benchmarks demonstrate that on average, write energy of encrypted MLC (TLC) NVMs is  $8.6 \times (8.9 \times)$  in comparison to unencrypted MLC (TLC) NVMs.

In summary, memory encryption is indispensable to protect NVMs against security vulnerabilities, but it comes at the cost of increased energy/latency and reduced lifetime.

Figure 5: This figure reports (a) verage cell flips per write and (b) geometric mean of write energy (normalized to unencrypted memory) for SPEC CPU2006 benchmarks for SLC/MLC/TLC RRAM. Average cell flips per write for encrypted SLC/MLC/TLC NVMs is 0.5/0.75/0.875. High average cell flips increase write energy/latency and reduce lifetime of NVMs. In comparison to unencrypted SLC/MLC/TLC NVM, energy of encrypted SLC/MLC/TLC NVM is  $6 \times / 8.6 \times / 8.9 \times$ .

#### **3.2 SECRET: CONTRIBUTIONS**

This section describes SECRET, a low hardware, low memory overhead scheme which significantly reduces the cell flips, decreases the write energy/latency, and improves the lifetime of MLC/ TLC NVMs without compromising its security.

#### 3.2.1 Smart encryption

Without exception, counter mode encryption ensures data security during the write-back of a cache line to main memory by re-encrypting all the words in a cache line with a new OTP. However, this introduces a high encryption penalty of increased cell flips leading to increased write energy/latency and reduced lifetime of NVM. SECRET proposes smart encryption to reduce the encryption penalty of counter mode encryption as follows:

- Whereas classical counter mode encryption uses a single counter for an entire cache line, SE-CRET allocates separate counters for each word, allowing word-level re-encryption at granularities smaller than a cache line.

- Zero-based partial encryption, where zero-words (i.e., words with only zeros) are maintained in their last encrypted states, saving the write overhead of re-encrypting zero-words.

During the write-back operation of a cache line, the majority of the words remain unmodified [11, 12]. Smart encryption preserves these words in their previous encrypted states, without compromising the security of the data. This is referred to as word-level data comparison write (DCW) in this work. SECRET performs word-level DCW to prevent undesired cell flips by blocking the re-encryption of the unmodified words. To perform word-level DCW, SECRET allocates a separate local counter to each word in a cache line, which is updated only when that particular word is modified during a write-back. SECRET also maintains a global counter for the entire cache line. During a write-back, each modified word is re-encrypted with an OTP, which is generated using a counter value obtained from the concatenation of the global counter and the updated local counter for that word, whereas the unmodified words are left unchanged.

The local counter (LC) associated with any word overflows when the corresponding word observes higher number of writes than what the local counter can handle ( $LC_{max}$ ). For e.g., a 2-bit

local counter can handle at most  $(2^2=)$  4 writes of the corresponding word before it overflows. Whenever a local counter in a cache line overflows, it compromises security because of the padreuse. To avert this situation and preserve the security in the event of a local counter overflow, smart encryption takes the following measure: all the local counters are reset to 0, the global counter is incremented by 1, and the entire cache line is re-encrypted using the new global and local counters. Thus, smart encryption prevents the re-encryption of unchanged non-zero-words without compromising the security of the data in memory.

To further reduce the encryption penalty of increased cell flips, SECRET leverages the fact that a significant fraction ( $\approx 60\%$  of the bytes) of the plaintext written to the memory is zero [33], and prevent the re-encryption of this zero data. SECRET provisions a single flag-bit for each word in a cache line, which records the status (i.e., zero/non-zero) of the word. SECRET sets the zero-flag of a word to 1 whenever a zero is written to it and leaves the word in its previous encrypted state in main memory during write-back. Note that zero-flags are written to the memory in encrypted state, which prevents an attacker from learning if the word written was zero (discussed in depth in Sec. 3.2.2). Since a majority of data during a write-back is zero, preventing zero-word re-encryption further assists in reducing cell flips due to encryption.

| Zero-         Local           flags         Counters           0         0         1         3         2         P | Old<br>Plaintext | Word 1           1         0         0         0         0         1         1 | Word 2<br>1 1 1 1 0 0 1 0   | Word 3               |

|--------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------|-----------------------------|----------------------|

| 0000132 Ci                                                                                                         | Old<br>phertext  | 0 1 1 0 1 0 0 1                                                                | 0 1 1 0 1 0 0               | 0 0 1 1 0 1 1 0      |

| Zero-flag Set Updated Cou                                                                                          | nter             |                                                                                | Unmodified Word             | Zero-word            |

|                                                                                                                    | New              |                                                                                |                             |                      |

| 0 0 1 2 3 2 P                                                                                                      | laintext         | 0 0 0 0 1 1 0 1                                                                | 1 1 1 1 0 0 1 0             | 0 0 0 0 0 0 0 0      |

| Unchanged Count                                                                                                    | ers              |                                                                                | <b>Unchanged Ciphertext</b> | Unchanged Ciphertext |

| 001232 Ci                                                                                                          | New<br>phertext  | 0 0 1 1 1 1 1 0                                                                | 0 1 1 0 1 0 0 0             | 0 0 1 1 0 1 1 0      |

Figure 6: Smart encryption, which prevents the re-encryption of unmodified words (word 2) and zero-words (word 3). Each word is allocated a local counter that facilitates smart encryption, and is updated only when the word is modified. The zero-flags track zero-words in a cache line; zero-flag = 1 for word 3 in the figure.

Figure 6 illustrates smart encryption. Without loss of generality, SECRET assumes a 24-bit cache line, with a word size of 8 bits and a local counter size of 2 bits. The first two lines show the previous plaintext, and the corresponding ciphertext that was written-back to main memory. The initial states of the local counters for words 1–3 (left to right) are 1, 3, and 2 respectively. The zero-flags of all the words are set to 0 initially. When the new data (plaintext) arrives, it is observed that word 2 has the same data, whereas word 3 has all zeros. Hence, the words are left in their respective previous encrypted state (unchanged ciphertext) in the main memory. The local counter for words 2 and 3 are unchanged and the zero-flag for word 3 is set to 1. Only word 1 is modified to a new non-zero value; hence its local counter is updated, and the new ciphertext corresponding to the updated counter is written to main memory. Thus, smart encryption successfully prevents re-encryption of unmodified/zero-words, thereby reducing cell flips and resulting in lower write energy/latency as well as improved lifetime.

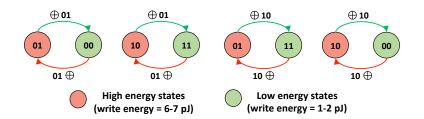

Figure 7: Transition from high to low and low to high energy states using XOR operation. Energy values are from [5,63].

#### 3.2.2 Energy masks

In order to ensure the security of the ciphertext, encryption algorithms introduce a high degree of confusion in the ciphertext [64]. Confusion refers to making the relationship between the secret key and the ciphertext as complex and as involved as possible. Thus, instead of long runs of zeros or ones (which are often seen in the plaintext), a large number of 01/10 pairs is seen in the ciphertext. Since programming an MLC into 01/10 states consumes  $3-4\times$  more energy in comparison to 00/11 states [5, 63], writing the ciphertext to memory is highly energy intensive in practice.

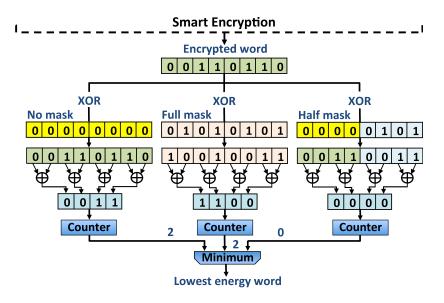

Whereas smart encryption is effective in reducing cell flips and therefore the energy of the unchanged and the zero-words, words which change are re-encrypted and written to the memory. To reduce the write energy of these re-encrypted words, SECRET incorporates post-encryption write optimization by filtering the words through energy masks. For every *n*-bit word (ciphertext), SECRET uses an *n*-bit full energy mask with n/2 pairs of 01 (high energy state), which are XORed with the ciphertext to transform the high energy states in the ciphertext into low energy states (i.e., states 00 or 11). Figure 7 depicts the XOR-based state transition of high energy states to low energy states and vice versa. Note that either state 01 or 10 can be used in the energy mask; this work uses 01 for the analysis. Additionally, SECRET uses an *n*-bit half energy mask covers the cases where high energy states are concentrated in the lower half of the word and not uniformly distributed.

Each word in encrypted cache line is XORed in parallel with a full and a half energy mask. Thereafter, the write energy of the full-mask word, half-mask word, and unmasked word are compared to identify the best mask for each word, as shown in figure 8. Continuing the example from figure 6, figure 9 illustrates the concept of energy masking. Word 1 is already in a low energy state,

Figure 8: Energy masking module to select the lowest energy mask for a word. The mask which gives the minimum number of high energy states is selected. Note that for parallel operation, a separate energy masking module is present for each word.

| Encoding               | Flags        | New        | Word 1        |           | Word 2          | Word 3          |  |

|------------------------|--------------|------------|---------------|-----------|-----------------|-----------------|--|

| 00                     | No flag      | Plaintext  | 0 0 0 0 1 1 0 | 1         | 1 1 1 1 0 0 1 0 | 0 0 0 0 0 0 0 0 |  |

| 01                     | Zero-flag    | New        |               |           |                 |                 |  |

| 10                     | Half mask    | Ciphertext | 00111111      | 0         | 0 1 1 0 1 0 0 0 | 0 0 1 1 0 1 1 0 |  |

| 11                     | 11 Full mask |            | $\oplus$      |           | $\oplus$        | $\oplus$        |  |

| 0 0 1                  | L 1 0 1      |            | 00000000      | 0         | 0 1 0 1 0 1 0 1 | 00000101        |  |

| Energy- and Zero-Flags |              | No Mask    |               | Full Mask | Half Mask       |                 |  |

|                        |              | Ų          |               | Ų         | Ų               |                 |  |

| Low Energy Ciphertext  |              | 00111111   | 0             | 001111101 | 0 0 1 1 0 0 1 1 |                 |  |

Figure 9: This figure depicts the energy masks for 3 different words from figure 6. Each word is XORed with an energy mask such that the overall write energy of the word is minimized. Note that if the zero-flag for a word is set, the energy mask for that word is not recorded in the flag-bits. The low energy ciphertext (LEC) obtained from application of the energy mask gets written on the NVM.

hence it is left unmodified. Word 2 uses a full mask and word 3 uses a half mask to reduce the ciphertext into a low energy ciphertext (LEC), which is finally written to the NVM. The information about energy mask and zero-word are encoded in a 2-bit flag for each word as follows: 00 - no flag, 01 - zero word, 10 - half energy mask, and 11 - full energy mask. Note that if the zero-flag is set for a word, then the energy mask information for that word is not required for decryption. The combined memory overhead for smart encryption and energy masking is 6.25% per cache line (refer Sec. 3.2.4). Hence, we need only 2 bits to uniquely detect 4 different states for a word.

#### **3.2.3** Flag-bit encryption

This work considers a 512-bit cache line consisting of eight 64-bit words. Thus, size of the metadata (i.e., zero-flags and energy-flags) is 16 bits (2 bits/word). For ensuring security of the data, the meta-data is also encrypted and stored along with the cache line in the memory. Since 16-bit encryption is susceptible to attacks, the size of the meta-data is extended to 66 bits by including 5 error-correcting pointers (ECP) [39], each of 10 bits (for a 512-bit cache line). An ECP uses a pointer to point to a failed cell and also stores the correct value for that cell. For example, on a row with 256 MLCs (i.e., 512-bit cache line), 8 logical bits are required to uniquely point to any failed cell (log<sub>2</sub>256) and 2 bits logical bits are required to store the data of the failed cell (1 MLC = 2 logical bits), i.e., a total of 10 logical bits. The standard ECP implementation reserves six ECPs for every 512-bit (single-level cell) memory block, enabling each 512-SLC block to recover from up to 6 hard errors. Since MLCs are more susceptible to errors, SECRET reserves 5 ECPs per 256 MLCs. Note that the use of ECPs for endurance enhancement of NVMs is common practice [39,63]. Hence, SECRET ensures the security of the meta-data for no overhead beyond the flag-bits, by incorporating already provisioned ECP bits along with the meta-data to form a secure word. The meta-data encryption is achieved by XORing the meta-data with an OTP generated from the line address and the concatenation of global and all the local counters.

## 3.2.4 SECRET: Architectural design

SECRET requires modifications to the write and read data-paths to realize smart encryption and energy masking. This section describes each in detail, and finally evaluate the hardware overhead of a practical implementation.

#### **3.2.4.1** Write operation

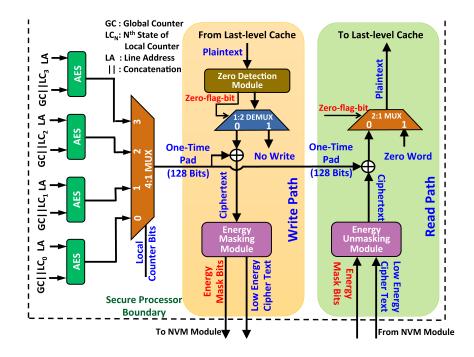

Figure 10 depicts the modified write data-path circuitry for SECRET. Writes result in (i) smart encryption followed by (ii) energy masking. Smart encryption performs a read-modify-write scheme at the word level, identifying the unmodified words, which are subsequently not written back to the NVM module (main memory). The modified words, referred to as the plaintext in figure 10, are then examined to identify the zero-words, which are also not written back to the NVM module. This is achieved by the zero detection module, which eliminates zero-word writes. The non-zerowords are then encrypted by XORing with an OTP. Parallel AES units generate all the possible combinations of one-time pads (OTPs) corresponding to all possible states of the local counter  $(2^2 = 4$  in this example), to avoid the latency of serial generation of OTPs. The line address (LA) and the sum of the global counter (GC) and individual local counters (LC) are provided as inputs to the AES units, which generate the corresponding OTPs. The appropriate OTP for a word is selected from the combinations based on the updated local counter bits of the modified word. The ciphertext is then passed through the energy masking module (EMM). The EMM transforms the ciphertext to a low energy ciphertext that is written back to the NVM module.

Figure 10: This figure depicts the architecture for write (yellow) and read (green) data-paths of SECRET. In the write path, the zero detection module and implements the zero-based partial write, whereas the energy masking module implements energy masking. In the read path, the energy unmasking module generates the true ciphertext from the low energy ciphertext, and the zero-flag-bits determine the zero-words during decryption.

# 3.2.4.2 Read operation

The modified read data-path to implement SECRET is also illustrated in figure 10. During a read, SECRET reverses the transformations that it applies to the data on a write operation. After the data is fetched from the NVM module, the meta-data (zero-flags, energy-flags, ECP) is first decrypted (not shown in the figure). The data, which is in the low energy ciphertext form, is transformed to the true ciphertext by passing it through the energy unmasking module (EUM). The EUM generates the true ciphertext by XORing the low energy ciphertext with the appropriate energy mask (no, half, full), which is selected on the basis of the energy-flag for that word. The true ciphertext is then decrypted by XORing it with the OTP corresponding to its local counter. However, if the zero-flag-bit of a word is set, a zero-word is forwarded as the plaintext to the cache.

#### 3.2.5 Hardware overhead

SECRET has memory overhead associated with storage of the (i) local counters, (ii) zero-flag-bits, and (iii) energy-flags. For a 512-bit cache line with 64-bit words, each word has a 2-bit local counter and 2 bits of combined zero-flag and energy-flag, i.e., an overhead of 6.25%. SECRET requires 4 additional AES units over conventional AES-based counter mode encryption. A highly optimized and energy-efficient hardware implementation of AES for the 22nm node is reported in [65]. The AES unit overhead is 8360 gates with an area of  $\approx 0.02 \text{mm}^2$ . The standard Intel i7 (22nm) die size is 160mm<sup>2</sup> [66], therefore, the AES unit area overhead (0.0125%) of SECRET is negligible in practice.

#### 3.3 SECRET: EVALUATION AND RESULTS

Trace-based simulations on an MLC/TLC RRAM architecture was performed using NVMain [37] on both integer and floating-point workloads from the SPEC CPU2006 [38] benchmark suite. NVMain is a cycle accurate main memory simulator designed to simulate emerging non-volatile memories at the architectural level. NVMain was configured with 8GB main memory, organized as a single channel, with 1 rank, and eight x8 devices/rank. The memory controller performs first-ready first-come-first-serve scheduling, with open page policy. NVMain was modeled with energy/latency parameters provided in [5,63]. Further, memory lifetime evaluation was performed using an in-house simulator that operates at the page level with a page size of 4KB. Along the lines of [39,63], simulations assumed perfect wear leveling and a mean cell lifetime of 10<sup>8</sup> writes until failure.

#### **3.3.1** Evaluated techniques

BLE [11] and DEUCE [12] are state-of-the-art counter mode encryption techniques that perform word-level DCW to reduce the number of re-encrypted words in a cache line. BLE splits a cache line into four 128-bit words and assigns a 2-bit local counter to each word. When a local counter reaches its terminal count, the entire cache line is re-encrypted. In contrast, DEUCE splits a cache

line into 32 16-bit words and maintains a leading and a trailing counter for the entire cache line. After a pre-determined number of writes (epoch), the entire cache line is re-encrypted. While the leading counter is incremented on every write, the trailing counter is fixed and incremented to the leading counter's value after every 32 writes (epoch interval). Due to its design, DEUCE requires that the words that are modified once in a given epoch interval be re-encrypted on every write during that epoch. In contrast, SECRET only encrypts non-zero modifies words, and incorporates XOR-based energy masking to reduce memory writes of encrypted data. Results compare write energy, latency, and memory lifetime of SECRET with BLE and DEUCE. AES-based counter mode encryption, which re-encrypts the entire cache line on every write, is the baseline.

## 3.3.2 Summary

Table 7 summarizes the energy, latency, and lifetime results for BLE, DEUCE, and SECRET, normalized to the baseline. Whereas BLE and DEUCE rely exclusively on read-modify-write to reduce memory writes, SECRET uses zero-based partial writes along with word-level DCW to reduce memory writes, and energy masks to lower the energy overhead of write operations.

| NVM         | Encryption technique | Energy reduction | Latency reduction | Lifetime<br>improvement | Memory<br>overhead |

|-------------|----------------------|------------------|-------------------|-------------------------|--------------------|

|             | BLE                  | 40%              | 23%               | 35%                     | 1.56%              |

| MLC<br>RRAM | DEUCE                | 40%              | 17%               | 36%                     | 6.25%              |

|             | SECRET               | 80%              | 37%               | 63%                     | 6.25%              |

| TLC<br>RRAM | BLE                  | 33%              | 31%               | 18%                     | 1.56%              |

|             | DEUCE                | 40%              | 23%               | 24%                     | 6.25%              |

|             | SECRET               | 63%              | 49%               | 56%                     | 7.84%              |

Table 2: Summary of energy, latency, lifetime improvements, and memory overhead of BLE, DEUCE, and SECRET over AES-based counter-mode encryption.

# 3.3.3 MLC RRAM NVM

First, the results for energy, latency, and lifetime, for an MLC RRAM architecture are presented. Note that an MLC stores 2 logical bits per cell; a 64-bit word is stored in 32 physical MLCs.

# **3.3.3.1** Energy and latency

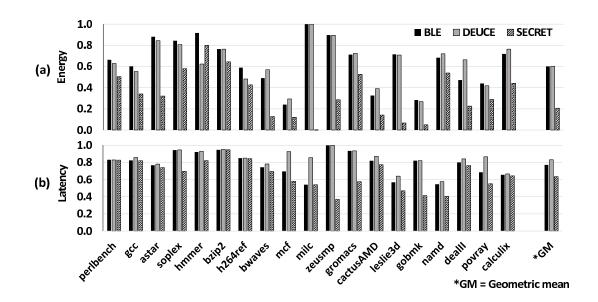

As shown in the figure 11, BLE, DEUCE, and SECRET reduce write energy by 40%, 40%, and 80%, respectively, over the baseline. While energy reductions for BLE (DEUCE) result from 128-bit (16-bit) word-level DCW only, energy reductions for SECRET result from 3 levels of optimization – 64-bit word-level DCW, zero-based partial writes, and energy masks. Latency reductions for BLE, DEUCE, and SECRET over the baseline are 23%, 17%, and 37%, respectively. It is interesting to note that for benchmarks such as perlbench and bzip2, the latency reductions for SECRET are lower than DEUCE. This occurs when a particular word in a cache line changes on every write, resulting in a rollover of its local counter. A counter rollover precipitates the re-encryption of the entire cache line, increasing memory latency.

Figure 11: (a) Write energy and (b) latency of BLE, DEUCE, and SECRET (normalized to baseline) evaluated using SPEC CPU2006 benchmarks [38] on NVMain [37]. For MLC RRAM, BLE, DEUCE, and SECRET reduce write energy (latency) by 40% (23%), 40% (17%), and 80% (37%), respectively, over baseline AES-based counter mode encryption.

Figure 12: Memory lifetime (normalized to AES-based counter mode encrytion) for MLC RRAM using BLE, DEUCE, and SECRET encryption architectures. Lifetime evaluated using an in-house simulator, using average cell lifetime of 10<sup>8</sup> writes until failure [63].

## 3.3.3.2 Memory lifetime

Figure 12 reports the improvements in memory lifetime of MLC RRAM NVM using BLE, DEUC-E, and SECRET, normalized to the baseline. As seen from the figure, there is no improvement in lifetime from BLE and DEUCE for the milc benchmark because the milc benchmark consists of a large number of zeros in the plaintext. Since SECRET eliminates zero encryption in the plaintext, only SECRET increases lifetime for the milc benchmark. In contrast, BLE and DEUCE re-encrypt zero words (that are significant in the milc benchmark), resulting in high cell flip rate and consequently low NVM lifetime. On average, BLE, DEUCE, and SECRET improve memory lifetime by 35%, 36%, and 63%, respectively. SECRET improves memory lifetime by reducing the number of programmed cells using both word-level DCW and zero-based partial encryption, thereby achieving the maximum reduction in the wear rate of memory.

#### 3.3.4 TLC RRAM NVM

Energy, latency, and lifetime of SECRET for TLC RRAM NVM are also evaluated. A 512-bit cache line is partitioned into nine 51-bit words and one 53-bit word for smart encryption and energy masking. A 51-bit (53-bit) word is stored in 17 (18) TLCs (3 logical bits per physical TLC). Although a 51/53-bit word is used for implementing SECRET, SECRET does not modify