**University of Bath**

### PHD

#### Interactive communication system simulator ICOSS.

Abdul-Wahab, A. S. M. S.

Award date: 1979

Awarding institution: University of Bath

Link to publication

## Alternative formats If you require this document in an alternative format, please contact: openaccess@bath.ac.uk

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

INTERACTIVE COMMUNICATION SYSTEM SIMULATOR ICOSS

submitted by <u>A S M S ABDUL-WAHAB</u> for the degree of PhD of the University of Bath 1979

#### COPYRIGHT

Attention is drawn to the fact that copyright of this thesis rests with its author. This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author. This these may be made available for consultation within the library of the University of Bath and may be photocopied or lent to other libraries for the purposes of A.S.M.S. AbdM-Wahab consultation. ProQuest Number: U442859

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest U442859

Published by ProQuest LLC(2015). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code. Microform Edition © ProQuest LLC.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### SUMMARY

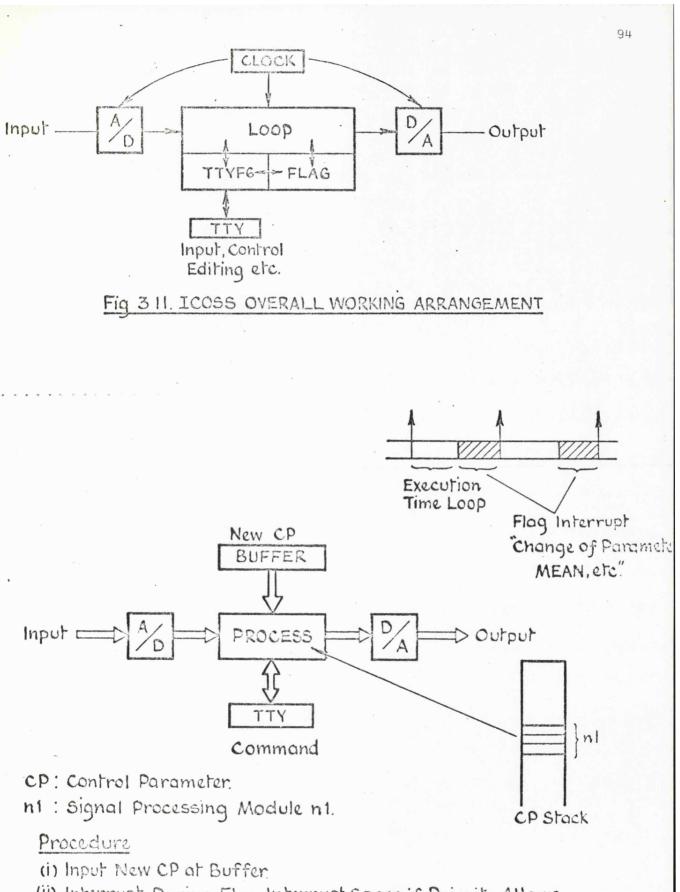

This work is concerned with the design of a generalpurpose time-domain interactive communication-system simulator ICOSS. Signal processing modules may be interconnected in any order, and module control parameters, as well as the system control parameters can be varied while the simulation is running. Editing of the system structure (inserting or deleting modules) can be done on-line.

The ultimate objective is to set-up a communication system simulation working on an on-line basis, with an interactive capability providing the engineer in a research environment with a bench tool, which complements the hardware apparatus.

Once the prototype of ICOSS was developed, an investigation was made into one of the main areas of further development, namely, processing speed, in which a dedicated processor containing a signal processing module, comprising of microprocessor controlled unit, is coupled with the main computer, where ICOSS resides.

The simulator novelty in engineering and research was tested, by using problems involving feedback links, namely, interference in a phase-lock loop and performance of fast acquisition phase-lock loop. These provided confirmation and deeper understanding of experimental work as well as proving that ICOSS was working

(ii)

correctly.

To implement the full system requires computing power and equipment which was unavailable. Therefore, only the prototype version was implemented.

#### CONTENTS

TITLE PAGE(i)SUMMARY(ii)CONTENTS(iv)

٠,

#### CHAPTER ONE: INTRODUCTION

-

| 1.1 | Commun | lication Systems                              | 1  |

|-----|--------|-----------------------------------------------|----|

|     | 1.1.1  | Definition and Characteristic                 | 1  |

|     | 1.1.2  | Areas of problems in communication<br>systems | 2  |

| 1.2 | Simula | ition `                                       | 3  |

|     | 1.2.1  | System studies                                | 3  |

|     | 1.2.2  | System simulation                             | 3  |

|     | 1.2.3  | Communication system simulation               | 5  |

| 1.3 | Thesis | ;                                             | 7  |

|     | 1.3.1  | Designing a new simulator, ICOSS              | 7  |

| `   | 1.3.2  | Outlook and modifications                     | 8  |

|     | 1.3.3  | Application                                   | 9  |

|     |        | SIMULATION TECHNIQUES AND SIMULATORS          | t, |

| 2.1 | Introd | luction                                       | 10 |

|     | 2.1.1  | Historical background                         | 10 |

|     | 2.1.2  | Simulation techniques                         | 13 |

|     | 2.1.3  | The block diagram technique                   | 15 |

|     | 2.1.4  | In this chapter                               | 17 |

| 2.2 | Implen | mentation:user side                           | 17 |

|     | 2.2.1  | Typical communication system                  | 18 |

|     | 2.2.2  | Limitations                                   | 25 |

|     | 2.2.3  | Projection                                    | 25 |

| 2.3 | Implen | nentation:computer side                       | 26 |

| 2.4 | Freque | ency domain simulation                        | 31 |

|     | 2.4.1  | Introduction                                  | 31 |

|     | 2.4.2  | Principle of operation                        | 31 |

|     | 2.4.3  | Execution procedure                           | 32 |

|       | 2.4.4   | System analysis                          | 32    |

|-------|---------|------------------------------------------|-------|

|       | 2.4.5   | Characteristics                          | 34    |

|       | 2.4.6   | Utilisation                              | 35    |

|       | 2.4.7   | Scaling                                  | 35    |

| 2.5   | Time d  | omain simulation                         | 35    |

|       | 2.5.1   | Basic principles and execution procedure | 35    |

|       | 2.5.2   | System state variables                   | 36    |

|       | 2.5.3   | Characteristics                          | 41    |

|       | 2.5.4   | General comments                         | 41    |

|       | 2.5.5   | Execution time                           | 42    |

| 2.6   | R.F. s  | ignal simulation                         | 43    |

| 2.7   | Off-li: | ne working                               | 45    |

|       | 2.7.1   | Principle of operation                   | 45    |

|       | 2.7.2   | Characteristics                          | 45    |

| 2.8   | On-lin  | e working                                | 46    |

|       | 2.8.1   | Principle of operation                   | 46    |

|       | 2.8.2   | Characteristics                          | 47    |

| 2.9   | Limita  | tions and objectives                     | 48    |

|       | 2.9.1   | Limitations                              | 48    |

| `     | 2.9.2   | Objectives                               | 48    |

| 2.10  | ICOSS   |                                          | 52    |

| 2.11  | Summar  | У                                        | 53    |

| Figu: | res rel | ating to Chapter 2                       | 54-58 |

| CHAP  | TER THR | EE: INTERACTIVE COMMUNICATION SYSTEM     |       |

|       |         | SIMULATOR ICOSS                          | 59    |

|       |         | ~                                        |       |

.

| 3.1 | Introduction        |           |                                                  |            |  |  |

|-----|---------------------|-----------|--------------------------------------------------|------------|--|--|

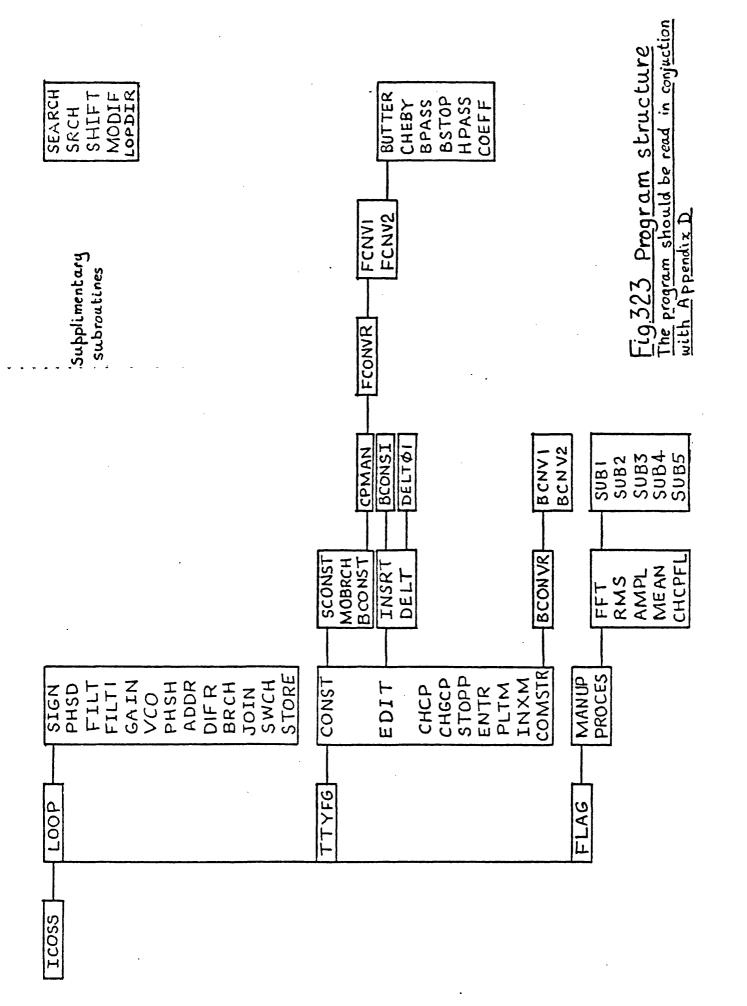

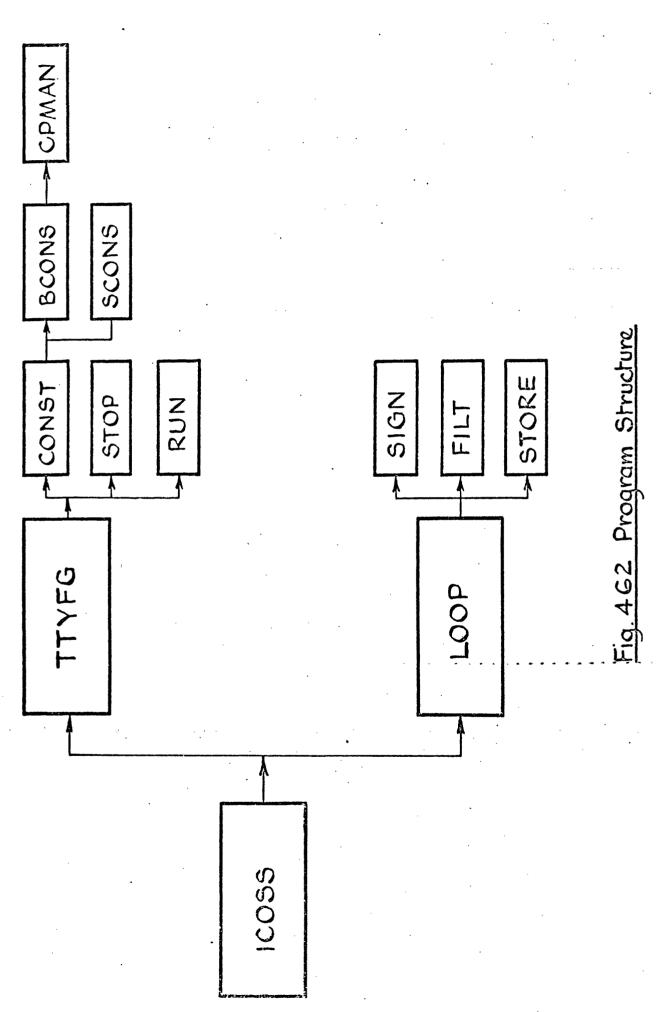

| 3.2 | Program structure   |           |                                                  |            |  |  |

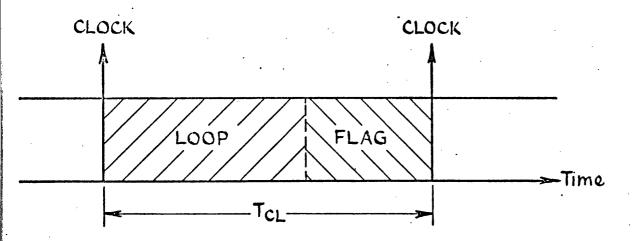

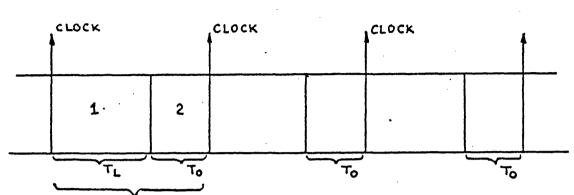

| 3.3 | Time a              | llocation | S                                                | 65         |  |  |

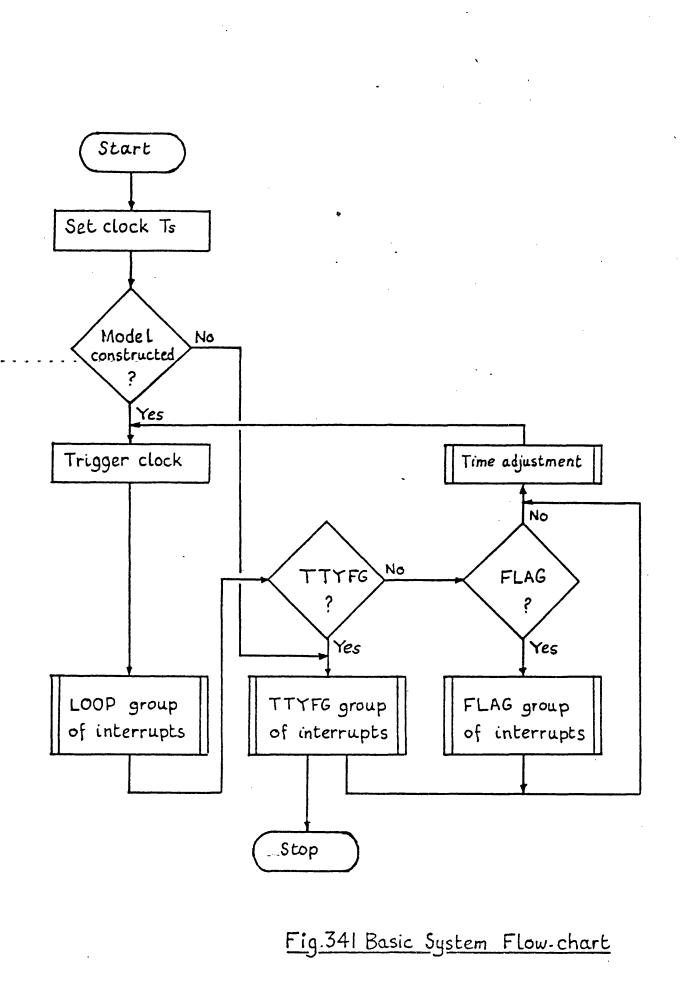

| 3.4 | Flow-chart          |           |                                                  |            |  |  |

| 3.5 | Complementary items |           |                                                  |            |  |  |

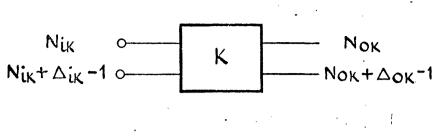

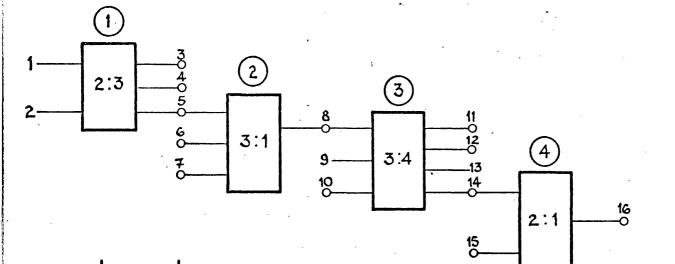

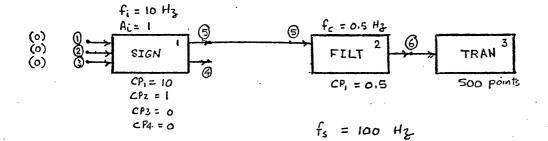

|     | 3.5.1               | -         | al processing modules input-<br>ode arrangements | 68         |  |  |

|     |                     | 3.5.1.1   | General notes                                    | 68         |  |  |

|     |                     | 3.5.1.2   | Node numbering                                   | 69         |  |  |

|     |                     | 3.5.1.3   | Signal value storage                             | 70         |  |  |

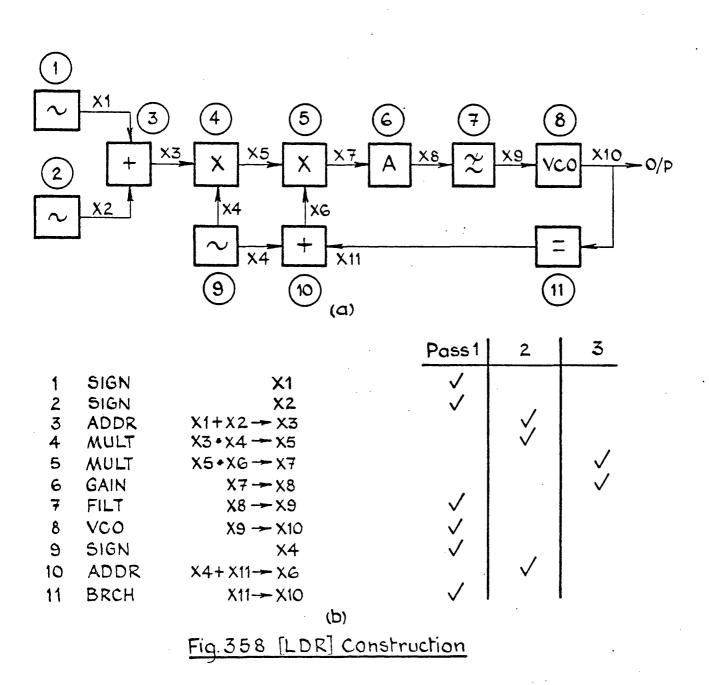

|     |                     | 3.5.1.4   | Example                                          | <b>7</b> 0 |  |  |

|      |          | 3.5.1.5           | Implementation                                     | 70     |

|------|----------|-------------------|----------------------------------------------------|--------|

|      | 3.5.2    | The contr         | rol parameters CPs and GCPs                        | 71     |

|      |          | 3.5.2.1           | Definitions, characteristics<br>and general points | 71     |

|      |          | 3.5.2.2           | Procedure                                          | 73     |

|      | •        | 3.5.2.3           | Storage arrangements                               | 74     |

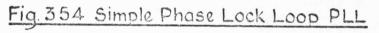

|      | 3.5.3    | The syste         | em matrix SM                                       | 75     |

|      | 3.5.4    | Loop dire         | ectives                                            | 76     |

|      |          | 3.5.4.1           | General notes                                      | 76     |

|      |          | 3.5.4.2           | System state                                       | 77     |

|      |          | 3.5.4.3           | Loop directive - implementation                    | 78     |

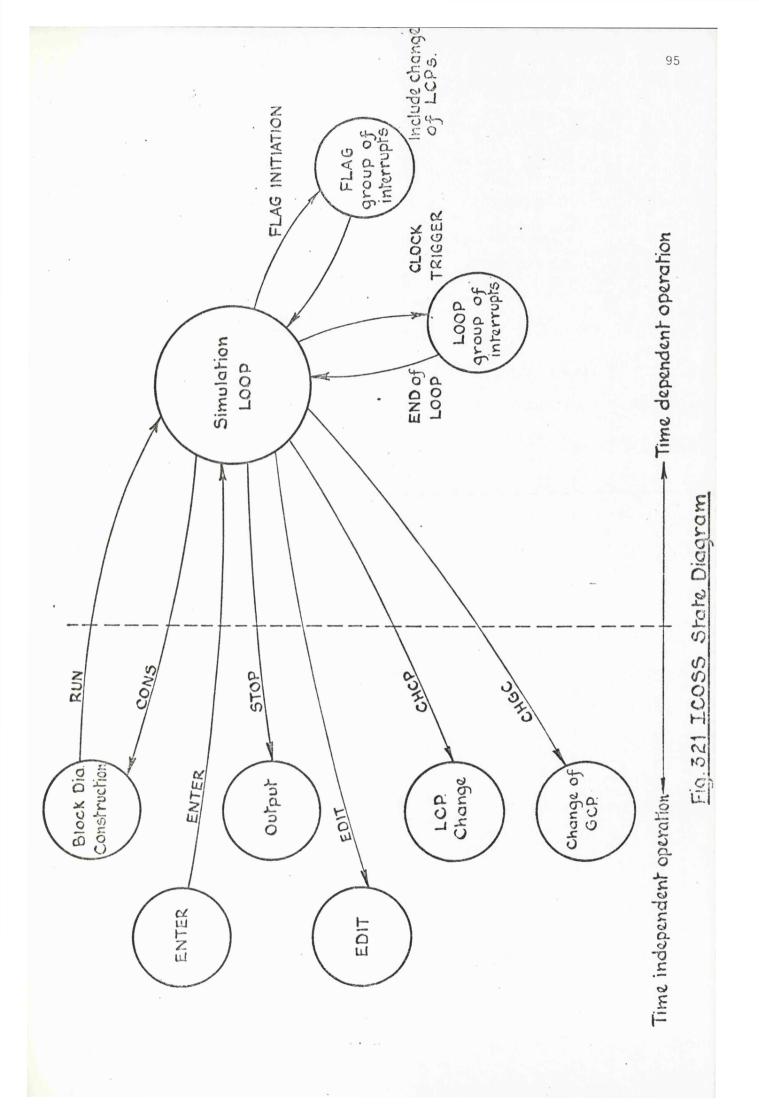

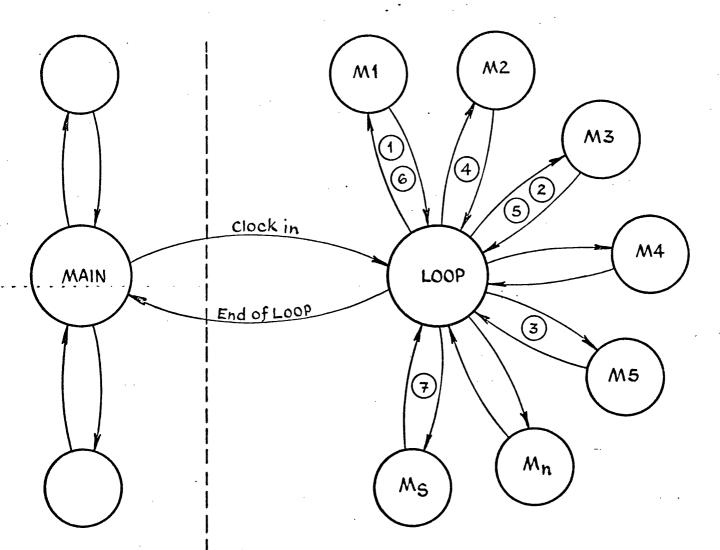

| 3.6  | The Loc  | op group d        | of interrupts LOOP                                 | 80     |

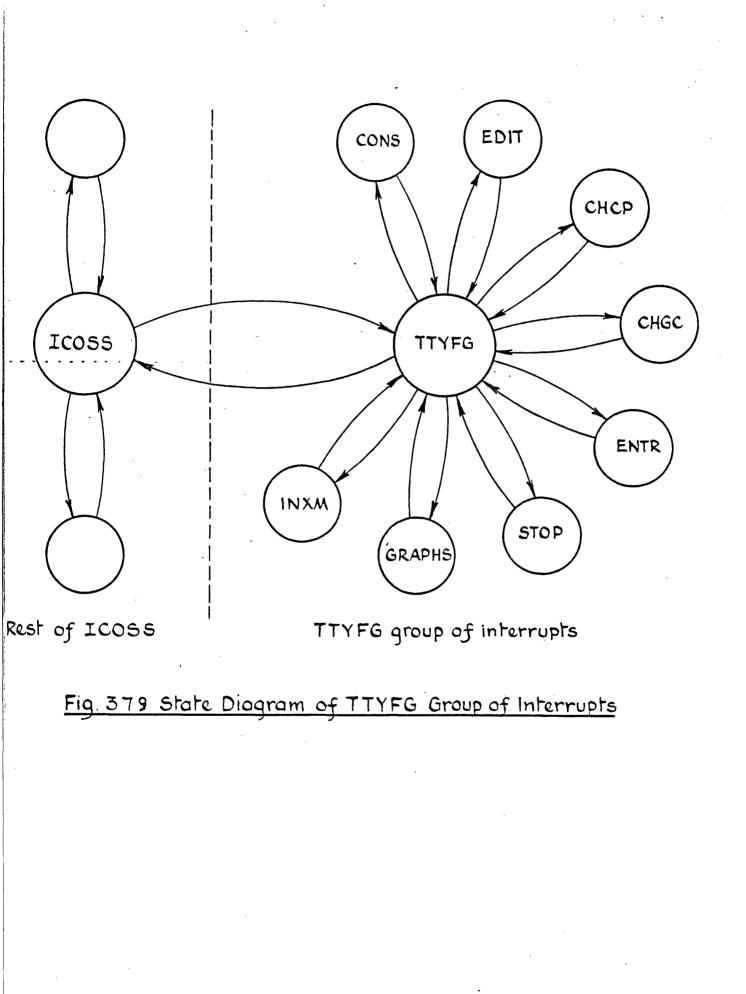

| 3.7  | The Tel  | Letype gro        | oup of interrupts TTYFG                            | 81     |

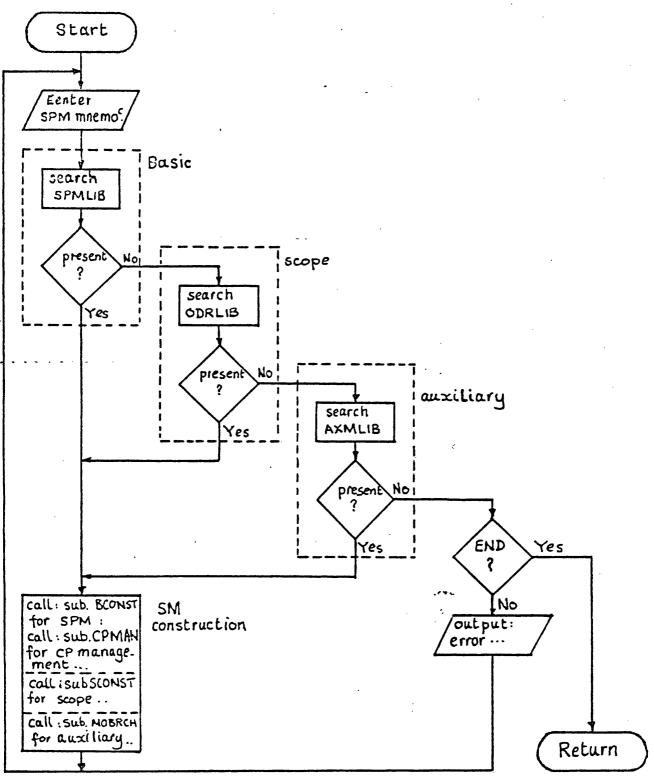

|      | 3.7.1    | Construct         | tion CONS                                          | 82     |

|      | 3.7.2    | Editing H         | EDIT                                               | 83     |

|      | 3.7.3    | Changing          | control parameters (Local) CHCP                    | 86     |

|      | 3.7.4    | Changing          | global control parameters CHGC                     | 86     |

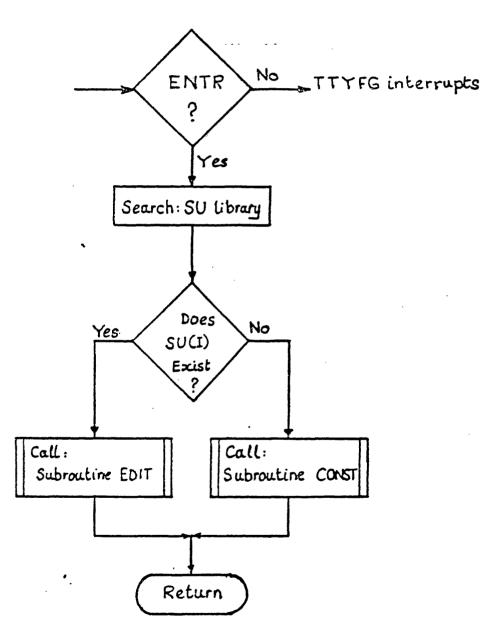

|      | 3.7.5    | Running a<br>ENTR | an already established system                      | 87     |

|      | 3.7.6    | Stopping          | (pausing) a running system STOP                    | 88     |

| `    | 3.7.7    | Block dia         | agram display CMST                                 | 89     |

|      | 3.7.8    | Graph plo         | otting management routine PLTM                     | 89     |

|      | 3.7.9    | Graph plo         | otting routine PLTG                                | 89     |

|      | 3.7.10   | Initialis         | sation routine interrupt INXM                      | 90     |

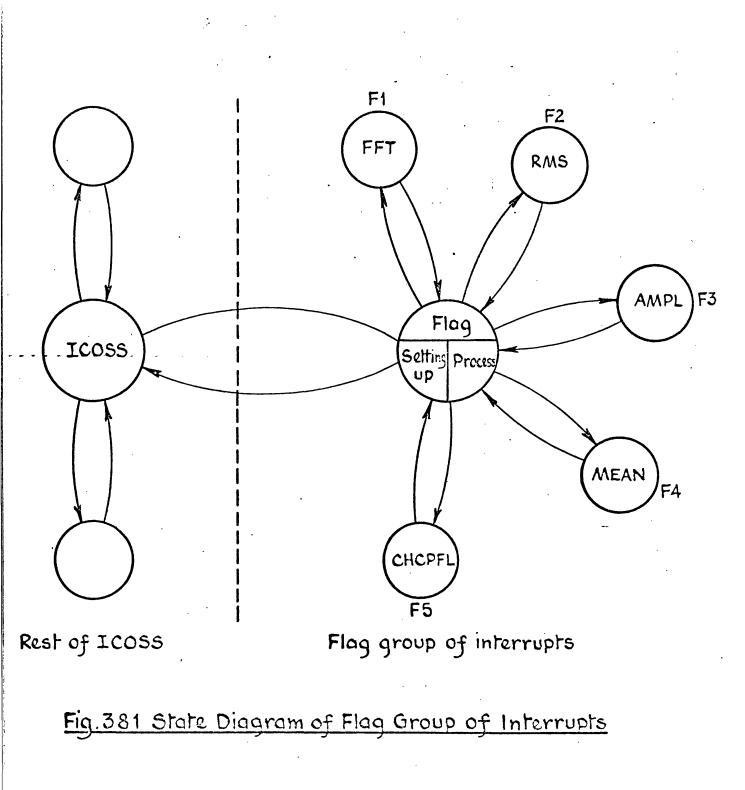

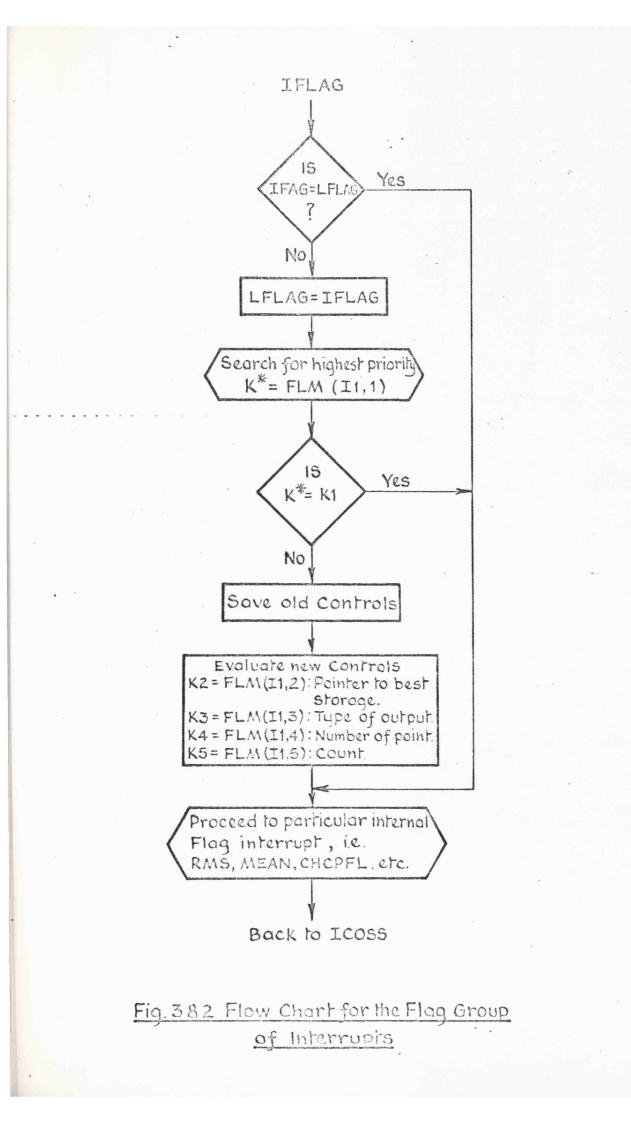

| 3.8  | The Fla  | ag group d        | of interrupts                                      | 90     |

| 3.9  | Develop  | pments and        | l further work                                     | 91     |

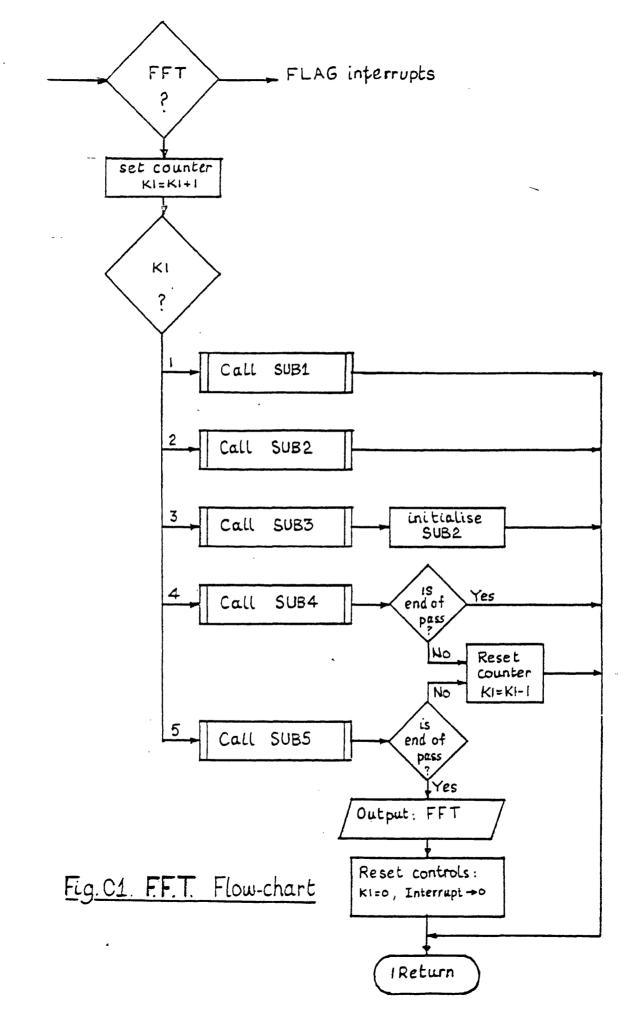

| Figu | res rela | ating to (        | Chapter 3                                          | 94-117 |

|      |          |                   |                                                    |        |

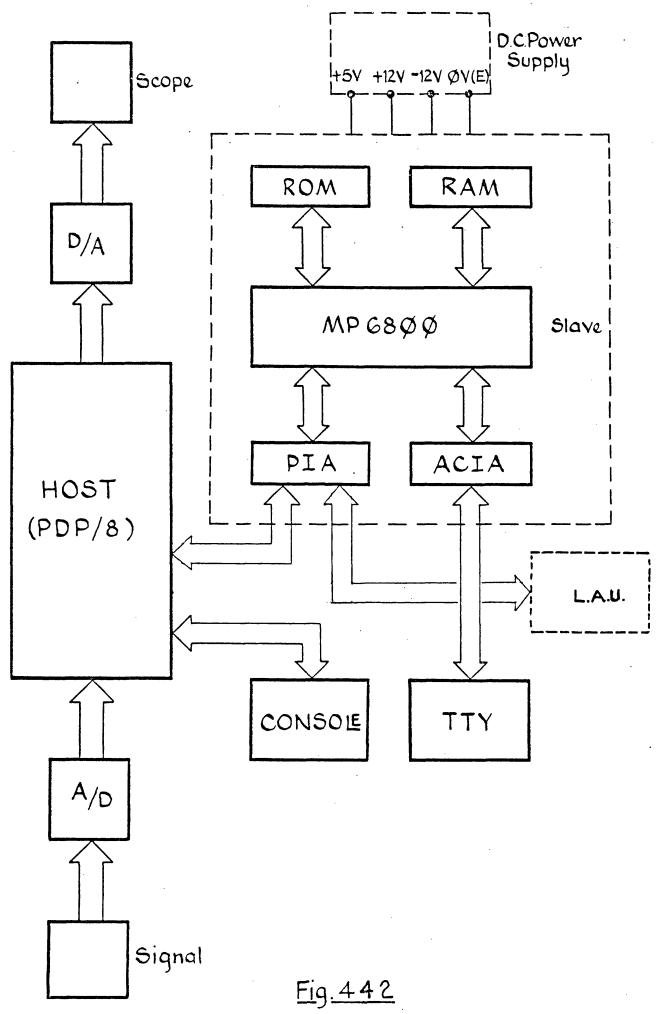

## CHAPTER FOUR: MICROPROCESSOR APPLICATION: BANK

|        | OF DIGITAL FILTERS (BOF)                             | 118                                                                                                                                                                                                                                             |

|--------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introd | uction                                               | 118                                                                                                                                                                                                                                             |

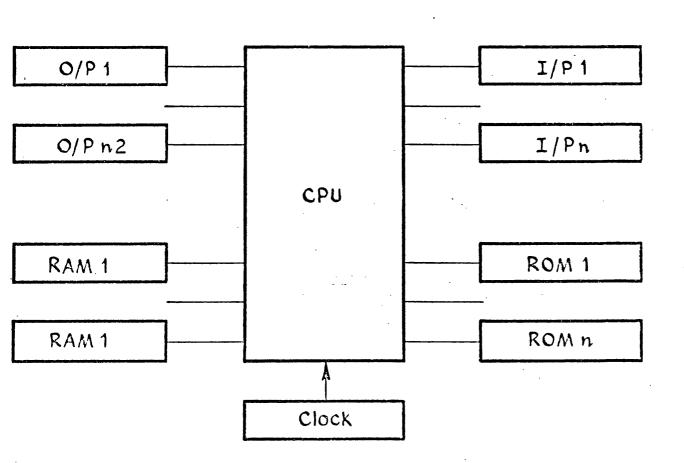

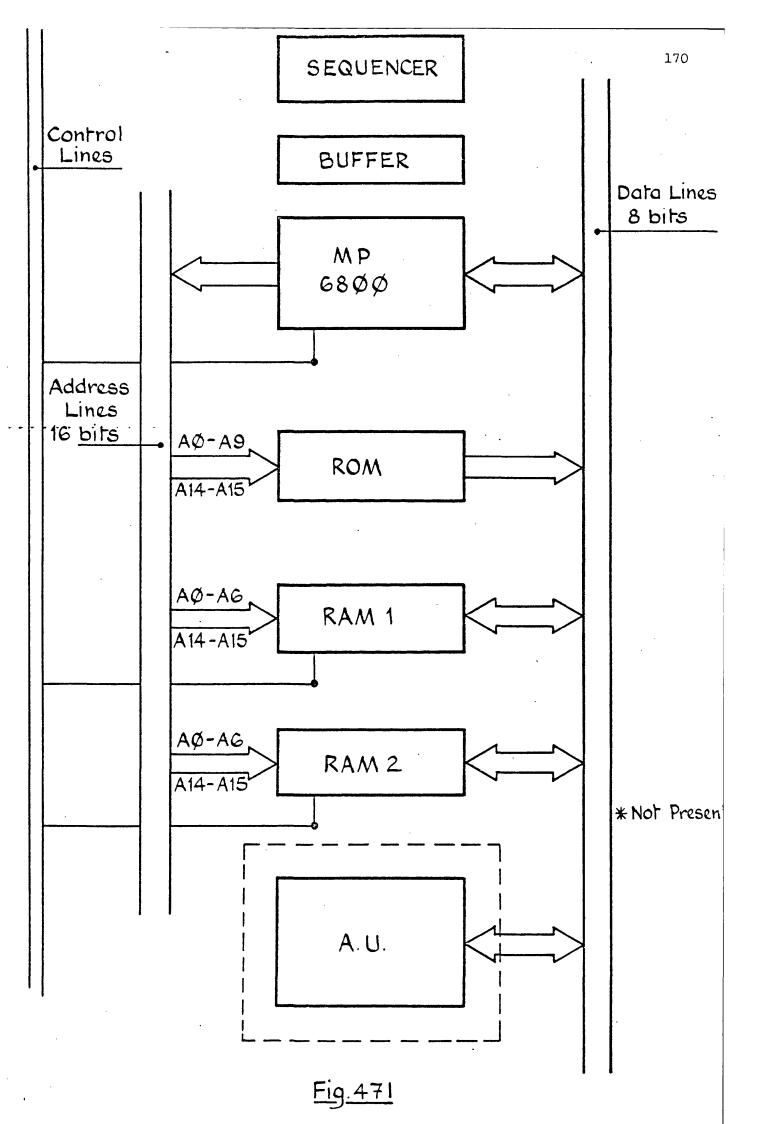

| Microp | processor systems                                    | 120                                                                                                                                                                                                                                             |

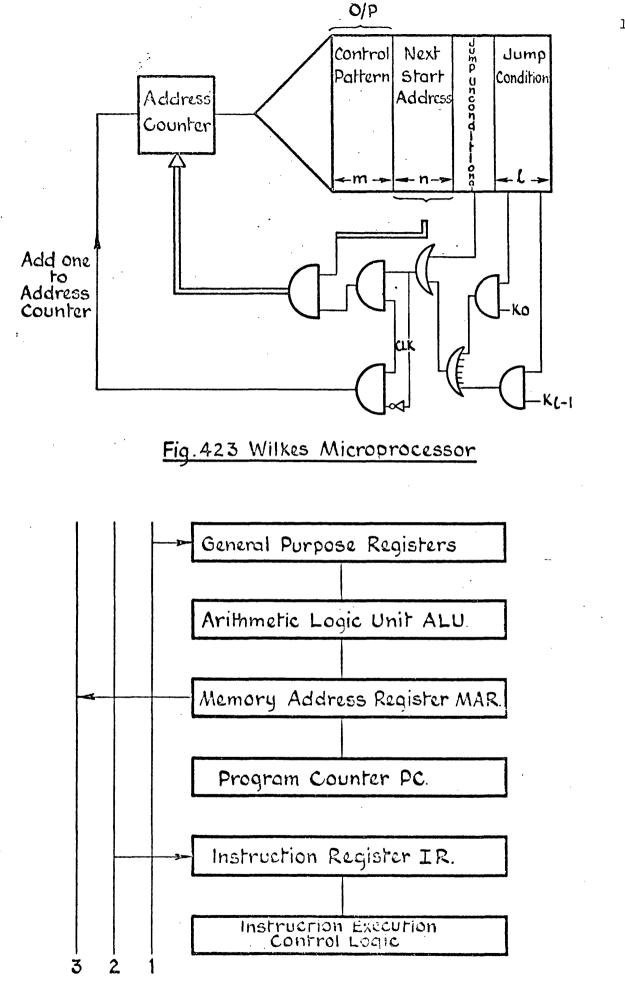

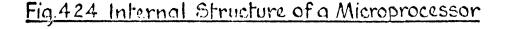

| 4.2.1  | Introduction                                         | 120                                                                                                                                                                                                                                             |

| 4.2.2  | Microprocessor architecture                          | 121                                                                                                                                                                                                                                             |

| 4.2.3  | Read only memory ROM                                 | 124                                                                                                                                                                                                                                             |

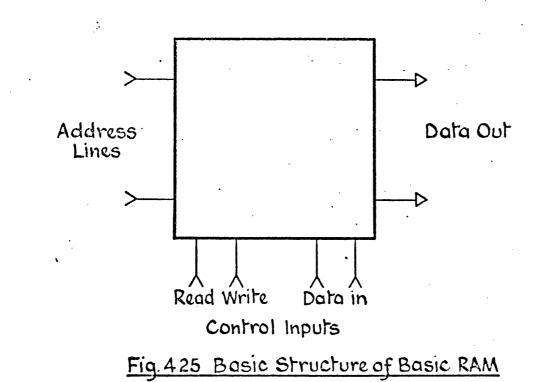

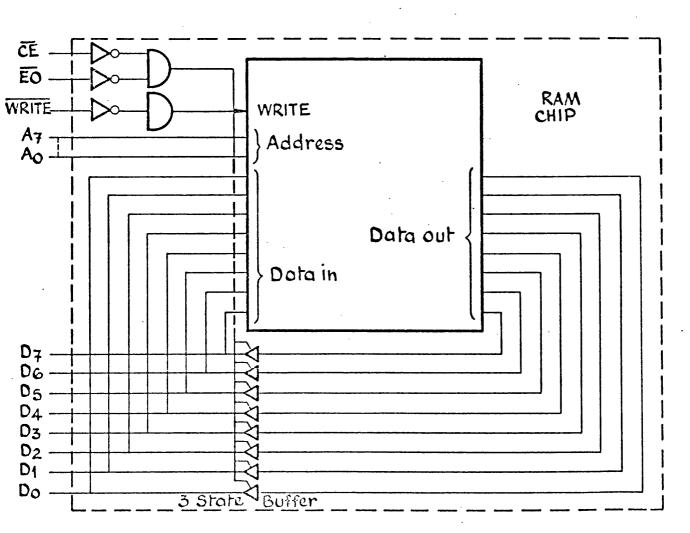

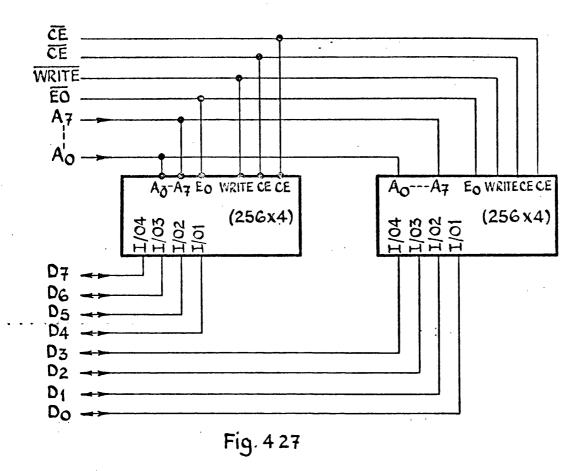

| 4.2.4  | Random access memory RAM                             | 125                                                                                                                                                                                                                                             |

| Config | ruration                                             | 129                                                                                                                                                                                                                                             |

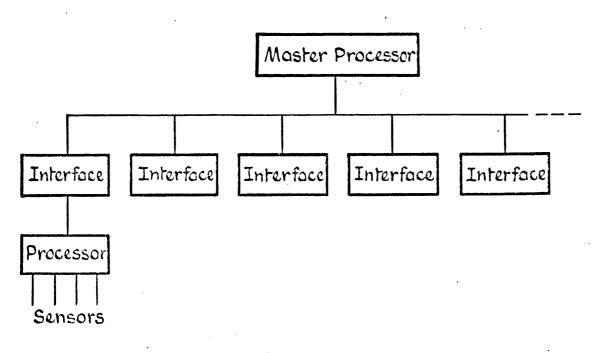

| 4.3.1  | Multiprocessing systems                              | 130                                                                                                                                                                                                                                             |

|        | Microp<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Config | OF DIGITAL FILTERS (BOF)<br>Introduction<br>Microprocessor systems<br>4.2.1 Introduction<br>4.2.2 Microprocessor architecture<br>4.2.3 Read only memory ROM<br>4.2.4 Random access memory RAM<br>Configuration<br>4.3.1 Multiprocessing systems |

|      | 4.3.2 Master-slave processors 1 |                                                   |         |  |  |  |  |  |

|------|---------------------------------|---------------------------------------------------|---------|--|--|--|--|--|

|      | 4.3.3 Signal processing module  |                                                   |         |  |  |  |  |  |

| 4.4  | Design                          | ing a slave processor for the BOF module          | 135     |  |  |  |  |  |

|      | 4.4.1                           | General                                           | 135     |  |  |  |  |  |

|      | 4.4.2                           | Theory ·                                          | 136     |  |  |  |  |  |

|      | 4.4.3                           | BOF module design requirements                    | 137     |  |  |  |  |  |

|      | 4.4.4                           | Module structure (hardware)                       | 138     |  |  |  |  |  |

| 4.5  | Softwar                         | re development of BOF module                      | 139     |  |  |  |  |  |

|      | 4.5.1                           | Program formulation                               | 139     |  |  |  |  |  |

|      | 4.5.2                           | Implementation                                    | 142     |  |  |  |  |  |

|      | 4.5.3                           | BOF program                                       | 143     |  |  |  |  |  |

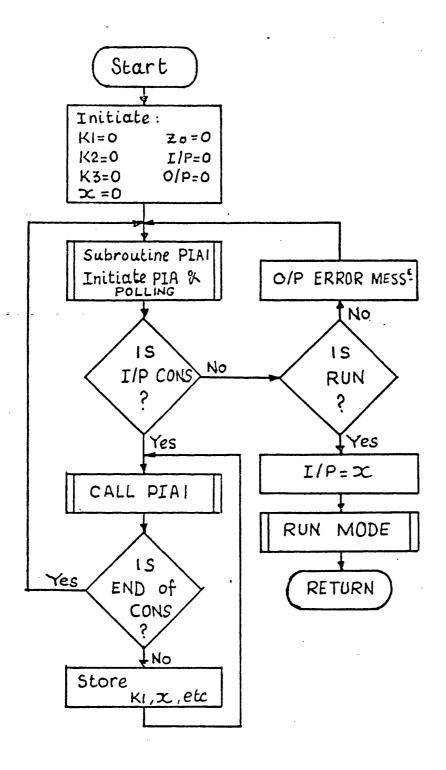

|      |                                 | 4.5.3.1 Interfacing                               | 143     |  |  |  |  |  |

|      |                                 | 4.5.3.2 Memory map                                | 144     |  |  |  |  |  |

|      |                                 | 4.5.3.3 Construction code CONS                    | 146     |  |  |  |  |  |

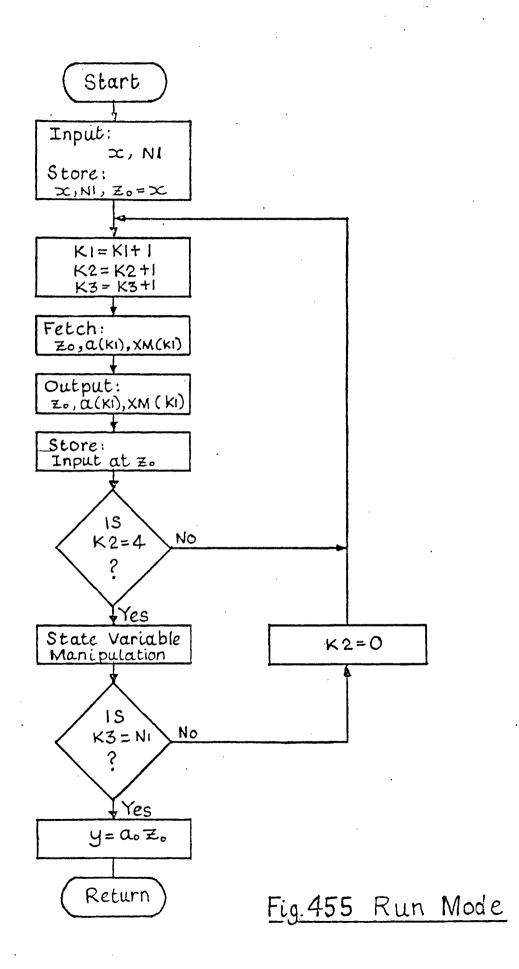

|      |                                 | 4.5.3.4 The run mode (RUN)                        | 147     |  |  |  |  |  |

| 4.6  |                                 |                                                   |         |  |  |  |  |  |

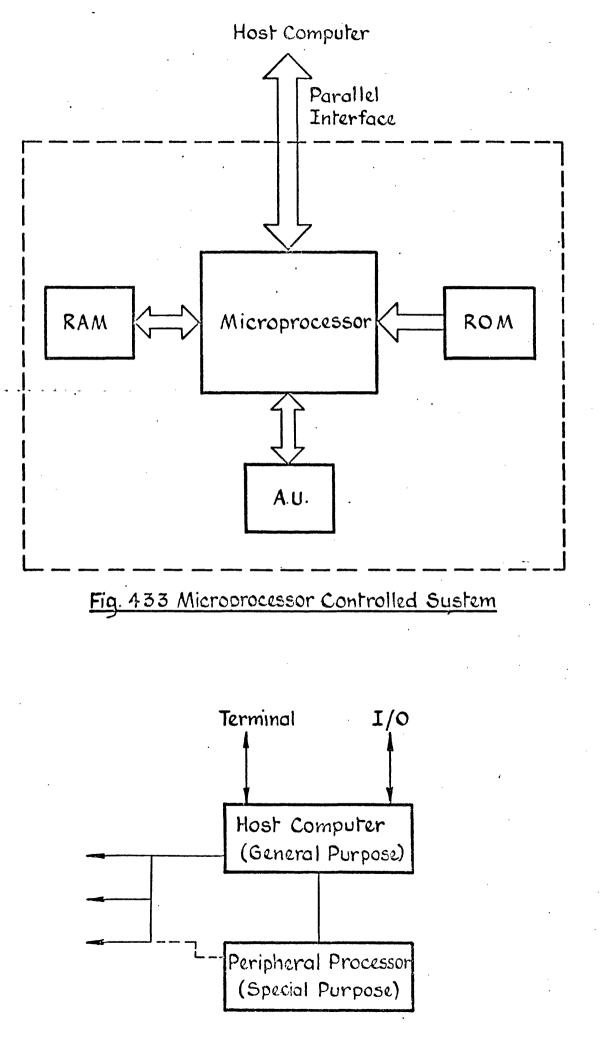

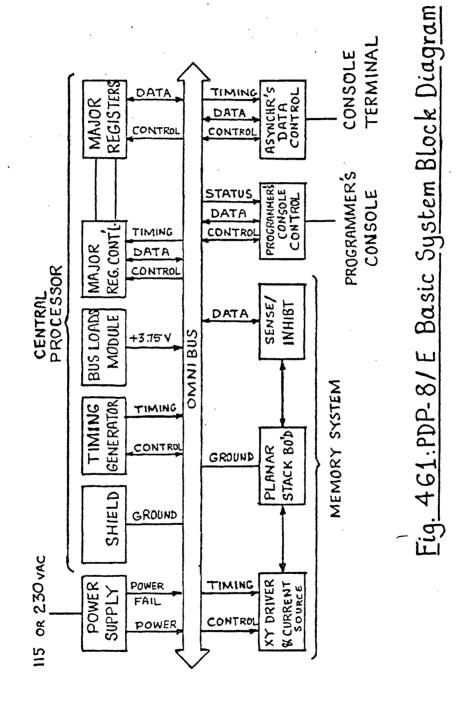

|      | 4.6.1                           | The Host machine: the Digital<br>Equipment PDP8/e | 147     |  |  |  |  |  |

|      | 4.6.2                           | 4.6.2.1 Main program: ICOSS                       | 149     |  |  |  |  |  |

|      |                                 | 4.6.2.2 Teletype group of<br>interrupts: TTYFG    | 149     |  |  |  |  |  |

|      |                                 | 4.6.2.3 Construction mode                         | 150     |  |  |  |  |  |

|      |                                 | 4.6.2.4 Running mode                              | 151     |  |  |  |  |  |

|      | 4.6.3                           | The Host computer interprocessor buffer           | 152     |  |  |  |  |  |

| 4.7  | Runnin                          | g of final system                                 | 154     |  |  |  |  |  |

| Figu | res rel                         | ating to Chapter 4                                | 156-170 |  |  |  |  |  |

| CHAP | TER FIV                         | E: APPLICATION PROBLEMS                           | 171     |  |  |  |  |  |

|      |                                 |                                                   |         |  |  |  |  |  |

| 5.1  | Introd                          | uction                                            | 171     |  |  |  |  |  |

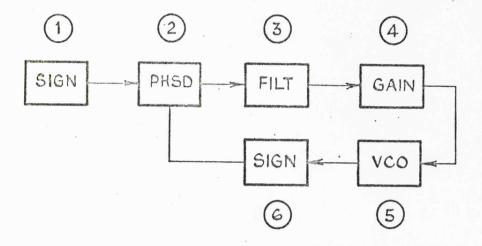

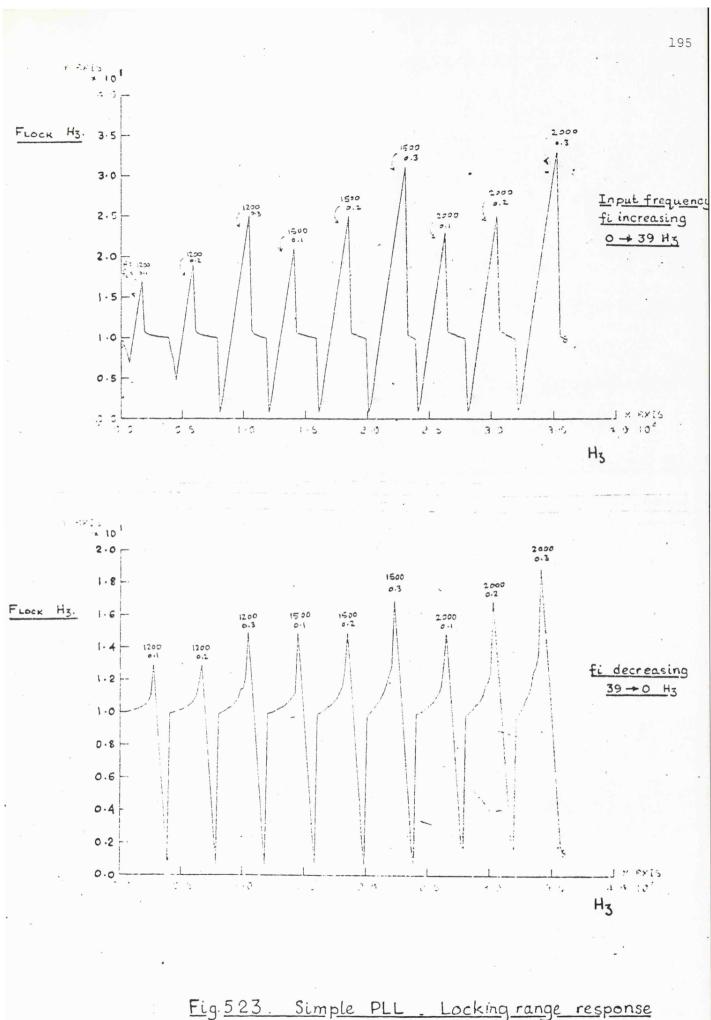

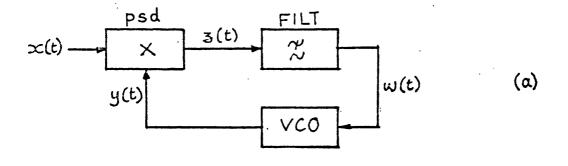

| 5.2  | Simple                          | PLL                                               | 172     |  |  |  |  |  |

|      | 5.2.1                           | Introduction                                      | 172     |  |  |  |  |  |

|      | 5.2.2                           | PLL parameters .                                  | 173     |  |  |  |  |  |

|      | 5.2.3                           | Direct approach                                   | 174     |  |  |  |  |  |

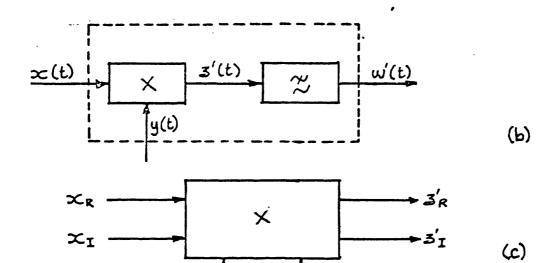

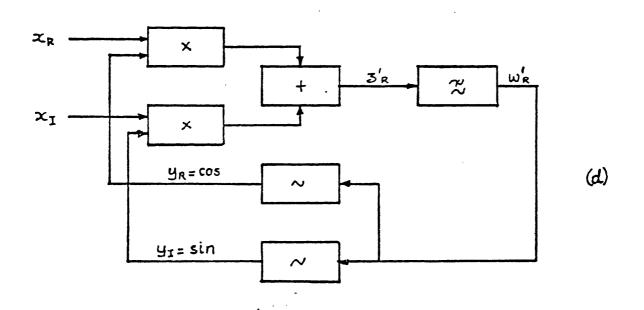

|      | 5.2.4                           | Complex-signal approach                           | 3.77    |  |  |  |  |  |

|      | 5.2.5                           | Comment                                           | T       |  |  |  |  |  |

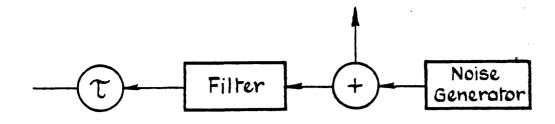

| 5.3  | Interf<br>simula                | erences in phase-lock loops, stochastic tion      | -<br>   |  |  |  |  |  |

|      | 5.3.1                           | Stochastic simulation                             |         |  |  |  |  |  |

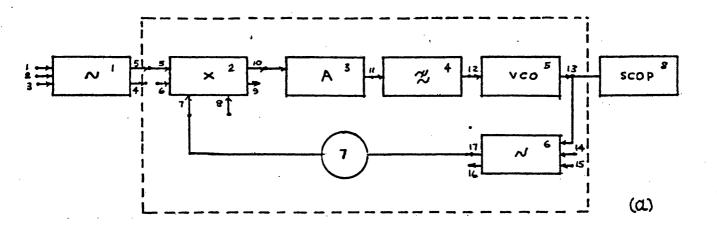

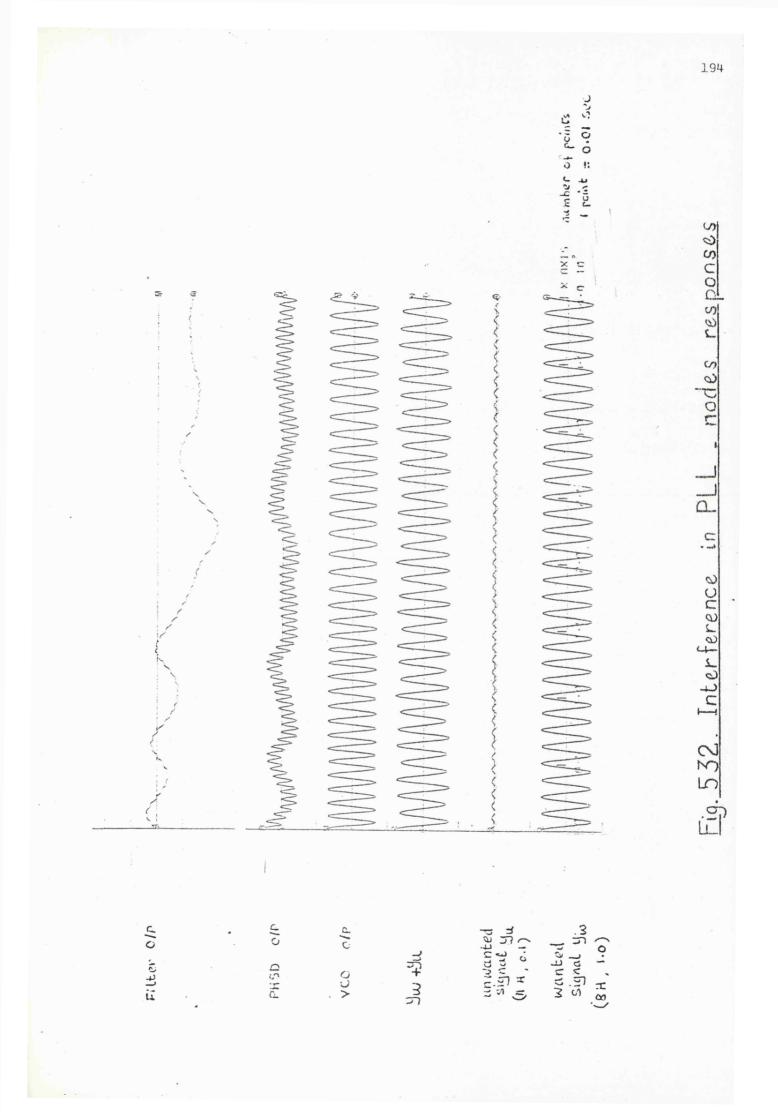

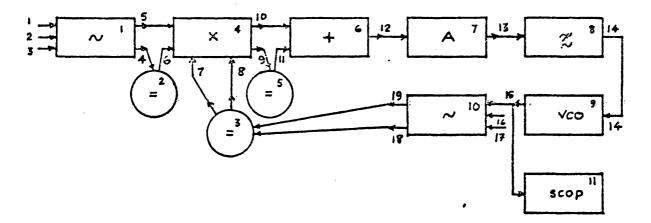

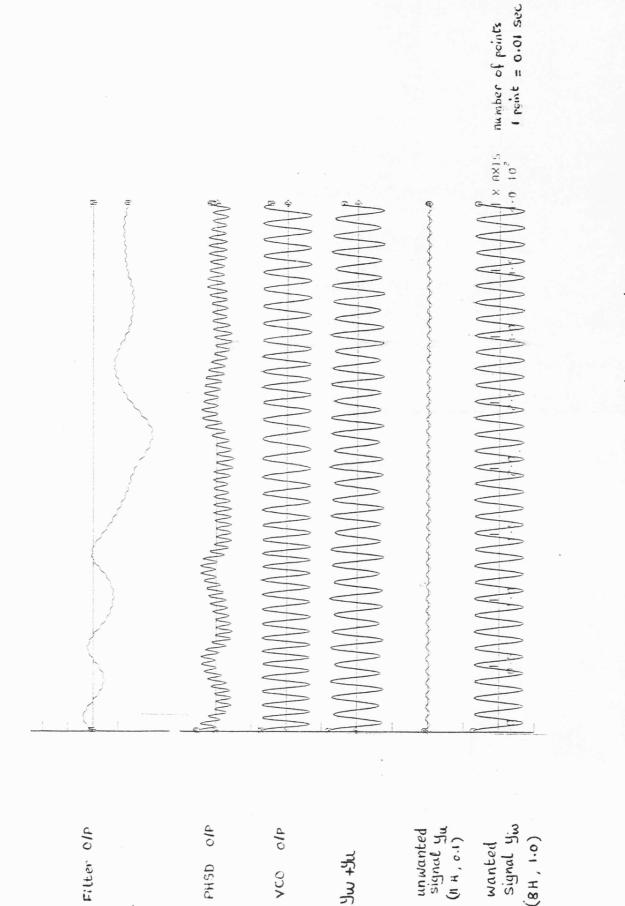

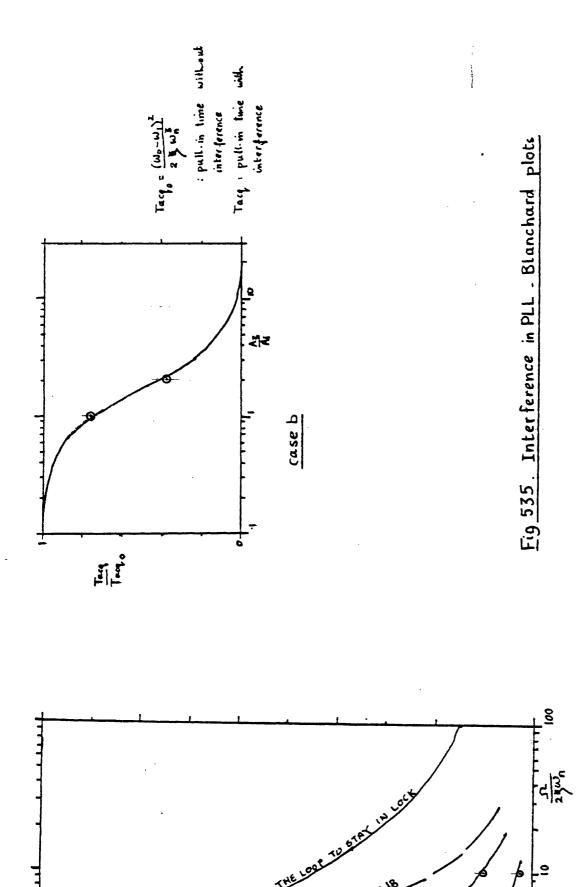

|                                  | 5.3.2 The problem of interferences in PLL | 183     |  |  |  |  |  |  |

|----------------------------------|-------------------------------------------|---------|--|--|--|--|--|--|

|                                  | 5.3.3 Problem formulation 184             |         |  |  |  |  |  |  |

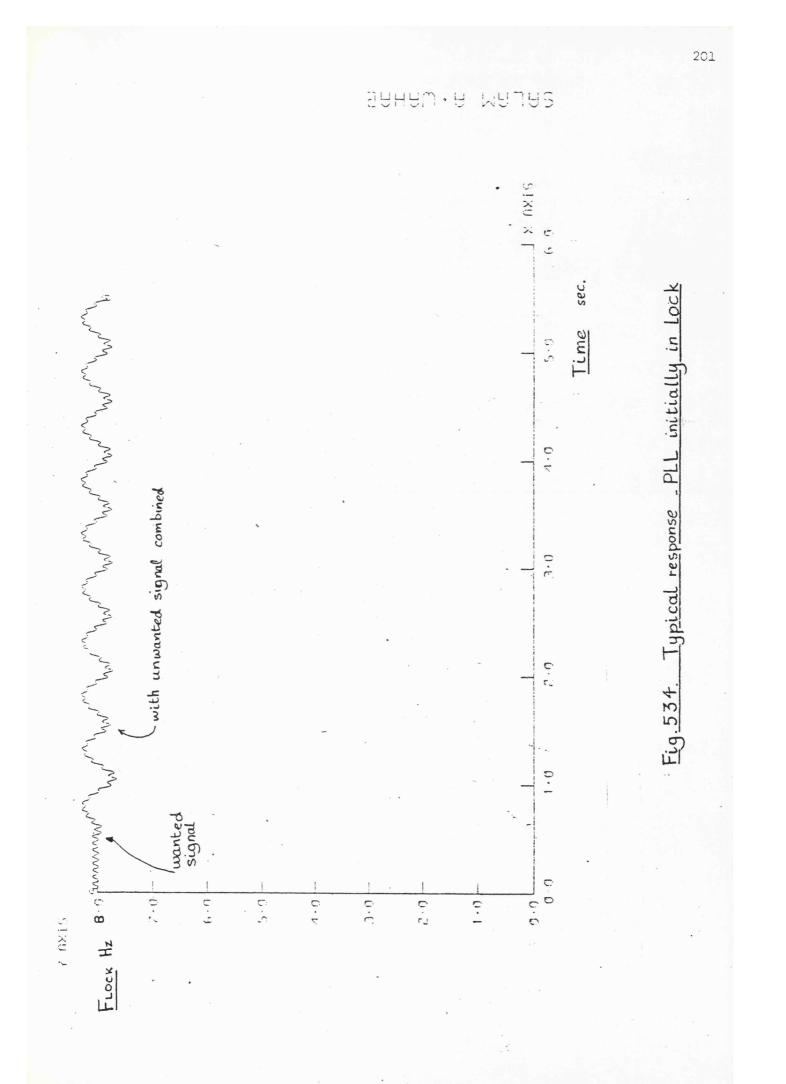

|                                  | 5.3.4 Results and comment                 | 186     |  |  |  |  |  |  |

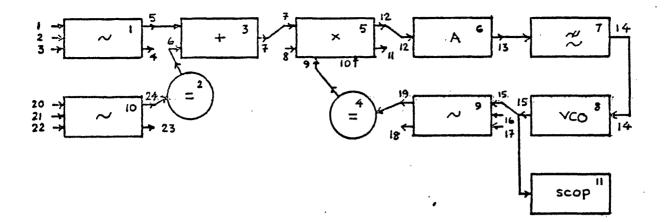

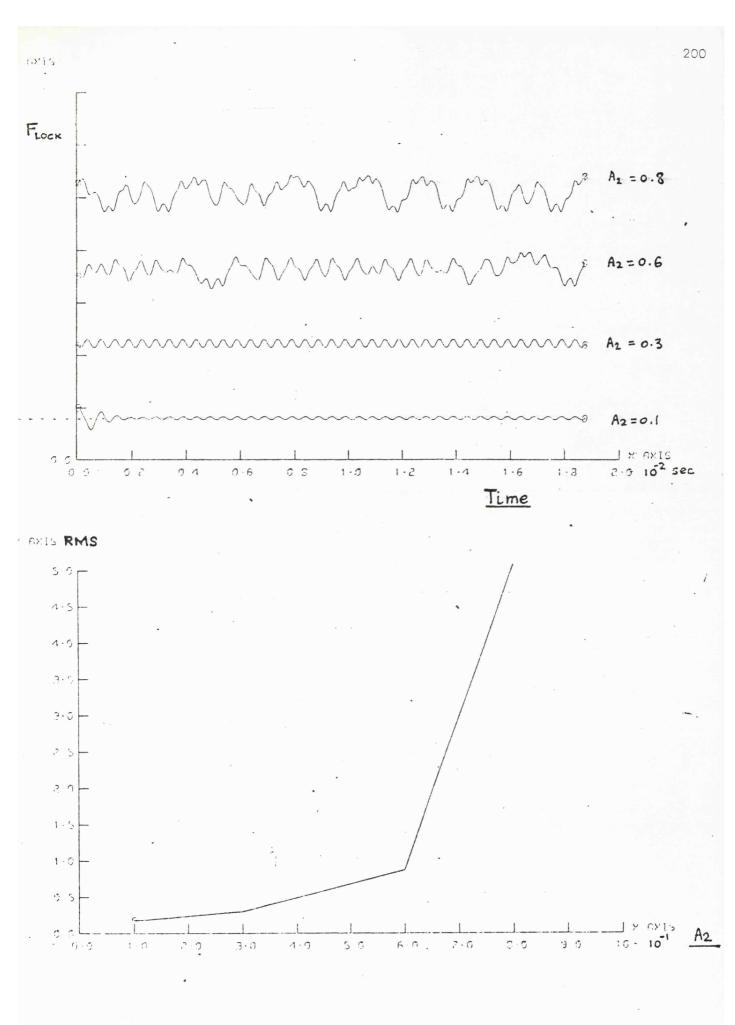

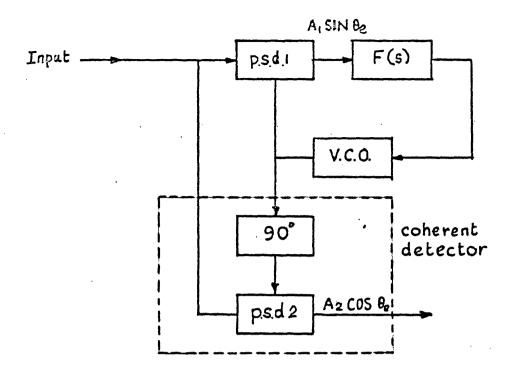

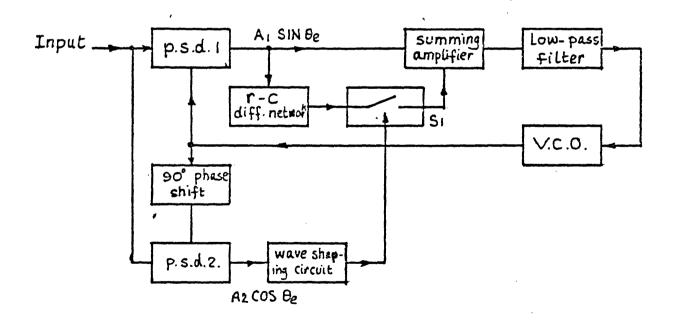

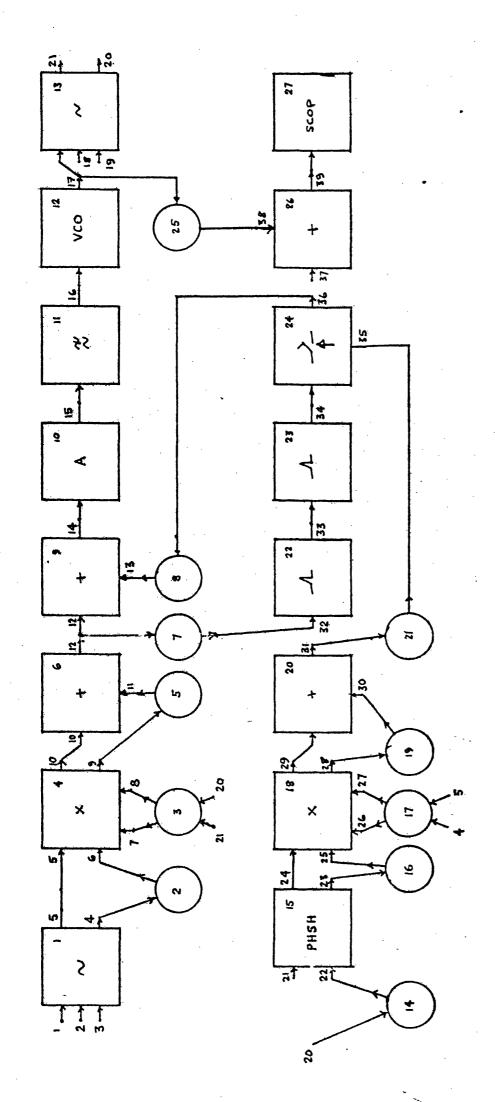

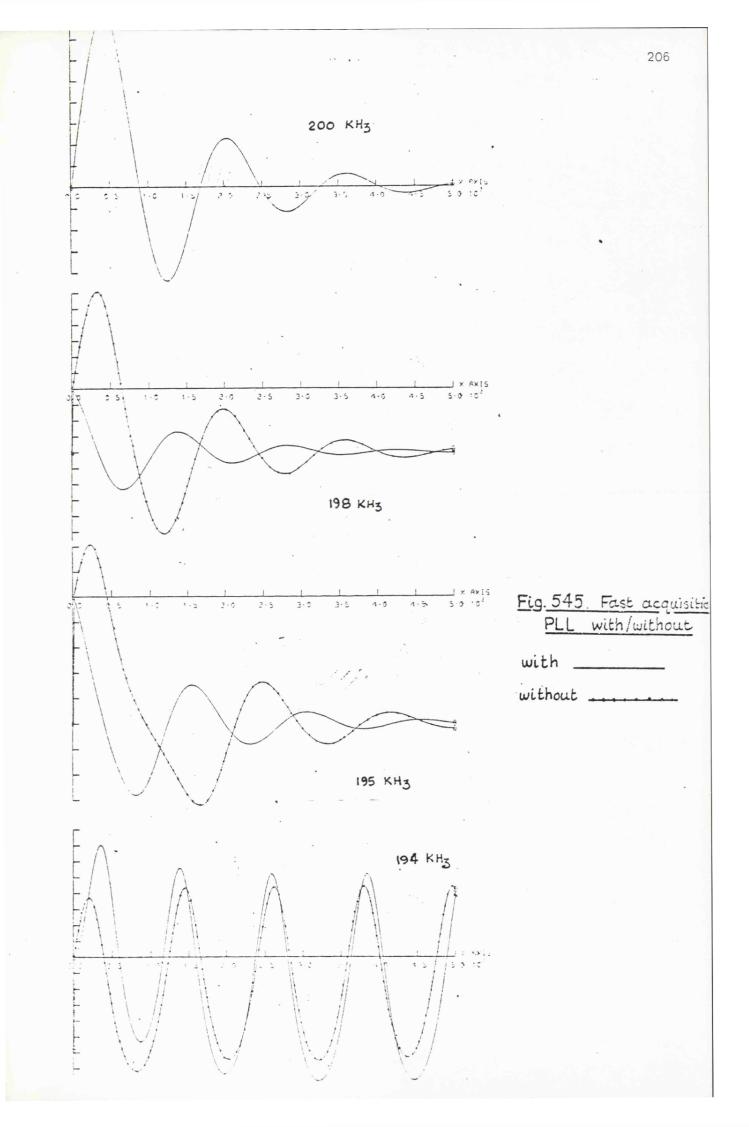

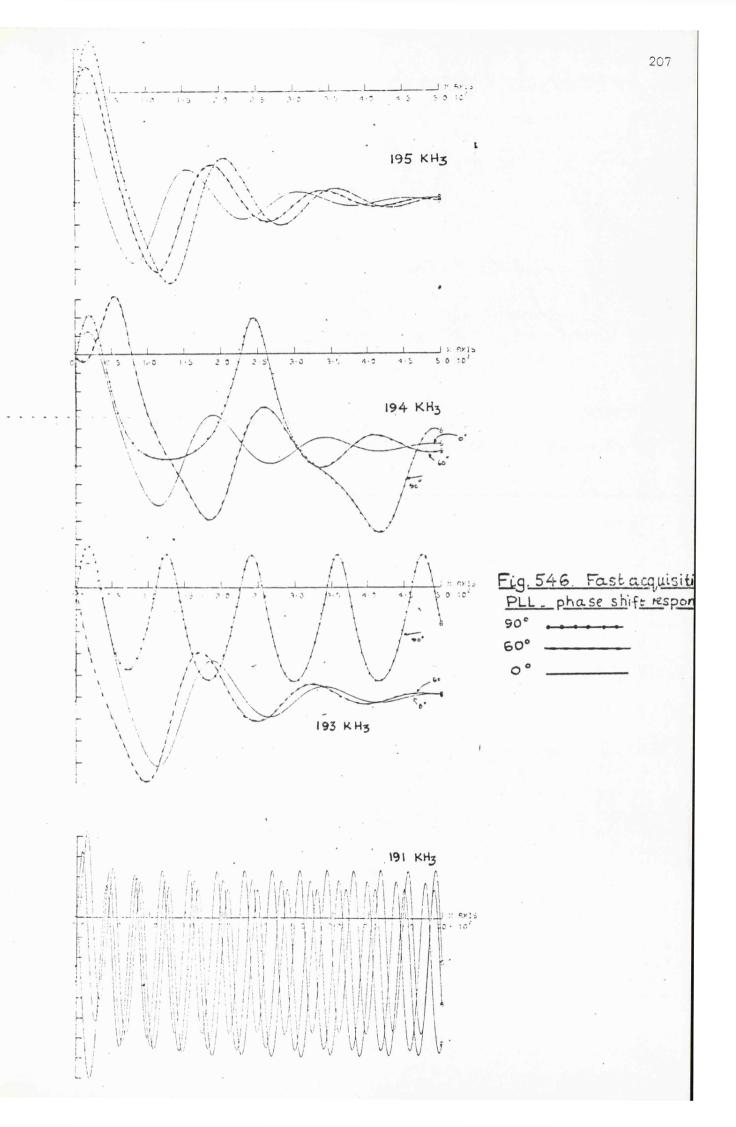

| 5.4                              | Fast acquisition PLL                      | 188     |  |  |  |  |  |  |

|                                  | 5.4.1 Description                         | 188     |  |  |  |  |  |  |

|                                  | 5.4.2 Parameters                          | 189     |  |  |  |  |  |  |

|                                  | 5.4.3 Method and measurements             | 191     |  |  |  |  |  |  |

|                                  | 5.4.4 Observations                        | 191     |  |  |  |  |  |  |

| Figu                             | res relating to Chapter 5                 | 192-207 |  |  |  |  |  |  |

| CHAP                             | TER SIX: DISCUSSION                       | 208     |  |  |  |  |  |  |

|                                  |                                           |         |  |  |  |  |  |  |

| 6.1                              |                                           |         |  |  |  |  |  |  |

|                                  | in general                                | 208     |  |  |  |  |  |  |

| 6.2                              | Discussion of ICOSS                       | 210     |  |  |  |  |  |  |

| 6.3                              | Discussion of application problems        | 221     |  |  |  |  |  |  |

| 6.4                              | Future work                               | 224     |  |  |  |  |  |  |

| 6.5                              | Conclusion                                | 232     |  |  |  |  |  |  |

| Figures relating to Chapter 6 23 |                                           |         |  |  |  |  |  |  |

|                                  | ACKNOWLEDGEMENTS                          | 235     |  |  |  |  |  |  |

|                                  |                                           | 236     |  |  |  |  |  |  |

|                                  | REFERENCES                                | 230     |  |  |  |  |  |  |

|                                  |                                           |         |  |  |  |  |  |  |

## APPENDICES

| A. | Comparison table between six important general-                                       |     |

|----|---------------------------------------------------------------------------------------|-----|

|    | purpose simulators.                                                                   | 243 |

| в. | The modules of the Loop group of interrupts<br>as implemented by the prototype ICOSS. | 246 |

| c. | Output display routines of the flag group as implemented by the prototype ICOSS.      | 251 |

| D. | Subroutines and their description of the prototype ICOSS.                             | 255 |

| E. | Tables, stacks, arrays and matrices.                                                  | 260 |

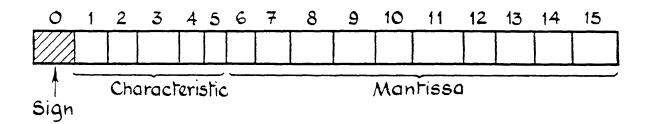

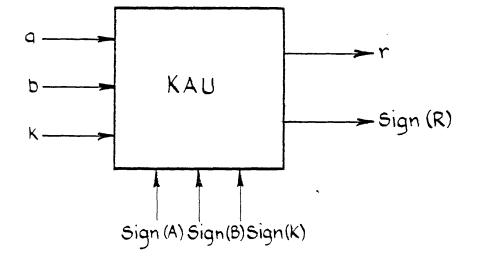

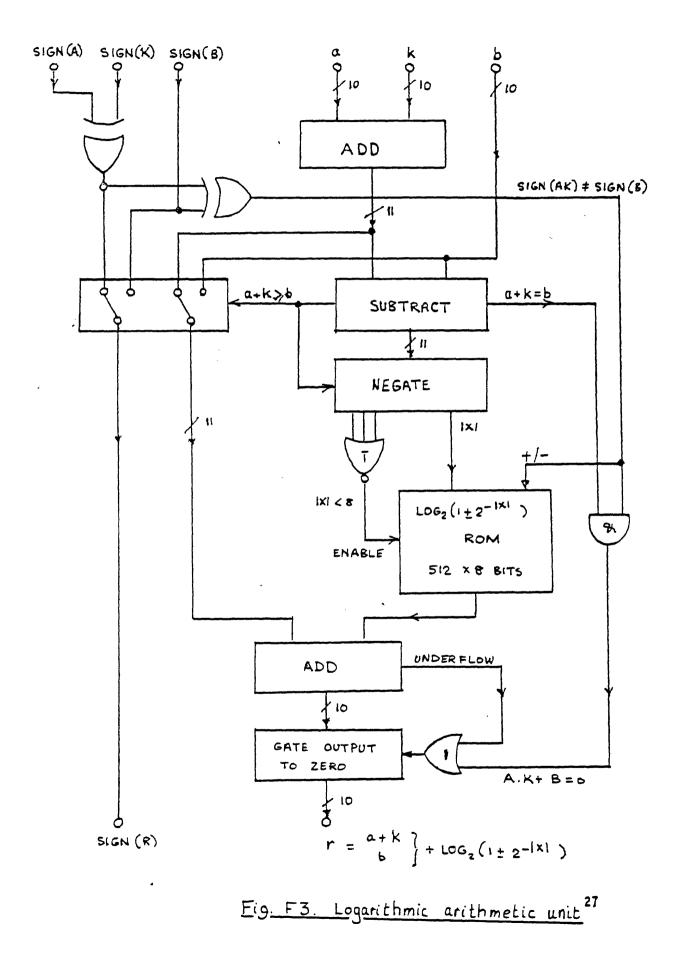

| F. | Logarithmic arithmetic unit.                                                          | 264 |

| G. | Procedure for adding a new LOOP/TTYFG/FLAG                                            | -   |

|    | interrupt.                                                                            | 270 |

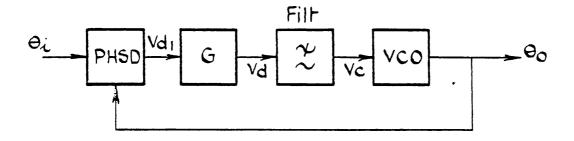

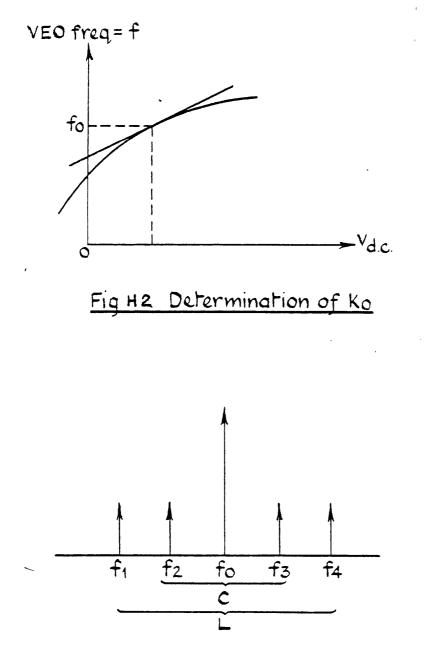

| H. | Phase-lock loop.                                                                      | 276 |

| Ί. | Computer run times                                                                    | 282 |

|    | (viii)                                                                                |     |

CHAPTER 1

#### INTRODUCTION

#### 1.1 COMMUNICATION SYSTEMS

## 1.1.1 Definition and Characteristic 35

Communication system design involves a complex interplay between the hazardous transmission environment and the skilful use of modulation techniques and electronic hardware. Many associated problems have successfully been solved by the traditional methods of experience and intuitive understanding, but it has always been clear that better judgements could be made and more realistic predictions of performance constructed if readily usable analytical techniques were available to the communication system designer. General analytical solutions are only available for the simplest of cases however, because of the general difficulties of the communication environment. Communication theory relates signalling speed, bandwidth and noise, which assumes well-behaved but non-realisable channel frequency characteristics; and the extension of these principles to real life is left to intuition. Nonlinear circuit elements such as blankers and chippers, leave a certain amount of vagueness in receiver calculations, particularly when allied with a variety of modulation styles. Communication filters are generally of high order,

typically fifth or greater, which, if several are included in one analysis, lead to complicated equations. Filter characteristics are consequently chosen for the convenience of their analytical description, rather than their suitability for the job in hand, and although optimum filters are capable of being designed for specific applications, it is difficult to predict how the filter will behave when conditions have altered from those assumed for the optimisation.

#### 1.1.2 Areas of problems in communication systems<sup>9</sup>

The areas of problems in communication systems are wide and ever increasing, but for the present discussion purposes, the following main areas of problems are defined as the major communication problems.

- (a) Stochastic: long averaging times, or large ensembles involved, eg phase jitter and digit synchronisation studies, frequency stability studies.

- (b) Signal analysis problems: long averaging times, long records, eg probability distribution generation, correlation function estimation, power and energy density spectra: P(f) and E(f) etc, for real signals, eg speech.

- (c) Interactive or real time problems: long data record involved, eg optimisation studies, of filter bandwidth.

- (d) Deterministic problems: short computation times

involved, eg transient studies such as "speed of lock" of a phase-lock receiver, distortion tests.

#### 1.2 SIMULATION

#### 1.2.1 System Studies

Analytical expertise in communication systems is both desirable and difficult to acquire. The alternative to exact analysis is to assemble the proposed system and investigate its behaviour experimentally; such investigations have been carried out since the science of electronics began. While providing some of the answers, this approach is expensive and also leaves many unsatisfied queries. What is really happening inside that mixer circuit? How would the system behave with slightly different filters? How sensitive is the system to circuit parameter changes? Computer simulation of communication may be the solution to these queries. But before introducing that, a brief introduction to the system simulation in general.

# 1.2.2 System Simulation 12

The need for the simulation of a system may arise in several ways. An analytical solution or approximation solution to a problem may have been found and some form of corroboration be required. In some cases this is most easily obtained from a hardware model, but with more complex systems, computer simulation may be a more attractive

proposition from the points of view of time, accuracy and economy. In computer simulation parameters can be modified, variables monitored, curve fitting and regression analysis performed, and statistics of the system performance obtained.

A simulation may range from a pure numerical calculation from analytical results, to partial simulation where some parts of the system are modelled analytically and the rest simulated, to a full simulation in which every element in the system is modelled and simulated. In the interests of efficiency it is usually desirable to describe as many parts of the system as possible by analytical expressions.

A simulation may be run serially in time, where the response at each instant of time is computed recursively from the state of the system and the inputs at that time. Alternatively, it may be possible to compute the overall time response in parallel, usually by transform techniques. The parallel simulation can be faster, but is difficult to implement if there are feedback paths in the system and may require a large amount of storage to simultaneously store the values of variables at every instant of time.

The use of digital computers for the simulation of analogue system is a wide field, and over recent years a large amount of literature has been published. The literature concerning simulation systems tends to fall into several main areas<sup>4</sup>:

- (\*) Discrete simulation: concerning discrete change simulation; eg queueing problem.

- (\*) Simulation designed around a particular problem: eg FFT package.

- (\*) Continuous (analogue) simulation methods: the importance of these methods is in their historical development, their organisation and the structure of their basic elements.

- (\*) Existing methods for the simulation of communication system: these are standard packages, see later.

#### 1.2.3 Communication system simulation

Simulation of communication system modules can take place either in terms of frequency or time domain. The difference between the two lies in the manner in which filters are described. A frequency-domain simulator specifies filters in terms of their frequency response, thus enabling ideal filters to be included. In a timedomain simulation, filters would be described through difference equations operating on a succession of signal time-samples. Both techniques suffer from the usual troubles introduced by signal sampling, limited frequency range and aliasing, but their time domain performance differs widely. The input to each transformation in the frequency-domain simulation is N time samples and the corresponding frequency scale has only N discrete points. The time scale is unlimited in the case of the time-domain

simulation, and the frequency scale is continuous up to the sampling frequency.

Communication system simulation can be classified into two types:

- (a) Special-purpose, in which the simulation is specific to a particular problem: most simulation for laboratory and research work falls within this type. The engineer, who will write the special-purpose simulation, must be a skilled programmer and sufficiently familiar with the mechanics of simulation to describe adequately his problem in terms which allow accurate simulation.

- (b) General-purpose: digital simulation allows a general approach to be made, where the programming effort is applied initially to construct in software a set of processing modules and some kind of data structure, which allows them to be strung together and signals and effective measuring instruments applied. Some familiarity with the basic concepts of programming will inevitably be required (although the tendency is to minimise them as much as possible), and also an understanding of the principles of the particular simulator. This type of simulation, the general purpose, will be adopted thereafter.

To simulate a given communication system, the block diagram of the system is constructed using processing modules (eg amplifiers, filters etc , ie having different fundamental functions); and then a certain form of connection of the blocks in the diagram is written in terms of the functions of the blocks and certain parameters. If the block diagram and the expression of these connections are fed as the source program into the simulation, then the complier in the simulation system generates the program written in the computer language, say Fortran IV, for the simulation of the given system. 1.3 THESIS

#### 1.3.1 Designing a new simulator, ICOSS

There are a large number of communication system simulation packages based on one technique or the other to perform a particular task or tackle one or more areas of communication system problems. A large number of papers and literature cover this subject as will be shown in the next chapter. However, communication system simulation does not stop at any particular boundary, but it progresses and becomes more and more ambitious. With the introduction of fast microprocessor and minicomputer systems, a new approach to communication system simulation is therefore needed in order to achieve the most ambitious requirements. A time domain simulator: the <u>Interactive</u> <u>Communication System Simulator</u> (ICOSS) is to be designed

with this background in mind. Its main objectives are: being able to change the simulated model control parameters while in the running mode, being able to edit its module structure (block diagram), be portable, and operate

interactively for real-time simulation. Also to provide the communication engineer with a bench tool which will prove vital in research and development laboratories.

In the pursuit of designing a new communication system simulator, the following procedure is followed in this thesis. A survey of communication system simulators is made in order to present the current state of the subject. They are then classified into a number of areas according to their principle of operation, type of problem they are capable of solving, and system set-up (ie computer capability and supporting equipment available). A summary of the objectives in the design of the new simulator are formulated, which must satisfy the ambitious requirements of a typical user as much as possible. A number of options are available to implement those objectives: choice of programming language, generality of application, domain (frequency or time) etc. Finally, once the new simulator is implemented, its credibility is examined by testing its functions in solving the type of problems it is designed for.

#### 1.3.2 Outlook and modifications

The intention of this work is not only to design and implement a new digital communication system simulator of unique characteristics, but to lay the foundation for simulation system with wider applications as outlined earlier. However, the inherent problem of real time simulation in

which fast processing is essential, can be overcome by either large or fast computer system, or alternatively processing parts of the simulation by fast dedicated processing working in conjunction with the mini or medium size computer. Although the objectives of the prototype version of ICOSS are achieved, the overall and final version of ICOSS system, running in real-time were not fully implemented, because of either the limitation of time or facilities. Therefore, there is still further work to be done, which will be outlined in Chapter 6.

#### 1.3.3 Application

The credibility of any new simulator is measured by its fulfillment of the objectives laid in the design, as well as its power in solving the type of problems it is designed for. Since one of the main features of timedomain simulators is the ability to simulate communication systems containing feedback links, phase-lock loop performance and the problems associated with it are an ideal testing case, which will be fully utilised.

#### SIMULATION TECHNIQUES AND SIMULATORS

#### 2.1 INTRODUCTION

#### 2.1.1 Historical Background

Simulation is the building of a model of a device or system<sup>(38)</sup>. Models are useful in that they provide a means of testing ideas and designs without the complication or expense of building a prototype system; and modelling is widely accepted in engineering. In some fields the models are physical devices, such as small scale versions of the actual system. When a system can be defined mathematically, modelling can proceed from a conceptual view point and the model need not be practically realisable. Such is the type of simulation that can be used for communication or signal processing systems.

Computer simulation of systems in general is a wide subject, each case influenced by the limits of computer capability and particular problem at hand, and there are numerous articles and books on the subject<sup>\*</sup>. Limiting the discussion to communication (or signal processing) system simulations, there are a number of approaches, depending on:

\* Refs 9-12, 15,16,21,24-26,29,30,35,38,40,41,48

- (\*) The simulated system itself and the degree of accuracy required of the simulator, as well as the degree of similarity with the actual system.

- (\*) The computer at hand and its capabilities (memory size, execution time etc).

- (\*) The degree of generality required by the simulator, ie will the simulator be used in a different environment or will it only be used for one particular problem.

- (\*) Continuous time or discrete time systems.

Historically, signal processing system (SPS) simulations started with analogue computers <sup>38</sup>, in which the system is modelled by differential equations, in which integrators, adders etc make up the system, and the problems can be solved quite easily many times over, using simple configurations. There are big advantages in analogue computer simulations, mainly:

- (\*) Fast speed of action, since there is only hardware involved, and the results are obtained immediately.

- (\*) Simple technique in solving certain difficult problems.

- (\*) Easily used by engineers.

However, there are disadvantages as well, mainly:

(\*) Difficult to set up for large problems.

- (\*) Variables must be scaled.

- (\*) Non-linear operations: such as multipliers, function generators are possible but have limited dynamic range.

- (\*) Only continuous time system, whose theoretical analysis is based on the solution of differential equations, can be simulated by this method; ie discrete time systems cannot be simulated.

- (\*) Limited in order of system, by number of integrators, ...

With progress toward developing digital computers, the analogue computers started to lose their predominance in the field of SPS simulation. Although the digital computer is flexible and capable of being programmed for many problems, such as solving discrete-time systems, whose analysis is based on difference equations (see later), yet the execution time is increased considerably as compared with analogue computer simulation <sup>16</sup>, vis lo0:1 ratio.

In order to overcome the time limit, hybrid computers were introduced in to combine the two types (analogue/digital) and obtain the advantages of both. With the simulation techniques of communication systems becoming more and more ambitious, the hybrid computers have been replaced by "Giant" computers  $^{16}$ , but the latter solution has proved to be rather expensive for the vast majority of applications.<sup>16</sup> The ultimate solution, with real-time online system simulations in mind, is to combine a digital computer of a medium size, with mini-computer network with storage and interfacing operated separately. In the coming sections a development to that end is described.

#### 2.1.2 Simulation Techniques

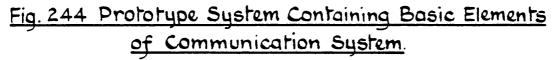

In order to simulate a system, one must have a clear understanding of the overall content of the communication system itself, as well as what is required from the simulation. In signal processing system simulation, the system can be looked at as a group of sections and subsections interlinked together. These can be summarised briefly as follows, for the example system shown in Fig 2.1.1:

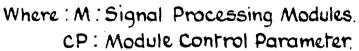

- (a) Signal processing modules (M): eg signal generators, filters etc.To simulate those modules, the following parameters have to be determined.

- (i) Module internal and external coefficients,ie local and global (see Chapter 3).

- (ii) Inputs/outputs node relationship of the module.

- (b) The state variable of the system.

- (c) The running mode (procedure).

- (d) Output signal measurements and evaluations.

The common denominator in practically all simulators is to present the signal processing system as near to the physical system as possible, and then utilising it in situation which would be impractical or difficult in the real system. The emphasis, therefore, is how simple the simulator appears to the user, in terms of familiarity to him as a bench tool, rather than learning how the simulator has been constructed. This is in contrast to the earlier work of signal processing system simulation<sup>26</sup>.

The simulation of the above signal processing system can take any of the following forms depending on the application and tests required; these are summarised as:

- 1. Frequency domain based simulation.

- 2. Time domain based simulation.

- 3. On-line operation.

- 4. Off-line operation.

Looking through the development of signal processing system simulators <sup>(\*)</sup>, which are mainly based on block diagram simulation (see below), one can see clearly the trend moving from being heavily dependent on programming technique, with specialist approach on the off-line basis, to that which is closer to the real physical situation, the on-line working basis; especially with the introduction of high speed computers.

#### 2.1.3 The Block Diagram Technique

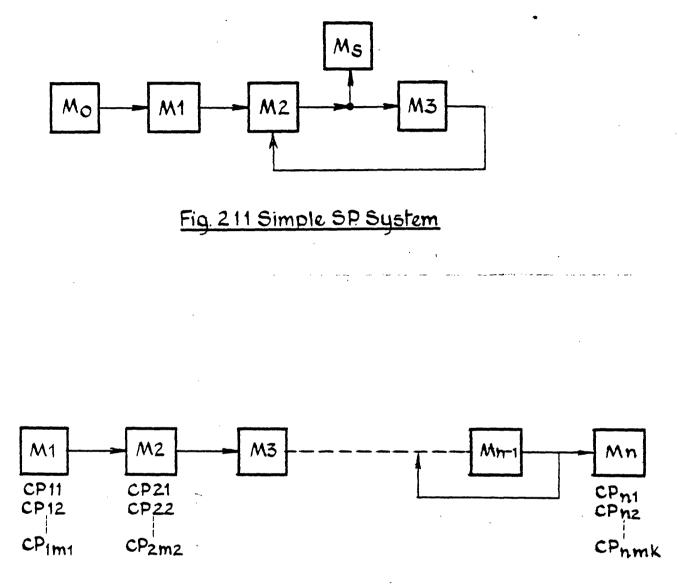

There are numerous simulators basing their analysis on the so-called block diagram technique<sup>(\*)</sup>. It is so called because the simulation is based on the ordinary block diagram representation of a system. For this reason, this technique is most suited to the simulation of communication systems, and shall be adopted for the present work. The main feature of this technique and method of implementation is briefly introduced at this stage, and a more rigorous examination will be given in later sections. The communication system is completely defined as cascaded blocks or units representing the signal processing modules (MO, MI, etc Fig 2.1.1), with the necessary interconnections for the feedback or crossover paths. Hence when simulating such a simple system, the following items have to be treated:

- (a) The signal processing modules MO, Ml etc: The transfer function of each module must be clearly defined, and a subroutine is created in the usual way.

- (b) The Local control parameters of those modules, such as the cut-off frequency of a digital filter, or the gain of an amplifier etc.

- (c) Input/output nodes of each module (multiple levels).

- (d) The inter-link between the modules (input/output nodes connections), which may take number of forms (+).

<sup>\*</sup> Refs 10,11,16,21,25,26,35,46

<sup>+</sup> Refs 11,16,35,41

They have to be uniquely defined; but once adopted they have to be precisely followed.

- (e) The "global" control parameters, ie the parameters which control more than one module, such as a sampling frequency of a digital communication simulation.

- (f) The type of output device which evaluates the signal at any node within the system, such as the measurement of a mean value of a signal etc.

There are three distinct stages which constitute the simulating procedure of this block diagram technique, they are:

1. The construction stage: in which the communication system is defined and its parameters are supplied to the simulator. This is implemented in various ways depending on the designer<sup>(\*)</sup>. However, it should be implemented in as simple a way as possible for the reason is that the user may have limited or no programming knowledge or experience at all <sup>15,35</sup>. Appendix A shows some samples of implementation of a number of important simulators. During this stage also a number of tables, strings and stacks are generated in order to set the simulator for the following stage.

2. The running stage: in which the incoming signal is processed through the system in orderly manner. This requires efficient storage arrangement of various parameters needed for signal processing as well as searching procedure with minimum elapsed time.

3. The output stage: in which the output signal at any node of interest is examined in order to evaluate the behaviour of the simulated communication system.

#### 2.1.4 In this Chapter

The signal processing system techniques are discussed in more detail and presented as the subject developed historically. The limitation and misgiving of the various techniques mentioned will be discussed, giving the lead to a new approach, which will be called ICOSS, the Intensive Communication System Simulator. The latter will be introduced only briefly, since it will be fully described in Chapter 3.

#### 2.2 IMPLEMENTATION: USER SIDE:

One of the big problems in communication system simulations is how to present the simulated system in simple terms recognisable by a user with limited or no programming experience. Various approaches were made to overcome this problem, which can be found in literature<sup>(\*)</sup>. These can be grouped according to application, machines and period of implementations. However there are two main ways of presenting the simulated communication system to

`the signal processing simulators; they are:

- (a) The block diagram method: which is commonly used and most suited for digital computer simulators.

- (b) The differential equations method: which is implemented for analogue (operational)computer oriented simulators.

In the following, a brief description of both methods and their limitations as implemented by well-known simulators is given, and the ideal solution is forecast. Typical examples are presented in Appendix A.

#### 2.2.1 Typical communication system

The object is to translate the representation of the typical communication system shown in Fig 2.2.1 to a set of computer instructions. The translation depends mainly on the type of simulation and computer in use. The discussion will be restricted to two types only, the analogue computer, and the digital computer, since any other type will be the combination of the two. The digital-microcomputer network will be mentioned in later chapters.

- (a) The analogue computer oriented simulators: The differential equation method.The procedure is summarised as follows:

- (i) The complete system is defined as a set of differential equations, and their elements (integrators, delay, adders etc), ie the conversion is from block diagram of the system to differential equations.

- (ii) The simulation is implemented by an orderly connection of these elements.

Generally, a patching panel is needed for the analogue computer, which can be programmed in the case of hybrid computer.

(b) The digital computers oriented simulators: The block diagram method. Historically BLODI<sup>26</sup> was one of the early simulators in which BLODI program accepts input program written in BLODI language. The latter corresponds closely to an engineer's block diagram of a circuit. The input code consists essentially of designating the connectivity of a number of boxes drawn from an alphabet of about 30 types. The object program produced by BLODI consists of 3 parts

- (i) the prefix which sets up the logic for the main loop

- (ii) the main loop, which is executed once for each sample processed

- (iii) the suffix, which causes the main loop to be repeated the proper number of times, empties output buffers, fills input buffers etc.

Example: for system shown in Figure 2.2.2

| line | 1 | : | SUM   | ADR | BUFF                                         |

|------|---|---|-------|-----|----------------------------------------------|

| line | 2 | : | BUFF  | FLT | a <sub>1</sub> ,a <sub>2</sub> parameters of |

|      |   |   |       | :   | filters, DELAY                               |

| line | 3 | : | DELAY | DEL | ••••                                         |

| etc  |   |   |       |     |                                              |

In later years the BLODI was modified to become  $BLODIB^{21}$ . The language of the latter is designed for programming sample-data system which may be represented either in block diagram form <u>OR</u> in the mathematical representation of the Z-transform calculus. Therefore, although it is basically for sample-data system, it may be used for sample-data approximation to continuous (analogue) systems. The procedure in simulating a system is summarised as follows:

- (i) the determination of an appropriate discrete representation for the system to be studied

- (ii) the preparation and compilation of a BLODIB computer program which causes the computer to perform the same operations as would be performed by the actual system

- (iii) the digitalisation of a real speech signal for processing by the computer,

There are 3 ways of representing the system

- (i) by MACROS or SUPER: defines new type of block(for basic type available)

- (ii) by SSUBR: which allows block of BLODIB coding to be used as an external "module" to a main BLODIB. But SSUBR are coded and compiled separately; then loaded for use by the main program.

- (iii) by SUBR, which permits coding an entire simulation so that it can be controlled by a main or "executive" program.

Example:

Inputs Control Parameters ADB MACRO I1,I2,I3,I4 A1,A0,B1,B2 IN MIP 1,DEF . . END

Another type of presentation was made by another group of simulators, and WASP<sup>11</sup> is a typical example. In this a fixed structure is established for the analysis of waveforms and spectra in the communication systems and then building on this framework a library of electronic or electromechanical modules of the type needed for the specific application. The procedure for WASP simulation is as follows:

- (i) Draw communication system as block diagram(each block must be one of the library modules)

- (ii) Number each node and decide on the node for the output device connection

- - -

(iii) Input data

|                          | comment or remark |          |           |                                                          |               |                            |   |  |                                                                                                       |                                                | X:module number, whose output is | required to be tested | / Y:type of output device required |

|--------------------------|-------------------|----------|-----------|----------------------------------------------------------|---------------|----------------------------|---|--|-------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------|-----------------------|------------------------------------|

| rary                     |                   |          |           |                                                          |               |                            |   |  |                                                                                                       |                                                | ~                                |                       | ~                                  |

| as it appears in library | module 2,         | module n | Parameter | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | t<br>1 -<br>1 |                            |   |  | 1<br>3<br>5<br>5<br>5<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 | 3<br>3<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |                                  |                       |                                    |

| module name              | module 1,         |          | module l  | 1<br>1<br>1<br>1<br>1<br>1<br>1                          | module 2      | 2<br>8<br>8<br>8<br>8<br>8 | • |  | module n                                                                                              | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1      | Title                            |                       |                                    |

| Example:                 | u                 |          | Т         |                                                          | 2             |                            |   |  | u                                                                                                     |                                                | ХҮ                               |                       |                                    |

.

/ Title: title on graph or results

(if applicable)

Finally, yet another approach which is relevant to this discussion, is the one made by SYSTID  $^{16}$ . The latter is a time domain simulator which relies on cards for the data input and each group of cards represents a communication system. Its language processor translates the simple English language user command supplied on cards, and links element descriptions and topology into the Fortran code necessary to establish a digital filter equivalent of each link. The data structure of this system is as shown in Fig 2.2.3.

Example: A model which squares a signal:

| MODE 1 | Ø | Example           |

|--------|---|-------------------|

| INPUT  | Ø | ≸ * ≸ Ø OUTPUT    |

| INPUT  | Ø | SIN (\$) Ø NODE 1 |

| END    | ø |                   |

#### 2.2.2 Limitations

There are many ways of simulating communication systems other than the ones mentioned above, but they all have some limitation. Some of these limitations are summarised below:

- Batch operated rather than interactive, so that data representing the communication system block diagram is supplied to the computer separately for each run.

- (ii) Modification of system structure once supplied to the simulator is difficult to achieve

- (iii) Variation of signal processing modules parameters is not direct, if at all

- (iv) The simulated system is not clearly related to the original communication system block diagram. Hence the user is not able to look upon the simulator as another bench tool identical to the simulated communication system.

#### 2.2.3 Projection

In order to achieve as near an ideal solution of this problem as possible, the following must be fulfilled:

- (i) Overcome the limitation of (2.2.2) above

- (ii) Establish a peripheral device on which the simulated communication system is drawn on it directly, and the user could modify the system

readily on the peripheral device. This will eliminate completely the difficulty of transforming the electrical block diagram onto the set rules of the simulator.

It is hoped that ICOSS will fulfil these conditions when it is finally completed.

#### 2.3 IMPLEMENTATION: COMPUTER SIDE

In the design of an efficient general purpose signal processing simulator, the designer has to aim for the following essential targets:

- (\*) Efficient utilisation of computer memory, speed of execution (cycle time), and computer facilities.

- (\*) Efficient programming without ambiguity and with minimum redundancy of occupied memory.

- (\*) Program the simulator to make it portable.

- (\*) Program routines to represent a complete set of general SPS modules.

Thence, in the design of SPS simulator on a digital computer, the following detailed points must be carefully considered:

1. Structured programming: in which the various sub-

routines which make up the simulator are interconnected without nesting and the overall program of the simulator can be modified by adding or taking away subroutines with minimum complication.

- 2. The use of simulation languages: presenting a simulator to a user in a language easy to understand, means creating a new computer "language". Since there exist nowadays communication system simulation language such as WASP<sup>11</sup> and CSSL<sup>3</sup>, then it will be beneficial to utilise such languages, if they are general enough.

- 3. The choice of a program language: since there are a number of computer languages such as Fortran, Algol, etc, then the choice must be made for a suitable language, eg for engineering application Fortran IV is most suitable and provides portability. It might be desirable to use assembler language or machine code in some part of the simulator program, in which time is of prime importance (see Chapter 5).

- 4. Signal processing modules transfer functions: must represent a fundamental set, enabling all common communication systems to be simulated.

- 5. Output devices can take many forms:one form is to have a real hardware peripheral or oscilloscope in the case of real-time operation. Or the output device can be simulated, which is the case in the majority of situations; eg RMS meter etc.

- Library construction: for signal processing modules,

data base (parameters, state variables, pointers etc).

Efficient arrangement is of vital importance in order to utilise the limited computer memory economically. In the course of running the simulator, there will be samples, pointers, state variables, links etc which have to be stored in stacks and there will be a relationship between the contents of one stack with another, which will be consulted during the process of execution. Therefore an efficient method in either space, or speed, ie access time depending on the simulation whether real time, stochastic or off-line simulation, must be devised.

- 7. Search procedure of tables (library): Serial or Hash<sup>39</sup> techniques depending on the situation, has to be efficient, since choosing the right technique means minimising the execution time, which is of vital importance in the on-line and stochastic simulation, in which large averaging times or large ensembles are involved such as fading problems (error rates studies) multi-channel interference problems (see later).

- 8. Storage of samples: at some stage within the execution, it will be found necessary to store block of samples of the signal at any node of the system so as to process it further at a later time, internally or externally.

- 9. Memory allocations (real and image): it is always beneficial to plan and utilise computer memory capacity according to the simulator need (program, tables etc).

10. Efficient processing (arithmetic and logic): one of the chief functions of a digital computer is to perform arithmetic operation upon numbers and series of numbers can represent the instantaneous amplitude of a signal. Therefore, if the correct arithmetic operations are used, sequences of numbers could be converted into other sequences, in such a way that the overall operation models some element in a communications systems. Such is the basis of simulation by digital computer<sup>38</sup>. Therefore, the computer arithmetic capability is an important factor when considering the design of a simulator. This is more apparent for the on-line real time simulation case where the time saving is of vital importance, eq

> If one instruction takes 1 m second then for 1000 instructions would take 1 second, giving a sampling frequency = 1Hz which is highly unacceptable.

It is preferred to have a high speed arithmetic unit in conjunction with computer system to solve this problem.

- 11. Multiprocessing attempts: Since communication simulation sometimes involves multiple processing and since time saving is an important factor in simulation then it is desirable to multiprocessing simulation but with additional problems in organisation. This can be achieved by software or hardware or both. The latter point will be elaborated in later Chapters.

- 12. Cross-reference of samples (nodes): as signal samples are flowing within the simulator passing through

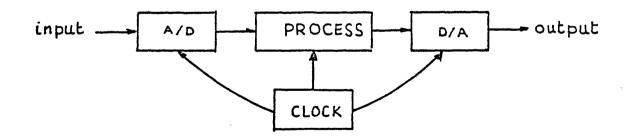

multiple input/output nodes, it is essential that at multiple inputs, each sample has the same time registration. Otherwise the simulation is invalid. Special care must be taken regarding this problem. Real-time simulation: this type of simulation has a number of criteria, namely:

14.

- (a) Real-time clock: this is preferably an external clock, which can be varied depending on the sampling frequency. Its accuracy therefore has a major factor on the running of the simulation.

- (b) Analogue/Digital and Digital/Analogue converters: the number of levels and digits in either direction, ie quantisation error, will influence the accuracy of the simulation. Therefore, it must be taken into account and made as small as possible. Wide dynamic range logarithmicconverters may be needed.

- 15. Continuous signal as represented by a digital system: the correspondence between the digital model and the continuous system depends on:

- (a) Satisfying the sampling theorem

- (b) Correctly relating the z-transform of digital filter structures to the frequency response of the continuous prototype.

#### 2.4 FREQUENCY DOMAIN SIMULATION

#### 2.4.1 Introduction

Ever since the development of computer procedure for performing the Fast Fourier Transform (FFT), the communication engineer has been provided with a simple method of achieving frequency domain processing (wave filtering) without the need to acquire skills in the technique of digital filtering<sup>9</sup>. Most communication simulators today are based on this type of domain and are well covered by the literature <sup>(\*)</sup>.

## 2.4.2 Principle of Operation

This type of simulation is based on processing a block of signal samples at a time. When filtering is required, these samples will be transformed to the frequency domain by applying the Discrete Fourier Transform (DFT) to this block of samples, then transforming to time domain by applying Inverse Discrete Fourier Transform (IDFT) for further non-linear processing. The number of samples in a block must be large enough to give a good resolution. However if there is a very long signal record to be processed,then successive sets of blocks are processed independently, and the processed blocks are joined up together so as to produce the continuation of signal record as before. However, this joining up process is complicated by the fact that this filtering performs a circular convolution instead of an aperiodic one<sup>49</sup>, so that a certain proportion of each segment must be discarded.

#### 2.4.3 Execution procedure

- (a) Obtain the filter response from either a pole-zero description, or a numerical description of a measured response curve.

- (b) Take N points of input signals.

- (c) Transform into the frequency domain using DFT.

- (d) Multiply each sample (point) by the corresponding filter response.

- (e) Transform resulting spectrum back to time domain using IDFT for further processing.

#### 2.4.4 System Analysis

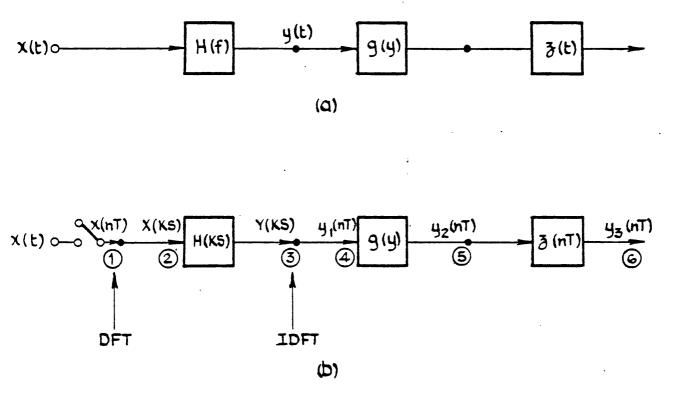

A prototype system containing the basic elements of a communication system, ie a filter, nonlinear module and a linear module, Fig 2.4.4(a), has a corresponding structure for frequency domain simulation, as shown in Fig 2.4.4(b). The signal analysis (signal calculations at nodes concerned), for an input signal X(t) having a bandwidth  $\omega$  Hz is as follows:

\* At node (1): analogue to digital conversion

$$x(t) = \sum_{-\infty}^{+\infty} x(nT) \operatorname{sinc} \left(\frac{t}{T} - n\right)$$

(1)

where T = the sampling frequency.

There is a major restriction which must be observed:

- T <<  $\frac{1}{2B}$  where B is the highest frequency component of the input signal (=  $\omega$  in this case). This is the limitation imposed by the sampling theorem<sup>8</sup>, so that folding back into the fundamental band, thus disturbing the representation, does not take place, also to overcome aliasing (or overlap or high frequency impersonation<sup>6</sup>).

- \* At node (2): Conversion to frequency domain

The conversion is performed using discrete fourier transform (DFT):

$X(K\delta) = \frac{1}{N} \sum_{n=0}^{N-1} x(nT) \exp - j \frac{2\pi Kn}{N}$

$K = 0, 1, 2, \dots, N-1$

\* At node (3): Filtering action

The filter coefficients are either stored (storing N points), or generated (N points), using the zeros and poles of the filter. The output signal  $Y(K\delta)$  is determined by multiplying signal component by the filter spectrum

$Y(K\delta) = H(K\delta) \cdot X(K\delta)$

\* At node (4): Conversion back to time domain

The conversion is performed using the inverse discrete fourier transform (IDFT)

$$y_{1}(nT) = \sum_{K=0}^{N-1} Y(K\delta) \text{ exp j } \frac{2\pi Kn}{N}$$

$n = 0, 1, 2, \dots, N-1$

\* At node (5): Time-invariant non-linear module

$$y_2(nT) = g(y_1(n_1T))$$

\* At node (6): Time-invariant linear module

$y_3(nT) = z(nT) \cdot y_2(nT)$

This is a simple multiplication.

## 2.4.5 Characteristics

- (a) Systems with feedback links cannot be handled since data is processed by the FFT in segments.

- (b) Slow, hence it cannot be used for stochastic simulation, unless hardware FFT machine is employed.

- (c) Resolution is limited by fixed number of points (samples).

- (d) Easier to handle complex signals than time domain

based simulators.

(e) Any type of computer can be utilised, but as an off-line oriented simulator.

## 2.4.6 Utilisation

Wide range of problems are being solved using this technique and could be found in literature, and some languages have been developed such as WASP<sup>11</sup>, MODSIM<sup>41</sup> and SIGSIM<sup>35</sup>

### 2.4.7 Scaling

For time scale of signal block consisting of N samples at spacing of T seconds, and frequency scale of signal block consisting of N samples at spacing of  $\delta$  frequency, then NT $\delta$  = 1 Thus, for a given number of points T  $\propto \frac{1}{\delta}$  (reciprocal relationship). But frequency scale is limited to  $\frac{1}{2}$  the sampling frequency then  $F_{max} = \frac{1}{2T} = \frac{N\delta}{2}$

#### 2.5 TIME DOMAIN SIMULATION

#### 2.5.1 Basic principles and execution procedure

The conversion from time to frequency domain for the purpose of filtering signal samples becomes unnecessary in time domain simulation, because the filter itself is simulated. This is done by correctly relating the ztransform of digital filter structure to the frequency response of the continuous prototype  $9^{-9}$ , and using the difference equation version of the filter response. However, digital filter cannot model the corresponding analogue filter in both impulse and frequency response, but it is possible to make the correspondence close with careful design  $49^{-9}$ . There is no limitation to the number of points and for this reason it is suitable for on-line real-time working simulation. It is possible to simulate systems with feedback links. However, state variables of the system have to be clearly defined.

## 2.5.2 System state variables

The state variables of a discrete-time system are the minimum set of variables which define the overall state of any system (linear or non-linear) at instant of  $\frac{9}{1000}$ . They are useful for the following reasons:

- (\*) It may be necessary to examine the behaviour of all relevant signals in a system.

- (\*) The need for a more general system description to treat multiple inputs and outputs.

- (\*) The need for a more compact system description in the study of complex systems.

- (\*) Often in the study of systems, only a general (qualitative) description of system behaviour is required.

The general mathematical formulation of the state variables concept is as follows  $^{17}$  :-

Assume a system, whose outputs represented by (y) and inputs by u, is defined by

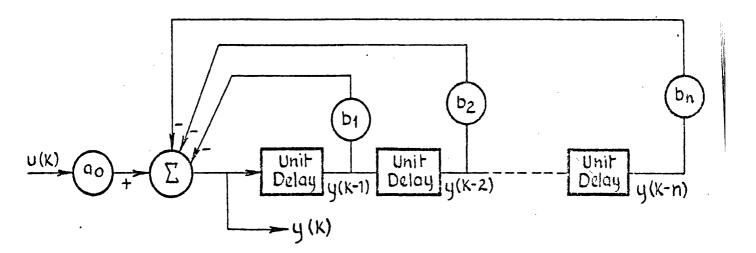

$y(k) + b_1 y(k-1) + ... + b_n y(k-n) = a_0 u(k)$  (1) for K  $\ge 0$

Defining the state variables as:  $x_{i}(K)$ , i = 1, 2, ..., nthus:  $x_{1}(k) = y(k-n)$   $x_{2}(k) = y(k-n+1)$   $\vdots$   $x_{n}(k) = y(k-1)$ Hence by substitution:  $x_{1}(k+1) = x_{2}(k)$   $x_{2}(k+1) = x_{3}(k)$   $\vdots$   $x_{n-1}(k+1) = x_{n}(k)$ and  $x_{n}(k) = y(k) = a_{0}u(k) - b_{n}x_{1}(k) \dots - b_{1}x_{n}(k)$

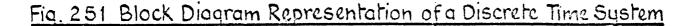

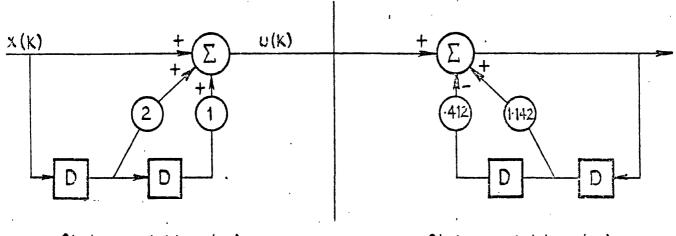

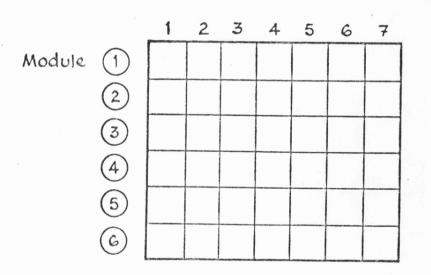

This equation is represented by block diagram shown in Fig 2.5.1.

Hence, using vectors  $[x(k+1)] = [A][x(k)] + [B] \cdot u(k)$  (2) where:  $\begin{bmatrix} x_1(k) \\ x_2(k) \\ \vdots \\ \vdots \\ x_n(k) \end{bmatrix}$ ,  $\begin{bmatrix} A \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 1 & . & . & 0 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & 1 \\ 0 & 0 & 0 & . & . & . & 1 \\ 0 & 0 & 0 & . & . & . & 1 \\ 0 & 0 & 0 & . & . & . & 1 \\ 0 & 0 & 0 & . & . & . & 1 \\ 0 & 0 & 0 & . & . & . & . \\ 0 & 0 & 0 & . & . & . & . \\ 0 & 0 & 0 & . & . & . & . \\ 0 & 0 & 0 & . & . & . & . \\ 0 & 0 & 0 & . & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . & . \\ 0 & 0 & 0 & . & . \\ 0 & 0 & 0 & . & . \\ 0 & 0 & 0 & . & . \\ 0 & 0 & 0 & 0 & . \\ 0 & 0 & 0 & . & . \\ 0 & 0 & 0 & 0 &$

## NOTE

A system is linear if and only if superposition and homogeneity hold<sup>17</sup>: ie

$$\alpha x_{1}(t) + \beta x_{2}(t) \rightarrow \alpha y_{1}(t) + \beta y_{2}(t)$$

In general for y(t) = H [x(t)], a system is linear if and only if H is a linear transformation: ie

$H\left[\alpha \ x_{1}(t) + \beta \ x_{2}(t)\right] = \alpha \ H\left[x_{1}(t)\right] + \beta \ H\left[x_{2}(t)\right]$

The output in terms of state variables:

$$y(k) = [C] \cdot [x(k)] + [D] u(k)$$

(3)

where  $[C] = \begin{bmatrix} -b_n & -b_{n-1} & \cdots & -b_1 \end{bmatrix}$  and  $[D] = a_0$

Rewriting in state variable representation:

The general equations for linear and non-linear systems

[x (k+1)] = [A] . [x (k)] + [B] . u (k)y (k) = [C] . [x (k)] + [D] . u (k)

The above formulations can be utilised in the simulation of digital filters, eg a second-order Butterworth lowpass digital filter with a cut-off frequency  $\omega_c = 0.3249$  rad/sec, has a transfer function given by  $\frac{1}{2}$ :

$$H(z^{-1}) = 0.0676 \left\{ \frac{1 + 2z^{-1} + z^{-2}}{1 - 1.142 z^{-1} + 0.412 z^{-2}} \right\}$$

Applying difference equation method :

$$y(k) = x(k) + 2 x(k-1) + x(k-2) + 1.142 y(k-1) - 0.412 y(k-2)$$

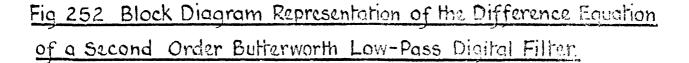

This is represented by a block diagram, Fig 2.5.2.

Using the above formulation for state variables:

$$v_1(k) = y(k-2)$$

)

$v_2(k) = y(k-1)$ ) for section (a) of Fig 2.5.2

$\omega_1(k) = x(k-2)$ )

$\omega_2(k) = x(k-1)$ ) for section (b) of Fig 2.5.2

Using equation (1), for section (a) of the filter: the state variables

$$\begin{bmatrix} v(k+1) \end{bmatrix} = \begin{bmatrix} A \end{bmatrix} \cdot \begin{bmatrix} v(k) \end{bmatrix} + \begin{bmatrix} B \end{bmatrix} \cdot u(k)$$

where

$$\begin{bmatrix} v(k) \end{bmatrix} = \begin{bmatrix} v_1(k) \\ v_2(k) \end{bmatrix} , \begin{bmatrix} A \end{bmatrix} = \begin{bmatrix} 0 & 1 \\ 1.142 & -0.412 \end{bmatrix}$$

state variables

$$\begin{bmatrix} \omega \end{bmatrix} \begin{bmatrix} B \end{bmatrix} = \begin{bmatrix} 0 \\ 1 \end{bmatrix}$$

Using equation (3), the output y(k) in term of state variables for section (a) of the filter is:

$$y(k) = [C] [v(k)] + [D] . u(k)$$

where  $[C] = [1.142 -0.412]$ ,  $[D] = 1$

Repeating calculations for section (b) of the filter and by inspection:

State variables:

$$\begin{bmatrix} w(k+1) \end{bmatrix} = \begin{bmatrix} A \end{bmatrix} \begin{bmatrix} w(k) \end{bmatrix} + \begin{bmatrix} B \end{bmatrix} \cdot x(k)$$

$$\begin{bmatrix} w(k) \end{bmatrix} = \begin{bmatrix} w_1(k) \\ w_2(k) \end{bmatrix} , \quad \begin{bmatrix} A \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ 0 & 1 \end{bmatrix} , \quad \begin{bmatrix} B \end{bmatrix} = \begin{bmatrix} 1 \\ 0 \end{bmatrix}$$

The output in terms of state variables:

$$u(k) = [C] \cdot [w(k)] + [D] \cdot x(k)$$

$[C] = [2 \ 1] , [D] = 1$

Solution of the general equations (1) and (2):

If the vector  $\mathbf{x}(k_0)$  for some  $k_0$  is known, then  $\mathbf{x}(k)$  can be computed, and hence the output  $\mathbf{y}(k)$ , for any  $k \ge k_0$  in terms of the input sequence  $\mathbf{u}(k_0)$ ,  $\mathbf{u}(k_0+1)$ ,..., $\mathbf{u}(k)$ . Thus the vector  $\mathbf{x}$  satisfies the definition for the state of a system. This n-dimensional vector is equivalent to the (n) initial conditions needed to solve the difference equation (1) in terms of input u. Accordingly the following definitions are obtained:

- X state vector of the system

- A state or system matrix: nxn matrix which relate the state at index k+l to the state at k.

Therefore there are two areas to consider when applying the above formulations to the problems of time domain, communication system simulation:

- (i) Modules containing delay elements, such as filters, differentiators etc.

- (ii) The multiple input/output modules, with feedback links.

These two items will be discussed in detail in Chapter 3, as part of the construction and running procedures of a simulated communication system, in the newly designed simulator ICOSS.

#### 2.5.3 Characteristics

- More suitable for stochastic simulation than frequency domain simulation.

- 2. On-line real time working is possible.

- Settling time is long, unless time scaling is introduced, see later.

- Non-linear system elements response are treated in an accurate straightforward way.

#### 2.5.4 General comments

Time domain simulation was classically applied to analogue computations for control systems. With the introduction of fast digital computers economic considerations favour the digital computer simulation opposed to analogue simulation  $^{16}$ . Comparison between analogue and digital computers is as follows:

## Analogue computers

- (a) Significant set-up and check-out time for initialisation.

- (b) Additional time for modification of original situation.

- (c) Extremely low unit run cost, even for wide bandwidth systems.

(d) Degradation of electronic elements may create large solution errors.

#### Digital computers

- (a) Assuming program developed and debugged, then

- (i) Minimum set-up time and very limited initial checking.

- (ii) Negligible additional time for parameters and topological variations.

- (b) High hourly cost.

## 2.5.5 Execution Time

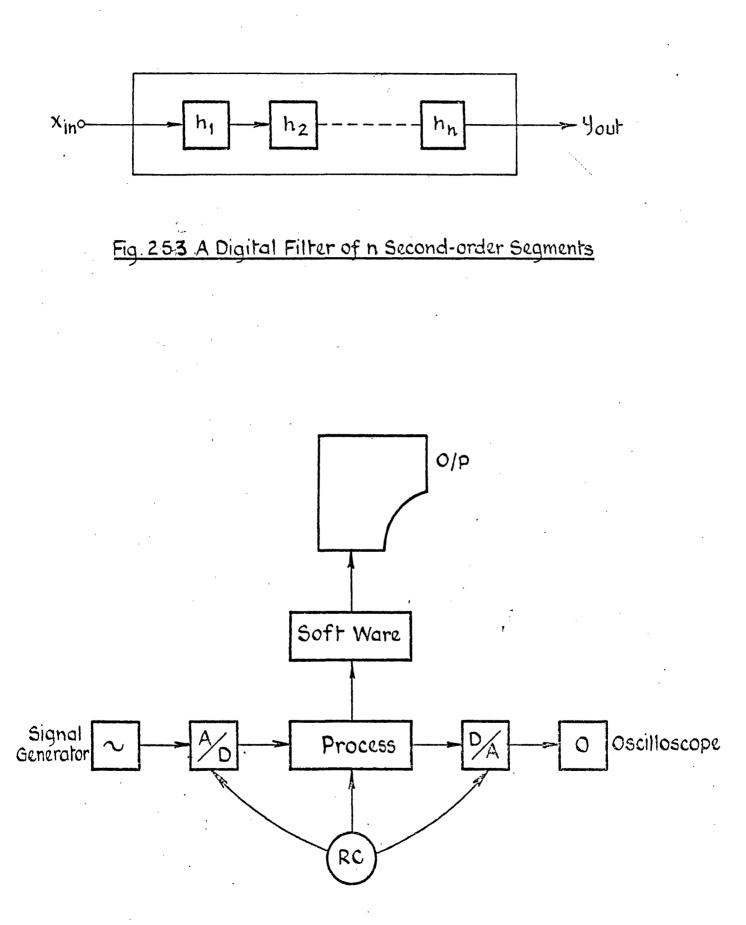

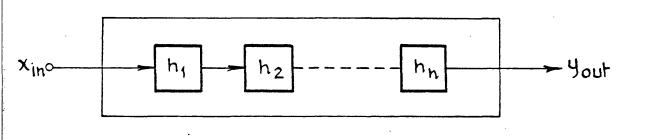

Assuming a digital filter made up of n second order segments, Fig 2.5.3, in which the transfer function of one segment  $h_i$  is given by<sup>20</sup>

$$h_{i} = \frac{1 + a_{i} z^{-1} + b_{i} z^{-2}}{1 + c_{i} z^{-1} + d_{i} z^{-2}}$$

giving a difference equation

$y_{i}(k) = x_{i}(k) + a_{i} x_{i}(k-1) + b_{i} x_{i}(k-2) - c_{i} y_{i}(k-1) - d_{i} y_{i}(k-2)$

$y_{out} = a_0 y_n$

Defining an operation as one multiply/add action, then there are 4 operations (second order segment). For n segments filter the total number of operations =  $4 \cdot n + 1$ (the 1 for the constant  $a_0$  of the final result). However, additional time is required for the state variable manipulations as mentioned earlier (2.5.2).

## 2.6 R.F. SIGNAL SIMULATION

In the digital simulation of continuous RF signals, the problem is in having a modulating signal as a small ratio to the carrier. The carrier which contains no useful information will predominate the sampling rate at the expense of the useful modulating signal. One method <sup>49</sup> of simulating RF signal is by decomposing the RF signal to:

(a) Useful modulating signal at baseband: m(t).

(b) Carrier.

For RF signal:  $x_m(t) = m(t) \cos \omega_c(t)$  (1)

Therefore the simulation will concentrate only on m(t), and the sampling frequency will be as ratio to the carrier frequency.

For various types of modulations, the modulating signal is given by

| (i)   | DSBSC          | m(t) = x(t)                 | )<br>) (2)             |

|-------|----------------|-----------------------------|------------------------|

| (ii)  | DSB-AM         | m(t) = 1 + a x(t)           |                        |

| (iii) | Phase modulati | on m(t) = l exp jx(t        | .)                     |

| (iv)  | Frequency modu | lation m(t) = 1 exp         | j { <b>j</b> x(t) dt}) |

| (v)   | SSB            | $m(t) = x(t) + \hat{jx}(t)$ | )                      |

where x is the Hilbert transform of x(t).

Equations (2) can be rewritten as 2 conjugate parts:

$$\mathbf{x}_{m}(t) = \frac{1}{2} \{m(t) \exp j\omega_{c}t + m^{*}(t) \exp(-j\omega_{c}t) \}$$

(3)