## **University of Bath**

|--|

Alternative approaches to combinational and sequential logic design.

Picton, P. D.

Award date: 1982

Awarding institution: University of Bath

Link to publication

**General rights**Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 22. May. 2019

# ALTERNATIVE APPROACHES TO COMBINATIONAL AND SEQUENTIAL LOGIC DESIGN

submitted by

P.D. PICTON

for the degree of Ph.D. of the University of Bath

1982

#### COPYRIGHT

"Attention is drawn to the fact that copyright of this thesis rests with its author. This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author".

"This thesis may be made available for consultation within the University Library and may be photocopied or lent to other libraries for the purposes of consultation".

P.D. Pister

ProQuest Number: U336667

### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest U336667

Published by ProQuest LLC(2015). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code.

Microform Edition © ProQuest LLC.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346 SUMMARY

This thesis is concerned with the developments firstly in combinational logic, where the problems involved in multi-threshold realisations are examined, and secondly in sequential logic, where the specific type of system known as serial input logic is considered.

Chapter 1 is an introduction which discusses the areas covered by this thesis and indicates their relationship to one another within the general framework of logic design.

Chapter 2 sets out to extend the number of functions that can be realised by a multi-threshold logic gate with near optimal weights and thresholds. Use is made of the already existing spectral translation method of obtaining a single threshold solution with additional exclusive-or gates, a multi-threshold solution being obtained by algebraic manipulation of the weights and threshold. The mathematical basis that enables this to be done is derived and examples given.

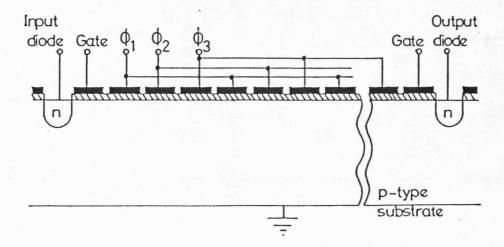

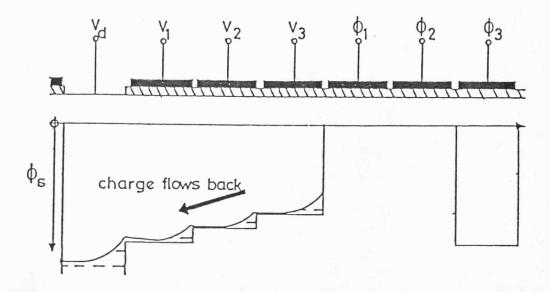

Chapter 3 discusses the possible advantages of using a multithreshold logic gate within a charge-coupled device over the alternative

Boolean AND/OR and quaternary logic gates. The fundamental operations

of a charge-coupled device are reviewed, and the tolerancing problems

that result from the charge transfer inefficiency and voltage fluctuations are considered as limiting factors on the logical complexity

of the gate.

Chapter 4 is concerned with the subject of serial input logic.

Initially it sets out to define serial input logic in terms of a general sequential system, and then goes on to show that with regard to state reduction using compatibles it is unique since it only requires the derivation of the implied maximal compatibles. Furthermore, a modular realisation is given, where the design procedure consists

of the use of reverse response trees. Various labelling schemes are considered and finally one is considered that guarantees an optimal solution.

Throughout the thesis emphasis is placed on finding general solutions whenever possible, so that not only do they apply to the situations described herein, but also may prove useful in as yet undeveloped areas of research.

LIST OF SYMBOLS

#### List of Symbols

Number of input variables to a logical n function  $x_{i}$ , i = 1 to nBinary input variable,  $x \in (0,1)$  $f(x), f(x_1, x_2, ..., x_n)$ Function of the x<sub>i</sub> variables,  $f(x) \in \langle 0, 1 \rangle$ Matrix Column matrix Arithmetic addition or logical OR Arithmetic product or logical AND (omitted when no ambiguity arises)  $r_i$ , i = 0,1,...,12...nRademacher-Walsh spectral coefficient Interchange iff If and only if Don't care Voltage Q Charge Surface potential Clock phase  $\phi_{\mathbf{i}}$ Charge transfer inefficiency Fractional voltage fluctuation  $^{\circ}$ , (%)Compatibility, (incompatibility) A subset of C, (¢) A proper subset of, (not a subset of) Contained in  $p_{i}$ , i = 0 to  $2^{n} - 1$ The ith minterm of a function f(x), where the corresponding row of input variables

digit

in the truth table read as a binary

number,  $x_n$  being the least significant

Union

J<sub>i</sub>, K<sub>i</sub>, R<sub>i</sub>, S<sub>i</sub>, T<sub>i</sub>

Rademacher-Walsh spectra of the characteristic functions of J-K, R-S, and

T bistables, respectively

AND gate

OR gate

Exclusive-or gate

Inverter

Gate

Drain

Used in C.C.D.'s

CONTENTS

# CONTENTS

|             |          |                                                                                 | Page Number |

|-------------|----------|---------------------------------------------------------------------------------|-------------|

| Title Page  |          |                                                                                 | i           |

| Summary     |          |                                                                                 | ii          |

| List of Syn | nbols    |                                                                                 | v           |

| Contents    |          |                                                                                 | ix          |

| Chapter 1   | Introduc | ction                                                                           | 1           |

|             | Referenc | ces                                                                             | 8           |

| Chapter 2   | Threshol | ld Logic                                                                        | 9           |

|             | 2.1      | Single Threshold Logic                                                          | 10          |

|             | 2.2      | Spectral Translation                                                            | 12          |

|             | 2.2.1    | Output Spectral Translation                                                     | 14          |

|             | 2.2.2    | Input Spectral Translation                                                      | 16          |

|             | 2.2.3    | Rademacher-Walsh Spectral<br>Classification                                     | 17          |

|             | 2.3      | Multi-threshold Logic                                                           | 20          |

|             | 2.4      | Conversion from Spectral<br>Translation Solution to<br>Multi-threshold Solution | 24          |

|             | 2.4.1    | Output Spectral Translation<br>Conversion                                       | 25          |

|             | 2.4.1.1  | Single Input Variable                                                           | 25          |

|             | 2.4.1.2  | More than One Input Variable                                                    | 31          |

|             | 2.4.1.3  | Non-threshold Initial Function f'(x)                                            | 34          |

|             | 2.4.1.4  | Final Adjustments                                                               | 36          |

|             | 2.4.2    | Input Spectral Translation<br>Conversion                                        | 44          |

|             | 2.4.2.1  | Single Input Variable                                                           | 44          |

|             | 2.4.2.2  | Non-threshold Initial Function f'(x)                                            | <b>4</b> 8  |

|           | 2.4.2.3  | More than One Input Variable                 | 50 |  |

|-----------|----------|----------------------------------------------|----|--|

|           | 2.5      | Conclusions and Further Work                 | 58 |  |

|           |          | References                                   | 61 |  |

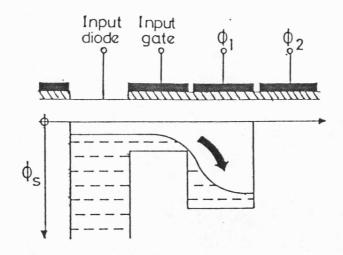

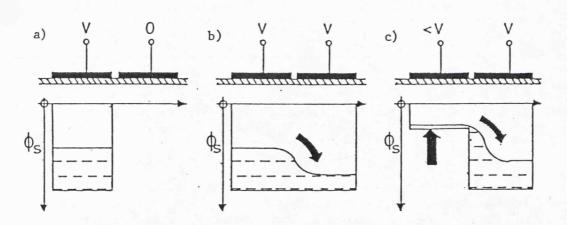

| Chapter 3 | Charge-C | oupled Devices (C.C.D.'s)                    | 63 |  |

|           | 3.1      | General Description                          | 64 |  |

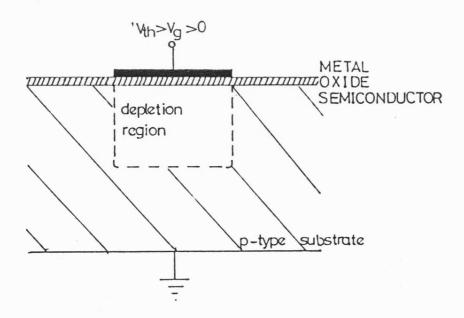

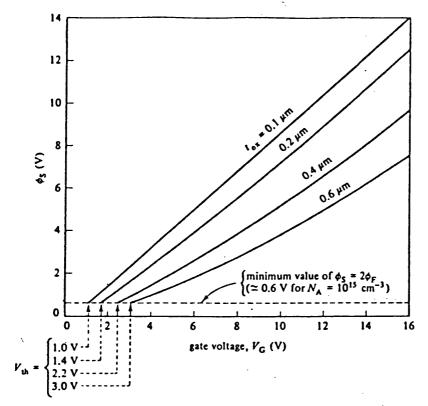

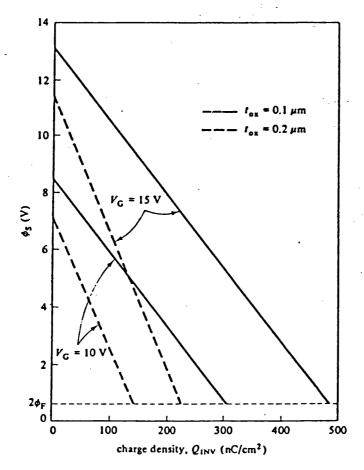

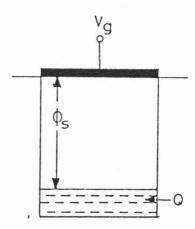

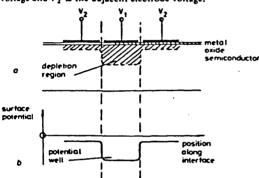

|           | 3.1.1    | Creation of a Well                           | 64 |  |

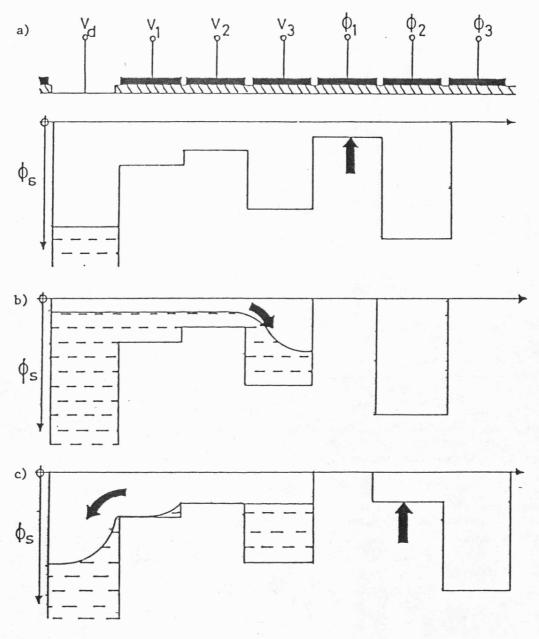

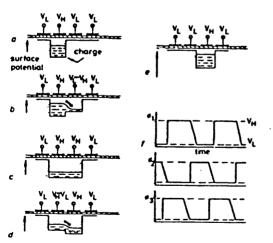

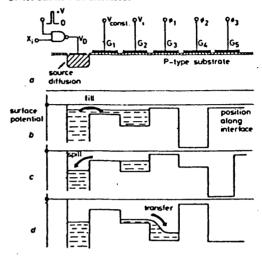

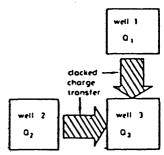

|           | 3.1.2    | Charge Transfer                              | 68 |  |

|           | 3.2      | Logic Design                                 | 71 |  |

|           | 3.2.1    | Some Additional C.C.D. Properties            | 71 |  |

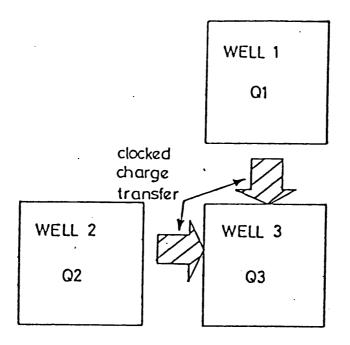

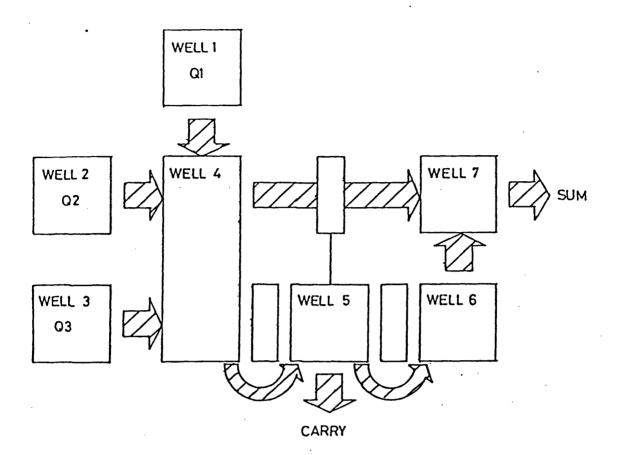

|           | 3.2.1.1  | Charge Summing                               | 71 |  |

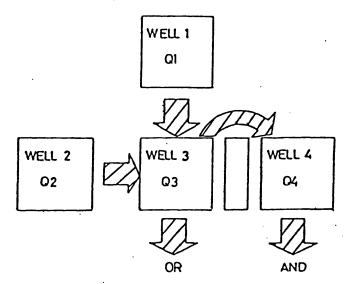

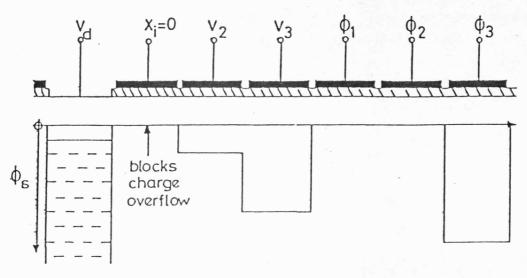

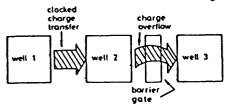

|           | 3.2.1.2  | Charge Overflow                              | 72 |  |

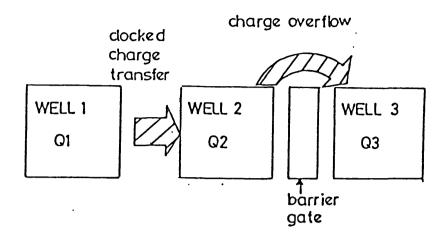

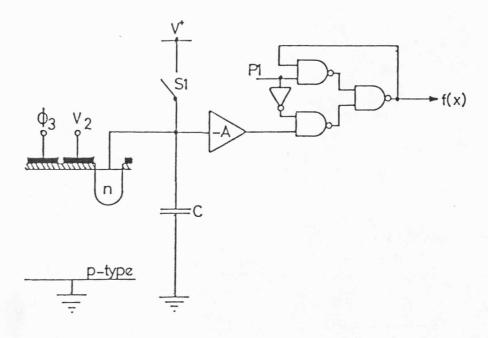

|           | 3.2.1.3  | Charge Sensing                               | 73 |  |

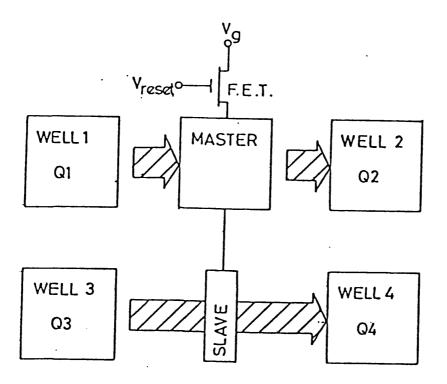

|           | 3.2.2    | Binary Logic                                 | 75 |  |

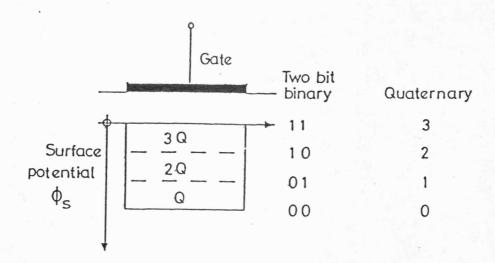

|           | 3.2.3    | 'Multi-valued Logic                          | 77 |  |

|           | 3.3      | Threshold Logic                              | 79 |  |

|           | 3.3.1    | Charge Input                                 | 80 |  |

|           | 3.3.2    | Charge Detection                             | 80 |  |

|           | 3.3.3    | System Integration                           | 83 |  |

|           | 3.3.3.1  | Charge Input                                 | 83 |  |

|           | 3.3.3.2  | Charge Output                                | 84 |  |

|           | 3.4      | Threshold Logic Gate                         | 87 |  |

|           | 3.4.1    | Limitations of the Threshold<br>Logic Device | 89 |  |

|           | 3.5      | Conclusions and Further Work                 | 94 |  |

|           |          | Pafarances                                   | 97 |  |

| Chapter 4 | Serial Input Logic |                                                           |     |  |  |  |  |  |

|-----------|--------------------|-----------------------------------------------------------|-----|--|--|--|--|--|

|           | 4.1                | General and Desirable Features                            | 101 |  |  |  |  |  |

|           | 4.2                | Conventional Sequential Logic<br>Realisation              | 103 |  |  |  |  |  |

|           | 4.2.1              | State Reduction in the Realisation of a Specific Function | 104 |  |  |  |  |  |

|           | 4.2.2              | State Reduction for a General Function                    | 113 |  |  |  |  |  |

|           | 4.2.3              | State Assignment and Hardware<br>Realisation              | 124 |  |  |  |  |  |

|           | 4.2.3.1            | Characteristic Equations of Bistables                     | 125 |  |  |  |  |  |

|           | 4.3                | Modular Solution                                          | 130 |  |  |  |  |  |

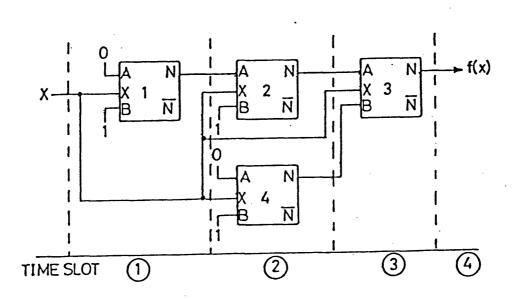

|           | 4.3.1              | Multiplexer-and-Delay Modules                             | 130 |  |  |  |  |  |

|           | 4.3.2              | Mode-Controlled Logic                                     | 134 |  |  |  |  |  |

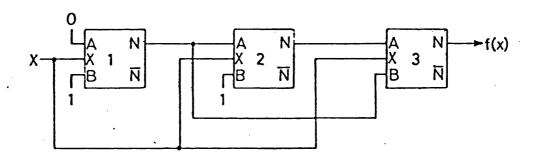

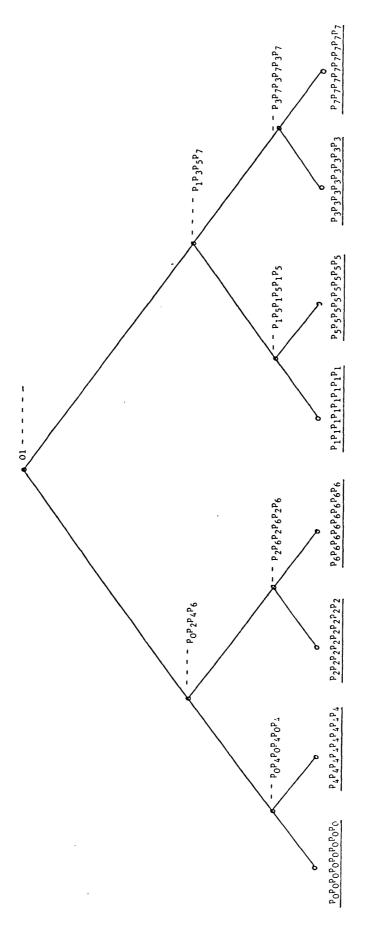

|           | 4.4                | Tree Structures                                           | 136 |  |  |  |  |  |

|           | 4.4.1              | Modular Solution Incorporating Don't Care Terms           | 137 |  |  |  |  |  |

|           | 4.4.2              | General Solution                                          | 140 |  |  |  |  |  |

|           | 4.4.2.1            | Random Assignment                                         | 144 |  |  |  |  |  |

|           | 4.4.2.2            | Invisible Don't Cares                                     | 146 |  |  |  |  |  |

|           | 4.4.2.3            | Specific Assignment of Don't<br>Care Terms                | 150 |  |  |  |  |  |

|           | 4.4.3              | Additional Features                                       | 158 |  |  |  |  |  |

|           | 4.4.3.1            | Incompletely Specified Functions                          | 159 |  |  |  |  |  |

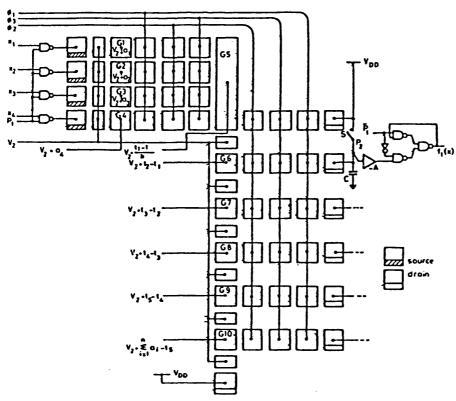

|           | 4.4.3.2            | Multi-output Systems                                      | 160 |  |  |  |  |  |

|           | 4.4.3.3            | Multi-input Systems                                       | 162 |  |  |  |  |  |

|           | 4.4.3.4            | Serial Multi-output                                       | 162 |  |  |  |  |  |

|           | 4.5                | Conclusions and Further Work                              | 166 |  |  |  |  |  |

|           |                    | References                                                | 171 |  |  |  |  |  |

| Chapter 5    | General Conclusions                                                      | 174 |

|--------------|--------------------------------------------------------------------------|-----|

| Acknowledger | ments                                                                    | 180 |

| Appendix A   | Chow's Parameters for Threshold Functions of $n \le 6$                   | 182 |

| Appendix B   | Rademacher-Walsh Spectral Classification of Functions of n $\leqslant$ 4 | 188 |

| Appendix C   | Copies of Published Material                                             | 190 |

CHAPTER 1

INTRODUCTION

#### 1. Introduction

Two of the observable current trends in logic design are:

- a) to accept that physical miniaturisation of circuits is a finite process and hence the search for devices with greater logical power per unit area of chip,

- b) to simplify and unify logic design procedures by the use of universal logic modules.

For the former, the bulk of research has been concentrated on multi-valued logic (usually ternary, 3-valued, or quaternary, 4-valued) and threshold logic. The subject of threshold logic has been extensively researched over the past two decades but its application has been limited, mainly due to the relatively few functions that can be directly realised with single threshold devices.

Chapter 2 of this thesis attempts to extend the use of threshold logic by the utilisation of multi-thresholds. To date the major features and operations of threshold logic theory are as follows [1]:

- a) the characterisation of threshold functions with n + 1 coefficients called the Chow's parameters.

- b) Lists of Chow's parameters are available for n ≤ 8 which can be used to determine whether or not a function is threshold realisable, and if so gives the optimised weights and thresholds to do so.

- c) the ability to invert a threshold function and/or any of its input variables by the negation of the relevant weights; also the ability to permutate the input variables.

- d) the classification of all functions including the nonthreshold ones by the use of the 2<sup>n</sup> coefficients known as the Rademacher-Walsh spectrum, functions in the same class being related by the use of "spectral translation".

- e) the division of these classes into threshold and nonthreshold classes, the former consisting of functions which

are, or upon the application of spectral translation become,

threshold functions, the latter functions being unable to be

translated into a threshold class.

- f) lists of the Rademacher-Walsh spectra of all functions of n ≤ 4 giving "optimised" weights and thresholds for a multithreshold realisation are available.

The aim of Chapter 2 is to extend the number of manipulations that can be done to the weights and thresholds of a function in order to obtain dissimilar functions. These manipulations can then be used to convert functions contained in the threshold class into multithreshold solutions, i.e. convert functions which are realisable with a single threshold gate plus any exclusive-or gates (to perform the equivalent in the Boolean domain as spectral translation in the spectral domain) into multi-threshold form. The reasons for wanting a multithreshold solution as opposed to the single threshold with additional hardware are given, and also proposed is the conversion of at least some of the functions contained in the non-threshold classes into a multi-threshold solution.

Another area of development in threshold logic has been in the design of the gate itself. Many have been developed using various technologies, two of the most promising being the Digital-Summation-Threshold-Logic gate (D.S.T.L.) and the  $I^2L$  gate  $\begin{bmatrix} 1 \end{bmatrix}$ . However, recently

a need has been expressed for the incorporation of logic in charge-coupled devices (C.C.D.'s), with a view to developing a system comprising both a digital memory and a logic processor on a single chip [2]. The previously mentioned threshold logic gates are incompatible with C.C.D. systems since the data would have to be taken out of the C.C.D. system, logic operations performed, and then the data returned.

The hitherto proposed alternative logical approaches which can be incorporated into C.C.D. technology are either arrays of binary AND/OR gates [2] or quaternary logic gates [3]. Chapter 3 sets out to indicate that the operations used in these logic gates, such as charge input, transfer, and overflow, can be applied equally well to a C.C.D. threshold logic gate. However, an additional feature is required for a threshold logic gate, namely the use of multi-levels of charge when the number of levels is greater than four, quaternary logic having already illustrated the use of up to four levels. A justification of this is therefore also included in Chapter 3.

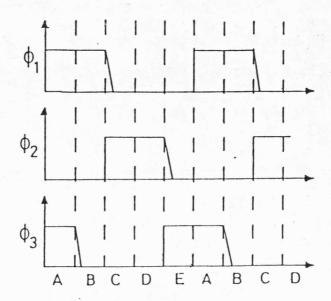

A multi-threshold logic gate structure is proposed and details of its mode of operation and timing diagrams are included. Its drawbacks are discussed, such as tolerancing problems and voltage rail fluctuations. The gate is then compared not only with the alternative C.C.D. logic gates but also with the previously suggested threshold logic gates.

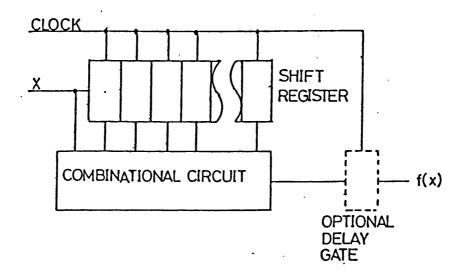

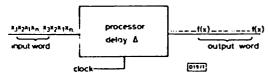

An interesting feature of the gate is that a clock is present and therefore it represents a synchronous system. The application of threshold logic to synchronous systems has received some attention but it is not pursued in this thesis. Of note, however, is the fact that the gate can also be described as having clocked parallel inputs. An alternative approach would therefore be to use clocked serial inputs.

Such a system with serial inputs would have to be synchronous since the data would be arriving on the same input line, and therefore each piece of data would have to occupy its own time slot. Thus the data can be envisaged as a word-formatted n bit serial stream. To date such systems have received little attention, that which it has received being confined to mode-controlled logic [4]. This area is therefore examined in more depth in Chapter 4.

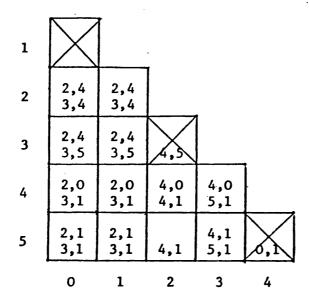

The intention of the first part of Chapter 4 is to define the subject more broadly and to examine it from the point of view of a general sequential system. In particular, the field of state reduction using compatibles is studied. The chapter sets out to prove that a serial input logic system is a special class of sequential system where the number of states can be reduced by merely considering the maximal compatibles, as opposed to the usual situation where a great deal of complex and time consuming manipulation is required.

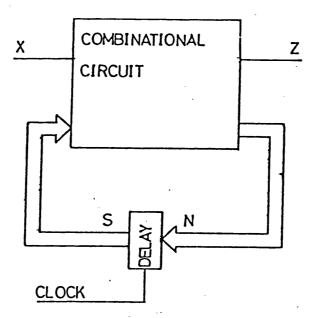

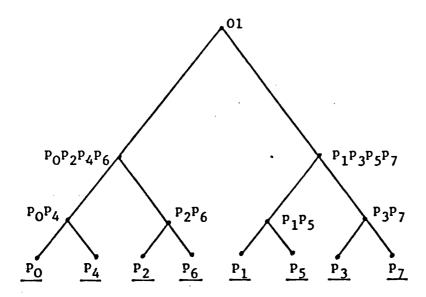

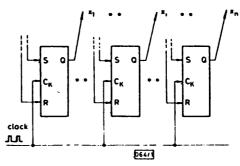

The chapter goes on to consider the use of modules in the design of serial input systems. As stated at the beginning of this introductory chapter, the use of universal logic modules is an important aspect of logic design in both combinational and sequential systems, the difference being that in sequential logic the modules usually contain delay elements whereas in combinational they do not. Of particular interest is the work that has been done on the application of modular networks to the design of any sequential system, where the network needs at most one feedback loop [5]. Furthermore, it has been shown that some machines, known as definite machines, do not need any feedback and are therefore more easily realisable and testable. The chapter shows that serial input logic systems are definite machines and therefore they too do not require any feedback.

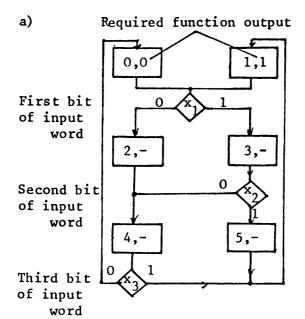

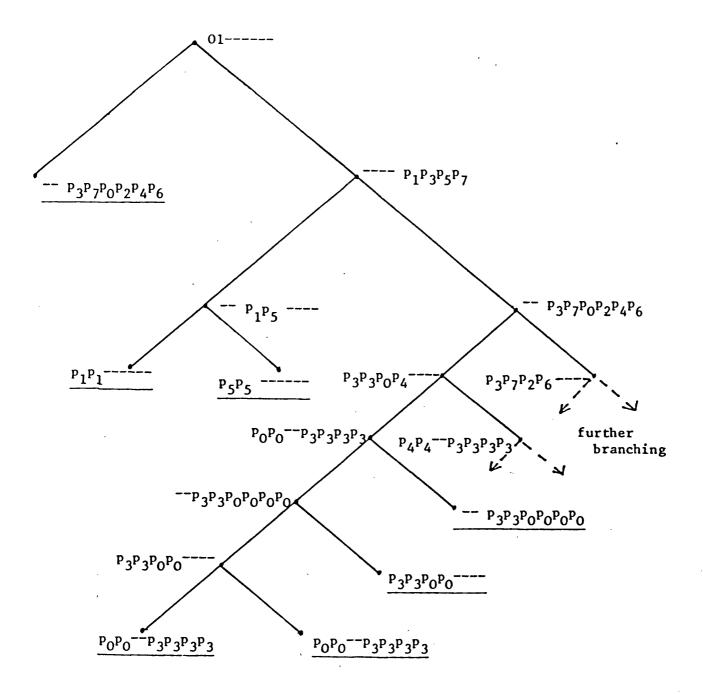

More specialised design procedures are considered where the need for flow diagrams, state tables, state reduction, and state assignment are dispensed with. These consist of reverse response trees, which are particularly easy to use, and it is shown that they can be drawn directly from either the Boolean expression of the required function or from its truth table vector.

The chapter then considers some additional features and shows that by relaxing some of the initial conditions some of the more commonly encountered systems such as code converters and serial adders can be designed.

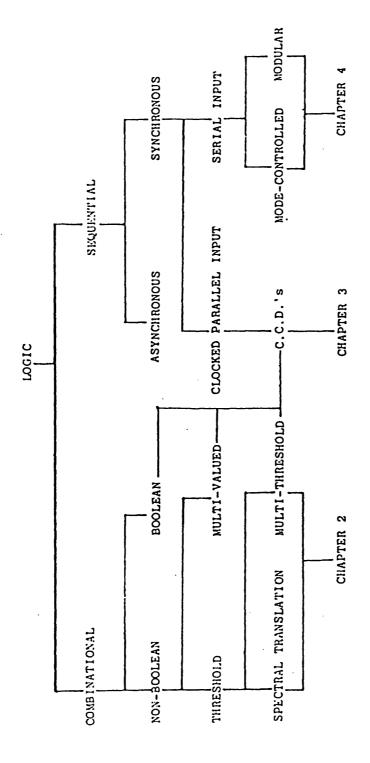

Overall, the thesis covers topics which involve many different areas of combinational and sequential logic. Figure 1.1 depicts schematically the relationship between these topics and indicates those that appear in the main chapter developments of this thesis.

Figure 1.1 Relationship between topics discussed in each chapter

#### References

- 1. Hurst, S.L.: "The Logical Processing of Digital Signals",

(Crane-Russak, New York, and Edward Arnold, London, 1978).

- Zimmerman, T.A., Allen, R.A., Jacobs, R.W.: "Digital charge-coupled logic (D.C.C.L.)", IEEE J. Solid State Circuits, SC-12, 5, pp.473-485, Oct. 1977.

- Kirkhoff, H.G., Kijstra, H.: "The application of C.C.D.'s in multiple-valued logic", Proc. 5th International Conference on Charge Coupled Devices, pp.304-309, 1979.

- 4. Daws, D.C., Jones, E.V.: "Mode-controlled serial logic systems",

IEEE International Symposium on Circuits and Systems, (Chicago),

pp.902-905, 27th-29th April 1981.

- 5. Friedman, A.D., Menon, P.R.: "Theory and Design of Switching Circuits", (Computer Science Press-Digital Design Series, 1975).

CHAPTER 2

THRESHOLD LOGIC

#### 2. Threshold Logic

#### 2.1 Single Threshold Logic .

Threshold logic has received much attention over the past twenty years [1,2,3,4] but has enjoyed very limited application. There are a number of reasons for this which will presently be discussed, but first a definition of threshold logic.

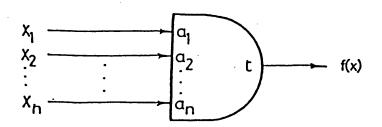

A threshold logic gate is a non-vertex gate which receives binary inputs and yields a binary output and which obeys the following equation:

$$f(x) = 1 \text{ iff } \sum_{i=1}^{n} a_i x_i \ge t$$

$$= 0 \text{ otherwise}$$

2.1

where  $a_i$  is an integer weight associated with the input variable  $x_i$  and t is an integer threshold value.

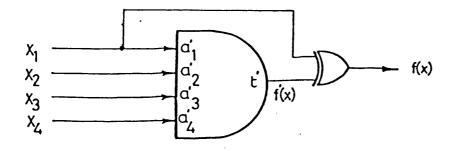

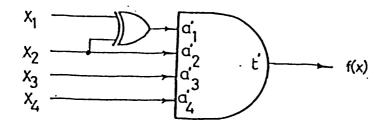

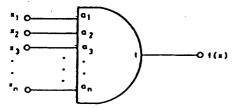

Figure 2.1 shows the conventional symbol for a threshold logic gate.

Figure 2.1 Symbol for a threshold logic gate

The first limitation of threshold logic is that although equation 2.1 is a very simple equation, it is extremely difficult to apply to a general Boolean function, firstly because not all are threshold functions, secondly because it is difficult to determine those that are from those that are not, and thirdly because of the problems of

finding suitable weights and thresholds for those that are. To a large extent these problems have been overcome by the use of tables of Chow's parameters [5,6]. Essentially, Chow showed that if a function is a threshold function then it can be uniquely characterised by n + 1 coefficients. For a given function if these coefficients are calculated, their moduli taken, and then set in descending order, they can be compared to available lists of known parameters of threshold functions, and thus determine whether or not the function is a threshold one. The tables also include optimised weights and thresholds which have been derived empirically. However, these tables are restricted to up to eight input variables only since the size of the tables become unmanageable for a greater number [7,8]. Appendix A gives a listing of Chow's parameters for up to six variables.

The second limitation of threshold logic is the physical realisation of the gate itself. Many gates have been suggested, more of which will be mentioned in the next chapter where one is proposed which consists of a charge-coupled device. However, none of these have ever been accepted commercially which is not due to any fault of the gates themselves, but to industries' lack of enthusiasm to support something having such a limited application, namely the realisation of the restricted class of simple threshold functions of up to eight input variables. Therefore work is still required to be done to extend the number of functions that it can realise. Two ways of doing this are by the use of either spectral translation or multi-threshold logic, both of which will be discussed in detail in the following sections.

#### 2.2 Spectral Translation

A spectrum is an alternative description of a function to the more conventional truth table which is used to highlight particular features that were previously concealed [1,4,9]. It is obtained by the following equation:

$$\begin{bmatrix} T \\ .F \end{bmatrix} = R$$

2.2

where R is the column matrix of the spectral coefficients F is the truth table vector of the function recoded in <1,-1> instead of <0,1>

and [T] is the  $2^n$  by  $2^n$  transform matrix.

Although there are many different transform matrices [10] one of the most commonly used is the Rademacher-Walsh, which will be the only once considered from here on. As an example of this matrix Figure 2.2 shows the case for n = 3.

| Equivalent to<br>the row entries                       | Transform matrix |    |    |    |    |     |    | Spectral function coefficients |    |                  |

|--------------------------------------------------------|------------------|----|----|----|----|-----|----|--------------------------------|----|------------------|

| <b>x</b> 0                                             | <b>1</b>         | 1  | 1  | 1  | 1  | · 1 | 1  | 1                              |    | r <sub>o</sub>   |

| × <sub>1</sub>                                         | 1                | 1  | 1  | 1  | -1 | -1  | -1 | -1                             |    | r <sub>1</sub>   |

| * <sub>2</sub>                                         | 1                | 1  | -1 | -1 | 1  | 1   | -1 | -1                             |    | r <sub>2</sub>   |

| *3                                                     | 1                | -1 | 1  | -1 | 1  | -1  | 1  | -1                             | .F | _ r <sub>3</sub> |

| $\mathbf{x}_1 \oplus \mathbf{x}_2$                     | 1                | 1  | -1 | -1 | -1 | -1  | 1  | 1                              |    | r <sub>12</sub>  |

| $x_1 \oplus x_3$                                       | 1                | -1 | 1  | -1 | -1 | 1   | -1 | 1                              |    | r <sub>13</sub>  |

| $\mathbf{x}_2 \oplus \mathbf{x}_3$                     | 1                | -1 | -1 | 1  | 1  | -1  | -1 | 1                              |    | r <sub>23</sub>  |

| $\mathbf{x}_1 \oplus \mathbf{x}_2 \oplus \mathbf{x}_3$ | 1                | -1 | -1 | 1  | -1 | 1   | 1  | -1 .                           |    | r <sub>123</sub> |

Figure 2.2 Rademacher-Walsh transform

It can be seen from Figure 2.2 that each row of the transform matrix, when converted back to the original  $\langle 0,1 \rangle$  coding, is equivalent to an input variable or the exclusive-or combination of input variables, which indicates the convention of the subscript labelling of the spectral coefficients.

If a function is a threshold function then the first n+1 coefficients, namely  $r_0r_1...r_n$  are equivalent to the Chow's parameters discussed earlier, and therefore uniquely describe that function. However, functions which are not threshold require up to the full  $2^n$  coefficients of the spectrum to describe them.

The inverse transform is readily available so that functions are retrievable from their spectra as follows:

$$2^{-n} \cdot \left[ T \right]^{-1} \cdot R = F$$

where  $\left[T\right]^{-1}$  is obtained from the relationship:

$$2^{-n} \cdot \left[T\right]^{-1} \cdot \left[T\right] = \left[I\right]$$

the unit matrix 2.4

As an example of a spectrum and its uses consider the following logic function:

$$f(x) = x_1 \cdot \overline{x}_2 + \overline{x}_1 \cdot x_2 + x_2 \cdot x_3$$

Applying the transform of equation 2.2:

Whence:

If the first n + 1 coefficients, in this case  $r_0r_1r_2r_3$ , are taken, the modulus of each found, and then placed in descending order, they can be compared with the table of Chow's b parameters in the list for n  $\leq$  3 (see Appendix A). It is found that there is no entry of 2222, and so the function is non-threshold. However, the spectrum contains the coefficient  $r_{12}$  = 6, so that if in some way this could be included in the set of n + 1 coefficients then the ordered set of their moduli would be 6222 which is among the entries in the table. One way of doing this is by "moving" or "translating" the coefficients. This is therefore known as spectral translation [4,11,12], which may be divided into two distinct operations namely output and input spectral translation.

#### 2.2.1 Output Spectral Translation

This is achieved by taking the exclusive-or of the function f'(x) with an input variable to obtain a new function f(x) which is related by equation 2.5.

$$f(x) = f'(x) \oplus x_i$$

2.5

The effect of this operation on the spectral coefficients of f'(x) is to delete i from the subscripts of coefficients which already have i in them, and to append i if they have not. In other words, pairs of coefficient values are exchanged according to the following rule:

$$r_{0} \longleftrightarrow r_{i}$$

$$r_{j} \longleftrightarrow r_{ij}$$

$$r_{ik} \longleftrightarrow r_{ijk}$$

2.6

Clearly this can be extended to include more than one input variable, in which case the subscript i in equation 2.6 is replaced by the combined subscripts of the variables involved.

In the previous example, if the exclusive-or is taken of the function and the input variable  $x_1$ , then the new spectrum is:

Comparing with the list of Chow's parameters, the relevant entry is:

parameter subscripts 0 1 2 3

b parameters 6 2 2 2

a parameters 2 1 1 1

When the a parameters are reordered and the signs reintroduced they become:

The threshold is found using the following equation:

$$t = \frac{1}{2} \cdot (\sum_{i=0}^{n} a_i + 1) = 1$$

2.7

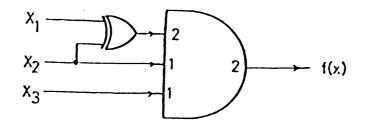

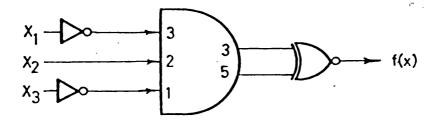

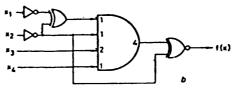

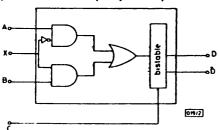

Figure 2.3 shows the final realisation of the function.

Figure 2.3 Realisation of the function  $f(x) = x_1 \cdot \overline{x}_2 + \overline{x}_1 \cdot x_2 + x_2 \cdot x_3$  using output spectral translation.

#### 2.2.2 Input Spectral Translation

This converts a function f'(x) into a new function f(x) by replacing one of its input variables with the exclusive-or of the same input variable and one other as in equation 2.8.

$$f(x_1, x_2, ..., x_i, x_j, ..., x_n) = f'(x_1, x_2, ..., x_i \oplus x_j, x_j, ..., x_n)$$

2.8

The effect on the spectral coefficients of f(x) is that if a coefficient contains i in its subscript then delete j if it is already present and append j if it is not. In other words, pairs of coefficient values are exchanged in accordance to the following rules:

$$r_{ik} \xrightarrow{r_{ij}} r_{ijk}$$

etc.

This can be extended to the situation where an input variable is replaced by the exclusive-or of itself and more than one other input variable, in which case j in equation 2.9 is replaced by the combined subscripts of the other variables involved.

Again consider the previous example, only this time replace  $\mathbf{x}_1$  by  $\mathbf{x}_1 \oplus \mathbf{x}_2$ . The new spectrum is:

The same Chow's b and a parameters are found as in the case of output spectral translation, but when reordered and the signs replaced the set of weights is found to be:

and a threshold using equation 2.7 of:

t = 2

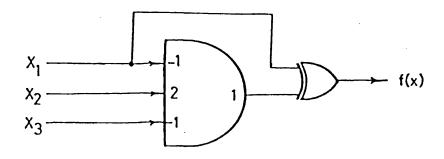

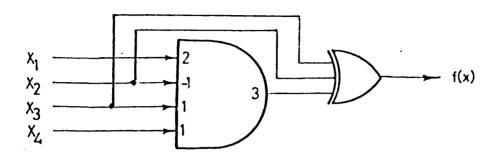

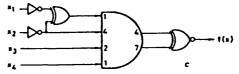

Figure 2.4 shows the final realisation of the function.

Figure 2.4 Realisation of the function  $f(x) = x_1 \cdot x_2 + x_1 \cdot x_2 + x_2 \cdot x_3$  using input spectral translation.

### 2.2.3 Rademacher-Walsh Spectral Classification

A scheme for the classification of functions has been proposed where functions are classed together if they are related by the following [4,11,12]:

- a) negation or inversion of one or more input variables

- b) permutation of one or more input variables

- c) negation or inversion of the entire function

- d) output spectral translation using one of more input variables

- e) input spectral translation involving one or more input variables

Lists can then be compiled where the entries are representative or prototype functions from each group. The first three relationships have been used for a classification system known as N.P.N. [4] (standing for negation, permutation, negation) which, for example, requires 221 entries for all functions of  $n \le 4$ . Using all five relations has yielded

the Rademacher-Walsh spectral classification which has, for example, only eight entries for  $n \le 4$  as shown in Appendix B. However, it is only convenient to use this system for up to five input variables, where 48 entries are required [13] since for n > 5 the lists are too large, for example, for  $n \le 6$  there would have to be in excess of 69,000 entries.

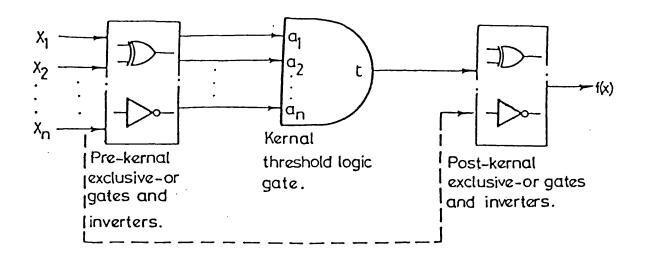

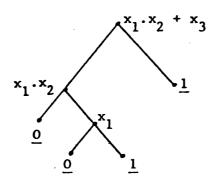

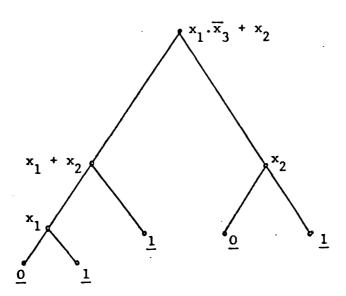

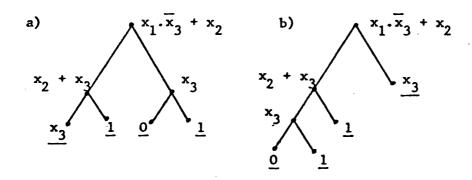

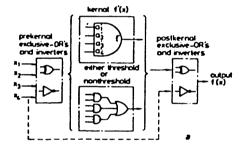

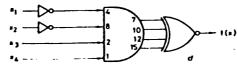

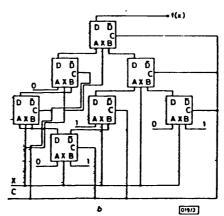

The interesting feature of this classification is that, of the eight entries for n < 4, seven are threshold functions. This means that a large proportion of non-threshold functions of four variables can be translated into threshold functions, yielding a design strategy, the topology of which is shown in Figure 2.5.

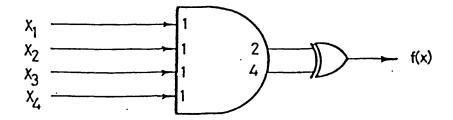

This method can be improved if the remaining non-threshold entries in the classification representative functions are found which are realised using multi-threshold gates. In the case of  $n \le 4$ , as stated earlier, there is only one such remaining entry for which the following could be a representative function:

$$f(x) = x_1.x_2 \oplus x_1.x_3 \oplus x_1.x_4 \oplus x_2.x_3 \oplus x_2.x_4 \oplus x_3.x_4$$

which has a spectrum of:

$$r_0$$

$r_1$   $r_2$   $r_3$   $r_4$   $r_{12}$   $r_{13}$   $r_{14}$   $r_{23}$   $r_{24}$   $r_{34}$   $r_{123}$   $r_{124}$   $r_{134}$   $r_{234}$   $r_{1234}$   $r_{234}$   $r_{234}$

Figure 2.6 shows the multi-threshold equivalent of this function, indicating why it is a good choice as a representative since it has unit weights and only two thresholds. If this function is chosen, then for  $n \le 4$  it is possible to realise any function using the topology of Figure 2.5 with a kernal function consisting of a threshold logic gate with at most two thresholds.

Figure 2.5 Design topology using Rademacher-Walsh spectral classification

For  $n \le 5$  there are 27 non-threshold entries, and it is proposed that multi-threshold representative functions may be chosen for these also. However, this is left for future research. For n > 5, the listing of representative functions is impractical, and so only functions belonging to groups which have single threshold representative functions can be realised using this method.

#### 2.3 Multi-threshold Logic

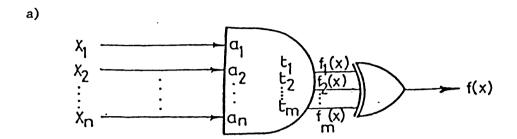

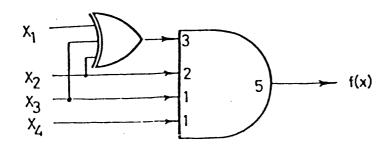

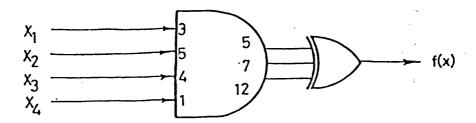

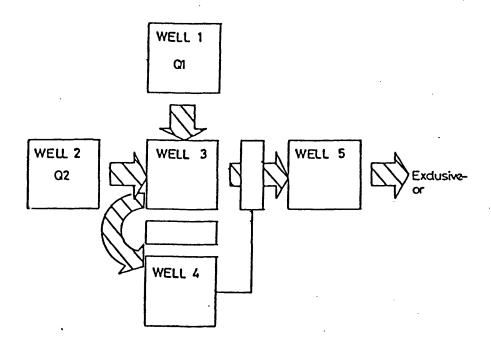

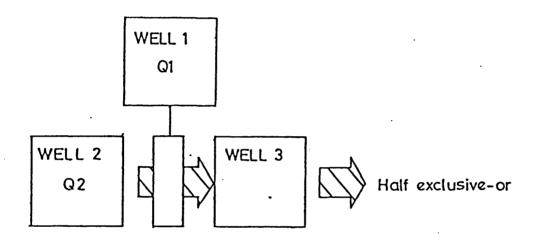

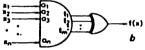

A multi-threshold gate [14,15] has more than one output each of which has a threshold associated with it and acts in exactly the same way as a single threshold gate. These outputs are then processed by an exclusive-or gate to give the final output f(x) as in equation 2.10.

$$f(x) = 1 \text{ iff } t_{2j} > \sum_{i=1}^{n} a_i x_i \ge t_{2j-1}$$

2.10

= 0 otherwise

where j = 1,2,3,etc.

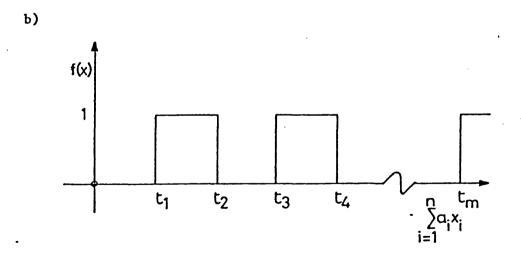

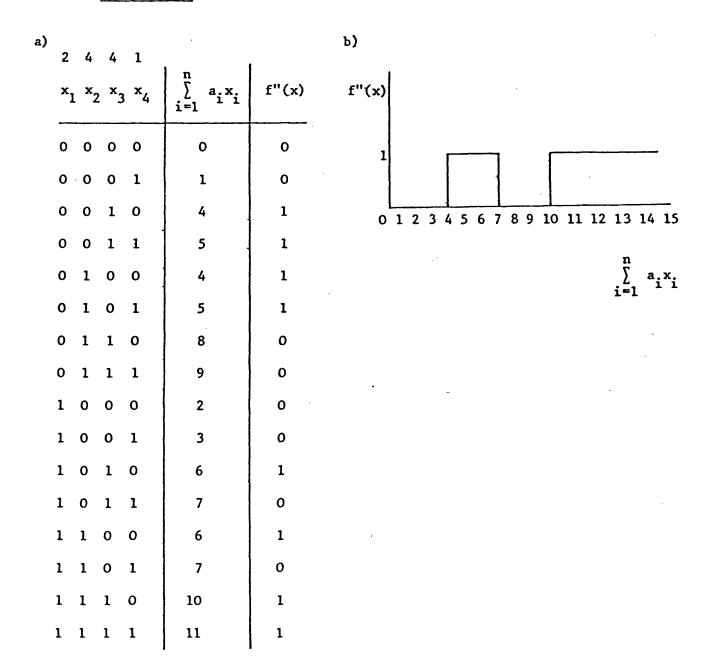

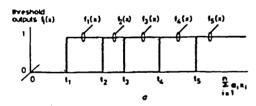

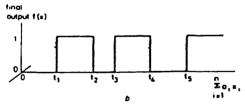

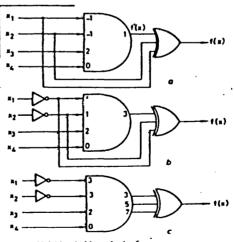

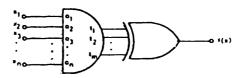

Figure 2.7(a) shows the conventional symbol for a multi-threshold logic gate and 2.7(b) shows a graphical representation of its output.

One of the most important aspects of a multi-threshold logic gate is that it is universal, i.e. any function can be realised with one. This is easily shown by considering a function to have weights  $a_i = 2^{n-i}$ , so that the sum  $\sum_{i=1}^{n} a_i x_i$  is different for every minterm position. Thresholds can then be assigned with the values of  $\sum_{i=1}^{n} a_i x_i$  where the function output changes from 0 to 1 or 1 to 0. Consider the example given in the previous section:

$$f(x) = x_1.\overline{x}_2 + \overline{x}_1.x_2 + x_2.x_3$$

Figure 2.7 (a) Symbol for a multi-threshold logic gate

(b) Multi-threshold logic gate output

Figure 2.8 shows the truth table of this function and the multithreshold solution. The function changes from 0 to 1 and 1 to 0 at points where  $\sum_{i=1}^{n} a_i x_i = 2,6,7$ , and so these values are the threshold values.

| $2^{2} 2^{1} 2^{0}$                          |                              |      | . t <sub>1</sub> =2 | t <sub>2</sub> =6  | . t <sub>3</sub> =7 |

|----------------------------------------------|------------------------------|------|---------------------|--------------------|---------------------|

| x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> | $\sum_{i=1}^{n} a_{i} x_{i}$ | f(x) | f <sub>1</sub> (x)  | f <sub>2</sub> (x) | f <sub>3</sub> (x)  |

| 0 0 0                                        | 0                            | 0    | 0                   | 0                  | 0                   |

| 0 0 1                                        | 1                            | o    | 0                   | 0                  | o                   |

| 0 1 0                                        | 2                            | 1    | 1                   | 0                  | o                   |

| 0 1 1                                        | 3                            | 1    | 1                   | 0                  | o                   |

| 1 0 0                                        | 4                            | 1    | . 1                 | 0                  | O                   |

| 1 0 1                                        | 5                            | 1    | 1                   | 0                  | O                   |

| 1 1 0                                        | 6                            | 0    | 1                   | 1                  | 0                   |

| 1 1 1                                        | 7                            | 1    | 1                   | 1                  | 1                   |

Figure 2.8 Truth table of function  $f(x) = x_1 \cdot \overline{x}_2 + \overline{x}_1 \cdot x_2 + x_2 \cdot x_3$  and a multi-threshold solution.

Thus the function is realised with a three threshold gate.

Although this weighting procedure could be applied to every function,

the values of weights are generally much larger than is necessary; for

example, the above function could be realised with a weight set of 2, 2

and 1 instead of 4, 2 and 1.

Another point about multi-threshold logic is that although it is conventional to include an exclusive-or gate at the outputs as in Figure 2.7, a simpler gate could in fact be used. Consider the following:

Since

$$t_1 < t_2 < t_3 < ... < t_m$$

2.11

then

$$f_1(x) \ge f_2(x) \ge f_3(x) \ge ... \ge f_m(x)$$

2.12

This means that it is impossible for  $f_{i+1}$  to be a 1 when  $f_i(x)$  is a 0, so that a "don't care" term appears in the truth table of Figure 2.9.

| _ | f <sub>i</sub> (x) | f <sub>i+1</sub> (x) | f(x) | _            |

|---|--------------------|----------------------|------|--------------|

|   | 0                  | 0                    | 0    |              |

|   | 0                  | 1                    | -    | cannot occur |

|   | 1                  | 0                    | 1    |              |

|   | 1                  | 1                    | 0    |              |

Figure 2.9 Truth table of f(x) showing don't care term

Assigning a value of 0 or 1 to the don't care term gives the two alternatives:

a)

$$f(x) = f_i(x) \cdot \overline{f_{i+1}(x)}$$

when the don't care = 0

b)  $f(x) = f_i(x) \cdot \overline{f_{i+1}(x)} + \overline{f_i(x)} \cdot f_{i+1}(x)$  when the don't care = 1

=  $f_i(x) \oplus f_{i+1}(x)$

The function (a), known as the "half-exclusive-or" [4], can be used in place of the conventional exclusive-or gate resulting in less gate complexity.

Finally, a single threshold gate has to perform three distinct operations:

- i) taking the product of each input variable with its associated weight,

- ii) summing all of these products,

iii) comparing the sum with the threshold to give a 0 or a 1 output.

If the first two operations are to be executed it seems wasteful not to extract the most power or usefulness from the gate by having one threshold. Indeed, in some gates such as the Digital-Summation-Threshold-Logic gate [4,12,13] more than one threshold are included in the structure, and so it would seem sensible to incorporate them into the final design.

These three reasons, namely the multi-threshold logic gates universality, the fact that the half-exclusive-or gates can be used instead of the conventional exclusive-or gates, and that the extension from a single threshold to multi-thresholds in a gate is usually available has led to the conclusion that this is the desirable solution to the problem of the realisation of non-threshold functions. However, the difficulty of this solution is the determination of the values of the weights and thresholds. Tables have been compiled  $\begin{bmatrix} 16,17 \end{bmatrix}$  which list solutions for n  $\leq$  4, but beyond this it is impractical to compile tables because they would be enormous.

The previous section showed that spectral translation can be used to find threshold solutions for at least some non-threshold functions of up to eight variables, including all functions of  $n \le 4$ . A method is proposed, therefore, to convert from the spectral translation solution to a multi-threshold one.

## 2.4 Conversion from Spectral Translation Solution to Multithreshold Solution

As stated earlier, spectral translation covers two distinct operations, output and input, each of which requires a different method of conversion to multi-threshold.

## 2.4.1 Output Spectral Translation Conversion

#### 2.4.1.1 Single Input Variable

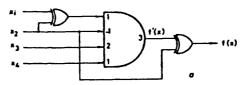

Consider the situation shown in Figure 2.10 where a four input variable threshold function f'(x) is exclusively-ored with the input variable  $x_1$  to give f(x) as in equation 2.14.

$$f(x) = f'(x) \oplus x_1$$

2.14

Since f'(x) is a threshold function it can be represented by a weight-threshold vector as in equation 2.15.

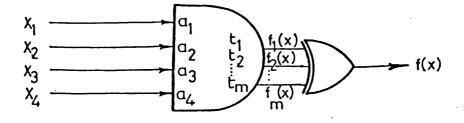

A multi-threshold equivalent of f(x) is shown in Figure 2.11, so that f(x) can be represented by a weight-threshold vector as in equation 2.16 or as an expression of the functions  $f_1(x)$  to  $f_m(x)$  in equation 2.17.

$$a_1 \ a_2 \ a_3 \ a_4; \ t_1, t_2, \dots, t_m$$

2.16

$f(x) = f_1(x) \oplus f_2(x) \oplus \dots \oplus f_m(x)$  2.17

The requirement is therefore to find functions  $f_1(x)$ ,  $f_2(x)$ , etc. which satisfy these two equations. Starting with equation 2.14, if f'(x) is decomposed about the variable  $x_1$  then:

$$f(x) = (\bar{x}_1 g_1(x) \oplus x_1 g_2(x)) \oplus x_1$$

2.18

Table 2.1 illustrates this situation.

| *1 | f'(x)              | x <sub>1</sub> |           |                                                          |

|----|--------------------|----------------|-----------|----------------------------------------------------------|

| 0  | g <sub>1</sub> (x) | 0              | Table 2.1 | Decomposition of<br>the constituent<br>functions of f(x) |

| 1  | g <sub>2</sub> (x) | 1              |           | about x <sub>1</sub>                                     |

Figure 2.10 Output spectral translation where  $f(x) = f'(x) \oplus x_1$

Figure 2.11 Multi-threshold equivalent of f(x)

Clearly, f'(x) and  $x_1$  cannot be a multi-threshold solution because they do not obey equation 2.12. If, however, the terms in Table 2.1 corresponding to  $x_1 = 1$ , namely  $g_2(x)$  and 1, are exchanged then the situation shown in Table 2.2 arises.

Table 2.2 Reordered functions

This gives  $f_1(x)$  and  $f_2(x)$  as defined in equation 2.19.

$$f_1(x) = f'(x) + x_1$$

$f_2(x) = f'(x).x_1$

2.19

Since  $f_1(x) \ge f_2(x)$  now, equation 2.12 is satisfied. Thus a valid solution has been found if it can be shown that  $f_1(x)$  and  $f_2(x)$  are threshold functions realisable with the same set of weights but different thresholds.

It can be shown that if a threshold function is decomposed about a variable then the two sub-functions formed are also threshold. Table 2.3 shows f'(x) decomposed about  $x_1$ .

Table 2.3 Decomposition of f'(x) about x<sub>1</sub> showing weight-threshold vectors

Now if a new function is considered which has the same weight-threshold vector as f'(x) but which has a constant c added to  $a_1'$  and a second threshold included having a value of the original threshold t' plus c, then its weight-threshold vector is as in equation 2.20 and its decomposition about  $x_1$  shown in Table 2.4.

$$x_1$$

$f_1(x)$

$f_2(x)$

0

$a'_2 a'_3 a'_4; t'$ ,  $t' + c$

1

$a'_2 a'_3 a'_4; t' - a'_1 - c$ ,  $t' - a'_1$

Table 2.4 Decomposition of the new function about  $x_1$

If the value of c is chosen such that it is large enough to ensure that the threshold t' + c is never reached by the sum  $\sum_{i=2}^{4} a_i x_i$ , and that the threshold t' -  $a_1'$  - c is always reached by  $\sum_{i=2}^{6} a_i x_i$ , then Table 2.4 is equivalent to Table 2.2. Therefore the function represented by equation 2.20 is a solution.

The value of the constant c can be found by the conditions stated above, namely:

$$\sum_{i=2}^{4} a_i x_i < t' + c$$

and

$$\sum_{i=2}^{4} a_i x_i \ge t' - a' - c$$

2.21

If all the weights are considered positive, which does not affect the generality of the situation, then the maximum and minimum values of  $\sum_{i=2}^{4} a_i x_i$  occur when all the  $x_i$ 's are 1 and 0 respectively, thus:

$$\sum_{i=2}^{4} a_{i} < t' + c$$

$$0 \ge t' - a'_{1} - c$$

2.22

Rearranging and making the number of input variables n for the general case:

$$c \ge \sum_{i=2}^{n} a_i - t' + 1$$

$c \ge t' - a'_i$

2.23

Note that even in the general case, the relevant variable is  $x_1$ . This means that given any one variable spectral translation involving  $x_i$ , the inputs must be permutated so that  $x_i = x_1$ . The reason for this becomes clearer later on where more complex general equations will be encountered.

Referring back to the example in section 2.2.1, Figure 2.3, a conversion can now be made, but first the weights have to be made positive. This is done by placing an inverter on any input variable that has a negative weight associated with it; the weight can then be made positive and since the threshold is related to the weights by equation 2.7, it must also be altered to a new value equivalent to its original value minus the weight values of the inputs being inverted. Since these weights were originally negative, the threshold value increases, as is shown in Figure 2.12.

Note that an inverter has been placed on the output of the exclusive-or gate. This is because when the weight  $a_1'$  is made positive by placing an inverter on  $x_1$ , due to the fact that  $x_1$  is fed forward to the exclusive-or gate, the function is unnecessarily inverted, and hence the re-inversion.

Figure 2.12 Example of output spectral translation to obtain the function  $f(x) = x_1 \cdot x_2 + x_1 \cdot x_2 + x_2 \cdot x_3$

Figure 2.13 Multi-threshold solution of  $f(x) = x_1 \cdot x_2 + x_1 \cdot x_2 + x_2 \cdot x_3$

Equation 2.23 can now be used to find the value of c.

$$c \ge 4 - 3 + 1 = 2$$

$$c \ge 3 - 1 = 2$$

$$...$$

c = 2

Equation 2.20 gives the weight-threshold vector as:

Thus the final realisation is shown in Figure 2.13.

#### 2.4.1.2 More than One Input Variable

The technique described in the previous section of taking the weight-threshold vector of the function f'(x) and increasing the relevant weight by the constant c and adding a threshold can also be applied if more than one variable is involved. Consider the situation where two input variables are exclusively-ored with the function as in equation 2.24.

$$f(x) = f'(x) \oplus x_1 \oplus x_2$$

2.24

If the constituents of f(x) are now decomposed about the variables  $x_1$  and  $x_2$  as in Table 2.5, it is immediately clear that as before these three functions do not obey equation 2.12.

| *1*2 | f'(x)               | × <sub>1</sub> | *2 |

|------|---------------------|----------------|----|

| 0 0  | g <sub>1</sub> (x)  | 0              | o  |

| 0 1  | g <sub>2</sub> (x)  | 0              | 1  |

| 10   | g <sub>3</sub> (x)  | 1              | 0  |

| 11   | g <sub>/,</sub> (x) | 1              | 1  |

Table 2.5 Decomposition of the constituents of f(x) about  $x_1$  and  $x_2$

If, as before, the terms are reorganised so that they do obey equation 2.12 then the result is shown in Table 2.6, and the functions  $f_1(x)$ ,  $f_2(x)$  and  $f_3(x)$  are as in equation 2.25.

| *1*2 | f <sub>1</sub> (x) | f <sub>2</sub> (x) | f <sub>3</sub> (x) |

|------|--------------------|--------------------|--------------------|

| 0 0  | g <sub>1</sub> (x) | 0                  | 0                  |

| 0 1  | 1                  | g <sub>2</sub> (x) | 0                  |

| 1 0  | 1                  | g <sub>3</sub> (x) | 0                  |

| 1 1  | 1                  | 1                  | g <sub>4</sub> (x) |

Table 2.6 Reorganised decomposition of the constituents of f(x)

$$f_1(x) = f'(x) + x_1 + x_2$$

$f_2(x) = f'(x).x_1 + f'(x).x_2 + x_1.x_2$  2.25

$f_3(x) = f'(x).x_1.x_2$

The requirement is, therefore, to show that  $f_1(x)$ ,  $f_2(x)$  and  $f_3(x)$  are threshold functions which can be realised with the same set of weights but different thresholds.

Consider the weight-threshold vector of equation 2.26,

$$a_1' + c a_2' + c a_3' a_4'$$

; t', t' + c, t' + 2c 2.26

Decomposed about  $x_1$  and  $x_2$  gives the situation shown in Table 2.7.

| *1*2 | f <sub>1</sub> (x)                   | f <sub>2</sub> (x)     | f <sub>3</sub> (x)     |

|------|--------------------------------------|------------------------|------------------------|

|      | a' <sub>3</sub> a' <sub>4</sub> ; t' | , t' + c               | , t' + 2c              |

|      | $a_3' a_4' ; t' - a_2' - c$          | , t' - a' <sub>2</sub> | , $t' - a_2' + c$      |

| 1 0  | a' a' ; t' - a' - c                  | , t' - a' <sub>1</sub> | $, t' - a_1' + c$      |

| 1 1  | $a_3' a_4' ; t' - a_1' - a_2' - 20$  | c, t'-a'_1-a'_2-       | $c , t' - a'_1 - a'_2$ |

Table 2.7 Decomposition of the function given in 2.26 about  $x_1$  and  $x_2$

If c is chosen such that all functions with thresholds containing the term -c are equivalent to logic 1's, and all those with thresholds containing the term +c are equivalent to logic 0's, then Tables 2.7 and 2.6 are identical. In order to achieve this, c must obey all of the following conditions:

$$c \ge t' - a_1'$$

$c \ge t' - a_2'$

$c \ge a_1' + a_3' + a_4' + 1 - t'$

$c \ge a_2' + a_3' + a_4' + 1 - t'$

Previously, it was stated that if an output spectral translation involves only one input variable, then that variable is to be called  $\mathbf{x}_1$ . Similarly, if two input variables are involved then they are to be called  $\mathbf{x}_1$  and  $\mathbf{x}_2$ , and have associated weights  $\mathbf{a}_1'$  and  $\mathbf{a}_2'$  which satisfy the condition:

$$a_1' \geqslant a_2'$$

2.28

More generally, if k variables are involved, then they are to be called  $\mathbf{x}_1$  to  $\mathbf{x}_k$  where their associated weights  $\mathbf{a}_1'$  to  $\mathbf{a}_k'$  satisfy the condition:

$$a_1' > a_2' > a_3' > \dots > a_k'$$

2.29

Thus the equation for a general conversion is:

$$a_{i} = a_{i}' + c$$

for  $i = 1$  to  $k$

$a_{i} = a_{i}'$  for  $i = k + 1$  to  $n$

2.30

$a_{i} = a_{i}' + (j - 1)c$  for  $j = 1$  to  $k + 1$

and where  $c \ge t' - a_k'$

and

$$c \ge \sum_{i=1}^{n} a_{i}' + 1 - t' - a_{k}'$$

## 2.4.1.3 Non-threshold Initial Function f'(x)

Consider the case where the initial function f'(x) is itself a non-threshold function, but which can be represented by a weight-threshold vector with p thresholds, where p > 1, as in equation 2.31.

$$a'_1 \ a'_2 \ a'_3 \ a'_4 \ ; \ t'_1, t'_2, \dots, t'_p$$

2.31

For instance, let p = 2, and exclusively-or the function with  $x_1$  to get f(x) as in equation 2.32.

$$f(x) = f'(x) \oplus x_1 = f_1'(x) \oplus f_2'(x) \oplus x_1$$

2.32

In order to convert this to a completely multi-threshold solution each function  $f_1'(x)$  has to be treated separately, as in the previous section. Thus each function is exclusively-ored with  $x_1$  as in equation 2.33.

$$f(\mathbf{x}) = f_1'(\mathbf{x}) \oplus f_2'(\mathbf{x}) \oplus \mathbf{x}_1 = (f_1'(\mathbf{x}) \oplus \mathbf{x}_1) \oplus (f_2'(\mathbf{x}) \oplus \mathbf{x}_1) \oplus \mathbf{x}_1$$

2.33

The extra  $x_1$  terms do not alter the function f(x) since  $x_1 \oplus x_1 = 0$ . Table 2.8 illustrates the functions decomposed about  $x_1$ .

| * <sub>1</sub> | f' <sub>1</sub> (x) | × <sub>1</sub> | f' <sub>2</sub> (x) | × <sub>1</sub> | × <sub>1</sub> |

|----------------|---------------------|----------------|---------------------|----------------|----------------|

| 0              | g <sub>1</sub> (x)  | 0              | h <sub>1</sub> (x)  | 0              | 0              |

| 1              | g <sub>2</sub> (x)  | 1              | h <sub>2</sub> (x)  | 1              | 1              |

Table 2.8 Decomposition of the constituent functions of f(x)

The same method as described in section 2.4.1.1 can be applied to each function, resulting firstly in the reordered functions as in Table 2.9, a weight-threshold vector as in equation 2.34 and the decomposition of this function in Table 2.10.

| <br>× <sub>1</sub> | f <sub>1</sub> (x) | f <sub>2</sub> (x) | f <sub>3</sub> (x) | f <sub>4</sub> (x) | f <sub>5</sub> (x) |  |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|

| 0                  | g <sub>1</sub> (x) | h <sub>1</sub> (x) | o                  | 0                  | 0                  |  |

| 1                  | 1                  | 1                  | 1                  | g <sub>2</sub> (x) | h <sub>2</sub> (x) |  |

Table 2.9 Reordered decomposition

$$a_1' + c a_2' a_3' a_4' ; t_1', t_2', c, t_1' + c, t_2' + c$$

2.34

$$x_1$$

$f_1(x)$

$f_2(x)$

$f_3(x)$

$f_4(x)$

$f_5(x)$

0

$a_2' a_3' a_4' ; t_1'$

$a_1' a_1' - c , t_2' - a_1' - c , -a_1' , t_1' - a_1' , t_2' - a_1'$

Table 2.10 Decomposition of the function of equation 2.34 about  $x_1$

If c is chosen as before so that thresholds containing -c belong to functions which are equivalent to logic 1's, and those with +c are equivalent to logic 0's, then Tables 2.9 and 2.10 are identical. Note that a new function has been added, namely  $\mathbf{x}_1$ , which has a threshold of c. This means that the value of c must be such that:

$$c \ge a_2' + a_3' + a_4' + 1$$

2.35  $c \ge t_2' - a_1'$

This extra function appears because initially f'(x) consisted of an even number of functions, i.e. p was even. If k variables are involved in the translation then k extra functions are required if p is even, having threshold values of c, 2c, 3c,..., kc. This can be summarised into a general equation with the thresholds ordered so that the extra ones appear last, thus:

$$a'_{i} = a'_{i} + c \qquad \text{for } i = 1 \text{ to } k$$

$$a_{i} = a'_{i} \qquad \text{for } i = k + 1 \text{ to } n$$

$$t_{j+(q-1)(k+1)} = t'_{q} + (j-1)c \qquad \text{for } j = 1 \text{ to } k + 1, \ q = 1 \text{ to } p$$

and if p is even:

$$t_{j+p(k+1)} = jc \qquad \text{for } j = 1 \text{ to } k \qquad 2.36$$

where  $c \ge t'_{p} - a'_{k}$

and  $c \ge \sum_{i=k+1}^{n} a'_{i} + 1 - \left[\frac{1-(-1)^{p}}{2}\right] \cdot \left[\sum_{i=1}^{k} a'_{i} - t'_{i}\right]$

#### 2.4.1.4 Final Adjustments

A situation which has not yet been taken into account is where some of the functions in the multi-threshold solution are identical and therefore can be cancelled out. For example, in the Tables 2.9 and 2.10, if  $h_1(x) = 0$ , then the functions  $f_2(x)$  and  $f_3(x)$  are identical, but one has a threshold of  $t_2'$  and the other a threshold of  $t_3'$  and so from the thresholds alone it may not be immediately apparent that the functions are the same. One way to overcome this problem is as follows. Firstly, note that the value of  $t_3'$  in equation 2.35 has to be greater than  $t_3' + t_3' + t_4' + t_5$ , so that the function  $t_3(x)$  in Table 2.10 is equivalent to  $t_3'$ . If the threshold  $t_3'$  is raised to  $t_3'$ , then the

function  $f_3(x)$  is unaltered if the value of c obeys the following:

$$c \ge a_2' + a_3' + a_4' + 1 - a_1'$$

2.37

Clearly this is less than that required in equation 2.35, and therefore it is an improvement. Reconsidering all five functions, the value of c must be such that:

for

$$f_1(x)$$

:  $c \ge t'_1 - a'_1$

$$f_2(x)$$

:  $c \ge t'_2 - a'_1$

$$f_3(x)$$

:  $c \ge a'_2 + a'_3 + a'_4 + 1 - a'_1$

$$f_4(x)$$

:  $c \ge a'_2 + a'_3 + a'_4 + 1 - t'_1$

and  $f_5(x)$ :  $c \ge a'_2 + a'_3 + a'_4 + 1 - t'_2$

Let

$$c = a_2' + a_3' + a_4' + 1 - a_1'$$

2.39

Then for

$$f_1(x)$$

:  $a_2' + a_3' + a_4' + 1 - a_1' \ge t_1' - a_1'$

or  $t_1' \le a_2' + a_3' + a_4' + 1$

2.40

otherwise  $g_1(x) = 0$  from Table 2.10.

If  $g_1(x) = 0$ , then  $f_1(x) = f_3(x) = x_1$ , and so  $t_1$  must be altered to  $t_3$ , i.e.  $c + a_1'$ .

The same applies to  $f_2(x)$ .

for

$$f_4(x)$$

:  $a_2' + a_3' + a_4' + 1 - a_1' \ge a_2' + a_3' + a_4' + 1 - t_1'$

or  $t_1' \ge a_1'$

2.41

otherwise  $g_2(x) = 1$  from Table 2.10.

If  $g_2(x) = 1$ , then  $f_4(x) = f_3(x) = x_1$ , and so  $t_4$  must be altered to  $t_3$ , i.e.  $c + a_1'$ .

The same applies to  $f_5(x)$ .

Thus the value of c in equation 2.39 is valid if the thresholds are:

$$t_1 = t_1' + (c + a_1' - t_1')$$

include terms in brackets if  $t_1' \ge a_2' + a_3' + a_4' + 1$

$t_2 = t_2' + (c + a_1' - t_2')$  " " " "  $t_2' \ge a_2' + a_3' + a_4' + 1$

$t_3 = c + a_1'$

$t_4 = t_1' + c + (a_1' - t_1')$  " " " "  $t_1' \le a_1'$

$t_5 = t_2' + c + (a_1' - t_2')$

$t_2' \le a_1'$

The presentation of these thresholds can be made more formal if the following function is included:

$$F = T(A \ge B)$$

where

$$F = 0 \text{ iff } A < B$$

and

$$F = 1 \text{ iff } A \ge B$$

Figure 2.14 shows the case when A and B have values of up to two.

Figure 2.14  $F = T (A \ge B)$

Using this function results, for example, in  $t_1$  from equation 2.42 becoming:

$$t_1 = t_1' + T(t_1' \ge a_2' + a_3' + a_4' + 1) \cdot \left[c + a_1' - t_1'\right]$$

2.44

A general solution can now be given which is the extension of equation 2.36 but which now has a new value for c, as in equation 2.39, and which incorporates the adjustments to the thresholds using the above method.

$$a_i = a_i^! + c$$

for  $i = 1$  to  $k$

$$a_i = a_i^!$$

for  $i = k + 1$  to  $n$

$$t_{j+(q-1)(k+1)} = t_{q}' + (j-1)c + T(t_{q}' \ge \sum_{i=k+1}^{n} a_{i}' + \sum_{i=1}^{j} a_{i}' - a_{j}' + 1).$$

$$\left[c - t_{q}' + \sum_{i=k+1-j}^{k} a_{i}' - T(j \ge k + 1). \left[a_{0}'\right]\right]$$

$$+ T(\sum_{i=k+1-j}^{k} a_{i}' - a_{k+1-j}' \ge t_{q}'). \left[\sum_{i=k+1-j}^{k} a_{i}' - t_{q}' - a_{k+1-j}'\right]$$

for j = 1 to k+1, q = 1 to p

If p is even then:

$$t_{p(k+1)+j} = jc + \sum_{i=k+1-j}^{k} a_i^t \quad \text{for } j = 1 \text{ to } k$$

where:

$$c = \sum_{i=1}^{n} a_{i}^{!} - \sum_{\substack{i=2k+1+(-1)^{k+1}\\4}}^{k} a_{i}^{!} - \sum_{\substack{i=2k+3+(-1)^{k}\\4}}^{k} a_{i}^{!} + 1$$

Although this equation can be applied easily with the aid of a computer, by hand it is difficult to use. However, the method described in section 2.3 and shown in Figure 2.8 for proving the universality of multi-threshold logic can be adopted with the weights from equation 2.45 being used. Both methods are shown in the following example.

#### Example

$$f(x) = \overline{x_1.x_2.x_3 + x_1.x_2.x_3 + x_1.x_2.x_3 + x_2.x_3.x_4 + x_1.x_3.x_4}$$

The spectrum of this function is:

Comparing the first five coefficients with the tables of Chow's parameters shows that there is no entry for  $n \le 4$  which is 44000, and so the function is non-threshold. However, if the function is exclusively-ored with  $x_2$  and  $x_3$ , then output spectral translation results in the spectrum:

The tables of Chow's parameters have an entry of 88444; therefore this function is a threshold function, and the corresponding a parameters are 22111. Thus:

Using equation 2.7 gives:

$$t = 3$$

Thus the weight-threshold vector of f(x) is:

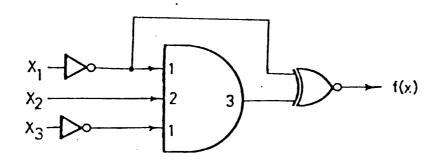

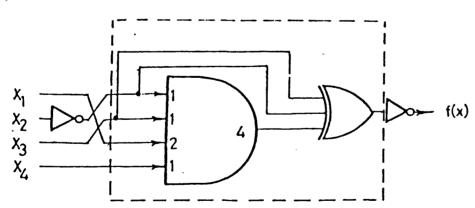

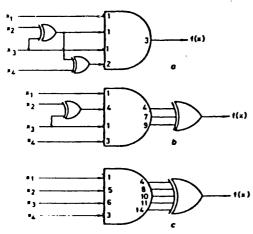

Figure 2.15(a) shows the final realisation of f(x), and Figure 2.15(b) shows the initial adjustments which have to be made in order that a conversion to multi-threshold can occur, namely the weights must be made positive, and the relevant input variables which are involved in the translation must be ordered according to equation 2.29.

**b**)

Figure 2.15 (a) Solution to function f(x)

(b) Reorganised function f(x) with positive weights

The function shown inside the dotted line can now be converted to multi-threshold using equation 2.45.

In this example k = 2, n = 4.

$$c = \sum_{i=1}^{4} a_{i}^{!} - \sum_{i=1}^{2} a_{i}^{!} - \sum_{i=2}^{2} a_{i}^{!} + 1 = a_{3}^{!} + a_{4}^{!} - a_{2}^{!} + 1 = 3$$

Thus,  $a_1 = 4$ ,  $a_2 = 4$ ,  $a_3 = 2$ ,  $a_4 = 1$ .

The thresholds according to equation 2.45 are therefore:

$$k = 2$$

,  $n = 4$ ,  $q = 1$ ,  $c = 3$ ,  $t' = 4$ .

$$t_{j} = 4 + (j - 1) \cdot 3 + T(4 \ge 3 + \sum_{i=1}^{j} a'_{i} - a'_{j+1}) \cdot \left[3 - 4 + \sum_{i=3-j}^{2} a'_{i}\right]$$

-

$$T(j \ge 3) \cdot \begin{bmatrix} a'_0 \end{bmatrix} + T(\sum_{i=3-j}^{2} a'_i - a'_{3-j} \ge 4) \cdot \begin{bmatrix} \sum_{i=3-j}^{2} a'_i - 4 - a'_{3-j} \end{bmatrix}$$

for

$$j = 1$$

to 3

$$t_{1} = 4 + T(4 \ge 4) \cdot \begin{bmatrix} -1 + 1 \end{bmatrix} + T(0 \ge 4) \cdot \begin{bmatrix} -4 \end{bmatrix} = 4$$

$$t_{2} = 4 + 3 + T(4 \ge 4 + 1) \cdot \begin{bmatrix} -1 + 2 \end{bmatrix} + T(1 \ge 4) \cdot \begin{bmatrix} 1 - 4 \end{bmatrix} = 7$$

$$t_{3} = 4 + 6 + T(4 \ge 4 + 2) \cdot \begin{bmatrix} -1 + 2 \end{bmatrix} + T(2 \ge 4) \cdot \begin{bmatrix} 2 - 4 \end{bmatrix} = 10$$

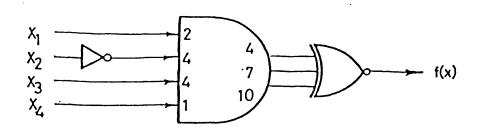

The solution is shown in Figure 2.16.

The thresholds could also have been calculated by using  $\sum_{i=1}^{n} a_i x_i$  with the  $a_i$  values of 2,4,4,1 calculated as before, and comparing with the function  $\overline{f(x_1,x_2,x_3,x_4)} = f''(x)$  as in Figure 2.17.

Thus comparing  $\sum_{i=1}^{n} a_i x_i$  with f''(x) in Figure 2.17(a) shows that f''(x) changes from 0 to 1 at values of 4 and 10, and 1 to 0 at the value of 7, which can be represented as in Figure 2.17(b).

Figure 2.16 Multi-threshold solution of f(x)

Figure 2.17 (a) Truth table of function f"(x)

(b) Graphical illustration of multi-threshold solution of f"(x)

## 2.4.2 Input Spectral Translation Conversion

## 2.4.2.1 Single Input Variable

Consider the situation shown in Figure 2.18 of a four input variable threshold function f'(x) where its input variable  $x_1$  has been replaced by the exclusive-or function of  $x_1$  and  $x_2$  as in equation 2.46.

Figure 2.18 Input spectral translation where  $x_1$  is replaced by  $x_1 \oplus x_2$ , to give f(x)

$$f(x_1,x_2,x_3,x_4) = f'(x_1 \oplus x_2,x_2,x_3,x_4)$$

2.46

As in section 2.4.2.2, since f'(x) is a threshold function it can be represented by the weight-threshold vector of equation 2.15, and the multi-threshold equivalent function can be represented as in Figure 2.11 and equations 2.16 and 2.17. The requirement is therefore to find a set of functions  $f_1(x)$  to  $f_m(x)$  which satisfy equations 2.16 and 2.17 and which, when exclusively-ored, give the function f(x).

If f'(x) is decomposed about the variables  $x_1$  and  $x_2$  then:

$$f'(x) = \overline{x}_1 \cdot \overline{x}_2 \cdot g_1(x) + \overline{x}_1 \cdot x_2 \cdot g_2(x) + x_1 \cdot \overline{x}_2 \cdot g_3(x) + x_1 \cdot x_2 \cdot g_4(x)$$

2.47

Substituting  $x_1 \oplus x_2$  for  $x_1$  to give f(x):

$$f(x) = \overline{x}_1 \cdot \overline{x}_2 \cdot g_1(x) + \overline{x}_1 \cdot x_2 \cdot g_4(x) + x_1 \cdot \overline{x}_2 \cdot g_3(x) + x_1 \cdot x_2 \cdot g_2(x)$$

2.48

This is illustrated in Table 2.11

| *1 *2 | f'(x)              | f(x)               |

|-------|--------------------|--------------------|

| 0 0   | g <sub>1</sub> (x) | g <sub>1</sub> (x) |

| 0 1   | g <sub>2</sub> (x) | g <sub>4</sub> (x) |

| 1 0   | g <sub>3</sub> (x) | g <sub>3</sub> (x) |

| 1 1   | g <sub>4</sub> (x) | g <sub>2</sub> (x) |

Table 2.11 Decomposition of f'(x) and f(x) about  $x_1$  and  $x_2$

Now consider the set of functions given in equation 2.49.

$$f_{1}(x) = g_{1}(x) + x_{1} + x_{2}$$

$$f_{2}(x) = x_{1} + x_{2}$$

$$f_{3}(x) = x_{1} \cdot g_{3}(x) + x_{2} \cdot g_{4}(x) + x_{1} \cdot x_{2}$$

$$f_{4}(x) = x_{1} \cdot x_{2}$$

$$f_{5}(x) = x_{1} \cdot x_{2} \cdot g_{2}(x)$$

2.49

Decomposing each of these functions about  $x_1$  and  $x_2$  gives:

| *1*2 | f <sub>1</sub> (x) | f <sub>2</sub> (x) | f <sub>3</sub> (x) | f <sub>4</sub> (x) | f <sub>5</sub> (x) |

|------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 0 0  | g <sub>1</sub> (x) | 0                  | 0                  | 0                  | 0                  |

| 0 1  | 1                  | 1                  | g <sub>4</sub> (x) | 0                  | 0                  |

| 1 0  | 1                  | 1                  | g <sub>3</sub> (x) | 0                  | o                  |

| 1 1  | 1                  | 1                  | 1                  | 1                  | g <sub>2</sub> (x) |

<u>Table 2.12</u> Decomposition of the function  $f_1(x)$  to  $f_5(x)$

It can be seen from Table 2.12 that if the five functions are exclusively-ored then the result is f(x), and thus these functions represent a solution which obeys equation 2.12. Thus, if these functions are threshold and can be represented by the same weights but different thresholds then a multi-threshold solution has been found.

The decomposition of the function, represented by the weight-threshold vector of equation 2.50, about  $\mathbf{x}_1$  and  $\mathbf{x}_2$  is shown in Table 2.13.

$$c a'_{2} + c a'_{3} a'_{4}$$

; t',c,t' + c -  $a'_{1}$ , 2c +  $a'_{2}$ , t' + 2c 2.50

| *1*2 | f <sub>1</sub> (x)                                                                               | f <sub>2</sub> (x)       | f <sub>3</sub> (x)                       | f <sub>4</sub> (x) f <sub>5</sub> | (x)                  |

|------|--------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------|-----------------------------------|----------------------|

| 0 0  | a' <sub>3</sub> a' <sub>4</sub> ; t'<br>a' <sub>3</sub> a' <sub>4</sub> ; t' - a' <sub>2</sub> - | , c                      | , t' + c <sup>1</sup> a' <sub>1</sub>    | , 2c + a' <sub>2</sub> , t'       | + 2c                 |

| 0 1  | a' a' ; t' - a' -                                                                                | c , -a' <sub>2</sub>     | , t' - a' <sub>1</sub> - a' <sub>2</sub> | , c , t'                          | - a <sub>2</sub> + c |

| 1 0  | a' <sub>3</sub> a' <sub>4</sub> ; t' - c                                                         | , 0                      | , t' - a' <sub>1</sub>                   | , c + $a_{2}^{1}$ , t'            | + c                  |

| 1 1  | a' <sub>3</sub> a' <sub>4</sub> ; t' - c<br>a' <sub>3</sub> a' <sub>4</sub> ; t' - a' -          | 2c, -a' <sub>2</sub> - c | , t' - a' - a' -                         | c, 0 , t'                         | - a <sub>2</sub> '   |

Table 2.13 Decomposition of weight-threshold vector of equation 2.50 about  $x_1$  and  $x_2$

If in Table 2.13 all weights are considered positive, then all functions with thresholds which are negative, 0, or contain -c can be considered logic 1's, and those containing +c as logic 0's so that Table 2.13 is equivalent to Table 2.12. The value of c must be chosen, therefore, such that all the following conditions are obeyed:

for

$$f_1(x)$$

:  $c \ge t'$

$f_2(x)$ :  $c \ge a_3' + a_4' + 1$

$f_3(x)$ :  $c \ge a_1' + a_3' + a_4' + 1 - t'$  and  $c \ge t' - a_1' - a_2'$  2.51

$f_4(x)$ :  $c \ge a_3' + a_4' + 1$

and  $f_5(x)$ :  $c \ge a_2' + a_3' + a_4' + 1 - t'$

Let

$$c = a_3' + a_4' + 1$$

2.52

which immediately satisfies  $f_2(x)$  and  $f_4(x)$ .

Then for

$$f_1(x)$$

:  $a_3' + a_4' + 1 \ge t'$  2.53

otherwise  $g_1(x) = 0$  from Table 2.12.

If  $g_1(x) = 0$ , then  $f_1(x) = f_2(x)$ , and so  $t_1$  can be altered to t<sub>2</sub>, i.e. c.

For

$$f_3(x)$$

:  $a_3' + a_4' + 1 \ge a_1' + a_3' + a_4' + 1 - t'$

or  $t' \ge a_1'$

otherwise  $g_4(x) = g_3(x) = 1$  from Table 2.12.

If  $g_4(x) = g_3(x) = 1$ , then  $f_3(x) = f_2(x)$  and so  $t_3$  can be altered to t<sub>2</sub>, i.e. c.

Also:

$$a_3' + a_4' + 1 \ge t' - a_1' + a_2'$$

or  $a_1' + a_2' + a_3' + a_4' + 1 \ge t'$  2.55

otherwise  $g_4(x) = g_3(x) = 0$  from Table 2.12.

If  $g_4(x) = g_3(x) = 0$ , then  $f_3(x) = f_4(x)$  and so  $t_3$  can be altered to  $t_4$ , i.e.  $2c + a_2'$ .

For

$$f_5(x)$$

:  $a_3' + a_4' + 1 \ge a_2' + a_3' + a_4' + 1 - t'$

or  $t' \ge a_2'$  2.56

otherwise  $g_2(x) = 1$  from Table 2.12.

If  $g_2(x) = 1$ , then  $f_5(x) = f_4(x)$  and so  $t_5$  can be altered to  $t_4$ , i.e.  $2c + a_2^{\dagger}$ .

Thus c in equation 2.52 is valid if the equations for the thresholds are as follows, where  $T(A \geqslant B)$  is as before in equation 2.43:

$$t_{1} = t' + T(t' \ge a_{3}' + a_{4}' + 1) \cdot \left[c - t'\right]$$

$$t_{2} = c$$

$$t_{3} = t' + c - a_{1}' + T(a_{1}' \ge t') \cdot \left[a_{1}' - t'\right] + T(t' \ge a_{1}' + a_{2}' + a_{3}' + a_{4}' + 1) \cdot \left[c + a_{1}' + a_{2}' - t'\right]$$

$$t_{4} = 2c + a_{2}'$$

$$t_{5} = t' + 2c + T(a_{2}' \ge t') \cdot \left[a_{2}' - t'\right]$$

2.57

2.57

The general solution for n input variables is therefore:

$$t_1 = t' + T(t' \ge \sum_{i=3}^{n} a_i' + 1) \cdot [c - t']$$

$$t_2 = c$$

$$t_3 = t' + c - a_1' + T(a_1' \ge t') \cdot \left[ a_1' - t' \right] + T(t' \ge \sum_{i=1}^{n} a_i' + 1) \cdot \left[ c + a_1' + a_2' - t' \right]$$

2.58

$$t_{4} = 2c + a_{2}^{\prime}$$

$$t_5 = t' + 2c + T(a_2' \ge t'). [a_2' - t']$$

where

$$c = \sum_{i=3}^{n} a_i^i + 1$$

Note that the general solution applies only to situations where the variable  $x_1$  is replaced by  $x_1 \oplus x_2$ , so that if a function has an input variable  $x_i$  replaced by  $x_i \oplus x_j$ , its inputs must be reordered such that i = 1, j = 2.

# 2.4.2.2 Non-threshold Initial Function f'(x)

This situation is identical to that at the start of section 2.4.1.3, so that f'(x) is still as in equation 2.31. Again, in order to find the multi-threshold solution to f(x), each of the functions  $f'_i(x)$  are treated separately, and so in this case each would be expanded into five threshold functions according to equation 2.58. For example, consider a two threshold function f'(x) as in equation 2.59.

$$a'_1$$

$a'_2$   $a'_3$   $a'_4$ ;  $t'_1, t'_2$

Using equation 2.58, the five thresholds for each new function are:

a)

$$t_1 = t_1' + T(t_1') \ge \sum_{i=3}^{n} a_i' + 1$$

.  $\left[c - t_1'\right]$

$t_2 = c$

$t_3 = t_1' + c - a_1' + T(a_1') \ge t_1'$ .  $\left[a_1' - t_1'\right] + T(t_1') \ge \sum_{i=1}^{n} a_i' + 1$ .  $\left[c + a_1' + a_2' - t_1'\right]$

$t_4 = 2c + a_2'$

$t_5 = t_1' + 2c + T(a_2') \ge t_1'$ .  $\left[a_2' - t_1'\right]$

b)  $t_1 = t_2' + T(t_2') \ge \sum_{i=3}^{n} a_i' + 1$ .  $\left[c - t_2'\right]$

$t_5 = c$

$t_7 = c$

$t_7 = c$

$t_8 = c$

Clearly each expansion of five thresholds contains  $t_2$  and  $t_4$  which are independent of the original threshold and pairs of them can be cancelled out. Thus if the original function f'(x) has p thresholds, then each one expands into three new thresholds which are obtained as  $t_1$ ,  $t_3$  and  $t_5$  in equation 2.58, and if p is odd then two more are added which are equivalent to  $t_2$  and  $t_4$ .

#### 2.4.2.3 More than One Input Variable

In this case, an input variable is replaced by the exclusive-or function of the same input variable and more than one other. Consider the situation of the function in equation 2.61.

$$f(x_1, x_2, x_3, x_4) = f'(x_1 \oplus x_2 \oplus x_3, x_2, x_3, x_4)$$

2.61

Table 2.14 shows the decomposition of this function f'(x) about  $x_1, x_2$  and  $x_3$ . Also shown is a set of seven functions which when exclusively-ored with each other give the function f(x).

| *1*2*3 | f'(x)              | f <sub>1</sub> (x) | f <sub>2</sub> (x) | f <sub>3</sub> (x) | f <sub>4</sub> (x) | f <sub>5</sub> (x) | f <sub>6</sub> (x) | f <sub>7</sub> (x) | f(x)               |

|--------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 0 0 0  | g <sub>1</sub> (x) | g <sub>1</sub> (x) | 0                  | 0                  | О                  | 0                  | 0                  | 0                  | g <sub>1</sub> (x) |

| 0 0 1  | g <sub>2</sub> (x) | 1                  | 1                  | g <sub>6</sub> (x) | 0                  | 0                  | 0                  | 0                  | g <sub>6</sub> (x) |

| 0 1 0  | g <sub>3</sub> (x) | 1                  | 1                  | g <sub>7</sub> (x) | 0                  | 0                  | 0                  | 0                  | g <sub>7</sub> (x) |

| 0 1 1  | g <sub>4</sub> (x) | 1                  | 1                  | 1                  | 1                  | g <sub>4</sub> (x) | 0                  | 0                  | g <sub>4</sub> (x) |

| 100    | g <sub>5</sub> (x) | 1                  | 1                  | g <sub>5</sub> (x) | 0                  | 0                  | 0                  | 0                  | g <sub>5</sub> (x) |

| 101    | g <sub>6</sub> (x) | 1                  | 1 .                | 1                  | 1                  | g <sub>2</sub> (x) | 0                  | 0                  | g <sub>2</sub> (x) |

| 110    | g <sub>7</sub> (x) | 1                  | 1                  | 1                  | 1                  | g <sub>3</sub> (x) | 0                  | 0                  | g <sub>3</sub> (x) |

| 111    | g <sub>8</sub> (x) | 1                  | 1                  | 1                  | 1                  | 1                  | 1                  | g <sub>8</sub> (x) | g <sub>8</sub> (x) |

Table 2.14 Decomposition of f(x), f'(x) and  $f_1(x)$  to  $f_7(x)$ , about  $x_1$ ,  $x_2$  and  $x_3$

The functions  $f_1(x)$  to  $f_7(x)$  satisfy equation 2.12, and so it is required to show that they are threshold functions which can be realised with the same set of weights but different thresholds to obtain a multithreshold solution.

Table 2.15 shows the decomposition of the function, represented by the weight-threshold vector of equation 2.62, about the variables  $\mathbf{x}_1$ ,  $\mathbf{x}_2$  and  $\mathbf{x}_3$ .

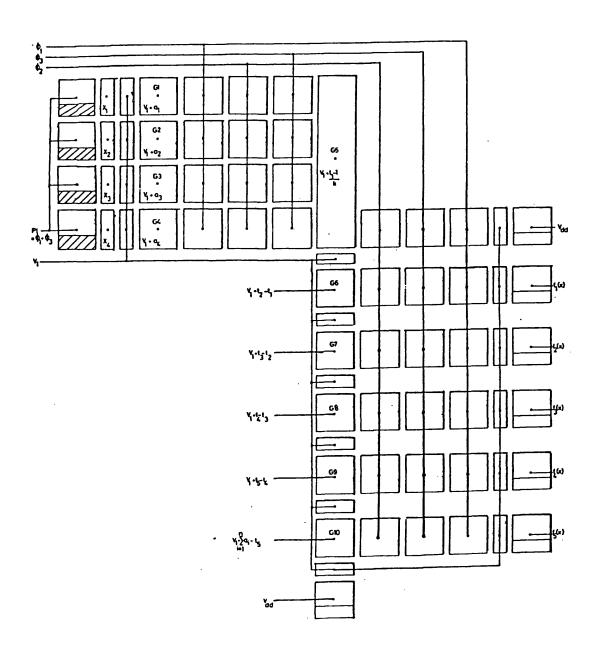

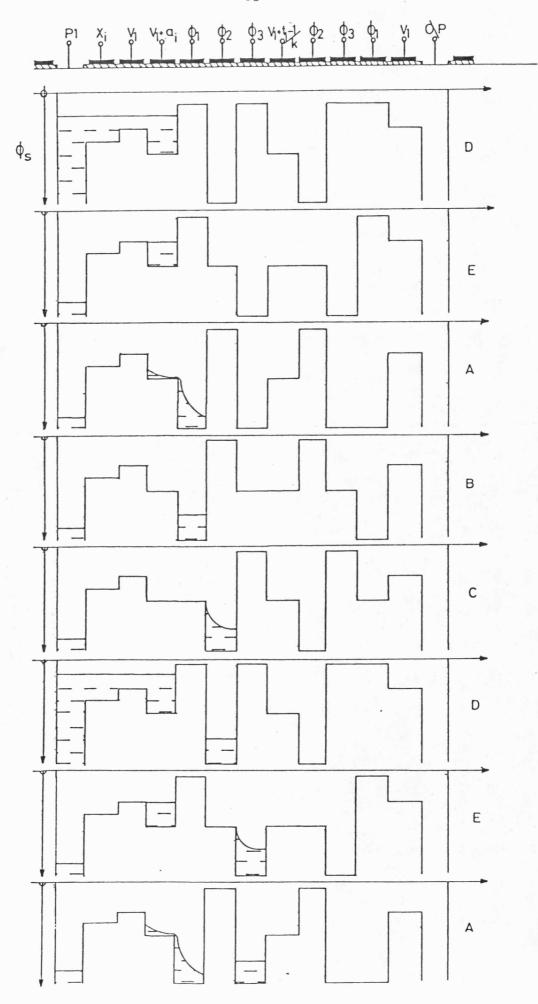

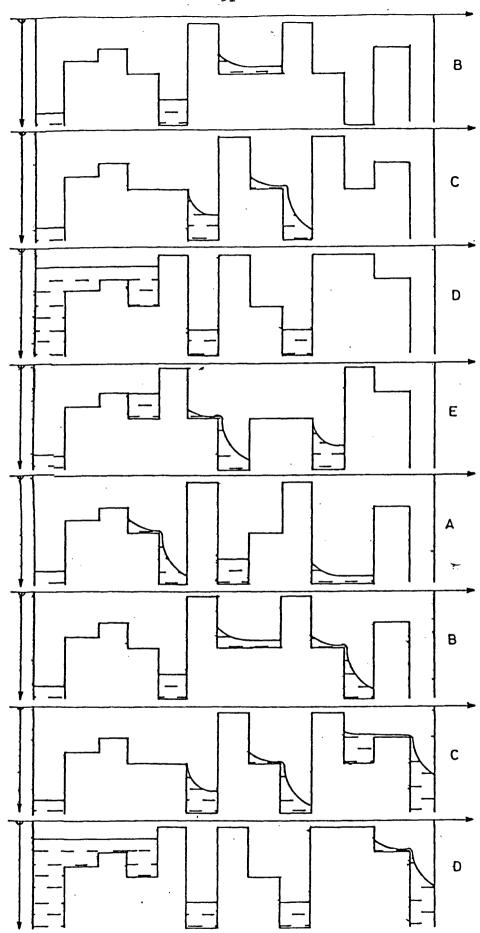

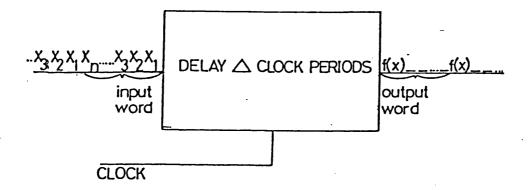

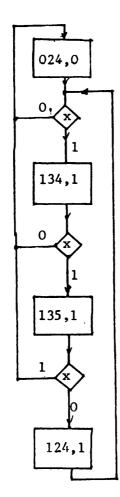

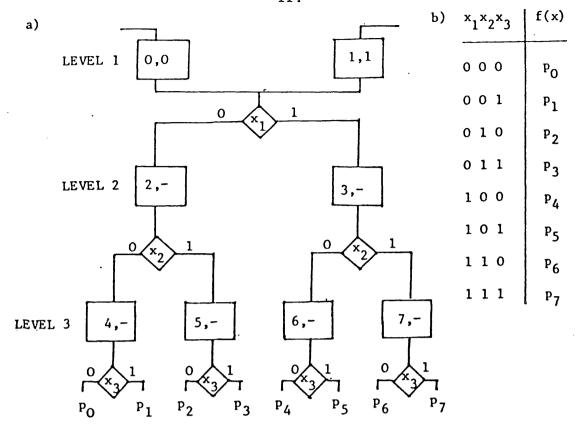

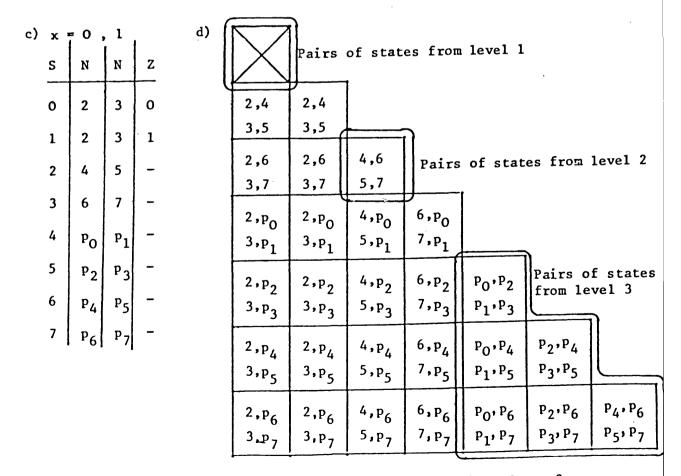

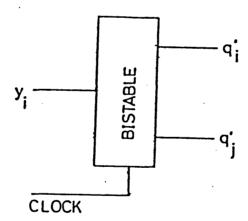

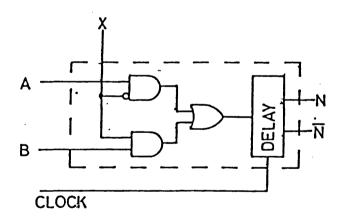

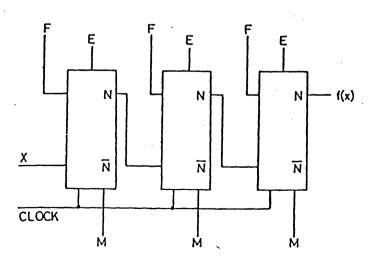

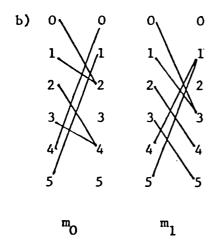

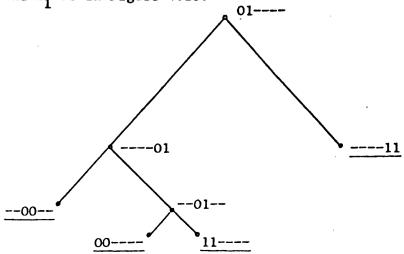

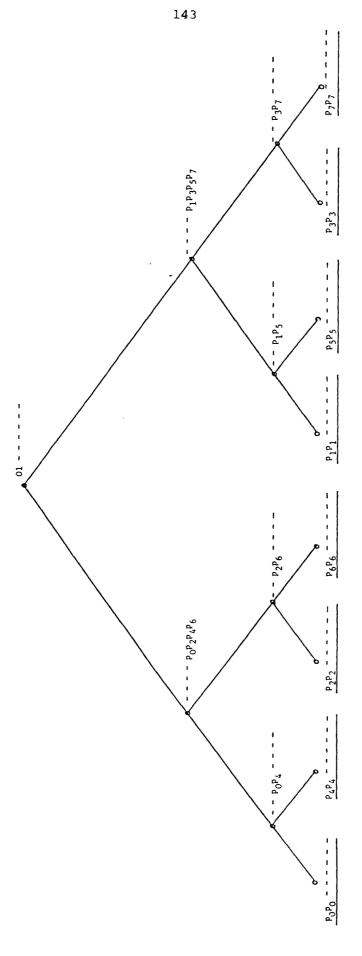

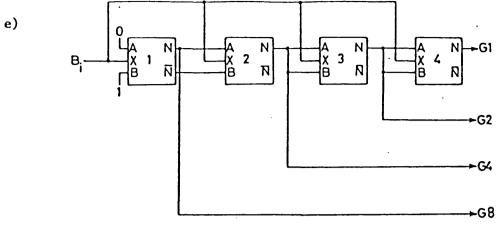

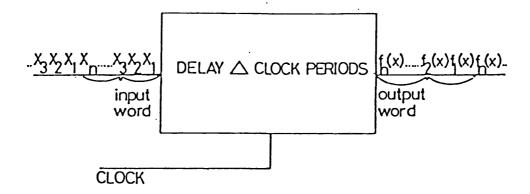

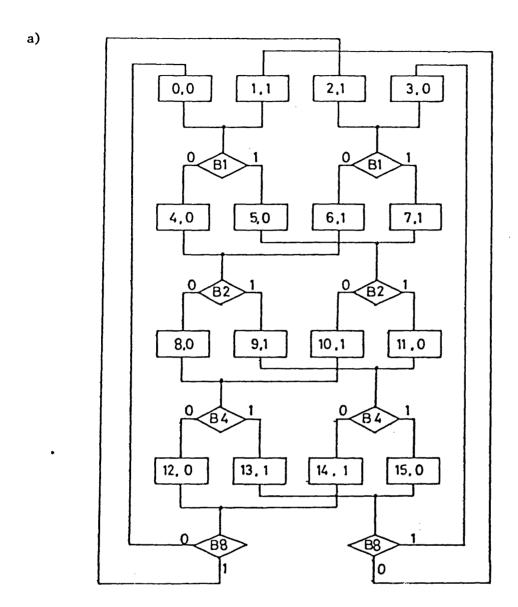

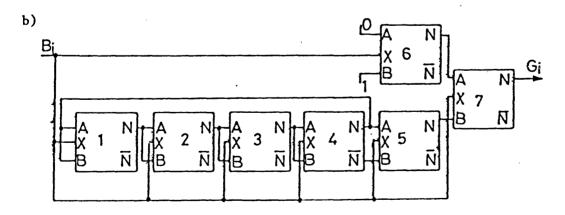

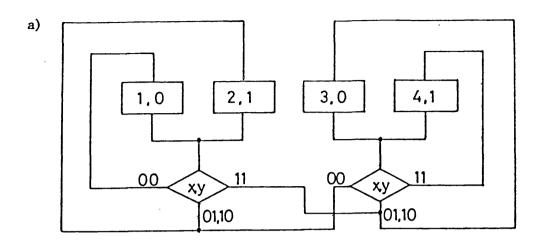

| x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> |             | f <sub>1</sub> (x) | f <sub>2</sub> (x) | f <sub>3</sub> (x)                                                | f <sub>4</sub> (x)                                             | f <sub>5</sub> (x) | f <sub>6</sub> (x)   | f <sub>7</sub> (x)       |