## PHD

#### Application of fault tolerant techniques to a real time control system.

Jackson, P. R.

Award date: 1983

Awarding institution: University of Bath

Link to publication

## Alternative formats If you require this document in an alternative format, please contact: openaccess@bath.ac.uk

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### APPLICATION OF FAULT TOLERANT TECHNIQUES

#### TO A REAL TIME CONTROL SYSTEM

submitted by P.R. Jackson B.Sc. for the degree of Ph.D. of the University of Bath 1983

#### COPYRIGHT

Attention is drawn to the fact that copyright of this thesis rests with the author. This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from this thesis and no information derived from it may be published without the prior written consent of the author.

This thesis may not be consulted, photocopied or lent to other libraries without the permission of the author for five years from the date of acceptance of the thesis.

P. Jackson

ProQuest Number: U641730

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest U641730

Published by ProQuest LLC(2015). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code. Microform Edition © ProQuest LLC.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# CONTENTS

| Synopsis. | (ix) |

|-----------|------|

|           |      |

|           |      |

| List of Symbols. | (x) |

|------------------|-----|

|                  |     |

| List of Figures. | (×i) |

|------------------|------|

| Chapter 1. | Introdu | age Page      |                | age 1                 |      |

|------------|---------|---------------|----------------|-----------------------|------|

|            | 1.1.    | Research      | Objectives.    |                       | 2    |

|            | 1.2.    | Research      | Model.         |                       | 3    |

|            | 1.3.    | Systems I     | mplementatio   | n and Investigation.  | 3    |

| Chapter 2. | Techni  | ques for Re   | liable System  | s Design.             | 5    |

|            | 2.1.    | Failures,     | Errors and Fa  | oults.                | 5    |

|            | 2.2.    | Fault Ave     | oidance.       |                       | 5    |

|            | 2.3.    | Fault Ren     | noval.         |                       | 8    |

|            | 2.4.    | Fault Tol     | erance.        |                       | 9    |

|            |         | 2.4.1.        | Characteris    | ation of Faults.      | 10   |

|            |         | 2.4.2.        | Redundancy     | / Techniques.         | 11   |

|            |         | 2.4.3.        | Fault Recov    | very.                 | 12   |

|            |         | 2.4.4.        | Fault Toler    | ant Software.         | 13   |

|            |         |               | 2.4.4.1.       | N-Version Programming | . 13 |

|            |         |               | 2.4.4.2.       | The Recovery Block.   | 14   |

|            | 2.5.    | Reliabili     | ty Modelling.  |                       | 15   |

|            |         | 2.5.1.        | Software Re    | eliability Modelling. | 16   |

|            |         | 2.5.2.        | Hardware R     | eliability Modelling. | 17   |

| Chapter 3. | Analys  | sis of a Sing | gle Microproc  | essor System.         | 19   |

|            | 3.1.    | Cause an      | d Effect of Fo | ults in a Typical     | 19   |

|            |         | Micropro      | cessor System  | •                     |      |

|            | 3.2.    | Discussio     | n of Failure / | Mode Effects.         | 25   |

| Chapter 4. | Real Ti | me Systems           | Description.  |                       | Page 27 |

|------------|---------|----------------------|---------------|-----------------------|---------|

|            | 4.1.    | Design O             | verview.      |                       | 27      |

|            | 4.2.    | Target Tr            | acking.       |                       | 28      |

|            |         | 4.2.1.               | Target Data   | Input.                | 28      |

|            |         | 4.2.2.               | Azimuth Inf   | nibit.                | 29      |

|            |         | 4.2.3.               | Range Inhib   | it.                   | 29      |

|            |         | 4.2.4.               | Approach/R    | ecede Identification. | 29      |

|            |         | 4.2.5.               | Missile Cov   | erage.                | 30      |

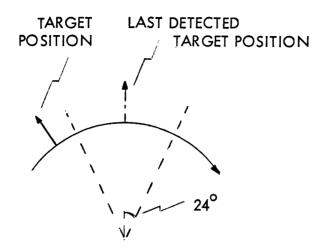

|            |         |                      | 4.2.5.1.      | Search Mode.          | 30      |

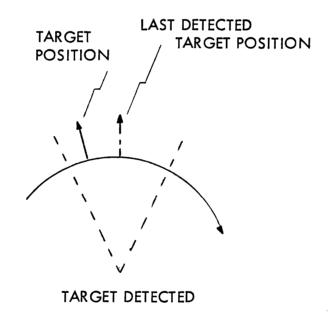

|            |         |                      | 4.2.5.2.      | Track Mode.           | 30      |

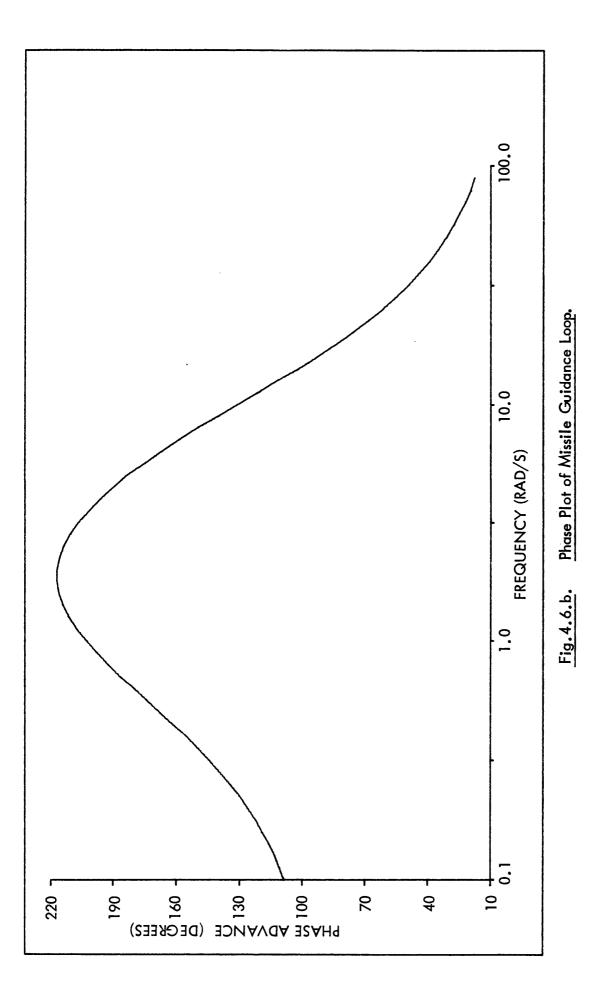

|            | 4.3.    | Missile G            | duidance Loop |                       | 30      |

| Chapter 5. | Modell  | ing of Real          | Time System.  |                       | 32      |

|            | 5.1.    | Target Si            | mulation.     |                       | 32      |

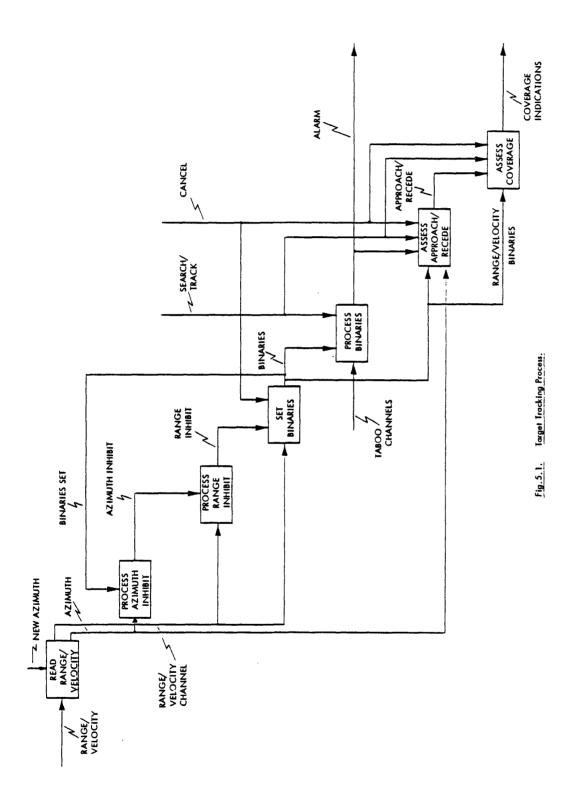

|            | 5.2.    | Target Tr            | acking Proces | s.                    | 33      |

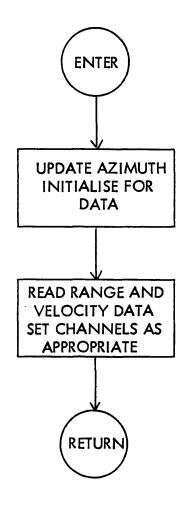

|            |         | 5.2.1.               | Read Routin   | e.                    | 33      |

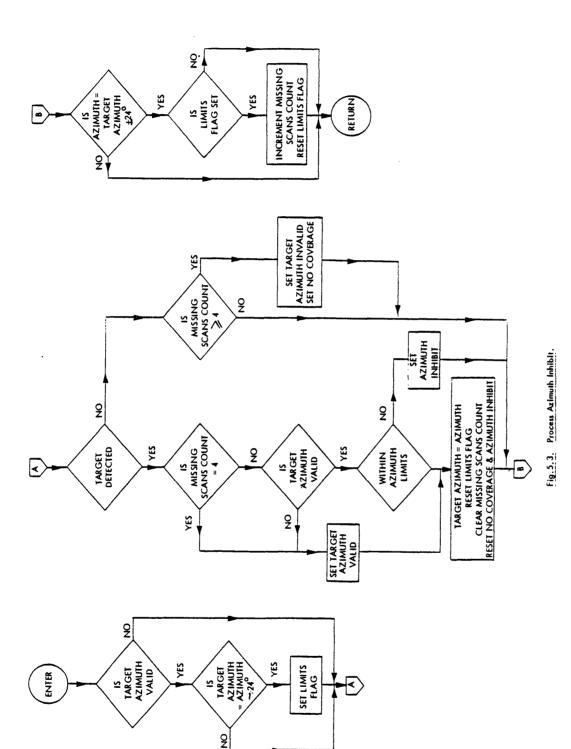

|            |         | 5.2.2.               | Process Azi   | muth Inhibit.         | 33      |

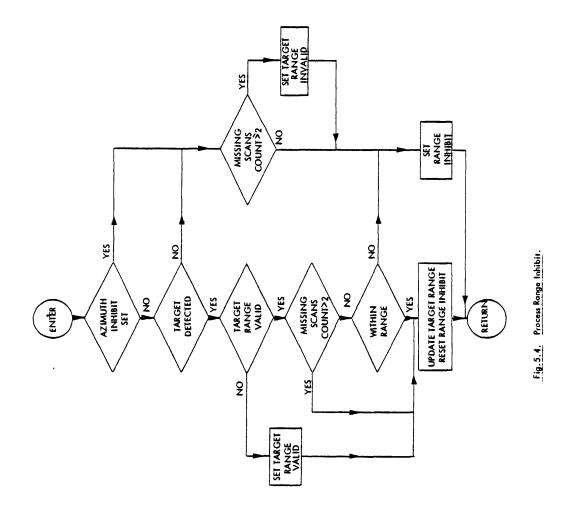

|            |         | 5.2.3.               | Process Ran   | ge Inhibit.           | 34      |

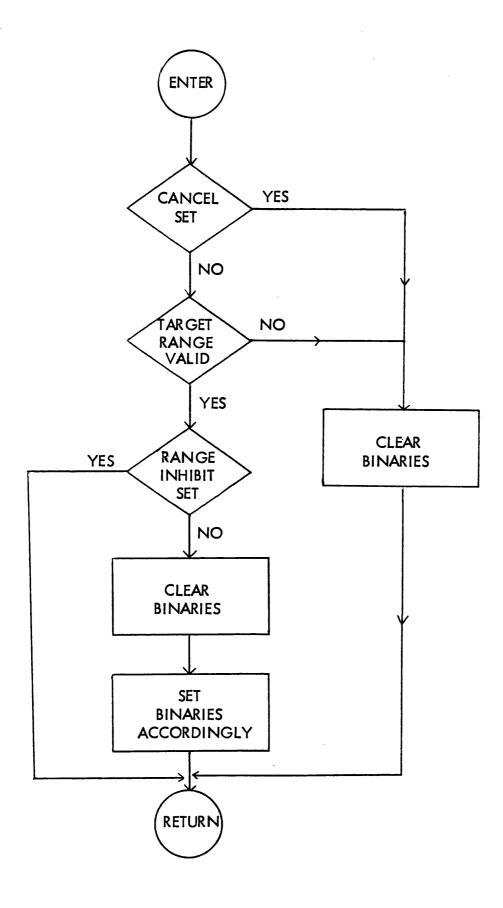

|            |         | 5.2.4.               | Set Binaries  | •                     | 34      |

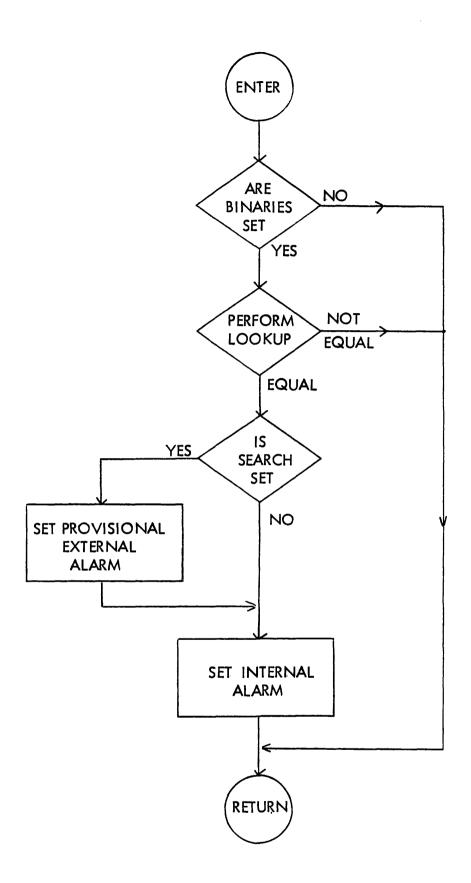

|            |         | 5.2.5.               | Process Bind  | aries.                | 34      |

|            |         | 5.2.6.               | Approach/R    | ecede Assessment.     | 34      |

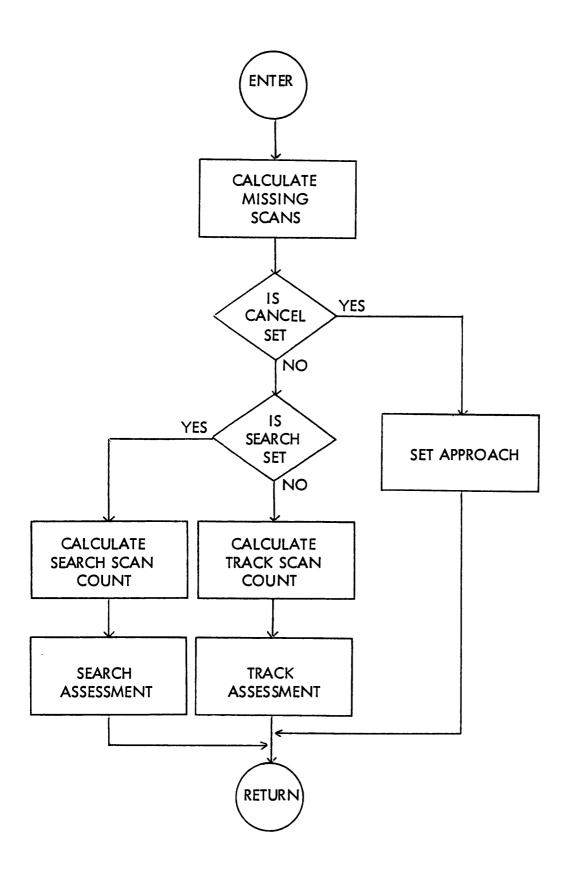

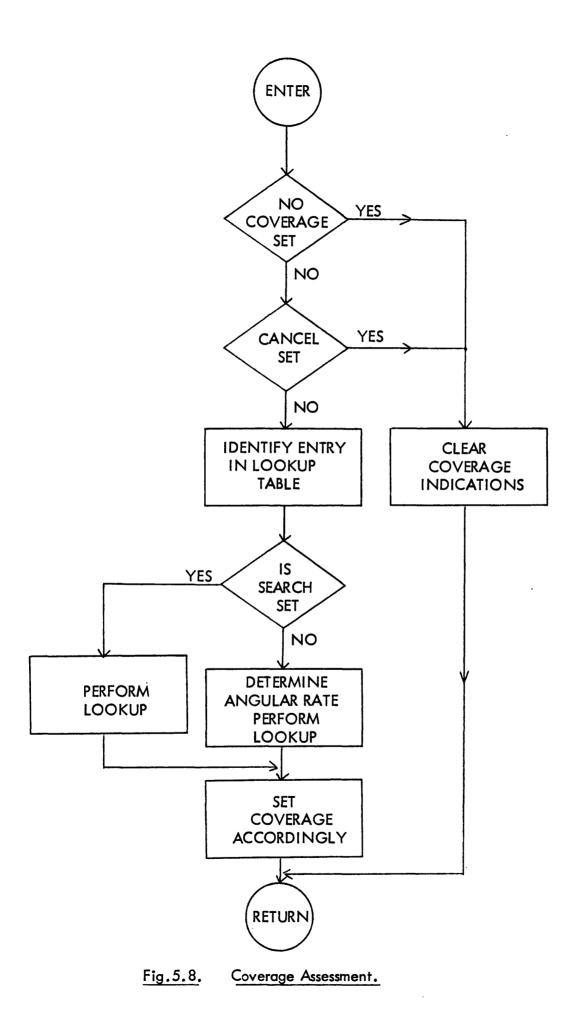

|            |         | 5.2.7.               | Coverage A    | ssessment.            | 35      |

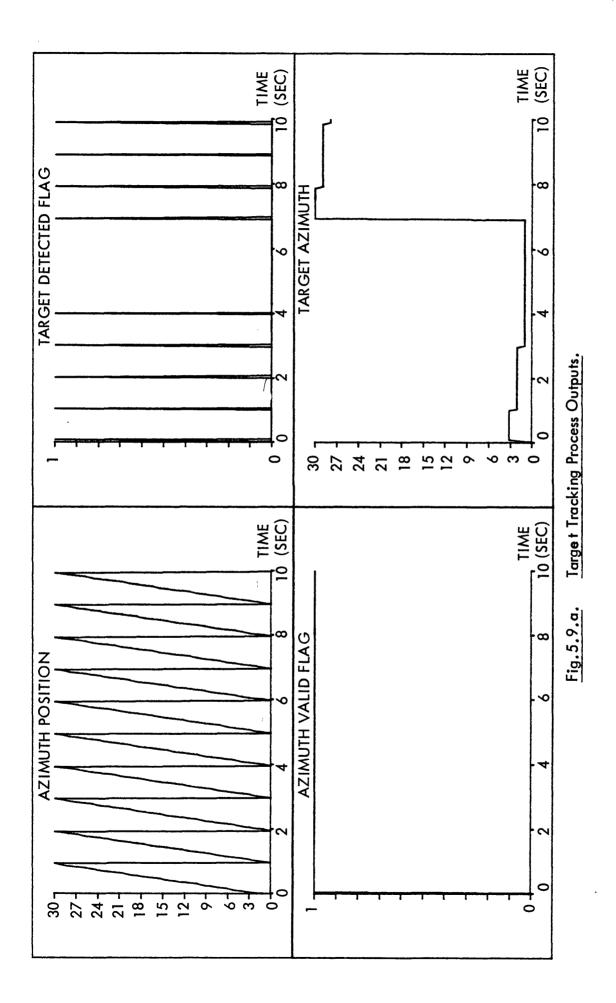

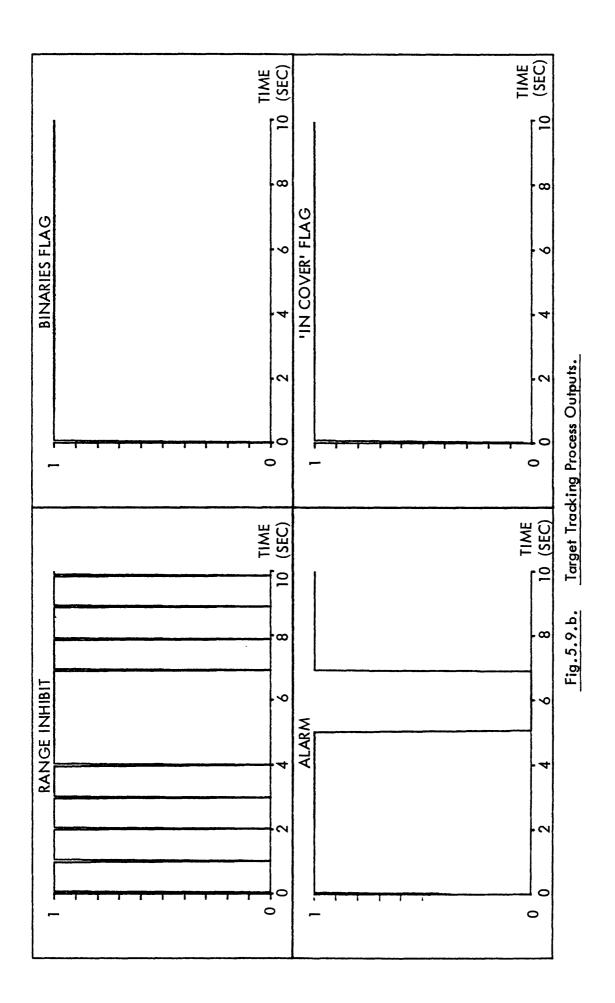

|            |         | 5.2.8.               | Baseline Pe   | rformance.            | 35      |

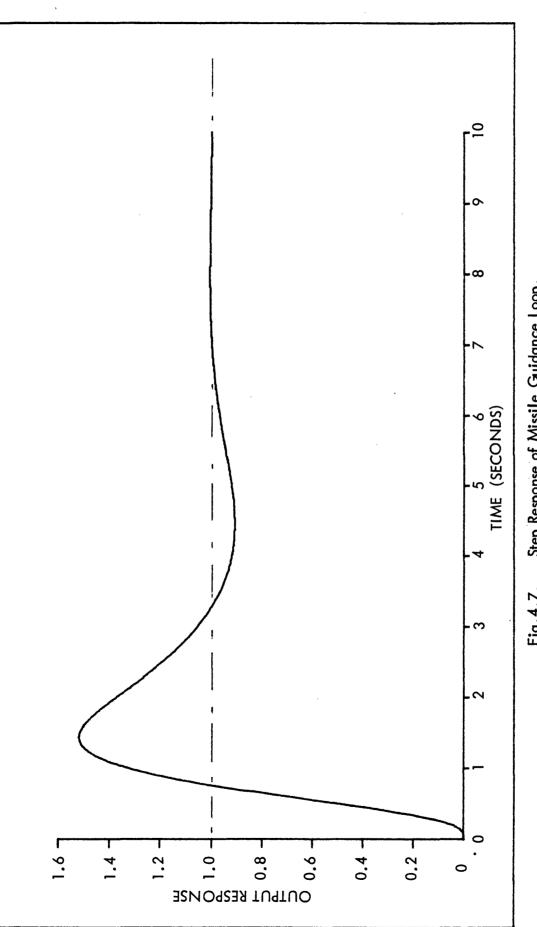

|            | 5.3.    | Missile G            | Guidance Loop |                       | 36      |

|            |         | 5.3.1.               | Floating Po   | int Arithmetic.       | 37      |

|            |         |                      | 5.3.1.1.      | Direct Realisation.   | 37      |

|            |         |                      | 5.3.1.2.      | Cascade Realisation.  | 38      |

|            |         |                      | 5.3.1.3.      | Parallel Realisation. | 39      |

|            |         | 5.3.2.               | Integer Arit  | hmetic.               | 39      |

| Chapter 6. | Implem  | entation.            |               |                       | 41      |

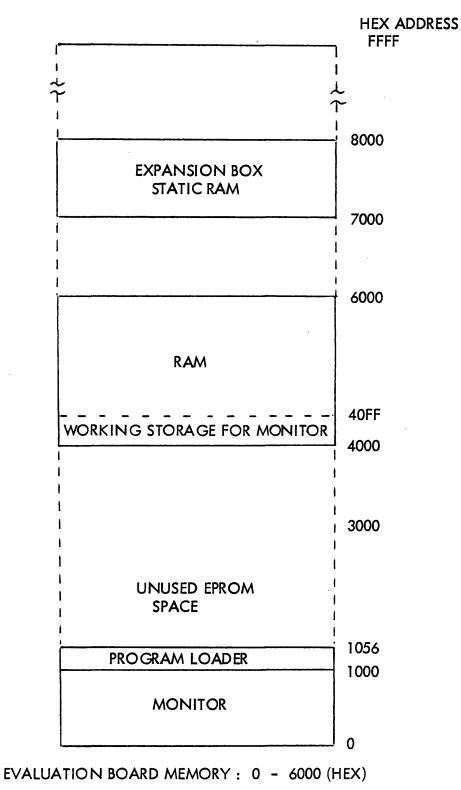

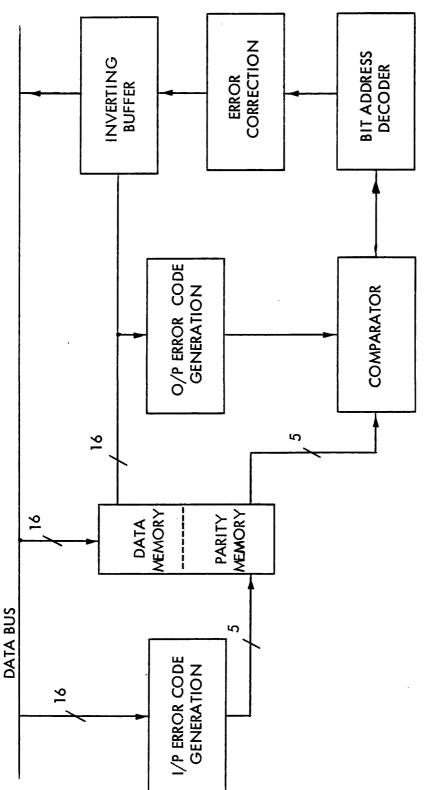

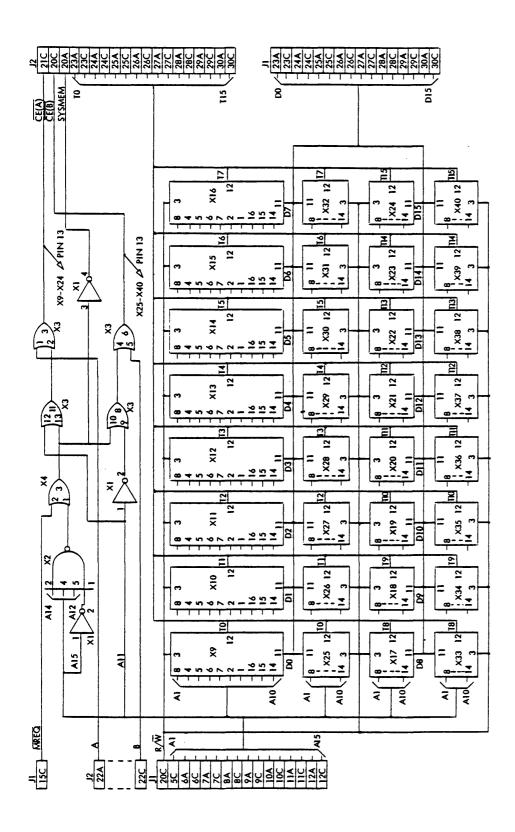

|            | 6.1.    | System M             | emory         |                       | 41      |

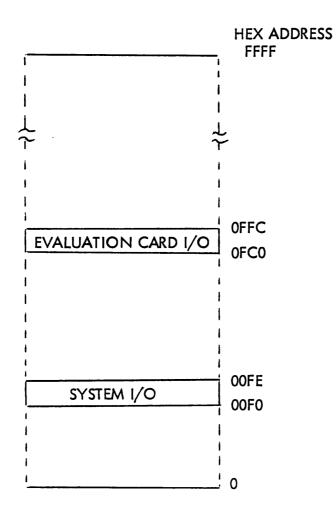

|            | 6.2.    | System Input/Output. |               |                       | 42      |

|            | 6.3.   | System So  | ftware.                             | Page 43 |

|------------|--------|------------|-------------------------------------|---------|

|            | 6.4.   | Fault Inje | ction.                              | 44      |

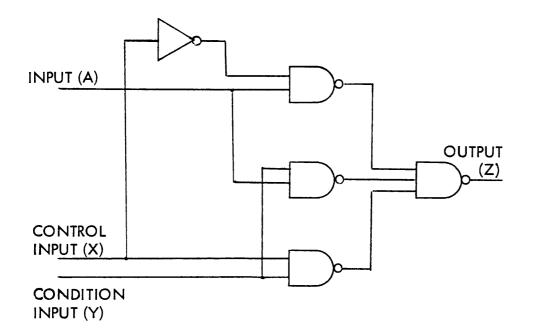

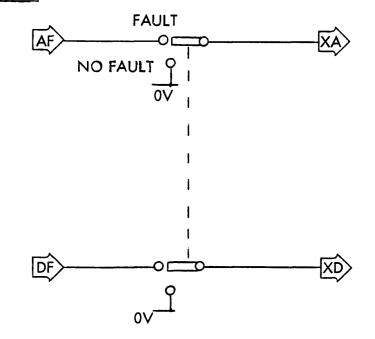

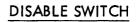

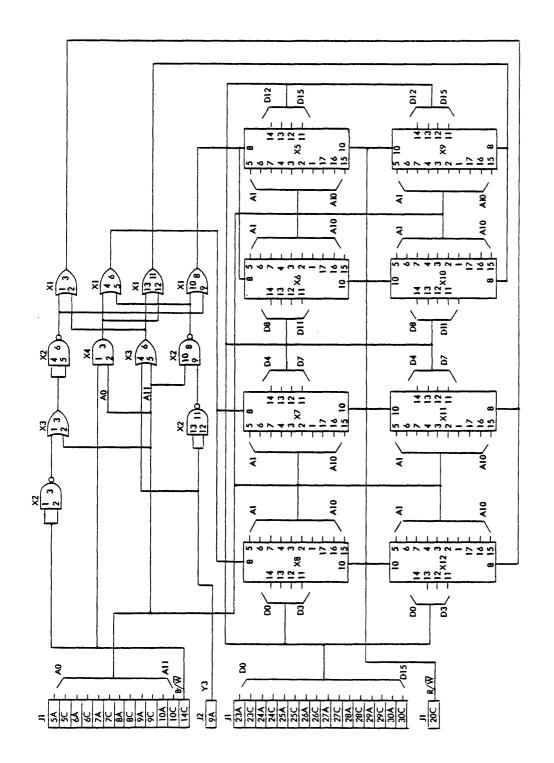

|            |        | 6.4.1.     | Design of Fault Injection Logic     | 44      |

|            |        | 6.4.2.     | Method of Fault Injection.          | 46      |

|            | 6.5.   | System In  | tegration and Test.                 | 46      |

| Chapter 7. | Design | Strategies | : Single Processor System.          | 47      |

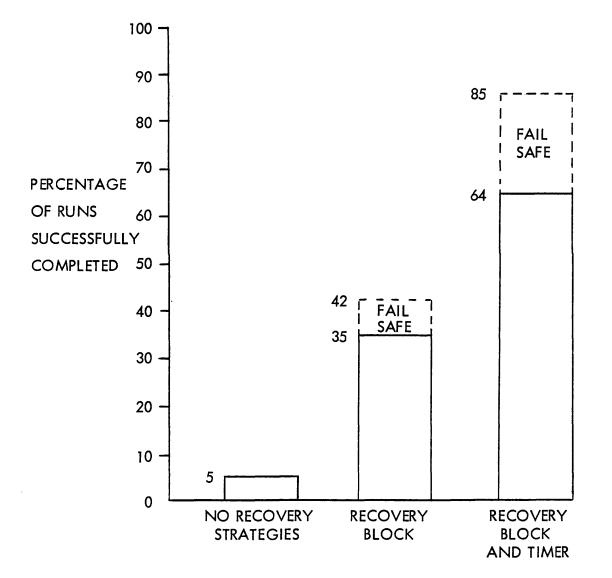

|            | 7.1.   | System wi  | th No Recovery.                     | 47      |

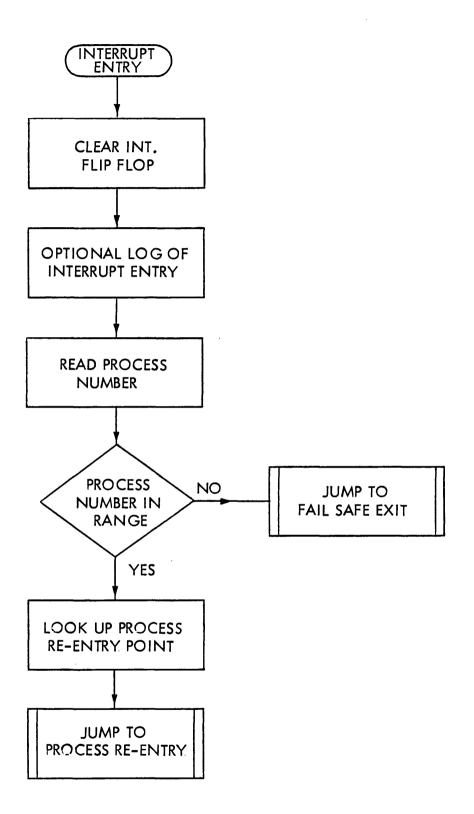

|            | 7.2.   | Basic Rec  | overy Block.                        | 48      |

|            |        | 7.2.1.     | Integrity ot Data.                  | 49      |

|            |        | 7.2.2.     | Design Discipline.                  | 50      |

|            |        | 7.2.3.     | System Performance.                 | 50      |

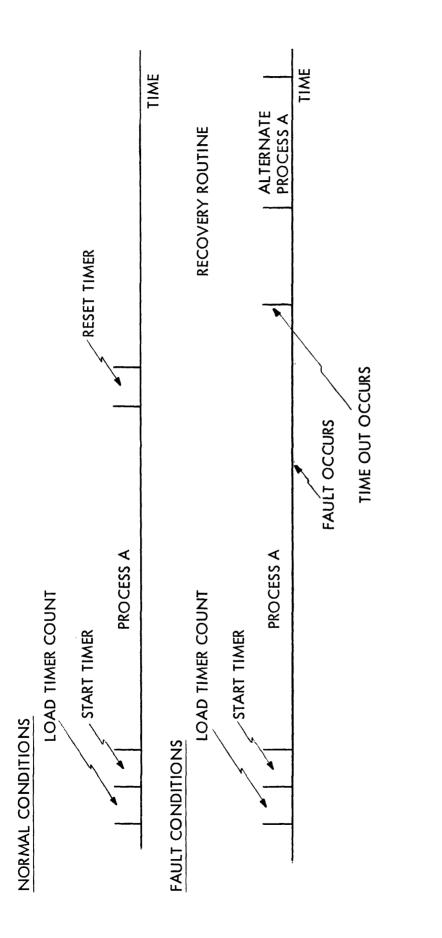

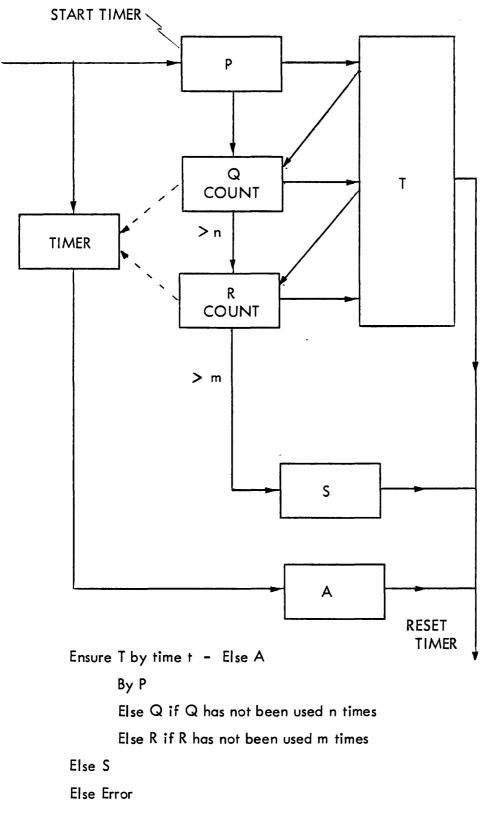

|            | 7.3.   | Addition   | ot Watchdog Timer.                  | 51      |

|            |        | 7.3.1.     | Recovery Using a Watchdog Timer.    | 51      |

|            |        | 7.3.2.     | System Performance.                 | 52      |

|            |        | 7.3.3.     | Summary.                            | 52      |

|            | 7.4.   | Typical F  | ault Effects.                       | 53      |

|            | 7.5.   | Further A  | dditions to Recovery.               | 55      |

|            |        | 7.5.1.     | Use of Unimplemented Instruction Tr | ap. 55  |

|            |        | 7.5.2.     | Default Data Bus.                   | 56      |

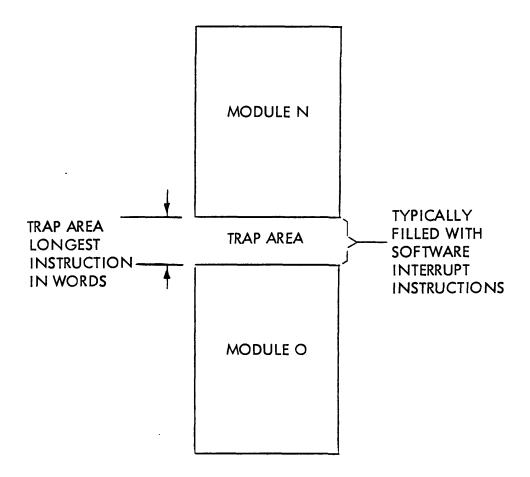

|            |        | 7.5.3.     | Trap Area.                          | 57      |

|            |        | 7.5.4.     | Performance Counter.                | 57      |

|            | 7.6.   | Extension  | s to the Recovery Block.            | 58      |

| Chapter 8. | Single | Microproc  | essor Study Conclusions.            | 60      |

|            | 8.1.   | Acceptan   | ce Test.                            | 60      |

|            | 8.2.   | CPU Loco   | l Storage.                          | 60      |

|            | 8.3.   | The Watc   | hdog Timer.                         | 60      |

|            | 8.4.   | Default D  | Data Bus.                           | 61      |

|            | 8.5.   | Micropro   | cessor Dependent Facilities.        | 61      |

|            | 8.6.   | Use of Tro | ap Areas.                           | 62      |

|            | 8.7.   | Performar  | nce Counter.                        | 62      |

|            | 8.8.   | Built in T | est.                                | 62      |

|            | 8.9.   | In Conclu  | usion.                              | 63      |

| Chapter 9.  | Introdu | oction to the | e Distributed Processing System. | Page 64 |

|-------------|---------|---------------|----------------------------------|---------|

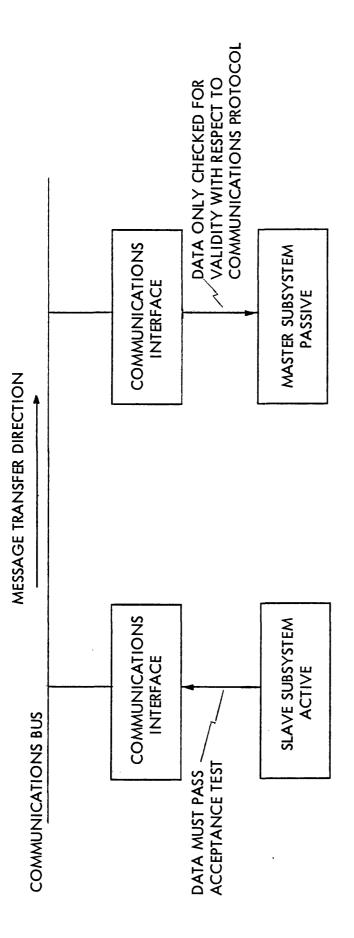

|             | 9.1.    | Design Ph     | ilosophy for Inter Processor     | 64      |

|             |         | Commur        | nication.                        |         |

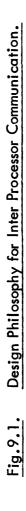

|             | 9.2.    | Local Rec     | overy Strategy.                  | 65      |

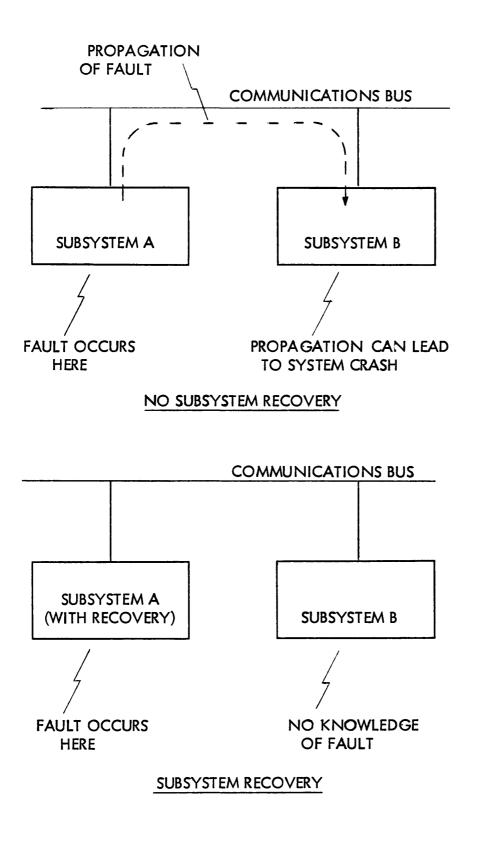

|             | 9.3.    | Global Re     | covery Strategy.                 | 65      |

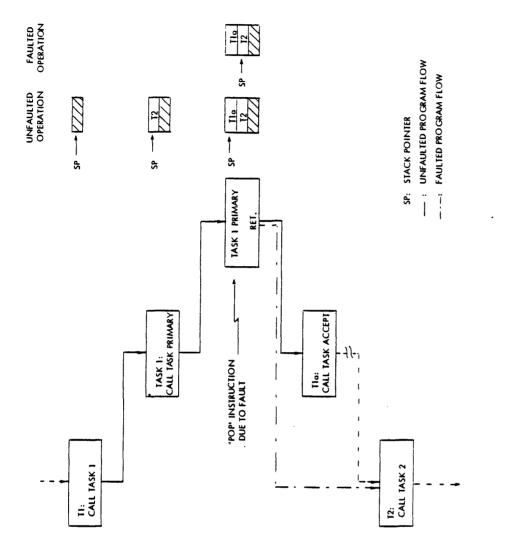

|             | 9.4.    | Task Swap     | ping.                            | 67      |

|             | 9.5.    | Functiona     | Decomposition of System.         | 67      |

|             | 9.6.    | Injection     | of Faults in Real Time.          | 68      |

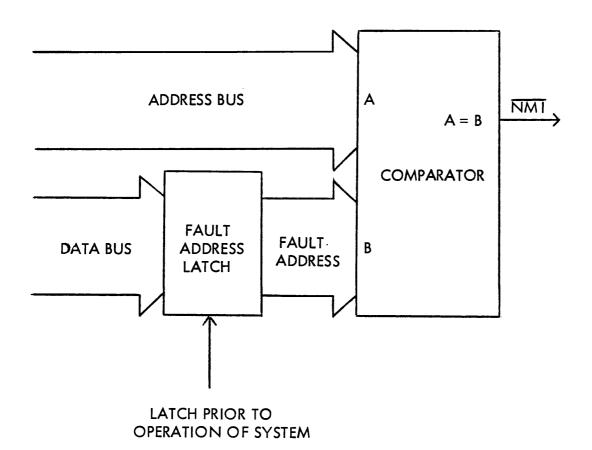

|             |         | 9.6.1.        | Mechanism of Fault Injection.    | 68      |

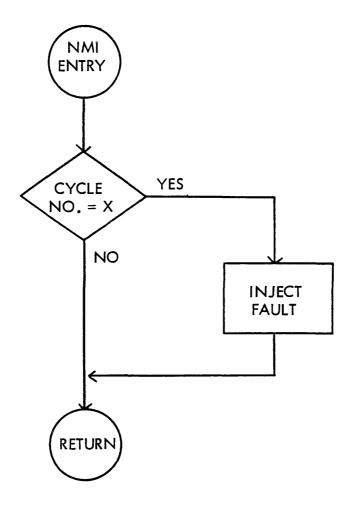

|             |         | 9.6.2.        | Specific Cycle Fault Injection.  | 69      |

| Chapter 10. | The Di  | stributed Pr  | ocessing System Description.     | 70      |

|             | 10.1.   | Central Pr    | ocessing Unit.                   | 70      |

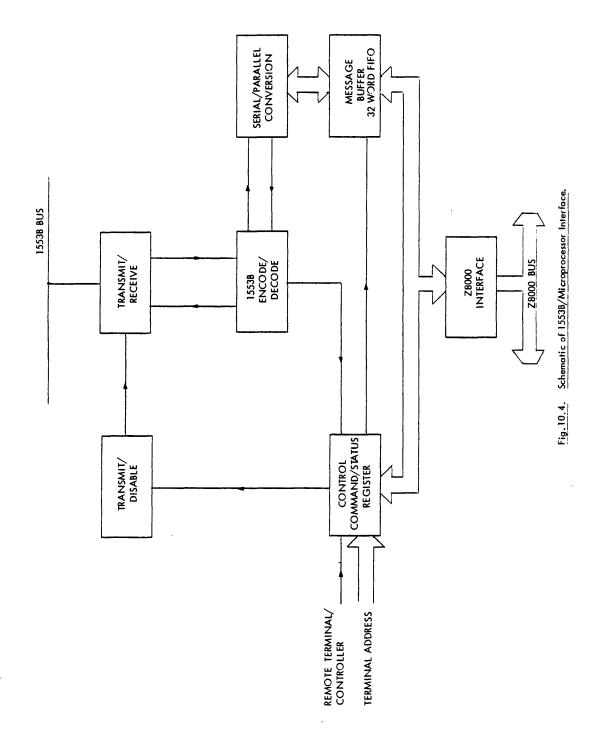

|             | 10.2.   | Microproc     | essor to 1553B Interface.        | 71      |

|             |         | 10.2.1.       | Control and Status Register.     | 72      |

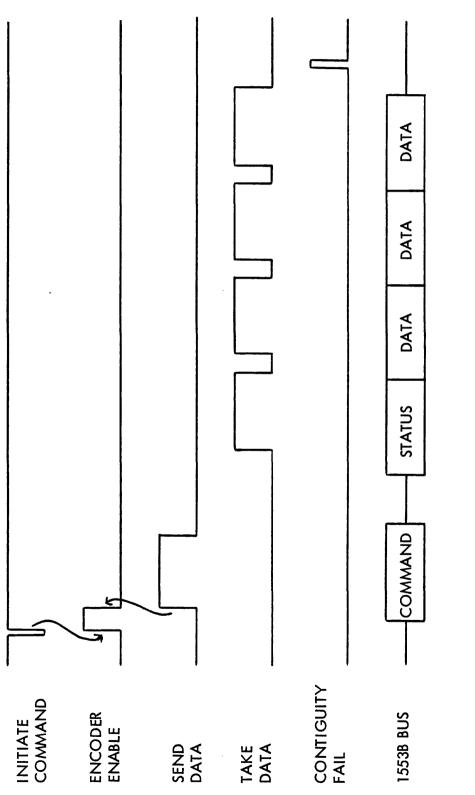

|             |         | 10.2.2.       | Message from Bus Controller.     | 73      |

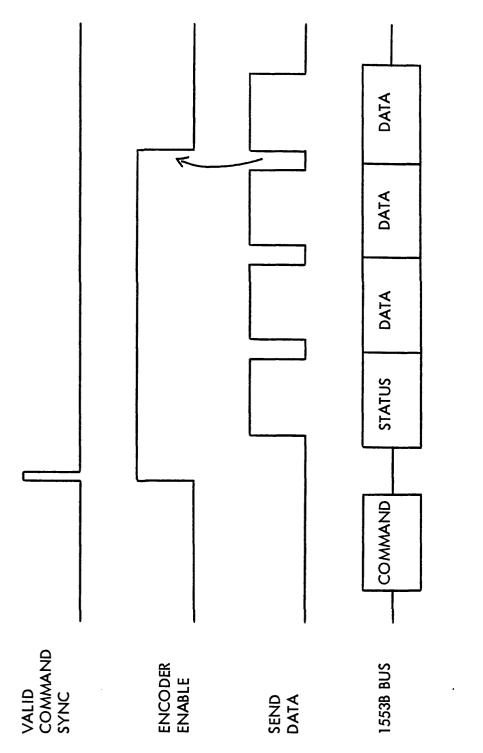

|             |         | 10.2.3.       | Message to Bus Controller.       | 74      |

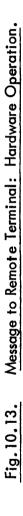

|             |         | 10.2.4.       | Message to Remote Terminal.      | 75      |

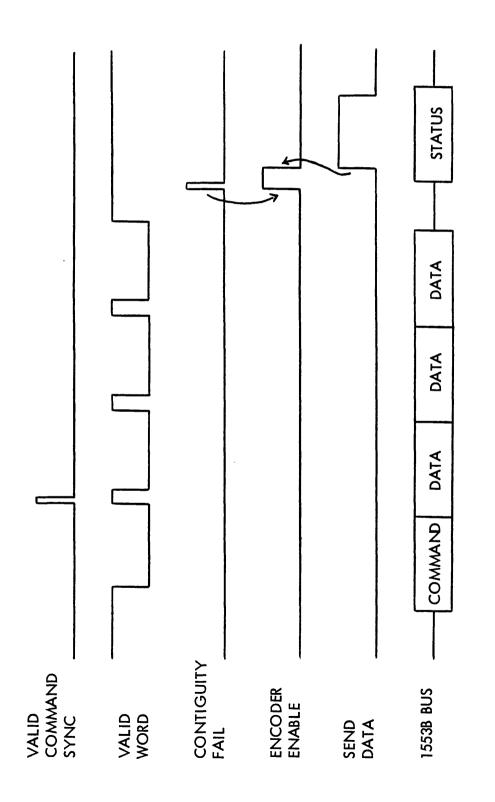

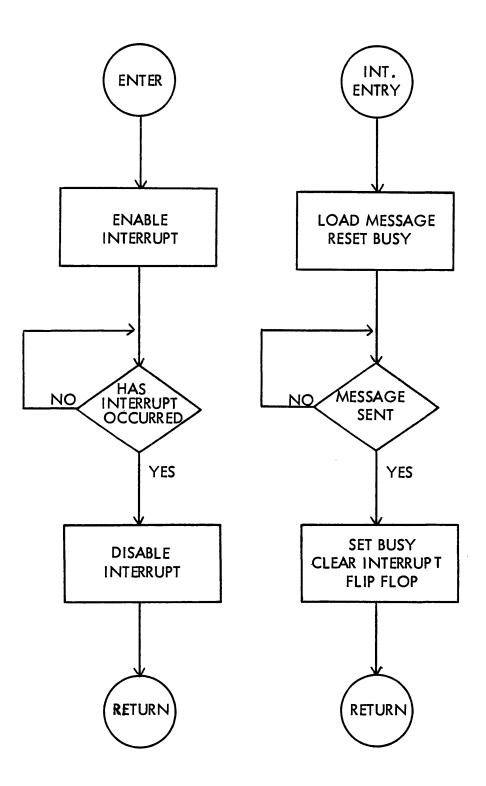

|             |         | 10.2.5.       | Message from Remote Terminal.    | 76      |

|             |         | 10.2.6.       | 1553B Protocol Fault Injection.  | 77      |

|             | 10.3.   | Communic      | ation Software.                  | 77      |

|             |         | 10.3.1.       | Message from Bus Controller.     | 78      |

|             |         | 10.3.2.       | Message to Bus Controller.       | 78      |

|             |         | 10.3.3.       | Message to Remote Terminal.      | 78      |

|             |         | 10.3.4.       | Message from Remote Terminal.    | 78      |

|             | 10.4.   | Systems In    | tegration and Test.              | 79      |

| Chapter 11. | Design  | Strategies:   | Distributed System.              | 80      |

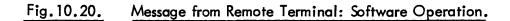

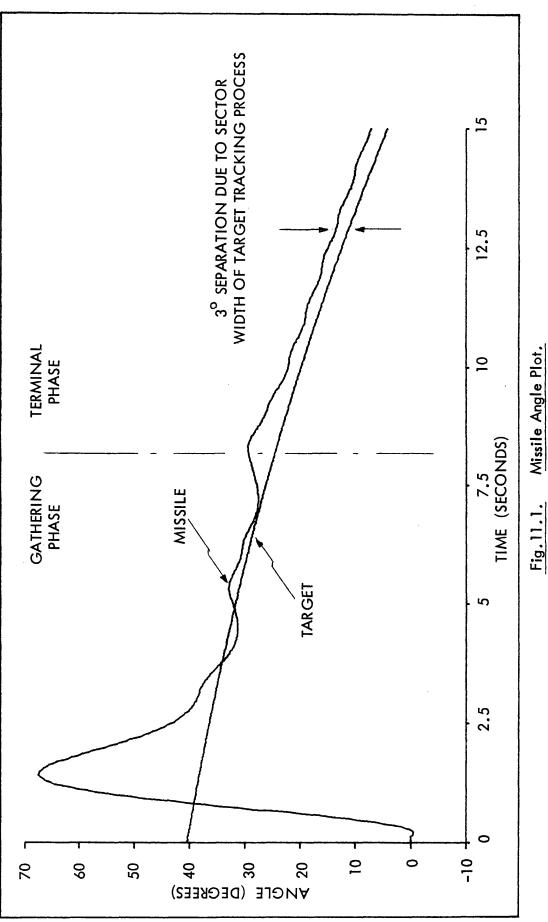

|             | 11.1.   | Target Ch     | aracteristics.                   | 80      |

|             | 11.2.   | Performar     | nce Index.                       | 81      |

|             | 11.3.   | System w      | ith No Recovery.                 | 82      |

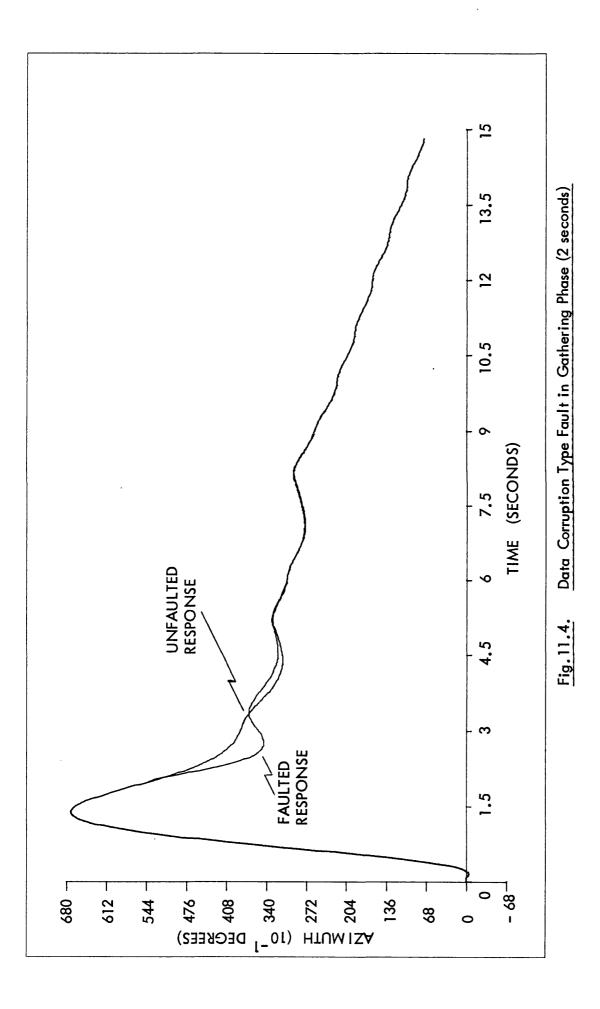

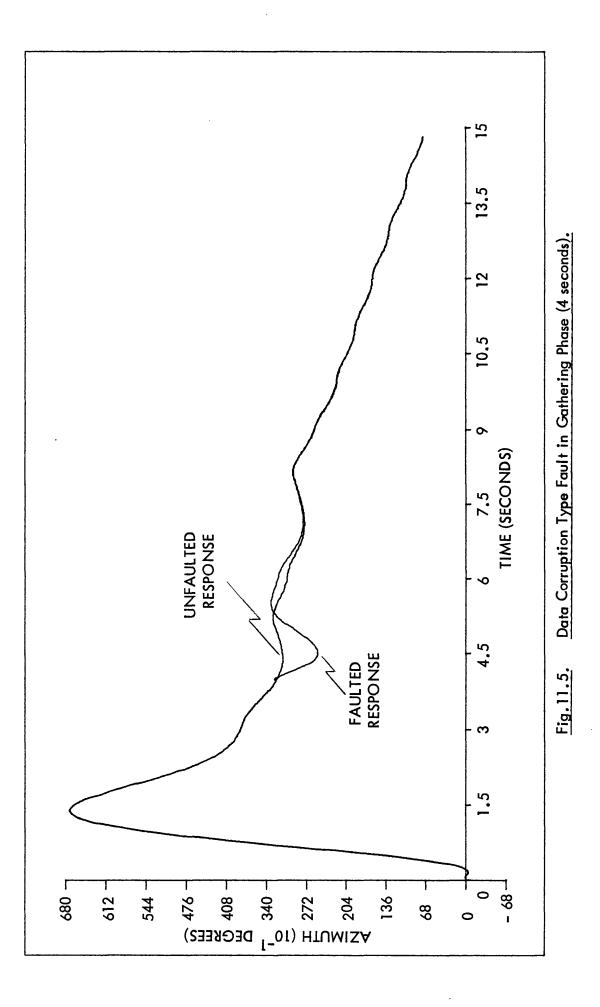

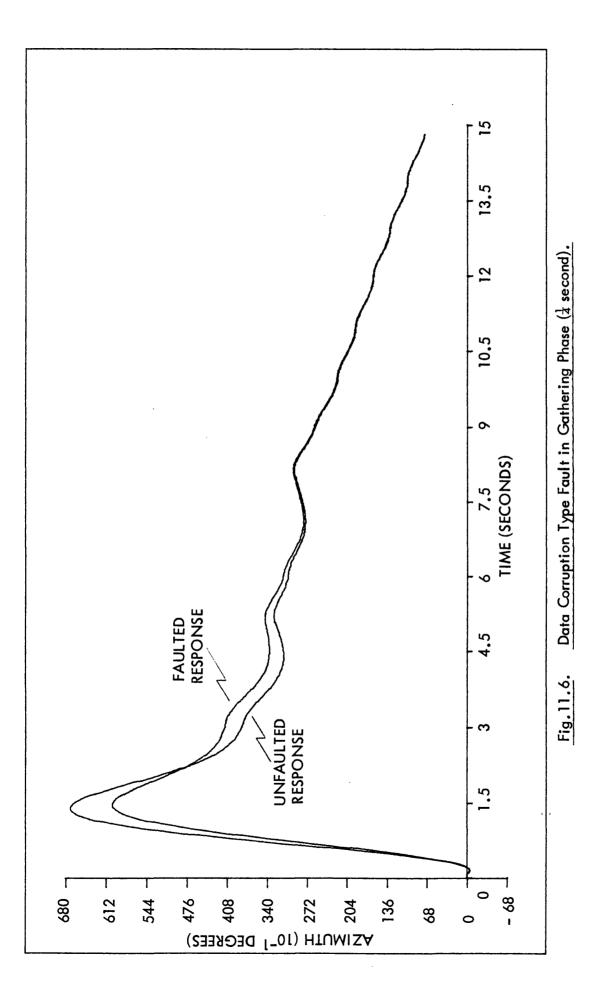

|             |         | 11.3.1.       | Data Corruption Type Faults.     | 82      |

|             |         | 11.3.2.       | Controller Crashes.              | 84      |

(v)

|             | 11.4.    | Basic Reco   | overy Block.                      | Page 84 |

|-------------|----------|--------------|-----------------------------------|---------|

|             |          | 11.4.1.      | Target Tracking Processor.        | 84      |

|             |          | 11.4.2.      | Digital Controller Processor.     | 84      |

|             |          | 11.4.3.      | Data Corruption Types.            | 85      |

|             |          | 11.4.4.      | Controller Crashes.               | 86      |

|             | 11.5.    | Use of Sol   | ftware Traps.                     | 86      |

|             | 11.6.    | Addition of  | of Watchdog Timer.                | 86      |

|             | 11.7.    | Global Re    | ecovery.                          | 87      |

|             |          | 11.7.1.      | Transient Failure and Recovery.   | 87      |

|             |          | 11.7.2.      | Example of Recovery.              | 88      |

| Chapter 12. | Standby  | / Processing | g Systems.                        | 89      |

|             | 12.1.    | Task Swap    | oping.                            | 89      |

|             | 12.2.    | Health Ma    | onitoring.                        | 90      |

|             | 12.3.    | Use of Fie   | eld Test Data.                    | 90      |

|             | 12.4.    | Failure of   | a Remote Terminal.                | 91      |

|             |          | 12.4.1.      | System Recovery.                  | 91      |

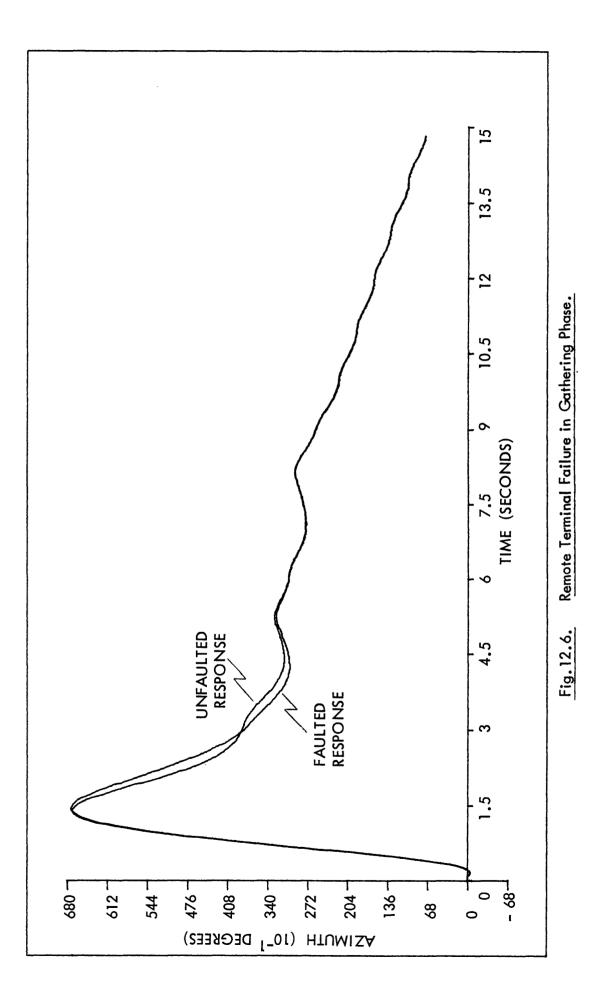

|             |          | 12.4.2.      | System Performance.               | 92      |

|             | 12.5.    | Failure of   | a Bus Controller.                 | 93      |

|             |          | 12.5.1.      | Use of Bus Monitor.               | 94      |

|             |          | 12.5.2.      | Effect of Failure on Performance. | 94      |

| Chapter 13. | Distribu | uted Proces  | sing Conclusions.                 | 97      |

|             | 13.1.    | Review of    | Design Philosophy.                | 97      |

|             | 13.2.    | Distribute   | d Proæssing Recovery.             | 97      |

|             |          | 13.2.1.      | Local Recovery.                   | 98      |

|             |          | 13.2.2.      | Global Recovery.                  | 98      |

|             |          | 13.2.3.      | Use of a Standby Processor.       | 98      |

|             | 13.3.    | Future Wa    | prk.                              | 99      |

| Chapter 14. | Toward   | s an Integro | ated Approach to Design.          | 101     |

|             | 14.1.    | Guideline    | es for Design                     | 101     |

|             |          | 14.1.1.      | Functional Decomposition.         | 101     |

|             |          | 14.1.2.      | Recovery Block.                   | 101     |

|             |        | 14.1.3.    | Watchdog Timer.                      | Page 102 |

|-------------|--------|------------|--------------------------------------|----------|

|             |        | 14.1.4.    | Run Time Overhead.                   | 102      |

|             |        | 14.1.5.    | System Traps.                        | 102      |

|             |        | 14.1.6.    | Reverionary Modes.                   | 102      |

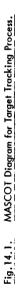

|             |        | 14.1.7.    | MASCOT ACP Diagram.                  | 102      |

|             |        | 14.1.8.    | Fault Scenarios.                     | 103      |

|             |        | 14.1.9.    | Design Reviews.                      | 103      |

|             |        | 14.1.10.   | Structured Walththroughs.            | 103      |

|             |        | 14.1.11.   | Testing.                             | 104      |

|             | 14.2.  | Single Pro | ocessor System.                      | 104      |

|             |        | 14.2.1.    | Functional Decomposition.            | 104      |

|             |        | 14.2.2.    | Recovery Block.                      | 104      |

|             |        | 14.2.3.    | Watchdog Timer.                      | 105      |

|             |        | 14.2.4.    | Run Time Overhead.                   | 105      |

|             |        | 14.2.5.    | Trap Areas.                          | 105      |

|             |        | 14.2.6.    | Reversionary Modes.                  | 105      |

|             |        | 14.2.7.    | MASCOT ACP Diagram.                  | 105      |

| Chapter 15. | Overal | l Review o | of Achievements.                     | 107      |

| Acknowledge | ments. |            |                                      | 109      |

| References. |        |            |                                      | 110      |

| Appendices: | A      | A. Digitis | ation of Guidance Loop.              | 113      |

|             | В      | . The Z8   | 000 Microprocessor                   | 115      |

|             | C      | C. The Mi  | icromaster.                          | 118      |

|             | 0      | . Z8002    | Microprocessor Program Assembler.    | 119      |

|             | E      | . Target   | Tracking Process: Acceptance Tests   | 128      |

|             |        | and        | Alternate Routines.                  |          |

|             | F      | . An Ov    | erview of MIL-STD 1553B.             | 132      |

|             | (      | G. Worst   | Case Limits for Parallel Realisation | 134      |

|             |        | of [       | Digital Controller.                  |          |

Figures.

Tables.

.

#### Synopsis.

The report describes a research investigation into fault tolerant strategies within a real time control system. Methods for increasing the reliability of a system other than through the use of fault tolerance have also been reviewed. The study which concentrated on a Recovery Block structure is separated into two parts, that is, a single and a distributed processing system. The single processor study involved modelling a subset of the control system; error recovery strategies are presented here as additions to the basic Recovery Block structure. Fault injection logic was specially designed and built in order that the recovery strategies could be tested under extreme operating conditions.

The distributed processing study is an extension of the single processor research. Three types of recovery are investigated to increase system availability; local recovery, global recovery and task swapping. The philosophy used in the distributed processing study was always to attempt recovery on a local basis, that is to prevent the propagation of faults to other microprocessors within the system. Global recovery is established as a method of maintaining continued safe operation when local recovery or communication between processors fails. The use of a standby processor system for dynamic task swapping is shown to give continued systems operation under conditions which would normally cause a catastrophic crash in non redundant systems.

The overall conclusion of the research is that fault recovery must be localised to prevent fault propagation from one process to the following process, with no distinction as to whether the communicating processes are in the same or different microprocessor subsystems, and that this can be successfully achieved in a real time environment by the use of a Recovery Block structure.

# List of Symbols

| ACP    | Activity Channel Pool                               |

|--------|-----------------------------------------------------|

| A/D    | Analogue/Digital                                    |

| BC     | Bus Controller                                      |

| CPU    | Central Processing Unit                             |

| D/A    | Digital/Analogue                                    |

| DMA    | Direct Memory Access                                |

| EMP    | Electromagnetic Pulse                               |

| FIFO   | First In First Out                                  |

| FMEA   | Failure Modes Effects Analysis                      |

| I/O    | Input/Output                                        |

| LED    | Light Emitting Diode                                |

| LSI    | Large Scale Integration                             |

| MASCOT | Modular Approach to Software Construction Operation |

|        | and Test                                            |

| RAM    | Random Access Memory                                |

| ROM    | Read only Memory                                    |

| RT     | Remote Terminal                                     |

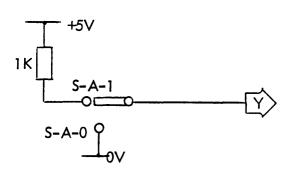

| s-a-0  | Stuck at logical '0'                                |

| s-a-1  | Stuck at logical '1'                                |

| TMR    | Triple Modular Redundancy                           |

| VLSI   | Very Large Scale Integration                        |

| Z      | Discrete Operator                                   |

|        |                                                     |

•

#### List of Figures

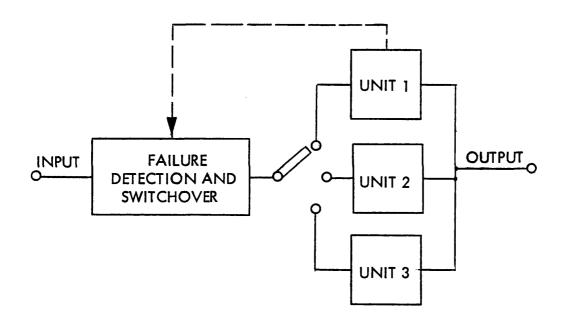

- Fig. 2.1. Cold Standby Redundancy

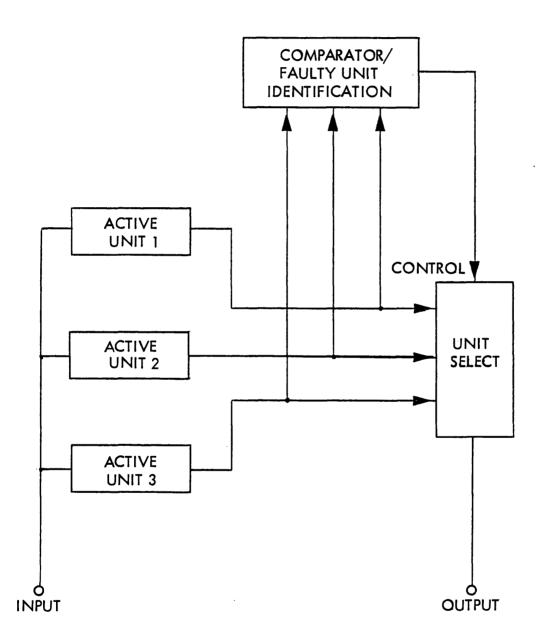

- Fig. 2.2. Hot Standby Redundancy

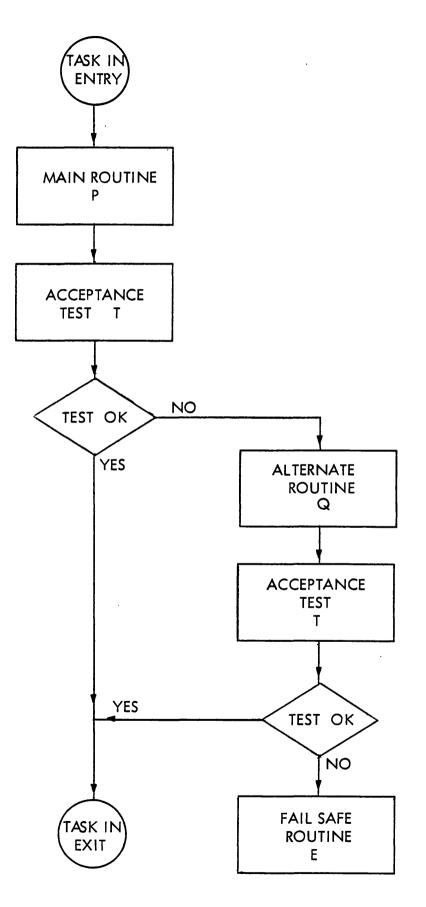

- Fig. 2.3. The Recovery Block

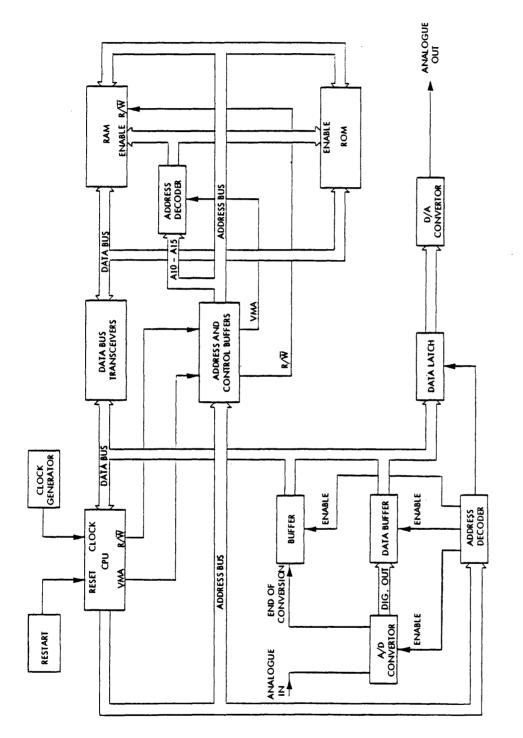

- Fig. 3.1. A Typical Microprocessor System

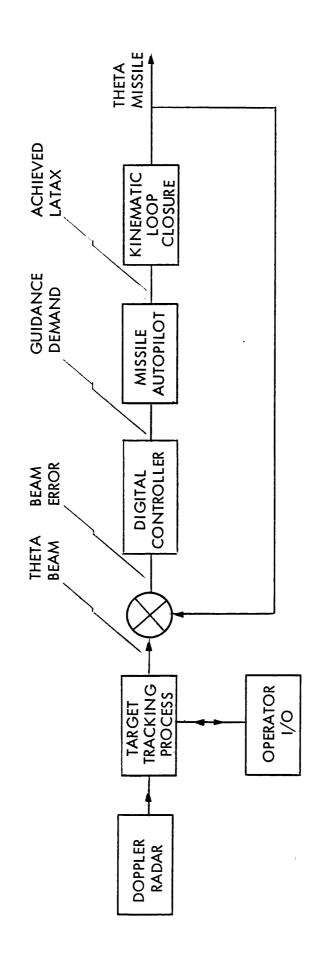

- Fig.4.1. Real Time System Schematic

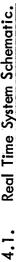

- Fig.4.2. Range/Velocity Gate Matrix

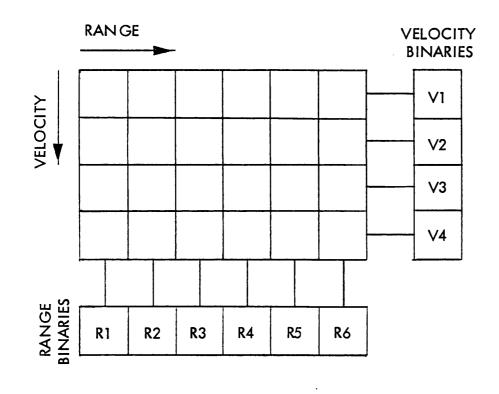

- Fig. 4.3. Taboo Channels

- Fig. 4.4. Principle of Azimuth Inhibit

- Fig. 4.5. Missile Guidance Loop

- Fig.4.6.a. Gain Plot of Missile Guidance Loop

- Fig. 4.6.b. Phase Plot of Missile Guidance Loop

- Fig.4.7. Step Response of Missile Guidance Loop

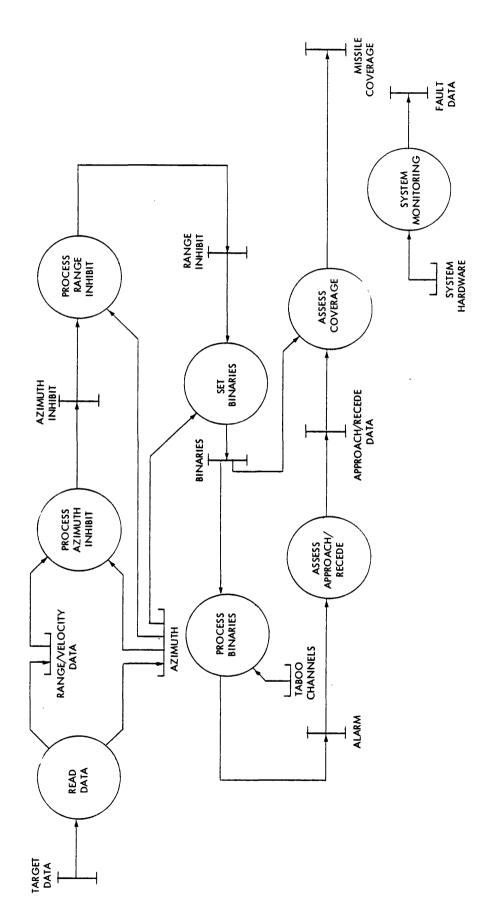

- Fig. 5.1. Target Tracking Process

- Fig. 5.2. Read Routine

- Fig. 5.3. Process Azimuth Inhibit

- Fig. 5.4. Process Range Inhibit

- Fig. 5.5. Set Binaries

- Fig. 5.6. Process Binaries

- Fig. 5.7. Approach/Recede Assessment

- Fig. 5.8. Coverage Assessment

- Fig. 5.9. Target Tracking Process Outputs

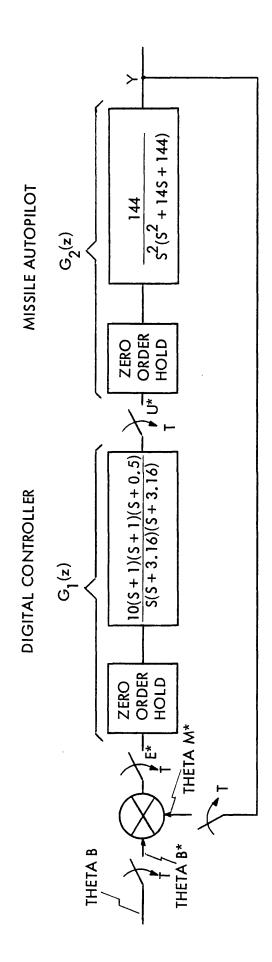

- Fig. 5.10. Digitisation of Guidance Loop

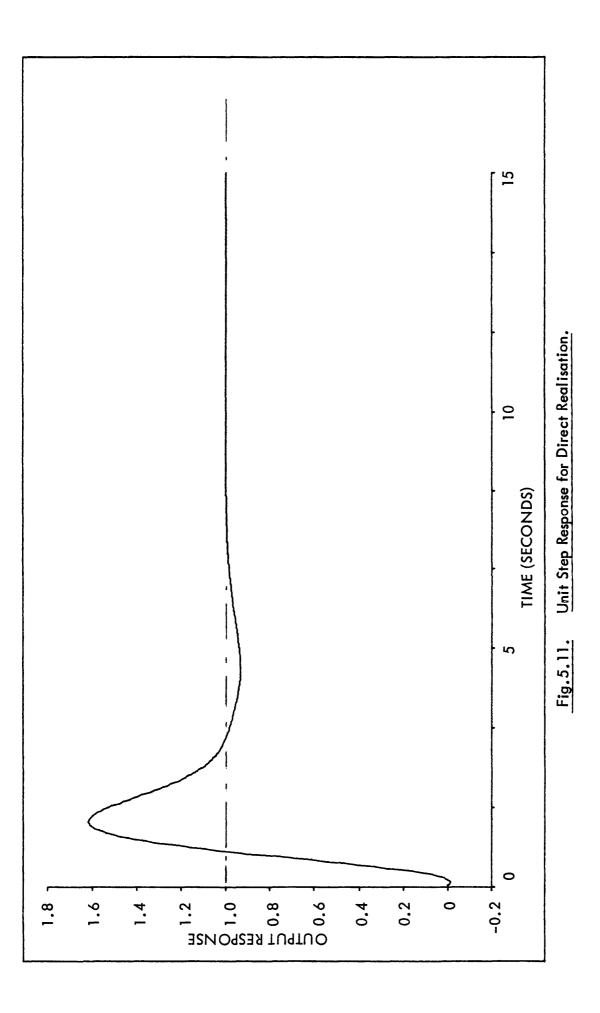

- Fig. 5.11. Unit Step Response for Direct Realisation

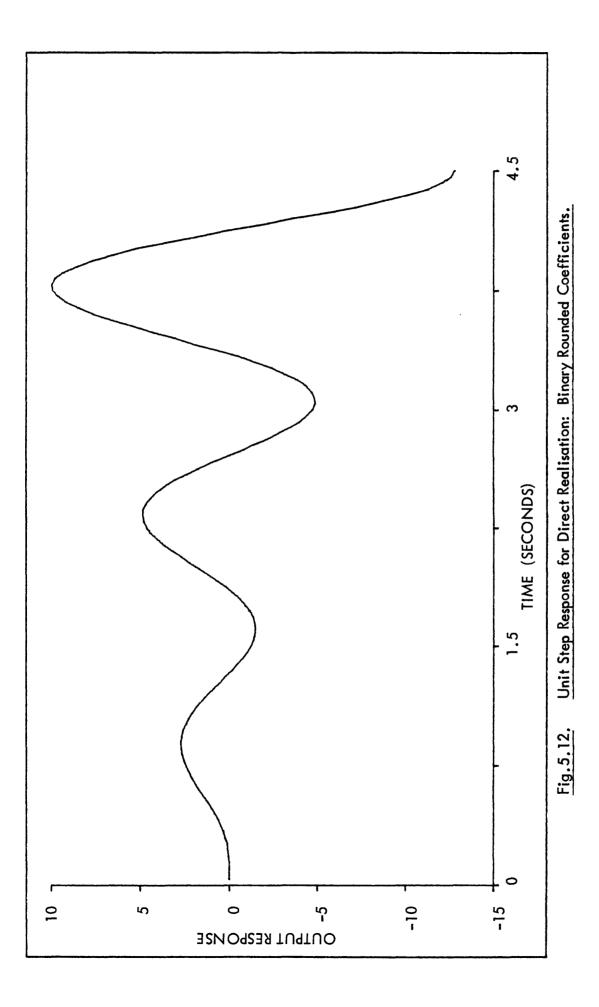

- Fig. 5.12. Unit Step Response for Direct Realisation: Binary Rounded Coefficients

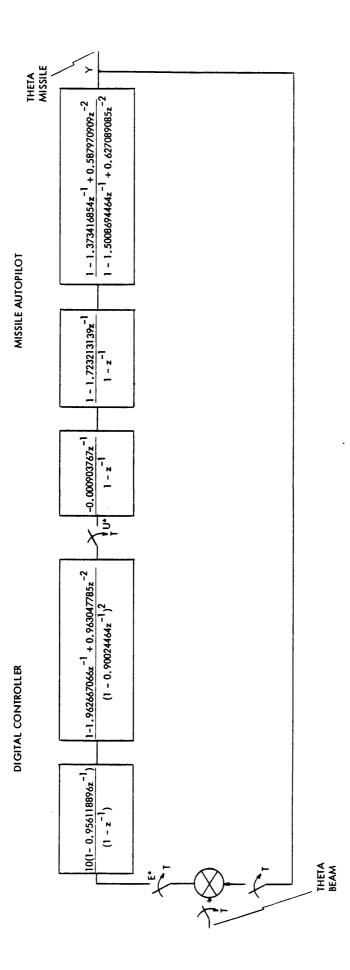

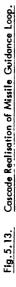

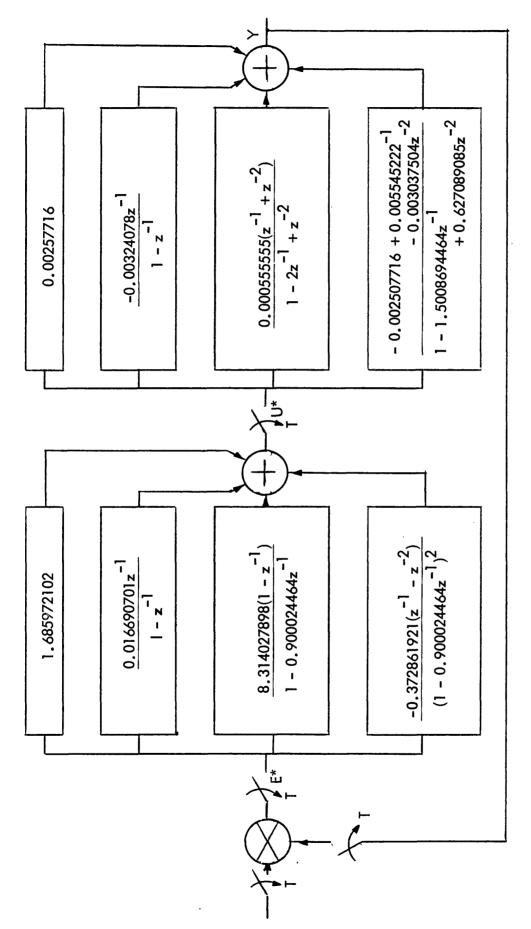

- Fig. 5.13. Cascade Realisation of Missile Guidance Loop

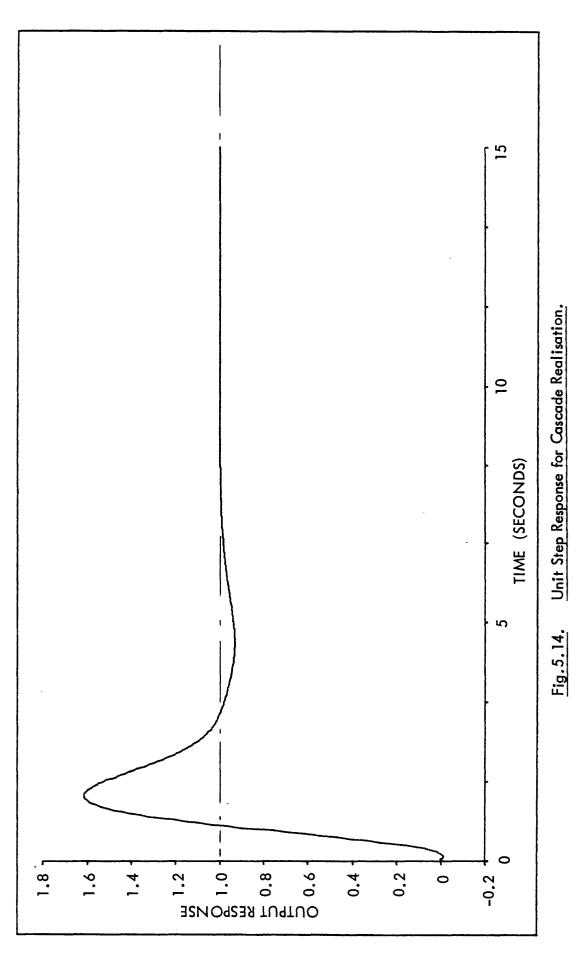

- Fig. 5.14. Unit Step Response for Cascade Realisation

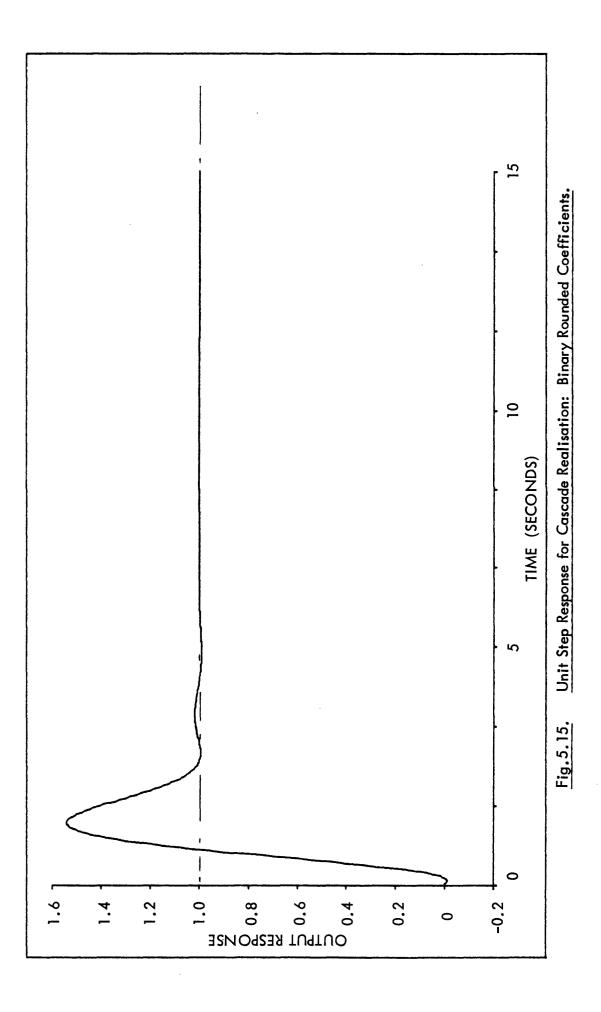

| Fig.5.15. | Unit Step Response for Cascade Realisation: |

|-----------|---------------------------------------------|

|           | Binary Rounded Coefficients                 |

- Fig. 5.16. Parallel Realisation of Guidance Loop

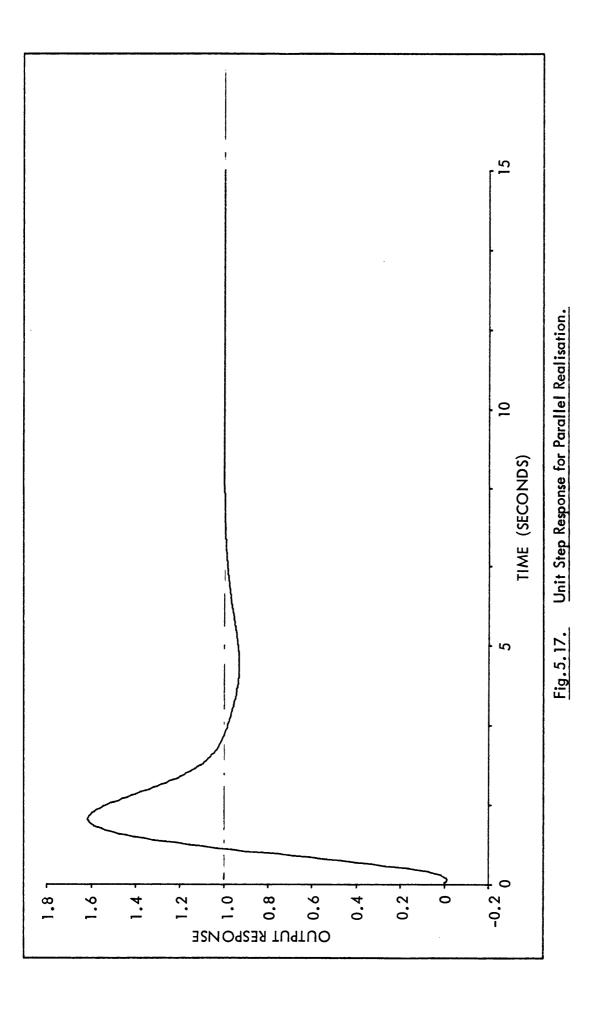

- Fig. 5.17. Unit Step Response for Parallel Realisation

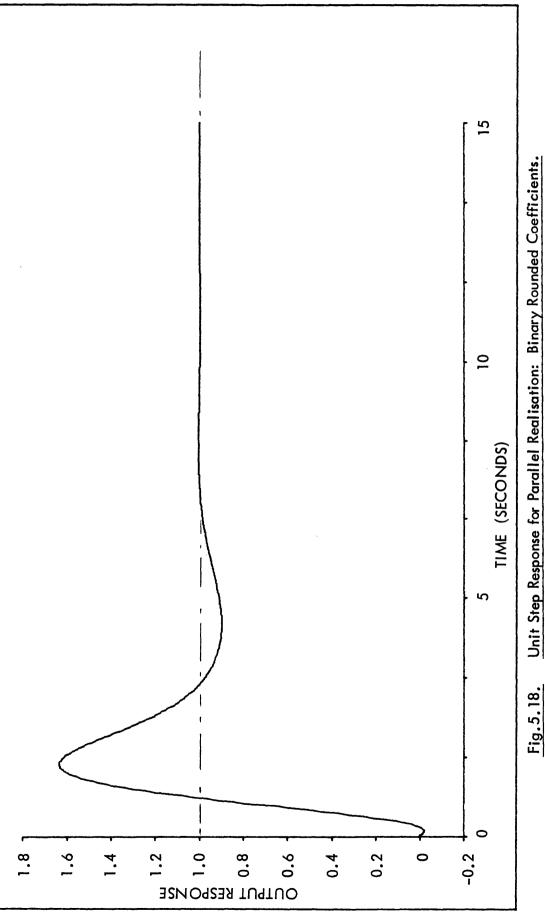

- Fig. 5.18. Unit Step Response for Parallel Realisation: Binary Rounded Coefficients

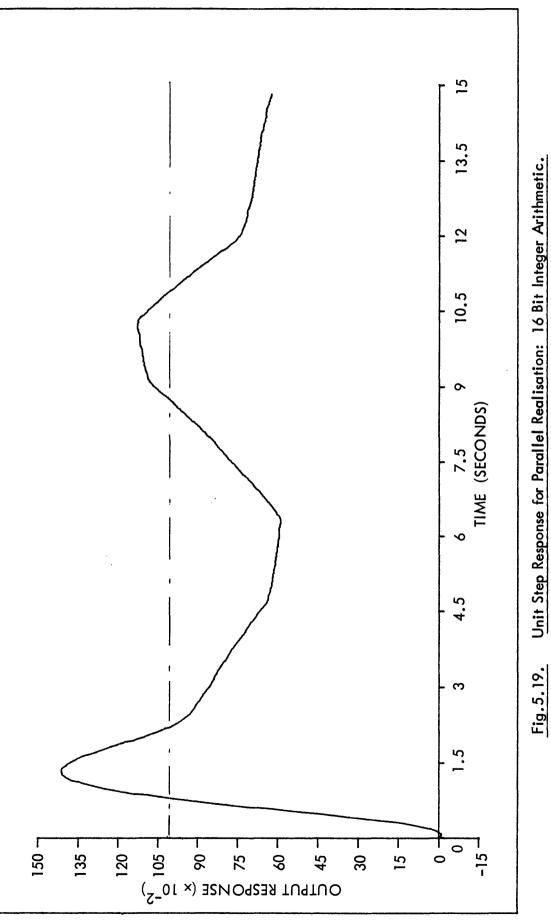

- Fig. 5.19. Unit Step Response for Parallel Realisation: 16 Bit Integer Arithmetic

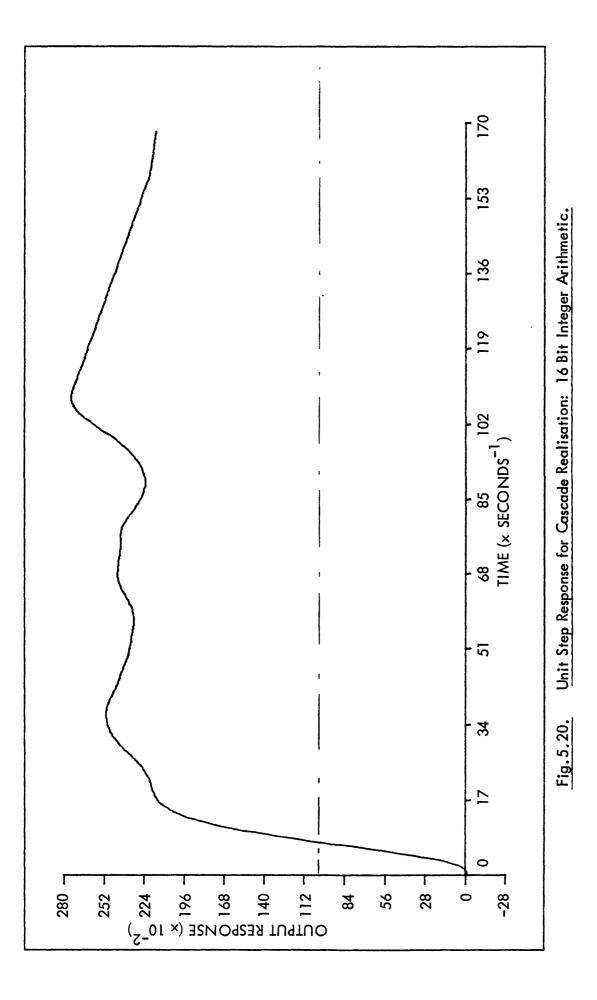

- Fig. 5.20. Unit Step Response for Cascade Realisation: 16 Bit Integer Arithmetic

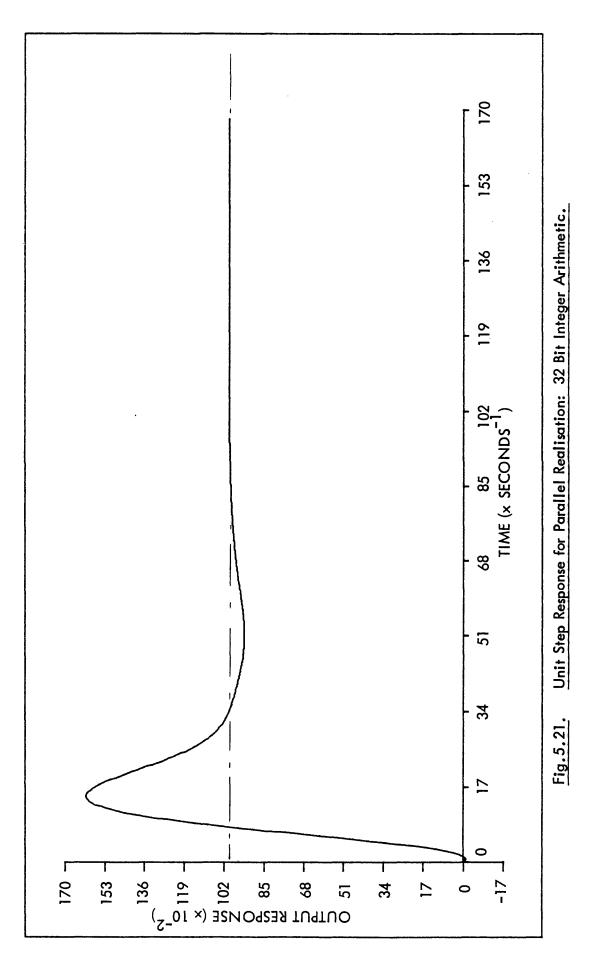

- Fig. 5.21. Unit Step Response for Parallel Realisation: 32 Bit Integer Arithmetic

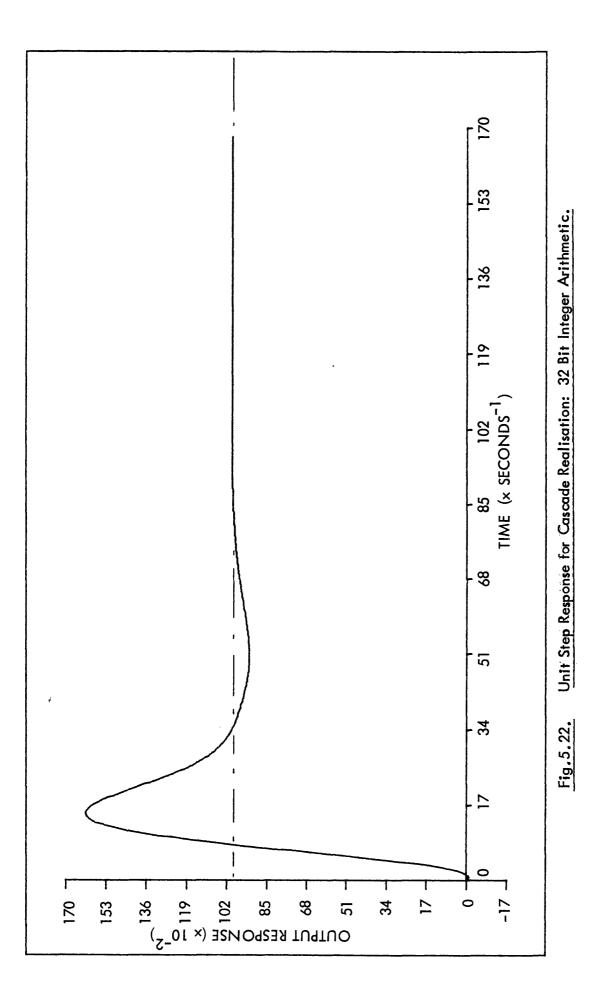

- Fig. 5.22. Unit Step Response for Cascade Realisation: 32 Bit Integer Arithmetic

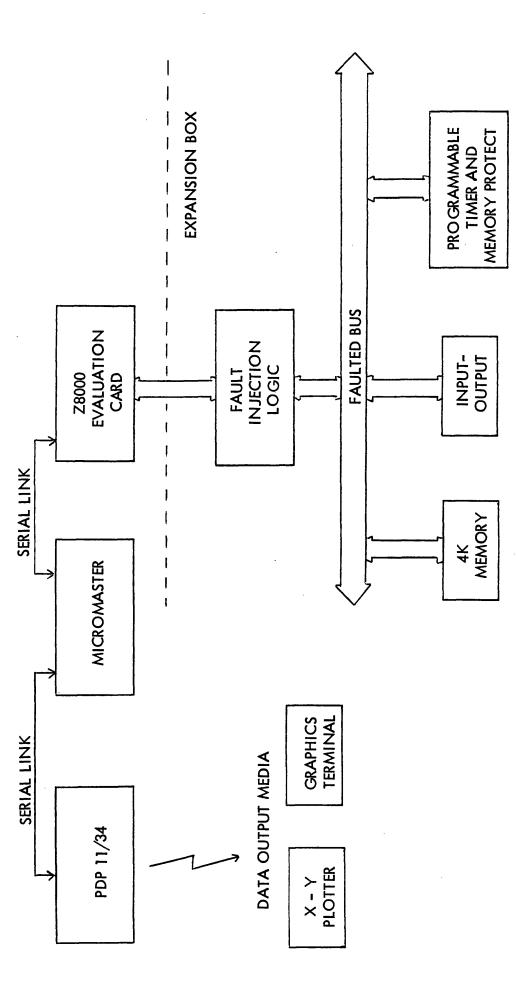

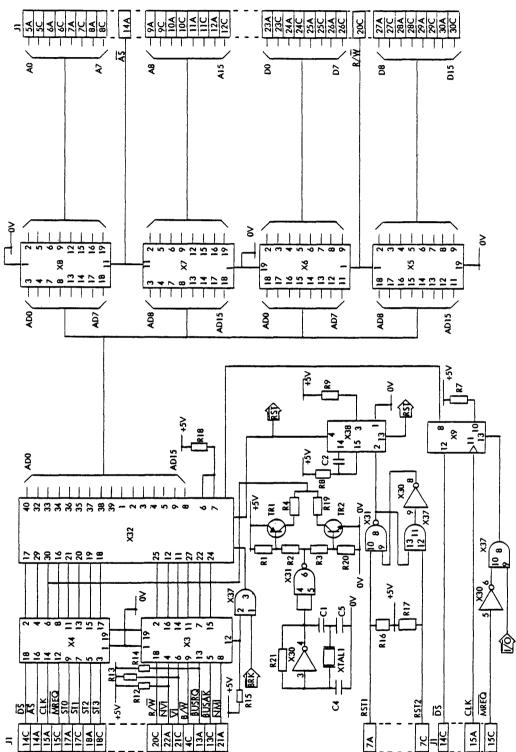

- Fig. 6.1. Overall Systems Diagram

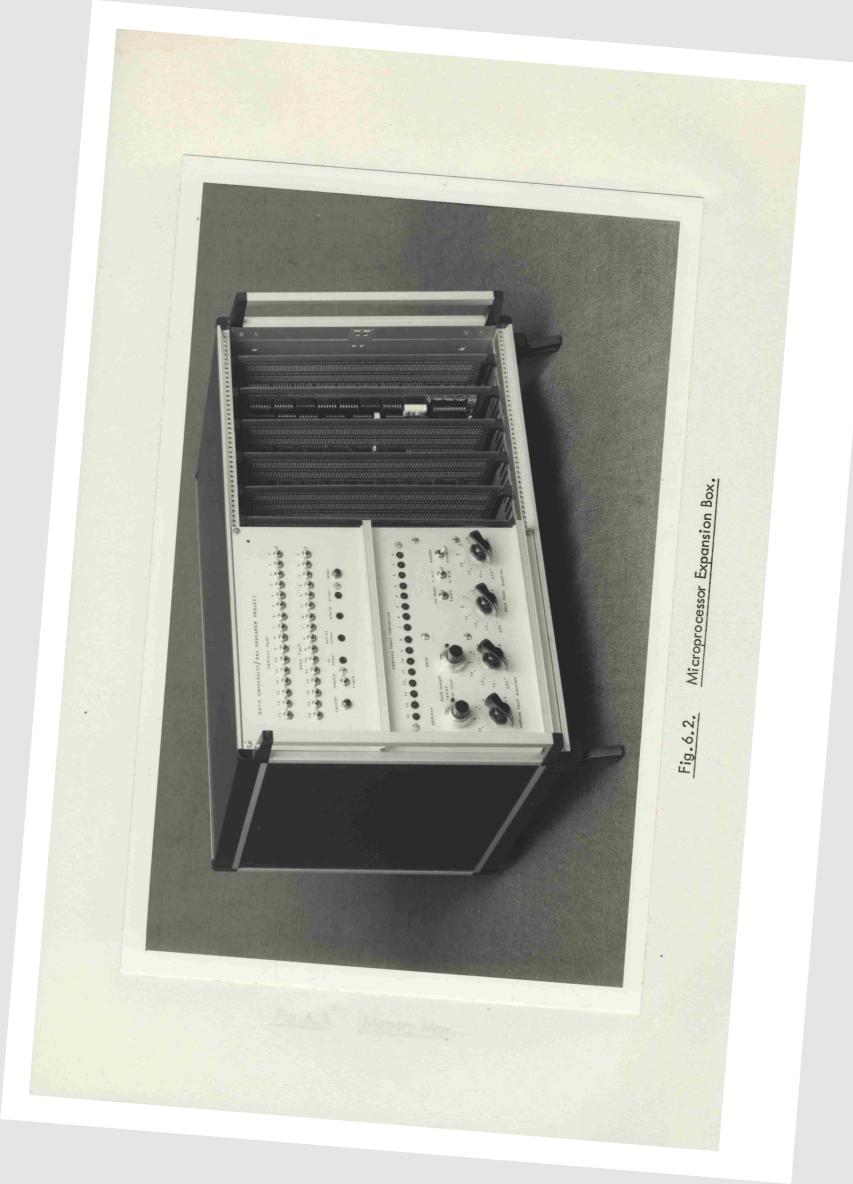

- Fig. 6.2. Photograph of Microprocessor Expansion Box

- Fig. 6.3. Memory Map

- Fig. 6.4. Input/Output Map

- Fig. 6.5. Schematic of Error Correcting Memory

- Fig. 6.6. Error Correcting Memory Board 1

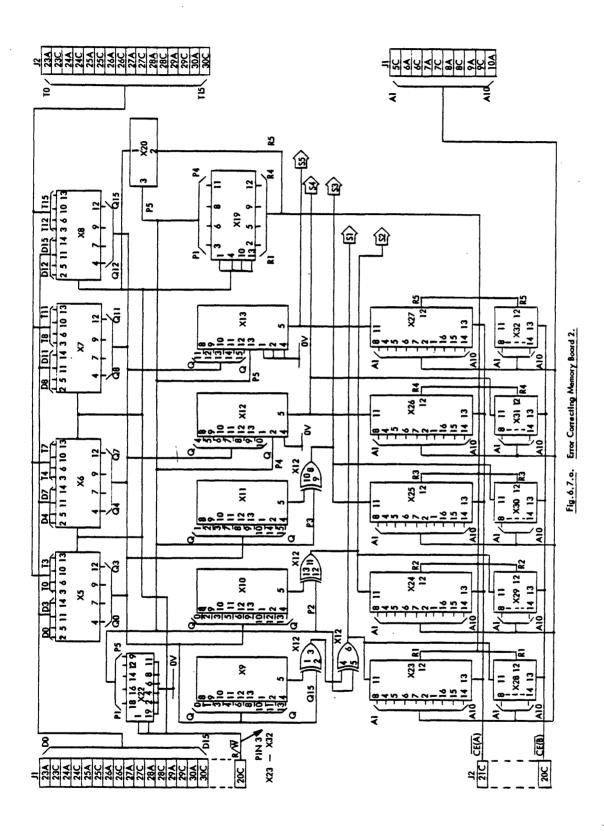

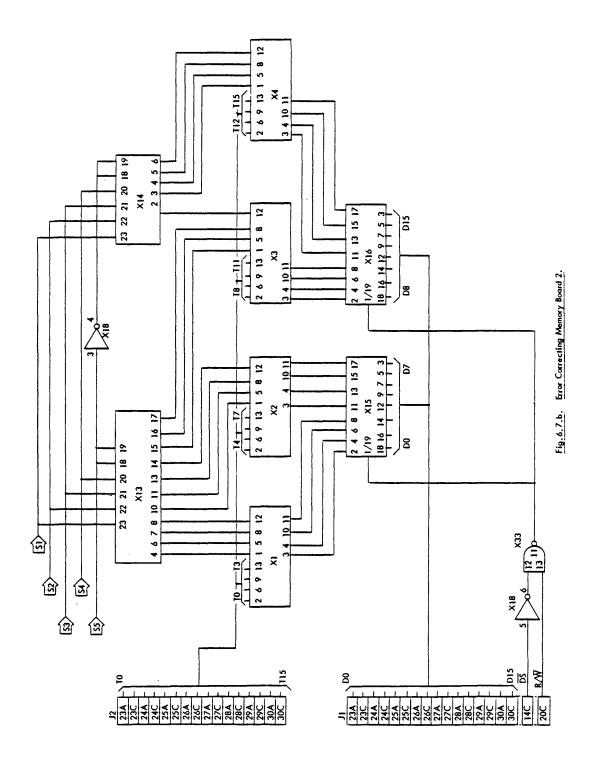

- Fig. 6.7. Error Correcting Memory Board 2

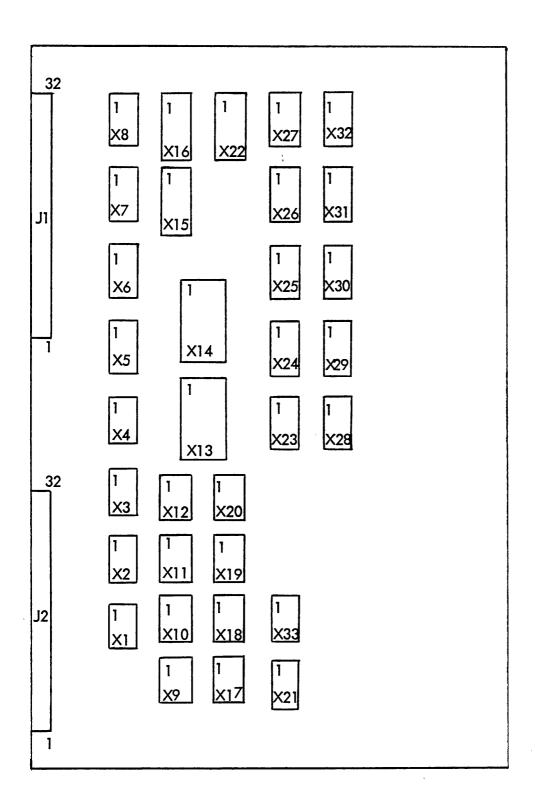

- Fig. 6.8. Layout of Error Correcting Memory Board 1

- Fig. 6.9. Layout of Error Correcting Memory Board 2

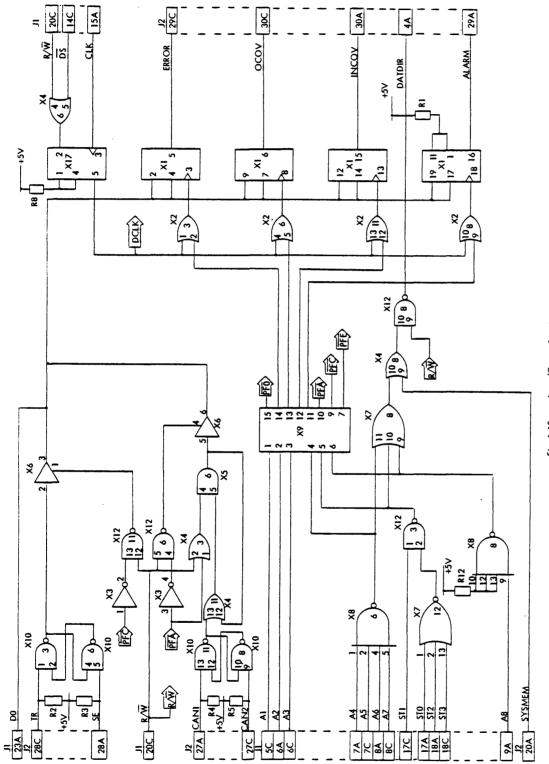

- Fig. 6.10. Input/Output Board

- Fig. 6.11. Layout of Input/Output Board

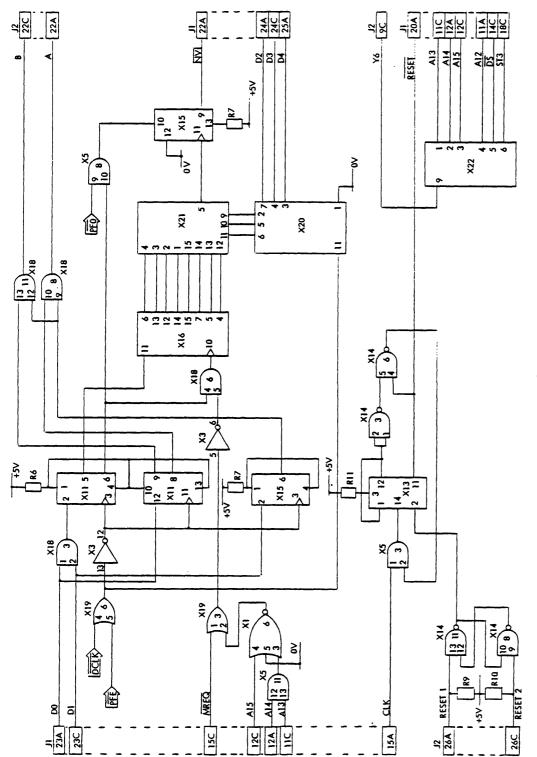

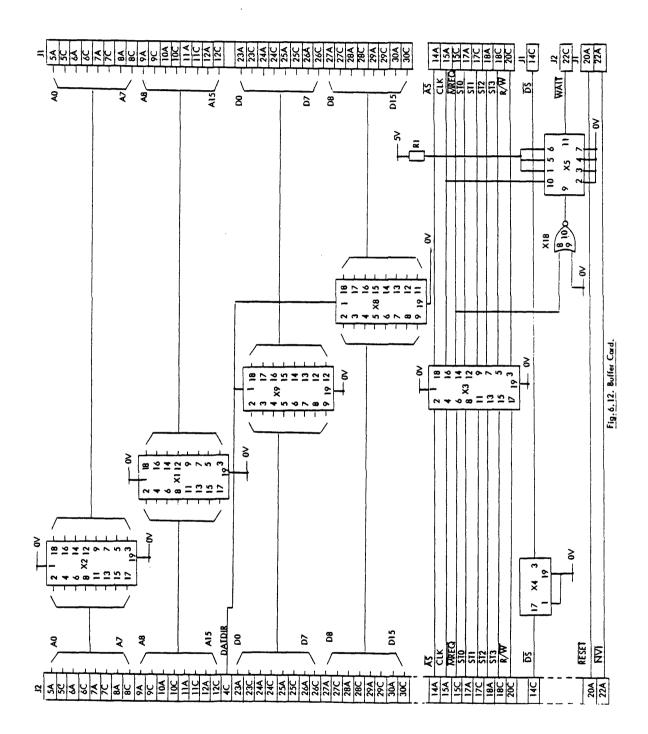

- Fig. 6.12. Buffer Card

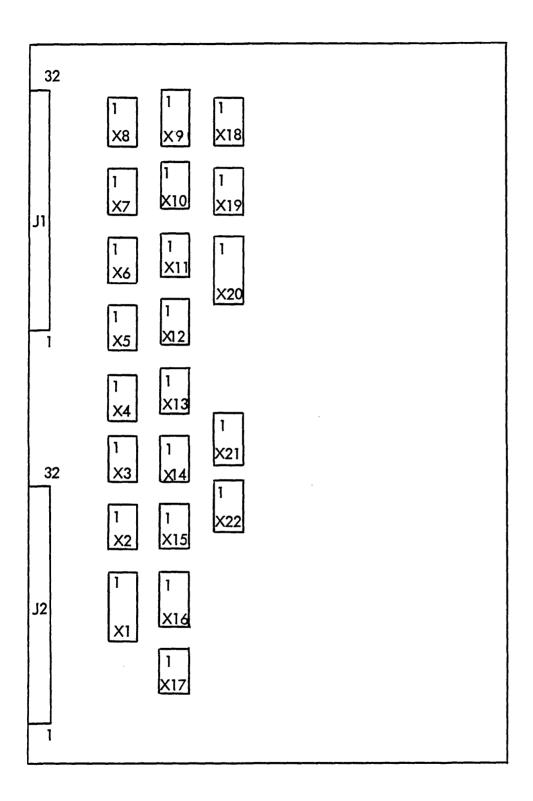

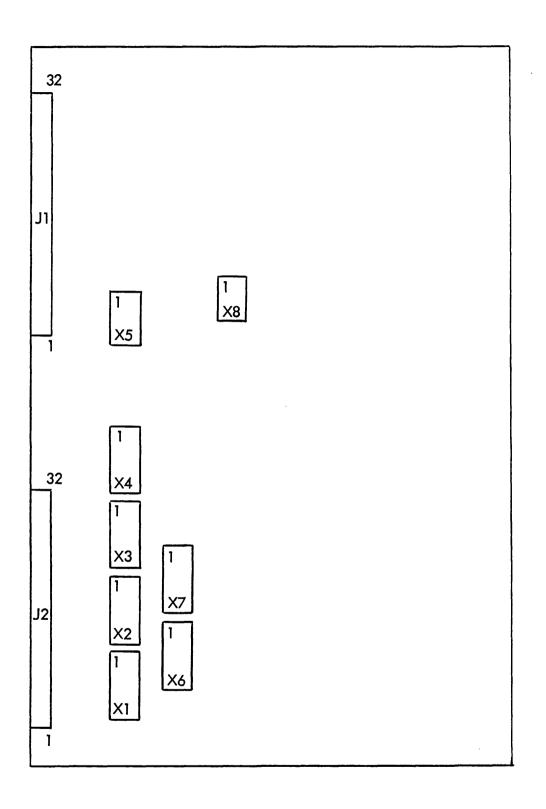

- Fig. 6.13. Layout of Buffer Card

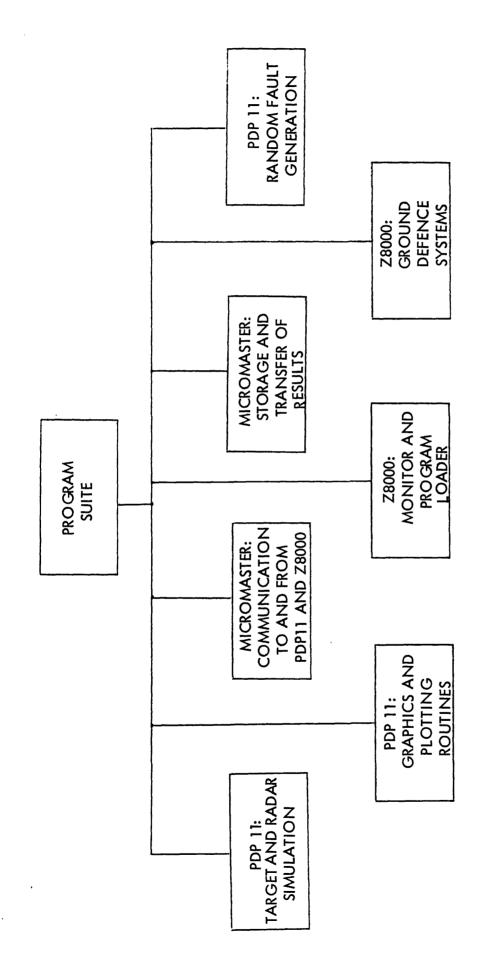

- Fig. 6.14. System Sottware Suite

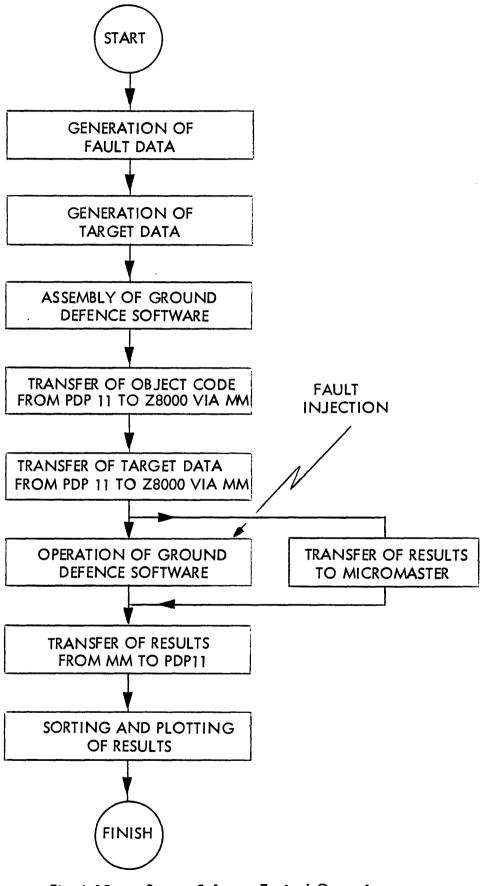

- Fig. 6.15. System Software Typical Operation

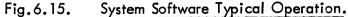

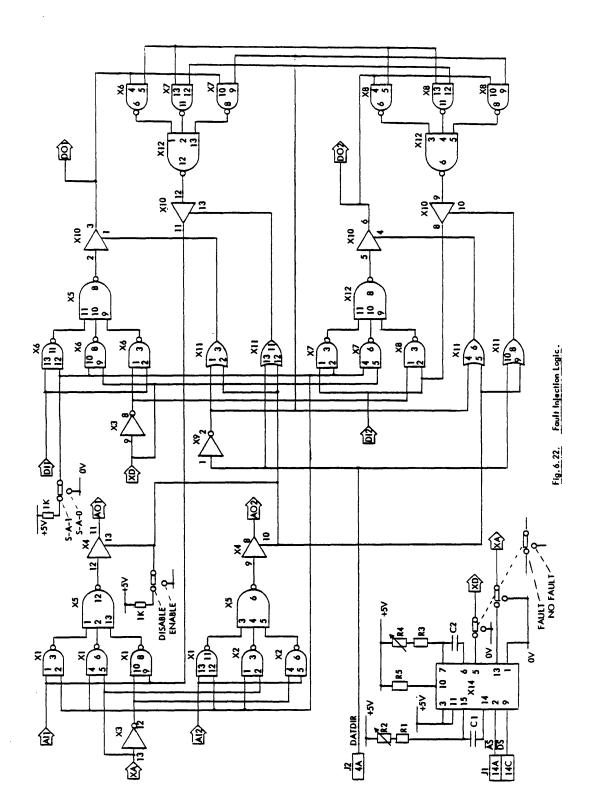

- Fig. 6.16. Schematic of Fault Injection Logic

- Fig. 6.17. Implementation of Address Fault Logic

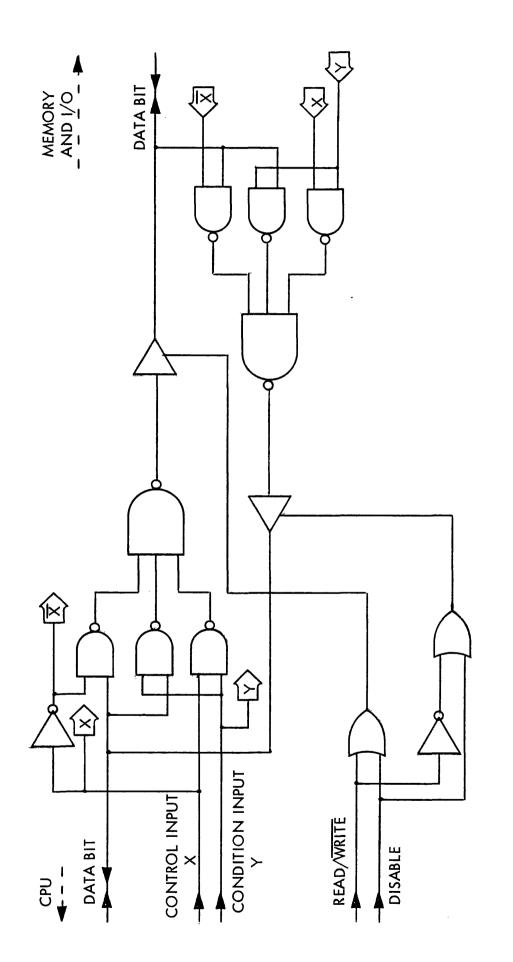

- Fig. 6.18. Control/Condition Input Circuitry

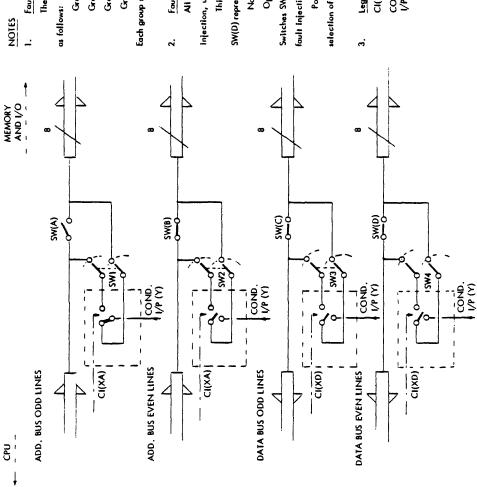

- Fig. 6. 19. Fault Injection Switching Arrangement

- Fig. 6.20. Implementation of Data Fault Logic

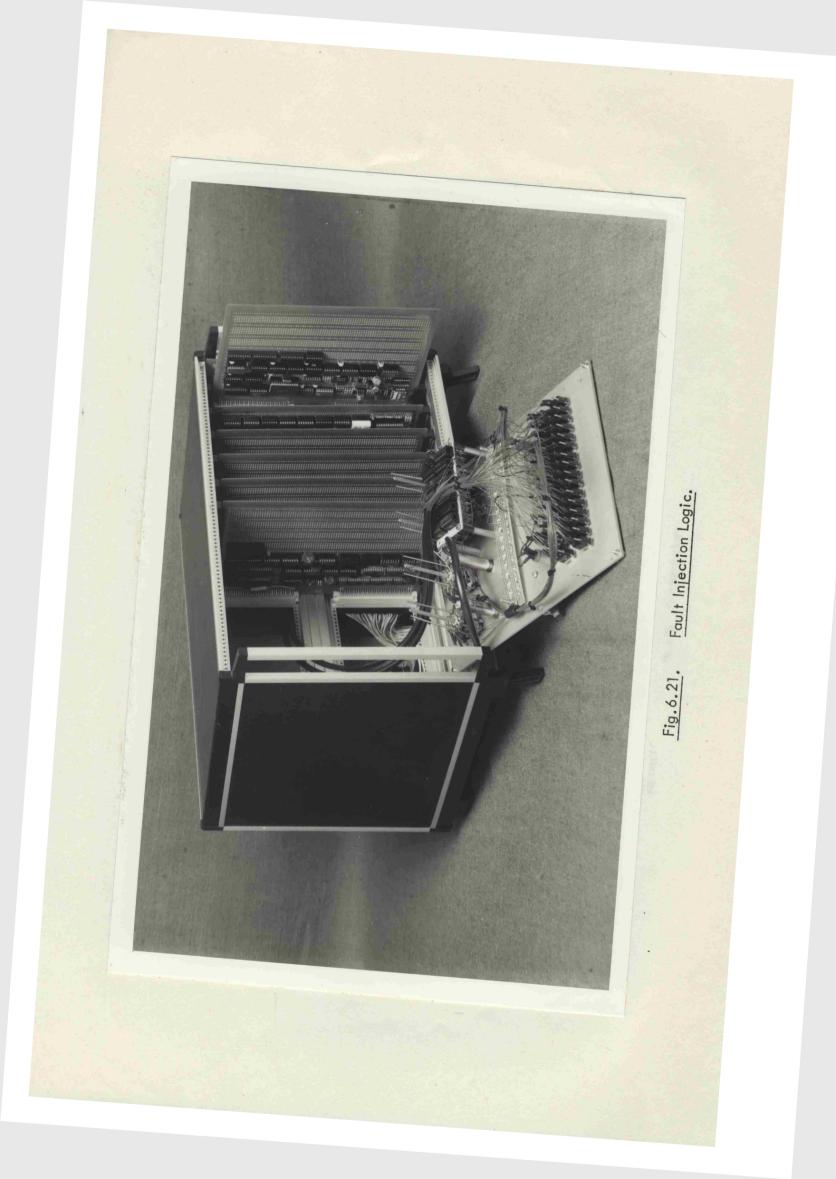

- Fig. 6.21. Photograph of Fault Injection Logic

- Fig. 6.22. Fault Injection Logic

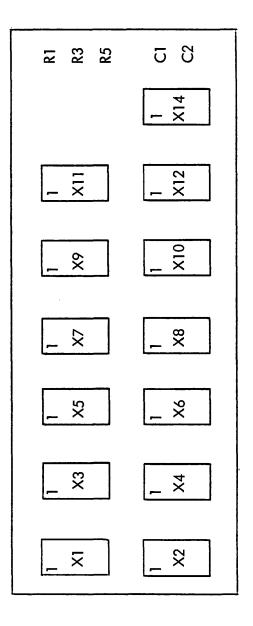

- Fig. 6.23. Layout of Fault Injection Logic

|  | Fig.7.1. | Three Leve | I Structure |

|--|----------|------------|-------------|

|--|----------|------------|-------------|

- Fig.7.2. Schematic of Watchdog Timer

- Fig.7.3. Recovery Interrupt Service Routine

- Fig.7.4. Default Data Bus

- Fig.7.5. Schematic of Trap Area

- Fig. 7.6. Generalised Form of Recovery Block

- Fig. 8.1. System Availability Related to Recovery Strategies

- Fig. 9.1. Design Philosophy for Inter Processor Communication

- Fig. 9.2. Local Recovery Strategy

- Fig. 9.3. Global Recovery Strategy

- Fig.9.4. Separation of Functions in Distributed System

- Fig. 9.5. Schematic of Real Time Fault Injection Mechanism

- Fig. 9.6. Specific Cycle Fault Injection

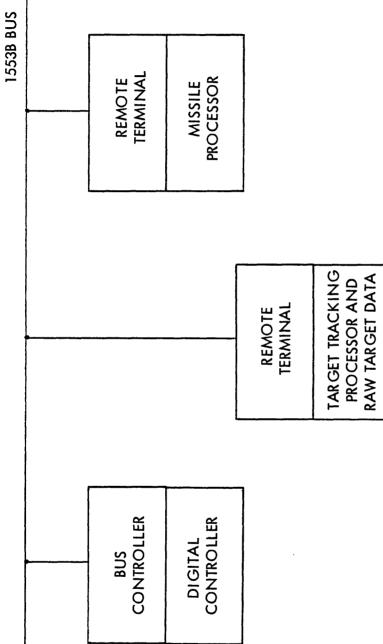

- Fig. 10.1. Overall Systems Diagram for Distributed Processing System

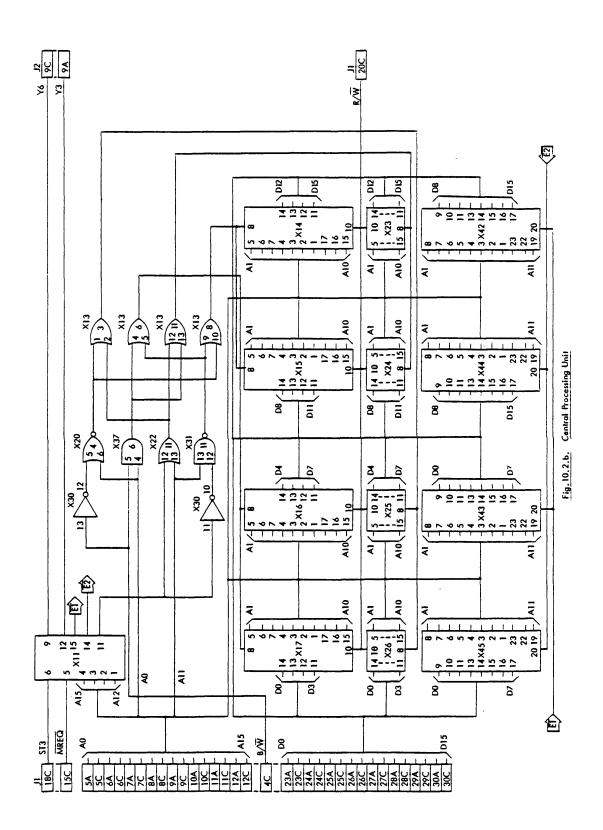

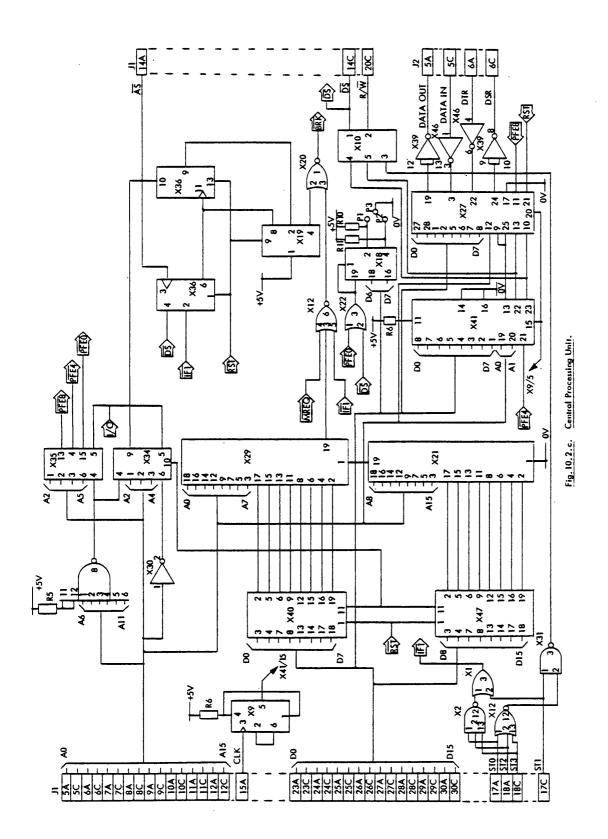

- Fig. 10.2. Central Processing Unit

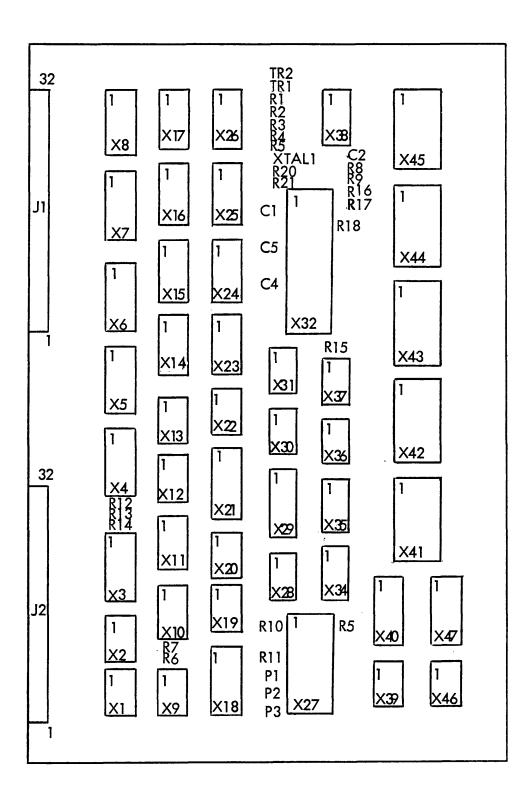

- Fig. 10.3. Layout of Central Processing Unit

- Fig. 10.4. Schematic of 1553B/Microprocessor Interface

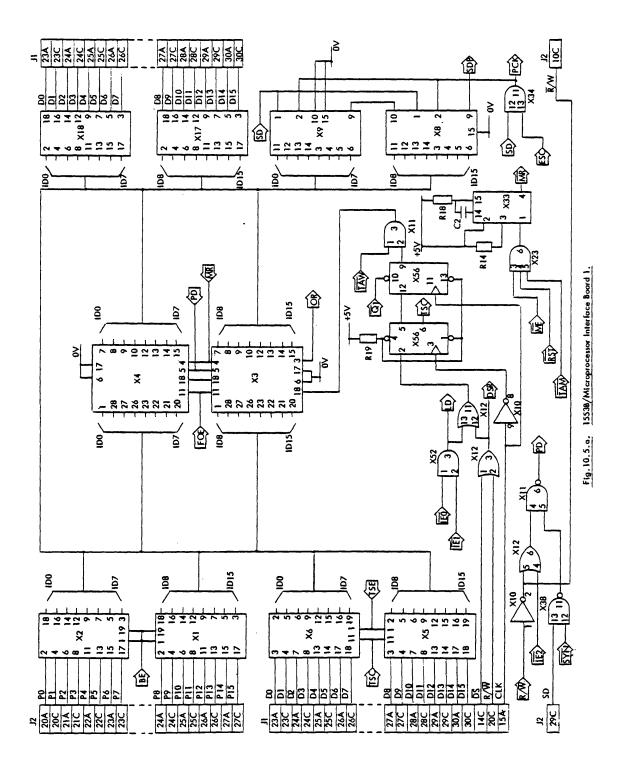

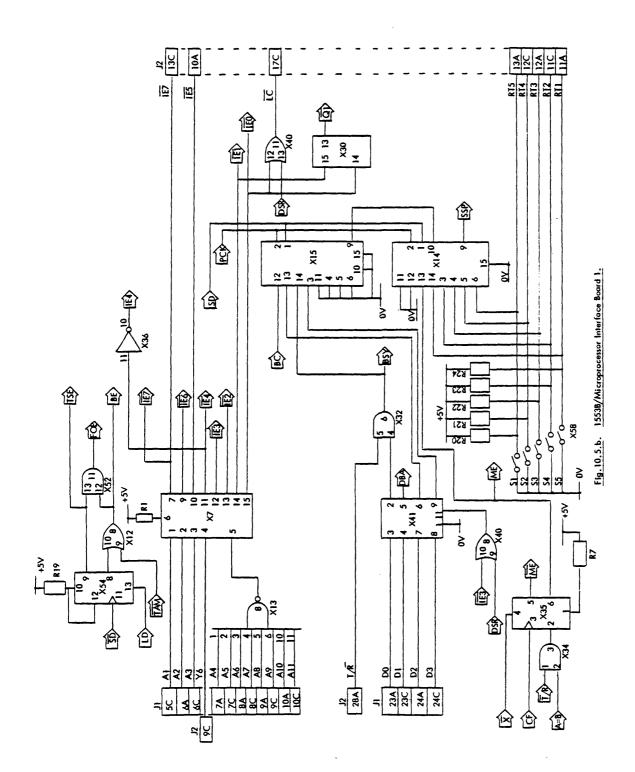

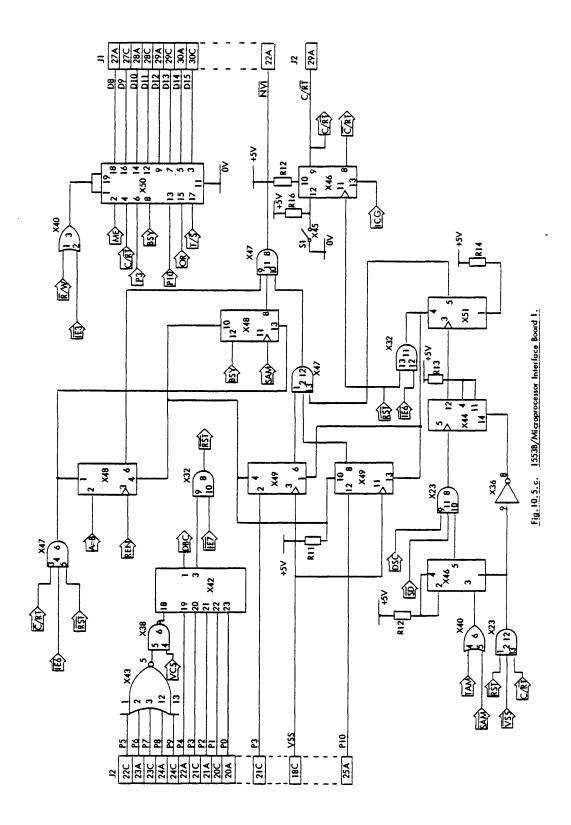

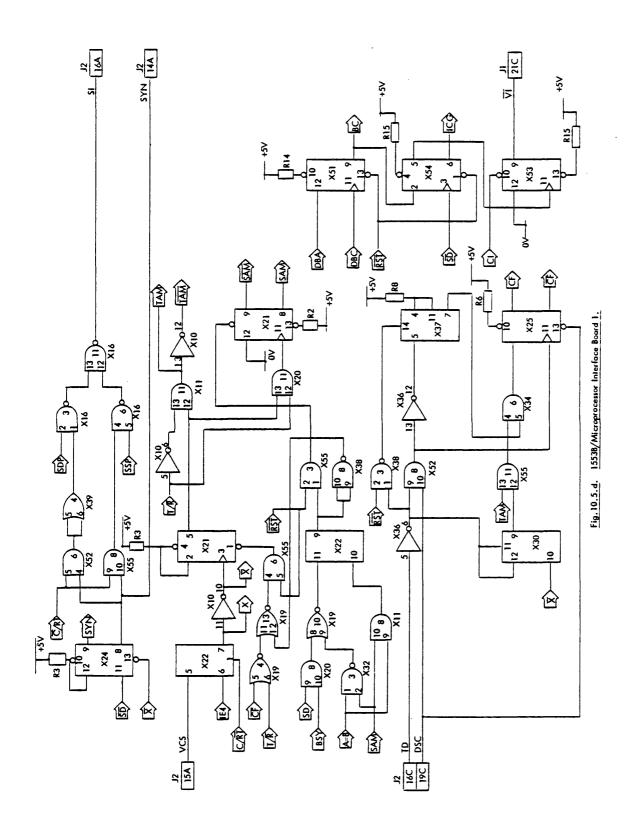

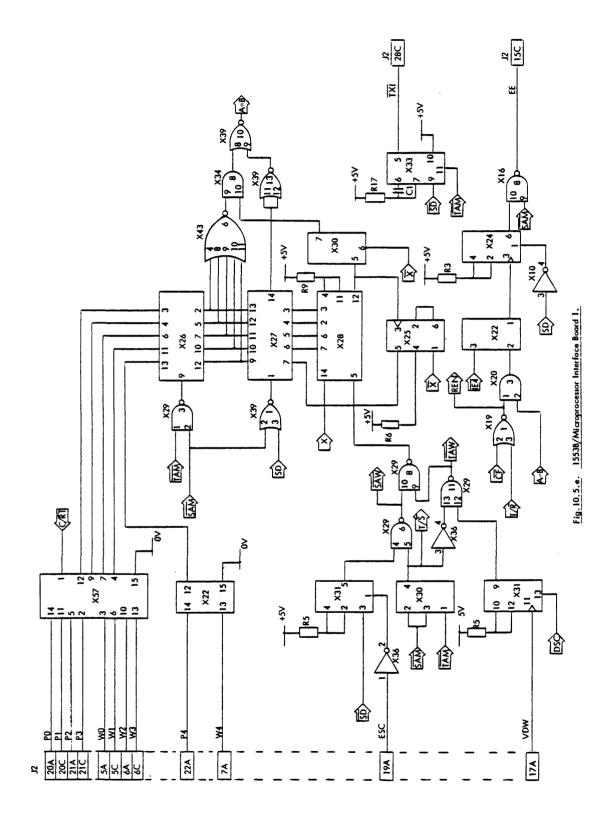

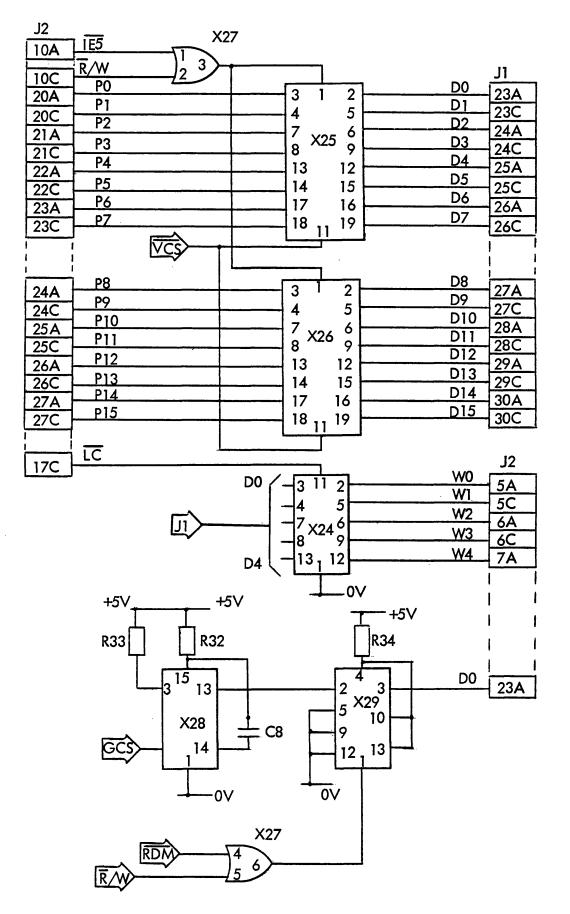

- Fig. 10.5. 1553B/Microprocessor Interface Board 1

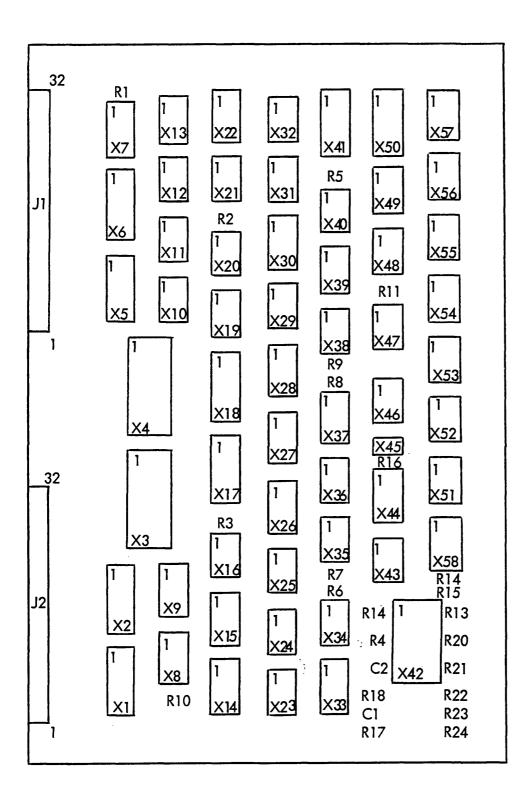

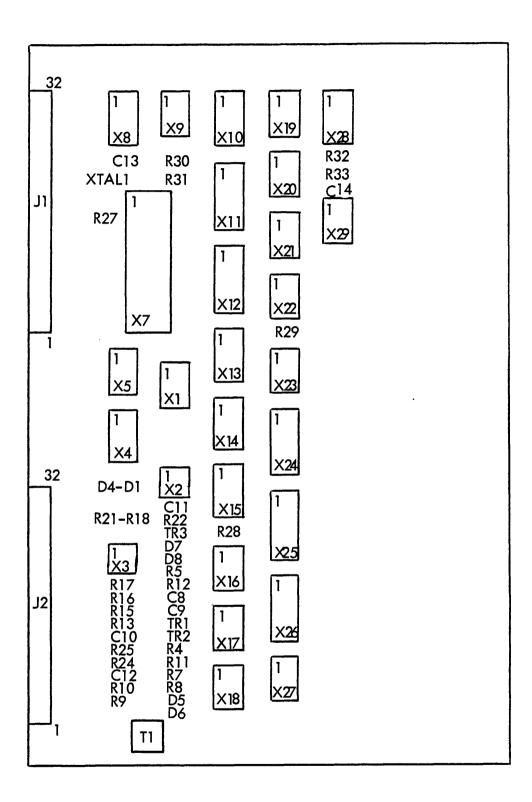

- Fig. 10.6. Layout of 1553B/Microprocessor Interface Board 1

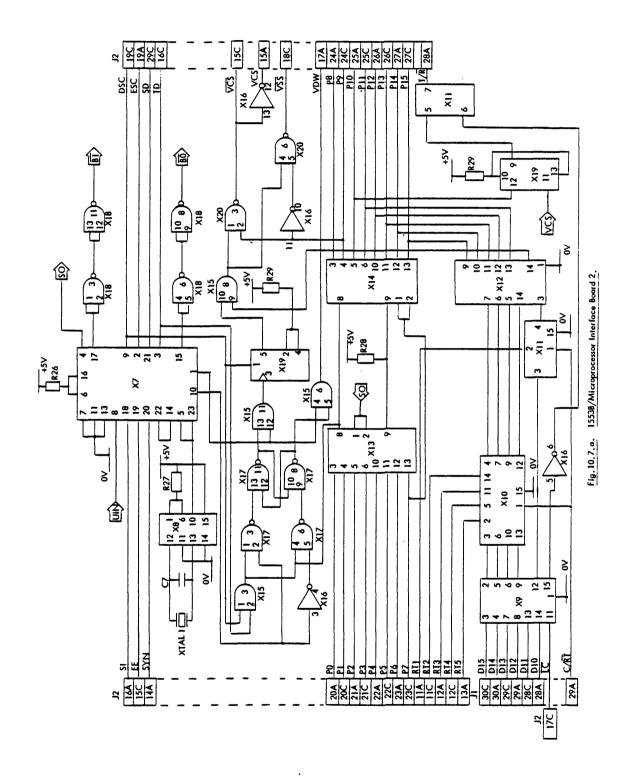

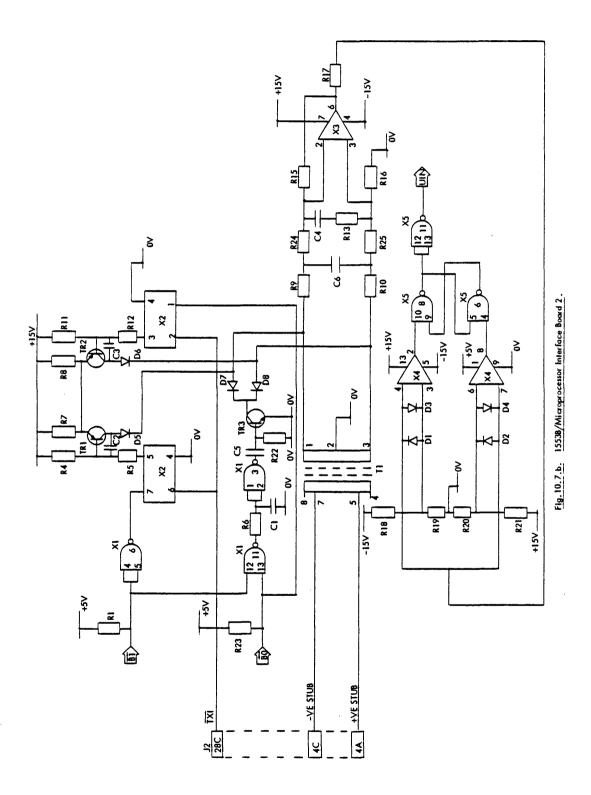

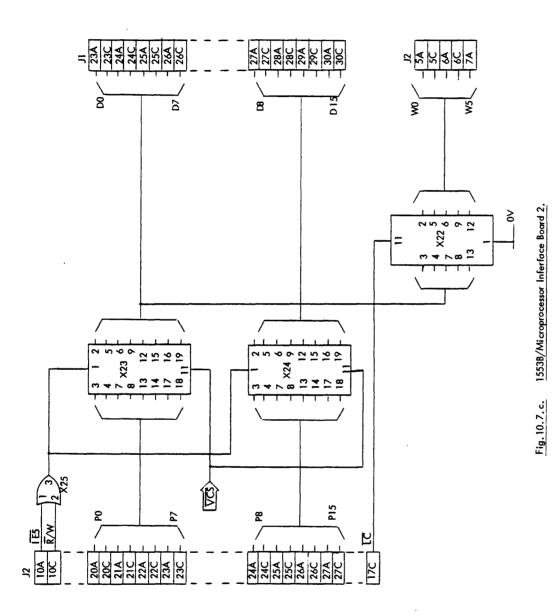

- Fig. 10.7. 1553B/Microprocessor Interface Board 2

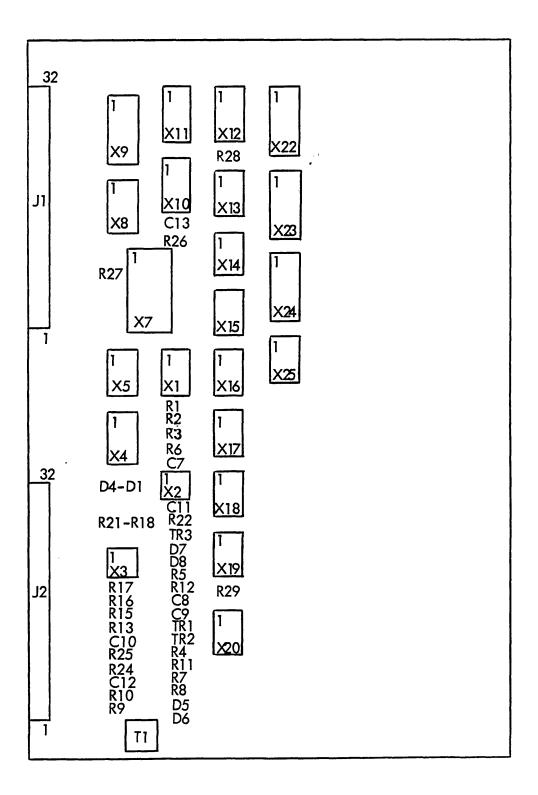

- Fig. 10.8. Layout of 1553B/Microprocessor Interface

- Fig. 10.9. Photograph of 1553B/Microprocessor Interface Boards

- Fig. 10.10. Message from Bus Controller: Hardware Operation

- Fig. 10.11. Connection of Terminal to 1553B Bus

- Fig. 10.12. Message to Bus Controller: Hardware Operation

- Fig. 10.13. Message to Remote Terminal: Hardware Operation

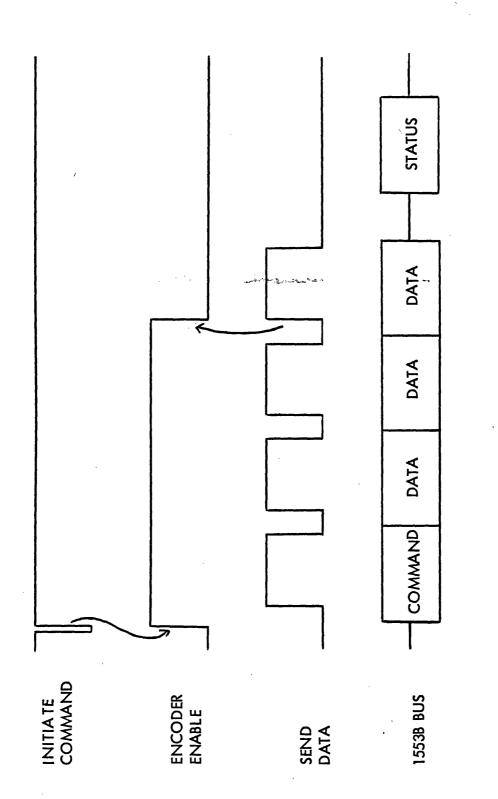

- Fig. 10.14. Message from Remote Terminal: Hardware Operation

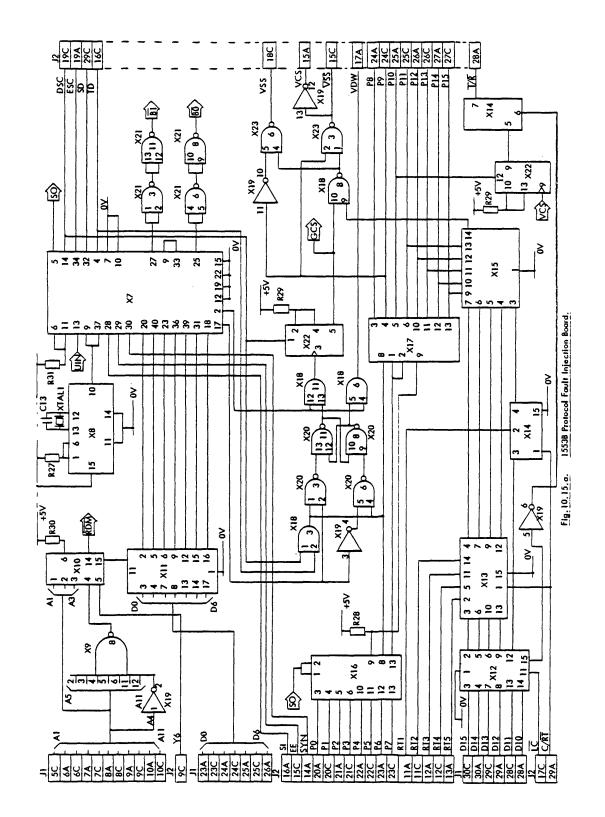

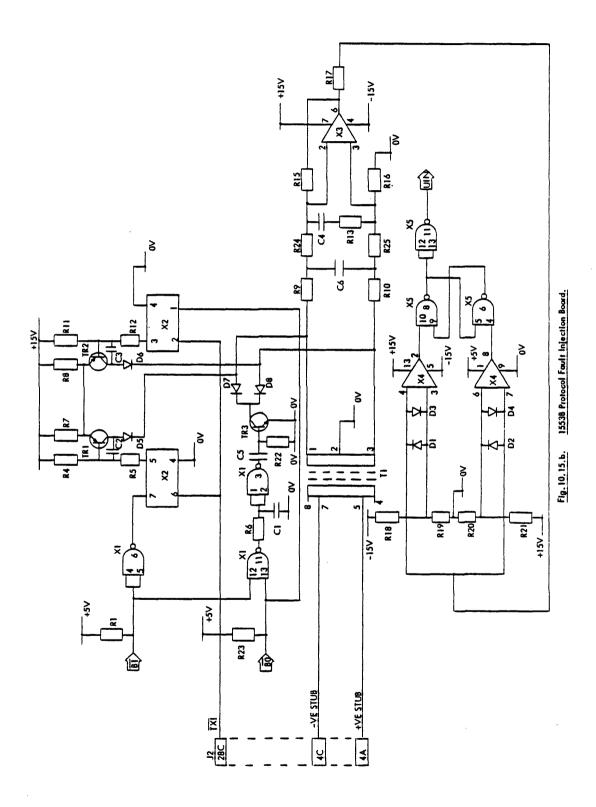

- Fig. 10.15. 1553B Protocol Fault Injection Board

- Fig. 10.16. Layout of 1553B Protocol Fault Injection Board

- Fig. 10.17. Message from Bus Controller: Software Operation

- Fig. 10.18. Message to Bus Controller: Software Operation

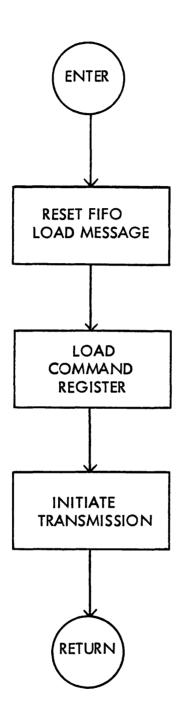

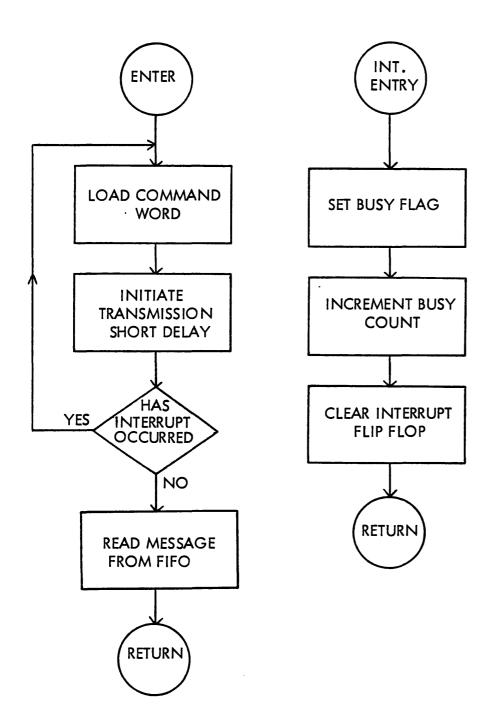

- Fig. 10.19. Message to Remote Terminal: Software Operation

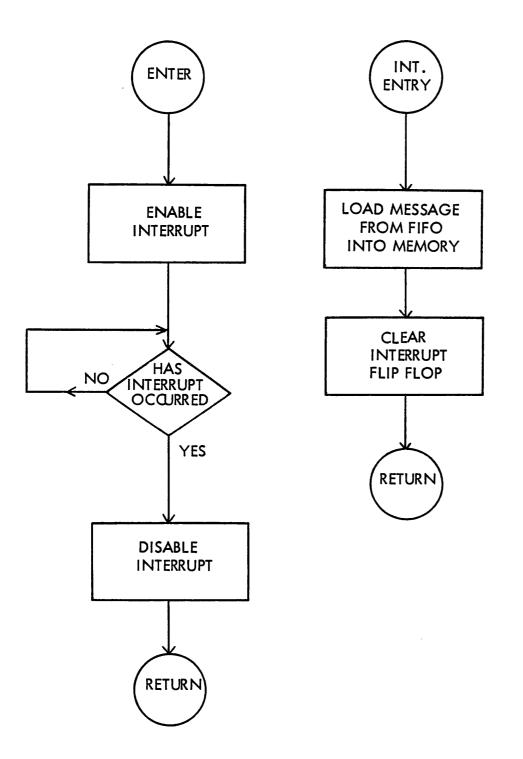

- Fig. 10.20. Message from Remote Terminal: Software Operation

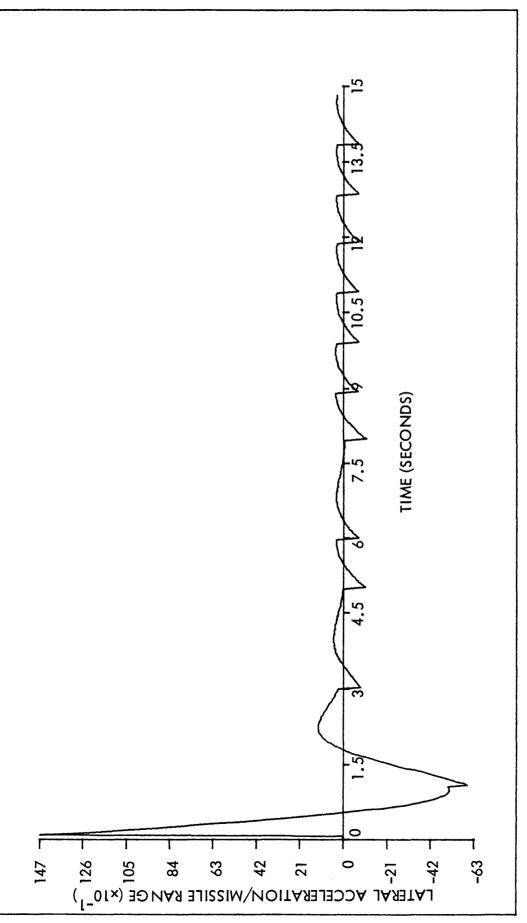

- Fig. 11.1. Missile Angle Plot

- Fig. 11.2. Missile Range Plot

- Fig. 11.3. System Configuration for Baseline Results

- Fig. 11.4. Data Corruption Type Fault in Gathering Phase (2 seconds)

- Fig. 11.5. Data Corruption Type Fault in Gathering Phase (4 seconds)

- Fig. 11.6. Data Corruption Type Fault in Gathering Phase  $(\frac{1}{4} \text{ second})$

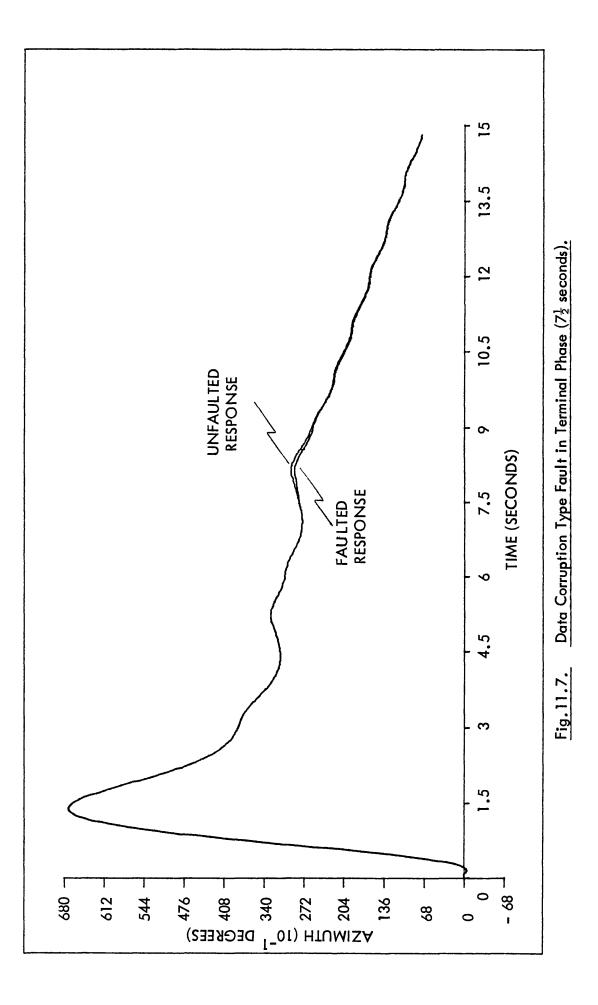

- Fig. 11.7. Data Corruption Type Fault in Terminal Phase  $(7\frac{1}{2} \text{ seconds})$

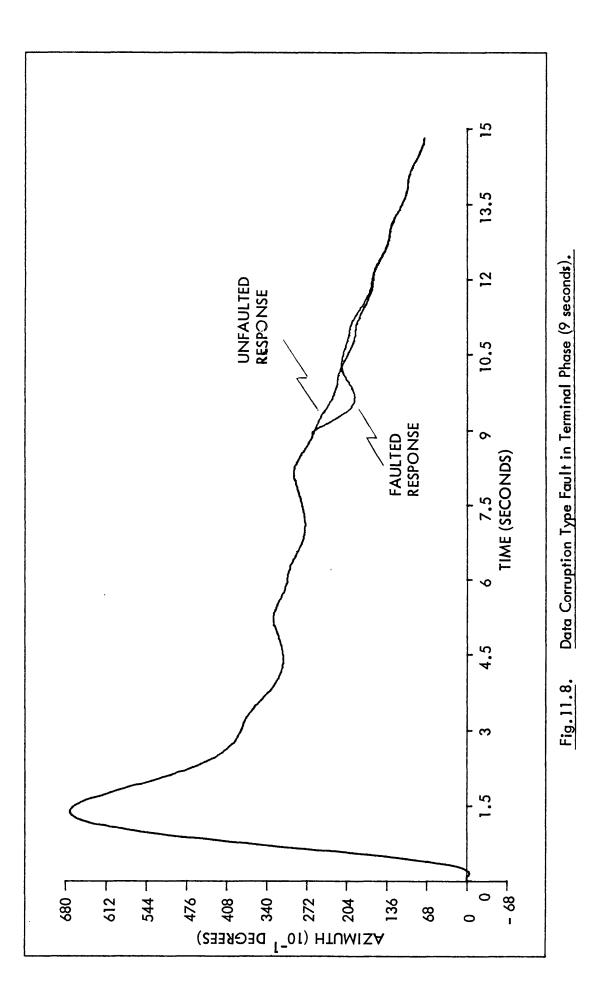

- Fig. 11.8. Data Corruption Type Fault in Terminal Phase (9 seconds)

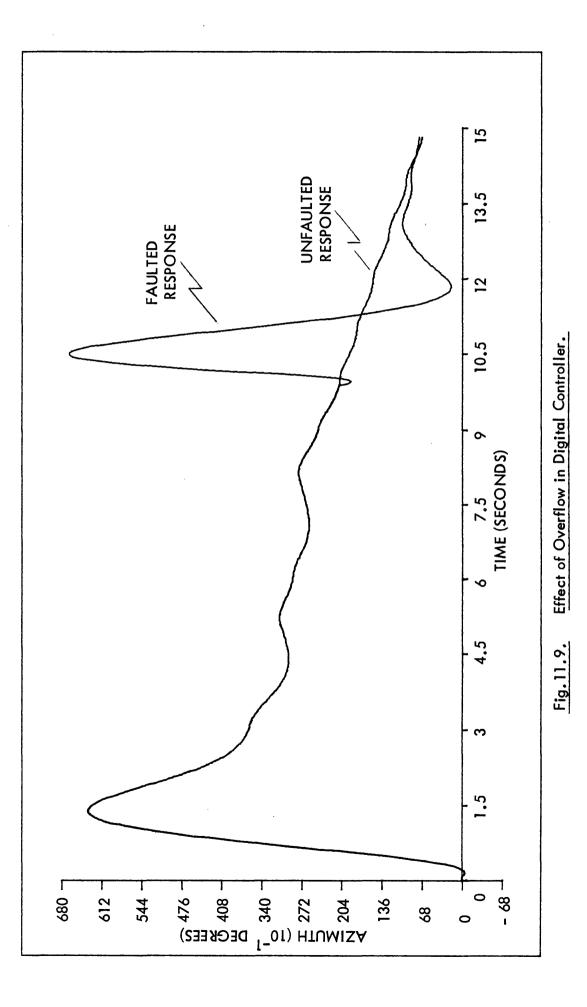

- Fig. 11.9. Effect of Overflow in Digital Controller

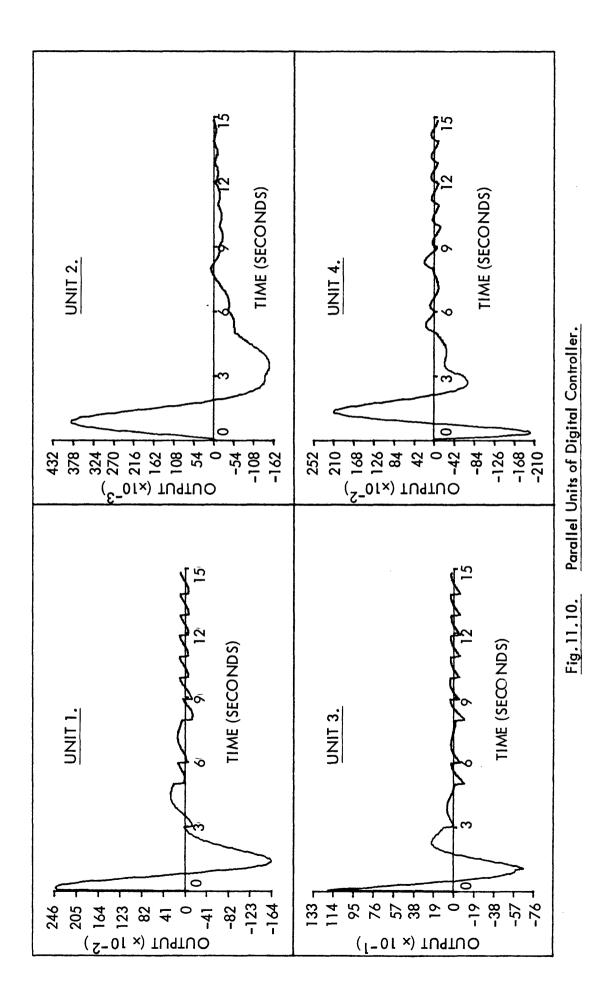

- Fig. 11.10. Parallel Units of Digital Controller

- Fig.11.11. Guidance Demand

- Fig. 11.12. Omission of Acceptance Test Due to a Fault

- Fig. 11.13. System Recovery

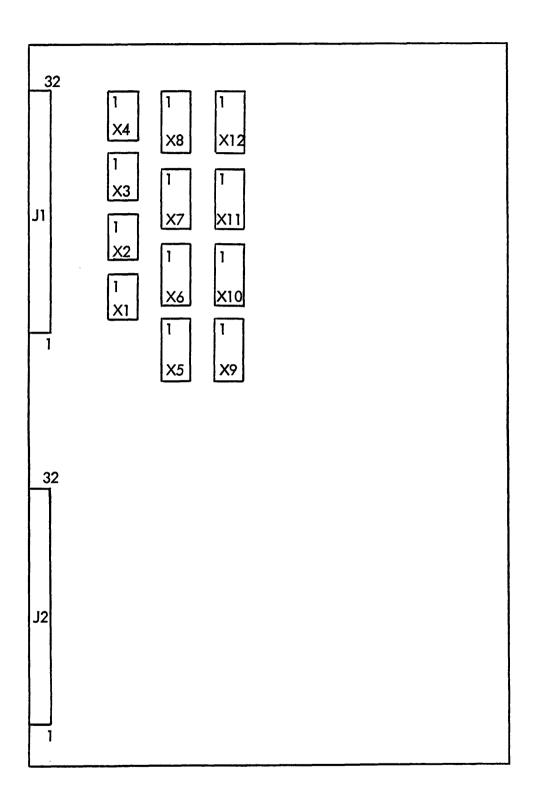

- Fig. 12.1. 4K Memory Board

- Fig. 12.2. Layout of 4K Memory Board

- Fig. 12.3. System Configuration for Remote Terminal Failure

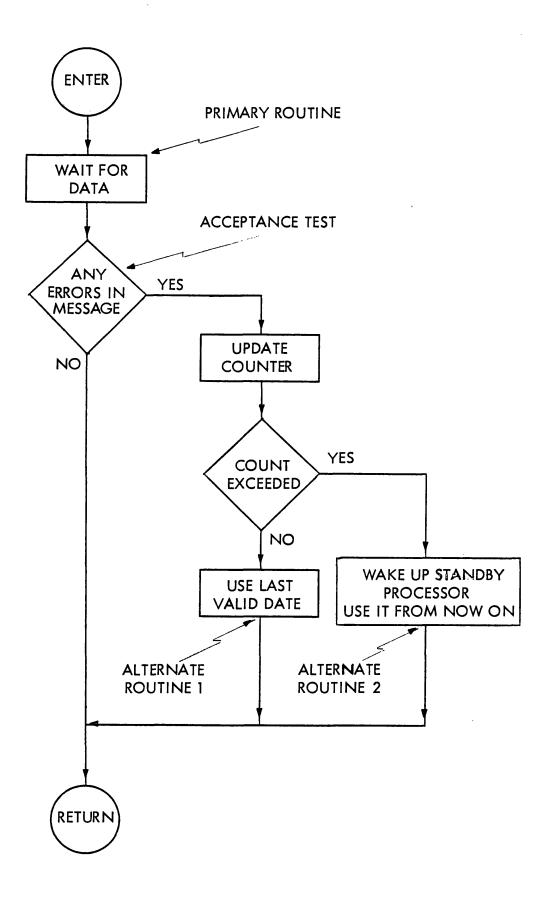

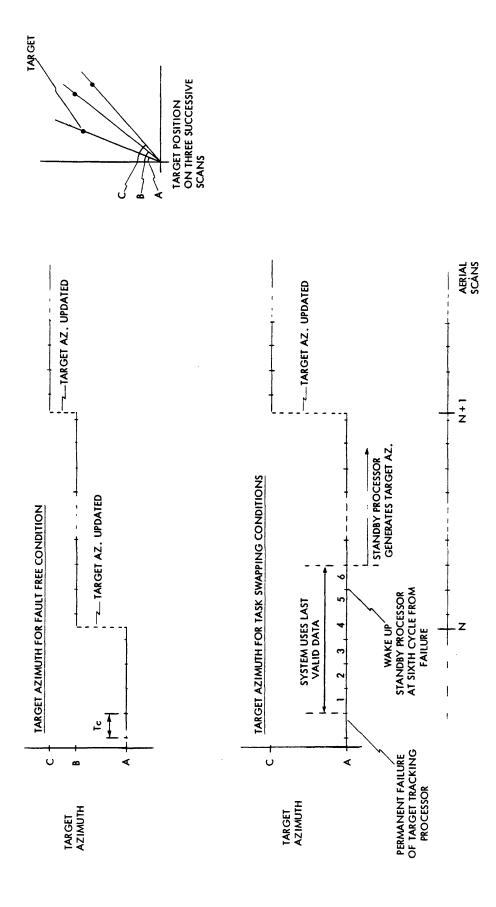

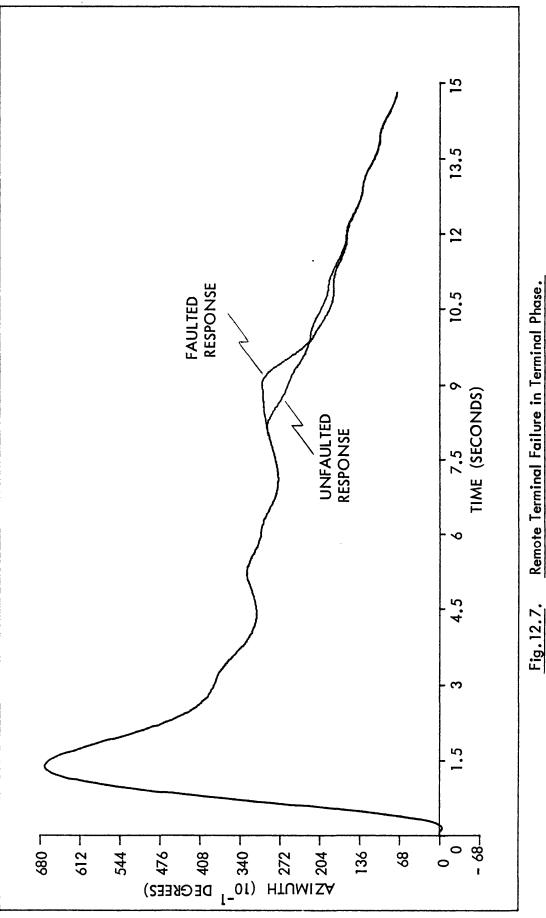

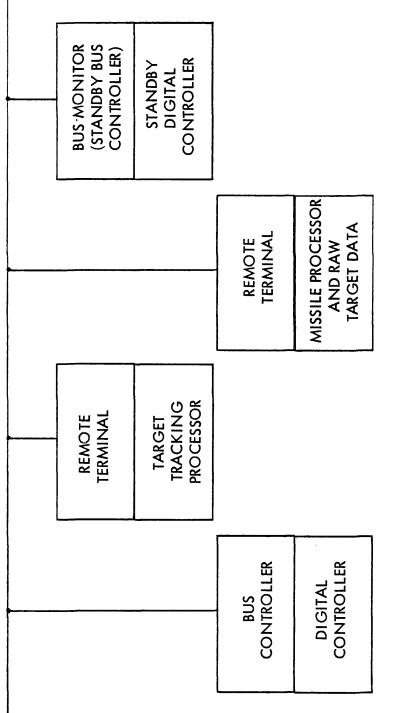

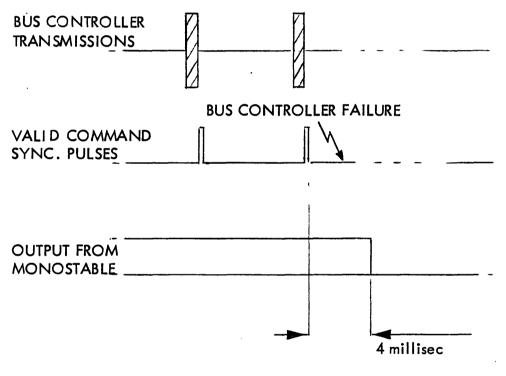

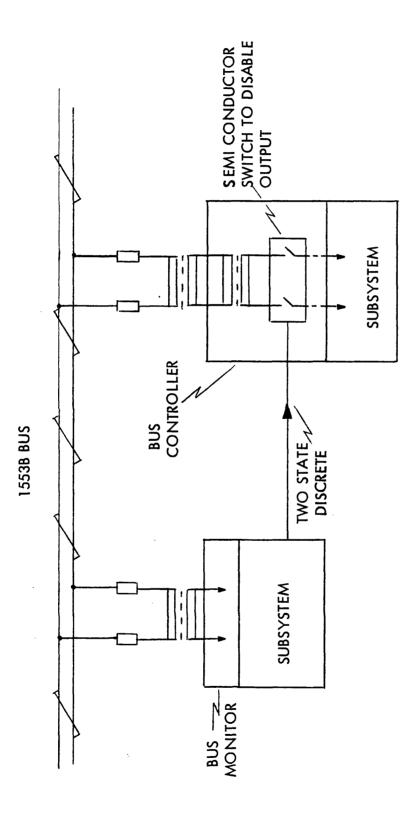

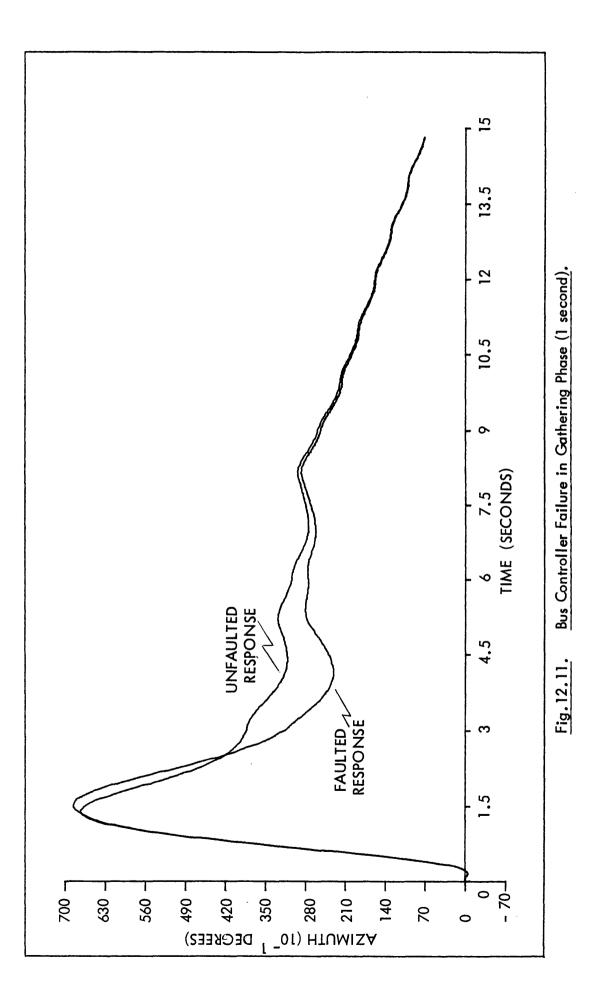

#### Schematic of Task Swapping Fig. 12.4. Fig. 12.5. Failure of Target Tracking Processor Fig. 12.6. Remote Terminal Failure in Gathering Phase Fig. 12.7. Remote Terminal Failure in Terminal Phase Fig. 12.8. System Configuration for Bus Controller Failure Fig. 12.9. **Bus Inactivity Detection** Fig. 12.10. Use of Discrete to Disable Failed Bus Controller Bus Controller Failure in Gathering Phase (1 second) Fig. 12.11.

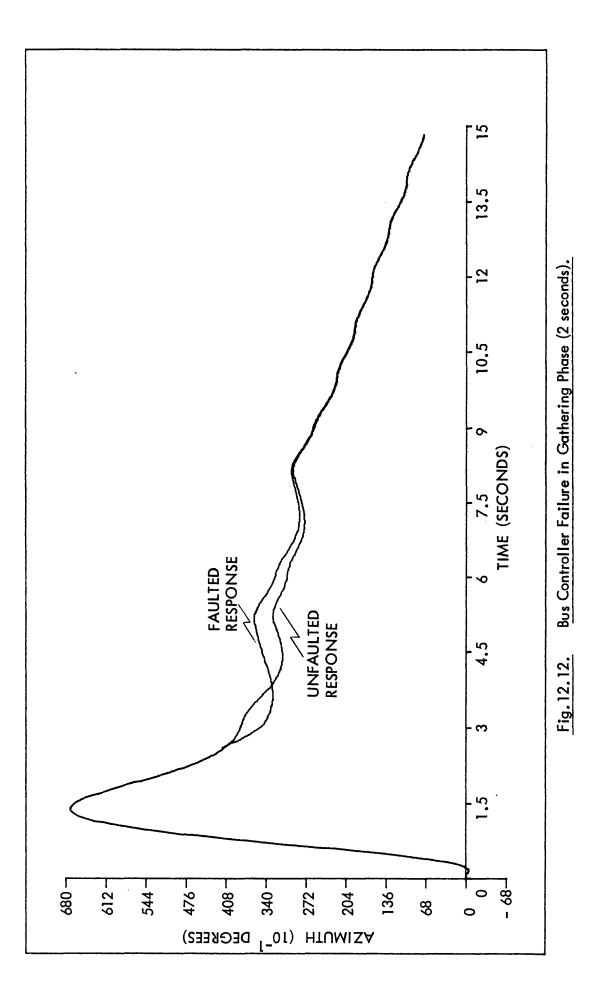

- Fig. 12.12. Bus Controller Failure in Gathering Phase (2 seconds)

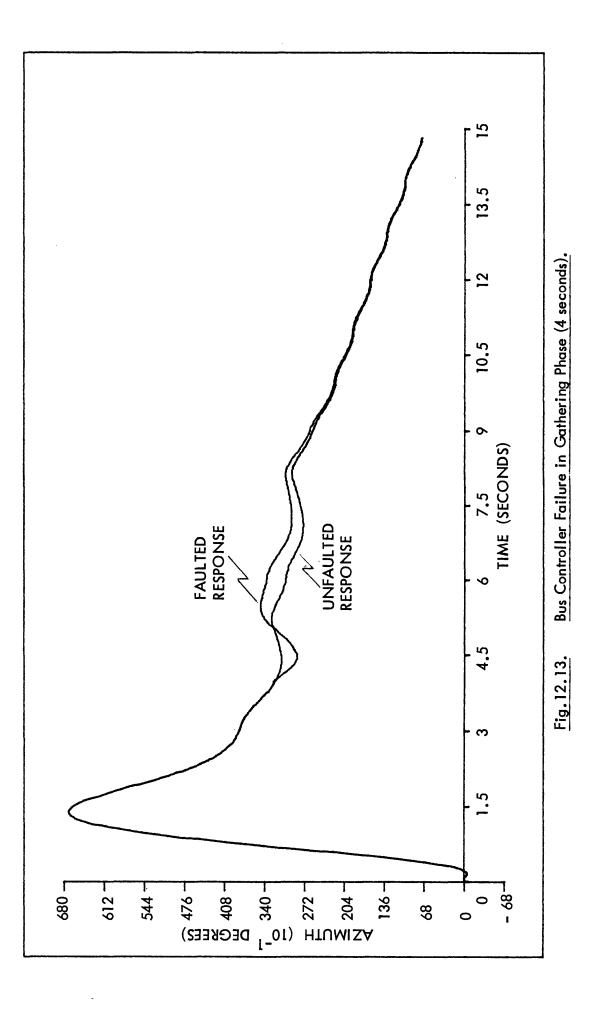

- Fig. 12.13. Bus Controller Failure in Gathering Phase (4 seconds)

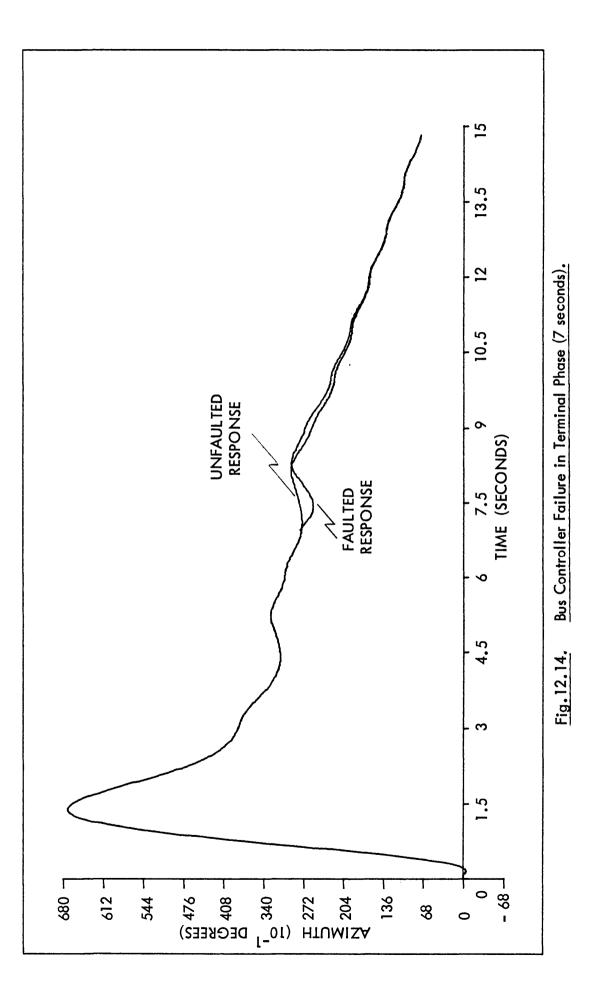

- Fig. 12.14. Bus Controller Failure in Terminal Phase (7 seconds)

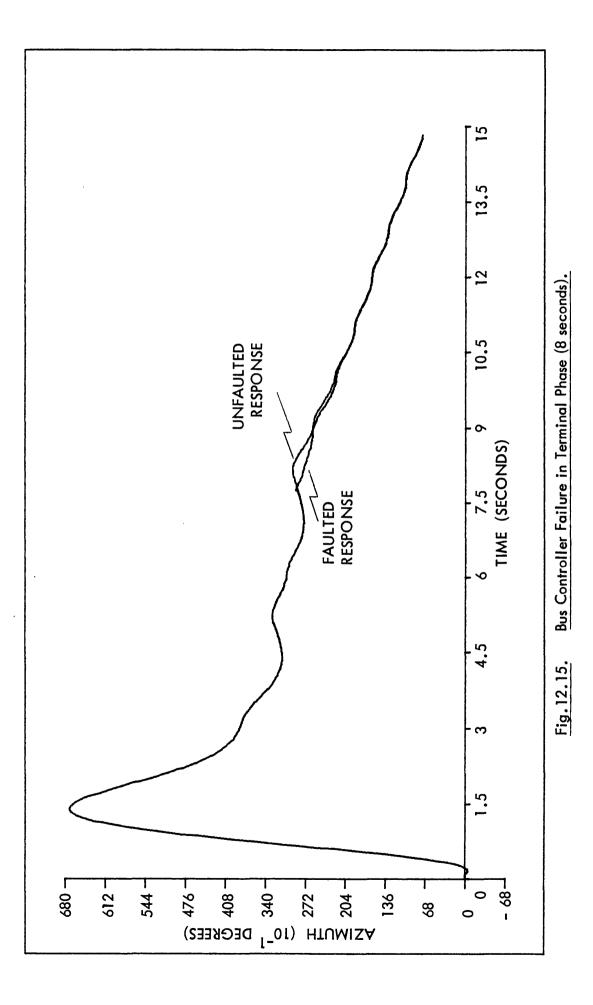

- Fig. 12.15. Bus Controller Failure in Terminal Phase (8 seconds)

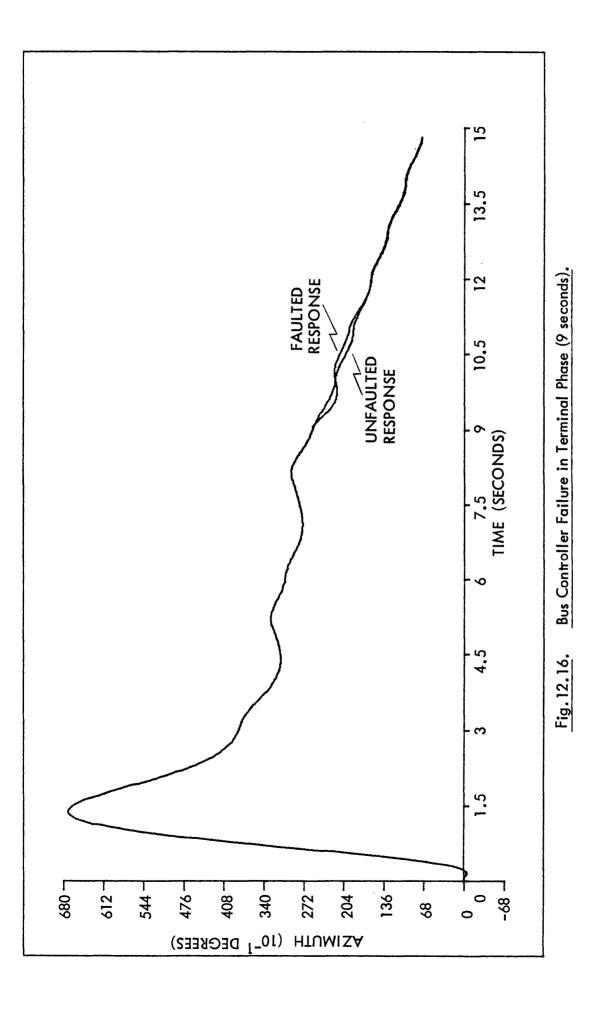

- Fig. 12.16. Bus Controller Failure in Terminal Phase (9 seconds)

- Fig. 14.1. MASCOT Diagram for Target Tracking Process

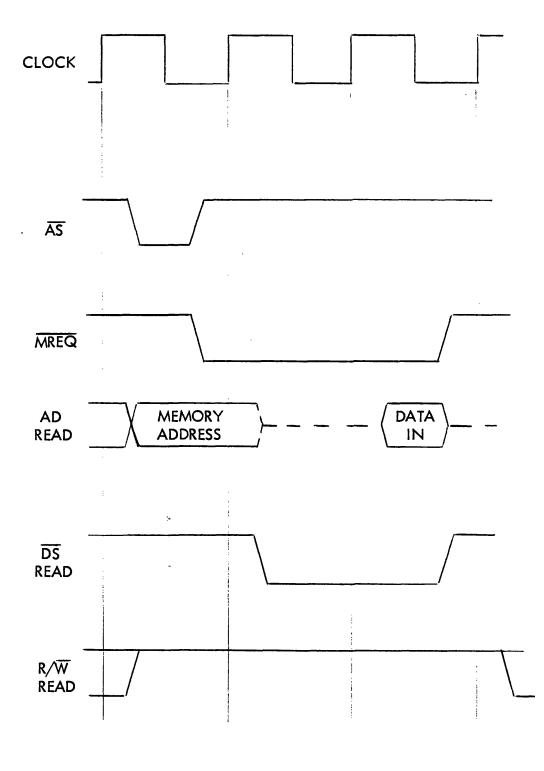

- Fig.B.1. Z8000 Memory Read Cycle

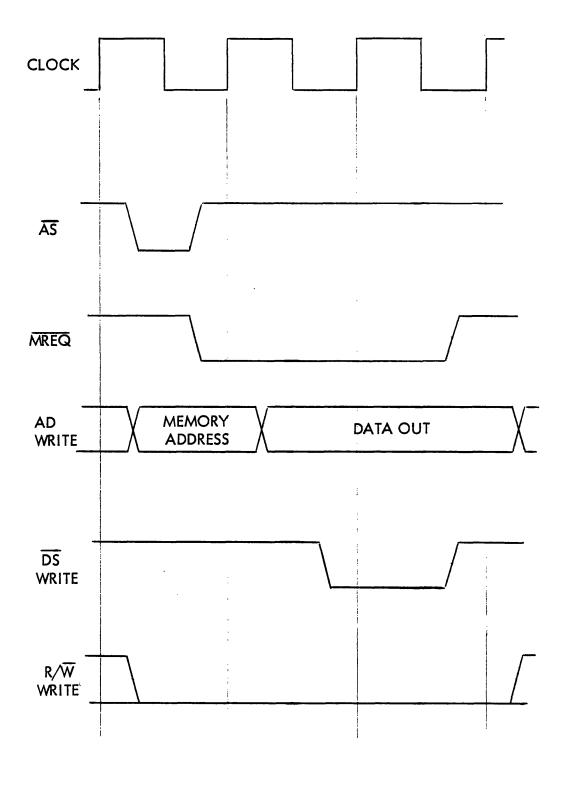

- Fig. B. 2. Z8000 Memory Write Cycle

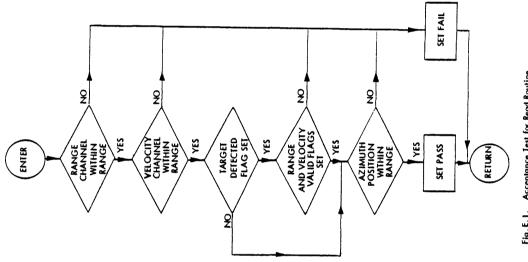

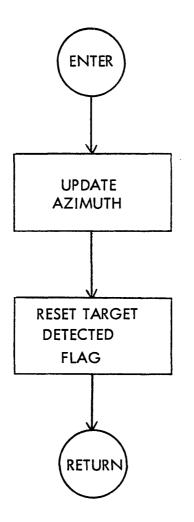

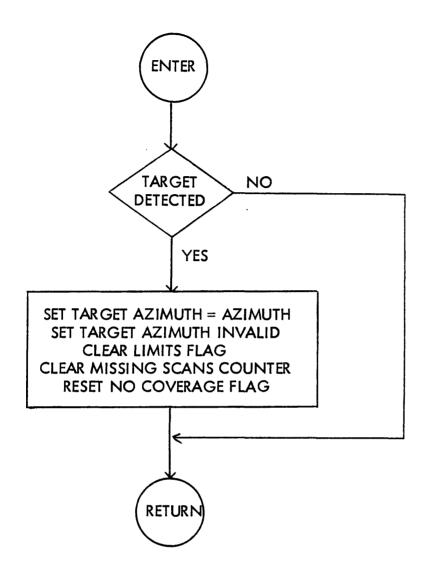

- Fig. E.1. Acceptance Test for Read Routine

- Fig. E.2. Read Alternate Routine

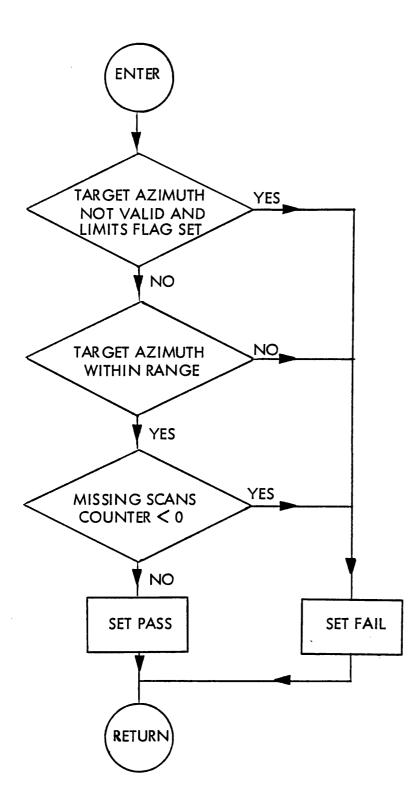

- Fig. E.3. Acceptance Test for Azimuth Inhibit

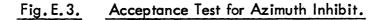

- Fig. E.4. Azimuth Inhibit Alternate Routine

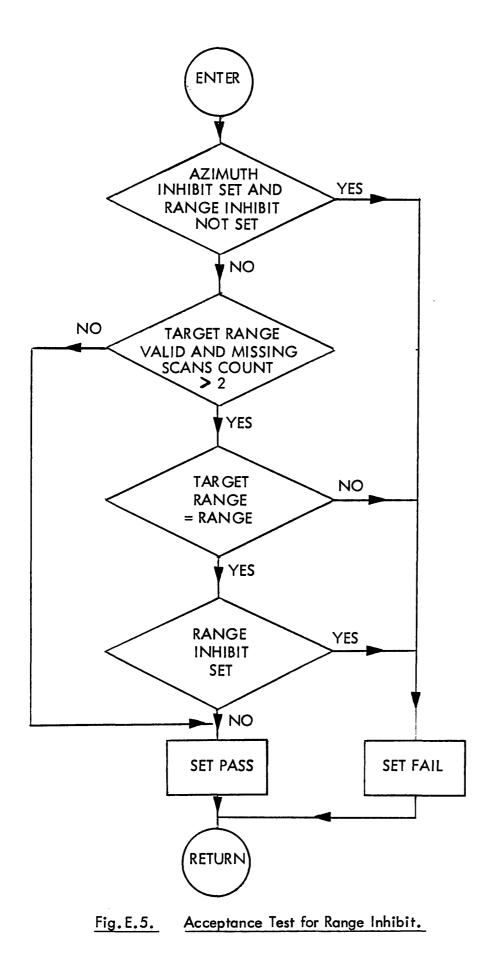

- Fig.E.5. Acceptance Test for Range Inhibit

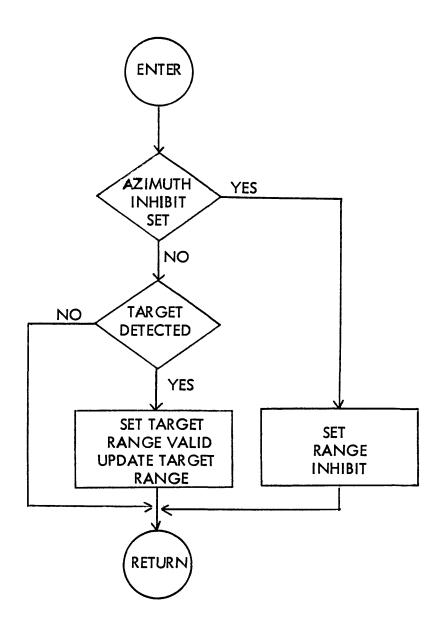

- Fig.E.6. Range Inhibit Alternate Routine

- Fig.E.7. Acceptance Test for Set Binaries

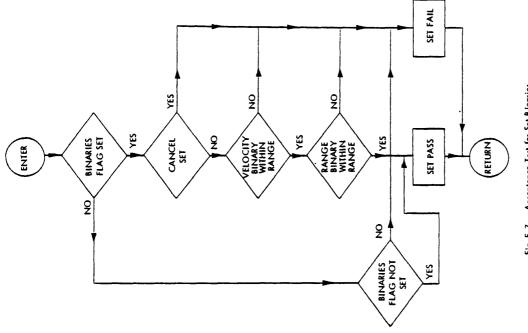

- Fig. E.8. Acceptance Test for Process Binaries

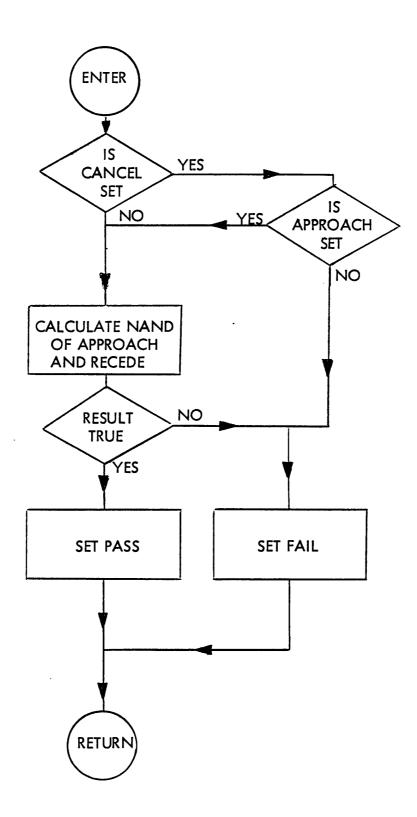

- Fig.E.9. Acceptance Test for Approach/Recede Assessment

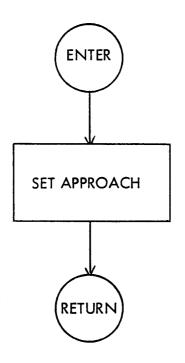

- Fig. E. 10. Approach/Recede Assessment Alternate Routine

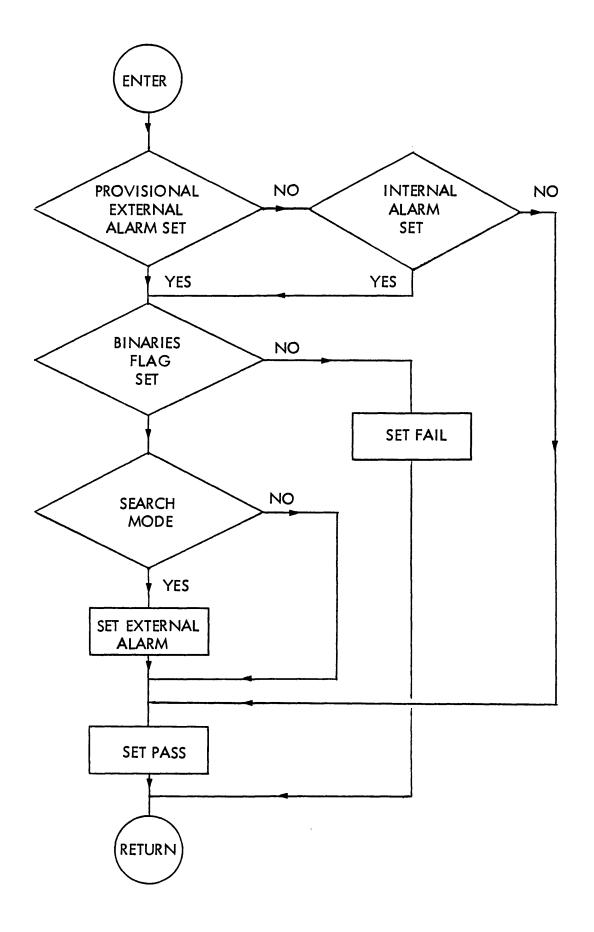

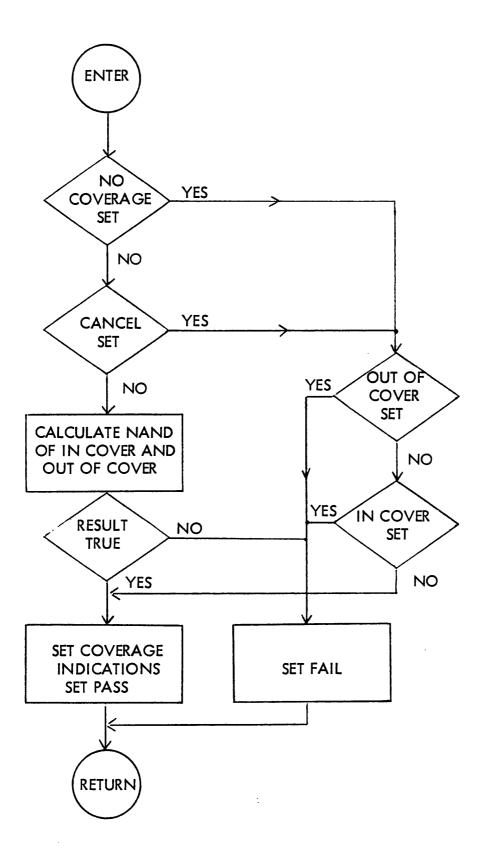

- Fig. E.11. Acceptance Test for Coverage Assessment

- Fig. E. 12. Coverage Assessment Alternate Routine

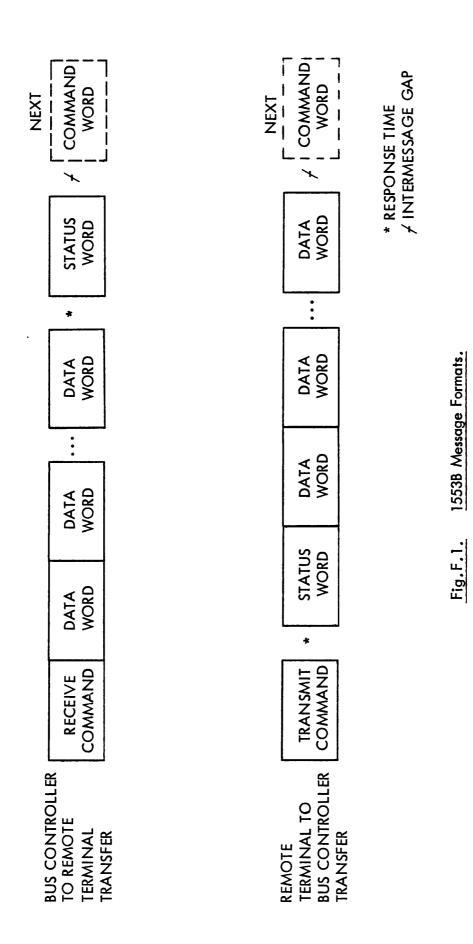

- Fig.F.1. 1553B Message Formats

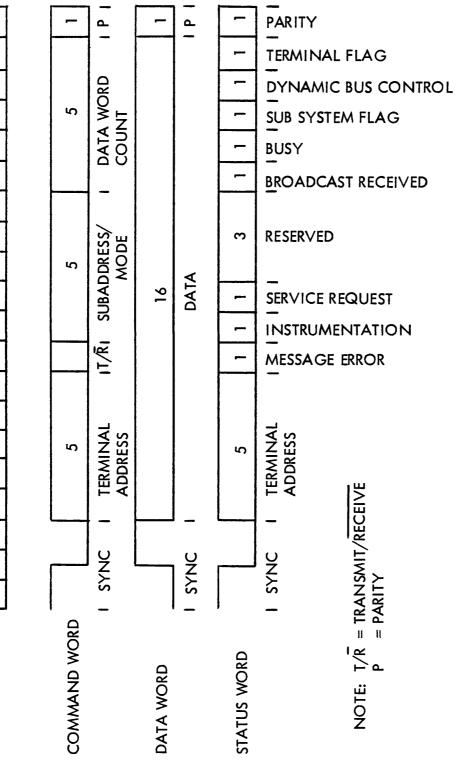

- Fig.F.2. 1553B Word Formats

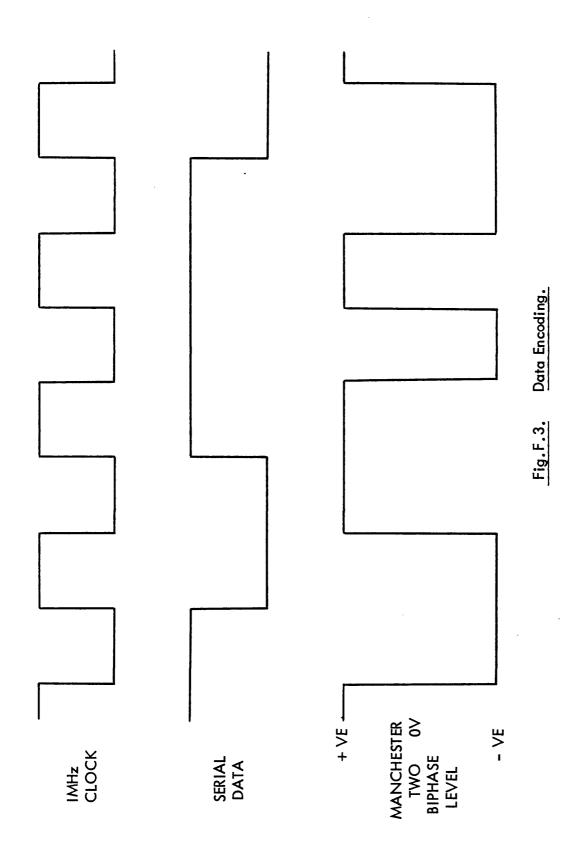

- Fig.F.3. Data Encoding

#### Table 4.1. Angular Rate Information

- Table 6.1. Parts List of Error Correcting Memory Board 1

- Table 6.2. Parts List of Error Correcting Memory Board 2

- Table 6.3. Parts List of Input/Output Board

- Table 6.4. Parts List of Buffer Card

- Table 6.5. Parts List of Fault Injection Logic

- Table 10.1. Baud Rate Selection

- Table 10.2. Parts List of Central Processing Unit

- Table 10.3. 1553B Interface Memory Addresses

- Table 10.4. Parts List of 1553B/Microprocessor Interface Board 1

- Table 10.5. Parts List of 1553B/Microprocessor Interface Board 2

- Table 10.6. Frame Length Adjustment

- Table 10.7. Parts List of 1553B Protocol Fault Injection Board

- Table 11.1. Major Causes of Microprocessor System's Crash

- Table 12.1. Parts List of 4K Memory Board

#### Chapter 1. Introduction.

With the introduction of low cost sophisticated processing, the use of microprocessors has become an important part of the industrial scene, with LSI and VLSI devices often replacing analogue or large digital equipment. In addition to small size and high processing power, a microprocessor based system provides system flexibility with the capability of system reconfiguration. A growing realisation of the new problems that the change to microprocessors has brought about is now evident; the consequence of a system failure in applications such as satellite attitude control is severe, leading to a need for analysis and design techniques to be adopted in order to improve system reliability and availability. Such system failures can originate at either the design or manufacturing stages or in operational use. Design errors typically include systems analysis, hardware design, incomplete specification, mismatch of hardware and software, software design and coding. An analysis of program errors points to the fact that incomplete, inconsistent or ambiguous software requirement specifications are a significant problem.<sup>1</sup>

The reliability of a system may be improved by a combination of different techniques which fall into three main categories, fault avoidance, fault removal and fault tolerance. Chapter 2 reviews the considered techniques which are summarised below.

The avoidance of faults at the analysis and design stage can be carried out by the use of a formal specification language and associated design techniques. Fault tree analysis and failure modes effects analysis (FMEA) can be used to detect critical parts of the system; certain failure modes can then be eliminated at the design stage.

Fault removal techniques involve the construction and integrated testing of hardware and software prototypes. In addition the use of structured software enables a more thorough testing of the system to be carried out. The use of correctness proofs of software is beginning to

emerge but is unlikely to replace prototype testing.

Fault tolerance is a further technique whereby redundant hardware and software is used for the protection and recovery from faults. The need for high reliability can be justified in systems where human life is at stake, where maintenance is not possible or in situations where a large financial loss results from a system crash.

#### 1.1. Research Objectives.

A method of increasing the availability of a given system is by the addition of redundant hardware and software to provide protection against and recovery from faults within and external to the system. It is important that the implementation of redundancy techniques is considered in terms of cost effectiveness, weight and power requirements; for example massive redundancy may not be a cost effective solution if only a marginal increase in reliability and availability is obtained.

The aim of the research study was therefore to investigate the possibility of increasing the availability of a given system by the inclusion of fault tolerant mechanisms for the protection and recovery from predefined faults. The aim can best be divided into constituent parts as follows:

(a) To establish good design practices based upon a practical rather than a mathematical approach.

(b) To establish a simple but obvious structure for system recovery.

(c) To establish design criteria for reliable inter-task communication within a single microprocessor system.

(d) To establish a design philosophy for message passing between microprocessors in a distributed system in order to inhibit the propagation of faults.

The research entailed an initial study of different strategies that could be adopted as a starting pcint. The next stage was to choose a system upon which the strategy could be applied. The aspects which govern

system recovery under faulted conditions become more critical as the response time of the system decreases. With these factors in mind a decision was made to choose a real time system as opposed to a batch processing system since requirements for processing speed, criticality of system outputs and fault recovery time are much more demanding.

#### 1.2. Research Model.

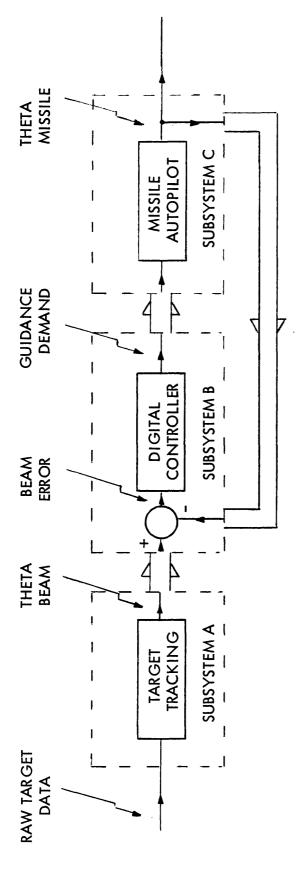

After careful consideration it was decided to base the study on a notional ground defence system, which consisted of a target tracking and missile guidance loop as described in Chapter 4, in order to establish the objectives previously mentioned.

The target tracking process consists of converting raw target data into a plot of target positions. The raw target data is produced from a radar whose aerial rotates at a constant rate, and consists of range and velocity data extracted from the returning radar signals.

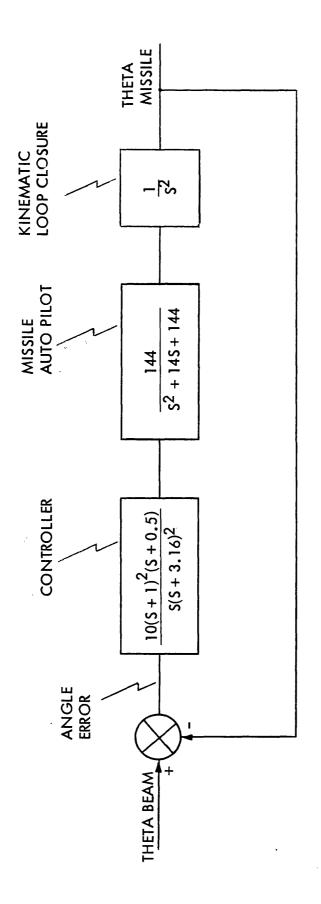

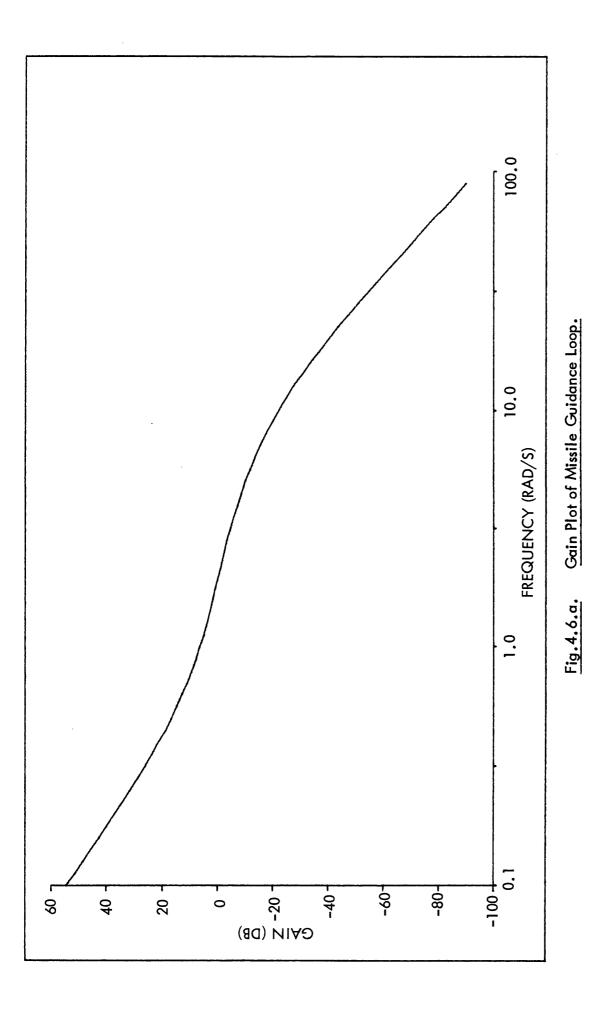

The missile guidance loop consists of a proportional plus integral controller and the missile itself whose autopilot is represented by a second order function.

The tracking process determines the angular position of the target which is known as the target azimuth. This angle becomes the input for the guidance loop, whose objective is to constrain the missile to lie on a line joining the tracking system and the target.

The modelling of these functions in a microprocessor environment is described in Chapter 5.

#### 1.3. Systems Implementation and Investigation.

A subset of the real time system was implemented on a single microprocessor to establish how well it was capable of detecting and recovering from faults within its system. The single microprocessor system carried out the function of the target tracking process with raw target data being provided from a PDP 11. The implementation of the target tracking process in a microprocessor system is described in Chapter 6. This system was then operated under fault conditions to provide a baseline

for the results. Following this a fault tolerant structure was implemented; the results obtained from this are discussed in Chapter 7. The conclusions of the single microprocessor study are stated in Chapter 8.

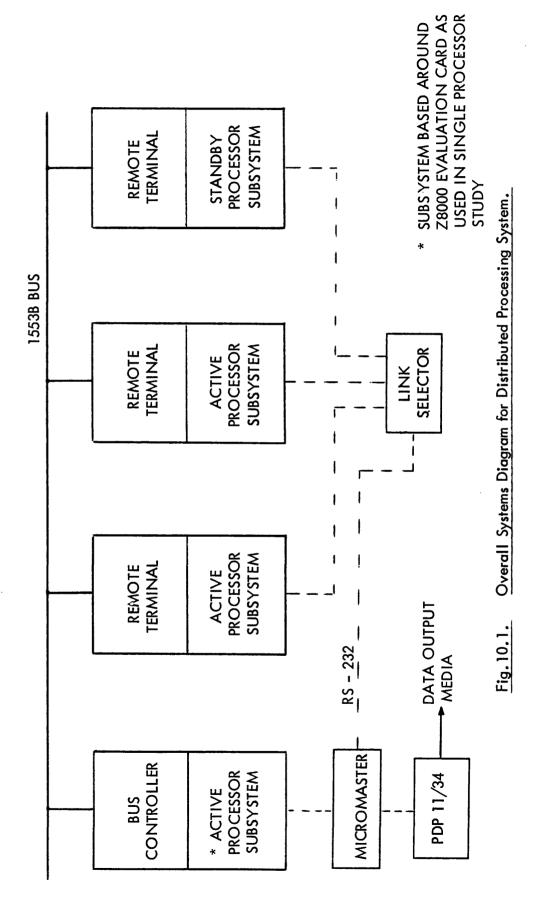

Having gained valuable experience about the workings of the system under fault conditions, a distributed processing system was then investigated, this involved the choice of a communications link and the method for injecting real time faults onto the system; these topics are discussed in Chapter 9. The implementation of the complete real time system in a distributed processing environment is described in Chapter 10. The study also involved looking at a three processor system with protection and recovery methods for increased availability under fault conditions, the results of which are given in Chapter 11.

The use of a standby processor system is shown to give continued systems operation under conditions which would normally cause a catastrophic crash in non-redundant systems.

Chapter 12 looks at the question of when should such a redundant processor subsystem be used and presents results for the recovery of the system from the failure of a complete subsystem. The conclusions of the distributed processing study can be found in Chapter 13. This is followed by a review of guidelines for reliable systems design and the initial design of a single microprocessor system within Chapter 14. A final chapter reviews the achievements made from the research study.

#### Chapter 2. Techniques for Reliable Systems Design.

The reliability of microprocessor based systems can be improved by a combination of several strategies: fault avoidance, fault removal and fault tolerance. The amount of work carried out in this area is considerable and this chapter summarises a number of techniques which are directed at enhancing the reliability of a system. In addition the problem of reliability prediction for microprocessor based systems is considered.

#### 2.1. Failures, Errors and Faults.

To avoid ambiguity the terms failures, faults and errors are defined<sup>2</sup> and are used throughout this thesis.

#### Failure.

A failure of a system occurs when the system does not perform its service in the manner specified. This may be either because it is unable to perform the service or because the system outputs are not in accordance with the specifications. Thus a failure is an event.

#### Error.

An error is a part of an erroneous state which constitutes a . difference from a valid state.

#### Faults.

A fault is the mechanical or algorithmic cause of an error. This encompasses areas of design inadequacies such as incorrect choice of component, system specification misinterpretation and incorrect interrelationship between system components (software and hardware).

## 2.2. Fault Avoidance.

The initial stage of a development process is the functional specification stage; this generally involves determining the requirements for both normal and abnormal operation of the system. Design faults that can arise during this phase include inconsistent requirements and misinterpretation or omission of requirements. Design inadequacies made during the requirements definition phase which are found at a later stage generally involve a redesign of software and/or system and repeat of the testing

process. A reduction in the number of errors resulting could possibly be obtained by the introduction of formal system specification languages which serve as a communication aid between systems design, implementation and user. Research in this area is at an early stage; an example of a formal specification language can be found in Ref.3.

There exists a number of semigraphical methods for systems analysis. The most widely accepted of these methods is probably HIPO<sup>4</sup> (Hierarchy, Input, Process and Output) whereby functional specification is created by naming the basic functions which have to be performed and decomposing them into hierarchically ordered sub-functions. A further technique is the Structured Analysis and Design Technique<sup>5</sup>. This is basically a diagramming language which is used to describe the relationship between objects and activities. The amount of detail shown in a single diagram is controlled and thus leads to diagrams which can be quickly understood by management and users.

A technique gaining more acceptance is MASCOT<sup>6</sup> which provides a formalism for expressing the software structure of a real time system which can be independent of computer configuration and programming. It also provides a disciplined approach to design, implementation and testing of the system along with a strategy for documentation.

One of the most effective ways of avoiding design faults is to keep the complexity of systems design under control. Many software design methodologies based on this premise have been developed. They aim to structure software in a simple hierarchy of reasonably independent software modules. Work in this area includes reliable software through composite design<sup>7</sup> and the decomposition of systems into modules<sup>8</sup>.

The use of small modules enables a complete understanding of their operation, in addition the consequence of modifications can be more easily seen than with one large program. Further, the use of structured programming leads to more reliable software and significantly improves

the readability and maintainability of a module since structured code is read from top to bottom.

Consider now the hardware design; this is a task of selecting the most appropriate microprocessor and associated circuitry. A hardware/ software trade-off has to be made, this is a matter of deciding which tasks are to be performed by software and which tasks by specialised hardware. Performing a task with specialised hardware incurs an extra cost in components and assembly for each product, whilst a software solution incurs a high development cost but has the advantage of non-recurring costs and ease of reconfiguration. A software solution to a problem will generally slow down the task execution unlike specialised hardware which can be designed to perform the task independently, for example a floating point arithmetic unit. Thus when difficulties arise in achieving the response time, then software should be replaced by hardware.

Systems design may be realised by a multi-processing solution since the processing power of a single microcomputer may be insufficient to meet the system requirements. In this case the software would be partitioned into independent tasks, each being located in the relevant subsystem. The communications protocol used between subsystems would then be determined by consideration of distance of transfer, data integrity and response requirements.

In applications where highly reliable systems are required, an analysis of failure modes is usually carried out following the design. An example of a technique for failure analysis is Fault Tree Analysis,<sup>9</sup> which starts by specifying a total system failure or safety critical failure. The analysis then proceeds downwards from this failure to identify part failure modes which could lead to such an overall failure. The final result is a highly detailed logic diagram depicting basic faults and events that can lead to the critical failure at the top of the diagram. Each basic fault is given a probability from an analytical or an empirical approach. The probability of the critical failure occurring is then calculated by

appropriate means from probabilities of the basic part failures. This technique is often applied in safety analysis, particularly in situations where human life is at risk or where cost of failure is prohibitive, or where certain system failure modes must be eliminated at the design stage.

The choice of programming language is another consideration of reducting the number of design faults and several high level languages have been introduced to meet the demanding requirements of a real time system. The choice of a language is made by considering language facilities such as interrupt handling, I/O facilities, program structure inherent in language implementation, data structure appropriate to application, portability and efficiency of execution of object code. Examples of this are languages such as Coral and RTL/2, which have been specifically designed for real time applications, although Coral suffers from lack of I/O facilities. Pascal has a good structure and is portable, whilst Concurrent Pascal has specifically been designed for multi tasking environments. Ada is still very new and may be too complicated to be reliable. In contrast PLM, PLZ and MPL have been specifically designed by Intel, Zilog and Motorola for their own chips and hence there is a lack of portability.

#### 2.3. Fault Removal.

Despite efforts to avoid faults in the analysis and design stages, system failures will still occur due to residual design faults. Fault removal techniques can be applied during the design phase in order to remove as many of these faults as possible consistent with cost, development time scale and reliability requirements.

In the case of hardware many well proven techniques exist; these include design reviews, the building and testing of prototypes, inspection and testing of printed circuit boards and the use of component Burn-In to eliminate early failures.

The correctness of a systems design is important and must be checked before software coding is started. The use of structured walk throughs and design reviews are desirable where the correctness of each design step can

be checked by the designer and project engineers.

A structured software system has the advantage that testing can be modular and more thorough thus removing a greater percentage of design faults. In top down testing, the top level is tested first, a lower segment is added and the combination tested. This is repeated down to the lowest level. Dummy segments temporarily replace the segment subordinate to the segment These dummy segments can vary in complexity and may return under test. constants or may be a primitive version of the segment being simulated. To enhance structured testing the length of a segment should be limited to a manageable level, say fifty statements to enhance readability and comprehension whilst minimising page turning. Usually each segment will correspond to one function and can be implemented as a procedure with a descriptive name corresponding to the function. Thus the limited size of segment in addition to single entry/exit, top to bottom flow of control makes programs easier to extend and maintain. Reliability is further enhanced because test plans for the segment are easier to specify and execute.

Techniques for formal proving of program correctness<sup>10, 11</sup> are unlikely to replace program testing, now or in the near future since there are many problems still to be overcome. It seems reasonable to doubt the ability of correctness proofs as it is difficult to write long programs without errors and program proving has so far been more difficult than the construction of programs. The solution may lie in the use of computer aids to check the proof or generate it. The problem that then arises is how do you check the proof checker. In addition, large program proofs probably have to be constructed of small modules which could lead to an interfacing problem between modules. The correctness proof must also include areas such as processor and system architecture, memory size and timing considerations.

#### 2.4. Fault Tolerance.

Microprocessor based systems of the future are unlikely to be designed and built so as to be free from faults during their operational life.

Residual software design faults and random hardware faults are likely to occur; these must be detected, corrected and the system restored to a working state which leads to a need for built in redundancy for highly reliable systems operation. However, such redundancy must be applied carefully and in the correct structure, otherwise increased system hardware and software could lead to a reduction in reliability.

There are certain applications areas where use of fault tolerance is vital. First, there are systems where maintenance is not possible such as in space vehicles whilst reconfiguration around a malfunction may be possible. Secondly, fault tolerance is important in systems where human life is at stake, for example control of nuclear plants, ground defence systems and transport systems. Finally, there are applications in which computer downtime leads to financial losses such as automated process control and communication systems.

Having discussed the need for fault tolerance, consider now the types of faults that may occur during the operational life of the system. 2.4.1. Characterisation of Faults.

Faults occurring in a system may be attributed to a number of factors, e.g. temporary, intermittent or permanent failure of hardware components, hardware or software design faults or manufacturing faults. A fault causes an error if an incorrect state is entered; the fault does not always cause an error to occur immediately, for example a memory cell having a stuck-at 'logical 1' fault will not cause an error until a 'logical 0' is incorrectly read as 'logical 1'.

Temporary or transient faults are those of limited duration and can be caused by malfunctions of components or by the introduction of interference. If the duration of a transient fault is longer than a predetermined time then it will be interpreted as a permanent fault; for example a communications link may allow up to three re-transmissions of data before a permanent fault is reported.

Consider next the permanent failures of components; if the fault is

not masked then it must be detected and recovery can then take place. This may consist of a software algorithm for hardware reconfiguration along with program and data rollback.

Local faults can be described as those that only affect a single logic variable whereas distributed faults are those which affect two or more variables. The advent of LSI and VLSI chips means that distributed faults are much more likely to occur than in the past, as a single gate is unlikely to fail without affecting other gates in a complex closely packed integrated circuit. Distributed faults can also be caused by failure of a single critical element, for example processor clock or power supply.

2.4.2. Redundancy Techniques.

The detection of a fault during operational use is the starting point of all fault tolerant mechanisms except those which use fault masking. In many systems it is important that these faults are detected quickly and are not allowed to propagate, otherwise system failure may occur.

In order to detect malfunctions the systems behaviour must be monitored in order to show deviations from the norm. This monitoring is generally performed by a combination of hardware and software techniques for detecting system malfunctions include the following:

(a) The pattern of states through which the system passes can be compared with expected or valid state transition patterns in order to reveal the presence of hardware or software faults.

(b) The performance of the system can be monitored to indicate fault free operation; this monitoring includes response time, system throughput and process calculation time.

(c) A malfunctioning system will often lead to the process trying to execute an invalid instruction or one that has an invalid address.

(d) The use of traps in processor software can be used to indicate, for example, division by zero or overflow conditions which may be caused by the propagation of a fault to the relevant instruction.

Hardware redundancy can be divided into two types, i.e. masking

and standby redundancy as described below. Redundancy in the form of software is considered in section 2.4.4.

Fault masking is a technique widely used, whereby the fault is masked by the presence of additional hardware, the output remaining error free as long as the protection is adequate. One form of fault masking is the use of n - modular redundancy where majority voting takes place on the outputs of an odd number of identical units. The use of error correcting codes is another form of fault masking, the most common code being the Hamming code<sup>12</sup>.

Standby redundancy can either be classed as cold or hot standby; the terms cold and hot relate to whether the redundant units are powered up. In cold standby redundancy, only one unit is powered up and operational, whilst the remaining units are not powered up. A schematic of cold standby redundancy is shown in Fig.2.1. A failure sensing and switchover device monitors the operation of the working unit and switches to one of the standby units when a failure of the working unit is detected.

In a hot standby redundancy scheme, all units are powered up, and are arranged typically as shown in Fig.2.2. This figure shows three units with the output of one of the units, chosen arbitrarily, providing the system output. If the comparator detects a disagreement, then the faulty unit must be identified and the system output taken from one of the other units. The time taken to switch from a faulty unit to a fault-free unit must be considered in the design phase.

2.4.3. Fault Recovery.

The detection of a fault provides the basis for the next step which is the correction and recovery of the system. Fault masking is a special case of system recovery which does not use separate fault detection.

In systems where high availability is necessary, the recovery from a fault must be automatic and not require human intervention.

Methods of recovery from a fault include:

(a) Re-try the operation that failed, if successful then continue.

This is particularly valid in the presence of temporary faults.

(b) Rollback of system to a position where system operation was known to be correct and repeat execution.

(c) Reconstruct or correct data structures from redundant data or status information.

(d) Re-initialise the system, with or without status information.

(e) Restore the system state to nominal or default values with the use of a status flag to indicate that output may contain inaccuracies.

(f) The use of standby spares either in a cold or a powered up condition.

System recovery can take one of three useful forms: full recovery, graceful degradation or safe shutdown. The techniques used in a particular system depend upon the extent of the damage, the possible cause of malfunction and the operating state of the system at the time of the fault.

2.4.4. Fault Tolerant Software.

The use of redundant elements is an established practice in fault tolerance of hardware. However, the use of redundant software for reliable operation requires special attention due to the nature of software. In contrast to hardware in which physical faults dominate, software defects are time invariant. Executing duplicate copies of a program in parallel does not improve the operation with respect to software defects, because software design faults will be inherent in both copies. The following paragraphs describe two methods of achieving fault tolerance in software: N -Version programming <sup>13</sup> and the Recovery Block <sup>14</sup>.

2.4.4.1. N-Version Programming.

This approach is analogous to the well known hardware method of replication and voting on the outputs of the hardware modules. A number  $(N \ge 2)$  of independently coded programs for a given process are run simultaneously on loosely coupled processors. The independent results are then compared, and in the case of a disagreement, a preferred

result is generated by majority voting (for N > 2) or by a predetermined strategy. The success of this technique depends upon the level of independence that can be achieved in the N Versions of the program. Independence is best obtained by the use of different algorithms and programming languages in each version. Different data structures could also be used to increase the independence. The critical areas for this technique are the voting algorithm and the housekeeping prior to and after voting.

A constraint on N-Version programming is the requirement for N computers that are hardware independent, yet are able to communicate efficiently. The problem of synchronising arises here, a voter may have to wait for a result or indeed a result may never arrive due to a fault. 2.4.4.2. The Recovery Block.

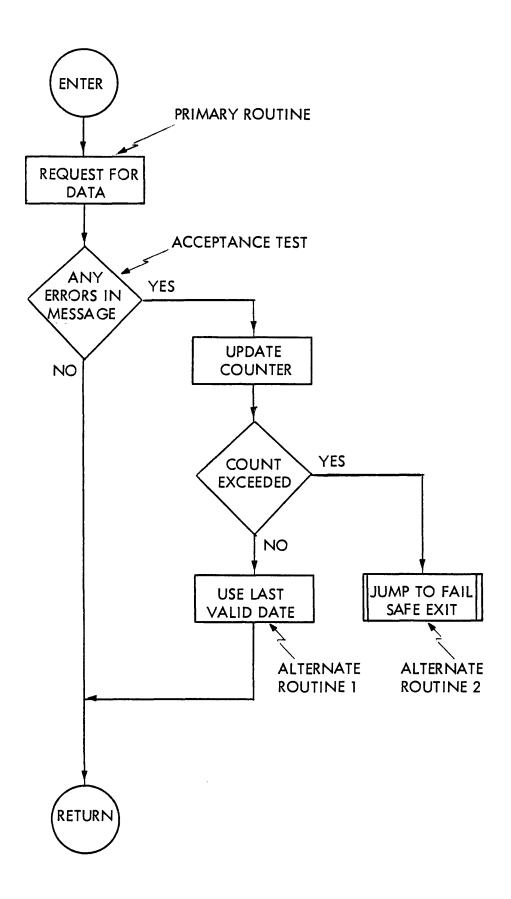

This technique, in contrast to N-Version programming, can be applied to any configuration of processors, including a single processor. The structure in its simplest form is shown in Fig.2.3., where a process is described by a primary routine P. The output of the primary routine must pass an acceptance test T before passing control to the next process, if the acceptance test fails or if a set time has expired whilst executing the primary routine then a transfer to the alternate routine, Q, is initiated. If the acceptance test fails after execution of the routine Q or if a time out occurs during Q then an error return results. This technique does not preclude the use of several alternate routines if necessary for critical parts of the system.

It follows that a critical feature of the Recovery Block is the acceptance test. The alternate routines are worthless if failure of the primary routine is not detected by the acceptance test, thus the acceptance test must be thorough without being too time consuming.

A number of different types of acceptance tests are described in the following paragraphs:

(a) In many cases the definitions of the process imposes conditions

which must be met at the completion of the process. These conditions can be used to construct the acceptance test. For example, an acceptance test for a sorting process may be to check the order, produced by the primary or alternate routines, is correct.

(b) Accounting checks can be used in acceptance tests for processes that are transaction oriented. The acceptance test could independently generate a checksum and compare it with the one produced by a primary or alternate routine.

(c) Another class of tests are called reasonableness tests. These tests are based on precomputed ranges of variables, expected sequences of program states or other occurrences that might be expected to occur in the system. Reasonableness tests are based on physical constraints whereas tests for requirements are based on mathematical or logical relationships. Tests used for acceptance can typically examine whether a variable is in range, whether the increment or decrement of a variable is in range or correlation between different variables is in range. For example, a process might calculate the acceleration of a missile. The acceptance test might simply test whether this acceleration is within predetermined limits, say <sup>+</sup> 10g in order to maintain structural integrity.

(d) In an important process such as a firing sequence, the use of flags is a good way to ensure the correct procedure has been followed.In such a case, the acceptance test could check to see if all the appropriate flags have been set before firing is allowed to occur.

#### 2.5. Reliability Modelling.

The reliability of microprocessor based systems has conveniently been divided into two areas, i.e. that of hardware and software, due to the two disciplines involved in the design. Hardware reliability modelling has been an established practise for many years whilst software reliability modelling has only made an appearance in the last ten years.

Consider first the modelling of software reliability.

#### 2.5.1. Software Reliability Modelling.

Software has the unique property that it suffers no natural degradation, except in the special case of software stored on magnetic media. The purpose of an error prediction model is largely as a management aid to decide when enough testing has taken place and in assessing the confidence levels that can be placed in the software.

Many models that have been put forward use a bug counting approach. This approach has been used by Jelinski and Moranda<sup>15</sup> and by Schooman<sup>16</sup>. Jelinski and Moranda developed a software reliability model which assumes exponential distribution of faults and a software failure rate, i.e. the rate at which the software system fails to meet informal system requirements, which decreases in discrete steps as a function of time. Schooman's model is based on the same underlying assumptions with the difference that failure rate is also dependent upon the debugging effort. These models imply that reliability improvement can only take place at a system failure, since it is only here that a design error can be removed.

Musa<sup>17</sup> presents another model, using program execution time as the time variable rather than calender or debugging time as in the previously mentioned models. In addition he introduces a factor for noncorrections of the cause of the failure.

Schick and Wolverton<sup>18</sup> address the problem to a reliability model by determining an analytic stochastic model for predicting the number of remaining errors in the software, the mean time to next failure, the time to discover the remaining errors and the standard deviation associated with the error prediction.

Littlewood and Verrall<sup>19</sup> use a contrasting approach of no news being good news, where failure rate decreases between failures and periods of failure free working cause the reliability to improve.

Even if assumptions about failure rates being proportional to the number of errors remaining are accepted, then estimation of model

parameters still poses great difficulty. One objective should be to measure the quality of the behaviour of the software, its operational reliability (integrity) rather than the number of design errors left in the program.

It is considered by the author that instead of establishing a figure for software reliability, in terms of number of remaining errors, that a range of software metrics be used for assessment of software integrity. This assessment must depend upon the compexity of the software modules, the criticality of each module to system performance, the tolerance of each module to errors caused by environmental factors and the maintainability and testability of the software.

Consider now the modelling of hardware reliability.

#### 2.5.2. Hardware Reliability Modelling

The effects of environmental stressing are known as random failures. These failures occur in all types of electronic equipment and are generally treated as exhibiting a constant failure rate. This constant failure rate in non-redundant systems is supported by the use of life test and field data, after accounting for infant mortalities and the effects of maintenance.

In microprocessor based systems, malfunctions are dependant upon the component configuration, for example a failure may result from a transistor sinking excess current. Thus a reliability model must take account of prevalent failure modes.

The laws of probability govern the outcome of a mission of a redundant system and simple probability formulae clearly show the advantage of redundancy. Consider a triple modular redundant (TMR) system where three identical computers are used to give an output based on a majority vote. This system will only give an improvement in the mean time to error if maintenance is provided before the 'mean time before failure' of the individual modules. TMR systems are vulnerable to voting and single point timing failures which reduce the reliability of such systems.

Error detection and correction can be incorporated into integrated

circuits to extend their 'mean time between failure' provided a comprehensive testing capability is also incorporated. An example of the design for testability of error correction circuitry for memory arrays is given in Ref.20. However, the effectiveness of any on chip redundancy will always be limited by the high correlation between malfunctions and the common thermal and structural failures.

In a complex system, the relationship between a random failure and its manifestation as an error is apt to be obscured by ill defined propagation paths. This is likely to cause problems for analytic models based on simple cause – effect relationships.

The modelling of some of the more complex redundant systems is often carried out by the use of Markov process models. These models can be made arbitrarily accurate by incorporating an arbitrary number of states. Caution must be applied in using these models on processes other than those with constant failure and recovery rates. A constant recovery rate is hard to imagine for a real time system as the time taken to recover depends upon configuration of the system at time of fault, the process being executed and the criticality of the fault.

Availability is measured as the percentage of time that a system is in an operational state. In some applications, the penalty for a single long unoperational period is much greater than that for many short periods, whereas the availability figure may be equal for the two instances. In this case, another parameter is required to describe the performance, i.e. time. This concept of penalising a slow recovery is discussed in Chapter 11.2.

Coverage of a system is the probability of the system recovering from a malfunction, it is a complex architectural attribute and is influenced by latency of fault, ambiguity in the perception of the fault and by the architectural anticipation of such a fault. An estimation of coverage made before experimental verification is likely to be largely inaccurate. Retrospective coverage can be obtained but cannot accurately reflect any system other than that for which it was gathered.

## Chapter 3. Analysis of a single Microprocessor System.

Having discussed techniques for reliable systems design in Chapter 2 an approach had to be chosen that could be used for single or distributed processing systems. A requirement of the research was that massive redundancy was to be avoided, if possible. The Recovery Block meets this requirement and in the view of the author was a good basis for further investigation, initially on a single microprocessor and then finally in a distributed processing environment.

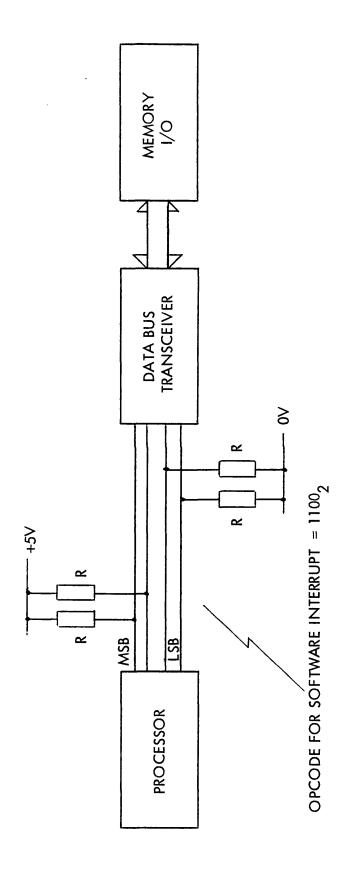

In order to determine recovery mechanisms for a processor system under fault conditions, it became necessary to identify the effect of faults on system operation. An example of this identification is given here on a typical processor system consisting of CPU, RAM ROM, A/D and D/A convertors along with the necessary interconnecting and buffering logic, as shown schematically in Fig.3.1. The data bus transceivers, address and control buffers as shown in Fig.3.1. are permanently enabled and the direction of the data bus transceivers defaults to drive away from the CPU except when reading memory.

The approach of identifying failure modes and their effects is a useful method of fault avoidance. As hazards are identified, software and hardware defences can be developed using fault tolerant or self checking techniques to reduce the probability of their occurrence once the system has been implemented.

In the following section, typical causes and effect of faults are given for the described system; in addition possible solutions are given for the purpose of system recovery.

#### 3.1. Cause and effect of Faults in a Typical Microprocessor System.

The following descriptions of causes and effects should be read with reference to Fig. 3.1. The list is not exhaustive, but sufficient to identify typical fault effects in the view of the author.

|    | Cause     | Effect                | Possible Solutions                                |

|----|-----------|-----------------------|---------------------------------------------------|

| 1. | No clock. | The system will stop. | The use of a fault tolerant clock <sup>21</sup> . |

#### Cause

Effect

2. Address bit failure.

Incorrect addressing occurs resulting in CPU fetching data and/or instructions from wrong addresses. Possible Solution

A time out can be used to indicate that the program sequence was not completed in time.

By monitoring of bus with other logic then it may be possible to re-arrange addressing of system, i.e. move program and data to another part of memory.

3. Reset failure. System fails to reset when required.

If reset fails then attempt to carry on processing.

4. Read/write line.

If the line is stuck at logical '1', that is always a read cycle, then CPU is always reading from memory and I/O. When attempting to write then bus conflict will occur with CPU and memory buffers driving against each other. If the line is stuck at logical '0' then the system always sees a write cycle. When a CPU read cycle occurs then memory is loaded with garbage. The effect of an undriven bus will inevitably result in incorrect program execution.

A time out will indicate that a fault has occurred. Monitoring logic could give information on the nature of the fault.

|    | Cause         | Effect                       | Possible Solutions           |  |

|----|---------------|------------------------------|------------------------------|--|

| 5. | Data bus      | If stuck at faults occur     | There is a possible          |  |

|    | transceivers. | on the data bus, then bad    | detection of an undriven     |  |

|    |               | data is read from or written | bus as the CPU will          |  |

|    |               | to memory. If a fault in     | probably read all 1's;       |  |

|    |               | the direction logic occurs   | alternatively the bus        |  |

|    |               | with direction always        | could be made to             |  |

|    |               | towards the CPU then bus     | default to a particular      |  |

|    |               | conflict will occur; when    | instruction. A conflict      |  |

|    |               | writing to memory no data    | on the data bus will         |  |

|    |               | will be stored. If a         | cause time-out or a trap     |  |

|    |               | direction fault occurs with  | due to attempted             |  |

|    |               | direction always to memory,  | execution of invalid         |  |

|    |               | then when reading from       | instruction.                 |  |

|    |               | memory the CPU will read     |                              |  |

|    |               | a bus which is not driven.   |                              |  |

|    |               |                              |                              |  |

| 6. | Memory        | Incorrect instruction/data   | The fault can be masked      |  |

|    | failure.      | is read from memory.         | by automatic error detecting |  |

|    |               |                              | correcting codes, although   |  |

7. Address As address bit failure. bus buffer.

See solution 2.

CPU intervention or

special logic may be needed

to correct multiple faults.

No memory accesses can 8. Clock failure. be made.

.

The duplication of address and control buffers is possible but not cost effective.

|     | Cause        | Effect                             | Possible Solution      |  |

|-----|--------------|------------------------------------|------------------------|--|

| 9.  | Valid Memory | lf stuck at logical '1' fault      | The effect is probably |  |

|     | Address      | occurs then memory is              | caught by a time out.  |  |

|     | Signal.      | accessed at wrong point in         |                        |  |

|     |              | time or spurious addressing        |                        |  |

|     |              | occurs. If stuck at logical        |                        |  |

|     |              | '0' fault occurs then memory       |                        |  |

|     |              | is never accessed.                 |                        |  |

| 10. | CPU.         | The effects of such a fault        | Repeated time-outs     |  |

|     |              | are wide ranging and include       | may possibly occur but |  |

|     |              | stuck at faults on buses,          | CPU may not respond    |  |

|     |              | invalid control signals and        | to them.               |  |

|     |              | incorrect operations.              |                        |  |

| 11. | Address      | If no outputs from the             | There is a possibility |  |

|     | Decode       | address decode logic are           | of using self checking |  |

|     | Logic.       | enabled, then the CPU reads        | logic here.            |  |

|     |              | an undriven bus.                   |                        |  |

|     |              | If one output from the address     |                        |  |

|     |              | decode logic is enabled, but       |                        |  |

|     |              | it is the incorrect output then    |                        |  |

|     |              | incorrect addressing occurs.       |                        |  |

|     |              | If two outputs are enabled then    |                        |  |

|     |              | memory is corrupted on a write     |                        |  |

|     |              | cycle, and a bus conflict          |                        |  |

|     |              | occurs on a read cycle.            |                        |  |

|     |              | If the address decode logic is not |                        |  |

|     |              | enabled then no memory accesses    |                        |  |

|     |              | will occur. If however the logic   |                        |  |

|     |              | is always enabled then accide      | ntal                   |  |

|     |              | addressing will probably occur     | •                      |  |

|     |              |                                    |                        |  |

| (   | Cause                                                   | Effect                                                                                                                                           | Possible Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

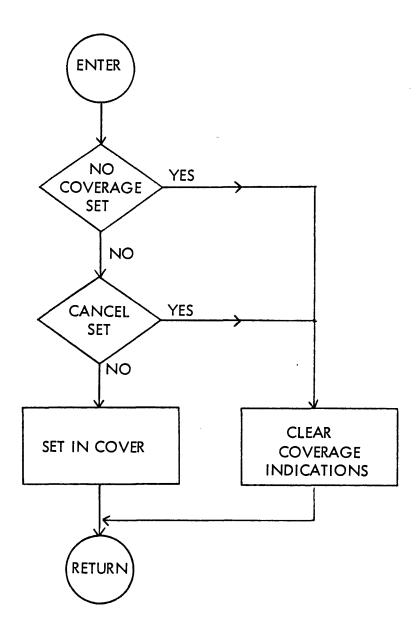

| 12. | Buffered<br>Read/write.                                 | As for effect 4.                                                                                                                                 | See solutions 4 and<br>8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |