Foundations and Trends<sup>®</sup> in Electronic Design Automation Vol. 11, No. 4 (2017) 362–461 © 2017 P. Stanley-Marbell and M. Rinard DOI: 10.1561/1000000049

### **Error-Efficient Computing Systems**

Phillip Stanley-Marbell University of Cambridge phillip.stanley-marbell@eng.cam.ac.uk

Martin Rinard Massachusetts Institute of Technology rinard@csail.mit.edu

### **Contents**

| 1 | Introduction                                                                                                                    |                                                                               |  |  |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

|   | 1.1                                                                                                                             | The Cost of Correctness                                                       |  |  |  |  |

|   | 1.2                                                                                                                             | Historical Context                                                            |  |  |  |  |

|   | <ul><li>1.3 Why Precision Matters in Many Numerical Computation</li><li>1.4 Why Some Applications Can Tolerate Errors</li></ul> |                                                                               |  |  |  |  |

|   |                                                                                                                                 |                                                                               |  |  |  |  |

|   | 1.5                                                                                                                             | Examples of Improving Efficiency by Permitting Errors 367                     |  |  |  |  |

|   | 1.6                                                                                                                             | Fundamental Physical Limits, Energy, and Noise 369                            |  |  |  |  |

|   | 1.7                                                                                                                             | Hardware and Software Systems That Exploit Errors 371                         |  |  |  |  |

|   | 1.8                                                                                                                             | Outline of the Remainder of This Review                                       |  |  |  |  |

| 2 | Types of Errors and Randomization                                                                                               |                                                                               |  |  |  |  |

|   | 2.1                                                                                                                             | Precision, Repeatability, Accuracy, and Reliability 381                       |  |  |  |  |

|   | 2.2                                                                                                                             | Accuracy of Models versus Precision of Computations $\ \ . \ \ . \ \ . \ 382$ |  |  |  |  |

|   | 2.3                                                                                                                             | Randomized Algorithms                                                         |  |  |  |  |

|   | 2.4                                                                                                                             | Stochastic Digital and Analog Computing                                       |  |  |  |  |

|   | 2.5                                                                                                                             | Probabilistic Programming                                                     |  |  |  |  |

| 3 | Computation, Energy, and Noise                                                                                                  |                                                                               |  |  |  |  |

|   | 3.1                                                                                                                             | Devices Use Energy to Guard against Faults 390                                |  |  |  |  |

|   | 3.2                                                                                                                             | Types and Sources of Noise and Faults                                         |  |  |  |  |

|   | 3.3                                                                                                                             | Traditional Fault-Tolerant Systems                                            |  |  |  |  |

| 4          | Tolerating Errors in Outputs 40 |                                                         |     |  |  |  |

|------------|---------------------------------|---------------------------------------------------------|-----|--|--|--|

|            | 4.1                             | Human Perception of Color                               | 403 |  |  |  |

|            | 4.2                             | Quantifying Errors in Images                            | 404 |  |  |  |

|            | 4.3                             | Display Technology                                      | 405 |  |  |  |

|            | 4.4                             | Exploiting Perception for Display Energy Efficiency     | 406 |  |  |  |

|            | 4.5                             | Exploiting Perceptual Flexibility in End-To-End Systems | 409 |  |  |  |

| 5          | 5 Tolerating Errors in Inputs   |                                                         |     |  |  |  |

|            | 5.1                             | Lax                                                     | 412 |  |  |  |

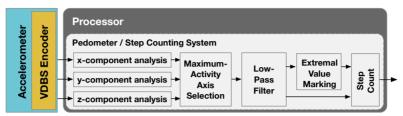

|            | 5.2                             | VDBS Encoding                                           | 422 |  |  |  |

|            | 5.3                             | End-to-end Evaluation                                   | 438 |  |  |  |

| 6          | Cor                             | nclusion                                                | 443 |  |  |  |

| References |                                 |                                                         |     |  |  |  |

#### **Abstract**

This survey explores the theory and practice of techniques to make computing systems faster or more energy-efficient by allowing them to make controlled errors. In the same way that systems which only use as much energy as necessary are referred to as being *energy-efficient*, you can think of the class of systems addressed by this survey as being *error-efficient*: They only prevent as many errors as they need to. The definition of what constitutes an error varies across the parts of a system. And the errors which are acceptable depend on the application at hand.

In computing systems, making errors, when behaving correctly would be too expensive, can conserve resources. The resources conserved may be time: By making some errors, systems may be faster. The resource may also be energy: A system may use less power from its batteries or from the electrical grid by only avoiding certain errors while tolerating benign errors that are associated with reduced power consumption. The resource in question may be an even more abstract quantity such as consistency of ordering of the outputs of a system.

This survey is for anyone interested in an end-to-end view of one set of techniques that address the theory and practice of making computing systems more efficient by trading errors for improved efficiency.

All software eventually works; all hardware eventually fails.

-Clod Berrera.

This review explores the theory and practice of techniques to make computing systems faster or more energy-efficient by allowing them to make controlled errors. In the same way that systems which only use as much energy as necessary are referred to as being *energy-efficient*, you can think of the class of systems addressed by this review as being *error-efficient*: they only prevent as many errors as they need to.

There are numerous related fields relevant to understanding, designing, and evaluating systems which trade controlled errors for improved performance or energy efficiency. These related fields range from sub-areas of computer science, electrical engineering, and materials science, to applied mathematics and psychophysics (the study of perception). There are numerous techniques proposed by researchers in these diverse areas, with a vibrant and growing body of research results. This review focuses on two elements:

• **Fundamental concepts** that underpin any exploration of errors, time-efficiency (i.e., performance), and energy efficiency. These concepts

have been developed over many decades in areas ranging from numerical analysis to the physics of semiconductor device behavior.

Practical hardware and software implementations of error-efficient techniques to reduce energy usage in either practical engineering applications or experimental research platforms.

Throughout the review, we will focus specifically on the interplay between errors and the effects of errors as processed by human perception.

#### 1.1 The Cost of Correctness

In computing systems, making errors when behaving correctly would be too expensive can conserve resources. The resources conserved in doing so may be *time*: by making some errors, they may be faster. The resource may also be *energy*: a system may use less power from its batteries or from the electrical grid by only avoiding certain errors while tolerating benign errors that are associated with reduced power consumption. The resource in question may be an even more abstract quantity such as consistency of ordering of the outputs of the system in question.

Which errors are acceptable depends on the application. The degree to which resources such as time or energy can be conserved likewise depends on the design of the computing system. And there are many different kinds of deviations in behavior which can be classified as "errors". This Chapter provides an overview of the landscape of the applications, computing systems, and techniques that can be used to trade improved efficiency in exchange for occasional errors.

#### 1.2 Historical Context

All hardware eventually fails. Reducing the likelihood of failure and the effects of failure comes at the cost of time, energy, or space. Making computing hardware more reliable was particularly important when the dominant applications of computing systems were in controlling weaponry and in financial applications. Today however, a large fraction of computing systems generate output solely for visual consumption.

Early computing systems based on vacuum tubes provided improvements in switching speed over their predecessors which were based on mechanical relays. They however also failed frequently: Failure rates in early vacuum-tube-based systems were as high as once every eight hours [von Neumann, 1956]. Because the possibility of intermittent and permanent failures has always been present in computing systems, the design of the basic elements of computation has evolved over time to inherently attempt to counteract the effects of failures.

One of the most fundamental techniques for dealing with the most basic source of failures (environmental noise) is to use digital logic, instead of performing computation directly in the analog signal domain. There is a rich body of work studying the tradeoffs between digital and analog computation, as well as on techniques to reduce both manufacture-time defects and runtime faults [Bushnell and Agrawal, 2000].

Redundancy, either in energy, space, or time, is a common approach used in digital logic to overcome the effects of noise. Error-correcting codes [Hamming, 1950] use redundancy in the representation of information to make it possible to detect and correct errors; the particular kinds and numbers of errors that can be detected and corrected depend on the amount of redundancy employed.

At a coarser grain, redundancy is also employed across complete computing systems, such as by replicating entire processors, complete servers, or even by replicating clusters and data centers. The challenges involved in such *fault-tolerant computing systems* are also the subject of a rich area of study [Avižienis et al., 2004].

Unlike traditional applications of computing systems, many modern applications of computation are in situations where the inputs to the system are from sources which are themselves noisy, unlike the inputs to a payroll application. Examples are the computations on sensor values in the many variants of health-tracking wearables. Similarly, the outputs of many applications are primarily for consumption via the human visual channel; an example is the rendering of images for a display. These applications could of course continue to be implemented with the level of redundancy used to guard against errors in traditional applications. Employing redundancy in space, time, and energy, independent of the needs of individual applications would likely have continued to be the way all computing systems are built. However, as the amount of energy used in a single logic operation reduced over time due to semiconduc-

tor process technology improvements, the overhead of the redundancy has become significant.

In those applications which do not require the same extremely low levels of errors, it is therefore now interesting to design systems which can trade errors for efficiency. And it is possible to go even further, to induce controlled amounts of errors if doing so would enable simpler, faster, cheaper, or more energy-efficient computing systems.

#### 1.3 Why Precision Matters in Many Numerical Computations

There are many important computations whose implementations require careful attention to numerical stability, however few implementors of large-scale scientific computations have deep knowledge of numerical analysis. In the absence of such expertise, an alternative is to employ greater numerical precision [Bailey, 2005]. Because there are few automated techniques for transforming applications to improve their numerical stability [Panchekha et al., 2015], high-precision computations will continue to be important for a large class of applications. One example of a system where higher precision was used as an expedient solution to numerical instability is illustrated in the work of He and Ding [2001], who showed how problems with the reproducibility of climate-modeling applications could be eliminated by switching to using 128-bit floating-point arithmetic. A central theme throughout this review is that the types and magnitudes of errors permissible in an application must always be considered in the context of the tradeoff between errors and resource usage: a technique should permit only as many errors as an application and context can tolerate. Techniques should weigh permitted errors against the improvement in resource usage obtained from permitting errors. One way to achieve this in numerical simulations is to use multiple levels of precision across the phases of computations.

One cause of numerical instability in the presence of errors is that most general-purpose computations have great *arithmetic depth* [von Neumann and Kurzweil, 2012]. Small errors may therefore get amplified across the steps of a computation.

#### 1.4 Why Some Applications Can Tolerate Errors

Despite the fact that many applications *cannot* tolerate any errors in their computations, there are also many applications which can. Typically, the applications that can tolerate errors are those that either:

- 1. **Operate on noisy inputs** (e.g., readings from sensors).

- 2. Have computation outputs requiring limited precision, e.g., because they are consumed primarily by human vision.

- 3. Employ iterative or self-policing algorithms. Examples of such algorithms are iterative methods where the computation will still produce the correct output in the presence of errors, provided that the computation makes progress in the right direction (on average) during each iteration.

- 4. Do not have data-dependent control-flow.

#### 1.5 Examples of Improving Efficiency by Permitting Errors

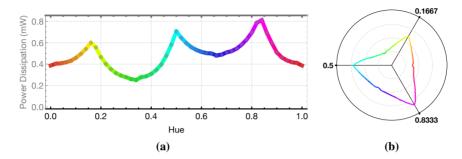

Because displays account for a large fraction of the power dissipation in popular computing platforms such as mobile phones and wearable devices, trading errors for reduced resource usage in displays is an interesting prospect. Organic light-emitting diode (OLED) displays present an interesting opportunity for trading errors for efficiency: Unlike traditional LCD displays, their power dissipation varies significantly as a function of the content displayed. It is therefore possible to purposefully introduce errors into displayed images to reduce the display's power consumption. The earliest examples of such approaches were originated by Dong et al. [2009a] and Dong et al. [2009b], who developed several of the first techniques for trading display power for visual fidelity in OLED displays. Recent research has developed more efficient techniques as well as new approaches that analyze and transform both the color and shape content of the rendered images to save power.

Figure 1.1 shows two variants of the same image, which differ in power dissipation by over 40% when displayed on a representative commercial OLED display panel. The image and corresponding shape and color transformations to reduce power dissipation on displays that behave similar to OLEDs were generated using the Crayon system [Stanley-Marbell et al.,

**Figure 1.1:** The image on the right dissipates more than 40% lower power than the one on the left when shown on OLED displays.

| Tolerable<br>Deviation |                | OCR<br>Text | Transition Reduction | Image<br>B | OCR<br>Text | Transition Reduction |

|------------------------|----------------|-------------|----------------------|------------|-------------|----------------------|

| 0%                     | cent <b>re</b> | "centre"    | 0%↓                  | EXIT       | "EXIT"      | 0%↓                  |

| 10%                    | centre         | "centre"    | 66%↓                 | SXIT       | "LTXIT"     | 61%↓                 |

| 20%                    | centre         | "centre"    | 73%↓                 | EXIT       | £ 33        | 73%↓                 |

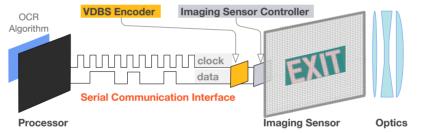

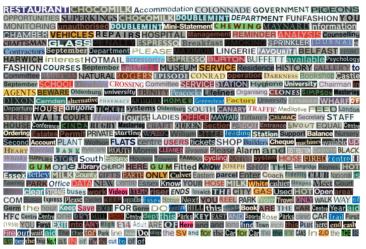

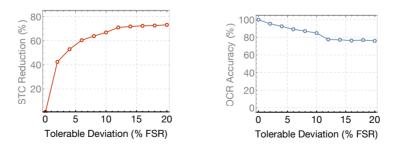

**Figure 1.2:** Encoding values so that they dissipate less power when transmitted can lead to significant power reductions before they begin to affect optical character recognition algorithms. This is despite the fact that the encoded images look very different to the human eye.

2016]. The difference between the original image and the modified one is that areas of the gray regions in the latter are reduced by 25% and the colors have been modified slightly. Chapter 4 explores techniques for exploiting tolerance in outputs in more depth.

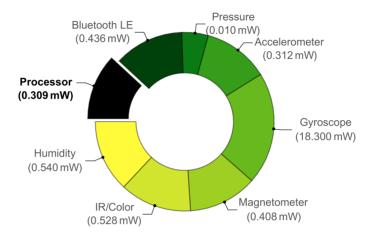

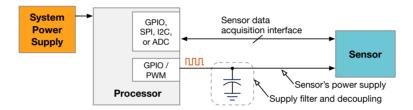

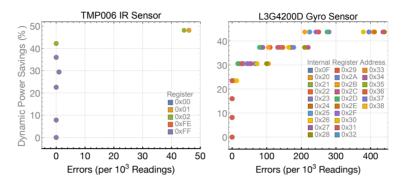

Not all systems have displays however. In the increasingly important domain of embedded sensor-driven systems, because the power dissipated in the digital logic components has continued to drop over the years, a significant fraction of the system's energy usage can result from the activation of sensors and the retrieval of data from them over their electrical communication interfaces.

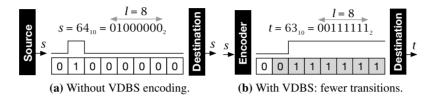

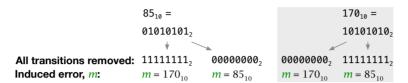

Figure 1.2 shows how techniques that reduce the energy cost of transmissions by lossy encoding of the data can enable significant reductions in the energy required for transmitting the data. However, when the algorithms consuming the encoded data can tolerate the types of errors introduced by the encoding, they lead to minimal application-level errors, even though the perceived visual distortion may seem significant to the human eye.

Even though tolerating errors in the inputs and output communication of algorithms can be exposed in the syntax of programming languages [Stanley-Marbell and Marculescu, 2006], tolerating errors in the steps of algorithms is much more involved when compared to tolerating errors in the data algorithms process or errors in their outputs. Approaches to tackling this challenge range from annotating individual variables in algorithms as being ones that can tolerate errors (or not) [Sampson et al., 2011], annotating variables corresponding to the outputs of functions to specify which ones are permitted to incur errors [Misailovic et al., 2014], and using program analysis techniques to provide guarantees about the effects of errors as they propagate through the algorithm [Carbin et al., 2013].

An alternative to providing specifications of the tolerable input or output error is to specify how much error is acceptable in the *relation between inputs* and outputs. Figure 1.3 illustrates the formal specification of the computation task of partial sorting, along with an example of an input-output pair that conforms to this computation behavior. This problem of obtaining a partial sort occurs in real applications: Partial sorting accounts for over 24% of the execution time of one popular discrete-event simulator [Jongerius et al., 2014]. One exciting open area of research is to synthesize algorithms (or hardware) that conform to such computation specifications and that permit some degree of error in the relation between their inputs and outputs.

#### 1.6 Fundamental Physical Limits, Energy, and Noise

Computing systems are designed to avoid errors at all levels<sup>1</sup>, from copying data from registers to their transmission to other systems or different processors. They prevent errors for all applications and, as a result, require error-correcting coding techniques at all levels; this introduces overheads that are unnecessary in some cases.

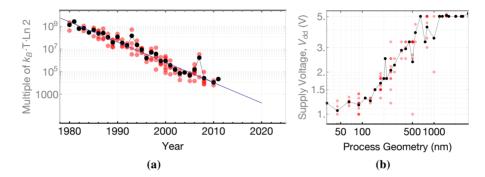

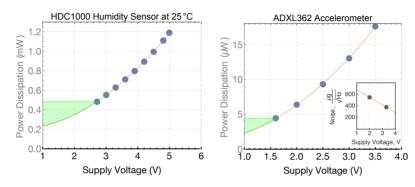

Because the traditional mechanisms for improving the density and power consumption of computing systems are reaching fundamental physical limits [Bennett and Landauer, 1985], there has been an increased interest in recent years to develop techniques to explore trading correctness for some tangible improvement in a system, such as improved speed or improved energy efficiency. Figure 1.4(a) shows the reduction in the energy required per bit of

<sup>&</sup>lt;sup>1</sup>Within the limit of economic and performance constraints

```

1 U0 : integers = <0 ... 20>

2 U1 = U0 >< U0 >< U0 >< U0 >< U0

3 S0 = \{12, 2, 14, 1, 7\} : U0

4

I0 = |S0|

U2 : integers = <1 ... I0>

7

P1 = forall i:U2[1] forall j:U2[1]

8

(_:U1[i] in S0) &

9

(_:U1[j] in S0) &

(!(_:U1[i] \leftarrow _:U1[j]) \mid (i \leftarrow j)) &

10

(!(i <= j) | (_:U1[i] <= _:U1[j]))

11

12

S2 = (P1 : U1)

13

(a)

(cardinality = 5, predicate tree size = 29)

(cardinality = 4084101, predicate tree size = 1)

{(1, 2, 7, 12, 14)}

Properties of input set:

Properties of set of candidate outputs:

Output, computed as a tuple:

```

**Figure 1.3:** Computation specification (a) for the computation that sorts a sequence of integers, expressed in the Sal low-level computation specification language Stanley-Marbell

[2010] and its output (b).

information processing, over several decades. Because the diminishing opportunities to reduce power consumption of computing systems is largely due to power delivery and cooling limitations, these challenges are unlikely to be easily resolved in the near future<sup>2</sup>, making the exploration of error-efficient systems ever more important in the future.

The underlying physical phenomenon permitting such energy versus correctness tradeoffs is well understood: For a device technology to be useful in constructing computational systems in which logic devices are linked together by non-ideal conductors, it must exhibit the property of *gain* (amplification) [Keyes, 1985]. This amplification requires an input energy source and the extent to which amplification occurs affects the likelihood of errors due to noise. If some amount of noise is tolerable, its presence can be traded for energy efficiency or performance.

<sup>&</sup>lt;sup>2</sup>Supply voltage scaling across technology nodes has ceased, as Figure 1.4(b) shows

**Figure 1.4:** (a) The energy per logic transition in traditional circuit techniques is approaching the fundamental thermodynamic limit of  $kT \ln 2$  Joules per bit of information (i.e., an ordinate value of 1 in (a) by ~2030). (b) One reason why energy usage in traditional CMOS logic is no longer scaling down, is that it is no longer feasible to decrease supply voltages. In both plots, the red points are published design data and the black points are the averages at a given abscissa [Stanley-Marbell et al., 2011].

#### 1.7 Hardware and Software Systems That Exploit Errors

Techniques to improve system dependability have traditionally taken the approach of hiding (masking) faults in the hardware data-path and control-flow with spatial and temporal redundancy. Such an approach is desirable when there must be no change of system behavior in the presence of faults, except, perhaps, for a change in performance.

Applications of computing systems such as signal processing (in desktops and workstations), and sensor-driven applications (in embedded systems) often drive outputs that are only directly perceived by humans (e.g., the outputs of audio and video processing), or have inputs that are taken from noisy analog sources (e.g., in sensor network applications). In such applications, programs can often tolerate some amount of "going-wrong". In particular, small deviations in values may be tolerable, and this is already exploited by some lossy compression algorithms for images (e.g., JPEG [Wallace, 1991]), audio, and video.

In many emerging applications of the recent decade, however, computing is moving from the sole purview of commercial business transaction management to more personal and pervasive applications such as embedded sensing and entertainment. In some of these new applications, such as embedded au-

tomotive control, there are still stringent requirements on correctness of machine state and computation. However, in many new applications, the need to maintain perfect error-free computation no longer exists.

As a result of these changes in applications of computing, a number of parallel research efforts have begun in recent years to explore ways to reduce the restrictions of perfect machine state. These efforts have ranged across:

- Reducing the number of bits used to represent data values and datapaths, either in storing those values or in synthesizing reduced-precision or reduced-accuracy logic in order to save energy (§ 1.7.1).

- Explicitly exploiting human perception to reduce resource usage (§ 1.7.2).

- Circuits that perform logic operations on probability distributions of values, rather than on unitary instance values (§ 1.7.3).

- Hardware and software architectures for counteracting the effects of soft errors (§ 1.7.4).

- Architectures that assume applications can tolerate errors in computation or timing, but have no contract with software on the permissible laxity (§ 1.7.5).

- Programming languages and runtime systems that incorporate annotation of imprecision in program state or operations, or exploit toleration of errors by applications (§ 1.7.6).

- Investigation of application domains that can tolerate various forms of computation errors or imprecision, in computation or state (§ 1.7.7).

These existing efforts have, however, mostly focused either only on adapting hardware independent of applications' requirements, or vice versa.

#### 1.7.1 Reducing representation precision in values and datapaths

The earliest efforts at harnessing potential tolerance of imprecision, at the hardware level, involved reducing the number of bits used in both integer [Stephenson et al., 2000] and floating-point [Tong et al., 2000] representations. These efforts were not based on explicit information exposed by, or extracted from programs, but rather, on the assumption that signal-processing applications inherently deal with values obtained from noisy real-world measurements, and that real-number representations in computers are inherently approximations. Techniques that reduce the bit-level precision of arithmetic, and those that expose notions of incorrectness at the language level must contend with issues of numerical analysis. Kulisch [2008] provides a thorough background on the interaction between numerics of computation and the architectures that facilitate computing. In reducing the number of bits however, while the precision or dynamic range (or both) are reduced, computation proceeds deterministically and independent of the properties (value distributions) due to the applications it executes.

An alternative approach to simply providing reduced precision independent of application properties, is to synthesize logic circuits based on the distributions of values and the tolerance to reduced accuracy of specific applications, as investigated by Lingamneni et al. [2013]

#### 1.7.2 Explicitly exploiting human perception

When the results of computation are consumed by the human aural or visual system, variations in accuracy, precision, or reliability may not always be perceptible. Such variations can be exploited directly in the generation of audio or display of results, for lower-energy, faster, or cheaper output devices (e.g., displays). For example, for displays, a few research efforts have investigated exploiting the variability in human sensitivity across the color spectrum. This phenomenon has been exploited to reduce power dissipation in OLED displays [Dong et al., 2009a, Zhao et al., 2013, Shin et al., 2011, Dong and Zhong, 2011, Harter et al., 2004, Li et al., 2014, Tan et al., 2013] as well as in those traditional LCDs that have coarse-grained controllable backlighting [Chuang et al., 2009]. Even when the results are consumed by non-human entities such as control systems, some amount of tolerance to imprecision, inaccuracy, and unreliability may still exist.

The interfaces for surfacing perceptual signals, such as displays and audio, contribute an increasing fraction of system energy usage in wearable and mobile systems. Because the phenomena underlying their operation (e.g.,

photon generation, mechanical displacement) are less amenable to improvements in transistor properties than computation is, their relative importance will likely grow in the future. Chapter 4 explores these concepts and implementations in more detail.

## 1.7.3 Probabilistic computation, probabilistic programming, and computing on probability distributions

In the traditional uses of probability in programming languages, the component which is probabilistic is the *behavior* of a computation, or a composition of concurrent processes [Stark and Smolka, 2000]. These approaches range from the *introduction of randomness into algorithms* [M. O. Rabin, 1976], the analysis of the behavior of randomized algorithms [Pnueli, 1983], and logics for probabilistic programs [Reif, 1980], to probabilistic parallel programs [Rao, 1994].

An alternative to the deterministic behavior of logic in hardware, whether of standard or of reduced precision, is to either employ randomness in the execution of hardware (to perform logic operations probabilistically [Palem, 2005, George et al., 2006]), or to consider the values of machine state due to executing applications, not as fixed instance values, but rather as probability distributions [Shanbhag et al., 2010, Vigoda et al., 2010, Vigoda, 2003]. The latter approach yields architectures that can be considered as forms of analog (as opposed to digital) computers.

### 1.7.4 Hardware and software architectures for counteracting the effects of soft errors

In the last decade, the observation that different applications (or classes thereof) may have differing tolerance to faults has been investigated [Wong and Horowitz, 2006], as have the possibility of applying different amounts of traditional software-based fault-tolerance techniques to different portions of an application [Reis et al., 2005a], as well as the influence of different hardware structures on the masking versus manifestation of faults as errors. These prior efforts, while recognizing the varying requirements for fault tolerance in applications and in hardware, have not attempted to tradeoff correctness for overheads.

There have been attempts to formalize the effects of soft-errors on the behavior of programs [Walker et al., 2006]. The model addressed in this recent work is one in which the goal is to attempt to nullify the effect of soft-errors

(faults), by redundant computation.

The observation that different portions of programs or of hardware may require differing amounts of fault-protection has previously been applied to reduce the implementation overheads of hardware systems. This observation has been extended to phases of programs [Reis et al., 2005c] as well as to the design of error-resilient processor architectures and silicon implementations [Leem et al., 2010, Bau et al., 2007, Borodin et al., 2009, Rhod et al., 2007, Mehrara et al., 2007].

Several research efforts have explored adding architectural support for low-overhead detection and correction of the effects of soft errors, such as the *software anomaly treatment (SWAT)* system and its derivatives [Srinivasan et al., 2004], by determining the effect of soft errors in components of processor microarchitectures on application behavior [Li et al., 2005, 2008]. Purely-software-based approaches can also be used to trade correctness for speed or reduced resource usage. Two examples of such approaches include *loop perforation* [Sidiroglou-Douskos et al., 2011], and relaxing locking requirements in GPU kernels [Samadi et al., 2013].

### 1.7.5 "Better-than-worst-case" design and approximate hardware architectures

In probabilistic computing architectures (§ 1.7.3), non-determinism is used in a well-defined manner. This is in contrast to so-called better-than-worst-case hardware architectures [Austin et al., 2005, Wagner and Bertacco, 2007, Kahng et al., 2010], which aggressively bias system properties (e.g., power supply voltage) into regimes which may furnish significant energy savings, but increase the chance of failure. These architectures then use a variety of methods (e.g., shadow latches in the Razor system [Austin et al., 2004]) for ensuring infrequently-occurring erroneous state is not committed to final architectural state, or that critical data is not adversely affected (e.g., by reducing DRAM refresh rates, but only for non-critical data, in the Flicker system [Liu et al., 2009]).

Taking the idea of better-than-worst-case design further, are a class of architectures that argue that permitting occasional errors can reduce power consumption. When these platforms rely on applications and system software to deal appropriately with the errors that may result, we will refer to the

platforms as *approximate hardware*. Examples of such approximate hardware range from processor architectures (or parts of processors such as ALUs) [Esmaeilzadeh et al., 2012b, Lingamneni et al., 2012], to complete accelerators [Esmaeilzadeh et al., 2012a, George et al., 2006, Sartori and Kumar, 2013], and to portions of the memory hierarchy [Sampson et al., 2013, Liu et al., 2009, Xu et al., 2004]. Techniques for approximation can be applied individually, or can be employed as part of a control system [Hoffmann, 2015] to ensure that a target energy reduction or accuracy constraint is satisfied.

As one example of these architectures, Truffle [Esmaeilzadeh et al., 2012a] defines an architecture in which individual operations (arithmetic instruction, memory accesses, etc.) may individually fail catastrophically with some probability, the rate at which they do so exhibiting a tradeoff with the amount of energy used. The manner in which this tradeoff is obtained is via the ability to set processor state and logic into a voltage-over-scaled (unreliable but energy-saving) state, with cycle-level granularity. Truffle relies on the programming language, compiler, and operating system to ensure that only individual instructions that can tolerate being in error are executed in the unreliable mode, and that unreliable state is appropriately quarantined from reliable state, with flow of data between reliable and unreliable computation obeying a well-defined set of constraints.

#### 1.7.6 Programming languages and runtime systems

Program-level annotation provides an alternative to relegating to hardware all decisions about what machine state's accuracy can be traded for energy efficiency or performance. Language-level specification of tolerable imprecision has ranged from the specification of coarse regions of application code that can, in some broad sense, tolerate errors [Reis et al., 2005c, Walker et al., 2006, Baek and Chilimbi, 2010], memory locations that contain critical data [Pattabiraman et al., 2008], to the elision of loop iterations to trade-off fidelity of computation results for energy efficiency or performance [Rinard et al., 2010, Rinard, 2006]. Program-level annotations of required precision such as the annotations provided by the EnerJ Java extension [Sampson et al., 2011] as well as tools to infer guarantees on correctness based on static program analysis [Carbin et al., 2013]. Detailed language-level facilities for specifying imprecision at the level of data types [Stanley-Marbell and

Marculescu, 2006] have also been developed, and extended to the declarative specification of the computation performed by a given subroutine, incorporating properties of imprecision [Stanley-Marbell, 2010].

## 1.7.7 Applications of "good-enough" computation in algorithms and software that are naturally resilient to errors

Given the aforementioned techniques for reduced precision arithmetic (§ 1.7.1), probabilistic computation (§ 1.7.3), hardware architectures and software techniques that take license with correctness (§ 1.7.4 and § 1.7.5), and language-level facilities for specifying how much incorrectness applications can tolerate (§ 1.7.6), a natural question is, which applications can best harness the possibilities afforded by these hardware and software innovations? Several proposals for potential application of such "good-enough" computation have been made in the research literature [Chakradhar and Raghunathan, 2010, Chippa et al., 2010, Breuer, 2010, 2005a, Meng et al., 2009, Chong and Ortega, 2007, Li and Yeung, 2007, Mohapatra et al., 2009, Breuer, 2005b, Salesin et al., 1989], however no consensus yet exists on a standard set of applications for evaluating proposed hardware and software techniques. Similarly, no commonly agreed-upon metrics exist for evaluating the degree to which behavior of benchmarks may deviate from correctness. Recent work has however taken an important step in this direction [Akturk et al., 2015].

One class of applications in which errors in computation are often tolerable is signal processing applications. This observation motivated some of the earliest work in trading correctness for performance and power from the work of Shanbhag on ANT [Hegde and Shanbhag, 1999, Shanbhag, 2002, Varatkar et al., 2009, Shanbhag et al., 2010], to silicon implementations of approximate signal processing from Amirtharajah and Chandrakasan [Amirtharajah and Chandrakasan, 2004] and Guo [Guo et al., 2006].

In addition to errors in values and control flow of computations, errors may occur in the timing of actions driven by computation, or in the latencies expected from computation. The term *imprecise computation* was coined in the nineties to denote real-time computing systems in which some deviation from temporal correctness was tolerable [Budin et al., 2004, Hull and Liu, 1993, Liu et al., 1991, Shih and Liu, 1995, Aydın et al., Liu et al., 1994, Kenny and Lin, 1991].

These efforts in computing systems and signal processing are of course predated by a large body of work in numerical analysis, uncertainty quantification (UQ) methods [Klir, 1994], tolerance graphs [Golumbic and Trenk, 2004], interval arithmetic [Hayes, 2003]), fuzzy logic and fuzzy set theory, approximation and randomized algorithms and, of course, existing work on in the broader field of fault-tolerant systems.

#### 1.8 Outline of the Remainder of This Review

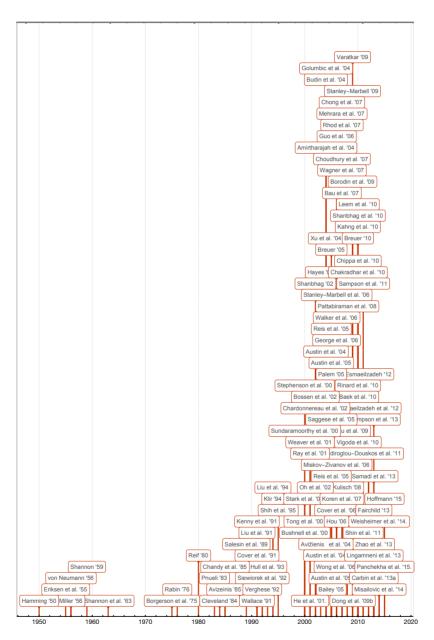

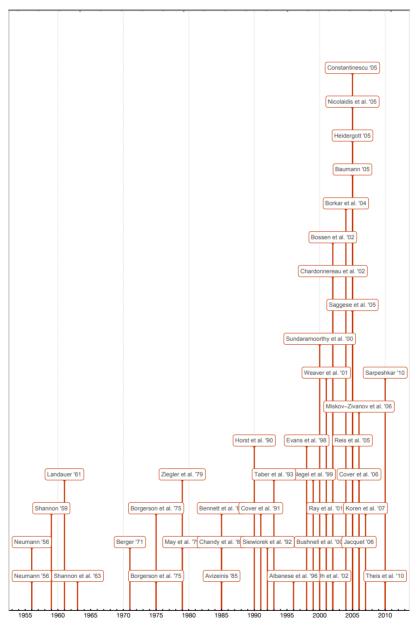

The present chapter provides a broad survey of the basic concepts explored in further detail throughout the review. It addresses the question of why errorefficient computing systems matter, and describes the context in which the material of the review is situated. It surveys the general state of the art in this area and positions the material of the review within it. Figure 1.5 summarizes the research referenced in this chapter. Chapter 2 (Types of Errors and Randomization) defines terminology, such as precision, accuracy, and reliability, which recur throughout the review and in any discussion of errors and of error efficiency. The definitions in Chapter 2 set the stage for the discussion of how errors affect efficiency in computing systems, in Chapter 3 (Computation, Energy, and Noise). Chapter 4 (Tolerating Errors in Outputs) addresses how many systems tolerate errors in their outputs. For example, any visual output that must be interpreted by a human may incur some amount of error before being perceptible. Chapter 5 (Tolerating Errors in Inputs) discusses the complementary problem of how many systems tolerate errors in their inputs. The review concludes in Chapter 6.

Figure 1.5: Timeline of referenced work in this chapter, listed by author.

### **Types of Errors and Randomization**

... even precision levels like  $1:10^5$  are inadequate for a large part of important problems ... The reasons for this surprising phenomenon are ... that when they are broken down into their constituent elements, [the procedures] turn out to be very long ... Now if there are large numbers of arithmetical operations, the errors occurring in each operation are superposed.

— John von Neuman, The Computer and the Brain.

In common science and engineering usage, the term *accuracy* refers, broadly speaking, to distance from ground truth. Precision, on the other hand, refers to repeatability or spread around a mean. Accuracy and precision both imply that when things go wrong, the system still obtains an output and that this output differs from the correct output *to a quantifiable degree*. In contrast, *reliability* typically refers to the likelihood that a system component will fail. Tolerance of unreliability, or tolerance of faults which lead to failures, is the focus of the well-established discipline of *fault-tolerant and dependable computing systems*. Reliability and fault-tolerance were discussed in Chapter 1.

Tolerance of inaccuracy in numerical computations has been studied for well over a half century in the domain of *numerical analysis*. Tolerance of

imprecision is well-studied, particularly in the context of imprecision in timing. There is a large body of work on *imprecise real-time systems*, dating back many decades.

In parallel with accuracy, precision, and reliability, the exploitation of randomness to improve algorithm performance has been explored in the area of *randomized algorithms* [Mitzenmacher and Upfal, 2005, Motwani and Raghavan, 2010]. Randomized algorithms employ randomness in the resolution of flow control in algorithms, such as by flipping a coin to determine which path on a branch to take. § 2.3 provides a concise introduction to randomized algorithms.

In contrast to this use of randomness in control flow, *stochastic computing* [Alaghi and Hayes, 2013] employs randomness in a different way. Rather than using randomness to choose which flow of control to follow as in the case of randomized algorithms, stochastic computing instead uses sources of entropy to generate distributions to represent different values to be used in arithmetic. § 2.4 introduces the concepts behind stochastic computing and explores how stochastic digital computing relates to analog-electrical computing.

Probabilistic programs [Goodman, 2013], like stochastic computers and randomized algorithms, also employ entropy in computation. However, in addition to employing values picked from some distribution in the steps of computation, they typically also infer or condition the distributions of values taken on by variables, based on values observed during computation. § 2.5 provides a brief overview of probabilistic programming.

#### 2.1 Precision, Repeatability, Accuracy, and Reliability

The term *precision* usually refers to the resolution or spacing between values represented in a system. For example, a ruler with markings at every millimeter is more precise than a ruler with markings at each centimeter. Similarly, real-valued numbers can be represented in C programming language type **double** with finer spacing (precision) than they can be represented with type **float**. Precision is typically a property of a measurement instrument or computing system. In the context of a measuring device, precision can also be thought of as the *repeatability* or *spread* between values obtained in measuring an unchanging quantity.

The term *accuracy*, in contrast to precision, refers to the difference between a measured or computed value and its true or nominal value. For example, a measurement that reports the speed of light as  $299792458\,m\cdot s^{-1}$  is accurate, while one that reports the speed of light as  $299792459\,m\cdot s^{-1}$  is less accurate (but expressed in a representation that is as precise as the previously-stated value). All measurements of values in the real world have some degree of uncertainty due to systematic or random errors in measurement. Measurement values with high accuracy are those with low uncertainty. Measurement values with low accuracy are referred to as *approximate*.

The term *reliability*, in contrast to precision, repeatability, and accuracy, is typically used to refer to the behavior of a system. Reliability refers to the relative frequency with which a device fails or is otherwise unavailable for use, regardless of whether it is precise or accurate.

#### 2.2 Accuracy of Models versus Precision of Computations

Accuracy is important when obtaining measurements of signals from the physical world. Once a measurement system has provided accurate measurements, higher precision in the data representation when storing or computing on the measured values may allow accurately-measured data to be used to obtain accurate results in data analyses. For example, a bar code scanner at a retail store must accurately determine the item being purchased. Once the scanning subsystem has accurately identified an item, subsequent computations such as charging a customers credit card must also occur accurately.

Not all measurement and computing systems require perfect accuracy however. There are many applications of data processing where the computing process into which measured data is fed is a model or algorithm that is itself an approximation of a poorly-understood physical process. Chapter 4 (tolerating errors in computing system inputs) and Chapter 5 (tolerating errors in computing system outputs) study two classes of systems where the users of computing systems and the algorithms consuming measurement data may tolerate varying degrees of inaccuracies in their inputs.

# 2.3 Randomized Algorithms: Making Randomized Decisions to Improve Algorithm Performance

Randomized algorithms are algorithms that make random decisions during their execution. These randomized decisions are based on *random*

sampling—repeatedly choosing random values according to a specific probability distribution. An example of a randomized algorithm is a variant of Quicksort [Hoare, 1961] with a random pivot. Such randomization of control decisions (or of the algorithms inputs) may enable algorithms to deal with pathological inputs, by making all inputs lead to algorithm behavior that is characteristic of typical inputs. Because some NP-hard problems may be easy to solve for typical inputs, using randomization to make all inputs look like average-case inputs is one important tool for tackling intractable computational problems. Randomized algorithms can be classified into two main groups. *Monte Carlo* algorithms may fail or may provide an incorrect answer. *Las Vegas* algorithms on the other hand always return the right answer, but may take a variable amount of time to do so.

When an algorithm makes random decisions, its performance can no longer be deterministic. Moreover, even deterministic algorithm behavior may vary with inputs. *Probabilistic analysis of algorithms* is a closely related topic that deals with estimating bounds on behavior of algorithms.

Even though they employ randomness, the use of randomness in randomized algorithms is at well-defined control-flow decision points. Randomness in randomized algorithms is not simply the introduction of random errors through an algorithm's control or data path. It is therefore incorrect to assume that randomized algorithms are inherently a good match for systems that make errors. The techniques from probabilistic analysis of algorithms may however still prove useful in analyzing properties of the behavior of algorithms executing on platforms which may incur random errors.

# 2.3.1 Analyzing randomized algorithms: Random variables characterize the actions of algorithms

Each instance where a randomized algorithm employs a random sample to influence a decision corresponds to an *event*. For example, in the case of randomized Quicksort, each event corresponds to a specific member of the input being chosen as the pivot. For example, we might say "the algorithm randomly chose the fourth element as the pivot in this iteration".

There are several pieces of terminology that are essential in discussing randomized algorithms and the probabilistic analysis of algorithms in the remainder of this chapter and in the research literature. The randomized actions of an algorithm can be represented formally with *random variables*. A random variable, X, is a function on the elements of the sample space of possible values,  $\Omega$ . A random variable, X on a sample space  $\Omega$  is a real-valued function on  $\Omega$ ; i.e.,  $X:\Omega\to\mathbb{R}$ . Events correspond to a random variable, say, X, (uppercase) taking on a specific value, say, x (lowercase). The probability of a random variable X taking on the specific value x is written as  $\Pr\{X=x\}$  or  $f_X(x)$ . An event consists of the random variable taking on a specific instance value.

#### 2.3.2 Probabilistic analysis of algorithms

Probabilistic analyses of deterministic and randomized algorithms use random variables to characterize properties of algorithm behavior and allow us to answer questions about the behavior of algorithms that make randomized decisions. For example, let X be a random variable denoting the number of comparisons made by a randomized version of Quicksort that randomly chooses its pivot. Then, we can use probabilistic analyses to answer questions such as the expected number of comparisons, E[X], and hence the expected running time.

# 2.4 Stochastic Digital and Analog Computing: Computing by Exploiting Explicitly-Random Inputs

Stochastic computing systems represent values with distributions whose parameters are a function of the values intended to be represented. For example, the number 4 might might be represented with a collection of 32 randomly-generated binary digits in which on average four of the 32 digits are 1s. Stochastic computers then use these distributions in computations, exploiting the property that certain operations which are complex when applied to values (e.g., multiplication) are simple when applied to distributions (e.g., a logical AND). Some approaches to stochastic computing eschew the use of random or pseudorandom bit sequences for deterministic sequences with a given ratio of zeros to ones [Alaghi and Hayes, 2013]. These approaches are in principle *deterministic unary arithmetic systems*, not stochastic.

The term *analog computing*, technically and historically, has two meanings: (1) computing with continuous values and (2) operation by analogy (simulation of one physical system or process using a second physical sys-

tem or process). We will use the term *analog* to mean continuously-varying electrical, unless noted otherwise.

If the systems being modeled, either computationally or by direct analogy, have similar stochastic behavior, then the limited accuracy and inherent stochasticity of analog computing (e.g., variations with temperature and time) are not a problem. Limited accuracy is also not an issue if the systems being modeled have similar resolution, or if the system being emulated has lower resolution. But, it is sometimes desired in modern science to simulate systems which have inherently different stochastics from those of analog computing systems, or require very high precision.

#### 2.4.1 Bridging the analog/digital gap

There are many signal processing steps that are efficiently implemented in the analog domain. These signal processing steps include filtering, mixing, and heterodyning. If we are to perform information processing in the analog domain, we must of course have the data we are to process in an analog representation, or digital data must explicitly be converted to an analog signal. Analog to digital conversion is however expensive. Sundström, Murmann, and Svensson [Sundström et al., 2009] present a first-principles derivation of the energy efficiency of several analog-to-digital converter (ADC) topologies and show the energy usage per conversion to be exponential in the number of bits of precision.

#### 2.4.2 Information processing in analog electronics

Techniques for performing non-signal-processing computations on analog computing systems have historically focused on using current-mode analog electrical circuits to solve differential equations. These techniques have largely exploited the integrative nature of charge accumulation on capacitors, summing operational amplifiers, and current multipliers. In some applications, the stochastic behaviors of the electrical circuit have been exploited in addition to the macro-scale numeric operations, to model systems such as gene transcription, with which they may have similar energy dynamics [Mandal and Sarpeshkar, 2009].

When exploiting the similarity of the energy dynamics of subthreshold analog electrical circuits to model biochemical processes, the primary benefit over traditional Gillespie simulation [Gillespie, 1977, 1976] is that the computationally-expensive generation of exponentially-distributed random samples, which is needed in the Gillespie method, is handled naturally by the exponentially-distributed noise in analog electronics. Instead of building analog circuits specifically to model biochemical circuits, it should be possible to attain most of the benefits simply by accelerating the random variate generation with analog circuits. Indeed, this idea has been explored by Marr and Hasler [Marr and Hasler, 2014].

There are however challenges to using analog circuits to generate random variates. If the random variate generation is based on thermal noise, then the process will be temperature dependent. Marr and Hasler [Marr and Hasler, 2014] and Bai and Lin [Bai and Lin, 2015] both acknowledge this challenge, and Marr and Hasler propose abandoning the thermal-noise-based approach altogether, in favor of chaos circuits.

#### 2.4.3 Precision and analog information processing

Analog electric computations have traditionally suffered from limited precision, since their precision was limited by the ability to build components (e.g., capacitors) with precise values. For components with a given value and precision, those values must not drift with temperature or other environmental conditions. Preventing such drift is not always easy or even possible to achieve. In contrast to analog electric computing systems, because Boolean-valued digital systems treat all values as being of one of only two possible levels, they only require as much control as needed to generate values of two distinguishable levels. Analog computing systems also traditionally suffered from an inability to limit the propagation of noise injected at individual steps in a chain. This inability to limit noise propagation is because, since analog electrical circuits are typically continuous-value systems, there is never a reference level to which noisy signals can be restored or thresholded.

The operation of analog circuits bears many similarities with stochastic digital computation [Alaghi and Hayes, 2013] and with unary arithmetic. This analogy has been alluded to in the work of Vigoda [Vigoda, 2003], but a much more forceful comparison can be made. Both stochastic digital computation and analog electrical computation achieve their computation through the combination of probability distributions. The number of samples needed

to assure a stochastic operation of a given resolution is analogous to the representation length needed to represent unary values with a given precision. Similarly, the tradeoff between analog and digital value representations as a function of the required precision, is analogous to both the stochastic sample count and unary representation length.

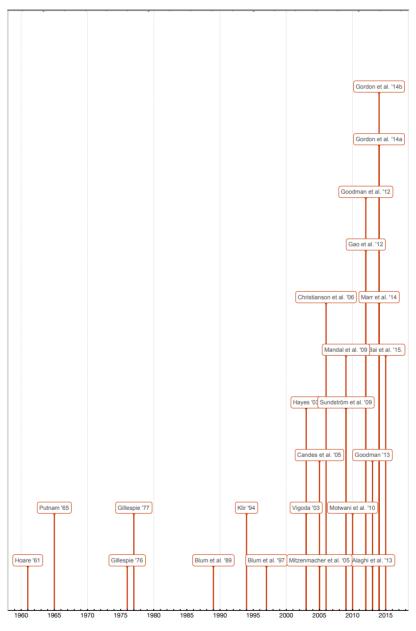

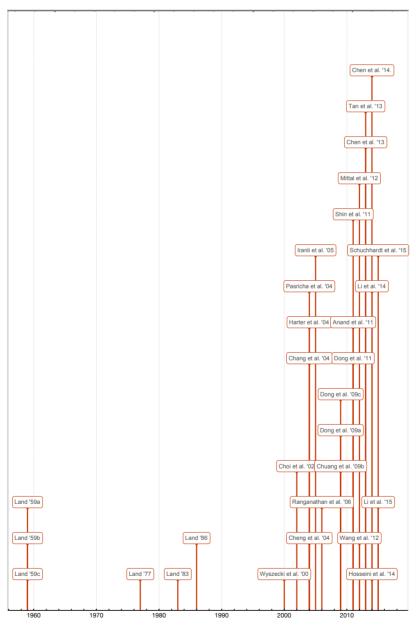

#### 2.5 Probabilistic Programming

The term *probabilistic programming* [Goodman et al., 2012, Gordon et al., 2014a,b] refers to a style of programs in which programs can generate random variates from one or more distributions and in which the programs can make control flow decisions based on the values taken by these random variates at runtime. Probabilistic programming languages thereby provide support for probabilistic inference using language-level constructs. Using properties of random variables and the laws of probability, probabilistic programs may perform inference to determine properties of unobserved random variables based on properties of observed random variables and the structure of the probabilistic program. Although the idiom of probabilistic programming can in principle be implemented in many existing programming languages, several special purpose probabilistic programming languages have been developed in recent years to make programming in this idiom more succinct. Figure 2.1 summarizes the research referenced in this chapter.

**Figure 2.1:** Timeline of referenced work in this chapter, listed by author.

### Computation, Energy, and Noise

These changes are indicated in terms of the dimensionless scaling factor  $\kappa$ ... The power dissipation of each circuit is reduced by  $\kappa^2$  due to the reduced voltage and current levels, so the power-delay product is improved by  $\kappa^3$ .

—Dennard et al. [1974].

Give a digital computer a problem in arithmetic, and it will grind away methodically, tirelessly, at gigahertz speed, until ultimately it produces the wrong answer.

—Hayes [2003].

The real world is noisy. To achieve reliable information processing in the presence of this noise, the basic elements of computing systems use redundancy in signals. In binary-valued digital systems, this redundancy involves amplifying a signal to one of two logic levels after each logic stage. In analog systems on the other hand, redundancy is usually achieved by averaging signals over time. In both the digital and analog systems, the techniques for obtaining useful signals in the presence of noise effectively trade the depletion of one resource (energy, time) for the improvement of another (signal quality). This chapter explores the relationship between computation, energy,

and noise. We begin in § 3.1 with an overview of how digital computing systems employ signal gain to guard against the accumulation of noise. We then explore the sources of noise in § 3.2 and review traditional fault-tolerant systems in § 3.3.

#### 3.1 Devices Use Energy to Guard against Faults

Theis and Solomon [2010] give a cogent explanation of the lower limits on supply voltage necessary to counteract the effects of thermal noise. They start from the Johnson-Nyquist voltage noise, which follows a Gaussian distribution with standard deviation of voltage noise

$$V_n = \sqrt{\frac{k \cdot T}{C}},\tag{3.1}$$

where k is Boltzmann's constant, T is temperature in Kelvin, and C is the load capacitance of a typical gate. They then take  $V_n$  as the minimum voltage needed to distinguish between two logic states. Thus, a logic voltage of m standard deviations will give a probability of reliable operation (logic value being greater than noise), given by the complementary error function, of

$$\frac{1}{2} \cdot \operatorname{Erfc}\left(\frac{m}{\sqrt{2}}\right).$$

(3.2)

It is thus possible to tradeoff probability of logic error for supply voltage, and hence active power dissipation. Lower supply voltages, in the traditional CMOS bulk FET, comes with exponential increases in leakage current. There are however a number of promising new device technologies which are not subject to this exponential dependence of leakage current on supply voltage, which in bulk CMOS is constrained by the subthreshold slope of 60 mV per decade, such as tunnel field-effect transistors (TFETs) [Theis and Solomon, 2010].

#### 3.2 Types and Sources of Noise and Faults

Design faults<sup>1</sup> are mistakes made in the specification or implementation of a system design. Manufacture-time defects (henceforth, *defects*) are the result

<sup>&</sup>lt;sup>1</sup>These are usually referred to as design errors. For consistency, we will however reserve the term *error* for special use, as explained in this section. We refer to design-time "mistakes" as *design faults*.

of aberrations in the manufacturing process which contrary to the desire of a system's designers cause intermittent or permanent failures. Faults, or more elaborately, *lifetime-faults*, are those deviations from correct functionality, that occur during the lifetime of a system. They may be the result of aging-related processes, in which case their effects will be time-dependent and often irreversible. Faults may also be the result of intermittent external phenomena, such as electrical noise, high energy neutrons or  $\alpha$ -particles. The term "softerror" is usually used to refer to such intermittent or transient faults. In this review however, the term "error" is used in a more restricted sense.

Faults and defects may be *masked* by appropriate design or runtime actions, in which case the system will continue to function correctly in their presence. In a detailed gate-level simulation of an entire embedded microprocessor, Saggese *et al.* [Saggese and Vetteth, 2005] show that faults in data values in the register file, load-store unit and bus interface account for more than 50% of the faults that are not masked. We will refer to defects and faults which are *not* masked as *errors*, and to temporary errors as *soft errors*. Errors lead to perceptibly erroneous behavior in a system. A system may be able to tolerate errors, detecting them and continuing functioning. There are many ways to detect errors in hardware and in software. Some fault-tolerant embedded systems [Chardonnereau, Damien and Keulen, Raijmond and Nicolaidis, Michael and Dupont, Eric and Torki, Kholdoun and Faure, Fabien and Velazco, Raoul, 2002] and workstation-class systems [Bossen et al., 2002] implement detection circuits for errors in on-chip memory and logic.

The abstraction of the effects of soft errors employed in this chapter will be that of soft errors leading to *bit flips* or *inversion upsets*, where a high logic level (logic 1) is incorrectly forced to a low logic level (logic 0) or vice versa. Rather than causing a logic  $0 \to 1$  transition or vice versa, a fault might cause a logic value to assume a state that is *ostensibly invalid* (i.e., neither 1 nor 0). Such upsets will be referred to as *erasures* or *erasure upsets*.

Facilities such as *watchdog timers* may be employed to detect errors that manifest as system deadlocks or latency constraint violations, and communication erasures may be detected with techniques such as the use of message sequence numbers. The term *failure* will be used to refer to errors which lead to irrecoverable system demise.

#### 3.2.1 Failure mechanisms and their sources

Soft errors have been observed in computing systems as far back as the late fifties, when they were first observed as intermittent failures of electronic equipment during nuclear bomb testing [Ziegler et al., 1996]. The mechanisms underlying their occurrence begun to be understood in the late seventies, and they have since been systematically studied from a variety of viewpoints. The sources of high-energy particles from device packaging material [May and Woods, 1979] and from cosmic rays, leading to a spectrum of energetic particles both on land and in avionics [Ziegler and Lanford, 1979, Taber and Normand, 1993], have been studied, as have the influence of such particles on integrated circuits [Ziegler and Lanford, 1981].

#### 3.2.2 Semiconductor-process-related faults

Semiconductor process scaling occurs along multiple axes, all of which have some bearing on defects and faults. On one axis is the scaling of minimum feature sizes, e.g., minimum gate length and minimum half-pitch; this is usually the most publicized result of process scaling. Scaling the dimensions of device structures means that there are ever fewer atoms making up device features. For example, the *critical charge*, the number of electrons representing a logic value, is reduced across generations. As a result, lower-energy disturbances can cause a logic value at any point in a circuit, whether in combinational logic or in memory, to be changed from a 0 to a 1 and *vice versa*, or placed in an altogether invalid state.

Another source of defects and faults is variation in device properties, between devices (say, in the same cell library), between cell libraries, across an integrated circuit, within a wafer, across wafers that are part of the same batch (Si ingot), and across batches. For example, at the 65 nm technology node, approximately 100 atoms control the threshold voltage of a transistor, thus a variation in as little as one atom is significant — variations in dopant concentration have been a problem in semiconductor processes for more than two decades [Borkar et al., 2004].

At some technology nodes, feature scaling requires drastic changes to the implementation of devices in an integrated circuit. These changes are manifested in new technologies such as copper interconnects, low- $\kappa$  dielectrics,

and new device structures such as multi-gate or fin-fet structures. These new technologies introduce new defect and failure modes. For example, interconnect thickness variability is primarily a problem for copper interconnects and not for traditional aluminum interconnects. This particular problem is mitigated by planarization techniques such as chemical-mechanical polishing. These planarization techniques however impose new requirements on circuit topologies, such as requirements on continuity of material densities (e.g., polysilicon or metal) across a wafer.

Although we are primarily interested in intermittent faults, it is worth briefly mentioning some of the sources of permanent faults (in addition to manufacture-time defects). Sources of permanent logic upsets in integrated circuits include irreversible aging-related phenomena, such as *electromigration-induced failures* in interconnect, *negative bias temperature instability (NBTI)* and *hot-carrier injection (HCI)* related failures. Electromigration is a process that leads to the narrowing and eventual severing of metal traces in integrated circuits. NBTI and hot-carrier injection lead to degradation of transistor characteristics with age, and may thus also be the cause of failures.

#### 3.2.3 Externally-induced intermittent faults

Temporary logic upsets might be the result of runtime disturbances in an integrated circuit, e.g., due to power supply noise, variation of device parameters with temperature, power supply droop, or ground bounce. These disturbances might in turn be due, for example, to dynamic system adaptation techniques, or to phenomena unrelated to the behavior of a system. Temporary faults have long been of concern in high-availability systems such as servers [Slegel et al., 1999, Horst et al., 1990].

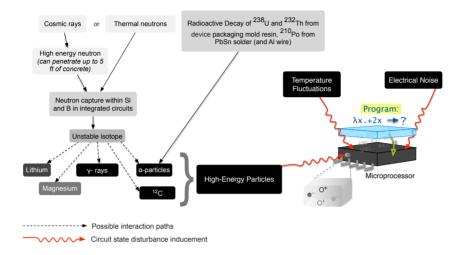

The dominant source of intermittent faults in integrated circuits in recent decades has been cited as high-energy particles such as neutrons and  $\alpha$ -particles [Baumann, 2005]. The  $\alpha$ -particle flux, the number of particle strikes per  $m^2/s$ , varies with altitude (with a peak at approximately 60,000 feet), with time (varies with the 11 year solar cycle), with application domain (e.g., terrestrial, versus space applications), and also varies with latitude [Heidergott, 2005]. Some of the sources of temporary logic upsets are illustrated in Figure 3.1. The reactions (e.g., neutron capture, radiation emission) resulting

Figure 3.1: Some sources of temporary logic upsets in hardware.

from interaction of high energy neutrons with integrated circuits are referred to as *spallation reactions*.

#### 3.2.4 Characterizing fault rates

In characterizing the resilience of computing systems to soft errors, two approaches are generally employed — *accelerated testing* and *real-time testing*. Accelerated testing uses an artificial source of high-energy particles, such as radioactive material (e.g., <sup>210</sup>Po), or a neutron beam. In such accelerated tests, it is desirable for the spectrum of particle energies to match those in the foreseen deployment environment, e.g., at ground level for terrestrial applications. Real-time testing on the other hand deploys the units under test in naturally high-particle-flux environments, such as at high elevations. Such experiments have been carried out in places such as a laboratory in Jungfraujoch, Switzerland, (elevation 11,400 ft) [Nicolaidis and Chardonnereau, 2005] and an IBM testing facility in Leadville, Colorado, in the United States (elevation 10,152 ft) [Ziegler et al., 1996].

The changes in state caused by energetic particles are generally referred to as *single-event effects (SEEs)*. A temporary SEE that is not masked is termed a *soft-error*, and a permanent one a *hard fail*. One example of a hard

fail is a *single-event latchup (SEL)*. It is possible that an SEE may lead to no erroneous change in state: For example, the transient pulse resulting from an SEE may be attenuated as it propagates through a combinational circuit, or it may occur outside the latching window in a sequential circuit. An SEE that *does* lead to a non-masked change in circuit state is usually referred to as a *single-event upset (SEU)*. The rate of occurrence of logic upsets (SEUs) is generally referred to as the *soft-error rate (SER)*. It is measured in units of *failures in time (FIT)*, where a soft-error rate of 1 FIT corresponds to one failure in a billion operation hours.

For memory technologies, the SER per bit usually decreases with decreasing feature size at a given operating voltage because the capture volume for interaction with high energy particles is smaller with smaller device area [Constantinescu, 2005]. Based on over 1000 tests performed on devices at different process technology nodes, Nicolaidis *et al.* [Nicolaidis and Chardonnereau, 2005] have shown that the FIT rate per megabyte decreases slightly across process nodes up to the 130 nm node, leveling off subsequently as manufacturing processes approached the 90 nm node.

To achieve constant-field scaling<sup>2</sup>, semiconductor processes also scale supply voltages as they scale transistor dimensions [Dennard et al., 1974]. This lowering of supply voltages and the lower gate capacitances that result from scaling gate dimensions mean that there is less charge representing a logic value at smaller process geometries, possibly offsetting the smaller capture volume.

Overall, the SER *per integrated circuit die* for common applications like microprocessors increases due to increasing circuit complexity, with increasing number of transistors per die. The current FIT rate in memories is approximately 1000 FIT [Nicolaidis and Chardonnereau, 2005] to 2000 FIT [Jacquet, 2006] per megabit. In comparison, the failure rate due to NBTI and HCI is about 100 FIT [Jacquet, 2006].

# 3.3 Traditional Fault-Tolerant Systems

The construction of computing systems which continue to provide utility in the presence of faults [von Neumann, 1956] has been an active area of

<sup>&</sup>lt;sup>2</sup>Keeping the electric field across the gate constant as the gate length is reduced between process technology generations.

research for many decades. With the advent of multi-processor systems in the 1960's, the idea of *gracefully-degrading systems* [Borgerson and Freitas, 1975] which tradeoff performance for utility in the presence of faults became of interest; the graceful degradation in these systems was graceful degradation with respect to their performance and not graceful degradation with respect to correctness (i.e., not what we might call adaptive error-efficient systems).

From the viewpoint of computing systems as information processors, the construction of fault-tolerant systems can be likened to the reliable transmission of information as considered in information theory [Shannon and Weaver, 1963]. The techniques employed in utilizing redundancy in providing reliable computation are analogous to the use of redundancy in information streams to enable forward error correction. The idea of trading off encoding overhead for the quality of the transmitted signal has been investigated in information theory, with the theoretical underpinnings of *rate distortion theory* [Berger, 1971], and with practical applications such as *unequal error protection* and *priority encoding transmission* [Albanese et al., 1996] taking advantage of semantic constraints on correctness of data streams. There have however been no equivalent efforts to trade off the correctness of computation for lower overheads in fault-tolerance. This could in part be seen as a result of the primary use of computers, prior to the present decade, in applications in which *any* form of (undetected) error was undesirable.

In contemporary digital computing systems, underlying physical processes (e.g., voltages) are usually treated as having only two states (logic 0 and logic 1) at the level of individual *binary digits (bits)*. Across multiple bits in the internal representation of a system, collections of bits are typically required to retain their assigned value and to do so without incurring any anomalous deviations. To achieve this illusion, computing systems have, over the years, devised and employed a variety of techniques for identifying errors in collections of bits (e.g., *cyclic redundancy check (CRC)* codes), and for employing redundancy to enable the correction of errors (e.g., *error-correcting codes (ECC)*, and simpler arrangements of coarse-grained redundancy paired with majority voting). These techniques have been applied at all levels of computing system implementations, from registers and buses, to on-chip memories, data transmitted on interconnection networks, to data stored

on a variety of media. All these techniques are important when absolutely no errant logic state should go uncorrected, or, at least, undetected, and is the subject of the important research areas of fault-tolerant systems [Koren and Krishna, 2007], coding theory [Cover and Thomas, 1991], and digital systems testing [Bushnell and Agrawal, 2000].

#### 3.3.1 Dealing with faults in computation and communication

Because computing systems traditionally attempt to prevent the occurrence of errors, there have been several techniques developed to counteract faults in computation and communication systems. Approaches to counteract soft errors include circuit-level techniques such as the use of high-value polysilicon transistors in the feedback paths of static random-access memory (SRAM) cells, alternative SRAM cell topologies and inter-digitating the chip-level layout of the bits of different memory words to reduce the chances of multi-bit errors within a single machine word. Architectural and system-level techniques include the use of error correcting codes (ECC) for memory and array structures, and the use of redundancy (e.g., triple modular redundancy (TMR)) for entire functional blocks. There also exist software techniques aimed primarily at providing algorithmic and high-level program-module-based fault tolerance [Avizeinis, 1985].

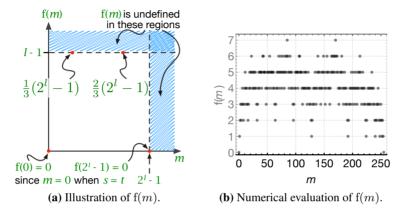

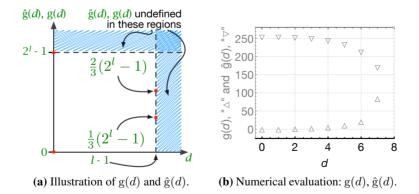

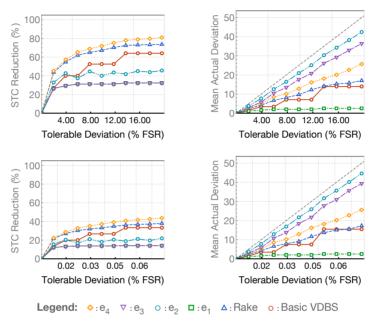

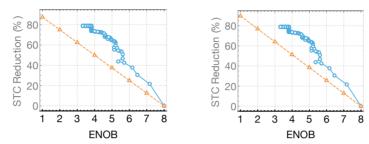

Approaches for improving reliability of computation have traditionally been placed under four main classifications: fault avoidance; fault detection; masking redundancy; and dynamic redundancy [Siewiorek and Swarz, 1992]. Fault avoidance involves proactively designing systems, at the hardware or software level, that prevent the occurrence of faults. Fault detection techniques provide mechanisms for the incorrect status of hardware or software to be detected, a simple example being parity bits in memories. Masking redundancy approaches employ redundant hardware or software resources to mask the presence of faults, e.g., by taking a majority vote over redundantly performed computations, as in N-modular redundancy (NMR). Masking redundancy approaches implicitly employ a static organization of resources to mask the presence of faults. Dynamic redundancy techniques on the other hand take advantage of redundantly available hardware resources as they are needed and may tradeoff performance for reliability, e.g., by also using redundantly available devices for useful computation.