# Low-loss 800V Lateral IGBT in Bulk Si Technology using a Floating Electrode

Vasantha Pathirana, Nishad Udugampola, Tanya Trajkovic and Florin Udrea

Abstract— An 800V rated lateral Insulated Gate Bipolar Transistor (LIGBT) for high frequency, low-cost applications is proposed. This LIGBT features a new method of adjusting the bipolar gain by using floating N+ and P+ regions connected by a floating electrode in front of the P+ collector. This floating structure lowers the injection efficiency at the collector side of the device, resulting in a very significant decrease in the turn-off time and substantially lower turn-off losses. The device was fabricated in a 0.5µm bulk silicon CMOS technology at a commercial foundry without additional processing steps or process optimisation. Tests on fabricated devices showed equivalent R<sub>dson</sub> below 70mΩ.cm<sup>2</sup> at 125°C with switching times as low as 250ns at 125°C. The novel LIGBT device showed avalanche capability and low gate capacitance and was used for the first time, in an AC/DC converter operating at 200kHz allowing significant improvements in performance, compactness and reduced component count.

Index Terms-Floating Electrode, Injection Control, LIGBT, **Bulk Silicon, Power Device, Lateral**

## I. INTRODUCTION

Lateral power devices are gaining popularity because of their suitability for realisation of more compact solutions: they can be easily monolithically integrated with controllers, protection circuits, etc. [1] or co-packed with other chips using standard assembly recipes or flip-chip techniques [2]. Recent lateral MOSFETs (LDMOSFETs) have shown improvement in current density, however, due to unipolar conduction they still suffer from low current density and hence become too large for use in applications where compactness is critical. In addition, LDMOSFETs suffer from significantly increased on-state resistance at high operating temperatures and EMI issues due to too fast switching.

Lateral IGBTs combine advantages of a MOS gate drive and high current densities of bipolar transistors. Electrical

Manuscript received February 14, 2018. This work was supported in part by the EPSRC National Centre for Power Electronics grant EP/K035304/1.

- V. Pathirana is with Electrical Engineering, University of Cambridge, CB3 0FA, UK and Cambridge Microelectronics Ltd, CB23 6DP, UK (phone: +44 (0)1223 748311; fax: +44 (0)1223 748348; e-mail: vp222@cam.ac.uk).

- N. Udugampola is with Electrical Engineering, University of Cambridge, CB3 0FA, UK and Cambridge Microelectronics Ltd, CB23 6DP, UK (e-mail: nku20@cam.ac.uk).

- T. Traikovic is with Electrical Engineering, University of Cambridge, CB3 0FA, UK and Cambridge Microelectronics Ltd, CB23 6DP, UK (e-mail: tt208@cam.ac.uk).

- F. Udrea is with Electrical Engineering, University of Cambridge, CB3 0FA, UK and Cambridge Microelectronics Ltd, CB23 6DP, UK (e-mail: fu@cam.ac.uk).

conductivity of the LIGBT is sharply increased by minority carrier injection from the collector and conductivity modulation of the drift region. However, a high level of charge, although beneficial for lowering on-state losses, slows down switching speed and increases turn-off losses. LIGBTs in bulk silicon technology are known to be especially slow as they suffer from injection of carriers deep into the substrate which are difficult to remove and can cause cross-talk problems.

There has been extensive research into lowering the turnoff losses in bulk silicon LIGBTs. One common approach is using an anode-shorted design [3]. However, this leads to an on-state snap-back (negative resistance) and as a result possible oscillations during switching. These effects can become more prominent at low temperatures. There have been many reported structures to adjust the collector injection efficiency without introducing the snap-back. Ref [4] reports an LIGBT having an anode structure characterised by an additional N+ region in front of the collector P+ formed in a shallow P layer to control the collector injection. Ref [5] investigates the LIGBT performance improvement by use of a passive gate at the collector side of the device. Another approach is to use a Schottky contact in front of the collector P<sup>+</sup> to lower the collector injection [6]. Ref [7] reports lowering the collector P+ doping and using a floating N+ in front of collector P+ to lower the switching losses. This structure is based on the idea of creating a physical barrier for hole injection and is helped by the Auger recombination process. This technique is only effective if coupled with a lower dose P injector. Most of these techniques will require additional processing steps and/or process optimisation, which can be expensive and time consuming.

We report here for the first time a novel 800V rated, compact, high speed, robust and reliable LIGBT in low-cost bulk Si technology. The device has been fabricated using a standard CMOS process, available from a commercial foundry, without any additional layers or process changes.

#### II. DEVICE DESIGN AND CONCEPT

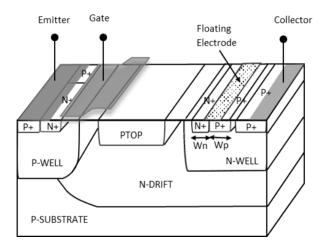

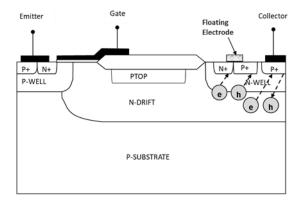

The half-cell cross-section of the novel LIGBT is shown in Fig. 1. It has a floating electrode consisting of connected N<sup>+</sup> and P+ regions adjacent to the P+ collector, both residing in the N-WELL buffer region. As a comparison, the standard LIGBT design has only a P<sup>+</sup> region connected to the collector terminal within the N-WELL. The drift region design is based on the

EDL-2018-04-0557

double-RESURF concept [8] and was optimised to achieve high breakdown voltage and fast switching performance.

Fig. 1. 3D schematic of the proposed 800V rated LIGBT design

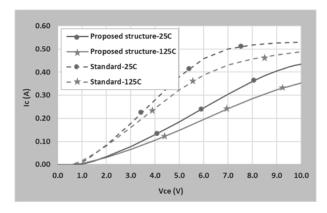

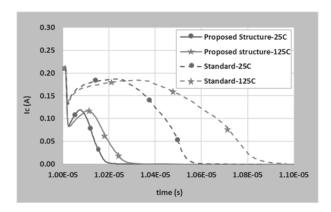

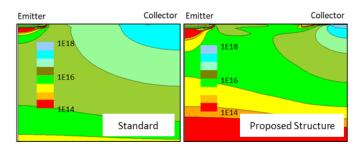

Figs. 2 and 3 compare TCAD simulation results of on-state and turn-off for the proposed design and the standard LIGBT. Only difference between these two structures is the collector design as described in the previous paragraph. The novel LIGBT shows higher conduction losses and significantly lower turn-off losses. At high temperature, both conduction and turn-off losses are increased. Fig. 4 depicts the hole concentration inside the two device designs at the same current at Tj=125°C. Higher carrier concentration deep in the substrate in the standard LIGBT will make it a very slow device in the turn-off and unsuitable for many modern applications. In contrast, the proposed LIGBT has a much lower carrier concentration deep in the substrate (>2 orders of magnitude), enabling very fast switching.

Fig. 5 shows the flow of electrons and holes in the N-WELL region. At the collector electrode, holes are injected into the device and electrons are extracted out of the device. At the floating electrode, holes injected by the collector P<sup>+</sup> are converted into electrons by the floating electrode, with sum of the electron and hole current being zero. Holes present at the floating electrode do not participate in the injection process, which means that the injection efficiency of the P<sup>+</sup> collector/N-WELL junction is reduced. Thus the conductivity modulation of the collector side of the drift region is weakened. Furthermore, presence of the floating electrode also helps the electron-hole recombination at the collector side of the drift region during turn-off enhancing the commutation speed and reducing the transient losses.

In Fig. 1, widths Wn and Wp can be adjusted to control injection efficiency and vary the trade-off between the on-state and switching losses. Wider Wn and Wp will reduce the injection efficiency thereby increasing the conduction losses and reducing the turn-off losses. Narrower gap between the floating electrode structure and collector P<sup>+</sup> will also reduce the injection efficiency.

Fig. 2. TCAD simulated on-state curves at Vg=5V

Fig. 3. TCAD simulated turn-off curves

Fig. 4. TCAD simulated hole distribution at Ic=0.2A at 125°C

Fig. 5. 2D schematic showing the flow of electrons and holes at the Collector

EDL-2018-04-0557 3

### III. MEASUREMENT RESULTS

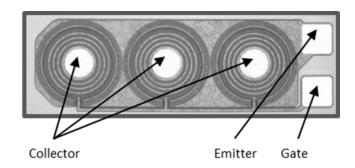

Fig. 6 shows a photograph of a fabricated device in a  $0.5\mu m$ , bulk Si CMOS process. These LIGBTs were designed with 150Å gate oxide and the threshold voltage was ~0.7V, making them suitable for applications with 5V gate drive. Measured device breakdown is in excess of 800V and the device has been evaluated and fully qualified in plastic packages for 800V operation. Leakage current at 800V is below 1nA at  $25^{\circ}\text{C}$  and below  $1\mu A$  at  $125^{\circ}\text{C}$ .

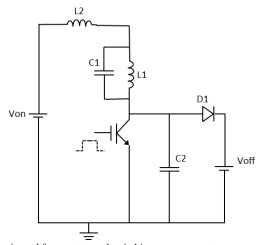

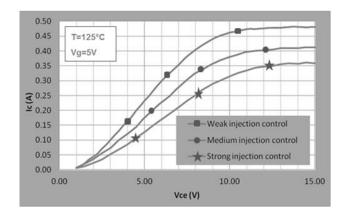

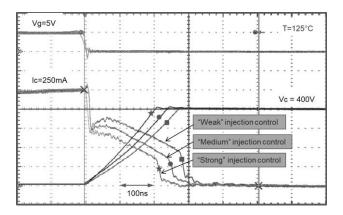

Fig. 7 shows the circuit used for the measurements of the pulsed on-state and turn-off losses. In this circuit, Von and L1 will define the on-state current and Voff will define the turnoff voltage. L2, C1 and C2 are parasitic components. Fig. 8 and Fig. 9 depict the on-state and turn-off curves of fabricated devices for different lengths of the floating P<sup>+</sup> (Wp in Fig. 1). Larger Wp value will reduce collector injection efficiency which will increase the conduction losses and lower the switching losses. This design allows layout-based fine-tuning of conduction vs. switching losses, which can be used to minimise total losses in the target application. The corresponding equivalent specific R<sub>dson</sub> of the devices for which the measurements are shown in Fig 8 is between 46 and 70 m $\Omega$ cm<sup>2</sup> (strong injection control to weak injection control) at 125°C. Similarly, depending on the device design, turn-off losses vary between 4.5µJ and 7.2µJ at 125°C.

Fig. 6. Photograph of a fabricated 800V rated LIGBT device

Fig. 7. Circuit used for on-state and switching measurements

Fig. 8. Measured on-state curves of fabricated devices at 125°C

Fig. 9. Measured switching curves of fabricated devices at 125°C

Fabricated and packaged devices have been tested under unclamped inductive switching conditions showing avalanche capability, which together with their blocking capability of >800V, can help remove external components used for surge protection and make the product more compact. Very low specific Rdson results in a very compact LIGBT devices with a small gate area and low capacitances (Ciss=15pF, Coss=10pF, Crss=3pF) allowing use of compact gate drivers using standard, low voltage CMOS devices.

#### IV. CONCLUSIONS

A novel, 800V rated, lateral IGBT for high frequency, low-cost applications has been proposed. It allows the device area to be reduced by 3-5 times compared to an LDMOS specified for the same application. The device, fabricated in 0.5µm bulk silicon CMOS technology, employs a new injection control feature which allows layout-based fine tuning of device characteristics to minimise the total device losses depending on application requirements. New injection control technique which minimises the amount of charge injected deep into the substrate resulted in devices with switching speeds of <250ns and equivalent specific  $R_{\rm dson}$  below  $70 {\rm m}\Omega {\rm cm}2$  at  $125^{\circ}{\rm C}$ . Furthermore, use of bulk Si with its relatively high thermal conductance yielded good avalanche capability. Also soft switching behaviour resulted in very low EMI, allowing further removal of external components.

EDL-2018-04-0557 4

#### REFERENCES

- [1] Don Disney, Ted Letavic, Tanya Trajkovic, Tomohide Terashima and Akio Nakagawa, "High-Voltage Integrated Circuits: History, State of the Art, and Future Prospects", IEEE Transactions on Electron Devices, Jan 2017, Vol. 64, pp. 659-673, DOI: 10.1109/TED.2016.2631125.

- [2] Tanya Trajkovic, Nishad Udugampola, Vasantha Pathirana, Florin Udrea, John Smithells and Tracy Wotherspoon, "Flip-chip Assembly and 3D Stacking of 1000V Lateral IGBT (LIGBT) Dies", Proc. ISPSD, June 2016, pp. 139-142, DOI: 10.1109/ISPSD.2016.7520797.

- [3] M. R. Simpson, P. A. Gough, F. I. Hshieh, V. Rumennik, "Analysis of the lateral insulated gate transistor," Proc. IEDM 1985, Volume: 31, pp740-743, DOI: 10.1109/IEDM.1985.191082.

- [4] A.Nakagawa, Y.Yamaguchi, T.Ogura, K.Watanabe, Y.Yasuhara, R.Sato, K.Endo and K.Furukawa, "500V Three Phase Inverter ICs Based on a New Dielectric Isolation Technique", Proc. ISPSD, May 1992, pp 328-332, DOI: 10.1109/ISPSD.1992.991296.

- [5] Tomohide Terashima, "A novel driving technology for a passive gate on a Lateral-IGBT", Proc. ISPSD, June 2009, pp. 45-48, DOI: .1109/ISPSD.2009.5157997.

- [6] Shigeki Takahashi, Akio Nakagawa, Youichi Ashida, Satoshi Shiraki, and Norihito Tokura "Carrier-Storage Effect and Extraction-Enhanced Lateral IGBT (E2 LIGBT): A Super-High Speed and Low On-state Voltage LIGBT Superior to LDMOSFET", Proc. ISPSD, June 2012, pp. 393-396, DOI: 10.1109/ISPSD.2012.6229104.

- [7] T. Trajkovic, N. Udugampola, V. Pathirana, G. Camuso, F. Udrea and G.A.J. Amaratunga, "800V Lateral IGBT in Bulk Si for Low Power Compact SMPS Applications", Proc. ISPSD, May 2013, pp. 401-404, DOI: 10.1109/ISPSD.2013.6694430.

- [8] D. R. Disney, A. K. Paul, M. N. Darwish, R. Basecki and V. Rumennik, "A new 800V lateral MOSFET with dual conduction paths", Proc. ISPSD, June 2001, pp. 399-402, DOI: 10.1109/ISPSD.2001.934638.