# **Durham E-Theses**

# Fault tolerance in digital controllers using software techniques

Halse, Robert G.

#### How to cite:

Halse, Robert G. (1984) Fault tolerance in digital controllers using software techniques, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/7474/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

## FAULT TOLERANCE IN DIGITAL CONTROLLERS USING

## SOFTWARE TECHNIQUES

by

Robert G. Halse

#### FAULT TOLERANCE IN DIGITAL CONTROLLERS USING SOFTWARE TECHNIQUES

#### Robert G. Halse

#### ABSTRACT

Microprocessor based systems for controlling gas supplies require very high levels of reliability for safety reasons. Non-redundant systems are considered to be inadequate, and an alternative approach is necessary. In digital systems, transient faults are as much as fifty times more common Therefore mechanisms which allow for recovery from than permanent faults. transients will provide large improvements in reliability. However, to enable effective design of recovery mechanisms it is necessary to understand failure modes.

The results from practical interference tests, designed to simulate transient faults, are presented. They show that corruption to the correct flow of program execution is a common failure, and that subsequent instruction fetches can be performed from any of the memory locations. Under these conditions any value of operation code can be interpreted as an instruction. including those undeclared bv the manufacturers. Four commonly used microprocessors are investigated to establish the functions of the undeclared codes, and other undeclared operations are revealed.

Analyses on the sequence of events following a random jump into the four main memory types of data, program, unused and input areas, are presented. Recovery from this type of execution can be achieved by the addition of restart codes into the areas, so that execution can transfer to a recovery routine. The effect of this mechanism on the recovery process is investigated.

Finally, some methods of testing systems, to check the levels of reliability improvement obtained by these techniques, are considered.

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to the people and organisations that have contributed to the work presented in this thesis. In paricular, to the Science and Engineering Research Council, and the British Gas Corporation's Engineering Research Station at Killingworth, for providing financial support. То my supervisor Dr. Clive Preece tor his encouragement, guidance and general advice throughout the research. To Dr. Ken Jenkins of the British Gas Corporation for providing much useful information and equipment. To Dr. Mansour Sahardi for his interest and discussion on the project. To Mandy for translation and typing work. Τo the electrical technicians (Jack, Trevor, Michael, Colin, Steve, Ian and lan) for their co-operation and assistance while I have been at the university. Finally, I would like to thank the Fleetham family for allowing me to practice my building skills on their house during my spare time.

## FAULT TOLERANCE IN DIGITAL CONTROLLERS USING SOFTWARE TECHNIQUES

by

Robert G. Halse

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

Thesis Submitted for the Degree of Doctor of Philosophy in the Faculty of Science University of Durham November 1984

1

H. The star

## List of Contents

| Section     |           |                                                        |      |

|-------------|-----------|--------------------------------------------------------|------|

| List of     | Figures   |                                                        | vili |

| List of     | Tables    |                                                        | x    |

| List of     | Symbols   | and Abbreviations                                      | xi   |

|             |           | CHAPTER 1                                              |      |

|             |           | Introduction and Review of System Reliability          |      |

| 1.1         | The Ne    | ed for a Reliable Controller                           | ]    |

|             | 1.1.1     | Present Mechanical Control                             | 2    |

|             | 1.1.2     | Future Micro-Electronic Control                        | 4    |

| 1.2         | Source    | of Failures                                            | 7    |

| 1.3         | Method    | s of Increasing Reliability                            | 9    |

|             | 1.3.1     | Reducing Failures due to Design Errors                 | 10   |

|             | 1.3.2     | Reducing Failures due to Component Malfunctions        | 12   |

|             | 1.3.3     | Reducing Failures due to Environmental Effects         | 15   |

| 1.4         | Reliabili | ity Improvements Obtained                              | 19   |

| 1.5         | Importa   | nce of Error Detection                                 | 21   |

| 1.6         | Possible  | e Dangers of Adding Redundancy                         | 24   |

| 1.7         | Require   | ments for Different Applications                       | 26   |

| 1.8         | Content   | s of the Thesis                                        | 28   |

|             |           | CHAPTER 2                                              |      |

|             | Pra       | ctical Tests to Determine Transient Failure Mechanisms |      |

| 2.1         | Introduc  | tion                                                   | 31   |

| <b>2</b> .2 | Test Sys  | stem                                                   | 32   |

|             | 2.2.1     | Processor Board                                        | 32   |

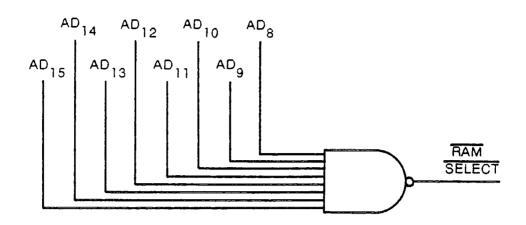

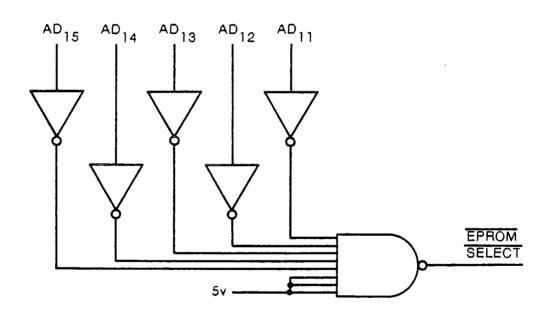

|             | 2.2.2     | Decoding Circuitry                                     | 33   |

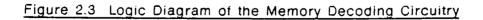

|             | 2.2.3     | Power Supply Unit                                      | 34   |

|             |           |                                                        |      |

١

i

|     | 2.2.4     | Software     |                                    | 34 |

|-----|-----------|--------------|------------------------------------|----|

|     |           | 2.2.4.1      | SYSTEST                            | 34 |

|     |           | 2.2.4.2      | RAMTEST                            | 35 |

| 2.3 | Practica  | I Tests Per  | formed                             | 36 |

| 2.4 | Test Re   | sults        |                                    | 38 |

|     | 2.4.1     | Interferenc  | e to the RAM                       | 39 |

|     | 2.4.2     | Interferenc  | e to the EPROM                     | 41 |

|     | 2.4.3     | Interferenc  | e to the Processor                 | 43 |

|     | 2.4.4     | Interferenc  | e to the Complete System           | 44 |

| 2.5 | Significa | ance of the  | Results                            | 46 |

| 2.6 | Observa   | tions of Per | rmanent Failures                   | 46 |

|     | 2.6.1     | Processor    | Failures                           | 47 |

|     | 2.6.2     | RAM Failu    | re                                 | 49 |

|     | 2.6.3     | Crystal Fai  | ilure                              | 49 |

| 2.7 | Summar    | у            |                                    | 50 |

|     |           |              | CHAPTER 3                          |    |

|     |           | Undecl       | ared Operations of Microprocessors |    |

| 3.1 | Introduc  | tion         |                                    | 52 |

| 3.2 | Undecla   | red Operati  | on Codes                           | 52 |

| 3.3 | Operatio  | ons of the 8 | 085                                | 54 |

| 3.4 | Operatio  | ons of the 6 | 800                                | 56 |

|     | 3.4.1     | Determinat   | ion of the Undeclared Instructions | 56 |

|     | 3.4.2     | Functions    | of the Undeclared Codes            | 58 |

|     | 3.4.3     | Cycling Th   | rough Memory                       | 59 |

|     | 3.4.4     | Compariso    | n with Published Data              | 61 |

| 3.5 | Operatio  | ons of the 4 | 8-series Microprocessors           | 62 |

|     | 3.5.1     | Undeclared   | d Memory in the 8035               | 63 |

|     | 3.5.2    | Determinir                                            | ig the Undeclared Instructions      | 64 |

|-----|----------|-------------------------------------------------------|-------------------------------------|----|

|     | 3.5.3    | The Effect                                            | s of Executing the Undeclared Codes | 65 |

|     |          | 3.5.3.1                                               | Intel 8035/8048                     | 65 |

|     |          | 3.5.3.2                                               | NEC 8035/8048                       | 66 |

|     | 3.5.4    | Other Devi                                            | ces in the Series                   | 67 |

| 3.6 | Operatio | ons of the 6                                          | 8000                                | 67 |

| 3.7 | Operatio | perations of the 6809 and Z80                         |                                     |    |

| 3.8 | Implicat | lications of the Undeclared Operations on Reliability |                                     |    |

|     | 3.8.1    | Significand                                           | ce for Watchdog Design              | 70 |

|     | 3.8.2    | Powering                                              | down to Enable Recovery             | 71 |

|     | 3.8.3    | Use of No                                             | n-Maskable Interrupts               | 72 |

|     | 3.8.4    | The Most                                              | Important Undeclared Operations     | 72 |

| 3.9 | Summa    | ry                                                    |                                     | 72 |

| Erroneous | Execution | in | Data | Areas |

|-----------|-----------|----|------|-------|

|           |           |    |      |       |

| 4.1 | Introduc | tion                              | 74 |

|-----|----------|-----------------------------------|----|

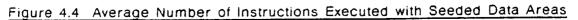

|     | 4.1.1    | Random Jump Within the Memory Map | 75 |

| 4.2 | Analysis | of Execution                      | 75 |

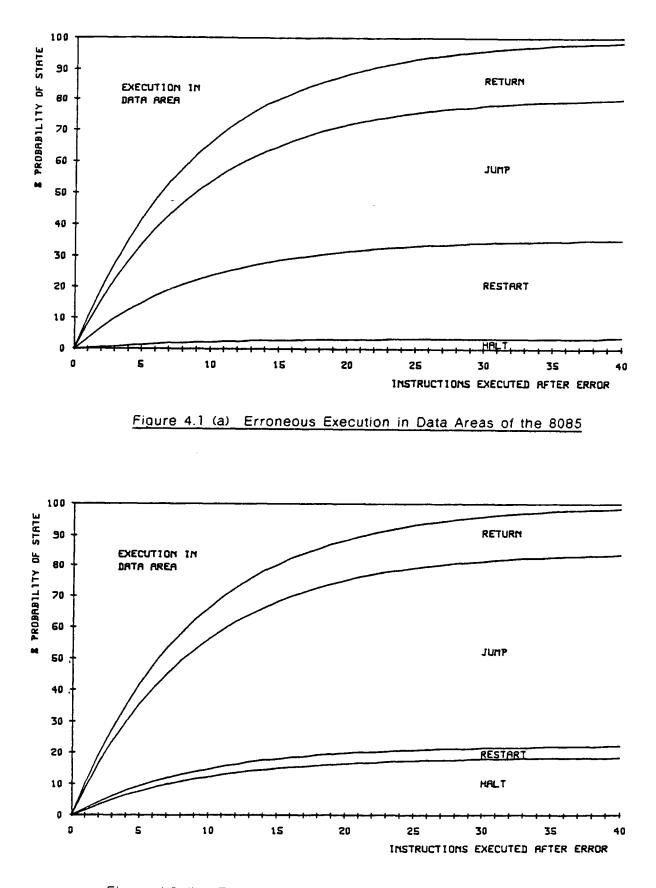

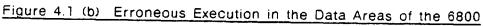

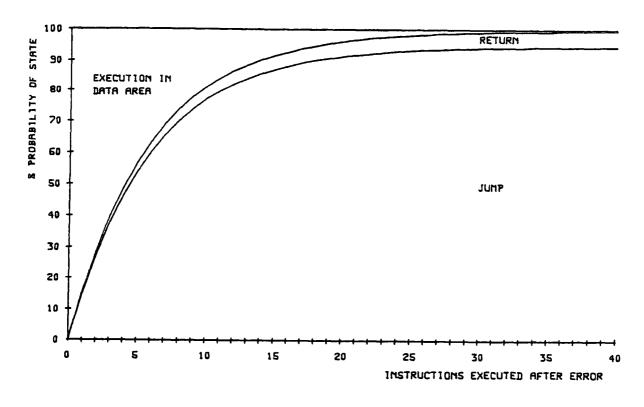

|     | 4.2.1    | Response of Different Processors  | 77 |

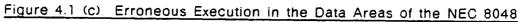

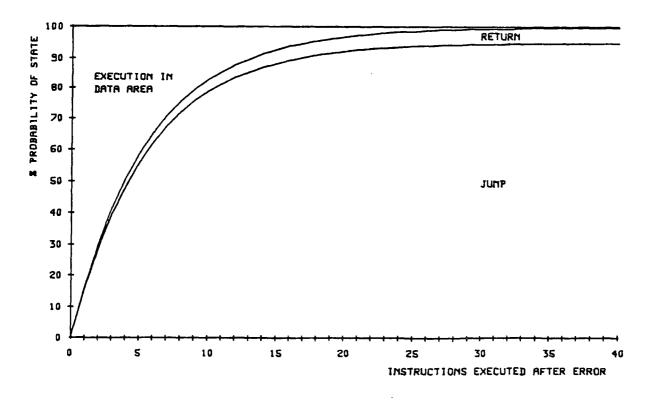

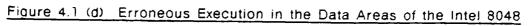

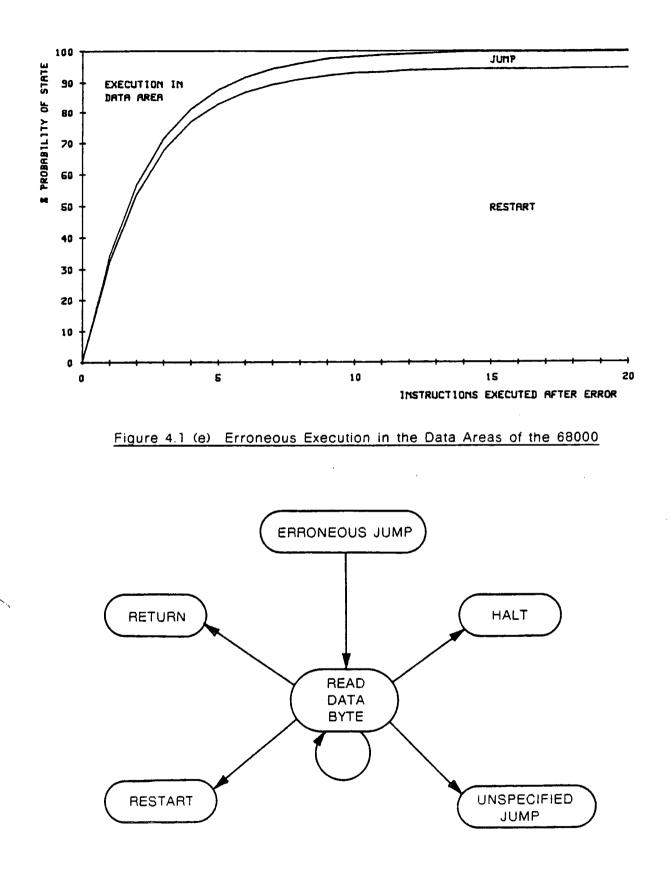

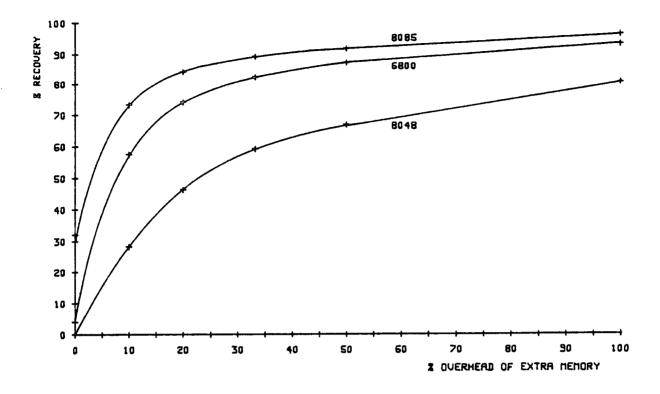

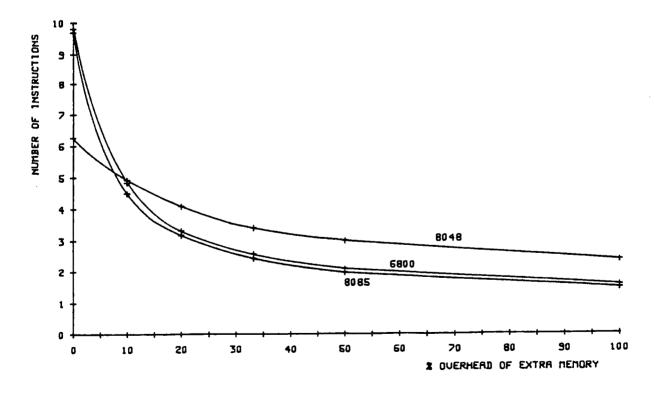

|     | 4.2.2    | Results from the Analysis         | 79 |

| 4.3 | Transfer | from the Data Area                | 79 |

|     | 4.3.1    | Halt Instructions                 | 79 |

|     | 4.3.2    | Restart Instructions              | 80 |

|     | 4.3.3    | Return Instructions               | 81 |

|     | 4.3.4    | Unspecified Jumps                 | 81 |

| 4.4 | Modifica | tion to the Analysis              | 82 |

| 4.5 | Improve  | ments in Recovery                 | 83 |

| 4.6 | Simulat                            | ion of Execution in Data Areas            | 83 |  |  |  |  |

|-----|------------------------------------|-------------------------------------------|----|--|--|--|--|

| 4.7 | Optimur                            | Optimum Seeding of Data                   |    |  |  |  |  |

|     | 4.7.1                              | 4.7.1 Data Structures for the 8085        |    |  |  |  |  |

|     | 4.7.2                              | Data Structures for the 6800              | 85 |  |  |  |  |

|     | 4.7.3 Data Structures for the 8048 |                                           |    |  |  |  |  |

|     | 4.7.4                              | Data Structures for the 68000             | 87 |  |  |  |  |

| 4.8 | The Effe                           | The Effect of Data Block Size on Recovery |    |  |  |  |  |

| 4.9 | Summa                              | ry                                        | 88 |  |  |  |  |

## Erroneous Execution in Program Areas

| 5.1 | Introduc       | ction                                              | 89  |

|-----|----------------|----------------------------------------------------|-----|

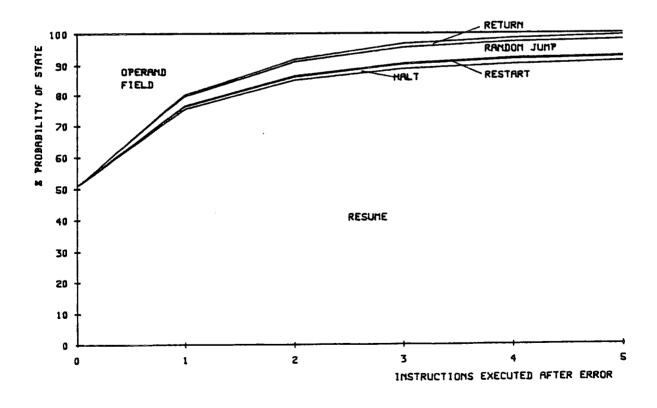

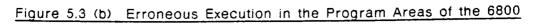

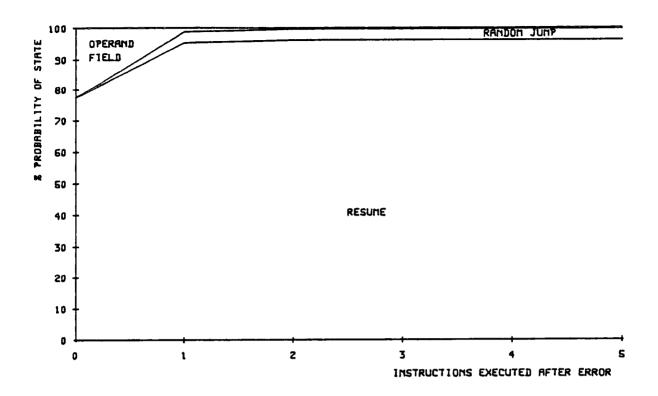

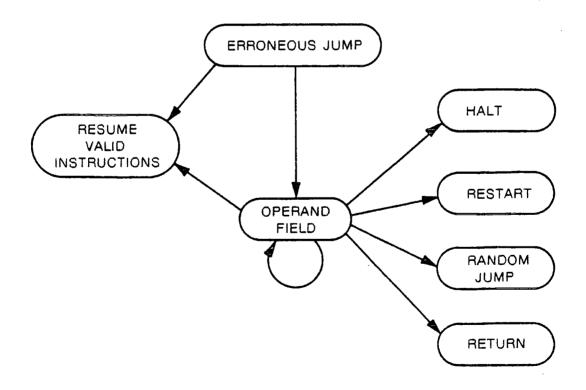

| 5.2 | Detailed       | d Analysis                                         | 89  |

|     | 5.2.1          | Comparison Between Instruction Sets                | 92  |

|     | 5.2.2          | Comparison Between Actual Programs                 | 93  |

| 5.3 | Simplifi       | ed Analysis                                        | 94  |

| 5.4 | Compar         | rison Between the Detalled and Simplified Analyses | 96  |

| 5.5 | Verifica       | tion of Results                                    | 97  |

| 5.6 | Improve        | ements in Recovery                                 | 97  |

|     | 5. <b>6</b> .1 | Low Level Detection                                | 98  |

|     | 5.6.2          | High Level Detection                               | 99  |

| 5.7 | Summa          | ry                                                 | 100 |

## CHAPTER 6

## Erroneous Execution in Unused and Input/Output Areas

| 6.1 | Introdu                   | Introduction                  |     |  |

|-----|---------------------------|-------------------------------|-----|--|

| 6.2 | Execution in Unused Areas |                               |     |  |

|     | 6.2.1                     | Unpopulated Memory Areas      | 102 |  |

|     | 6.2.2                     | Unpopulated Areas of the 8085 | 103 |  |

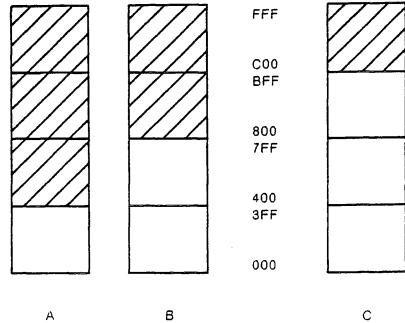

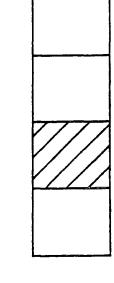

|     | 6.2.3                          | Unpopulated Areas of the 8048           | 105 |

|-----|--------------------------------|-----------------------------------------|-----|

|     | 6.2.4                          | Unpopulated Areas of the 6800 and 68000 | 108 |

| 6.3 | Execution in Memory Mapped I/O |                                         |     |

|     | 6.3.1                          | Execution of Input Data by the 8048     | 110 |

| 6.4 | Summai                         | ry                                      | 111 |

## Flow of Execution Between Different Memory Areas

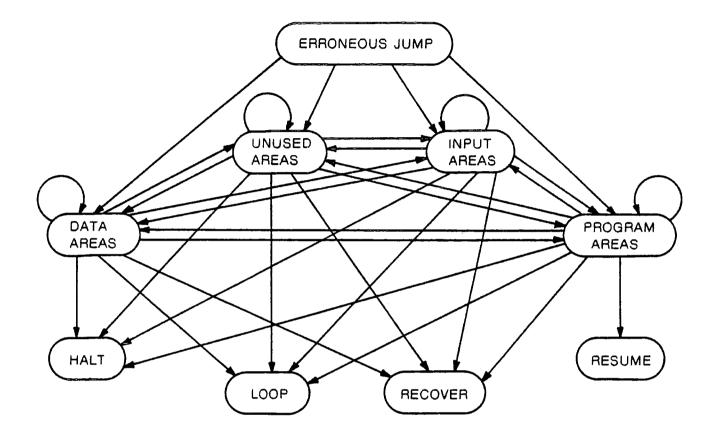

| 7.1  | Introdu                              | ction         |                                      | 112 |

|------|--------------------------------------|---------------|--------------------------------------|-----|

| 7.2  | Method                               | of Analysis   |                                      | 112 |

| 7.3  | Initial Error                        |               |                                      |     |

| 7.4  | Transfer from Different Memory Areas |               |                                      |     |

| 7.5  | Executi                              | on of an Infi | nite Loop                            | 115 |

|      | 7.5.1                                | Loops in D    | ata Areas                            | 115 |

|      | 7.5.2                                | Loops in L    | Inused Areas                         | 116 |

|      | 7.5.3                                | Loops in Ir   | nput Areas                           | 117 |

| 7.6  | The Ex                               | pected Num    | per of Instructions Executed         | 118 |

| 7.7  | The Eff                              | ects of Mem   | ory Map Usage on Erroneous Execution | 119 |

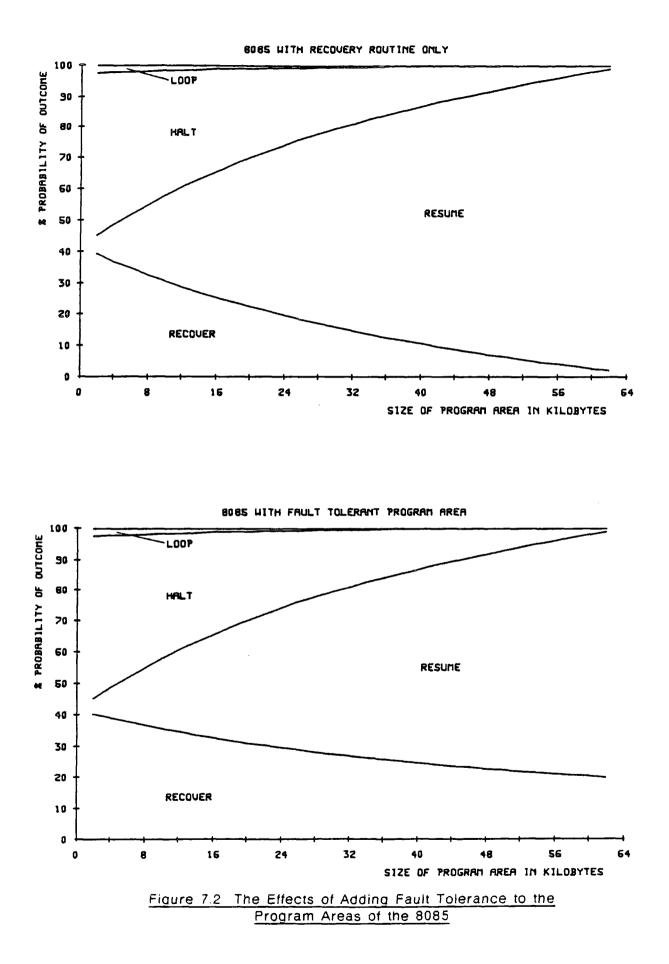

|      | 7.7.1                                | Memory M      | aps of the 8085                      | 120 |

|      |                                      | 7.7.1.1       | Fault Tolerant Program Area          | 121 |

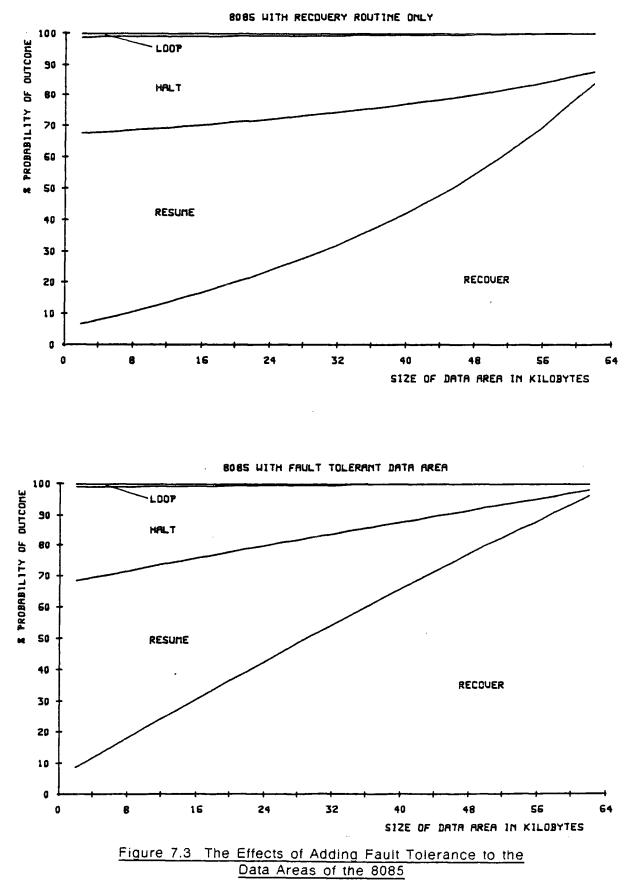

|      |                                      | 7.7.1.2       | Fault Tolerant Data Area             | 122 |

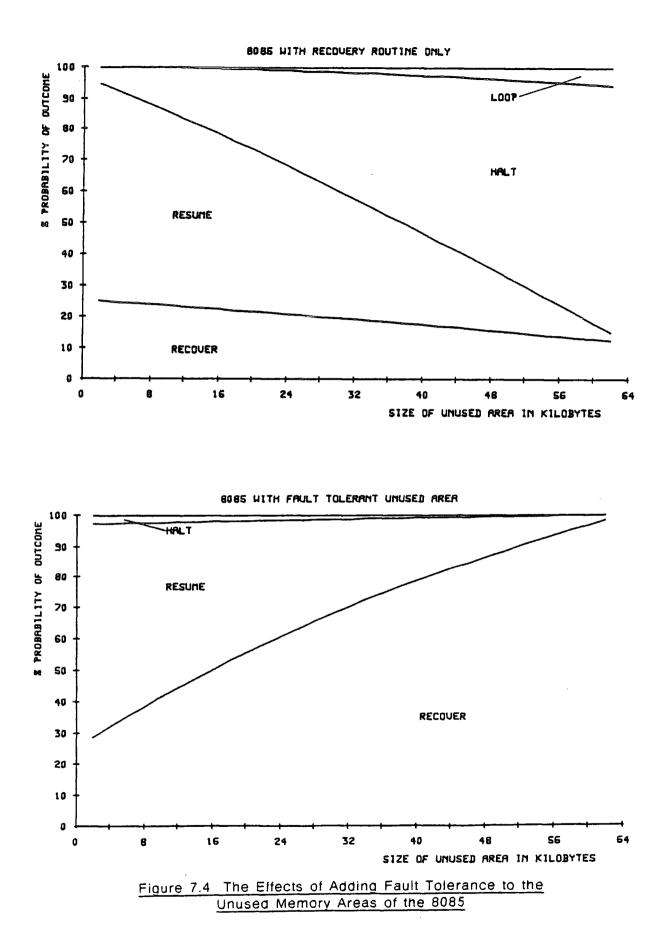

|      |                                      | 7.7.1.3       | Fault Tolerant Unused Areas          | 123 |

|      | 7.7.2                                | Memory M      | aps of the 6800                      | 123 |

|      | 7.7.3                                | Memory M      | aps of the 68000                     | 125 |

|      | 7.7.4                                | Memory M      | aps of the 8048                      | 126 |

| 7.8  | Numbe                                | r of Erroneo  | us Instructions Executed             | 127 |

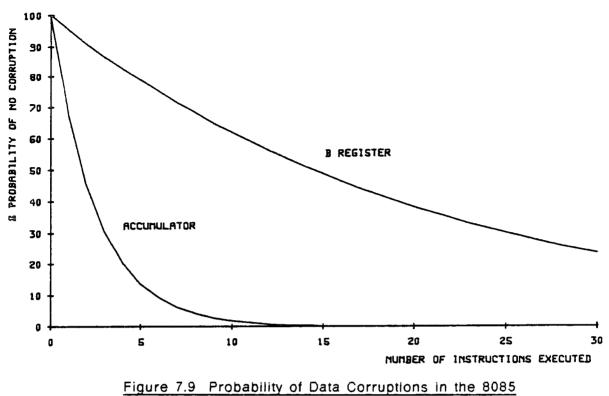

| 7.9  | Probab                               | ility of Data | Corruption                           | 128 |

| 7.10 | Summa                                | ry            |                                      | 128 |

## Selection of Error Detection Mechanisms

| 8.1 | Introduction |                                                     |     |

|-----|--------------|-----------------------------------------------------|-----|

| 8.2 | Specific     | c System Considered                                 | 131 |

| 8.3 | The Eff      | ects of Adding Error Detection Mechanisms           | 132 |

|     | 8.3.1        | The Non-Fault Tolerant System                       | 132 |

|     | 8.3.2        | Removal of Input Areas from the Memory Map          | 133 |

|     | 8.3.3        | Addition of a Recovery Routine                      | 134 |

|     | 8.3.4        | Forcing Restart Instructions into the Unused Areas  | 135 |

|     | 8.3.5        | Modifying the Program and Data Areas                | 135 |

|     | 8.3.6        | Detection Within the Software                       | 136 |

| 8.4 | Watchd       | og Timers                                           | 137 |

| 8.5 | Other H      | lardware Implemented Detection Mechanisms           | 139 |

|     | 8.5.1        | Wait State Recognition                              | 139 |

|     | 8.5.2        | Illegal Instruction Fetches                         | 139 |

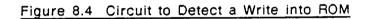

|     | 8.5.3        | Detection of a Write Outside RAM Areas              | 140 |

|     | 8.5.4        | Detection of Undeclared or Unused Instructions      | 141 |

|     | 8.5.5        | Voltage Level Detection                             | 141 |

| 8.6 | Choice       | of Mechanisms for General Systems                   | 143 |

| 8.7 | Summa        | ry                                                  | 144 |

|     |              | CHAPTER 9                                           |     |

|     |              | Development of a Facility to Test Redundant Systems |     |

| 9.1 | Introdu      | ction                                               | 145 |

| 9.2 | Fault In     | njection                                            | 146 |

| 9.3 | Genera       | tion of Interrupts                                  | 148 |

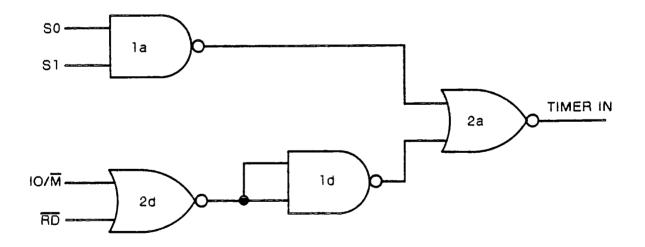

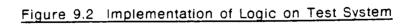

| 9.4 | Memory       | y Boundary on Test Program                          | 149 |

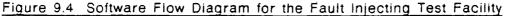

| 9.5 | Softwar      | e Design                                            | 152 |

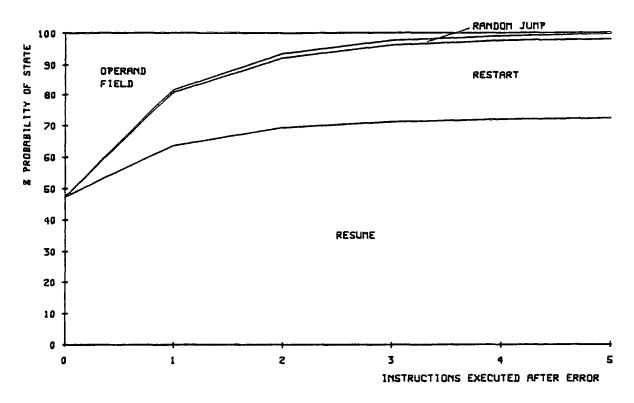

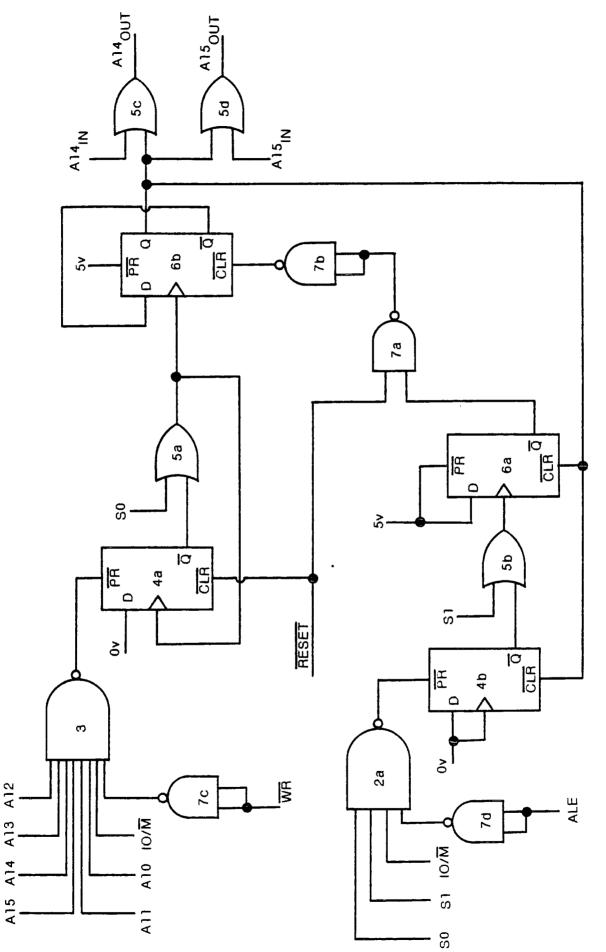

| 9.6 | Initial Results       | 154 |

|-----|-----------------------|-----|

| 9.7 | Possible Developments | 156 |

| 9.8 | Summary               | 157 |

## Conclusions

| 10.1       | Introduction                                                             | 158 |

|------------|--------------------------------------------------------------------------|-----|

| 10.2       | Practical Tests to Determine Fallure Mechanisms                          | 158 |

| 10.3       | Undeclared Operations in Microprocessors                                 | 159 |

| 10.4       | Execution Following an Erroneous Jump                                    | 160 |

| 10.5       | Recovery from Erroneous Execution                                        | 162 |

| 10.6       | Choice of Recovery Mechanisms                                            | 163 |

| 10.7       | Summary                                                                  | 164 |

| References |                                                                          | 166 |

| Figures    |                                                                          | 179 |

| Tables     |                                                                          | 211 |

|            | APPENDICES                                                               |     |

| Al         | Software to Test the Effects of Executing Undeclared<br>Operation Codes  | 222 |

| A2         | The Effects of Executing the Undeclared Operation Codes of the 8035/8048 | 226 |

| A3         | Instruction Set Parameters                                               | 236 |

| A4         | Equations for Transfers within a Program Area                            | 244 |

| A5         | Results of Execution in Unpopulated Memory Areas                         | 248 |

| A6         | Software for the Fault Simulation Test Facility                          | 250 |

## List of Figures

| Figure |                                                                              | Page No.     |

|--------|------------------------------------------------------------------------------|--------------|

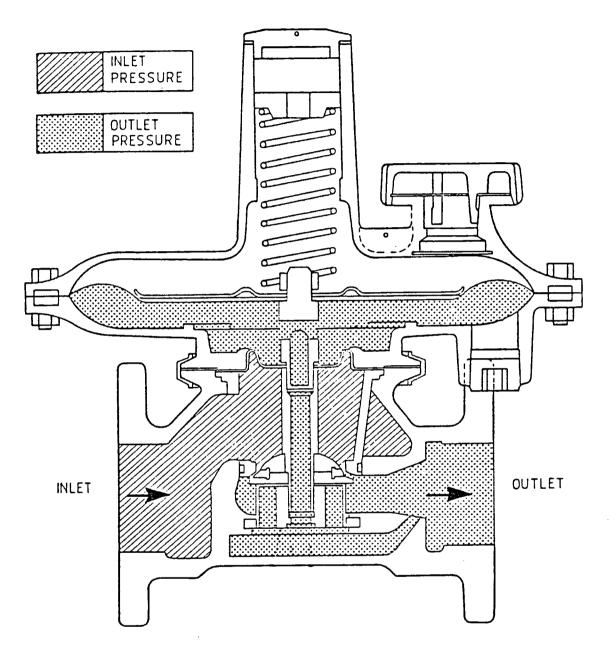

| 1.1    | Typical Diaphragm Operated Regulator                                         | 179          |

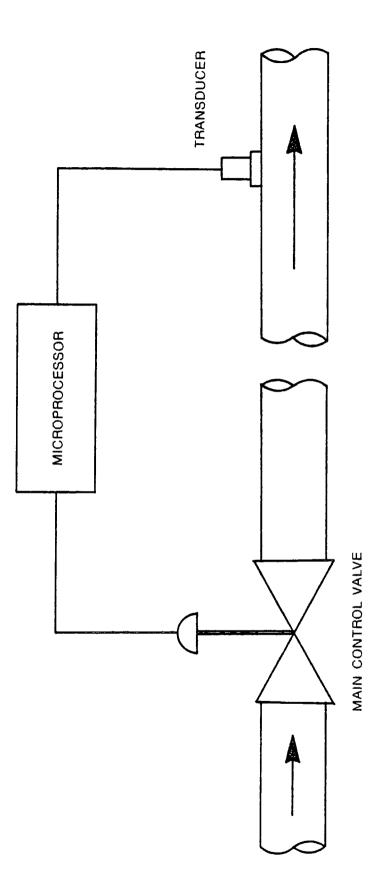

| 1.2    | Simple Microprocessor Control Arrangement                                    | 180          |

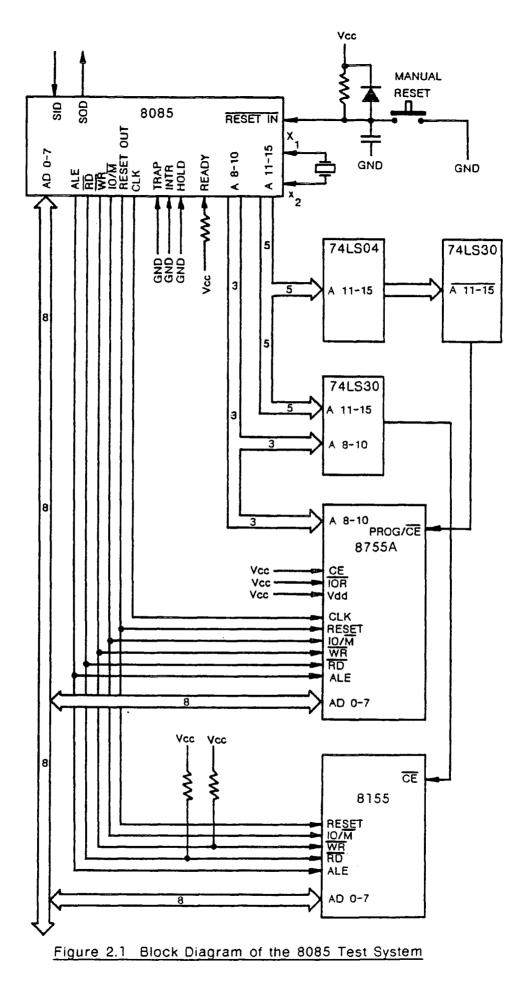

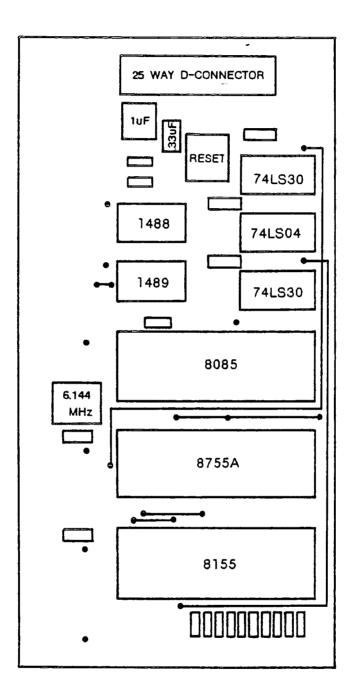

| 2.1    | Block Diagram of the 8085 Test System                                        | 181          |

| 2.2    | Layout of the Components                                                     | 182          |

| 2.3    | Logic Diagram of the Memory Decoding Circuitry                               | 183          |

| 2.4    | Circuit Diagram of the Test Power Supply Unit                                | 184          |

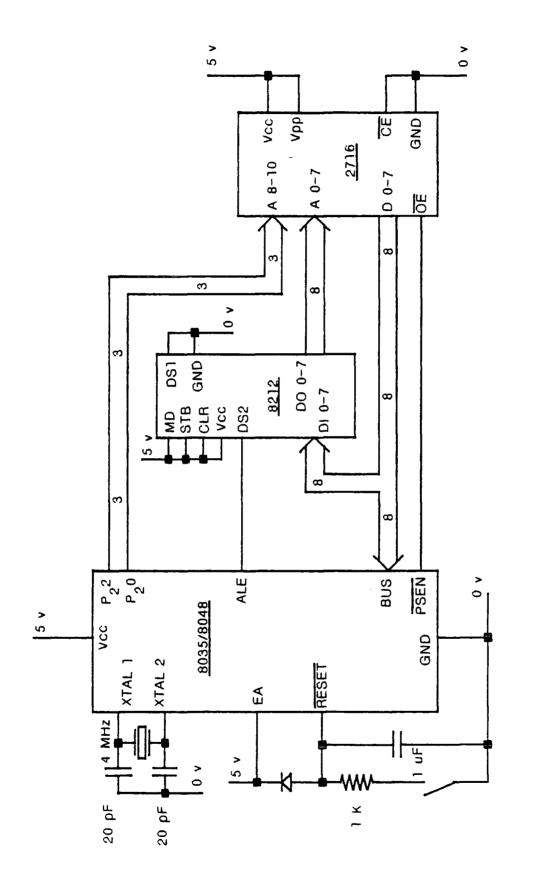

| 3.1    | Block Diagram of the 8035/8048 Test System                                   | 185          |

| 3.2    | Full Instruction Set for the 8048 Manufactured by Intel                      | 186          |

| 3.3    | Full Instruction Set for the 8048 Manufactured by NEC                        | 187          |

| 4.]    | Erroneous Execution in Data Areas for Various Processors                     | 188          |

| 4.2    | Flow of Execution in Random Data                                             | 190          |

| 4.3    | Recovery Improvements Obtained by Seeding Data Areas                         | 191          |

| 4.4    | Average Number of Instructions Executed with Seeded Data<br>Areas            | 191          |

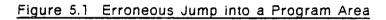

| 5.1    | Erroneous Jump into a Program Area                                           | 192          |

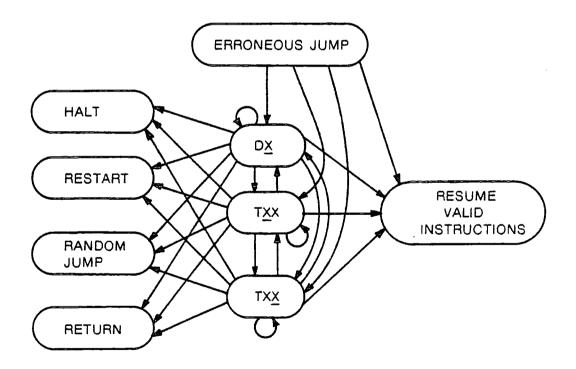

| 5.2    | Flow of Erroneous Execution in Program Areas                                 | 192          |

| 5.3    | Erroneous Execution in Program Areas for Various Processors                  | 1 <b>9</b> 3 |

| 5.4    | Simplified Flow of Execution in Program Areas                                | 194          |

| 5.5    | Erroneous Execution in Program Areas of the 68000                            | 195          |

| 6.1    | Common Memory Arrangements for the 8048                                      | 195          |

| 7.1    | Flow of Execution Between Different Memory Areas                             | 196          |

| 7.2    | The Effects of Adding Fault Tolerance to the Program Areas of the 8085       | 197          |

| 7.3    | The Effects of Adding Fault Tolerance to the Data Areas of the 8085          | 198          |

| 7.4    | The Effects of Adding Fault Tolerance to the Unused Memory Areas of the 8085 | 199          |

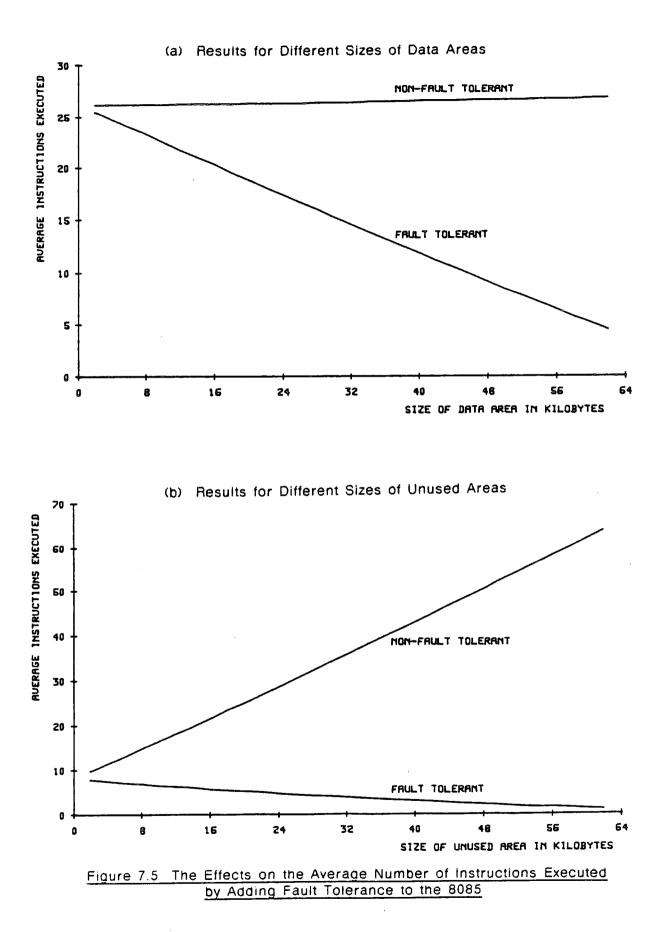

| 7.5 | The Effects on the Average Number of Instructions Executed by Adding Fault Tolerance to the 8085 | 200 |

|-----|--------------------------------------------------------------------------------------------------|-----|

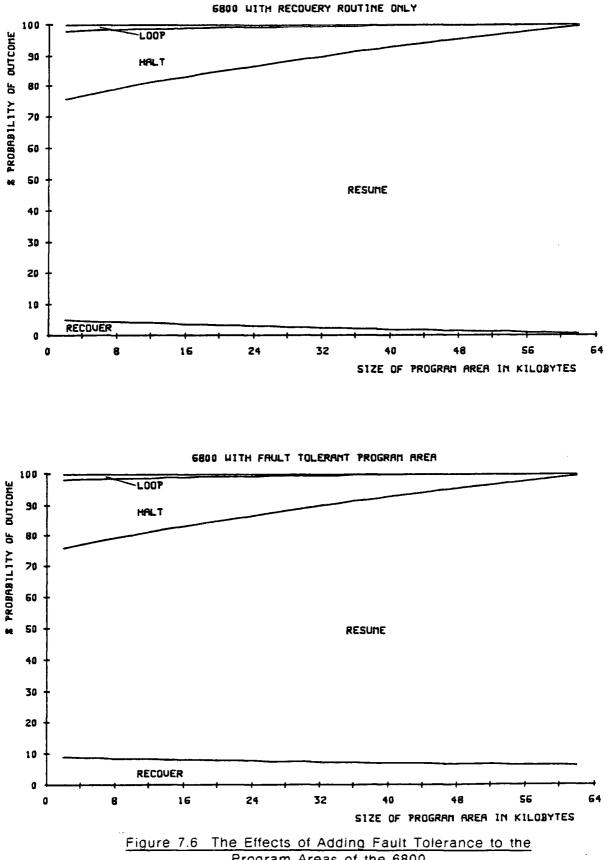

| 7.6 | The Effects of Adding Fault Tolerance to the Program Areas of the 6800                           | 201 |

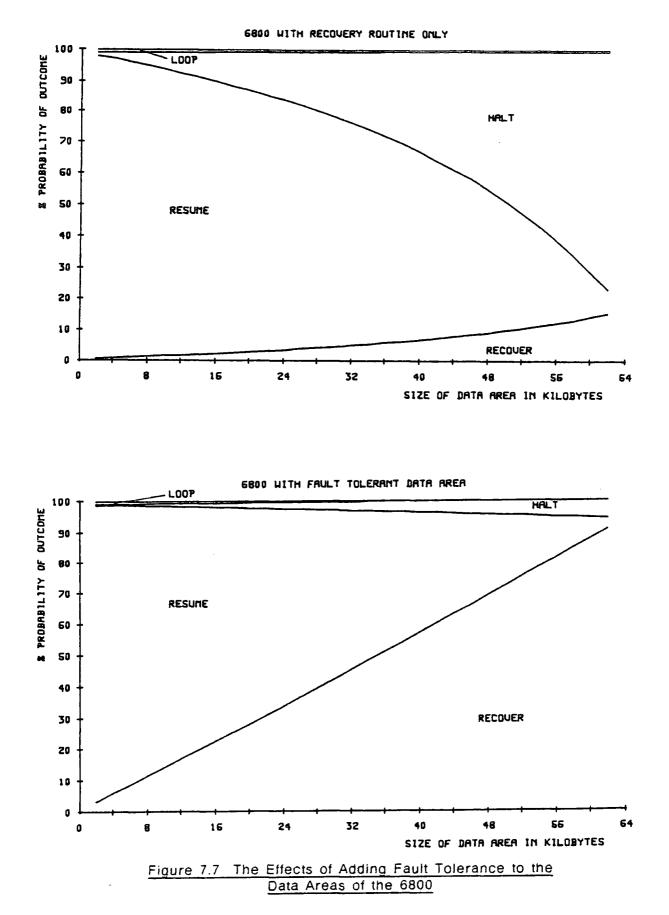

| 7.7 | The Effects of Adding Fault Tolerance to the Data Areas of the 6800                              | 202 |

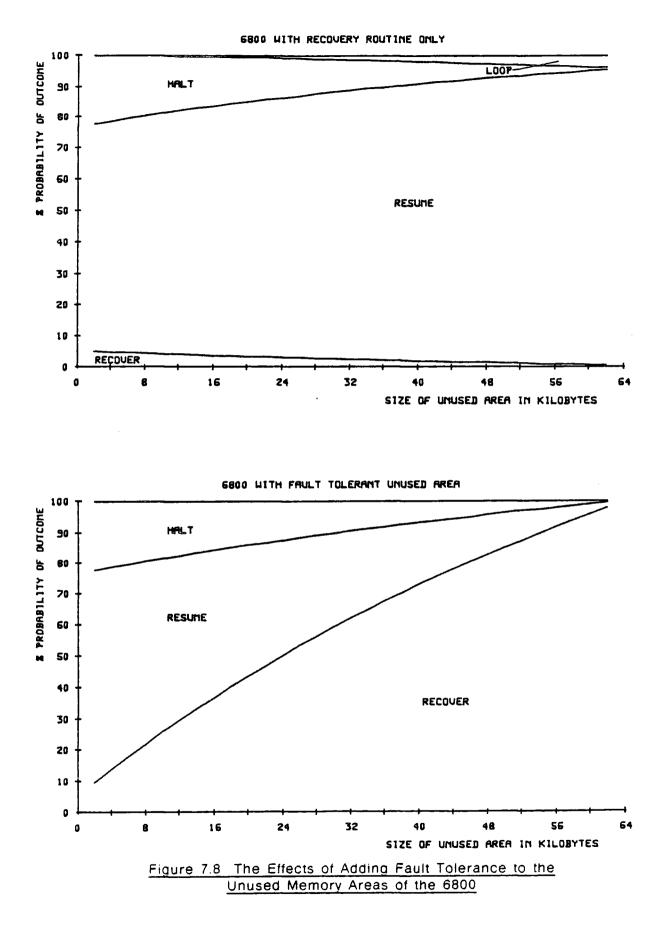

| 7.8 | The Effects of Adding Fault Tolerance to the Unused Memory Areas of the 6800                     | 203 |

| 7.9 | Probability of Data Corruptions in the 8085                                                      | 204 |

| 8.1 | Memory Map of the Specific System Studied                                                        | 205 |

| 8.2 | Wait State Recognition Circuit                                                                   | 206 |

| 8.3 | Circuit to Detect an Illegal Instruction Fetch                                                   | 206 |

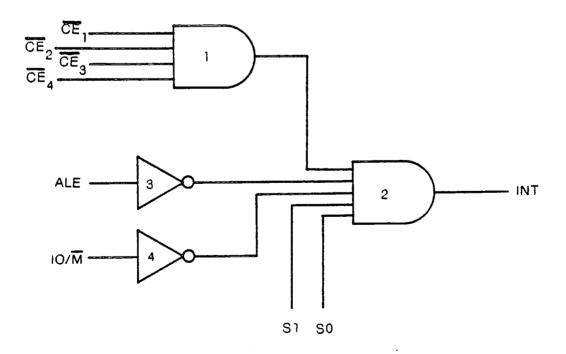

| 8.4 | Circuit to Detect a Write into ROM                                                               | 207 |

| 8.5 | Circuit to Detect a Write Outside RAM Areas                                                      | 207 |

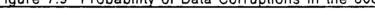

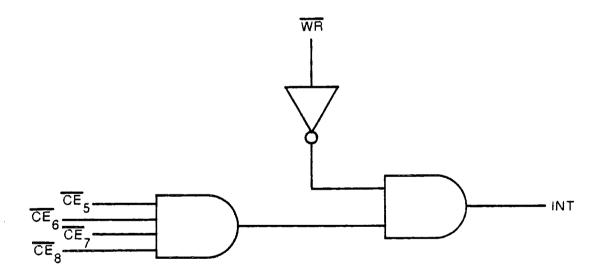

| 9.1 | Logic Required to Detect an Operation Code Fetch                                                 | 208 |

| 9.2 | Implementation of Logic on Test System                                                           | 208 |

| 9.3 | Circuit to Restrict Execution to 16 K of Memory                                                  | 209 |

| 9.4 | Software Flow Diagram for the Fault Injecting Test Facility                                      | 210 |

## List of Tables

| Table |                                                                                                                   | Page No. |

|-------|-------------------------------------------------------------------------------------------------------------------|----------|

| 1.1   | Reliability Requirements for Different Applications                                                               | 211      |

| 2.1   | Voltage Level at which Errors Occurred in 8155 RAM Chips                                                          | 212      |

| 2.2   | Location and Value of the First Errors Observed                                                                   | 212      |

| 2.3   | First Data Corruptions in RAM chip R5                                                                             | 213      |

| 2.4   | Length of Interruptions to the Test Supply, in Cycles,<br>Necessary to Cause Corruptions                          | 214      |

| 3.1   | Internal Memory of the 48-Series Microprocessors                                                                  | 214      |

| 4.1   | Results of Execution in Random Data                                                                               | 215      |

| 4.2   | Comparison Between Different Data Structures                                                                      | 215      |

| 5.1   | Comparison Between Processors for Erroneous Execution in Program Areas                                            | 216      |

| 5.2   | Comparison Between Actual Programs                                                                                | 216      |

| 5.3   | Results from the Simplified Analysis of Erroneous Execution in Program Areas                                      | 217      |

| 5.4   | Detailed Analysis of Modified Programs                                                                            | 217      |

| 6.1   | Probability of Different Outcomes After a Random Jump into<br>an Unused Memory Area of an 8085                    | 218      |

| 6.2   | Outcomes After a Random Jump into an Unused Memory Area of an 8085, Assuming Address Range C000 to FFFF is Unused | 218      |

| 6.3   | Transfer from Unpopulated Areas of an 8048                                                                        | 219      |

| 6.4   | Transfer from Partially Decoded Memory Mapped Input Ports                                                         | 219      |

| 7.1   | Data Corruptions in the 8085 Caused by Erroneous Execution                                                        | 220      |

| 8.1   | Erroneous Execution Under Different System Arrangements                                                           | 221      |

ł

#### List of Symbols and Abbreviations

| A/C      | Alternating Current                                                                  |

|----------|--------------------------------------------------------------------------------------|

| ACM      | Association of Computing Machinery                                                   |

| AFIPS    | American Federation of Information Processing Societies                              |

| AIAA     | American Institute of Aeronautics and Astronautics                                   |

| CCD      | Charge-Coupled Device                                                                |

| CE       | Chip Enable                                                                          |

| CMOS     | Complementary Metal Oxide Semiconductor                                              |

| D/C      | Direct Current                                                                       |

| DAG      | Demand Activated Governing                                                           |

| DX       | Op-Code Fetch from the Second Byte of a Double Byte Instruction                      |

| e        | The Exponential Function                                                             |

| EA       | External Access                                                                      |

| EMI      | Electromagnetic Interference                                                         |

| EMP      | Electromagnetic Pulse                                                                |

| ENSIMAG  | Ecole Nationale Superieure D'Informatique et de Mathematiques<br>Appliquees Grenoble |

| EPROM    | Erasable Programmable Read Only Memory                                               |

| FMEA     | Fault Mode Effect Analysis                                                           |

| FTCS     | Fault Tolerant Computing Symposium                                                   |

| HLT      | Halt Instruction                                                                     |

| I        | Number of Instruction Cycles or Transfers                                            |

| i.c.     | Integrated Circuit                                                                   |

| 1/0      | Input/Output                                                                         |

| IEE      | Institution of Electrical Engineers                                                  |

| IEEE     | Institute of Electrical and Electronic Engineers                                     |

| in. w.g. | Inches Water Gauge                                                                   |

| IRQ      | Interrupt Request                                                                    |

| J               | Joules                                                          |

|-----------------|-----------------------------------------------------------------|

| JMP             | Jump Instruction to a Non-Specific Location                     |

| к               | Number of Instructions Executed                                 |

| к               | Kilo-Bytes                                                      |

| kV              | Kilo-Volts                                                      |

| L               | Length of Instructions in Bytes                                 |

| In              | Natural Logarithm                                               |

| LSI             | Large Scale Integration                                         |

| LSTTL           | Low Power Schottky Transistor Transistor Logic                  |

| mA              | Milli-Amperes                                                   |

| mbar            | Milli-bars                                                      |

| mJ              | Milli-Joules                                                    |

| ms              | Milli-seconds                                                   |

| MHz             | Mega-Hertz                                                      |

| mm              | Millimetres                                                     |

| mV              | Milli-Volts                                                     |

| MTBF            | Mean Time Between Failures                                      |

| N               | Number of Instructions Executed                                 |

| N <sub>B</sub>  | Total Number of Bytes in the Program Area                       |

| N <sub>BE</sub> | Expected Number of Data Bytes Read                              |

| N <sub>CJ</sub> | Number of Conditional Jump Instructions in the Instruction Set  |

| N <sub>DA</sub> | Actual Number of Data Bytes in the Memory Map                   |

| N <sub>DI</sub> | Number of Double Byte Instructions in the Program Area          |

| N               | Total Number of Instructions in the Program Area                |

| NJ              | Number of Bytes Interpreted as Jumping Instructions             |

| Nĸ              | Number of Execution Sequences of K Instructions                 |

| N <sub>LJ</sub> | Number of Bytes Interpreted as Jumping Instructions of Length L |

| N <sub>LNJ</sub>        | Number of Bytes Interpreted as Non-Jumping Instructions of Length L                  |

|-------------------------|--------------------------------------------------------------------------------------|

| N <sub>NJ</sub>         | Number of Bytes Interpreted as Non-Jumping Instructions                              |

| N <sub>PB</sub>         | Number of Program Bytes which Appear in the Memory Map                               |

| N <sub>RST</sub>        | Effective Number of Restart Instructions                                             |

| NS                      | Total Number of Execution Sequences                                                  |

| N <sub>T</sub>          | Total Number of Possible Op-Codes                                                    |

| N <sub>TB</sub>         | Total Number of Bytes in the Memory Map                                              |

| N <sub>TI</sub>         | Number of Triple Byte Instructions in the Program Area                               |

| NASA                    | National Aeronautics and Space Administration                                        |

| NATO                    | North Atlantic Treaty Organisation                                                   |

| NBAV                    | Average or Expected Number of Bytes Read Before a Jump                               |

| NEC                     | Nippon Electric Company                                                              |

| NIAV                    | Average or Expected Number of Instruction Executed Before a Jump                     |

| NIE                     | Expected Total Number of Instructions Executed                                       |

| NIL                     | Upper Limit on the Number of Instructions Executed                                   |

| NMI                     | Non-Maskable Interrupt                                                               |

| NMOS                    | N-Channel Metal Oxide Semiconductor                                                  |

| NMR                     | N-Modular Redundancy                                                                 |

| NOP                     | No Operation                                                                         |

| NRAV                    | Average Number of Instructions Executed Before Resuming Valid<br>Instruction Fetches |

| ns                      | Nano-Second                                                                          |

| op-code                 | Operation Code                                                                       |

| P <sub>CJ</sub>         | Probability that a Conditional Instruction will cause a Jump                         |

| PD                      | Probability of Entering a Data Area                                                  |

| <sup>Р</sup> D <u>X</u> | Probability of Entering the Operand Field of a Double Byte Instruction               |

| PE                      | A Proportion of the Total Errors                                                     |

| Probability of Entering an Area of Input Data                           |

|-------------------------------------------------------------------------|

| Probability of Entering the Input Area Twice                            |

| Probability of a Loop after Entering the Input Area Twice               |

| Probability of Interpreting a Jump Instruction                          |

| Probability of Forming a Loop in the Data Area                          |

| Probability of Forming a Loop in the Input Area                         |

| Probability of Forming a Loop in the Unused Area                        |

| Probability that Particular Data is Not Corrupted                       |

| Probability of Executing a Given Number of Instructions or More         |

| Probability of Interpreting a Non-Jumping Instruction                   |

| Probability of Entering a Program Area                                  |

| Probability of Resuming Valid Instruction Fetches                       |

| Probability of Interpreting a Restart Instruction                       |

| Probability of Entering the Second Byte of a Triple Byte<br>Instruction |

| Probability of Entering the Third Byte of a Triple Byte<br>Instruction  |

| Probability of Entering an Unused Memory Area                           |

| Probability of Entering the Unused Area Twice                           |

| Probability of a Loop after Entering the Unused Area Twice              |

| Probability of a Transfer from an Unused Area to Memory Area Xi         |

| Probability of Entering an Operand Field in the Program Area            |

| Probability of Reaching a Particular Final State                        |

| Probability of Transfering from Memory Area XI to an Unused Area        |

| Probability of Transfering from Memory Area Xj to Memory Area Xi        |

| Probability of Interpreting a Restart in an Operand Field               |

| Pico-Farads                                                             |

| Programmable Read Only Memory                                           |

|                                                                         |

xiv

| RAM          | Random Access Memory                                            |

|--------------|-----------------------------------------------------------------|

| RC           | Resistor and Capacitor                                          |

| RET          | Return Instruction                                              |

| RFI          | Radio Frequency Interference                                    |

| ROM          | Read Only Memory                                                |

| RST          | Restart Instruction                                             |

| SDK          | System Design Kit                                               |

| SEC/DED      | Single Error Correction/Double Error Detection                  |

| SERC         | Science and Engineering Research Council                        |

| SPC          | Jump Instruction to a Specific Location                         |

| SSI          | Small Scale Integration                                         |

| TMR          | Triple Modular Redundancy                                       |

| т <u>х</u> х | Op-Code Fetch from the Second Byte of a Triple Byte Instruction |

| тх <u>х</u>  | Op-Code Fetch from the Third Byte of a Triple Byte Instruction  |

| uF           | Micro-Farad                                                     |

| UPS          | Uninterruptible Power Supply                                    |

| us           | Micro-Second                                                    |

| US           | United States                                                   |

| v            | Volts                                                           |

| Xf           | Represents a Particular Final State                             |

| Xi           | Represents a Particular Memory Area                             |

| Xj           | Represents Each of the Four Different Memory Areas              |

No material contained in this thesis has previously been submitted for a degree in this or any other university.

•

7

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

#### Introduction and Review of System Reliability

#### 1.1 The Need for a Reliable Controller

With the conversion from town gas to natural gas, the supply to the consumer has changed from a large number of isolated networks to one fully integrated distribution system. This system is connected to the supplies of natural gas in the North and Irish seas, and transports it around the country in large diameter pipes (up to 1050mm), at high pressures (up to 70 bar). The pressure is reduced in stages into smaller diameter pipes until it is at a safe level to supply to the consumer.

An analogy can be drawn with the National Grid for electricity supply, where voltage corresponds to pressure, and current corresponds to flow rate. However, unlike the electricity system, gas can and must be stored within the network. This is necessary because the supply is obtained at a constant rate from the gas fields, whereas the demand by the consumer varies both throughout the day and throughout the year. Also any peak demand within a particular area must be supplied locally due to the time delay in transporting gas through the system. Therefore the network presents a complex arrangement requiring sophisticated control.

At the high pressure end of the system large volumes of gas are being handled, and small increases in efficiency result in significant financial savings. Also failure at this level is likely to affect a large number of consumers, and this justifies high expenditure on control and safety equipment. As the pressures reduce, the quantities and hence the value of gas being handled becomes less, and high expenditure on control equipment is not justified. A low cost controller is therefore required and this is the aim of the current research.

At the low pressure end of the system, accurate pressure control is required for several reasons. Much of this part of the network is constructed from short sections of cast iron pipes laid many years ago, and it is estimated that there are almost 60 million joints. Small leaks can occur but rarely create a safety problem. However, taken collectively they represent a substantial loss of revenue. Therefore methods which reduce this leakage can have both financial and safety benefits. An extensive programme to replace old sections of the network has been in progress for several years and has cost hundreds of millions of pounds. Meanwhile a reduction of pressure within the system provides significant benefits by reducing leakage, and also repair and maintenance costs. it can also postpone eventual reinforcement of the network necessary to cater for increased demand, thus saving revenue equivalent to borrowed capital interest.

Obviously the pressure cannot be reduced below a certain level or the gas would not reach the consumer. This would lead to the possibility of air entering the pipework producing a potentially hazardous condition. Low pressures can also affect the efficiency of some appliances. For these reasons a statutory minimum pressure has been set. This is **5** in. w.g. (inches water gauge) which is equivalent to the height of a column of water that the pressure can support, and is approximately **12.3** mbar. Clearly the aim is to supply the consumer with the minimum acceptable pressure throughout the daily load cycle.

#### 1.1.1 Present Mechanical Control

Traditionally, an entirely mechanical approach has been adopted for the control of the low pressure distribution system. The use of diaphragm operated gas regulators, as shown in figure 1.1, is widespread, with

approximately 17,000 installed throughout the country. They aim to reduce the pressure to a steady value independent of the flow rate. This is achieved by feeding back the down-stream pressure into a chamber under the diaphragm. The force on the diaphragm is balanced by a spring or a series of weights. Any imbalance causes the valve to open or close and has the effect of increasing or reducing the down-stream pressure. By adjusting the loading, different output pressures can be maintained. However, this arrangement does not give perfect pressure control. The pressure tends to flow rate increases, and this is known as the 'droop' fall as the characteristic of the regulator.

So far only the pressure at the outlet of the regulator has been considered. However, the consumer may be over a mile away from the outlet and therefore, by simple fluid mechanics theory, a pressure drop will exist along the pipework and will be proportional to the square of the flow rate. Consequently, with the simple regulator described above, it is necessary to set the output pressure at a higher level to guarantee that the consumer will be supplied with at least the minimum statutory pressure, at times of Clearly this will result in a pressure well above the peak demand. statutory minimum at other times. This is refered to as the 'over pressure' of the system, and has a maximum value of the sum of the regulator droop, the pipework losses and a safety margin, as the flow rate The safety margin is included to allow back-up equipment to reduces. intervene if an abnormally low pressure is detected. Obviously the aim is to reduce the 'over pressure' to a minimum.

The above example considers only one regulator and one consumer, in reality the situation is in fact far more complicated. Low pressure networks can be fed by more than one regulator and supply several thousands

of consumers. Due to varying demands from the system, the low pressure point may not always be at the same physical location. This makes effective control even more difficult.

In the past, methods have been devised to provide automatic changes in the set point of a regulator to try and follow the pattern of demand. However, these do not operate directly on the district pressure, but on other parameters which are associated with demand, such as the time of day or the ambient temperature. Both of these parameters are not strongly linked with demand but control based on them has provided some savings. A third approach has used the flow through the regulator to adjust the set point, and has proved most successful. This is commonly know as demand activated governing (DAG).

Spearman (98) has reported a number of DAG schemes which have all shown significant savings in repair and maintenance costs. They have provided DAG by mechanical means but have several disadvantages. At least three additional valves and a substantial amount of extra pipework is required. A complex setting up and commissioning procedure is necessary to ensure optimum performance, and this has to be repeated periodically to allow for changes in the network or demand. Therefore there is scope for further improvements.

#### 1.1.2 Future Micro-Electronic Control

To overcome the problems with mechanically implemented DAG mentioned above, and to allow for other developments, it has been proposed that micro-electronic techniques could be applied to the control of gas pressure. A simple arrangement for such a system is shown in figure 1.2. It contains a microprocessor which reads the remote low pressure point from a transducer, and activates the valve to maintain a steady supply. To

ensure overall system safety and availability, all three parts must be both reliable and must be fail-safe.

The valve could be operated by a simple solenoid providing only open and closed positions. The pressure would then be controlled by pulse width modulation on the supply to the solenoid. Although this is a simple solution, it tends to be very unreliable due to the large number of operations needed to maintain a steady pressure. Another disadvantage is that failures in either of the normal operating positions produce dangerous conditions.

A better solution would be to use a motorised valve. This will be more reliable as actuations are only required when the pressure changes, resulting in less mechanical wear. However, the response under fault conditions will be poor.

The arrangement which has been used in initial trials with digital control utilises an indirect approach. The main pressure reduction regulator is retained in the traditional configuration, but with the set point controlled by the microprocessor. This provides a much better solution as failure of the microprocessor system causes control to revert to mechanical pressure regulation.

To adjust the set point a method of increasing and decreasing the spring loading within the regulator is required. Two prototype arrangements have been built. The first uses a stepper motor to adjust the length of the spring and hence the loading. The second uses two solenoid valves to feed up-stream or down-stream pressure under a second diaphragm which acts on the spring to adjust the loading. The solenoid system is preferred as it can be arranged to 'fall safe' on power failure, by setting the regulator to its maximum set point. Burrow (20) states that generally

the 'fail safe' approach has been neglected. It is much cheaper to implement than 'fail operational' designs, and is clearly acceptable in this application as failure will only result in a reversion to a high pressure setting within the network. The 'fail safe' approach still ensures that no area drops below the statutory minimum pressure. The stepper motor, however, will stay at its current position during a power failure. As mentioned above, this reverts to mechanical control, but, if demand increases, the low pressure point will fall below the statutory minimum.

Initial trials have been carried out with both arrangements. As mentioned previously, the ideal solution is to monitor the remote low pressure point and relay the information back to the controller, and this requires some sort of telemetry link. The use of hard-wired links is expensive, and therefore other methods of transmitting the data are being investigated. However, a system operating in the United States, described by Reese (84), uses telemetry and has shown that the cost of the equipment can be recovered within the first year, due to the reduction in lost gas alone.

These initial trials have shown that micro-electronic control of the gas network is both feasible and economic. Another area to which it could be applied is the control of storage facilities. As indicated previously, it is necessary to store gas within the network and a number of arrangements have been developed such as gas holders, liquefaction plants and underground caverns. Recent interest has been directed towards the use of the medium pressure part of the network as a means of storage, and can be achieved by increasing the pressure and thus compressing the gas. This is known as 'line-pack' and is possible in this particular part of the

network because the pipework is relatively new and does not suffer from leakage.

very stringent safety requirements, it was Due to the felt that further work should be carried out to investigate methods of increasing the reliability of these control systems. British Gas has had long term experience with mechanical regulators, and, as a result, has in-depth knowledge and expertise on their operation. This has led to the development of very reliable equipment. With regard to the control of the low pressure network, micro-electronics has only recently been used by the Therefore, this work is aimed at investigating methods of Corporation. increasing the reliability of the micro-electronic parts of the systems.

#### 1.2 Source of Failures

All equipment can fail, and usually does so in a variety of different ways. In a complex electronic system the cause of failure can be due to design errors, component failures or to environmental effects. In microprocessor based systems, design errors can occur in both the hardware and software, and can be introduced at the specification, implementation or construction phases of a project. Shooman (92) gives an example of a data acquisition system where, over a nine month period, nearly half the failures were due to software errors. At the specification stage errors can be made due to an insufficient knowledge of the system to be controlled, or by an incomplete description of the required response under The importance of these errors is emphasised by all operating conditions. Soi and Gopal (97) who suggest that nearly 60% occur at this stage in the software. At the implementation stage, the choice of the wrong type of components in hardware, or the wrong algorithm in software, can lead to failure. Finally, errors can be made during the construction of hardware

or the coding of software.

Components can fail due to a number of different failure mechanisms, and generally they follow the familiar 'bath-tub' curve. It shows a high failure rate at the beginning of their life due to manufacturing defects. This is followed by a period of constant failure rate, due to random which is normally considered to effects, be the useful life of the component. After this period the failure rate increases again due to wear A description of the types of failures observed in electronic out. components is given by Doyle (31), and a study of microprocessor devices is presented by Hnatek (47) who describes a number of physical failure mechanisms and how they can be detected.

The correct operation of electrical and electronic systems can be disturbed by environmental conditions. In analogue devices it can result in noisy signals, but in digital equipment severe disruption of the processing sequence can occur. Sources of disruption include radio frequency interference (RFI), electromagnetic interference (EMI), radiation effects, static discharges and power supply variations.

Whallen et al (113) have shown that RFI can disrupt digital circuits by changing their state. Sources of EMI in high voltage substations are listed by Pellegrini et al (79), and most are due to various forms of switching. The effects of lightning are also considered. May and Woods (64) highlight the problem of alpha particle interaction originating from packaging material. This has become a problem with the development of higher density chips, and affects most devices. General radiation effects on semiconductors have been investigated by Sexton et al (90), and they have shown that device parameters drift with dosage.

Faults can be either permanent or temporary. Permanent faults occur

as a result of catastrophic failure of a component or subsystem, and also from inherent design errors. Some sources of temporary faults are described by Ng and Avizienis (70) and include component drifts around the limits of their specifications, and environmental factors. However, the errors produced by permanent faults may appear temporary. For example, a single node stuck at zero can only produce an error when it should be set at one, and this is illustrated by Gunther and Carter (39). Also a part of the circuit which is infrequently used may not cause any errors until it is exercised. Goldberg (37) indicates that some design faults, such as timing problems, can appear to be induced environmentally, and may be difficult to distinguish. For these reasons faults can remain undetected for а considerable length of time.

McConnel et al (61) draw a distinction between intermittent errors and Intermittents occur as a transient errors. result of an underlying will periodically permanent fault and reappear, whereas а particular transient will occur only once. Ball and Hardle (5) indicate from practical experience that 90% of field failures are intermittent and are particularly difficult to isolate.

Most reliability work in the past has considered only stuck at faults. More recently bridging faults have been considered where electrical contact is made between adjacent tracks, and these are described by Kodandapani and Pradham (52). Toschi and Watanbe (103) state that soft fails in memories can also be due to data patterns, timing and read/write sequencing. All produce and particularly difficult these intermittent errors are to identify.

#### 1.3 Methods of Increasing Reliability

There are two complimentary approaches available to increase

reliability and these are described by Avizienis (4). The first attempts to eliminate all sources of failure and is known as the fault intolerance approach. The second recognises that failures will occur, and attempts to mask their effects by the use of redundancy, this is known as fault tolerance. To achieve very high reliability a combination of both these approaches is necessary, and can be applied to each of the three sources of failure described above.

#### 1.3.1 Reducing Failures due to Design Errors

Errors in hardware design have been reduced to a very low level by the implementation of rigorous procedures at all stages. Complex computer programs are used to analyse and simulate the hardware to check for a number of faults. Hazard and race conditions in logic circuits can be detected, interconnections can be checked for the correct routing, and loading on each node can be analysed to ensure, for example, that maximum fan-out is not exceeded. Once the hardware is constructed, thorough testing is carried out to verify correct operation.

Fault free design is more easily achieved due to recently developed integrated circuits which have themselves been designed for simple interconnection. This reduces the amount of work necessary by the system designer, but increases the effort required by the chip designer. Design errors within large scale integrated circuits (LSI) are more likely to occur due to the increased complexity of these devices. This problem is highlighted by Sequin (89).

An advantage with microprocessor based hardware is that the basic circuit can be used for many applications. This reduces the possibility of introducing errors into new projects. Software, however, has been treated in a different manner in the past, and remains a serious source of failure.

This is due mainly to the unlimited way in which software can be arranged and that, in almost all cases, new code is written for each application.

Recently much more emphasis has been placed on software reliability. This is due to the increased proportional cost of the software within systems, which results from increased complexity and reduced hardware costs. Greenspan and McGowan (38) state that 70% of US Air Force computing expenditure was for software in 1972, and this is expected to rise to 90% bv 1985. Both fault intolerant and fault tolerant approaches have been investigated to alleviate this problem. The advantages of structured programming are widely recognised, making programs easier to read and understand, and thus simplifying the process of identifying errors. It tends to force the programmer to divide the problem into a series of modules. Nelson (66) reports on analyses which have shown that the error rate increases with the routine size. This is because smaller modules are far more easy to understand and test, and therefore methods which enforce the use of smaller modules will increase reliability.

As well as the language itself, the environment under which programs are developed is also important in enabling efficient testing and isolation of errors. For these reasons the United States Department of Defense has sponsored an extensive project to design a new language (Ada), and its associated development environment. Programming in Ada is more difficult than other languages due to tight restrictions on syntax and variable types. But it facilitates the early detection of errors at both compile and run time, reducing the overall development time. It also makes the code easier to understand and modify. This is particularly important as Dunn and Uliman (32) have shown; in badly written packages more errors can be introduced than are removed at the debugging stage, making the whole

system less reliable.

The fault tolerant approach recognises that bugs will remain in the software, and two methods of counteracting their effects have been proposed. Randell (83) suggests the use of recovery blocks. In this method an acceptance test is executed after each program module, and, if the results fail the test, an alternate algorithm is used. This process can be repeated until an acceptable set of results is obtained, or until alternate algorithms have been tried. In the latter case all the а different form of recovery must then be used. A practical example of recovery blocks in action is given by Anderson and Kerr (1).

The other approach is called N-version programming as described by Chudleigh (23). In this case all versions of a particular program module are executed and a majority vote is taken on all the results.

Both methods have their own advantages and disadvantages. For example, the recovery block procedure operates much faster in the absence of errors, but, to enable accurate error detection, complex acceptance tests are sometimes necessary. These can themselves be a source of error, as can the voting software in N-version programming. However, in the latter case the critical software is much smaller and will be less susceptible to errors. A comparison between the two techniques is given by Wei (109). He concludes that N-version programming is better than the use of recovery blocks because of problems with acceptance tests.

#### 1.3.2 Reducing Failures due to Component Malfunctions

Unlike design errors which can, theoretically, be eliminated from a system, component failures are always possible. In the past both fault tolerant and fault intolerant approaches have been favoured at different times. In the early days of digital computers thousands of valves were

used in each machine, and reliability was poor due to the high failure rates of the components. Redundancy was necessary to improve performance. With the advent of the transistor and the subsequent development of the integrated circuit, less emphasis has been placed on redundancy due to the vast increase in the reliability of the components. Examples of fault tolerance in early computers is given by Carter and Bouricius (21).

In more recent years some computer applications have required even higher levels of reliability. These include cases where human life is involved or large financial losses are incurred on failure, such as manned and unmanned space flight, hospital life support equipment and aircraft control. Attempts have been made to increase still further the reliability of components used in these applications. Significant improvements can be achieved by screening out weak devices, and Pappu et al (75) describe methods of detecting them. Burn-in is a popular technique whereby equipment is operated at elevated temperatures before actual use. Even with these improvements it has again been necessary to use the fault tolerant approach.

A popular arrangement has been the use of triple modular redundancy (TMR) which was first proposed by Von Neumann in 1956 (105). TMR consists of three identical modules, each performing the same function, which are connected to a majority voting circuit. If one module fails, the voting circuit masks any errors by outputting the values from the other two. Clearly this requires at least three times as much hardware as a simplex system.

In many cases the extra cost could not be justified, and, in these cases, dual systems have been used. They can be configured in a number of ways. In a cold standby arrangement, a second module is maintained in an

inactive state and requires initialisation before use. Lonn et al (58) describe a hot standby system where the second module continually monitors the process, ready to take immediate control. In many control applications the switch over to the standby system is performed manually after the activation of an alarm. In a duplex arrangement both modules perform identical operations and comparisons are made between their outputs. This provides simple error detection but does not readily indicate which module is in error.

As the cost of hardware has fallen and the requirements of reliability have increased, more complex arrangements have been developed. N-modular redundancy (NMR), where N represents the number of modules, has been proposed in cases where the reliability of TMR is considered insufficient. Examples using four channels have been constructed for the F-8 fighter aircraft described by Bumby (19), and for NASA's space shuttle described by Gelderloos and Wilson (36). In both cases the requirement is for safe operation in the presence of two failures.

An important property of these systems is that reliability is drastically reduced after each failure. For example, TMR is at least twice as unreliable as a simplex system after a single failure, and therefore it is important to repair failed modules quickly. In closed systems, such as unmanned spacecraft, manual repair is not possible. NMR can be used to survive severai failures by increasing the number of modules. Alternatively a number of standby spares can be provided so that the system can reconfigure itself in order to substitute a failed component or subsystem for a good one. This effectively provides automatic repair.

Wensley (110) proposes the use of a number of loosely connected units. with the fault tolerance implemented by software. In this way critical

tasks can be executed on several units with voting carried out in the program. This arrangement allows dynamic reconfiguration to eliminate faulty units after they have been identified. This sort of arrangement is commonly used in telephone switching equipment, and has also been proposed for aircraft applications by Hamill and Phillips (40).

Hybrid systems utilising a combination of the above architectures to exploit their individual advantages are becoming more popular. For example, Hopkins (48) describes a processing concept for space vehicles which uses duplex, TMR and standby sparing.

#### 1.3.3 Reducing Failures due to Environmental Effects

Significant improvements in reliability can be obtained by reducing the effects of environmental phenomena. The fault intolerant approach does this by providing a stable local environment for the equipment. Basu (9) and Williamson (115) give comprehensive details of possible steps for reducing the effects of noise, and indicate that the design of the system enclosure is of great importance. In the United States the level of EMI emitted from digital equipment is restricted. To meet these requirements good shielding is necessary, which not only reduces emissions, but also reduces the susceptibility of the equipment from external EMI.

Boothman (14) describes methods of designing cabinets for optimum shielding, and suggests the use of metals, metalised coatings on plastics or conductive plastics. Ideally a continuous unbroken metal enclosure forming a Faraday cage is preferred in order to eliminate most electrical interference. However, all systems need to communicate with the outside world and most require an external power supply. Therefore apertures in the enclosure are inevitable and Boothman shows the importance of both their size and location relative to the internal components. Rostek (86)

suggests a 'Rule of Thumb' of restricting maximum openings to 25mm for each nanosecond rise time of the digital circuits.

He also emphasises the importance of conducted interference on power supply and signal lines and suggests the use of comprehensive filtering. Routing of power and signal cables and the quality of their sheilding is also important, and is discussed by Dick (30). With the development of fibre optics, data transmission can be made far more secure. Dyer (33) recommends their use, especially in military equipment, for immunity of both EMI and the more damaging EMP generated by nuclear explosions.

As well as EMI superimposed on the power supply, brown-outs and blackouts can occur, where the voltage is reduced or lost completely over a period of time. In these cases filtering alone is not sufficient. These occur frequently and have the development problems led to of uninterruptible power supplies (UPS). A number of arrangements have been developed for large installations, with the standby power source provided by batteries or diesel generators. These are described by Sulway (99), and in these cases an A/C supply is maintained.

In smaller systems batteries alone can directly provide the necessary This has led to the development of higher capacity minature D/C levels. batteries, such zinc/air type described by Pytches as the (82). Rechargeable batteries can be trickle charged when the external source is available, ensuring that they are in good condition when required. This sort of arrangement has been used in the NATO III communication satellites described by McKinney and Briggs (62). Solar cells provide the external source to charge several sets of batteries, and are required for peak demand and to ensure continuous operation during solar eclipses.

Other environmental factors such as mechanical shock and vibration

must also be taken into account, and can usually be suppressed by suitable Thermal effects are also important. It is widely recognised that damping. high component temperature leads to an increased failure rate. It can also cause a general drift in component properties, therefore, methods which restrict temperature such as cooling fins or convective fans will produce However, the use of fans drawing air in from outside the cabinet benefits. can have detrimental effects, since openings are required to allow for the passage of air, and these introduce the possibility of increasing the susceptibility to EMI as described above. It also allows moisture, solid particles and corrosive substances to enter the enclosure. Filtering can be used to reduce the possibility of contamination, but in certain cases a totally sealed unit is preferred.

Shielding is effective in many cases but does not prevent all external interaction. Ziegler and Lanford (117) have shown that even half a metre of concrete has little effect on reducing interference to charge-coupled devices (CCD) from certain types of cosmic rays. However, they do suggest that the orientation of the devices can be used to reduce the problem. Shielding is also ineffective against internally generated interference and alpha particle interaction originating from package material.

In these cases the components themselves can be designed to be less susceptible to certain disturbances. Brodsky (16) suggests methods of improving RAM's against alpha particle attack, and Kim et al (51) describe methods of hardening devices against general forms of radiation. Certain device technologies are inherently less susceptible to radiation than others. Barton et al (8) show that bipolar devices are superior to complementary metal oxide semiconductors (CMOS), which in turn are better than N-channel devices (NMOS).

As described above, fault intolerance can be used to reduce the influence of environmental phenomena. In general, great improvements can be obtained for a small cost if careful consideration is taken at the design stage. Additional improvements can be made but usually involve ever increasing costs. In such cases the fault tolerant approach is worth while.

Environmental disturbances can either cause permanent or temporary With the precautions taken above, damage will be damage to systems. reduced and transient effects will predominate. The redundancy techniques provided mentioned in previous section will be effective the that simultaneous faults in different channels do not occur. Much work has been aimed at developing techniques to detect and correct errors in memory Most techniques rely on error detection and correction codes. systems. such as those proposed by Hamming (41). Extra bits of information are added to each of the data words and these can indicate which particular bit is in error if a fault occurs. Levine and Meyers (57) indicate the number of check bits required for single error correction and double error detection (SEC/DED). However, if more than two bits fail they may not be detected or an erroneous correction may be made. In these cases Walker et al (108) describe a memory system which is capable of masking off failed bits to survive multiple faults.

Time redundancy is a useful means of counteracting transient faults. This method uses the re-execution of a program segment at a later time, in the anticipation that transient disturbances will have subsided. A number of different stategies can be adopted. For example, a particular segment could be executed repeatedly until two or three consecutive results are the same. Alternatively the segment could be executed a fixed number of times

and a majority vote taken. This is similar to N-version programming with all versions identical.

Rollback techniques are another effective defence against transient In this case the program periodically saves information about its faults. This is known as a checkpoint. When an error is detected, current state. execution can then be restarted at one of these points. O'Brien (72) studies several checkpointing stategies, and he recognises that in control applications the speed of recovery is usually critical, requiring the frequent insertion of rollback points. He shows that a large overhead is necessary with regard to both execution time and memory space. To limit overheads, a checkpoint should be saved when the critical data is at a minimum, and this will normally occur at the end of a calculation. it is recommended that a checkpoint should be saved at least once during each control loop.

A disadvantage of this technique is that added complexity in the software is both costly and prone to error. Barigazzi and Strigini (6) suggest that the setting of recovery points should be transparent to the programmer to overcome these problems. This has been implemented on the Cm<sup>\*</sup> computer by Siewiorek (93). Checkpointing and rollback are similar to the use of recovery blocks, where instead of using alternate algorithms the same segment is repeated until an acceptible set of results is obtained. Lee et al (56) have proposed a method of reducing the programming requirement in the use of recovery blocks by using a recovery cache. This automatically saves critical data as the program executes and could be used in simple rollback recovery.

# 1.4 Reliability Improvements Obtained

To determine the improvements obtained by adding one of the features

described above, it is necessary to determine the failure rate of the system with and without the modification. Modern microprocessor based systems have high reliability with a mean time between failures (MTBF) of several thousand hours. Therefore practical testing under normal operating conditions is both time consuming and costly. For individual component failure rates a number of data bases exist, such as MIL-HDBK-217D (121) compiled by the US Military, and HRD3 (122) compiled by British Telecom. HRD3 is based mainly on field data, whereas MIL-217D is based both on field data and accelerated life testing. A comparison between various failure rate data bases is given by Siewiorek et al (94).

Accelerated life tests have become very popular. They aim to speed up the failure process by subjecting the device to a more severe environment than normal, such as increased humidity, vibration or temperature. However, great care must be taken with the results. Siewiorek et al (94) show how the Arrhenius equation can be used to translate accelerated test data to ambient conditions and indicate that a factor of 62 difference in predicted failure rate can be obtained by the choice of activation energy. Another problem with accelerated tests is that if the conditions are varied too much, then failures due to other mechanisms can occur which will not be present under normal conditions, and this is illustrated by Hart et al (42).

However, these tests do provide useful results if care is taken, but, unfortunately, are normally carried out only at the component level. Full system testing can be achieved but requires bulky equipment and is time consuming. For these reasons a great deal of research has been aimed at modelling systems and predicting overall failure rates from the components. To assist in the calculations several computer programs have been written,

such as ARIES, described by Ng and Avizienis (71), and PREDICTION, described by Bell et al (10).