# **Durham E-Theses**

# Trapping effects in Cds devices

Robertson, Michael J.

#### How to cite:

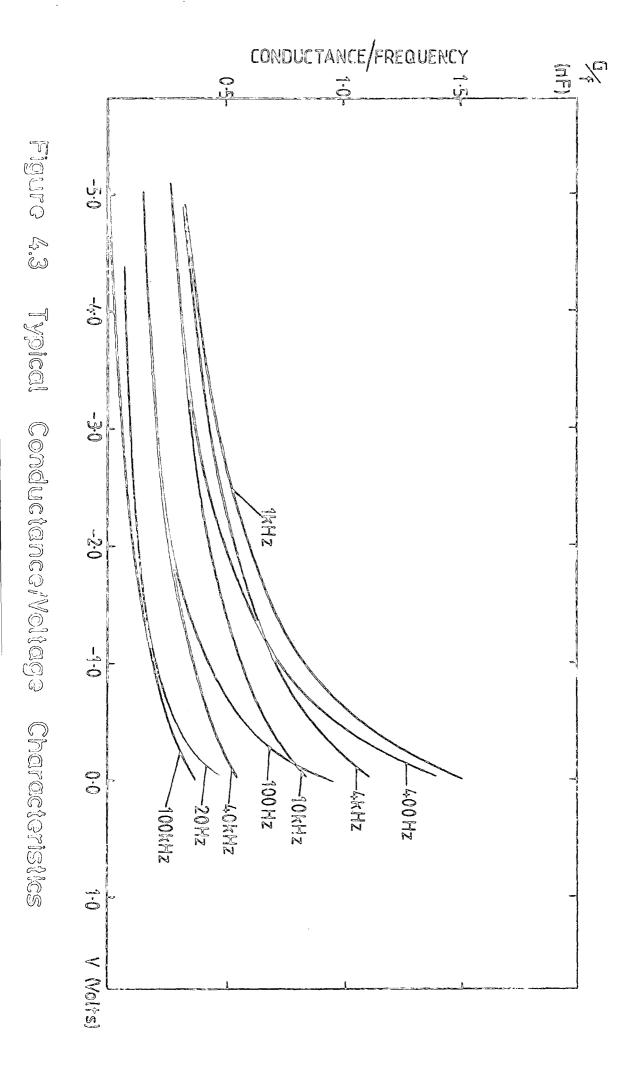

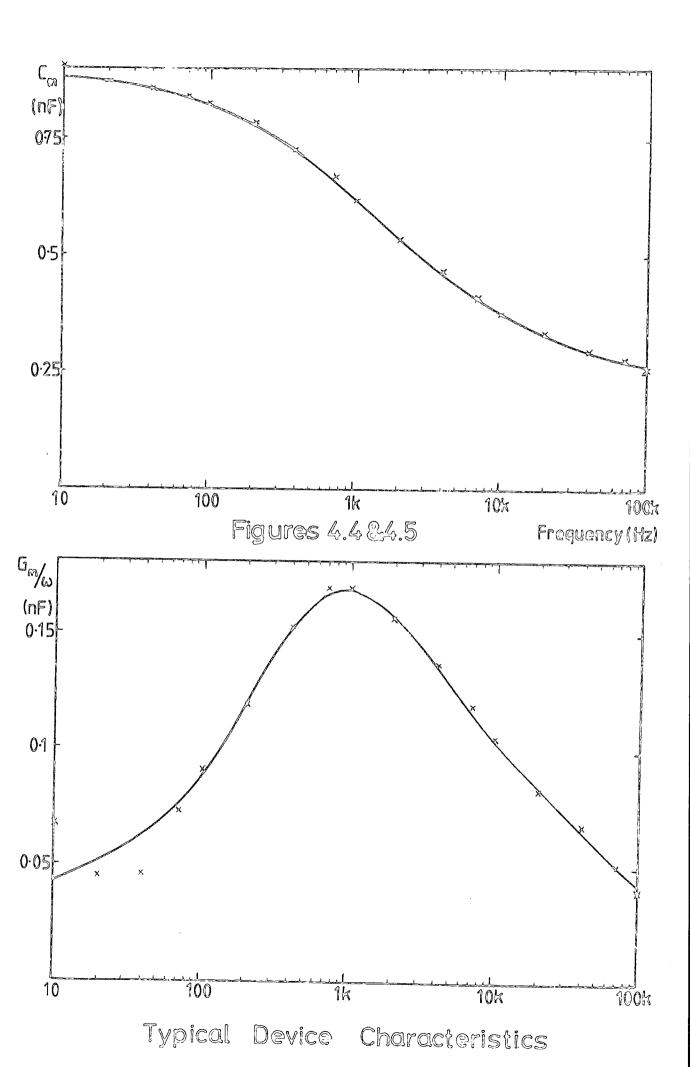

Robertson, Michael J. (1980) Trapping effects in Cds devices, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/7427/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

### TRAPPING EFFECTS IN Cds DEVICES

by

Michael J. Robertson, B.Sc. (St.Andrews)

Presented in candidature for the Degree of

Doctor of Philosophy in the University of Durham

#### OCTOBER 1980

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

#### **ACKNOWLEDGEMENTS**

I would like to thank Professor G.G.Roberts and the S.R.C. for allowing me to use the facilities of the Applied Physics Department and providing finance for my work over three years.

I am especially grateful to my supervisor, Dr. J. Woods, for his valuable suggestions and helpful encouragement throughout my stay in Durham. I also wish to extend thanks to Dr. G.J.Russell for help with electron microscopy and enthusiasm in the many useful discussions on all aspects of this thesis; to Mr. N. Thompson for the growth of crystals and a great amount of technical assistance, and to Mr. F. Spence and the staff of the workshop for their willingness to provide their skills and advice as and when required.

Finally, my thanks to my wife, Anita, for being understanding and patient throughout the time I have been writing this thesis, and for checking the typescript; and to my parents for their constant encouragement throughout this work.

#### ABSTRACT

In order to study the possible effect of intexface states on the efficiency of the CdS/Cu<sub>2</sub>S heterojunction solar cell, the simpler structure of metal-on-insulator-on-CdS has been investigated. It has proved impossible to apply the theories appropriate to MIS devices on silicon, mainly because of the difficulties of producing a uniform oxide layer. However, a hypothesis has been put forward which is consistent with the experimental observations and which may be applicable to other results reported in the literature. The use of a scanning electron microscope (S.E.M.) particularly in the induced current mode, has allowed complementary investigations of surface properties to be carried out. The chemical preparation of a copper sulphide layer on CdS under different conditions is described and the various phases of Cu<sub>x</sub>S produced are identified. The optical and electronic properties of these devices have been investigated under two-beam illumination to excite trapping effects.

Further use of the S.E.M. with these structures has shown how useful this instrument can be in the analysis of semiconductor junctions. Finally, a number of conclusions relevant to the production of a more efficient cell are presented and a modified band structure model of the heterojunction is proposed.

# CONTENTS

|           | CONTENTS                                       | Page Nos |

|-----------|------------------------------------------------|----------|

| ABSTRACT  |                                                | i        |

| CHAPTER 1 | HISTORY AND DEVELOPMENT OF PHOTOVOLTAIC CELLS  | 1        |

|           | 1.1 Photoelectric Effects                      | 1        |

|           | l.l.l Photovoltaic Effect                      | 2        |

|           | 1.2 Importance of Photovoltaic Cells           | 3        |

|           | 1.3 Costs and Efficiences                      | 4        |

|           | 1.4 Choice of Semiconducting Material          | 6        |

|           | 1.5 Type of Cells                              | 8        |

|           | 1.5.1 Homojunctions and Heterojunctions        | 8        |

|           | 1.5.2 Schottky Cells                           | 9        |

|           | 1.6 The CdS/Cu <sub>2</sub> S Solar Cell       | 9        |

|           | 1.7 Theory of the CdS/Cu <sub>2</sub> S Device | 11       |

|           | 1.7.1 Te Velde Model                           | 12       |

|           | 1.7.2 Clevite Model                            | 13       |

|           | 1.7.3 Experimental Evidence                    | 14       |

|           | 1.8 Stability and Degradation                  | 15       |

|           | References                                     |          |

| CHAPTER 2 | BASIC THEORY OF SCHOTTKY AND MIS DEVICES       | 18       |

|           | 2.1 Introduction                               | 18       |

|           | 2.2 Metal-Semiconductor Contact                | 18       |

|           | 2.3 Conduction in Schottky Diodes              | 21       |

|           | 2.4 Measurement of Barrier Height              | 22       |

|           | 2.4.1 Capacitance-Voltage Characteristics      | 22       |

|           | 2.4.2 Effect of Interfacial Layer              | 23       |

|           | 2.4.3 Photoelectric Threshold                  | 26       |

|           | 2.4.4 Current-Voltage Characteristics          | 27       |

|           |                      |                                            | Page Nos |

|-----------|----------------------|--------------------------------------------|----------|

|           | 2.5 Meta             | al~Insulator-Semiconductor (MIS)Diodes     | 28       |

|           | 2.6 Inte             | erface States                              | 30       |

|           | 2.7 Equi             | valent Circuit of an M.I.S. Device         | 33       |

|           | 2.8 Gene             | eralised Surface State Model               | 34       |

|           | Reference            | es                                         |          |

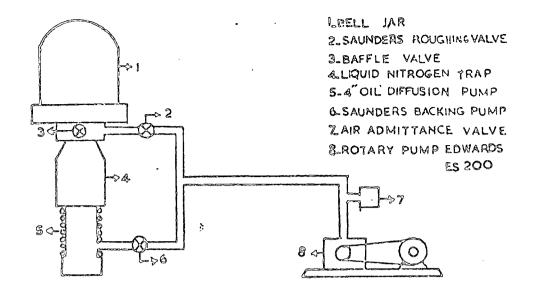

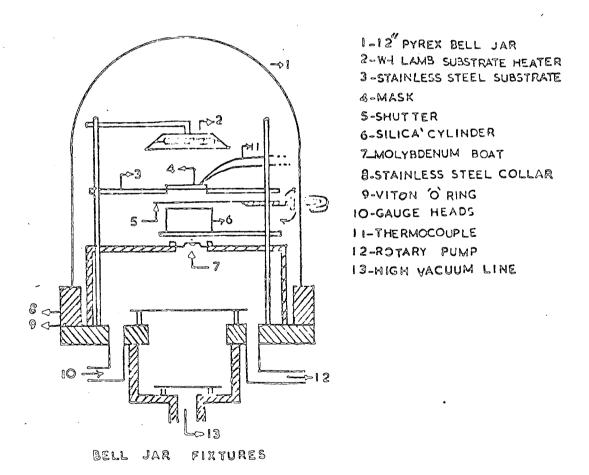

| CHAPTER 3 | CRYSTAL C            | GROWTH, MIS DEVICE PREPARATION AND         | 36       |

|           | 3.1 Grow             | th of CdS Crystals                         | 36       |

|           | 3.2 Prop             | perties of Cadmium Sulphide                | 37       |

|           | 3.3 Cadm             | nium Sulphide Sample Preparation           | 38       |

|           | 3.4 Devi             | ce Preparation                             | 39       |

|           | _                    | paration of Metal-Semiconductor and Diodes | 40       |

|           | 3.6 Meas             | surement Techniques                        | 42       |

|           | Reference            | es                                         |          |

| CHAPTER 4 | EXPERIMENT SIO AS IN | TTAL RESULTS ON MIS DEVICES ON Cds WITH    | 44       |

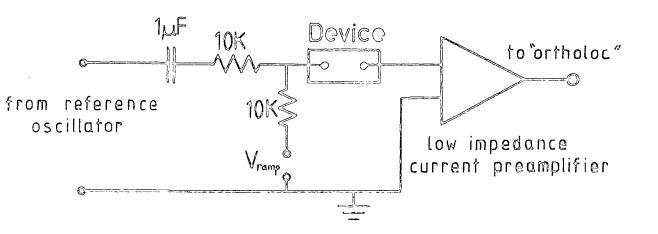

|           | 4.1 The              | Insulating Layer                           | 44       |

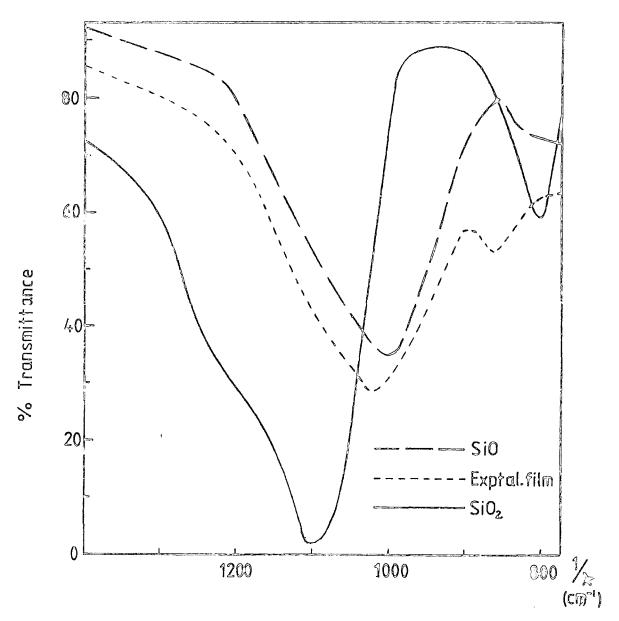

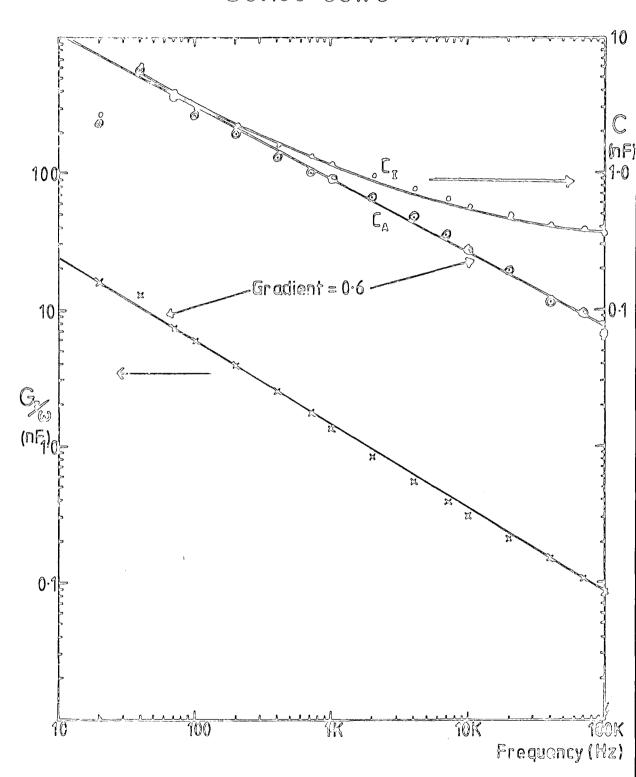

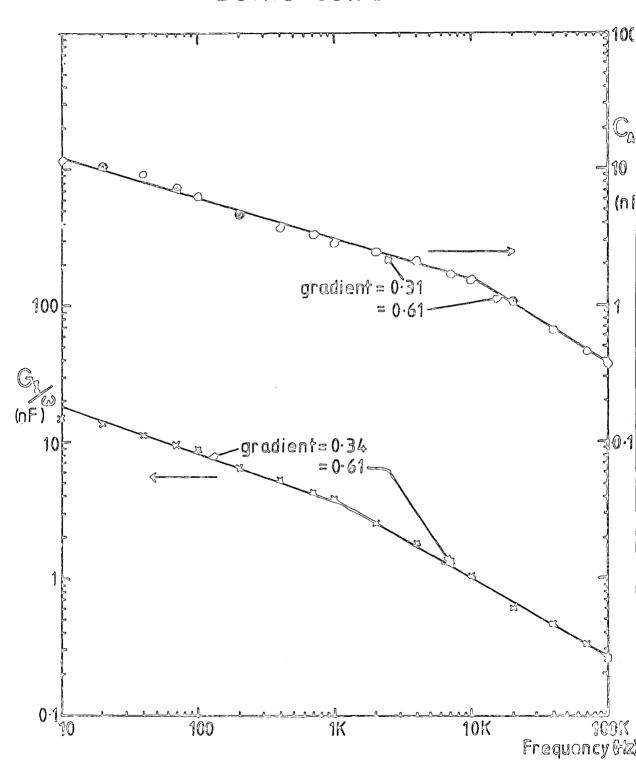

|           | 4.2 Expe             | erimental Results                          | 45       |

|           | 4.3 A Su             | rface State Model                          | 46       |

|           | 4.4 A Mo             | dified Model                               | 49       |

|           | 4.4.                 | l High and Low Frequency Limits            | 49       |

|           | 4.4.                 | 2 Extension to all Frequencies             | 50       |

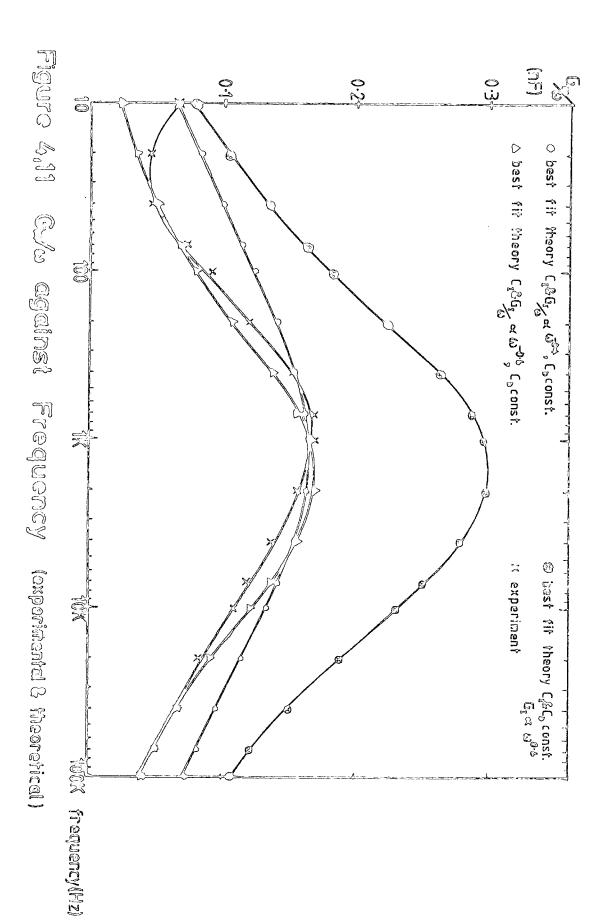

|           | 4.4.                 | 3 Alternative Method of Analysis           | 55       |

|           | 4.5 Disc             | russion                                    | 56       |

|           | 4.6 Fina             | l Considerations                           | 61       |

|           | Reference            | s                                          |          |

|           | ,                 |                                               | Page Nos |  |

|-----------|-------------------|-----------------------------------------------|----------|--|

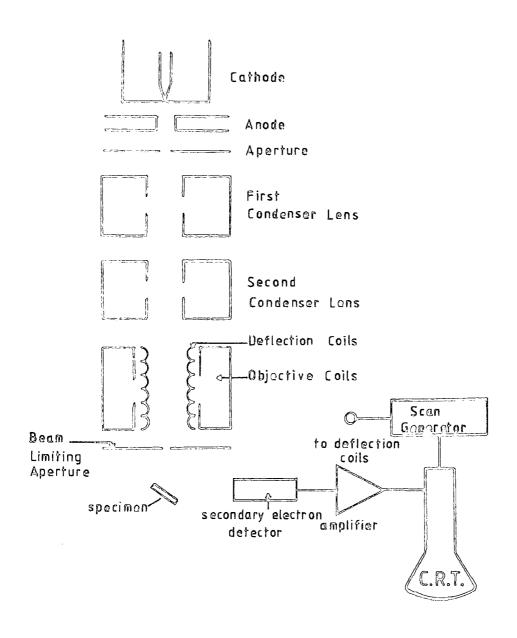

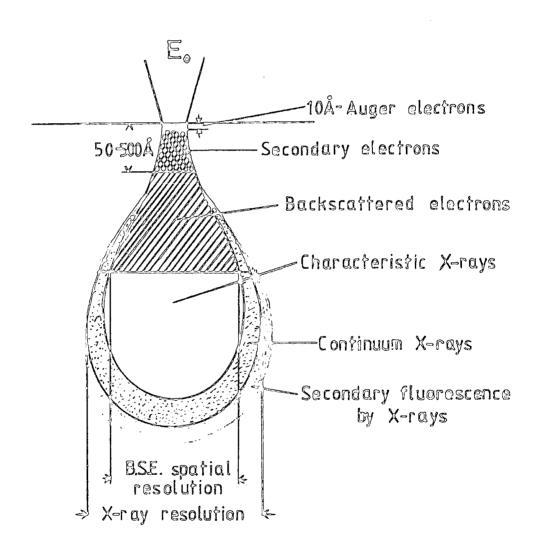

| CHAPTER 5 | SCAN              | NING ELECTRON MICROSCOPY OF MIS DEVICES       | 62       |  |

|           | 5.1               | Introduction                                  |          |  |

|           | 5.2               | Operation of the Scanning Electron Microscope | 62       |  |

|           |                   | 5.2.1 The Secondary Emission Mode             | 62       |  |

|           |                   | 5.2.2 Cathodoluminescence                     | 63       |  |

|           |                   | 5.2.3 The Electron Beam Induced Current Mode  | 64       |  |

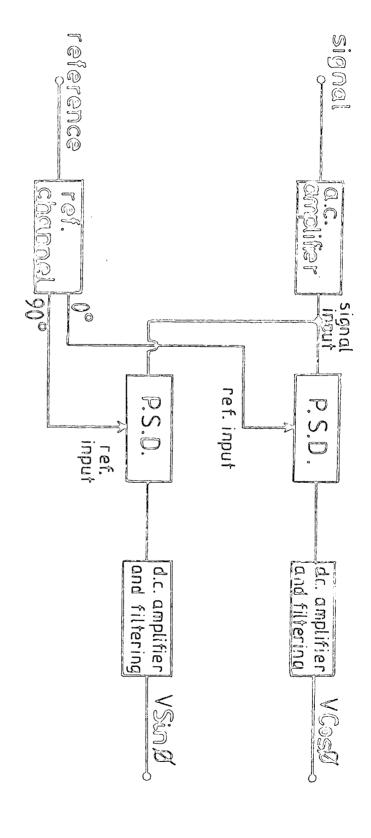

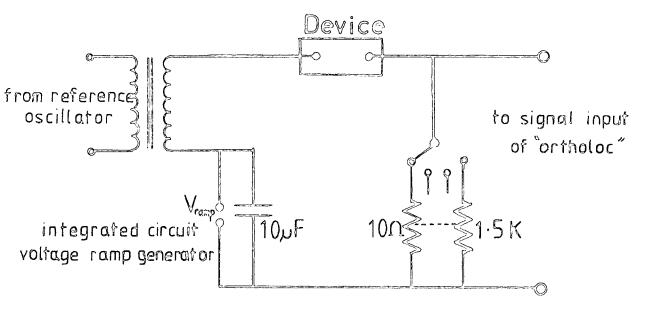

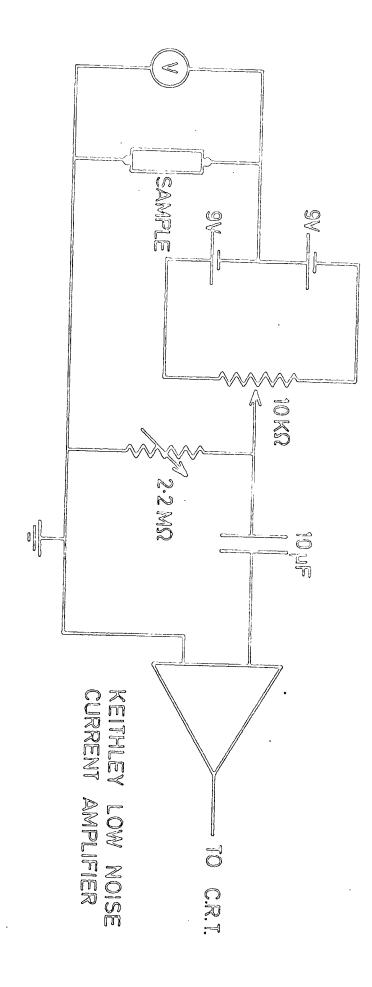

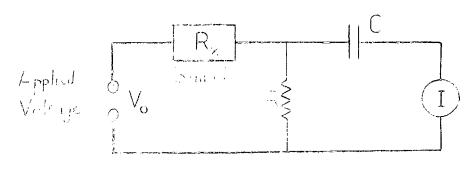

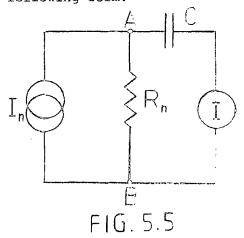

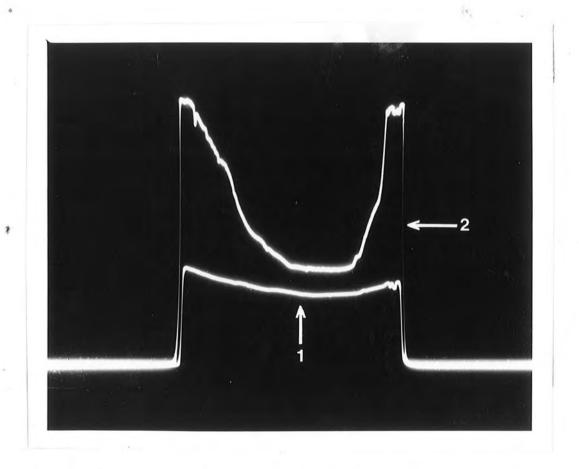

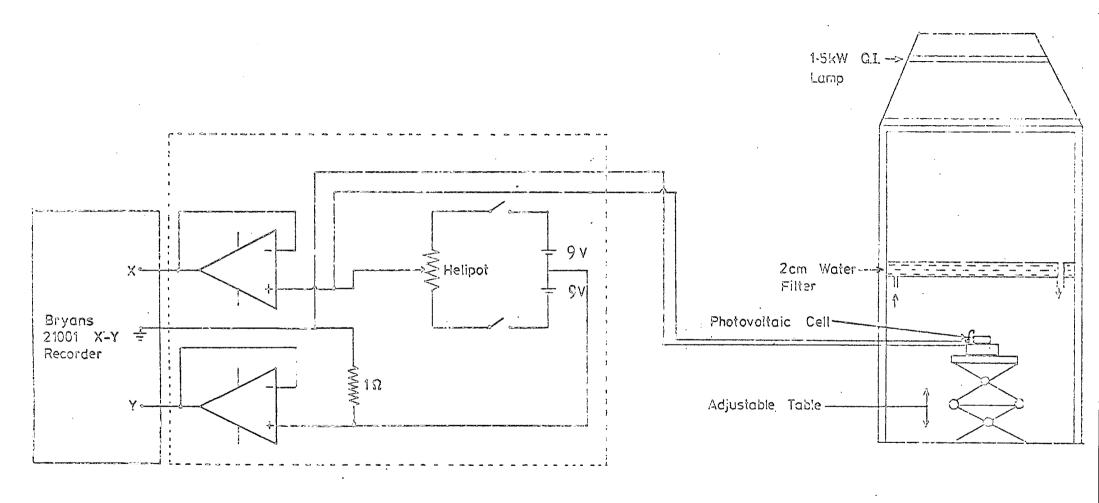

|           | 5.3               | The Analysis Circuit                          | 67       |  |

|           | 5.4               | Sample Preparation                            | 71       |  |

|           | 5.5               | Experimental Results                          | 72       |  |

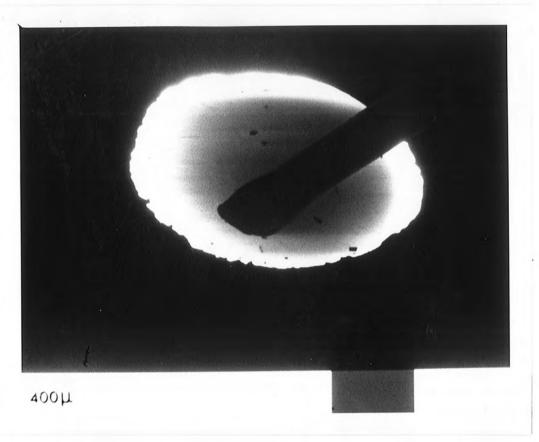

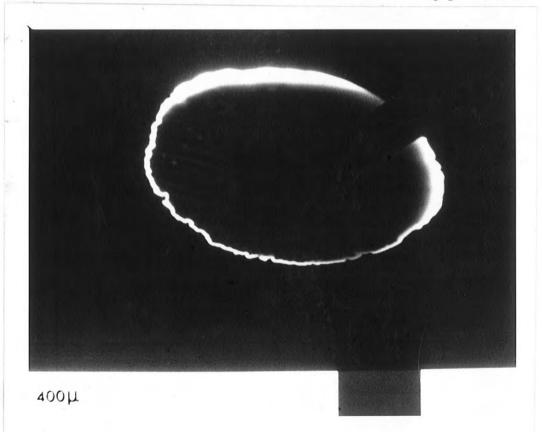

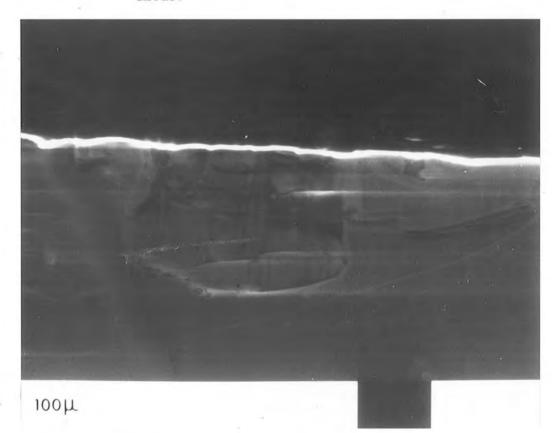

|           |                   | 5.5.1 Cleaved Diodes                          | 72       |  |

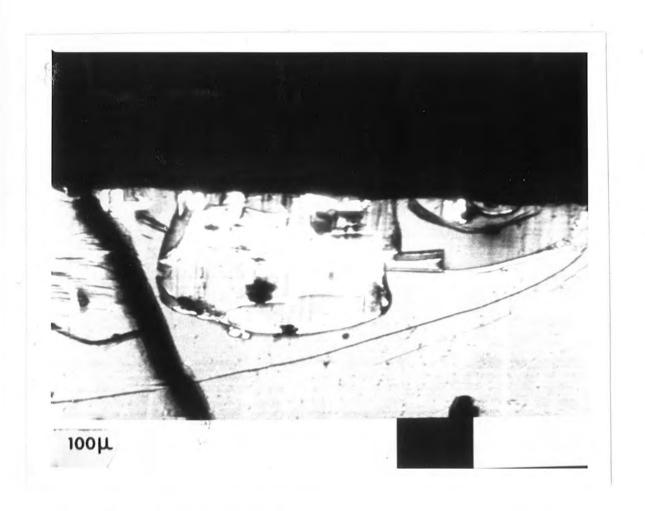

|           |                   | 5.5.2 Etched Diodes                           | 73       |  |

|           |                   | 5.5.3 Polished Surface Diodes                 | 73       |  |

|           |                   | 5.5.4 MIS Structures                          | 74       |  |

|           | 5.6               | Discussion                                    | 75       |  |

|           | 5.7               | Conclusions                                   | 82       |  |

|           | Refe              | rences                                        |          |  |

| CHAPTER 6 | Cu <sub>2</sub> S | on cds                                        | 84       |  |

|           | 6.1               | Introduction                                  | 84       |  |

|           | 6.2               | Growth of Copper Sulphide Layer               | 84       |  |

|           | 6.3               | Sample Preparation                            | 86       |  |

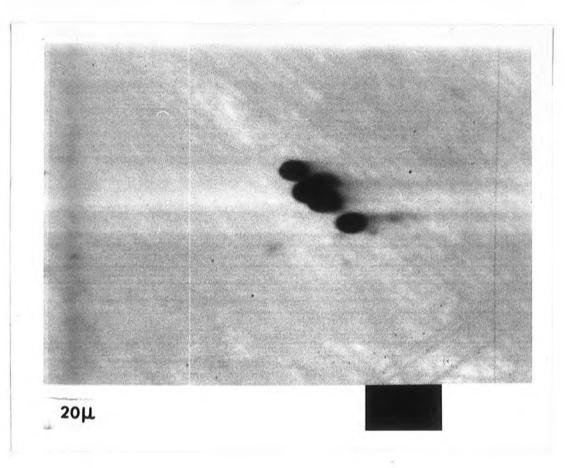

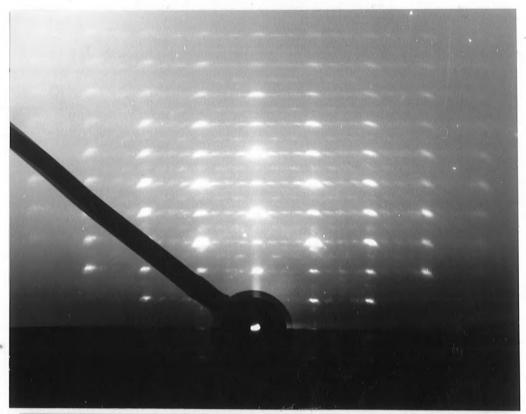

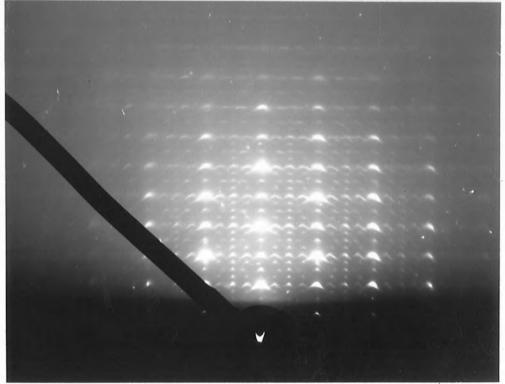

|           | 6.4               | Reflection Electron Diffraction               | 86       |  |

|           | 6.5               | Electron Diffraction Results and Analysis     | 88       |  |

|           |                   | 6.5.1 The Effect of Thermal Mass              | 91       |  |

|           |                   | 6.5.2 Etching                                 | 92       |  |

|           |                   | 6.5.3 Consequences of Heat Treatment          | 93       |  |

|           |                   | 6.5.4 Variation in pH. of Plating Solution    | 95       |  |

|           | 6.6               | Conclusions                                   | 97       |  |

|           | Refe              | rences                                        |          |  |

|           |                                                                  | Page Nos |

|-----------|------------------------------------------------------------------|----------|

| CHAPTER 7 | PHOTORESPONSE MEASUREMENTS                                       | 98       |

|           | 7.1 Introduction                                                 | 98       |

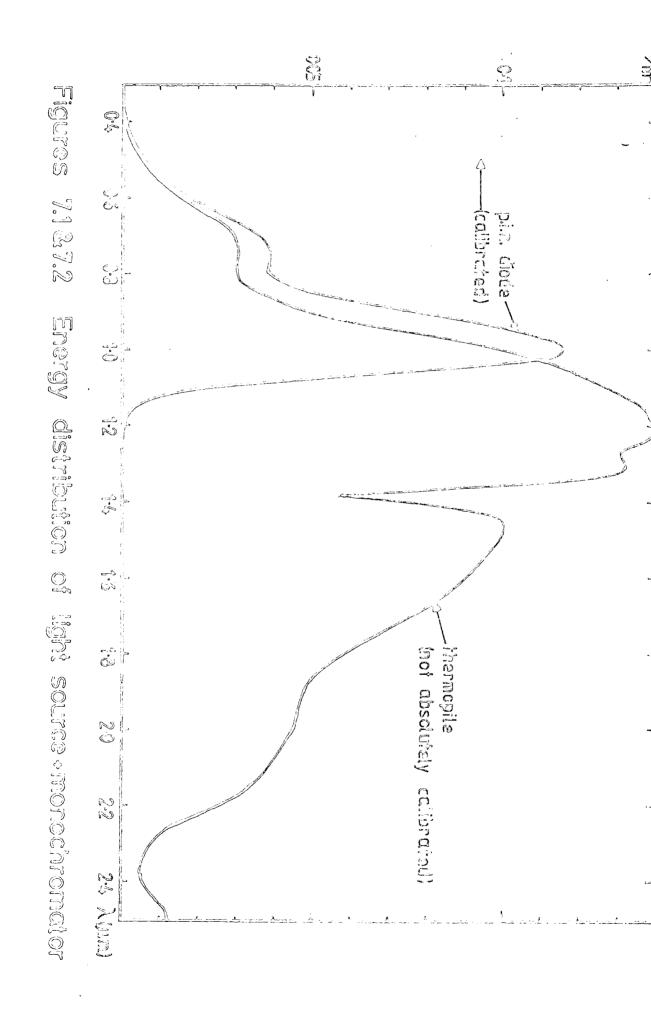

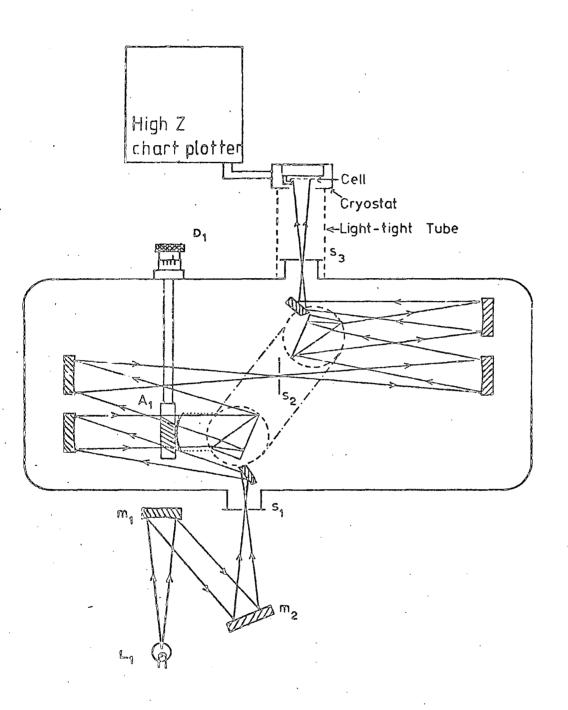

|           | 7.2 Measurement of Spectral Response                             | 98       |

|           | 7.2.1 Setting up Procedure                                       | 99       |

|           | 7.3 Photoconductivity                                            | 100      |

|           | 7.3.1 Sensitisation                                              | 100      |

|           | 7.3.2 Infra-red Quenching                                        | 103      |

|           | 7.4 Experimental Techniques                                      | 103      |

|           | 7.4.1 Photocapacitance                                           | 104      |

|           | 7.4.2 I-V Measurements                                           | 105      |

|           | 7.4.3 Photovoltage and Photocurrent                              | 106      |

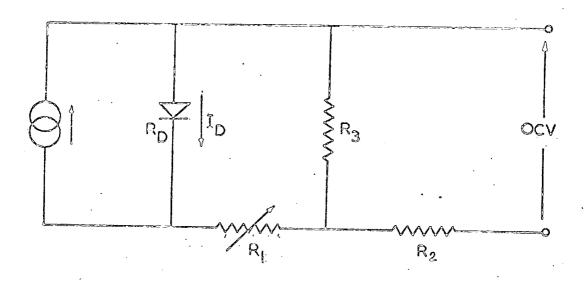

|           | 7.5 Model of the Photovoltaic Cell                               | 107      |

|           | References                                                       |          |

| CHAPTER 8 | EXPERIMENTAL RESULTS OF THE Cds/Cu <sub>2</sub> S HETEROJUNCTION | 109      |

|           | 8.1 Introduction                                                 | 109      |

|           | 8.2 The Effect of Copper as a Dopant in CdS                      | 109      |

|           | 8.3 Photocapacitance Measurements                                | 110      |

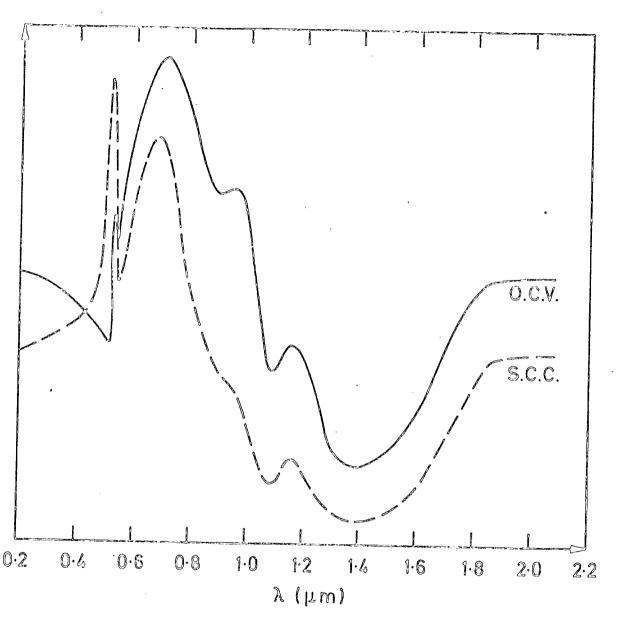

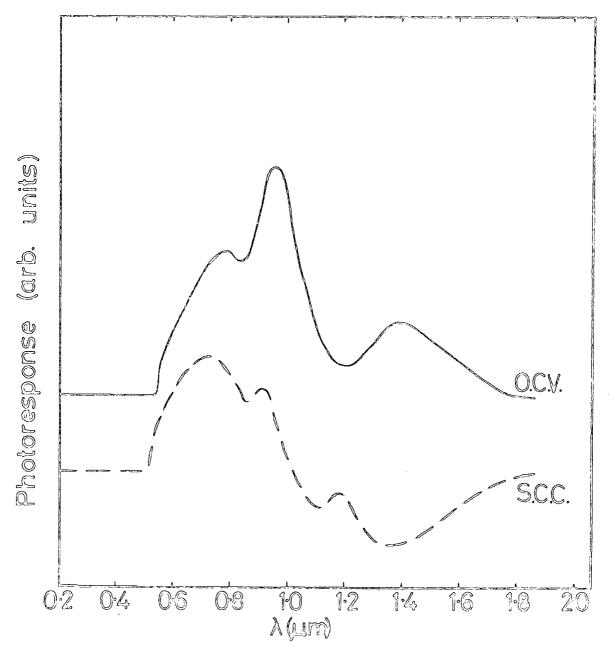

|           | 8.4 O.C.V. Measurements                                          | 111      |

|           | 8.5 Photoconductive Effects                                      | 112      |

|           | 8.6 InV Measurements                                             | 113      |

|           | 8.7 Comparison of O.C.V. and S.C.C.Responses                     | 114      |

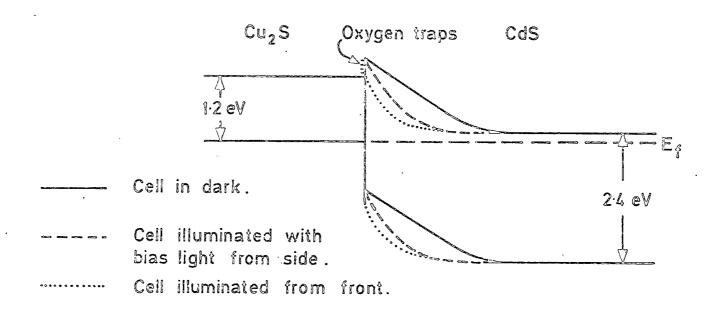

|           | 8.8 A Proposed Model                                             | 115      |

|           | 8.9 Explanation of Results                                       | 118      |

|           | 8.10 Discussion                                                  | 120      |

|           | 8.11 Final Considerations                                        | 121      |

|           | References                                                       |          |

|            |                                                         | Page Nos |

|------------|---------------------------------------------------------|----------|

|            |                                                         |          |

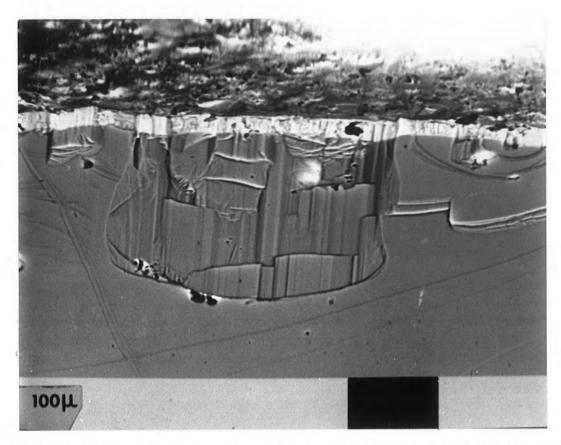

| CHAPTER 9  | SCANNING ELECTRON MICROSCOPE STUDIES OF HETEROJUNCTIONS | 122      |

|            | 9.1 Introduction                                        | 122      |

|            | 9.2 Experimental Observations                           | 122      |

|            | 9.3 Discussion                                          | 124      |

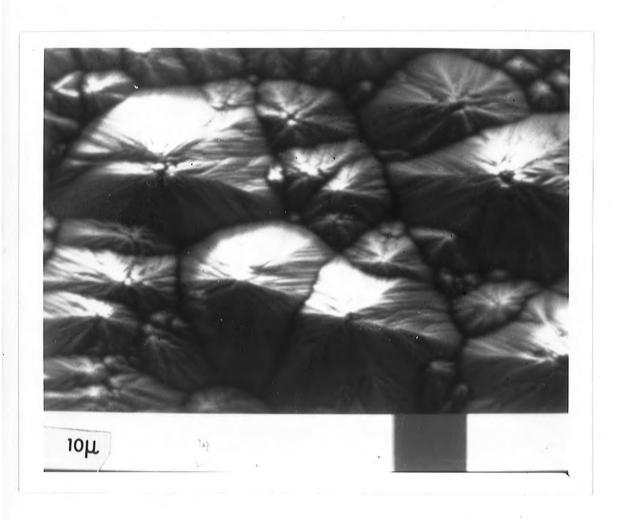

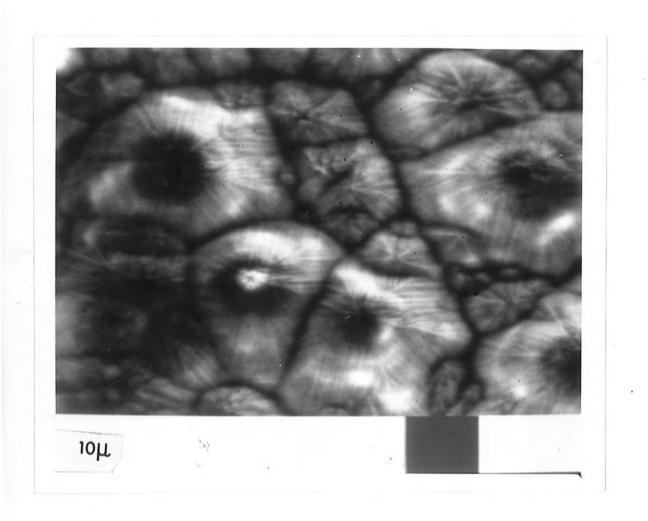

|            | 9.3.1 Surface Topography                                | 124      |

|            | 9.3.2 Degradation                                       | 126      |

|            | 9.3.3 Etching Procedure                                 | 127      |

|            | References                                              |          |

| CHAPTER 10 | CONCLUSIONS                                             | 129      |

|            | 10.1 In Conclusion                                      | 129      |

|            | 10.2 Suggestions for Further Work                       | 132      |

## APPENDIX A

#### CHAPTER 1

#### HISTORY AND DEVELOPMENT OF PHOTVOLTAIC CELLS

## 1.1 Photoelectric Effects

The discovery that light could be converted directly into electricity dates back to 1839, when Henri Becquerel observed that when two electrodes were immersed in an ionic solution and one was illuminated, a potential difference was developed across them. This is known as the photoelectric effect. The first reference to a similar effect occurring in a solid was the observation in 1876 by Adams and Day in selenium.

In addition to this photovoltaic effect, there are two other photoelectric processes, namely the photoconductive effect and the photoemissive effect. The former requires that the electrical conductivity of

the material increases when it is illuminated by light of a suitable

wavelength. This effect was first discovered in selenium in 1873 by

W. Smith. The effect also occurs in CdS where the absorption of light

with sufficient photon energy causes the excitation of electrons from the

valence band to the conduction band. As a result the free electron concentration is increased and aids conduction; the holes are quickly

captured at defect or impurity centres leaving the electrons to make the

major contribution to the conductivity. This will be seen later to have

important consequences in the operation of the CdS/Cu<sub>2</sub>S heterojunction

photocell which forms the major topic of this thesis.

A less important effect associated with photoconductive materials is the Dember effect. This is the production of a potential difference across a sample by non-uniform illumination. If light is incident normally on the surface of the photoconductor, it will produce electronhole pairs, which will diffuse into the non-illuminated bulk. Since in

a material such as CdS, the electron mobility is much greater than the hole mobility, the electrons will proceed further until sufficient field is set up to oppose continued motion. Thus with a suitable contact geometry, a Dember voltage may be measured. The effect may usually be neglected; in Ge for example, it may be  $\sim 0.01 \text{ V}$ .

The photoemissive effect was discovered by Hertz in the course of his work on L-C circuits in 1887. He found that a spark jumped a gap more readily when the negative electrode was illuminated by a spark from another coil. Further work established that it was the ultra-violet radiation in the spark that affected the cathode. Hallwachs demonstrated that negative charge was emitted from the cathode under U-V illumination and Lenard later showed that the charge consisted of electrons. The first photoemissive cell was produced by Elster and Geitel in 1895. Subsequent work has led to the development of the more sensitive photoemissive materials which are used in the photomultipliers and television camera tubes of today.

## 1.1.1 Photovoltaic Effect

The search for an explanation of the photovoltaic effect continued in the 20th century with the discovery by Grondahl (1927) and Lange (1936) of an e.m.f. generated across the contact between copper and copper oxide. Schottky (1930, 1931) was able to clarify this phenomenon. In spite of such an early discovery it is only in the last 25 years that serious attempts have been made to exploit the photovoltaic effect, namely in the conversion of solar radiation into electricity. Before this, probably the most important application of the effect was in selenium p.v. cells for exposure meters in photography. This is because the materials technology has not hitherto been available for the production of the large slices of high purity semiconductor required for efficient

photovoltaic conversion. To produce a photovoltage, the electrons and holes generated by light in the semiconductor must be physically separated by an inhomogeneity such as the internal electric field that occurs at a metal-semiconductor junction or a p-n junction. Thus a current can be made to flow simply by connecting a load externally between the p- and n-type regions while the junction region is illuminated.

Photocells whether photoconducting or photovoltaic have been used for many years in applications such as intruder alarms, industrial controls, and conveyor belts, where a person or object breaks a light beam irradiating the cell; in all these examples, the cells are used as light-operated switches.

#### 1.2 Importance of Photovoltaic Cells

The 'space-age' is certainly one of the major factors promoting recent interest in photovoltaic cells as direct energy convertors rather than as mere energy sensors. The conception of satellites circling the earth would be totally impractical without some light-weight power source which will last almost indefinitely without maintenance. Photovoltaic solar cells were the obvious answer and much money has therefore been poured into their development, especially by the U.S.A.

At the same time, the western world has been awakening to the fact that with ever-increasing energy demands (at something like an exponential rate), our fossil fuel supplies are unlikely to last for ever. Current estimates show that supplies of oil and natural gas will run out within 30-40 years, and of coal in little more than a century. The implications of this on life, as we know it today, are colossal, and it is frightening that so little is being done in researching alternative energy sources.

The two most important alternative energy sources are nuclear power and solar power. The former has the disadvantage of its waste disposal and latent radiation, and therefore environmentally the latter must be the more favourable. Photovoltaic cells are just one of many types of solar energy converter, but they have the advantage of converting solar radiation directly into electricity - probably the most useful form of energy.

In the shorter term, interest in terrestrial solar cells has focussed on their potential to contribute to the development of the third world. A recent conference on 'Solar Energy for Development'in 1979 discussed its use in the provision of water, power production and heating and cooling, (Palz, 1979). Solar electricity is attractive for such applications, even if it is dearer per watt than conventionally generated supplies because of its flexibility; it requires less maintenance, no fuel supplies and no transmission lines. Even a small photovoltaic generator, which in a western home would be of no importance, can provide electricity to operate a television set, bringing education and literacy to a whole village. Such provision has been successfully made in Nigeria and the Ivory Coast and other African countries. Other obvious examples are in pumping drinking water, providing telephones and lighting.

#### 1.3 Costs and Efficiencies

Photovoltaic power for development is currently cost-competitive in the pure economic sense for small applications up to a few kW in remote regions, however because of limited resources in the third world, it is crucial that prices reduce rapidly in the coming years. This is also important for the west, because the lower the price per watt, the more interest will be shown in photovoltaic cells and the sooner they can take over from the dwindling fossil fuels.

A background of costs and relative efficiencies of different photovoltaic materials, and projections into the future was provided by

Rappaport and Magid at the 1979 Photovoltaic Solar Energy Conference in

Berlin, and will be summarised here. The present (1978 figures) annual

volume of solar cell energy is in excess of 1 MW and mostly due to silicon

cells. The cost of an installed system is between \$20 and \$40/Watt,

although the cost of the cell array alone is only \$7 - \$15/Watt; consequently

there is a need not only to reduce device costs but also systems costs.

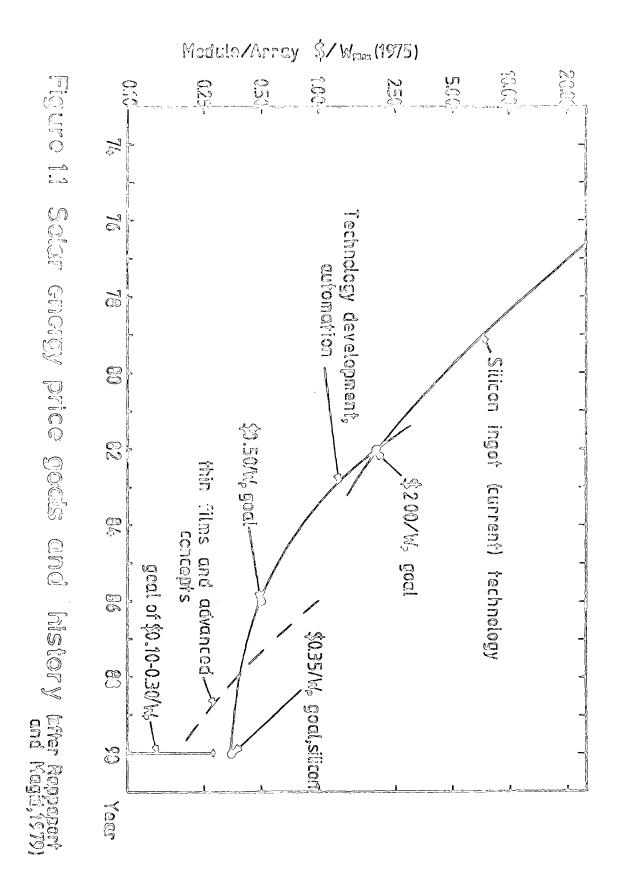

Figure 1.1 shows a graph of projected costs, the goal of \$0.10 - \$0.30/Watt

is calculated to make solar electricity directly competitive with conventional power station generated electricity. Prospects for various types

of solar cell are shown in Table 1.1.

| Array Technology                              |              | Goal (1975\$)               | Prospect       |

|-----------------------------------------------|--------------|-----------------------------|----------------|

| Si Flat Plate: Si Czochr. single crystal      |              | ( a500 () v                 |                |

| Si Semicrystalline Sheet Si Ribbon and sheets |              |                             | Excellent      |

| Si Amorphous Layers                           |              |                             |                |

| Concentrator:                                 | ١            |                             |                |

| Si                                            |              | / #E00 /1-t1                | Warma Gand     |

| GaAs                                          |              | <pre>\$500/kw (1986)</pre>  | Very Good      |

| Total Energy                                  | <i>!</i><br> |                             |                |

| cds/Cu <sub>2</sub> s thin film               |              | <b>≼</b> \$500/k₩<br>(1986) | Very Good      |

| Other thin films:                             |              |                             | Ì              |

| GaAs, InSnO <sub>2</sub> /Si, CdTe etc.       |              | \$100-300 kW                | Very Promising |

Present efficiencies of different types of thin film solar cells are:-

- (2) GaAs High single crystal efficiencies ~ 20% have been obtained

- (3) Polycrystalline Si 9%

- (4) InSnO<sub>2</sub>/Si 12% on single crystal Si

- (5) Amorphous Si 6% has been attained

- (6) CdS/CuInSe<sub>2</sub> 6.7% evaporated cell, improved lattice match compared to Cu<sub>2</sub>S/CdS

- (7) CdS/InP 14% on single crystal.

The reason why these particular materials have been chosen for solar cells will become clear in what follows.

#### 1.4 Choice of Semiconducting Material

One important point in the material selection which might appear obvious is that the cost, in terms of energy, of producing a cell, must be considerably less than the energy that cell will produce during its lifetime. This is crucial for silicon single crystal cells, because growing silicon by the Czochralski technique is very 'energy-intensive'. The elements of the material for solar cells clearly must be in great abundance upon the earth's crust. In addition to these considerations the factors affecting the choice of a photovoltaic material are:-

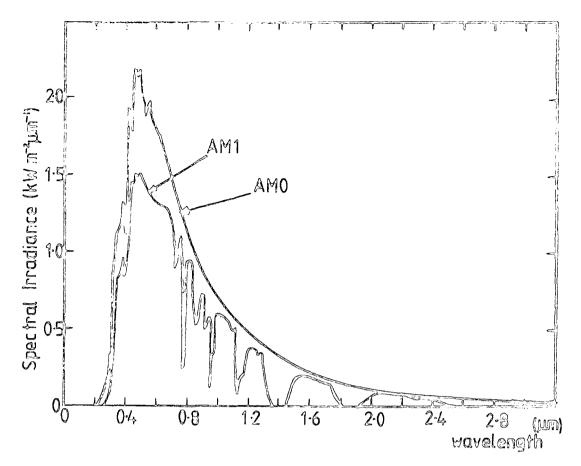

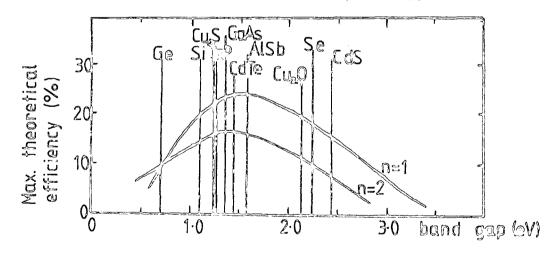

The bandrap of the material must be chosen properly. The larger 1. the band gap, the less light is usefully absorbed as most light with hv < Eg is transmitted. However the smaller the band gap, the lower the conversion efficiency of short wavelength light, since the absorption of any photon of energy, hv > Eg only creates useful electrical energy of Eq, the remainder being wasted as heat from intra-band transitions. other words, the maximum internal barrier is lower, resulting in a reduction in achievable open circuit voltage. Clearly the band gap of the material has to be matched in some way to the radiant energy distribution of the sun shown in Figure 1.2. This diagram also shows the proportion of the energy usefully absorbed by several semiconducting materials. Calculations of theoretical efficiency for solar energy conversion as a function of band gap (Loferski 1956, Wysocki and Rappaport 1960 and Wolf 1960) have shown that materials with band gaps between 1.25 eV and 1.5 eV are optimal with theoretical conversion efficiencies of 24%. would suggest that silicon with a band gap of 1.1 eV would not be ideal for a solar cell. However, silicon technology is far more advanced than that of any other semiconductor so that what the material lacks in optimum theoretical match, at present can be more than satisfied by technology. Indium phosphide with a band gap of 1.27 eV and GaAs (1.34 eV) would appear to be promising materials as they have a high mobility, about four times that of silicon. Unfortunately, preparation of III-V materials is difficult and so far only 'concentrator' systems have proved viable. concentrator system is essentially one where sunlight is focussed by lenses on to a small area device). The considerations described above would suggest that CdS with a band gap of 2.4 eV would be unsuitable as the basis for a solar cell. This is true, but it must be remembered that the useful light absorption occurs in the  $p-Cu_{\gamma}S$  side of the heterojunction and the band gap of  $Cu_2S$  is ~1.2 eV.

Figure 1.2(a) Energy distribution of sun AMO-Distribution outside atmosphere AM1-Distribution at sea level

Figure 1.2(b) Proportion of sun usefully absorbed by semiconductors (n=diode ideality factor)

- 2. The semicenductor must have a high optical absorption coefficient in order to absorb the maximum amount of solar radiation.

- 3. Ideally the whole spectrum of sunlight should be used to create electron-hole pairs.

- 4. All electron-hole pairs produced should be collected at the junction, i.e. all electron-hole pairs should be created within one diffusion length from the junction.

Also the following more general points should be satisfied by a cell:

- (a) Reflection losses at the top surface should be a minimum.

- (b) The internal series resistance should be minimal.

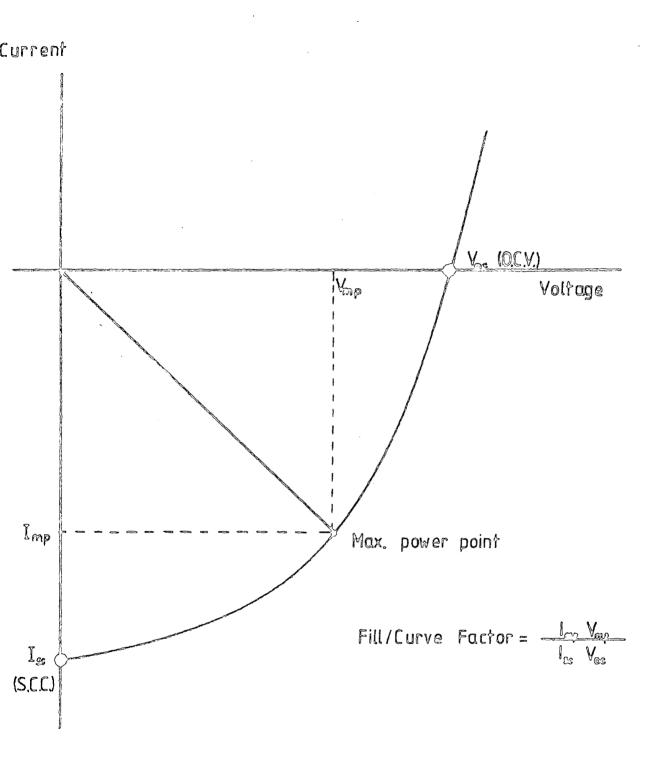

- (c) The fill factor (sometimes known as the curve factor, see Figure 1.3) defined as the ratio of power at the maximum power point to the product of open circuit voltage and short circuit current, should be a maximum.

- (d) For space use especially, the cell should be resistant to radiation damage.

#### 1.5 Type of Cells

There are three basic types of photovoltaic device, having both advantages and disadvantages, which with different materials can satisfy some of the above conditions. These are p-n homojunctions, heterojunctions or metal-semiconductor cells.

#### 1.5.1 Homojunctions and Heterojunctions

Cells based on homojunctions are limited to materials which can be made both n- and p-type. However it can be an advantage to use a heterojunction which has materials with different properties on either side of the junction. Thus light should be absorbed by a material with band gap of 1.25 - 1.5 eV then if the other material is chosen to have a wide band

Figure 1.3 Definition of Fill/Curve Factor

gap, the device may be operated in the 'back-wall' configuration, i.e. illuminated through the high band gap material and the light will be absorbed close to the junction. Additionally in a homojunction the top layer is usually made by diffusing dopants into a region already doped in the opposite manner, and this leads to a region with low minority carrier lifetime and hence poor collection efficiency.

A disadvantage of the heterojunction is that because it consists of two different materials there will be, inevitably, stress due to mismatch of the two crystal lattices. This will create recombination centres at the junction with consequent lowering of efficiency.

#### 1.5.2 Schottky Cells

The metal-semiconductor or Schottky barrier cell (and more recently the M.I.S. cell (Fonash 1976) has the advantage of ease of preparation, since it does not require diffusion processes to be carried out at elevated temperatures as the other two do.

From these considerations, the most promising cell to emerge to date is the polycrystalline silicon p-n junction device for which efficiencies of 9% have been achieved, and the CdS/Cu<sub>2</sub>S heterojunction cell, consisting of a polycrystalline layer of CdS,  $\sim$  30  $\mu$ m thick deposited on plastic or glass. The surface of the CdS is converted to a layer of Cu<sub>2</sub>S  $\sim$ 1  $\mu$ m thick by a chemical exchange reaction. Such a cell may have an efficiency of 9% and is cheap to prepare. Amorphous silicon is the most recent material to show promise for the construction of inexpensive cells in large quantities. Assuming the present figure of 6% efficiency can be improved by further research, these may well provide the cells of the future.

# 1.6 The CdS/Cu<sub>2</sub>S Solar Cell

The original observation of a photovoltaic effect on CdS was made

when a copper contact was illuminated (Reynolds et al 1954) and since then a great deal of effort has been put into improving the efficiency of the cell and increasing the understanding of the physical processes involved. Williams and Bube (1960) observed a voltage in cells where the copper was deposited electrolytically on to CdS, and suggested it was due to electron emission from metal into semiconductor. Alternatively, Woods and Champion suggested that a high concentration of copper diffused into the CdS and produced a p-type region in the CdS, thus creating a p-n junction photovoltaic effect. Hall measurements showed that the hole conduction was via an impurity band. This idea was supported by Grimmeis and Memming (1962). Since copper has a limited solubility in CdS, however, the hole conductivity must have been associated with a separate phase of copper sulphide (Te Velde 1967). This was later demonstrated by electron diffraction measurements (Cook et al 1970). Hall measurements showed that copper sulphide was p-type with a mobility at room temperature of 2 cm $^2$ /V sec, and a hole concentration of  $10^{20}$ /cm $^3$ .

In 1966, N. Duc Cuong and J. Blair produced a photovoltaic cell by evaporating copper on to low resistivity single crystal CdS. They found that the spectral response of the cell in the infra-red was enhanced by two orders of magnitude under simultaneous illumination with green light (band gap). They suggested that this was due to the creation of extra minority carriers by excitation of electrons from the valence band to impurity states in the CdS.

Thin film cells were prepared by Chamberlain and Skarman in 1966 by a spray technique. They used an aqueous solution of cadmium chloride and thiourea, which was sprayed on to a heated glass substrate coated with tin oxide. A solution of copper sulphide was then sprayed on at room temperature. The CdS in this device was only 2 µm thick, and the cell gave efficiencies of ~4%. This is a very promising technique for the mass

production of cheap cells. The photovoltaic effect in these cells owes its origin to the field at the heterojunction of the copper sulphide and the cadmium sulphide.

# 1.7 Theory of the CdS/Cu<sub>2</sub>S Device

Mytton in 1968 made cells by chemically plating Cu<sub>X</sub>S on to CdS. He measured their spectral responses as a function of the plating concentration and time. His results indicated that the intrinsic response of the cell depended on both the concentration and the dipping time in the plating solution. On the other hand, the extrinsic CdS response was largely unaffected by the dip time and dependent only on concentration. Mytton, therefore, suggested a band structure for the cell in which the junction was not abrupt, but consisted of a transition from p-Cu<sub>2</sub>S through photoconducting (high resistance) Cu-doped CdS to n-type CdS. This model is similar to those suggested by Keating in 1965 and Bockemuehl et al in 1961.

A more detailed version of this model, the Clevite Model, was proposed by Shiozawa et al in 1967, following detailed considerations of the measured electrical, optical and structural properties of a large number of cells. Other models suggested for the CdS/Cu<sub>2</sub>S cell include the Harshaw Model by Hill and Keramidas, 1966; the Lewis Model by Potter and Schalla, 1967; and the E.S.R.O. model by Van Aershodt et al, 1968; all contain common features but differ in the details of the shape of the potential energy barrier at the CdS/Cu<sub>2</sub>S junction.

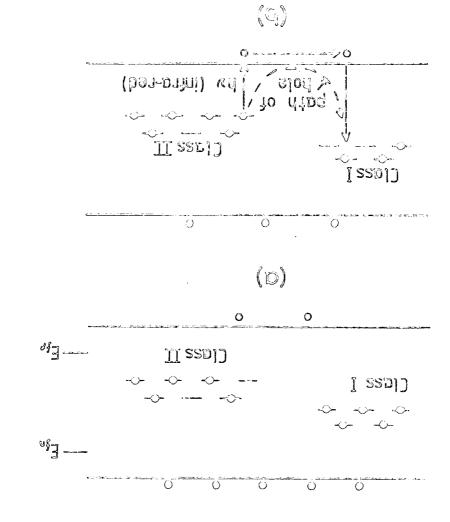

Gill and Bube, 1970, suggested a model in which the central feature was hole trapping at deep imperfection centres in CdS near the junction to account for experimental evidence of quenching and enhancement of the photoresponse under secondary illumination. In their model a spike exists

in the conduction band at the interface. Electrons diffusing across the junction have to tunnel through this spike and the tunnelling probability is controlled by the occupancy of the deep lying acceptor states (see Figure 1.4). In 1972 Lindquist and Bube carried out photocapacitance measurements on the CdS/Cu<sub>2</sub>S junction, which they interpreted as supporting their original hypothesis. The acceptor levels were attributed to copper diffused into the CdS during junction manufacture.

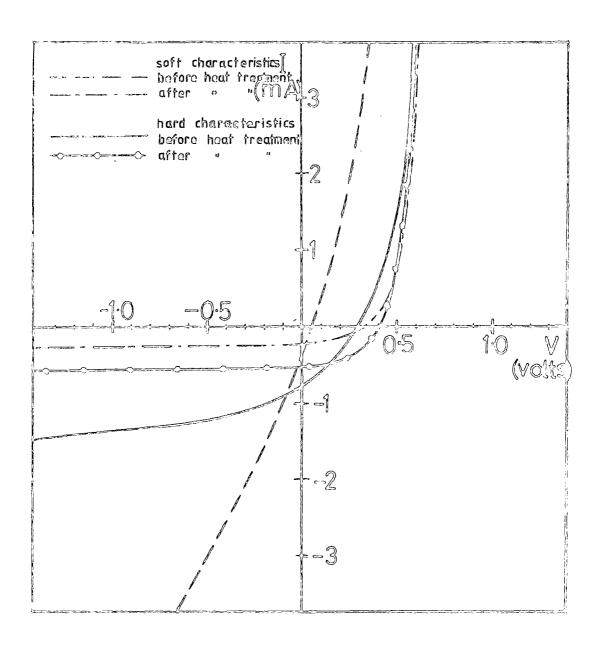

#### 1.7.1 Te Velde Model

An important feature of the CdS/Cu<sub>2</sub>S cell is that it is usually considered necessary to bake a cell in air at 200°C for 2 minutes or so before optimum efficiency is achieved. Te Velde (1973) made a mathematical analysis of the CdS/Cu<sub>2</sub>S heterojunction and concluded that while copper does diffuse into the CdS, the main effect of the sensitising heat treatment is to allow the diffusion of oxygen to the junction interface, where it forms electron traps. As this takes place, the barrier between the  $\operatorname{Cu}_2\operatorname{S}$  and  $\operatorname{CdS}$  increases so that it is possible that a conduction band spike forms at the junction. If the barrier is low, i.e. there is a 'notch' in the conduction bands at the interface, then the open circuit voltage (O.C.V.) of the cell will be low, although the short circuit current (S.C.C.) may be good. If, on the other hand, there is a sizeable spike at the junction, then the O.C.V. will have reached a maximum, but the short circuit current will be small as a result of the poor collection efficiency of electrons flowing from the Cu<sub>2</sub>S into the CdS. The optimum heat treatment according to Te Velde is therefore one which leads to practically no discontinuity of the conduction bands. This theory fits well qualitatively with what is observed experimentally for the variation of O.C.V. and S.C.C. as the length of heat treatment in air is increased.

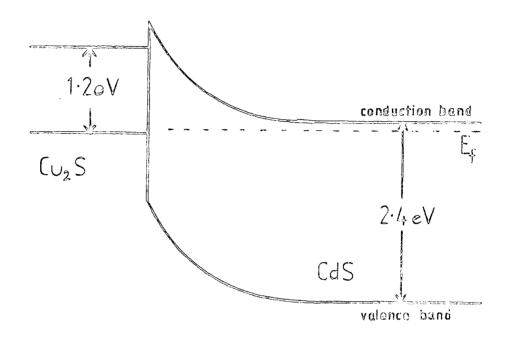

Fig.1.4 Model of CdS/Cu<sub>2</sub>S Heterojunction Band Structure (after Gill & Bube, 1970)

# 1.7.2 Clevite Model

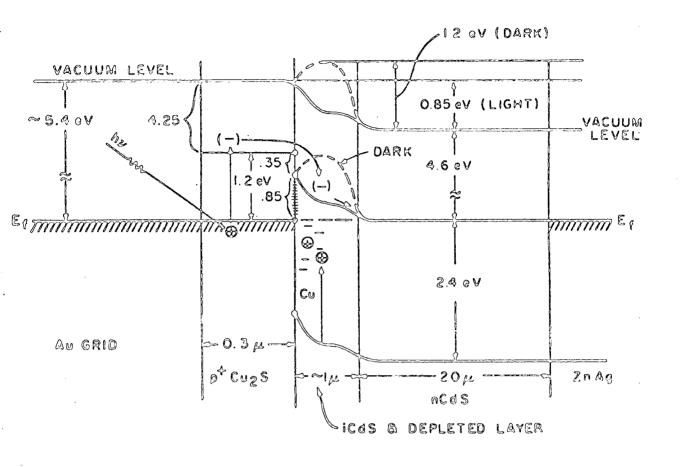

The Clevite model is probably the most comprehensive yet proposed, and hence it will be described in some detail (see Figure 1.5), since it forms the basis for much of the later discussion. The basic assumptions on which the model is based are:

- (1) Gold makes an ohmic contact to  $p-Cu_2S$ , and ZnAg is used as a substrate and makes an ohmic contact to n-CdS.

- (2) Almost all the useful light absorption takes place in the thin layer of p-Cu<sub>2</sub>S. Thus, the spectral response of the cell corresponds to the intrinsic absorption spectrum of  $\text{Cu}_2\text{S}_\tau$  modified by the photoconductive response of the insulating CdS, (i-CdS).

- (3) The i-CdS layer results from Cu diffusion during cell fabrication. This layer which is insulating in the dark is photoconductive and its resistance is therefore reduced when the cell is illuminated with sunlight. The quasi-Fermi level for electrons moves upwards during illumination and the layer becomes weakly n-type. It has the photoconductive properties of Cu-compensated CdS.

- (4) When illuminated, the main junction in the cell occurs between  $\text{Cu}_2\text{S}$  and i-CdS. The barrier height is then about 0.85 eV.

- (5) In the dark, the principal junction occurs between the i-CdS and n-CdS. The barrier height is about 1.2 eV. A small junction of reversed polarity with barrier height of 0.35 eV occurs between the Cu<sub>2</sub>S and i-CdS.

- (6) The interface states at the p-Cu<sub>2</sub>S:i-CdS junction are mainly responsible for the recombination which occurs under forward bias conditions.

When the cell is illuminated by light of energy less than 1.2 eV, the photons pass through the  $\mathrm{Cu}_2\mathrm{S}$ , through the CdS and are absorbed or reflected by the ZnAg layer. With photons of energy between 1.2 eV and 2.4 eV, absorption takes place, but this is not complete as  $\mathrm{Cu}_2\mathrm{S}$  has an indirect band gap at 1.2 eV, i.e. absorption must be phonon assisted. Because of

FIG. 1-5 ENERGY BAND DIAGRAM FOR  $Cu_2S-CdS$  SOLAR CELL UNDER ILLUMINATED SHORT CIRCUIT CONDITIONS (CLEVITE MODEL)

the combination of this and the small thickness of  $\text{Cu}_2\text{S}$ ,  $\sim 0.3~\mu\text{m}$ , some photons with energy between 1.2 eV and 2.4 eV, reach the i-CdS layer where they make it photoconducting, i.e. weakly n-type. Photons with energies greater than 2.4 eV are absorbed in the  $\text{Cu}_2\text{S}$  layer. The greater the photon energy, the closer the absorption takes place to the surface illuminated.

The photons absorbed in the Cu<sub>2</sub>S layer create electron-hole pairs. The electrons, in spite of being minority carriers have a relatively long lifetime because of the indirect band gap. Consequently, they can diffuse to the Cu<sub>2</sub>S/CdS junction where they are collected by the junction field and transported into the n-CdS, whence they reach the ZnAg contact. The corresponding photoexcited holes meanwhile drift towards the gold contact where they are annihilated by incoming electrons. Recombination occurs in the bulk of the Cu<sub>2</sub>S, but chiefly at the interfaces, due to recombination centres. Thus photons of energy greater than 2.4 eV which are absorbed near the front surface are unlikely to contribute to the photocurrent. Hence the diminished response of the cell to high energy radiation.

# 1.7.3 Experimental Evidence

Some of the experimental evidence which supports the existence of the Cu-compensated i-layer is as follows:

- (1) The enhancement of the red part of the spectral response by simultaneous illumination with green (band gap of CdS) light.

- (2) The diminution of the green portion of the spectral response by an infra-red biasing light (quenching of photoconductivity).

- (3) The appearance of the above two effects only after the sensitising heat treatment of cells which indicates that the i-layer is formed by copper diffusion.

- (4) The decrease in cell capacitance by the heat treatment .

- (5) Enhancement of the spectral response at longer wavelengths by doping the n-CdS layer with indium. The photoconductive response of In-doped, Cu-compensated CdS extends to much longer wavelengths.

- (6) The cross-over of the dark and light I-V characteristics associated with the photoconductive effect in the i-CdS layer. No cross-over occurs in silicon cells.

- (7) The growth of the i-CdS with heat treatment results in a loss of tunnelling and shunting paths at the junction and consequently improves the 'squareness' of the I-V curves.

- (8) The series resistance of cells heated in vacuum or inert gas increases irreversibly. This effect is due to the growth of the copper i-layer by diffusion, and can be reduced by donor doping.

# 1.8 Stability and Degradation

In the assessment of the practical use of a cell, the stability and degradation are major factors. Therefore, in recent years, a large amount of money has been spent on life-testing cells in hostile environments, such as desert conditions with extremes of temperature. These experiments are not only designed to test the performance of the cell itself, but also of the packaging, anti-reflection coatings etc.

The  ${\rm Cu}_2{\rm S/CdS}$  heterojunction is subject to a number of degradation mechanisms (W. Palz et al, 1970, 1973; Mytton et al, 1972; Shiozawa et al, 1969).

- (1) The polycrystalline surface is reactive with oxygen in the atmosphere.

- (2) The existence of other phases of copper sulphide besides Cu<sub>2</sub>S (chalcocite) presents possibilities for degradation.

- (3) The mobility of  $\operatorname{Cu}^{\dagger}$  as an ion in  $\operatorname{Cu}_2\operatorname{S}$  is a mechanism for ionic segregation when a potential difference is developed across the  $\operatorname{Cu}_2\operatorname{S}$ .

- (4) Cu diffusion into CdS provides another mechanism for degradation,

migration occurring via Cu<sup>+</sup> vacancies. The diffusing copper leads to the growth of the i-CdS layer which results in increased series resistance of the cell. This effect can be reduced by the introduction of donors into the CdS.

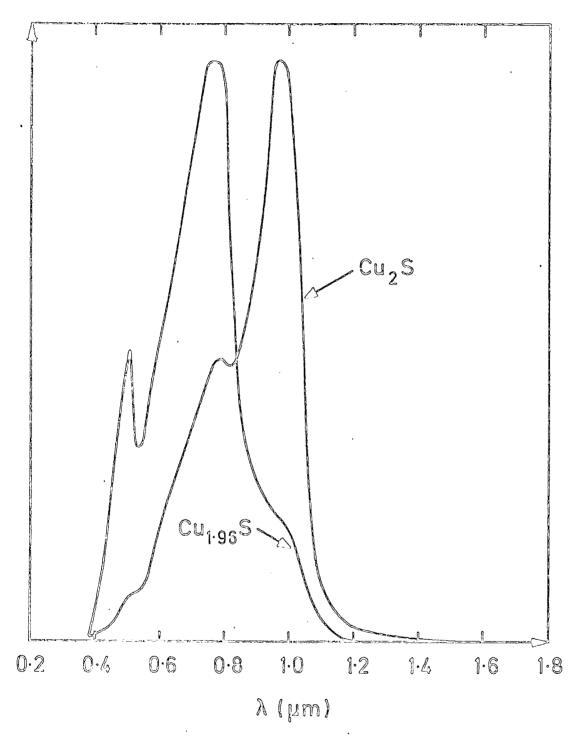

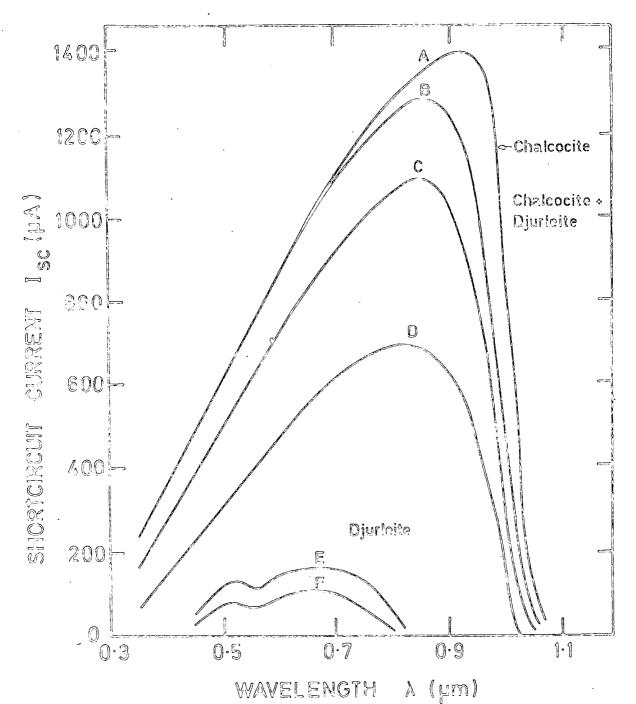

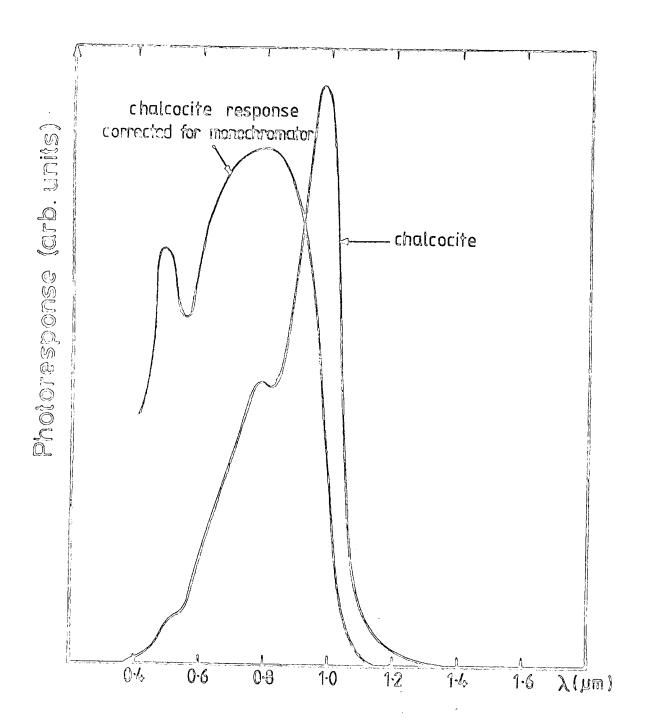

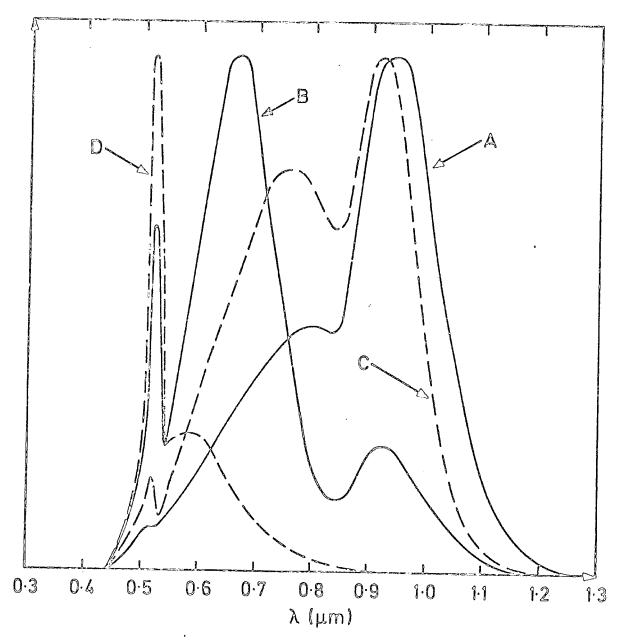

The composition of the copper sulphide layer affects the spectral response of the short circuit current and open circuit voltage and their magnitudes vary considerably (Palz et al 1972). This will be discussed in greater detail later. The quantum efficiency of cells with orthohombic chalcocite (Cu<sub>2</sub>S) layers is the highest, but is reduced as the composition of the copper sulphide changed by chemical reaction with the atmosphere.

Copper sulphide can also exist as  $\text{Cu}_{1.96}\text{S}$  (Djurleite), and  $\text{Cu}_{1.8}\text{S}$  (Digenite). In addition, there is at least one hexagonal phase of  $\text{Cu}_{x}\text{S}$  where x is nearly 2 (Cook et al 1970). X-ray studies by Shiozawa et al (1969) have revealed that typical degradation accompanies a change from Cu-rich to Cu-deficient copper sulphide due to oxidation. This causes a reduction in the short circuit current. Studies of the output from cells prepared with different  $\text{Cu}_{x}\text{S}$  compositions show that there is a gradual decrease in S.C.C. as x decreases, exactly the same as with ageing. The best results are obtained when x = 2.0, i.e. when the copper sulphide layer is composed of chalcocite.

Degradation is enhanced at higher temperatures and different effects occur in vacuum and in air. In vacuum, the series resistance of the cell increases, as expected, since the resistivity of semiconducting n-CdS increases after heating in vacuum. Heating in air, conversely, oxidises the copper sulphide and lowers the S.C.C. while leaving the series resistance substantially unaltered.

Various means of reducing the effects of the various degradation mechanisms have been reported, e.g. by doping the CdS (Palz et al, 1973), or using a special etch solution (Mytton et al, 1972) or depositing excess copper (Bogus and Mattes, 1972) to act as a 'reservoir' when

degradation mechanisms attempt to reduce the copper concentration of the Cu\_S.

In this thesis, the conditions under which the various phases of copper sulphide can be prepared on cadmium sulphide will be discussed, as will their effect on the spectral response of the cell. Post-deposition phase changes will also be discussed. The possible role of interface states at the junction of the heterojunction will also be described following work on Metal-Insulator-Semiconductor devices on CdS. A modified model of the band structure of the heterojunction following the sensitising heat treatment has been developed to explain the spectral response of the O.C.V., S.C.C. and photocapacitance of devices with and without bias illumination. In addition, studies on electron barrier effects in II-VI semiconductors made with a scanning electron microscope will be discussed.

#### REFERENCES

#### CHAPTER 1

Adams W.G. and Day R.E. (1876) Proc. Royal Soc. A25, 113.

Becquerel H. (1839) Compt. Rend. 9, 145.

Bockemuehl R.J., Kauppila J.E. and Eddy D.S. (1961) J.Appl.Phys., 32, 1324.

Bogus K. and Mattes S. (1972) Proc.9th P.V. Spec. Conf, p 121.

Chamberlain R.R. and Skarman J.S. (1966) Sol.St.Electron., 9, 819.

Cook W.R., Shiozawa L.R. and Augustine F. (1970), J.Appl. Phys., 41,3058.

Duc Cuong N. and Blair J. (1966) J.Appl. Phys. 37, 1660.

Elster J. and Geitel H. (1895) Wied. Ann. 55, 685.

Fonash S. J. (1976) Thin Solid Films 36, 387.

Gill W.D. and Bube R.H. (1970) J.Appl.Phys. 41, 3731.

Grimmeis H.G. and Memming R. (1962) J.Appl.Phys. 33, 2217, 3596.

Grondahl L.O. and Geiger P.H. (1927) Trans. A.I.E.E., 46, 357.

Hallwachs W. (1888) Ann. Physik, 33, 301.

Hertz H. (1887) Ann. Physik, 31, 421, 983.

Hill E.R. and Keramidas B.G. (1966) Rev. de. Phys. Appl. 1, 189.

Keating P.N. (1965) J.Appl. Phys., 36, 564.

Lange B. (1936) "Die Photoelemente und Ihre Anwendung", J.A.Barth, Leipzig.

Lenard P. (1900) Ann. Physik 2, 359.

Lindquist P. and Bube R.H.(1972) J.Appl.Phys. 43, 2839.

Loferski J.J. (1956) J.Appl.Phys. 27, 7/7.

Mytton R.J. (1968) J. Phys. D: Appl. Phys. 1, 721.

Mytton R.J., Clark L., Gale R.W. and Moore K. (1972) Proc.9th P.V. Spec.Conf., p 133.

Palz W., Besson J., Fremy J., Nguyen Duy T. and Vedel J. (1970)

Proc. 8th P.V. Spec. Conf., p 16.

Palz W., Besson J., Nguyen Duy T. and Vedel J. (1972) Proc. 9th P.V. Spec. Conf., p 91. Palz W., Besson J., and Nguyen Duy T. (1973) Proc. 10th P.V. Spec. Conf., p 69.

Palz W. (1979) Proc.2nd E.C. Photovoltaic Solar Energy Conf., Berlin, p 49.

Potter A.E. and Schalla R.L. (1967) N.A.S.A. Tech.Report D-3849.

Rappaport P. and Magid L.M.(1979) Proc. 2nd E.C.Photovoltaic Solar Energy Conf. Berlin, p 20.

Reynolds D.C., Leies G., Antes L.L. and Marburger R.E. (1954)

Phys. Rev., 96, 533.

Schottky W. (1930) Phys. Zeits. 31, 913.

Schottky W. (1931) Phys. Zeits. 32, 833.

Shiozawa L.R., Sullivan G.A. and Augustine F. (1967) Aerospace Research Labs., Report ARL 67-0190.

Shiozawa L.R., Augustine F., Sullivan G.A., Smith J.M. and Cook W.R. (1969) Aerospace Research Labs., Report ARL 69-0155.

"Solar Energy for Development" E.E.C. Conf. Varennes, Italy, March 1979.

Smith W. (1873) Am.J.Sci. 5, 301.

Te Velde T.S. (1967) Performance forecast of selected static energy conversion devices, 927, Agard.

Te Velde T.S.(1973) Solid St. Electron. 16, 1305.

Van Aershodt A.E., Capart J.J., David K.H., Fabricotti M., Heffels K.H., Loferski J.J. & Reinhartz K.K. (1968) Proc.7th P.V. Spec. Conf, p 30.

Williams R. and Bube R.H. (1960) J.Appl. Phys. 31, 968.

Wolf M. (1960) Proc. I.R.E. 48, 1246.

Woods J. and Champion J.A. (1959) J. Electron. & Control. 7, 243.

Wysocki J. J. and Rappaport P. (1960) J.Appl. Phys. 31, 571.

#### CHAPTER 2

# BASIC THEORY OF SCHOTTKY AND MIS DEVICES

#### 2.1 Introduction

As previously mentioned, interface states at the CdS/Cu<sub>2</sub>S boundary are thought to lower the efficiency of the solar cell by acting as recombination paths for free holes and electrons. They are also likely to control or affect the magnitude of the barrier height and hence the value of open circuit voltage (O.C.V.). Part of the work reported in this thesis has therefore been carried out in an attempt to investigate their properties with the ultimate aim of reducing their density, or at least decreasing their effects on efficiency.

Because the CdS/Cu<sub>2</sub>S heterojunction is a very complex device, it was anticipated that effects other than those directly concerned with interface states might obscure the experimental observations. Therefore, in an initial preliminary study, Metal-Insulator-Semiconductor (MIS) structures were fabricated on CdS, and measurements of their properties were made in the hope that these structures would prove simple to interpret. The theoretical basis of that work is outlined in what follows.

#### 2.2 Metal-Semiconductor Contact

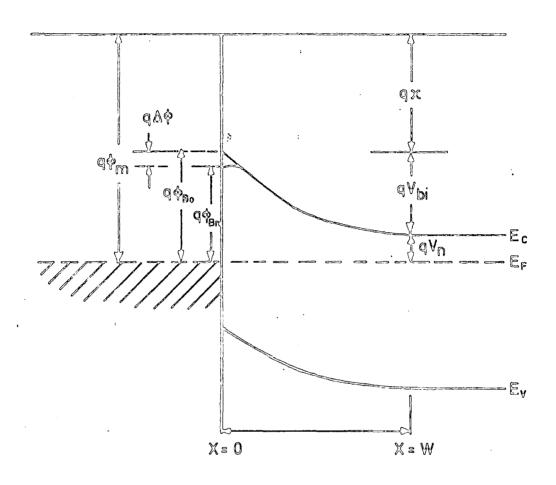

When a metal is brought into intimate contact with a semiconductor and thermal equilibrium is established, the Fermi levels of the two materials must be coincident. In general, for this to happen, there must be a transfer of charge between metal and semiconductor. If the work function of the metal is  $\phi_m$  and that of the n-type semiconductor is  $\phi_{_{\rm S}}$ , and  $\phi_m > \phi_{_{\rm S}}$  then a flow of electrons from the semiconductor to the metal will occur. This results in a bending of the semiconductor bands at the interface, as shown in Figure 2.1. In the absence of surface states, the amount of band bending simply accommodates the difference between the two

FIG. 2-1 ENERGY BAND DIAGRAM OF A METAL-n-TYPE SEMICONDUCTOR CONTACT

work functions. This potential difference,  $q \phi_m - q(\chi + V_n)$  is known as the contact potential, where  $q\chi$  is the electron affinity of the semiconductor measured from the bottom of the conduction band to vacuum level, and  $q V_n$  is the energy difference between the Fermi level and the conduction band in the bulk. If Schottky barrier lowering and the possible presence of an interfacial layer are neglected, the barrier height is given by:

$$q\phi_{Bn} = q(\phi_m - \chi) \tag{2.1}$$

In the presence of a large number of surface states, when the interfacial layer is thin, a small change in band bending would be accompanied by a large alteration in charge, because the surface states will be in equilibrium with the metal. Thus they would tend to pin the barrier relative to the Fermi level in the metal, the barrier height being determined by the surface states independently of the metal work function. With an interfacial layer thicker than  $\sim 30$  Å the surface states are in equilibrium with the semiconductor (Card and Rhoderick 1971). As the thickness of interfacial layer increases, the device behaves less like an ideal Schottky diode; the case of an MIS diode will be discussed later. In what follows an ideal contact is considered between a metal and a uniform n-type semiconductor. For simplification, it is assumed that the charge density,  $\rho$ , in the semiconductor is given by  $\rho = qN_D$  ( $N_D$  = donor doping density) for x < W and  $\rho$  = 0 for x > W (W = depletion width). Integration of Poisson's equation with these boundary conditions yields

$$V(\dot{x}) = \frac{qN_{D}}{\varepsilon_{S}} (Wx - \frac{1}{2}x^{2}) - \phi_{Bn}$$

(2.2)

Electric field

$$\left| E(\mathbf{x}) \right| = \frac{qN_D}{\varepsilon_S} \quad (W - \mathbf{x})$$

(2.3)

Depletion width

$$W = \left[\frac{2\varepsilon}{qN_D} (V_{bi} - V - \frac{kT}{q})\right]^{\frac{1}{2}}$$

(2.4)

Here  $\varepsilon_s$  is the permittivity of the semiconductor,  $V_{bi}$  is the diffusion potential at zero bias, and  $\frac{kT}{q}$  arises from the kinetic energy of the mobile charge carriers. The space charge  $Q_{SC}$  per unit area, assuming total ionisation of the donors and the depletion capacitance per unit area are given by

$$Q_{SC} = qN_{D}W = \left[2q\varepsilon_{S}N_{D}(V_{bi} - V - \frac{kT}{q})\right]^{\frac{1}{2}}$$

(2.5)

and

$$C = \frac{\partial Q_{SC}}{\partial V} = \left[ \frac{q \varepsilon_{S}^{N} D}{2(V_{bi} - V - \frac{kT}{q})} \right]^{\frac{1}{2}} = \frac{\varepsilon_{S}}{W}$$

(2.6)

Thus the depletion layer capacitance is voltage dependent, and inversely proportional to the depletion width, similar to an ordinary parallel plate capacitor. Equation (2.6) may be written more usefully as:

$$\frac{1}{c^2} = \frac{2(V_{\text{bi}} - V - \frac{kT}{q})}{q \varepsilon_s N_D}$$

(2.7)

Providing that  $N_D$  remains constant throughout the depletion width, a plot of  $\frac{1}{c^2}$  against V should produce a straight line, the voltage intercept of which gives the diffusion potential  $V_{bi}$  while the gradient yields the donor density,  $N_D$ . If there are electron traps present in the depletion layer, then when a large reverse bias is applied to the diode, and the Fermi level drops relative to the semiconductor bands, some traps will empty. Depending on whether or not the trap concentration is large compared with the donor density, a plot of  $\frac{1}{c^2}$  against bias will be either a straight line or have a downward concave curvature (Goodman 1963).

# 2.3 Conduction in Schottky Diodes

The normal means of forward conduction in an n-type Schottky diode is by transport of electrons from the semiconductor over the barrier into the metal. There are other processes which can occur, and these cause the deviations from ideality which are found in real diodes. Henisch (1957) gives a summary of the early work in this field. Some examples of the mechanisms are (i) injection of holes into the neutral region of the semiconductor (Green and Shewchun 1974), (ii) recombination of holes and electrons in the depletion region of the semiconductor via recombination centres (Yu and Snow 1968), and (iii) quantum mechanical tunnelling of electrons through the barrier (Padovani and Stratton 1966).

Several theories have been proposed to explain conduction over the barrier. The first of these, known as the diffusion theory, was put forward by Wagner (1931) and by Schottky and Mott (1939). In 1942 the thermionic emission theory was proposed by Bethe. This suggests that conduction occurs by the thermal emission of electrons over the barrier into the metal. It assumes that the quasi-Fermi level in the semi-conductor is constant and hence that the mean free path  $\lambda$  is long compared with the depletion width. Both theories result in the same form of equation

$$J = J_{S} \left( \exp \left( \frac{eV}{kT} \right) - 1 \right)$$

(2.8)

but in the diffusion theory  $J_s$  is field dependent while in the thermionic model  $J_s$  is more temperature dependent. Bethe's theory accurately describes the current when  $E_{max}$   $\lambda > \frac{kT}{q}$  where  $E_{max}$  is the maximum field in the barrier and  $\lambda$  is the mean free path of electrons. When this condition is not satisfied, the diffusion theory is more accurate. Crowell and Sze (1966) developed a theory which combines these two to form one of universal applicability. This is done by the introduction of

a recombination velocity,  $V_{\rm p}$ , for electrons at the metal semiconductor interface. Then, depending on whether the effective electron diffusion velocity within the depletion region  $V_{p}$  is less than or greater than  $V_{p}$ , the diffusion or thermionic emission theories apply respectively. In his book, "Metal-Semiconductor Contacts", Rhoderick shows that in terms of an energy band .diagram, the basic difference between the diffusion and thermionic emission theories lies in the location of the quasi-Fermi level for electrons at the barrier. The quasi-Fermi level is the hypothetical energy level which gives the correct concentration of electrons, if inserted into the Fermi-Dirac distribution function even though the system is not in true thermal equi-Far from the junction, the quasi-Fermi level must coincide with librium. the Fermi levels in the metal and the semiconductor respectively. In the diffusion theory, the quasi-Fermi level is coincident with the metal Fermi level at the junction, rising (in forward bias) to join the semiconductor level within the depletion region. The thermionic emission theory, on the other hand, requires the quasi-Fermi level through the semiconductor to remain constant, dropping (in forward bias) within the metal. (1972) has found that the thermionic emission theory describes the currentvoltage characteristics of Au/CdS diodes very adequately.

#### 2.4 Measurement of Barrier Height

The most common techniques for measuring barrier heights in metal-semiconductor diodes utilise C-V, I-V and photoelectric threshold measurements. In the first two of these, the diode has to be biased and thus is perturbed by an external field, whereas with the photoelectric method, the measurement is direct and therefore can be most accurate.

# 2.4.1 Capacitance-Voltage Characteristics

It has already been shown that it is possible to measure barrier height

and donor concentration by this method. In a real device it may be necessary to consider an equivalent circuit, which in the absence of an interfacial layer may consist of a conductance, G, and capacitor, C, in parallel, both voltage dependent, together with a resistor, r, in series, corresponding to the semiconductor bulk resistance. Since it is possible only to measure the admittance and hence G' and C' for the combination of components, there will be restrictions on the use of the simple theory to predict results of experiments. It can be shown quite simply that if rG << 1 and  $\omega^2 r^2 C^2$  << 1, G and C correspond to the measured values, where  $\omega$  is the a.c. frequency of the bias voltage. C and G are both frequency dependent because of the effects of trapped charge; however, this dependence may be reduced by using a frequency high enough so that the traps are not excited by the a.c. signal.

### 2.4.2 Effect of Interfacial Layer

It has been shown by Crowell et al (1965), that an interfacial layer of non-zero thickness must exist between metal and semiconductor even when both are in intimate atomic contact. This affects the measured barrier height which is in fact a function of the thickness of the layer. Cowley, (1966) proved that for a device with an interfacial layer but without surface states, the voltage intercept,  $V_{o}$ , of a plot of  $\frac{1}{c^2}$  versus V is:

$$V_{o} = V_{bi} - \frac{kT}{q} + \frac{V_{1}}{4} + (V_{1}V_{bi})^{\frac{1}{2}}$$

(2.9)

where

$$v_{1} = \frac{2 q \varepsilon_{s} N_{D} d_{i}^{2}}{\varepsilon_{i}^{2}}$$

(2.10)

V = diffusion potential at zero bias

d; = thickness of the interfacial layer

$\varepsilon$  = permittivity of semiconductor

$\varepsilon_{i}$  = permittivity of interfacial layer

He extended the theory to cover a contact with a uniform density of surface states in equilibrium with the metal surface. This corresponds to an interfacial layer less than  $\sim 30$  Å thick with the Fermi level at the semiconductor surface remaining 'pinned' to the metal Fermi level (Card and Rhoderick, 1971). The equations from the previous section are altered by the inclusion of a voltage dependent surface state charge to modify the equation of Gauss' Law across the interface region. This yields a value of voltage intercept which can be shown to be equivalent to:

$$v_{o} = v_{bi} + \left[v_{1}^{\frac{1}{2}} \left(v_{bi} - \frac{kT}{q}\right)^{\frac{1}{2}}\right] / \left(1 + \alpha\right) + \frac{v_{1}}{4(1 + \alpha)^{2}} - \frac{kT}{q}$$

(2.11)

where

$$\alpha = qN_{ss} \frac{d_{i}}{\epsilon_{i}}$$

with  $N_{ss} = surface state density / eV/cm<sup>2</sup>$

Thus if the diffusion potential is known accurately (by photothreshold measurements for example) an estimate of the surface state density may be made from the value of the voltage intercept.

Another, more general approach is that of Crowell and Roberts (1969); their method does not require the limiting assumption of a constant surface state density. An n-type semiconductor with donor density  $N_D$  and surface state density  $N_{SS}/eV/cm^2$  is placed in contact with a metal with an interfacial layer of thickness  $\delta_i$  and permittivity  $\epsilon_i$ . A field E will exist at the surface of the semiconductor due to the ionised donors in the depletion region. If the applied bias is altered, or if there is a change in the doping concentration of the semiconductor, this field will change by an amount  $\Delta E$ , corresponding to a change in charge  $\epsilon \Delta E$  in the semiconductor. This will be accompanied by a similar variation in the charge in the surface states and metal to maintain overall neutrality. It gives rise to a change in the interface field and the density of filled

surface states, resulting in a barrier height alteration of  $\Delta \phi_{\text{Bm}}$ , thus:

$$\varepsilon_{s}^{\Delta E} = -q N_{ss}^{\Delta \phi}_{Bn} - \left(\frac{\varepsilon_{i}}{\delta_{i}}\right) \Delta \phi_{bn}$$

(2.12)

or

$$\frac{d\phi_{bn}(E)}{dE} = -\varepsilon_{s} \left[ qN_{ss} \div \left( \frac{\varepsilon_{i}}{\delta_{i}} \right) \right]^{-1}$$

(2.13)

Once again the assumption has been made that the occupation of surface states is determined by the Fermi level in the metal.

The quantity  $\frac{d\phi_{\rm bn}(E)}{dE}$  will affect the capacitance voltage characteristic. From Poisson's equation in the depletion region the expression

$$E^{2} = \frac{2qN_{D}}{\varepsilon_{c}} \left(\phi_{Dn} - \phi_{n} - v - \frac{kT}{q}\right) \qquad (2.14)$$

can be derived. Here  $q\phi_{\,n}$  is the energy difference between the conduction band and the Fermi level in the bulk of the semiconductor. The depletion capacitance can be written as

$$C = \varepsilon_{s} \left( \frac{dE}{dV} \right)$$

(2.15)

Differentiation of (2.14) with respect to E gives:

$$\frac{dV}{dE} = -\left(\frac{\varepsilon_s E}{qN_D}\right) + \frac{d\phi_{bn}}{dE}$$

(2.16)

and hence

$$\frac{1}{c^2} = \frac{2}{\varepsilon_s q N_D} \left[ \phi_{bn} - V - \phi_n - \frac{kT}{q} - E \left( \frac{d\phi_{bn}}{dE} \right) + \frac{q N_D}{2\varepsilon_s} \left( \frac{d\phi_{bn}}{dE} \right)^2 \right]$$

(2.17)

This equation shows that if

$$\left[ \left( \frac{\mathrm{qN}_{\mathrm{D}}}{\varepsilon_{\mathrm{S}}} \right) \left( \frac{\mathrm{d}^{\varphi}_{\mathrm{bn}}}{\mathrm{dE}} \right) - \mathrm{E} \right] \left( \frac{\mathrm{d}^{2}^{\varphi}_{\mathrm{bn}}}{\mathrm{dE}^{2}} \right) \left( \frac{\mathrm{dE}}{\mathrm{dV}} \right) << 1$$

(2.18)

then the slope of the plot of  $1/C^2$  versus V gives the donor density. The voltage intercept,  $V_i$ , leads to an apparent barrier height  $\phi_a$  defined by

$$\phi_{a} = V_{i} + \phi_{n} + \frac{kT}{q} = \phi_{bn} - E\left(\frac{d\phi_{bn}}{dE}\right) + \left(\frac{qN_{D}}{2\epsilon_{s}}\right)\left(\frac{d\phi_{Bn}}{dE}\right)^{2} \quad (2.19)$$

As the term  $\left(\frac{d\phi_{bn}}{dE}\right)$  is always negative as defined, the true barrier height must always be less than that measured. This equation is directly equivalent to (2.11) above.

#### 2.4.3 Photoelectric Threshold

It has already been stated that the photoelectric method of measuring barrier height is most direct. The theory will now be outlined. Under illumination with monochromatic light of energy hv , the metal surface of a metal-semiconductor junction can emit an electron over the barrier into the semiconductor if hv >  $q\phi_{bn}$ . If the light is incident on a thin metal layer, and the photon energy hv is greater than the band gap  $E_g$  of the semiconductor, electron-hole pairs will be produced in the depletion region and then separated by the internal field. In the open-circuit configuration this will cause a photovoltage to appear across the device. If the illumination is from the back, (i.e. via the semi-conductor) the same photoelectric emission process from metal to semi-conductor is observed, however if hv > Eg then the light will be very strongly absorbed at the back contact and the electron-hole pairs will simply recombine in the absence of a field to separate them.

According to the theory developed by Fowler (1931), the photoemissive current produced by each incident photon is given by:

$$R \approx \frac{T^2}{\sqrt{E_s - h\nu}} \left[ \frac{x^2}{2} \div \frac{\pi^2}{6} - \left( e^{-x} - \frac{e^{-2x}}{4} + \frac{e^{-3x}}{9} \dots \right) \right] \text{ for } x > 0$$

(2.20)

where E is the sum of hv (  $\equiv$  q $\phi$  ) and the Fermi energy measured from the bottom of the metal conduction band  $x \equiv \frac{hv - hv}{kT}$ . Subject to the conditions that E  $_{S}$  >> hv and x > 3, the above equation simplifies to

$$R \simeq (hv - hv_0)^2 \tag{2.21}$$

or the form in which it will be used later ,

$$\sqrt{R} \simeq hv - hv$$

(2.22)

# 2.4.4 Current-Voltage Characteristics

The current flowing in an ideal Schottky diode under the conditions of thermionic emission is given by

$$J = A^*T^2 \exp\left(-\frac{q\phi_{bn}}{kT}\right) \left(\exp\frac{qV}{kT} - 1\right)$$

(2.23)

where  $A^*$  is the modified Richardson constant.  $\phi_{\rm bn}$  is the true barrier height and is a function of voltage because of the barrier lowering of the image force.

$$\phi_{\rm bn} = \phi_{\rm bo} - \Delta \phi \tag{2.24}$$

where  $\Delta \phi = \sqrt{\frac{qE}{4\pi\epsilon}}$  and E is the field at the semiconductor surface,

$$E = \left[\frac{2q N_{D}}{\varepsilon_{s}} \left(V_{Di} - V - \frac{kT}{q}\right)\right]^{\frac{1}{2}}$$

(2.25)

With forward bias  $V > \frac{3kT}{q}$ , the current density may be simplified to

$$J = A*T^{2} exp\left(-\frac{q \phi_{bo}}{kT}\right) exp \frac{q(\Delta \phi + V)}{kT}$$

(2.26)

However, because  $A^*$  and  $\Delta \phi$  are both voltage dependent, this equation can be rewritten

$$J = J_{S} \left( \exp \frac{qV}{nkT} \right)$$

(2.27)

where

$$n = \frac{q}{kT} \left[ \frac{d(\log_e J)}{dV} \right]^{-1}$$

(2.28)

Note that n, the so-called ideality factor, is a function of V, as defined here. More generally n is a function of barrier height and temperature as well as voltage. This is to embrace the non-ideality introduced by the mechanisms of current flow previously mentioned such as recombination in the depletion region and tunnelling through the barrier. As V tends to zero,  $\log_e J$  extrapolates back to  $\log_e J_S$  and therefore the barrier height is given by

$$\phi_{\text{bn}} = \frac{kT}{q} \log_e \left\{ \frac{A^*T^2}{J_c} \right\}$$

(2.29)

# 2.5 Metal-Insulator-Semiconductor (MIS) Diodes

The principle of the metal on insulator on semiconductor diode has very wide applications in the field of modern electronics, especially for memory devices which utilise the insulator properties to store a charge almost indefinitely. Another use is in high density logic circuits, relying on the fact that the controlling mechanism is an electric field, not the movement of carriers as in a bipolar device. The power dissipation is consequently much lower. In the field of device physics a study of MIS devices offers one of the most useful techniques for investigating semiconductor surfaces. Since the surface properties of a semiconductor material can determine the stability of a device, such a study is of great importance. It is worth noting that most theories of MIS diodes assume that the insulator is perfect, i.e. that it has a very large band gap, zero conductance, and

perfect uniformity of thickness. Space does not permit a detailed account of MIS theory. For this, "Semiconductor Surfaces" by Many et al, and "Physics of Semiconductor Devices" by Sze give a good comprehensive treatment. A brief outline of the operation of an MIS diode follows.

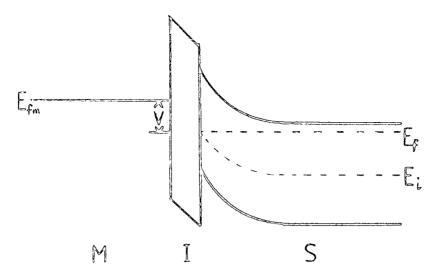

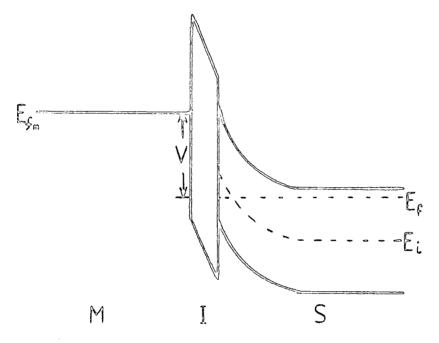

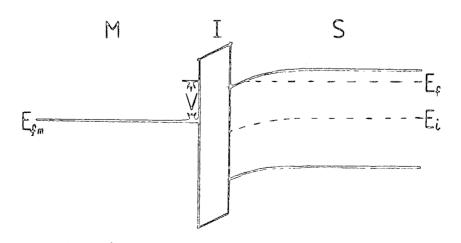

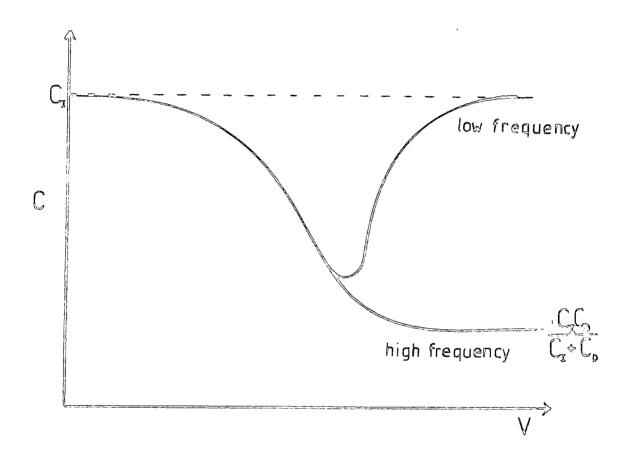

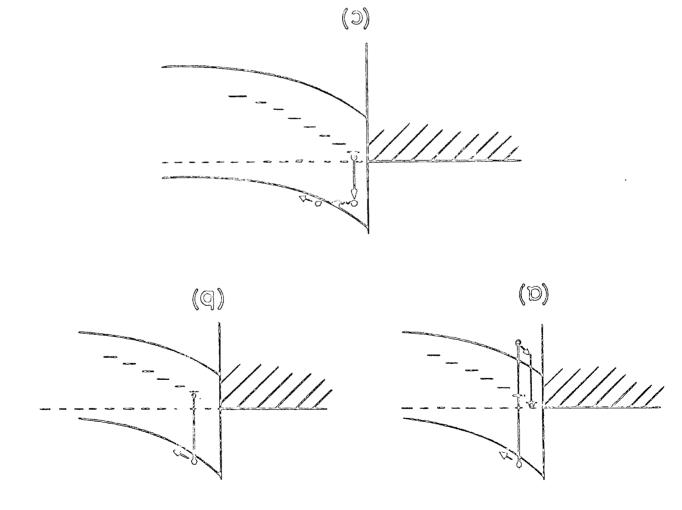

The energy band diagram of an MIS diode on an n-type semiconductor is shown in Figure 2.2. This depicts the semiconductor surface in the so-called depletion mode, i.e. there is a depletion region similar to that found in a Schottky diode. Hence the capacitance of the device can be considered as the series combination of an insulator and a depletion capacitance. If the applied voltage (reverse bias) is increased, the band diagram in Figure 2.3 results. Here  $E_{i}$ , the intrinsic Fermi level has crossed  $E_{f}$ at the surface. This implies that the number of minority carriers (holes) exceeds the number of majority carriers (electrons); the surface is thus inverted and the inversion mode has been formed. The capacitance of the device can be explained in the following way: a small change in voltage occurring slowly causes a change in the charge in the inversion layer and the charge at the metal-insulator interface. Thus the capacitance is simply that of the insulator alone. At high frequency, the charge in the inversion layer cannot follow the applied voltage and the capacitance is therefore that of insulator and depletion region capacitances in series.

When the applied voltage is reversed the band diagram is as shown in Figure 2.4. In this mode there is an accumulation of electrons at the insulator-semiconductor interface and therefore the capacitance becomes that of the insulator alone. The capacitance voltage curve therefore looks like that shown in Figure 2.5.

It can be demonstrated (Goetzberger and Sze, 1969) that  $\mathbf{C}_{\mathbf{D}}$  for an n-type semiconductor is given by:

Fig.22 In Depletion Mode

Fig.2.3 In Inversion Mode

Fig.2.4 In Accumulation Mode

Band Structure of MIS Diode (n-type semiconductor)

Fig. 2.5 Capacitance against Voltage for an MIS diode

$$C_{D} = \frac{\varepsilon_{S}}{\lambda_{n}} \frac{\left[1 - e^{-q\psi_{S}/kT} + \frac{P_{O}}{n_{O}} \left(e^{q\psi_{S}/kT} - 1\right)\right]}{G\left(\psi_{S}, \frac{P_{O}}{n_{O}}\right)}$$

(2.30)

where  $\lambda_n$  is the extrinsic Debye length for electrons,  $\psi_s$  is the surface potential (the band bending) of the semiconductor,  $n_o$  and  $p_o$  are the bulk densities of electrons and holes, and  $G(\psi_s, \frac{p_o}{n_o})$  is given by

$$G\left(\psi_{s}, \frac{p_{o}}{n_{o}}\right) = \left\{e^{q\psi_{s}/kT} - \frac{q\psi_{s}}{kT} - 1 + \frac{p_{o}}{n_{o}} \left[e^{-q\psi_{s}/kT} + \frac{q\psi_{s}}{kT} - 1\right]\right\}^{\frac{1}{2}}$$

(2.31)

The voltage applied across an MIS device is divided accordingly:

$$V = V_I + \psi_S + \phi_{mS}/q$$

$(V_I = insulator voltage)$  (2.32)

where

$$V_{I} = \frac{\varepsilon_{s}}{\lambda_{n}C_{I}} \times \frac{2kT}{q} \times G\left(\psi_{s}, \frac{p_{o}}{n_{o}}\right) \qquad (2.33)$$

and

$$\phi_{ms} = \phi_{m} - \phi_{s}$$

# 2.6 Interface States

The above theory applies to the case of a 'perfect' semiconductor surface, i.e. one without any surface states or traps. When surface or interface states are present they will affect both the capacitance and conductance of the device. A very detailed treatment has been given by Nicollian and Goetzberger (1967). The surface states are occupied according to the Fermi-Dirac distribution, and therefore each occupied state adds a capacitance of one electron charge. If as the applied voltage is altered, the Fermi level sweeps through the state and empties it, the capacitance will be reduced. The change is therefore in the form of a step. Interface

states, however, cannot capture or emit electrons infinitely quickly and thus a loss mechanism and time constant must be associated with them, this gives rise to a conductance. This situation should be compared with the ideal MIS device with zero conductance.

On application of an a.c. signal, the Fermi level varies with time, and according to Shockley and Read (1952), the capture rate of electrons, as majority carriers, by a single-level state is:

$$R_n(t) = N_S C_n \left[1 - f(t)\right] n_S(t)$$

(2.34)

and emission rate

$$G_n(t) = N_s e_n f(t)$$

(2.35)

where N  $_{\rm S}$  is the density of states/cm $^2$ , C  $_{\rm n}$  the electron capture probability,  ${\rm e}_{\rm n}$  the electron emission constant, f(t) the Fermi function at time t, and  ${\rm n}_{\rm S}$ (t) the electron density at the silicon surface at time t.

The net current density flowing is:

$$i_s(t) = q N_s C_n \left[1 - f(t)\right] n_s(t) - q N_s e_n f(t)$$

(2.36)

To simplify this, it is necessary to split the equation into d.c. and a.c. components.

$$f(t) = f + \delta f \qquad (2.37)$$

$$n_{s}(t) = n_{so} + \delta n_{s}$$

(2.38)

Substituting and neglecting second order terms, (small signal approximation) gives

$$i_s(t) = q N_s C_n \left[ (1 - f_o) n_{so} + (1 - f_o) \delta n_s - n_{so} \delta f \right] - q e_n N_s (f_o + \delta f)$$

(2.39)

It is also necessary that there should be d.c. equilibrium, i.e.  $R_n = G_n, \quad \text{therefore}$

$$qN_S^C_n = qe_n N_S^C_0$$

(2.40)

Substituting in equation (2.39)

$$i_{s}(t) = q N_{s} C_{n} \left[ (1 - f_{o}) \delta n_{s} - n_{so} (\delta f_{o}/f_{o}) \right]$$

(2.41)

This current can also be expressed by the time derivative of the Fermi function

$$i_s(t) = qN_s\left(\frac{df}{dt}\right)$$

(2.42)

Equating (2.41) & (2.42) gives

$$\frac{\mathrm{df}}{\mathrm{dt}} = C_{n} (1-f_{0}) \delta n_{s} - C_{n} n_{so} \delta f/f_{0}$$

For a sinusoidal a.c. signal  $\delta f = f_m e^{i\omega t}$ , so that  $\frac{df}{dt} = i\omega \delta f$

thus

$$\delta f = \frac{\int_{0}^{f} \frac{(1 - f) \delta n}{o s}}{\int_{0}^{n} \frac{(1 + i\omega f/c_{n})}{o n so}}$$

(2.43)

and

$$i_{s}(t) = \frac{i\omega q N_{s} f_{o} (1 - f_{o}) \delta n_{s}}{n_{so} (1 + i\omega f_{o}/C_{n} n_{so})}$$

(2.44)

From the Boltzmann relation  $n_s = n_{so} e^{(\psi_{so} - \psi_s)q/kT}$ , therefore

$$\frac{\delta n}{n} = \frac{q}{kT} \delta \psi_{S} \qquad (2.45)$$

and

$$i_s(t) = i\omega \frac{q^2}{kT} \frac{N_s f_o(1-f_o) \delta \psi_s}{(1+i\omega f_o/C_n)}$$

(2.46)

This may be written in terms of admittance as

$$i_{s}(t) = Y_{s} \delta \psi_{s} \tag{2.47}$$

therefore

$$Y_{S} = i\omega \frac{q^{2}}{kT} \frac{N_{SO}(1-f_{O})}{(1+i\omega f_{O}/C_{n} n_{SO})}$$

(2.48)

Equation (2.48) describes the admittance of an RC series network with capacitance  $C_S = q^2 N_S f_0 (1 - f_0)/kT$  and time constant  $\tau = f_0/C_n r_{so}$ . equivalent parallel capacitance of a single-level surface state is therefore

$$C = C_{s}/(1 + \omega^{2}\tau^{2})$$

(2.49)

and conductance

$$G = C_s \omega^2 \tau / (1 + \omega^2 \tau^2)$$

(2.50)

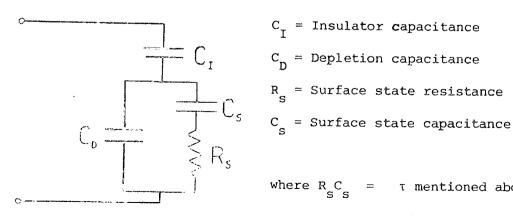

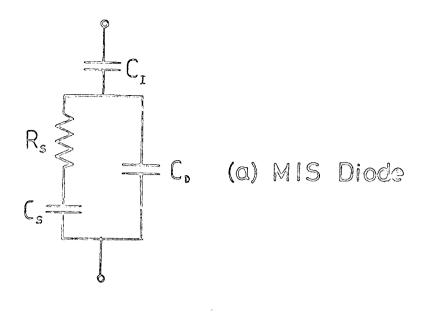

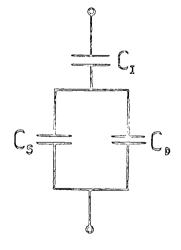

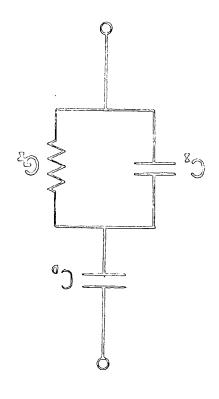

#### 2.7 Equivalent Circuit of an M.I.S. Device

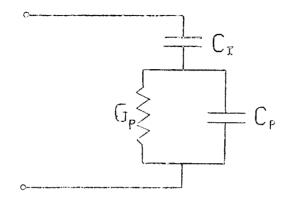

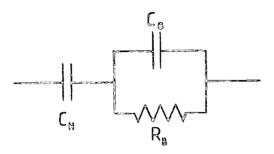

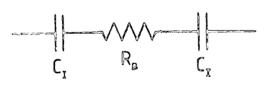

Since the total small signal a.c. current is obviously the sum of the contributions of the space charge and interface charge, and the potential  $\psi_{_{\mbox{\scriptsize S}}}$  is the same in both cases, this network must be in parallel with the depletion capacitance. The contribution from the insulator capacitance must be in series with this parallel combination, and therefore the equivalent circuit of the M.I.S. device with a single level of surface states is:

$C_{I} = Insulator capacitance$

$C_{I}$   $C_{D}$  = Depletion capacitance

where  $RC = \tau$  mentioned above.

Figure 2.6

This may be arranged in a more convenient way for comparison with experiment as

Figure 2.7

where

$$\frac{c_{\mathrm{g}}}{p} = \frac{c_{\mathrm{s}} \omega^2 \tau}{1 + \omega^2 \tau^2} \tag{2.51}$$

and

$$C_{p} = C_{D} + \frac{C_{s}}{1 + \omega^{2} \tau^{2}}$$

(2.52)

It is easily shown that  $G/\omega$  goes through a maximum when  $\omega\tau=1$  and  $C/\omega = \frac{S}{2}$ . Therefore, once the conductance has been corrected for the insulator capacitance,  $\tau$  and  $C/\omega = \frac{C}{S}$  may be found directly. The surface state density is then simply given by  $N/S = \frac{C/S}{QA}$  where A is the area of the contact.

# 2.8 Generalised Surface State Model

So far only the case of a single-level interface state has been considered. In general, there will be a continuum of states of varying density and capture cross-section. These complications will lower the maximum point and broaden the peak of the conductance curve by requiring integration over all the states. The peak, however, is still found to be

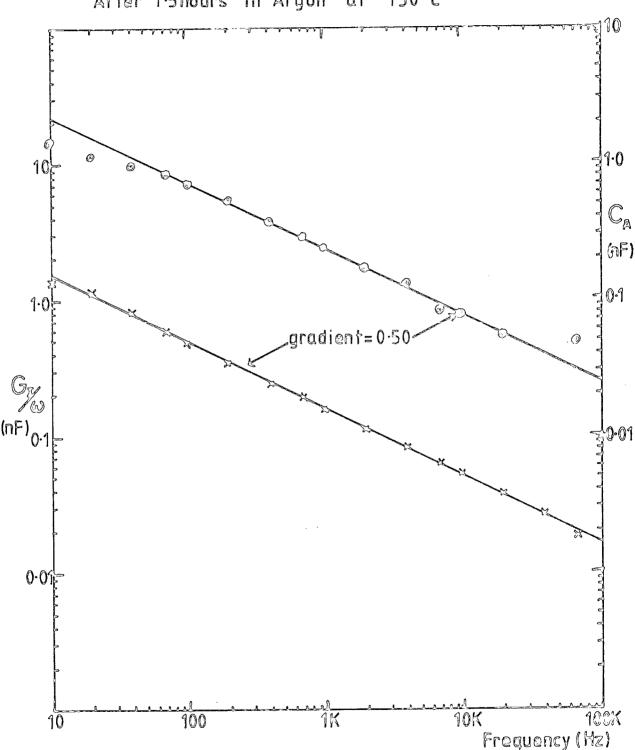

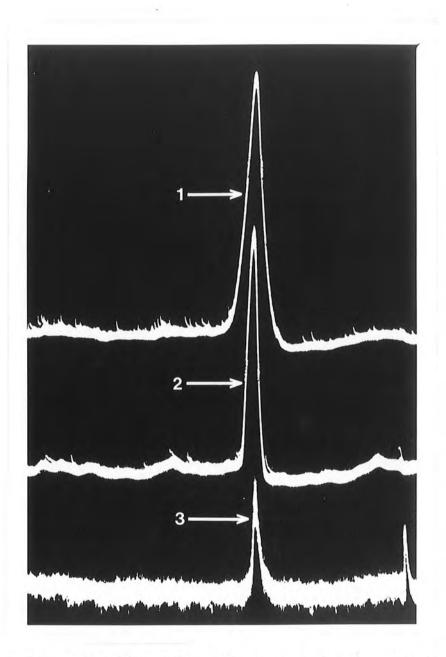

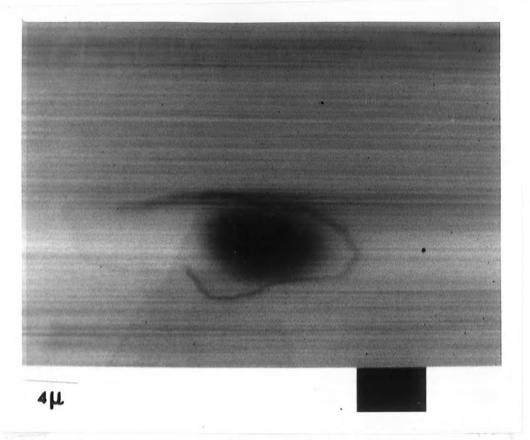

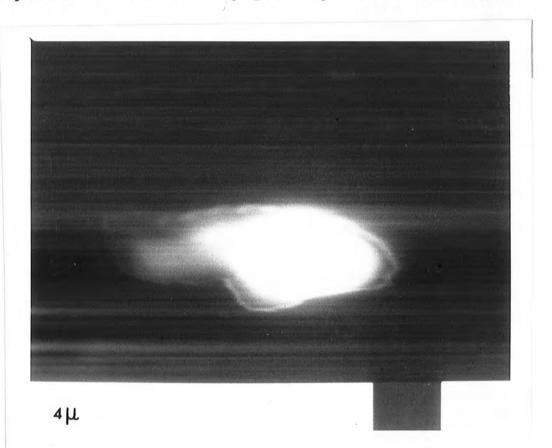

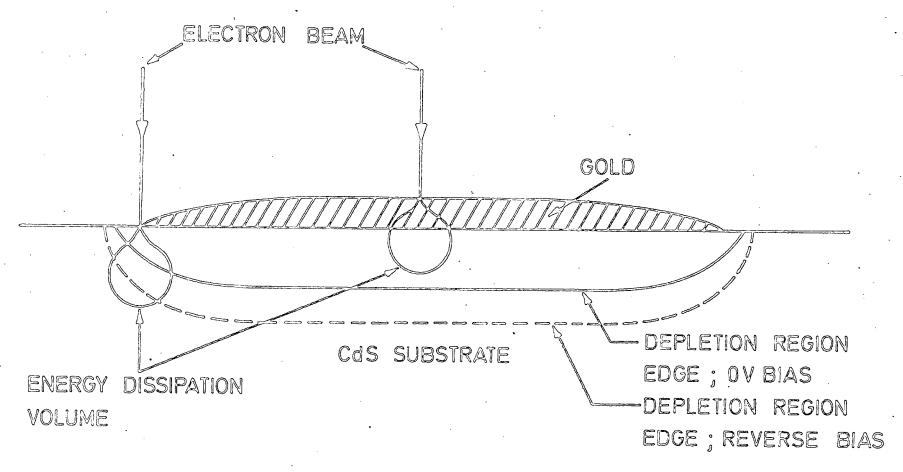

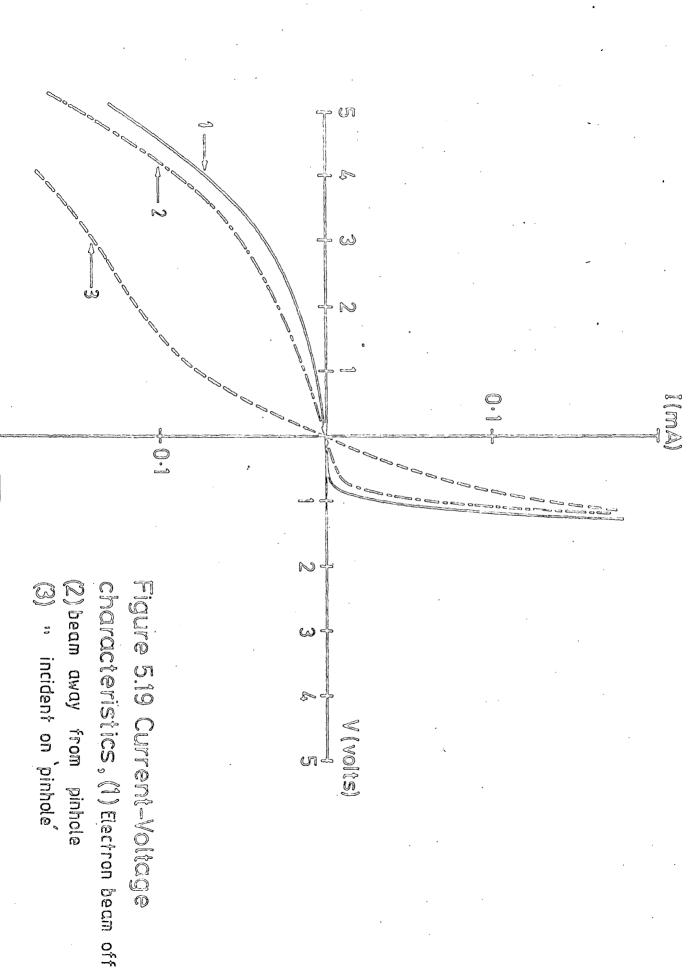

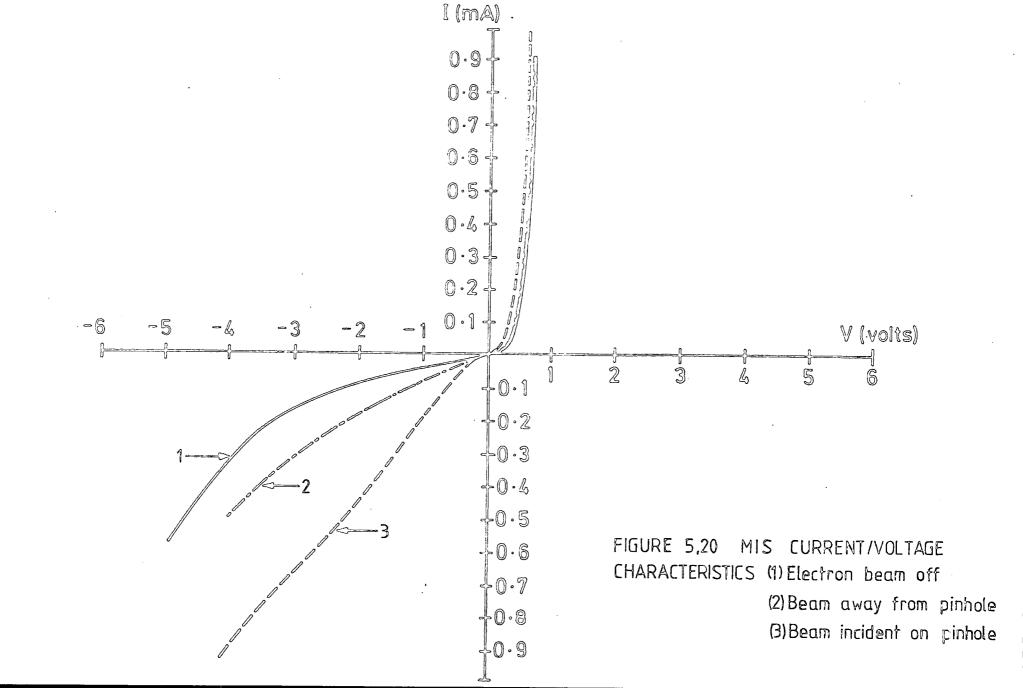

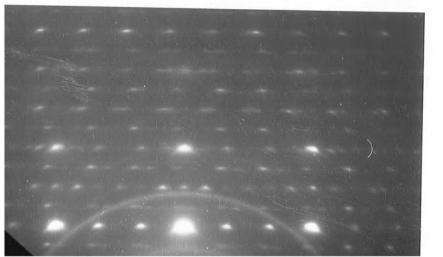

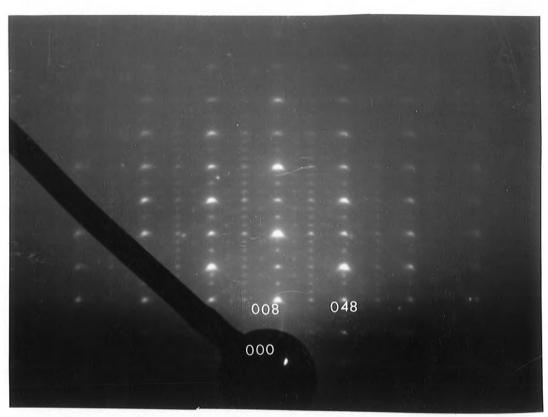

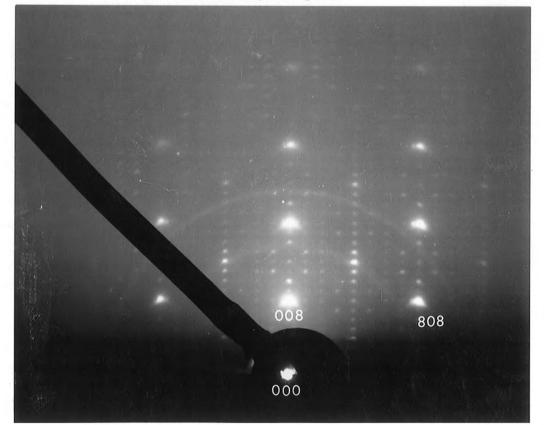

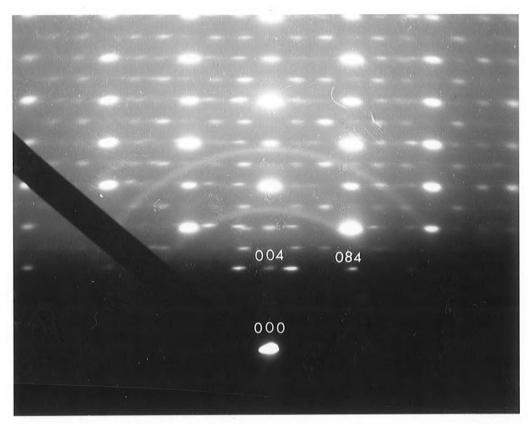

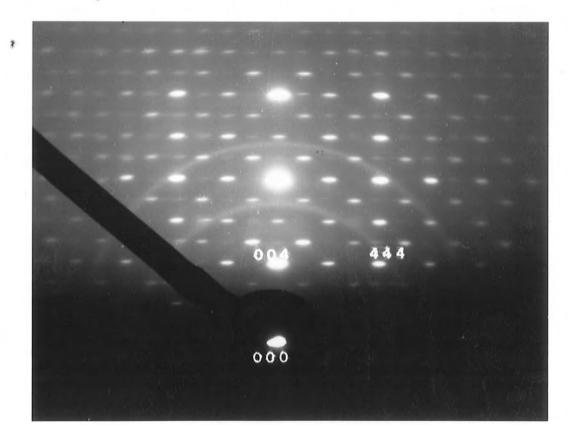

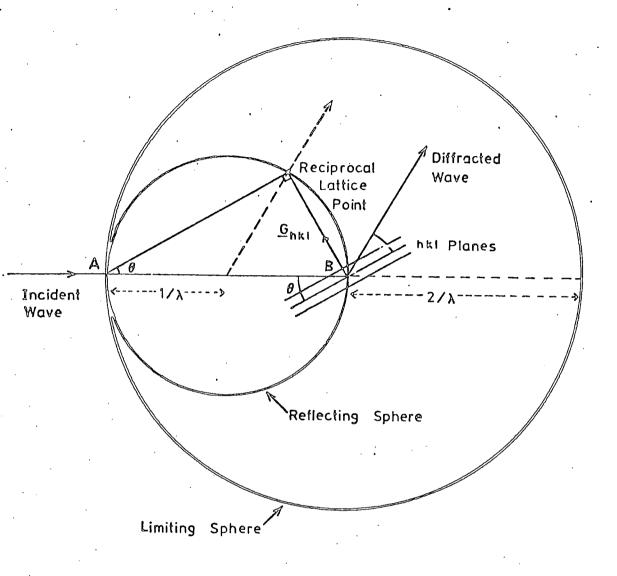

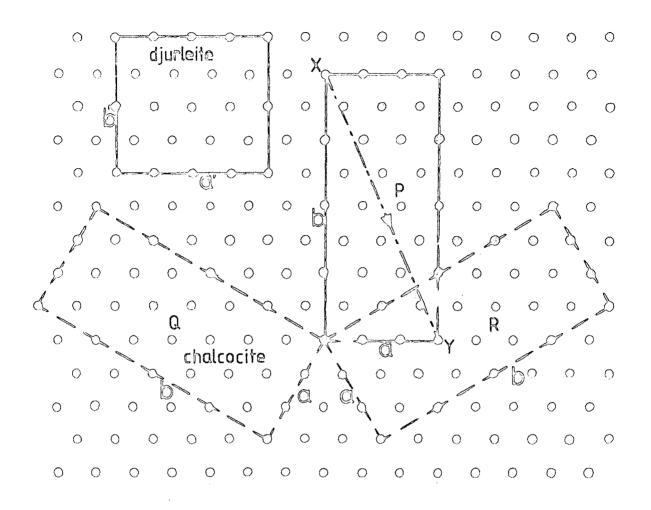

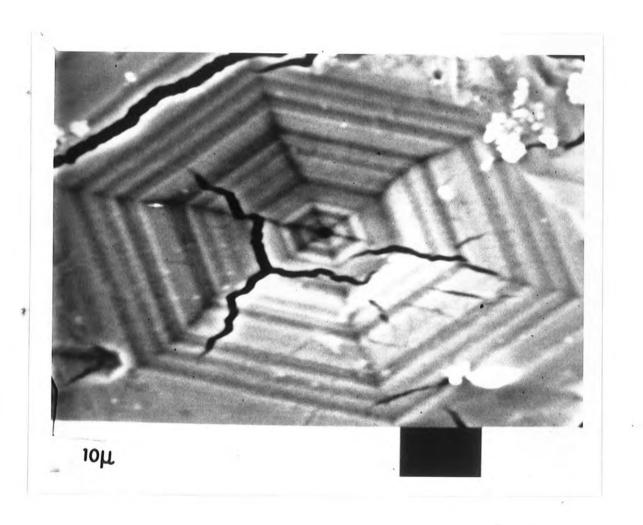

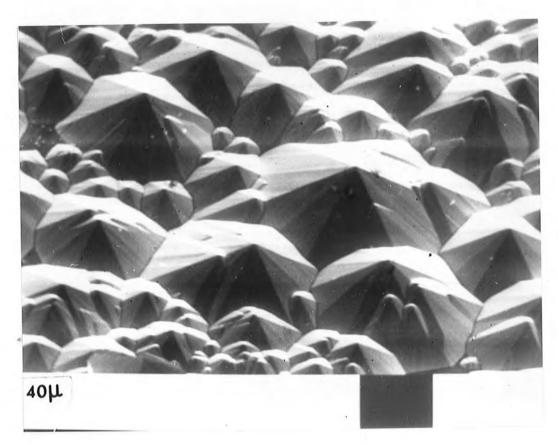

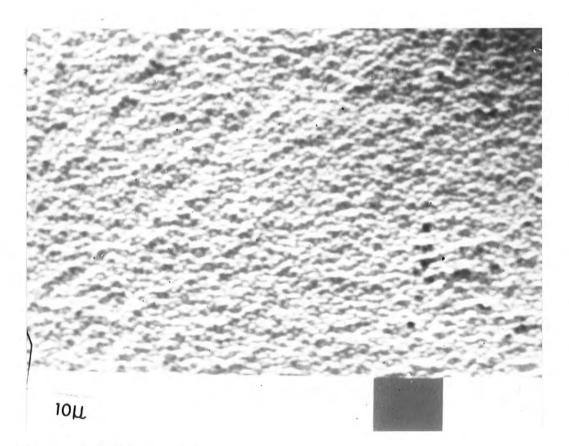

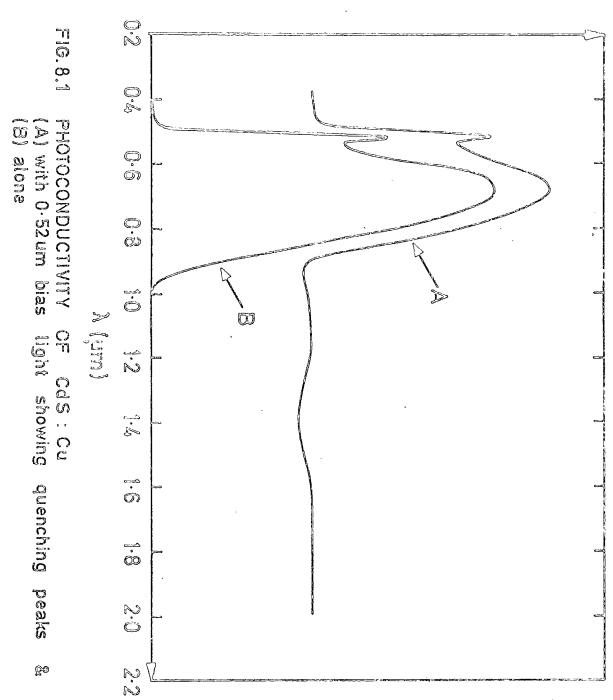

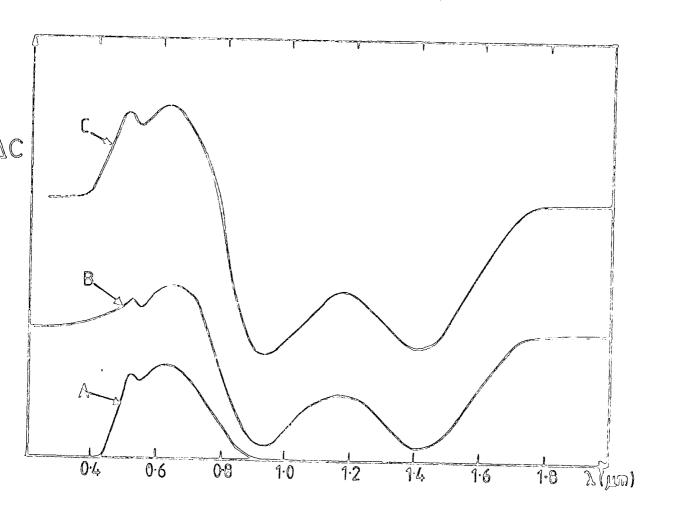

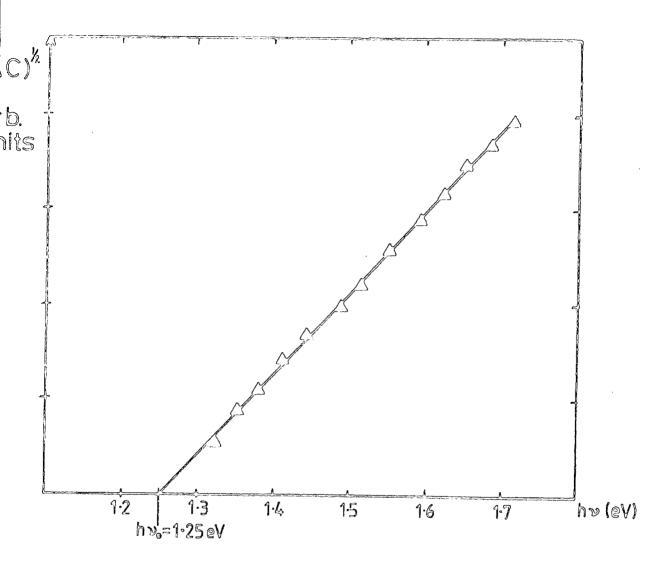

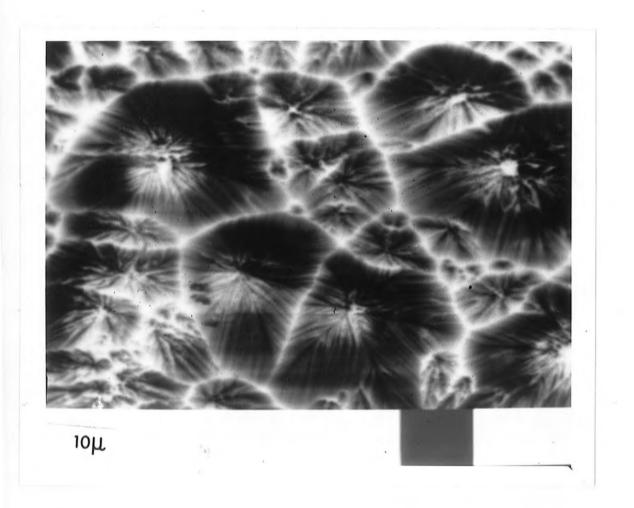

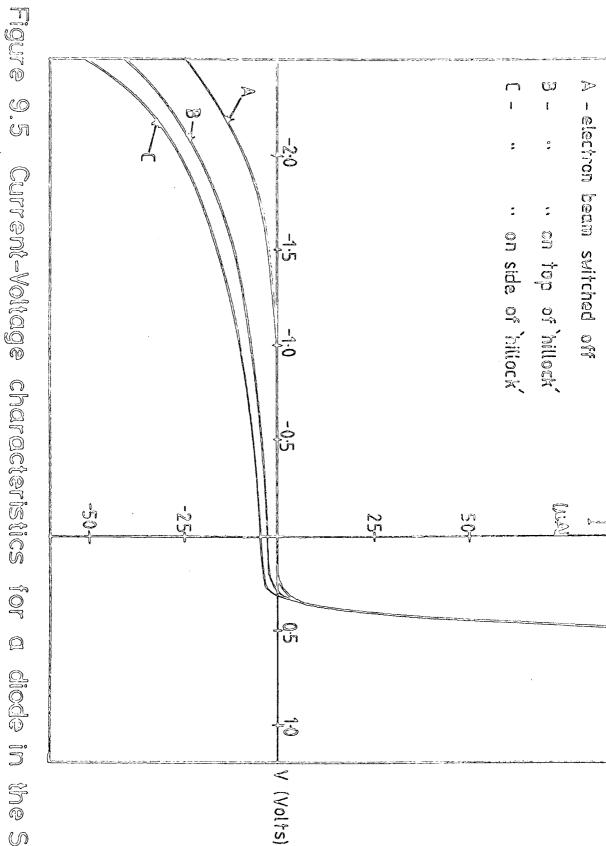

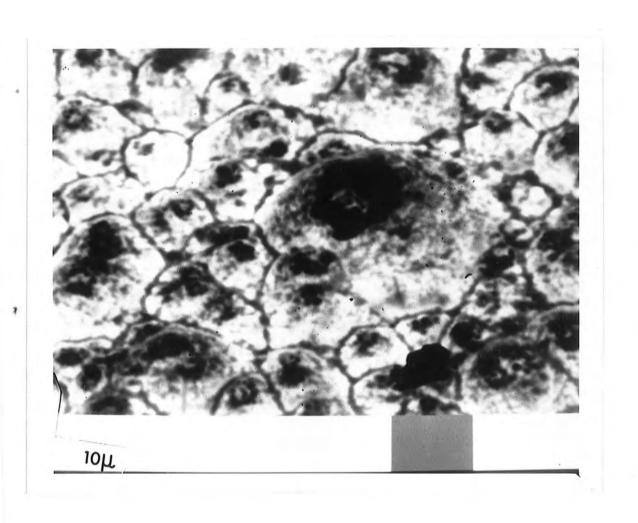

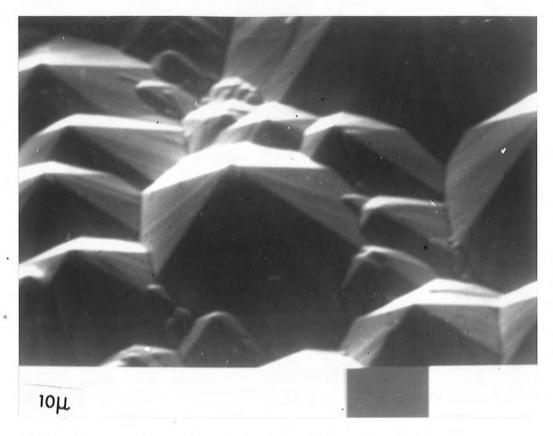

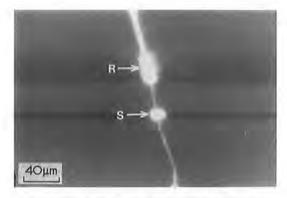

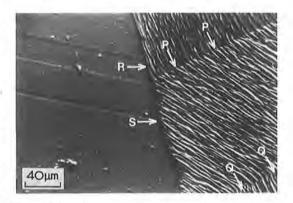

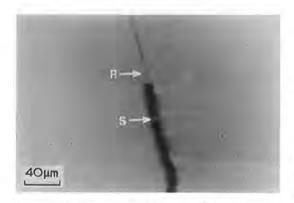

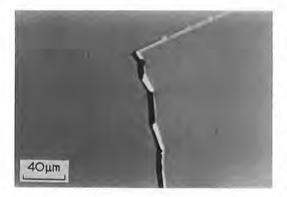

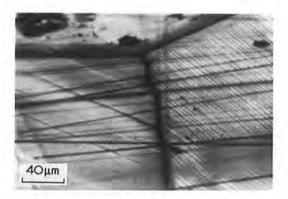

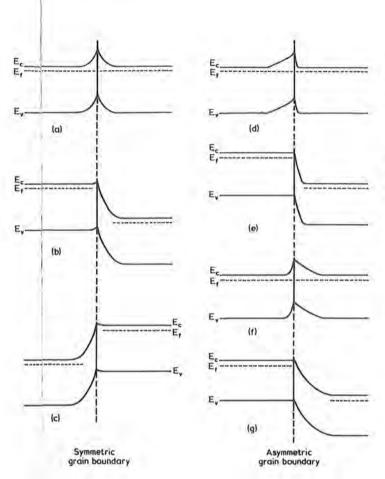

too sharp to fit experimental results, and Nicollian and Goetzberger (1967) therefore introduce the idea of statistical surface potential fluctuations, while Preier (1967) presents a theory of tunnelling to surface states as a cause of further dispersion in the conductance peak. Goetzberger et al (1976) provide a comprehensive review of the theory of interface states at the insulator semiconductor interface and alternative experimental techniques for their measurements.