### **Durham E-Theses**

## The design and implementation of a microprocessor controlled adaptive filter

Ahmed, Kadrya Mohammed

#### How to cite:

Ahmed, Kadrya Mohammed (1986) The design and implementation of a microprocessor controlled adaptive filter, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/7092/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# THE DESIGN AND IMPLEMENTATION OF A MICROPROCESSOR CONTROLLED ADAPTIVE FILTER

by

Kadrya Mohammed Ali Ahmed, B.Sc.

A thesis submitted in accordance with the regulations for the degree of Doctor of Philosophy in the University of Durham Department of Applied Physics & Electronics

1986

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

Thesis 1986/AHM

#### The Design and Implementation of a Microprocessor

Controlled Adaptive Filter

Kadrya Mohammed Ali Ahmed

#### ABSTRACT

This thesis describes the construction and implementation of a microprocessor controlled recursive adaptive filter applied as a noise canceller. It describes the concept of the adaptive noise canceller, a method of estimating the recieved signal corrupted with additive interference (noise). This canceller has two inputs, the primary input containing the corrupted signal and the reference input consisting of the additive noise correlated in some unknown way to the primary noise. The reference input is filtered and subtracted from the primary input without degrading the desired components of the signal. This filtering process is adaptive and based on Widrow-Hoff Least-Mean-Square algorithm. Adaptive filters are programmable and have the capability to adjust their own parameters in situations where minimum a piori knowledge is available about the inputs. For recursive filters, these parameters include feed-forward (non-recursive) as well as feedback (recursive) coefficients. A new design and implementation of the adaptive filter is suggested which uses a high speed 68000 microprocessor to accomplish the coefficients updating operation. Many practical problems arising in the hardware implementation are investigated. Simulation results illustrate the ability of the adaptive noise canceller to have an acceptable performance when the coefficients updating operation is carried out once every N sampling periods. Both simulation and hardware experimental results are in agreement.

#### **ACKNOWLEDGEMENTS**

I wish to express my gratitude to Prof. C.T. Spracklen, at Engineering Department, Aberdeen University, for his supervision, encouragement and securing the required facilities. I am indebted to Dr. B.J. Stanier at Durham University for his guidance, constructive suggestions, invaluable advice and kindly help throughout the period of this work.

I would also like to thank Prof. G.G. Roberts who made available to me the facilities of the Applied Physics and Electronics Department at Durham University. I like to give my thanks to the members of the workshop at Durham and Aberdeen University for providing their advice and technical assistance.

I greatfully acknowledge with thanks the valuable discussions and help of my colleagues in the Digital Electronics Group during the past years. I am grateful to the staff of the Computer Unit and the Science Library at Durham and Aberdeen Universities for their co-operation and friendly help. I also give my deepest thanks to Dr. Patrick Hughes at British Telecom Research Laboratories, Dr. Colin Cowan and Bernard Mulgrew at Edinburgh University who gave me the opportunity for interesting and helpful discussions.

I would also like to express my sincerest thanks to the State of Qatar and the University of Qatar for the award of a research studentship and financial support.

Finally, a special note of appreciation and gratitude to my parents, brothers and sisters for their encouragement, motivation, moral and intuitive support which provided me with a relaxed and secure life.

I DEDICATE THIS WORK TO MY BELOVED PARENTS, WHO HAVE INSTILLED IN ME A LOVE OF THE PURSUIT OF EXCELLENCE. BY THEIR CONSTANT SUPPORT AND GUIDANCE THEY HAVE ENCOURAGED ME TO PERSEVERE IN MY GOALS, BROTHERS AND SISTERS.

#### Glossary of Terms

ADC Analogue to Digital Converter

ALE Adaptive Line Enhancer

ALP Adaptive Linear Prediction

ALU Arithmetic Logic Unit

ANC Adaptive Noise Canceller

CCD Charge Coupled Device

CPU Central Processing Unit

DAC Digital to Analogue Converter

DFT Discrete Fourier Transform

DSP Digital Signal Processing

EPROM Eraseable Programmable Read Only Memory

FAD chip Digital Filter and Detect chip

FIR Finite Impulse Response

IC Integrated Circuit

IIR Infinite Impulse Response

LMS Least Mean Square

LSB Least Significant Bit

LSI Large Scale Integration

LSW Least Significant Word

M Misadjutment

MMSE Minimum Mean Square Error

MSB Most Significant Bit

MSE Mean Square Error

MSW Most Significant Word

MUX Multiplexer

NRCOEFF Non-Recursive Coefficient

PIA Peripheral Interface Adapter

PROM Programmable Read Only Memory

RAM Random Access Memory

RCOEFF Recursive Coefficiet

ROM Read Only Memory

SAW Surface Acoustic Wave

SNR Signal to Noise Ratio

SYNC pulse Synchronisation pulse

VLSI Very Large Scale Integration

#### CONTENTS

#### ABSTRACT

#### ACKNOWLEDGEMENTS

#### Glossary of Terms

| CTTA | DTTD | 4   |

|------|------|-----|

| CHA  | PILL | - 1 |

#### Background

- 1.1 Introduction

- 1.2 Digital and analogue filters1.3 History and development of adaptive filters

- 1.4 Conclusion

#### CHAPTER 2

#### Digital Filtering

- 2.1 Introduction

- 2.2 Sampled data signals

- 2.2.1 Introduction

- 2.2.2 Mathematical description using the Dirac "5" function

- 2.3 The Z-transform

- 2.4 Z-transform properties

- 2.5 Relation between the Z-domain and S-domain

- 2.6 The inverse Z-transform

- 2.7 The difference equation and the digital transfer function

- 2.8 State variable analysis

- 2.8.1 Introduction

- 2.8.2 State space description for discrete systems

- 2.9 Frequency response of digital filters

- 2.10 Digital filter design techniques

- 2.11 Realization of digital filters

- 2.11.1 The realization of recursive digital filters

- 2.11.1.1 Direct form I

- 2.11.1.2 The direct form II or canonic form

- 2.11.1.3 Prallel form

- 2.11.1.4 Cascade form

- 2.11.2 The realization of non-recursive digital filters

- 2.12 frequency transformation for digital filters

- 2.13 Quantization effects

- 2.13.1 Round-off noise

- 2.13.2 Input quantization noise2.13.3 Coefficients rounding effect

- 2.13.4 Limit cycle oscillations

- 2.13.5 Overflow oscillations

- 2.14 Conclusion

#### CHAPTER 3

#### Adaptive Filtering

3.1 Introduction

- 3.2 The concept of adaptive noise cancelling

- 3.3 The LMS adaptive filter

- 3.3.1 Adaptive linear combiner

- 3.3.2 The LMS adaptive algorithm

- 3.3.3 The convergence factor ""

- 3.4 Wiener solution to the statistical noise cancelling problem

- 3.5 The recursive LMS adaptive filter

- 3.6 Quantization effects

- 3.7 Misadjustment due to gradient noise

- 3.8 Conclusion

#### CHAPTER 4

#### Computer Simulation

- 4.1 Intoduction

- 4.2 Computing IIR filter transfer function

- 4.3 IIR adaptive filter performance with different N and  $\mu$

- 4.3.1 Conventional type

- 4.3.2 N Time interval

- 4.3.3 Successive input&output samples

- 4.3.4 Blocks type

- 4.4 Comparisons of the filter implementation types

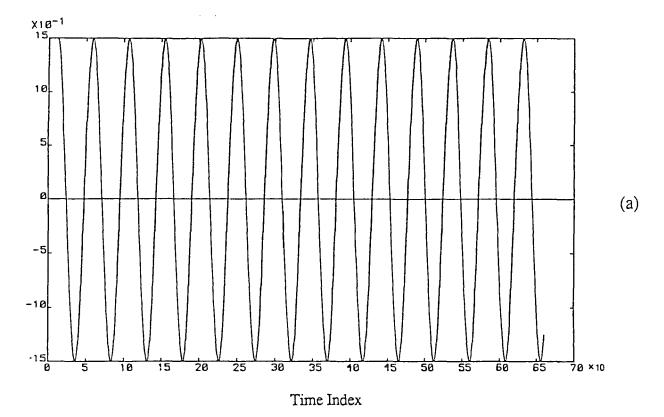

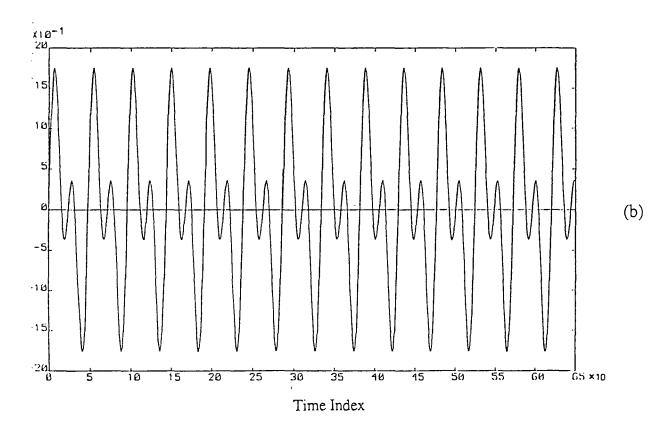

- 4.5 The ANC performance

- 4.5.1 Floating point simulation

- 4.5.2 Fixed point simulation

- 4.6 Conclusion

#### CHAPTER 5

#### Design Analysis

- 5.1 Introduction

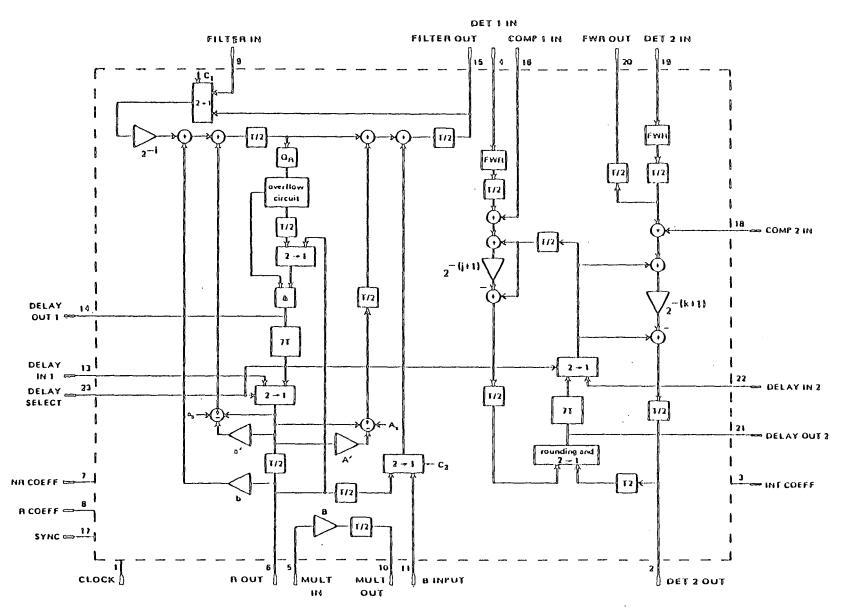

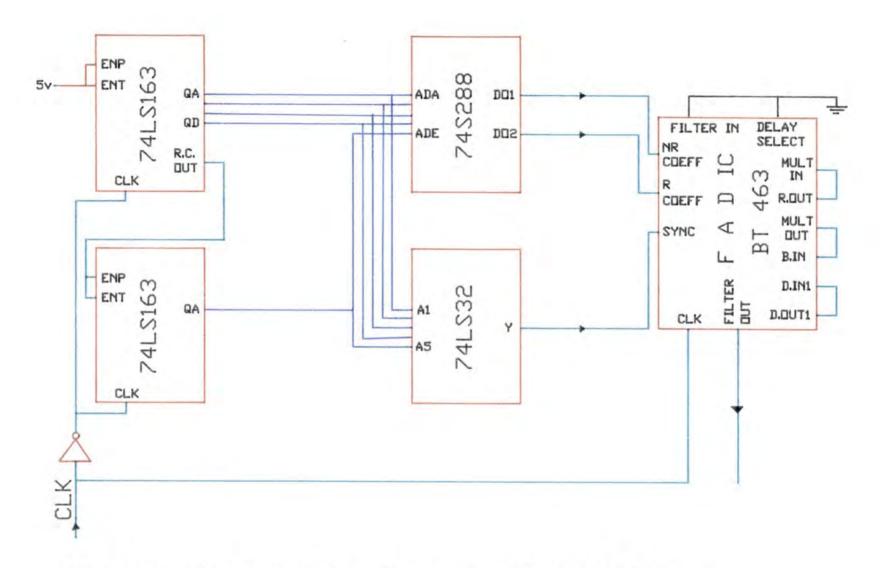

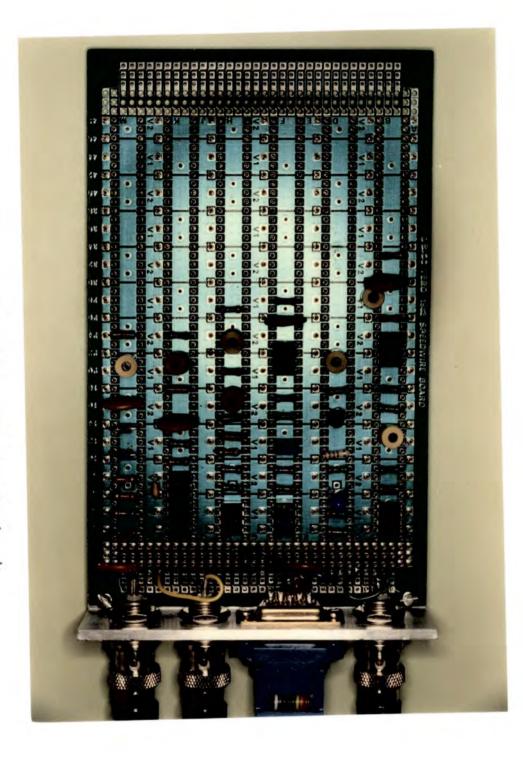

- 5.2 Structure of the FAD chip

- 5.2.1 The FAD IC components

- 5.2.1.1 Coefficient multipliers

- 5.2.1.2 The quantizer

- 5.2.1.3 The input scaler and overflow circuit

- 5.2.1.4 Data selectors (multiplexers)

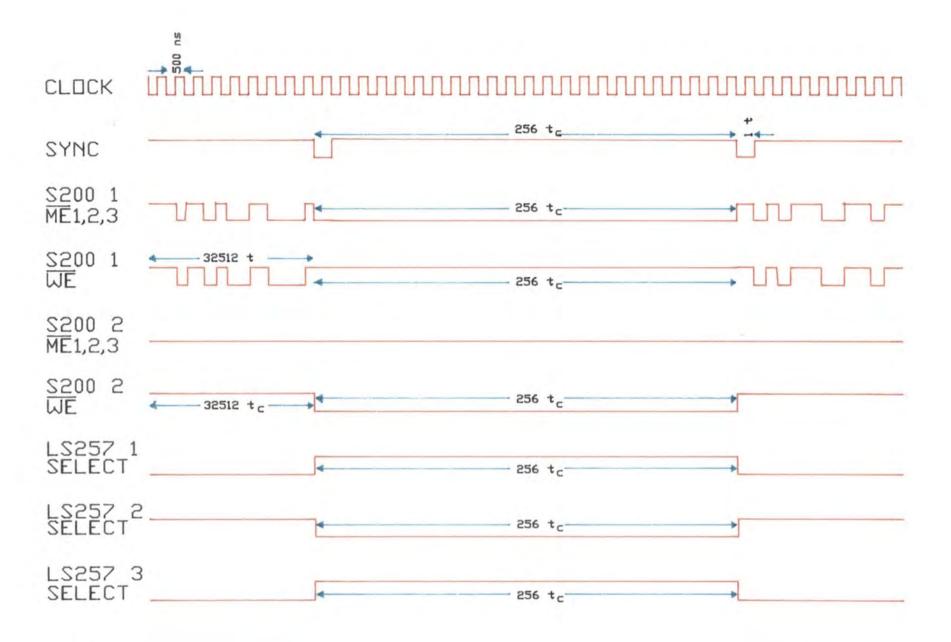

- 5.2.2 Timing

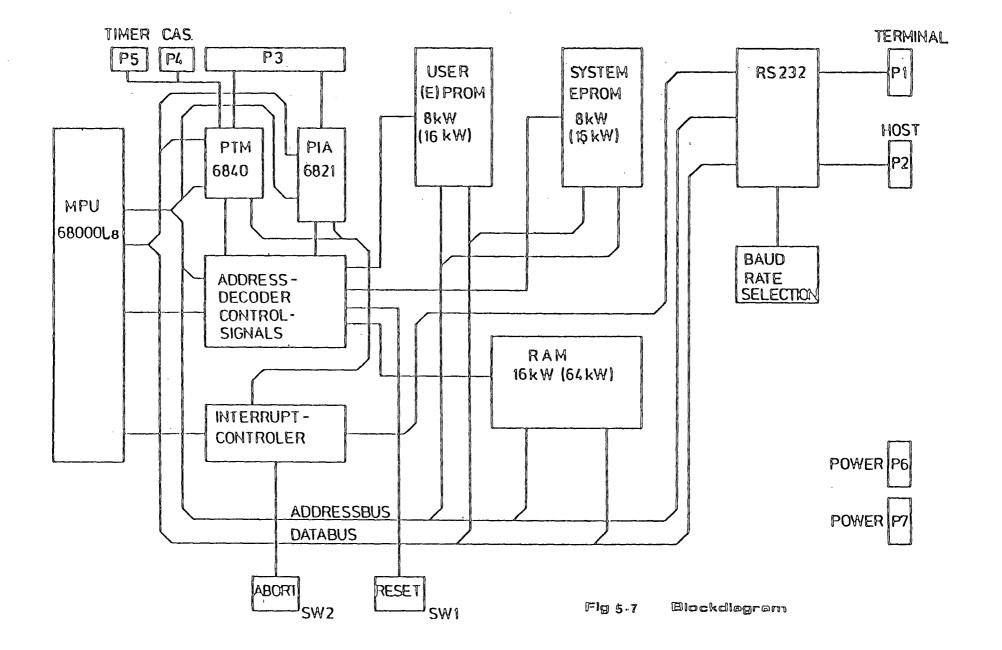

- 5.3 68000 Microprocessor

- 5.3.1 Introduction

- 5.3.2 MC68000 architecture

- 5.4 FRC 68000 PROFI KIT

- 5.5 Practical implementation problems

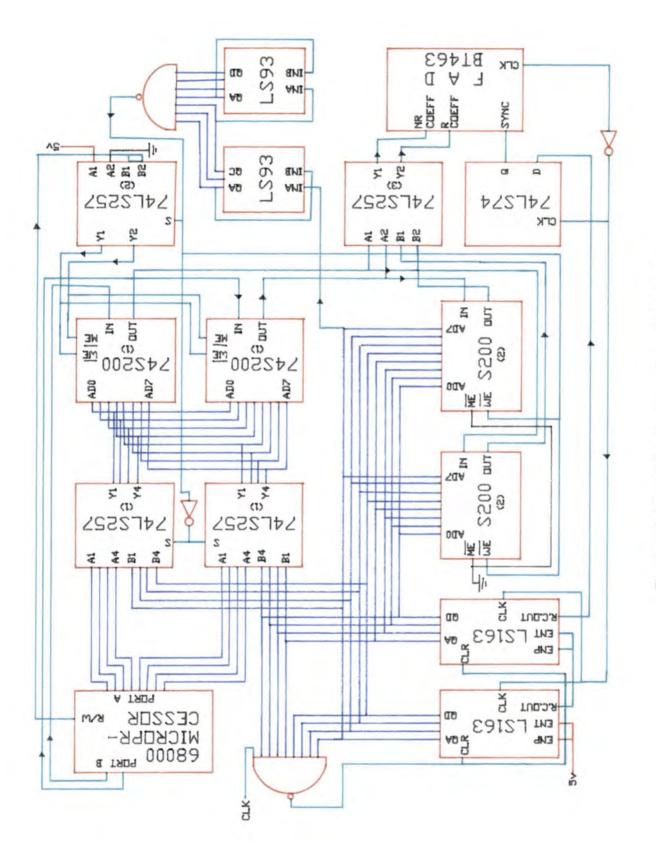

- 5.5.1 Coefficients timing

- 5.5.1.1 Writing data into RAM1

- 5.5.1.2 Transfering data from RAM1 to RAM2

- 5.5.2 Writing data into the MC68000

- 5.6 Interfacing considerations

- 5.6.1 Input samples to the FAD

- 5.6.2 FAD to output samples

- 5.6.3 Producing the error output

- 5.7 Conclusion

#### CHAPTER 6 Adaptive Noise Canceller Implementation

#### 6.1 Introduction

- 6.2 Solving the FAD IC problem

- 6.3 The FAD IC as 16<sup>th</sup> order filter

- 6.4 The input-output sampled data

- 6.4.1 Expressing the input samples in two.s complement

- 6.4.2 Writing data into the MC68000

- 6.4.3 Adjusting bits locations

- 6.4.4 Extending the 12 bits to 16 bits

- 6.4.5 Circular list process and saving input&output data

- 6.5 The filter coefficients

- 6.5.1 Updating the coefficients

- 6.5.2 The coefficients and control bits representation

- 6.5.3 Coefficients entry

- 6.6 The system implementation

- 6.7 Conclusion

#### CHAPTER 7

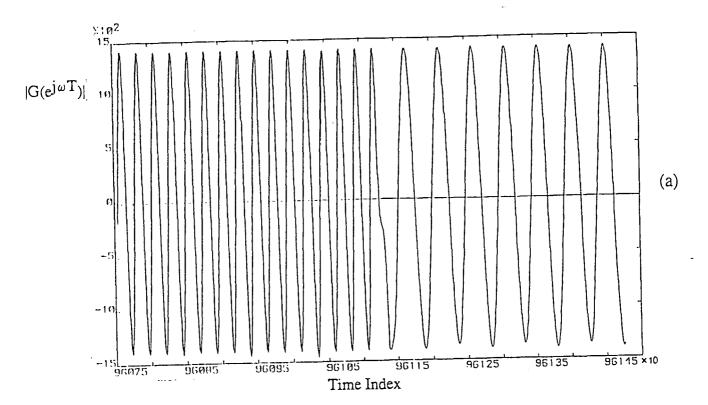

#### Experimental Results

- 7.1 Introduction

- 7.2 The ANC system performance and the results

- 7.3 Further results7.4 IIR adaptive filter stability

- 4.5 Conclusion

#### CHAPTER 8

#### Conclusion

#### REFERENCES

- APPENDIX A Pascal programs for implementing the LMS adaptive filter

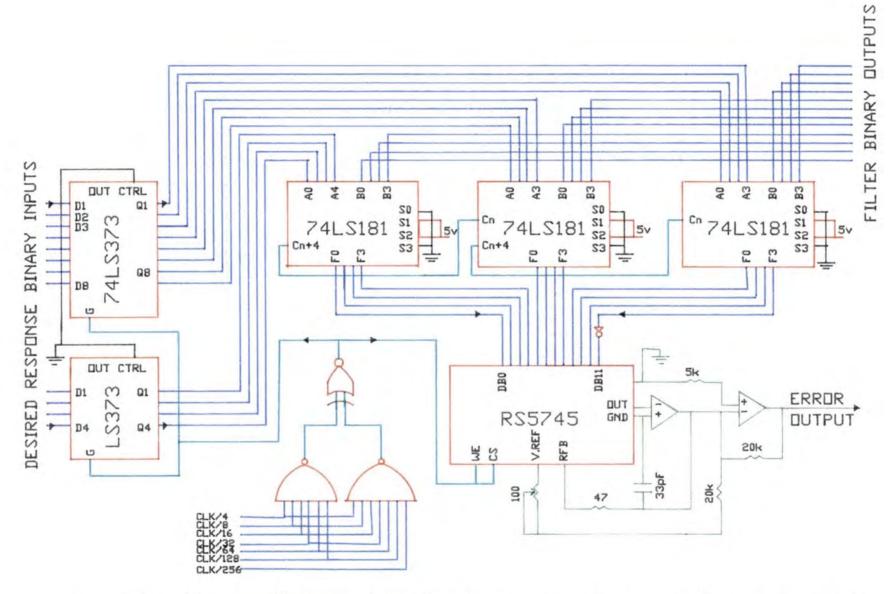

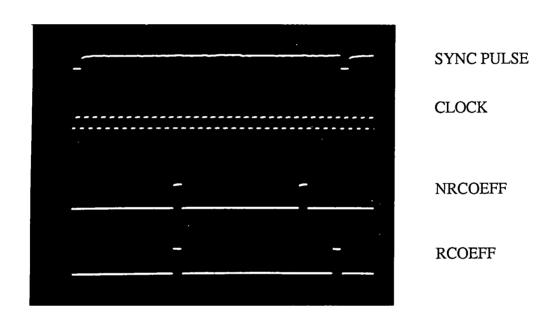

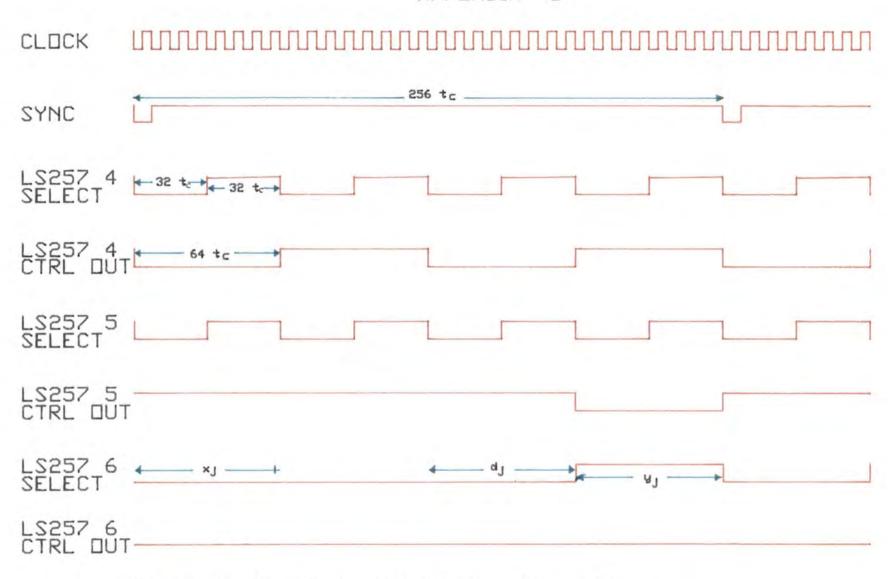

- APPENDIX B Circuit and timing diagrams of the data multiplexer

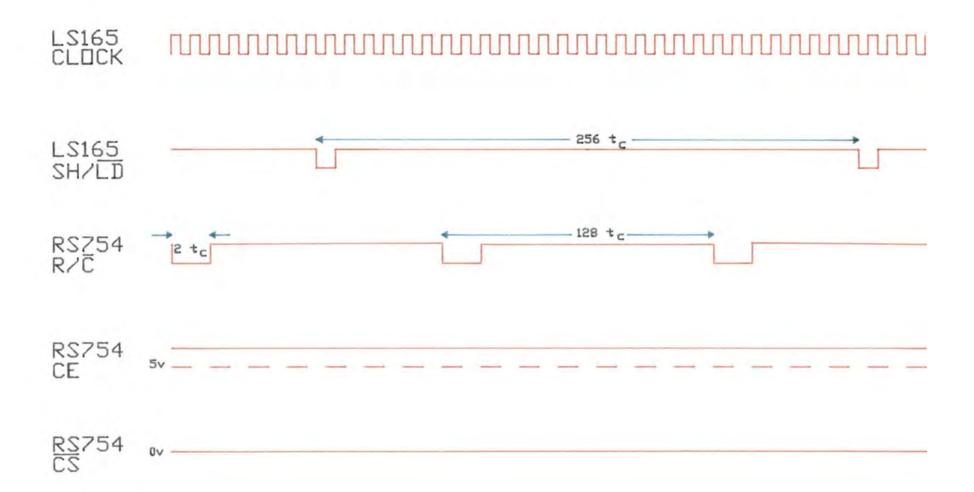

- APPENDIX C Parallel to serial conversion circuit and timing diagrams of the filter input

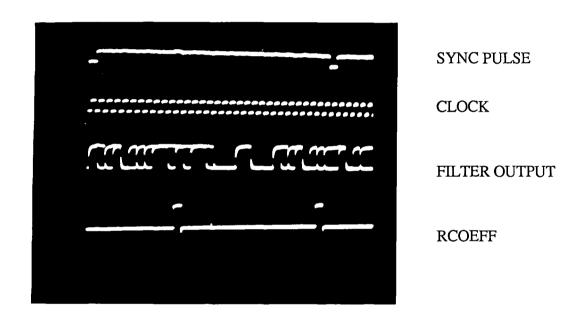

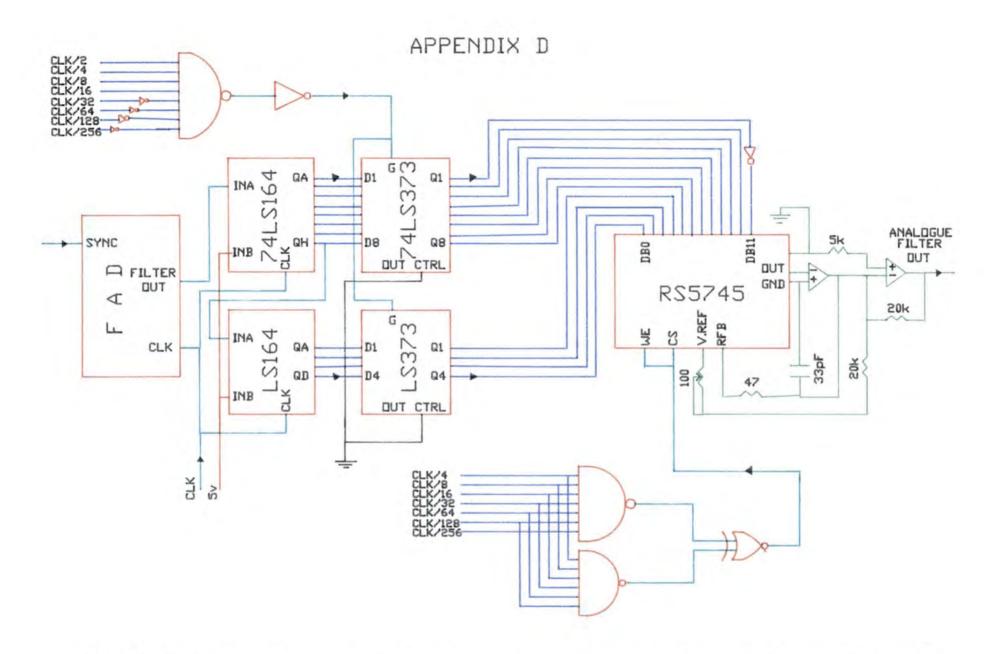

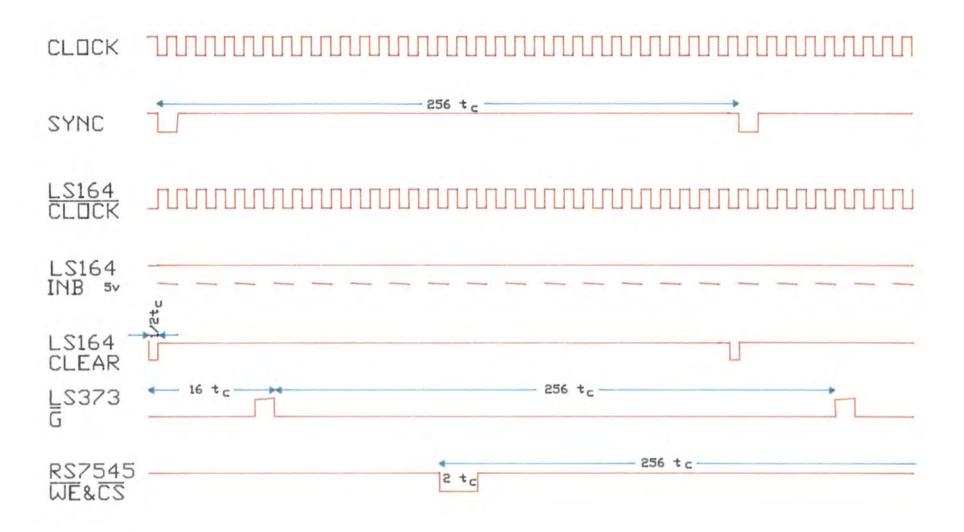

- APPENDIX D Circuit and timing diagrams for producing the analogue filter output

- APPENDIX E 68000 assembly language program for implementing 16<sup>th</sup> order adaptive filter

#### CHAPTER -1-

#### Background

#### 1.1 Introduction

In any communications system, the transmission of signals from the transmitter to the receiver involves their contamination with noise. This is the basic problem of communication and limits the capability of the system.

By noise we mean unwanted or unpredictable signals that corrupt the message. Noise can be classified according to the source into two categories:

- (a) internal noise, which is generated by components within the communication system.

- (b) external noise, which includes man-made noise and extraterrestrial natural sources (1,2).

To suppress this noise, signal processors such as filters can be used.

In the decade 1960-1970 high speed digital computers were developed and became widely available for serious research and development work. Consequently it became possible to use the theoretical basis of digital signal processing, such as Fourier analysis, waveform sampling, Z-transform, etc., in digital signal design (3,4).

This background provided the impetus for the introduction of digital signal processors as a means for implementing digital filters.

The term digital signal processing (DSP) implies the description of a complete set of operations such as arithmetic calculation and numerical manipulations. These represent the processing of the signal considered as a sequence of numbers or symbols in order to produce a form which is in some sense more desirable. Many different functions can be accomplished in this way; spectral analysis, filtering (which is of particular interest) transcoding, modulation, detection, and estimation and extraction of parameters by using a suitable digital computer (5,6).

DSP is concerned with signals or systems that are the discrete-time counterpart of the more familiar continuous-time systems. DSP has many applications in a very wide range of fields such as the analysis of biomedical signals, vibration-analysis, picture processing, analysis of seismic signals and speech analysis. However, telecommunication forms a very important field of applications which provides a major stimulus for research and development (4,5).

DSP has become an established method of filtering electrical waveforms, and the associated theory of discrete-time systems can often be employed in a number of disciplines (4).

The term 'filter' implies any frequency selective device or processor which passes certain ranges of frequencies and rejects others. Filters can be classified according to the frequency ranges they pass or reject into; low-pass, high-pass, pass-band, and stop-band filters. For example, a low-pass filter passes a low frequency input signals below a certain value, and attenuates the signals of frequency above this value (7).

Filters can also be classified according to their signal type into:

analogue (or continuous filters).

and digital filters.

#### 1.2 Comparison of Digital and Continuous Filters

Digital and continuous filters have exactly the same aim of suppressing a noisy signal and producing one with less distortion, but the physical realization is different, since continuous filters are constructed from linear electrical components, such as resistors, capacitors and inductors, and linear continuous filter theory is based on linear differential equations and the Laplace transform. Digital filters however are based on linear difference equations and the Z-transform (which is a special form of the Laplace transform, which will be described in detail in the next chapter). It can be shown that digital filters are mathematically equivalent to continuous filters with sampled data inputs and outputs.

Digital filters have several advantages over continuous filters and some of these are given below:

- (1) the absence of impedance-matching problems.

- (2) the frequency response characteristics can be made to be relatively close to the ideal and can be changed by varying the stored coefficients.

- (3) the possibility of implementing any type of filter with the same hardware by using multiplexing and frequency transformation.

- (4) adaptive filtering is relatively simple to achieve.

(5) there are no drift problems as a result of realizing stable filters with very high 'Q's'.

#### (6) low cost.

However, in spite of all these advantages, digital filters also have limitations. The limited word length available on the digital computer leads to quantization errors, which will be investigated in some detail in chapter 2. Much work has been carried out to overcome these errors (4,7,9).

Because of the availability of the digital computer as a research tool in all branches of science and technology, and the existance of analogue-to-digital converter (ADC) and digital-to-analogue converter (DAC), digital filters became widely used. Many established continuous-time filter systems have been replaced by equivalent digital filter systems because of their advantages.

A digital filter is defined (7,9) as the computational process or algorithm by which a sampled signal or sequence of numbers, acting as an input, is transformed into a second sequence of numbers, termed the output, using digital components as the basic elements for implementation. The process can be any arbitrary filtering operation, such as low-pass filtering, high-pass filtering, pass-band filtering or stop-band filtering etc..

The digital filter may be represented by a linear difference equation which defines the output signal as a function of the present input sample and any number of previous input and output samples (4,7).

Digital filters can be fixed or adaptive. The optimal design

of fixed filters is based on a complete a priori knowledge of both the signal and the interference (noise). Adaptive filters, on the other hand, require much less prior knowledge in their design and have the ability to adjust their own parameters during operation to optimize their performance. The adjustable parameters of adaptive filters are called the weights (impulse response). These weights are usualy updated by a least mean square (LMS) algorithm which adjusts the filter weights so that the filter output is an estimate of the signal (10,11).

In this project an adaptive filter is used as a noise canceller in which a corrupted signal passes through a filter that tends to supress the noise while leaving the signal relatively unchanged (11).

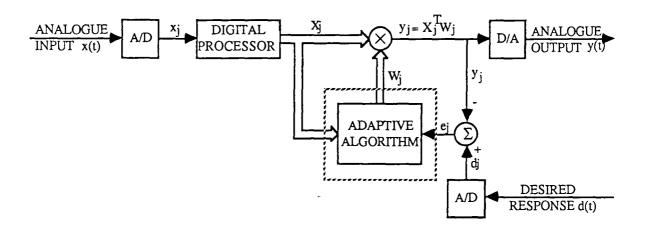

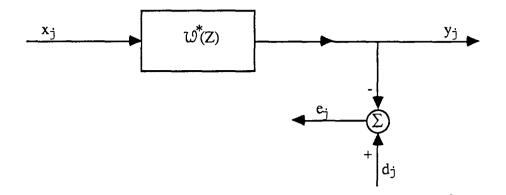

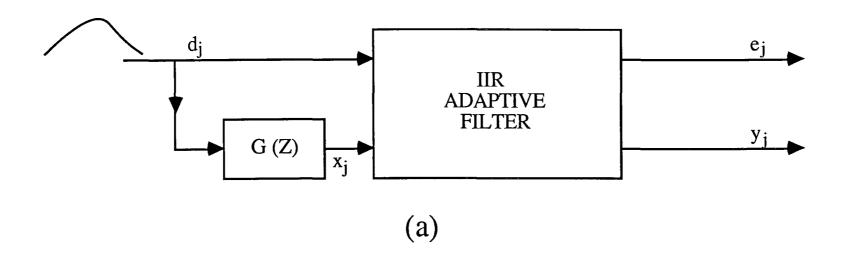

Fig. 1.1 illustrates the block diagram of a basic adaptive noise canceller (ANC). It has two inputs, the desired response input  $d_j$  (primary input) containing the corrupted signal and the input signal  $x_j$  (reference input) containing noise correlated in some unknown way with the primary noise. The reference input is adaptively filtered and subtracted from the primary input to obtain the signal with less destortion. The objective of the system is to minimize the error  $e_j$  between the filter output  $y_j$  and  $d_j$  in the LMS manner by iteratively updating the filter weights in accordance with the LMS algorithm (11,12), this is discussed in detail in chapter 3.

To realize an adaptive filter in real time, the digital technique must be fast enough to complete the computational process within the available time.

Fig .1.1 Basic adaptive filter

Adaptive filters are versatile signal processing elements which have a wide range of applications where only a limited a priori knowledge of the expected signal and noise is available. These applications include:

#### (a) Noise canceller

In noise cancelling system the additive noise or interference will be rejected from a waveform containing a signal of interest. Noise cancelling is a variation of optimal filtering that is highly advantageous in many applications. These applications include for intance the cancelling of 60-Hz interference in electrocardiography, the donor electrodiogram in heart transplant electrocardiography and cancelling noise in speech signals which plays an important roll in our communications-oriented society. Much work has been carried out to remove the unwanted noise components from the speech signals (11,13,14,15,16).

#### (b) Channel equalizer

The main problem in digital communications is the recovery of the message which, when sent over the channel, is distorted with noise and intersymbol interference due to the nonlinear phase and amplitude characteristics of the channel. To overcome these effects the channel equalizer is used. Many methods have been investigated for the optimal implementation of digital channel equalizers (17,18,19,20).

#### (c) Adaptive line enhancer (ALE)

The ALE is considered as an adaptive digital filter which is designed to remove uncorrelated components (broad-band noise) from its input, while passing any narrow-band signals or components with

little attenuation (21,22,23).

#### (d) Adaptive linear prediction (ALP)

The ALP signal processing has been applied with great success for many problems such as spectral analysis, system modeling and speech encoding. The conventional approach for implementing ALP involves computing and updating the sample covariance matrix for a block of data and then obtaining the predictor coefficients. Morgan and Craic have published an alternative approach which uses the LMS algorithm, to compute the predictor coefficients (24,25).

Adaptive filters can be implemented by a software program on a digital computer with a special interface and by digital hardware. In this project, an IC implemented as a digital filter which is designed as a general purpose device suitable for filtering noisy signals in the audio frequency band is used to implement a 16<sup>th</sup> order recursive LMS adaptive filter. The adaptive filter is used as a noise canceller, in which a corrupted signal passes through the filter and this coherently supresses the noise while leaving the desired signal relatively unchanged.

In the next chapter, the basic principles of digital filtering will be described. The first part presents the relationship between input&output of the discrete-time system. The second part dicusses the various methods of realizing the recursive and non-recursive digital filters, and quantization errors due to the limited-word length available on a digital computer.

In chapter 3, the basic concept of adaptive noise cancelling, and the so-called Wiener solution to the statistical noise cancelling problems are considered. The LMS adaptive algorithm for

updating the feed-forward (non-recursive) and feed-back (recursive) coefficients will be described and the quantization effects due to the limited-word length and finite precision arithmetic of a digital processor, will be investigated.

In chapter 4, a flexible computer simulation program has been developed to investigate the behaviour of the recursive LMS adaptive filter, employed as an ANC, under different conditions and various parameters. The performance of the filter has been discussed in both fixed point and floating point arithmetic representations

Chapter 5 is concerned with describing step by step approach to the design and construction of a 16<sup>th</sup> order recursive LMS adaptive filter exposing a brief introduction to the 68000 microprocessor and the digital filter IC used in the design. The interfacing considerations and problems arising in the implementation of the filter have also been investigated.

Chapter 6 discusses extensively how the single board 68000 microcomputer can be applied to update the adaptive filter coefficients in order to write one bit of each recursive and non-recursive coefficient into the filter IC every clock cycle.

Chapter 7 describes the implementation of the filter to be used as an ANC and presents the results of cancelling undesirable interference. This chapter also reflects some light on the effect of the implication of the feed-back in recursive (IIR) filter on its stability.

#### 1.3 History and Development of Adaptive Filters

The earliest work on adaptive noise cancelling was performed by Howells and Applebaum and their colleagues at the General Electric Company between 1957 and 1960. They designed and built a system for antenna sidelobe cancelling that used a reference input derived from an auxillary antenna and a simple two-weight adaptive filter (26).

At the time of this work, only a handful of people were interested in adaptive systems, and development of multiweight adaptive filters was only just begining. Much of this early efforts were proceeding by independent studies in different research organizations. A notable early development occured at Stanford University when Widrow and Hoff devised the LMS adaptive algorithm and the pattern recognition scheme in 1959 (27,28).

Further relevant work being conducted simultaneously at the Institute of Automatics and Telemechanics in Moscow. In Great Britain, in 1961 Gabor and his associates were developing adaptive filters (29).

In the early and middle 1960.s, work on adaptive systems intensified. Many papers on adaptation, adaptive controls, adaptive filtering, and adaptive signal processing appeared in the literature (4,30,31).

The first applicable adaptive filter is credited to Lucky at the Bell Laboratories for his design in 1966 of an equalizer which compansated for distortion in data transmission systems. The first adaptive noise cancelling system at Stanford University was designed and built in 1965 by two students. The purpose was to

cancel 60-Hz interference at the output of an electrocardiographic amplifier and recorder.

Since 1965, adaptive noise cancelling has been successfully applied to a number of additional problems as shown in (11).

In 1967 Widrow, et al. (11) proposed a technique for an adaptive digital filter based on the LMS algorithm (or gradient search technique) which has come from the Stanford University pattern recognition work. The main advantage of this algorithm is its computational simplicity for real time processing with little storage which converges toward the optimum solution much more efficiently than do other algorithms.

Various implementations have been discussed and published in the literature. In general, adaptive filters can be implemented in the time domain or the frequency domain. Reed and Feintuch (32) have described the behaviour of a frequency domain adaptive filter configured as a broad-band canceller with white Gaussian inputs. Bershad and Feintuch (23) have presented a mathematical model for predicting the mean weight behaviour of the recursive adaptive filter when used as an ALE in the frequency domain.

Most practical adaptive filters have been realized by computer programs. In recent years Feintuch (33) implemented an adaptive recursive LMS filter in the time domain using two transversal adaptive filters using simulation results to demonstrate its capability (34). Mikhael, et al. (35) has proposed using individual convergence factors to adapt the individual recursive adaptive filter parameters, and then to adjust them in real time,

so that their values are kept optimal for each new set of input variables, rather than using the conventional technique, which uses a fixed time constant convergence factor, which is chosen to be the same for all the filter parameters. He has presented computer simulation results which indicate that the individual adaptation approach gives much better results than the conventional approach. Paul (13) has investigated and published two adaptive digital techniques for audio noise cancellation. The first technique, adaptive predictive deconvolution, used an ALP to estimate and cancel correlated noise components of the audio signal. The second technique, adaptive filtering, employs two audio signal inputs.

However, the realization of adaptive filters in hardware has also developed rapidly. The growth of large scale integrated circuits (LSI) decreases the cost and increases the speed of components. Cowan et al. (36) have published a technique for implementing a digital adaptive filter which used no digital multiplication, but instead relies on the use of the operations of memory access, addition and scaling by integer powers of 2. The technique is based on the distributed arithmetic (alternatively read-only memory (ROM)/accumulator) filter architecture originally proposed for a fixed frequency filter implemented by Peled and Liu (37). This technique has the advantage that only standard TTL type logic circuits need to be used without recource to specialised signal processing functions (such as hardware multipliers). Cowan and Grant also published another digital adaptive filter design based on the LMS algorithm which relies heavily on the use of linear digital multipliers (38).

In 1983 Holt and Mullholand (12) published a technique for a

high speed micoprogrammed adaptive filter implementation using the AM2900 bit slice device and a hardware multiplier-accumulator. The implementation was based upon a clipped LMS algorithm.

With the continuing advances in digital technology and the availability of LSI components, the adaptive filter is now available on a single chip. South (39) has developed a digital adaptive filter in LSI form for use in the audio band which makes it ideal for solving problems of cancelling unwanted signals in telephony and other fields at low cost.

#### 1.4 Conclusion

The advantages of the adaptive digital filters over the fixed coefficients digital filters, are that they are programmable, so their coefficients (weights) are updated and adjusted in accordance with the incoming signals. They are versatile signal processing elements which can be applied in situations where an absolute minimum knowledge is available about the incoming signals.

The robustness and the simplicity of implementation of the LMS algorithm, make the LMS adaptive filter attractive for many applications. These applications include, noise cancelling, channel equalization, line enhancing and adaptive linear prediction. The rapid advance in LSI and VLSI technology and the desire to provide improved speech communications, make telecommunications a fertile field for the application of adaptive filters.

#### CHAPTER -2-

#### Digital Filtering

#### 2.1 Introduction

The early 1970s marked the beginning of a revolution in the electronics world, and computer technology has developed rapidly. With the advent of relatively cheap digital computers and availability of the A/D and D/A converters, powerful digital filters have now become an attractive subject and commonly used. Consequently, the number of practical applications significantly increased.

Some digital filters have found important uses in an increasing number of fields in science and engineering and the required techniques have been developed to achieve the desired filter characteristics.

Many digital filters are fabricated as a single IC making the use of such filter components in commercial systems economically feasible and technically desirable.

Many programmable LSI digital filters have been designed and have been used in many applications (40). British Telecom Research Laboratories (41) have designed an LSI digital filter and detect (FAD) chip as a general purpose device suitable for filtering noisy signals and detecting tones in the audio frequency band.

This chapter describes the basic principles of digital filtering. Two methods of describing the discrete-time systems, namely the Z-transform and state variables technique, will be

investigated. The mathematical concept of the Z-Transform, which is the basic mathematical tool of digital filtering, is described in the first section. The linear difference equation, the central element in the concept of the digital filter, is then investigated. Different realisations of recursive digital filters and the considerations that should be taken into account in choosing between them are also presented. Due to the limited word length available on the digital computer, quantization noise occurs, the last section introduces some aspects of these errors.

#### 2.2 Sampled Data Signals

#### 2.2.1 Introduction

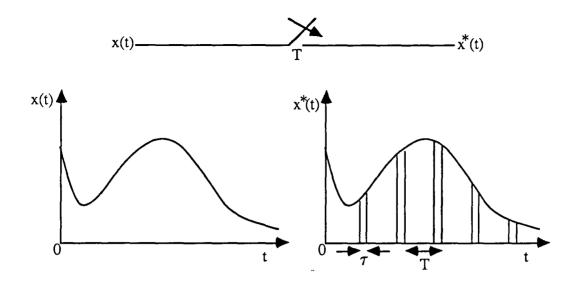

The sampling process represents the signal x(t) by its value x(nT) at integral time increments T (called the sampling period) so that the sampled data signal defines values only at certain instants of time. Since it is not possible to feed continuous data into a digital computer, any signal or data input must be represented as a set of samples. A simple model of the sampling process is one which considers that the samples can be acquired by closing a switch at interval times every T seconds for a short time  $\tau$  seconds as shown in fig.2.1. Referring to fig. 2.1 it is obvious that the switch output is a set of pulses separated by period T with finite width. However, if the pulse width, $\tau$ , is negligible compared with interval between successive samples,T, the output of the sampler  $x^*(t)$  may be described as a set of impulses with their heights proportional to the values of x(t) at the sampling instants (4.5).

#### 2.2.2 Mathematical Description Using the Dirac " $\delta$ " Function

The Dirac function, which is usually referred to as the unit

Fig. 2.1 Model of the sampling process

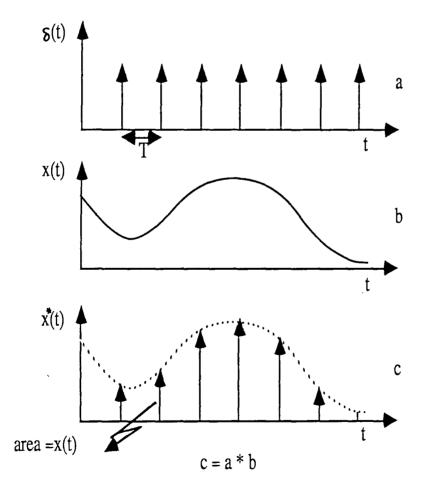

Fig. 2.2 The sampling process regarded as a modulation process

(a) Train of unit Dirac impulses

(b) Continuous signal

(c) Sampled signal

impulse function, is a pulse of extremely small width and unit area. In other words, the product of its width and its mean height is unity, even though its precise shape is undefined.

As shown in fig. 2.2, the ideal sampling function can be represented as a train of unit impulses, and is defined by the equation

$$\delta_{\mathrm{T}}(t) = \sum_{n=-\infty}^{\infty} \delta(t-nT), \qquad 2.2.1$$

where  $\delta(t)$  represents a Dirac pulse (unit impulse) occurring at t=0, and  $\delta(t-nT)$  is a Dirac function shifted by integral number of T occurring at t=nT. Therefore

$$x^*(t) = x(t) \sum_{n=-\infty}^{\infty} \delta(t-nT)$$

, 2.2.2

where x(t) is the original continuous signal and  $x^*(t)$  is the sampled signal.

Since the value of x(t) is only known for t=nT, and for a physical system x(t)=0 for t<0, then

$$x^*(t) = \sum_{n=0}^{\infty} x(n)T \delta(t-nT)$$

2.2.3

It is obvious that  $x^*(t)$  is a weighted sum of shifted unit impulses, so that x(n)T is the weighting factor of the impulse function  $\delta(t-nT)$ , as indicated by the value in fig. 2.2.c (4).

Referring to eqn. 2.2.1,  $\delta_{\rm T}(t)$  can be expanded as a Fourier series, that is

$$\delta_{T}(t) = \sum_{n=-\infty}^{\infty} C_{n} e^{jn\omega_{S}t}$$

where

$$C_n = (1/T) \int_0^T \delta_T(t) e^{-jn\omega_S t} dt$$

and  $\omega_{\mathrm{S}}$  is the sampling frequency equal to  $2\pi/\mathrm{T}$  rad/sec.

Since the area of the Dirac pulse is unity, then

$$\int_{0}^{T} \delta_{T}(t) e^{-jn\omega_{S}t} dt = 1$$

and therefore,  $C_n = 1/T$ , hence

$$\delta_{T}(t) = (1/T) \sum_{n=-\infty}^{\infty} e^{jn\omega_{s}t}$$

and we have seen in fig. 2.2 that for the impulse modulator

$$x^*(t) = \delta(t) x(t)$$

, therfore

$$x^*(t) = 1/T \sum_{n=-\infty}^{\infty} x(t) e^{jn\omega_s t}$$

2.2.4

By taking Laplace transforms and stating the associated shifting theorem, we obtain

$$X^*(S) = \int [x^*(t)] = (1/T) \sum_{n=-\infty}^{\infty} X(S-jn\omega_S)$$

where  $S=j_{\omega}$ ,

therefore

$$X^*(j\omega) = (1/T)\sum_{n=-\infty}^{\infty} X[j(\omega-n\omega_S)]$$

2.2.5

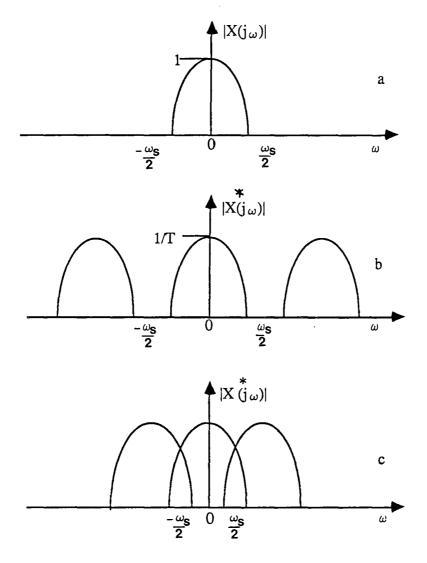

It is observed from eqn. 2.2.5 that, as a result of impulse-sampling, the frequency spectrum of the signal  $\mathbf{x}^*(t)$  is the same as the spectrum of the original signal  $\mathbf{x}(t)$  but is periodic with period  $\omega_{\rm S}$  ( $2\pi/T$ ), that is to say, the sampling has introduced a periodicity into the frequency space, which constitutes a fundamental characteristic of the sampled signal shown in fig. 2.3. Referring to fig. 2.3 if the highest frequency component is greater than  $\omega_{\rm S}/2$  (see fig. 2.3.c), a fold-over distortion or aliasing of the frequency response function is introduced, which may be avoided by increasing the sampling frequency. Consequently the original

Fig. 2.3 (a) Frequency spectrum of the signal (b) Frequency spectrum of the sampled signal (c) Aliasing of frequency specrta

Fig. 2. 4 Digital convolution-summation property

signal cannot be reclaimed from the sampled-data signal. From this, the sampling or Shannon's theorem is derived, in which it specifies the minimum sampling rate for adequate representation of a continuous signal. If the frequency  $f=\omega/2\pi$ , and to avoid the folding condition, it has been already shown that

$\omega \langle \pi/T$

or

$f = \omega/2\pi \langle 1/2T$

and hence

$T < \pi / \omega = 1/2f$

Formally, the sampling theorem may therefore be stated as follows: "A continuous signal which does not contain any component with frequency greater than f Hertz may in principle be recovered from its sampled version, if the sampling interval T is less than 1/2f seconds".

The interval 1/2f is called Nyquist interval and 2f is known as the Nyquist frequency (4,5,7).

#### 2.3 The Z-Transform

In general the analysis and design of linear systems may be carried out by one of two major approaches which relies:

- (a) on the use of a transform, such as Laplace and Z-transform and block diagrams.

- (b) the state variable technique, which will be discribed in the next section.

As we mentioned before, filters can be classified into analogue filters (continuous-time systems) and digital filters

(discrete-time systems).

In continuous-time systems, (42) Laplace transformation is used (a) to solve the differential equations, in which the output signal and its derivatives are related to the input signal and its derivatives and also (b) to express the behaviour of a filter in terms of a transfer function which describe a signal in terms of a set of poles and zeros in S-plane (S-domain). The Z-transform, on the other hand, is used to describe the properties of a discrete-time systems (sampled data signals) and leads to a useful method of representing the discrete-time systems by either a finite set of poles and zeros in Z-plane (frequency domain representation) or by a linear difference equation (time domain representation).

The Z-transform (4) can be considered as a rule that converts a sequence of numbers into a function of the complex variable Z. The Z-transform of a sampled-data signal may be directly determined from its Laplace transform. Referring to eqn. 2.2.3 we find that

$$x^* = x(0)T\delta(t)+x(1)T\delta(t-T)+x(2)T\delta(t-2T)+...$$

The Laplace transform of  $x^*(t)$  is given by

$$\int [x^*] = x(0)T + x(1)Te^{-ST} + x(2)Te^{-2ST} + ...$$

where S is a complex frequency variable.

We now define the new variable  $Z = e^{ST}$  and denote the Z-transform of the signal by X(Z). Hence

$$X(Z) = x(0)T+x(1)TZ^{-1}+x(2)TZ^{-2}+ ...$$

that is

$$X(Z) = \sum_{n=0}^{\infty} x(n)T Z^{-n}$$

2.3.1

Z is a new complex frequency variable. Thus if  $S = \sigma + j\omega$

$$Z = e^{ST} = e^{\sigma T} \cdot e^{j\omega T}$$

The term  $Z^{-n}$  implies a time delay of n sampling periods.

Murankami et al. (43) have presented a new complex number-theoretic Z-transform (CNT Z-transform) over a finite ring. It was shown that a digital filter with any desired impulse response can be expressed in terms of the CNT Z-transform. They have found that filters designed on a finite ring have some advantages over the usual Z-transform, i.e. they are errorless and information lossless.

#### 2.4 Z-Transform Properties

#### 1. Linearity:

$$X(Z) = \sum_{n=0}^{\infty} (Ax_{1}(n)T + Bx_{2}(n)T)Z^{-n}$$

$$= A \sum_{n=0}^{\infty} x_{1}(n)TZ^{-n} + B \sum_{n=0}^{\infty} x_{2}(n)Z^{-n}$$

$$= A X_{1}(Z) + B X_{2}(Z)$$

where A and B are constants.

2. Right-Shifting "delay" :

$$Y(Z) = \sum_{n=0}^{\infty} x(n-k)TZ^{-n} = \left[\sum_{n=0}^{\infty} x(n)TZ^{-n} Z^{-k}\right]$$

=  $X(Z) Z^{-k}$

3. Left-Shifting:

$$Y(Z) = \sum_{n=0}^{\infty} x(n+k)TZ^{-n}$$

$$= Z^{k}X(Z) - \sum_{n=0}^{k-1} x(n)TZ^{-(n-k)}$$

#### 4. Convolution-Summation:

The input and output signals of a digital filter are related to each other through the convolution-summation property. Referring to fig. 2.4 and using this property, we have

$$y(n)T = g(0)Tx(n)T+g(1)Tx(n-1)T+g(2)Tx(n-2)T+...$$

where g(i)T is the weighting sequence of the filter. Using eqn. 2.3.1, we obtain

$$Y(Z) = \sum_{n=0}^{\infty} [g(0)Tx(n)T+g(1)Tx(n-1)T + g(2)Tx(n-2)T + ...] Z^{-n}$$

therefore

$$Y(Z) = g(0)TX(Z) + g(1)TZ^{-1}X(Z) + g(2)TZ^{-2}X(Z) + ...$$

=  $[g(0)T + g(1)TZ^{-1} + g(2)TZ^{-2} + ...]X(Z)$

therefore

$$Y(Z) = G(Z) X(Z)$$

$$G(Z) = Y(Z)/X(Z)$$

The ratio Y(Z)/X(Z) (equal to G(Z)), is commonly referred to as the pulse transfer function of the digital filter.

#### 5. Summation:

Suppose that

$$g(n)T = \sum_{i=0}^{n} x(i)T$$

for  $n = 0, 1, 2, ...$

and using eqn. 2.3.1 we obtain

$$X(Z) = \sum_{n=0}^{\infty} [g(n)T-g(n-1)]T Z^{-n}$$

$$= G(Z)-Z^{-1}G(Z)$$

$$= G(Z) \underline{[(Z-1)/Z]}$$

therefore

$$G(Z) = \begin{bmatrix} Z/(Z-1) \end{bmatrix} X(Z)$$

for further detailes of the Z-transform refer to references (4,6).

#### 2.5 Relation Between the Z-Domain and S-Domain

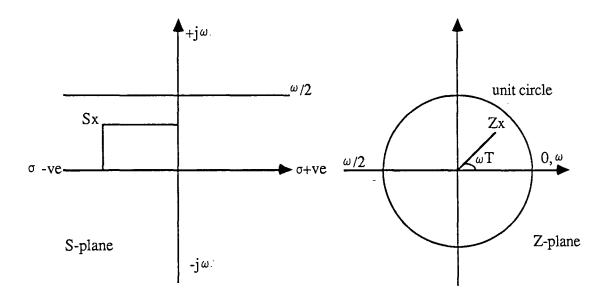

In order to gain some insight into the relation between S-plane and Z-plane poles and zeros, it is important to investigate what happens to the complex variable Z when S has certain typical values. The process by which a point in one plane is transfered to the other plane is called mapping, and that mapping process is governed by the law:

$$S = \sigma + j\omega$$

and  $Z = e^{ST} = e^{(\sigma + j\omega)T}$

=  $e^{\sigma T} \cdot e^{j\omega T}$

where T is the period of the sampling process.

It is obvious that for any constant value of  $\sigma$ , Z is a function of  $\omega$  and is repetitive in form with a period equals  $2\pi/T$  radians/sec. The previous value of Z is represented by a vector of length  $e^{\sigma T}$  which makes an angle  $\omega T$  radians with the positive real axis. As shown in fig. 2.5 any point  $S_x$  in the S-plane corresponds to just one point  $Z_x$  in the Z-plane. Now referring to table 2.1, it is seen that the imaginary axis in the S-plane transforms (maps) to the circumference of the unit circle in the Z-plane.

From fig. 2.5, it can be seen that if:

- (1)  $\sigma < 0$  Z < 1, the left-hand half of the S-plane transforms into the inside the unit circle in the Z-plane.

- (2)  $\sigma = 0 \longrightarrow |Z| = 1$ , every point on the imaginary axis (j $\omega$ ) in the

Fig. 2.5 S-plane to Z-plane transformation

Fig. 2.6 Block diagram representation for the state variable description

| σ=0, ω <sub>S</sub> = 2π/T |                 |  |

|----------------------------|-----------------|--|

| jω                         | Z=1 <i>L</i> ωT |  |

| o                          | 1 L0°           |  |

| ω <sub>S</sub> /8 ·        | 1 L45°          |  |

| ω <sub>s</sub> ,4          | 1               |  |

| 3ω <sub>S</sub> /8         | 1 <i>L</i> 135° |  |

| ω <sub>S</sub> /2          | 1 <i>L</i> 180° |  |

| 5ω <sub>s</sub> /8         | 1 <i>L</i> 225° |  |

| 3ω <sub>s</sub> /4         | 1 <i>L</i> 270° |  |

| 7ω <sub>S</sub> /8         | 1 L315°         |  |

| $\omega_{\mathbf{S}}$      | 1 L360°         |  |

|                            |                 |  |

Table 2.1

S-plane is mapped into a point on the unit circle in the Z-plane.

(3)  $\sigma > 0 \longrightarrow |Z| > 1$ , the right-hand half of the S-plane can be mapped onto the outside of the unit circle in the Z-plane (4.44).

#### 2.6 The Inverse Z-Transform

The inversion of the Z-transform is conducted to determine the time-domain description of the digita filter from the corresponding frequency-domain description (4).

The inverse Z-transform relation is expressed as

$$x(n)T = (1/2\pi j) \oint_C X(Z)Z^{n-1} dZ$$

2.6.1

where c is the counterclockwise contour that encircles the origin. For rational Z-transform contours, integrals of the form of eqn. 2.6.1 are often conveniently evaluated using the residue theorem, i.e.

$x(n)T = \sum \text{residue of } [X(Z)Z^{n-1}] \text{at the poles incide c} 2.6.2$  where

$$\label{eq:residue} residue= (1/(m-1)!) \lim_{Z\to X} \left\{ (d^{m-1}/dZ^{m-1}) \left[ (Z-x)^m X(Z)Z^{n-1}) \right] \right\} \ \ 2.6.3$$

for a pole of order m at z=x.

Another technique for recovering the sampled time function corresponding to a given Z-transform is simply to expand the Z-transform into a power series by ordinary long division.

A third method of determining the inverse Z-transform is to expand X(Z) into partial fractions, and then refer directly to a table of Z-transform pairs to obtain the corresponding Z-inverse, x(n)T, of each partial fraction (4,6).

## 2.7 The Difference Equation and the Digital Transfer Function

It has been established in section 2.3, that a digital filter may be represented by a linear difference equation, which is the counterpart of the differential equation in the linear continuous system. Furthermore, it has been established that the pulse transfer function of the filter is a ratio function of Z expressed as Y(Z)/X(Z), where Y(Z) and X(Z) are the Z-transforms of the set y(n)T and x(n)T respectively.

In general, the pulse transfer function of the digital filter G(Z) is given by

$$G(Z) = \underbrace{a_0 + a_1 Z^{-1} + a_2 Z^{-2} + \dots + a_N Z^{-N}}_{1 + b_1 Z^{-1} + b_2 Z^{-2} + \dots + b_M Z^{-M}} = \underbrace{Y(Z)}_{X(Z)}$$

2.7.1

$$G(Z) = \frac{\sum_{i=0}^{N} a_i Z^{-i}}{1 + \sum_{i=1}^{N} b_i Z^{-i}}$$

2.7.2

where  $\mathbf{a}_{i}$  and  $\mathbf{b}_{i}$  represent the filter coefficients.

The pulse transfer function representation of eqn. 2.7.2 leads to a useful method for determining the filter's response to various input signals. This can be achieved by obtaining X(Z) and G(Z) and multiplying them together to give the Z-transform of the filter output response Y(Z). Finally the inverse Z-transform of Y(Z) is obtained to yield y(n)T. So it is obvious that the first stage in the design of a digital filter is to find the coefficients of the transfer function.

Now from eqn. 2.7.1, we obtain

$$X(Z) \left[ a_0 + a_1 Z^{-1} + a_2 Z^{-2} + ... + a_N Z^{-N} \right] = Y(Z) \left[ 1 + b_1 Z^{-1} + b_2 Z^{-2} + ... + b_M Z^{-M} \right]$$

and since  $Z^{-k}$  represents a time delay of k sampling periods, then it follows that the input and output sampled-data signals are related by a linear difference equation which can be expressed as

$$\sum_{i=0}^{N} a_i x(n-i) T = \sum_{i=1}^{M} b_i y(n-i) T$$

2.7.3

since  $b_0 = 1$ , therefore

$$y(n)T = a_0x(n)T + a_1x(n-1)T + ... + a_Nx(n-N)T$$

$$-(b_1Y(n-1)T + b_2y(n-2)T + ... + b_My(n-M)T)$$

$$= \sum_{i=0}^{N} a_i x(n-i)T - \sum_{i=1}^{M} b_iy(n-i)T$$

The linear difference equation is the basic element in the concept of the digital filter, so the implementation of any digital filter should satisfy its difference equation. For further details refer to (4,42,45).

### 2.8 State Variable Analysis

#### 2.8.1 Introduction

In the previous sections we investigated a way of describing the input-output relation of a system by a linear difference equation and transform domain description (Z-transform of the linear system in a discrete time system). This section discusses another method of describing the input-output relation of systems, namely the state space or state variable description. Generally, the state of a system at time t is that set of variables required at time t so that, given the inputs to the system for  $\tau$ >t, one can exactly specify the future behaviour of the system for  $\tau$ >t. So the state of a system may be represented by the values of a number of variables representing the state variables. A system might have an infinite or only a finite number of states and it can be applied to

both continuous and discrete time systems. In this section we will discuss the state space description of the behaviour of discrete time system. Many textbooks and articles grant general insight to this powerful technique for system analysis and design (46,47,48,49,50,51).

## 2.8.2 State Space Description for Discrete Time System

Let the variables  $q_1(n)$ ,  $q_2(n)$ , ...,  $q_r(n)$  represent the state variables of a discrete system. At any instant n, the value of the output of the system, y(n), can be computed from the values of the state variables at that instant and the values of the inputs x(n), x(n+1), ... For the discrete time system, the normal form of the difference equation may be expressed in matrix form as:

$$q(n+1) = A q(n) + B x(n)$$

2.8.1

and the corresponding state output equation is

$$\underline{y}(n) = \underline{C} q(n) + \underline{D} \underline{x}(n)$$

2.8.2

where q(n) is the state vector of the system of n state variables  $\underline{x}(n)$  is the input vector.

y(n) is the output vector.

A is the matrix of coefficients of the state variables.

B is the input signals coefficients matrix.

C is the matrix of the output signals coefficients.

$\underline{D}$  is the matrix of the input signals terms contained in the output equation.

Eqns. 2.8.1 and 2.8.2 are referred to as the state equations, and a description of a system behaviour by these equations is called the state space description.

Consider, for example, a discrete time system represented by the difference equation

$$y(n) + b_1y(n-1) + ... + b_ky(n-k) = a_0x(n)$$

2.8.3

This equation could be represented by a block diagram as illustrated in fig. 2.6. Because eqn. 2.8.3 is an n<sup>th</sup> order difference equation, therefore, n state variables should be specified to describe the system (47). Defining the state variables as the outputs of delay elements, we obtain

$$q_1(n) = y(n-k)$$

$q_2(n) = y(n-k+1)$

...

$q_k(n) = y(n-1)$

referring to fig. 2.6, each state variable at time (n+1) could be written in terms of those at time n as

$$q_{1}(n+1) = q_{2}(n)$$

$$q_{2}(n+1) = q_{3}(n)$$

$$\vdots$$

$$q_{k-1}(n+1) = q_{k}(n)$$

$$q_{k}(n+1) = y(n) = a_{0}x(n) - b_{k}q_{1}(n) - \dots - b_{1}q_{k}(n)$$

To obtain the state variable representation in matrix form. eqn. 2.8.5 is rewritten as

$$\begin{bmatrix} q_{1}(n+1) \\ q_{2}(n+1) \\ \vdots \\ q_{k}(n+1) \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ \vdots \\ 0 & 0 & 0 & 1 \\ -b_{k} & -b_{k-1} & -b_{k-2} & \dots & -b_{1} \end{bmatrix} \begin{bmatrix} q_{1}(n) \\ q_{2}(n) \\ \vdots \\ q_{k}(n) \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ \vdots \\ 0 \\ a_{0} \end{bmatrix} x(n)$$

and \_

$$y(n) = \begin{bmatrix} -b_k & -b_{k-1} & \cdots & -b_1 \end{bmatrix} \begin{bmatrix} q_1(n) \\ q_2(n) \\ \vdots \\ q_k(n) \end{bmatrix} + \begin{bmatrix} a_0 \end{bmatrix} x(n)$$

The state equation can be solved at any time n by solving for the succeeding values of the state variables in terms of the preceding values and the input sequence. Starting with the state at time zero, the q(n) can be computed in a step-by-step manner as follows (48):

$$q(1) = \underline{A}q(0) + \underline{B}x(0)$$

$$q(2) = \underline{A}q(1) + \underline{B}x(1)$$

$$= \underline{A} \left[ \underline{A}q(0) + \underline{B}x(0) \right] + \underline{B}x(1)$$

$$= \underline{A}^{2}q(0) + \underline{A}\underline{B}x(0) + \underline{B}x(1)$$

$$q(3) = \underline{A}q(2) + \underline{B}x(2)$$

$$= \underline{A}^{3}q(0) + \underline{A}^{2}\underline{B}x(0) + \underline{A}\underline{B}x(1) + \underline{B}x(2)$$

by continuing this procedure we get a general expression as follows:

$$\underline{q}(n) = \underline{A}^{n}q(0) + \sum_{m=0}^{n-1} \underline{A}^{n-1-m} \underline{B}\underline{x}(m)$$

It is obvious from the previous equation that the behaviour of such

a state system depends on successive powers of the matrix  $\underline{A}$ . This equation is referred to as a discrete-transition equation of the system. The system output in that case can be written as

$$\underline{y}(n) = \underline{CA}^{n}q(0) + \underline{C}\sum_{m=0}^{n-1}\underline{A}^{n-1-m}\underline{Bx}(m) + \underline{Dx}(n)$$

The matrix  $\underline{A}^n$  is referred to as the discrete state-transition matrix.

## 2.9 Frequency Response of Digital Filters

The frequency response can be determined geometrically from values of the transfer function of the filters. However, for discrete-time systems, the frequency response is usually determined by evaluating the transfer function G(z) around the unit circle in the Z-plane, where for continuous-time systems, the frequency response is obtained by evaluating the transfer function along the imaginary axis  $j\omega$  (4).

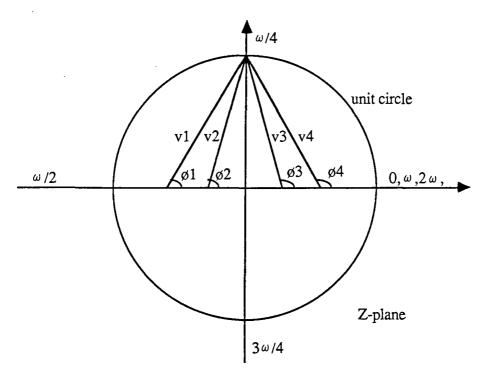

To determine the amplitude and phase characteristics, the poles and zeros of the digital transfer function are plotted in the Z-plane, as shown in fig. 2.7. The amplitude response  $|G(e^{j\omega T})|$  may be expressed as

$$|G(e^{j\omega T})| = \prod_{i=1}^{r} \text{ vector magnitudes from the } i^{th} \text{ zero to the point}$$

$$= \lim_{i=1}^{m} \text{ vector magnitudes from the } k^{th} \text{ pole to the point}$$

$$= \lim_{k=1}^{m} \text{ vector magnitudes from the } k^{th} \text{ pole to the point}$$

and the phase response  $\angle G(e^{j\omega T})$  may be obtained as

For example, let  $v_2$  ,  $v_3$  be the zero vectors and

Fig. 2.7 Z-Plane pole-zero configuration

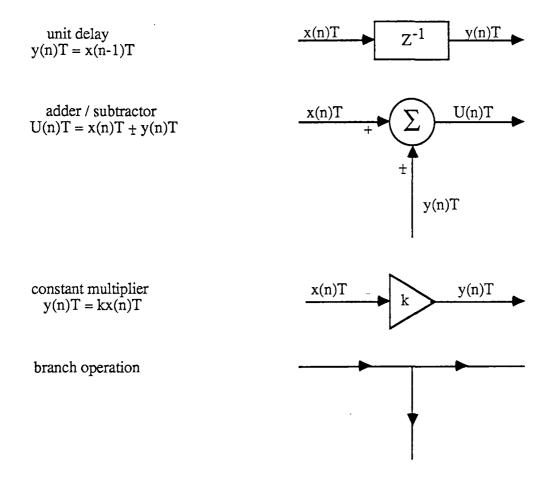

Fig. 2.8 The recommended terminology used in digital filtering

$v_1$  ,  $v_4$  the pole vectors

therefore

$$|G(e^{j\omega T})| = \frac{|v_2| \cdot |v_3|}{|v_1| \cdot |v_4|}$$

let  $\theta_2$  ,  $\theta_3$  be the zero angles and

$\theta_1$  ,  $\theta_4$  be the pole angles

therefor

$$\mathcal{L}^{G(e^{j\omega T})} = (\theta_2 + \theta_3) - (\theta_1 + \theta_4)$$

The above relationships for  $|G(e^{j\omega T})|$  and  $\angle G(e^{j\omega T})$  are point by point relationships only, in other words, vectors must be drawn on the Z-plane from the zeros and poles to every point on the axis as shown in fig. 2.7, for which the amplitude and phase response is required.

The frequency response can also be determined by substituting  $e^{j\omega T}$  for Z in G(Z), and computing directly  $|G(e^{j\omega T})|$  and  $\angle G(e^{j\omega T})$  (4).

## 2.10 Digital Filter Design Techniques

Digital filters can be classified into two categories; finite impulse response (FIR) or non-recursive digital filters and infinite impulse response (IIR) or recursive digital filters. The term non-recursive means that the output of the filter is computed using the present and previous inputs only, i.e.  $b_i=0$ . On the other hand, the term recursive means that the output of the digital filter is computed using the present input and the previous inputs and outputs, i.e.  $b_i \neq 0$  (4,45).

It has been mentioned before that the main problem in digital filter design is the determination of the coefficients to obtain

its difference equation. These coefficients can be determined by suitable approximation or truncation of the impulse response functions in either the time or frequency domain.

There are at least two different frequency domain approaches in designing the IIR filters (4,52):

- (1) the direct approach which is concerned with the Z-plane representation of the digital filter, where the coefficients can be determined using some computational algorithm directly from the filter specifications. This direct approach may be used in the designing of frequency sampling filters and those based on squared magnitude functions.

- (2) the indirect approach in which the coefficients of the digital filter are determined by transfering the frequency response of the analogue filter G(S) via an appropriate S-plane mapping to a corresponding digital filter transfer function G(Z). The mapping process can be one of the following processes:

- (a) Z-transform (impulse-invariant design method).

- (b) Bilinear Z-transform.

- (c) Matched Z-transform.

FIR filters (52) have linear phase characteristics and may be designed by a number of methods, of which the following are considered:

- (1) frequency sampling, where the coefficients may be determined using the discrete Fourier transform (DFT) which is equivalent to a least-square approximation.

- (2) the window methods (weighting functions), used for

functions containing discontinuities. Much work has been devoted to developing suitable window methods. There are many useful window functions which may used in the design of non-recursive digital filters (52) such as:

- (a) Hamming window.

- (b) Blackman window.

- (c) Hanning window, for detail refer to (4,7).

- (3) Optimal design methods, these are the most accurate (and complex) ways of designing FIR filters.

Forsythe (53) has developed a new method for computing the coefficients of a digital filter, in which the poles of the transfer function G(S) in the S-plane are mapped directly into the corresponding Z-plane, but the positions of the Z-plane zeros are derived by a more complex process using a Taylor series expansion. This method has the capability of approaching the filter response's theoritical limit unlike any other.

#### 2.11 Realization of Digital Filters

## 2.11.1 The Realization of Recursive Digital Filters

The terminology shown in fig. 2.8 is suggested by Rabiner (54) for digital filtering. Referring to the linear difference equation (eqn.2.7.4) given in section (2.7). It is obvious that the digital filters are composed of circuits which perform three fundamental operations of storage, multiplication and addition (5). There are many network realizations (45) of IIR filters. One consideration that should be taken into account in the choice between these different realizations is the number of operations to be performed and their precision. That is, networks with the fewest constant

multipliers and the fewest delay branches are often the most desirable. The recursive difference equation may be realized in the following forms:

#### 2.11.1.1 Direct Form I

Since the difference equation (eqn. 2.7.4) can be written directly by inspection of the transfer function (in the form of eqn. 2.7.1), the network corresponding to eqn. 2.7.4 is called the direct form of the system by (eqn. 2.7.1).

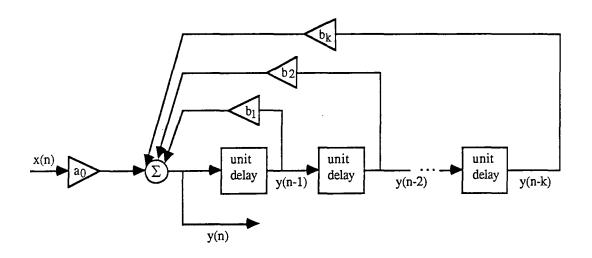

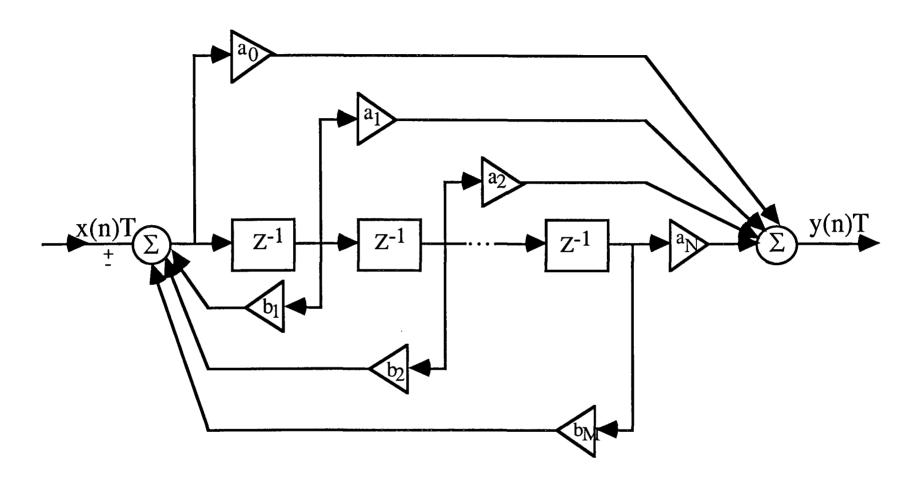

The realization structure shown in fig. 2.9 represents a direct form implementation of eqn. 2.7.4, and it is seen that a  $k^{th}$  order filter requires 2k delay operations. The polynomial coefficients are the multiplier values in the feed-forward and feed-back paths (4,6,45).

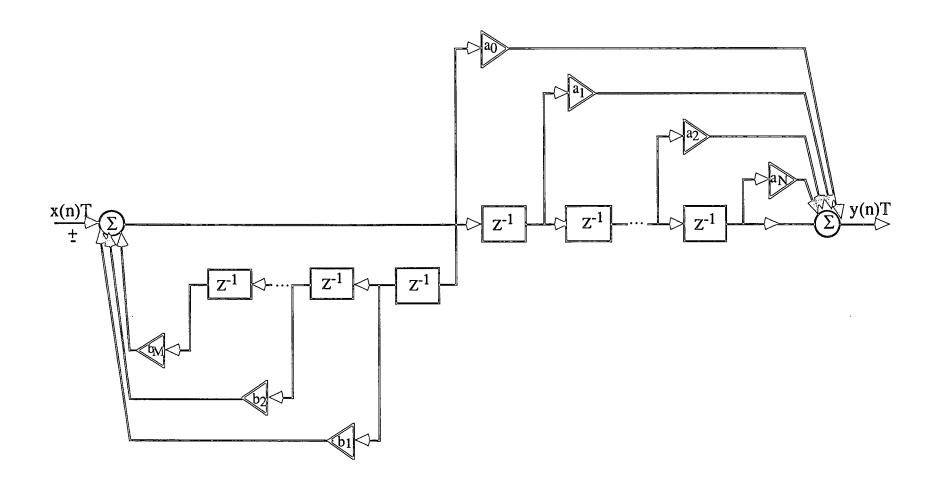

#### 2.11.1.2 The Direct Form II or Canonic Form

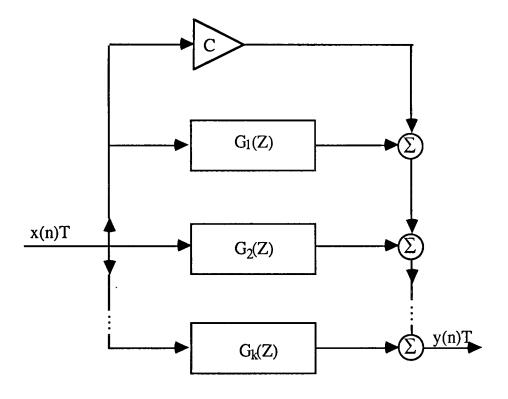

In the canonic form, the feed-forward and feed-back paths share the same delays. In that case the filter is realized more concisely saving a number of delays so k delay operations are required as shown in fig. 2.10 (44,45).

As an example Hwang (55) has presented a new method of digital network realization. A total of 14 regular canonic forms have been obtained.

Hence the total filtering operation is often subdivided into many different processes which are combined to give the required overall transfer function. This subdivision may be achieved in two basic forms (45).

Fig. 2.9 Block diagram representation of the direct form  ${\mathbb I}$

Fig. 2.10 Block diagram representation of direct form II for an n<sup>th</sup> order filter

#### 2.11.2.3 Parallel Form

To realize a digital filter in parallel form the pulse transfer function G(Z) is expressed as a sum using a partial fraction expansion.

$$G(Z) = C + \sum_{i=1}^{k} G_{i}(Z)$$

where each  $G_i(Z)$  is a first or second order transfer function. The filter can then be realized via a parallel connection of lower order filters in either of the direct forms as depicted in fig.2.11 (8,55).

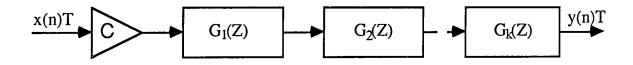

#### 2.11.2.4 Cascade Form

To realize a digital filter in a cascade form, the pulse transfer function G(Z) is factorised to the form

$$G(Z) = C \prod_{i=1}^{k} G_i(Z)$$

In this form the output y(n)T is the product of the outputs of several subfilters. Similarly it can be realized via the cascaded connection of lower order filters in either of the direct forms as depicted in fig. 2.12 (8,55).

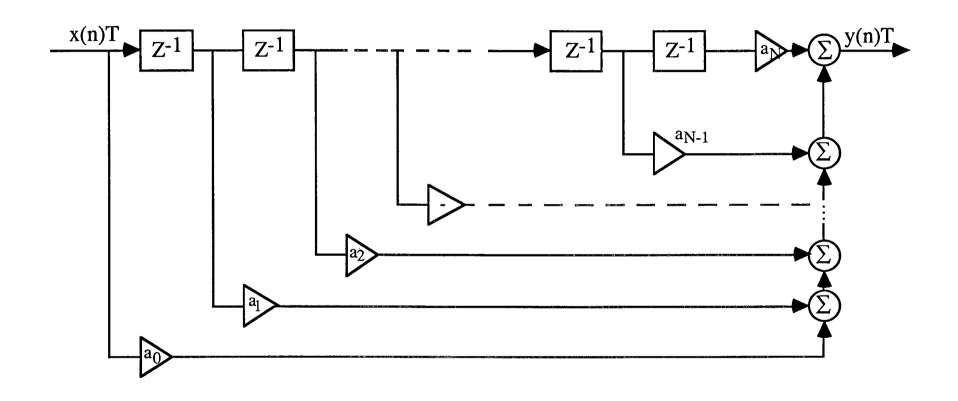

## 2.11.2 Realization of Non-Recursive Digital Filters

For a non-recursive digital filter, the constant coefficients  $b_i$ =0, and the transfer function reduces to the polynomial Z<sup>-1</sup>. Therefore, the current output only depends on the present and previous input samples, and the filter can be realized as in fig. 2.13 (8).

## 2.12 Frequency transformation for digital filters

Frequency transformation is a method of implementing a desired

Fig. 2.11 Block diagram representation of the parallel form

Fig. 2.12 Block diagram representation of the cascade form

Fig. 2.13 Block diagram representation of non-recursive digital filter

filter from a given normalized filter. A normalized low pass digital filter is one in which the cutoff frequency is a quarter of the sampling frequency. The transformation may be accomplished by changing the transfer function of a given filter to the desired filter. These transformations generally preserve the normalized filter magnitude response (attenuation); other characteristics of it are often retained (8).

Constantinides (56,57) has developed a theory of transforming a given low-pass pulse transfer function into (a) high pass, (b) band-pass and band-stop on the Z-plane without reference to the frequency transformations for an analogue filter.

Table 2.2 below lists the frequency transformation from a normalized low-pass filter to other types of filters at any cutoff frequency:

| Filter   | Substitute for Z <sup>-1</sup>            | Cutoff frequency                                      | Center frequency  |

|----------|-------------------------------------------|-------------------------------------------------------|-------------------|

| highpass | -Z-1                                      | <sup>ω</sup> cl=ωs−ωch                                | ω <sub>S</sub> /2 |

| bandpass | $\frac{-Z^{-1}(Z^{-1}-\alpha)}{1-Z^{-1}}$ | $\omega_{ m cl}$ = $\omega_{ m s}$ - $\omega_{ m ch}$ | ωO                |

| bandstop | $\frac{Z^{-1}(Z^{-1}-\alpha)}{1-Z^{-1}}$  | $\omega_{\text{cl}} = s^{-(\omega_2 - \omega_1)}$     | $\omega_0$        |

Table 2.2

where  $\alpha = \cos(2 \omega_0/\omega_s)$ , and

$\omega_{\mbox{cl}}$  is the cutoff frequency of the normalized low-pass filter.

$\omega_{\mbox{\footnotesize{ch}}}$  is the cutoff frequency of high-pass filter.

$\omega_0$  is the center frequency.

$\omega_1$  and  $\omega_2$  are the lower and upper cutoff frequencies respectively.

#### 2.13 Quantization Effects

When a digital filter is implemented on a general or special purpose computer, errors due to the limit of the word length available, which represents the number in the digital computer, become critical and may lead to a filter that does not satisfy its original specifications (58). Here the quantization has been defined as the approximation or the replacement of the signal value by the nearest of a set of quantization levels differing by steps of the size  $Q = 1/2^{W-1}$ , where w is the word length. The effect of that quantization is to superimpose an error signal e(t), called the quantization noise, on the original signal. So the input to the digital filter is considered to be the sum of two signals, namely, a noiseless input x(n)T and a noise input e(n)T. That is, the quantized input signal is expressed as:

$$x(n)T | q = x(n)T + e(n)T$$

and the amplitude of the error signal is extended for -Q/2 to Q/2 (4,58).

The quantization errors normally take the form:

- (I) quantization errors due to round-off and truncation in arithmetic operations.

- (II) quantization errors due to the inaccuracy of the input signal since it is represented by a set of discrete values.

- (III) quantization errors due to representing the coefficeints by a finite number of bits.

- (IV) limit cycle oscillations; and

- (V) overflow oscillations.

#### 2.13.1 Round-Off Noise

To implement a digital filter, the signal must be multiplied by a constant coefficients. The result of this multiplication must, in general, be approximated to a number of bits that can be stored properly. This approximation (round-off) can be rounding or truncation (59). The effect of truncation or rounding depends on whether fixed-point or floating-point arithmetic operations are used and how negative numbers are represented. If the quantization step is assumed to be constant for all signal amplitudes, in the other words if noise samples are assumed to be uniformly distributed, then the variance of the input noise is simply  $Q^2/12$ ,  $Q^2/3$  for rounding and truncation respectively (60).

Mitra et al. (60) have developed a simple method of calculating a steady state value for the output noise variance of a digital filter as a result of the input quantization noise.

Liu (61) has analysed the round-off noise for each form of digital filter realization showing that the accuracy of a digital filter depends on two important factors; the form of realization and the type of arithmetic used. For fixed point arithmetic, the mean square value of the output noise variance is expressed as

$$(1/2 \pi j) \oint \Phi_{ee}(Z) dZ/Z$$

where  $\Phi_{ee}(\mathbf{Z})$  is the power spectral density of the round-off noise for each form of realization.

According to the studies in (61) for a fixed-point word length, realizing the high-order filter with either parallel or cascade form is considerably more accurate than the direct

realization of the same filter. Thus first and second order filters should be used as basic building blocks for higher order filters.

It has been shown that the accuracy of a digital filter design depends on the implementation method, but to achieve still better accuracy, some other advantages need to be sacrified. Barnes has (62) shown that the direct form structures are computationally efficient, but they have high round-off noise gain for narrow-band filters, high coefficient quantization sensitivity, and show some overflow noise. On the other hand optimal state space structures have low round-off gain noise, possess near-minimal coefficient sensitivity, and are free from the overflow or limit cycles independent of the arithmetic convergence. However, the last structure requires three more multipliers per second order section than the direct form. For further details about these structures refer to (62,63).

## 2.13.2 Input Quantization Noise

In the implementation of a practical digital filter system when a signal is converted from a continuous to a discrete form by an ADC, which normally produces a fixed-point binary number representation of the input samples (4), the digital output has a finite word length which implies a difference between the actual value and the fixed-point representation. This is commonly referred to as white noise (44).

The mean square value used in assessing this noise in the ADC is  $\sigma^2 = Q^2/12$  and the mean square value of the error at the output due to input quantization is expressed as

=

$$(Q^2/12)(1/2\pi j) \oint G(Z) G^*(1/Z) dZ$$

#### 2.13.3 Coefficients Rounding Effect

Since the coefficients of the difference equation represent the digital filter, inaccuracy of the coefficients can cause degeneration in the frequency response of the filter. Specifically, changes in the coefficients values give rise to migration of the poles and zeros of the filter, and if any of the poles happen to migrate outside the unit circle in the Z-plane, then the filter, which with accurate coefficients would have been stable, becomes unstable (64).

Knowled and Olcayto (65) have shown that the quantization of a digital filter's coefficients can be represented by a (stray) transfer function in parallel with a corresponding ideal filter. They have also given a measure of the degeneration in filter performance due to coefficient errors by the following statistical mean-squre convergence criterion

$$\sigma_{\mathbf{W}}^{2} = (T/2\pi) \int_{0}^{2\pi/T} |G^{*}(j\omega) - G_{\infty}^{*}(j\omega)|^{2} d\omega$$

where  $G^*(j_\omega)$  and  $G^*_\omega(j_\omega)$  represent the frequency response of the actual and ideal filter, and T is the sampling period.

It is contended that loss of stability in a realization will occur only after the deviation between the actual and ideal frequency response has become intolerable.

To select the minimum word-length, the expression

$$3\sqrt{\sigma_{\mathbf{w}}^2}$$

< | Acceptable Gain Fluctuation |

must be satisfied, provided that the output noise due to data

quantization and multiplicative round off errors is also acceptable with this word length.

Liu (61) has indicated that the effect of coefficients inaccuracy is more pronounced for a high order filter when it is realized in the direct form than when it is realized in the parallel or cascade form.

## 2.13.4 Limit Cycle Oscillations

Limit cycles are defined to be the autonomous dc or periodic behaviour of a digital filter under zero input conditions, so that with zero input, the output of a recursive digital filter may be non-zero due to the arithmetic rounding or truncation (66).

Munson et al. (67) have used an algorithm to find maximum amplitude limit cycles for many different filters using sign-magnitude and two's complement rounding and truncation with either one or two quantizers.

## 2.13.5 Overflow Oscillations

The fact that overflow oscillations can exist in digital filters is due to the nonlinearity associated with overflow which occurs due to the fixed point arithmetic addition.

The necessary and sufficient condition for the absence of overflow oscillation "nonlinearity" for digital filter with two's complement arithmetic is that:

The Total Input to the Adder | < 1 (68).

### 2.14 Conclusion

This chapter has presented some methods of describing the

input-output relation of the system such as linear difference equation, z-transform and the state space description. The basic concepts of sampled-data signals has also been discussed. We have seen in this chapter that the standard Z-transform is fundamental to a basic understanding of digital filter concepts and its convolution-summation property provides the relationship between the filter's input and output signals. Methods of realizing FIR and IIR digital filters have also been investigated. In fact, IIR filters are generally more economical in execution and computation time and storage requirements compared with FIR filters, but have less stability.

The practical implementation of digital filters is affected by quantization errors due to the finite word length of the input and coefficients. Errors in the coefficients will obviously cause the frequency response of the filter to depart to some extent from that desired, more serious difficulties arise with the IIR filters which may become unstable as a result of its Z-plane poles movement outside the unit circle- in the case of a small change in one or more of its recursive coefficients (or if its recursive multipliers are inaccuratly specified).

#### CHAPTER -3-

#### Adaptive Filtering

#### 3.1 Introduction

The basic concepts involved in FIR adaptive filters have been known for many years. They are versatile signal processing elements which have found numerous applications in situations where only a limited knowledge about the signal and the interference is available.

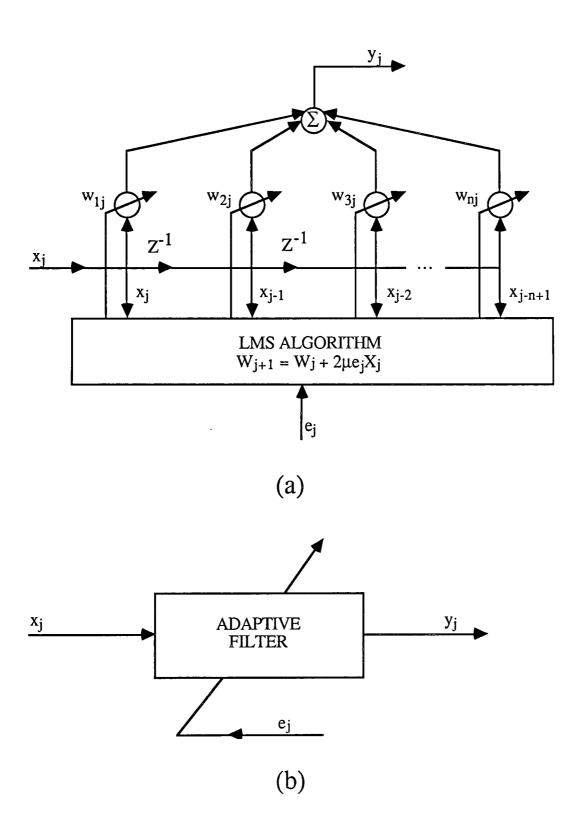

Current real-time adaptive filters are based on Widrow's LMS algorithm, a practical solution to the Widrow-Hoff or (LMS) algorithm. The main advantage of this algorithm is its simple structure which makes it easy to be computed in real time (69).

Adaptive filters can be implemented in the time or frequency domain. Ferrara (70) has shown that the frequency domain implementation of adaptive filters requires less computational time than the time domain implementation. But this is only true for very high order filters, for example the ratio of the number of multipliers required for frequency domain implementation to the time domain implementation is 1.2 for a  $32^{nd}$  order, while it is 0.69 for a  $64^{th}$  order LMS adaptive filter. So for  $n \ge 64$ , where n is the order of the filter, there is some computational saving gained by implementing an LMS adaptive filter in the frequency domain.

Moschner (11,71) and Deivasigamani (72) have proposed the Clipped-LMS algorithm which operates on clipped input data and has convergence properties somewhat inferior to the conventional LMS algorithm and gives a small loss in the performance of the adaptive

filter but is significantly simpler to implement and operates faster.

In this chapter, the basic concept of an adaptive noise canceller that selectively rejects an undesired signal from a composite of signal and noise, and the Wiener solution to the statistical noise cancelling problem are discussed. The LMS algorithm for updating the recursive and non-recursive coefficients will also be described. Quantization noise effects of the variables in the adaptive filter, which minimize the mean square error (MSE) of the filter response, due to the limited-word length and finite precision arithmetic of the digital processor and in particular the coefficient's error due to the value they take when finite precision arithmetic is used, will be investigated.

### 3.2 The Concept of the ANC

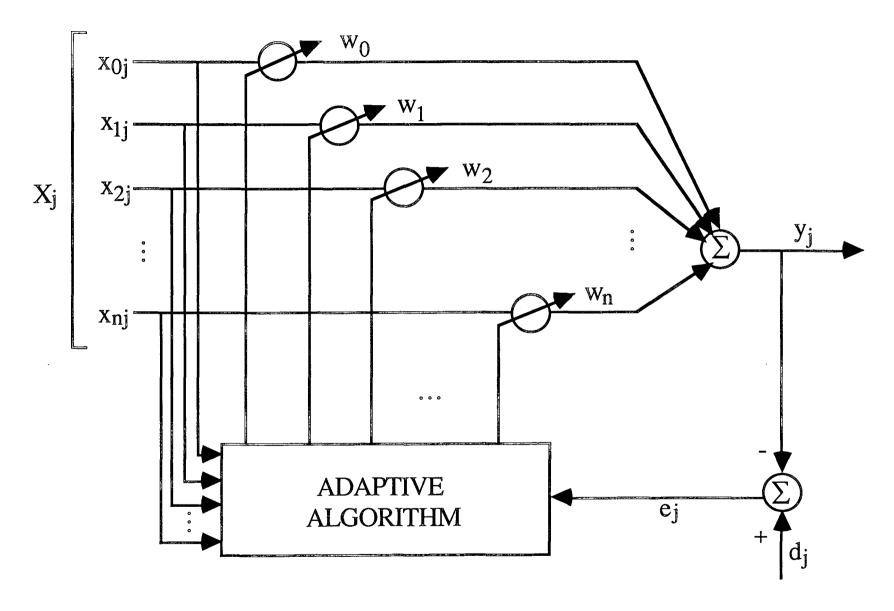

Characteristically an adaptive filter has three main components as shown in fig.3.1:

- (a) The processor, a single input multiple output device, which provides memory for the system. The outputs of the processor are distinct linear functions of present as well as past values of the input.

- (b) A set of adjustable weights which multiply the processor outputs. The sum of the weighted processor outputs is the output of the adaptive filter.

- (c) Some means to compute new weight values according to the adaptive algorithm in use and means by which the weights can be updated (10).

Fig. 3.1 Digital adaptive filter

Fig. 3.2 The adaptive noise cancelling concept

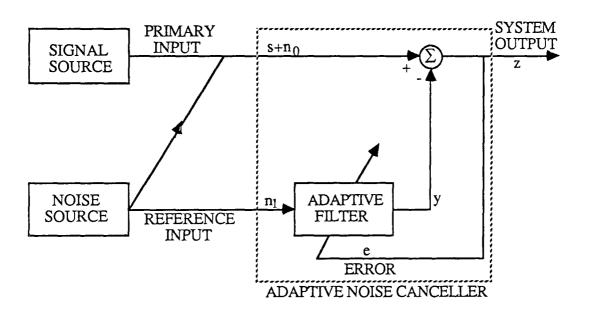

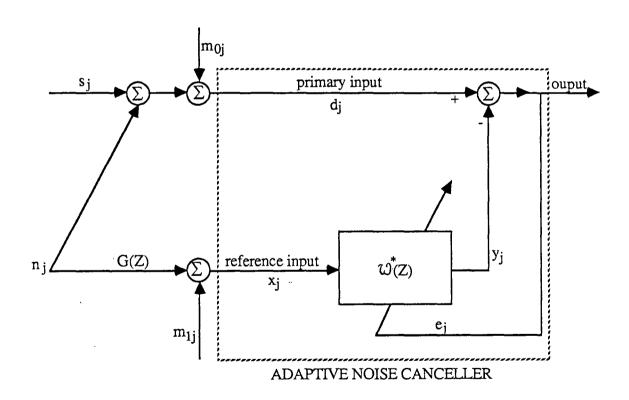

Fig. 3.2 illustrates the basic priciples of adaptive noise cancelling. The input to the adaptive filter is a noise signal  $n_1$  that is highly correlated in some unknown way with the additive noise (interference)  $n_0$ , but is uncorrelated with the clean signal s. The noise  $n_1$  forms the reference input to the canceller. The combined signal and interference  $s+n_0$  form the primary input to the canceller. The noise  $n_1$  is filtered to produce an output y that is subtracted from the primary input to produce the system output z (11,14,73).

The adaptive filter has the ability to automatically adjust its own impulse response (weights) using an algorithm that responds to an error signal dependent on the filter's output. Thus using a proper adjustment algorithm, the filter can be operated in systems whose characteristics develop with time. In noise cancelling systems, the objective is to produce a system output z that is an estimate of the signal s. This objective is accomplished by feeding the system output back to the adaptive filter and adjusting the filter through an algorithm such as the (LMS) adaptive algorithm, (which will be described in detail in the next sections) to minimize the system output power, this will be explained later (11,12,74).

Assuming that the signal s is uncorrelated with both  $n_0$  and  $n_1$  and that s,  $n_0$ ,  $n_1$  and y are statistically stationary and have zero means, then the system output z is given as:

$$z = s + n_0 - y$$

3.2.1

Squaring eqn. 3.2.1 we obtain

$$z^2 = s^2 + (n_0 - y)^2 + 2s(n_0 - y)$$

3.2.2

Taking the expectation of both sides of eqn. 3.2.2, yields:

$$E[z^{2}] = E[s^{2}] + E[(n_{0} - y)^{2}]$$

$$+2E[s(n_{0} - y)]$$

3.2.3

since the signal s is assumed to be uncorrelated with  $n_0$  and y. Since the signal power  $E[s^2]$  is a fixed quantity, minimizing the output power yields:

min

$$E[z^2] = E[s^2] + min E[(n_0 - y)^2]$$

3.2.4

Thus, when the noise cancelling filter is adjusted so that  $E[z^2]$  is minimized,  $E[(n_0-y)^2]$  is also minimized. The filter output y is then a best square estimate of the primary noise  $n_0$ . Moreover, when  $E[(n_0-y)^2]$  is minimized,  $E[(z-s)^2]$  is also minimized, since from eqn. 3.2.1

$$(z-s) = (n_0-y)$$

3.2.5

Thus, z is a best least-square estimate of the signal s since minimizing the total output power causes the output z to be a best least-square estimate of the signal s. The output z will contain the signal plus noise. From eqn. 3.2.1, the output noise is given by  $(n_0-y)$ . Minimizing the total output power,  $E[z^2]$ , allows one to minimize the output noise power,  $E[(n_0-y)^2]$ . Minimizing the total output power maximizes the output signal-to-noise (SNR) ratio as long as the output signal remains constant.

It is seen from eqn. 3.2.3 that the smallest possible output power is

$$E[z^2] = E[s^2]$$

When this is achieved,

$$E[(n_0-y)^2] = 0$$

Therefore,

$$y=n_0$$

and  $z=s$

In this case, minimizing the output power causes the output signal to be perfectly noise free (11,15).

## 3.3 The LMS Adaptive Filter

The LMS adaptive filter is the basic element of the adaptive noise cancelling system.

## 3.3.1 Adaptive Linear Combiner

The adaptive linear combiner is the basic component, or the most significant portion, of most adaptive filtering and signal processing systems. A set of input signals are weighted and summed to form an output signal as shown in fig 3.3. The input signal vector  $\underline{X}_{i}$  is defined as

$$\underline{x}_{j} \triangleq \begin{bmatrix} x_{0j} \\ x_{1j} \\ \vdots \\ x_{nj} \end{bmatrix}$$

3.3.1

The input signal components are assumed to occur simultaneously on all input lines discretely in time indexed by the subscript j. The weighting coefficients or multiplying factors are not fixed and are adjustable depending on the system. The weight vector  $\underline{W}$  is defined by

Fig. 3.3 The adaptive linear combiner

$$\underline{W} = \begin{bmatrix} w_0 \\ w_1 \\ \vdots \\ w_n \end{bmatrix}$$

3.3.2

Thus at the j<sup>th</sup> instant, the output  $y_j$  is equal to the inner product of  $\underline{X}_j$  and  $\underline{W}$

$$y_{j} = \underline{X}_{j}^{T}\underline{W} = \underline{W}^{T}\underline{X}_{j}$$

3.3.3

where the superscript T denotes matrix transposition. The estimation error output at  $j^{\mathrm{th}}$  time interval  $e_j$  is

$$e_j = d_j - \underline{X}_j^T \underline{W} = d_j - \underline{W}^T \underline{X}_j$$

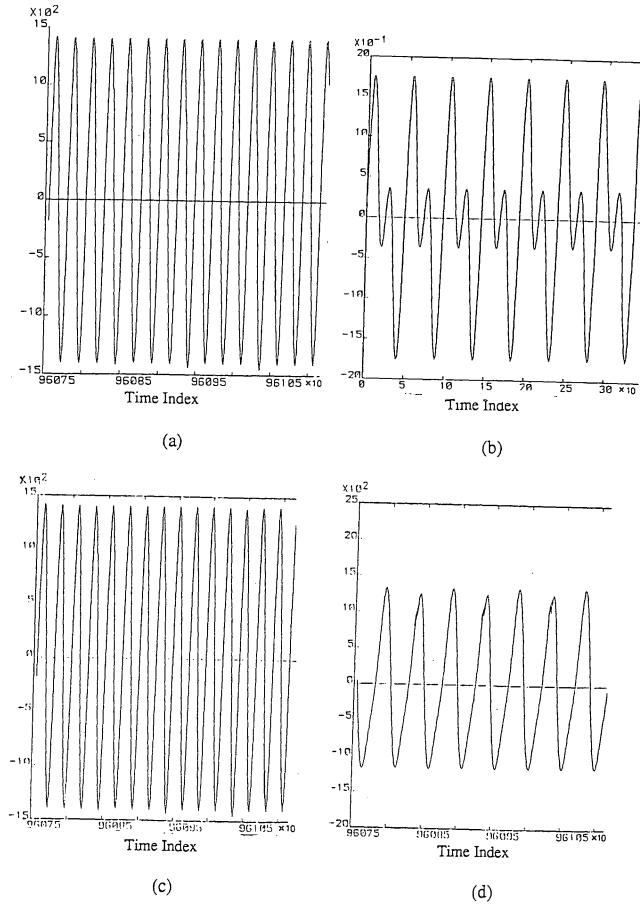

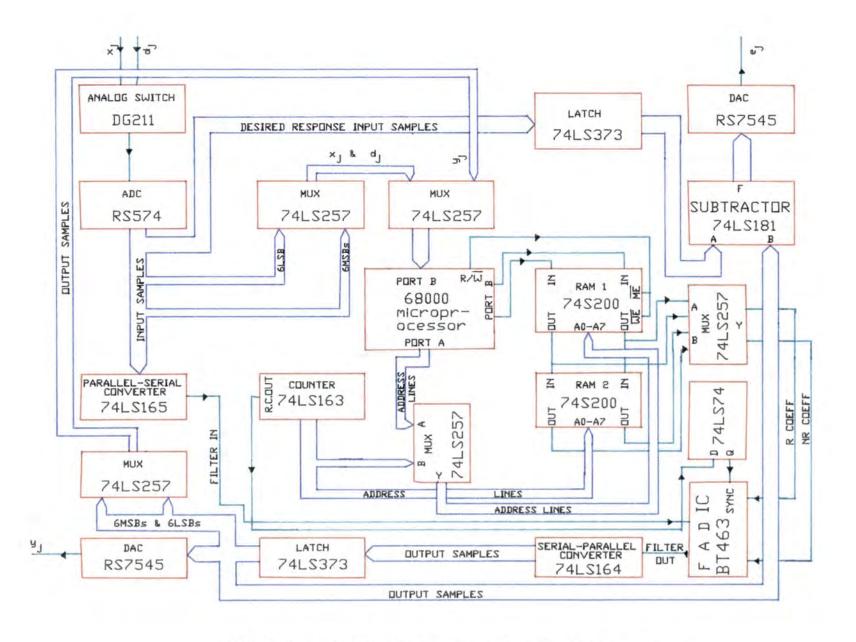

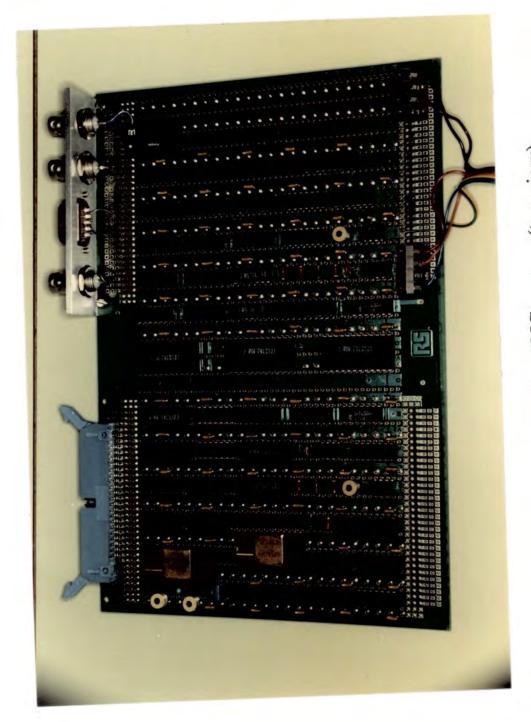

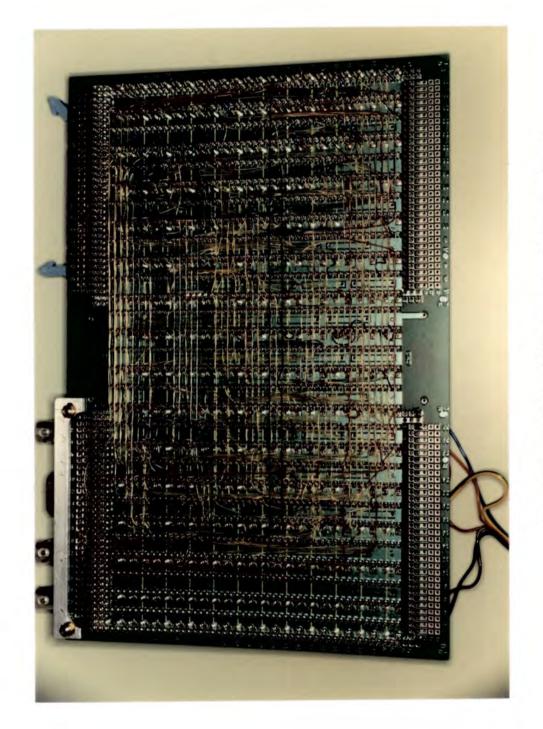

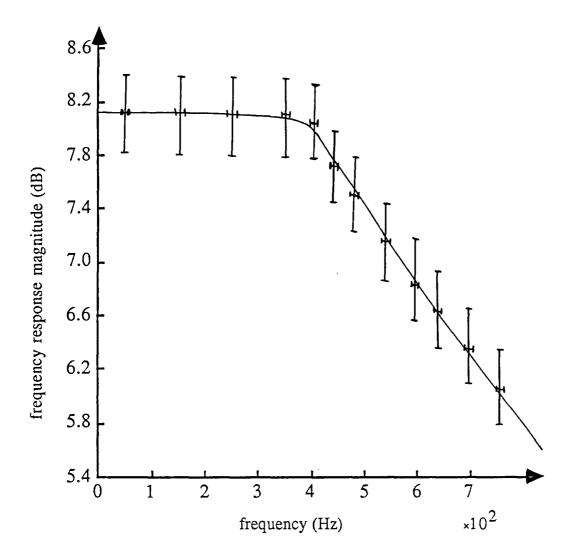

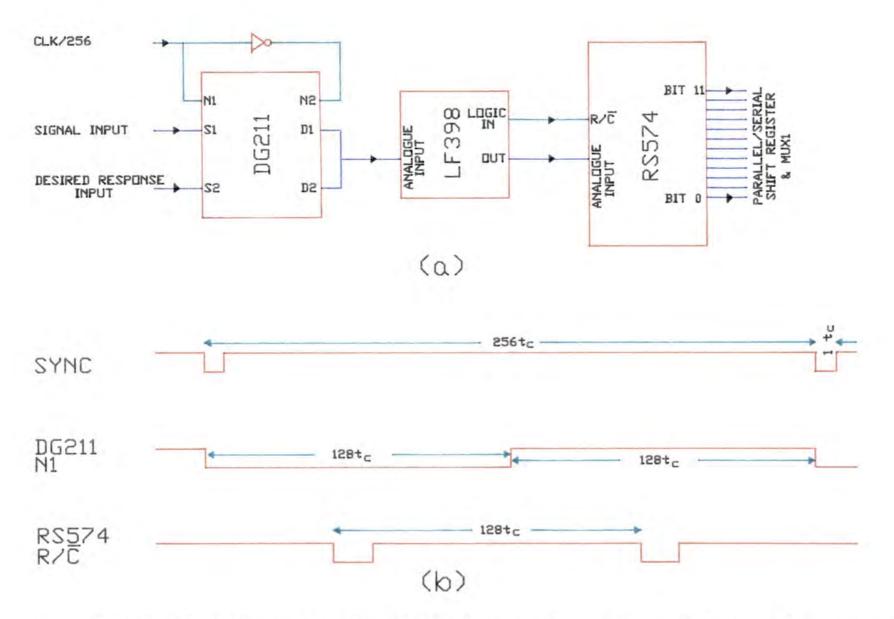

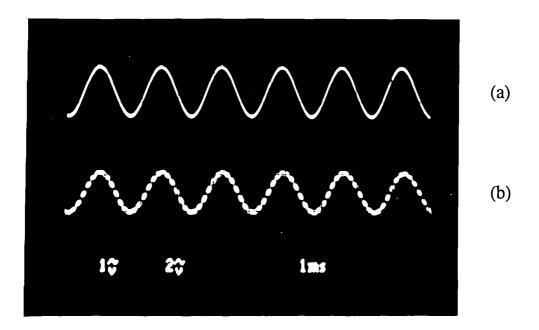

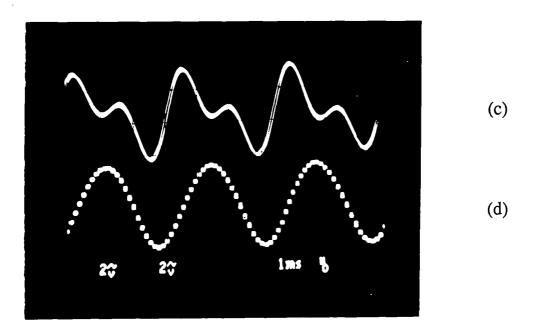

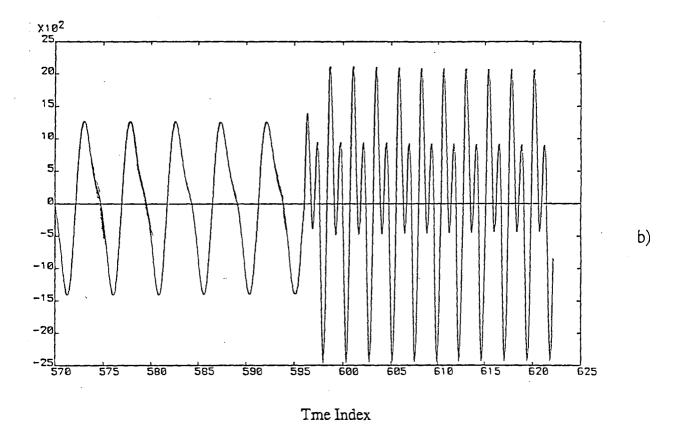

3.3.4